(12)发明专利申请

(10)申请公布号 CN 109473063 A

(43)申请公布日 2019.03.15

(21)申请号 201811489457.8

(22)申请日 2018.12.06

(71)申请人 武汉华星光电半导体显示技术有限公司

地址 430079 湖北省武汉市东湖新技术开发区高新大道666号光谷生物创新园C5栋305室

(72)发明人 李骏

(74)专利代理机构 深圳翼盛智成知识产权事务所(普通合伙) 44300

代理人 黄威

(51)Int.Cl.

G09G 3/3225(2016.01)

权利要求书2页 说明书5页 附图5页

(54)发明名称

像素补偿电路及像素补偿方法

(57)摘要

一种像素补偿电路包含有机发光二极管、第一晶体管、补偿晶体管、存储电容以及第二晶体管。所述有机发光二极管的阴极连接至第一参考电平。所述第一晶体管的源极连接至高电平以及数据信号。所述补偿晶体管的源极与栅极连接至第二参考电平,所述补偿晶体管的漏极连接至所述第一晶体管的漏极,使所述第一晶体管漏极的电位等于或小于所述第二参考电平与所述补偿晶体管阈值电压的总和。所述存储电容设置于所述高电平与所述第一晶体管的栅极之间。利用本发明提供的像素补偿电路可以改善驱动晶体管老化的现象,提升驱动晶体管的均匀度。

1. 一种像素补偿电路,其特征在于,包含:

有机发光二极管,其阴极连接至第一参考电平;

第一晶体管,其源极连接至高电平以及数据信号,其漏极连接至所述有机发光二极管的阳极;

补偿晶体管,其源极与栅极连接至第二参考电平,其漏极连接至所述第一晶体管的漏极,

使所述第一晶体管漏极的电位等于或小于所述第二参考电平与所述补偿晶体管阈值电压的总和;

存储电容,设置于所述高电平与所述第一晶体管的栅极之间;以及

第二晶体管,其栅极连接本级扫描信号,其源极连接至所述第一晶体管的栅极,其漏极连接至所述第一晶体管的漏极与补偿晶体管的漏极;

其中当所述本级扫描信号为低电平时,所述第二晶体管导通,使得所述第一晶体管的栅极与漏极短接。

2. 如权利要求1所述的像素补偿电路,其特征在于,所述像素补偿电路包含第三晶体管,其栅极连接至所述本级扫描信号,其源极连接至所述数据信号,其漏极连接至所述第一晶体管的源极,当所述本级扫描信号为低电平时,所述第三晶体管导通将所述数据信号传送至所述第一晶体管的源极。

3. 如权利要求1所述的像素补偿电路,其特征在于,所述像素补偿电路包含第四晶体管,其栅极连接至上一级扫描信号,其源极连接至所述第一晶体管的栅极,其漏极连接至第三参考电平,当所述上一级扫描信号为低电平时,所述第四晶体管导通将所述第三参考电平传送至所述第一晶体管的栅极,使所述第一晶体管栅极的电平复位至所述第三参考电平。

4. 如权利要求1所述的像素补偿电路,其特征在于,所述像素补偿电路包含第五晶体管及第六晶体管,所述第五晶体管及所述第六晶体管的栅极接入发光信号,所述第五晶体管的源极连接至所述第一晶体管的漏极,所述第五晶体管的漏极连接至所述有机发光二极管的阳极,所述第六晶体管的源极连接至所述高电平,所述第六晶体管的漏极连接至所述第一晶体管的源极,当所述发光信号为低电平时,所述第六晶体管导通将所述高电平传送至所述第一晶体管的源极,使所述有机发光二极管发光。

5. 如权利要求3所述的像素补偿电路,其特征在于,所述像素补偿电路包含第七晶体管,其栅极连接至所述本级扫描信号,当所述本级扫描信号为低电平时,所述第七晶体管导通将所述第三参考电平传送至所述第一晶体管的源极。

6. 一种像素补偿方法,其特征在于,包含:

将有机发光二极管的阴极连接至第一参考电平;

将第一晶体管的源极连接至高电平以及数据信号,将所述第一晶体管的漏极连接至所述有机发光二极管的阳极;

将补偿晶体管的源极与栅极连接至第二参考电平,将补偿晶体管的漏极连接至所述第一晶体管的漏极,使所述第一晶体管漏极的电位等于或小于所述第二参考电平与所述补偿晶体管阈值电压的总和;

将存储电容设置于所述高电平与所述第一晶体管的栅极之间;以及

将第二晶体管的栅极连接本级扫描信号,将所述第二晶体管的源极连接至所述第一晶体管的栅极,将所述第二晶体管的漏极连接至所述第一晶体管的漏极与补偿晶体管的漏极;

其中当所述本级扫描信号为低电平时,所述第二晶体管导通,使得所述第一晶体管的栅极与漏极短接。

7. 如权利要求6所述的像素补偿方法,其特征在于,其包含将第三晶体管的栅极连接至所述本级扫描信号,将所述第三晶体管的源极连接至所述数据信号,将所述第三晶体管的漏极连接至所述第一晶体管的源极,当所述本级扫描信号为低电平时,所述第三晶体管导通将所述数据信号传送至所述第一晶体管的源极。

8. 如权利要求6所述的像素补偿方法,其特征在于,其包含将第四晶体管的栅极连接至上一级扫描信号,将所述第四晶体管的源极连接至所述第一晶体管的栅极,将所述第四晶体管的漏极连接至第三参考电平,当所述上一级扫描信号为低电平时,所述第四晶体管导通将所述第三参考电平传送至所述第一晶体管的栅极,使所述第一晶体管栅极的电平复位至所述第三参考电平。

9. 如权利要求6所述的像素补偿方法,其特征在于,将第五晶体管及第六晶体管的栅极接入发光信号,将所述第五晶体管的源极连接至所述第一晶体管的漏极,将所述第五晶体管的漏极连接至所述有机发光二极管的阳极,将所述第六晶体管的源极连接至所述高电平,将所述第六晶体管的漏极连接至所述第一晶体管的源极,当所述发光信号为低电平时,所述第六晶体管导通将所述高电平传送至所述第一晶体管的源极,使所述有机发光二极管发光。

10. 如权利要求8所述的像素补偿方法,其特征在于,将第七晶体管的栅极连接至所述本级扫描信号,当所述本级扫描信号为低电平时,所述第七晶体管导通将所述第三参考电平传送至所述第一晶体管的源极。

## 像素补偿电路及像素补偿方法

### 技术领域

[0001] 本发明涉及显示技术领域,尤其是涉及像素驱动电路的像素补偿电路。

### 背景技术

[0002] 有机发光二极管(Organic Light Emitting Diode,OLED)显示器具有色域广、对比度高、亮度高、反应快、耗能低、具柔软性等优点,因此逐渐成为显示领域发展的重点技术。因上述优点,与薄膜晶体管(Thin film transistor,TFT)显示器相比,OLED显示器更适合用于制备大尺寸、薄型、柔性、透明及双面显示的显示器。其中主动矩阵有机发光二极管(Active-Matrix Organic Light-Emitting Diode,AMOLED)相较于一般薄膜晶体管更具有厚度薄的优势,因此AMOLED成为有机发光二极管应用的重点技术。

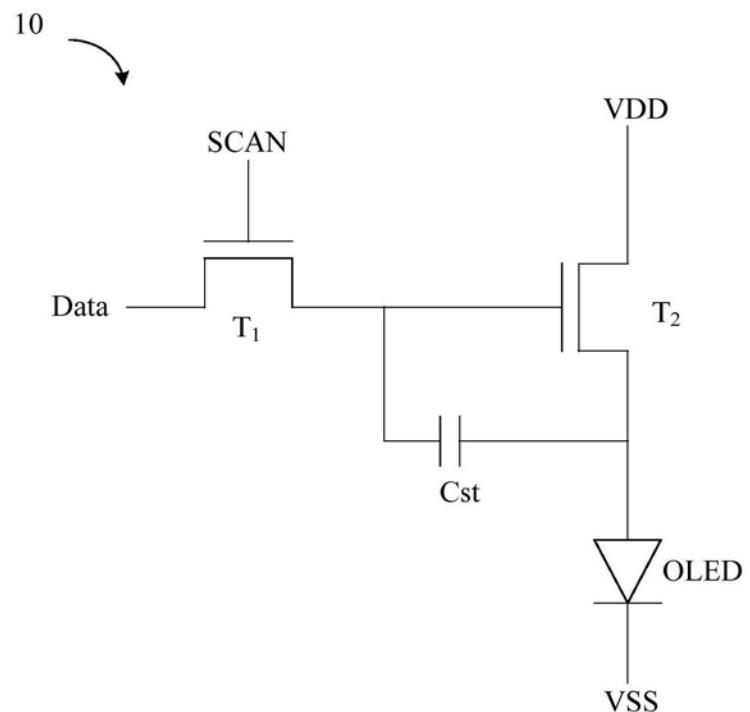

[0003] 如图1所示,驱动AMOLED的基础驱动电路10是由两个薄膜晶体管(T1与T2)及一个存储电容Cst所组成,薄膜晶体管T1为开关晶体管,薄膜晶体管T1的栅极接入SCAN信号,源极接入数据信号Data,当栅极接收到高电平的SCAN信号时,薄膜晶体管T1导通数据信号Data。薄膜晶体管T2为驱动晶体管,提供给有机发光二极管OLED的电流由薄膜晶体管T2控制,薄膜晶体管T2的源极接入电压源VDD,薄膜晶体管T2的栅极与薄膜晶体管T1的漏极相连,因此当薄膜晶体管T1导通数据信号Data,薄膜晶体管T2也将被导通,此时流经有机发光二极管OLED的电流 $I_{OLED}=k(V_{gs}-V_{th})^2$ ,其中k为薄膜晶体管T2的电流放大系数,k的数值由薄膜晶体管T2本身的特性决定,Vth为薄膜晶体管T2的阈值电压,Vgs为薄膜晶体管T2的栅极与源极之间的电压差。由于薄膜晶体管T2的阈值电压容易漂移使得有机发光二极管OLED的驱动电流不稳定而影响OLED面板的显示品质,因此需要阈值电压补偿电路来减少阈值电压飘移的现象。

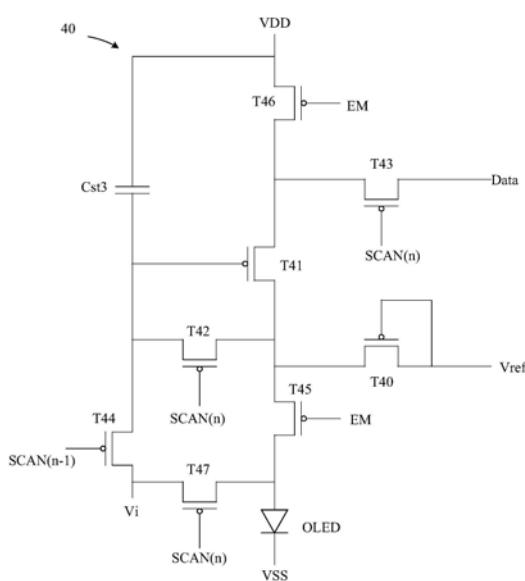

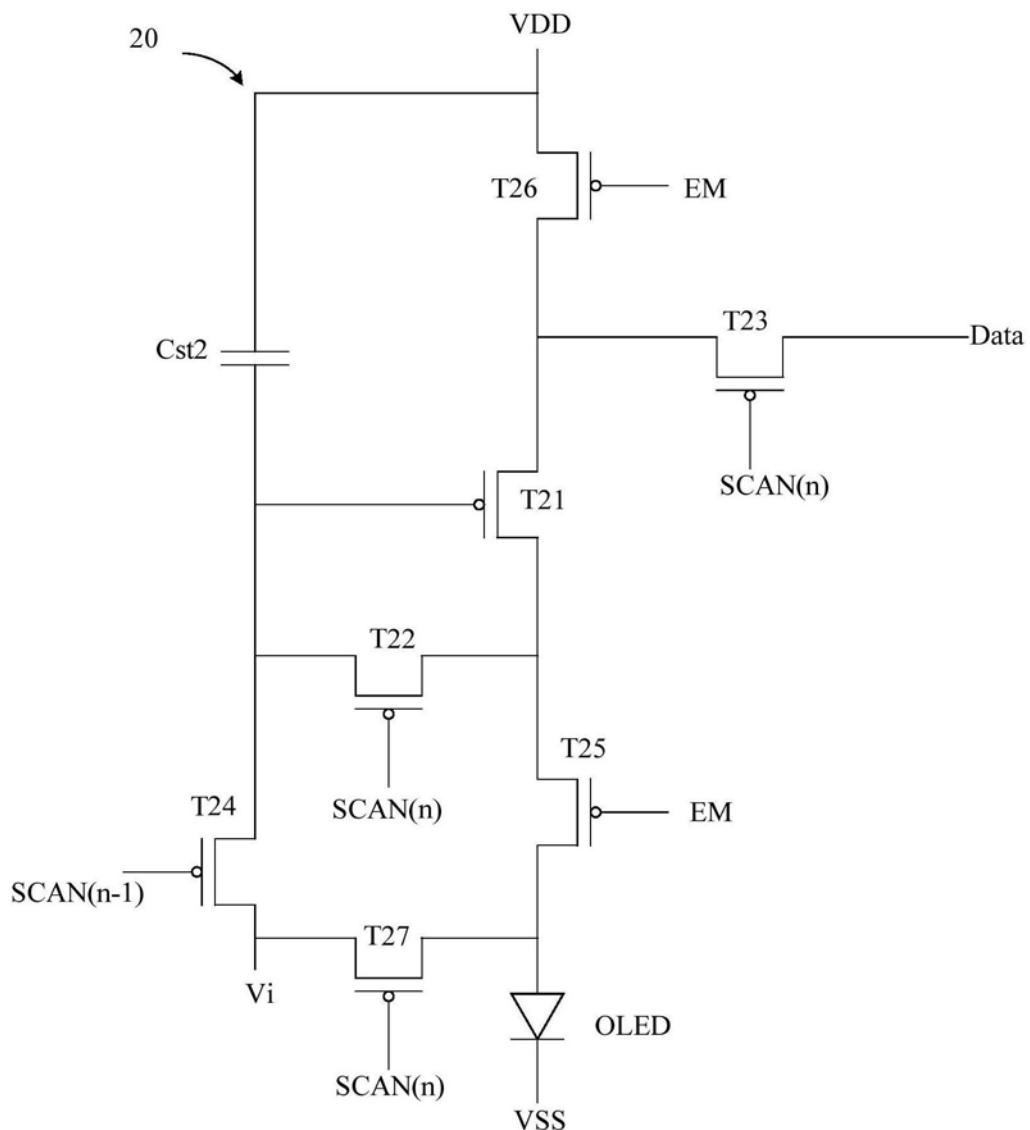

[0004] 图2所示为目前常见的7T1C像素补偿电路20,由7个晶体管T21-T27、一个存储电容Cst2组成。7T1C像素补偿电路20用于补偿有机发光二极管OLED,其中第一晶体管T21为驱动晶体管。第二晶体管T22、第三晶体管T23以及第七晶体管T27的栅极接入本级的扫描信号SCAN(n),第四晶体管T24的栅极接入上一级的扫描信号SCAN(n-1),第四晶体管T24的源极连接第二晶体管T22的源极,第四晶体管T24的漏极分别连接第七晶体管T27的源极与低电平Vi。

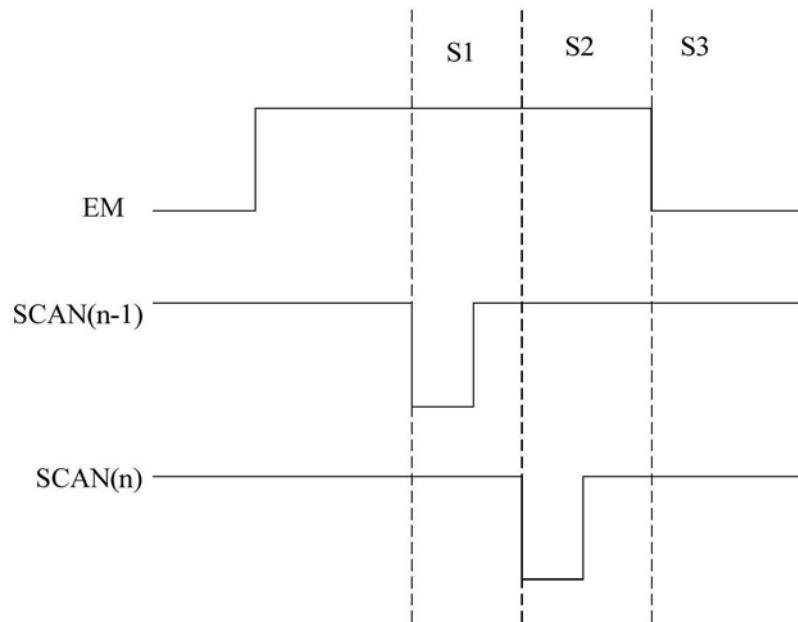

[0005] 如图3所示,图3为图2中7T1C像素补偿电路20的时序图。7T1C像素补偿电路20的作用可分为复位阶段S1、补偿阶段S2与发光阶段S3。在复位阶段S1中,上一级的扫描信号SCAN(n-1)为低电平,本级的扫描信号SCAN(n)与发光信号EM为高电平,因此第四晶体管T24导通,使得第一晶体管T21的栅极复位为低电平Vi。

[0006] 在电压补偿阶段S2中,发光信号EM一样为高电平,而上一级的扫描信号SCAN(n-1)变为高电平,本级的扫描信号SCAN(n)变为低电平,因此第三晶体管T23导通使第一晶体管T21的源极接入数据信号Data。由于此时第一晶体管T21的栅极和漏极短接,因此第一晶体管T21形成二极管结构,因此在第一晶体管的源极接入数据信号Data后,第一晶体管T21的栅极会充电至第一电位Vdata-Vth,其中Vdata为数据信号Data的电平,Vth为第一晶体管

T21的阈值电压。即第一晶体管T21的栅极的电平会等于数据信号Data与第一晶体管阈值电压之间的电压差。同时第二晶体管T22与第七晶体管T27也接入低电平的本级扫描信号SCAN(n),因此第七晶体管T27导通使得有机发光二极管OLED的阳极复位至低电平Vi。

[0007] 在发光阶段S3中,发光信号EM为低电平,上一级的扫描信号SCAN(n-1)与本级的扫描信号SCAN(n)皆为高电平,因此第二晶体管T22、第三晶体管T23、第四晶体管T24与第七晶体管T27皆为不导通,电压源VDD通过第一晶体管T21及第五晶体管T25传输到有机发光二极管OLED的阳极,此时通过有机发光二极管OLED的电流I<sub>OLED</sub>为:

$$I_{OLED} = k (VDD - (Vdata - Vth) - Vth)^2 = k (VDD - Vdata)^2$$

[0009] 因此,驱动有机发光二极管OLED的电流与第一晶体管T21的阈值电压Vth无关,可以避免驱动晶体管阈值电压漂移造成面板显示品质不良的问题。然而上述的7T1C像素补偿电路仍存在亚阈值电压与漏电区域不均匀的问题。比如在像素显示电极的显示灰阶为零时,驱动晶体管仍有电流产生,因此会有电流通过有机发光二极管使其发光,因此在像素显示低灰阶的情况下,会因为漏电流使得灰阶值与期望值不同,导致显示面板的对比度变差。

[0010] 因此,需要一种像素补偿电路,来解决在低显示灰阶时,驱动晶体管的漏电流会影响显示灰阶,造成对比度变差的问题。

## 发明内容

[0011] 本发明提供一种像素补偿电路,包含有机发光二极管、第一晶体管、补偿晶体管、存储电容以及第二晶体管。所述有机发光二极管的阴极连接至第一参考电平。所述第一晶体管的源极连接至高电平以及数据信号,所述第一晶体管的漏极连接至所述有机发光二极管的阳极。所述补偿晶体管的源极与栅极连接至第二参考电平,所述补偿晶体管的漏极连接至所述第一晶体管的漏极,使所述第一晶体管漏极的电位等于或小于所述第二参考电平与所述补偿晶体管阈值电压的总和。所述存储电容设置于所述高电平与所述第一晶体管的栅极之间。所述第二晶体管的栅极连接本级扫描信号,所述第二晶体管的源极连接至所述第一晶体管的栅极,所述第二晶体管的漏极连接至所述第一晶体管的漏极与补偿晶体管的漏极。

[0012] 较佳地,所述像素补偿电路包含第三晶体管,其栅极连接至所述本级扫描信号,其源极连接至所述数据信号,其漏极连接至所述第一晶体管的源极,当所述本级扫描信号为低电平时,所述第三晶体管导通将所述数据信号传送至所述第一晶体管的源极。

[0013] 较佳地,所述像素补偿电路包含第四晶体管,其栅极连接至上一级扫描信号,其源极连接至所述第一晶体管的栅极,其漏极连接至第三参考电平,当所述上一级扫描信号为低电平时,所述第四晶体管导通将所述第三参考电平传送至所述第一晶体管的栅极,使所述第一晶体管栅极的电平复位至所述第三参考电平。

[0014] 较佳地,所述像素补偿电路包含第五晶体管及第六晶体管,所述第五晶体管及所述第六晶体管的栅极接入发光信号,所述第五晶体管的源极连接至所述第一晶体管的漏极,所述第五晶体管的漏极连接至所述有机发光二极管的阳极,所述第六晶体管的源极连接至所述高电平,所述第六晶体管的漏极连接至所述第一晶体管的源极,当所述发光信号为低电平时,所述第六晶体管导通将所述高电平传送至所述第一晶体管的源极,使所述有机发光二极管发光。

[0015] 较佳地,所述像素补偿电路包含第七晶体管,其栅极连接至所述本级扫描信号,当所述本级扫描信号为低电平时,所述第七晶体管导通将所述第三参考电平传送至所述第一晶体管的源极。

[0016] 本发明还提供一种像素补偿方法,包含将有机发光二极管的阴极连接至第一参考电平。将第一晶体管的源极连接至高电平以及数据信号,将所述第一晶体管的漏极连接至所述有机发光二极管的阳极。将补偿晶体管的源极与栅极连接至第二参考电平,将补偿晶体管的漏极连接至所述第一晶体管的漏极,使所述第一晶体管漏极的电位等于或小于所述第二参考电平与所述补偿晶体管阈值电压的总和。将存储电容设置于所述高电平与所述第一晶体管的栅极之间。以及将第二晶体管的栅极连接本级扫描信号,将所述第二晶体管的源极连接至所述第一晶体管的栅极,将所述第二晶体管的漏极连接至所述第一晶体管的漏极与补偿晶体管的漏极。其中当所述本级扫描信号为低电平时,所述第二晶体管导通,使得所述第一晶体管的栅极与漏极短接。

[0017] 较佳地,本发明提供的像素补偿方法包含将第三晶体管的栅极连接至所述本级扫描信号,将所述第三晶体管的源极连接至所述数据信号,将所述第三晶体管的漏极连接至所述第一晶体管的源极,当所述本级扫描信号为低电平时,所述第三晶体管导通将所述数据信号传送至所述第一晶体管的源极。

[0018] 较佳地,本发明提供的像素补偿方法包含将第四晶体管的栅极连接至上一级扫描信号,将所述第四晶体管的源极连接至所述第一晶体管的栅极,将所述第四晶体管的漏极连接至第三参考电平,当所述上一级扫描信号为低电平时,所述第四晶体管导通将所述第三参考电平传送至所述第一晶体管的栅极,使所述第一晶体管栅极的电平复位至所述第三参考电平。

[0019] 较佳地,本发明提供的像素补偿方法包含将第五晶体管及第六晶体管的栅极接入发光信号,将所述第五晶体管的源极连接至所述第一晶体管的漏极,将所述第五晶体管的漏极连接至所述有机发光二极管的阳极,将所述第六晶体管的源极连接至所述高电平,将所述第六晶体管的漏极连接至所述第一晶体管的源极,当所述发光信号为低电平时,所述第六晶体管导通将所述高电平传送至所述第一晶体管的源极,使所述有机发光二极管发光。

[0020] 较佳地,本发明提供的像素补偿方法包含将第七晶体管的栅极连接至所述本级扫描信号,当所述本级扫描信号为低电平时,所述第七晶体管导通将所述第三参考电平传送至所述第一晶体管的源极。

[0021] 本发明的优点在于,利用本发明的像素补偿电路及方法,可以改善驱动晶体管老化的现象,提升驱动晶体管的均匀度。

## 附图说明

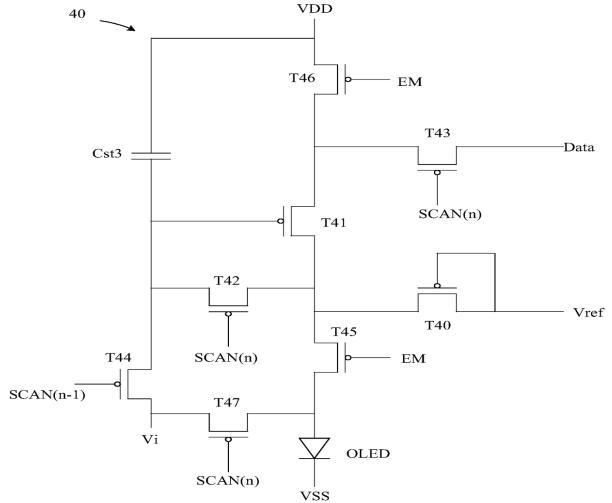

- [0022] 图1绘示像素驱动电路;

- [0023] 图2绘示现有7T1C的像素补偿电路;

- [0024] 图3绘示现有7T1C的像素补偿电路的时序图;

- [0025] 图4绘示本发明7T1C的像素补偿电路;

- [0026] 图5绘示现有的7T1C像素补偿电路中驱动晶体管的漏极与栅极测试曲线;

[0027] 图6绘示本发明7T1C像素补偿电路中驱动晶体管的漏极与栅极测试曲线。

### 具体实施方式

[0028] 下面结合附图对本发明提供的显示面板及显示装置做详细说明。具体实施方式中的纵向、横向、上、下、左、右、前、后仅是为了便于描述各部件之间的相对关系,而非用来限定本发明的实施方式。显然,所描述的实施例仅是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

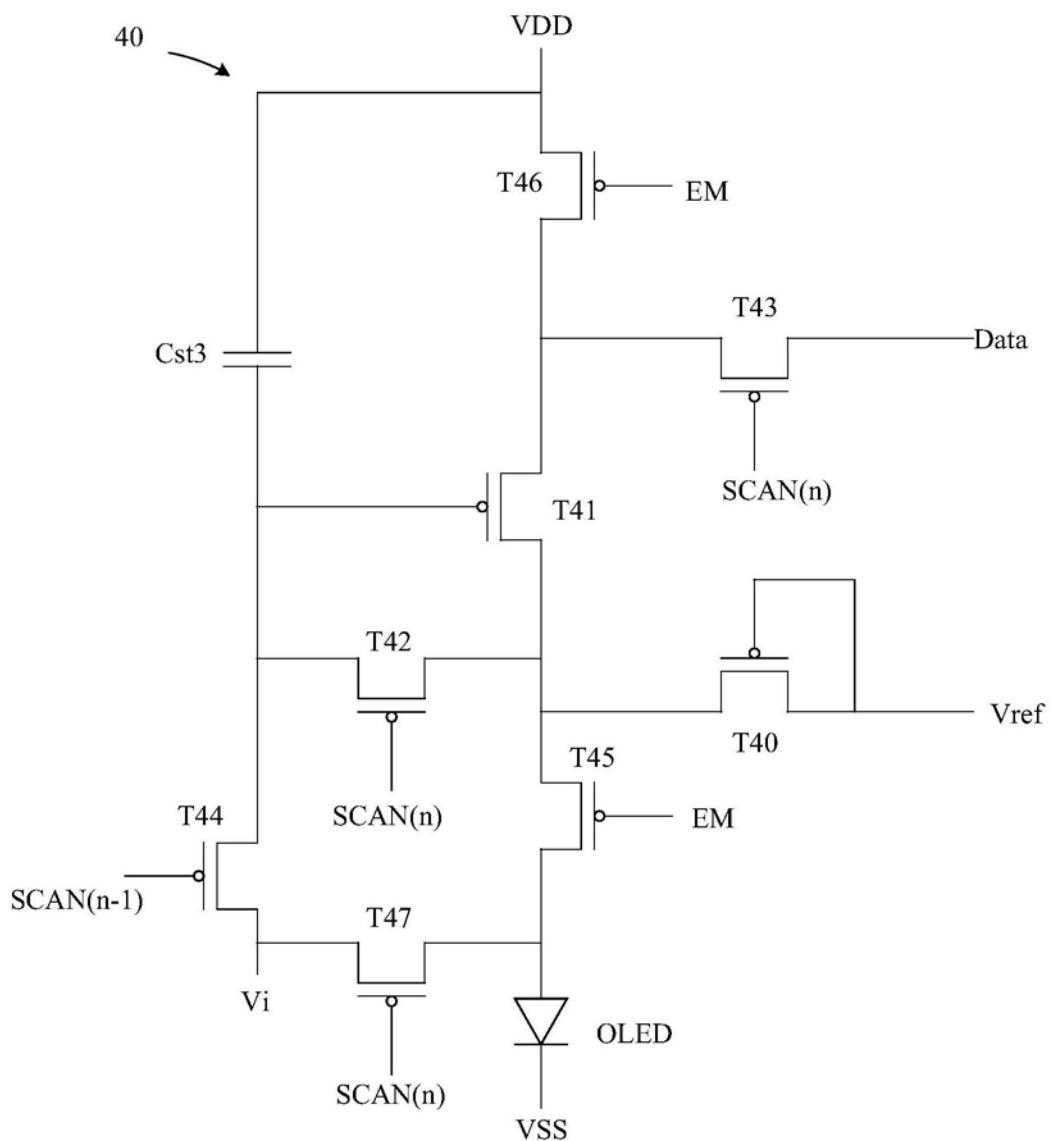

[0029] 请参考图4,图4所示为本发明7T1C的像素补偿电路。像素补偿电路40包含一个补偿晶体管T40、七个晶体管T41-T47、一个存储电容Cst3以及一个有机发光二极管OLED,其中第一晶体管T41为驱动晶体管。

[0030] 在本发明的像素补偿电路40中,补偿晶体管T40的源极与栅极连接至参考电平Vref,补偿晶体管T40的漏极连接至第一晶体管T41的漏极。第一晶体管T41的源极通过第六晶体管T46连接至高电平VDD,同时第一晶体管T41的源极通过第三晶体管T43连接至数据信号Data,第一晶体管T41的栅极通过存储电容Cst3连接至高电平VDD,第一晶体管T41的漏极通过第五晶体管T45连接至参考电平VSS。

[0031] 第二晶体管T42、第三晶体管T43以及第七晶体管T47的栅极接入本级的扫描信号SCAN(n),第三晶体管T43的源极接入Data信号,第四晶体管T44的栅极接入上一级的扫描信号SCAN(n-1)。第二晶体管T42的源极与漏极分别连接到第一晶体管T21的栅极与漏极,因此当本级的扫描信号SCAN(n)为低电平时,第一晶体管T21的栅极与漏极会短接使得第一晶体管T21以二极管的形式运作。第三晶体管T43的源极与漏极分别连接到数据信号Data与第一晶体管T41的源极,因此当本级的扫描信号SCAN(n)为低电平时,数据信号Data会传送至第一晶体管T41的源极。

[0032] 第四晶体管T44的源极连接第二晶体管T42的源极,第四晶体管T44的漏极分别连接第七晶体管T47的源极与低电平Vi。因此在复位阶段中,当上一级的扫描信号SCAN(n-1)为低电平时,第一晶体管T41的栅极会被复位为低电平Vi,同时有机发光二极管OLED的阳极连接低电平Vi,因此在复位阶段中,有机发光二极管OLED不会发光。与现有技术不同的是,由于补偿晶体管T40源极与栅极皆连接至参考电平Vref,在本发明较佳的实施例中,参考电平Vref设置于-20V至-30V之间,低电平Vi设置于6V至10V间。因此第一晶体管T41的漏极所连接的电平均等于或小于Vref+|Vth0|,其中Vth0为补偿晶体管T40的阈值电压,因此第一晶体管T41的栅极与漏极之间的电压差超过30V。

[0033] 第五晶体管T45与第六晶体管T46的栅极连接发光信号EM,因此当发光信号EM为低电平时,高电平VDD会通过第六晶体管T46、第一晶体管T41与第五晶体管T45传送到有机发光二极管的阳极,使有机发光二极管OLED发光。通过本发明的像素补偿电路40,由于第一晶体管T41的栅极与漏极之间的电压差超过30V,因此在显示灰阶较低的情况下,驱动晶体管(即,第一晶体管T41)不会因为栅极与漏极之间的电压差太小使得第一晶体管T41导通,确保在发光信号EM为高电平时有机发光二极管OLED不会发光。

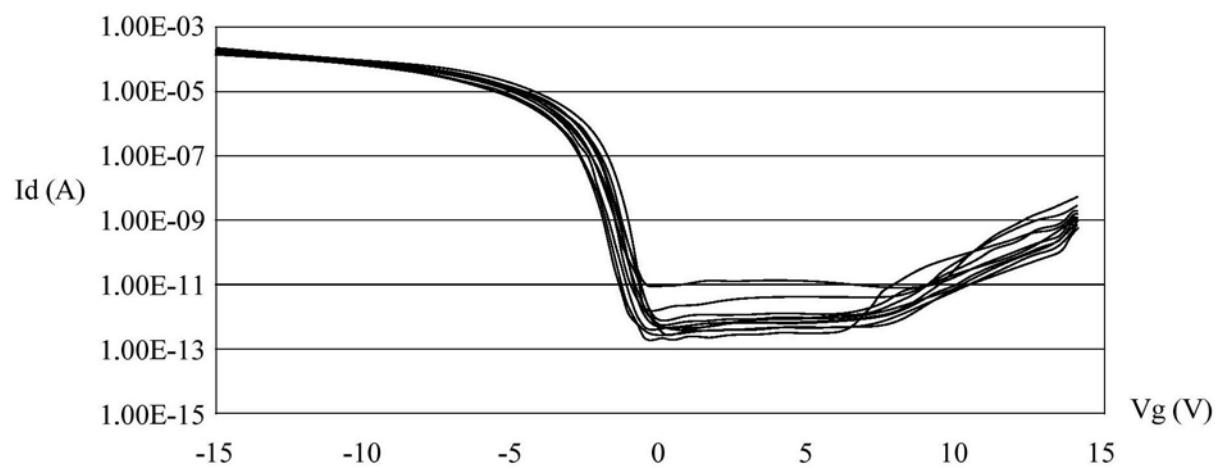

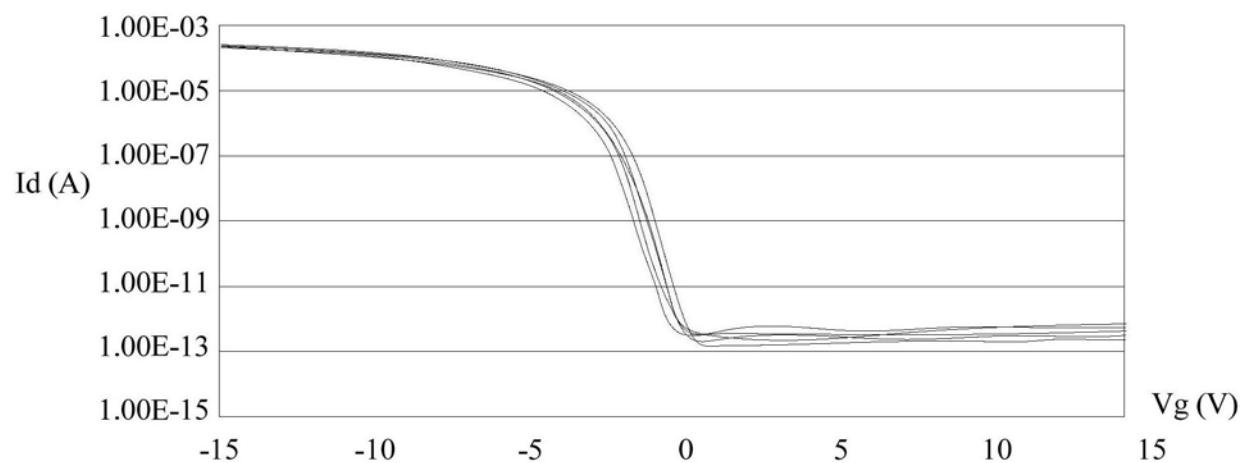

[0034] 图5绘示现有(即图2所示)的7T1C像素补偿电路中驱动晶体管T21的漏极与栅极测试曲线。图6绘示本发明(即图4)的7T1C像素补偿电路中驱动晶体管T41的漏极与栅极测试

曲线。其中图5与图6的横轴表示驱动晶体管的栅极电压大小,纵轴为驱动晶体管漏电流的大小。如图5所示,在现有的7T1C像素补偿电路中,驱动晶体管T21由于晶体管老化导致均匀性不佳。接着请参考图6,利用本发明的7T1C像素补偿电路,驱动晶体管T21的栅极接入低电平 $V_i$ 、漏极通过与补偿晶体管T40相连而接入约等于或小于 $V_{ref} + |V_{th0}|$ 大小的电平,使得驱动晶体管T41栅极与漏极之间的电压差超过30V,如此一来可以有效改善晶体管老化的现象,提高驱动晶体管的均匀性。

[0035] 以上所述仅是本发明的优选实施方式,应当指出,对于本技术领域的普通技术人员,在不脱离本发明原理的前提下,还可以做出若干改进和润饰,这些改进和润饰也应视为本发明的保护范围。

图1

图2

图3

图4

图5

图6

|         |                              |                      |            |

|---------|------------------------------|----------------------|------------|

| 专利名称(译) | 像素补偿电路及像素补偿方法                |                      |            |

| 公开(公告)号 | <a href="#">CN109473063A</a> | 公开(公告)日              | 2019-03-15 |

| 申请号     | CN201811489457.8             | 申请日                  | 2018-12-06 |

| [标]发明人  | 李骏                           |                      |            |

| 发明人     | 李骏                           |                      |            |

| IPC分类号  | G09G3/3225                   |                      |            |

| CPC分类号  | G09G3/3225                   |                      |            |

| 代理人(译)  | 黄威                           |                      |            |

| 外部链接    | <a href="#">Espacenet</a>    | <a href="#">SIPO</a> |            |

## 摘要(译)

一种像素补偿电路包含有机发光二极管、第一晶体管、补偿晶体管、存储电容以及第二晶体管。所述有机发光二极管的阴极连接至第一参考电平。所述第一晶体管的源极连接至高电平以及数据信号。所述补偿晶体管的源极与栅极连接至第二参考电平，所述补偿晶体管的漏极连接至所述第一晶体管的漏极，使所述第一晶体管漏极的电位等于或小于所述第二参考电平与所述补偿晶体管阈值电压的总和。所述存储电容设置于所述高电平与所述第一晶体管的栅极之间。利用本发明提供的像素补偿电路可以改善驱动晶体管老化的现象，提升驱动晶体管的均匀度。