(12) 发明专利

(10) 授权公告号 CN 102956192 B

(45) 授权公告日 2015. 12. 16

(21) 申请号 201210080316. 7

US 2005/0105031 A1, 2005. 05. 19, 全文.

(22) 申请日 2012. 03. 16

审查员 冯莹

(30) 优先权数据

10-2011-0081701 2011. 08. 17 KR

(73) 专利权人 乐金显示有限公司

地址 韩国首尔

(72) 发明人 韩仁孝 李玹行 韩成晚

(74) 专利代理机构 北京律诚同业知识产权代理

有限公司 11006

代理人 徐金国

(51) Int. Cl.

G09G 3/32(2006. 01)

(56) 对比文件

US 2011/0227903 A1, 2011. 09. 22, 说明书第

2 页第 0043 段—第 4 页第 0067 段, 附图 2—4.

US 2009/0309503 A1, 2009. 12. 17, 说明书第

2 页第 0028 段—第 4 页第 0050 段, 附图 2、4—5.

US 2009/0079679 A1, 2009. 03. 26, 全文.

US 2008/0169754 A1, 2008. 07. 17, 全文.

权利要求书3页 说明书13页 附图11页

(54) 发明名称

有机发光二极管显示装置

(57) 摘要

本文涉及一种补偿驱动 TFT 的阈值电压、供

电电压源的压降以及驱动 TFT 的迁移率的显示装

置。显示装置可包括多个像素。至少一个像素可

以包括诸如第一电容、第二电容、数据晶体管、控制

晶体管、发射晶体管、初始化晶体管、驱动晶体管

和在其他部件中的有机发光二极管 (OLED) 之类

的部件。

1. 一种显示像素，所述显示像素包括：

第一电容，所述第一电容耦接在第一节点和第二节点之间；

第二电容，所述第二电容耦接在所述第二节点和供电电压源之间；

数据晶体管 (T3)，所述数据晶体管与所述第一节点耦接，并且所述数据晶体管被配置为响应于所述数据晶体管的导通而将所述第一节点设定至数据电压；

控制晶体管 (T4)，所述控制晶体管与所述第二节点耦接，并且所述控制晶体管被配置为响应于所述控制晶体管的导通而将所述第二节点设定至供电电压，其中将所述第二节点设定至所述供电电压使得经所述第一电容引起所述第一节点处的所述数据电压的调整，以在所述第一节点处产生经调整的数据电压；

驱动晶体管 (Td)，所述驱动晶体管的栅极与所述第一节点耦接，并且所述驱动晶体管的源极与所述第二节点耦接，其中所述第一节点处的所述经调整的数据电压被施加给所述驱动晶体管的栅极，以控制有机发光二极管 (OLED) 中的电流；

发射晶体管 (T2)，所述发射晶体管耦接在所述驱动晶体管与所述有机发光二极管之间，并且使所述驱动晶体管和所述有机发光二极管之间的电流通路能启用；以及

初始化晶体管 (T1)，所述初始化晶体管与所述第一节点耦接，并且所述初始化晶体管被配置为将所述第一节点设定到参考电压，

其中在所述初始化晶体管将所述第一节点设定到所述参考电压之后，并且在所述数据晶体管将所述第一节点设定到所述数据电压之前，所述初始化晶体管被截止以将所述第一节点浮置，并且

其中从所述第一节点被设定到所述数据电压到所述第二节点被设定到所述供电电压，所述发射晶体管被配置为使在所述驱动晶体管与所述有机发光二极管之间的电流通路禁用。

2. 根据权利要求 1 所述的显示像素，其中所述供电电压包括高电势供电电压。

3. 根据权利要求 1 所述的显示像素，

其中将所述第一节点设定到所述数据电压使得经所述第一电容引起所述第二节点处的电压改变。

4. 根据权利要求 3 所述的显示像素，其中当所述第一节点被浮置时，所述第一节点和所述第二节点随着时间的推移电压降低。

5. 根据权利要求 3 所述的显示像素，

其中所述第二节点处的电压改变是基于所述第一电容和所述第二电容的电容值的比。

6. 根据权利要求 5 所述的显示像素，其中所述初始化晶体管被截止的时间、所述数据晶体管被导通的时间、以及所述第一电容和所述第二电容的值被配置为补偿所述驱动晶体管的电子迁移率。

7. 根据权利要求 1 所述的显示像素，其中当使所述电流通路能启用时，还产生所述第一节点处的经调整的数据电压，以表明压降。

8. 根据权利要求 1 所述的显示像素，进一步包括与所述有机发光二极管耦接的旁路晶体管 (T5)，以响应于所述旁路晶体管的导通而使电流绕过所述有机发光二极管。

9. 根据权利要求 8 所述的显示像素，其中所述初始化晶体管 (T1) 的栅极与第一初始化线耦接，并且所述旁路晶体管 (T5) 的栅极与第二初始化线耦接。

10. 根据权利要求 1 所述的显示像素，其中所述控制晶体管 (T4) 的源极与供电电压源耦接，所述控制晶体管的漏极与所述第二节点耦接，并且所述控制晶体管的栅极与控制线耦接。

11. 一种显示装置，所述显示装置包括多个像素，其中所述像素的至少一个像素包括：第一电容，所述第一电容耦接在第一节点和第二节点之间；

第二电容，所述第二电容耦接在所述第二节点和供电电压源之间；

数据晶体管 (T3)，所述数据晶体管与所述第一节点耦接，并且所述数据晶体管被配置为响应于所述数据晶体管的导通而将所述第一节点设定至数据电压；

控制晶体管 (T4)，所述控制晶体管与所述第二节点耦接，并且所述控制晶体管被配置为响应于所述控制晶体管的导通而将所述第二节点设定至供电电压，其中将所述第二节点设定至所述供电电压使得经所述第一电容引起所述第一节点处的所述数据电压的调整，以在所述第一节点处产生经调整的数据电压；

驱动晶体管，所述驱动晶体管的栅极与所述第一节点耦接，并且所述驱动晶体管的源极与所述第二节点耦接，其中所述第一节点处的所述经调整的数据电压被施加给所述驱动晶体管的栅极，以控制有机发光二极管 (OLED) 中的电流；

发射晶体管 (T2)，所述发射晶体管耦接在所述驱动晶体管与所述有机发光二极管之间，并且使所述驱动晶体管和所述有机发光二极管之间的电流通路能启用；以及

初始化晶体管 (T1)，所述初始化晶体管与所述第一节点耦接，并且所述初始化晶体管被配置为将所述第一节点设定到参考电压，

其中在所述初始化晶体管将所述第一节点设定到所述参考电压之后，并且在所述数据晶体管将所述第一节点设定到所述数据电压之前，所述初始化晶体管被截止以将所述第一节点浮置，并且

其中从所述第一节点被设定到所述数据电压到所述第二节点被设定到所述供电电压，所述发射晶体管被配置为使在所述驱动晶体管与所述有机发光二极管之间的电流通路禁用。

12. 根据权利要求 11 所述的显示装置，进一步包括：

初始化线，其中所述初始化晶体管的栅极与所述初始化线耦接；

发射线，其中所述发射晶体管的栅极与所述发射线耦接；

扫描线，其中所述数据晶体管的栅极与所述扫描线耦接；以及

控制线，所述控制晶体管的栅极与所述控制线耦接。

13. 根据权利要求 11 所述的显示装置，其中所述像素的至少一个像素进一步包括：

旁路晶体管，所述旁路晶体管与所述有机发光二极管耦接，并且所述旁路晶体管适用于使电流绕过所述有机发光二极管。

14. 一种操作如权利要求 1 所述的显示像素的方法，所述显示像素具有驱动晶体管，所述驱动晶体管的栅极与第一节点耦接，并且所述驱动晶体管的源极与第二节点耦接，所述方法包括以下步骤：

将所述第一节点设定到参考电压；

在将所述第一节点设定到所述参考电压之后，将所述第一节点浮置；

在将所述第一节点浮置之后，将所述第一节点设定到数据电压；

将所述第二节点设定到供电电压,以使得经所述第一节点和所述第二节点之间耦接的电容引起所述第一节点处的所述数据电压的调整,使得在所述第一节点处产生经调整的数据电压;

从所述第一节点被设定到所述数据电压到所述第二节点被设定到所述供电电压,使在所述驱动晶体管与有机发光二极管(OLED)之间的电流通路禁用;以及

将所述经调整的数据电压施加给所述驱动晶体管的栅极,以控制所述有机发光二极管中的电流。

15. 根据权利要求 14 所述的方法,进一步包括以下步骤:

响应于将所述第一节点设定到所述数据电压,使得经所述电容和第二电容引起所述第二节点处的电压改变。

16. 根据权利要求 14 所述的方法,进一步包括以下步骤:

当 (i) 所述第一节点被设定到所述参考电压, (ii) 所述第一节点被浮置以及 (iii) 所述经调整的数据电压被施加给所述驱动晶体管的所述栅极时,使得所述驱动晶体管和所述有机发光二极管之间的所述电流通路能启用。

17. 根据权利要求 14 所述的方法,进一步包括以下步骤:

当将所述第一节点设定到所述参考电压时,使电流绕过所述有机发光二极管。

## 有机发光二极管显示装置

[0001] 相关申请的交叉引用

[0002] 本申请要求享有于 2011 年 8 月 17 日提交的韩国专利申请 No. 10-2011-0081701 的权益，在此援引该专利申请的全部内容作为参考。

### 技术领域

[0003] 本文涉及一种能够补偿驱动薄膜晶体管 (TFT) 的阈值电压、供电电压的压降以及驱动 TFT 的迁移率的有机发光二极管 (OLED) 显示装置。

### 背景技术

[0004] 近年来，人们对于显示装置的需求越来越大。诸如液晶显示器 (LCD)、等离子体显示面板 (PDP) 以及有机发光二极管 (OLED) 显示器之类的各种平板显示器已得到广泛应用以满足这种需求。与其它平板显示器相比，OLED 显示装置以较低的电压驱动、更薄、并具有更宽的视角和更快的响应速度。

[0005] 一种特殊类型的 OLED 显示装置是有源矩阵 OLED 显示装置。有源矩阵 OLED 显示装置具有用于显示图像的以矩阵形式设置的多个像素。有源矩阵 OLED 显示装置的多个像素由扫描线和数据线限定。每个像素都包括扫描薄膜晶体管 (TFT)，该扫描薄膜晶体管 (TFT) 响应来自扫描线的扫描信号来提供来自数据线的数据电压。每个像素还包括驱动 TFT，该驱动 TFT 响应提供给该驱动 TFT 的栅极的数据电压来控制提供给 OLED 的电流的量。提供给有机发光二极管的、在驱动 TFT 的漏极和源极之间的电流  $I_{ds}$  可由等式 1 来表示：[ 等式 1 ]

$$I_{ds} = k' \cdot (V_{gs} - V_{th})^2$$

[0006] 在等式 1 中， $k'$  表示由驱动 TFT 的结构和物理性质所确定的比例系数， $V_{gs}$  表示驱动 TFT 的栅极和源极之间的电压差，并且  $V_{th}$  表示驱动 TFT 的阈值电压。

[0007] 然而，由于因驱动 TFT 的恶化所引起的阈值电压的漂移，每个像素的驱动 TFT 的阈值电压  $V_{th}$  都具有不同的值。驱动 TFT 的漏极和源极之间的电流  $I_{ds}$  取决于驱动 TFT 的的阈值电压  $V_{th}$ 。因此，即使给每个像素提供相同的数据电压，每个像素的驱动 TFT 的漏极和源极之间的电流  $I_{ds}$  也会改变。于是，出现了即使给每个像素提供相同的数据电压，从每个像素的 OLED 发出的光的光亮度 (luminance) 也会改变的问题。为了解决这个问题，已经提出了用于补偿每个像素的驱动 TFT 的阈值电压的各种类型的像素结构。

### 发明内容

[0009] 在一个实施例中，一种显示像素包括：第一电容、数据晶体管、控制晶体管和驱动晶体管。第一电容耦接在像素的第一节点和像素的第二节点之间。驱动晶体管的栅极与第一节点耦接并且驱动晶体管的源极与第二节点耦接。数据晶体管当导通时将第一节点设定到数据电压电平。例如，数据电压电平可表示像素的预期亮度级 (intensity level)。控制晶体管当导通时将第二节点设定到高供电电压电平。将第二节点设定到高供电电压电平使得经第一节点和第二节点之间耦接的第一电容引起第一节点处的数据电压的调整，使得在

第一节点处产生经调整的数据电压。经调整的数据电压被施加给驱动晶体管的栅极，以控制在有机发光二极管（OLED）中的电流。经调整的数据电压可表示驱动晶体管的阈值电压V<sub>th</sub>和显示面板各处的VDD的改变，使得V<sub>th</sub>和VDD二者都被补偿。

[0010] 在一个实施例中，显示像素还包括与第一节点耦接的初始化晶体管。初始化晶体管被配置为响应于初始化晶体管的导通而将第一节点设定到参考电压。然后初始化晶体管截止，以将第一节点浮置。数据晶体管被配置为在第一节点被浮置后将第一节点设定到数据电压。第二电容耦接在第二节点和供电电压之间，并且由将第一节点设定到数据电压引起的第二节点处的电压改变是基于第一和第二电容的电容值的比。

[0011] 在一个实施例中，发射晶体管与OLED耦接。发射晶体管被配置为响应于发射晶体管的导通来使得驱动晶体管和OLED之间的电流通路能启用（工作）。在一个实施例中，旁路晶体管也与OLED耦接，以响应于旁路晶体管的导通而使电流绕过OLED。

[0012] 在一个实施例中，公开了一种在显示像素中的操作方法。显示像素具有驱动晶体管，所述驱动晶体管的栅极与第一节点耦接，并且所述驱动晶体管的源极与第二节点耦接。第一节点被设定到数据电压。第二节点被设定到供电电压。将第二节点设定到供电电压使得经第一节点和第二节点之间耦接的电容引起第一节点处的数据电压的调整，使得在所述第一节点处产生经调整的数据电压。经调整的数据电压被施加给驱动晶体管的栅极，以控制有机发光二极管（OLED）中的电流。

## 附图说明

[0013] 本文各个实施例的教导可以通过考虑与附图结合的以下详细的文字描述来容易地理解。

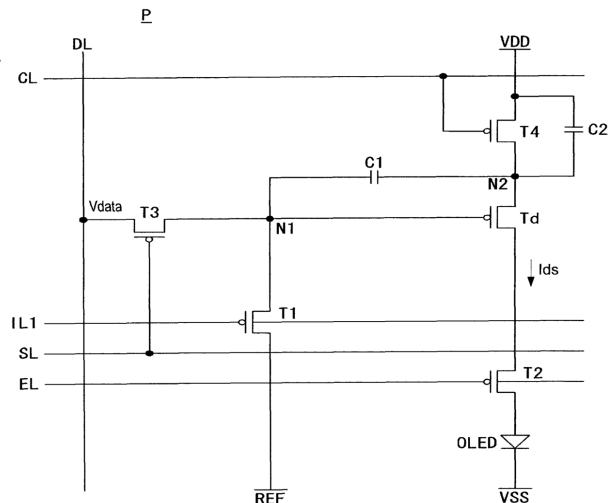

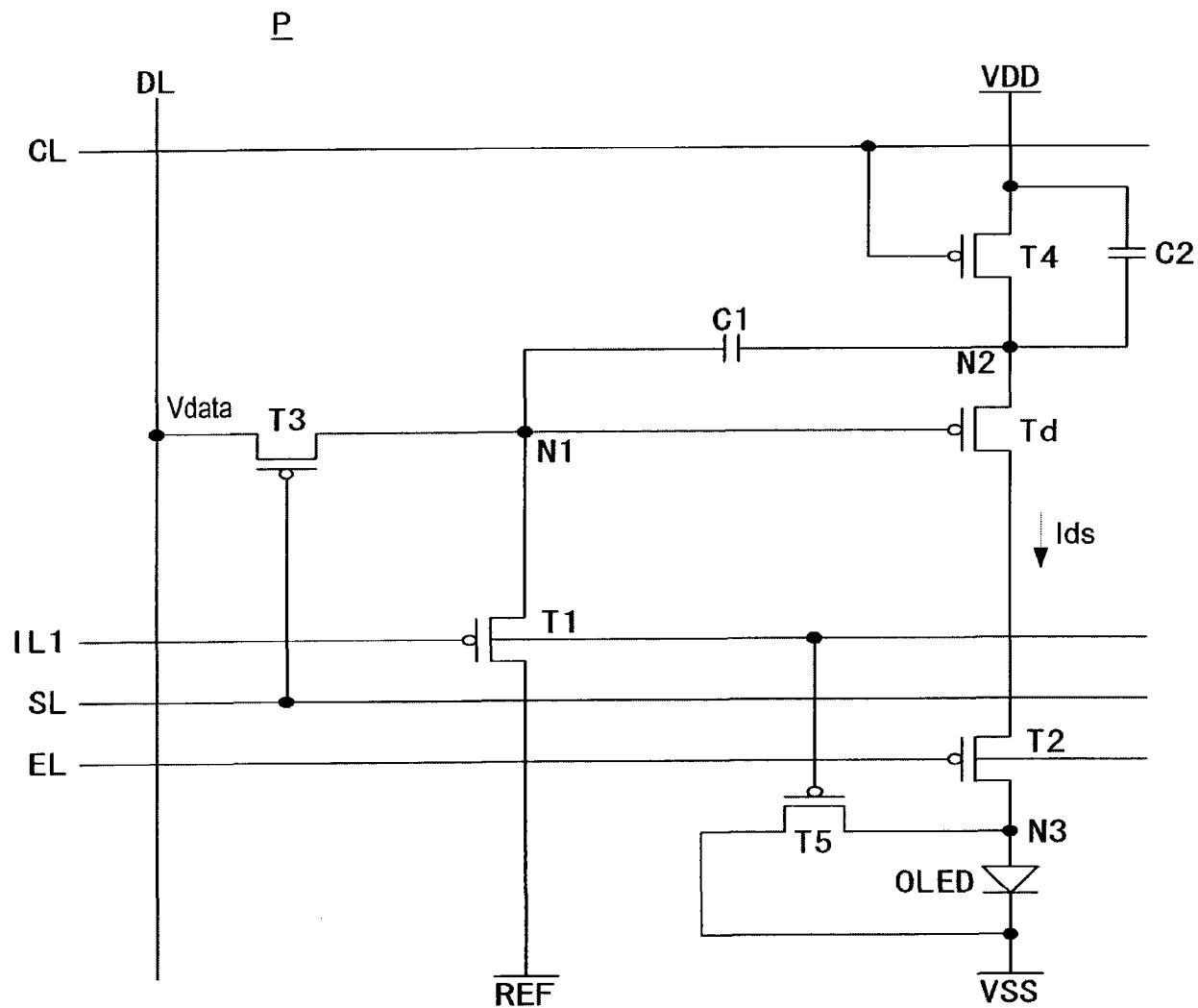

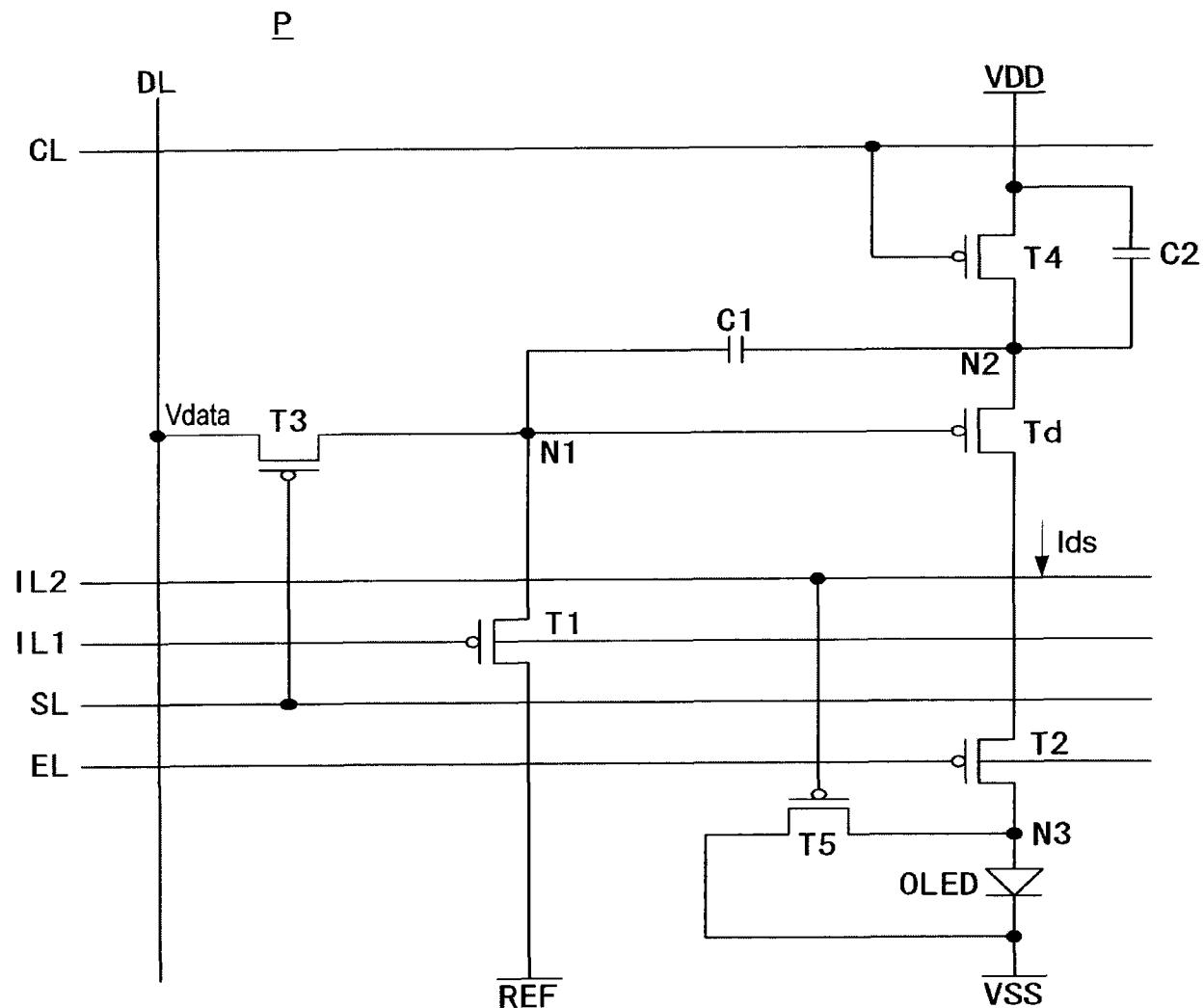

[0014] 图1是根据第一示例性实施例的显示面板的像素的等效电路图。

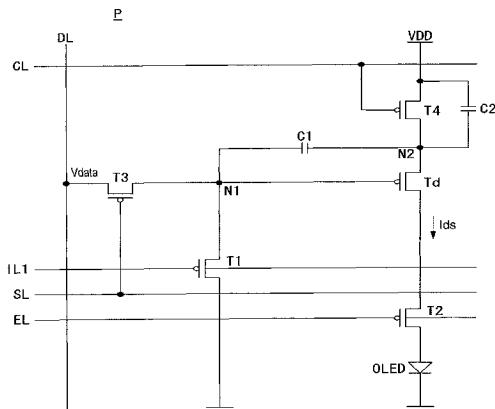

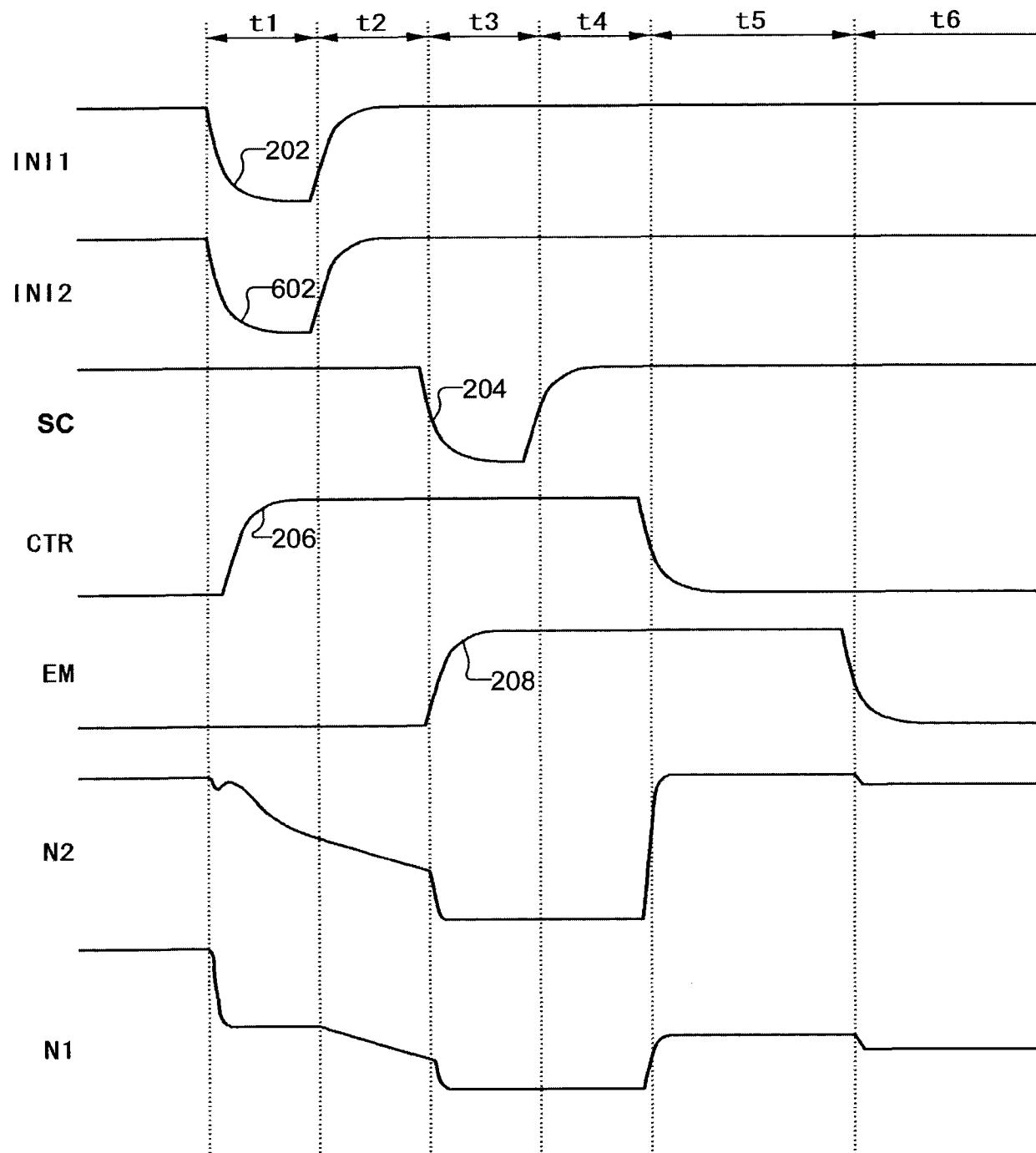

[0015] 图2是示出根据第一示例性实施例的输入至图1的像素的信号以及第一节点和第二节点的电压变化的波形图。

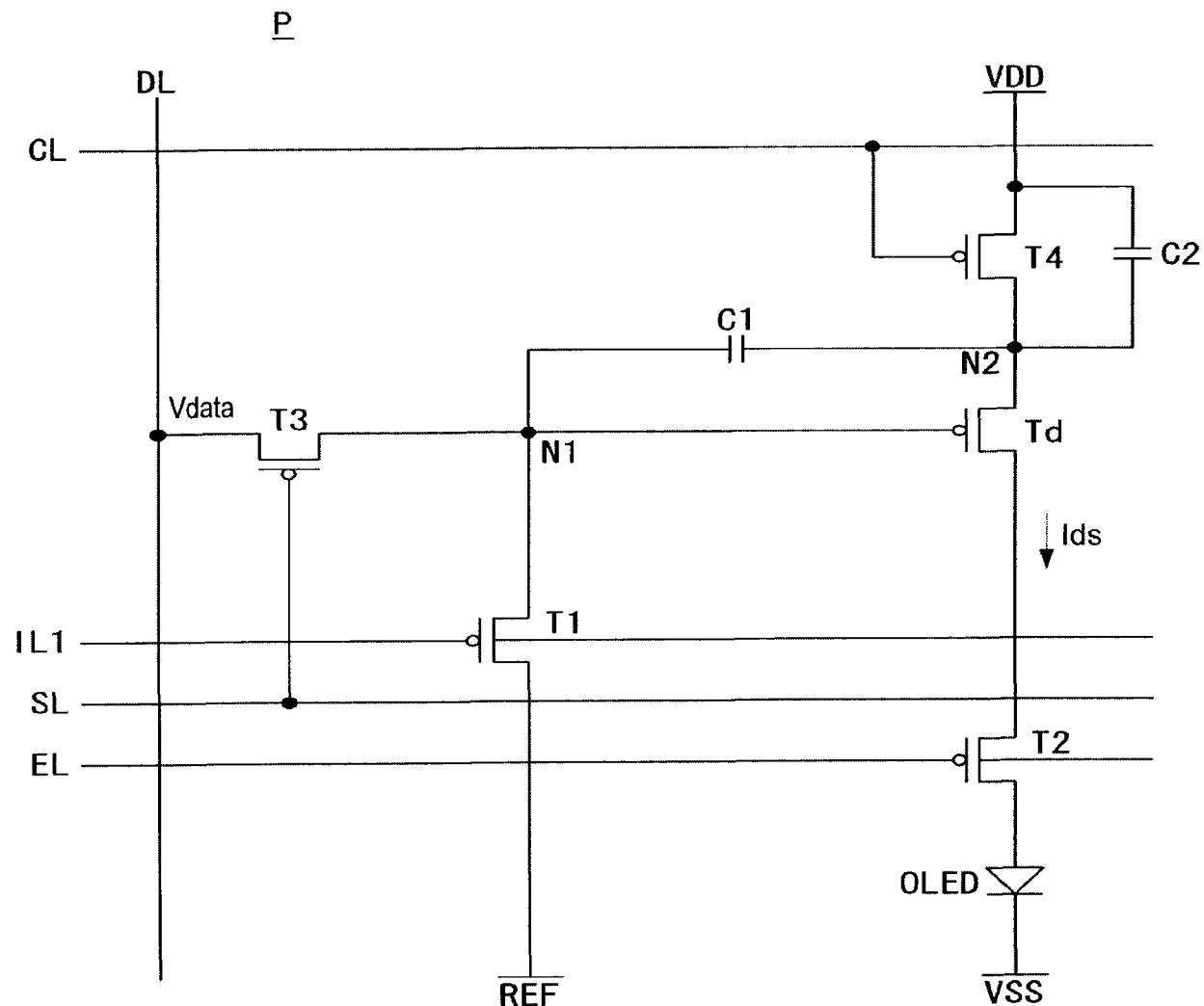

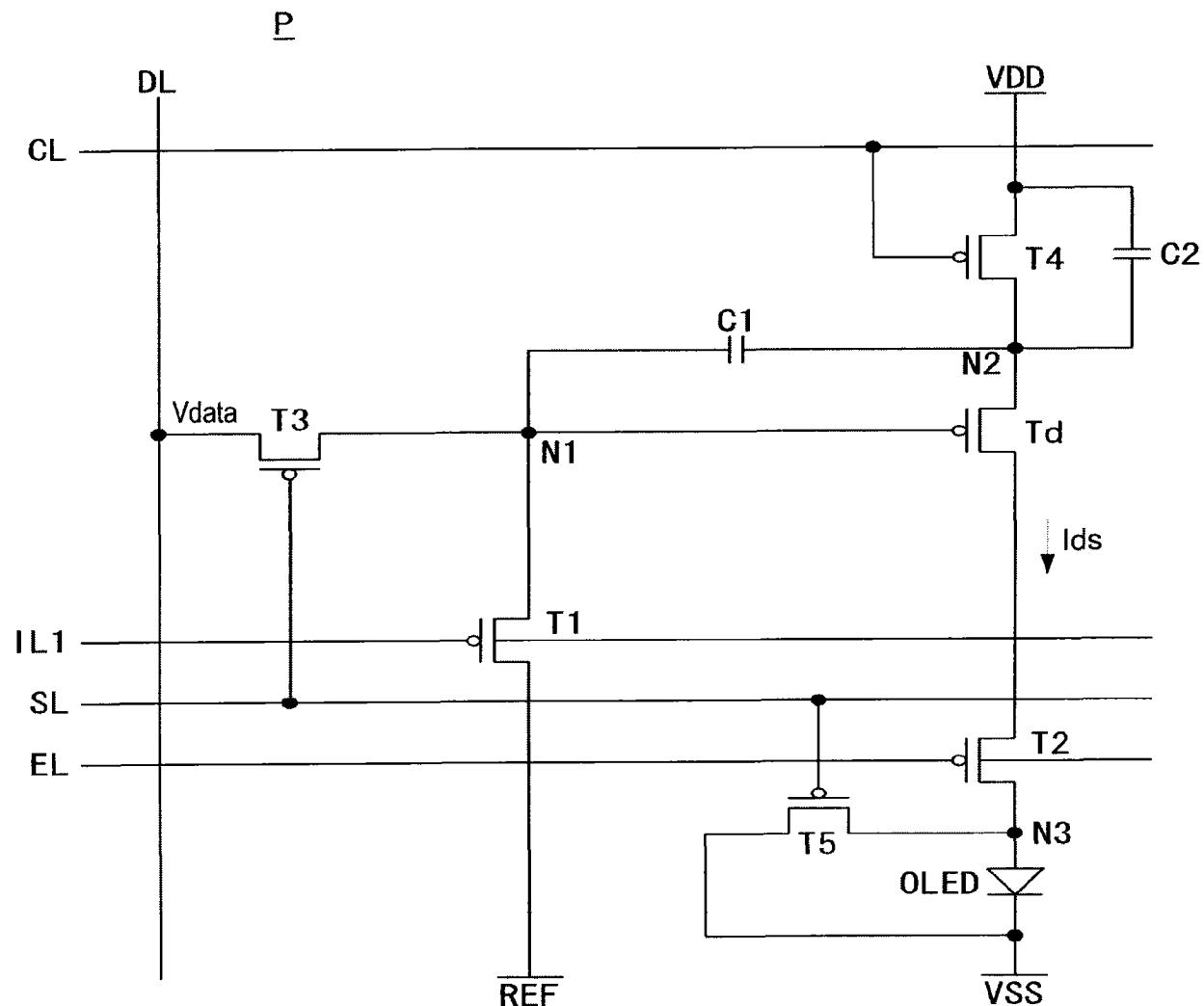

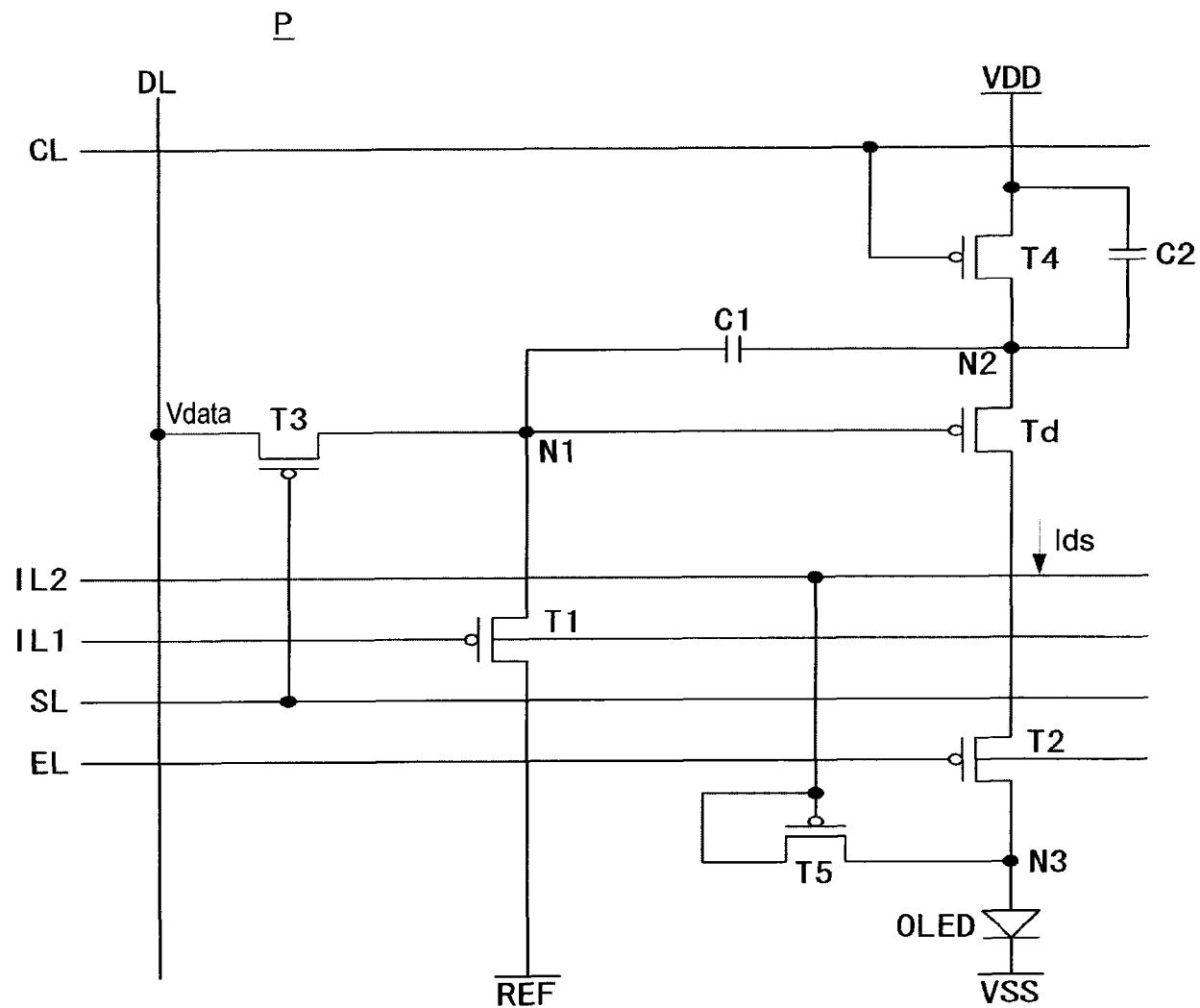

[0016] 图3是根据第二示例性实施例的显示面板的像素的等效电路图。

[0017] 图4是根据第三示例性实施例的显示面板的像素的等效电路图。

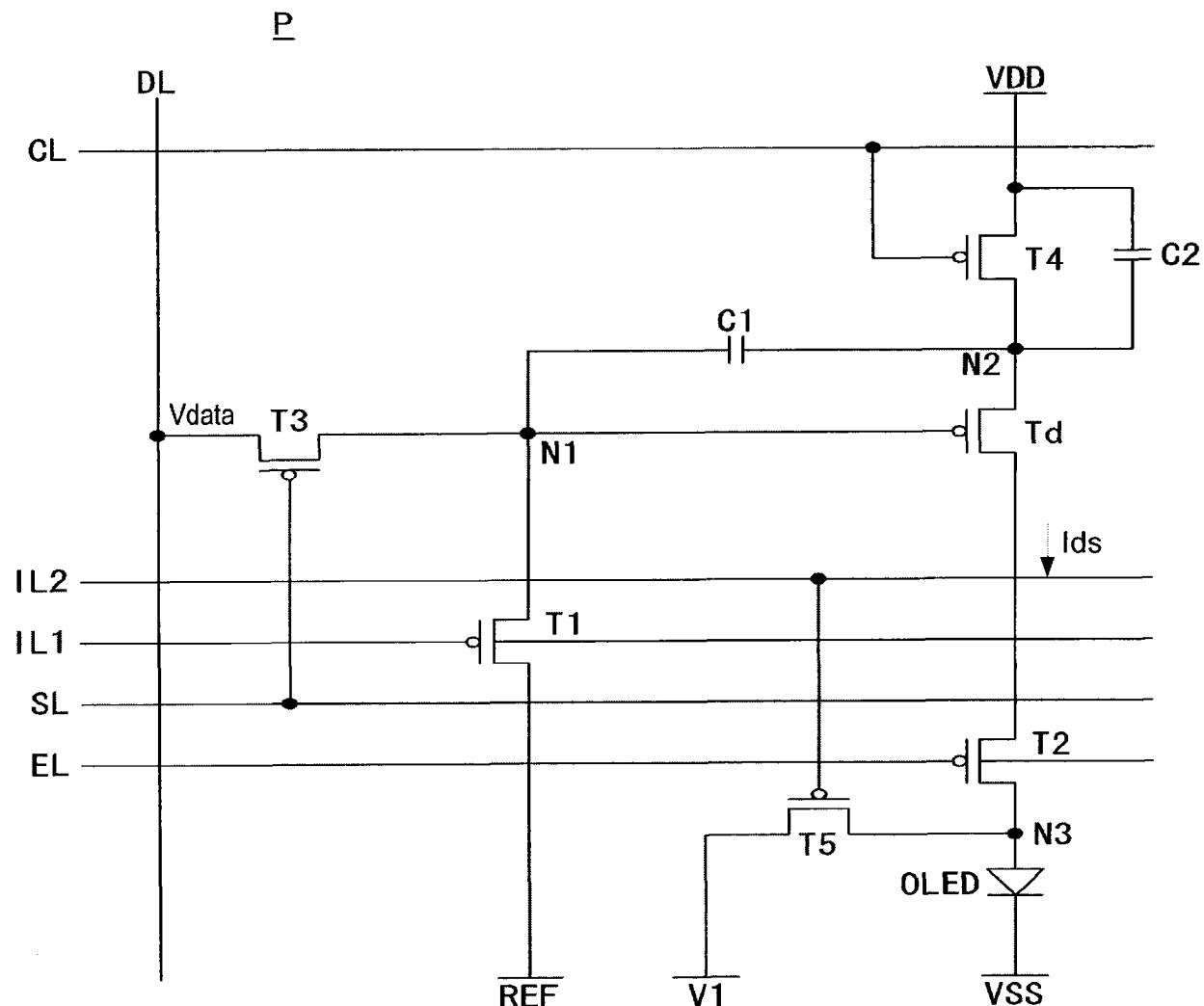

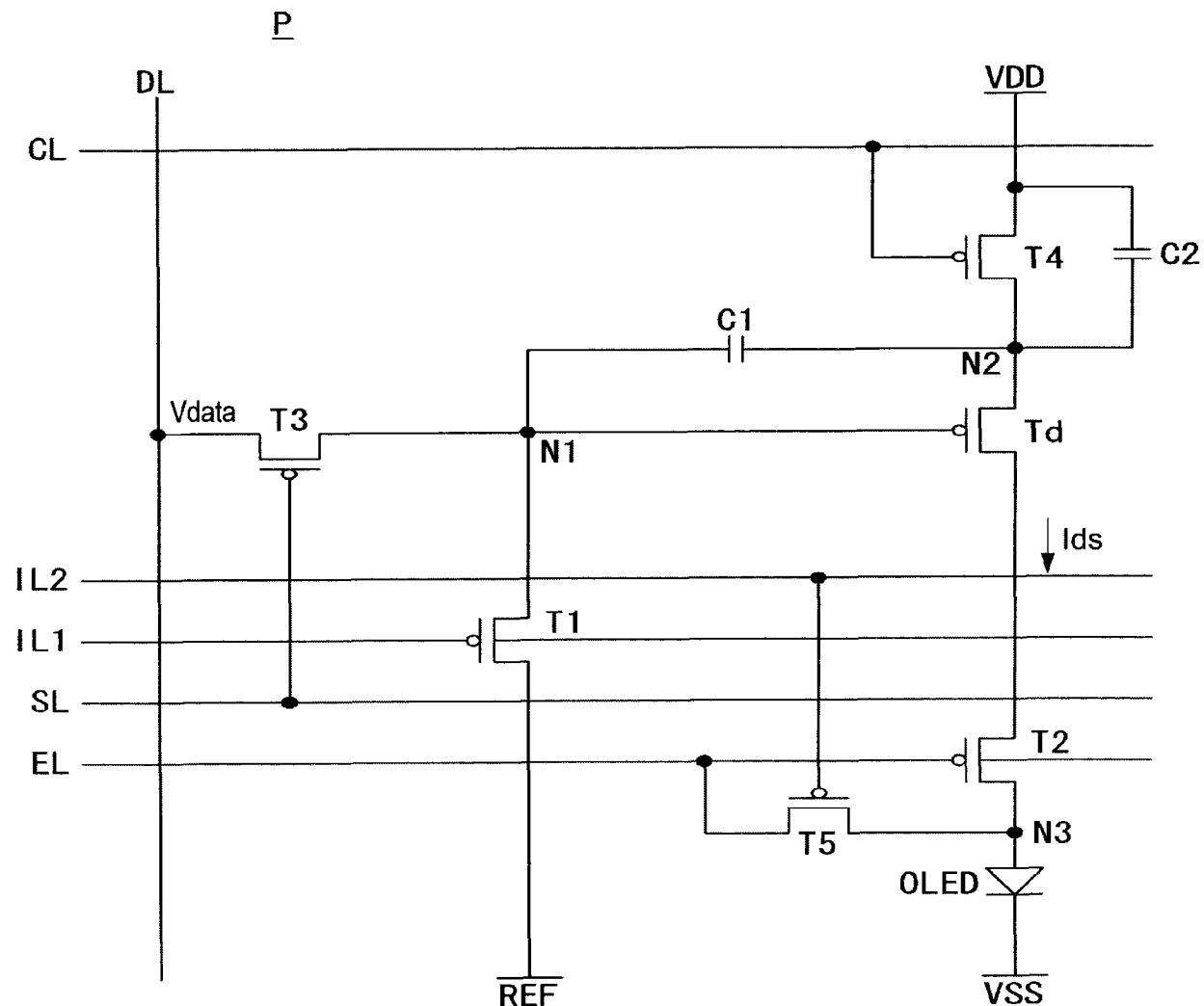

[0018] 图5是根据第四示例性实施例的显示面板的像素的等效电路图。

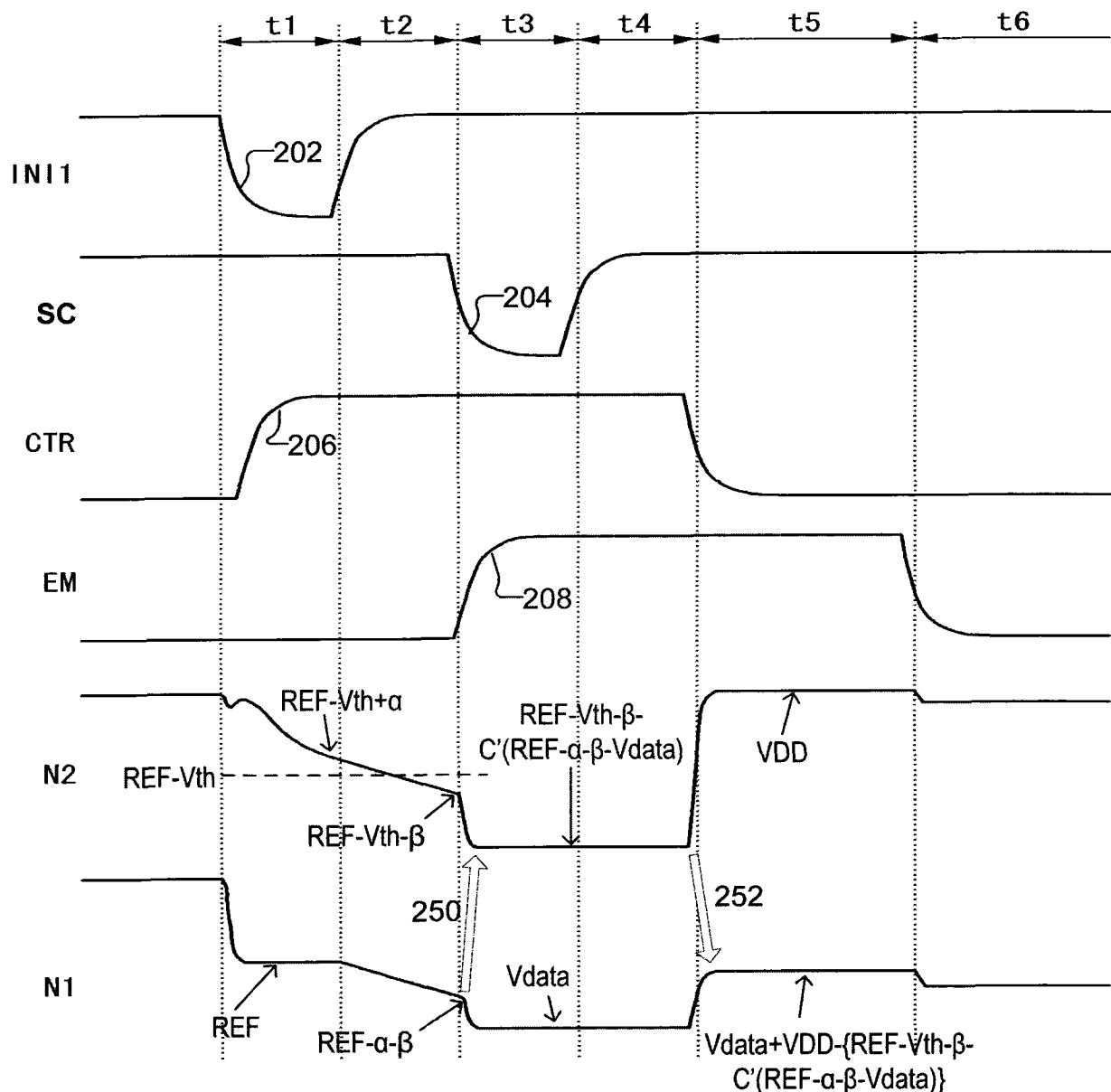

[0019] 图6是示出根据第四示例性实施例的输入至图5的像素的信号以及第一节点和第二节点的电压变化的波形图。

[0020] 图7是根据第五示例性实施例的显示面板的像素的等效电路图。

[0021] 图8是根据第六示例性实施例的显示面板的像素的等效电路图。

[0022] 图9是根据第七示例性实施例的显示面板的像素的等效电路图。

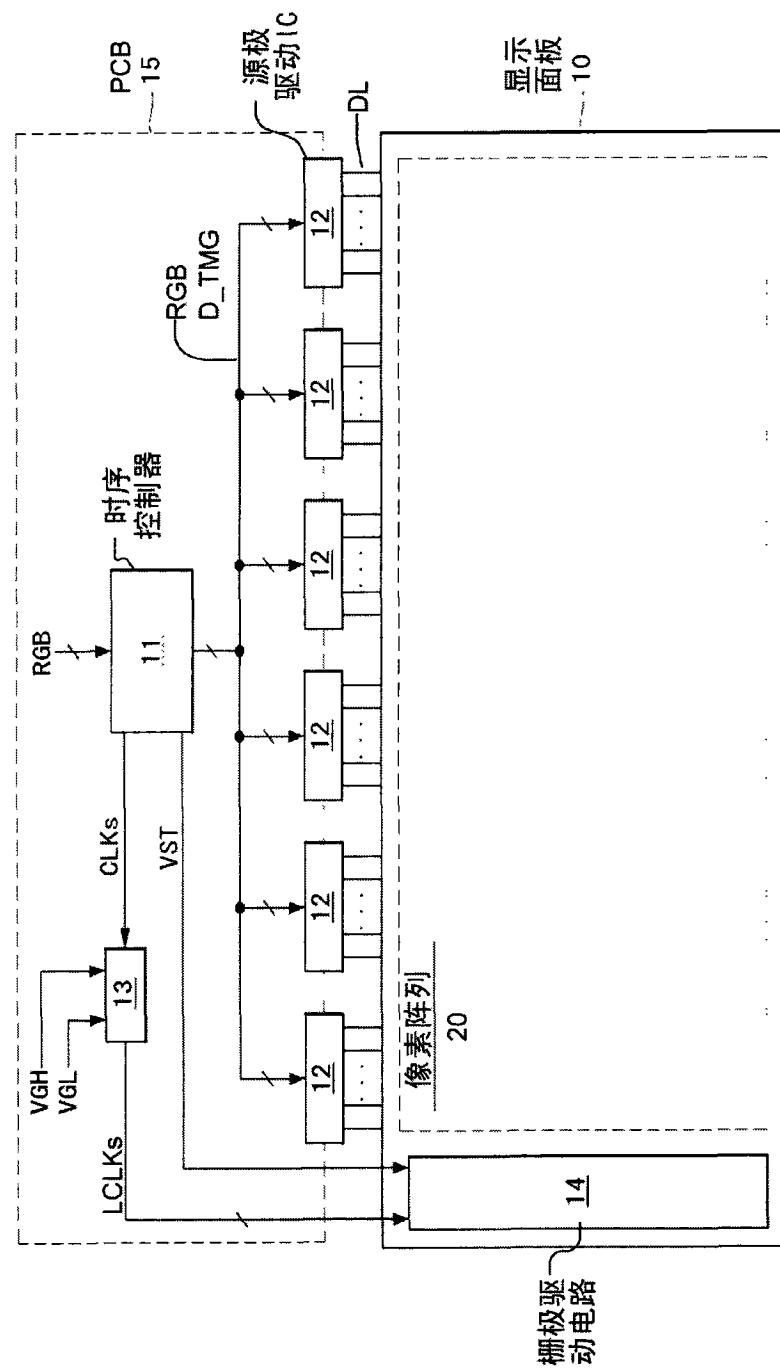

[0023] 图10是示意性地示出根据示例性实施例的有机发光二极管显示装置的方框图。

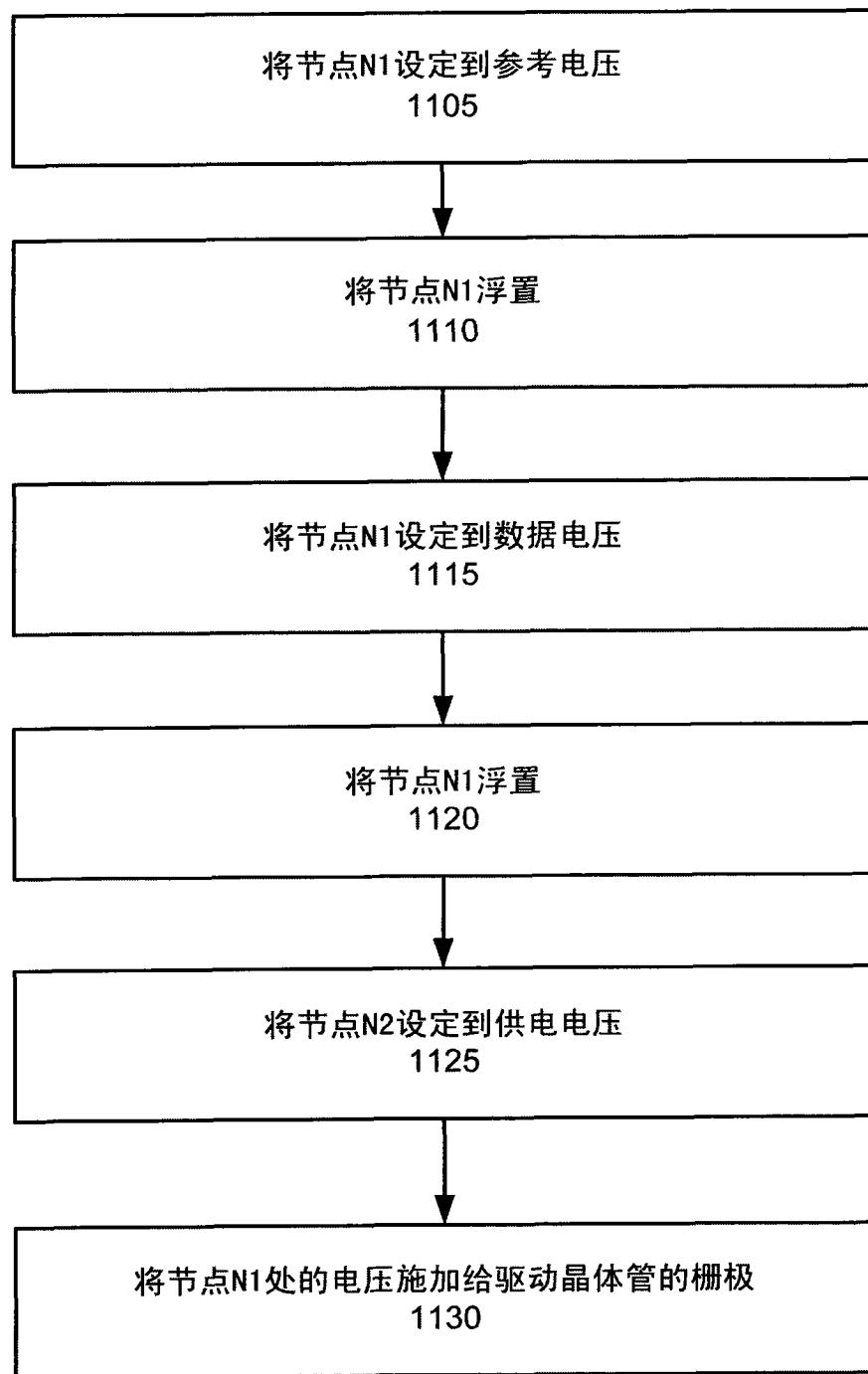

[0024] 图11是表示根据实施例的在显示装置的显示像素中的操作方法的流程图。

## 具体实施方式

[0025] 以下将参照附图详细描述本文的各个实施例。在整个说明书中，相似的附图标记可表示相似的元件。在以下的描述中，为了清楚，可省略公知的功能或结构的详细描述。只是为了方便而选择用于以下解释的各个元件的名称，这些名称可因此与它们在实际产品中

的名称不同。

[0026] 图 1 是根据第一示例性实施例的显示面板的像素的等效电路图。参照图 1, 根据第一示例性实施例的显示面板 10 的一个像素 P 由彼此交叉的一条数据线 DL 和几条脉冲线来限定。脉冲线包括 : 扫描线 SL、控制线 CL、发射线 (emission line) EL 以及第一初始化线 IL1。该像素 P 还包括 : 驱动 TFT Td、有机发光二极管 OLED 以及控制电路, 所述控制电路包括 : 第一 TFT T1、第二 TFT T2、第三 TFT T3、和第四 TFT T4。

[0027] 第一 TFT T1 是初始化晶体管, 所述初始化晶体管响应于第一初始化线 IL1 的第一初始化信号 (INI1) 而被导通或截止, 以将像素 P 的第一节点 N1 初始化至参考电压 REF。第一 TFT T1 的栅极与第一初始化线 IL1 耦接, TFT T1 的源极与第一节点 N1 耦接, 并且 TFT T1 的漏极与参考电压 REF 耦接。

[0028] 第二 TFT T2 是发射晶体管 (emission transistor), 所述发射晶体管响应于来自发射线 EL 的发射信号 (EM) 而被导通或截止, 以将驱动 TFT Td 和有机发光二极管 OLED 连接。将驱动 TFT Td 和 OLED 连接, 使得在 TFT Td 和 OLED 之间实现了电流路径 (current path), 从而使得电流能够流过 OLED。第二 TFT T2 的栅极与发射线 EL 耦接, TFT T2 的源极与驱动 TFT Td 的漏极耦接, 并且 TFT T2 的漏极与有机发光二极管 OLED 的阳极耦接。

[0029] 第三 TFT T3 是数据晶体管 (data transistor), 所述数据晶体管响应于来自扫描线 SL 的扫描信号 (SS) 而被导通或截止, 以将来自数据线 DL 的数据电压 Vdata 提供给第一节点 N1。数据电压 Vdata 代表 OLED 的预期亮度级 (intended intensity level)。数据电压 Vdata 用来将在节点 N1 处的电压电平设定至数据电压 Vdata 电平, 这进而影响流过驱动 TFT Td 的电流 Ids 和 OLED 的亮度。第三 TFT T3 的栅极与扫描线 SL 耦接, TFT T3 的源极与第一节点 N1 耦接, 并且 TFT T3 的漏极与数据线 DL 耦接。

[0030] 第四 TFT T4 是控制晶体管 (control transistor), 所述控制晶体管响应于来自控制线 CL 的控制信号 (CTR) 而被导通或截止, 以利用高供电电压 VDD 将第二节点 N2 充电。第四 TFT T4 的栅极与控制线 CL 耦接, TFT T4 的源极与高供电电压 VDD 终端耦接, 并且 TFT T4 的漏极与第二节点 N2 耦接。

[0031] 驱动 TFT Td 的栅极与第一节点 N1 耦接, TFT Td 的源极与第二节点 N2 耦接, 并且 TFT Td 的漏极与第二 TFT T2 的源极耦接。驱动 TFT Td 控制漏极和源极之间电流 Ids 的量, 这取决于施加给 TFT Td 栅极的电压的幅度 (magnitude)。

[0032] 根据第一示例性实施例的像素 P 的第一 TFT T1、第二 TFT T2、第三 TFT T3 和第四 TFT T4 以及驱动 TFT Td 每一个都可由薄膜晶体管组成。第一 TFT T1、第二 TFT T2、第三 TFT T3 和第四 TFT T4 以及驱动 TFT Td 的半导体层每一个都可由非晶硅 (a-Si)、多晶硅 (poly-Si) 以及氧化物半导体任何一种组成。此外, 第一示例性实施例被描述为集中在这样的示例, 即, 在所述示例中, 第一 TFT T1、第二 TFT T2、第三 TFT T3 和第四 TFT T4 以及驱动 TFT Td 每一个都作为 P- 型 MOS-FET 来实施。在其他实施例中, 一个或更多个 TFT 可以用 N- 型 MOS-FET 来实施。

[0033] 有机发光二极管 OLED 的阳极与第二 TFT T2 的漏极耦接, 并且有机发光二极管 OLED 的阴极与低供电电压源 VSS 耦接。有机发光二极管 OLED 根据驱动 TFT Td 的漏极和源极之间的电流 Ids 来发光。第一电容 C1 耦接在第一节点 N1 和第二节点 N2 之间。第二电容 C2 耦接在第四 TFT T4 的源极和漏极之间。

[0034] 在一个实施例中,高供电电压源 VDD 可被设定为提供高电势 DC 电压,并且低供电电压源 VSS 可被设定为提供低电势 DC 电压。参考电压 REF 是用于将第一节点 N1 初始化的电压。

[0035] 第一节点 N1 是在驱动 TFT Td 的栅极、第一 TFT T1 的源极和第三 TFT T3 的源极之间的触点。第二节点 N2 是驱动 TFT Td 的源极和第四 TFT T4 的漏极之间的触点。

[0036] 在一个实施例中,晶体管以这样的方式被导通或截止,即,所述方式是感测驱动晶体管 Td 的阈值电压  $V_{th}$ ,并且防止阈值电压  $V_{th}$  影响流过驱动晶体管 Td 的电流的量。最初,在 N1 处的电压电平被设定为 REF 电压电平,并且在 N2 处的电压慢慢地通过晶体管 Td 耗散 (dissipate)。在 N2 处的电压电平用作阈值电压  $V_{th}$  电平的指示。节点 N1 被设定至数据电压。阈值电压  $V_{th}$  的指示通过电容 C1 从节点 N2 传输至节点 N1,以在节点 N1 处产生经调整的数据电压电平。结果,阈值电压  $V_{th}$  在节点 N1 处的经调整的数据电压电平中反映出来。经调整的数据电压被施加给驱动晶体管 Td 的栅极,以控制电流  $I_{ds}$ 。因为阈值电压  $V_{th}$  已经以在 N1 处的电压表示,所以 VDD 不影响电流  $I_{ds}$  的水平。

[0037] 在一个实施例中,像素 P 中电容 C1 和 C2 的值以及晶体管 (例如 T1 和 T2) 的导通 / 截止时间被严格控制,并且防止驱动晶体管 Td 的电子迁移率影响流过驱动晶体管 Td 的电流的量。这些部件的仔细控制使得节点 N1 处的电压被精细地调谐至特定的经调整的数据电压电平。当节点 N1 处的电压随后被施加给驱动晶体管 Td 的栅极以控制电流  $I_{ds}$  时,电子迁移率不影响电流  $I_{ds}$  的水平。反而,电流  $I_{ds}$  能够可预计地被确定为  $V_{data}$  电压电平、REF 电压电平以及电容 C1 和 C2 数值的函数。

[0038] 此外,注意到显示面板具有许多像素 P,它们每一个都可接收来自公共供电电压 VDD 源的供电电压 VDD。由于面板的尺寸和从供电电压 VDD 源获得功率的像素的数量,供电电压 VDD 电平可在整个显示面板各处并不相同。更靠近供电电压 VDD 源的像素可接收较高的供电电压 VDD,而其他像素可接收较低的供电电压 VDD。

[0039] 在一个实施例中,像素 P 的操作防止在像素 P 处观察到的供电电压 VDD 的精确值影响流过驱动晶体管 Td 的电流的量。具体地,节点 N2 被设定到在像素 P 处观察到的供电电压 VDD 电平。由将节点 N2 设定到供电电压 VDD 电平引起的电压的改变通过电容 C1 施加给节点 N1,以在节点 N1 处产生经调整的数据电压电平。结果,在节点 N1 处的经调整的数据电压电平表明了供电电压 VDD 的电平。当在节点 N1 处的电压接着被施加给驱动晶体管 Td 的栅极以控制电流  $I_{ds}$  时,VDD 不影响电流  $I_{ds}$  的水平。

[0040] 现在将参照图 2 更详细地描述这些和其他实施例。

[0041] 图 2 是示出输入至图 1 的像素的信号以及第一节点和第二节点的电压改变的波形图。图 2 表示输入至显示面板 10 的像素 P 的第一初始化信号INI1、扫描信号 SC、控制信号 CTR 以及发射信号 EM。另外,图 2 表示像素 P 的第一节点 N1 和第二节点 N2 的电压改变的量。注意到可不按比例绘制波形 (例如,N1 和 N2 可相对于彼此不按比例)。

[0042] 第一初始化信号INI1、扫描信号 SC、控制信号 CTR 以及发射信号 EM 是用于控制像素 P 的第一 TFT T1、第二 TFT T2、第三 TFT T3 和第四 TFT T4 的信号。每个信号在栅极低电压 VGL 和栅极高电压 VGH 之间摆动 (swing)。在一个实施例中,栅极高电压 VGH 被设定在约 14V 与 20V 之间,而栅极低电压 VGL 被设定在约 -12V 与 -5V 之间。

[0043] 如图 2 所示,每个信号都包括信号“脉冲”。第一初始化信号INI1 包括周期 t1 期

间的第一初始化脉冲 202。扫描信号 SC 包括周期 t3 期间的扫描脉冲 204。控制信号 CTR 包括周期 t1、t2、t3 和 t4 期间的控制脉冲 206。发射信号 EM 包括周期 t3、t4 和 t5 期间的发射脉冲 208。

[0044] 第一初始化脉冲 202 和扫描脉冲 204SC 产生于栅极低电压 VGL。相反，控制脉冲 206 和发射脉冲 208 产生于栅极高电压 VGH。另外，在每一帧周期期间，周期地产生这些脉冲。帧周期指的是与单一图像帧有关的一段时间。帧周期的长度可由其中像素 P 正被使用的显示面板的刷新率 (refresh rate) 来控制。

[0045] 在产生扫描脉冲 204 和发射脉冲 208 之前产生第一初始化脉冲 202 和控制脉冲 206。第一初始化脉冲 202 和扫描脉冲 204 具有比控制脉冲 206 和发射脉冲 208 的脉冲宽度短的脉冲宽度。第一初始化脉冲 202 可具有与扫描脉冲 204 相同的脉冲宽度。控制脉冲 206 和发射脉冲 208 可具有相同的脉冲宽度。

[0046] 以下将参照图 1 和图 2 详细描述在周期 t1 至 t6 期间根据第一示例性实施例的像素 P 的操作。一般而言，在周期 t1 和 t2 期间，驱动 TFT Td 的阈值电压 Vth 被感测并在节点 N2 处的电压电平中反映出来。在周期 t3 和 t4 期间，接收数据电压 Vdata 并且所述数据电压 Vdata 被用来设定节点 N1 处的电压。在周期 t5 期间，将阈值电压 Vth 传输至节点 N1。此外，在周期 t5 期间，在显示面板各处的高供电电压 VDD 的压降被补偿。在周期 t6 期间，有机发光二极管 (OLED) 发光。

[0047] 在周期 t1 期间，产生具有栅极低电压 VGL 的第一初始化信号INI1 和发射信号EM。此外，产生具有栅极高电压 VGH 的扫描信号 SC 和控制信号 CTR。

[0048] 第一 TFT T1 响应于第一初始化信号INI1 被导通，以将第一节点 N1 初始化至参考电压 REF。第二 TFT T2 响应于发射信号EM 被导通，以将驱动 TFT Td 的漏极与有机发光二极管 OLED 的阳极连接。第三 TFT T3 被扫描信号 SP 截止。第四 TFT T4 被控制信号 CTR 截止。

[0049] 因为第一节点 N1 被初始化至参考电压 REF，所以在驱动 TFT Td 的栅极和源极之间的压差 Vgs 变得大于阈值电压 Vth。然后电流流过 TFT Td 并慢慢降低在驱动 TFT Td 的源极处的电压。在周期 t1 期间，由于诸如驱动 TFT Td 的沟道电阻等的非理想因素，所述降低不是瞬时的。

[0050] 如果周期 t1 的长度是无限的，则在栅极和源极之间的压差 Vgs 会最终达到阈值电压 Vth，于是电流会停止流过 TFT Td。因此，如果周期 t1 有足够长度，则，驱动 TFT Td 的源极（即节点 N2）的电压在周期 t1 的结束时会被降低至参考电压 REF 和阈值电压 Vth 之间的压差 REF-Vth。

[0051] 然而，因为 t1 具有期限，所以第二节点 N2 的电压在周期 t1 的结束时可不完全地降低到压差 REF-Vth。反而，第二节点 N2 的电压在周期 t1 的结束时可降低到“REF-Vth+ $\alpha$ ”，所述“REF-Vth+ $\alpha$ ”是通过将  $\alpha$  加到压差 REF-Vth 得到的。 $\alpha$  可以被看作为一预定值，该预定值表示由驱动 TFT Td 的沟道电阻引起的误差。因此， $\alpha$  越大，用节点 N2 处的电压电平来感测阈值电压的误差越大。

[0052] 此外，驱动 TFT Td 的电子迁移率可与 TFT Td 的沟道电阻或类似项对应。例如，沟道电阻越大，驱动 TFT Td 的电子迁移率越低。换句话说，因为  $\alpha$  随沟道电阻的增加而增加，所以驱动 TFT Td 的电子迁移率与  $\alpha$  的值有关。在一个实施例中，通过控制 t1 的长度使得

在节点 N2 处的电压等于在周期 t1 的结束时的“REF-V<sub>th</sub>+α”，然后控制周期 t2 的时序以及 C1 和 C2 的电容值，驱动 TFT Td 的电子迁移率可被补偿，如同将要被详细解释的。

[0053] 在周期 t2 期间，产生具有栅极低电压 VGL 的发射信号 EM。此外，产生每一个都具有栅极高电压 VGH 的第一初始化信号 INI1、扫描信号 SC 和控制信号 CTR。

[0054] 第二 TFT T2 响应于发射信号 EM 而被导通。当导通时，TFT T2 将驱动 TFT Td 的漏极和有机发光二极管 OLED 的阳极连接。第一 TFT T1 被第一初始化信号 INI1 截止。第三 TFT T3 被扫描信号 SC 截止。第四 TFT T4 被控制信号 CTR 截止。

[0055] 第一节点 N1 在第二周期 t2 期间浮置。第二节点 N2 的电压通过驱动晶体管 Td 放电，并且因为两节点 N1 和 N2 通过电容 C1 彼此耦接，所以在节点 N2 处的电压的下降影响浮置节点 N1 处的电压。因此，在节点 N1 和 N2 处的电压一起逐渐降低。

[0056] 在 N2 处的电压电平从周期 t2 的开始时的“REF-V<sub>th</sub>+α”下降到周期 t2 的结束时的“REF-V<sub>th</sub>-β”。β 简单地表示发生在节点 N2 的电压达到“REF-V<sub>th</sub>”的电压电平之后的电压降低的量。于是，如第二节点 N2 处电压的公式所示，N2 处的电压继续反映第二周期 t2 期间的驱动 TFT Td 的阈值电压。

[0057] 第二节点在周期 t2 期间的电压改变的量是“-α-β”。在周期 t2 期间，电压改变的这个量通过第一电容 C1 施加给第一节点 N1。结果，第一节点 N1 的电压在周期 t2 的结束时降低至“REF-α-β”。

[0058] 在周期 t3 期间，产生具有栅低压 VGL 的扫描信号 SC。此外，产生每一个都具有栅极高电压的第一初始化信号 INI1、控制信号 CTR 和发射信号 EM。

[0059] 第三 TFT T3 响应于扫描信号 SC 而被导通，以将数据线 DL 的数据电压 Vdata 施加给第一节点 N1。第一 TFT T1 被第一初始化信号 INI1 截止。第二 TFT T2 被发射信号 EM 截止。第四 TFT T4 被控制信号 CTR 截止。

[0060] 在周期 t3 期间，第一节点 N1 被设定到数据电压 Vdata。第一节点 N1 的电压改变的量“REF-α-β-Vdata”通过第一电容 C1 被施加给第二节点 N2(250)。第二节点 N2 位于串联的第一电容 C1 和第二电容 C2 之间。于是，在节点 N2 处的电压改变的量是基于比值 C'，如等式 2 所示：

[0061] [等式 2]

$$[0062] C' = \frac{CA1}{CA1+CA2}$$

[0063] 在等式 2 中，CA1 表示第一电容 C1 的电容量，并且 CA2 表示第二电容 C2 的电容量。因此，第二节点 N2 的电压在周期 t3 期间降低到“REF-V<sub>th</sub>-β-C' (REF-α-β-Vdata)”。

[0064] 因为等式 2 可被重写为  $1/(1+CA2/CA1)$ ，因此 C' 还以看作是基于 C2 与 C1 的电容值的比。如将要更详细的解释的，CA1 和 CA2 的电容值可被设定为这样的值，所述值在周期 t6 中抵消了 α 和 β 对通过 LED 发出的光的影响。

[0065] 在周期 t4 期间，产生每一个都具有栅极高电压 VGH 的第一初始化信号 INI1、扫描信号 SC、控制信号 CTR 和发射信号 EM。

[0066] 第一 TFT T1 被第一初始化信号 INI1 截止。第二 TFT T2 被发射信号 EM 截止。第三 TFT T3 被扫描信号 SC 截止。第四 TFT T4 被控制信号 CTR 截止。N1 和 N2 的电压电平在

周期 t4 期间保持相对不变。

[0067] 在周期 t4 期间,通过使第一 TFT T1 和第三 TFT T3 二者都截止而使节点 N1 有效地浮置。周期 t4 可被看作稳定周期,确保在第四 TFT T4 在周期 T5 中导通之前节点 N1 浮置。

[0068] 在周期 t5 期间,产生具有栅极低电压 VGL 的控制信号 CTR。此外,产生每一个都具有栅极高电压的第一初始化信号 INI1、扫描信号 SC 和发射信号 EM。

[0069] 第四 TFT T4 响应于控制信号 CTR 而被导通,以将高供电电压 VDD 的终端与第二节点 N2 连接。第一 TFT T1 被第一初始化信号 INI1 截止。第二 TFT T2 被发射信号 EM 截止。第三 TFT T3 被扫描信号 SC 截止。

[0070] 在周期 t5 的开始,第二节点 N2 的电压升高到高供电电压 VDD。第二节点 N2 的电压改变的量“ $VDD - \{REF - Vth - \beta - C' (REF - \alpha - \beta - Vdata)\}$ ”通过第一电容 C1 施加给第一节点 N1 (252)。因此,第一节点 N1 的电压从 Vdata 增加到“ $Vdata + VDD - \{REF - Vth - \beta - C' (REF - \alpha - \beta - Vdata)\}$ ”。在第一节点 N1 处的电压因此是经调整的数据电压,该经调整的数据电压说明数据电压 Vdata 和阈值电压 Vth 二者。

[0071] 在周期 t6 期间,产生具有栅极低电压 VGL 的发射信号 EM。此外,产生每一个都具有栅极高电压 VGH 的第一初始化信号 INI1、扫描信号 SC 和控制信号 CTR。

[0072] 第二 TFT T2 响应于发射信号 EM 而被导通,以将驱动 TFT Td 与有机发光二极管 OLED 连接。第一 TFT T1 被第一初始化信号 INI1 截止。第三 TFT T3 被扫描信号 SC 截止。第四 TFT T4 被控制信号 CTR 截止。

[0073] 在周期 t6 的开始,因为电流开始流过控制晶体管 T4 并流到 OLED,所以在节点 N2 处的电压轻微地降低。轻微的电压降低可由控制晶体管 T4 的漏 - 源接通电阻 (drain-to-source resistance) 引起。在节点 N2 处的电压降低通过电容 C1 被施加给节点 N2,并在节点 N2 处的经调整的数据电压中反映出来。因为这个电压降低相对小并且不影响驱动晶体管 Td 的 Vgs 电压,因此为了清楚,在以下的讨论中将忽略。

[0074] 在周期 t6 期间,在驱动 TFT Td 的漏极和源极之间的电流 Ids 通过第二 TFT T2 被施加给有机发光二极管 OLED。有机发光二极管 OLED 根据在驱动 TFT Td 的漏极和源极之间的电流 Ids 来发光。驱动 TFT Td 的漏极和源极之间的电流 Ids 可由等式 3 来表示 :

[0075] [ 等式 3 ]

$$I_{ds} = k' \cdot (V_{gs} - V_{th})^2$$

[0077] 在等式 3 中,  $k'$  表示由驱动 TFT 的结构和物理性质所确定的比例系数,这由驱动 TFT Td 的迁移率、沟道宽度、沟道长度等确定。Vgs 表示在驱动 TFT Td 的栅极和源极之间的压差,并且 Vth 表示驱动 TFT Td 的阈值电压。在周期 t6 期间的  $Vgh - Vth$  如等式 4 所示 :

[0078] [ 等式 4 ]

$$V_{gs} - V_{th} = [Vdata + VDD - \{REF - Vth - \beta - C' (REF - \alpha - \beta - Vdata)\} - VDD] - Vth$$

[0080] 在等式 4 中,在驱动 TFT Td 的漏极和源极之间的电流 Ids 由等式 5 导出 :

[0081] [ 等式 5 ]

$$I_{ds} = k' [(1 - C') \cdot (Vdata - REF) + \beta - C' (\alpha + \beta)]^2$$

[0083] 在等式 5 中,如果第二电容 C2 的电容量 CA2 被设定为是第一电容 C1 的电容量 CA1 的 4 倍,则 C' 算得为 0.2。通过调整周期 t1 和周期 t2 的长度,  $\alpha$  和  $\beta$  的比可以被设定为

$\alpha = 4\beta$ 。如果  $C' = 0.2$  且  $\alpha = 4\beta$ , 则  $\beta - C'(\alpha + \beta)$  算得为 0 并可从等式 5 中去掉。结果, 在驱动 TFT Td 的漏极和源极之间的电流  $I_{ds}$  可由等式 6 表示:

[0084] [等式 6]

$$[0085] I_{ds} = k' [(1-C') \cdot (V_{data}-REF)]^2$$

[0086] 如等式 6 所示, 在周期  $t_6$  期间施加给有机发光二极管 OLED 的、在驱动 TFT Td 的源极和漏极之间的电流  $I_{ds}$  只取决于比例系数  $k'$ 、电容  $C_1$  和  $C_2$  的值、数据电压  $V_{data}$  和参考电压  $REF$ 。电流  $I_{ds}$  不取决于驱动 TFT Td 的阈值电压  $V_{th}$ 。因此, 驱动 TFT Td 的阈值电压  $V_{th}$  被补偿。

[0087] 还如等式 6 所示, 在周期  $t_6$  期间施加给有机发光二极管 OLED 的、在驱动 TFT Td 的源极和漏极之间的电流  $I_{ds}$  不取决于  $\alpha$ 。因此, 驱动 TFT Td 的电子迁移率被补偿。

[0088] 还如等式 6 所示, 在周期  $t_6$  期间施加给有机发光二极管 OLED 的、在驱动 TFT Td 的源极和漏极之间的电流  $I_{ds}$  不取决于供电电压  $VDD$ 。因此, 从一个像素到下一个像素的在显示面板各处的供电电压  $VDD$  上的任何下降都被补偿。

[0089] 图 3 是根据第二示例性实施例的显示面板的像素的等效电路图。根据第二示例性实施例的显示面板 10 的像素 P 的控制电路包括第五 TFT T5, 所述第五 TFT T5 用作 OLED 旁路晶体管 (bypass transistor)。当不希望 OLED 发光时, 第五 TFT T5 在时间周期 (例如周期  $t_1$ ) 期间使电流绕过 OLED。

[0090] 第五 TFT T5 响应于第一初始化线 IL1 的第一初始化信号 INI1 而被导通, 以利用低供电电压  $VSS$  使第三节点 N3 放电。第五 TFT T5 的栅极与第一初始化线 IL1 耦接, 第五 TFT T5 的源极与第三节点 N3 耦接, 并且第五 TFT T5 的漏极与低供电电压  $VSS$  的终端耦接。第三节点 N3 是第二 TFT T2 的漏极、第五 TFT T5 的源极以及有机发光二极管 OLED 的阳极之间的触点。

[0091] 根据第二示例性实施例的像素 P 的第五 TFT T5 可由薄膜晶体管组成。第五 TFT T5 的半导体层可由 a-Si、poly-Si 以及氧化物半导体任何一种组成。此外, 已经用一示例描述了第二示例性实施例, 在所述示例中, 第五 TFT T5 作为 P- 型 MOS-FET 来实施。在其他实施例中, 第五 TFT T5 可作为 N- 型 MOS-FET 来实施。

[0092] 图 3 的根据第二示例性实施例的显示面板的像素 P 的剩余配置与图 1 所示的第一示例性实施例基本相同。以下将参照图 2 和图 3 详细描述图 3 的像素 P 的操作。

[0093] 在周期  $t_1$  期间, 产生具有栅极低电压  $VGL$  的第一初始化信号 INI1。第五 TFT T5 响应于第一初始化信号 INI1 而被导通, 以利用低供电电压  $VSS$  使第三节点 N3 放电。

[0094] 因为由于第五 TFT T5 的导通的缘故, 利用低供电电压  $VSS$  使有机发光二极管 OLED 的阳极放电, 所以驱动 TFT Td 的感测电流在周期  $t_1$  期间没有施加给有机发光二极管 OLED。因此, 由于驱动 TFT Td 的感测电流的缘故, 有机发光二极管 OLED 在周期  $t_1$  期间不发光, 从而防止图像失真, 并且增大对比度。

[0095] 图 3 的像素 P 在周期  $t_2$  至  $t_6$  期间的剩余操作与已经参照图 1 和图 2 描述的第一示例性实施例基本相同。

[0096] 图 4 是根据第三示例性实施例的显示面板的像素的等效电路图。参照图 4, 根据第三示例性实施例的显示面板 10 的像素 P 的第五 TFT T5 响应于扫描线 SL 的扫描信号 SC 而被导通, 以利用低供电电压  $VSS$  使第三节点 N3 放电, 从而使电流绕过 OLED。第五 TFT T5

的栅极与扫描线 SL 耦接,第五 TFT T5 的源极与第三节点 N3 耦接,并且第五 TFT T5 的漏极与低供电电压 VSS 的终端耦接。

[0097] 根据图 4 的第三示例性实施例的显示面板的像素 P 的剩余操作与已经参照图 1 描述的第一示例性实施例基本相同。以下将参照图 2 和图 4 详细描述图 4 的像素 P 的操作。

[0098] 在周期 t3 期间,产生具有栅极低电压 VGL 的扫描信号 SC。第五 TFT T5 响应于扫描信号 SC 而被导通,以利用低供电电压 VSS 使第三节点 N3 放电。

[0099] 因为由于第五 TFT T5 的导通的缘故,利用低供电电压 VSS 使有机发光二极管 OLED 的阳极放电,所以驱动 TFT Td 的漏电流在周期 t3 期间没有施加给有机发光二极管 OLED。因此,由于驱动 TFT Td 的漏电流的缘故,有机发光二极管 OLED 在周期 t3 期间不发光,从而防止图像失真,并且增大对比度。

[0100] 图 4 的像素 P 在周期 t1、t2 和 t4 至 t6 期间的剩余操作与已经参照图 1 和图 2 描述的第一示例性实施例基本相同。

[0101] 图 5 是根据第四示例性实施例的显示面板的像素的等效电路图。参照图 5,根据第四示例性实施例的显示面板 10 的像素 P 的第五 TFT T5 响应于第二初始化线 IL2 的第二初始化信号 INI2 而被导通,以利用第一电压 V1 使第三节点 N3 放电。第五 TFT T5 的栅极与第二初始化线 IL2 耦接,第五 TFT T5 的源极与第三节点 N3 耦接,并且第五 TFT T5 的漏极与第一电压 V1 的终端耦接。

[0102] 第二初始化线 IL2 可与第一初始化线 IL1 平行的形成。第一电压 V1 可被设定到比有机发光二极管 OLED 的阈值电压 Vth 低的电压,例如,低供电电压 VSS。

[0103] 根据图 5 的第四示例性实施例的显示面板的像素 P 的剩余配置与已经参照图 3 描述的第二示例性实施例基本相同。

[0104] 图 6 是示出输入至图 5 的像素的信号以及第一节点和第二节点的电压改变的波形图。参照图 6,第二初始化信号 INI2 显示为在周期 t1 期间的具有第二初始化脉冲 602。可在每一帧期间重复产生第二初始化脉冲 602。此外,在每一帧周期产生第二初始化脉冲 602。第二初始化脉冲 602 产生于栅极低电压 VGL。在产生扫描脉冲 204 和发射脉冲 208 之前产生第二初始化脉冲。第二初始化脉冲 602 还具有比控制脉冲 206 和发射脉冲 208 短的脉冲宽度。第二初始化脉冲 602 可具有与第一初始化脉冲 202 相同的脉冲宽度,并且可与第一初始化脉冲 202 同步的产生。

[0105] 图 6 的波形图的剩余部分与已参照图 1 描述的波形图的剩余部分基本相同。以下将参照图 5 和图 6 详细描述根据第四示例性实施例的显示面板 10 的像素 P 的操作。

[0106] 在周期 t1 期间,产生具有栅极低电压 VGL 的第二初始化信号 INI2。第五 TFT T5 响应于第二初始化信号 INI2 而被导通,以利用第一电压 V1 使第三节点 N3 放电,从而使电流绕过 OLED。

[0107] 因为由于第五 TFT T5 导通的缘故,利用第一电压 V1 使有机发光二极管 OLED 的阳极放电,所以驱动 TFT Td 的感测电流在周期 t1 期间没有施加给有机发光二极管 OLED。因此,由于驱动 TFT Td 的感测电流的缘故,有机发光二极管在周期 t1 期间不发光,从而防止图像失真,并且增大对比度。

[0108] 在一些实施例中,第二初始化信号 INI2 可在周期 t1 和周期 t2 二者期间都具有栅极低电压 VGL。因此第五 TFT T5 在周期 t1 和周期 t2 二者期间都被导通,以防止有机发光

二极管 OLED 在周期 t1 和周期 t2 二者期间发光。

[0109] 根据图 5 的第四示例性实施例的显示面板的像素 P 的剩余配置与已经参照图 1 和图 2 描述的第一示例性实施例基本相同。

[0110] 图 7 是根据第五示例性实施例的显示面板的像素的等效电路图。参照图 7, 根据第五示例性实施例的显示面板 10 的像素 P 的第五 TFT T5 响应于第二初始化线 IL2 的第二初始化信号 INI2 而被导通, 以利用低供电电压 VSS 使第三节点 N3 放电。第五 TFT T5 的栅极与第二初始化线 IL2 耦接, 第五 TFT T5 的源极与第三节点 N3 耦接, 并且第五 TFT T5 的漏极与低供电电压 VSS 的终端耦接。

[0111] 根据图 7 的第五示例性实施例的显示面板的像素 P 的剩余配置与已经参照图 5 描述的第四示例性实施例基本相同。以下将参照图 6 和图 7 详细描述图 7 的像素 P 的操作。

[0112] 在周期 t1 期间, 产生具有栅极低电压 VGL 的第二初始化信号 INI2。第五 TFT T5 响应于第二初始化信号 INI2VGL 而被导通, 以利用低供电电压 VSS 使第三节点 N3 放电, 从而使电流绕过 OLED。

[0113] 因为由于第五 TFT T5 导通的缘故, 利用低供电电压 VSS 使有机发光二极管 OLED 的阳极放电, 所以驱动 TFT Td 的感测电流在周期 t1 期间没有施加给有机发光二极管 OLED。因此, 由于驱动 TFT Td 的感测电流的缘故, 有机发光二极管在周期 t1 期间不发光, 从而防止图像失真, 并且增大对比度。

[0114] 根据图 7 的第五示例性实施例的显示面板的像素 P 的剩余操作与已经参照图 1 和图 2 描述的第一示例性实施例基本相同。

[0115] 图 8 是根据第六示例性实施例的显示面板的像素的等效电路图。参照图 8, 根据第六示例性实施例的显示面板的像素 P 的第五 TFT T5 响应于第二初始化线 IL2 的第二初始化脉冲 INI2 而被导通, 以将第三节点 N3 与第二初始化线 IL2 连接。第五 TFT T5 的栅极与第二初始化线 IL2 耦接, 第五 TFT T5 的源极与第三节点 N3 耦接, 并且第五 TFT T5 的漏极与栅极耦接。也就是, 第五 TFT T5 是二极管接法的 (diode-connected)。

[0116] 根据图 8 的第六示例性实施例的显示面板的像素 P 的剩余配置与已经参照图 5 描述的第四示例性实施例基本相同。以下将参照图 6 和图 8 详细描述图 8 的像素 P 的操作。

[0117] 在周期 t1 期间, 产生栅极低电压 VGL 的第二初始化脉冲 INI2。第五 TFT T5 响应于栅极低电压 VGL 的第二初始化脉冲 INI2 而被导通, 以利用栅极低电压 VGL 使第三节点 N3 放电, 从而使电流绕过 OLED, 所述栅极低电压 VGL 是第二初始化线 IL2 的电压。

[0118] 因为由于第五 TFT T5 导通的缘故, 利用栅极低电压 VGL 使有机发光二极管 OLED 的阳极放电, 所以驱动 TFT Td 的感测电流在周期 t1 期间没有施加给有机发光二极管 OLED。因此, 由于驱动 TFT Td 的感测电流的缘故, 有机发光二极管 OLED 在周期 t1 期间不发光, 从而防止图像失真, 并且增大对比度。

[0119] 根据图 8 的第六示例性实施例的显示面板的像素 P 的剩余操作与已经参照图 1 和图 2 描述的第一示例性实施例基本相同。

[0120] 图 9 是根据第七示例性实施例的显示面板的像素的等效电路图。参照图 9, 根据第七示例性实施例的显示面板的像素 P 的第五 TFT T5 响应于第二初始化线 IL2 的第二初始化脉冲 INI2 而被导通, 以将第三节点 N3 与发射线 EL 连接。第五 TFT T5 的栅极与第二初始化线 IL2 耦接, 第五 TFT T5 的源极与第三节点 N3 耦接, 并且第五 TFT T5 的漏极与发射

线 EL 耦接。

[0121] 根据图 9 的第七示例性实施例的显示面板的像素 P 的剩余配置与已经参照图 5 描述的第四示例性实施例基本相同。以下将参照图 6 和图 9 详细描述根据第七示例性实施例的显示面板的像素 P 的操作。

[0122] 在周期 t1 期间,产生栅极低电压 VGL 的第二初始化脉冲 INI2。第五 TFT T5 响应于栅极低电压 VGL 的第二初始化脉冲 INI2 而被导通,以利用栅极低电压 VGL 使第三节点 N3 放电,从而使电流绕过 OLED,所述栅极低电压 VGL 是发射线 EL 的电压。

[0123] 因为由于第五 TFT T5 导通的缘故,利用栅极低电压 VGL 使有机发光二极管 OLED 的阳极放电,所以驱动 TFT Td 的感测电流在周期 t1 期间没有施加给有机发光二极管 OLED。因此,由于驱动 TFT Td 的感测电流的缘故,有机发光二极管 OLED 在周期 t1 期间不发光,从而防止图像失真,并且增大对比度。

[0124] 根据图 9 的第七示例性实施例的显示面板的像素 P 的剩余操作与已经参照图 1 和图 2 描述的第一示例性实施例基本相同。

[0125] 图 10 是示意性地示出根据示例性实施例的有机发光二极管显示装置的方框图。参照图 10,根据示例性实施例的有机发光二极管显示装置包括:显示面板 10、数据驱动电路(例如可以包括源极驱动 IC 12)、栅极驱动电路 14 以及时序控制器 11。

[0126] 显示面板 10 具有彼此交叉的数据线 DL 和扫描线 SL(未示出)。此外,显示面板 10 具有与扫描线 SL(未示出)平行的第一初始化线 IL1(未示出)、控制线 CL(未示出)以及发射线 EL(未示出)。显示面板 10 可额外具有与第一初始化线 IL1(未示出)平行的第二初始化线 IL2(未示出)。显示面板 10 包括像素阵列,所述像素阵列具有在由数据线 DL 和扫描线 SL 限定的单元区域(cell area)中以矩阵形式设置的像素。前文通过参照图 1 至图 9 描述了显示面板 10 的像素阵列的每个像素 P 的详细说明。

[0127] 数据驱动电路包括多个源极驱动 IC 12。源极驱动 IC 12 接收来自时序控制器 11 的数字视频数据 RGB。源极驱动 IC 12 响应于来自时序控制器 11 的源极时序控制信号 D\_TMG 而将数字视频数据 RGB 转换为伽马校正电压以产生数据电压,并将数据电压同步于来自栅极驱动电路 14 的扫描脉冲提供给在显示面板组件 10 的数据线 DL。可通过 COG(chip on glass, 玻载芯片) 工艺或 TAB(tape automated bonding, 带式自动接合) 工艺将源极驱动 IC 12 与显示面板组件 10 中的数据线 DL 耦接。

[0128] 电平移位器 13 对从时序控制器 11 输出的各时钟 CLK 的 TTL(晶体管-晶体管-逻辑)电平电压进行电平移位,使其具有栅极高电压 VGH 和栅极低电压 VGL。将各个电平移位的时钟 LCLK 输入至栅极驱动电路 14。

[0129] 栅极驱动电路 14 包括:扫描信号输出单元(未示出)、第一初始化信号输出单元(未示出)、控制信号输出单元(未示出)以及发射信号输出单元(未示出)。扫描信号输出单元与显示面板 10 的扫描信号 SL 连接。扫描信号输出单元输出扫描信号 SC,所述扫描信号 SC 包括顺序扫描脉冲。第一初始化信号输出单元与显示面板 10 的第一初始化线 IL1 连接。第一初始化信号输出单元输出用于控制每个像素的初始化的初始化信号 INI,所述初始化信号 INI 包括顺序输出初始化脉冲。控制信号输出单元与显示面板 10 的控制线 CL 连接。控制信号输出单元输出控制信号 CTR,所述控制信号 CTR 包括顺序输出控制脉冲。发射信号输出单元与发射线 EL 连接。发射信号输出单元输出发射信号 EM,所述发射信号 EM 包

括用于控制有机发光二极管 OLED 的发光的发射脉冲。

[0130] 此外,栅极驱动电路 14 可进一步包括第二初始化信号输出单元(未示出)。第二初始化信号输出单元与显示面板 10 的第二初始化线 IL2 连接。第二初始化信号输出单元输出第二初始化信号 INI2,所述第二初始化信号 INI2 包括第二初始化脉冲 INI2 以控制比有机发光二极管 OLED 的阈值电压 Vth 低的电压提供给有机发光二极管 OLED 的阳极。前文通过参照图 1 至图 9 描述了扫描信号 SC、第一初始化信号 INI1 和第二初始化信号 INI2、控制信号 CTRL 以及发射信号 EM 的详细说明。

[0131] 通过 GIP(gate in panel, 板内选通) 方案,可在显示面板 10 的下基板上直接形成栅极驱动电路 14。通过 GIP 方案,可在印刷电路板 15 上安装电平移位器 13,并且可在显示面板 10 的下基板上形成栅极驱动电路 14。如果通过 TAB 方案连接栅极驱动电路,则栅极驱动电路 14 可连接在显示面板 10 和时序控制器 11 之间。

[0132] 时序控制器 11 通过接口接收来自外部主机系统的数字视频数据 RGB,所述接口诸如是 LVDS(low voltage differential signaling, 低压差分信令) 接口、TMDS(transition minimized differential signaling, 最小化传输差分信令) 接口或者类似接口。时序控制器 11 把从主机系统输入的数字视频数据 RGB 传输至源极驱动 IC 12。

[0133] 时序控制器 11 通过 LVDS 或 TMDS 接口接收电路(未示出)接收来自主机系统的时序信号,所述时序信号诸如是垂直同步信号 Vsync、水平同步信号 Hsync、数据使能信号 DE 和主时钟 MCLK 等等。基于来自主机系统的时序信号,时序控制器 11 产生用于控制数据驱动电路和栅极驱动电路 14 的操作时序的时序控制信号。时序控制信号包括:用于控制栅极驱动电路 14 的操作时序的栅极时序控制信号、和用于控制源极驱动 IC 12 的操作时序和数据电压的极性的数据时序信号 D\_TMG。

[0134] 用于栅极驱动电路 14 的栅极时序控制信号包括以 i(i 是大于 2 的自然数) 相位(phase) 顺序地产生的各时钟 CLK 和起始电压 VST。将起始电压 VST 输入至栅极驱动电路 14,以控制扫描信号输出单元、第一初始化信号输出单元和第二初始化信号输出单元、控制信号输出单元以及发射信号输出单元的各移位初始时序。将各时钟 CLK 输入至移位寄存器 13 并将这些时钟 CLK 移位,然后它们作为各个电平移位的时钟 LCLK 输入至栅极驱动电路 14,并且被用作用于将起始电压 VST 移位的时钟信号。

[0135] 用于源极驱动 IC 12 的数据时序控制信号 D\_TMG 包括:源极起始脉冲 SSP、源极采样时钟 SSC、极性控制信号 POL 以及源极输出使能信号 SOE 等等。源极起始脉冲 SSP 控制源极驱动 IC 12 的移位起始时序。源极采样时钟 SSC 是控制源极驱动 IC 12 中关于上升沿或下降沿的数据采样时序的时钟信号。极性控制信号 POL 控制从源极驱动 IC 12 输出的数据电压的极性。如果在时序控制器 11 与源极驱动 IC 12 之间的数据传输接口是迷你 LVDS 接口,则可省略源极起始脉冲 SSP 和源极采样时钟 SSC。

[0136] 图 11 是一流程图,该流程图表示根据实施例的在显示装置的显示像素中的操作方法。一般而言,该流程图描述图 1 至图 10 所示的各种实施例。

[0137] 在步骤 1105,通过将第一 Tft T1 导通,将节点 N1 设定到参考电压 REF 电平。将节点 N1 设定到参考电压 REF 电平使得在节点 N2 处的电压改变。在步骤 1110,通过将第一 Tft T1 截止,将节点 N1 浮置。将第一节点 N1 浮置使得在第二节点 N2 处的电压的进一步改变,所述第二节点 N2 通过第一电容 C1 与第一节点 N1 耦接。在一个实施例中,步骤 1105 和

步骤 1110 可被看做用于感测在第二节点 N2 处的驱动 Tft Td 的阈值电压 Vth 的感测步骤。

[0138] 在步骤 1115, 通过将第三 Tft T3 导通, 将节点 N1 设定到数据电压 Vdata 电平。将节点 N1 设定到数据电压 Vdata 使得在节点 N1 处的电压电平改变。由于节点 N1 和 N2 通过电容 C1 耦接, 所以将节点 N1 设定到数据电压 Vdata 还引起在节点 N2 处的电压改变。在节点 N2 处的电压改变的量可基于 C1 和 C2 的电容值的比。

[0139] 在步骤 1120, 通过将第三 Tft T3 截止, 将第一节点 N1 浮置。

[0140] 在步骤 1125, 通过将第四 Tft T4 导通, 将第二节点 N2 设定到供电电压 VDD。将节点 N2 设定到供电电压 VDD 使得经第一电容 C1 引起在节点 N1 处的数据电压 Vdata 电平的调整, 这使得在节点 N1 处产生经调整的数据电压电平。调整的量代表驱动 Tft Td 的阈值电压 Vth。调整的量还代表从像素 P 观察的供电电压 VDD 电平。在一些实施例中, 还产生节点 N1 处的经调整的数据电压来表明其他压降, 所述压降诸如是在周期 t6 的开始时的跨第四 Tft T4 的压降。

[0141] 在步骤 1130, 将节点 N1 处的经调整的数据电压施加给驱动 Tft Td 的栅极, 以在 OLED 中产生电流 Ids。因为节点 N1 处的经调整的数据电压表明驱动 Tft Td 的 Vth 和显示面板各处的 VDD 中的任何压降, 所以流过驱动 Tft Td 和 OLED 的电流的量不依赖于 Vth 和显示面板各处的 VDD 中的任何压降。

[0142] 另外, 通过将第二 Tft T2 导通, 可在步骤 1105、1110 和 1130 期间, 使得驱动 Tft Td 和 OLED 之间的电流通路能启用。通过将第二 Tft T2 截止, 可在步骤 1115、1120 和 1125 期间, 使该电流通路禁用。在一个实施例中, 通过将第五 Tft T5 导通, 在步骤 1105 中使电流绕过 OLED。

[0143] 如上所述, 在一个实施例中, 感测驱动 TFT 的阈值电压 Vth, 并且将感测的驱动 TFT 的阈值电压通过第一电容 C1 施加给像素 P 的第一节点 N1, 其与驱动 TFT Td 的栅极耦接。结果, 本发明能够补偿驱动 TFT 的阈值电压。

[0144] 此外, 在周期 t1 期间感测与驱动 TFT 的电子迁移率有关的  $\alpha$ , 在周期 t2 期间感测  $\beta$ , 并且通过第一电容和第二电容将  $\alpha$  和  $\beta$  施加给第一节点。此外, 为了补偿  $\alpha$  和  $\beta$ , 可以调整第一周期和第二周期的长度以及第一电容和第二电容的电容比。结果, 所披露的像素 P 能够补偿与驱动 TFT Td 的电子迁移率有关的  $\alpha$  和  $\beta$ 。

[0145] 另外, 该像素 P 包括 TFT T4, 所述 TFT T4 控制高供电电压 VDD 施加给第二节点, 所述第二节点与驱动 TFT Td 的源极耦接。因此, 可以将高供电电压 VDD 的压降通过第一电容 C1 施加给第一节点 N1。结果, 该像素 P 能够补偿显示面板各处的高供电电压 VDD 的压降。

[0146] 再者, 在有机发光二极管 OLED 发光之前, 利用低供电电压或者栅极低电压使有机发光二极管 OLED 的阳极放电。结果, 该像素能够防止在有机发光二极管 OLED 发光之前由驱动 TFT 的感测电流引起的发光, 从而防止图像失真, 并且增大对比度。

[0147] 尽管已经参考多个示例性的实例描述了实施例, 但是应当理解的是: 可以由所属领域技术人员构思出属于本文内容的原理范围内的大量其他改型和实施例。尤其是, 可以在本文、附图和所附权利要求书的范围内对主题组合方案的组成部件和 / 或布置作出各种变化和修改。除了组成部件和 / 或布置的变化和修改之外, 替代使用对于所属领域技术人员而言也是显而易见的。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

|                |                                                                   |         |            |

|----------------|-------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机发光二极管显示装置                                                       |         |            |

| 公开(公告)号        | <a href="#">CN102956192B</a>                                      | 公开(公告)日 | 2015-12-16 |

| 申请号            | CN201210080316.7                                                  | 申请日     | 2012-03-16 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                          |         |            |

| 申请(专利权)人(译)    | 乐金显示有限公司                                                          |         |            |

| 当前申请(专利权)人(译)  | 乐金显示有限公司                                                          |         |            |

| [标]发明人         | 韩仁孝<br>李玹行<br>韩成晚                                                 |         |            |

| 发明人            | 韩仁孝<br>李玹行<br>韩成晚                                                 |         |            |

| IPC分类号         | G09G3/32                                                          |         |            |

| CPC分类号         | G09G3/3233 G09G2300/0819 G09G2300/0852 G09G2300/0861 G09G2320/045 |         |            |

| 代理人(译)         | 徐金国                                                               |         |            |

| 审查员(译)         | 冯莹                                                                |         |            |

| 优先权            | 10201110081701 2011-08-17 KR                                      |         |            |

| 其他公开文献         | CN102956192A                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                    |         |            |

## 摘要(译)

本文涉及一种补偿驱动TFT的阈值电压、供电电压源的压降以及驱动TFT的迁移率的显示装置。显示装置可包括多个像素。至少一个像素可包括诸如第一电容、第二电容、数据晶体管、控制晶体管、发射晶体管、初始化晶体管、驱动晶体管和在其他部件中的有机发光二极管(OLED)之类的部件。