(12) 发明专利

(10) 授权公告号 CN 102592539 B

(45) 授权公告日 2016.01.20

(21) 申请号 201110344357.8

US 2007/0063933 A1, 2007.03.22, 全文.

(22) 申请日 2011.11.03

US 2010/0188316 A1, 2010.07.29, 全文.

(30) 优先权数据

审查员 勒海

10-2011-0001419 2011.01.06 KR

(73) 专利权人 三星显示有限公司

地址 韩国京畿道

(72) 发明人 张桓寿 卞昌洙

(74) 专利代理机构 北京德琦知识产权代理有限公司 11018

代理人 罗正云 宋志强

(51) Int. Cl.

G09G 3/3266(2016.01)

G11C 19/18(2006.01)

G11C 19/28(2006.01)

(56) 对比文件

CN 101527110 A, 2009.09.09, 全文.

JP 特开 2007-279667 A, 2007.10.25, 全文.

TW 201003605 A1, 2010.01.16, 全文.

权利要求书4页 说明书9页 附图5页

(54) 发明名称

发射控制线驱动器以及使用该驱动器的有机发光显示器

(57) 摘要

本发明公开了发射控制线驱动器及使用该驱动器的有机发光显示器。发射控制线驱动器能够保证输出稳定性，并能自由控制发射控制信号的宽度。发射控制线驱动器包括分别耦合到发射控制线的多级。每级包括被配置为输出发射控制信号的多个晶体管。可对应起始信号的宽度控制发射控制信号的宽度。另外，级的电路结构得以简化。

1. 一种发射控制线驱动器,包括多级,其中每级包括:

耦合在第一输出端和第一电源之间的第一晶体管,所述第一晶体管被配置为对应于施加到与所述第一晶体管的栅电极耦合的第一节点的电压被导通或截止;

耦合在所述第一输出端和输出低于所述第一电源的电压的第二电源之间的第二晶体管,所述第二晶体管被配置为对应于施加到与所述第二晶体管的栅电极耦合的第二节点的电压被导通或截止;

耦合在第四输入端和所述第一节点之间的第三晶体管,所述第三晶体管具有耦合到第一输入端的栅电极;

耦合在所述第一电源和所述第二节点之间的第四晶体管,所述第四晶体管具有耦合到所述第一节点的栅电极;

耦合到所述第一输入端和第二输入端的第一控制器,以向第二输出端提供采样信号;

耦合到所述第一输入端和第三输入端的第二控制器,以控制所述第二节点的电压;和

耦合在所述第二输入端和所述第二节点之间的第一电容器,

其中所述第一输入端被配置为接收第一时钟信号,

其中所述第二输入端被配置为接收第二时钟信号,

其中所述第三输入端被配置为接收第三时钟信号,和

其中所述第四输入端被配置为接收起始信号或前一级的采样信号。

2. 根据权利要求 1 的发射控制线驱动器,进一步包括耦合在所述第一节点和所述第一电源之间的第二电容器。

3. 根据权利要求 1 的发射控制线驱动器,其中所述第一时钟信号、所述第二时钟信号和所述第三时钟信号互不重叠。

4. 根据权利要求 1 的发射控制线驱动器,

其中所述第一时钟信号和所述第二时钟信号的每一个被设置在  $i$  水平周期的周期内,和

其中所述第三时钟信号被设置在  $i/2$  水平周期的周期内,

其中  $i$  为自然数。

5. 根据权利要求 4 的发射控制线驱动器,其中所述第三时钟信号在所述第一时钟信号或所述第二时钟信号在水平周期内被提供之后在该水平周期内被提供。

6. 根据权利要求 1 的发射控制线驱动器,其中所述第一控制器包括:

耦合在所述第四输入端和第三节点之间的第五晶体管,所述第五晶体管具有耦合到所述第一输入端的栅电极;

耦合在第六节点和所述第二输入端之间的第六晶体管,所述第六晶体管具有耦合到所述第三节点的栅电极;

耦合在所述第六节点和所述第一电源之间的第七晶体管,所述第七晶体管具有耦合到所述第一输出端的栅电极;

耦合在所述第三节点和所述第六节点之间的第三电容器;和

耦合在所述第一输出端和所述第一电源之间的第四电容器。

7. 根据权利要求 6 的发射控制线驱动器,其中所述第二输出端被电耦合到所述第六节点。

8. 根据权利要求 1 的发射控制线驱动器, 其中所述第二控制器包括 :

耦合在所述第一输入端和第四节点之间的第八晶体管, 所述第八晶体管具有耦合到所述第一节点的栅电极;

耦合在所述第四节点和所述第二电源之间的第九晶体管, 所述第九晶体管具有耦合到所述第一输入端的栅电极;

耦合在所述第二节点和第五节点之间的第十晶体管, 所述第十晶体管具有耦合到所述第三输入端的栅电极;

耦合在所述第五节点和所述第三输入端的第十一晶体管, 所述第十一晶体管具有耦合到所述第四节点的栅电极; 和

耦合在所述第四节点和所述第五节点之间的第五电容器。

9. 根据权利要求 1 的发射控制线驱动器, 进一步包括 :

耦合在所述第四输入端和所述第三晶体管之间的第十二晶体管, 所述第十二晶体管被配置为当第一控制信号被提供给所述第十二晶体管的栅电极时被导通; 和

耦合在第五输入端和所述第一控制器之间的第十三晶体管, 所述第十三晶体管被配置为当第二控制信号被提供给所述第十三晶体管的栅电极时被导通。

10. 根据权利要求 9 的发射控制线驱动器, 其中所述第一控制信号和所述第二控制信号互不重叠。

11. 根据权利要求 9 的发射控制线驱动器, 其中所述第五输入端被配置为接收起始信号或下一级的采样信号。

12. 根据权利要求 1 的发射控制线驱动器, 进一步包括耦合在所述第一节点和所述第二电源之间的第十四晶体管, 所述第十四晶体管被配置为当复位信号被提供给所述第十四晶体管的栅电极时被导通。

13. 根据权利要求 12 的发射控制线驱动器, 其中所述复位信号被共同提供给所有级。

14. 一种有机发光显示器, 包括 :

用于依次向扫描线提供扫描信号的扫描驱动器;

用于向数据线提供数据信号的数据驱动器;

用于向发射控制线提供发射控制信号的发射控制线驱动器; 和

被放置在所述扫描线、所述数据线和所述发射控制线的交叉区域的像素, 其中所述发射控制线驱动器包括分别耦合到所述发射控制线的级, 并且其中每级包括 :

耦合在第一输出端和第一电源之间的第一晶体管, 所述第一晶体管被配置为对应于施加到与所述第一晶体管的栅电极耦合的第一节点的电压被导通或截止;

耦合在所述第一输出端和输出低于所述第一电源的电压的第二电源之间的第二晶体管, 所述第二晶体管被配置为对应于施加到与所述第二晶体管的栅电极耦合的第二节点的电压被导通或截止;

耦合在第四输入端和所述第一节点之间的第三晶体管, 所述第三晶体管具有耦合到第一输入端的栅电极;

耦合在所述第一电源和所述第二节点之间的第四晶体管, 所述第四晶体管具有耦合到所述第一节点的栅电极;

耦合到所述第一输入端和第二输入端的第一控制器, 以向第二输出端提供采样信号;

耦合到所述第一输入端和第三输入端的第二控制器，以控制所述第二节点的电压；和

耦合在所述第二输入端和所述第二节点之间的第一电容器，

其中所述级中第 i 级的所述第一输入端以及第 i+1 级的所述第二输入端被配置为接收

第一时钟信号，

其中所述第 i 级的所述第二输入端以及所述第 i+1 级的所述第一输入端被配置为接收

第二时钟信号，

其中所述第 i 级和所述第 i+1 级的所述第三输入端被配置为接收第三时钟信号，

其中所述第 i 级和所述第 i+1 级的所述第四输入端被配置为接收起始信号或前一级的

采样信号，并且

其中 i 为自然数。

15. 根据权利要求 14 的有机发光显示器，进一步包括耦合在所述第一节点和所述第一

电源之间的第二电容器。

16. 根据权利要求 14 的有机发光显示器，

其中所述第一时钟信号和所述第二时钟信号的每一个被设置在 i 水平周期的周期内，

和

其中所述第三时钟信号被设置在 i/2 水平周期的周期内。

17. 根据权利要求 16 的有机发光显示器，其中所述第三时钟信号在所述第一时钟信号

或所述第二时钟信号在水平周期内被提供之后在该水平周期内被提供。

18. 根据权利要求 14 的有机发光显示器，其中提供给所述第 i 级和所述第 i+1 级的所

述第三时钟信号经由不同的传输线被提供。

19. 根据权利要求 14 的有机发光显示器，其中所述第一控制器包括：

耦合在所述第四输入端和第三节点之间的第五晶体管，所述第五晶体管具有耦合到所

述第一输入端的栅电极；

耦合在第六节点和所述第二输入端之间的第六晶体管，所述第六晶体管具有耦合到所

述第三节点的栅电极；

耦合在所述第六节点和所述第一电源之间的第七晶体管，所述第七晶体管具有耦合到

所述第一输出端的栅电极；

耦合在所述第三节点和所述第六节点之间的第三电容器；和

耦合在所述第一输出端和所述第一电源之间的第四电容器。

20. 根据权利要求 19 的有机发光显示器，其中所述第二输出端被电耦合到所述第六节

点。

21. 根据权利要求 14 的有机发光显示器，其中所述第二控制器包括：

耦合在所述第一输入端和第四节点之间的第八晶体管，所述第八晶体管具有耦合到所

述第一节点的栅电极；

耦合在所述第四节点和所述第二电源之间的第九晶体管，所述第九晶体管具有耦合到所

述第一输入端的栅电极；

耦合在所述第二节点和第五节点之间的第十晶体管，所述第十晶体管具有耦合到所

述第三输入端的栅电极；

耦合在所述第五节点和所述第三输入端的第十一晶体管，所述第十一晶体管具有耦合

到所述第四节点的栅电极；和

耦合在所述第四节点和所述第五节点之间的第五电容器。

22. 根据权利要求 14 的有机发光显示器，进一步包括：

耦合在所述第四输入端和所述第三晶体管之间的第十二晶体管，所述第十二晶体管被配置为当第一控制信号被提供给所述第十二晶体管的栅电极时被导通；和

耦合在第五输入端和所述第一控制器之间的第十三晶体管，所述第十三晶体管被配置为当第二控制信号被提供给所述第十三晶体管的栅电极时被导通，

其中所述第十二晶体管和所述第十三晶体管被配置为在不同的时间被导通。

23. 根据权利要求 14 的有机发光显示器，进一步包括耦合在所述第一节点和所述第二电源之间的第十四晶体管，所述第十四晶体管被配置为当复位信号被提供给所述第十四晶体管的栅电极时被导通。

## 发射控制线驱动器以及使用该驱动器的有机发光显示器

[0001] 相关申请的交叉引用

[0002] 本申请要求于 2011 年 1 月 6 日在韩国知识产权局递交的韩国专利申请 No. 10-2011-0001419 的优先权和权益，其全部内容通过引用合并于此。

### 技术领域

[0003] 根据本发明实施例的方面涉及一种发射控制线驱动器以及使用该驱动器的有机发光显示器。

### 背景技术

[0004] 近来，已经开发出与阴极射线管 (CRT) 显示器相比具有较小重量和体积的各种平板显示器 (FPD)。FPD 包括液晶显示器 (LCD)、场发射显示器 (FED)、等离子体显示面板 (PDP) 和有机发光显示器。

[0005] 在 FPD 中，有机发光显示器使用通过电子和空穴的重组产生光的有机发光二极管 (OLED) 显示图像。有机发光显示器具有较快的响应速度并且以较低的功耗驱动。一个典型的有机发光显示器通过形成在像素中的晶体管向 OLED 提供对应于数据信号的电流，从而 OLED 发射出光。

[0006] 典型的有机发光显示器包括向数据线提供数据信号的数据驱动器、依次向扫描线提供扫描信号的扫描驱动器、向发射控制线提供发射控制信号的发射控制线驱动器以及包括耦合到数据线、扫描线和发射控制线的多个像素的显示单元。

[0007] 在扫描信号被提供给扫描线时，包括在显示单元中的像素被选择，以接收来自数据线的数据信号。接收数据信号的像素产生具有对应于数据信号的亮度（例如预定亮度）的光，并显示预定图像。在此，像素的发射时间由发射控制线提供的发射控制信号控制。通常，发射控制信号被提供以与提供给一条扫描线或两条扫描线的扫描信号重叠，从而将提供有数据信号的像素设置非发射状态下。

[0008] 因此，发射控制线驱动器包括耦合到发射控制线的级。这些级接收至少四个时钟信号并向输出线输出高电压或低电压。

[0009] 然而，由于典型发射控制线驱动器包含的级由至少四个时钟信号驱动，因此包含了大量的晶体管。因此，生产成本提高并且很难保证驱动可靠性。另外，当发射控制线驱动器由 PMOS 晶体管形成时，低电平输出不稳定。

[0010] 具体来说，当低信号被提供给发射控制线时，输出该低信号的晶体管的栅电极被保持在低于低信号的电压下。然而，该晶体管的栅电极的电压会因为漏电流而增加，并且低信号的输出不稳定。

### 发明内容

[0011] 因此，本发明实施例致力于一种能够保证输出稳定性并能自由控制发射控制信号的宽度的发射控制线驱动器，以及使用所述发射控制线驱动器的有机发光显示器。

[0012] 根据本发明的一个实施例，提供了一种包括多级的发射控制线驱动器。每级包括：耦合在第一输出端和第一电源之间的第一晶体管，所述第一晶体管被配置为对应于施加到与所述第一晶体管的栅电极耦合的第一节点的电压被导通或截止；耦合在所述第一输出端和输出低于所述第一电源的电压的第二电源之间的第二晶体管，所述第二晶体管被配置为对应于施加到与所述第二晶体管的栅电极耦合的第二节点的电压被导通或截止；耦合在第四输入端和所述第一节点之间的第三晶体管，所述第三晶体管具有耦合到第一输入端的栅电极；耦合在所述第一电源和所述第二节点之间的第四晶体管，所述第四晶体管具有耦合到所述第一节点的栅电极；耦合到所述第一输入端和第二输入端的第一控制器，以向第二输出端提供采样信号；耦合到所述第一输入端和第三输入端的第二控制器，以控制所述第二节点的电压；以及耦合在所述第二输入端和所述第二节点之间的第一电容器。

[0013] 所述发射控制线驱动器可以进一步包括耦合在所述第一节点和所述第一电源之间的第二电容器。所述第一输入端可以被配置为接收第一时钟信号。所述第二输入端可以被配置为接收第二时钟信号。所述第三输入端可以被配置为接收第三时钟信号。所述第四输入端可以被配置为接收起始信号或前一级的采样信号。所述第一时钟信号、所述第二时钟信号和所述第三时钟信号可以互不重叠。所述第一时钟信号和所述第二时钟信号的每一个可以被设置在  $i$  ( $i$  是自然数) 水平周期的周期内。所述第三时钟信号可以被设置在  $i/2$  水平周期的周期内。所述第三时钟信号可以在所述第一时钟信号或所述第二时钟信号在水平周期内被提供之后在该水平周期内被提供。

[0014] 所述第一控制器可以包括：耦合在所述第四输入端和第三节点之间的第五晶体管，所述第五晶体管具有耦合到所述第一输入端的栅电极；耦合在第六节点和所述第二输入端之间的第六晶体管，所述第六晶体管具有耦合到所述第三节点的栅电极；耦合在所述第六节点和所述第一电源之间的第七晶体管，所述第七晶体管具有耦合到所述第一输出端的栅电极；耦合在所述第三节点和所述第六节点之间的第三电容器；以及耦合在所述第一输出端和所述第一电源之间的第四电容器。所述第二输出端可以被电耦合到所述第六节点。

[0015] 所述第二控制器可以包括：耦合在所述第一输入端和第四节点之间的第八晶体管，所述第八晶体管具有耦合到所述第一节点的栅电极；耦合在所述第四节点和所述第二电源之间的第九晶体管，所述第九晶体管具有耦合到所述第一输入端的栅电极；耦合在所述第二节点和第五节点之间的第十晶体管，所述第十晶体管具有耦合到所述第三输入端的栅电极；耦合在所述第五节点和所述第三输入端的第十一晶体管，所述第十一晶体管具有耦合到所述第四节点的栅电极，以及耦合在所述第四节点和所述第五节点之间的第五电容器。

[0016] 所述发射控制线驱动器可以进一步包括：耦合在所述第四输入端和所述第三晶体管之间的第十二晶体管，所述第十二晶体管被配置为当第一控制信号被提供给所述第十二晶体管的栅电极时被导通，以及耦合在第五输入端和所述第一控制器之间的第十三晶体管，所述第十三晶体管被配置为当第二控制信号被提供给所述第十三晶体管的栅电极时被导通。所述第一控制信号和所述第二控制信号可以互不重叠。所述发射控制线驱动器可以进一步包括耦合在所述第一节点和所述第二电源之间的第十四晶体管，所述第十四晶体管被配置为当复位信号被提供给所述第十四晶体管的栅电极时被导通。所述复位信号可以被

共同提供给所有级。

[0017] 根据一个实施例，一种有机发光显示器包括：用于依次向扫描线提供扫描信号的扫描驱动器，用于向数据线提供数据信号的数据驱动器，用于向发射控制线提供发射控制信号的发射控制线驱动器，以及被放置在所述扫描线、所述数据线和所述发射控制线的交叉区域的像素。所述发射控制线驱动器包括分别耦合到所述发射控制线的级。每级包括：耦合在第一输出端和第一电源之间的第一晶体管，所述第一晶体管被配置为对应于施加到与所述第一晶体管的栅电极耦合的第一节点的电压被导通或截止；耦合在所述第一输出端和输出低于所述第一电源的电压的第二电源之间的第二晶体管，所述第二晶体管被配置为对应施加到与所述第二晶体管的栅电极耦合的第二节点的电压导通或截止；耦合在第四输入端和所述第一节点之间的第三晶体管，所述第三晶体管具有耦合到第一输入端的栅电极；耦合在所述第一电源和所述第二节点之间的第四晶体管，所述第四晶体管具有耦合到所述第一节点的栅电极；耦合到所述第一输入端和第二输入端的第一控制器，以向第二输出端提供采样信号；耦合到所述第一输入端和第三输入端的第二控制器，以控制所述第二节点的电压；以及耦合在所述第二输入端和所述第二节点之间的第一电容器。

[0018] 根据本发明实施例所描述的发射控制线驱动器和使用该发射控制线驱动器的有机发光显示器，输出低信号的晶体管的栅电极的电压使用时钟信号被周期性地降低，从而输出的稳定性可以得到保证。此外，根据本发明的实施例，可以对应起始信号的宽度控制发射控制信号的宽度。另外，根据本发明的实施例，由于级接收三个时钟信号，电路结构可以得以简化。

## 附图说明

[0019] 附图连同说明书一起示出本发明的示例实施例，并且连同描述一起用于解释本发明的原理。

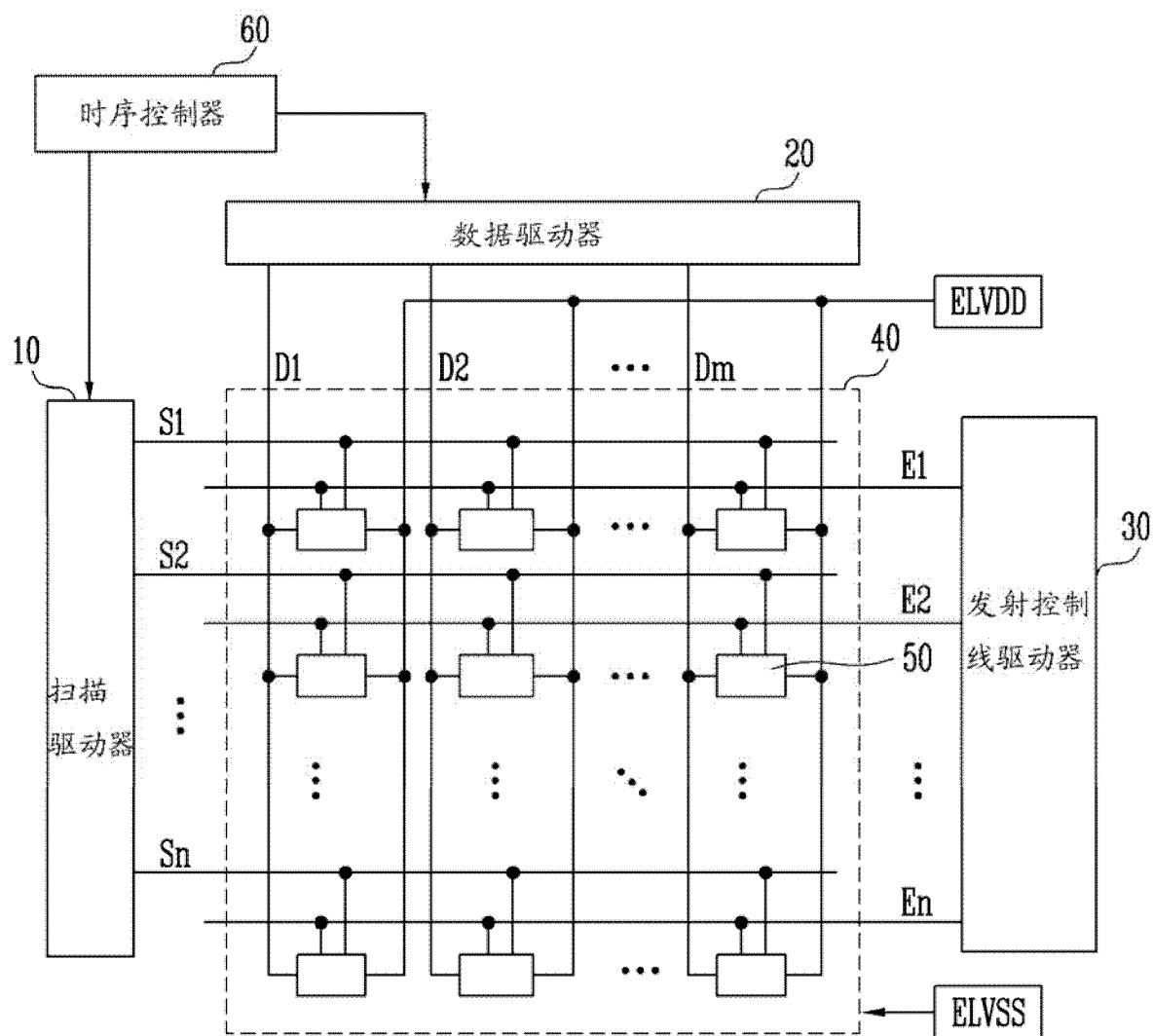

[0020] 图 1 是示出根据本发明实施例的有机发光显示器的框图；

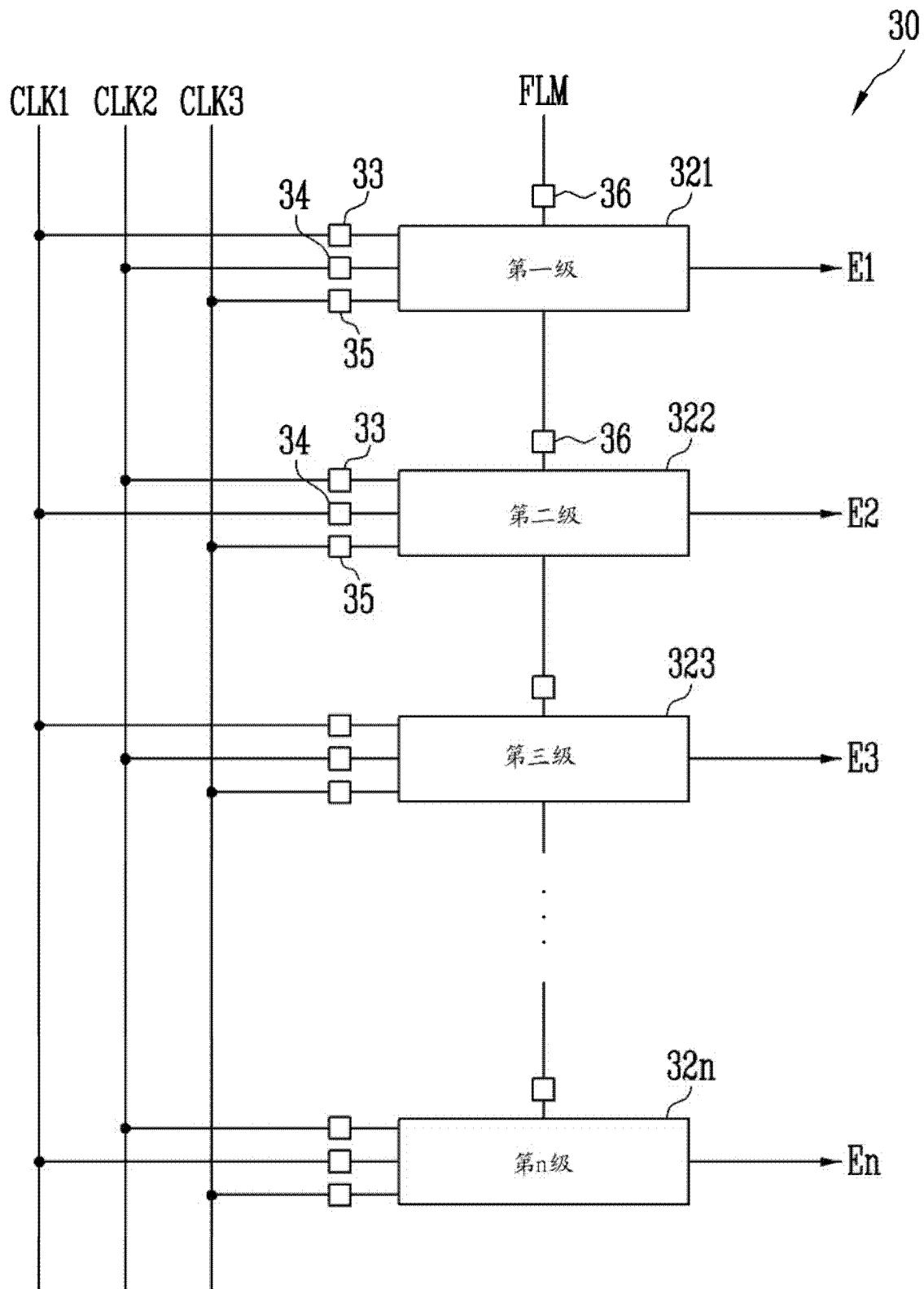

[0021] 图 2 是示意性地示出图 1 的发射控制线驱动器的级的框图；

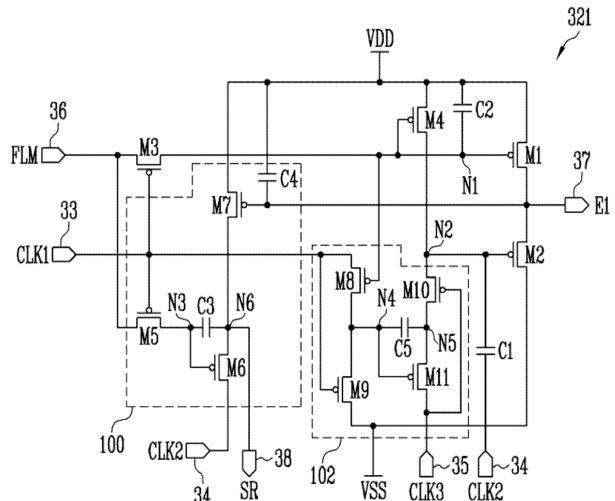

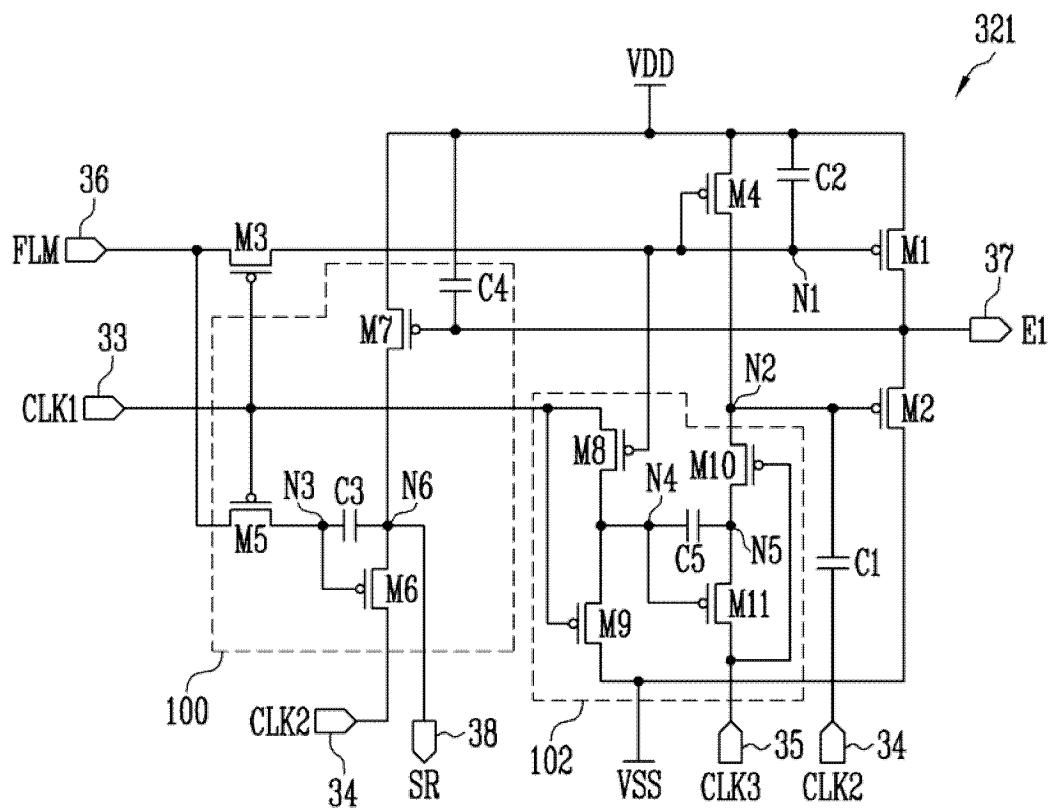

[0022] 图 3 是示出图 2 的级之一的第一实施例的电路图；

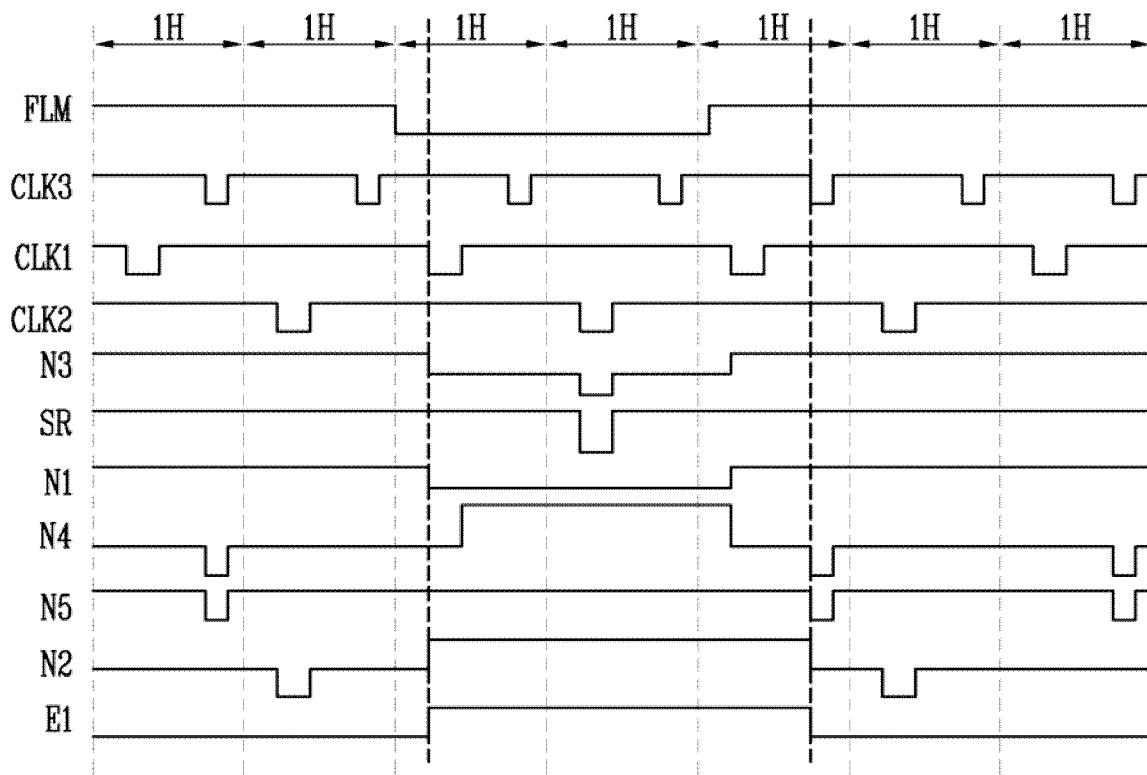

[0023] 图 4 是示出图 3 的级的操作过程的波形图；

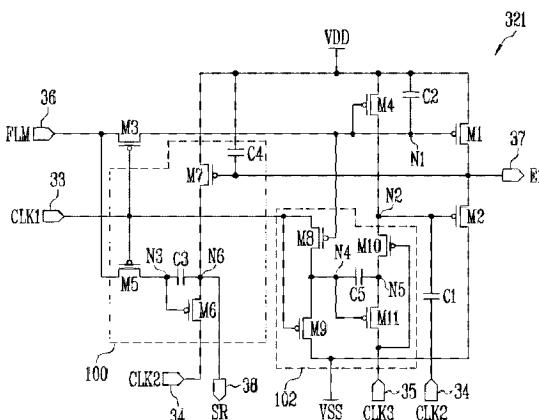

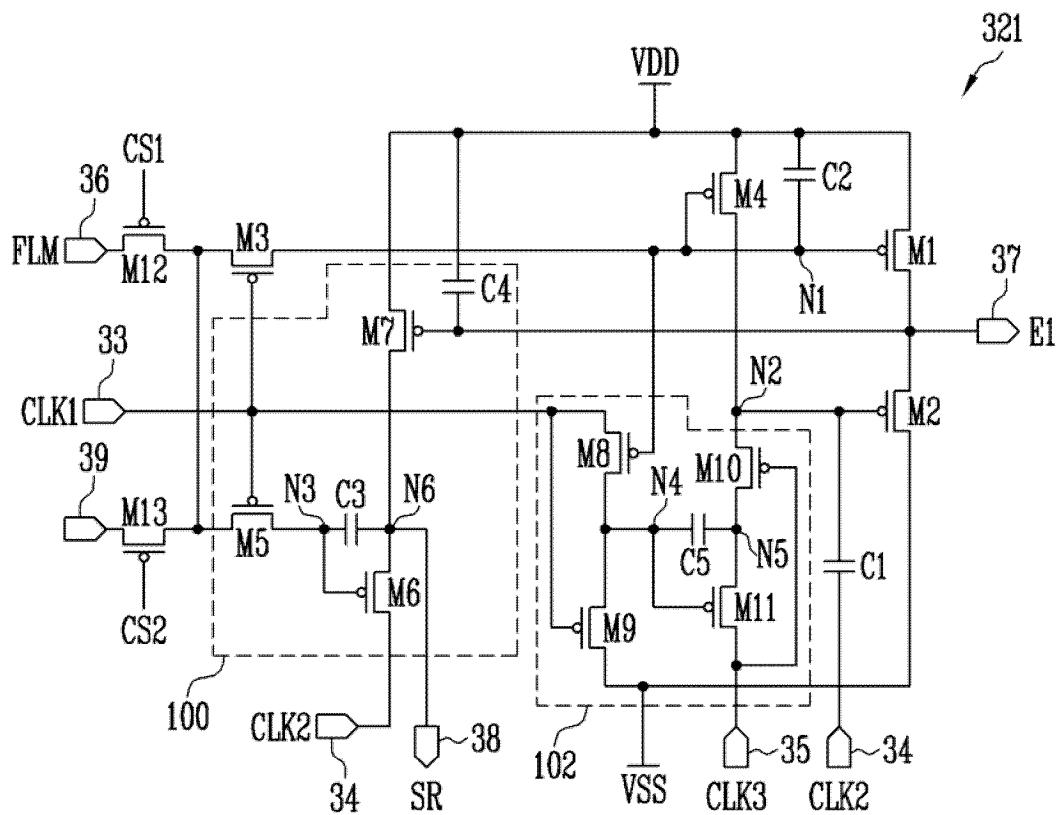

[0024] 图 5 是示出图 2 的级之一的第二实施例的电路图；和

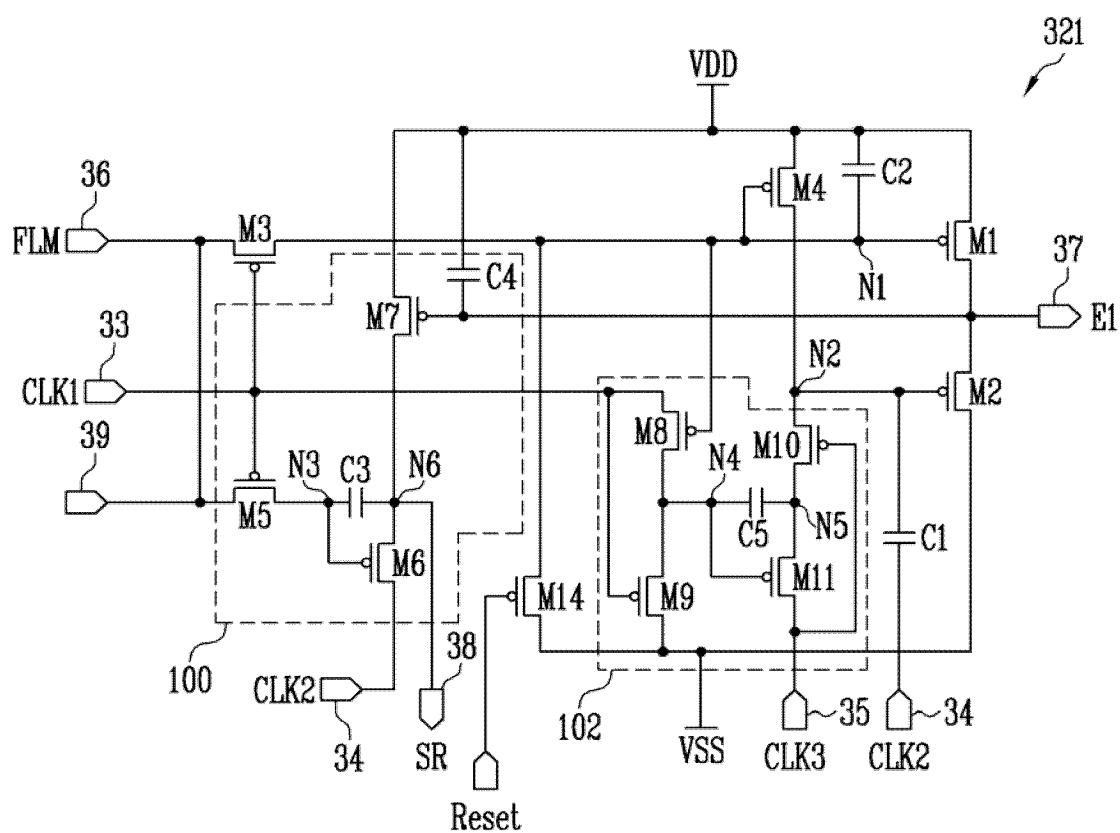

[0025] 图 6 是示出图 2 的级之一的第三实施例的电路图。

## 具体实施方式

[0026] 在下文中，将参考附图描述根据本发明的某些示例实施例。在此，当描述第一元件被耦合到第二元件时，第一元件可以直接耦合到第二元件或经由一个或多个第三元件间接耦合到第二元件。另外，为清楚起见，省略了对完整理解本发明不是必要的某些元件。并且相同的附图标记始终指代相同的元件。

[0027] 在下文中，将参考图 1 到图 6 详述本领域技术人员通过其可实现本发明的本发明示例实施例。

[0028] 图 1 是示出根据本发明实施例的有机发光显示器的框图。

[0029] 参考图 1，根据本发明实施例的有机发光显示器包括：包括放置在扫描线 S1 到 Sn、

数据线 D1 到 D<sub>m</sub> 和发射控制线 E1 到 E<sub>n</sub> 的交叉区域的像素 50 的显示单元 40, 用于驱动扫描线 S1 到 S<sub>n</sub> 的扫描驱动器 10, 用于驱动数据线 D1 到 D<sub>m</sub> 的数据驱动器 20, 用于驱动发射控制线 E1 到 E<sub>n</sub> 的发射控制线驱动器 30, 以及用于控制驱动器 10、20 和 30 的时序控制器 60。

[0030] 扫描驱动器 10 依次向扫描线 S1 到 S<sub>n</sub> 提供扫描信号。当扫描信号被提供给扫描线 S1 到 S<sub>n</sub> 时, 以水平线为单位(例如逐行)选择像素 50。

[0031] 数据驱动器 20 与扫描信号同步地向数据线 D1 到 D<sub>m</sub> 提供数据信号。提供给数据线 D1 到 D<sub>m</sub> 的数据信号被提供给由扫描信号选择的像素 50。

[0032] 发射控制线驱动器 30 依次向发射控制线 E1 到 E<sub>n</sub> 提供发射控制信号。在此, 发射控制线驱动器 30 在对应于数据信号的电压被充电的周期期间提供发射控制信号, 从而像素 50 被设置在非发射状态。因此, 提供给第 i(i 是自然数)条发射控制线 E<sub>i</sub> 的发射控制信号与提供给第 i 条扫描线 S<sub>i</sub> 的扫描信号重叠。另一方面, 发射控制信号的宽度可合适地设置为与像素 50 的结构和要实现的亮度对应。

[0033] 图 2 是示意性地示出图 1 的发射控制线驱动器的级的框图。

[0034] 参考图 2, 为了向 n 条发射控制线 E1 到 E<sub>n</sub> 提供发射控制信号, 根据本发明实施例的发射控制线驱动器 30 包括 n 级 321 到 32n。级 321 到 32n 分别耦合到发射控制线 E1 到 E<sub>n</sub>, 并通过三个时钟信号 CLK1、CLK2 和 CLK3 驱动。

[0035] 级 321 到 32n 中的每一级都包括第一输入端 33、第二输入端 34、第三输入端 35 和第四输入端 36。

[0036] 第 k(k 是奇数或偶数)级 32k 的第一输入端 33 接收第一时钟信号 CLK1, 并且第二输入端 34 接收第二时钟信号 CLK2。第 k+1 级 32k+1 的第一输入端 33 接收第二时钟信号 CLK2, 并且第二输入端 34 接收第一时钟信号 CLK1。第三时钟信号 CLK3 被提供给级 321 到 32n 中每级的第三输入端 35, 并且起始信号 FLM 或前一级的采样信号被提供给第四输入端 36。

[0037] 级 321 到 32n 可以由同样的电路组成, 并产生具有改变为对应于起始信号 FLM 的宽度的发射控制信号。

[0038] 图 3 是示出图 2 的级之一的第一实施例的电路图。在图 3 中, 为方便起见, 将示出第一级 321。

[0039] 参考图 3, 根据本发明的第一实施例, 级 321 包括第一晶体管 M1、第二晶体管 M2、第三晶体管 M3、第四晶体管 M4、第一电容器 C1、第二电容器 C2、第一控制器 100 和第二控制器 102。

[0040] 第一晶体管 M1 耦合在第一输出端 37 和第一电源 VDD 之间。第一晶体管 M1 的栅电极耦合到第一节点 N1。第一晶体管 M1 对应于施加到第一节点 N1 的电压控制第一输出端 37 的电压。在此, 当第一晶体管 M1 导通时, 第一电源 VDD(例如高电压)被提供给第一输出端 37。由于第一输出端 37 耦合到发射控制线 E1, 因此提供给第一输出端 37 的高电压被用作发射控制信号。

[0041] 第二晶体管 M2 耦合在第一输出端 37 和第二电源 VSS 之间。第二晶体管 M2 的栅电极耦合到第二节点 N2。第二晶体管 M2 对应于施加到第二节点 N2 的电压控制第一输出端 37 的电压。在此, 当第二晶体管 M2 导通时, 第二电源 VSS(例如低电压)被提供给第一输出端 37。

[0042] 第三晶体管 M3 耦合在第四输入端 36 和第一节点 N1 之间。第三晶体管 M3 的栅电极耦合到第一输入端 33。第三晶体管 M3 对应于提供给第一输入端 33 的第一时钟信号 CLK1 导通或截止。当第三晶体管 M3 被导通时,第四输入端 36 和第一节点 N1 彼此电耦合。当起始信号 FLM( 或前一级采样信号 ) 被提供给第四输入端 36 时,第一晶体管 M1 导通。

[0043] 第四晶体管 M4 耦合在第一电源 VDD 和第二节点 N2 之间。第四晶体管 M4 的栅电极耦合到第一节点 N1。为了控制第二节点 N2 的电压,第四晶体管 M4 对应于施加到第一节点 N1 的电压被导通或截止。也就是说,当低电压被施加到第一节点 N1 时第四晶体管 M4 导通,从而将第一电源 VDD 的电压提供给第二节点 N2。当该低电压被施加到第一节点 N1 时,第一电源 VDD 的高电压被提供给第二节点 N2,从而第一晶体管 M1 和第二晶体管 M2 在不同的时间导通或截止。

[0044] 第一电容器 C1 耦合在第二输入端 34 和第二节点 N2 之间。第一电容器 C1 对应于提供给第二输入端 34 的第二时钟信号 CLK2 控制第二节点 N2 的电压。第一电容器 C1 的操作过程将在稍后进行更加详细地描述。

[0045] 第二电容器 C2 耦合在第一节点 N1 和第一电源 VDD 之间。第二电容器 C2 以对应于第一晶体管 M1 的导通或截止的电压被充电。

[0046] 第一控制器 100 对应于第一时钟信号 CLK1 和第二时钟信号 CLK2 向第二输出端 38 提供采样信号。因此,第一控制器 100 包括第五晶体管 M5、第六晶体管 M6、第七晶体管 M7、第三电容器 C3 和第四电容器 C4。

[0047] 第五晶体管 M5 耦合在第四输入端 36 和第三节点 N3 之间。第五晶体管 M5 的栅电极耦合到第一输入端 33。为了控制第三节点 N3 的电压,第五晶体管 M5 对应于提供给第一输入端 33 的第一时钟信号 CLK1 被导通或截止。

[0048] 第六晶体管 M6 耦合在第六节点 N6 和第二输入端 34 之间。第六晶体管 M6 的栅电极耦合到第三节点 N3。第六晶体管 M6 对应于施加到第三节点 N3 的电压控制第六节点 N6 的电压。

[0049] 第七晶体管 M7 耦合在第一电源 VDD 和第六节点 N6 之间。第七晶体管 M7 的栅电极耦合到第一输出端 37。为了控制第六节点 N6 的电压,第七晶体管 M7 对应于施加到第一输出端 37 的电压被导通或截止。

[0050] 第三电容器 C3 耦合在第三节点 N3 和第六节点 N6 之间。第三电容器 C3 以对应于第六晶体管 M1 的导通或截止的电压被充电。

[0051] 第四电容器 C4 耦合在第一电源 VDD 和第一输出端 37 之间。第四电容器 C4 以对应于第七晶体管 M7 的导通或截止的电压被充电。

[0052] 在图 3 中,第二输出端 38 耦合到第六节点 N6。第二输出端 38 将施加给第六节点 N6 的电压作为采样信号提供给下一级 322。

[0053] 第二控制器 102 对应于第一时钟信号 CLK1 和第三时钟信号 CLK3 控制第二节点 N2 的电压。在此,在发射控制信号未被提供给第一输出端 37 的时段,第二控制器 102 将第二节点 N2 的电压保持为低电压。在图 3 中,第二控制器 102 包括第八晶体管 M8、第九晶体管 M9、第十晶体管 M10、第十一晶体管 M11 和第五电容器 C5。

[0054] 第八晶体管 M8 耦合在第一输入端 33 和第四节点 N4 之间。第八晶体管 M8 的栅电极耦合到第一节点 N1。为了控制第四节点 N4 的电压,第八晶体管 M8 对应于施加到第一节

点 N1 的电压被导通或截止。

[0055] 第九晶体管 M9 耦合在第四节点 N4 和第二电源 VSS 之间。第九晶体管 M9 的栅电极耦合到第一输入端 33。为了控制第四节点 N4 的电压,第九晶体管 M9 对应于提供给第一输入端 33 的第一时钟信号 CLK1 被导通或截止。

[0056] 第十晶体管 M10 耦合在第二节点 N2 和第五节点 N5 之间。第十晶体管 M10 的栅电极耦合到第三输入端 35。为了控制第二节点 N2 的电压,第十晶体管 M10 对应于提供给第三输入端 35 的第三时钟信号 CLK3 被导通或截止。

[0057] 第十一晶体管 M11 耦合在第五节点 N5 和第三输入端 35 之间。第十一晶体管 M11 的栅电极耦合到第四节点 N4。为了控制第五节点 N5 的电压,第十一晶体管 M11 对应于施加到第四节点 N4 的电压被导通或截止。

[0058] 第五电容器 C5 耦合在第四节点 N4 和第五节点 N5 之间。第五电容器 C5 以对应于第十一晶体管 M11 的导通或截止的电压被充电。

[0059] 图 4 是示出了图 3 的级的操作过程的波形图。

[0060] 参考图 4,第一时钟信号 CLK1 和第二时钟信号 CLK2 在 iH 周期 (i 是自然数,例如水平周期) 中被提供,第三时钟信号 CLK3 在 i/2H 周期中被提供。在图 4 中,方便起见,第一时钟信号 CLK1 和第二时钟信号 CLK2 被设置在在 2H 周期中,第三时钟信号 CLK3 被设置在 1H 周期中。

[0061] 在图 4 中,第一时钟信号 CLK1 和第二时钟信号 CLK2 在不同的水平周期 H 被提供,第三时钟信号 CLK3 在每个水平周期 H 被提供,从而第一时钟信号 CLK1 与第三时钟信号 CLK3 不重叠。然后,在水平周期 H,第一时钟信号 CLK1 或第二时钟信号 CLK2 被提供后,第三时钟信号 CLK3 被提供。也就是,在一个示例水平周期,第三时钟信号 CLK3 在第一时钟信号 CLK1 被提供以后被提供。在下一个水平周期,第三时钟信号 CLK3 在第二时钟信号 CLK2 被提供以后被提供。

[0062] 下面将对处理过程进行详述。首先,起始信号 FLM(例如低信号)被提供给第四输入端 36。起始信号 FLM 被提供给第四输入端 36 后,第一时钟信号 CLK1 被提供给第一输入端 33。当第一时钟信号 CLK1 被提供时,第三晶体管 M3、第五晶体管 M5 和第九晶体管 M9 被导通。

[0063] 当第三晶体管 M3 被导通时,起始信号 FLM 被提供给第一节点 N1。当起始信号 FLM 被提供给第一节点 N1 时,第一晶体管 M1、第四晶体管 M4 和第八晶体管 M8 被导通。当第一晶体管 M1 被导通时,对应于第一晶体管 M1 的导通的电压被充在第二电容器 C2。

[0064] 当第一晶体管 M1 被导通时,第一电源 VDD 的电压被提供给第一输出端 37。在这种情况下,发射控制信号被提供给发射控制线 E1。

[0065] 当第四晶体管 M4 被导通时,第一电源 VDD 被提供给第二节点 N2。当第一电源 VDD 被提供给第二节点 N2 时,第二晶体管 M2 被截止。当第二晶体管 M2 被截止时,第一电源 VDD 可以被稳定提供给第一输出端 37。

[0066] 当第八晶体管 M8 被导通时,第四节点 N4 和第一输入端 33 互相电耦合。在此,由于第一时钟信号 CLK1 被提供给第一输入端 33,第四节点 N4 接收低电压。

[0067] 当第五晶体管 M5 被导通时,起始信号被提供给第三节点 N3。当起始信号被提供给第三节点 N3 时,第六晶体管 M6 被导通。当第六晶体管 M6 被导通时,第六节点 N6 和第二输

入端 34 被互相电耦合。在此,由于第二时钟信号 CLK2 未被提供给第二输入端 34,第六节点 N6 保持高电压,从而采样信号不会被提供给第二输出端 38。另一方面,由于第六晶体管 M6 被导通,对应于第六晶体管 M6 的导通的电压被充在第三电容器 C3。

[0068] 当第九晶体管 M9 被导通时,第二电源 VSS 的电压被提供给第四节点 N4。当第二电源 VSS 被提供给第四节点 N4 时,第十一晶体管 M11 被导通。当第十一晶体管 M11 被导通时,第五节点 N5 和第三输入端 35 被互相电耦合。在此,由于第三时钟信号 CLK3 未被提供给第三输入端 35,第五节点 N5 保持高电压。另一方面,由于第十一晶体管 M11 被导通,对应于第十一晶体管 M11 的导通的电压被充在第五电容器 C5。

[0069] 然后,停止将第一时钟信号 CLK1 提供给第一输入端 33。当停止提供第一时钟信号 CLK1 时,第三晶体管 M3、第五晶体管 M5 和第九晶体管 M9 被截止。

[0070] 当第三晶体管 M3 被截止时,第四输入端 36 和第一节点 N1 被互相电隔离。在此,第一节点 N1 通过第二电容器 C2 保持低电压。因此,第一晶体管 M1 保持导通状态,从而第一电源 VDD 的电压被输出到第一输出端 37。由于第四晶体管 M4 通过第二电容器 C2 的电压保持导通状态,第二晶体管 M2 稳定地保持截止状态。

[0071] 当第五晶体管 M5 被截止时,第四输入端 36 和第三节点 N3 被互相电隔离。在此,第六晶体管 M6 对应第三电容器 C3 上被充电的电压保持导通状态,从而第二输出端 38 保持之前的电压。

[0072] 当第九晶体管 M9 被截止时,第四节点 N4 和第二电源 VSS 被互相电隔离。在此,由于第八晶体管 M8 对应于施加到第一节点 N1 的电压保持导通状态,第四节点 N4 和第一输入端 33 被互相电耦合。因此,第四节点 N4 的电压增加到提供给第一输入端 33 的电压(例如高信号的电压)。当第四节点 N4 接收高信号的电压时,第十一晶体管 M11 被截止。在此,第五电容器 C5 以对应于第十一晶体管 M11 的截止的电压被充电。

[0073] 然后,第三时钟信号 CLK3 被提供给第三输入端 35。当第三时钟信号 CLK3 被提供时,第十晶体管 M10 被导通。当第十晶体管 M10 被导通时,第二节点 N2 和第五节点 N5 被互相电耦合。这时,由于第四晶体管 M4 保持导通状态并且第十一晶体管 M11 保持截止状态,第二节点 N2 保持第一电源 VDD 的电压。

[0074] 在第三时钟信号 CLK3 被提供以后,第二时钟信号 CLK2 在下一个水平周期被提供给第二输入端 34。在此,由于第六晶体管 M6 被设置为导通状态,第二时钟信号 CLK2 被提供给第六节点 N6。作为采样信号提供给第六节点 N6 的第二时钟信号 CLK2 通过第二输出端 38 被提供给下一级。另一方面,当第二时钟信号 CLK2 被提供给第六节点 N6 时,第三节点 N3 的电压由于第三电容器 C3 的耦合降低。因此,第六晶体管 M6 稳定地保持导通状态。

[0075] 此外,提供给第二输入端 34 的第二时钟信号 CLK2 由于第一电容器 C1 的耦合被传送给第二节点 N2。在此,由于第二节点 N2 接收第一电源 VDD,第一电源 VDD 的电压被保持,而没有电压变化。

[0076] 然后,第三时钟信号 CLK3 被提供给第三输入端 35。当第三时钟信号 CLK3 被提供时,第十晶体管 M10 被导通。当第十晶体管 M10 被导通时,第二节点 N2 和第五节点 N5 被互相电耦合。在此,由于第四晶体管 M4 保持导通状态并且第十一晶体管 M11 保持截止状态,第二节点 N2 保持第一电源 VDD 的电压。

[0077] 在第三时钟信号 CLK3 被提供后,在下一个水平周期停止提供起始信号 FLM(例如

高电压),且第一时钟信号 CLK1 被提供给第一输入端 33。

[0078] 当第一时钟信号 CLK1 被提供时,第三晶体管 M3、第五晶体管 M5 和第九晶体管 M9 被导通。

[0079] 当第三晶体管 M3 被导通时,第一节点 N1 和第四输入端 36 被互相电耦合。在此,由于高电压被提供给第一节点 N1,第一晶体管 M1、第四晶体管 M4 和第八晶体管 M8 被截止。当第一晶体管 M1 被截止时,第一输出端 37 被设置为浮接状态 (floating state)。在这种情况下,第一输出端 37 保持是前一周期输出信号的高电压。

[0080] 由于提供给发射控制线 E1 的发射控制信号被提供给像素 50,像素的电容器实施充电。因此,虽然第一输出端 37 被设置在浮接状态,前一周期的输出电压通过像素 50 的寄生电容器和发射控制线被保持。

[0081] 当第五晶体管 M5 被导通时,高电压被提供给第三节点 N3,从而第六晶体管 M6 被截止。当第六晶体管 M6 被截止时,第六节点 N6 和第二输入端 34 被互相电隔离。在此,第三电容器 C3 以对应于第六晶体管 M6 的截止的电压被充电。

[0082] 当第九晶体管 M9 被导通时,第四节点 N4 和第二电源 VSS 被互相电耦合。在此,第四节点 N4 接收第二电压 VSS 的电压,从而第十一晶体管 M11 被导通。当第十一晶体管 M11 被导通时,第五节点 N5 和第三输入端 35 被互相电耦合。另一方面,对应于导通第十一晶体管 M11 的电压被储存在第五电容器 C5。

[0083] 然后,第三时钟信号 CLK3 被提供给第三输入端 35。当第三时钟信号 CLK3 被提供时,第十晶体管 M10 被导通。当第十晶体管 M10 被导通时,第二节点 N2 和第三输入端 35 经由第五节点 N5 被互相电耦合。在此,第三时钟信号 CLK3(例如低电压)被提供给第二节点 N2。当该低电压被提供给第二节点 N2 时,第二晶体管 M2 被导通,从而第二电源 VSS 的电压被输出到第一输出端 37。在这种情况下,停止向发射控制线 E1 提供发射控制信号。当第二电源 VSS 被提供给第一输出端 37 时,第七晶体管 M7 被导通。当第七晶体管 M7 被导通时,第一电源 VDD 的电压被提供给第六节点 N6。

[0084] 根据本发明的实施例,第三时钟信号 CLK3 可以被设置为低于第二电源 VSS 的电压,从而第二晶体管 M2 可以被稳定地导通。然后,级 321 输出第一电源 VDD 的电压给第一输出端 37,直到下一个起始信号 FLM 被提供。

[0085] 此外,根据本发明的实施例,无论何时第二时钟信号 CLK2 被提供,第二节点 N2 的电压由于第一电容器 C1 的耦合被降低。因此,第二节点 N2 的电压稳定地保持在低电压,从而第二电源 VSS 的电压可以被稳定输出给第一输出端 37。

[0086] 另一方面,采样信号与第二时钟信号 CLK2 同步地被提供给下一级(在下一级,第二时钟信号 CLK2 被提供给第一输入端)。在这种情况下,下一级使用该采样信号稳定地输出发射控制信号。

[0087] 此外,在图 4 中,示出了一个采样信号对应于起始信号 FLM 产生。然而,本发明并不限于此。例如,当起始信号 FLM 与两个第一时钟信号 CLK1 重叠时,两个采样信号被提供给下一级。所以,根据本发明实施例,起始信号 FLM 的宽度被控制,从而发射控制信号的宽度可以被自由控制。

[0088] 图 5 是示出了图 2 的级之一的第二实施例的电路图。在图 5 中,与图 3 相同的元件由相同的附图标记指代,并且将省略其详细描述。

[0089] 参考图 5, 根据本发明第二实施例, 级 321 进一步包括用于双向驱动的第十二晶体管 M12 和第十三晶体管 M13。

[0090] 第十二晶体管 M12 耦合在第四输入端 36 和第三晶体管 M3 之间。第十二晶体管 M12 的栅电极接收第一控制信号 CS1。当第一控制信号 CS1 被提供时, 第十二晶体管 M12 被导通。

[0091] 第十三晶体管 M13 耦合在第五输入端 39 和第五晶体管 M5(或第一控制器 100)之间。然后, 第十三晶体管 M13 的栅电极接收第二控制信号 CS2。当第二控制信号 CS2 被提供时, 第十三晶体管 M13 被导通。第五输入端 39 接收起始信号或下一级的采样信号。

[0092] 在此, 第一控制信号 CS1 和第二控制信号 CS2 在不同的时间被提供(例如相互不重叠)。例如, 当发射控制信号在第一方向(从面板的顶部到底部)被提供时, 第一控制信号 CS1 被提供, 从而第十二晶体管 M12 被导通并且第十三晶体管 M13 保持截止状态。当发射控制信号在第二方向(从面板的底部到顶部)被提供时, 第二控制信号 CS2 被提供, 从而第十三晶体管 M13 被导通, 并且第十二晶体管 M12 保持截止状态。

[0093] 根据本发明第二实施例, 级 321 进一步包括用于双向驱动的第十二晶体管 M12 和第十三晶体管 M13, 并且操作过程实质上和图 3 所示的第一实施例相同。

[0094] 图 6 是示出了图 2 的级之一的第三实施例的电路图。在图 6 中, 与图 3 相同的元件由相同的附图标记指代, 并且将省略其详细描述。

[0095] 参考图 6, 根据本发明第三实施例, 级 321 进一步包括耦合在第一节点 N1 和第二电源 VSS 之间的第十四晶体管 M14。当复位信号(Reset)被提供给第十四晶体管 M14 的栅电极时, 第十四晶体管 M14 被导通, 从而向第一节点 N1 提供第二电源 VSS 的电压。当第二电源 VSS 被提供给第一节点 N1 时, 第一晶体管 M1 被导通, 从而第一电源 VDD 的电压被提供给第一输出端 37。

[0096] 在此, 当电源被接通和 / 或关断时, 复位信号(Reset)被共同提供给所有级 321 到 32n。如上所述, 当复位信号(Reset)被提供且电源被接通和 / 或关断时, 发射控制信号被提供给发射控制线 E1 到 En, 从而像素 50 被设置在非发射状态下。也就是说, 根据本发明第三实施例, 可以使用复位信号防止在接通和 / 或关断电源时过电流流动或产生不必要的光。

[0097] 此外, 在图 2 中, 第三时钟信号 CLK3 被提供给所有级 321 到 32n。然而, 本发明并不限于上述。例如, 第三时钟信号 CLK3 可以经由不同的传输线被提供给奇数和偶数级。然后, 第三时钟信号 CLK3 的负荷被最小化或降低, 从而可以改善驱动级的稳定性。

[0098] 尽管参考某些示例实施例对本发明进行了描述, 应当理解本发明并不限于公开的实施例, 而是相反, 本发明欲覆盖包含在所附权利要求的精神和范围及其等同物内的各种修改和等同布置。

图 1

图 2

图 3

图 4

图 5

图 6

|                |                                                                                                                      |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 发射控制线驱动器以及使用该驱动器的有机发光显示器                                                                                             |         |            |

| 公开(公告)号        | <a href="#">CN102592539B</a>                                                                                         | 公开(公告)日 | 2016-01-20 |

| 申请号            | CN201110344357.8                                                                                                     | 申请日     | 2011-11-03 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                             |         |            |

| 申请(专利权)人(译)    | 三星移动显示器株式会社                                                                                                          |         |            |

| 当前申请(专利权)人(译)  | 三星显示有限公司                                                                                                             |         |            |

| [标]发明人         | 张桓寿<br>卞昌洙                                                                                                           |         |            |

| 发明人            | 张桓寿<br>卞昌洙                                                                                                           |         |            |

| IPC分类号         | G09G3/3266 G11C19/18 G11C19/28                                                                                       |         |            |

| CPC分类号         | G09G3/3266 G09G2300/0861 G09G2310/0262 G09G2310/0283 G09G2310/0286 G09G2330/025<br>G09G2330/027 G11C19/184 G11C19/28 |         |            |

| 代理人(译)         | 宋志强                                                                                                                  |         |            |

| 优先权            | 1020110001419 2011-01-06 KR                                                                                          |         |            |

| 其他公开文献         | <a href="#">CN102592539A</a>                                                                                         |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                       |         |            |

### 摘要(译)

本发明公开了发射控制线驱动器及使用该驱动器的有机发光显示器。发射控制线驱动器能够保证输出稳定性，并能自由控制发射控制信号的宽度。发射控制线驱动器包括分别耦合到发射控制线的多级。每级包括被配置为输出发射控制信号的多个晶体管。可对应起始信号的宽度控制发射控制信号的宽度。另外，级的电路结构得以简化。