(12) 发明专利申请

(10) 申请公布号 CN 103295522 A

(43) 申请公布日 2013.09.11

(21) 申请号 201310038875.6

(22) 申请日 2013.01.31

(30) 优先权数据

10-2012-0021210 2012.02.29 KR

(71) 申请人 三星显示有限公司

地址 韩国京畿道

(72) 发明人 郑镇泰

(74) 专利代理机构 北京英赛嘉华知识产权代理

有限责任公司 11204

代理人 余朦 刘铮

(51) Int. Cl.

G09G 3/32 (2006.01)

权利要求书4页 说明书12页 附图9页

(54) 发明名称

发光驱动单元、发光驱动部及有机发光显示

装置

(57) 摘要

发光驱动单元包括：输入信号生成电路、逆变器电路以及输出切换电路。输入信号生成电路响应于第一时钟信号接收帧线标记(FrameLine Mark, 简称为 FLM)信号，响应于所述 FLM 信号接收第二时钟信号并且输出逐次输入信号。逆变器电路响应于第一时钟信号接收 FLM 信号，反转所述 FLM 信号以生成逆变器输出信号。输出切换电路响应于逆变器输出信号，将高电平的第一电压或者低电平的第二电压作为发光信号予以输出。输入信号生成电路、逆变器电路以及输出切换电路可以由相同的单一晶体管构成。

1. 一种发光驱动单元,其特征在于,包括:

输入信号生成电路,用于响应于第一时钟信号接收帧线标记信号,并且用于响应于所述帧线标记信号接收第二时钟信号并且输出逐次输入信号;

逆变器电路,用于响应于所述第一时钟信号接收所述帧线标记信号,反转所述帧线标记信号以生成逆变器输出信号;以及

输出切换电路,用于响应于所述逆变器输出信号,将高电平的第一电压或者低电平的第二电压作为发光信号予以输出;

所述输入信号生成电路、所述逆变器电路以及所述输出切换电路由相同的单一晶体管构成。

2. 根据权利要求 1 所述的发光驱动单元,其特征在于,

所述发光信号具有将所述帧线标记信号反转的形态。

3. 根据权利要求 2 所述的发光驱动单元,其特征在于,

所述输入信号生成电路、所述逆变器电路以及所述输出切换电路由 N 沟道金属氧化物半导体晶体管构成。

4. 根据权利要求 3 所述的发光驱动单元,其特征在于,所述输入信号生成电路包括:

第一晶体管,具有:源电极、用于接收所述帧线标记信号的漏电极以及用于接收所述第一时钟信号的栅电极,所述第一晶体管响应于所述第一时钟信号,从所述漏电极向所述源电极施加所述帧线标记信号;

第二晶体管,具有:用于接收所述第二时钟信号的漏电极、与所述第一晶体管的所述源电极连接的栅电极以及用于输出所述逐次输入信号的源电极;以及

第一电容器,连接在所述第一晶体管的所述源电极和所述第二晶体管的所述源电极之间。

5. 根据权利要求 4 所述的发光驱动单元,其特征在于,所述逆变器电路包括:

第三晶体管,用于响应于所述第一时钟信号,向第一节点提供所述帧线标记信号;

第四晶体管,具有:与所述第一节点连接的栅电极、与第二电压供应端连接的源电极以及与第二节点连接的漏电极;

第二电容器,连接在所述第一节点和所述第二电压供应端之间;

第五晶体管,具有:与所述输入信号生成电路的所述第二晶体管的所述源电极连接的漏电极、与所述第二电压供应端连接的源电极以及与所述第二节点连接的栅电极;

第六晶体管,具有:与所述第二节点连接的源电极、与第三节点连接的漏电极以及用于接收所述第二时钟信号的栅电极;

第七晶体管,具有:与所述第三节点连接的源电极、与第一电压供应端连接的漏电极以及用于接收所述第一时钟信号的栅电极;

第八晶体管,具有:与所述第三节点连接的栅电极、用于接收所述第二时钟信号的漏电极以及与第四节点连接的源电极;以及

第三电容器,连接在所述第三节点和所述第四节点之间。

6. 根据权利要求 5 所述的发光驱动单元,其特征在于,所述输出切换电路包括:

输出端,用于输出所述发光信号;

第九晶体管,具有:与所述第一节点连接的栅电极、与所述第二电压供应端连接的源电

极以及与所述输出端连接的漏电极；以及

第十晶体管，具有：与所述第二节点连接的栅电极、与所述输出端连接的源电极以及与所述第一电压供应端连接的漏电极。

7. 根据权利要求 6 所述的发光驱动单元，其特征在于，还包括：

输出控制电路，具有：

第一输出控制晶体管，连接在所述第一电压供应端和所述第一节点之间；以及

第二输出控制晶体管，连接在所述第二电压供应端和所述第二节点之间。

8. 根据权利要求 7 所述的发光驱动单元，其特征在于，

当高电平的输出控制信号施加至所述输出控制电路时，将所述第二电压作为所述发光信号以 DC 电平的方式予以输出。

9. 根据权利要求 2 所述的发光驱动单元，其特征在于，

所述输入信号生成电路、所述逆变器电路以及所述输出切换电路由 P 沟道金属氧化物半导体晶体管构成。

10. 根据权利要求 9 所述的发光驱动单元，其特征在于，所述输入信号生成电路包括：

第一晶体管，具有：漏电极、用于接收所述帧线标记信号的源电极以及用于接收所述第一时钟信号的栅电极，所述第一晶体管用于响应于所述第一时钟信号将所述帧线标记信号从所述源电极施加至所述漏电极；

第二晶体管，具有：用于接收所述第二时钟信号的源电极、与所述第一晶体管的所述漏电极连接的栅电极以及用于输出所述逐次输入信号的漏电极；以及

第一电容器，连接在所述第一晶体管的所述漏电极和所述第二晶体管的所述漏电极之间。

11. 根据权利要求 10 所述的发光驱动单元，其特征在于，所述逆变器电路包括：

第三晶体管，用于响应于所述第一时钟信号，将所述帧线标记信号提供给第一节点；

第四晶体管，具有：与所述第一节点连接的栅电极、与第一电压供应端连接的源电极以及与第二节点连接的漏电极；

第二电容器，连接在所述第一节点和所述第一电压供应端之间；

第五晶体管，具有：与所述输入信号生成电路的所述第二晶体管的所述漏电极连接的漏电极、与所述第一电压供应端连接的源电极以及与所述第二节点连接的栅电极；

第六晶体管，具有：与所述第二节点连接的源电极、与第三节点连接的漏电极以及用于接收所述第二时钟信号的栅电极；

第七晶体管，具有：与所述第三节点连接的源电极、与第二电压供应端连接的漏电极以及用于接收所述第一时钟信号的栅电极；

第八晶体管，具有：与所述第三节点连接的栅电极、用于接收所述第二时钟信号的源电极以及与第四节点连接的漏电极；以及

第三电容器，连接在所述第三节点和所述第四节点之间。

12. 根据权利要求 11 所述的发光驱动单元，其特征在于，所述输出切换电路包括：

输出端，用于输出所述发光信号；

第九晶体管，具有：与所述第一节点连接的栅电极、与所述第一电压供应端连接的源电极以及与所述输出端连接的漏电极；以及

第十晶体管,具有:与所述第二节点连接的栅电极、与所述输出端连接的源电极以及与所述第二电压供应端连接的漏电极。

13. 根据权利要求 12 所述的发光驱动单元,其特征在于,还包括:

输出控制电路,与所述逆变器电路连接,并且受输出控制信号的控制,

当向所述输出控制电路施加低电平的所述输出控制信号时,将所述第一电压作为所述发光信号以 DC 电平的方式予以输出。

14. 一种发光驱动部,其特征在于,包括:

第一发光驱动单元,用于将帧线标记信号作为输入信号予以接收,受第一时钟信号和第二时钟信号的控制,并且用于输出第一发光信号和第一逐次输入信号;以及

第二发光驱动单元至第 n 发光驱动单元,分别受所述第一时钟信号和所述第二时钟信号的控制,并且分别用于输出第二发光信号至第 n 发光信号,其中 n 为大于或等于 3 的整数,

所述第一发光驱动单元至第 (n-1) 发光驱动单元分别用于将所述第一逐次输入信号和第二至第 (n-1) 逐次输入信号作为输入信号依次提供给所述第二发光驱动单元至第 n 发光驱动单元,

所述第一发光驱动单元至第 n 发光驱动单元分别具有:

输入信号生成电路,用于响应于所述第一时钟信号接收所述输入信号,并且用于响应于所述输入信号接收所述第二时钟信号并且输出在所述第一逐次输入信号至第 (n-1) 逐次输入信号中的一个信号;

逆变器电路,用于响应于所述第一时钟信号接收所述输入信号,反转所述输入信号以生成逆变器输出信号;以及

输出切换电路,用于响应于所述逆变器输出信号,将高电平的第一电压或者低电平的第二电压作为在所述第一发光信号至第 n 发光信号中的一个信号予以输出。

15. 根据权利要求 14 所述的发光驱动部,其特征在于,

所述第一发光驱动单元至第 n 发光驱动单元分别由相同的单一晶体管构成。

16. 根据权利要求 15 所述的发光驱动部,其特征在于,

所述第一发光信号至第 n 发光信号具有将所述帧线标记信号反转的形态。

17. 一种有机发光显示装置,其特征在于,包括:

显示面板,包括分别具有有机发光二极管的多个像素电路,用于接收第一电源电压和第二电源电压;

扫描驱动部,用于通过第一扫描线至第 n 扫描线向所述像素电路依次提供第一扫描信号至第 n 扫描信号,其中 n 为大于或等于 3 的整数;

数据驱动部,用于根据所述第一扫描信号至第 n 扫描信号,通过多个数据线向所述像素电路提供数据电压;

发光驱动部,用于通过第一发光控制线至第 n 发光控制线向所述像素电路依次提供第一发光信号至第 n 发光信号;以及

时序控制器,用于向所述扫描驱动部、所述数据驱动部以及所述发光驱动部提供第一时钟信号和第二时钟信号;

所述发光驱动部包括分别生成所述第一发光信号至第 n 发光信号的第一发光驱动单

元至第 n 发光驱动单元，

所述第一发光驱动单元至第 n 发光驱动单元中的每一个受所述第一时钟信号和所述第二时钟信号的控制，用于将帧线标记信号或者第一逐次输入信号至第 (n-1) 逐次输入信号作为输入信号予以接收，所述第一发光驱动单元至第 n 发光驱动单元由相同的单一晶体管构成。

18. 根据权利要求 17 所述的有机发光显示装置，其特征在于，

当所述发光驱动部由 N 沟道金属氧化物半导体晶体管构成时，所述第一发光信号至第 n 发光信号为低电平的区间与在所述像素电路中执行数据编程的区间相对应，所述第一发光信号至第 n 发光信号为高电平的区间与分别包括在所述像素电路中的有机发光二极管发光的区间相对应。

19. 根据权利要求 18 所述的有机发光显示装置，其特征在于，

当所述发光驱动部由 N 沟道金属氧化物半导体晶体管构成时，通过控制所述第一发光信号至第 n 发光信号的待机比，控制所述显示面板显示黑色图像区间的长度。

20. 根据权利要求 19 所述的有机发光显示装置，其特征在于，

通过所述发光驱动部向所述像素电路依次提供所述第一发光信号至第 n 发光信号，分别包括在所述像素电路的有机发光二极管依次发光。

## 发光驱动单元、发光驱动部及有机发光显示装置

### 技术领域

[0001] 本发明涉及发光驱动部 (emission driver), 具体涉及包括逆变器电路的、由 n 型或者 p 型的单一晶体管构成的发光驱动部。

### 背景技术

[0002] 逐行发光方式为有机发光显示装置的驱动方法之一, 逐行发光方式是指, 根据依次施加的扫描信号扫描数据, 然后根据依次施加的发光(emission)信号使最先被扫描的线的 OLED 元件开始发光的方式。此时, 通过调整未施加发光信号的区间的长度、即待机比 (off dutyratio), 能够得到连续的黑暗(dimming)效果, 并且具有与插入黑带时相同的效果, 因此可以消除运动模糊(motion blur)现象。

[0003] 然而, 通过互补金属氧化物半导体(CMOS)晶体管构成用于提供上述发光信号的发光驱动部的情况下, 存在速度慢的问题, 并且还需要反转(inverted)输入信号。

### 发明内容

[0004] 本发明的一目的在于提供包括逆变器电路从而可以由 n 型或者 p 型的单一晶体管构成的发光驱动单元。

[0005] 本发明的另一目的在于提供包括上述发光驱动单元从而可以以一个非反转输入信号进行控制的发光驱动部。

[0006] 本发明的再一目的在于提供包括上述发光驱动部从而可进行脉冲(impulse)驱动的有机发光显示装置。

[0007] 然而, 本发明所要解决的技术问题并不限于此, 在不脱离本发明的思想和领域的范围内可以进行多种扩展。

[0008] 为了达到本发明的一目的, 根据本发明的实施例的发光驱动单元包括: 输入信号生成电路; 逆变器电路; 以及输出切换电路。所述输入信号生成电路、所述逆变器电路以及所述输出切换电路由相同的单一晶体管构成。

[0009] 所述输入信号生成电路用于响应于第一时钟信号接收帧线标记(FrameLineMark, 简称为 FLM)信号, 并且用于响应于所述 FLM 信号接收第二时钟信号并且输出逐次输入信号。

[0010] 所述逆变器电路用于响应于所述第一时钟信号接收所述 FLM 信号, 反转所述 FLM 信号以生成逆变器输出信号。

[0011] 所述输出切换电路用于响应于所述逆变器输出信号, 将高电平的第一电压或者低电平的第二电压作为发光(emission)信号予以输出。

[0012] 根据一实施例, 所述发光信号可以具有将所述 FLM 信号反转(inverted)的形态。

[0013] 根据一实施例, 所述输入信号生成电路、所述逆变器电路以及所述输出切换电路可以由 N 沟道金属氧化物半导体(N-channel MetalOxideSemiconductor, 简称为 NMOS)晶体管构成。

[0014] 根据一实施例,所述输入信号生成电路可以包括:第一晶体管、第二晶体管以及第一电容器。所述第一晶体管包括:源电极、用于接收所述FLM信号的漏电极以及用于接收所述第一时钟信号的栅电极,所述第一晶体管可以响应于所述第一时钟信号将所述FLM信号从所述漏电极向所述源电极施加。所述第二晶体管可以包括:用于接收所述第二时钟信号的漏电极;与所述第一晶体管的所述源电极连接的栅电极;以及用于输出所述逐次输入信号的源电极。所述第一电容器可以连接在所述第一晶体管的所述源电极和所述第二晶体管的所述源电极之间。

[0015] 根据一实施例,所述逆变器电路可以包括:第三晶体管至第八晶体管、第二电容器以及第三电容器。所述第三晶体管可以用于响应于所述第一时钟信号,向第一节点提供所述FLM信号。所述第四晶体管可以包括:与所述第一节点连接的栅电极;与第二电压供应端连接的源电极;以及与第二节点连接的漏电极。所述第二电容器可以连接在所述第一节点和所述第二电压供应端之间。所述第五晶体管可以包括:与所述输入信号生成电路的所述第二晶体管的所述源电极连接的漏电极;与所述第二电压供应端连接的源电极;以及与所述第二节点连接的栅电极。所述第六晶体管可以包括:与所述第二节点连接的源电极;与第三节点连接的漏电极;以及用于接收所述第二时钟信号的栅电极。所述第七晶体管可以包括:与所述第三节点连接的源电极;与第一电压供应端连接的漏电极;以及用于接收所述第一时钟信号的栅电极。所述第八晶体管可以包括:与所述第三节点连接的栅电极;用于接收所述第二时钟信号的漏电极;以及与第四节点连接的源电极。所述第三电容器可以连接在所述第三节点和所述第四节点之间。

[0016] 根据一实施例,所述输出切换电路可以包括:输出端、第九晶体管以及第十晶体管。所述输出端可以用于输出所述发光信号。所述第九晶体管可以包括:与所述第一节点连接的栅电极;与所述第二电压供应端连接的源电极;以及与所述输出端连接的漏电极。所述第十晶体管可以包括:与所述第二节点连接的栅电极;与所述输出端连接的源电极;以及与所述第一电压供应端连接的漏电极。

[0017] 根据一实施例,所述发光驱动单元还可以包括:输出控制电路,其中,所述输出控制电路包括:连接在所述第一电压供应端和所述第一节点之间的第一输出控制晶体管;以及连接在所述第二电压供应端和所述第二节点之间的第二输出控制晶体管。

[0018] 根据一实施例,当高电平的输出控制信号施加至所述输出控制电路时,可以将所述第二电压作为所述发光信号以DC电平的方式予以输出。

[0019] 根据一实施例,所述输入信号生成电路、所述逆变器电路以及所述输出切换电路可以由P沟道金属氧化物半导体(P-channel MetalOxide Semiconductor,简称为PMOS)晶体管构成。

[0020] 根据一实施例,当所述发光驱动单元由P沟道金属氧化物半导体构成时,所述发光驱动单元还可以包括:与所述逆变器电路连接并且受输出控制信号的控制的输出控制电路。当向所述输出控制电路施加了低电平的所述输出控制信号时,可以将所述第一电压作为所述发光信号以DC电平的方式予以输出。

[0021] 为了达到本发明的另一目的,根据本发明的实施例的发光驱动部包括:第一发光驱动单元,用于将帧线标记(Frame Line Mark,简称为FLM)信号作为输入信号予以接收,受第一时钟信号和第二时钟信号的控制,并且用于输出第一发光(emission)信号和第一逐次

输入信号；以及第二发光驱动单元至第 n 发光驱动单元，分别受所述第一时钟信号和所述第二时钟信号的控制，并且分别用于输出第二发光信号至第 n 发光信号，其中 n 为大于或等于 3 的整数。

[0022] 所述第一发光驱动单元至第 n 发光驱动单元分别包括：输入信号生成电路，用于响应于所述第一时钟信号接收所述输入信号，并且用于响应于所述输入信号接收所述第二时钟信号并且输出所述第一逐次输入信号至第 (n-1) 逐次输入信号中的一个信号；逆变器电路，用于响应于所述第一时钟信号接收所述输入信号，反转所述输入信号以生成逆变器输出信号；以及输出切换电路，用于响应于所述逆变器输出信号，将高电平的第一电压或者低电平的第二电压作为所述第一发光信号至第 n 发光信号中的一个信号输出。

[0023] 根据一实施例，所述第一发光驱动单元至第 n 发光驱动单元分别可以由相同的单一晶体管构成。

[0024] 根据一实施例，所述第一发光信号至第 n 发光信号可以具有将所述 FLM 信号反转 (inverted) 的形态。

[0025] 为了达到本发明的再一目的，根据本发明的实施例的有机发光显示装置包括：显示面板，包括分别具有有机发光二极管的多个像素电路，用于接收第一电源电压和第二电源电压；扫描驱动部，用于通过第一扫描线至第 n 扫描线向所述像素电路依次提供第一扫描信号至第 n 扫描信号，其中 n 为大于或等于 3 的整数；数据驱动部，用于根据所述第一扫描信号至第 n 扫描信号，通过多个数据线向所述像素电路提供数据电压；发光驱动部，用于通过第一发光(emission)控制线至第 n 发光控制线向所述像素电路依次提供第一发光信号至第 n 发光信号；以及时序控制器，用于向所述扫描驱动部、所述数据驱动部以及所述发光驱动部提供第一时钟信号和第二时钟信号。

[0026] 所述发光驱动部包括：分别生成所述第一发光信号至第 n 发光信号的第一发光驱动单元至第 n 发光驱动单元。所述第一发光驱动单元至第 n 发光驱动单元中的每一个受所述第一时钟信号和所述第二时钟信号的控制，用于将帧线标记(Frame Line Mark，简称为 FLM) 信号或者第一逐次输入信号至第 (n-1) 逐次输入信号作为输入信号予以接收，并且由相同的单一晶体管构成。

[0027] 根据一实施例，当所述发光驱动部由 N 沟道金属氧化物半导体(NMOS)晶体管构成时，所述第一发光信号至第 n 发光信号为低电平的区间可以与在所述像素电路中执行数据编程的区间相对应，所述第一发光信号至第 n 发光信号为高电平的区间可以与分别包括在所述像素电路中的有机发光二极管发光的区间相对应。

[0028] 根据一实施例，当所述发光驱动部由 N 沟道金属氧化物半导体晶体管构成时，通过控制所述第一发光信号至第 n 发光信号的待机比(off-duty ratio)，可以控制所述显示面板显示黑色图像的区间的长度。

[0029] 根据一实施例，通过所述发光驱动部向所述像素电路依次提供所述第一发光信号至第 n 发光信号，分别包括在所述像素电路的有机发光二极管可以依次发光。

[0030] 根据本发明的实施例的发光驱动单元通过在内部包括逆变器电路，从而可以由 n 型或者 p 型的单一晶体管构成。

[0031] 根据本发明的实施例的发光驱动部可以被一个非反转输入信号控制，通过控制所述输入信号的脉冲宽度，可以调整发光信号的脉冲宽度。

[0032] 根据本发明的实施例的有机发光显示装置可以以较高的速度实现脉冲驱动。

[0033] 然而,本发明的效果并不限于此,在不脱离本发明的思想和领域的范围内可以进行多种扩展。

## 附图说明

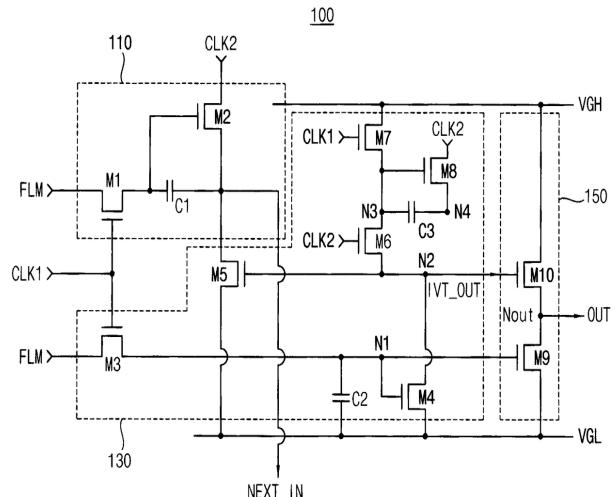

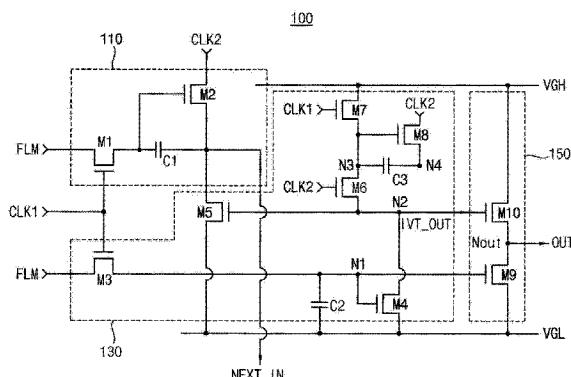

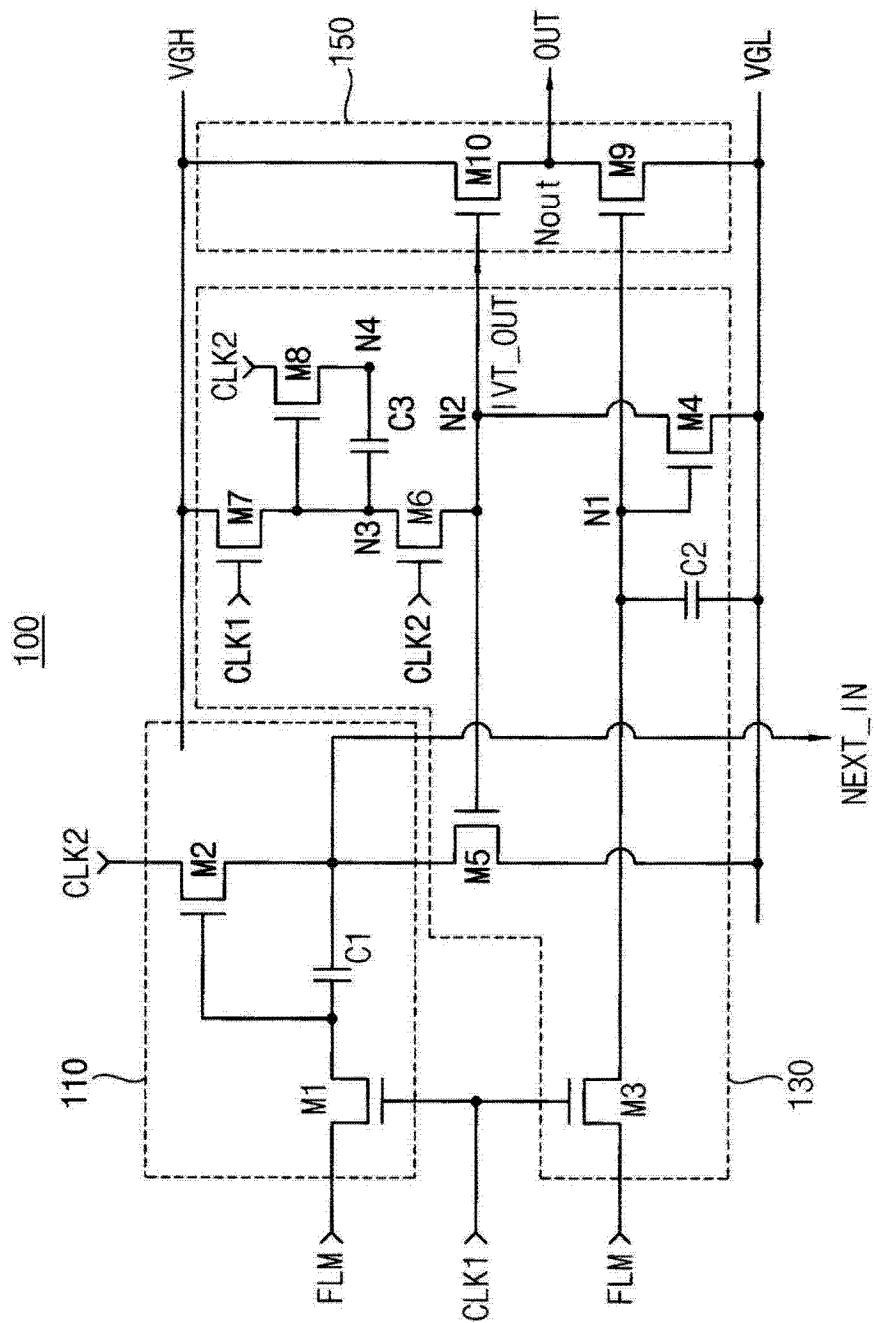

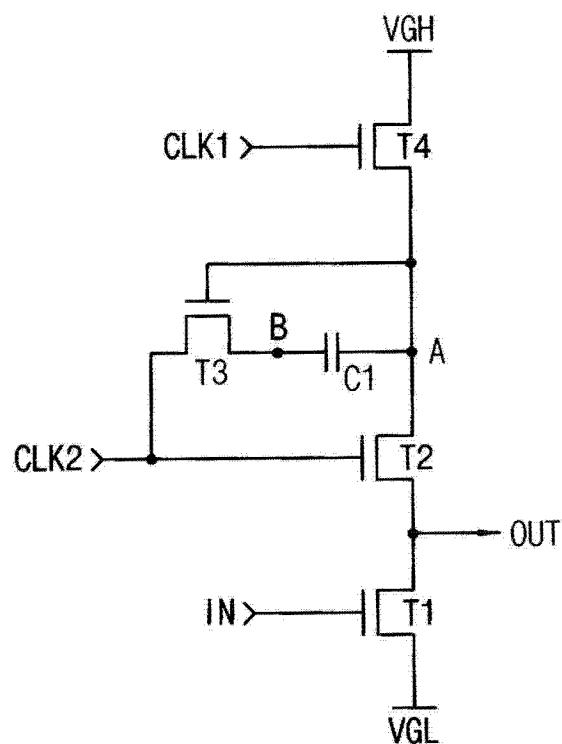

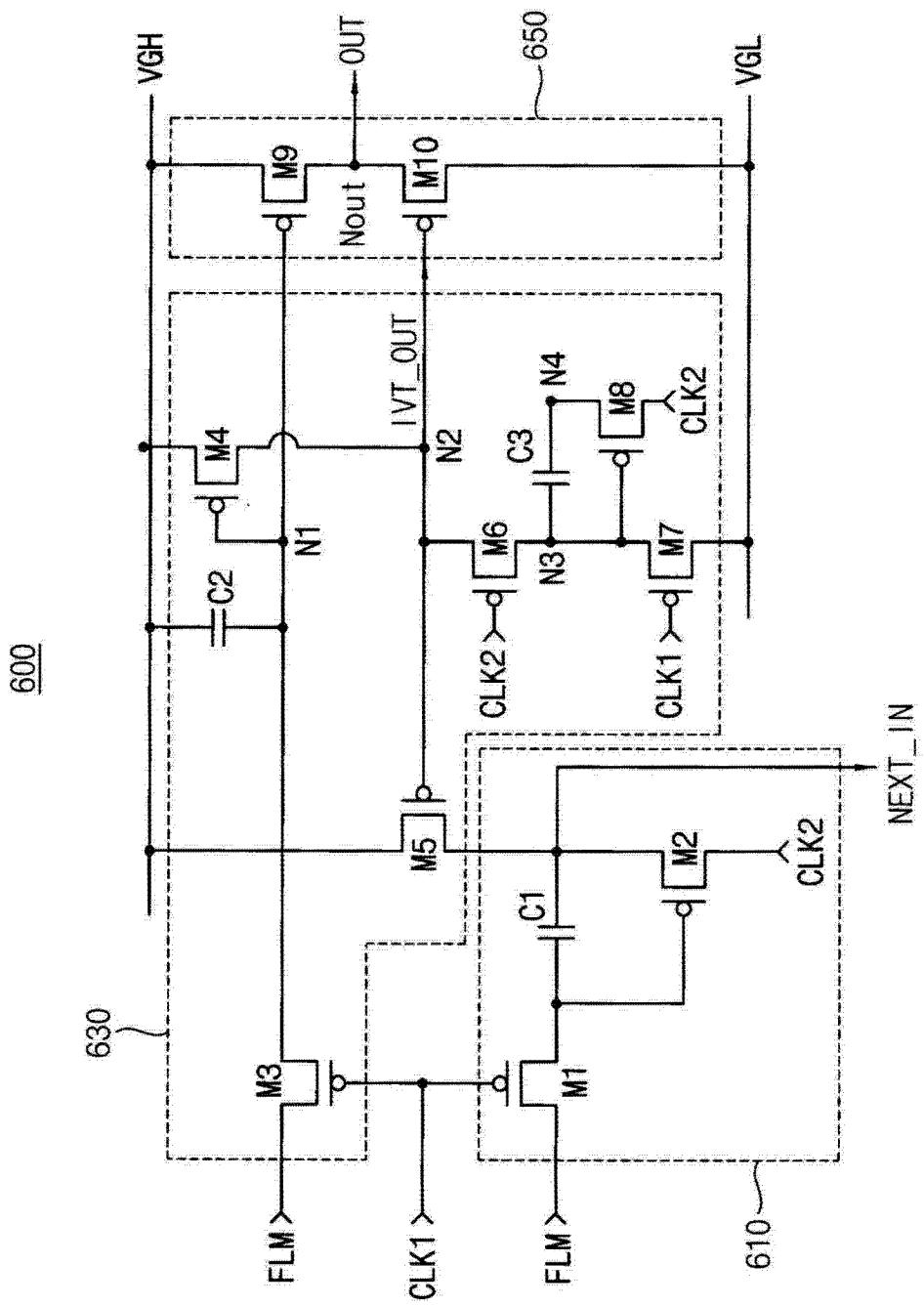

- [0034] 图 1 是表示根据本发明一实施例的发光驱动单元的电路图 ;

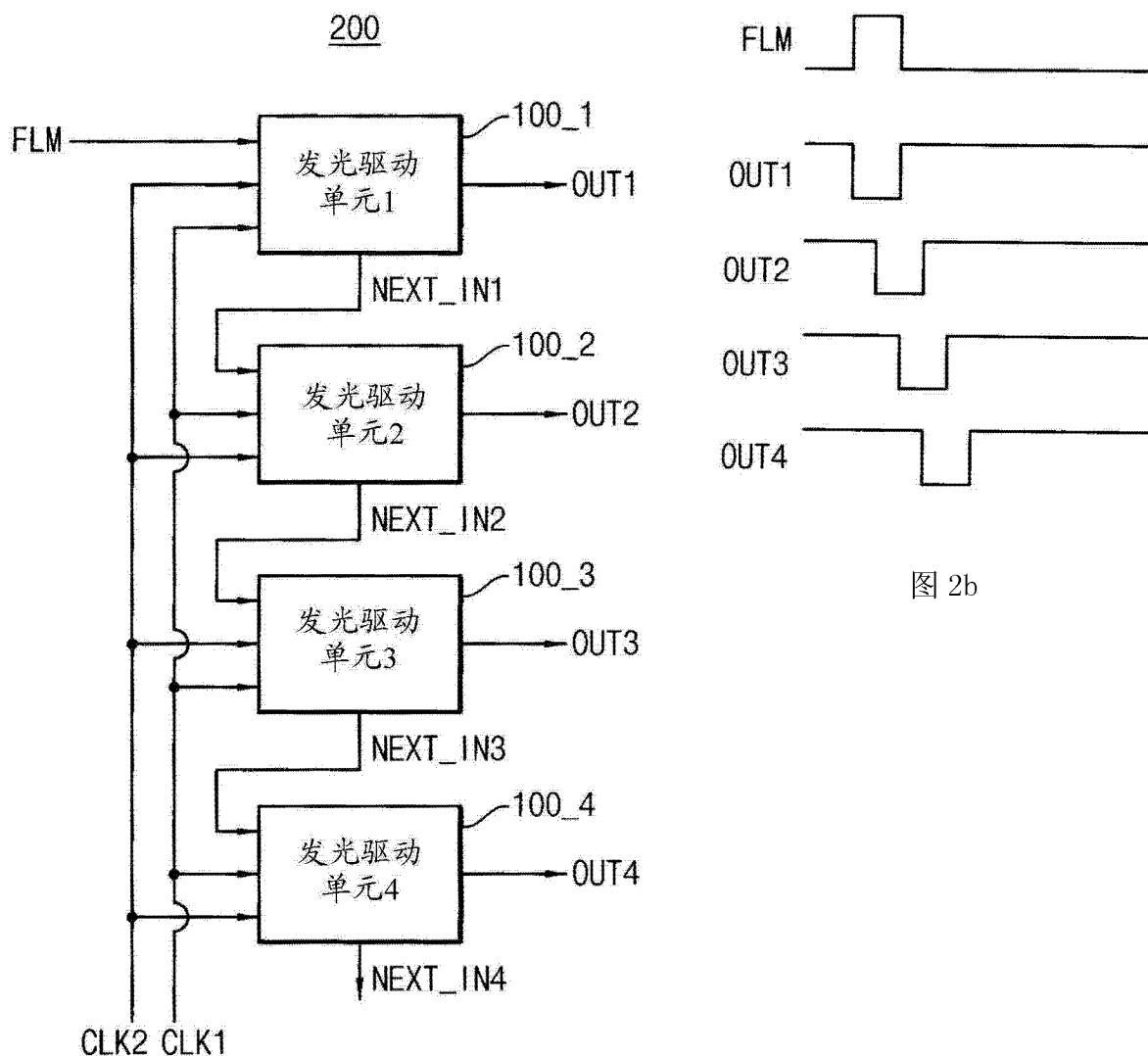

- [0035] 图 2a 是表示根据本发明一实施例的发光驱动部的框图 ;

- [0036] 图 2b 是表示图 2a 的发光驱动部的运行的时序图 ;

- [0037] 图 3a 是表示图 1 的发光驱动单元所包括的逆变器电路的电路图 ;

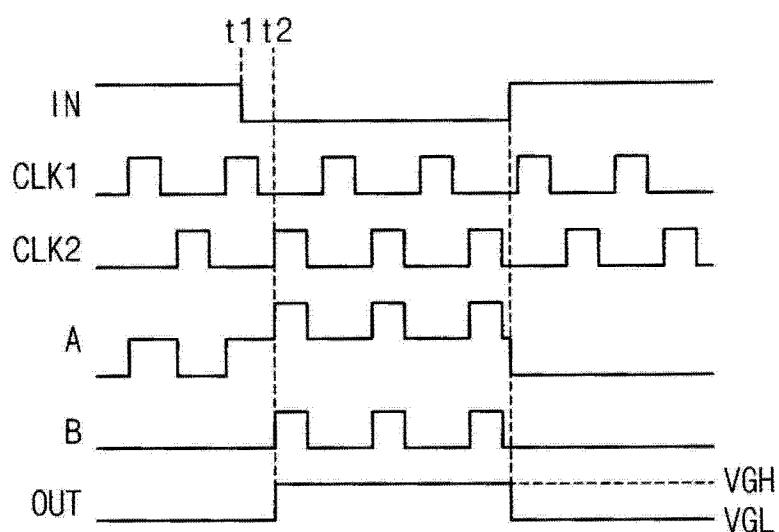

- [0038] 图 3b 是表示图 3a 的逆变器电路的运行的时序图 ;

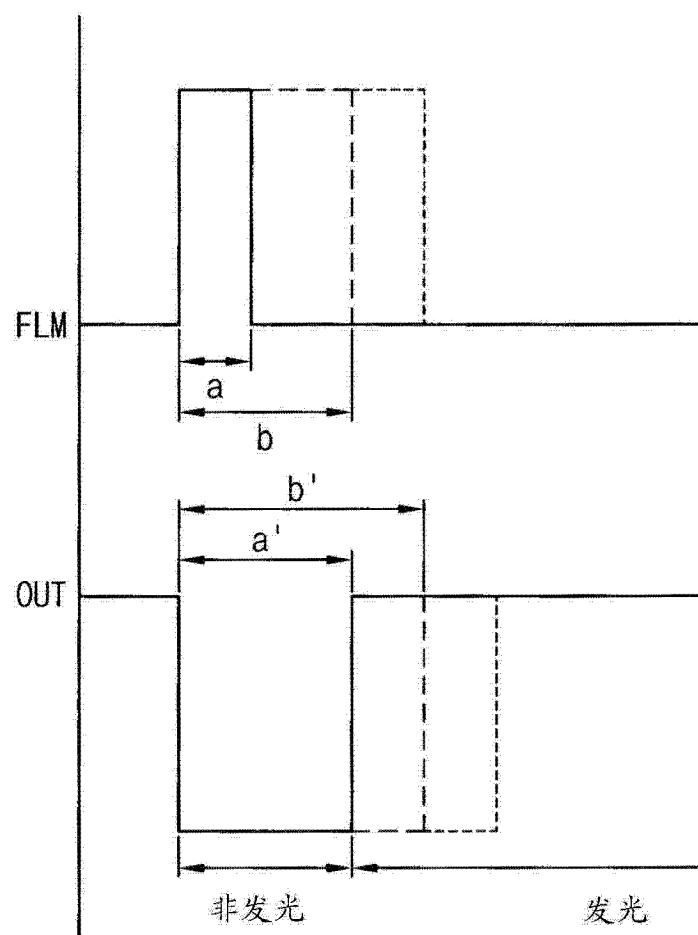

- [0039] 图 4 是表示图 1 的发光驱动单元中输入和输出关系的示意图 ;

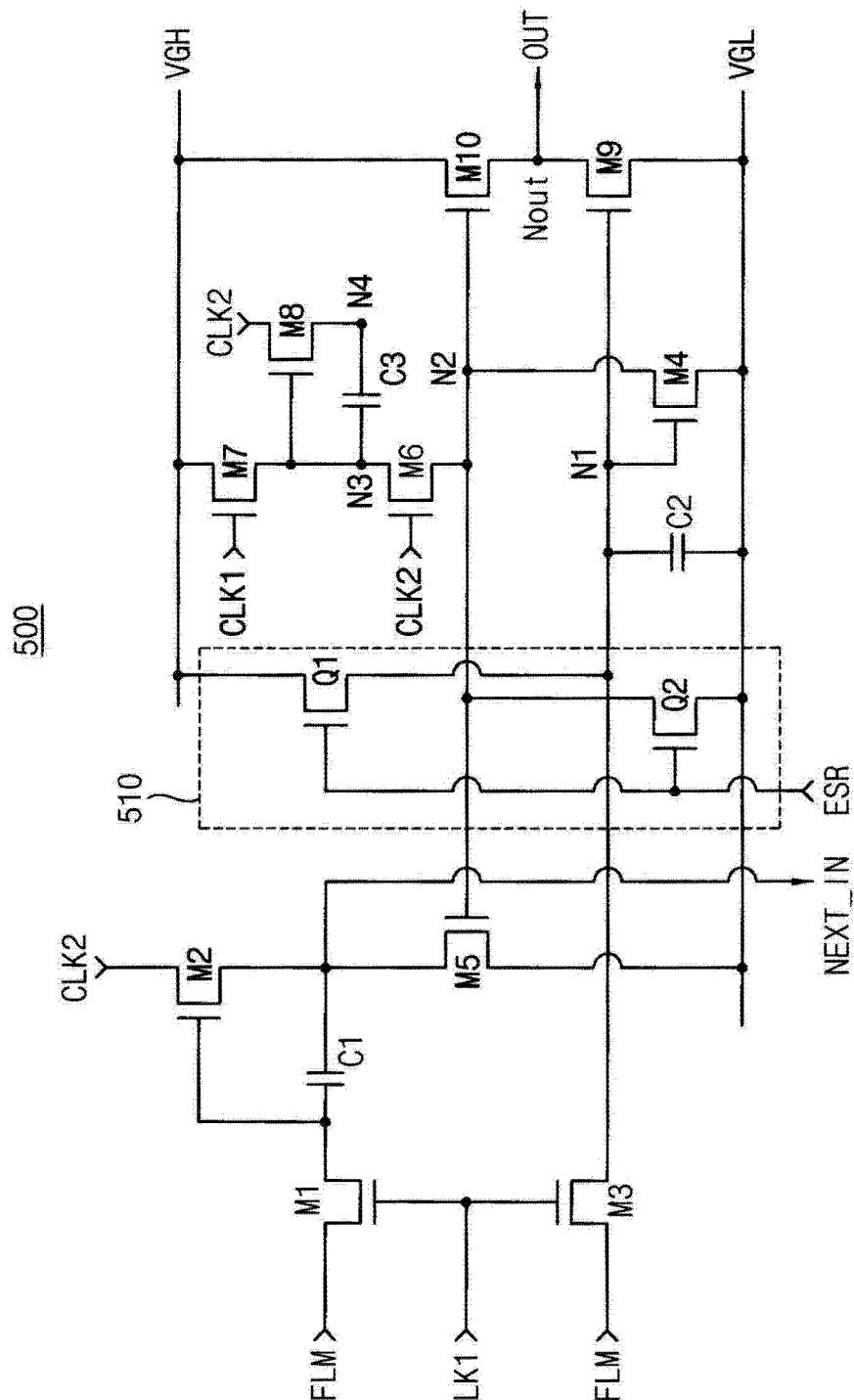

- [0040] 图 5 是表示根据本发明另一实施例的发光驱动单元的电路图 ;

- [0041] 图 6 是表示根据本发明再一实施例的发光驱动单元的电路图 ;

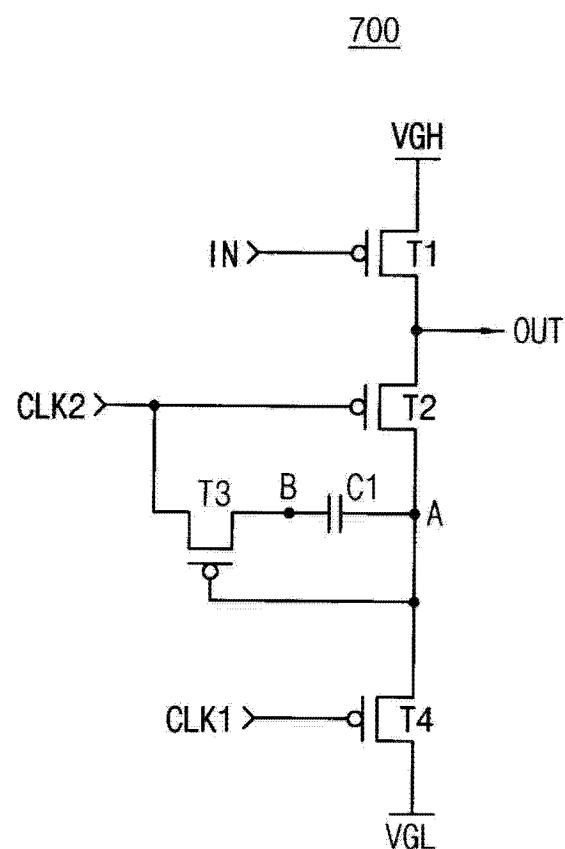

- [0042] 图 7 是表示图 6 的发光驱动单元所包括的逆变器电路的电路图 ;

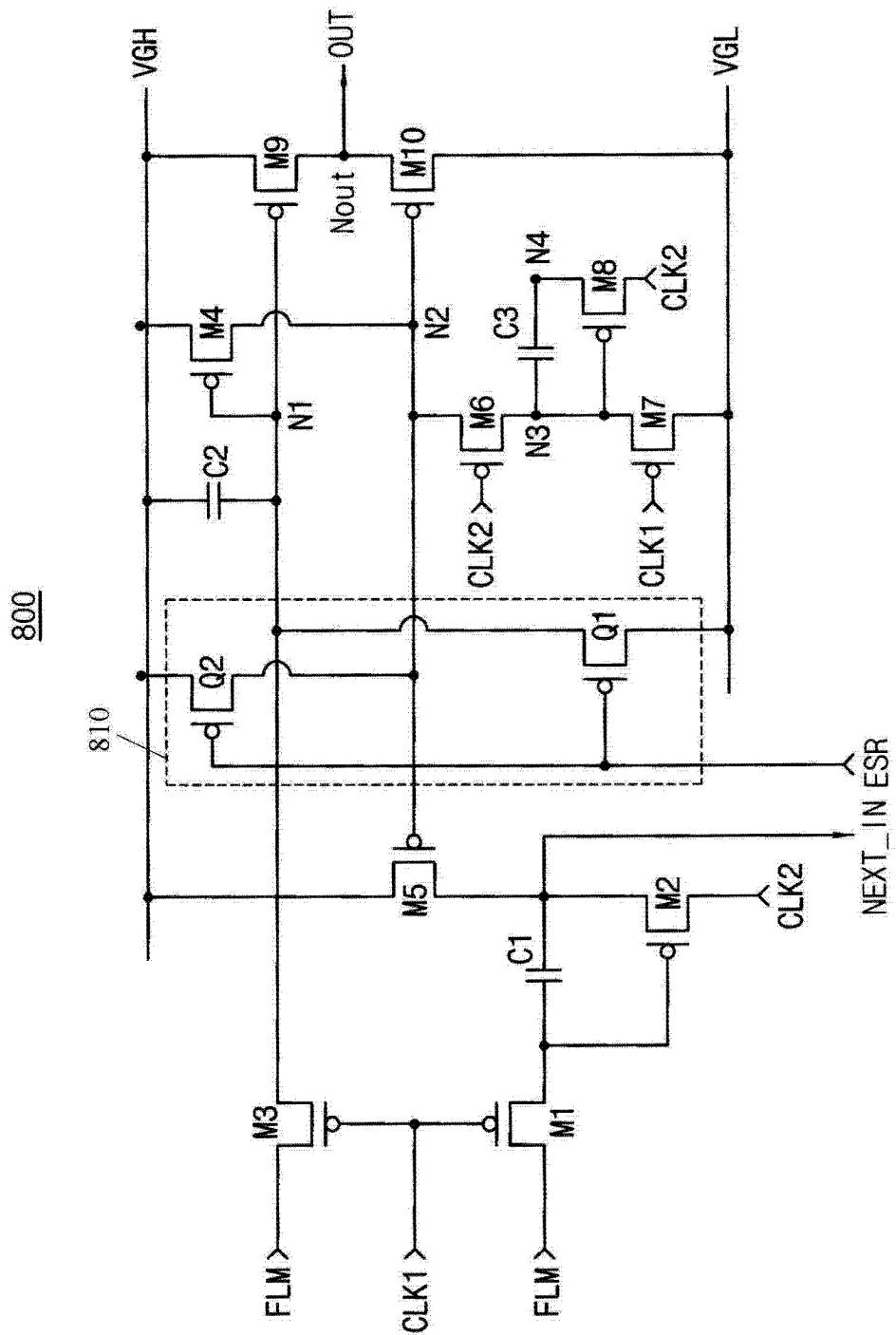

- [0043] 图 8 是表示根据本发明再一实施例的发光驱动单元的电路图 ;

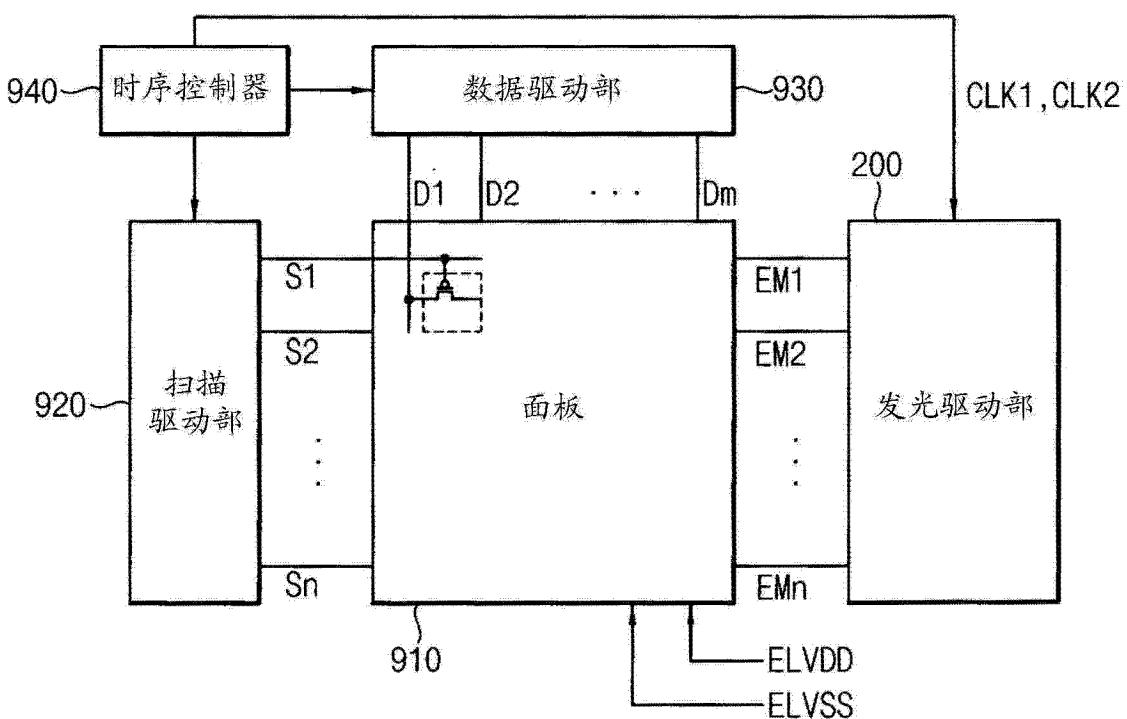

- [0044] 图 9 是表示根据本发明一实施例的有机发光显示装置的框图 ;

- [0045] 图 10 是表示包括图 9 的有机发光显示装置的电子设备的框图。

## 具体实施方式

[0046] 就本发明所公开的本发明的实施例,其特定的结构或功能性说明仅以示例性地说明本发明的实施例为目的,本发明的实施例能够以多种形式实施,而不能解释为本发明仅限于本文中说明的实施例。

[0047] 本发明可进行多种变化并具有多种形态,在此仅将特定实施例图示在附图中并在本文中进行详细说明。但是本发明不限定在特定的公开形态,在不脱离本发明的思想及技术范围的情况下应理解为包括所有变更、等同物以及替代物。

[0048] 虽然第一、第二等术语可以用于说明多种组成要素,但所述组成要素不限于所述术语。使用所述术语的目的在于区别一个组成要素与另一个组成要素。例如,在不脱离本发明的保护范围下,第一组成要素可以命名为第二组成要素,类似地,第二组成要素也可以命名为第一组成要素。

[0049] 某种组成要素与另外的组成要素描述为“连接”或“接触”,表示其与另外的组成要素直接连接或接触,也应理解为中间还可以存在其它组成要素。相反,某种组成要素与另外组成要素“直接连接”或“直接接触”,应理解为中间不存在其它组成要素。说明组成要素之间关系的其他表述方式,即“…之间”、“就在…之间”或者“与…相邻”和“…直接相邻”也应进行相同的解释。

[0050] 本申请所使用的术语仅以说明特定实施例而使用,并不用于限定本发明。单数表述在上下文中其含义有明显不同的以外,包括复数含义。本申请中“包括”、“具备”或“具有”等术语,应理解为仅用于阐明存在着所述的特征、数字、步骤、动作、组成要素、部件或者其结合,并不是预先排除一个或一个以上的其它特征、数字、步骤、动作、组成要素、部件或其结合的存在或附加的可能性。

[0051] 没有其他定义时,包括技术或科学术语,在此使用的所有术语,具有与本发明所属领域的普通技术人员通常理解的相同的含义。通常使用的词典所定义的相同的术语,应理解为与相关技术上下文所具有的含义一致,除本发明明确定义以外,不应解释成理想或过于形式的含义。

[0052] 以下结合附图,对本发明的优选实施例进行进一步详细的说明。对于附图中的同一组成要素使用相同的附图标记,并省略对同一组成要素的重复说明。

[0053] 图 1 是表示根据本发明一实施例的发光驱动单元的电路图。

[0054] 在一实施例中,发光驱动单元 100 能够仅由 N 沟道金属氧化物半导体(NMOS)晶体管构成。在另一实施例中,发光驱动单元 100 能够仅由 P 沟道金属氧化物半导体(PMOS)晶体管构成。现有的发光驱动部由包括 p- 沟道晶体管和 n- 沟道晶体管的互补金属氧化物半导体(CMOS)晶体管构成。从而,虽然功耗低,但运行速度慢,尤其需要额外的反转输入信号。根据本发明的实施例的发光驱动部通过在内部包括逆变器电路,从而能够以 n 型或者 p 型的单一晶体管构成,并且仅通过一个非反转输入信号和两个时钟信号就能够进行控制。

[0055] 图 1 表示由 N 沟道金属氧化物半导体晶体管构成的发光驱动单元 100。下面说明由 N 沟道金属氧化物半导体晶体管构成的发光驱动单元 100 的组成以及运行。

[0056] 如图 1 所示,发光驱动单元 100 包括:输入信号生成电路 110、逆变器电路 130 以及输出切换电路 150。

[0057] 输入信号生成电路 110 响应于第一时钟信号 CLK1 接收帧线标记(Frame Line Mark, 简称为 FLM)信号 FLM;响应于帧线标记信号 FLM 接收第二时钟信号 CLK2;并且输出逐次输入信号 NEXT\_IN。在一实施例,输入信号生成电路 110 可以包括:第一晶体管 M1、第二晶体管 M2 以及第一电容器 C1。第一晶体管 M1 包括:源电极;接收帧线标记信号 FLM 的漏电极;以及响应于第一时钟信号 CLK1 将帧线标记信号 FLM 施加至所述源电极的栅电极。第二晶体管 M2 包括:接收第二时钟信号 CLK2 的漏电极;与第一晶体管 M1 的源电极连接的栅电极;以及输出逐次输入信号 NEXT\_IN 的源电极。第一电容器 C1 连接在第一晶体管 M1 的源电极和第二晶体管 M2 的源电极之间。

[0058] 逆变器电路 130 响应于第一时钟信号 CLK1 接收帧线标记信号 FLM,并反转帧线标记信号 FLM,以生成逆变器输出信号 IVT\_OUT。在一实施例中,逆变器电路 130 可以包括:第三晶体管 M3、第四晶体管 M4、第五晶体管 M5、第六晶体管 M6、第七晶体管 M7、第八晶体管 M8;以及第二电容器 C2、第三电容器 C3。

[0059] 在逆变器电路 130 中,第三晶体管 M3 响应于第一时钟信号 CLK1 将帧线标记信号 FLM 提供给第一节点 N1。第四晶体管 M4 包括:与第一节点 N1 连接的栅电极;与第二电压供应端 VGL 连接的源电极;以及与第二节点 N2 连接的漏电极。第二电容器 C2 连接在第一节点 N1 和第二电压供应端 VGL 之间。第五晶体管 M5 包括:与输入信号生成电路 110 的第二晶体管 M2 的源电极连接的漏电极;与第二电压供应端 VGL 连接的源电极;以及与第二节点 N2 连接的栅电极。第六晶体管 M6 包括:与第二节点 N2 连接的源电极;与第三节点 N3 连接的漏电极;以及接收第二时钟信号 CLK2 的栅电极。第七晶体管 M7 包括:与第三节点 N3 连接的源电极;与第一电压供应端 VGH 连接的漏电极;以及接收第一时钟信号 CLK1 的栅电极。第八晶体管 M8 包括:与第三节点 N3 连接的栅电极;接收第二时钟信号 CLK2 的漏电极;以及与第四节点 N4 连接的源电极。第三电容器 C3 连接在第三节点 N3 和第四节点 N4 之间。

[0060] 逆变器电路 130 实现下述功能,即,响应于周期性地施加的时钟信号,反转输入信号并将其输出。因此,逆变器电路 130 可以响应于第一时钟信号 CLK1 和第二时钟信号 CLK2 反转帧线标记信号 FLM,从而生成逆变器输出信号 IVT\_OUT。关于逆变器电路 130 的具体运行,将在后面参考图 3a 和图 3b 进行详细的说明。

[0061] 输出切换电路 150 响应于逆变器输出信号 IVT\_OUT,将高电平的第一电压 VGH 或者低电平的第二电压 VGL 作为发光(emission)信号 OUT 而予以输出。由此,发光驱动单元 100 的输出 OUT 可以具有脉冲形态。在一实施例中,输出切换电路 150 可以包括:输出端 Nout、第九晶体管 M9 以及第十晶体管 M10。输出端 Nout 输出发光信号 OUT。第九晶体管 M9 包括:与第一节点 N1 连接的栅电极;与第二电压供应端 VGL 连接的源电极;以及与输出端 Nout 连接的漏电极。第十晶体管 M10 包括:与第二节点 N2 连接的栅电极;与输出端 Nout 连接的源电极;以及与第一电压供应端 VGH 连接的漏电极。

[0062] 在发光驱动单元 100 中,发光信号 OUT 可以具有将帧线标记信号 FLM 予以反转(inverted)的形态。在一实施例中,当帧线标记信号 FLM 具有从低电平升至高电平的一次高脉冲(high-pulse)的情况下,发光信号 OUT 具有从高电平降至低电平的一次低脉冲(low-pulse)。根据发光驱动单元 100,包括于像素电路的发光晶体管也由 N 沟道金属氧化物半导体晶体管构成。因此在发光信号 OUT 为低电平的区间,所述发光晶体管被断开(turn-off);在发光信号 OUT 为高电平的区间,所述发光晶体管被导通(turn-on),从而与其连接的有机发光二极管会发光。

[0063] 在一实施例中,第一电压 OUT 可以具有导通 N 沟道金属氧化物半导体晶体管的足够高的电压电平,第二电压 OUT 可以具有断开 N 沟道金属氧化物半导体晶体管的足够低的电压电平。

[0064] 图 2a 是表示根据本发明一实施例的发光驱动部的框图。

[0065] 如图 2a 所示,发光驱动部 200 包括:与显示装置的扫描线的数量相对应的多个发光驱动单元,即第一发光驱动单元 100\_1、第二发光驱动单元 100\_2、第三发光驱动单元 100\_3、第四发光驱动单元 100\_4。例如,当在显示面板和扫描驱动部之间设置有 n 个扫描线的情况下,发光驱动部 200 可以包括 n 个发光驱动单元 100\_1 至发光驱动单元 100\_n。图 2a 中仅示出了四个发光驱动单元,即第一发光驱动单元 100\_1、第二发光驱动单元 100\_2、第三发光驱动单元 100\_3、第四发光驱动单元 100\_4,然而根据实施例,发光驱动部 200 可以包括不同种数量的发光驱动单元。下面,通过四个发光驱动单元,即第一发光驱动单元 100\_1、第二发光驱动单元 100\_2、第三发光驱动单元 100\_3、第四发光驱动单元 100\_4 来说明发光驱动部 200 的运行。

[0066] 第一发光驱动单元 100\_1 将帧线标记信号 FLM 作为输入信号予以接收,被第一时钟信号 CLK1 和第二时钟信号 CLK2 控制,并且输出第一发光信号 OUT1 和第一逐次输入信号 NEXT\_IN1。第一发光信号 OUT1 通过第一发光线施加至显示面板,第一逐次输入信号 NEXT\_IN1 作为输入信号被施加至下一端 100\_2。换言之,从上一端输出的逐次输入信号能够在相邻的下一端用作输入信号。如上所述,只要对第一发光驱动单元 100\_1 施加额外的输入信号 FLM,则在发光驱动单元,即第一发光驱动单元 100\_1、第二发光驱动单元 100\_2、第三发光驱动单元 100\_3、第四发光驱动单元 100\_4 分别生成的逐次输入信号,即第一逐次输入信号 NEXT\_IN1、第二逐次输入信号 NEXT\_IN2、第三逐次输入信号 NEXT\_IN3 能够依次施加至下

一端的发光驱动单元,即第二发光驱动单元 100\_2、第三发光驱动单元 100\_3、第四发光驱动单元 100\_4。

[0067] 每个发光驱动单元,即第一发光驱动单元 100\_1、第二发光驱动单元 100\_2、第三发光驱动单元 100\_3、第四发光驱动单元 100\_4 可以包括:输入信号生成电路、逆变器电路以及输出切换电路。所述输入信号生成电路响应于第一时钟信号 CLK1 接收输入信号,即 FLM、NEXT\_IN1 至 NEXT\_IN3;响应于输入信号,即响应于 FLM、NEXT\_IN1 至 NEXT\_IN3 接收第二时钟信号 CLK2,并且输出第一逐次输入信号 NEXT\_IN1、第二逐次输入信号 NEXT\_IN2、第三逐次输入信号 NEXT\_IN3、第四逐次输入信号 NEXT\_IN4 中的一个信号。所述逆变器电路响应于第一时钟信号 CLK1 接收输入信号,即 FLM、NEXT\_IN1 至 NEXT\_IN3,并且反转输入信号,即翻转 FLM、NEXT\_IN1 至 NEXT\_IN3,从而生成逆变器输出信号。所述输出切换电路响应于所述逆变器输出信号,作为第一发光信号 OUT1 至第四发光信号 OUT4 中的一个信号输出高电平的第一电压或者低电平的第二电压。如上所述,根据本发明的实施例的发光驱动部 200 在不需要额外的反转信号的情况下,仅用三个信号,即仅用 FLM、CLK1、CLK2 就可以控制发光驱动部 200。在一实施例中,第一发光驱动单元 100\_1 至第四发光驱动单元 100\_4 分别可以由相同的单一晶体管构成。

[0068] 图 2b 是表示图 2a 的发光驱动部的运行的时序图。

[0069] 如图 2a 和图 2b 所示,首先帧线标记信号 FLM 施加至第一发光驱动单元 100\_1,然后依次施加第一逐次输入信号 NEXT\_IN1 至第三逐次输入信号 NEXT\_IN3,从而依次输出第一发光信号 OUT1 至第四发光信号 OUT4。即,所生成的第一发光信号 OUT1 至第四发光信号 OUT4 的低脉冲之间位移有一定的时间间隔。由此,显示面板接收发光信号 OUT1 至 OUT4,并且能够以每个线为单位依次发光。在一实施例中,第一发光信号 OUT1 至第四发光信号 OUT4 可以具有将帧线标记信号 FLM 反转的形态。

[0070] 图 3a 是表示图 1 的发光驱动单元所包括的逆变器电路的电路图,图 3b 是表示图 3a 的逆变器电路的运行的时序图。

[0071] 图 3a 的逆变器电路 300 实质上与图 1 的逆变器电路 130 相对应。具体而言,逆变器电路 300 的输入信号 IN、输出信号 OUT、节点 A 分别与逆变器电路 130 的帧线标记信号 FLM、逆变器输出信号 IVT\_OUT、第三节点 N3 相对应。如图 3a 所示,逆变器电路 300 由 N 沟道金属氧化物半导体晶体管构成。下面参考图 3a 和图 3b 来说明逆变器电路 300 的运行。

[0072] 第一晶体管 T1 响应于高电平的输入信号 IN,将低电平的第二电压 VGL 作为输出信号 OUT 予以输出。换言之,当输入信号 IN 为高电平的情况下,第一晶体管 T1 被导通,第二电压 VGL 施加至输出信号 OUT。当输入信号 IN 为低电平的情况下,第一晶体管 T1 被断开,并且根据第一时钟信号 CLK1 和第二时钟信号 CLK2,将高电平的第一电压 VGH 作为输出信号 OUT 予以输出。具体而言,在输入信号 IN 的下降沿(edge)t1 以后第二时钟信号 CLK2 初次上升的上升沿 t2,输出信号 OUT 也上升为高电平 VGH。换言之,在位置 t2 处,输出信号 OUT 与第二时钟信号 CLK2 同步,从而上升至高电平 VGH。通过这种方式,输入信号 IN 经过逆变器电路 300 时发生反转,从而可以作为输出信号 OUT 输出。

[0073] 图 4 是表示图 1 的发光驱动单元中输入和输出关系的示意图。

[0074] 如图 1 和图 4,可知输入信号 FLM 和输出信号 OUT 为互相反转的形态。输入信号 FLM 可以与图 1 的帧线标记信号 FLM 相对应,输出信号 OUT 可以与图 1 的发光信号 OUT 相对

应。在一实施例中,当以N沟道金属氧化物半导体晶体管构成显示装置的情况下,施加高电平的发光信号时,相对应的有机发光二极管可以发光。另一方面,施加低电平的发光信号的区间可以相当于非发光区间。

[0075] 如图4所示,输入信号FLM的高电平脉冲的宽度可以与输出信号OUT的低电平脉冲的宽度成比例。例如,输入信号FLM的高电平脉冲的宽度从a增加至b时,输出信号OUT的低电平的宽度也从a'增加至b'。由此,非发光区间NON-EMISSION的长度也会增加。根据本发明的实施例,通过调整向发光驱动单元100输入的帧线标记信号FLM的高电平脉冲的宽度,可以调整非发光区间NON-EMISSION的长度。在非发光区间NON-EMISSION,在像素电路中实施数据扫描和驱动晶体管的阈值电压补偿等,因此可以通过控制非发光区间NON-EMISSION的长度,来充分地确保用于实施数据扫描和补偿驱动晶体管的阈值电压的时间。

[0076] 另外,由于有机发光二极管在非发光区间NON-EMISSION不发光,因此通过调整非发光区间NON-EMISSION的长度,可以得到连续的黑暗(dimming)效果,并且具有与插入黑带时相同的效果,因此可以消除运动模糊(motion blur)现象。由此,采用由N沟道金属氧化物半导体晶体管构成的发光驱动单元100,可以实施脉冲驱动。

[0077] 图5是表示根据本发明另一实施例的发光驱动单元的电路图。

[0078] 如图5所示,除了输出控制电路510之外,图5的发光驱动单元500具有实质上与图1的发光驱动单元100相同的结构。下面省略与图1的发光驱动单元100重复的说明,而是以输出控制电路510的功能为中心,对发光驱动单元500的运行进行说明。

[0079] 输出控制电路510连接在逆变器电路内部,并且被输出控制信号ESR控制。输出控制电路510可以包括:第一输出控制晶体管Q1和第二输出控制晶体管Q2。

[0080] 在一实施例中,当高电平的输出控制信号ESR施加至输出控制电路510的情况下,将第二电压VGL作为发光信号OUT,以DC电平的方式输出。具体而言,若施加高电平的输出控制信号ESR,则第一输出控制晶体管Q1和第二输出控制晶体管Q2被导通。此时,高电平的第一电压VGH施加至第九晶体管M9的栅电极以导通第九晶体管M9,低电平的第二电压VGL施加至第十晶体管M10的栅电极以断开第十晶体管M10。结果,通过第九晶体管M9,可以将第二电压VGL作为发光信号OUT予以输出。如上所述,包括输出控制电路510的发光驱动单元500可以将发光信号OUT控制成DC电平。例如,如发光驱动单元500,当显示装置由N沟道金属氧化物半导体晶体管构成的情况下,可以将发光信号OUT控制成DC低电平。相反地,当显示装置由P沟道金属氧化物半导体晶体管构成的情况下,可以将发光信号OUT控制成DC高电平。并且,当低电平的输出控制信号ESR施加至输出控制电路510的情况下,第一输出控制晶体管Q1和第二输出控制晶体管Q2会被断开,从而成为实质上与图1的发光驱动单元100相同的电路。

[0081] 如上所述,输出控制电路510实现将发光信号OUT保持为高电平或者低电平的DC信号的功能。在一实施例中,在刚开始驱动显示装置时,可以有效地使用包括输出控制电路510的发光驱动单元500。刚开始驱动显示装置时,则在进入正常运行模式之前需要预定的准备时间,此时可以防止有机发光二极管意外发光的现象。从而,在刚开始驱动显示装置时向输出控制电路510施加了低电平的输出控制信号ESR,则在预定的时间内可以将发光信号OUT保持为DC低电平,从而使有机发光二极管处在被断开的状态。

[0082] 图 6 是表示根据本发明再一实施例的发光驱动单元的电路图。图 6 表示由 P 沟道金属氧化物半导体晶体管构成的发光驱动单元 600。

[0083] 如图 6 所示,发光驱动单元 600 包括:输入信号生成电路 610、逆变器电路 630 以及输出切换电路 650。

[0084] 输入信号生成电路 610 响应于第一时钟信号 CLK1 接收帧线标记信号 FLM;响应于帧线标记信号 FLM 接收第二时钟信号 CLK2,并且输出逐次输入信号 NEXT\_IN。在一实施例中,输入信号生成电路 610 可以包括:第一晶体管 M1、第二晶体管 M2 以及第一电容器 C1。第一晶体管 M1 包括:漏电极;接收帧线标记信号 FLM 的源电极;以及响应于第一时钟信号 CLK1 将帧线标记信号 FLM 向所述漏电极施加的栅电极。第二晶体管 M2 包括:接收第二时钟信号 CLK2 的源电极;与第一晶体管 M1 的漏电极连接的栅电极;以及输出逐次输入信号 NEXT\_IN 的漏电极。第一电容器 C1 连接在第一晶体管 M1 的漏电极与第二晶体管 M2 的漏电极之间。

[0085] 逆变器电路 630 响应于第一时钟信号 CLK1 接收帧线标记信号 FLM,并且反转帧线标记信号 FLM 来生成逆变器输出信号 IVT\_OUT。在一实施例中,逆变器电路 630 可以包括:第三晶体管 M3、第四晶体管 M4、第五晶体管 M5、第六晶体管 M6、第七晶体管 M7、第八晶体管 M8;以及第二电容器 C2、第三电容器 C3。

[0086] 在逆变器电路 630 中,第三晶体管 M3 响应于第一时钟信号 CLK1 将帧线标记信号 FLM 提供给第一节点 N1。第四晶体管 M4 包括:与第一节点 N1 连接的栅电极;与第一电压供应端 VGH 连接的源电极;以及与第二节点 N2 连接的漏电极。第二电容器 C2 连接在第一节点 N1 和第一电压供应端 VGH 之间。第五晶体管 M5 包括:与输入信号生成电路 610 的第二晶体管 M2 的漏电极连接的漏电极;与第一电压供应端 VGH 连接的源电极;以及与第二节点 N2 连接的栅电极。第六晶体管 M6 包括:与第二节点 N2 连接的源电极;与第三节点 N3 连接的漏电极;以及接收第二时钟信号 CLK2 的栅电极。第七晶体管 M7 包括:与第三节点 N3 连接的源电极;与第二电压供应端 VGL 连接的漏电极;以及接收第一时钟信号 CLK1 的栅电极。第八晶体管 M8 包括:与第三节点 N3 连接的栅电极;接收第二时钟信号 CLK2 的源电极;以及与第四节点 N4 连接的漏电极。第三电容器 C3 连接在第三节点 N3 与第四节点 N4 之间。逆变器电路 630 响应于第一时钟信号 CLK1 和第二时钟信号 CLK2 反转帧线标记信号 FLM,从而可以生成逆变器输出信号 IVT\_OUT。

[0087] 输出切换电路 650 响应于逆变器输出信号 IVT\_OUT,将高电平的第一电压 VGH 或者低电平的第二电压 VGL 作为发光信号 OUT 而予以输出。由此,发光驱动单元 600 的输出 OUT 可以具有脉冲形态。在一实施例中,输出切换电路 650 可以包括:输出端 Nout、第九晶体管 M9 以及第十晶体管 M10。输出端 Nout 输出发光信号 OUT。第九晶体管 M9 包括:与第一节点 N1 连接的栅电极;与第一电压供应端 VGH 连接的源电极;以及与输出端 Nout 连接的漏电极。第十晶体管 M10 包括:与第二节点 N2 连接的栅电极;与输出端 Nout 连接的源电极;以及与第二电压供应端 VGL 连接的漏电极。

[0088] 在发光驱动单元 600 中,发光信号 OUT 可以具有将帧线标记信号 FLM 予以反转的形态。在一实施例中,当帧线标记信号 FLM 具有从高电平降至低电平的一次低脉冲(low-pulse)的情况下,发光信号 OUT 具有从低电平升至高电平的一次高脉冲(high-pulse)。根据发光驱动单元 600,包括于像素电路的发光晶体管也由 P 沟道金属氧化

物半导体晶体管构成。因此在发光信号 OUT 为高电平的区间,所述发光晶体管被断开;在发光信号 OUT 为低电平的区间,所述发光晶体管被导通,从而与其连接的有机发光二极管会发光。

[0089] 在一实施例中,第一电压 OUT 可以具有断开 P 沟道金属氧化物半导体晶体管的足够高的电压电平,第二电压 OUT 可以具有导通 P 沟道金属氧化物半导体晶体管的足够低的电压电平。

[0090] 图 7 是表示图 6 的发光驱动单元所包括的逆变器电路的电路图。

[0091] 图 7 的逆变器电路 700 实质上与图 6 的逆变器电路 630 相对应。具体而言,逆变器电路 700 的输入信号 IN、输出信号 OUT、节点 A 分别与逆变器电路 630 的帧线标记信号 FLM、逆变器输出信号 IVT\_OUT、第三节点 N3 相对应。如图 7 所示,逆变器电路 700 由 P 沟道金属氧化物半导体晶体管构成。第一晶体管 T1 响应于低电平的输入信号 IN,将高电平的第一电压 VGH 作为输出信号 OUT 予以输出。当输入信号 IN 为高电平的情况下,第一晶体管 T1 被断开,并且根据第一时钟信号 CLK1 和第二时钟信号 CLK2,将低电平的第二电压 VGL 作为输出信号 OUT 予以输出。

[0092] 图 8 是表示根据本发明再一实施例的发光驱动单元的电路图。

[0093] 如图 8 所示,除了输出控制电路 810 之外,图 8 的发光驱动单元 800 具有实质上与图 6 的发光驱动单元 600 相同的结构。

[0094] 输出控制电路 810 连接在逆变器电路内部,并且被输出控制信号 ESR 控制。输出控制电路 810 可以包括:第一输出控制晶体管 Q1 和第二输出控制晶体管 Q2。

[0095] 在一实施例中,当低电平的输出控制信号 ESR 施加至输出控制电路 810 的情况下,将第一电压 VGH 作为发光信号 OUT,以 DC 电平的方式输出。进一步具体地,若施加低电平的输出控制信号 ESR,则第一输出控制晶体管 Q1 和第二输出控制晶体管 Q2 被导通。此时,低电平的第二电压 VGL 施加至第九晶体管 M9 的栅电极以导通第九晶体管 M9,高电平的第一电压 VGH 施加至第十晶体管 M10 的栅电极以断开第十晶体管 M10。结果,通过第九晶体管 M9,可以将第一电压 VGH 作为发光信号 OUT 予以输出。另一方面,当高电平的输出控制信号 ESR 施加至输出控制电路 810 的情况下,第一输出控制晶体管 Q1 和第二输出控制晶体管 Q2 被断开,从而成为实质上与图 6 的发光驱动单元 600 相同的电路。

[0096] 图 9 是表示根据本发明一实施例的有机发光显示装置的框图。

[0097] 如图 9 所示,有机发光显示装置 900 包括:显示面板 910、扫描驱动部 920、数据驱动部 930、发光驱动部 200 以及时序控制器 940。

[0098] 显示面板 910 包括多个像素电路,并且接收第一电源电压 ELVDD 和第二电源电压 ELVSS。所述像素电路分别包括有机发光二极管。扫描驱动部 920 通过第一扫描线 S1 至第 n 扫描线 Sn(其中,n 为大于或等于 3 的整数),给所述像素电路依次提供第一扫描信号至第 n 扫描信号。数据驱动部 930 根据所述第一扫描信号至第 n 扫描信号,通过多个数据线 D1 至 Dm 向所述像素电路提供数据电压。发光驱动部 200 通过第一发光(emission)控制线 EM1 至第 n 发光控制线 EMn,给所述像素电路依次提供第一发光信号至第 n 发光信号。时序控制器 940 给扫描驱动部 920、数据驱动部 930 以及发光驱动部 200 提供第一时钟信号 CLK1 和第二时钟信号 CLK2。

[0099] 在一实施例中,发光驱动部 200 可以包括:分别生成所述第一发光信号至第 n 发光

信号的第一发光驱动单元至第 n 发光驱动单元。根据本发明的实施例,所述第一发光驱动单元至第 n 发光驱动单元在内部包括逆变器电路,从而可以仅由 N 沟道金属氧化物半导体晶体管或者 P 沟道金属氧化物半导体晶体管构成。根据第一时钟信号 CLK1 和第二时钟信号 CLK2 分别控制所述第一发光驱动单元至第 n 发光驱动单元,并且将 FLM 信号或者第一逐次输入信号至第 (n-1) 逐次输入信号作为输入信号予以接收,并且可以由相同的单一晶体管构成。

[0100] 根据实施例,当发光驱动部 200 由 N 沟道金属氧化物半导体晶体管构成时,所述第一发光信号至第 n 发光信号为低电平的区间可以与在所述像素电路中执行数据编程 (programming) 的区间相对应,所述第一发光信号至第 n 发光信号为高电平的区间可以与分别包括在所述像素电路中的有机发光二极管的发光区间相对应。

[0101] 另外,发光驱动部 200 由 N 沟道金属氧化物半导体晶体管构成时,通过控制所述第一发光信号至第 n 发光信号的待机比 (off duty ratio),可以控制显示面板 910 显示黑色图像 (black image) 的区间的长度。由此,采用由单一晶体管构成的发光驱动部 200,可以实施脉冲驱动。

[0102] 在一实施例中,随着发光驱动部 200 依次向所述像素电路提供所述第一发光信号至第 n 发光信号,分别包括在所述像素电路中的 OLED 可以依次发光。

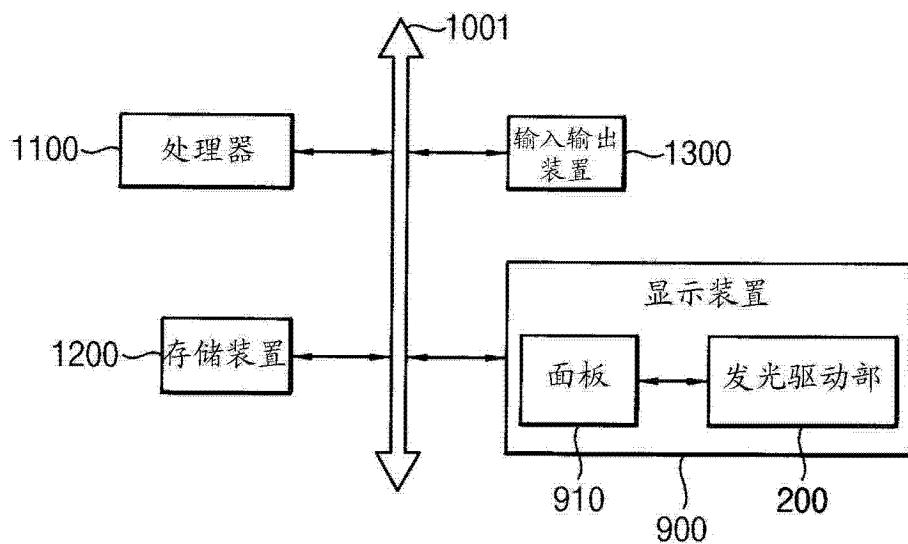

[0103] 图 10 是表示包括图 9 的有机发光显示装置的电子设备的框图。

[0104] 如图 10 所示,电子设备 1000 可以包括:处理器 1100、存储装置 1200、输入输出装置 1300 以及显示装置 900。

[0105] 处理器 1100 可以实现多种计算功能,如执行特定计算或者任务 (task) 的特定软件等。例如,处理器 1100 可以为微处理器或者中央处理器 (Central Processing Unit, 简称为 CPU)。处理器 1100 可以通过总线 1001 与存储装置 1200 连接。处理器 1100 可以通过地址总线 (address bus)、控制总线 (control bus) 以及数据总线 (data bus) 等连接于存储装置 1200 和显示装置 900 以进行通信。在示例性的实施例中,处理器 1100 还可以连接于如外设元件互连 (Peripheral Component Interconnect, 简称为 PCI) 总线等扩展总线。

[0106] 存储装置 1200 例如可以包括:如动态随机存取存储器 (Dynamic Random Access Memory, 简称为 DRAM)、静态随机存取存储器 (Static Random Access Memory, 简称为 SRAM) 等挥发性存储装置;以及如可擦除可编程只读存储器 (Erasable Programmable Read-Only Memory, 简称为 EPROM)、电可擦可编程只读存储器 (Electrically Erasable Programmable Read-Only Memory, 简称为 EEPROM) 以及闪存存储器 (flash memory device) 等非挥发性存储装置。存储装置 1200 可以存储通过处理器 1100 运行的软件。

[0107] 输入输出装置 1300 连接在总线 1001,可以包括如键盘或者鼠标等输入单元以及如打印机等输出单元。处理器 1100 可以控制输入输出装置 1300 的运行。

[0108] 显示装置 900 通过总线 1001 与处理器 1100 连接。显示装置 900 可以包括:显示面板 910 以及发光驱动部 200。如上所述,发光驱动部 200 在其内部包括逆变器电路,从而可以以单一晶体管构成;并且控制输入信号的脉冲宽度,从而可以自由调整发光信号的脉冲宽度。

[0109] 电子设备 1000 可以为任意的电子装置,其可以包括:通过显示装置 900 向用户呈现图像的手机、智能手机、智能平板电脑 (smart pad)、电视、掌上电脑 (Personal Digital

Assistant, 简称为 PDA)、MP3 播放器、笔记本电脑、台式电脑(desktop computer)、数码相机等。

[0110] 工业应用性

[0111] 本发明可以广泛地应用于包括显示装置的多种领域中。例如,可以有效地应用于包括显示装置的显示器、笔记本电脑、PDA、智能手机、智能平板电脑、大中型显示面板等中。

[0112] 以上参考优选的实施例说明了本发明,但是所属技术领域的技术人员能够明白,在不脱离权利要求书中记载的本发明思想和领域的范围内能够对本发明进行多种修改和变更。

图 1

图 2b

图 2a

300

图 3a

图 3b

图 4

图 5

图 6

图 7

图 8

900

图 9

1000

图 10

|                |                              |                      |            |

|----------------|------------------------------|----------------------|------------|

| 专利名称(译)        | 发光驱动单元、发光驱动部及有机发光显示装置        |                      |            |

| 公开(公告)号        | <a href="#">CN103295522A</a> | 公开(公告)日              | 2013-09-11 |

| 申请号            | CN201310038875.6             | 申请日                  | 2013-01-31 |

| [标]申请(专利权)人(译) | 三星显示有限公司                     |                      |            |

| 申请(专利权)人(译)    | 三星显示有限公司                     |                      |            |

| 当前申请(专利权)人(译)  | 三星显示有限公司                     |                      |            |

| [标]发明人         | 郑镇泰                          |                      |            |

| 发明人            | 郑镇泰                          |                      |            |

| IPC分类号         | G09G3/32                     |                      |            |

| 代理人(译)         | 刘铮                           |                      |            |

| 优先权            | 1020120021210 2012-02-29 KR  |                      |            |

| 其他公开文献         | <a href="#">CN103295522B</a> |                      |            |

| 外部链接           | <a href="#">Espacenet</a>    | <a href="#">Sipo</a> |            |

### 摘要(译)

发光驱动单元包括：输入信号生成电路、逆变器电路以及输出切换电路。输入信号生成电路响应于第一时钟信号接收帧线标记 ( FrameLine Mark , 简称为FLM ) 信号 , 响应于所述FLM信号接收第二时钟信号并且输出逐次输入信号。逆变器电路响应于第一时钟信号接收FLM信号 , 反转所述FLM信号以生成逆变器输出信号。输出切换电路响应于逆变器输出信号 , 将高电平的第一电压或者低电平的第二电压作为发光信号予以输出。输入信号生成电路、逆变器电路以及输出切换电路可以由相同的单一晶体管构成。