## (12)实用新型专利

(10) 授权公告号 CN 210379052 U

(45)授权公告日 2020.04.21

(21)申请号 201921977920.3

(22)申请日 2019.11.15

(73)专利权人 京东方科技集团股份有限公司

地址 100015 北京市朝阳区酒仙桥路10号

专利权人 成都京东方光电科技有限公司

(72)发明人 何帆 董向丹 肖云升 都蒙蒙

张波

(74)专利代理机构 北京市柳沈律师事务所

11105

代理人 焦玉恒

(51) Int. GI

H011 27/32(2006 01)

H011 51/52(2006-01)

(ESM)同样的发明创造已同日申请发明专利

权利要求书4页 说明书20页 附图9页

### (54)实用新型名称

## 阵列基板和显示装置

## (57) 摘要

一种阵列基板和显示装置。该阵列基板包括衬底基板、像素驱动层、平坦层、有机发光器件、封装层、第一挡墙和多条第一通道线；第一挡墙位于周边区且包括沿第一方向延伸的第一挡墙部；多条第一通道线位于周边区，且位于封装层远离衬底基板的一侧；封装层包括有机封装层，平坦层包括沿第一方向延伸的第一边缘部，第一边缘部位于第一挡墙部和显示区之间，第一边缘部在衬底基板上的正投影被有机封装层在衬底基板上的正投影覆盖，且多条第一通道线中的至少一条第一通道线在衬底基板上的正投影位于第一边缘部远离显示区的一侧。该阵列基板可减小周边区的宽度，从而可实现采用该阵列基板的显示装置的窄边框设计。

1. 一种阵列基板，其特征在于，包括：

衬底基板，包括显示区和位于所述显示区周边的周边区；

像素驱动层，位于所述衬底基板上；

平坦层，位于所述像素驱动层远离所述衬底基板的一侧；

有机发光器件，位于所述平坦层远离所述像素驱动层的一侧；

封装层，位于所述有机发光器件远离所述衬底基板的一侧；

第一挡墙，位于所述周边区且包括沿第一方向延伸的第一挡墙部；以及

多条第一通道线，位于所述周边区，且位于所述封装层远离所述衬底基板的一侧，各所述多条第一通道线沿所述第一方向延伸，所述多条第一通道线沿第二方向排列，所述第二方向大致垂直于所述第一方向；

所述封装层包括有机封装层，所述平坦层包括沿所述第一方向延伸的第一边缘部，所述第一边缘部位于所述第一挡墙部和所述显示区之间，所述第一边缘部在所述衬底基板上的正投影被所述有机封装层在所述衬底基板上的正投影覆盖，且所述多条第一通道线中的至少一条第一通道线在所述衬底基板上的正投影位于所述第一边缘部远离所述显示区的一侧。

2. 根据权利要求1所述的阵列基板，其特征在于，所述有机封装层包括沿所述第一方向延伸的第二边缘部，所述第二边缘部位于所述第一边缘部与所述第一挡墙部之间，所述多条第一通道线中的至少一条第一通道线在所述衬底基板上的正投影位于所述第二边缘部在所述衬底基板上的正投影之内。

3. 根据权利要求2所述的阵列基板，其特征在于，所述多条第一通道线包括位于所述第一边缘部远离所述衬底基板的一侧的多条第一平坦通道线和位于所述第二边缘部远离所述衬底基板的一侧的多条第一斜坡通道线，

相邻两条所述第一斜坡通道线之间的间距大于相邻两条所述第一平坦通道线之间的间距。

4. 根据权利要求3所述的阵列基板，其特征在于，相邻两条所述第一斜坡通道线之间的间距为相邻两条所述第一平坦通道线之间的间距的1.05-2倍。

5. 根据权利要求3所述的阵列基板，其特征在于，在所述多条第一斜坡通道线中，相邻两条所述第一斜坡通道线之间的间距为所述第一斜坡通道线的宽度的1.05-2倍。

6. 根据权利要求1-5中任一项所述的阵列基板，其特征在于，所述多条第一通道线中最远离所述显示区的一条第一通道线为地线的一部分，并且所述多条第一通道线中最远离所述显示区的一条第一通道线在所述衬底基板上的正投影位于所述有机封装层在所述衬底基板上的正投影与所述第一挡墙部在所述衬底基板上的正投影之间。

7. 根据权利要求1-5中任一项所述的阵列基板，其特征在于，还包括：

多个触控驱动电极，位于所述显示区且位于所述封装层远离所述衬底基板的一侧；

多个触控感应电极，位于所述显示区且位于所述封装层远离所述衬底基板的一侧；

触控驱动信号线，与各所述触控驱动电极相连并延伸至所述周边区；以及

触控感应信号线，与各所述触控感应电极相连并延伸至所述周边区，

其中，所述多条第一通道线的至少部分第一通道线为所述触控驱动信号线或所述触控感应信号线的一部分。

8. 根据权利要求2-5中任一项所述的阵列基板,其特征在于,所述第一挡墙包括沿所述第二方向延伸的第二挡墙部,所述阵列基板还包括:

多条第二通道线,沿所述第二方向延伸,

其中,所述平坦层包括沿所述第二方向延伸的第三边缘部,所述第三边缘部位于所述第二挡墙部和所述显示区之间,所述第三边缘部在所述衬底基板上的正投影被所述有机封装层在所述衬底基板上的正投影覆盖,且所述多条第二通道线中的至少一条第二通道线在所述衬底基板上的正投影位于所述第三边缘部远离所述显示区的一侧。

9. 根据权利要求8所述的阵列基板,其特征在于,还包括:

多个触控驱动电极,位于所述显示区且与位于所述封装层远离所述衬底基板的一侧;

多个触控感应电极,位于所述显示区且位于所述封装层远离所述衬底基板的一侧;

触控驱动信号线,与各所述触控驱动电极相连并延伸至所述周边区;以及

触控感应信号线,与各所述触控感应电极相连并延伸至所述周边区,

其中,各所述多个触控感应电极沿所述第一方向延伸,所述多个触控感应电极沿所述第二方向排列,所述多条第一通道线的至少部分第一通道线为所述触控感应信号线的一部分,

各所述多个触控驱动电极沿所述第二方向延伸,所述多个触控驱动电极沿所述第一方向排列,所述多条第二通道线的至少部分第二通道线为所述触控驱动信号线的一部分。

10. 根据权利要求8所述的阵列基板,其特征在于,所述有机封装层包括沿所述第二方向延伸的第四边缘部,所述第四边缘部位于所述第三边缘部与所述第二挡墙部之间,所述多条第二通道线中的至少一条第二通道线在所述衬底基板上的正投影位于所述第四边缘部在所述衬底基板上的正投影之内。

11. 根据权利要求10所述的阵列基板,其特征在于,所述多条第二通道线包括位于所述第三边缘部远离所述衬底基板的一侧的多条第二平坦通道线和位于所述第四边缘部远离所述衬底基板的一侧的多条第二斜坡通道线,

相邻两条所述第二斜坡通道线之间的间距大于相邻两条所述第二平坦通道线之间的间距。

12. 根据权利要求11所述的阵列基板,其特征在于,相邻两条所述第二斜坡通道线之间的间距为相邻两条所述第二平坦通道线之间的间距的1.05-2倍。

13. 根据权利要求11所述的阵列基板,其特征在于,在所述多条第二斜坡通道线中,相邻两条所述第二斜坡通道线之间的间距大于等于所述第一斜坡通道线的宽度的1.05-2倍。

14. 根据权利要求1-5中任一项所述的阵列基板,其特征在于,还包括:

第二挡墙,设置在所述衬底基板上且位于所述周边区,

其中,所述第二挡墙位于所述第一挡墙与所述显示区之间,所述第二挡墙包括沿所述第一方向延伸的第三挡墙部,

所述多条第一通道线中的至少一条第一通道线在所述衬底基板上的正投影位于所述第三挡墙部在所述衬底基板上的正投影之内。

15. 根据权利要求1-5中任一项所述的阵列基板,其特征在于,还包括:

第二挡墙,设置在所述衬底基板上且位于所述周边区,

其中,所述第二挡墙位于所述第一挡墙与所述显示区之间,所述第二挡墙包括沿所述

第一方向延伸的第三挡墙部，

所述多条第一通道线在所述衬底基板上的正投影位于所述第三挡墙部在所述衬底基板上的正投影靠近所述显示区的一侧。

16. 根据权利要求1-5中任一项所述的阵列基板，其特征在于，所述有机发光器件包括沿远离所述衬底基板的方向上依次层叠的阳极、发光层和阴极。

17. 根据权利要求1-5中任一项所述的阵列基板，其特征在于，所述封装层还包括：

第一无机封装层，位于所述有机发光器件远离所述衬底基板的一侧；以及

第二无机封装层，位于所述有机封装层远离所述第一无机封装层的一侧，

其中，所述第一无机封装层和所述第二无机封装层覆盖所述第一挡墙，所述有机封装层夹设在所述第一无机封装层和所述第二无机封装层之间，所述多条第一通道线位于所述第二无机封装层远离所述衬底基板的一侧。

18. 一种显示装置，其特征在于，包括根据权利要求1-17中任一项所述的阵列基板。

19. 一种阵列基板，其特征在于，包括：

衬底基板，包括显示区和位于所述显示区周边的周边区；

像素驱动层，位于所述衬底基板上；

有机发光器件，位于所述像素驱动层上；

封装层，位于所述有机发光器件上，所述封装层包括依次设置的第一无机封装层和有机封装层；

多条第一通道线，位于所述周边区，且位于所述封装层远离所述衬底基板的一侧，各所述多条第一通道线沿第一方向延伸，所述多条第一通道线沿第二方向排列，所述第二方向大致垂直于所述第一方向；

在所述周边区，所述第一无机封装层，在从所述显示区到所述周边区的方向上，包括连续设置的第一无机封装部、无机封装连接部和第二无机封装部，所述无机封装连接部被配置为连接所述第一无机封装部和第二无机封装部；

在所述周边区，在从所述显示区到所述周边区的方向上，所述有机封装层包括连续设置的第一有机封装部和第二有机封装部，所述第二有机封装部远离所述显示区的边缘为所述有机封装层的边缘，所述第一有机封装部在所述衬底基板上的正投影与所述第一无机封装部和无机封装连接部在衬底基板上的正投影重叠，所述第二有机封装部在所述衬底基板上的正投影与所述第二无机封装部在所述衬底基板上的正投影重叠，

在垂直于所述衬底基板的方向上，所述第一无机封装部与所述衬底基板之间的距离d1大于所述第二无机封装部与所述衬底基板之间的距离d2，所述多条第一通道线中的至少一条第一通道线在所述衬底基板上的正投影落入第二无机封装部在所述衬底基板上的正投影之内。

20. 根据权利要求19所述的阵列基板，其特征在于，还包括：

第一挡墙，位于所述周边区且包括沿所述第一方向延伸的第一挡墙部；以及

平坦层，位于所述像素驱动层远离所述衬底基板的一侧，

其中，所述平坦层包括沿所述第一方向延伸的第一边缘部，所述第一边缘部位于所述第一挡墙部和所述显示区之间，所述第一无机封装部和无机封装连接部在所述衬底基板上的正投影与所述第一边缘部在所述衬底基板上正投影重叠，

所述第一无机封装部与所述衬底基板之间的距离d1和所述第二无机封装部与所述衬底基板之间的距离d2之差大于等于所述平坦层在垂直于衬底基板的方向上与所述无机封装连接部相互交叠的部分的最大的厚度。

21. 根据权利要求20所述的阵列基板，其特征在于，所述平坦层包括：

第一子平坦层，位于所述像素驱动层远离所述衬底基板的一侧；以及

第二子平坦层，位于所述第一子平坦层远离所述像素驱动层的一侧，

其中，所述第一无机封装部与所述衬底基板之间的距离d1和所述第二无机封装部与所述衬底基板之间的距离d2之差大于等于所述第一子平坦层在垂直于衬底基板的方向上与所述无机封装连接部相互交叠的部分的最大厚度与所述第二子平坦层在垂直于所述衬底基板的方向上与所述无机封装连接部相互交叠的部分的最大厚度之和。

22. 根据权利要求19-21中任一项所述的阵列基板，其特征在于，所述多条第一通道线包括位于所述第一有机封装部远离所述衬底基板的一侧的多条第一平坦通道线和位于所述第二有机封装部远离所述衬底基板的一侧的多条第一斜坡通道线，

相邻两条所述第一斜坡通道线之间的间距大于相邻两条所述第一平坦通道线之间的间距。

23. 根据权利要求22所述的阵列基板，其特征在于，相邻两条所述第一斜坡通道线之间的间距为相邻两条所述第一平坦通道线之间的间距的1.05-2倍。

24. 根据权利要求22所述的阵列基板，其特征在于，在所述多条第一斜坡通道线中，相邻两条所述第一斜坡通道线之间的间距为所述第一斜坡通道线的宽度的1.05-2倍。

25. 一种显示装置，其特征在于，包括根据权利要求19-24中任一项所述的阵列基板。

## 阵列基板和显示装置

### 技术领域

[0001] 本公开的实施例涉及一种阵列基板和显示装置。

### 背景技术

[0002] 随着触控技术的不断发展，手机、平板电脑等智能电子产品均集成有具有触控功能的触控基板。另一方面，随着手机、平板电脑等智能电子产品的高速发展，手机、平板电脑等智能电子产品逐渐采用窄边框，甚至无边框的设计，即“全面屏”设计，从而为用户提供更优秀的使用体验。

### 实用新型内容

[0003] 本公开实施例提供一种阵列基板和显示装置。该阵列基板通过将至少部分通道线设置在封装层的斜坡上，可进一步减小周边区的宽度，从而可实现采用该阵列基板的显示装置的窄边框甚至无边框设计。

[0004] 本公开至少一个实施例提供一种阵列基板，其包括：衬底基板，包括显示区和位于所述显示区周边的周边区；像素驱动层，位于所述衬底基板上；平坦层，位于所述像素驱动层远离所述衬底基板的一侧；有机发光器件，位于所述平坦层远离所述像素驱动层的一侧；封装层，位于所述有机发光器件远离所述衬底基板的一侧；第一挡墙，位于所述周边区且包括沿第一方向延伸的第一挡墙部；以及多条第一通道线，位于所述周边区，且位于所述封装层远离所述衬底基板的一侧，各所述多条第一通道线沿所述第一方向延伸，所述多条第一通道线沿第二方向排列，所述第二方向大致垂直于所述第一方向；所述封装层包括有机封装层，所述平坦层包括沿所述第一方向延伸的第一边缘部，所述第一边缘部位于所述第一挡墙部和所述显示区之间，所述第一边缘部在所述衬底基板上的正投影被所述有机封装层在所述衬底基板上的正投影覆盖，且所述多条第一通道线中的至少一条第一通道线在所述衬底基板上的正投影位于所述第一边缘部远离所述显示区的一侧。

[0005] 例如，在本公开一实施例提供的一种阵列基板中，所述有机封装层包括沿所述第一方向延伸的第二边缘部，所述第二边缘部位于所述第一边缘部与所述第一挡墙部之间，所述多条第一通道线中的至少一条第一通道线在所述衬底基板上的正投影位于所述第二边缘部在所述衬底基板上的正投影之内。

[0006] 例如，在本公开一实施例提供的一种阵列基板中，所述多条第一通道线包括位于所述第一边缘部远离所述衬底基板的一侧的多条第一平坦通道线和位于所述第二边缘部远离所述衬底基板的一侧的多条第一斜坡通道线，相邻两条所述第一斜坡通道线之间的间距大于相邻两条所述第一平坦通道线之间的间距。

[0007] 例如，在本公开一实施例提供的一种阵列基板中，相邻两条所述第一斜坡通道线之间的间距为相邻两条所述第一平坦通道线之间的间距的1.05-2倍。

[0008] 例如，在本公开一实施例提供的一种阵列基板中，在所述多条第一斜坡通道线中，相邻两条所述第一斜坡通道线之间的间距为所述第一斜坡通道线的宽度的1.05-2倍。

[0009] 例如,在本公开一实施例提供的一种阵列基板中,所述多条第一通道线中最远离所述显示区的一条第一通道线为地线的一部分,并且所述多条第一通道线中最远离所述显示区的一条第一通道线在所述衬底基板上的正投影位于所述有机封装层在衬底基板上的正投影与所述第一挡墙部在衬底基板上的正投影之间。

[0010] 例如,本公开一实施例提供的一种阵列基板还包括:多个触控驱动电极,位于所述显示区且位于所述封装层远离所述衬底基板的一侧;多个触控感应电极,位于所述显示区且位于所述封装层远离所述衬底基板的一侧;触控驱动信号线,与各所述触控驱动电极相连并延伸至所述周边区;以及触控感应信号线,与各所述触控感应电极相连并延伸至所述周边区,所述多条第一通道线的至少部分第一通道线为所述触控驱动信号线或所述触控感应信号线的一部分。

[0011] 例如,在本公开一实施例提供的一种阵列基板中,所述第一挡墙包括沿所述第二方向延伸的第二挡墙部,所述阵列基板还包括:多条第二通道线,沿所述第二方向延伸,所述平坦层包括沿所述第二方向延伸的第三边缘部,所述第三边缘部位于所述第二挡墙部和所述显示区之间,所述第三边缘部在所述衬底基板上的正投影被所述有机封装层在所述衬底基板上的正投影覆盖,且所述多条第二通道线中的至少一条第二通道线在所述衬底基板上的正投影位于所述第三边缘部远离所述显示区的一侧。

[0012] 例如,本公开一实施例提供的一种阵列基板还包括多个触控驱动电极,位于所述显示区且与位于所述封装层远离所述衬底基板的一侧;多个触控感应电极,位于所述显示区且位于所述封装层远离所述衬底基板的一侧;触控驱动信号线,与各所述触控驱动电极相连并延伸至所述周边区;以及触控感应信号线,与各所述触控感应电极相连并延伸至所述周边区,各所述多个触控感应电极沿所述第一方向延伸,所述多个触控感应电极沿所述第二方向排列,所述多条第一通道线的至少部分第一通道线为所述触控感应信号线的一部分,各所述多个触控驱动电极沿所述第二方向延伸,所述多个触控驱动电极沿所述第一方向排列,所述多条第二通道线的至少部分第二通道线为所述触控驱动信号线的一部分。

[0013] 例如,在本公开一实施例提供的一种阵列基板中,所述有机封装层包括沿所述第二方向延伸的第四边缘部,所述第四边缘部位于所述第三边缘部与所述第二挡墙部之间,所述多条第二通道线中的至少一条第二通道线在所述衬底基板上的正投影位于所述第四边缘部在所述衬底基板上的正投影之内。

[0014] 例如,在本公开一实施例提供的一种阵列基板中,所述多条第二通道线包括位于所述第三边缘部远离所述衬底基板的一侧的多条第二平坦通道线和位于所述第四边缘部远离所述衬底基板的一侧的多条第二斜坡通道线,相邻两条所述第二斜坡通道线之间的间距大于相邻两条所述第二平坦通道线之间的间距。

[0015] 例如,在本公开一实施例提供的一种阵列基板中,相邻两条所述第二斜坡通道线之间的间距为相邻两条所述第二平坦通道线之间的间距的1.05-2倍。

[0016] 例如,在本公开一实施例提供的一种阵列基板中,在所述多条第二斜坡通道线中,相邻两条所述第二斜坡通道线之间的间距大于等于所述第一斜坡通道线的宽度的1.05-2倍。

[0017] 例如,本公开一实施例提供的一种阵列基板还包括:第二挡墙,设置在所述衬底基板上且位于所述周边区,所述第二挡墙位于所述第一挡墙与所述显示区之间,所述第二挡

墙包括沿所述第一方向延伸的第三挡墙部，所述多条第一通道线中的至少一条第一通道线在所述衬底基板上的正投影位于所述第三挡墙部在所述衬底基板上的正投影之内。

[0018] 例如，本公开一实施例提供的一种阵列基板还包括：第二挡墙，设置在所述衬底基板上且位于所述周边区，所述第二挡墙位于所述第一挡墙与所述显示区之间，所述第二挡墙包括沿所述第一方向延伸的第三挡墙部，所述多条第一通道线在所述衬底基板上的正投影位于所述第三挡墙部在所述衬底基板上的正投影靠近所述显示区的一侧。

[0019] 例如，在本公开一实施例提供的一种阵列基板中，所述有机发光器件包括沿远离所述衬底基板的方向上依次层叠的阳极、发光层和阴极。

[0020] 例如，在本公开一实施例提供的一种阵列基板中，所述封装层还包括：第一无机封装层，位于所述有机发光器件远离所述衬底基板的一侧；以及第二无机封装层，位于所述有机封装层远离所述第一无机封装层的一侧，所述第一无机封装层和所述第二无机封装层覆盖所述第一挡墙，所述有机封装层夹设在所述第一无机封装层和所述第二无机封装层之间，所述多条第一通道线位于所述第二无机封装层远离所述衬底基板的一侧。

[0021] 本公开至少一个实施例还提供一种阵列基板，其包括衬底基板，包括显示区和位于所述显示区周边的周边区；像素驱动层，位于所述衬底基板上；有机发光器件，位于所述像素驱动层上；封装层，位于所述有机发光器件上，所述封装层包括依次设置的第一无机封装层和有机封装层；多条第一通道线，位于所述周边区，且位于所述封装层远离所述衬底基板的一侧，各所述多条第一通道线沿第一方向延伸，所述多条第一通道线沿第二方向排列，所述第二方向大致垂直于所述第一方向；在所述周边区，所述第一无机封装层，在从所述显示区到所述周边区的方向上，包括连续设置的第一无机封装部、无机封装连接部和第二无机封装部，所述无机封装连接部被配置为连接所述第一无机封装部和第二无机封装部，在所述周边区，在从所述显示区到所述周边区的方向上，所述有机封装层包括连续设置的第一有机封装部和第二有机封装部，所述第二有机封装部远离所述显示区的边缘为所述有机封装层的边缘，所述第一有机封装部在所述衬底基板上的正投影与所述第一无机封装部和无机封装连接部在衬底基板上的正投影重叠，所述第二有机封装部在所述衬底基板上的正投影与所述第二无机封装部在所述衬底基板上的正投影重叠，在垂直于所述衬底基板的方向上，所述第一无机封装部与所述衬底基板之间的距离d1大于所述第二无机封装部与所述衬底基板之间的距离d2，所述多条第一通道线中的至少一条第一通道线在所述衬底基板上的正投影落入第二无机封装部在所述衬底基板上的正投影之内。

[0022] 例如，本公开一实施例提供的阵列基板还包括：第一挡墙，位于所述周边区且包括沿所述第一方向延伸的第一挡墙部；以及平坦层，位于所述像素驱动层远离所述衬底基板的一侧，所述平坦层包括沿所述第一方向延伸的第一边缘部，所述第一边缘部位于所述第一挡墙部和所述显示区之间，所述第一无机封装部在所述衬底基板上的正投影与所述第一边缘部在所述衬底基板上正投影重叠，所述第一无机封装部与所述衬底基板之间的距离d1和所述第二无机封装部与所述衬底基板之间的距离d2之差大于等于所述平坦层在垂直于所述衬底基板的方向上与所述无机封装连接部相互交叠的部分的最大的厚度。

[0023] 例如，在本公开一实施例提供的一种阵列基板中，所述平坦层包括：第一子平坦层，位于所述像素驱动层远离所述衬底基板的一侧；以及第二子平坦层，位于所述第一子平坦层远离所述像素驱动层的一侧，所述第一无机封装部与所述衬底基板之间的距离d1和所

述第二无机封装部与所述衬底基板之间的距离d2之差大于等于所述第一子平坦层在垂直于衬底基板的方向上与所述无机封装连接部相互交叠的部分的最大厚度与所述第二子平坦层在垂直于所述衬底基板的方向上与所述无机封装连接部相互交叠的部分的最大厚度之和。

[0024] 例如,在本公开一实施例提供的一种阵列基板中,所述多条第一通道线包括位于所述第一有机封装部远离所述衬底基板的一侧的多条第一平坦通道线和位于所述第二有机封装部远离所述衬底基板的一侧的多条第一斜坡通道线,相邻两条所述第一斜坡通道线之间的间距大于相邻两条所述第一平坦通道线之间的间距。

[0025] 例如,在本公开一实施例提供的一种阵列基板中,相邻两条所述第一斜坡通道线之间的间距为相邻两条所述第一平坦通道线之间的间距的1.05-2倍。

[0026] 例如,在本公开一实施例提供的一种阵列基板中,在所述多条第一斜坡通道线中,相邻两条所述第一斜坡通道线之间的间距为所述第一斜坡通道线的宽度的1.05-2倍。

[0027] 本公开至少一个实施例还提供一种显示装置,包括上述任一项所述的阵列基板。

## 附图说明

[0028] 为了更清楚地说明本公开实施例的技术方案,下面将对实施例的附图作简单地介绍,显而易见地,下面描述中的附图仅仅涉及本公开的一些实施例,而非对本公开的限制。

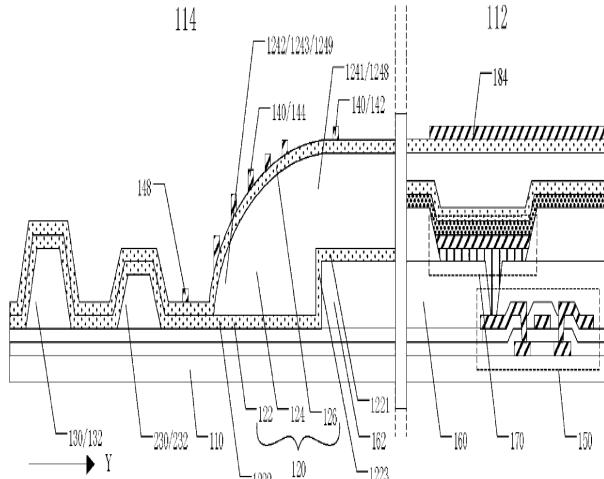

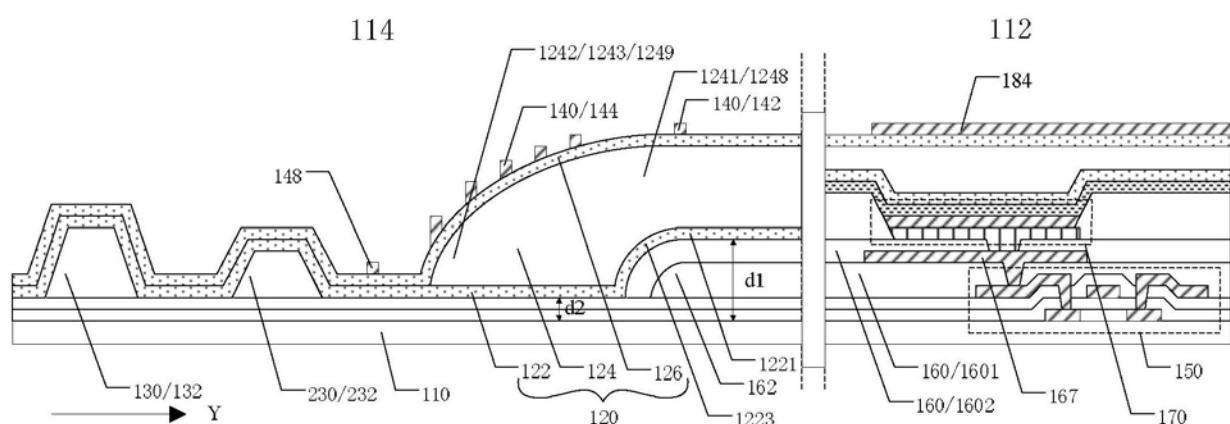

[0029] 图1为一种阵列基板的周边区的剖面示意图;

[0030] 图2为另一种阵列基板的周边区的剖面示意图;

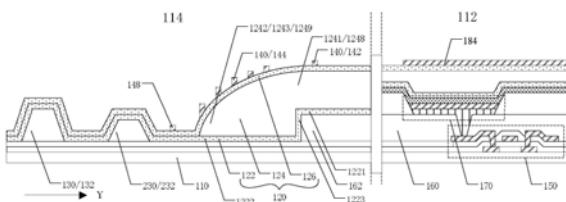

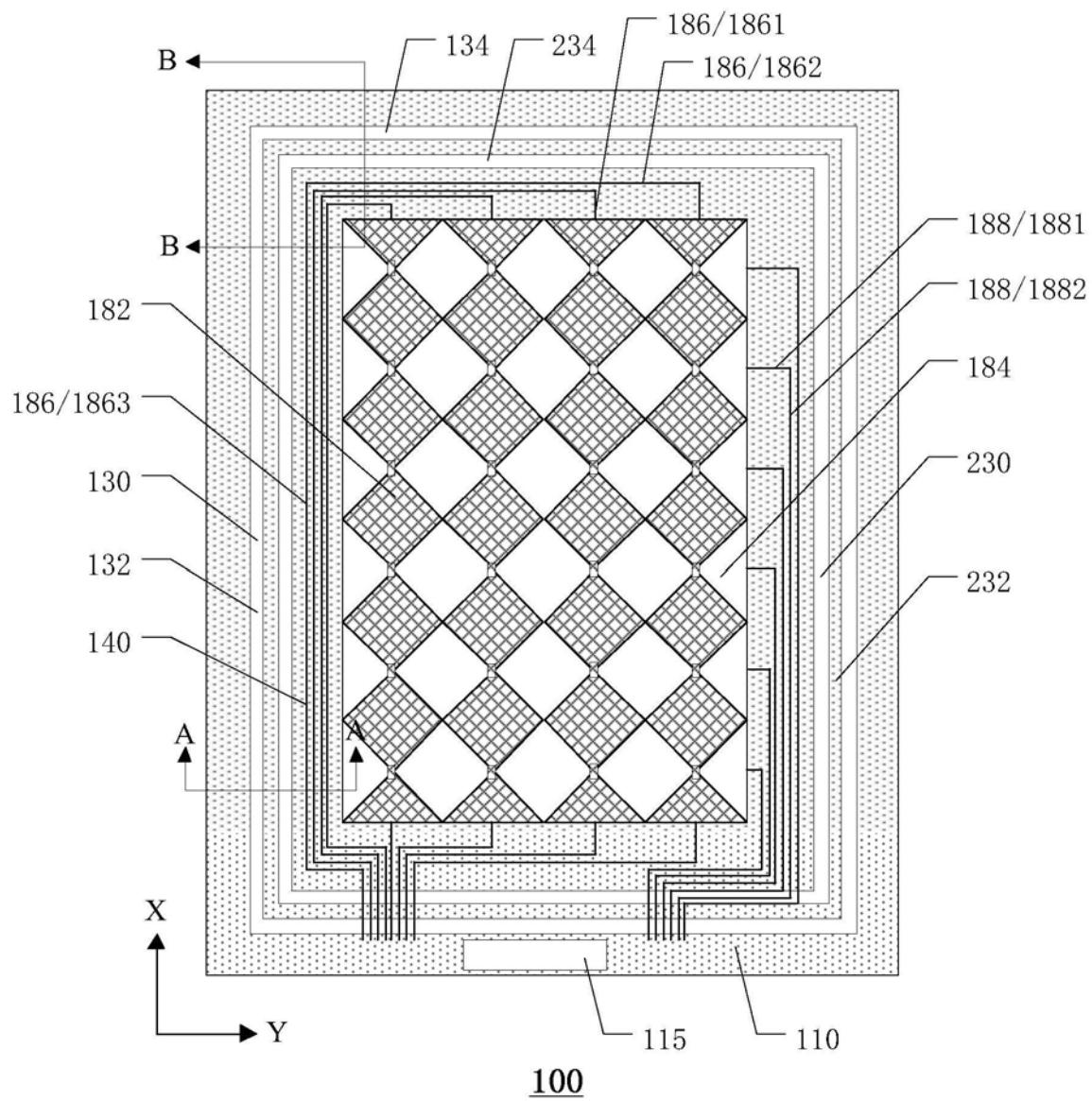

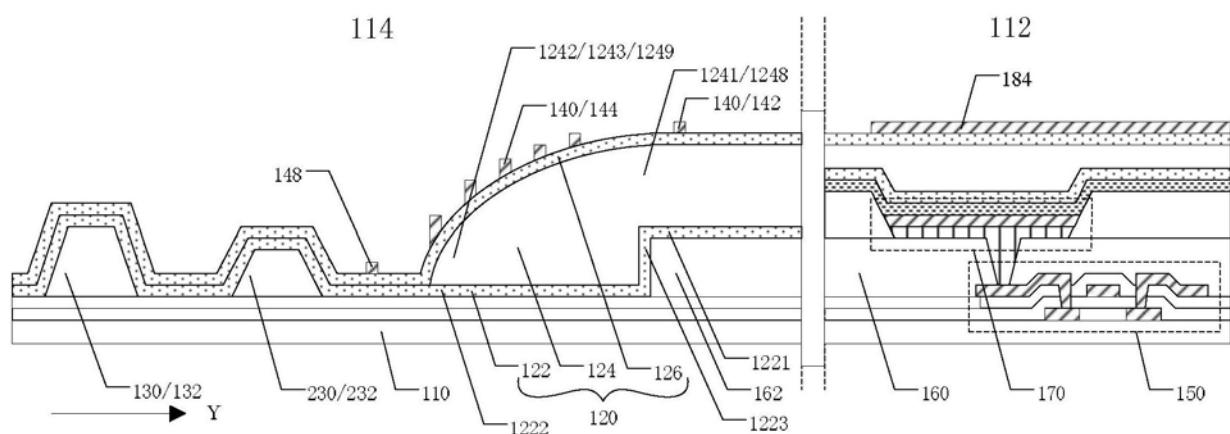

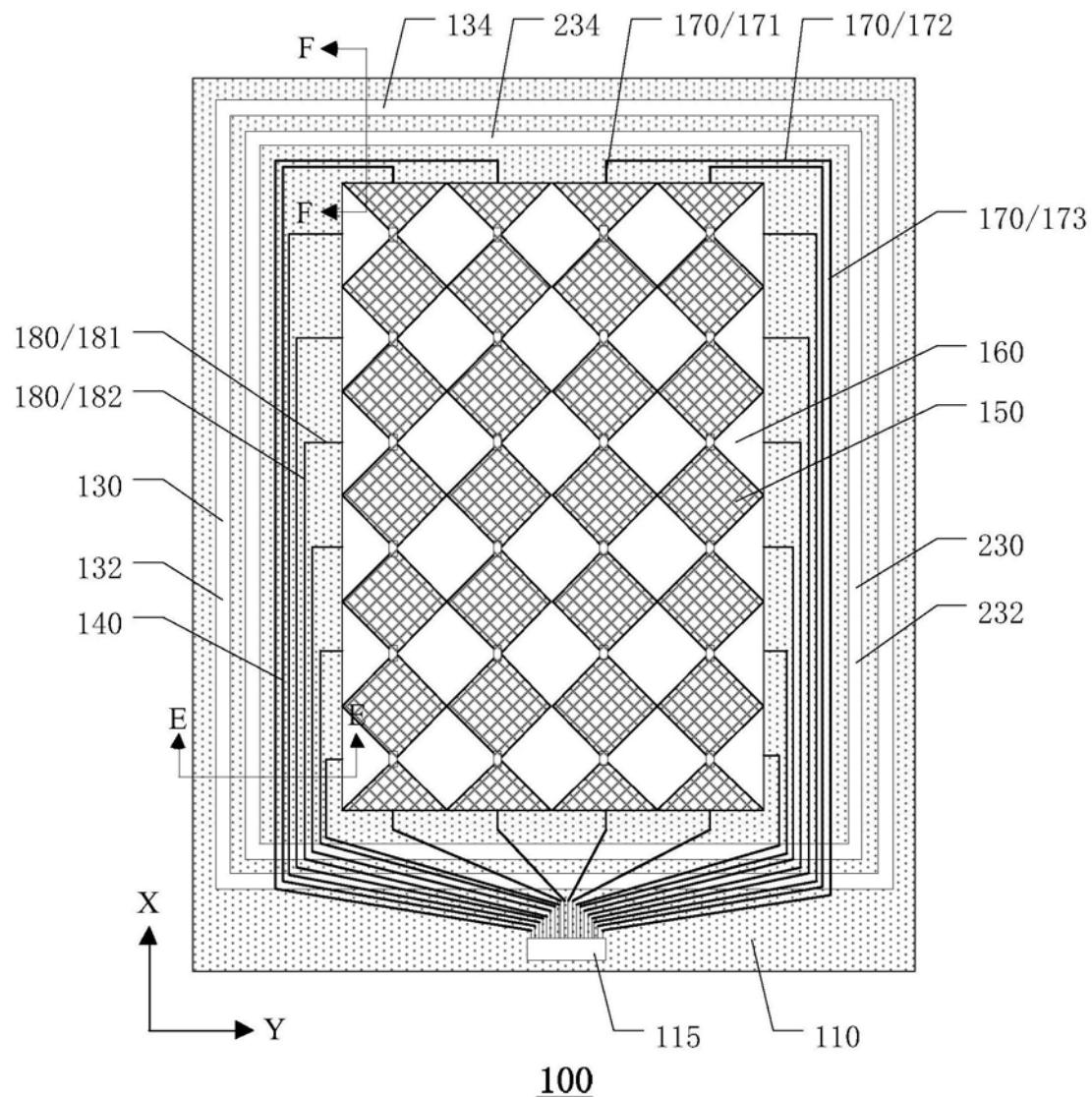

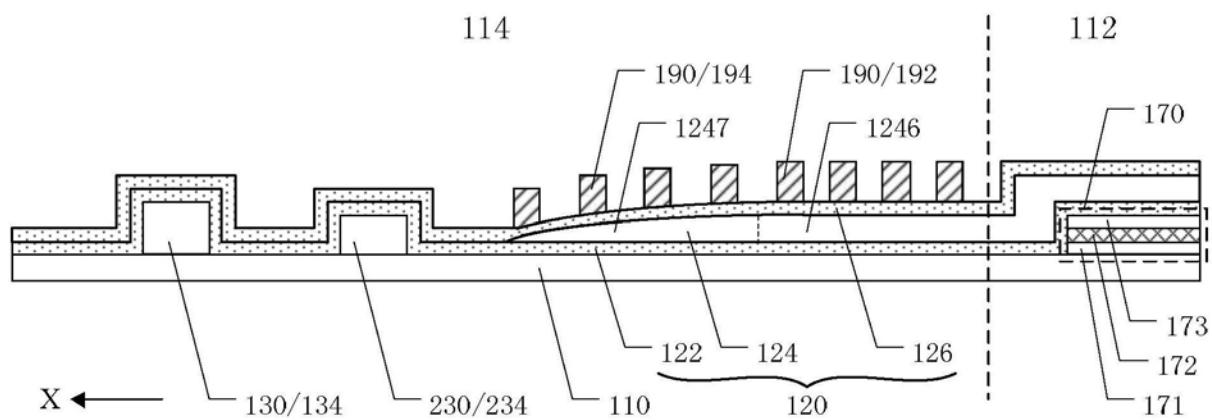

[0031] 图3为根据本公开一实施例提供的一种阵列基板的平面示意图;

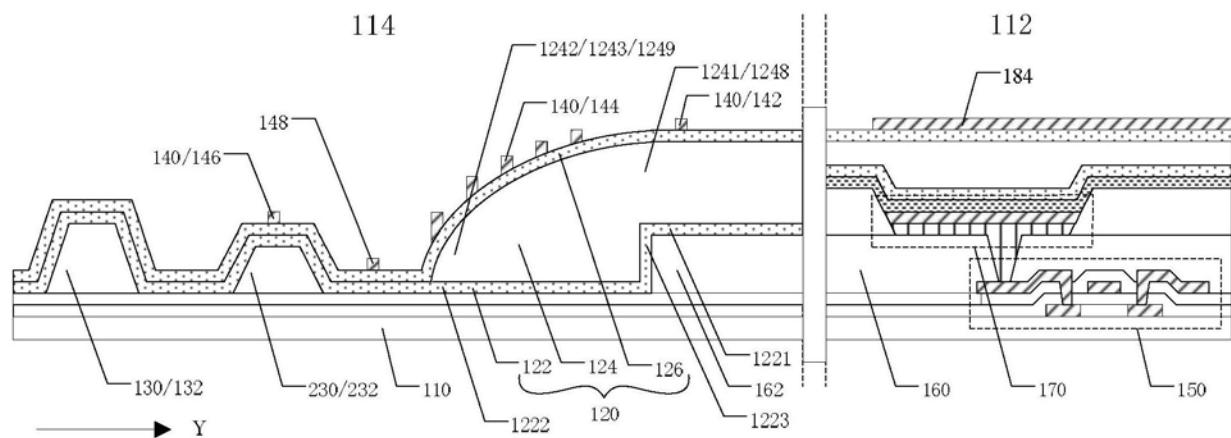

[0032] 图4为根据本公开一实施例提供的一种阵列基板沿图3中AA方向的剖面示意图;

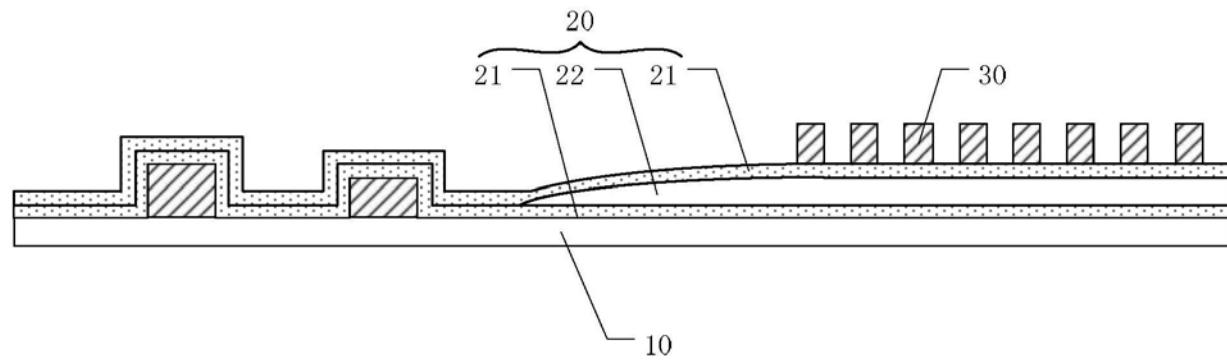

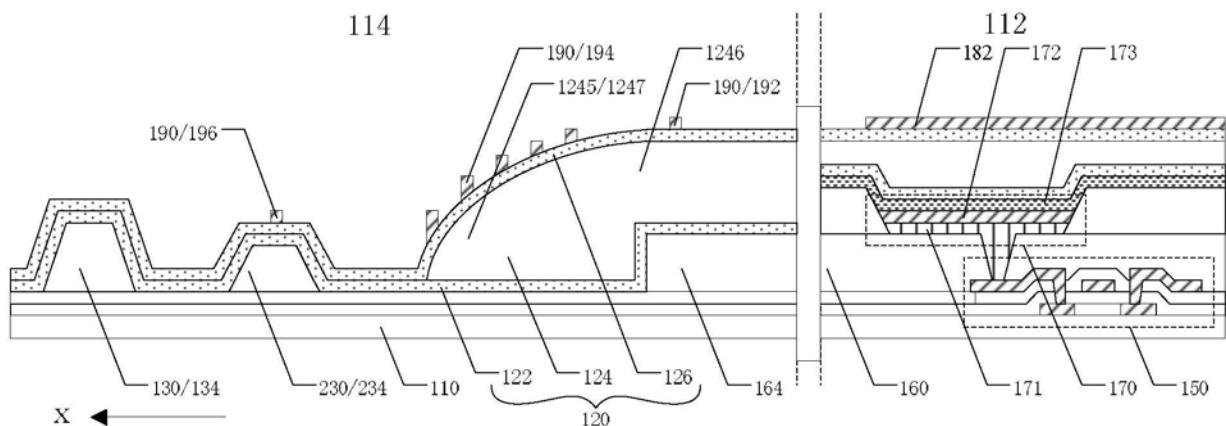

[0033] 图5为根据本公开一实施例提供的一种阵列基板沿图3中BB方向的剖面示意图;

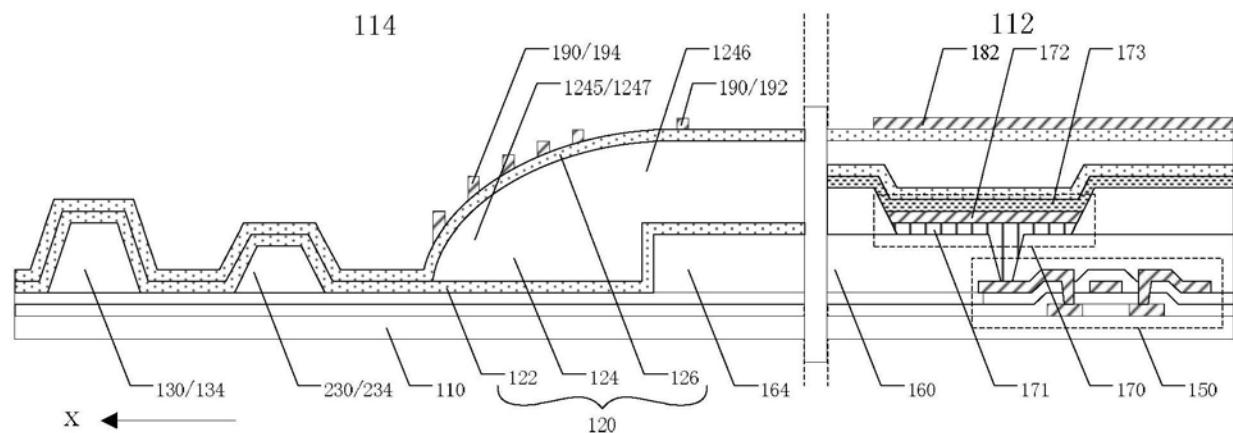

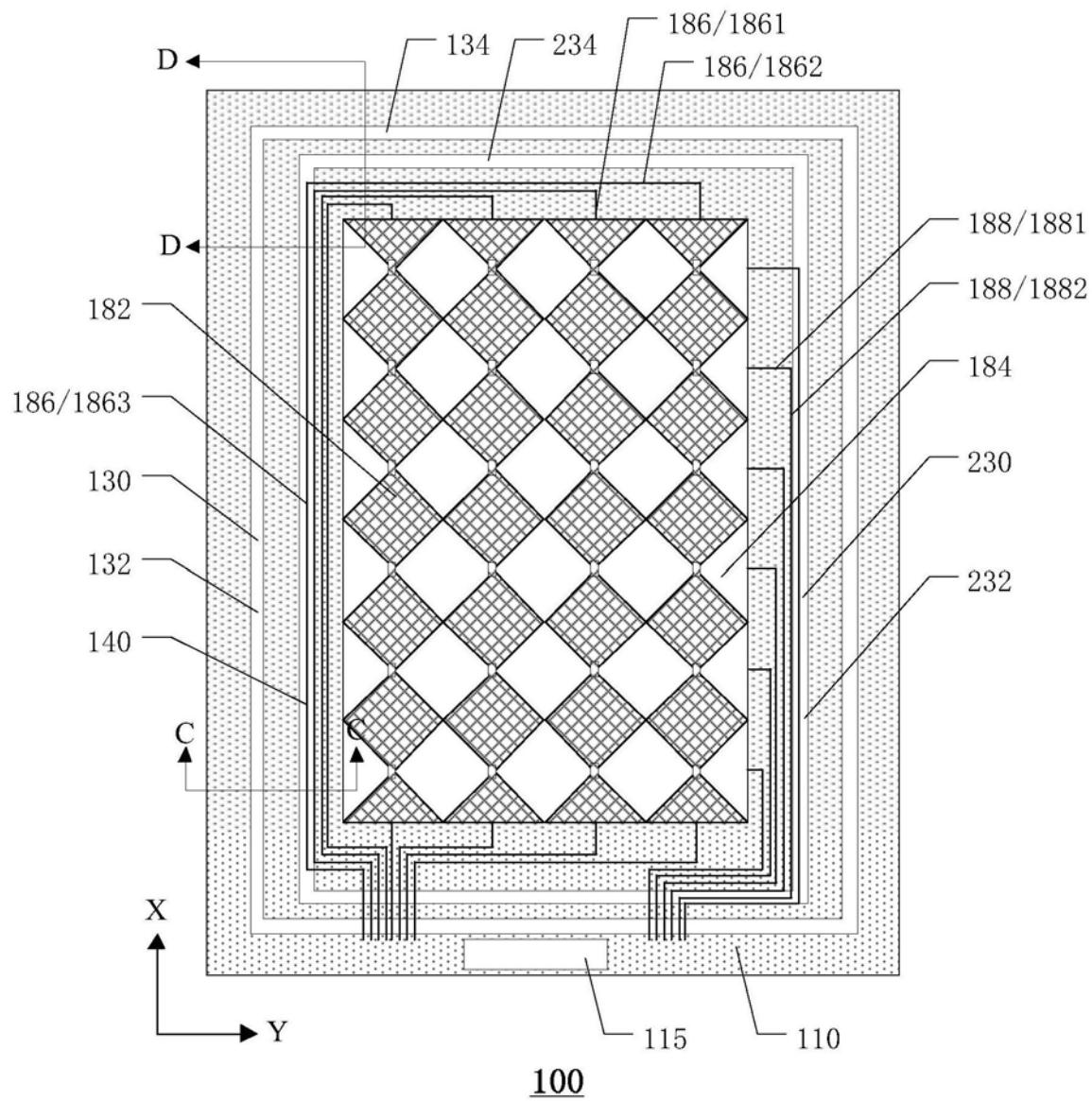

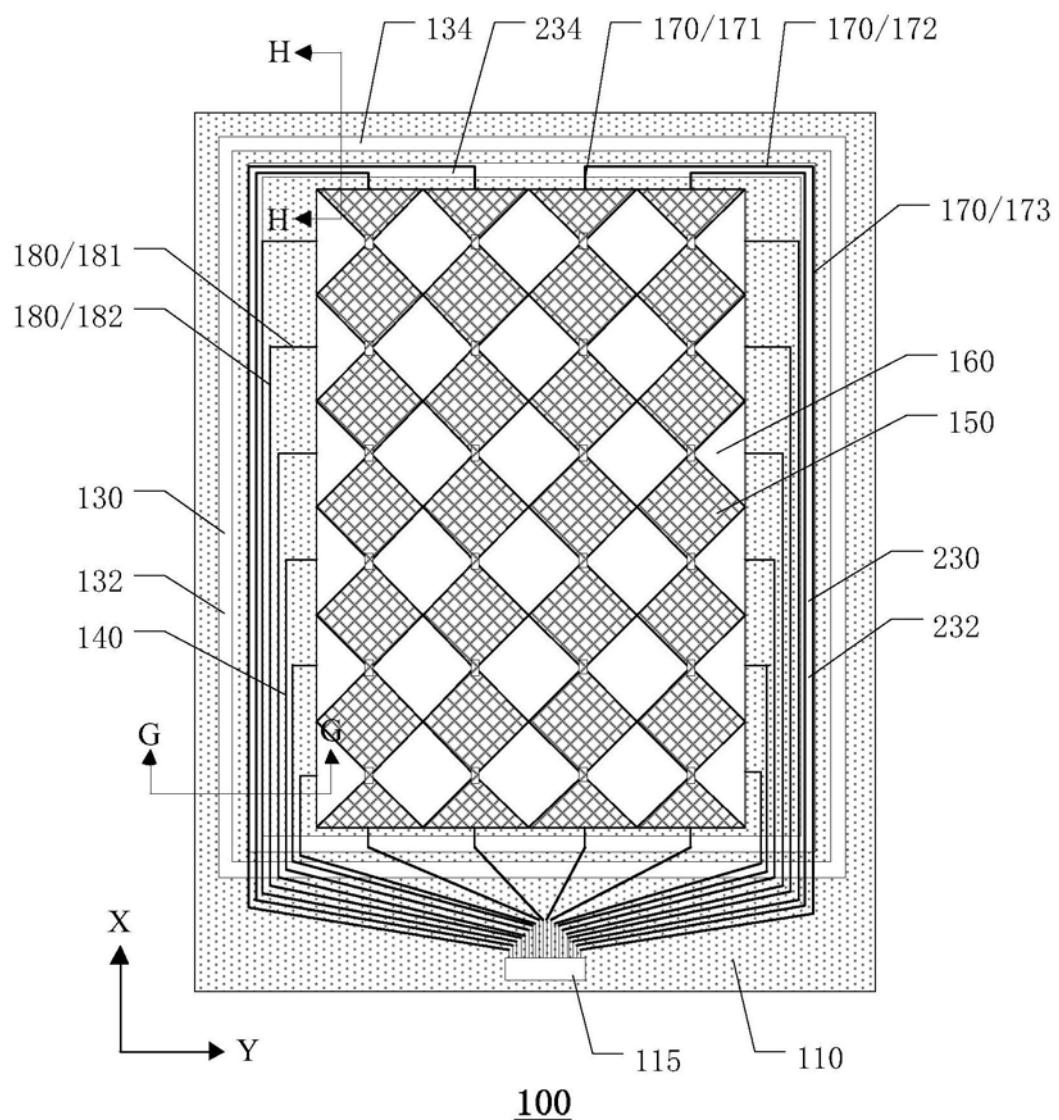

[0034] 图6为根据本公开一实施例提供的另一种阵列基板的平面示意图;

[0035] 图7为根据本公开一实施例提供一种阵列基板沿图6中CC方向的剖面示意图;

[0036] 图8为根据本公开一实施例提供一种阵列基板沿图6中DD方向的剖面示意图;

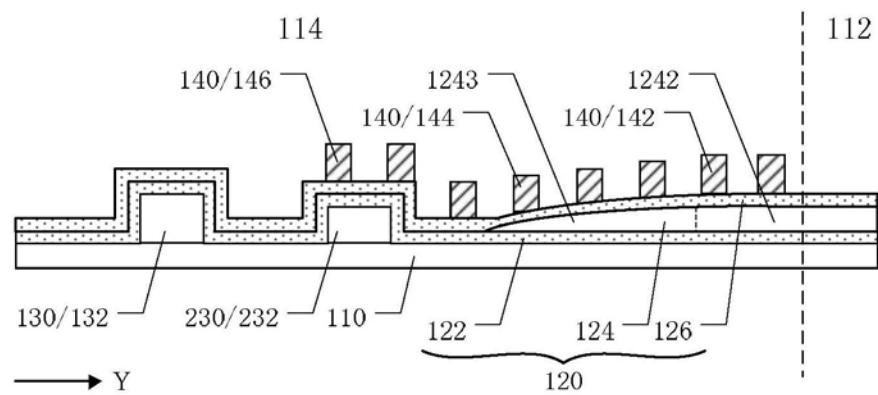

[0037] 图9为根据本公开一实施例提供的一种阵列基板的平面示意图;

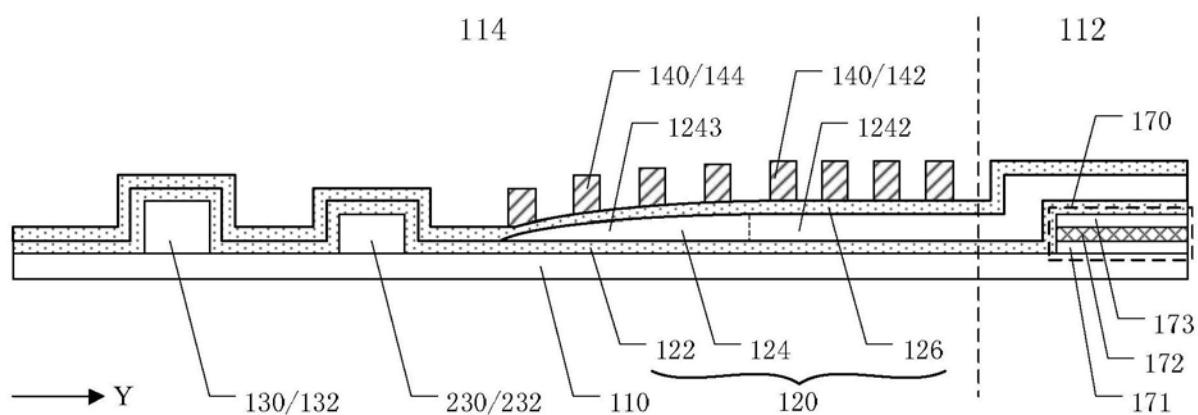

[0038] 图10为根据本公开一实施例提供的一种阵列基板沿图9中EE方向的剖面示意图;

[0039] 图11为根据本公开一实施例提供的一种阵列基板沿图9中FF方向的剖面示意图;

[0040] 图12为根据本公开一实施例提供的另一种阵列基板的平面示意图;

[0041] 图13为根据本公开一实施例提供一种阵列基板沿图5中GG方向的剖面示意图;

[0042] 图14为根据本公开一实施例提供一种阵列基板沿图5中HH方向的剖面示意图;

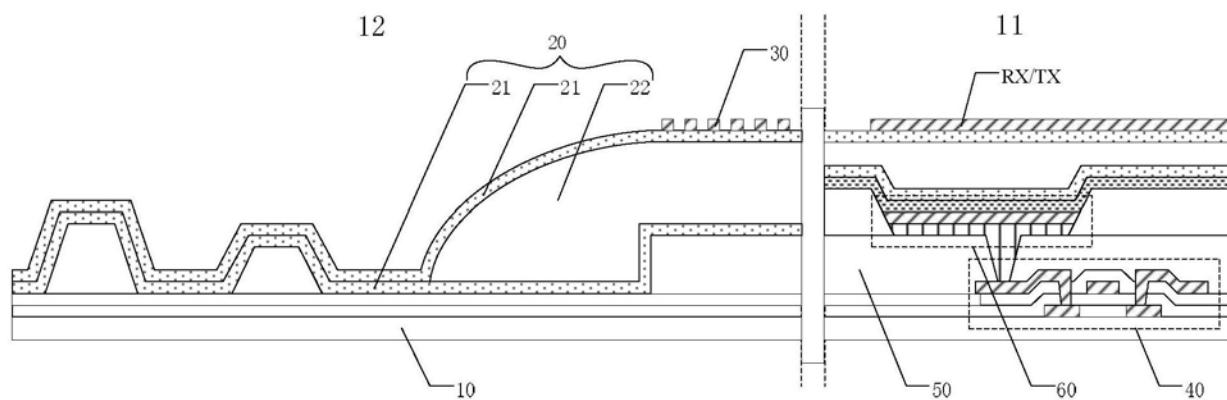

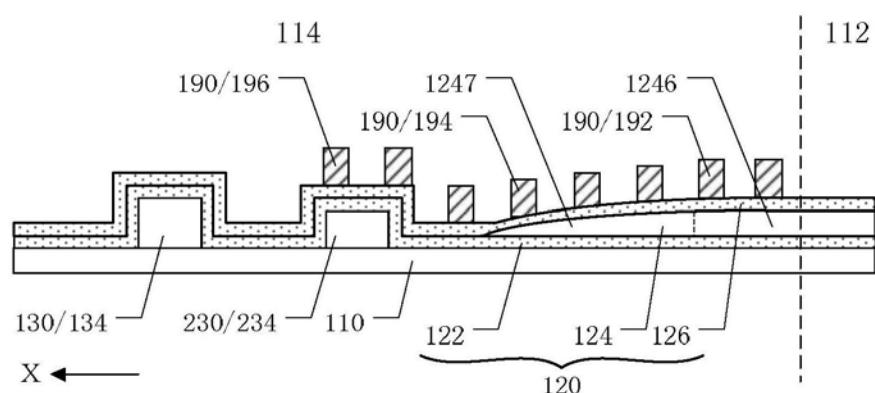

[0043] 图15为根据本公开一实施例提供的一种阵列基板的剖面示意图;以及

[0044] 图16为根据本公开一实施例提供的一种显示装置的结构示意图。

## 具体实施方式

[0045] 为使本公开实施例的目的、技术方案和优点更加清楚,下面将结合本公开实施例的附图,对本公开实施例的技术方案进行清楚、完整地描述。显然,所描述的实施例是本公开的一部分实施例,而不是全部的实施例。基于所描述的本公开的实施例,本领域普通技术人员在无需创造性劳动的前提下所获得的所有其他实施例,都属于本公开保护的范围。

[0046] 除非另外定义,本公开使用的技术术语或者科学术语应当为本公开所属领域内具有一般技能的人士所理解的通常意义。本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性,而只是用来区分不同的组成部分。“包括”或者“包含”等类似的词语意指出现该词前面的元件或者物件涵盖出现在该词后面列举的元件或者物件及其等同,而不排除其他元件或者物件。“连接”或者“相连”等类似的词语并非限定于物理的或者机械的连接,而是可以包括电性的连接,不管是直接的还是间接的。

[0047] 目前,为了实现显示装置(例如,有机发光二极管显示装置)的轻薄化设计,可将显示面板和触控结构集成在一起。因此,FMLOC(Flexible Multiple Layer On Cell)触控技术应运而生,FMLOC触控技术是直接在封装层上制作触控结构的各种电极层和各种走线,从而将触控结构集成在显示面板上。由此,采用FMLOC触控技术的显示装置不仅可实现显示装置的轻薄化,还可实现柔性显示和柔性触控。

[0048] 在采用FMLOC触控技术的显示装置中,该显示装置的周边区设置有与触控驱动电极(Tx)和触控感应电极(Rx)相连的信号通道线。图1为一种阵列基板的周边区的剖面示意图。如图1所示,衬底基板10上设置有封装层20;封装层20包括两层无机封装层21和夹设在两层无机封装层21之间的有机封装层22;封装层20远离衬底基板10的表面上形成有与触控驱动电极(Tx)或触控感应电极(Rx)相连的信号走线30。由于有机封装层22会经过一个流平的过程,从而会在该阵列基板的周边区形成厚度逐渐减小的斜坡部。为了避免斜坡对于信号走线30的影响,通常会将上述的信号走线30形成在有机封装层22的平缓部所对应的位置,从而导致周边区的宽度较大,不利于实现显示装置的窄边框设计。

[0049] 图2为另一种阵列基板的剖面示意图。如图2所示,该阵列基板包括衬底基板10、封装层20、信号走线30、像素驱动层40、平坦层50和有机发光器件60。衬底基板10包括显示区11和显示区11周边的周边区12;像素驱动层40位于衬底基板10上,且位于衬底基板10的显示区11;平坦层50位于像素驱动层40远离衬底基板10的一侧;有机发光器件60位于平坦层50远离像素驱动层40的一侧;封装层20位于有机发光器件60远离衬底基板10的一侧;封装层20包括两层无机封装层21和夹设在两层无机封装层21之间的有机封装层22;封装层20远离衬底基板10的表面上形成有与触控驱动电极(Tx)或触控感应电极(Rx)相连的信号走线30。由于平坦层50并非整层设置,因此平坦层50上的封装层20与衬底基板10的距离会在平坦层50的边缘突然减小,并且有机封装层22会经过一个流平的过程,从而会在该阵列基板的周边区形成厚度逐渐减小的斜坡部。为了避免上述的斜坡部对于信号走线30的影响,通常会将上述的信号走线30形成在有机封装层22的平缓部所对应的位置,也即平坦层50上的位置。由此,采用该阵列基板的显示装置的边框的宽度包括斜坡部的宽度与平缓部的宽度,并且平缓部的宽度较大,从而不利于实现窄边框设计。

[0050] 另一方面,随着窄边框设计的发展,显示装置的边框越来越窄,上述的信号走线的空间越来越小;此时,仅通过减小线宽和线距已经不足以解决采用窄边框设计的显示装置的走线需求。

[0051] 对此,本公开实施例提供一种阵列基板和显示装置。该阵列基板包括衬底基板、像素驱动层、平坦层、有机发光器件、封装层、第一挡墙和多条第一通道线。衬底基板包括显示区和位于显示区周边的周边区;像素驱动层位于衬底基板上;平坦层位于像素驱动层远离衬底基板的一侧;有机发光器件位于平坦层远离像素驱动层的一侧;封装层,位于有机发光

器件远离衬底基板的一侧；第一挡墙位于周边区且包括沿第一方向延伸的第一挡墙部；多条第一通道线位于周边区且位于封装层远离衬底基板的一侧，各多条第一通道线沿第一方向延伸，多条第一通道线沿第二方向排列，第二方向大致垂直于第一方向；封装层包括有机封装层，平坦层包括沿第一方向延伸的第一边缘部，第一边缘部位于第一挡墙部和显示区之间，第一边缘部在衬底基板上的正投影被有机封装层在衬底基板上的正投影覆盖，且多条第一通道线中的至少一条第一通道线在衬底基板上的正投影位于第一边缘部远离显示区的一侧。由此，该阵列基板通过将多条第一通道线中的至少一条第一通道线设置在第一边缘部远离显示区的一侧(即封装层的斜坡部)可减小周边区的宽度，从而可实现采用该阵列基板的显示装置的窄边框甚至无边框设计。

[0052] 下面，结合附图对本公开实施例提供的阵列基板和显示装置进行详细的说明。

[0053] 图3为根据本公开一实施例提供的一种阵列基板的平面示意图；图4为根据本公开一实施例提供的一种阵列基板沿图3中AA方向的剖面示意图。如图3和图4所示，该阵列基板100包括衬底基板110、像素驱动层150、平坦层160、有机发光器件170、封装层120、第一挡墙130和多条第一通道线140。衬底基板110包括显示区112和位于显示区112周边的周边区114；像素驱动层150位于衬底基板110上；平坦层160位于像素驱动层150远离衬底基板110的一侧；有机发光器件170位于平坦层160远离像素驱动层150的一侧；封装层120位于有机发光器件170远离衬底基板110的一侧；第一挡墙130位于周边区114且包括沿第一方向延伸的第一挡墙部132；多条第一通道线140位于周边区114且位于封装层120远离衬底基板110的一侧，各第一通道线140沿第一方向X延伸，多条第一通道线140沿第二方向Y排列，第二方向大致垂直于第一方向。需要说明的是，上述的像素驱动层可包括像素电路，用于驱动对应的有机发光器件进行发光显示；另外，上述的第二方向大致垂直于第一方向包括第一方向和第二方向之间的夹角等于90度的情况和第一方向和第二方向之间的夹角大于80度且小于100度的情况。

[0054] 如图3和图4所示，封装层120可在部分区域直接设置在衬底基板110，也可在封装层120和衬底基板110之间设置其他膜层结构，例如上述的像素驱动层150、平坦层160、有机发光器件170等；封装层120可将衬底基板110上形成的像素驱动层150和有机发光器件170封装，防止外界环境中水氧腐蚀像素驱动层150和有机发光器件170。第一挡墙130设置在衬底基板110上且位于周边区114；第一挡墙130可在封装层120的形成过程中阻挡封装层120中的流体材料流出第一挡墙130之外。

[0055] 如图3和图4所示，封装层120包括有机封装层124，平坦层160包括沿第一方向X延伸的第一边缘部162，第一边缘部162位于第一挡墙部132和显示区112之间，第一边缘部162在衬底基板110上的正投影被有机封装层124在衬底基板110上的正投影覆盖，且多条第一通道线140中的至少一条第一通道线140在衬底基板110上的正投影位于第一边缘部162远离显示区112的一侧。

[0056] 在本公开实施例提供的阵列基板中，由于平坦层160并非整层设置，封装层120与衬底基板110的距离会在第一边缘部162突然减小，并且有机封装层124会经过一个流平的过程，从而会在周边区114形成厚度逐渐减小的第一斜坡部1243，而有机封装层124在第一边缘部162的上方的部分为第一平坦部1241。该阵列基板通过将多条第一通道线140中的至少一条第一通道线140设置在第一边缘部162远离显示区112的一侧(即第一斜坡部1243或

者第一斜坡部1243远离显示区112的一侧)可减小在第一平坦部1241上设置的第一通道线的数量,甚至不在第一平坦部1241上设置第一通道线,从而可减小第一平坦部1241的宽度,进而减小周边区114的宽度。由此,该阵列基板有利于实现采用该阵列基板的显示装置的窄边框甚至无边框设计。

[0057] 例如,上述的显示区可为该阵列基板的画面显示区域,即出光区;上述的周边区可为该阵列基板不显示画面的区域,即非出光区。周边区可围绕显示区,也可以位于显示区的周边的一部分。

[0058] 例如,衬底基板100可为柔性衬底基板100,例如可为聚酰亚胺(polyimide,PI),以形成柔性显示装置。柔性衬底基板100的材质不限于聚酰亚胺。

[0059] 在一些示例中,如图3和图4所示,有机封装层124包括沿第一方向延伸的第二边缘部1242,第二边缘部1242位于第一边缘部162与第一挡墙部132之间,多条第一通道线140中的至少一条第一通道线140在衬底基板110上的正投影位于第二边缘部1242在衬底基板110上的正投影之内。由此,该阵列基板通过将多条第一通道线中的至少一条第一通道线设置在第二边缘部上可减小在第一平坦部上设置的第一通道线的数量,甚至不在第一平坦部上设置第一通道线,从而可减小第一平坦部的宽度,进而减小周边区的宽度。

[0060] 在一些示例中,如图3和图4所示,多条第一通道线140包括位于第一边缘部162远离衬底基板110的一侧的多条第一平坦通道线142和位于第二边缘部1242远离衬底基板110的一侧的多条第一斜坡通道线144。由于通常的通道线均设置在第一边缘部远离衬底基板的一侧,即第一平坦部上,因此第一平坦部在第二方向Y上的宽度较大,而本公开实施例提供的阵列基板中的第一平坦通道线形成在第一边缘部远离衬底基板的一侧,第一斜坡通道线形成在第二边缘部远离衬底基板的一侧,从而使得第一平坦部需要承载的第一通道线的数量减少,从而可减小第一平坦部在第二方向Y上的宽度,进而可减小该阵列基板的周边区在第二方向Y上的宽度。由此,采用该阵列基板的显示装置可具有较窄的边框。

[0061] 在一些示例中,如图3和图4所示,相邻两条第一斜坡通道线144之间的间距大于相邻两条第一平坦通道线142之间的间距。由于第一斜坡通道线形成在斜坡上,在对导电膜层进行图案化工艺以形成上述的第一平坦通道线和第一斜坡通道线的过程中,当曝光机的性能有限时,容易导致斜坡上的第一斜坡通道线的曝光不足,进而导致相邻的两条第一斜坡通道线之间发生短路现象。在本示例提供的阵列基板中,通过将相邻两条第一斜坡通道线之间的间距设置为大于相邻两条第一平坦通道线之间的间距,该阵列基板可避免第一斜坡通道线的曝光不足而发生的短路等各种不良。

[0062] 在一些示例中,相邻两条第一斜坡通道线144之间的间距为相邻两条第一平坦通道线142之间的间距的1.05-2倍。由此,该阵列基板可避免因将第一斜坡通道线形成在第一斜坡部上而导致的曝光问题,从而可避免因为曝光问题而导致的各种不良。

[0063] 例如,相邻两条第一斜坡通道线144之间的间距为相邻两条第一平坦通道线142之间的间距的1.5倍。一方面,该阵列基板可避免因将第一斜坡通道线形成在第一斜坡部上而导致的曝光问题,另一方面,该阵列基板还可使得相邻两条第一斜坡通道线之间的间距较小,从而在第一斜坡部上设置更多的第一斜坡通道线。

[0064] 当然,本公开实施例包括但不限于此,相邻两条第一斜坡通道线之间的间距也可与相邻两条第一平坦通道线之间的间距相等。例如,相邻两条第一斜坡通道线之间的间距

也可与相邻两条第一平坦通道线之间的间距相等,但是第一斜坡通道线的线宽大于第一平坦通道线的线宽。在一些示例中,在多条第一斜坡通道线144中,相邻两条第一斜坡通道线144之间的间距为第一斜坡通道线144的宽度的1.05-2倍。由于相邻两条第一斜坡通道线之间的间距设置得较大,因此该阵列基板可避免因将第一斜坡通道线形成在第一斜坡部上而导致的曝光问题,从而可避免因为曝光问题而导致的各种不良。

[0065] 在一些示例中,如图3和图4所示,多条第一通道线140中最远离显示区112的一条第一通道线148为地线的一部分,并且多条第一通道线140中最远离显示区112的一条第一通道线148在衬底基板110上的正投影位于有机封装层124在衬底基板110上的正投影与第一挡墙部132在衬底基板110上的正投影之间。也就是说,多条第一通道线中最外侧的一条通道线为地线的一部分,并且地线设置在第一挡墙部和有机封装层之间。由此,该阵列基板还可利用第一挡墙部和有机封装层之间的空间来设置地线,从而进一步减小封装层的平坦部分上的通道线的数量,进而降低该阵列基板的周边区的宽度。

[0066] 在一些示例中,如图3和图4所示,该阵列基板100还包括多个触控驱动电极182、多个触控感应电极184、触控驱动信号线186和触控感应信号线188;多个触控驱动电极182和多个触控感应电极184均位于显示区112且位于封装层120远离衬底基板110的一侧;触控驱动信号线186与各触控驱动电极182相连并延伸至周边区114;触控感应信号线188与各触控感应电极184相连并延伸至周边区114;例如,触控驱动信号线186和触控感应信号线188均可延伸至周边区114中的绑定区115,以与外接电路绑定,从而实现触控的驱动、数据接收和数据处理。在本示例提供的阵列基板中,多条第一通道线140中的至少部分第一通道线140为触控驱动信号线186或触控感应信号线188的一部分。

[0067] 例如,触控驱动电极和触控感应电极可为透明电极或者金属网格。触控驱动电极和触控感应电极在交叠的位置可形成电容,当有手指触摸时,影响了触摸点附近电容的耦合,从而改变了触摸点附近电容的电容量,由此,可利用这种电容量的变化可判断出触控位置。本公开实施例不限于此,例如,触控层可包括互电容式的触控结构,也可包括自电容式的触控结构。

[0068] 图5为根据本公开一实施例提供的一种阵列基板沿图3中BB方向的剖面示意图。如图3、图4和图5所示,第一挡墙130包括沿第二方向延伸的第二挡墙部134。例如,第二挡墙部134和第一挡墙部132相连,两个第一挡墙部132和两个第二挡墙部134首尾相连以形成围绕显示区112的矩形第一挡墙134。

[0069] 在一些示例中,如图5所示,该阵列基板100还包括多条第二通道线190;各第二通道线190沿第二方向延伸;平坦层160包括沿第二方向延伸的第三边缘部164,第三边缘部164位于第二挡墙部134和显示区112之间,第三边缘部164在衬底基板110上的正投影被有机封装层124在衬底基板110上的正投影覆盖,且多条第二通道线190中的至少一条第二通道线190在衬底基板110上的正投影位于第三边缘部164远离显示区112的一侧。由于平坦层160并非整层设置,封装层120与衬底基板110的距离会在第三边缘部164突然减小,并且有机封装层124会经过一个流平的过程,从而会在周边区114形成厚度逐渐减小的第二斜坡部1247,而有机封装层124在第三边缘部164的上方的部分为第二平坦部1246。该阵列基板通过将多条第二通道线190中的至少一条第二通道线190设置在第三边缘部164远离显示区112的一侧(即第二斜坡部1247或者第二斜坡部1247远离显示区112的一侧)可减小在第二

平坦部1246上设置的第二通道线的数量，甚至不在第二平坦部1246上设置第二通道线，从而可减小第二平坦部1246的宽度，进而减小周边区114的宽度。由此，该阵列基板有利于实现采用该阵列基板的显示装置的窄边框甚至无边框设计。

[0070] 在一些示例中，如图3、图4和图5所示，该阵列基板100还包括多个触控驱动电极182、多个触控感应电极184、触控驱动信号线186和触控感应信号线188；多个触控驱动电极182和多个触控感应电极184均位于显示区112且位于封装层120远离衬底基板110的一侧；触控驱动信号线186与各触控驱动电极182相连并延伸至周边区114；触控感应信号线188与各触控感应电极184相连并延伸至周边区114；例如，触控驱动信号线186和触控感应信号线188均可延伸至周边区114中的绑定区115，以与外接电路绑定，从而实现触控的驱动、数据接收和数据处理。各触控感应电极184沿第一方向延伸，多个触控感应电极184沿所述第二方向排列，多条第一通道线140的至少部分第一通道线140为触控感应信号线188的一部分，各多个触控驱动电极182沿第二方向延伸，多个触控驱动电极182沿第一方向排列，多条第二通道线190的至少部分第二通道线190为触控驱动信号线186的一部分。

[0071] 例如，如图3、图4和图5所示，触控驱动信号线186包括沿触控驱动电极182的延伸方向延伸的第一部分1861、沿多个触控驱动电极182的排列方向延伸的第二部分1862以及沿触控驱动电极182的延伸方向延伸的第三部分1863；第一部分1861与触控驱动电极182相连，第二部分1862与第一部分1861相连，第三部分1863与第二部分1862相连。此时，各触控驱动电极182的延伸方向为第一方向X，多个触控驱动电极182的排列方向为第二方向Y。各第一通道线140可为触控驱动信号线186的第三部分1863。

[0072] 例如，如图3、图4和图5所示，触控感应信号线188包括沿触控感应电极184的延伸方向延伸的第四部分1881和沿多个触控感应电极184的排列方向延伸的第五部分1882；第四部分1881与触控感应电极184相连，第五部分1882与第四部分1881相连。此时，各触控感应电极184的延伸方向为第二方向Y，多个触控感应电极184的排列方向为第一方向X。各第一通道线140可为触控感应信号线188的第五部分1882。此时，部分第一通道线140为触控驱动信号线186的一部分，部分第一通道线140为触控感应信号线188的一部分。

[0073] 在一些示例中，如图3、图4和图5所示，有机封装层124包括沿第二方向延伸的第四边缘部1245，第四边缘部1245位于第三边缘部164与第二挡墙部134之间，多条第二通道线190中的至少一条第二通道线190在衬底基板110上的正投影位于第四边缘部1245在衬底基板110上的正投影之内。该阵列基板通过将多条第二通道线190中的至少一条第二通道线190在衬底基板110上的正投影设置在第四边缘部1245在衬底基板110上的正投影之内（即：将多条第二通道线190中的至少一条第二通道线190设置在第四边缘部1245上）可减小在第二平坦部1246上设置的第二通道线的数量，甚至不在第二平坦部1246上设置第二通道线，从而可减小第二平坦部1246的宽度，进而减小周边区114的宽度。由此，该阵列基板有利于实现采用该阵列基板的显示装置的窄边框甚至无边框设计。

[0074] 在一些示例中，如图3、图4和图5所示，多条第二通道线190包括位于第三边缘部164远离衬底基板110的一侧的多条第二平坦通道线192和位于第四边缘部1245远离衬底基板110的一侧的多条第二斜坡通道线194。由于通常的通道线均设置在第三边缘部164远离衬底基板110的一侧，即第二平坦部1246上，因此第二平坦部1246在第一方向X上的宽度较大，而本公开实施例提供的阵列基板中的第二平坦通道线192形成在第三边缘部164远离衬底基板110的一侧，第二斜坡通道线194形成在第四边缘部1245远离衬底基板110的一侧，从而可减小第二平坦部1246的宽度，进而减小周边区114的宽度。由此，该阵列基板有利于实现采用该阵列基板的显示装置的窄边框甚至无边框设计。

通道线形成在第四边缘部远离衬底基板的一侧,从而使得第二平坦部需要承载的第二通道线的数量减少,从而可减小第二平坦部在第一方向X上的宽度,进而可减小该阵列基板的周边区在第一方向X上的宽度。由此,采用该阵列基板的显示装置可具有较窄的边框。

[0075] 在一些示例中,如图3和图5所示,相邻两条第二斜坡通道线194之间的间距大于相邻两条第二平坦通道线192之间的间距。由于第二斜坡通道线形成在斜坡上,在对导电膜层进行图案化工艺以形成上述的第二平坦通道线和第二斜坡通道线的过程中,当曝光机的性能有限时,容易导致斜坡上的第二斜坡通道线的曝光不足,进而导致相邻的两条第二斜坡通道线之间发生短路等不良现象。在本示例提供的阵列基板中,通过将相邻两条第二斜坡通道线之间的间距设置为大于相邻两条第二平坦通道线之间的间距,该阵列基板可避免第二斜坡通道线的曝光不足而发生的短路等各种不良。

[0076] 在一些示例中,相邻两条第二斜坡通道线194之间的间距为相邻两条第二平坦通道线192之间的间距的1.05-2倍。由此,该阵列基板可避免因将第二斜坡通道线形成在第二斜坡部上而导致的曝光问题,从而可避免因为曝光问题而导致的各种不良。

[0077] 例如,相邻两条第二斜坡通道线194之间的间距为相邻两条第二平坦通道线192之间的间距的1.5倍。一方面,该阵列基板可避免因将第二斜坡通道线形成在第二斜坡部上而导致的曝光问题,另一方面,该阵列基板还可同时使得相邻两条第二斜坡通道线之间的间距较小,从而在第二斜坡部上设置更多的第二斜坡通道线。

[0078] 在一些示例中,在多条第二斜坡通道线194中,相邻两条第二斜坡通道线194之间的间距为第二斜坡通道线194的宽度的1.05-2倍。由于相邻两条第二斜坡通道线之间的间距设置得较大,因此该阵列基板可避免因将第二斜坡通道线形成在第二斜坡部上而导致的曝光问题,从而可避免因为曝光问题而导致的各种不良。

[0079] 在一些示例中,如图3、图4和图5所示,有机发光器件170包括沿远离衬底基板110的方向上依次层叠的阳极171、发光层172和阴极173。由此,该有机发光器件170可通过上述的发光层172进行发光。

[0080] 在一些示例中,如图3、图4和图5所示,封装层120还包括:第一无机封装层122和第二无机封装层126;第一无机封装层122设置在有机发光器件170远离衬底基板110的一侧,第二无机封装层126设置在第一无机封装层122远离衬底基板110的一侧;有机封装层124夹设在第一无机封装层122和第二无机封装层126之间,多条第一通道线140位于第二无机封装层126远离衬底基板110的一侧。由此,该封装层具有较强的隔绝水氧的能力,从而可有效地防止外界环境的水氧对封装层所封装的器件的腐蚀。

[0081] 例如,上述的第一无机封装层和第二无机封装层的材料可选自氧化硅、氮化硅或氮氧化硅的一种或多种。由于无机材料的致密性高,从而可以防止水、氧等侵入而影响发光元件的性能。上述的有机封装层的材料可包括高分子树脂,例如聚酰亚胺、聚丙烯酸酯等,有机封装层具有平坦化、缓和应力等作用。

[0082] 在一些示例中,如图3和图4所示,在周边区114,第一无机封装层122包括第一无机封装部1221、第二无机封装部1222和连接第一无机封装部1221和第二无机封装部1222的无机封装连接部1223,第一无机封装部1221在衬底基板110上的正投影与第一边缘部162在衬底基板110上的正投影重叠。也就是说,第一无机封装部1221设置在第一边缘部162上,第二无机封装部1222设置在衬底基板110上,且位于第一边缘部162远离显示区112的一侧。

[0083] 有机封装层124包括连续设置的第一有机封装部1248和第二有机封装部1249，第二有机封装部1249远离显示区112的边缘为有机封装层124的边缘，第一有机封装部1248在衬底基板110上的正投影与第一无机封装部1221和无机封装连接部1223在衬底基板110上的正投影重叠，第二有机封装部1249在衬底基板110上的正投影与第二无机封装部1222在衬底基板110上的正投影重叠。在垂直于衬底基板110的方向上，第一无机封装部1221与衬底基板110之间的距离d1大于第二无机封装部1222与衬底基板110之间的距离d2，且d1和d2的差值大于等于平坦层160的厚度，多条第一通道线140中的至少一条第一通道线140在衬底基板110上的正投影落入第二无机封装部1222在衬底基板110上的正投影之内。

[0084] 在本公开实施例提供的阵列基板中，由于第一无机封装部1221与衬底基板110之间的距离d1大于第二无机封装部1222与衬底基板110之间的距离d2，且d1和d2的差值大于等于平坦层160的厚度，从而使得形成在第一无机封装层122上的有机封装层124会在第二无机封装部1222的位置形成厚度逐渐减小的斜坡部，即第二有机封装部1249为斜坡部，而第一有机封装部1248为平坦部。该阵列基板通过将多条第一通道线140中的至少一条第一通道线140在衬底基板110上的正投影落入第二无机封装部1222在衬底基板110上的正投影之内(即第二有机封装部1249或者第二有机封装部1249远离显示区112的一侧)可减小在有机封装层124的平坦部上设置的第一通道线的数量，甚至不在有机封装层124的平坦部上设置第一通道线，从而可减小有机封装层124的平坦部的宽度，进而减小周边区114的宽度。由此，该阵列基板有利于实现采用该阵列基板的显示装置的窄边框甚至无边框设计。

[0085] 在一些示例中，如图3、图4和图5所示，该阵列基板100还包括第二挡墙230；第二挡墙230设置在衬底基板110上且位于周边区114。第二挡墙230位于第一挡墙130与显示区112之间，第二挡墙230包括沿第一方向延伸的第三挡墙部232，多条第一通道线140在衬底基板110上的正投影位于第三挡墙部232在衬底基板110上的正投影靠近显示区112的一侧。当然，本公开实施例包括但不限于此。

[0086] 在一些示例中，如图3、图4和图5所示，有机封装层124的第二边缘部1242可位于第二挡墙230靠近显示区112的一侧；此时，位于第二边缘部上的第一通道线140在衬底基板110上的正投影位于第三挡墙部232在衬底基板110上的正投影靠近显示区112的一侧。当然，本公开包括但不限于此，有机封装层的第二边缘部也可延伸超过第二挡墙，并位于第二挡墙和第一挡墙之间；此时，位于第二边缘部上的第一通道线也可位于第二挡墙上或者第二挡墙与第一挡墙之间。

[0087] 在一些示例中，像素驱动层可包括薄膜晶体管等器件。例如，像素驱动层可包括位于衬底基板上的有源层、位于有源层远离衬底基板的一侧的第一栅极绝缘层、位于第一栅极绝缘层远离有源层的一侧的栅极、位于栅极远离第一栅极绝缘层的一侧的第二栅极绝缘层、和位于第二栅极绝缘层远离栅极的一侧的源极和漏极。有源层可包括源极区域、沟道区和漏极区域。栅极在衬底基板上的正投影与沟道区在衬底基板上的正投影至少部分重叠；源极与有源层的源极区域相接触，漏极与有源层的漏极区域相接触。当然，像素驱动层中的具体像素结构可参见现有设计，例如2T1C结构、7T1C等像素驱动结构等。

[0088] 例如，衬底基板可为玻璃基板、聚酰亚胺基板或其他基板。

[0089] 例如，第一栅极绝缘层和第二栅极绝缘层的材料可选自氧化硅、氮化硅和氮氧化硅中的至少之一。

[0090] 例如,第一无机封装层122和第二无机封装层126覆盖第一挡墙130和第二挡墙230,从而进一步增强该封装层具有较强的隔绝水氧的能力。图6为根据本公开一实施例提供的另一种阵列基板的平面示意图。图7为根据本公开一实施例提供一种阵列基板沿图6中CC方向的剖面示意图。如图6和

[0091] 图7所示,该阵列基板100还包括第二挡墙230;第二挡墙230设置在衬底基板110上且位于周边区114。第二挡墙230位于第一挡墙130与显示区112之间,第二挡墙230包括沿第一方向延伸的第三挡墙部232,多条第一通道线140中的至少一条第一通道线140在衬底基板110上的正投影位于第三挡墙部232在衬底基板110上的正投影之内。也就是说,多条第一通道线140中的至少一条第一通道线140设置在第三挡墙部232上。此时,通过将多条第一通道线的至少一条第一通道线设置在第三挡墙部上,该阵列基板可进一步减小周边区的宽度,从而可进一步降低采用该阵列基板的显示装置的边框宽度,从而实现窄边框设计。

[0092] 需要说明的是,当多条第一通道线的至少一条第一通道线设置在第三挡墙部上时,封装层的第一无机封装层和第二无机封装层可设置在第三挡墙部远离衬底基板的一侧,而设置在第三挡墙上的第一通道线可设置在第二无机封装层远离衬底基板的一侧。

[0093] 在一些示例中,如图7所示,多条第一通道线140包括位于第三挡墙部232上的多条第一挡墙通道线146。也就是说,多条第一挡墙通道线146在衬底基板110上的正投影落入第三挡墙部232在衬底基板110上的正投影之中。由此,在通常的设计中,由于多条第一通道线均设置在第一平坦部上,因此第一平坦部在第二方向Y上的宽度较大,而本公开实施例提供的阵列基板中的第一平坦通道线形成在第一平坦部上,第一斜坡通道线形成在第一斜坡部上,第一挡墙通道线形成在第三挡墙部上,从而使得第一平坦部需要承载的第一通道线的数量大大减少,从而可减小第一平坦部在第二方向Y上的宽度,进而可减小该阵列基板的周边区在第二方向Y上的宽度。由此,采用该阵列基板的显示装置可具有较窄的边框。

[0094] 图8为根据本公开一实施例提供一种阵列基板沿图6中DD方向的剖面示意图。如图8所示,第二挡墙230包括沿第二方向延伸的第四挡墙部234,多条第二通道线190中的至少一条第二通道线190在衬底基板110上的正投影落入第四挡墙部234在衬底基板110上的正投影之内。也就是说,多条第二通道线190中的至少一条第二通道线190设置在第四挡墙部234上。此时,通过将多条第二通道线190中的至少一条第二通道线190设置在第四挡墙部上,该阵列基板可进一步减小周边区的宽度,从而可进一步降低采用该阵列基板的显示装置的边框宽度,从而实现窄边框设计。

[0095] 在一些示例中,如图8所示,多条第二通道线190包括位于第四挡墙部234上的多条第二挡墙通道线196。也就是说,多条第二挡墙通道线196在衬底基板110上的正投影落入第四挡墙部234在衬底基板110上的正投影之中。由此,本公开实施例提供的阵列基板中的第二平坦通道线形成在第二平坦部上,第二斜坡通道线形成在第二斜坡部上,第二挡墙通道线形成在第四挡墙部上,从而使得第二平坦部需要承载的第二通道线的数量大大减少,从而可减小第二平坦部在第一方向X上的宽度,进而可减小该阵列基板的周边区在第一方向X上的宽度。由此,采用该阵列基板的显示装置可具有较窄的边框。

[0096] 本公开另一实施例还提供一种阵列基板。图9为根据本公开一实施例提供的一种阵列基板的平面示意图;图10为根据本公开一实施例提供的一种阵列基板沿图9中EE方向的剖面示意图。如图9和图10所示,该阵列基板100包括衬底基板110、封装层120、第一挡墙

130和多条第一通道线140。衬底基板110包括显示区112和位于显示区112周边的周边区114，此时，该阵列基板100也可通过显示区112和周边区114进行划分。封装层120设置在衬底基板110上，例如，封装层120可在部分区域直接设置在衬底基板110，也可在封装层120和衬底基板110之间设置其他膜层结构，例如发光结构和驱动发光结构进行发光的电路结构；封装层120可将衬底基板110上形成的发光结构和电路结构封装，防止外界环境中水氧腐蚀发光结构和电路结构。第一挡墙130设置在衬底基板110上且位于周边区114；第一挡墙130可在封装层120的形成过程中阻挡封装层120中的流体材料流出第一挡墙130之外。多条第一通道线140位于周边区114且位于封装层120远离衬底基板110的一侧。

[0097] 如图9和图10所示，各第一通道线140沿第一方向X延伸，多条第一通道线140沿第二方向Y排列，第一挡墙130包括沿第一方向X延伸的第一挡墙部132。封装层120包括有机封装层124，有机封装层124沿第一方向X延伸的边缘部位于第一挡墙部132与显示区112之间，该边缘部包括第一平坦部1241和第一斜坡部1243；多条第一通道线140至少部分位于第一斜坡部1243上。需要说明的是，上述的第一平坦部的斜率小于1/50，上述的第一斜坡部的斜率大于1/50；上述的多条第一通道线至少部分位于第一斜坡部上是指多条第一通道线在衬底基板上的正投影与第一斜坡部在衬底基板上的正投影至少部分重叠。

[0098] 在本公开实施例提供的阵列基板中，由于有机封装层会经过一个流平的过程，从而会在周边区形成厚度逐渐减小的第一斜坡部。该阵列基板通过将多条第一通道线至少部分设置在第一斜坡部上，该阵列基板可减小周边区的宽度，从而可降低采用该阵列基板的显示装置的边框宽度，从而实现窄边框设计。

[0099] 在一些示例中，如图9和图10所示，有机封装层124包括沿第一方向延伸的第二边缘部1242，即上述的第一斜坡部1243，第二边缘部1242位于第一边缘部162与第一挡墙部132之间，多条第一通道线140中的至少一条第一通道线140在衬底基板110上的正投影位于第二边缘部1242在衬底基板110上的正投影之内。由此，该阵列基板通过将多条第一通道线至少部分设置在第二边缘部上可减小在第一平坦部上设置的第一通道线的数量，甚至不在第一平坦部上设置第一通道线，从而可减小第一平坦部的宽度，进而减小周边区的宽度。

[0100] 在一些示例中，如图9和图10所示，多条第一通道线140包括位于第一平坦部1241上的多条第一平坦通道线142和位于第一斜坡部1243上的多条第一斜坡通道线144。也就是说，多条第一平坦通道线142在衬底基板110上的正投影落入第一平坦部1241在衬底基板110上的正投影之中，多条第一斜坡通道线144在衬底基板110上的正投影落入第一斜坡部1243在衬底基板110上的正投影之中。由此，在通常的设计中，由于多条第一通道线均设置在第一平坦部上，因此第一平坦部在第二方向Y上的宽度较大，而本公开实施例提供的阵列基板中的第一平坦通道线形成在第一平坦部上，第一斜坡通道线形成在第一斜坡部上，从而使得第一平坦部需要承载的第一通道线的数量减少，从而可减小第一平坦部在第二方向Y上的宽度，进而可减小该阵列基板的周边区在第二方向Y上的宽度。由此，采用该阵列基板的显示装置可具有较窄的边框。

[0101] 在一些示例中，如图9和图10所示，相邻两条第一斜坡通道线144之间的间距大于相邻两条第一平坦通道线142之间的间距。由于第一斜坡通道线形成在斜坡上，在对导电膜层进行图案化工艺以形成上述的第一平坦通道线和第一斜坡通道线的过程中，当曝光机的性能有限时，容易导致斜坡上的第一斜坡通道线的曝光不足，进而导致相邻的两条第一斜

坡通道线之间发生短路现象。在本示例提供的阵列基板中，通过将相邻两条第一斜坡通道线之间的间距设置为大于相邻两条第一平坦通道线之间的间距，该阵列基板可避免第一斜坡通道线的曝光不足而发生的短路等各种不良。

[0102] 在一些示例中，相邻两条第一斜坡通道线144之间的间距为相邻两条第一平坦通道线142之间的间距的1.05-2倍。由此，该阵列基板可避免因将第一斜坡通道线形成在第一斜坡部上而导致的曝光问题，从而可避免因为曝光问题而导致的各种不良。

[0103] 在一些示例中，如图9和图10所示，相邻两条第一斜坡通道线144之间的间距大于等于相邻两条第一平坦通道线142之间的间距的1.5倍。通过将相邻两条第一斜坡通道线之间的间距设置为大于等于相邻两条第一平坦通道线之间的间距的1.5倍，该阵列基板可避免因将第一斜坡通道线形成在第一斜坡部上而导致的曝光问题，从而可避免因为曝光问题而导致的各种不良。

[0104] 例如，由于第一斜坡通道线形成在第一斜坡部上，在对导电膜层进行图案化工艺以形成上述的第一平坦通道线和第一斜坡通道线的过程中，当曝光机的性能有限时，容易导致第一斜坡通道线的曝光不足，进而导致相邻的两条第一斜坡通道线之间发生短路现象。在本示例提供的阵列基板中，通过将相邻两条第一斜坡通道线之间的间距设置为大于等于相邻两条第一平坦通道线之间的间距的1.5倍，该阵列基板可避免第一斜坡通道线的曝光不足而发生的短路现象。

[0105] 在一些示例中，在多条第一斜坡通道线144中，相邻两条第一斜坡通道线144之间的间距为第一斜坡通道线144的宽度的1.05-2倍。由于相邻两条第一斜坡通道线之间的间距设置得较大，因此该阵列基板可避免因将第一斜坡通道线形成在第一斜坡部上而导致的曝光问题，从而可避免因为曝光问题而导致的各种不良。

[0106] 在一些示例中，如图9和图10所示，在多条第一斜坡通道线中，相邻两条第一斜坡通道线144之间的间距为第一斜坡通道线144的宽度(即线宽)的1.5倍。该阵列基板通过将相邻两条第一斜坡通道线之间的间距设置得较大可避免因将第一斜坡通道线形成在第一斜坡部上而导致的曝光问题，从而可避免因为曝光问题而导致的各种不良。

[0107] 在一些示例中，如图9和图10所示，第一斜坡部1243和第一平坦部1241沿第二方向Y连续设置，第一斜坡部1243位于第一平坦部1241靠近第一挡墙部132的一侧。也就是说，第一斜坡部和第一平坦部为有机封装层流平而形成的沿第一方向X延伸的第一边缘部的连续的两个部分。

[0108] 在一些示例中，如图9和图10所示，多条第一通道线140中最远离显示区112的第一通道线140位于第一斜坡部1243远离显示区112的边缘。也就是说，第一斜坡部1243上方的位置均被利用来设置上述的第一通道线140(即第一斜坡通道线144)，从而可较大地降低该阵列基板的周边区的宽度，从而更有利地实现窄边框设计。

[0109] 在一些示例中，如图10所示，封装层120还包括：第一无机封装层122和第二无机封装层126；第一无机封装层122设置在衬底基板110上，第二无机封装层126设置在第一无机封装层122远离衬底基板110的一侧；有机封装层124夹设在第一无机封装层122和第二无机封装层124之间。由此，该封装层具有较强的隔绝水氧的能力，从而可有效地防止外界环境的水氧对封装层所封装的器件的腐蚀。

[0110] 例如，上述的第一无机封装层和第二无机封装层的材料可选自氧化硅、氮化硅或

氮氧化硅的一种或多种。上述的有机封装层的材料可为有机树脂。

[0111] 在一些示例中,如图9和图10所示,该阵列基板100还包括多个触控驱动电极182、多个触控感应电极184、触控驱动信号线186和触控感应信号线188;多个触控驱动电极182和多个触控感应电极184均位于显示区112且位于封装层120远离衬底基板110的一侧;触控驱动信号线186与各触控驱动电极182相连并延伸至周边区114;触控感应信号线188与各触控感应电极184相连并延伸至周边区114;例如,触控驱动信号线186和触控感应信号线188均可延伸至周边区114中的绑定区115,以与外接电路绑定,从而实现触控的驱动、数据接收和数据处理。在本示例提供的阵列基板中,各多条第一通道线140为触控驱动信号线186或触控感应信号线188的一部分。

[0112] 例如,如图9和图10所示,触控驱动信号线186包括沿触控驱动电极182的延伸方向延伸的第一部分1861、沿多个触控驱动电极182的排列方向延伸的第二部分1862以及沿触控驱动电极182的延伸方向延伸的第三部分1863;第一部分1861与触控驱动电极182相连,第二部分1862与第一部分1861相连,第三部分1863与第二部分1862相连。此时,各触控驱动电极182的延伸方向为第一方向X,多个触控驱动电极182的排列方向为第二方向Y。各第一通道线140可为触控驱动信号线186的第三部分1863。

[0113] 例如,图9和图10所示,触控感应信号线188包括沿触控感应电极184的延伸方向延伸的第四部分1881和沿多个触控感应电极184的排列方向延伸的第五部分1882;第四部分1881与触控感应电极184相连,第五部分1882与第四部分1881相连。此时,各触控感应电极184的延伸方向为第二方向Y,多个触控感应电极184的排列方向为第一方向X。各第一通道线140可为触控感应信号线188的第五部分1882。此时,部分第一通道线140为触控驱动信号线186的一部分,部分第一通道线140为触控感应信号线188的一部分。

[0114] 图11为根据本公开一实施例提供的一种阵列基板沿图9中FF方向的剖面示意图。如图9、图10和图11所示,第一挡墙130包括沿第二方向延伸的第二挡墙部134。例如,第二挡墙部134和第一挡墙部132相连,两个第一挡墙部132和两个第二挡墙部134首尾相连以形成围绕显示区112的矩形第一挡墙134。

[0115] 在一些示例中,如图11所示,该阵列基板100还包括多条第二通道线190;各第二通道线190沿第二方向延伸;有机封装层124沿第二方向延伸的边缘部位于第二挡墙部134与显示区112之间。该边缘部包括第二平坦部1246和第二斜坡部1247,多条第二通道线190至少部分位于第二斜坡部1247上。也就是说,多条第二通道线190在衬底基板110上的正投影与第二斜坡部1247在衬底基板110上的正投影至少部分重叠。在本示例提供的阵列基板中,由于有机封装层会经过一个流平的过程,从而会在周边区形成上述的第二斜坡部;通过将多条第二通道线至少部分设置在第二斜坡部上,该阵列基板可减小周边区在第一方向上的宽度,从而可降低采用该阵列基板的显示装置的边框宽度,从而实现窄边框设计。

[0116] 在一些示例中,如图11所示,多条第二通道线190包括位于第二平坦部1246上的多条第二平坦通道线192和位于第二斜坡部1247上的多条第二斜坡通道线194。也就是说,多条第二平坦通道线192在衬底基板110上的正投影落入第二平坦部1246在衬底基板110上的正投影之中,多条第二斜坡通道线194在衬底基板110上的正投影落入第二斜坡部1247在衬底基板110上的正投影之中。由此,在通常的设计中,由于多条第二通道线均设置在第二平坦部上,因此第二平坦部在第一方向X上的宽度较大,而本示例提供的阵列基板中的第二平

坦通道线形成在第二平坦部上,第二斜坡通道线形成在第二斜坡部上,从而使得第二平坦部需要承载的第二通道线的数量减少,从而可减小第二平坦部在第一方向上的宽度,进而可减小该阵列基板的周边区在第一方向上的宽度。由此,采用该阵列基板的显示装置可具有较窄的边框。

[0117] 在一些示例中,如图11所示,相邻两条第二斜坡通道线194之间的间距大于等于相邻两条第二平坦通道线192之间的间距的1.5倍。通过将相邻两条第二斜坡通道线之间的间距设置为大于等于相邻两条第二平坦通道线之间的间距的1.5倍,该阵列基板可避免因将第二斜坡通道线形成在第二斜坡部上而导致的曝光问题,从而可避免因为曝光问题而导致的各种不良。

[0118] 例如,由于第二斜坡通道线形成在第二斜坡部上,在对导电膜层进行图案化工艺以形成上述的第二平坦通道线和第二斜坡通道线的过程中,当曝光机的性能有限时,容易导致第二斜坡通道线的曝光不足,进而导致相邻的两条第二斜坡通道线之间发生短路现象。在本示例提供的阵列基板中,通过将相邻两条第二斜坡通道线之间的间距设置为大于等于相邻两条第二平坦通道线之间的间距的1.5倍,该阵列基板可避免第二斜坡通道线的曝光不足而发生的短路现象。

[0119] 在一些示例中,如图11所示,在多条第二斜坡通道线中,相邻两条第二斜坡通道线194之间的间距为第二斜坡通道线194的宽度(即线宽)的1.5倍。

[0120] 在一些示例中,如图11所示,第二斜坡部1247和第二平坦部1246沿第一方向X连续设置,第二斜坡部1247位于第二平坦部1246靠近第二挡墙部134的一侧。也就是说,第二斜坡部和第二平坦部为有机封装层流平而形成的沿第二方向延伸的第二边缘部的连续的两个部分。

[0121] 在一些示例中,如图11所示,多条第二通道线190中最远离显示区112的第二通道线190位于第二斜坡部1247远离显示区112的边缘。也就是说,第二斜坡部1247上方的位置均被利用来设置上述的第二通道线190(即第二斜坡通道线194),从而可较大地降低该阵列基板的周边区的宽度,从而更有利地实现窄边框设计。

[0122] 在一些示例中,如图9和图11所示,触控驱动信号线186包括沿触控驱动电极182的延伸方向延伸的第一部分1861、沿多个触控驱动电极182的排列方向延伸的第二部分1862以及沿触控驱动电极182的延伸方向延伸的第三部分173;第一部分1861与触控驱动电极182相连,第二部分1862与第一部分1861相连,第三部分1863与第二部分1862相连。此时,各触控驱动电极182的延伸方向为第一方向X,多个触控驱动电极182的排列方向为第二方向Y。第二通道线190可为触控驱动信号线186的第二部分1862。

[0123] 需要说明的是,在上述的图9、图10和图11所示的阵列基板中,第一通道线的延伸方向(即第一方向)为触控驱动信号线的延伸方向,第二通道线的延伸方向(即第二方向)为触控感应信号线的延伸方向。然而,上述的图9、图10和图11仅为本公开实施例提供的阵列基板的一种示例,本公开实施例包括但不限于此,第一通道线的延伸方向(即第一方向)也可为触控感应信号线的延伸方向,第二通道线的延伸方向(即第二方向)也可为触控驱动信号线的延伸方向。另外,该阵列基板也可仅包括第一通道线,而不设置第二通道线。

[0124] 在一些示例中,如图10和11所示,该阵列基板100还包括有机发光结构170;有机发光器件170位于显示区112,且位于封装层120与衬底基板110之间。此时,封装层120可用于

封装有机发光器件170，以防止外界环境的水氧腐蚀该有机发光器件170。

[0125] 例如，有机发光器件170可包括阳极171、有机发光层172和阴极173。当然，有机发光机构170还可包括其他功能层，例如空穴传输层、电子传输层等，本公开实施例在此不再赘述。

[0126] 图12为根据本公开一实施例提供的另一种阵列基板的平面示意图。图13为根据本公开一实施例提供一种阵列基板沿图12中GG方向的剖面示意图。如图12和图13所示，该阵列基板100还包括第二挡墙230；第二挡墙230设置在衬底基板110上且位于周边区114。第二挡墙230位于第一挡墙130与显示区112之间，第二挡墙230包括沿第一方向延伸的第三挡墙部232，多条第一通道线140在衬底基板110上的正投影与第三挡墙部232在衬底基板110上的正投影至少部分重叠。也就是说，多条第一通道线140至少部分设置在第三挡墙部232上。此时，通过将多条第一通道线至少部分设置在第三挡墙部上，该阵列基板可进一步减小周边区的宽度，从而可进一步降低采用该阵列基板的显示装置的边框宽度，从而实现窄边框设计。

[0127] 需要说明的是，当多条第一通道线至少部分设置在第三挡墙部上时，封装层的第一无机封装层和第二无机封装层可设置在第三挡墙部远离衬底基板的一侧，而设置在第三挡墙上的第一通道线可设置在第二无机封装层远离衬底基板的一侧。

[0128] 在一些示例中，如图13所示，多条第一通道线140包括位于第三挡墙部232上的多条第一挡墙通道线146。也就是说，多条第一挡墙通道线146在衬底基板110上的正投影落入第三挡墙部232在衬底基板110上的正投影之中。由此，在通常的设计中，由于多条第一通道线均设置在第一平坦部上，因此第一平坦部在第二方向Y上的宽度较大，而本公开实施例提供的阵列基板中的第一平坦通道线形成在第一平坦部上，第一斜坡通道线形成在第一斜坡部上，第一挡墙通道线形成在第三挡墙部上，从而使得第一平坦部需要承载的第一通道线的数量大大减少，从而可减小第一平坦部在第二方向Y上的宽度，进而可减小该阵列基板的周边区在第二方向Y上的宽度。由此，采用该阵列基板的显示装置可具有较窄的边框。

[0129] 图14为根据本公开一实施例提供一种阵列基板沿图12中HH方向的剖面示意图。如图14所示，第二挡墙230包括沿第二方向延伸的第四挡墙部234，多条第二通道线190在衬底基板110上的正投影与第四挡墙部234在衬底基板110上的正投影至少部分重叠。也就是说，多条第二通道线190至少部分设置在第四挡墙部234上。此时，通过将多条第二通道线至少部分设置在第四挡墙部上，该阵列基板可进一步减小周边区的宽度，从而可进一步降低采用该阵列基板的显示装置的边框宽度，从而实现窄边框设计。

[0130] 在一些示例中，如图14所示，多条第二通道线190包括位于第四挡墙部234上的多条第二挡墙通道线196。也就是说，多条第二挡墙通道线196在衬底基板110上的正投影落入第四挡墙部234在衬底基板110上的正投影之中。由此，本公开实施例提供的阵列基板中的第二平坦通道线形成在第二平坦部上，第二斜坡通道线形成在第二斜坡部上，第二挡墙通道线形成在第四挡墙部上，从而使得第二平坦部需要承载的第二通道线的数量大大减少，从而可减小第二平坦部在第一方向X上的宽度，进而可减小该阵列基板的周边区在第一方向X上的宽度。由此，采用该阵列基板的显示装置可具有较窄的边框。

[0131] 本公开一实施例还提供一种阵列基板。图15为根据本公开一实施例提供的一种阵列基板的剖面示意图。如图15所示，该阵列基板包括衬底基板110、像素驱动层150、有机发

光器件170、封装层120和多条第一通道线140。衬底基板110包括显示区112和位于显示区112周边的周边区114；像素驱动层150位于衬底基板110上；有机发光器件170位于平坦层160远离像素驱动层150的一侧；封装层120位于有机发光器件170远离衬底基板110的一侧；多条第一通道线140位于周边区114且位于封装层120远离衬底基板110的一侧，各第一通道线140沿第一方向X延伸，多条第一通道线140沿第二方向Y排列，第二方向Y大致垂直于第一方向X。需要说明的是，上述的像素驱动层可包括像素电路，用于驱动对应的有机发光器件进行发光显示；另外，上述的第二方向大致垂直于第一方向包括第一方向和第二方向之间的夹角等于90度的情况和第一方向和第二方向之间的夹角大于80度且小于100度的情况。

[0132] 如图15所示，封装层120包括依次设置的第一无机封装层122和有机封装层124。在周边区114，从显示区112到周边区114的方向上，第一无机封装层122包括连续设置的第一无机封装部1221、无机封装连接部1223和第二无机封装部1222；无机封装连接部1223用于连接第一无机封装部1221和第二无机封装部1222。在周边区114，在从显示区112到周边区114的方向上，有机封装层124包括连续设置的第一有机封装部1241和第二有机封装部1242，第二有机封装部1242远离显示区的边缘为有机封装层124的边缘；第一有机封装部1241在衬底基板110上的正投影与第一无机封装部1221和无机封装连接部1223在衬底基板110上的正投影重叠。在垂直于衬底基板110的方向上，第一无机封装部1221与衬底基板110之间的距离d1大于第二无机封装部1222与衬底基板110之间的距离d2，多条第一通道线140中的至少一条第一通道线140在衬底基板110上的正投影落入第二无机封装部1222在衬底基板110上的正投影之内。

[0133] 在本公开实施例提供的阵列基板中，由于第一无机封装部1221与衬底基板110之间的距离d1大于第二无机封装部1222与衬底基板110之间的距离d2，第一有机封装部1241与衬底基板110的距离会突然减小，并且有机封装层124会经过一个流平的过程，从而第二有机封装部1242会在周边区114形成厚度逐渐减小的第一斜坡部1243。该阵列基板通过将多条第一通道线140中的至少一条第一通道线140在衬底基板110上的正投影落入第二无机封装部1222在衬底基板110上的正投影之内（即第一斜坡部1243或者第一斜坡部1243远离显示区112的一侧）可减小在相对平坦的第一有机封装部1241上设置的第一通道线的数量，甚至不在第一有机封装部1241上设置第一通道线，从而可减小第一有机封装部1241的宽度，进而减小周边区114的宽度。由此，该阵列基板有利于实现采用该阵列基板的显示装置的窄边框甚至无边框设计。

[0134] 在一些示例中，如图15所示，该阵列基板还包括第一挡墙130和平坦层160。平坦层160位于像素驱动层150远离衬底基板110的一侧；有机发光器件170位于平坦层160远离像素驱动层150的一侧；第一挡墙130位于周边区114且包括沿第一方向延伸的第一挡墙部132。平坦层160包括沿第一方向延伸的第一边缘部162，第一边缘部162位于第一挡墙部132和显示区112之间，第一无机封装部1221在衬底基板110上的正投影与第一边缘部162在衬底基板110上正投影重叠，第一无机封装部1221与衬底基板110之间的距离d1和第二无机封装部1222与衬底基板110之间的距离d2之差大于等于平坦层160在垂直于衬底基板110的方向上与无机封装连接部1223相互交叠的部分的最大的厚度。

[0135] 在一些示例中，如图15所示，平坦层160包括第一子平坦层1601和第二子平坦层1602；第一子平坦层1601位于像素驱动层150远离衬底基板110的一侧；第二子平坦层1602

位于第一子平坦层1601远离像素驱动层150的一侧。第一无机封装部1221与衬底基板110之间的距离d1和第二无机封装部1222与衬底基板110之间的距离d2之差大于等于第一子平坦层1601在垂直于衬底基板110的方向上与无机封装连接部1223相互交叠的部分的最大厚度与第二子平坦层1602在垂直于衬底基板110的方向上与无机封装连接部1223相互交叠的部分的最大厚度之和。

[0136] 在一些示例中,如图15所示,多条第一通道线140包括位于第一有机封装部1241远离衬底基板110的一侧的多条第一平坦通道线142和位于第一有机封装部1242远离衬底基板110的一侧的多条第一斜坡通道线144。相邻两条第一斜坡通道线144之间的间距大于相邻两条第一平坦通道线142之间的间距。由于第一斜坡通道线形成在斜坡上,在对导电膜层进行图案化工艺以形成上述的第一平坦通道线和第一斜坡通道线的过程中,当曝光机的性能有限时,容易导致斜坡上的第一斜坡通道线的曝光不足,进而导致相邻的两条第一斜坡通道线之间发生短路现象。在本示例提供的阵列基板中,通过将相邻两条第一斜坡通道线之间的间距设置为大于相邻两条第一平坦通道线之间的间距,该阵列基板可避免第一斜坡通道线的曝光不足而发生的短路等各种不良。

[0137] 在一些示例中,相邻两条第一斜坡通道线144之间的间距为相邻两条第一平坦通道线142之间的间距的1.05-2倍。由此,该阵列基板可避免因将第一斜坡通道线形成在第一斜坡部上而导致的曝光问题,从而可避免因为曝光问题而导致的各种不良。

[0138] 例如,相邻两条第一斜坡通道线144之间的间距为相邻两条第一平坦通道线142之间的间距的1.5倍。一方面,该阵列基板可避免因将第一斜坡通道线形成在第一斜坡部上而导致的曝光问题,另一方面,该阵列基板还可使得相邻两条第一斜坡通道线之间的间距较小,从而在第一斜坡部上设置更多的第一斜坡通道线。

[0139] 当然,本公开实施例包括但不限于此,相邻两条第一斜坡通道线之间的间距也可与相邻两条第一平坦通道线之间的间距相等。例如,相邻两条第一斜坡通道线之间的间距也可与相邻两条第一平坦通道线之间的间距相等,但是第一斜坡通道线的线宽大于第一平坦通道线的线宽。

[0140] 在一些示例中,在多条第一斜坡通道线144中,相邻两条第一斜坡通道线144之间的间距为第一斜坡通道线144的宽度的1.05-2倍。由于相邻两条第一斜坡通道线之间的间距设置得较大,因此该阵列基板可避免因将第一斜坡通道线形成在第一斜坡部上而导致的曝光问题,从而可避免因为曝光问题而导致的各种不良。在一些示例中,如图15所示,该阵列基板还包括位于第一子平坦层1601和第二子平坦层1602之间的连接电极167,连接电极167通过第一子平坦层1601中的过孔与像素驱动层150的一个薄膜晶体管的漏极相连,有机发光器件170的阳极通过第二子平坦层1602中的过孔与连接电极167相连。

[0141] 本公开一实施例还提供一种显示装置。图16为根据本公开一实施例提供的一种显示装置的结构示意图。如图16所示,该显示装置300包括上述的阵列基板100。由于有机封装层会在周边区形成厚度逐渐减小的第一斜坡部,该阵列基板通过将多条第一通道线中的至少一条第一通道线设置在第一边缘部远离显示区的一侧(即第一斜坡部或者第一斜坡部远离显示区的一侧)可减小在第一平坦部上设置的第一通道线的数量,甚至不在第一平坦部上设置第一通道线,从而可减小第一平坦部的宽度,进而减小周边区的宽度。由此,该显示装置可具有较窄的边框,并且还可实现柔性显示和柔性触控,具体可参见上述实施例的相

关描述,在此不再赘述。

[0142] 在一些示例中,该显示装置可为手机、笔记本电脑、平板电脑、导航仪、电子相框等具有显示功能的电子产品。

[0143] 有以下几点需要说明:

[0144] (1) 本公开实施例附图中,只涉及到与本公开实施例涉及到的结构,其他结构可参考通常设计。

[0145] (2) 在不冲突的情况下,本公开同一实施例及不同实施例中的特征可以相互组合。

[0146] 以上,仅为本公开的具体实施方式,但本公开的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本公开揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本公开的保护范围之内。因此,本公开的保护范围应以权利要求的保护范围为准。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16

|                |                                |                      |            |

|----------------|--------------------------------|----------------------|------------|

| 专利名称(译)        | 阵列基板和显示装置                      |                      |            |

| 公开(公告)号        | <a href="#">CN210379052U</a>   | 公开(公告)日              | 2020-04-21 |

| 申请号            | CN201921977920.3               | 申请日                  | 2019-11-15 |

| [标]申请(专利权)人(译) | 京东方科技集团股份有限公司<br>成都京东方光电科技有限公司 |                      |            |

| 申请(专利权)人(译)    | 京东方科技集团股份有限公司<br>成都京东方光电科技有限公司 |                      |            |

| 当前申请(专利权)人(译)  | 京东方科技集团股份有限公司<br>成都京东方光电科技有限公司 |                      |            |

| [标]发明人         | 何帆<br>董向丹<br>肖云升<br>都蒙蒙<br>张波  |                      |            |

| 发明人            | 何帆<br>董向丹<br>肖云升<br>都蒙蒙<br>张波  |                      |            |

| IPC分类号         | H01L27/32 H01L51/52            |                      |            |

| 代理人(译)         | 焦玉恒                            |                      |            |

| 外部链接           | <a href="#">Espacenet</a>      | <a href="#">SIPO</a> |            |

## 摘要(译)

一种阵列基板和显示装置。该阵列基板包括衬底基板、像素驱动层、平坦层、有机发光器件、封装层、第一挡墙和多条第一通道线；第一挡墙位于周边区且包括沿第一方向延伸的第一挡墙部；多条第一通道线位于周边区，且位于封装层远离衬底基板的一侧；封装层包括有机封装层，平坦层包括沿第一方向延伸的第一边缘部，第一边缘部位于第一挡墙部和显示区之间，第一边缘部在衬底基板上的正投影被有机封装层在衬底基板上的正投影覆盖，且多条第一通道线中的至少一条第一通道线在衬底基板上的正投影位于第一边缘部远离显示区的一侧。该阵列基板可减小周边区的宽度，从而可实现采用该阵列基板的显示装置的窄边框设计。