(12)发明专利申请

(10)申请公布号 CN 110910829 A

(43)申请公布日 2020.03.24

(21)申请号 201911176917.6

(22)申请日 2019.11.26

(71)申请人 深圳市华星光电半导体显示技术有限公司

地址 518132 广东省深圳市光明新区公明

街道塘明大道9-2号

(72)发明人 李东伟

(74)专利代理机构 深圳紫藤知识产权代理有限公司 44570

代理人 何辉

(51)Int.Cl.

G09G 3/3225(2016.01)

权利要求书1页 说明书7页 附图5页

(54)发明名称

OLED像素结构及OLED显示面板

(57)摘要

本发明提供了一种OLED像素结构及OLED显示面板，该像素结构包括驱动电路层、发光功能层、以及色阻层，驱动电路层内形成有像素驱动电路，色阻层包括阵列排布的红色色阻、绿色色阻和蓝色色阻，其中，像素驱动电路位于色阻长边外侧的间隔区域内。通过将像素驱动电路设置在色阻长边外侧的间隔区域内，像素驱动电路的尺寸远大于走线的宽度，增加了相邻像素之间的间隔区域的宽度，避免了由于像素间隔过小带来的像素漏光问题。

1. 一种OLED像素结构,其特征在于,包括:

驱动电路层,所述驱动电路层内形成有像素驱动电路,所述像素驱动电路用于驱动像素发光显示;

发光功能层,形成于所述驱动电路层上,包括依次层叠设置的像素电极层、像素定义层、发光材料层、以及公共电极层。

以及色阻层,包括阵列排布的红色色阻、绿色色阻和蓝色色阻,所述色阻包括相对设置的两个长边和相对设置的两个短边;

其中,所述像素驱动电路位于所述色阻长边外侧的间隔区域内。

2. 如权利要求1所述的OLED像素结构,其特征在于,所述像素驱动电路设置在所述色阻长边左侧的间隔区域内。

3. 如权利要求1所述的OLED像素结构,其特征在于,所述像素驱动电路设置在所述色阻长边右侧的间隔区域内。

4. 如权利要求1所述的OLED像素结构,其特征在于,所述短边为直线。

5. 如权利要求1所述的OLED像素结构,其特征在于,所述短边为外凸的圆弧。

6. 如权利要求1所述的OLED像素结构,其特征在于,相邻的两个所述色阻长边之间的间隔区域的宽度为30um~60um。

7. 如权利要求1所述的OLED像素结构,其特征在于,所述色阻层位于所述驱动电路层和所述发光功能层之间。

8. 如权利要求1所述的OLED像素结构,其特征在于,所述色阻层位于所述发光功能层远离所述驱动电路层的一侧。

9. 如权利要求1所述的OLED像素结构,其特征在于,所述像素驱动电路包括第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、存储电容、以及发光二极管,所述第一薄膜晶体管的源极与所述存储电容的第一电极板、所述第三薄膜晶体管的栅极连接,所述存储电容的第二电极板与所述第二薄膜晶体管的源极、第三薄膜晶体管的源极、发光二极管的阳极连接。

10. 一种OLED显示面板,其特征在于,包括如权利要求1至9任一所述的OLED像素结构。

## OLED像素结构及OLED显示面板

### 技术领域

[0001] 本发明涉及显示领域,尤其涉及一种OLED像素结构及OLED显示面板。

### 背景技术

[0002] 现有大尺寸AMOLED(Active Matrix Organic Light Emitting Diode,有源矩阵有机发光二极管)显示面板像素通常采用白光OLED搭配红、绿、蓝三基色色阻实现不同颜色。

[0003] 然而,目前AMOLED显示面板的像素间隔通常只有十几微米,如此小的像素间隔带来了一定程度的像素漏光问题。

[0004] 因此,现有AMOLED显示面板存在像素间隔过小的问题,需要解决。

### 发明内容

[0005] 本发明提供一种OLED像素结构,以缓解现有AMOLED显示面板存在像素间隔过小的问题。

[0006] 为解决以上问题,本发明提供的技术方案如下:

[0007] 本发明提供一种OLED像素结构,其包括:

[0008] 驱动电路层,所述驱动电路层内形成有像素驱动电路,所述像素驱动电路用于驱动像素发光显示;

[0009] 发光功能层,形成于所述驱动电路层上,包括依次层叠设置的像素电极层、像素定义层、发光材料层、以及公共电极层。

[0010] 以及色阻层,包括阵列排布的红色色阻、绿色色阻和蓝色色阻,所述色阻包括相对设置的两个长边和相对设置的两个短边;

[0011] 其中,所述像素驱动电路位于所述色阻长边外侧的间隔区域内。

[0012] 在本发明提供的OLED像素结构中,所述像素驱动电路设置在所述色阻长边左侧的间隔区域内。

[0013] 在本发明提供的OLED像素结构中,所述像素驱动电路设置在所述色阻长边右侧的间隔区域内。

[0014] 在本发明提供的OLED像素结构中,所述短边为直线。

[0015] 在本发明提供的OLED像素结构中,所述短边为外凸的圆弧。

[0016] 在本发明提供的OLED像素结构中,相邻的两个所述色阻长边之间的间隔区域的宽度为30um~60um。

[0017] 在本发明提供的OLED像素结构中,所述色阻层位于所述驱动电路层和所述发光功能层之间。

[0018] 在本发明提供的OLED像素结构中,所述色阻层位于所述发光功能层远离所述驱动电路层的一侧。

[0019] 在本发明提供的OLED像素结构中,所述像素驱动电路包括第一薄膜晶体管、第二

薄膜晶体管、第三薄膜晶体管、存储电容、以及发光二极管，所述第一薄膜晶体管的源极与所述存储电容的第一电极板、所述第三薄膜晶体管的栅极连接，所述存储电容的第二电极板与所述第二薄膜晶体管的源极、第三薄膜晶体管的源极、发光二极管的阳极连接。

[0020] 同时，本发明提供一种OLED显示面板，其包括如上任一所述的OLED像素结构。

[0021] 本发明的有益效果为：本发明提供一种OLED像素结构及OLED显示面板，该像素结构包括驱动电路层、发光功能层、以及色阻层，驱动电路层内形成有像素驱动电路，色阻层包括阵列排布的红色色阻、绿色色阻和蓝色色阻，其中，像素驱动电路位于色阻长边外侧的间隔区域内。通过将像素驱动电路设置在色阻长边外侧的间隔区域内，像素驱动电路的尺寸远大于走线的宽度，增加了相邻像素之间的间隔区域的宽度，避免了由于像素间隔过小带来的像素漏光问题。

## 附图说明

[0022] 为了更清楚地说明实施例或现有技术中的技术方案，下面将对实施例或现有技术描述中所需要使用的附图作简单介绍，显而易见地，下面描述中的附图仅仅是发明的一些实施例，对于本领域普通技术人员来讲，在不付出创造性劳动的前提下，还可以根据这些附图获得其他的附图。

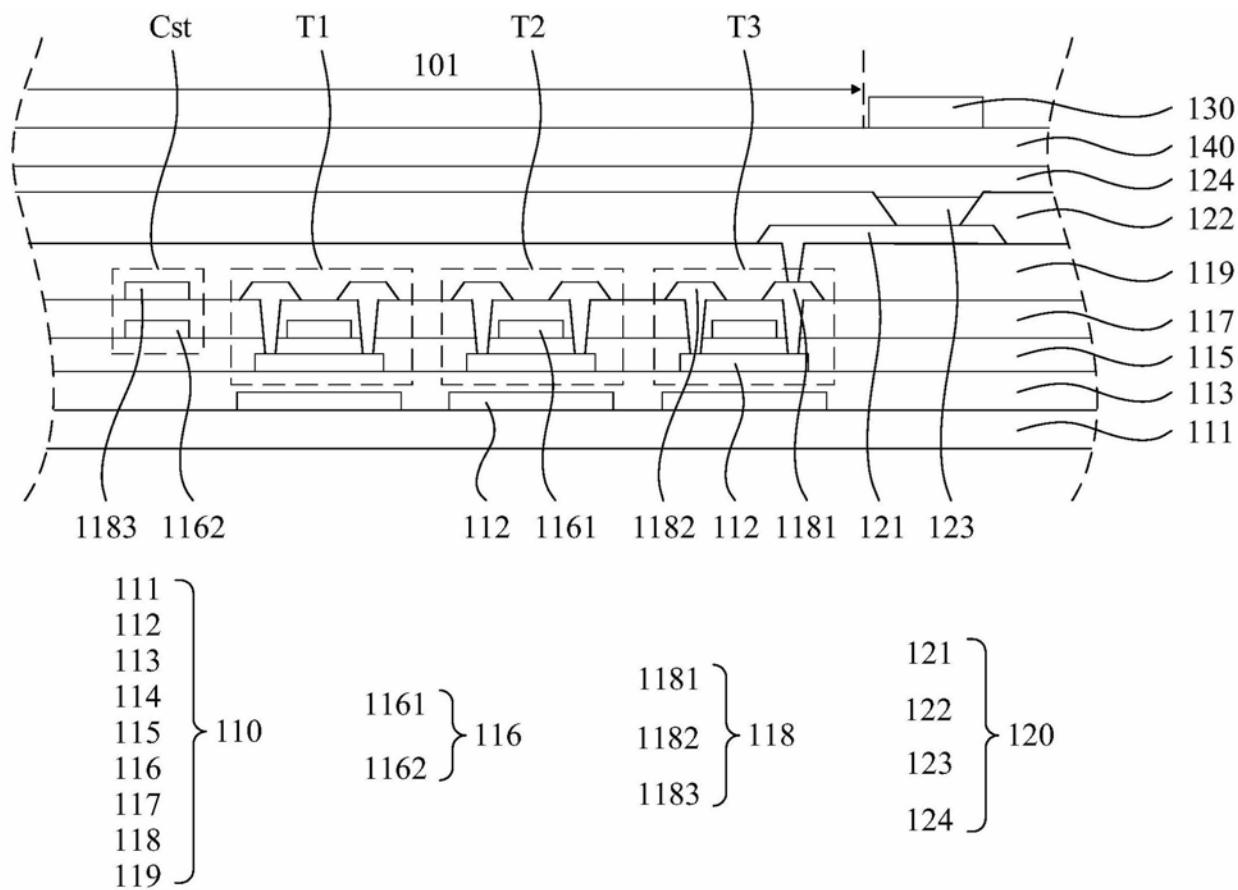

[0023] 图1为本发明实施例提供的OLED像素结构的第一种膜层结构示意图。

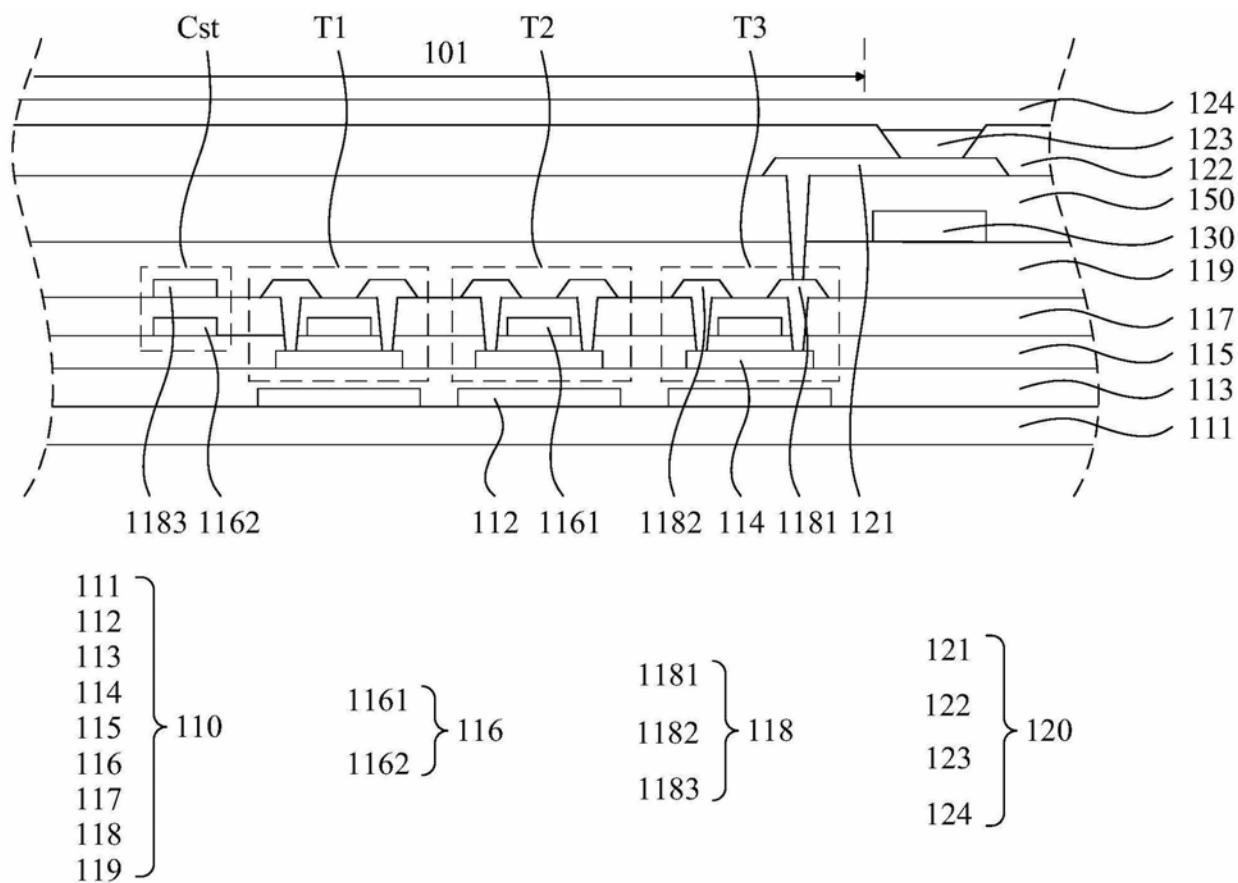

[0024] 图2为本发明实施例提供的OLED像素结构的第二种膜层结构示意图。

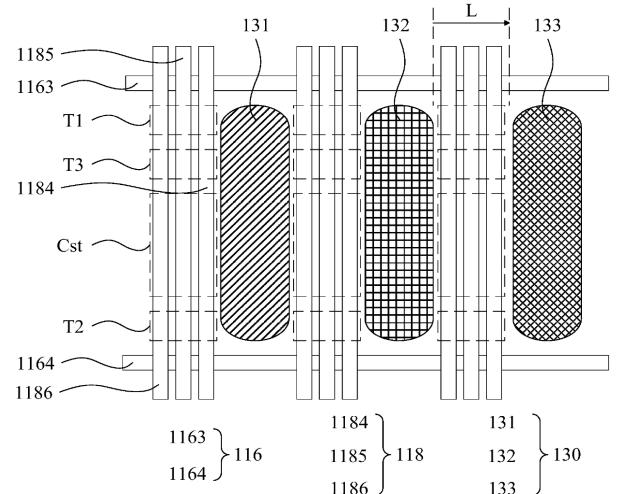

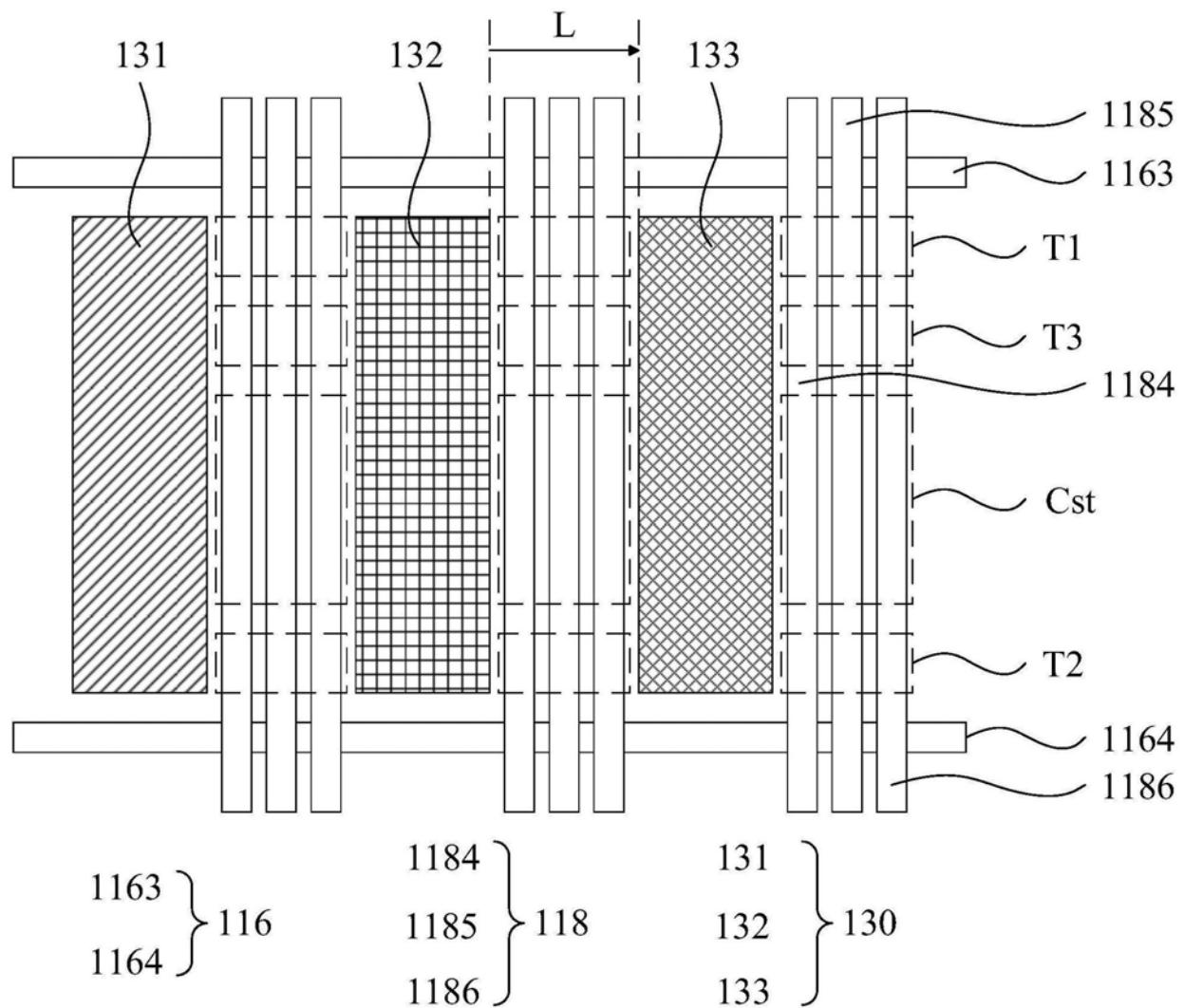

[0025] 图3为本发明实施例提供的栅极层、源漏极层、色阻层的第一种平面叠加示意简图。

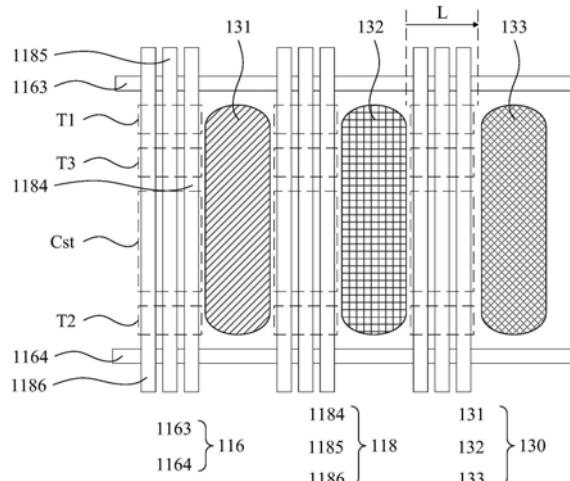

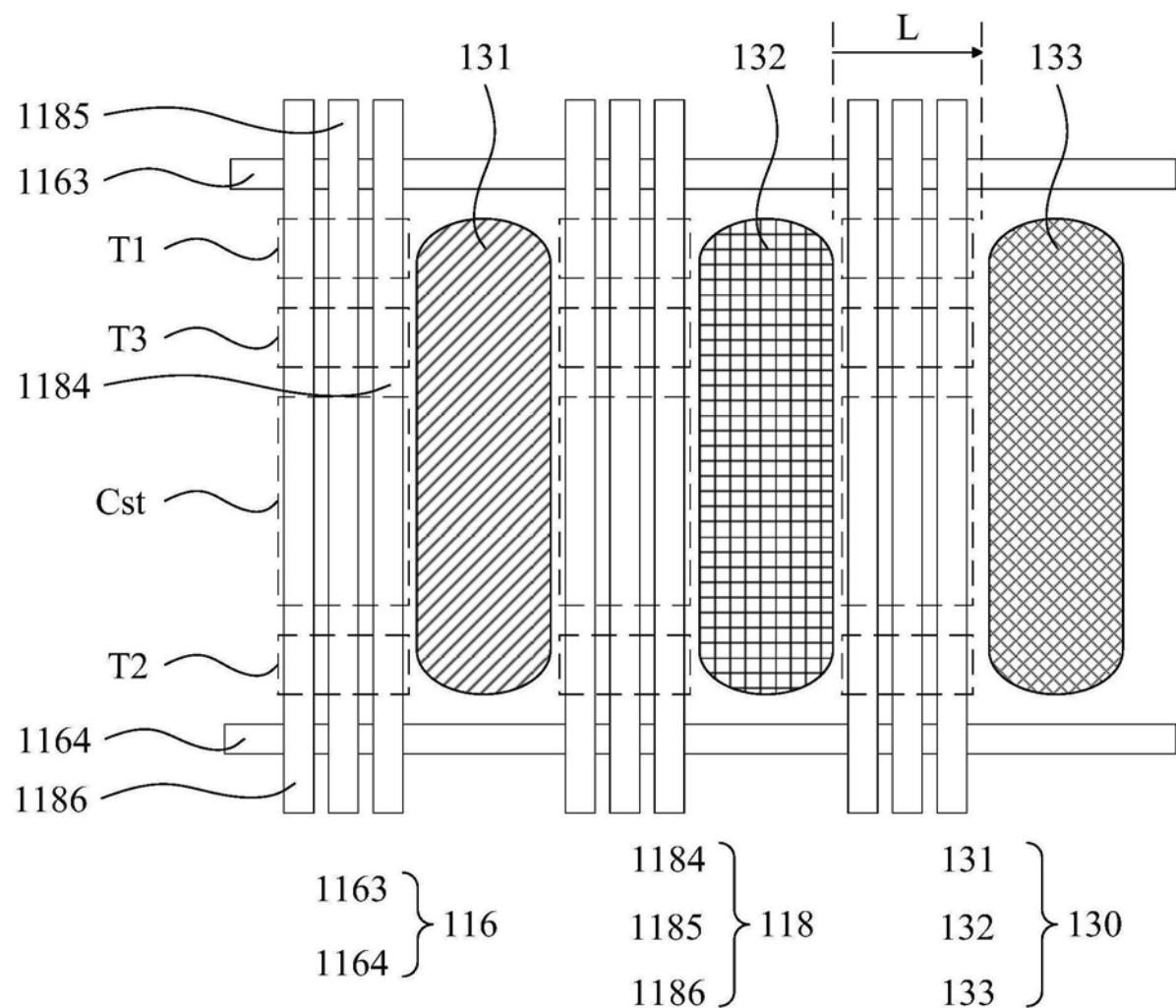

[0026] 图4为本发明实施例提供的栅极层、源漏极层、色阻层的第二种平面叠加示意简图。

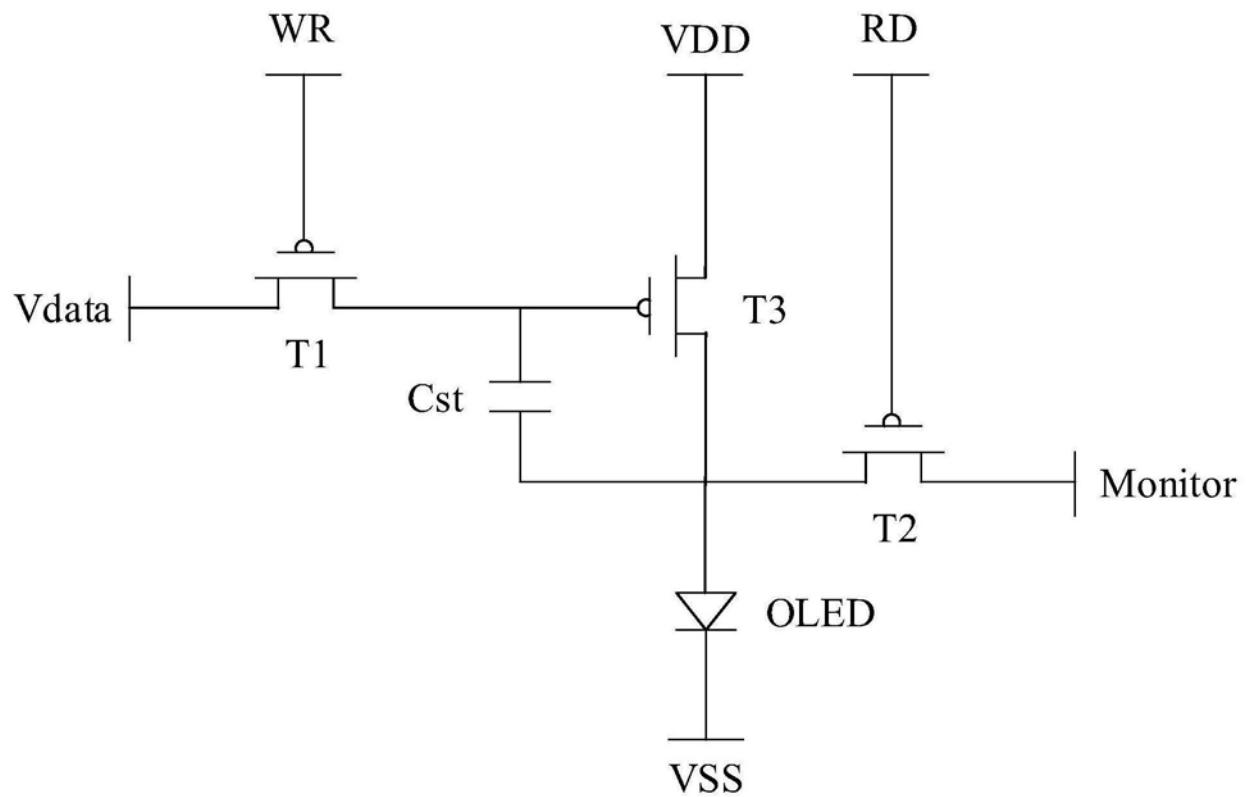

[0027] 图5为本发明实施例提供的像素驱动电路图。

## 具体实施方式

[0028] 下面将结合本发明的具体实施方案，对本发明实施方案和/或实施例中的技术方案进行清楚、完整的描述，显而易见的，下面所描述的实施方案和/或实施例仅仅是本发明一部分实施方案和/或实施例，而不是全部的实施方案和/或实施例。基于本发明中的实施方案和/或实施例，本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施方案和/或实施例，都属于本发明保护范围。

[0029] 本发明所提到的方向用语，例如[上]、[下]、[左]、[右]、[前]、[后]、[内]、[外]、[侧]等，仅是参考附加图式的方向。因此，使用的方向用语是用以说明和理解本发明，而非用以限制本发明。术语“第一”、“第二”等仅用于描述目的，而不能理解为指示或是暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此，限定有“第一”、“第二”等的特征可以明示或者隐含地包括一个或者更多个该特征。

[0030] 针对现有AMOLED显示面板存在像素间隔过小的问题，本发明提供一种OLED像素结构可以缓解这个问题。

[0031] 在一种实施例中，如图1至图4所示，本发明提供的OLED像素结构包括：

[0032] 驱动电路层110，驱动电路层110内形成有像素驱动电路，像素驱动电路用于驱动

像素发光显示；

[0033] 发光功能层120，形成于驱动电路层110上，包括依次层叠设置的像素电极层121、像素定义层122、发光材料层123、以及公共电极层124；

[0034] 以及色阻层130，包括阵列排布的红色色阻131、绿色色阻132和蓝色色阻133，色阻包括相对设置的两个长边和相对设置的两个短边；

[0035] 其中，像素驱动电路位于色阻长边外侧的间隔区域101内。

[0036] 本实施例提供了一种OLED像素结构，该像素结构包括驱动电路层、发光功能层、以及色阻层，驱动电路层内形成有像素驱动电路，色阻层包括阵列排布的红色色阻、绿色色阻和蓝色色阻，其中，像素驱动电路位于色阻长边外侧的间隔区域内。通过将像素驱动电路设置在色阻长边外侧的间隔区域内，像素驱动电路的尺寸远大于走线的宽度，增加了相邻像素之间的间隔区域的宽度，避免了由于像素间隔过小带来的像素漏光问题。

[0037] 本发明提供的OLED像素结构包括呈阵列排布的多个子像素结构，下面将以单个子像素，结合具体实施例对本发明提供的OLED像素结构做进一步详细说明。

[0038] 在一种实施例中，当OLED像素结构的发光类型为顶发光时，如图1所示，图1为本发明实施例提供的OLED像素结构的第一种膜层结构示意图，本实施例提供的OLED像素结构包括：

[0039] 驱动电路层110，驱动电路层110包括从下到上依次层叠设置的衬底111、遮光层112、缓冲层113、有源层114、栅极绝缘层115、栅极层116、层间绝缘层117、源漏极层118、以及钝化层119；

[0040] 发光功能层120，形成于驱动电路层110上，包括从下到上依次层叠设置的像素电极层121、像素定义层122、发光材料层123、以及公共电极层124；

[0041] 色阻层130，形成于发光功能层120上；

[0042] 驱动电路层110内形成有第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3、以及电容Cst，第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3和电容Cst共同构成像素驱动电路。该像素驱动电路位于色阻层130所在区域外的间隔区域101内。

[0043] 驱动电路层110的具体膜层结构包括：

[0044] 衬底111，包括玻璃衬底或柔性衬底。玻璃衬底由铝硅酸盐和其他成分构成。柔性衬底一般包括第一柔性衬底、第二柔性衬底、以及位于第一柔性衬底和第二柔性衬底之间的无机层；其中第一柔性衬底和第二柔性衬底的材料通常为聚乙酰胺或聚对苯二甲酸乙二醇酯等有机聚合物，用于保证柔性衬底的柔性；无机层的材料通常为氮化硅或氧化硅，用于阻隔阵列基板外的水或氧气进入薄膜晶体管。

[0045] 遮光层112，用于遮蔽背光，防止有源层受到强光照射产生光生载流子，进而发生光电漏电，导致器件漏电流增大的问题。遮光层112的材料一般为单晶硅、金属等遮光材料。优选遮光层112的材料为金属钼。

[0046] 缓冲层113，形成于遮光层112上，且覆盖遮光层112和衬底111，用于防止衬底111中的杂质在热制程中扩散到薄膜晶体管中，降低漏电流。缓冲层113为氮化硅/氧化硅堆叠方式形成的膜层结构，氮化硅具有较强的离子阻隔能力和很好的水氧隔绝能力，氧化硅与多晶硅的界面润湿性较好。

[0047] 有源层114，形成于缓冲层113上，图案化形成薄膜晶体管的有源区，有源区包括沟

道区和位于沟道区两端的掺杂区。

[0048] 棚极绝缘层115,形成于有源层114上,且覆盖有源层114和缓冲层113。棚极绝缘层一般为氧化硅/氮化硅形成的堆叠结构,氮化硅具有较高的击穿电压,可作为良好的棚极绝缘材料,氧化硅与多晶硅表面具有良好的晶界匹配和应力匹配,同时氧化硅具有良好的台阶覆盖性。

[0049] 棚极层116,形成于棚极绝缘层115上,图案化形成薄膜晶体管的棚极1161、存储电容Cst的第一电极板1162、以及棚极信号线(未画出),棚极层116的材料一般为金属钼、金属铝或铝合金。

[0050] 层间绝缘层117,形成于棚极层116上,并覆盖棚极层116和棚极绝缘层115,同棚极绝缘层115相似,层间绝缘层117一般也是氧化硅/氮化硅形成的堆叠结构。

[0051] 源漏极层118,形成于层间绝缘层117上,图案化形成薄膜晶体管的源极1181、漏极1182,存储电容Cst的第二电极板1183、以及源漏极信号线(未画出)。源极和漏极分别通过过孔与有源区连接,源漏极层118的材料为钛/铝/钛的叠层结构,或是钼/铝/钼的叠层结构。

[0052] 钝化层119,形成于源漏极层118上,覆盖源漏极层118和层间绝缘层117,钝化层119的材料一般为氮化硅。

[0053] 发光功能层120的具体膜层结构包括:

[0054] 像素电极层121,形成于钝化层119上,图案化形成像素电极,像素电极通过钝化层119内的过孔与第三薄膜晶体管T3的源极连接。像素电极层121的材料一般为氧化铟锡、金属银、石墨烯等材料。

[0055] 像素定义层122,形成于像素电极层121上,图案化形成有像素定义区,用于限定像素区域。

[0056] 发光材料层123,形成于像素定义区内,本发明实施例提供的发光材料层均为白光材料层,发光材料层123可以是将不同颜色的发光材料混合而成的单层发光材料层,也可是不同颜色的发光材料堆叠而成的多层发光材料层。

[0057] 公共电极层124,形成于发光材料层123上,连接并覆盖发光材料层123。由于本实施例提供的像素结构为顶发光类型,光线需要穿透公共电极层124,因此公共电极层124的材料为氧化铟锡等透明材料。

[0058] 阻隔层140,形成于公共电极层124上,阻隔层140为一般为氮化硅、氧化硅单层结构,或氮化硅/氧化硅的堆叠结构。

[0059] 色阻层130,形成于阻隔层140上,与发光材料层123相对应。如图3和图4所示,色阻层130图案化形成阵列排布的红色色阻131、绿色色阻132和蓝色色阻133。

[0060] 在另一种实施例中,当OLED像素结构的发光类型为底发光时,如图2所示,图2为本发明实施例提供的OLED像素结构的第二种膜层结构示意图,本实施例提供的OLED像素结构包括:

[0061] 驱动电路层110,驱动电路层110包括从下到上依次层叠设置的衬底111、遮光层112、缓冲层113、有源层114、棚极绝缘层115、棚极层116、层间绝缘层117、源漏极层118、以及钝化层119;

[0062] 色阻层130,形成于驱动电路层110上;

[0063] 平坦化层150,形成于色阻层130上,覆盖色阻层130和发光功能层120,用于平坦化色阻层130;

[0064] 发光功能层120,形成于平坦化层150上,包括从下到上依次层叠设置的像素电极层121、像素定义层122、发光材料层123、以及公共电极层124;

[0065] 驱动电路层110内形成有第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3、以及电容Cst,第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3和电容Cst共同构成像素驱动电路。该像素驱动电路位于色阻层130所在区域外的间隔区域101内。

[0066] 本实施例提供的驱动电路层110、像素定义层122、发光材料层123、以及色阻层130的膜层结构,分别与图1所示的实施例中的驱动电路层110、像素定义层122、发光材料层123、以及色阻层130的膜层结构相类似,具体可参照上述实施例,在此不再赘述。

[0067] 在本实施例中,平坦化层150,形成于色阻层130上,覆盖色阻层130和钝化层119,用于平坦化色阻层130,为后续像素结构的制备提供平坦的基底,其材料一般为聚酰亚胺(PI)、聚对苯二甲酸乙二醇酯(PET)或其他有机物。

[0068] 像素电极层121,形成于平坦化层150上,图案化形成像素电极,像素电极通过平坦化层150、钝化层119内的过孔与第三薄膜晶体管T3的源极连接。由于本实施例提供的像素结构为底发光类型,光线需要穿透像素电极层121,因此像素电极层121的材料为氧化铟锡等透明材料。

[0069] 公共电极层124,形成于发光材料层123上,连接并覆盖发光材料层123,公共电极层124的材料一般为镱(Yb)、钙(Ca)、镁(Mg)、银(Ag)等金属中的一种或几种,或其合金。

[0070] 在一种实施例中,如图3所示,图3为本发明实施例提供的单个像素的栅极层、源漏极层、色阻层的第一种平面叠加示意简图(部分结构未画出)。

[0071] 色阻层130包括红色色阻131、绿色色阻132和蓝色色阻133,红色色阻131、绿色色阻132和蓝色色阻133的形状相同,均包括相对设置的两个长边和相对设置的两个短边。两个长边为直线,两各短边也为直线,两个长边和两个短边共同围成矩形的色阻图案。

[0072] 栅极层116图案化形成有写入信号线1163和读取信号线1164,写入信号线1163和读取信号线1164,分别设置于色阻的两个短边外侧的间隔区域内。相邻的两个色阻短边之间的间隔区域的宽度为20um~40um。

[0073] 源漏极层118图案化形成有感测信号线1184、电源信号线1185、以及数据信号线1186,感测信号线1184、电源信号线1185、以及数据信号线1186相互平行,感测信号线1184、电源信号线1185、以及数据信号线1186同时设置于色阻的右侧长边外侧的间隔区域内。在另一种实施例中,请参照图4,感测信号线1184、电源信号线1185、以及数据信号线1186也可以同时设置于色阻的左侧长边外侧的间隔区域内;在其他实施方案中,感测信号线1184、电源信号线1185、以及数据信号线1186还可以,分开设置于色阻左侧长边外侧和右侧长边外侧的间隔区域内,在此不做限定。

[0074] 像素驱动电路包括第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3、以及存储电容Cst,第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3、以及存储电容Cst均形成于色阻右长边外侧的间隔区域内。

[0075] 在本实施例中,由于像素驱动电路内薄膜晶体管和存储电容的尺寸都远大于信号走线的宽度,将像素驱动电路设置在色阻长边外侧的间隔区域内,增加了相邻色阻之间的

间隔区域的宽度,相邻两个色阻长边外侧的间隔区域的宽度L可以达到30um~60um。从而避免了由于像素间隔过小带来的像素漏光问题。

[0076] 同时,本实施例将色阻图案设置为矩形,在像素阵列设置的结构中,保证了尽可能大的像素开口率。

[0077] 在另一种实施例中,如图4所示,图4为本发明实施例提供的单个像素的栅极层、源漏极层、色阻层的第二种平面叠加示意简图(部分结构未画出)。

[0078] 色阻层130包括红色色阻131、绿色色阻132和蓝色色阻133,红色色阻131、绿色色阻132和蓝色色阻133的形状相同,均包括相对设置的两个长边和相对设置的两个短边。两个长边为直线,两各短边为外凸的圆弧形,连个长边和两个短边共同围成类似椭球形的色阻图案。

[0079] 栅极层116图案化形成有写入信号线1163和读取信号线1164,写入信号线1163和读取信号线1164,分别设置于色阻的两个短边外侧的间隔区域内。相邻的两个色阻短边之间的间隔区域的宽度为20um~40um。

[0080] 源漏极层118图案化形成有感测信号线1184、电源信号线1185、以及数据信号线1186,感测信号线1184、电源信号线1185、以及数据信号线1186相互平行,感测信号线1184、电源信号线1185、以及数据信号线1186同时设置于色阻的左侧长边外侧的间隔区域内。在另一种实施例中,请参照图3,感测信号线1184、电源信号线1185、以及数据信号线1186也可以同时设置于色阻的右侧长边外侧的间隔区域内;在其他实施方案中,感测信号线1184、电源信号线1185、以及数据信号线1186还可以,分开设置于色阻左侧长边外侧和右侧长边外侧的间隔区域内,在此不做限定。

[0081] 像素驱动电路包括第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3、以及存储电容Cst,第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3、以及存储电容Cst均形成于色阻左侧长边外侧的间隔区域内。

[0082] 在本实施例中,由于像素驱动电路内薄膜晶体管和存储电容的尺寸都远大于信号走线的宽度,将像素驱动电路设置在色阻长边外侧的间隔区域内,增加了相邻色阻之间的间隔区域的宽度,相邻两个色阻长边外侧的间隔区域的宽度L可以达到30um~60um。从而避免了由于像素间隔过小带来的像素漏光问题。

[0083] 同时,本实施例将色阻图案设置为类似椭球形,在色阻的制备工艺中,类似椭球形使得色阻的成膜均匀性更好,有利于显示面板的显示均一性。

[0084] OLED像素结构包括呈阵列排布的多个子像素结构,每个子像素结构内设置有一个像素驱动电路,如图5所示,图5为本发明实施例提供的像素驱动电路图。该像素驱动电路包括第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3、存储电容Cst和有机发光二极管OLED。

[0085] 第一薄膜晶体管T1的源极与存储电容Cst的第一电极板、第三薄膜晶体管T3的栅极连接,存储电容Cst的第二电极板与第二薄膜晶体管T2的源极、第三薄膜晶体管T3的源极、有机发光二极管OLED的阳极连接。

[0086] 第一薄膜晶体管T1的栅极接入写入信号WR,第一薄膜晶体管T1的漏极接入数据信号Vdata;第二薄膜晶体管T2的栅极接入读取信号RD,第二薄膜晶体管T2的漏极接入感测信号Monitor;第三薄膜晶体管T3的漏极接入电源信号VDD;有机发光二极管OLED的阴极接入

地信号VSS。

[0087] 第三薄膜晶体管T3为驱动晶体管,用于驱动有机发光二极管OLED发光;第一薄膜晶体管T1为开关晶体管,用于对驱动晶体管的栅极进行充电,从而控制像素电路是否导通;第二薄膜晶体管T2为补偿晶体管,用于对驱动晶体管T3进行电路补偿;存储电容Cst用于存储第三薄膜晶体管T3的栅极电位,从而使得开关晶体管T1关闭时,驱动晶体管T3的栅极依然处于原电位。

[0088] 同时,本发明还提供一种AMOLED显示面板,其包括OLED像素结构,该OLED像素结构包括:

[0089] 驱动电路层,所述驱动电路层内形成有像素驱动电路,所述像素驱动电路用于驱动像素发光显示;

[0090] 发光功能层,形成于所述驱动电路层上,包括依次层叠设置的像素电极层、像素定义层、发光材料层、以及公共电极层。

[0091] 以及色阻层,包括阵列排布的红色色阻、绿色色阻和蓝色色阻,所述色阻包括相对设置的两个长边和相对设置的两个短边;

[0092] 其中,所述像素驱动电路位于所述色阻长边外侧的间隔区域内。

[0093] 在一种实施例中,所述像素驱动电路设置在所述色阻长边左侧的间隔区域内。

[0094] 在一种实施例中,所述像素驱动电路设置在所述色阻长边右侧的间隔区域内。

[0095] 在一种实施例中,所述短边为直线。

[0096] 在一种实施例中,所述短边为外凸的圆弧。

[0097] 在一种实施例中,相邻的两个所述色阻长边之间的间隔区域的宽度为30μm~60μm。

[0098] 在一种实施例中,相邻的两个所述色阻短边之间的间隔区域的宽度为20μm~40μm。

[0099] 在一种实施例中,所述色阻层位于所述驱动电路层和所述发光功能层之间。

[0100] 在一种实施例中,所述色阻层位于所述发光功能层远离所述驱动电路层的一侧。

[0101] 在一种实施例中,所述像素驱动电路包括第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、存储电容、以及发光二极管,所述第一薄膜晶体管的源极与所述存储电容的第一电极板、所述第三薄膜晶体管的栅极连接,所述存储电容的第二电极板与所述第二薄膜晶体管的源极、第三薄膜晶体管的源极、发光二极管的阳极连接。

[0102] 根据上述实施例可知:

[0103] 本发明实施例提供了一种OLED像素结构及OLED显示面板,该像素结构包括驱动电路层、发光功能层、以及色阻层,驱动电路层内形成有像素驱动电路,色阻层包括阵列排布的红色色阻、绿色色阻和蓝色色阻,其中,像素驱动电路位于色阻长边外侧的间隔区域内。通过将像素驱动电路设置在色阻长边外侧的间隔区域内,像素驱动电路的尺寸远大于走线的宽度,增加了相邻像素之间的间隔区域的宽度,避免了由于像素间隔过小带来的像素漏光问题。

[0104] 综上所述,虽然本发明已以优选实施例揭露如上,但上述优选实施例并非用以限制本发明,本领域的普通技术人员,在不脱离本发明的精神和范围内,均可作各种更动与润饰,因此本发明的保护范围以权利要求界定的范围为准。

图1

图2

图3

图4

图5

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | OLED像素结构及OLED显示面板                              |         |            |

| 公开(公告)号        | <a href="#">CN110910829A</a>                   | 公开(公告)日 | 2020-03-24 |

| 申请号            | CN201911176917.6                               | 申请日     | 2019-11-26 |

| [标]申请(专利权)人(译) | 深圳市华星光电技术有限公司                                  |         |            |

| [标]发明人         | 李东伟                                            |         |            |

| 发明人            | 李东伟                                            |         |            |

| IPC分类号         | G09G3/3225                                     |         |            |

| CPC分类号         | G09G3/3225                                     |         |            |

| 代理人(译)         | 何辉                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明提供了一种OLED像素结构及OLED显示面板，该像素结构包括驱动电路层、发光功能层、以及色阻层，驱动电路层内形成有像素驱动电路，色阻层包括阵列排布的红色色阻、绿色色阻和蓝色色阻，其中，像素驱动电路位于色阻长边外侧的间隔区域内。通过将像素驱动电路设置在色阻长边外侧的间隔区域内，像素驱动电路的尺寸远大于走线的宽度，增加了相邻像素之间的间隔区域的宽度，避免了由于像素间隔过小带来的像素漏光问题。