(12)发明专利申请

(10)申请公布号 CN 108711399 A

(43)申请公布日 2018.10.26

(21)申请号 201810535429.9

(22)申请日 2018.05.29

(71)申请人 昆山国显光电有限公司

地址 215300 江苏省苏州市昆山市开发区

龙腾路1号4幢

(72)发明人 胡思明 黄秀颀 吴剑龙 韩珍珍

张露

(74)专利代理机构 上海思微知识产权代理事务

所(普通合伙) 31237

代理人 智云

(51)Int.Cl.

G09G 3/3225(2016.01)

权利要求书2页 说明书6页 附图3页

(54)发明名称

发射控制驱动电路、发射控制驱动器及有机

发光显示装置

(57)摘要

本发明提供了一种发射控制驱动电路、发射控制驱动器及有机发光显示装置，每个发射控制驱动电路构成一个级，多个级依次相连，所述发射控制驱动电路包括输入单元、第一栅控电路、第二栅控电路、输出单元和初始驱动控制器，其中：所述输入单元响应于第一时钟信号、第二时钟信号和起始信号，传输第一信号和第二信号中的任意一个；所述第一栅控电路通过第一信号或第二信号控制所述初始驱动控制器输出下一级发射控制驱动电路的初始驱动信号；所述第二栅控电路通过第一信号或第二信号控制所述输出单元输出发射控制信号。

1. 一种发射控制驱动电路，每个发射控制驱动电路构成一个级，多个级依次相连，其特征在于，所述发射控制驱动电路包括输入单元、第一栅控电路、第二栅控电路、输出单元和初始驱动控制器，其中：

所述输入单元响应于第一时钟信号、第二时钟信号和起始信号，传输第一信号和第二信号中的任意一个；

所述第一栅控电路通过第一信号或第二信号控制所述初始驱动控制器输出下一级发射控制驱动电路的初始驱动信号；

所述第二栅控电路通过第一信号或第二信号控制所述输出单元输出发射控制信号。

2. 如权利要求1所述的发射控制驱动电路，其特征在于，所述输入单元包括第一晶体管、第二晶体管和第一电容，其中：

所述第一晶体管和所述第二晶体管为P型薄膜晶体管；

所述第一晶体管的栅极响应于所述第一时钟信号，所述第一晶体管的源极响应于所述起始信号，所述第一晶体管的漏极连接所述第二晶体管的栅极；

所述第二晶体管的源极响应于所述第二时钟信号，所述第二晶体管的漏极连接所述第一栅控电路；

所述第一电容的一端连接所述第二晶体管的栅极，另一端连接所述第二晶体管的漏极。

3. 如权利要求2所述的发射控制驱动电路，其特征在于，所述第一栅控电路包括第三晶体管、第四晶体管和第五晶体管，其中：

所述第三晶体管、所述第四晶体管和所述第五晶体管为P型薄膜晶体管；

所述第三晶体管的栅极连接所述第二晶体管的漏极，所述第三晶体管的源极连接第一电源，所述第三晶体管的漏极连接所述第四晶体管的源极；

所述第四晶体管的栅极响应于所述第一时钟信号，所述第四晶体管的漏极连接第二电源；

所述第五晶体管的栅极连接所述第三晶体管的漏极，所述第五晶体管的源极连接第一电源；所述第五晶体管的漏极连接所述第二晶体管的漏极。

4. 如权利要求3所述的发射控制驱动电路，其特征在于，所述第二栅控电路包括第七晶体管，其中：

所述第七晶体管为P型薄膜晶体管；

所述第七晶体管的栅极响应于所述第一时钟信号，所述第七晶体管的漏极连接第二电源。

5. 如权利要求4所述的发射控制驱动电路，其特征在于，所述输出单元包括第九晶体管、第十晶体管和第十二晶体管，其中：

所述第九晶体管、所述第十晶体管和所述第十二晶体管为P型薄膜晶体管；

所述第九晶体管的栅极连接所述第七晶体管的源极，所述第九晶体管的漏极连接所述第二电源；

所述第十晶体管的栅极连接所述第九晶体管的源极，所述第十晶体管的源极连接所述第十二晶体管的栅极，所述第十晶体管的漏极连接所述第二电源；

所述第十二晶体管的源极输出所述发射控制信号，所述第十二晶体管的漏极连接所述

第二电源。

6. 如权利要求5所述的发射控制驱动电路,其特征在于,所述输出单元还包括第二电容和第三电容,其中:

所述第二电容的一端连接所述第九晶体管的栅极,另一端连接所述第九晶体管的源极;

所述第三电容的一端连接所述第十二晶体管的栅极,另一端连接所述第十二晶体管的源极。

7. 如权利要求6所述的发射控制驱动电路,其特征在于,所述初始驱动控制器包括第六晶体管、第八晶体管和第十一晶体管,其中:

所述第六晶体管、所述第八晶体管和所述第十一晶体管为P型薄膜晶体管;

所述第六晶体管的栅极连接所述第五晶体管的漏极,并输出所述初始驱动信号;所述第六晶体管的源极连接所述第八晶体管的漏极,所述第六晶体管的漏极连接所述第七晶体管的源极;

所述第八晶体管的栅极连接所述第五晶体管的漏极,所述第八晶体管的源极连接所述第一电源,所述第八晶体管的漏极连接所述第九晶体管的源极;

所述第十一晶体管的源极连接所述第一电源,所述第十一晶体管的漏极输出所述发射控制信号。

8. 如权利要求1所述的发射控制驱动电路,其特征在于,所述第一时钟信号和所述第二时钟信号具有相同的时间段并且具有不重叠的相位,所述起始信号在所述第一时钟信号第一个下降沿电压来临时,输出下降沿电压并持续至所述第二时钟信号第一个下降沿电压来临。

9. 一种发射控制驱动器,其特征在于,所述发射控制驱动器包括多个如权利要求1~8任一项所述的发射控制驱动电路,每个所述发射控制驱动电路的初始驱动信号提供至下一级发射控制驱动电路的起始信号端。

10. 一种有机发光显示装置,其特征在于,所述有机发光显示装置包括多个如权利要求9所述的发射控制驱动器。

## 发射控制驱动电路、发射控制驱动器及有机发光显示装置

### 技术领域

[0001] 本发明涉及光电技术领域,特别涉及一种发射控制驱动电路、发射控制驱动器及有机发光显示装置。

### 背景技术

[0002] 近年,国内外开发出了众多类型的显示装置,例如液晶显示装置,等离子显示装置,电润湿显示装置,电泳显示装置,有机发光显示装置等。其中有机发光显示装置利用电子空穴对在特定材料中的复合,发出特定波长的光,来显示图像,具有快速响应,功耗低,轻薄,色域广等优点。

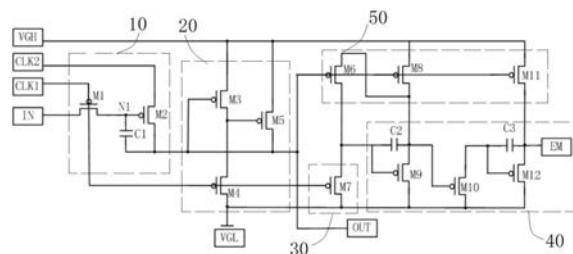

[0003] 如图1所示,有机发光显示装置包括:多个像素( $PX_{11}$ 、 $PX_{12}$ 、 $\cdots$ 、 $PX_{n1}$ 、 $PX_{n2}$ )形成的像素电路100,用于显示图像;数据驱动器300,将数据电压施加到像素;扫描驱动器200,将扫描信号顺序地施加到像素;发射控制驱动器400,将发射控制信号施加到像素;像素响应扫描信号而接收数据电压,像素产生具有与数据电压对应的预定亮度的光以显示图像。像素的发射时间段由发射控制信号控制。发射控制驱动器400响应于初始控制信号被初始化,并产生发射控制信号。

[0004] 一般来讲,不同的像素电路需要不同的驱动时序信号。比如2T1C像素电路,仅需要一个扫描驱动信号,而6T2C像素电路则需要两个扫描信号和一个发射控制信号,设计电路和控制方式非常复杂。

### 发明内容

[0005] 本发明的目的在于提供一种发射控制驱动电路、发射控制驱动器及有机发光显示装置,以解决现有的像素电路的发射控制电路和控制方式复杂的问题。

[0006] 为解决上述技术问题,本发明提供一种发射控制驱动电路,每个发射控制驱动电路构成一个级,多个级依次相连,所述发射控制驱动电路包括输入单元、第一栅控电路、第二栅控电路、输出单元和初始驱动控制器,其中:

[0007] 所述输入单元响应于第一时钟信号、第二时钟信号和起始信号,传输第一信号和第二信号中的任意一个;

[0008] 所述第一栅控电路通过第一信号或第二信号控制所述初始驱动控制器输出下一级发射控制驱动电路的初始驱动信号;

[0009] 所述第二栅控电路通过第一信号或第二信号控制所述输出单元输出发射控制信号。

[0010] 可选的,在所述的发射控制驱动电路中,所述输入单元包括第一晶体管、第二晶体管和第一电容,其中:

[0011] 所述第一晶体管和所述第二晶体管为P型薄膜晶体管;

[0012] 所述第一晶体管的栅极响应于所述第一时钟信号,所述第一晶体管的源极响应于所述起始信号,所述第一晶体管的漏极连接所述第二晶体管的栅极;

[0013] 所述第二晶体管的源极响应于所述第二时钟信号,所述第二晶体管的漏极连接所述第一栅控电路;

[0014] 所述第一电容的一端连接所述第二晶体管的栅极,另一端连接所述第二晶体管的漏极。

[0015] 可选的,在所述的发射控制驱动电路中,所述第一栅控电路包括第三晶体管、第四晶体管和第五晶体管,其中:

[0016] 所述第三晶体管、所述第四晶体管和所述第五晶体管为P型薄膜晶体管;

[0017] 所述第三晶体管的栅极连接所述第二晶体管的漏极,所述第三晶体管的源极连接第一电源,所述第三晶体管的漏极连接所述第四晶体管的源极;

[0018] 所述第四晶体管的栅极响应于所述第一时钟信号,所述第四晶体管的漏极连接第二电源;

[0019] 所述第五晶体管的栅极连接所述第三晶体管的漏极,所述第五晶体管的源极连接第一电源;所述第五晶体管的漏极连接所述第二晶体管的漏极。

[0020] 可选的,在所述的发射控制驱动电路中,所述第二栅控电路包括第七晶体管,其中:

[0021] 所述第七晶体管为P型薄膜晶体管;

[0022] 所述第七晶体管的栅极响应于所述第一时钟信号,所述第七晶体管的漏极连接第二电源。

[0023] 可选的,在所述的发射控制驱动电路中,所述输出单元包括第九晶体管、第十晶体管和第十二晶体管,其中:

[0024] 所述第九晶体管、所述第十晶体管和所述第十二晶体管为P型薄膜晶体管;

[0025] 所述第九晶体管的栅极连接所述第七晶体管的源极,所述第九晶体管的漏极连接所述第二电源;

[0026] 所述第十晶体管的栅极连接所述第九晶体管的源极,所述第十晶体管的源极连接所述第十二晶体管的栅极,所述第十晶体管的漏极连接所述第二电源;

[0027] 所述第十二晶体管的源极输出所述发射控制信号,所述第十二晶体管的漏极连接所述第二电源。

[0028] 可选的,在所述的发射控制驱动电路中,所述输出单元还包括第二电容和第三电容,其中:

[0029] 所述第二电容的一端连接所述第九晶体管的栅极,另一端连接所述第九晶体管的源极;

[0030] 所述第三电容的一端连接所述第十二晶体管的栅极,另一端连接所述第十二晶体管的源极。

[0031] 可选的,在所述的发射控制驱动电路中,所述初始驱动控制器包括第六晶体管、第八晶体管和第十一晶体管,其中:

[0032] 所述第六晶体管、所述第八晶体管和所述第十一晶体管为P型薄膜晶体管;

[0033] 所述第六晶体管的栅极连接所述第五晶体管的漏极,并输出所述初始驱动信号;所述第六晶体管的源极连接所述第八晶体管的漏极,所述第六晶体管的漏极连接所述第七晶体管的源极;

[0034] 所述第八晶体管的栅极连接所述第五晶体管的漏极,所述第八晶体管的源极连接所述第一电源,所述第八晶体管的漏极连接所述第九晶体管的源极;

[0035] 所述第十一晶体管的源极连接所述第一电源,所述第十一晶体管的漏极输出所述发射控制信号。

[0036] 可选的,在所述的发射控制驱动电路中,所述第一时钟信号和所述第二时钟信号具有相同的时间段并且具有不重叠的相位,所述起始信号在所述第一时钟信号第一个下降沿电压来临时,输出下降沿电压并持续至所述第二时钟信号第一个下降沿电压来临。

[0037] 本发明还提供发射控制驱动器,所述发射控制驱动器包括多个如上述任一项所述的发射控制驱动电路,每个所述发射控制驱动电路的初始驱动信号提供至下一级发射控制驱动电路的起始信号端。

[0038] 本发明还提供一种有机发光显示装置,所述有机发光显示装置包括多个如上所述的发射控制驱动器。

[0039] 在本发明提供的发射控制驱动电路、发射控制驱动器及有机发光显示装置中,只需要第一时钟信号、第二时钟信号和起始信号,以及十二个晶体管,即可实现发射控制信号的输出,以及整个发射控制驱动器的各级电路的运行,设计电路和控制方式简单。

## 附图说明

[0040] 图1是现有技术中有机发光显示装置示意图;

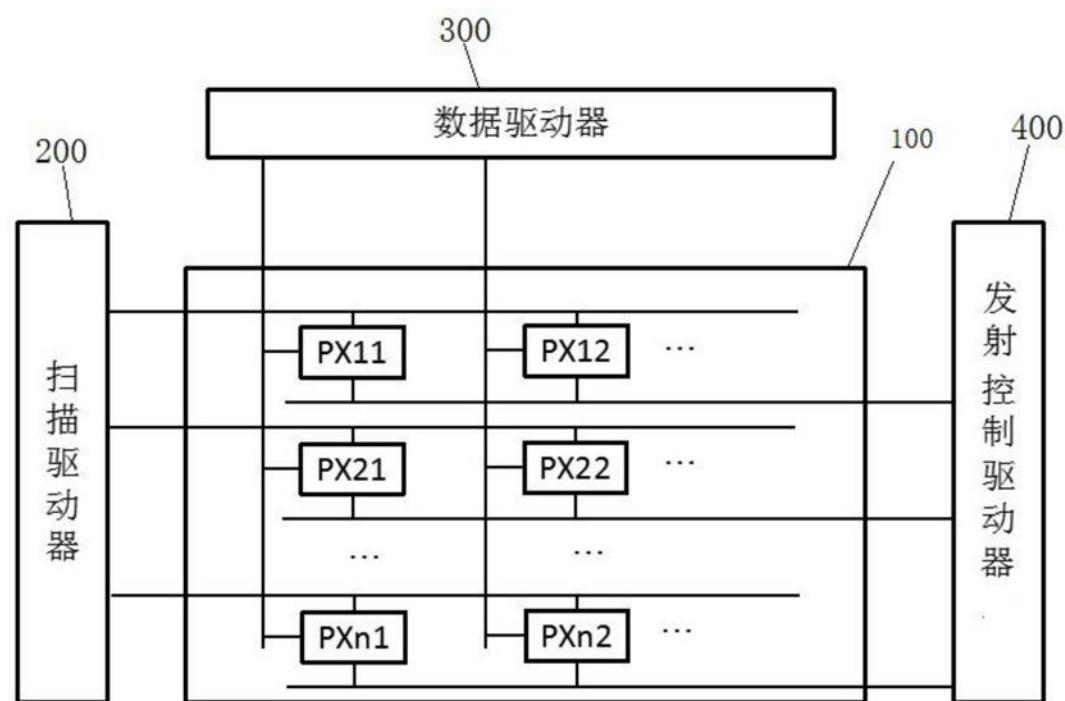

[0041] 图2是本发明一实施例多个发射控制驱动电路连接示意图;

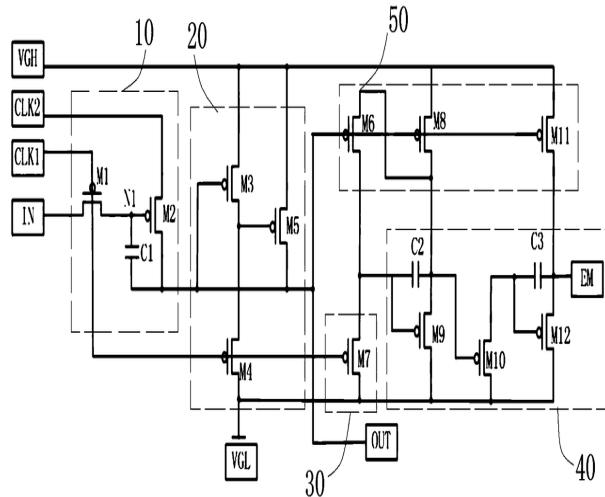

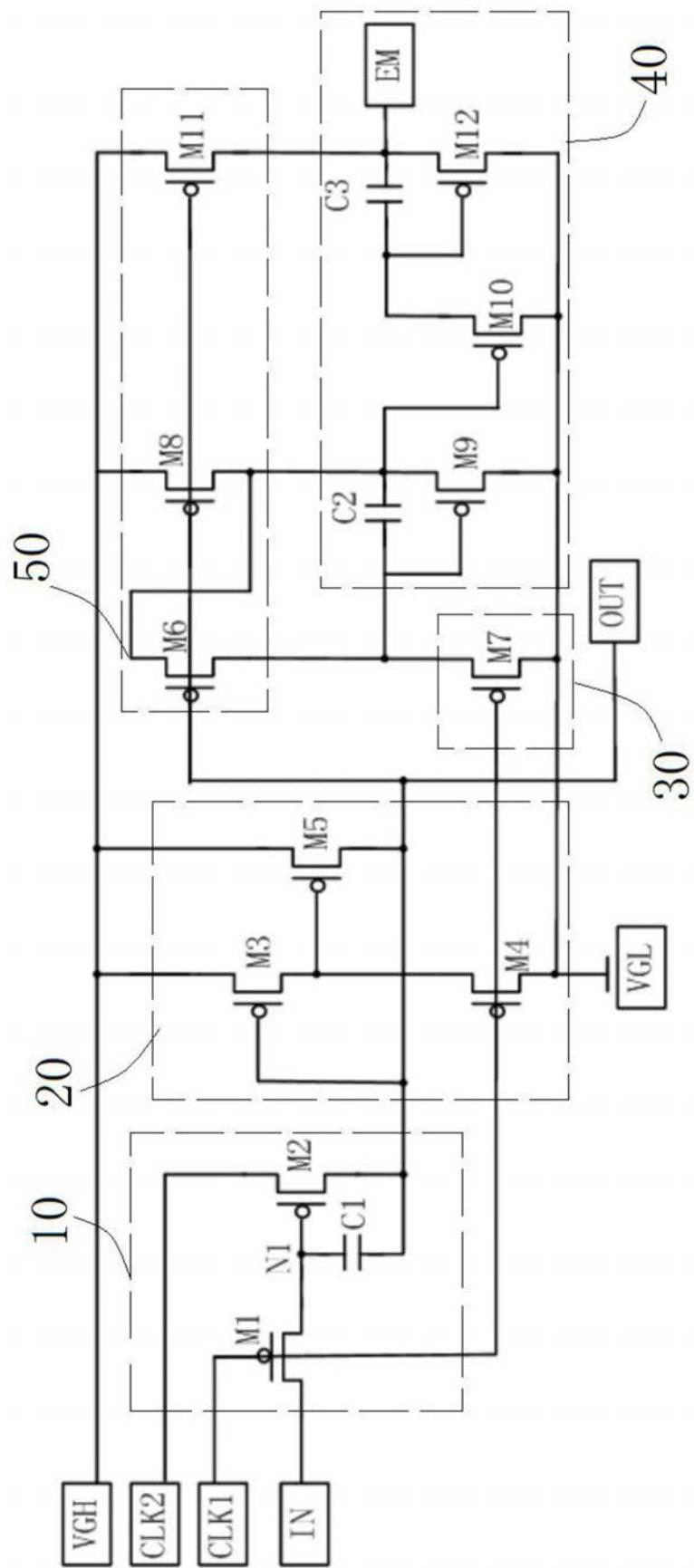

[0042] 图3是本发明一实施例发射控制驱动电路示意图;

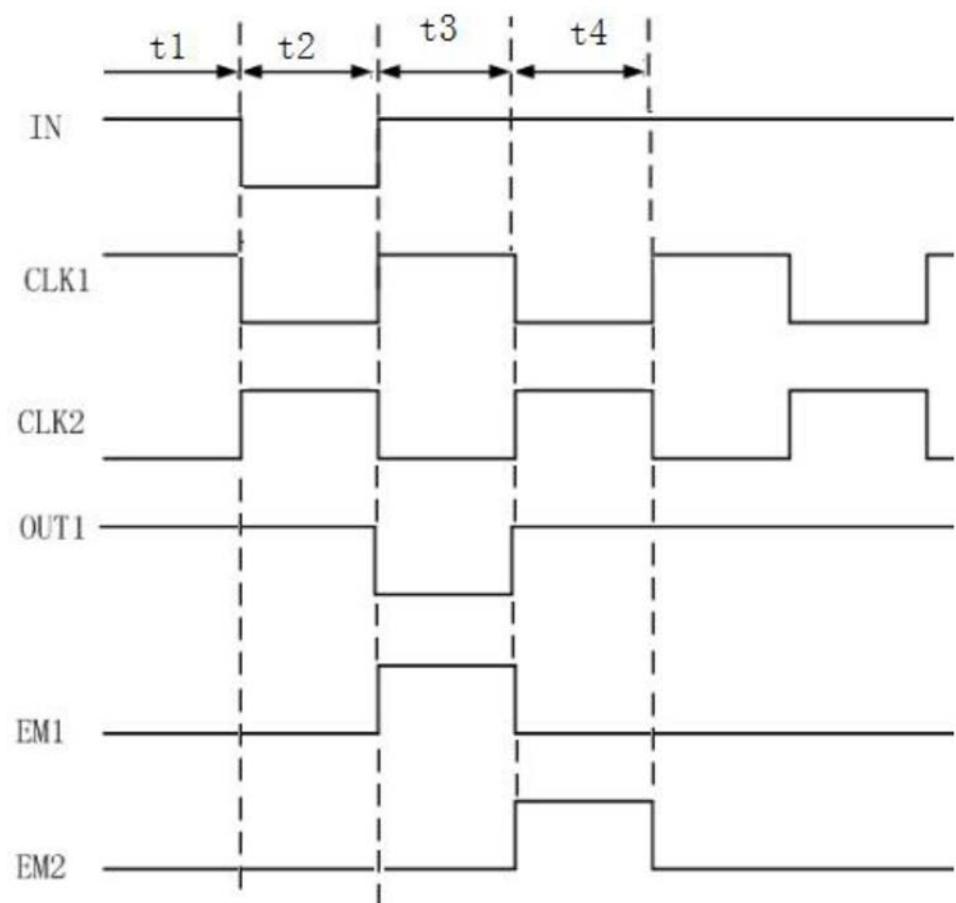

[0043] 图4是本发明一实施例发射控制驱动电路信号波形图;

[0044] 图中所示:1-第一个发射控制驱动电路(奇数发射控制驱动电路);2-第二个发射控制驱动电路(偶数发射控制驱动电路);10-输入单元;20-第一栅控电路;30-第二栅控电路;40-输出单元;50-初始驱动控制器;100-像素电路;200-扫描驱动器;300-数据驱动器;400-发射控制驱动电路。

## 具体实施方式

[0045] 以下结合附图和具体实施例对本发明提出的发射控制驱动电路、发射控制驱动器及有机发光显示装置作进一步详细说明。根据下面说明和权利要求书,本发明的优点和特征将更清楚。需说明的是,附图均采用非常简化的形式且均使用非精准的比例,仅用以方便、明晰地辅助说明本发明实施例的目的。

[0046] 本发明的核心思想在于提供一种发射控制驱动电路、发射控制驱动器及有机发光显示装置,以解决现有的像素电路的发射控制电路和控制方式复杂的问题。

[0047] 为实现上述思想,本发明提供了一种发射控制驱动电路、发射控制驱动器及有机发光显示装置,每个发射控制驱动电路构成一个级,多个级依次相连,如图2所示,第一个发射控制驱动电路1的输出端连接第二个发射控制驱动电路2,并按该结构依次连接后续的发射控制驱动电路,并最终形成图1中的发射控制驱动器400,第一个发射控制驱动电路1为奇数发射控制驱动电路,第二个发射控制驱动电路2为偶数发射控制驱动电路,图2中的每个所述发射控制驱动电路的详细电路结构图如图3所示,所述发射控制驱动电路包括输入单

元10、第一栅控电路20、第二栅控电路30、输出单元40和初始驱动控制器50，其中：所述输入单元10响应于第一时钟信号CLK1、第二时钟信号CLK2和起始信号IN，传输第一信号和第二信号中的任意一个；所述第一栅控电路20通过第一信号或第二信号控制所述初始驱动控制器50输出下一级发射控制驱动电路的初始驱动信号OUT；所述第二栅控电路30通过第一信号或第二信号控制所述输出单元40输出发射控制信号EM。

[0048] 具体的，在所述的发射控制驱动电路中，所述输入单元10包括第一晶体管M1、第二晶体管M2和第一电容C1，其中：所述第一晶体管M1和所述第二晶体管M2为P型薄膜晶体管；所述第一晶体管M1的栅极响应于所述第一时钟信号CLK1，所述第一晶体管M1的源极响应于所述起始信号IN，所述第一晶体管M1的漏极连接所述第二晶体管M2的栅极；所述第二晶体管M2的源极响应于所述第二时钟信号CLK2，所述第二晶体管M2的漏极连接所述第一栅控电路20；所述第一电容C1的一端连接所述第二晶体管M2的栅极，另一端连接所述第二晶体管M2的漏极。

[0049] 进一步的，在所述的发射控制驱动电路中，所述第一栅控电路20包括第三晶体管M3、第四晶体管M4和第五晶体管M5，其中：所述第三晶体管M3、所述第四晶体管M4和所述第五晶体管M5为P型薄膜晶体管；所述第三晶体管M3的栅极连接所述第二晶体管M2的漏极，所述第三晶体管M3的源极连接第一电源VGH，所述第三晶体管M3的漏极连接所述第四晶体管M4的源极；所述第四晶体管M4的栅极响应于所述第一时钟信号CLK1，所述第四晶体管M4的漏极连接第二电源VGL；所述第五晶体管M5的栅极连接所述第三晶体管M3的漏极，所述第五晶体管M5的源极连接第一电源VGH；所述第五晶体管M5的漏极连接所述第二晶体管M2的漏极。所述第二栅控电路30包括第七晶体管M7，其中：所述第七晶体管M7为P型薄膜晶体管；所述第七晶体管M7的栅极响应于所述第一时钟信号CLK1，所述第七晶体管M7的漏极连接第二电源VGL，所述第七晶体管M7的源极连接所述输出单元40中的第六晶体管。第一电源VGH的电平高于第二电源VGL的电平。

[0050] 如图3所示，在所述的发射控制驱动电路中，所述输出单元40包括第九晶体管M9、第十晶体管M10和第十二晶体管M12，其中：所述第九晶体管M9、所述第十晶体管M10和所述第十二晶体管M12为P型薄膜晶体管；所述第九晶体管M9的栅极连接所述第七晶体管M7的源极，所述第九晶体管M9的源极连接所述初始驱动控制器50中的第八晶体管，所述第九晶体管M9的漏极连接所述第二电源VGL；所述第十晶体管M10的栅极连接所述第九晶体管M9的源极，所述第十晶体管M10的源极连接所述第十二晶体管M12的栅极，所述第十晶体管M10的漏极连接所述第二电源VGL；所述第十二晶体管M12的源极输出所述发射控制信号EM，所述第十二晶体管M12的漏极连接所述第二电源VGL；所述输出单元40还包括第二电容C2和第三电容C3，其中：所述第二电容C2的一端连接所述第九晶体管M9的栅极，另一端连接所述第九晶体管M9的源极；所述第三电容C3的一端连接所述第十二晶体管M12的栅极，另一端连接所述第十二晶体管M12的源极。

[0051] 另外，在所述的发射控制驱动电路中，所述初始驱动控制器50包括第六晶体管M6、第八晶体管M8和第十一晶体管M11，其中：所述第六晶体管M6、所述第八晶体管M8和所述第十一晶体管M11为P型薄膜晶体管；所述第六晶体管M6的栅极连接所述第五晶体管M5的漏极，并输出所述初始驱动信号OUT；所述第六晶体管M6的源极连接所述第八晶体管M8的漏极，所述第六晶体管M6的漏极连接所述第七晶体管M7的源极；所述第八晶体管M8的栅极连

接所述第五晶体管M5的漏极,所述第八晶体管M8的源极连接所述第一电源VGH,所述第八晶体管M8的漏极连接所述第九晶体管M9的源极;所述第十一晶体管M11的源极连接所述第一电源VGH,所述第十一晶体管M11的漏极输出所述发射控制信号EM。

[0052] 如图2~4所示,在所述的发射控制驱动电路中,所述第一晶体管的源极接收前一发射控制驱动电路的输出信号,第二个发射控制驱动电路2的第一晶体管的源极连接到第一个发射控制驱动电路1的初始驱动信号OUT1端,接收第一个发射控制驱动电路1的初始驱动信号OUT1,初始驱动信号OUT1的波形如图4所示,第一个发射控制驱动电路1的第一晶体管的源极接收起始信号IN,起始信号IN的波形如图4所示,奇数发射控制驱动电路,例如第一个发射控制驱动电路1的所述第一晶体管的栅极接收第一时钟信号CLK1,奇数发射控制驱动电路,例如第一个发射控制驱动电路1的所述第二晶体管的源极接收第二时钟信号CLK2;偶数发射控制驱动电路,例如第二个发射控制驱动电路2的所述第一晶体管的栅极接收第二时钟信号CLK2,偶数发射控制驱动电路,例如第二个发射控制驱动电路2的所述第二晶体管的源极接收第一时钟信号CLK1,第一时钟信号CLK1和第二时钟信号CLK2的波形如图4所示。

[0053] 如图4所示,在所述的发射控制驱动电路中,所述第一时钟信号CLK1和所述第二时钟信号CLK2具有相同的时间段并且具有不重叠的相位,所述起始信号IN在所述第一时钟信号CLK1第一个下降沿电压来临时,输出下降沿电压并持续至所述第二时钟信号CLK2第一个下降沿电压来临。

[0054] 本实施例对第一个发射控制驱动电路的时序波形进行分析,如图4所示,起始信号IN和第一时钟信号CLK1在第一时间点t1具有高电平,第二时钟信号CLK2在第一时间段t1具有低电平。由于第一晶体管M1、第二晶体管M2、第四晶体管M4和第七晶体管M7皆为P型薄膜晶体管,第一晶体管、第二晶体管、第四晶体管和第七晶体管关断。

[0055] 在第二时间点t2,起始信号IN和第一时钟信号CLK1具有低电平,第二时钟信号CLK2具有高电平。第一晶体管、第二晶体管、第四晶体管和第七晶体管导通,且由于第一电容的电压保持效应,第二晶体管栅极和漏极之间的电压保持稳定,第四晶体管的导通使第五晶体管的栅极连接第二电源,第五晶体管导通,初始驱动信号端连接第一电源,输出高电平,第七晶体管的导通使第九晶体管的栅极连接第二电源,第九晶体管导通,进一步的使第十晶体管和第十二晶体管导通,发射控制信号输出低电平。

[0056] 在第三时间点t3,起始信号IN和第一时钟信号CLK1具有高电平,第二时钟信号CLK2具有低电平。由于第二晶体管保持导通,因此,此时第三晶体管的栅极响应于第二时钟信号,第三晶体管导通,第五晶体管关断,初始驱动信号直接耦合至第二时钟信号,输出低电平,而第四晶体管、第七晶体管、第九晶体管、第十晶体管和第十二晶体管关断,第六晶体管、第八晶体管和第十一晶体管导通,发射控制信号为高电平。

[0057] 在第四时间点t4,起始信号IN和第二时钟信号CLK2具有高电平,第一时钟信号CLK1具有低电平。由于第二晶体管保持导通,因此,此时第三晶体管的栅极响应于第二时钟信号,第三晶体管关断,初始驱动信号直接耦合至第二时钟信号,输出高电平,而第四晶体管(第五晶体管导通)、第七晶体管、第九晶体管、第十晶体管和第十二晶体管导通,第六晶体管、第八晶体管和第十一晶体管关断,发射控制信号为低电平。

[0058] 本实施例还提供发射控制驱动器,如图2所示,所述发射控制驱动器包括多个如上

述任一项所述的发射控制驱动电路,每个所述发射控制驱动电路的初始驱动信号OUT提供至下一级发射控制驱动电路的起始信号端IN。本实施例还提供一种有机发光显示装置,所述有机发光显示装置包括多个如上所述的发射控制驱动器。

[0059] 在本发明提供的发射控制驱动电路、发射控制驱动器及有机发光显示装置中,只需要第一时钟信号CLK1、第二时钟信号CLK2和起始信号IN,以及十二个晶体管,即可实现发射控制信号EM的输出,以及整个发射控制驱动器的各级电路的运行,设计电路和控制方式简单。

[0060] 综上,上述实施例对发射控制驱动电路、发射控制驱动器及有机发光显示装置的不同构型进行了详细说明,当然,本发明包括但不限于上述实施中所列举的构型,任何在上述实施例提供的构型基础上进行变换的内容,均属于本发明所保护的范围。本领域技术人员可以根据上述实施例的内容举一反三。

[0061] 上述描述仅是对本发明较佳实施例的描述,并非对本发明范围的任何限定,本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

图1

图2

图3

图4

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 发射控制驱动电路、发射控制驱动器及有机发光显示装置                      |         |            |

| 公开(公告)号        | <a href="#">CN108711399A</a>                   | 公开(公告)日 | 2018-10-26 |

| 申请号            | CN201810535429.9                               | 申请日     | 2018-05-29 |

| [标]申请(专利权)人(译) | 昆山国显光电有限公司                                     |         |            |

| 申请(专利权)人(译)    | 昆山国显光电有限公司                                     |         |            |

| 当前申请(专利权)人(译)  | 昆山国显光电有限公司                                     |         |            |

| [标]发明人         | 胡思明<br>黄秀颀<br>吴剑龙<br>韩珍珍<br>张露                 |         |            |

| 发明人            | 胡思明<br>黄秀颀<br>吴剑龙<br>韩珍珍<br>张露                 |         |            |

| IPC分类号         | G09G3/3225                                     |         |            |

| CPC分类号         | G09G3/3225                                     |         |            |

| 其他公开文献         | CN108711399B                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明提供了一种发射控制驱动电路、发射控制驱动器及有机发光显示装置，每个发射控制驱动电路构成一个级，多个级依次相连，所述发射控制驱动电路包括输入单元、第一栅控电路、第二栅控电路、输出单元和初始驱动控制器，其中：所述输入单元响应于第一时钟信号、第二时钟信号和起始信号，传输第一信号和第二信号中的任意一个；所述第一栅控电路通过第一信号或第二信号控制所述初始驱动控制器输出下一级发射控制驱动电路的初始驱动信号；所述第二栅控电路通过第一信号或第二信号控制所述输出单元输出发射控制信号。