(12)实用新型专利

(10)授权公告号 CN 207182881 U

(45)授权公告日 2018.04.03

(21)申请号 201721269903.5

(22)申请日 2017.09.29

(73)专利权人 京东方科技股份有限公司

地址 100015 北京市朝阳区酒仙桥路10号

(72)发明人 高雪岭

(74)专利代理机构 北京正理专利代理有限公司

11257

代理人 付生辉

(51)Int.Cl.

G09G 3/3233(2016.01)

G09G 3/3291(2016.01)

(ESM)同样的发明创造已同日申请发明专利

权利要求书4页 说明书10页 附图5页

(54)实用新型名称

像素驱动电路、阵列基板及显示装置

(57)摘要

本实用新型公开一种像素驱动电路，包括驱动晶体管、第一至第四开关元件、存储电容。通过不同控制信号控制上述开关元件的导通和关断来实现像素驱动电路的补偿功能，并实现OLED的发光电流仅与OLED的阈值电压和数据信号有关，而与驱动晶体管的阈值电压和背板电源压降无关，从而解决驱动晶体管阈值电压偏移和背板电源压降造成发光亮度不均的问题。本实用新型还公开一种阵列基板及显示装置。

1. 一种OLED的像素驱动电路,其特征在于,包括驱动晶体管、第一至第四开关元件、存储电容,其中

所述驱动晶体管的第二端与所述OLED的第一极连接,用于驱动OLED进行发光,所述OLED的第二极接收第二电源信号;

所述第一开关元件用于响应第一驱动开关信号而导通,以将第一电源信号传输至所述驱动晶体管的第一端;

所述第二开关元件用于响应第二驱动开关信号而导通,以将所述驱动晶体管的第一端通过所述存储电容与所述驱动晶体管的控制端连通;

所述第三开关元件用于响应写入开关信号而导通,以将所述驱动晶体管的第一端通过所述存储电容与所述驱动晶体管的第二端连通;

所述第四开关元件用于响应所述写入开关信号而导通,以将数据信号传输至所述驱动晶体管的控制端。

2. 根据权利要求1所述的像素驱动电路,其特征在于,所述第一至第四开关元件分别为第一至第四晶体管,其中

所述第一晶体管的控制端接收所述第一驱动开关信号,第一端接收所述第一电源信号,第二端与所述驱动晶体管的第一端和所述存储电容的第一端连接;

所述第二晶体管的控制端接收所述第二驱动开关信号,第一端与所述存储电容的第二端连接,第二端与所述驱动晶体管的控制端连接;

所述第三晶体管的控制端接收所述写入开关信号,第一端与所述存储电容的第二端连接,第二端与所述驱动晶体管的第二端连接;

所述第四晶体管的控制端接收所述写入开关信号,第一端接收所述数据信号,第二端与所述驱动晶体管的控制端连接。

3. 根据权利要求2所述的像素驱动电路,其特征在于,

所有所述晶体管均为P型薄膜晶体管,所有所述P型薄膜晶体管的第一端为源极,第二端为漏极,控制端为栅极;

所述OLED的第一极为阳极,第二极为阴极;并且

所述第一电源信号为高电平信号,所述第二电源信号为低电平信号,

或者

所有所述晶体管均为N型薄膜晶体管,所有所述N型薄膜晶体管的第一端为源极,第二端为漏极,控制端为栅极;

所述OLED的第一极为阴极,第二极为阳极;并且

所述第一电源信号为低电平信号,所述第二电源信号为高电平信号。

4. 根据权利要求1-3中任一项所述的像素驱动电路,其特征在于,所有所述开关元件和驱动晶体管均为低温多晶硅晶体管。

5. 根据权利要求1-3中任一项所述的像素驱动电路,其特征在于,所述驱动时序包括:

初始化阶段:利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第一开关元件、第三开关元件和第四开关元件并关断第二开关元件,利用数据信号关断驱动晶体管,并使驱动晶体管控制端和第一端之间形成固定电压偏置;

补偿阶段:利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第三开

关元件和第四开关元件并关断第一开关元件和第二开关元件,以将数据信号和驱动晶体管的阈值电压写入存储电容的第一端,并将OLED的阈值电压写入存储电容的第二端;

发光阶段:利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第一开关元件和第二开关元件并关断第三开关元件和第四开关元件,以通过存储电容中的电压信号导通所述驱动晶体管,使第一电源信号驱动OLED发光。

6.根据权利要求5所述的像素驱动电路,其特征在于,在所有所述开关元件和驱动晶体管为P型薄膜晶体管的情况下,

所述初始化阶段中,所述写入开关信号和第一驱动开关信号为低电平信号,所述第二驱动开关信号为高电平信号,所述数据信号为第一数据信号;

所述补偿阶段中,所述写入开关信号为低电平信号,所述第一驱动开关信号和第二驱动开关信号为高电平信号,所述数据信号为第二数据信号;

所述发光阶段中,所述写入开关信号为高电平信号,所述第一驱动开关信号、第二驱动开关信号和数据信号为低电平信号;

其中,所述第一数据信号的电压值高于所述第二数据信号的电压值。

7.一种OLED的像素驱动电路,其特征在于,包括驱动晶体管、第一至第五开关元件、存储电容,其中

所述驱动晶体管的第二端与所述OLED的第一极连接,用于驱动OLED进行发光,所述OLED的第二极接收第二电源信号;

所述第一开关元件用于响应第一驱动开关信号而导通,以将第一电源信号传输至所述驱动晶体管的第一端;

所述第二开关元件用于响应第一驱动开关信号而导通,所述第五开关元件用于响应第二驱动开关信号而导通,以将所述驱动晶体管的第一端通过所述存储电容与所述驱动晶体管的控制端连通;

所述第三开关元件用于响应写入开关信号而导通,以将所述驱动晶体管的第一端通过所述存储电容与所述驱动晶体管的第二端连通;

所述第四开关元件用于响应所述写入开关信号而导通,以将数据信号传输至所述驱动晶体管的控制端。

8.根据权利要求7所述的像素驱动电路,其特征在于,所述第一至第五开关元件分别为第一至第五晶体管,其中

所述第一晶体管的控制端接收所述第一驱动开关信号,第一端接收所述第一电源信号,第二端与所述驱动晶体管的第一端和所述存储电容的第一端连接;

所述第二晶体管的控制端接收所述第一驱动开关信号,第一端与所述存储电容的第二端连接,第二端与所述第五晶体管的第一端连接;

所述第三晶体管的控制端接收所述写入开关信号,第一端与所述存储电容的第二端连接,第二端与所述驱动晶体管的第二端连接;

所述第四晶体管的控制端接收所述写入开关信号,第一端接收所述数据信号,第二端与所述驱动晶体管的控制端连接;

所述第五晶体管的控制端接收所述第二驱动开关信号,第二端与所述驱动晶体管的控制端连接。

9. 根据权利要求8所述的像素驱动电路,其特征在于,

所有所述晶体管均为P型薄膜晶体管,所有所述P型薄膜晶体管的第一端为源极,第二端为漏极,控制端为栅极;

所述OLED的第一极为阳极,第二极为阴极;并且

所述第一电源信号为高电平信号,所述第二电源信号为低电平信号,

或者

所有所述晶体管均为N型薄膜晶体管,所有所述N型薄膜晶体管的第一端为源极,第二端为漏极,控制端为栅极;

所述OLED的第一极为阴极,第二极为阳极;并且

所述第一电源信号为低电平信号,所述第二电源信号为高电平信号。

10. 根据权利要求7-9中任一项所述的像素驱动电路,其特征在于,所有所述开关元件和驱动晶体管均为低温多晶硅晶体管。

11. 根据权利要求7-9中任一项所述的像素驱动电路,其特征在于,所述驱动时序包括:

初始化阶段:利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第一开关元件、第三开关元件和第四开关元件并关断第二开关元件和第五开关元件,利用将数据信号关断驱动晶体管,并使驱动晶体管控制端和第一端之间形成固定电压偏置;

补偿阶段:利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第三开关元件和第四开关元件并关断第一开关元件、第二开关元件和第五开关元件,以将数据信号和驱动晶体管的阈值电压写入存储电容的第一端,并将OLED的阈值电压写入存储电容的第二端;

预发光阶段:利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第三开关元件、第四开关元件和第五开关元件并关断第一开关元件和第二开关元件,以延长写入时间;

发光阶段:利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第一开关元件、第二开关元件和第五开关元件并关断第三开关元件和第四开关元件,以通过存储电容中的电压信号导通所述驱动晶体管,使第一电源信号驱动OLED发光。

12. 根据权利要求11所述的像素驱动电路,其特征在于,在所有所述开关元件和驱动晶体管均为P型薄膜晶体管的情况下,

所述初始化阶段中,所述写入开关信号和第一驱动开关信号为低电平信号,所述第二驱动开关信号为高电平信号,所述数据信号为第一数据信号;

所述补偿阶段中,所述写入开关信号为低电平信号,所述第一驱动开关信号和第二驱动开关信号为高电平信号,所述数据信号为第二数据信号;

所述预发光阶段中,所述写入开关信号和第二驱动开关信号为低电平信号,所述第一驱动开关信号为高电平信号,所述数据信号为第二数据信号;

所述发光阶段中,所述写入开关信号为高电平信号,所述第一驱动开关信号、第二驱动开关信号和数据信号为低电平信号;

其中,所述第一数据信号的电压值高于所述第二数据信号的电压值。

13. 一种阵列基板,其特征在于,包括如权利要求1-12中任意一项所述的像素驱动电路。

14. 一种显示装置,其特征在于,包括如权利要求13所述的阵列基板。

## 像素驱动电路、阵列基板及显示装置

### 技术领域

[0001] 本实用新型涉及有机发光二极管显示技术领域。更具体地，涉及一种OLED像素驱动电路、阵列基板及显示装置。

### 背景技术

[0002] 有机发光二极管(Organic Light Emitting Diode,OLED)显示技术是指有机发光材料在电流驱动下，通过载流子注入和复合导致发光的技术。OLED发光原理是用ITO电极和金属电极分别作为器件的第一极和第二极，在一定的电流驱动下，电子和空穴分别从第二极和第一极注入到电子和空穴传输层，电子和空穴分别经过电子和空穴传输层迁移到发光层，在有发光特性的有机物质内复合，形成处于激发态的激子并使发光分子激发，激发的发光分子经过辐射弛豫而发出可见光。OLED根据其驱动方式分为无源OLED(Passive Matrix OLED,PMOLED)和有源OLED(Active Matrix OLED,AMOLED)，其中AMOLED显示技术是一种应用于电视和移动设备的显示技术，以其低功耗、大尺寸的特点在对功耗敏感的便携电子设备中有着广阔的应用前景。

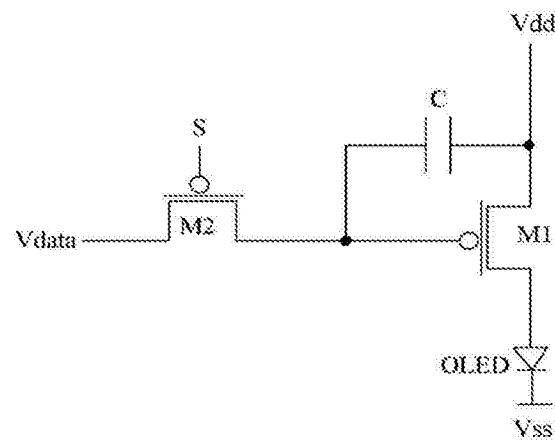

[0003] 如图1所示，传统的AMOLED像素驱动电路包括OLED元件、驱动晶体管M1、开关晶体管M2和电容器C。其中电容器C的一端连接电源电压Vdd和驱动晶体管M1的源极，另一端连接开关晶体管M2的漏极和驱动晶体管的栅极，用于存储驱动晶体管M1的阈值电压。开关晶体管M2的栅极连接扫描线S，源极连接数据电压Vdata，漏极连接驱动晶体管M1的栅极。开关晶体管M2的通断由扫描线S控制，进而控制数据电压Vdata的输入，驱动晶体管M1的源极连接电源电压Vdd，漏极连接OLED的阳极，OLED的阴极连接参考电压Vss。数据电压Vdata通过开关晶体管M2供应到驱动晶体管M1的栅极，以控制驱动晶体管M1的通断和电流的大小，进而控制OLED的发光及强弱。OLED发光时流经OLED的电流I<sub>OLED</sub>为驱动晶体管M1对应于栅源电压Vgs的电流，电流I<sub>OLED</sub>可表示为：

$$I_{OLED} = k (V_{gs} - V_{th})^2 = k (V_{dd} - V_{data} - |V_{th}|)^2,$$

[0005] 其中，k表示常数。

[0006] 从上式中可以看出，在上述OLED像素驱动电路中，电流I<sub>OLED</sub>取决于驱动晶体管M1的阈值电压V<sub>th</sub>和电源电压V<sub>dd</sub>。不可避免地，晶体管阈值电压偏移和背板电源压降将造成OLED发光亮度不均的问题。

[0007] 目前，由于低温多晶硅薄膜晶体管(LTPS TFT)具有更高的迁移率和更稳定的特性，所以AMOLED中多采用LTPS TFT构建像素电路，为OLED器件提供相应的电流。但同时由于晶化工艺的局限性，在大面积玻璃基板上制作的LTPS TFT常常在诸如阈值电压、迁移率等电学参数上具有非均匀性，这种非均匀性会转化为OLED显示器件的电流差异和亮度差异，并被人眼所感知，即云纹现象(mura)。另外，在大尺寸显示应用中，由于背板电源线存在一定电阻，且所有像素的驱动电流都由ELVDD提供，因此在背板中靠近ELVDD电源供电位置区域的电源电压相比较离供电位置较远区域的电源电压要高，这种现象被称为电阻压降(IR Drop)，由于ELVDD的电压与电流相关，IR Drop也会造成不同区域的电流差异，进而影响显

示效果。

[0008] 现有的OLED像素驱动电路中的补偿技术大多针对阈值电压偏移这一问题,而忽视了随着OLED尺寸大型化的趋势,信号线的负载也会越来越大,致使信号线上会出现电压的衰减,从而影响显示区域电流均匀性。因此,需要一种OLED的像素驱动电路、阵列基板及显示装置。

## 发明内容

[0009] 为了解决OLED的发光电流受驱动晶体管的阈值电压和背板电源压降影响而产生发光亮度不均的问题,本实用新型第一方面提供一种OLED的像素驱动电路,包括驱动晶体管、第一至第四开关元件和存储电容。

[0010] 在上述像素驱动电路中,驱动晶体管的第二端与OLED的第一极连接,用于驱动OLED进行发光,OLED的第二极接收第二电源信号;第一开关元件用于响应第一驱动开关信号而导通,以将第一电源信号传输至驱动晶体管的第一端;第二开关元件用于响应第二驱动开关信号而导通,以将驱动晶体管的第一端通过存储电容与驱动晶体管的控制端连通;第三开关元件用于响应写入开关信号而导通,以将驱动晶体管的第一端通过存储电容与驱动晶体管的第二端连通;第四开关元件用于响应写入开关信号而导通,以将数据信号传输至驱动晶体管的控制端。

[0011] 本实用新型的第一方面通过不同控制信号控制上述开关元件的导通和关断来实现像素驱动电路的补偿功能,并实现OLED的发光电流仅与OLED的阈值电压和数据信号有关,而与驱动晶体管的阈值电压和背板电源压降无关,从而解决驱动晶体管阈值电压偏移和背板电源压降造成的发光亮度不均的问题。

[0012] 在一个优选实施例中,第一至第四开关元件分别为第一至第四晶体管,其中第一晶体管的控制端接收第一驱动开关信号,第一端接收第一电源信号,第二端与驱动晶体管的第一端和存储电容的第一端连接;第二晶体管的控制端接收第二驱动开关信号,第一端与存储电容的第二端连接,第二端与驱动晶体管的控制端连接;第三晶体管的控制端接收写入开关信号,第一端与存储电容的第二端连接,第二端与驱动晶体管的第二端连接;第四晶体管的控制端接收写入开关信号,第一端接收数据信号,第二端与驱动晶体管的控制端连接。

[0013] 在该实施例中,通过引入第一和第二驱动开关信号分别对第一和第二晶体管的导通和关断进行控制,使得电路结构随驱动开关信号的高低电平变化而改变。同时,写入开关信号控制数据信号的写入过程,将数据信号和驱动晶体管的阈值电压写入存储电容的第一端并将OLED的阈值电压写入存储电容的第二端,完成存储电容两端电压的写入,实现OLED的发光电流仅与OLED的阈值电压和数据信号有关,从而解决驱动晶体管阈值电压偏移和背板电源压降造成的发光亮度不均的问题。

[0014] 在又一个优选实施例中,所有晶体管均为P型薄膜晶体管,所有P型薄膜晶体管的第一端为源极,第二端为漏极,控制端为栅极;OLED的第一极为阳极,第二极为阴极;并且第一电源信号为高电平信号,第二电源信号为低电平信号。或者,所有晶体管均为N型薄膜晶体管,所有N型薄膜晶体管的第一端为源极,第二端为漏极,控制端为栅极;OLED的第一极为阴极,第二极为阳极;并且第一电源信号为低电平信号,第二电源信号为高电平信号。

[0015] 在上述实施例中，晶体管可以为P型薄膜晶体管或N型薄膜晶体管。对应地，电路中OLED的电流流向及电源信号的高低电平随着采用不同导电类型的薄膜晶体管作为电路的开关元件的不同而改变。

[0016] 在又一个优选实施例中，所有开关元件和驱动晶体管均为低温多晶硅晶体管。

[0017] 在该实施例中，采用低温多晶硅晶体管降低了制造成本和产品功耗，具有更快的电子迁移率和更小的薄膜电路面积，提高了显示的分辨率和稳定性。

[0018] 在又一个优选实施例中，驱动时序包括：

[0019] 初始化阶段：利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第一开关元件、第三开关元件和第四开关元件并关断第二开关元件，利用数据信号关断驱动晶体管，并使驱动晶体管控制端和第一端之间形成固定电压偏置；

[0020] 补偿阶段：利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第三开关元件和第四开关元件并关断第一开关元件和第二开关元件，以将数据信号和驱动晶体管的阈值电压写入存储电容的第一端，并将OLED的阈值电压写入存储电容的第二端；

[0021] 发光阶段：利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第一开关元件和第二开关元件并关断第三开关元件和第四开关元件，以通过存储电容中的电压信号导通驱动晶体管，使第一电源信号驱动OLED发光。

[0022] 本实施例中通过第一驱动开关信号、第二驱动开关信号以及写入开关信号对电路中各开关元件，完成不同阶段电路的控制。具体地，在初始化阶段通过调整数据信号，在驱动晶体管控制端和第一端之间形成固定电压偏置，改善OLED的短期残像问题；在补偿阶段，将数据信号和驱动晶体管的阈值电压写入存储电容的第一端并将OLED的阈值电压写入存储电容的第二端，完成存储电容两端电压的写入，实现OLED的发光电流仅与OLED的阈值电压和数据信号有关；在发光阶段，通过存储电容中的电压信号导通驱动晶体管，使第一电源信号驱动OLED发光，从而解决驱动晶体管阈值电压偏移和背板电源压降造成发光亮度不均的问题。

[0023] 在一个优选实施例中，当所有开关元件和驱动晶体管均为P型薄膜晶体管的情况下，各控制信号具有如下电平关系：初始化阶段中，写入开关信号和第一驱动开关信号为低电平信号，第二驱动开关信号为高电平信号，数据信号为第一数据信号；补偿阶段中，写入开关信号为低电平信号，第一驱动开关信号和第二驱动开关信号为高电平信号，数据信号为第二数据信号，其中，第一数据信号的电压值高于第二数据信号的电压值；发光阶段中，写入开关信号为高电平信号，第一驱动开关信号、第二驱动开关信号和数据信号为低电平信号。

[0024] 本实用新型第二方面提供一种OLED的像素驱动电路，包括驱动晶体管、第一至第五开关元件、存储电容。

[0025] 在上述像素驱动电路中，驱动晶体管的第二端与OLED的第一极连接，用于驱动OLED进行发光，OLED的第二极接收第二电源信号；第一开关元件用于响应第一驱动开关信号而导通，以将第一电源信号传输至驱动晶体管的第一端；第二开关元件用于响应第一驱动开关信号而导通，第五开关元件用于响应第二驱动开关信号而导通，以将驱动晶体管的第一端通过存储电容与驱动晶体管的控制端连通；第三开关元件用于响应写入开关信号而导通，以将驱动晶体管的第一端通过存储电容与驱动晶体管的第二端连通；第四开关元件

用于响应写入开关信号而导通，以将数据信号传输至驱动晶体管的控制端。

[0026] 本实用新型的第二方面通过不同控制信号控制上述开关元件的导通和关断来实现像素驱动电路的补偿功能，并实现OLED的发光电流仅与OLED的阈值电压和数据信号有关，而与驱动晶体管的阈值电压和背板电源压降无关，从而解决驱动晶体管阈值电压偏移和背板电源压降造成的发光亮度不均的问题。进一步地，上述控制信号中，第一驱动开关信号和第二驱动开关信号相差一个时序周期，即上述第二驱动开关信号可由第一驱动开关信号经移位寄存处理得到，减少了控制信号的个数，降低了电路的控制复杂度。

[0027] 在一个优选实施例中，第一至第五开关元件分别为第一至第五晶体管，其中第一晶体管的控制端接收第一驱动开关信号，第一端接收第一电源信号，第二端与驱动晶体管的第一端和存储电容的第一端连接；第二晶体管的控制端接收第一驱动开关信号，第一端与存储电容的第二端连接，第二端与第五晶体管的第一端连接；第三晶体管的控制端接收写入开关信号，第一端与存储电容的第二端连接，第二端与驱动晶体管的第二端连接；第四晶体管的控制端接收写入开关信号，第一端接收数据信号，第二端与驱动晶体管的控制端连接；第五晶体管的控制端接收第二驱动开关信号，第二端与驱动晶体管的控制端连接。

[0028] 在该实施例中，通过引入第一和第二驱动开关信号分别对第一和第二晶体管的导通和关断进行控制，使得电路结构随驱动开关信号的高低电平变化而改变，第二驱动开关信号可由第一驱动开关信号处理得到。同时，写入开关信号控制数据信号的写入过程，将数据信号和驱动晶体管的阈值电压写入存储电容的第一端并将OLED的阈值电压写入存储电容的第二端，完成存储电容两端电压的写入，实现OLED的发光电流仅与OLED的阈值电压和数据信号有关，从而解决驱动晶体管阈值电压偏移和背板电源压降造成的发光亮度不均的问题。

[0029] 在又一个优选实施例中，所有晶体管均为P型薄膜晶体管，所有P型薄膜晶体管的第一端为源极，第二端为漏极，控制端为栅极；OLED的第一极为阳极，第二极为阴极；并且第一电源信号为高电平信号，第二电源信号为低电平信号。或者，所有晶体管均为N型薄膜晶体管，所有N型薄膜晶体管的第一端为源极，第二端为漏极，控制端为栅极；OLED的第一极为阴极，第二极为阳极；并且第一电源信号为低电平信号，第二电源信号为高电平信号。

[0030] 在上述实施例中，晶体管可以为P型薄膜晶体管或N型薄膜晶体管。对应地，电路中OLED的电流流向及电源信号的高低电平随着采用不同导电类型的薄膜晶体管作为电路的开关元件的不同而改变。

[0031] 在又一个优选实施例中，所有开关元件和驱动晶体管均为低温多晶硅晶体管。

[0032] 在该实施例中，采用低温多晶硅晶体管降低了制造成本和产品功耗，具有更快的电子迁移率和更小的薄膜电路面积，提高了显示的分辨率和稳定性。

[0033] 在又一个优选实施例中，驱动时序包括：

[0034] 初始化阶段：利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第一开关元件、第三开关元件和第四开关元件并关断第二开关元件和第五开关元件，利用数据信号关断驱动晶体管，并使驱动晶体管控制端和第一端之间形成固定电压偏置；

[0035] 补偿阶段：利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第三开关元件和第四开关元件并关断第一开关元件、第二开关元件和第五开关元件，以将数据信号和驱动晶体管的阈值电压写入存储电容的第一端，并将OLED的阈值电压写入存储电

容的第二端；

[0036] 预发光阶段：利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第三开关元件、第四开关元件和第五开关元件并关断第一开关元件和第二开关元件，以延长写入时间；

[0037] 发光阶段：利用第一驱动开关信号、第二驱动开关信号以及写入开关信号导通第一开关元件、第二开关元件和第五开关元件并关断第三开关元件和第四开关元件，以通过存储电容中的电压信号导通驱动晶体管，使第一电源信号驱动OLED发光。

[0038] 本实施例中通过第一驱动开关信号、第二驱动开关信号以及写入开关信号对电路中各开关元件，完成不同阶段电路的控制。具体地，在初始化阶段通过调整数据信号，在驱动晶体管控制端和第一端之间形成固定电压偏置，改善OLED的短期残像问题；在补偿阶段，将数据信号和驱动晶体管的阈值电压写入存储电容的第一端并将OLED的阈值电压写入存储电容的第二端，完成存储电容两端电压的写入，实现OLED的发光电流仅与OLED的阈值电压和数据信号有关；在预发光阶段，延长写入时间，获得更好的写入效果；在发光阶段，通过存储电容中的电压信号导通驱动晶体管，使第一电源信号驱动OLED发光，从而解决驱动晶体管阈值电压偏移和背板电源压降造成的发光亮度不均的问题。

[0039] 在一个优选实施例中，当所有开关元件和驱动晶体管均为P型薄膜晶体管的情况下，各控制信号具有如下电平关系：初始化阶段中，写入开关信号和第一驱动开关信号为低电平信号，第二驱动开关信号为高电平信号，数据信号为第一数据信号；补偿阶段中，写入开关信号为低电平信号，第一驱动开关信号和第二驱动开关信号为高电平信号，数据信号为第二数据信号，其中，第一数据信号的电压值高于第二数据信号的电压值；预发光阶段中，写入开关信号和第二驱动开关信号为低电平信号，第一驱动开关信号为高电平信号，数据信号为第二数据信号；发光阶段中，写入开关信号为高电平信号，第一驱动开关信号、第二驱动开关信号和数据信号为低电平信号。

[0040] 本实用新型的第三方面提供一种阵列基板，包括第一方面或第二方面的像素驱动电路。由于包含第一方面或第二方面的像素驱动电路，故该阵列基板自然具有像素驱动电路带来的有益效果。

[0041] 本实用新型的第四方面提供一种显示装置，包括第三方面的阵列基板。由于包含第三方面的阵列基板，故该显示装置自然具有阵列基板带来的有益效果。

## 附图说明

[0042] 下面结合附图对本实用新型的具体实施方式作进一步详细的说明。

[0043] 图1示出传统的OLED像素驱动电路的结构示意图。

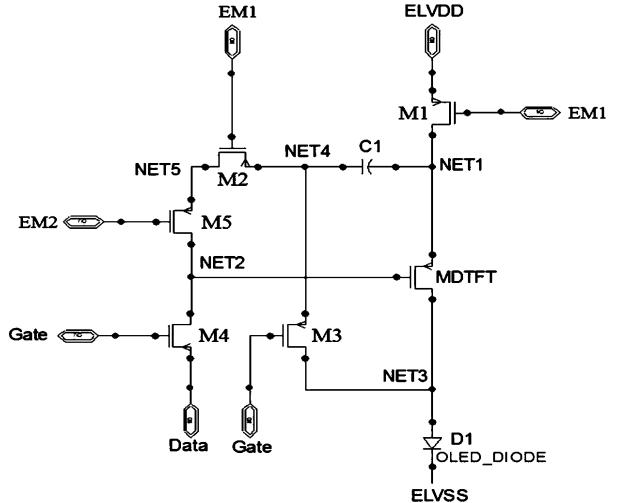

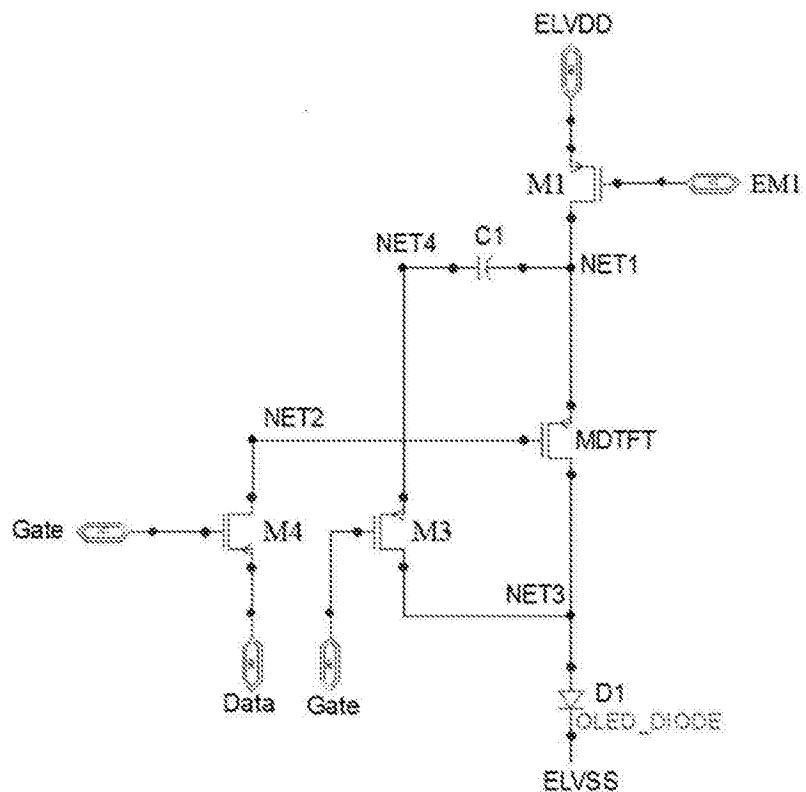

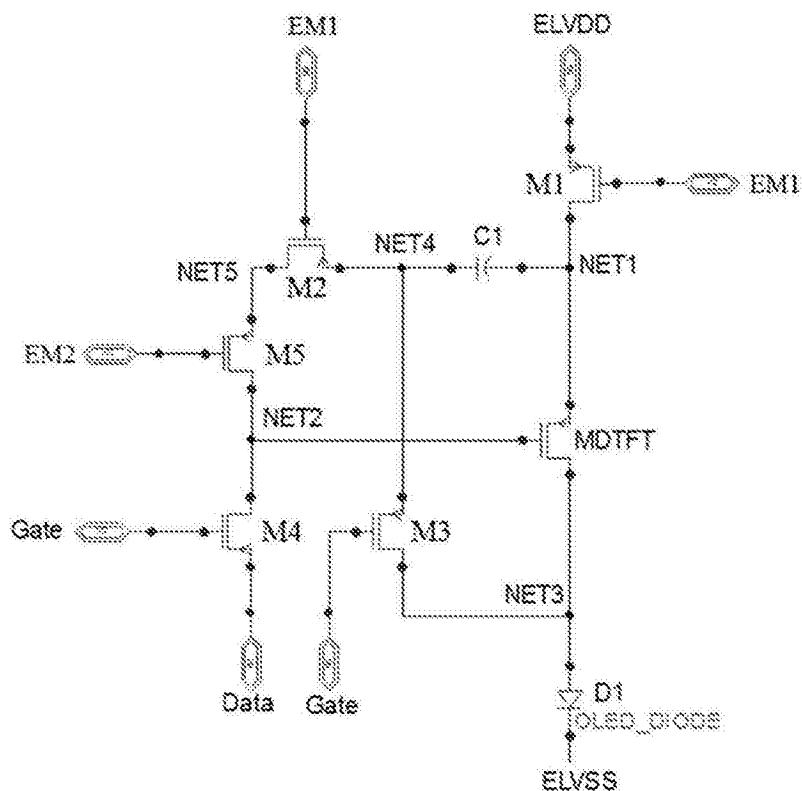

[0044] 图2示出实施例1中OLED像素驱动电路的结构示意图。

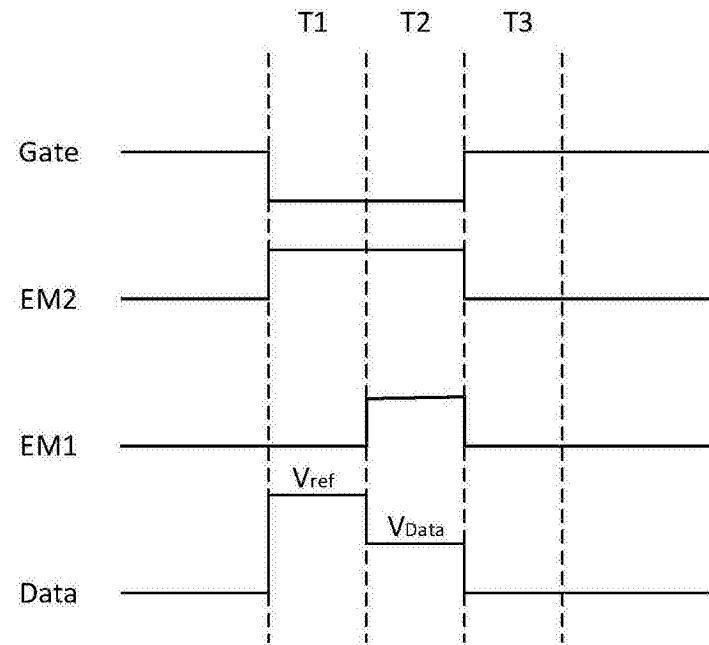

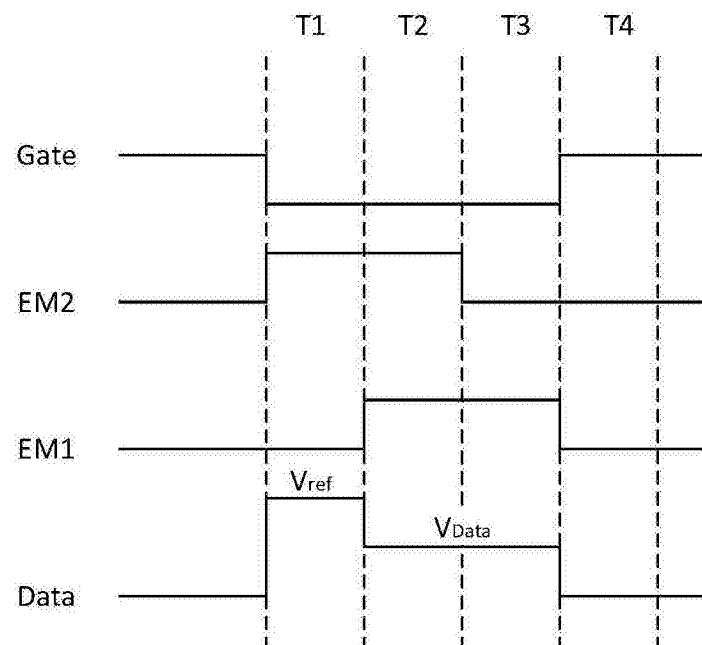

[0045] 图3示出实施例1中信号的时序关系图。

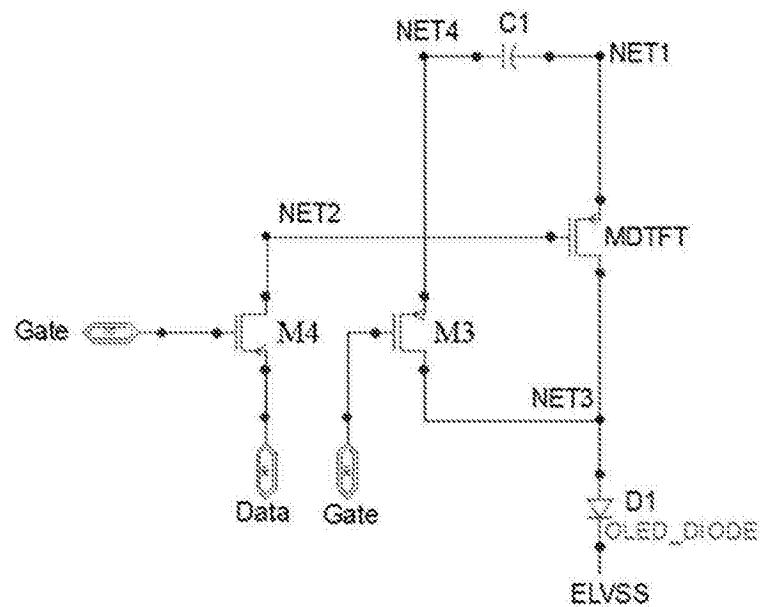

[0046] 图4示出实施例1中OLED像素驱动电路的初始化阶段结构示意图。

[0047] 图5示出实施例1中OLED像素驱动电路的补偿阶段结构示意图。

[0048] 图6示出实施例1中OLED像素驱动电路的发光阶段结构示意图。

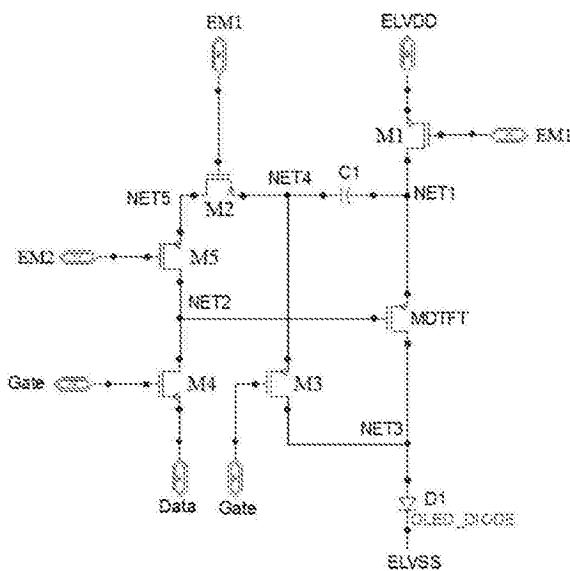

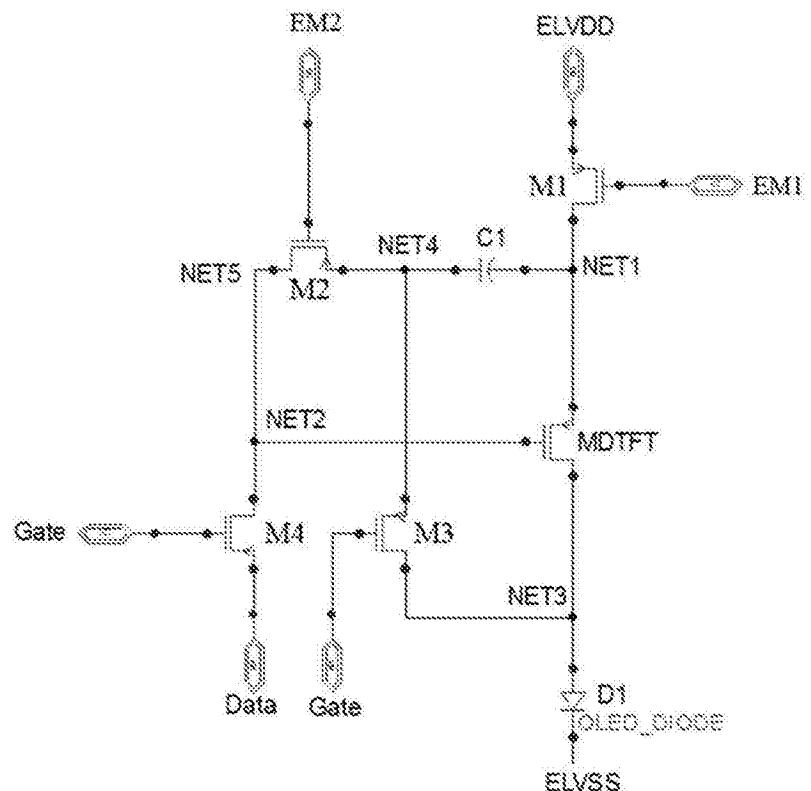

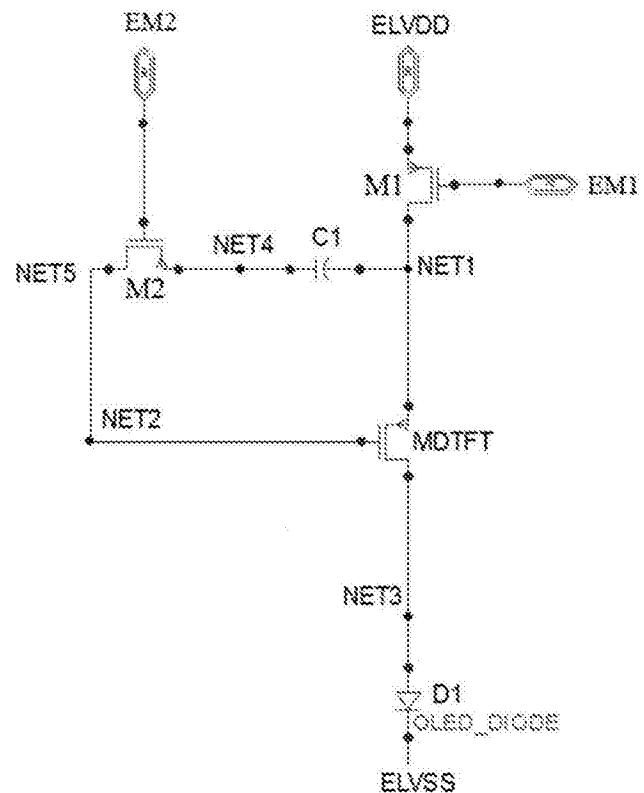

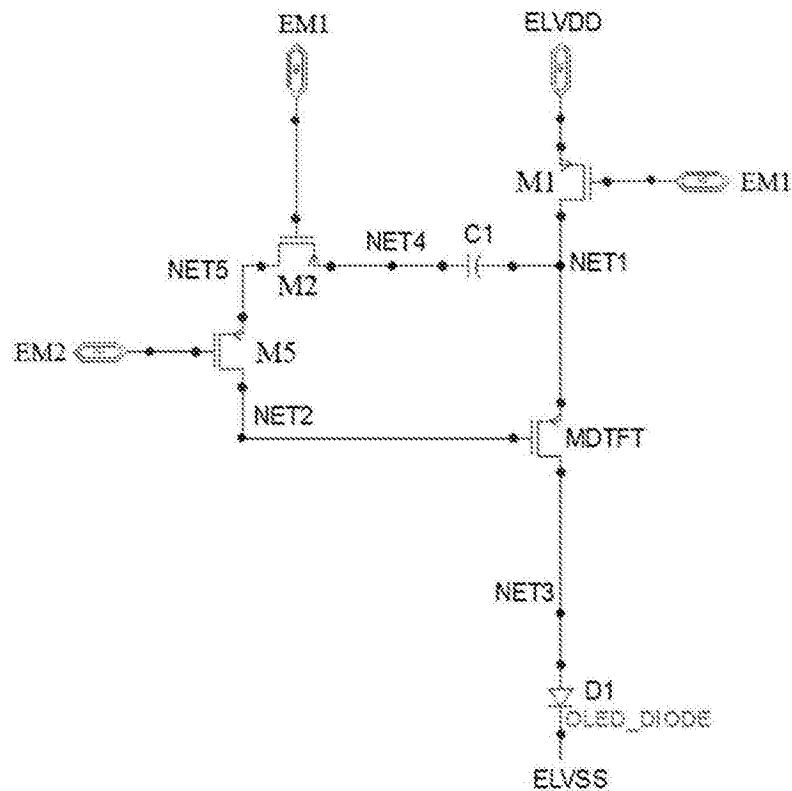

[0049] 图7示出实施例2中OLED像素驱动电路的结构示意图。

[0050] 图8示出实施例2中信号的时序关系图。

[0051] 图9示出实施例2中OLED像素驱动电路的发光阶段结构示意图。

### 具体实施方式

[0052] 为了更清楚地说明本实用新型，下面结合优选实施例和附图对本实用新型做进一步的详细说明。在下面的详细描述中，阐述了许多具体的细节以提供对本公开的实施例的全面理解。然而，本领域技术人员应当理解，一个或多个实施例在没有具体细节的情况下也可以被实施。在其他情况下，公知的结构和装置以图示的方式体现以简化附图。应注意，措辞“包括”不排除其它元件或步骤，措辞“一”或“一个”不排除多个。

[0053] 本实用新型中，通过不同控制信号控制多个开关元件的导通和关断来实现像素驱动电路的补偿功能，并实现OLED的发光电流仅与OLED的阈值电压和数据信号有关，而与驱动晶体管的阈值电压和背板电源压降无关，从而解决驱动晶体管阈值电压偏移和背板电源压降造成发光亮度不均的问题。

[0054] 实施例1

[0055] 如图2所示，一种OLED的像素驱动电路，包括驱动晶体管MDTFT、第一至第四晶体管M1～M4和存储电容C1。其具体电路连接关系如下：

[0056] 第一晶体管M1的栅极接收第一驱动开关信号EM1，源极接收第一电源信号ELVDD，漏极与驱动晶体管MDTFT的源极和存储电容C1的第一端连接。第一晶体管M1响应第一驱动开关信号EM1而导通，以将第一电源信号ELVDD传输至驱动晶体管MDTFT的源极。

[0057] 第二晶体管M2的栅极接收第二驱动开关信号EM2，源极与存储电容C1的第二端连接，漏极与驱动晶体管MDTFT的栅极连接。第二晶体管M2响应第二驱动开关信号EM2而导通，以将驱动晶体管MDTFT的源极通过存储电容C1与驱动晶体管MDTFT的栅极连通。

[0058] 第三晶体管M3的栅极接收写入开关信号Gate，源极与存储电容C1的第二端连接，漏极与驱动晶体管MDTFT的漏极连接。第三晶体管M3响应写入开关信号Gate而导通，以将驱动晶体管MDTFT的源极通过存储电容C1与驱动晶体管MDTFT的漏极连通。

[0059] 第四晶体管M4的栅极接收写入开关信号Gate，源极接收数据信号Data，漏极与驱动晶体管MDTFT的栅极连接。第四晶体管M4响应写入开关信号Gate而导通，以将数据信号Data传输至驱动晶体管MDTFT的栅极。

[0060] 驱动晶体管MDTFT的漏极与OLED的阳极连接，用于驱动OLED进行发光，OLED的阴极接收第二电源信号ELVSS。

[0061] 本实施例中以P型薄膜晶体管为例进行说明。应理解的是，当选用N型薄膜晶体管时，对应电路中OLED的电流流向及电源信号的高低电平随着采用不同导电类型的薄膜晶体管作为电路的开关元件的不同而改变。在本实施例选用P型薄膜晶体管时，确定第一电源信号ELVDD为高电平信号，第二电源信号ELVSS为低电平信号。

[0062] 本实施例中，各薄膜晶体管选用低温多晶硅晶体管，能够降低制造成本和产品功耗，具有更快的电子迁移率和更小的薄膜电路面积，提高显示的分辨率和稳定性。

[0063] 在该实施例中，通过引入第一和第二驱动开关信号分别对第一和第二晶体管的导通和关断进行控制，使得电路结构随驱动开关信号的高低电平变化而改变。同时，写入开关信号Gate控制数据信号Data的写入过程，将数据信号Data和驱动晶体管MDTFT的阈值电压Vth写入存储电容C1的第一端并将OLED的阈值电压Vth写入存储电容的第二端，完成存储电

容C1两端电压的写入,实现OLED的发光电流 $I_{OLED}$ 仅与OLED的阈值电压 $V_{th}$ 和数据信号Data有关,从而解决驱动晶体管阈值电压 $V_{th}$ 偏移和背板电源ELVDD压降造成发光亮度不均的问题。

[0064] 下面结合具体阶段对上述像素驱动电路的驱动过程及原理进行说明

[0065] 如图3示出各信号的时序关系图。由于本实施例中选用P型薄膜晶体管,当晶体管栅极信号为低电平时,对应晶体管导通;当晶体管栅极信号为高电平时,对应晶体管关断。应说明的是,选用不同导电类型的晶体管时,对应控制信号的高低电平做相应变化。

[0066] 本实施例中的驱动过程分为:初始化阶段T1、补偿阶段T2和发光阶段T3,下面按照时序顺序依次进行介绍。

[0067] [初始化阶段T1]

[0068] 该阶段中,利用第一驱动开关信号EM1、第二驱动开关信号EM2以及写入开关信号Gate导通第一晶体管M1、第三晶体管M3和第四晶体管M4,同时关断第二晶体管M2,利用将数据信号Vref关断驱动晶体管MDTFT,并使驱动晶体管MDTFT的栅极和源极之间形成固定电压偏置。

[0069] 初始化时,写入开关信号Gate为低电平,用于导通第三晶体管M3和第四晶体管M4;第一驱动开关信号EM1为低电平,用于导通第一晶体管M1;第二驱动开关信号EM2为高电平,用于关断第二晶体管M2;数据信号Vref为高电平,用于关断驱动晶体管MDTFT。初始化阶段的等效电路结构如图4所示。

[0070] 在该阶段中,第一节点电压Vnet1为第一电源信号电压,即 $V_{net1}=ELVDD$ ;第二节点Vnet2电压为数据信号Data电压,即 $V_{net2}=V_{ref}$ ;驱动晶体管MDTFT的栅源电压为Vgs,且 $V_{gs}=V_{ref}-ELVDD$ 。

[0071] 为了保证驱动晶体管MDTFT的关断状态,此时,设置驱动晶体管MDTFT的栅源电压Vgs大于其阈值电压 $V_{th}$ ,即 $V_{ref}-ELVDD > V_{th}$ 。可知,通过设定 $V_{ref} > ELVDD + V_{th}$ 可实现驱动晶体管MDTFT的关断。

[0072] 由于OLED中驱动晶体管存在磁滞效应,导致由白画面转至灰阶画面时和由黑画面转至灰阶画面时对应不同的驱动电流,造成子像素之间的亮度差,带来短期残像。通过上述分析可知,本实施例在初始化阶段中,驱动晶体管MDTFT栅源两端形成固定电压偏置,从而可改善短期残像不良现象,优化显示效果。

[0073] [补偿阶段T2]

[0074] 该阶段中,利用第一驱动开关信号EM1、第二驱动开关信号EM2以及写入开关信号Gate导通第三晶体管M3和第四晶体管M4并关断第一晶体管M1和第二晶体管M2,以将数据信号Data和驱动晶体管的阈值电压 $V_{th}$ 写入存储电容C1的第一端,并将OLED的阈值电压 $V_{th}$ 写入存储电容C1的第二端。

[0075] 进行补偿时,写入开关信号Gate为低电平,用于导通第三晶体管M3和第四晶体管M4;第一驱动开关信号EM1为高电平,用于关断第一晶体管M1;第二驱动开关信号EM2为高电平,用于关断第二驱动晶体管M2;数据信号Vdata导通驱动晶体管MDTFT。补偿阶段的等效电路结构如图5所示。

[0076] 在该阶段中,驱动晶体管MDTFT导通,且其栅极电压为数据信号电压Vdata,其源极电压逐渐降至 $V_{data}-V_{th}$ ,即第一节点电压Vnet1由ELVDD下降至 $V_{data}-V_{th}$ 。第二节点电压

$V_{net2}=V_{data}$ 。由于 $V_{gs} > V_{th}$ ,驱动晶体管MDTFT被关断,此时流经驱动晶体管MDTFT的电流逐渐减小为零,此时第三节点电压 $V_{net3}=V_{oIed\_o}$ ,其中, $V_{oIed\_o}$ 为OLED的阈值电压。第四节点电压 $V_{net4}=V_{net3}=V_{oIed\_o}$ 。

[0077] 补偿阶段完成时,存储电容C1两端的电压情况为: $V_{net1}=V_{data}-V_{th}$ , $V_{net4}=V_{oIed\_o}$ ,存储电容C1上下极板间电压差 $V_{c1}$ 为:

[0078]  $V_{c1}=V_{net1}-V_{net4}=V_{data}-V_{th}-V_{oIed\_o}$ 。

[0079] [发光阶段T3]

[0080] 该阶段中,利用第一驱动开关信号EM1、第二驱动开关信号EM2以及写入开关信号Gate导通第一晶体管M1和第二晶体管M2,关断第三晶体管M3和第四晶体管M4,以通过存储电容C1中的电压信号导通驱动晶体管,使第一电源信号ELVDD驱动OLED发光。

[0081] 发光时,写入开关信号Gate为高电平,用于关断第三晶体管M3和第四晶体管M4;第一驱动开关信号EM1为低电平,用于导通第一晶体管M1;第二驱动开关信号EM2为低电平,用于导通第二驱动晶体管M2;数据信号Vdata为低电平,存储电容C1并联于驱动晶体管MDTFT的栅极和源极之间。发光阶段的等效电路结构如图6所示。

[0082] 在该阶段中,第一节点电压 $V_{net1}$ 由 $V_{data}-V_{th}$ 突变为ELVDD;由于上一阶段中,存储电容C1上下极板间存在电压差 $V_{c1}$ ,导致第四节点电压 $V_{net4}$ 的电压值跳变至 $ELVDD-V_{c1}$ ,即

[0083]  $V_{net4}=ELVDD-V_{c1}=ELVDD-V_{data}+V_{th}+V_{oIed\_o}$ ;

[0084] 此时,OLED的发光电流 $I_{oled}$ 为

[0085]  $I_{oled}=k(V_{gs}-V_{th})^2$

[0086]  $=k(V_{net4}-V_{net1}-V_{th})^2$

[0087]  $=k(ELVDD-V_{data}+V_{th}+V_{oIed\_o}-ELVDD-V_{th})^2$

[0088]  $=k(V_{oIed\_o}-V_{data})^2$

[0089] 其中,k为系数。

[0090] 由上式可知,OLED的发光电流 $I_{oled}$ 仅与OLED的阈值电压 $V_{th}$ 和数据信号Data有关,从而解决驱动晶体管阈值电压 $V_{th}$ 偏移和背板电源ELVDD压降造成发光亮度不均的问题。

[0091] 实施例2

[0092] 如图7所示,一种OLED的像素驱动电路,包括驱动晶体管MDTFT、第一至第五晶体管M1~M5和存储电容C1。其具体电路连接关系如下:

[0093] 第一晶体管M1的栅极接收第一驱动开关信号EM1,源极接收第一电源信号ELVDD,漏极与驱动晶体管MDTFT的源极和存储电容C1的第一端连接。第一晶体管M1响应第一驱动开关信号EM1而导通,以将第一电源信号ELVDD传输至驱动晶体管MDTFT的源极。

[0094] 第二晶体管M2的栅极接收第一驱动开关信号EM1,源极与存储电容C1的第二端连接,其漏极与第五晶体管M5的源极连接。第五晶体管M5的栅极接收第二驱动开关信号EM2,漏极与驱动晶体管MDTFT的栅极连接。第二晶体管M2响应第一驱动开关信号EM1而导通,第五晶体管M5响应第二驱动开关信号EM2而导通,以将驱动晶体管MDTFT的源极通过存储电容C1与驱动晶体管MDTFT的栅极连通。

[0095] 第三晶体管M3的栅极接收写入开关信号Gate,源极与存储电容C1的第二端连接,漏极与驱动晶体管MDTFT的漏极连接。第三晶体管M3响应写入开关信号Gate而导通,以将驱

动晶体管MDTFT的源极通过存储电容C1与驱动晶体管MDTFT的漏极连通。

[0096] 第四晶体管M4的栅极接收写入开关信号Gate，源极接收数据信号Data，漏极与驱动晶体管MDTFT的栅极连接。第四晶体管M4响应写入开关信号Gate而导通，以将数据信号Data传输至驱动晶体管MDTFT的栅极。

[0097] 驱动晶体管MDTFT的漏极与OLED的阳极连接，用于驱动OLED进行发光，OLED的阴极接收第二电源信号ELVSS。

[0098] 在本实施例中，晶体管的选择与上述实施例相同，在此不再赘述。

[0099] 本实施例与实施例1的区别在于：引入了第五晶体管EM5。相应地，第一晶体管M1和第二晶体管M2由第一驱动开关信号EM1控制导通或关断，第五晶体管M5由第二驱动开关信号EM2控制导通或关断。

[0100] 该实施例中，通过不同控制信号控制上述开关元件的导通和关断来实现像素驱动电路的补偿功能，并实现OLED的发光电流仅与OLED的阈值电压和数据信号有关，而与驱动晶体管的阈值电压和背板电源压降无关，从而解决驱动晶体管阈值电压偏移和背板电源压降造成的发光亮度不均的问题。进一步地，上述控制信号中，第一驱动开关信号和第二驱动开关信号相差一个时序周期，即上述第二驱动开关信号可由第一驱动开关信号经移位寄存处理得到，减少了控制信号的个数，降低了电路的控制复杂度。

[0101] 下面结合具体阶段对上述像素驱动电路的驱动过程及原理进行说明

[0102] 如图8示出各信号的时序关系图。本实施例中的驱动过程分为：初始化阶段T1、补偿阶段T2、预发光阶段T3和发光阶段T4，下面按照时序顺序依次进行介绍。

[0103] [初始化阶段T1]

[0104] 初始化时，写入开关信号Gate为低电平，用于导通第三晶体管M3和第四晶体管M4；第一驱动开关信号EM1为低电平，用于导通第一晶体管M1和第二晶体管M2；第二驱动开关信号EM2为高电平，用于关断第五晶体管M5；数据信号Vref为高电平，用于关断驱动晶体管MDTFT。初始化阶段的等效电路结构如图4所示。

[0105] 该阶段中，同样地，驱动晶体管MDTFT栅源两端形成固定电压偏置，从而可改善短期残像不良现象，其过程与原理与实施例1中相似，在此不再赘述。

[0106] [补偿阶段T2]

[0107] 补偿时，写入开关信号Gate为低电平，用于导通第三晶体管M3和第四晶体管M4；第一驱动开关信号EM1为高电平，用于关断第一晶体管M1和第二晶体管M2；第二驱动开关信号EM2为高电平，用于关断第五晶体管M5；数据信号Vdata导通驱动晶体管MDTFT。补偿阶段的等效电路结构如图5所示。

[0108] 在该阶段中，存储电容C1两端获得上下极板间的电压差为Vc1，其分析过程同上述实施例1。

[0109] [预发光阶段T3]

[0110] 与实施例1不同的是，本实施例中还包括预发光阶段T3。在该阶段中，第二驱动开关信号EM2为低电平。此时，虽然第五晶体管M5在第二驱动开关信号EM2的控制下导通，但由于第二晶体管M2仍处于关断状态，该阶段电路等效结构没有改变。

[0111] 通过采用与第一驱动开关信号相差一个时序周期的信号作为第二驱动开关信号，且该信号可由第一驱动开关信号经移位寄存处理得到，减少了控制信号的个数，降低了电

路的控制复杂度。

[0112] 进一步地,本实施例中,补偿阶段T2和预发光阶段T3都用于数据信号的写入,延长了写入的时间,能够获得更好的写入效果。应说明的是,在实施例1中,同样可通过增加补偿阶段的时间来获得更好的写入效果。

[0113] [发光阶段T4]

[0114] 发光时,写入开关信号Gate为高电平,用于关断第三晶体管M3和第四晶体管M4;第一驱动开关信号EM1为低电平,用于导通第一晶体管M1和第二晶体管M2;第二驱动开关信号EM2为低电平,用于导通第五晶体管M5;数据信号Vdata为低电平,存储电容C1并联于驱动晶体管MDTFT的栅极和源极之间。发光阶段的等效电路结构如图9所示。

[0115] 本实施例中,OLED的发光电流 $I_{OLED}$ 为 $I_{OLED}=k(V_{gs}-V_{th})^2$ ,其计算过程与实施例1相同,在此不再赘述。可知,OLED的发光电流 $I_{OLED}$ 仅与OLED的阈值电压 $V_{th}$ 和数据信号Data有关,从而解决驱动晶体管阈值电压 $V_{th}$ 偏移和背板电源ELVDD压降造成的发光亮度不均的问题。

[0116] 实施例3

[0117] 本实施例提供一种阵列基板,包括实施例1或2中所述的像素驱动电路。

[0118] 实施例4

[0119] 本实施例提供一种显示装置,包括实施例3中所述的阵列基板。该显示设备可以为:手机、平板电脑、电视机、显示器、笔记本电脑、数码相框、导航仪等任何具有显示功能的产品或部件。

[0120] 显然,本实用新型的上述实施例仅仅是为清楚地说明本实用新型所作的举例,而并非是对本实用新型的实施方式的限定,对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动,这里无法对所有的实施方式予以穷举,凡是属于本实用新型的技术方案所引伸出的显而易见的变化或变动仍处于本实用新型的保护范围之列。

图1

图2

图3

图4

图5

图6

图7

图8

图9

|                |                              |                      |            |

|----------------|------------------------------|----------------------|------------|

| 专利名称(译)        | 像素驱动电路、阵列基板及显示装置             |                      |            |

| 公开(公告)号        | <a href="#">CN207182881U</a> | 公开(公告)日              | 2018-04-03 |

| 申请号            | CN201721269903.5             | 申请日                  | 2017-09-29 |

| [标]申请(专利权)人(译) | 京东方科技股份有限公司                  |                      |            |

| 申请(专利权)人(译)    | 京东方科技股份有限公司                  |                      |            |

| 当前申请(专利权)人(译)  | 京东方科技股份有限公司                  |                      |            |

| [标]发明人         | 高雪岭                          |                      |            |

| 发明人            | 高雪岭                          |                      |            |

| IPC分类号         | G09G3/3233 G09G3/3291        |                      |            |

| 代理人(译)         | 付生辉                          |                      |            |

| 外部链接           | <a href="#">Espacenet</a>    | <a href="#">Sipo</a> |            |

#### 摘要(译)

本实用新型公开一种像素驱动电路，包括驱动晶体管、第一至第四开关元件、存储电容。通过不同控制信号控制上述开关元件的导通和关断来实现像素驱动电路的补偿功能，并实现OLED的发光电流仅与OLED的阈值电压和数据信号有关，而与驱动晶体管的阈值电压和背板电源压降无关，从而解决驱动晶体管阈值电压偏移和背板电源压降造成发光亮度不均的问题。本实用新型还公开一种阵列基板及显示装置。