(12)发明专利申请

(10)申请公布号 CN 110911468 A

(43)申请公布日 2020.03.24

(21)申请号 201911269539.6

(22)申请日 2019.12.11

(71)申请人 京东方科技股份有限公司

地址 100015 北京市朝阳区酒仙桥路10号

(72)发明人 徐攀 李永谦 张大成 刘娘

(74)专利代理机构 北京中博世达专利商标代理有限公司 11274

代理人 申健

(51)Int.Cl.

H01L 27/32(2006.01)

权利要求书2页 说明书11页 附图11页

(54)发明名称

一种显示用基板及电致发光显示装置

(57)摘要

本发明实施例提供一种显示用基板及电致发光显示装置,涉及显示技术领域,可以改善减少第一电源线,导致相同颜色的亚像素发光不一致的问题。该显示用基板包括多个显示单元,每个所述显示单元包括至少两列像素;所述像素包括至少三个亚像素;每个所述显示单元设置至少一条第一电源线和至少一条第二电源线;所述显示单元中所述亚像素均与设置在该所述显示单元中的所述第一电源线电连接;所述第一电源线和所述第二电源线设置在不同列像素中,位于所述第一电源线两侧的所述亚像素的颜色与位于所述第二电源线两侧的所述亚像素颜色相同。用于电致发光显示装置中。

1. 一种显示用基板,其特征在于,包括多个显示单元,每个所述显示单元包括至少两列像素;所述像素包括至少三个亚像素;

每个所述显示单元设置至少一条第一电源线和至少一条第二电源线;所述显示单元中所述亚像素均与设置在该所述显示单元中的所述第一电源线电连接;

其中,所述第一电源线和所述第二电源线设置在不同列像素中,位于所述第一电源线两侧的所述亚像素的颜色与位于所述第二电源线两侧的所述亚像素颜色相同。

2. 根据权利要求1所述的显示用基板,其特征在于,每列所述像素设置一条所述第一电源线或一条所述第二电源线。

3. 根据权利要求2所述的显示用基板,其特征在于,每个所述显示单元包括所述像素的列数相同;

每个所述显示单元设置的所述第一电源线的条数相同。

4. 根据权利要求3所述的显示用基板,其特征在于,所述显示单元包括n列所述像素;每个所述显示单元设置1条所述第一电源线,设置n-1条所述第二电源线;

其中,n≥2,n为正整数。

5. 根据权利要求1-4任一项所述的显示用基板,其特征在于,相邻所述第一电源线之间设置的所述像素的列数相同。

6. 根据权利要求1所述的显示用基板,其特征在于,所述第一电源线和所述第二电源线设置于衬底上,所述显示用基板还包括设置在所述第一电源线和所述第二电源线远离所述衬底一侧的发光器件;所述发光器件包括依次层叠设置的第一电极层、发光功能层以及透明的第二电极层;

所述第二电源线与所述第二电极层电连接。

7. 根据权利要求1或6所述的显示用基板,其特征在于,所述第二电源线的电阻等于所述第一电源线的电阻的0.9~1.1倍。

8. 根据权利要求6所述的显示用基板,其特征在于,所述第二电源线的电阻与沿垂直于所述衬底的方向,所述第二电极层中与该所述第二电源线重叠部分的电阻并联后的电阻之和等于所述第一电源线的电阻的0.9~1.1倍。

9. 根据权利要求1所述的显示用基板,其特征在于,所述第一电源线和所述第二电源线同层同材料。

10. 根据权利要求1所述的显示用基板,其特征在于,所述显示用基板还包括数据线;

所述第一电源线和所述第二电源线均与所述数据线同层同材料。

11. 根据权利要求9或10所述的显示用基板,其特征在于,所述第一电源线的线宽大于或等于所述第二电源线的线宽。

12. 根据权利要求1所述的显示用基板,其特征在于,所述第一电源线包括第一部分和第二部分,所述第二电源线包括第三部分和第四部分;所述第一部分和所述第三部分分别位于相邻两个所述亚像素的像素开口区之间;

所述第一部分的线宽与所述第三部分的线宽的差值范围为0~1μm。

13. 根据权利要求1所述的显示用基板,其特征在于,所述第一电源线为VDD电源线,所述第二电源线为VSS电源线。

14. 根据权利要求1所述的显示用基板,其特征在于,所述像素包括红色亚像素、绿色亚

像素以及蓝色亚像素；

或者，所述像素包括红色亚像素、绿色亚像素、蓝色亚像素以及白色亚像素。

15. 一种电致发光显示装置，其特征在于，包括如权利要求1-14任一项所述的显示用基板。

## 一种显示用基板及电致发光显示装置

### 技术领域

[0001] 本发明涉及显示技术领域,尤其涉及一种显示用基板及电致发光显示装置。

### 背景技术

[0002] 电致发光显示装置由于具有自发光、低功耗、宽视角、响应速度快以及高对比度等优点,因而成为目前显示装置的主流发展趋势。

[0003] 电致发光显示装置包括显示用基板以及用于封装显示用基板的封装层。显示用基板包括多个亚像素,每个亚像素包括像素电路和发光器件,显示用基板还包括走线,例如第一电源线,第一电源线与像素电路中的VDD电压端电连接,用于为VDD电压端提供直流信号。

### 发明内容

[0004] 本发明的实施例提供一种显示用基板及电致发光显示装置,可以改善减少第一电源线,导致相同颜色的亚像素发光不一致的问题。

[0005] 为达到上述目的,本发明的实施例采用如下技术方案:

[0006] 一方面,提供一种显示用基板,包括多个显示单元,每个所述显示单元包括至少两列像素;所述像素包括至少三个亚像素;每个所述显示单元设置至少一条第一电源线和至少一条第二电源线;所述显示单元中所述亚像素均与设置在该所述显示单元中的所述第一电源线电连接;其中,所述第一电源线和所述第二电源线设置在不同列像素中,位于所述第一电源线两侧的所述亚像素的颜色与位于所述第二电源线两侧的所述亚像素颜色相同。

[0007] 在一些实施例中,每列所述像素设置一条所述第一电源线或一条所述第二电源线。

[0008] 在一些实施例中,每个所述显示单元包括所述像素的列数相同;每个所述显示单元设置的所述第一电源线的条数相同。

[0009] 在一些实施例中,所述显示单元包括n列所述像素;每个所述显示单元设置1条所述第一电源线,设置n-1条所述第二电源线;其中,n≥2,n为正整数。

[0010] 在一些实施例中,相邻所述第一电源线之间设置的所述像素的列数相同。

[0011] 在一些实施例中,所述第一电源线和所述第二电源线设置于衬底上,所述显示用基板还包括设置在所述第一电源线和所述第二电源线远离所述衬底一侧的发光器件;所述发光器件包括依次层叠设置的第一电极层、发光功能层以及透明的第二电极层;所述第二电源线与所述第二电极层电连接。

[0012] 在一些实施例中,所述第二电源线的电阻等于所述第一电源线的电阻的0.9~1.1倍。

[0013] 在一些实施例中,所述第二电源线的电阻与沿垂直于所述衬底的方向,所述第二电极层中与该所述第二电源线重叠部分的电阻并联后的电阻之和等于所述第一电源线的电阻的0.9~1.1倍。

[0014] 在一些实施例中,所述第一电源线和所述第二电源线同层同材料。

[0015] 在一些实施例中,所述显示用基板还包括数据线;所述第一电源线和所述第二电源线均与所述数据线同层同材料。

[0016] 在一些实施例中,所述第一电源线的线宽大于或等于所述第二电源线的线宽。

[0017] 在一些实施例中,所述第一电源线包括第一部分和第二部分,所述第二电源线包括第三部分和第四部分;所述第一部分和所述第三部分分别位于相邻两个所述亚像素的像素开口区之间;所述第一部分的线宽与所述第三部分的线宽的差值范围为0~1μm。

[0018] 在一些实施例中,所述第一电源线为VDD电源线,所述第二电源线为VSS电源线。

[0019] 在一些实施例中,所述像素包括红色亚像素、绿色亚像素以及蓝色亚像素;或者,所述像素包括红色亚像素、绿色亚像素、蓝色亚像素以及白色亚像素。

[0020] 另一方面,提供一种电致发光显示装置,包括上述的显示用基板。

[0021] 本发明实施例提供一种显示用基板及电致发光显示装置,显示用基板包括多个显示单元,每个显示单元包括至少两列像素;每个像素包括至少三个亚像素;每个显示单元设置至少一条第一电源线和至少一条第二电源线;显示单元中亚像素均与设置在该显示单元中的第一电源线电连接;第一电源线和第二电源线设置在不同列像素中,位于第一电源线两侧的亚像素的颜色与位于第二电源线两侧的亚像素颜色相同。由于每个显示单元包括至少两列像素,显示单元设置至少一条第一电源线和至少一条第二电源线,且第一电源线和第二电源线设置在不同列像素中,因而相对于每列像素设置一条第一电源线,本发明实施例中设置的第一电源线的数量减少。

[0022] 在此基础上,由于第一电源线上信号的大小以及施加信号时第一电源线发出的热量会影响位于第一电源线两侧的亚像素发出的光,第二电源线上信号的大小以及施加信号时第二电源线发出的热量会影响位于第二电源线两侧的亚像素发出的光,而第一电源线和第二电源线设置在不同列像素中,且位于第一电源线两侧的亚像素的颜色与位于第二电源线两侧的亚像素颜色相同,因而在给相同颜色的亚像素施加相同信号的情况下,可以确保设置有第一电源线和第二电源线的像素中相同颜色的亚像素发出的光一致,因此改善了减少第一电源线,导致的相同颜色的亚像素发光不一致的问题,改善了显示均匀性,提高了显示效果。

## 附图说明

[0023] 为了更清楚地说明本发明实施例或相关技术中的技术方案,下面将对实施例或相关技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本发明的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

[0024] 图1为本发明实施例提供的一种电致发光显示装置的结构示意图;

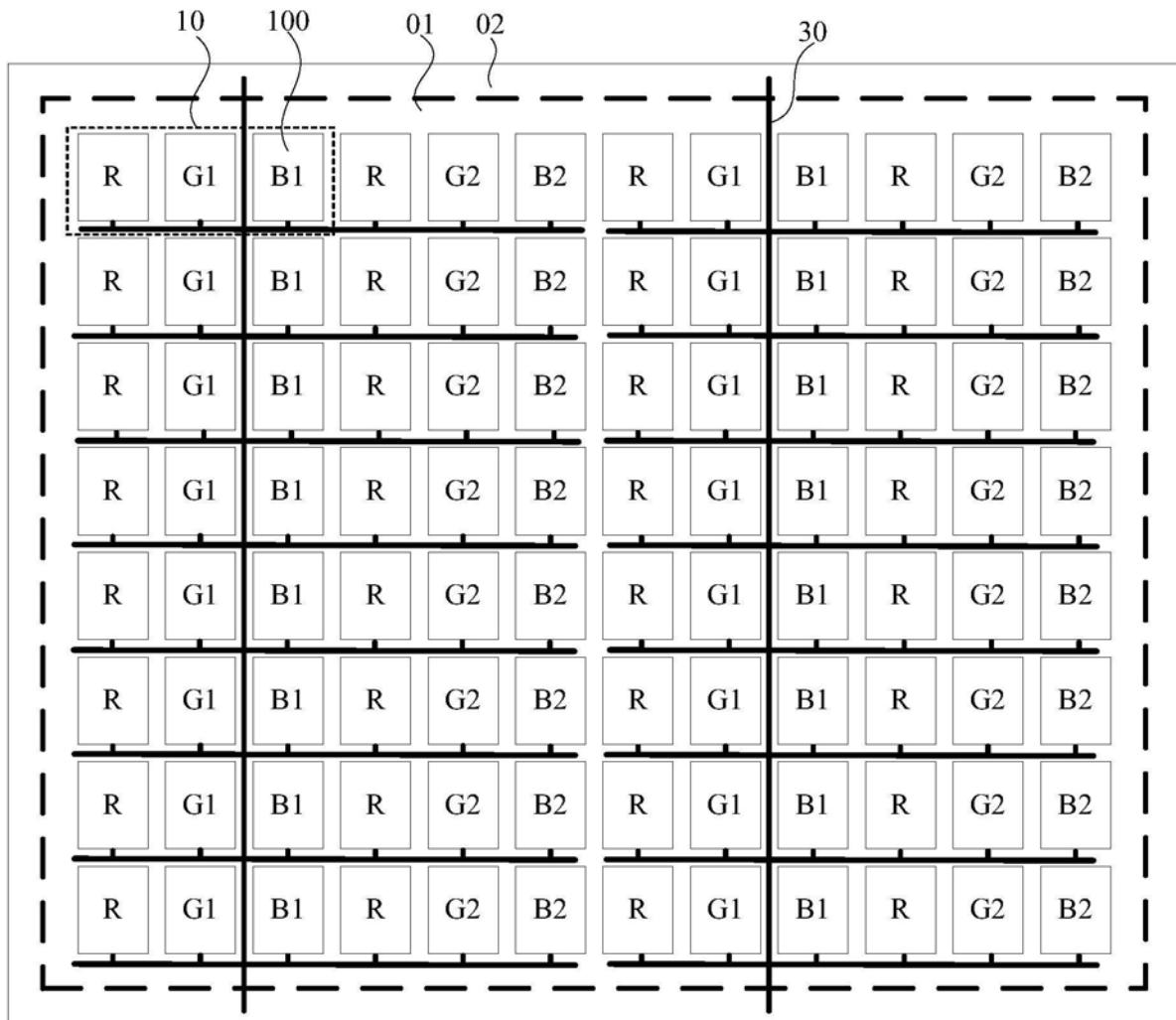

[0025] 图2为本发明实施例提供的一种电致发光显示面板的区域划分示意图;

[0026] 图3为本发明实施例提供的一种电致发光显示面板的结构示意图;

[0027] 图4为本发明实施例提供的一种像素电路的结构示意图;

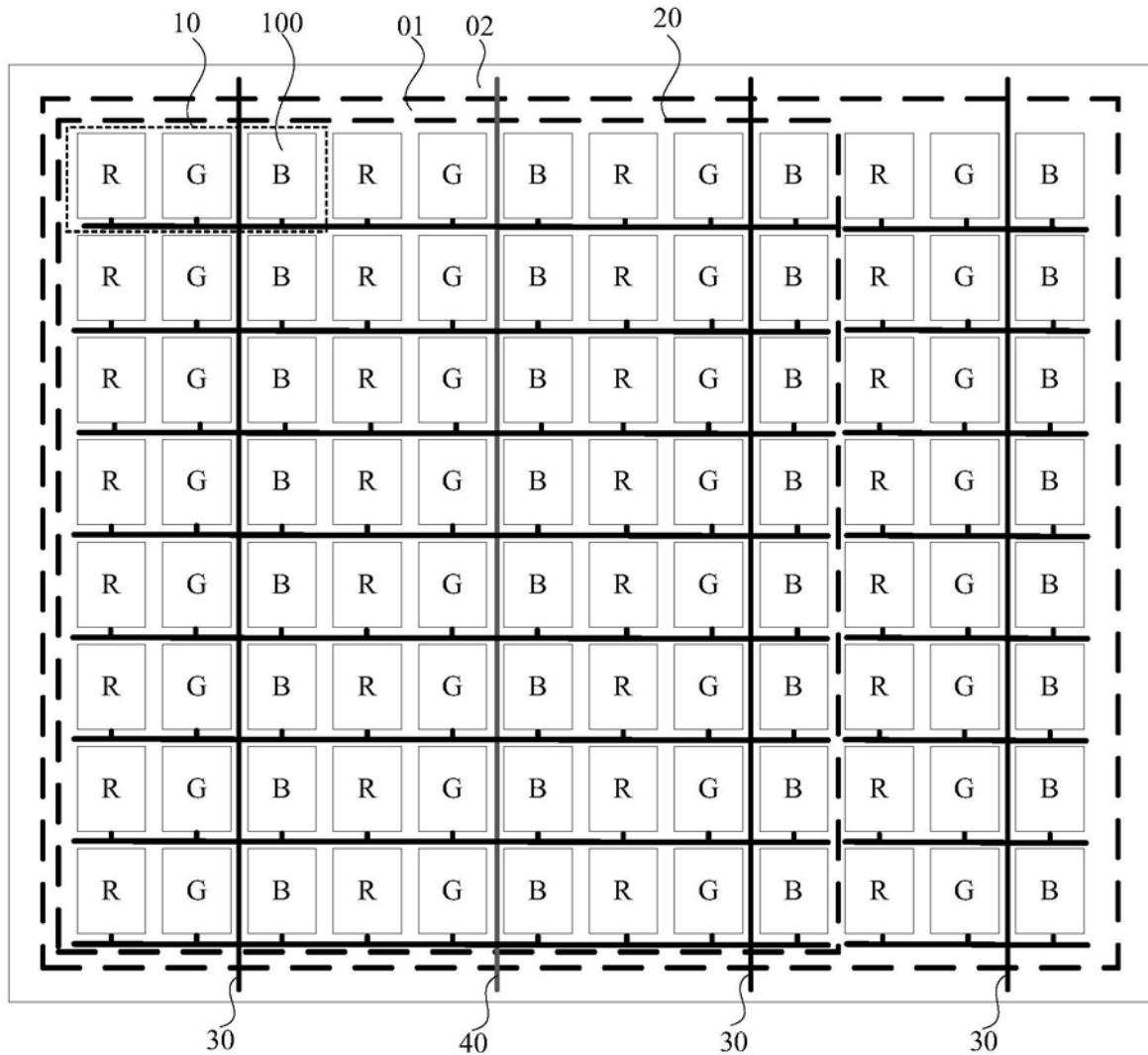

[0028] 图5为本发明实施例提供的一种显示用基板的结构示意图一;

[0029] 图6为本发明实施例提供的一种显示用基板的结构示意图二;

[0030] 图7为本发明实施例提供的一种显示用基板的结构示意图三;

- [0031] 图8为本发明实施例提供的一种显示用基板的结构示意图四；

[0032] 图9为本发明实施例提供的一种显示用基板的结构示意图五；

[0033] 图10为相关技术提供的一种显示用基板的结构示意图一；

[0034] 图11为相关技术提供的一种显示用基板的结构示意图二；

[0035] 图12为本发明实施例提供的一种亚像素中第二电极层电阻的等效图示意图；

[0036] 图13a为本发明实施例提供的一种显示用基板的结构示意图六；

[0037] 图13b为本发明实施例提供的一种显示用基板的结构示意图七；

[0038] 图14为图13a或图13b中电阻等效后的电阻网络图。

[0039] 附图标记：

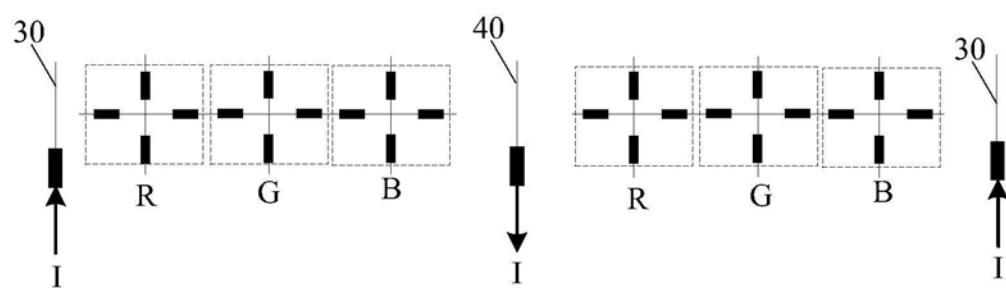

[0040] 01-显示区；02-周边区；1-电致发光显示面板；2-框架；3-盖板玻璃；4-电路板；10-像素；11-显示用基板；12-封装层；20-显示单元；30-第一电源线；301-第一部分；302-第二部分；40-第二电源线；401-第三部分；402-第四部分；100-亚像素；110-衬底；111-薄膜晶体管；112-第一电极层；113-发光功能层；114-第二电极层；115-像素界定层；116-平坦层；117-缓冲层；118-遮光层。

## 具体实施方式

[0041] 下面将结合本发明实施例中的附图，对本发明实施例中的技术方案进行清楚、完整地描述，显然，所描述的实施例仅仅是本发明一部分实施例，而不是全部的实施例。基于本发明中的实施例，本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例，都属于本发明保护的范围。

[0042] 本发明实施例提供一种电致发光显示装置，为便于对本发明中的各实施例的理解，下面对该电致发光显示装置的结构进行示例性的介绍。然而，下面的示例性的介绍并不能理解为对本发明所提供的电致发光显示装置的结构的限定，本发明所提供的电致发光显示装置的结构不仅限于下面的示例性介绍，其还可以有其他的变化。

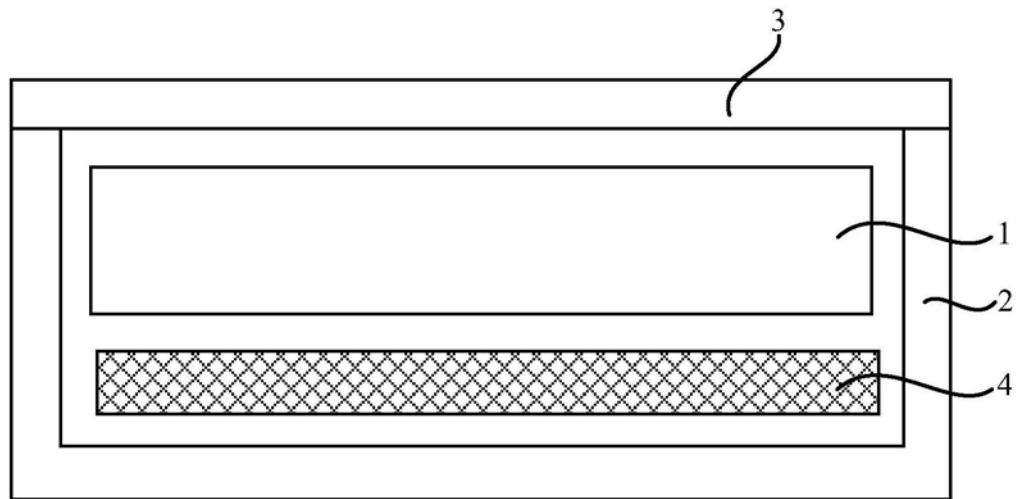

[0043] 如图1所示，电致发光显示装置包括电致发光显示面板1、框架2、盖板玻璃3以及电路板4等其它电子配件。

[0044] 其中，框架2的纵截面呈U型，电致发光显示面板1、电路板4以及其它电子配件均设置于框架2内，电路板4设置于电致发光显示面板1的下方，盖板玻璃2设置于电致发光显示面板1远离电路板4的一侧。

[0045] 本发明实施例提供的电致发光显示装置可以是有机电致发光显示装置(Organic Light-Emitting Diode Display, 简称OLED)，在此情况下，电致发光显示面板1为有机电致发光显示面板；也可以是量子点电致发光显示装置(Quantum Dot Light Emitting Diodes Display, 简称QLED)，在此情况下，电致发光显示面板1为量子点电致发光显示面板。

[0046] 本发明实施例提供的电致发光显示装置可以是手机、电视(Television, 简称TV)、电脑、平板电脑、车载显示器等。

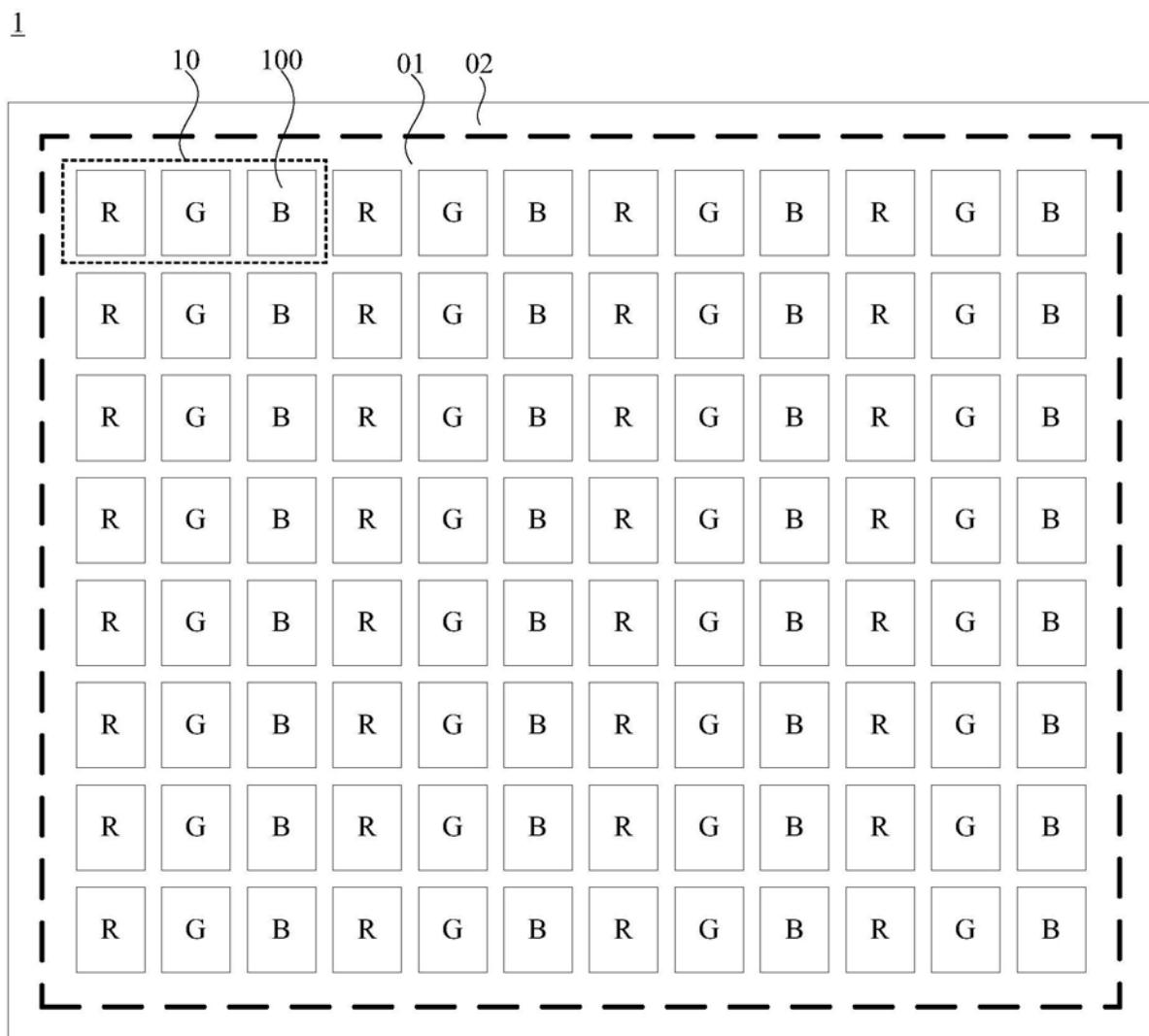

[0047] 如图2所示，电致发光显示面板1包括显示区01和周边区02，附图2以周边区02包围显示区01为例进行示意。显示区01包括多个像素10，每个像素10包括至少三个亚像素100。周边区02用于布线，此外，也可以将栅极驱动电路设置于周边区02。

[0048] 如图3所示，电致发光显示面板1的主要结构包括显示用基板11以及用于封装显示

用基板11的封装层12。此处,封装层12可以为封装薄膜,也可以为封装基板。

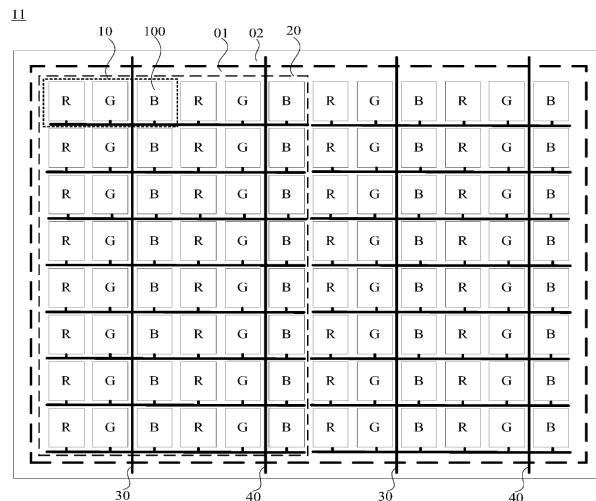

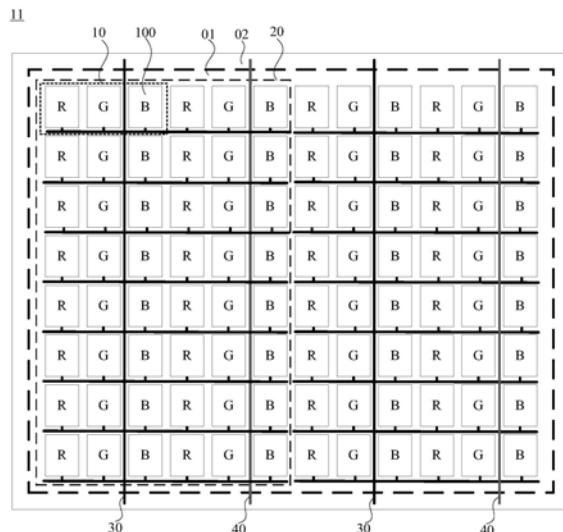

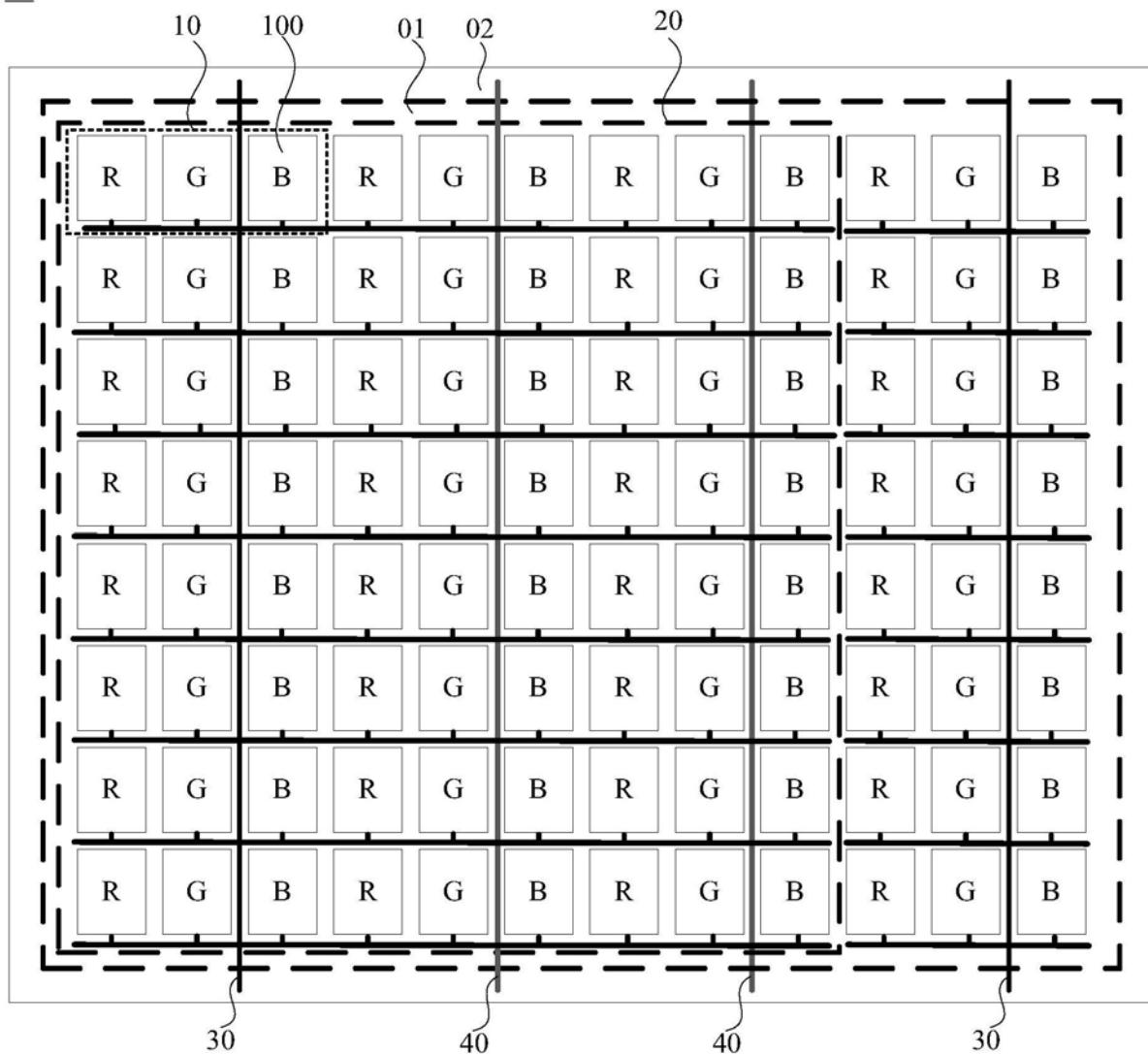

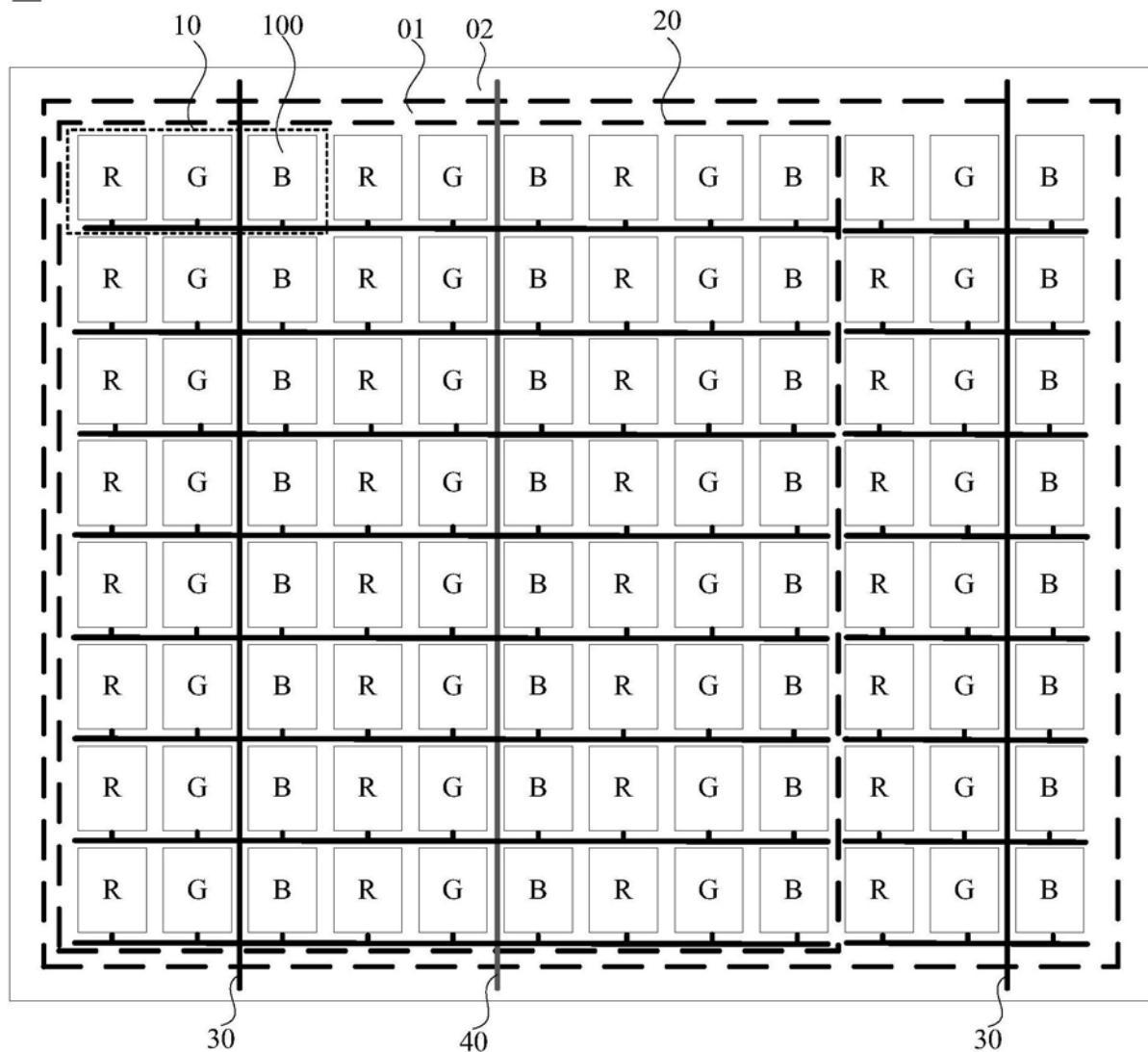

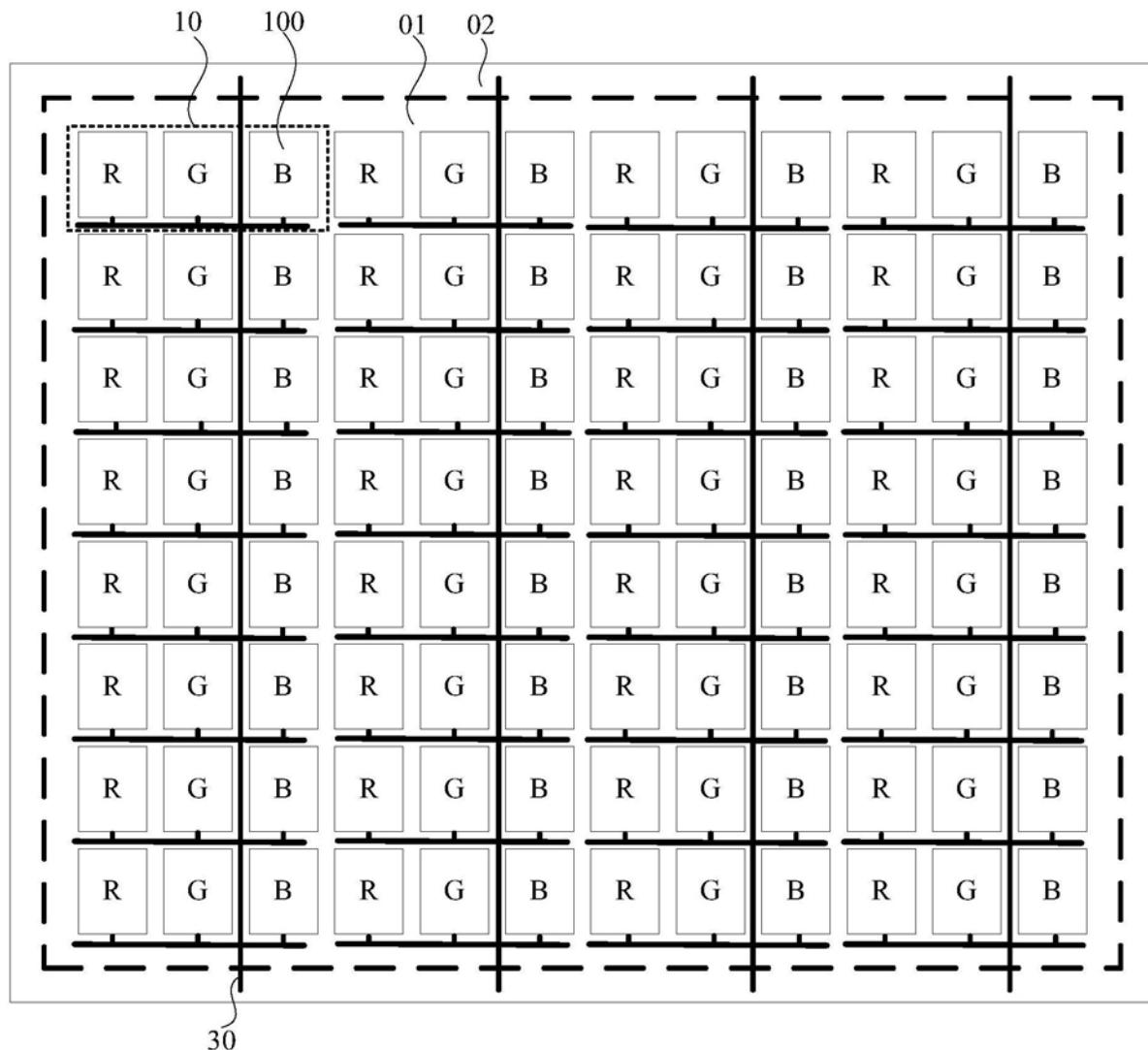

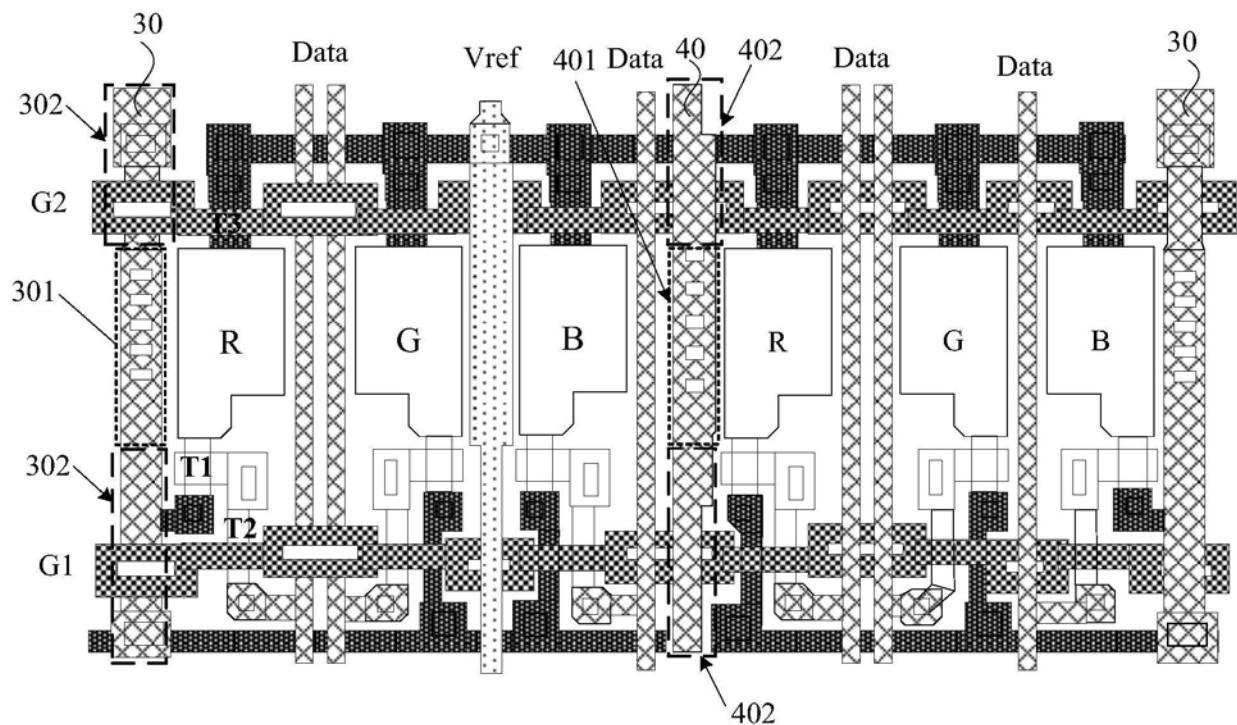

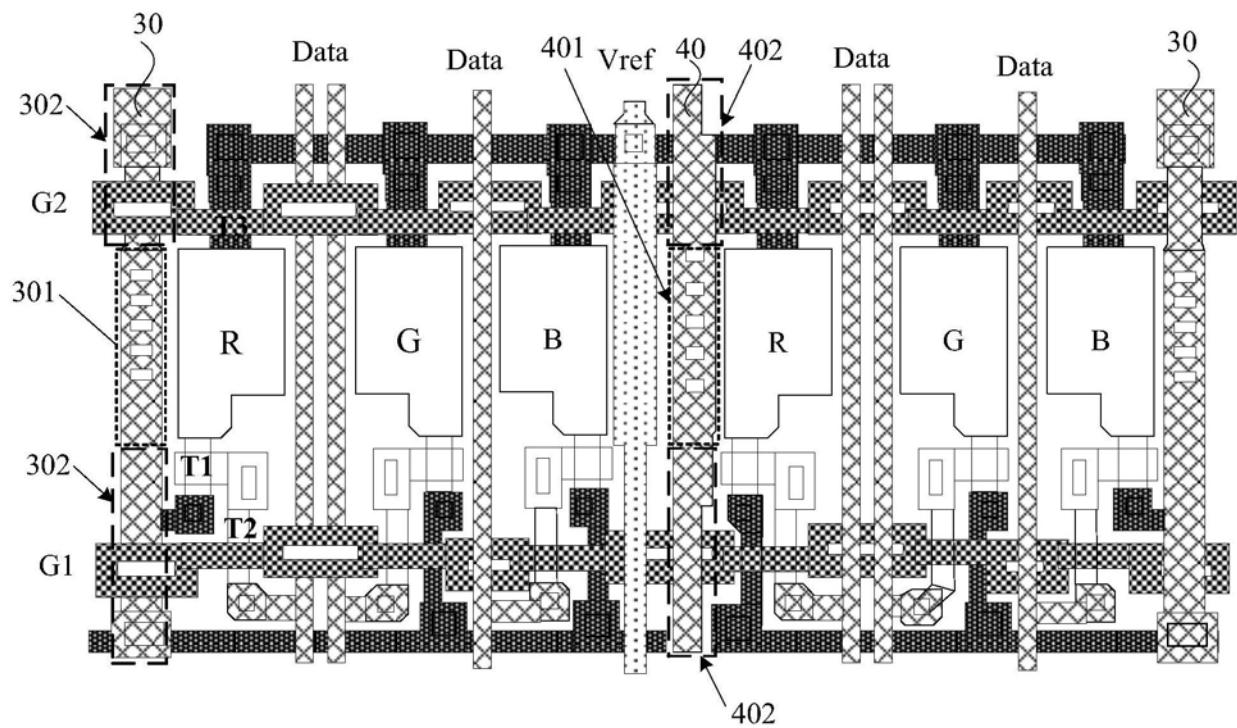

[0049] 本发明实施例提供一种显示用基板11,可以应用于上述的电致发光显示面板1中。如图5、图6、图7、图8以及图9所示,显示用基板11包括多个显示单元20,每个显示单元20包括至少两列像素10;每个像素10包括至少三个亚像素100;每个显示单元20设置至少一条第一电源线(Power Line)30和至少一条第二电源线40;显示单元20中亚像素100均与设置在该显示单元20中的第一电源线30电连接;其中,第一电源线30和第二电源线40设置在不同列像素10中,位于第一电源线30两侧的亚像素100的颜色与位于第二电源线40两侧的亚像素100颜色相同。

[0050] 在一些实施例中,第一电源线30为VDD电源线,第二电源线40为VSS电源线。

[0051] 本领域技术人员应该明白,显示用基板11的亚像素100与电致发光显示面板1的亚像素100是一一正对的。

[0052] 在一些实施例中,每个像素10包括三个亚像素100,分别为红色亚像素(R)、绿色亚像素(G)以及蓝色亚像素(B)。在另一些实施例中,每个像素10包括四个亚像素,分别为红色亚像素、绿色亚像素、蓝色亚像素以及白色亚像素(W)。本发明实施例的附图均以每个像素10包括红色亚像素、绿色亚像素以及蓝色亚像素为例进行示意。

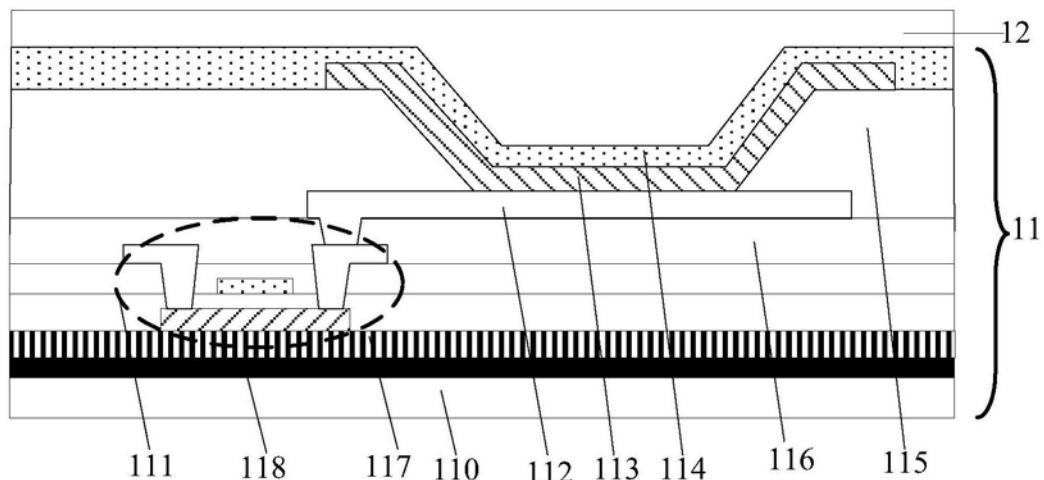

[0053] 如图3所示,上述的显示用基板11的每个亚像素100均包括设置在衬底110上的发光器件和像素电路,像素电路包括多个薄膜晶体管111。发光器件包括依次层叠设置的第一电极层112、发光功能层113以及第二电极层114,第一电极层112和多个薄膜晶体管111中作为驱动晶体管的薄膜晶体管111的漏极电连接。显示用基板11还包括像素界定层115,像素界定层115包括多个开口区,一个发光器件设置在一个开口区中。在一些实施例中,发光功能层113包括发光层(Emitting Layer,简称EL)。在另一些实施例中,发光功能层113除包括发光层外,还包括电子传输层(electron transporting layer,简称ETL)、电子注入层(electron injection layer,简称EIL)、空穴传输层(hole transporting layer,简称HTL)以及空穴注入层(hole injection layer,简称HIL)中的一层或多层。

[0054] 此外,对于形成发光功能层113中各个层的方法不进行限定,例如可以采用打印或蒸镀的方法形成发光功能层113中的各个层。发光层仅位于像素界定层115的开口区,电子传输层、电子注入层、空穴传输层以及空穴注入层可以仅位于像素界定层115的开口区;也可以不仅位于像素界定层115的开口区,而且覆盖像素界定层115,即电子传输层、电子注入层、空穴传输层以及空穴注入层整层设置。

[0055] 例如,发光功能层113中的所有层都通过打印的方法形成,即采用全打印的方法形成发光功能层113,且发光功能层113中的每个层都仅形成在像素界定层115的开口区内。

[0056] 如图3所示,显示用基板11还包括设置在像素电路和第一电极层112之间的平坦层116。

[0057] 此外,薄膜晶体管111可以是顶栅型薄膜晶体管,也可以是低栅型薄膜晶体管。在一些实施例中,如图3所示,显示用基板11还包括依次设置在衬底110上的遮光层(shield)118和缓冲层(Buffer)117,薄膜晶体管111设置在缓冲层117远离衬底110的一侧。

[0058] 在一些实施例中,各个亚像素100中发光器件的第二电极层114是电连接在一起的。可以采用蒸镀的方法同时多个第二电极层114,即形成整面电极。

[0059] 在一些实施例中,第一电极层112为阳极,第二电极层114为阴极。在另一些实施例

中,第一电极层112为阴极,第二电极层114为阳极。

[0060] 此处,第一电源线30的延伸方向、第二电源线40的延伸方向与显示用基板11上数据线的延伸方向相同。显示单元20中亚像素100通过第一辅助连接线与设置在该显示单元20中的第一电源线30电连接。在一些实施例中,第一辅助连接线和第一电源线30分层制作。第一辅助连接线可以和显示用基板11中的导电层同时制作,例如,第一辅助连接线与显示用基板11中设置在顶栅型薄膜晶体管靠近衬底一侧的遮光层118同层同材料,即第一辅助连接线与遮光层118同时制作。

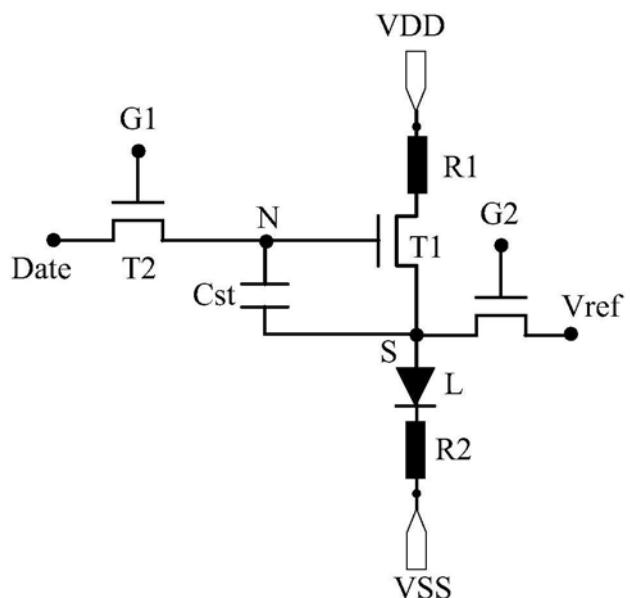

[0061] 在此基础上,对于每个亚像素100中的像素电路不进行限定,可以是2T1C、3T1C、6T1C或7T1C等其它类型的像素电路。此处,  $nTmC$  表示一个像素电路包括  $n$  个薄膜晶体管(用字母“T”表示)和  $m$  个电容(用字母“C”表示)。附图4以像素电路为3T1C像素电路为例进行示意。此外,本领域技术人员应该明白,每个亚像素100的像素电路均包括VDD电压端,在第一电源线30为VDD电源线的情况下,显示单元20中亚像素100的VDD电压端均与设置在该显示单元20中的VDD电源线电连接。

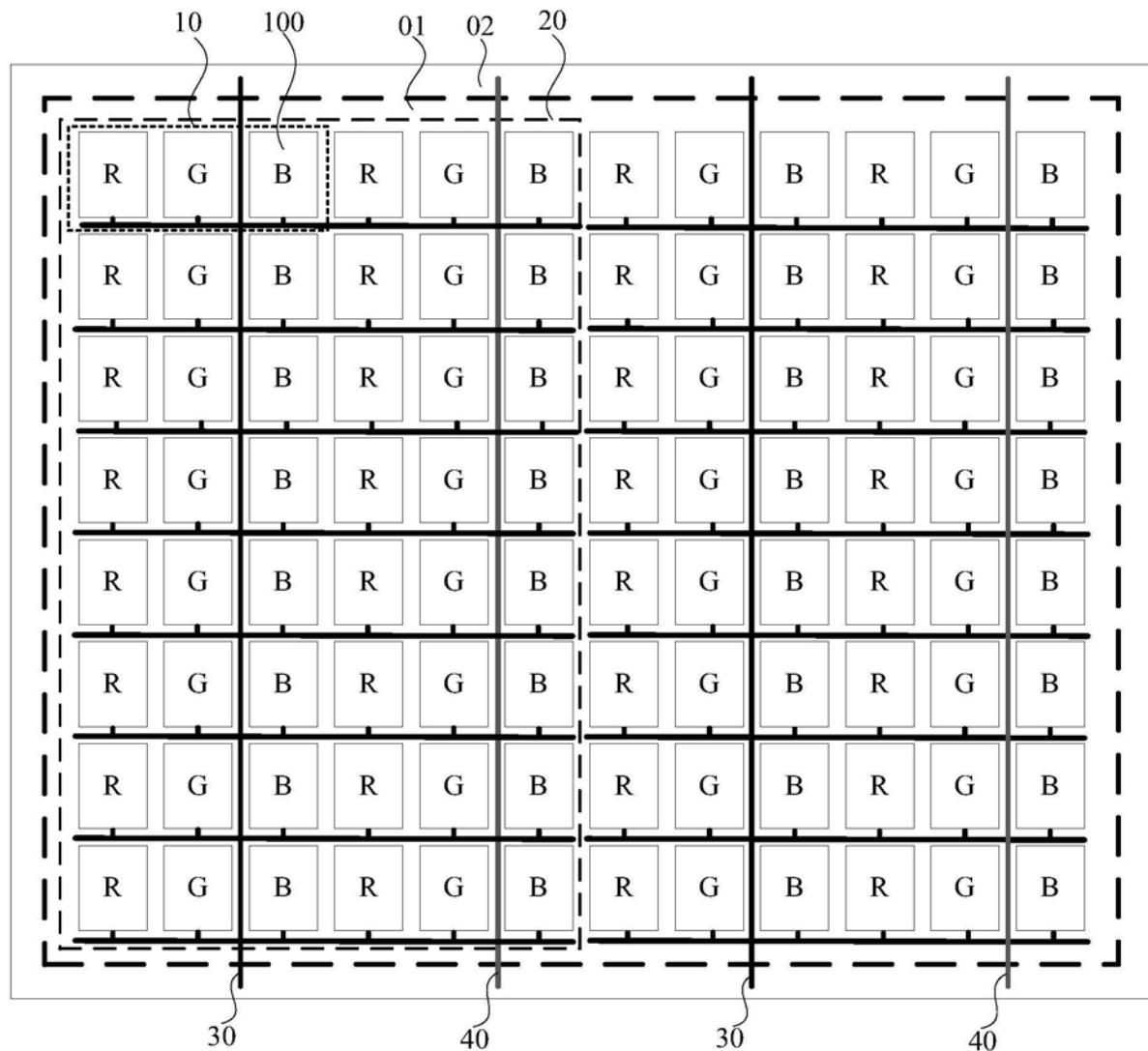

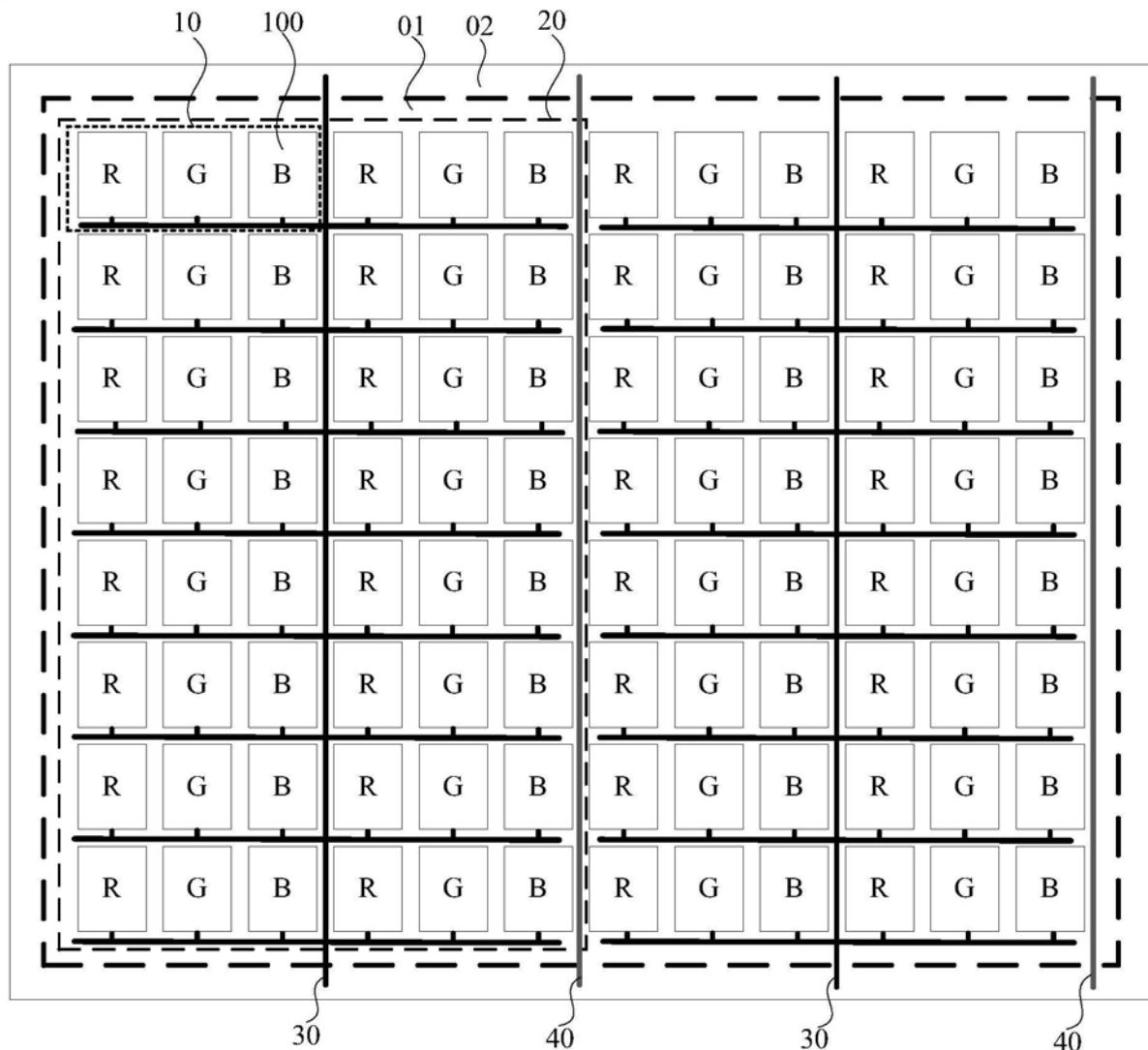

[0062] 此处,每个显示单元20可以如图5和图6所示,包括两列像素10;也可以包括三列或三列以上像素10。附图7、图8以及图9以显示单元20包括三列像素10为例进行示意。此外,每个显示单元20包括的像素10列数可以相同,也可以不相同。

[0063] 对于第一电源线30或第二电源线40在一列像素10中的设置位置不进行限定,可以是如图5所示,第一电源线30和第二电源线40设置在该列像素10中相邻两列亚像素100之间;也可以是如图6所示,第一电源线30和第二电源线40设置在该列像素10中位于最外侧的一列亚像素100的外侧。

[0064] 应当理解到,如图5和图6所示,在显示单元20包括两列像素10的情况下,由于每个显示单元20设置至少一条第一电源线30和至少一条第二电源线40,且第一电源线30和第二电源线40设置在不同列像素10中,因此显示单元20中一列像素10设置一条第一电源线30,另一列像素10设置一条第二电源线40。

[0065] 在显示单元20包括三列或三列以上像素10的情况下,在一些实施例中,显示单元20包括的像素10的列数与该显示单元20中设置的第一电源线30和第二电源线40的条数之和相等。在此情况下,如图7和图8所示,显示单元20中每列像素10设置一条第一电源线30或一条第二电源线40。在另一些实施例中,显示单元20包括的像素10的列数大于该显示单元20中设置的第一电源线30和第二电源线40的条数之和。在此情况下,如图9所示,显示单元20中部分列像素10设置有第一电源线30或第二电源线40,部分列像素10未设置有第一电源线30和第二电源线40。

[0066] 在显示单元20包括三列或三列以上像素10的情况下,对于显示单元20设置的第一电源线30的数量和第二电源线40的数量不进行限定,可以根据需要进行设置。例如,如图7所示,显示单元20包括三列像素10,显示单元20设置两条第一电源线30和一条第二电源线40,第一电源线30和第二电源线40设置在不同列像素10中。又例如,如图8所示,显示单元20包括三列像素10,显示单元20设置一条第一电源线30和两条第二电源线40,第一电源线30和第二电源线40设置在不同列像素10中。

[0067] 如图7所示,在显示单元20包括两条或两条以上第一电源线30的情况下,显示单元20中所有亚像素100可以与设置在该显示单元20中任意一条或几条第一电源线30电连接。

[0068] 应当理解到,位于第一电源线30两侧的亚像素100指的是位于第一电源线30的两侧,且最靠近第一电源线30的亚像素100。位于第二电源线40两侧的亚像素100指的是位于第二电源线40两侧,且最靠近第二电源线40的亚像素100。示例的,如图5所示,位于第一电源线30两侧的亚像素100为蓝色亚像素和绿色亚像素,位于第二电源线40两侧的亚像素100为蓝色亚像素和绿色亚像素。

[0069] 相关技术中的显示用基板11在设计时,如图10所示,每列像素10设置一条第一电源线30,该列像素10中所有亚像素100均与设置在该列像素10中的第一电源线30电连接。由于每列像素10设置一条第一电源线30,会导致第一电源线30的数量较多,为了解决该问题,因而相关技术中的显示用基板11在设计时,如图11所示,两列像素10设置一条第一电源线30,该两列像素10中所有亚像素100均与设置在该两列像素10中的第一电源线30电连接,这样便可以减少第一电源线30的数量。

[0070] 电致发光显示面板1在显示时,在给相同颜色的亚像素100相同信号的情况下,相同颜色的亚像素100发出光一致(包括亮度、色度等一致),才能保证显示的均匀性。影响亚像素100发出光的因素包括薄膜晶体管111的大小、存储电容的大小、像素界定层115开口区的大小以及周边寄生电容的大小等。其中,在制作显示用基板11时,只需要设计相同颜色的亚像素100中薄膜晶体管111的大小、存储电容的大小、像素界定层115开口区的大小以及周边寄生电容的大小一致,就可以确保薄膜晶体管111的大小、存储电容的大小、像素界定层115开口区的大小以及周边寄生电容的大小对相同颜色的亚像素100发出光的影响是相同的。在此基础上,由于第一电源线30上的信号是直流信号,第一电源线30相当于一个电阻R1,电流经过第一电源线30时发热比较严重,因而第一电源线30上信号的大小以及热量会对薄膜晶体管111和发光器件造成影响,因此第一电源线30上信号的大小以及热量也会影响亚像素100发出的光。

[0071] 基于上述,相关技术中,若两列像素10设置一条第一电源线30,则该条第一电源线30会对一列像素10中位于第一电源线30两侧的亚像素100发出的光有影响,而对另一列像素10中亚像素100发出的光没有影响,这样一来,在给相同颜色的亚像素100相同信号的情况下,相同颜色的亚像素100发出的光不一致,从而影响了显示的均匀性,显示效果较差。示例的,参考图11,第一电源线30发出的热量会影响绿色亚像素G1和蓝色亚像素B1发出的光,而不会影响绿色亚像素G2和蓝色亚像素B2发出的光,因此在给绿色亚像素G1和绿色亚像素G2相同信号的情况下,绿色亚像素G1和绿色亚像素G2发光的光不一致,在给蓝色亚像素B1和蓝色亚像素B2相同信号的情况下,蓝色亚像素B1和蓝色亚像素B2发光的光不一致,从而影响了显示的均匀性。

[0072] 本发明实施例提供一种显示用基板11,显示用基板11包括多个显示单元20,每个显示单元20包括至少两列像素10;每个像素10包括至少三个亚像素100;每个显示单元20设置至少一条第一电源线30和至少一条第二电源线40;显示单元20中亚像素100均与设置在该显示单元20中的第一电源线30电连接;第一电源线30和第二电源线40设置在不同列像素10中,位于第一电源线30两侧的亚像素100的颜色与位于第二电源线40两侧的亚像素100颜色相同。由于每个显示单元20包括至少两列像素10,显示单元20设置至少一条第一电源线30和至少一条第二电源线40,且第一电源线30和第二电源线40设置在不同列像素10中,因而相对于每列像素10设置一条第一电源线30,本发明实施例中设置的第一电源线30的数量

减少。

[0073] 在此基础上,由于第一电源线30上信号的大小以及施加信号时第一电源线30发出的热量会影响位于第一电源线30两侧的亚像素100发出的光,第二电源线40上信号的大小以及施加信号时第二电源线40发出的热量会影响位于第二电源线40两侧的亚像素100发出的光,而第一电源线30和第二电源线40设置在不同列像素10中,且位于第一电源线30两侧的亚像素100的颜色与位于第二电源线40两侧的亚像素100颜色相同,因而在给相同颜色的亚像素施加相同信号的情况下,可以确保设置有第一电源线30和第二电源线40的像素10中相同颜色的亚像素100发出的光一致,因此改善了减少第一电源线30,导致的相同颜色的亚像素发光不一致的问题,改善了显示均匀性,提高了显示效果。

[0074] 示例的,参考图5,以显示单元20包括两列像素10,一条第一电源线30设置在一列像素10的绿色亚像素和蓝色亚像素之间,一条第二电源线40设置在另一列像素10的绿色亚像素和蓝色亚像素之间为例,第一电源线30上信号的大小以及施加信号时第一电源线30发出的热量会影响设置在第一电源线30两侧的绿色亚像素和蓝色亚像素发出的光。由于增加第二电源线40后,第二电源线40上信号的大小以及施加信号时第二电源线40发出的热量会影响设置在第二电源线40两侧的绿色亚像素和蓝色亚像素发出的光,因此可以确保两列像素10中相同颜色的亚像素100发出的光一致或近似一致。

[0075] 基于上述,对于第一电源线30和第二电源线40上信号的大小不进行限定,施加到第一电源线30上信号的大小可以根据亚像素100显示的需要进行相应选择。在电致发光显示面板1的使用过程中,在一些实施例中,施加到第一电源线30上信号的大小与施加到第二电源线40上信号的大小相同。

[0076] 考虑到若部分列像素10设置有第一电源线30或第二电源线40,部分列像素10未设置有第一电源线30和第二电源线40,则对于相同颜色亚像素100,在施加信号相同的情况下,设置有第一电源线30或第二电源线40的像素10中位于第一电源线30或第二电源线40两侧的亚像素100发出光和未设置有第一电源线30或第二电源线40的像素10中亚像素100发出光会不一致,从而会影响显示的均匀性。基于此,在一些实施例中,如图5、图6、图7以及图8所示,每列像素10设置一条第一电源线30或一条第二电源线40。

[0077] 本发明实施例中,由于每列像素10设置一条第一电源线30或一条第二电源线40,且位于第一电源线30两侧的亚像素100的颜色与位于第二电源线40两侧的亚像素100颜色相同,因而不同列像素10中位于第一电源线30或第二电源线40两侧,相同颜色的亚像素100发出的光都会受到第一电源线30或第二电源线40上信号或施加信号时发出热量的影响,进一步确保了相同颜色的亚像素100发出光的一致性,提高了显示均匀性。

[0078] 在一些实施例中,第二电源线40的电阻等于第一电源线30的电阻。

[0079] 本发明实施例中,由于第二电源线40上的电阻等于第一电源线30上的电阻,因而第二电源线40产生的热量与第一电源线30产生的热量相同,这样一来,第二电源线40和第一电源线30产生的热量对位于第二电源线40和第一电源线30两侧相同颜色的亚像素100发出光的影响是相同的。

[0080] 基于上述,在施加到第一电源线30上信号的大小与施加到第二电源线40上信号的大小相同,且第二电源线40的电阻等于第一电源线30的电阻的情况下,第一电源线30对位于第一电源线30两侧的亚像素100发出光的影响和第二电源线40对位于第二电源线40两侧

的亚像素100发出光的影响基本相同的。

[0081] 在一些实施例中,每个显示单元20包括像素10的列数相同;每个显示单元20设置的第一电源线30的条数相同。

[0082] 例如,每个显示单元20均包括三列像素10,每个显示单元20设置1条或2条第一电源线30。

[0083] 本发明实施例,由于每个显示单元20包括像素10的列数相同,且每个显示单元20设置的第一电源线30的条数相同,因而将每个显示单元20看做一个整体,每个显示单元20发出的光都是均匀的。

[0084] 在一些实施例中,如图5、图6以及图8所示,显示单元20包括n列像素10;每个显示单元20设置1条第一电源线30,设置n-1条第二电源线40;其中,n≥2,n为正整数。

[0085] 由于每个显示单元20只有一列像素10设置1条第一电源线30,其余列像素10均设置第二电源线40,因而可以极大地减小第一电源线30的数量。显示用基板11会绑定多个IC (Integrated Circuit, 集成电路), 显示用基板11的第一电源线30会与其中的至少一个IC 进行绑定, 由于一个芯片能绑定的第一电源线30的数量有限, 因此若第一电源线30的数量较多, 则需要绑定的IC的数量较多, 本发明实施例由于极大地减小了第一电源线30的数量, 因此能够使得与第一电源线30绑定的IC的数量减小。

[0086] 在此基础上, 在一些实施例中, 相邻第一电源线30之间设置的像素10的列数相同。

[0087] 应当理解到, 在第一电源线30设置在像素10中相邻两列亚像素100的情况下, 计算相邻第一电源线30之间设置的像素10列数时, 应不包括该列像素10。

[0088] 本发明实施例, 由于相邻第一电源线30之间设置的像素10的列数相同, 因而显示用基板11上的第一电源线30是均匀分布的, 进一步确保了第一电源线30对亚像素100发出光的影响是均匀的, 进一步提高了电致发光显示面板1的显示均匀性。

[0089] 在一些实施例中, 第二电极层114为透明或半透明电极, 发光功能层113发出的光从第二电极层114出射, 在此情况下, 电致发光显示装置为顶发射型电致发光显示装置。

[0090] 在第二电极层114为透明或半透明电极的情况下, 第二电极层114的材料一般为ITO(氧化铟锡, Indium Tin Oxide)、IZO(氧化铟锌, Indium Zinc Oxide)或IGZO(Indium Gallium Zinc Oxide, 钨镓锌氧化物)等, 由于第二电极层114的电阻较大, 因而IR Drop(电压降)较大, 从而导致电致发光显示面板1发出的光不均匀。基于此, 在一些实施例中, 第二电源线40与第二电极层114电连接。

[0091] 由于第二电源线40与第二电极层114电连接, 因而相当于给第二电极层114并联一个电阻, 从而可以降低第二电极层114的电阻, 减小IR Drop。

[0092] 在此基础上, 参考图4, 在第一电源线30为VDD电源线, 第二电源线40与第二电极层114电连接的情况下, VDD电源线上的电流信号经过像素电路中的VDD电压端、发光器件流向第二电极层114和第二电源线40, 由于第二电极层114的电阻较大, 第二电极层114上的电流较小, 可以忽略不考虑, 因而可以认为VDD电源线(即第一电源线30)上电流信号的大小与第二电源线40上电流信号的大小相同, 因此第一电源线30上的电流信号与第二电源线40上的电流信号对位于第一电源线30和第二电源线40两侧的亚像素100发出光的影响是相同的。

[0093] 在一些实施例中, 第二电源线40的电阻与沿垂直于衬底110的方向, 第二电极层114中与该第二电源线40重叠部分的电阻并联后的电阻之和等于第一电源线30的电阻的

0.9~1.1倍。

[0094] 例如,第二电源线40的电阻与沿垂直于衬底110的方向,第二电极层114中与该第二电源线40重叠部分的电阻并联后的电阻之和等于第一电源线30的电阻。又例如,第二电源线40的电阻与沿垂直于衬底110的方向,第二电极层114中与该第二电源线40重叠部分的电阻并联后的电阻之和等于第一电源线30的电阻0.9倍或1.1倍。

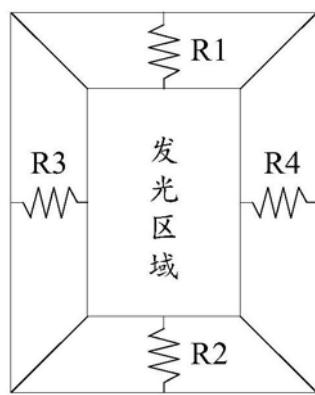

[0095] 附图4中R1为第一电源线30的电阻,R2为第二电源线40的电阻与沿垂直于衬底110的方向,第二电极层114中与该第二电源线40重叠部分的电阻并联后的电阻之和。

[0096] 本发明实施例中,在第一电源线30为VDD电源线的情况下,由于第二电源线40与第二电极层114电连接,因而第一电源线30上的电流信号的大小与第二电源线40上的电流信号的大小相同,且第二电源线40的电阻与沿垂直于衬底110的方向,第二电极层114中与该第二电源线40重叠部分的电阻并联后的电阻之和等于第一电源线30的电阻的0.9~1.1倍,因此第一电源线30产生的热量与第二电源线40产生的热量相同或相近,从而确保了第一电源线30与第二电源线40对亚像素100发出光的影响是基本一致的,更有利提高显示均匀性。

[0097] 多个发光器件的第二电极层114连接在一起构成透明面电极,透明面电极的点校阻抗有多种近似等效方式,比较简化的是整面的透明面电极等效成上下左右四个电阻(等效的电阻越多越精确)。如图12所示,每个亚像素100中的第二电极层114的电阻都可以等效为上下左右四个电阻,通过积分的方式,可以算出R1、R2、R3以及R4的电阻,亚像素100的中间的发光区域可等效为一个电流源(所述电流源用于为该亚像素电流提供电流)。

[0098] 附图13a和图13b示意出两个像素10,每个像素10包括红色亚像素、绿色亚像素和蓝色亚像素,每个亚像素100的像素电路如图4所示。附图13a或图13b的像素版图中电阻等效后的电阻网络图如图14所示。如图14所示,每个亚像素100中的第二电极层114的电阻可以等效为上下左右四个电阻,一个像素10内的一条第一电源线30等效为一个电阻,一个像素10内的一条第二电源线40等效为一个电阻。

[0099] 附图13a和图13b中的Vref线(也可以称为Sense线)用于提供参考电位,检测像素电路的电流或电压,用于对图4中所示的驱动晶体管的阈值电压进行补偿。Vref线的延伸方向与数据线的延伸方向相同,显示用基板11中的亚像素100通过第二辅助连接线与Vref线电连接。在一些实施例中,第二辅助连接线和Vref线分层制作。第二辅助连接线可以和显示用基板11中的导电层同时制作,例如,第二辅助连接线与遮光层118同层同材料,即第二辅助连接线与遮光层118同时制作。

[0100] 从如图14所示的电阻等效图可以看出,电流主要经过第一电源线30、第二电源线40以及沿垂直于衬底110的方向,第二电极层114中与该第二电源线40重叠的部分。因此,第一电源线30的电阻Rvdd等于第二电源线40的电阻Raux与沿垂直于衬底110的方向,第二电极层114中与该第二电源线40重叠部分的电阻Rcathode并联后的电阻之和Rvss,即Rvdd=Rvss=Raux//Rcathode,“//”表示并联。

[0101] 基于此,根据Rvdd=Rvss=Raux//Rcathode可知,第一电源线30的电阻Rvdd与第二电源线40的电阻Raux的相对关系为:Rvdd=k×Raux,其中,k与第二电源线40的材料及厚度有关,k大于1。

[0102] 由于第二电极层114的电阻非常大,因而第二电源线40的电阻与沿垂直于衬底110的方向,第二电极层114中与该第二电源线40重叠部分的电阻并联后的电阻之和与第二电

源线40的电阻相近,因此在一些实施例中,可以忽略沿垂直于衬底110的方向,第二电极层114中与该第二电源线40重叠部分的电阻,这样一来,显示用基板11在实际设计时,只需考虑使第二电源线40的电阻即可。在一些实施例中,一条第二电源线40的电阻等于一条第一电源线30的电阻的0.9~1.1倍。

[0103] 例如,一条第二电源线40的电阻等于一条第一电源线30的电阻。又例如,一条第二电源线40的电阻等于一条第一电源线30的电阻的0.9倍或1.1倍。

[0104] 本发明实施例中,第二电源线40可以与显示用基板11上已有的走线同时制作,也可以单独制作,此处不进行限定。

[0105] 在一些实施例中,第一电源线30和第二电源线40同层同材料。

[0106] 本发明实施例,由于第一电源线30和第二电源线40同层同材料,因而可以同时制作第一电源线30和第二电源线40,从而简化了显示用基板11的制作工艺。

[0107] 显示用基板11还包括数据线(Date)、栅线(Gate)以及其它信号线。

[0108] 应当理解到,每列亚像素100设置一条数据线,在每个显示单元20包括两列像素10,每个像素10包括沿行方向排列的三个亚像素100的情况下,显示用基板11中第一电源线30与数据线的数量之比为1:6。

[0109] 在一些实施例中,第一电源线30和第二电源线40均与数据线同层同材料。

[0110] 本发明实施例中,由于第一电源线30和第二电源线40均与数据线同层同材料,因而可以在制作数据线的同时,制作第一电源线30和第二电源线40,不会因增加第二电源线40而增加工艺,从而简化了显示用基板11的制作工艺。

[0111] 应当理解到,在第一电源线30和第二电源线40同层同材料的情况下,第一电源线30的材料和第二电源线40的材料相同,且第一电源线30的厚度和第二电源线40的厚度相同。

[0112] 在第一电源线30和第二电源线40同层同材料的情况下,由于第一电源线30的材料和第二电源线40的材料相同,且第一电源线30的厚度和第二电源线40的厚度相同,若第一电源线30的线宽大于第二电源线40的线宽,则第二电源线40的电阻大于第一电源线30的电阻。

[0113] 在第一电源线30的电阻等于第二电源线40上的电阻与沿垂直于衬底110的方向,第二电极层114中与该第二电源线40重叠部分的电阻并联后的电阻之和的情况下,第一电源线30的电阻小于第二电源线40上的电阻。在第一电源线30和第二电源线40同层同材料的情况下,在设计第一电源线30和第二电源线40时,只需要满足第一电源线30的线宽大于第二电源线40的线宽,就可以使第一电源线30的电阻小于第二电源线40的电阻。

[0114] 基于上述,在一些实施例中,第一电源线30的线宽大于或等于第二电源线40的线宽。

[0115] 应当理解到,显示用基板11上除了设置有第一电源线30和第二电源线40外,还设置有其它走线,例如栅线、数据线等,为了给其它走线布线提供空间,因此沿第一电源线30的延伸方向,第一电源线30位于不同区域的线宽会有差异,即第一电源线30有的部分的线宽较宽,有的部分的线宽较窄。同样的,第二电源线40有的部分的线宽较宽,有的部分的线宽较窄。

[0116] 在本发明的一些实施例中,第一电源线30的线宽指的是第一电源线30的线宽的平

均值,第二电源线40的线宽指的是第二电源线40的线宽的平均值。

[0117] 此处,在第一电源线30的线宽大于第二电源线40的线宽的情况下,对于第一电源线30的线宽与第二电源线40的线宽的差值不进行限定,可以根据第一电源线30的电阻与第二电源线40的电阻的差值,相应设计第一电源线30的线宽与第二电源线40的线宽,以使第一电源线30的电阻等于或近似等于第二电源线40的电阻与沿垂直于衬底110的方向,第二电极层114中与该第二电源线40重叠部分的电阻并联后的电阻之和。

[0118] 本发明实施例,在第一电源线30和第二电源线40同层同材料的情况下,第二电源线40的线宽等于第一电源线30的线宽,第二电源线40的电阻等于第一电源线30的电阻。在制作显示用基板11时,在不考虑第二电极层114的电阻的情况下,若要求第二电源线40的电阻与第一电源线30的电阻相等,则只需设计第二电源线40的线宽等于第一电源线30的线宽即可。

[0119] 基于上述,在第一电源线30和第二电源线40同层同材料的情况下,在一些实施例中,第二电源线40的线宽等于第一电源线30的线宽。

[0120] 在一些实施例中,如图13a和图13b所示,第一电源线30包括第一部分301和第二部分302,第二电源线40包括第三部分401和第四部分402;第一部分301和第三部分401均位于相邻两个亚像素100的像素开口区之间;第一部分301的线宽与第三部分401的线宽的差值范围为0~1μm。

[0121] 其中,第一电源线30的第一部分301的线宽和第二部分302的线宽不相同,第二电源线40的第三部分401的线宽和第四部分402的线宽不相同。

[0122] 例如,第一部分301的线宽与第三部分401的线宽的差值可以为0、0.5μm、0.8μm或1μm等。

[0123] 以上所述,仅为本发明的具体实施方式,但本发明的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本发明揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本发明的保护范围之内。因此,本发明的保护范围应以所述权利要求的保护范围为准。

图1

图2

1

图3

图4

11

图5

11

图6

11

图7

11

图8

11

图9

11

图10

11

图11

图12

图13a

图13b

图14

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种显示用基板及电致发光显示装置                               |         |            |

| 公开(公告)号        | <a href="#">CN110911468A</a>                   | 公开(公告)日 | 2020-03-24 |

| 申请号            | CN201911269539.6                               | 申请日     | 2019-12-11 |

| [标]申请(专利权)人(译) | 京东方科技股份有限公司                                    |         |            |

| 申请(专利权)人(译)    | 京东方科技股份有限公司                                    |         |            |

| 当前申请(专利权)人(译)  | 京东方科技股份有限公司                                    |         |            |

| [标]发明人         | 徐攀<br>李永谦<br>张大成<br>刘烺                         |         |            |

| 发明人            | 徐攀<br>李永谦<br>张大成<br>刘烺                         |         |            |

| IPC分类号         | H01L27/32                                      |         |            |

| CPC分类号         | H01L27/3218 H01L27/3276                        |         |            |

| 代理人(译)         | 申健                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

**摘要(译)**

本发明实施例提供一种显示用基板及电致发光显示装置，涉及显示技术领域，可以改善减少第一电源线，导致相同颜色的亚像素发光不一致的问题。该显示用基板包括多个显示单元，每个所述显示单元包括至少两列像素；所述像素包括至少三个亚像素；每个所述显示单元设置至少一条第一电源线和至少一条第二电源线；所述显示单元中所述亚像素均与设置在该所述显示单元中的所述第一电源线电连接；所述第一电源线和所述第二电源线设置在不同列像素中，位于所述第一电源线两侧的所述亚像素的颜色与位于所述第二电源线两侧的所述亚像素颜色相同。用于电致发光显示装置中。