(12)发明专利申请

(10)申请公布号 CN 107819012 A

(43)申请公布日 2018.03.20

(21)申请号 201710936407.9

H01L 29/786(2006.01)

(22)申请日 2017.10.10

H01L 21/77(2017.01)

(71)申请人 武汉华星光电半导体显示技术有限公司

地址 430000 湖北省武汉市东湖新技术开发区高新大道666号光谷生物创新园C5栋305室

(72)发明人 喻蕾 李松杉

(74)专利代理机构 深圳汇智容达专利商标事务所(普通合伙) 44238

代理人 潘中毅 熊贤卿

(51)Int.Cl.

H01L 27/32(2006.01)

H01L 29/423(2006.01)

H01L 21/336(2006.01)

权利要求书3页 说明书7页 附图5页

(54)发明名称

N型薄膜晶体管及其制备方法、OLED显示面板及其制备方法

(57)摘要

本发明提供一种N型薄膜晶体管及其制备方法、OLED显示面板及其制备方法，薄膜晶体管由下至上包括：多晶硅层、栅极层、源极、漏极；其中，多晶硅层包括沟道区，以及沟道区两侧的源极区和漏极区，栅极层位于沟道区上方，且栅极层在多晶硅层上的投影与源极区和漏极区部分重合，源极区和漏极区上方的栅极层厚度，均小于沟道区上方的栅极层厚度；且源极区和漏极区均包含重掺杂区和与重掺杂区连接的轻掺杂区，轻掺杂区均位于栅极层下方，源极位于源极区的重掺杂区上方且与源极区的重掺杂区电性连接，漏极位于漏极区的重掺杂区上方且与漏极区的重掺杂区电性连接。本发明可以减小薄膜晶体管的漏电流，改善薄膜晶体管的器件特性。

1. 一种N型薄膜晶体管，其特征在于，由下至上包括：多晶硅层、栅极层、源极、漏极；

其中，所述多晶硅层包括沟道区，以及所述沟道区两侧的源极区和漏极区，所述栅极层位于所述沟道区上方，且所述栅极层在所述多晶硅层上的投影与所述源极区和所述漏极区部分重合，所述源极区和所述漏极区上方的栅极层厚度，均小于所述沟道区上方的栅极层厚度；

所述源极区和所述漏极区均包含重参杂区和与所述重参杂区连接的轻参杂区，所述轻参杂区均位于所述栅极层下方，所述源极位于所述源极区的重参杂区上方且与所述源极区的重参杂区电性连接，所述漏极位于所述漏极区的重参杂区上方且与所述漏极区的重参杂区电性连接。

2. 根据权利要求1所述的N型薄膜晶体管，其特征在于，

所述重参杂区和所述轻参杂区掺杂的离子均为磷离子；

所述多晶硅层与所述栅极层之间还设置有栅极绝缘层；

所述栅极绝缘层上还设置有介电层，且所述介电层覆盖所述栅极层，所述介电层包含SiNx和/或SiOy，其中， $x \geq 1, y \geq 1$ ；

所述介电层上设置有两个第一连接孔，所述栅极绝缘层上设置有两个第二连接孔，两个所述第一连接孔分别与两个所述第二连接孔正对，且两个所述第二连接孔分别与所述源极区的重参杂区和所述漏极区的重参杂区正对；

所述源极和所述漏极均设置在所述介电层上，且所述源极通过所述第一连接孔和所述第二连接孔，与所述源极区的重参杂区电性连接，所述漏极通过所述第一连接孔和所述第二连接孔，与所述漏极区的重参杂区电性连接。

3. 一种OLED显示面板，其特征在于，包括权利要求1或2所述的N型薄膜晶体管；

所述薄膜晶体管的多晶硅层下方设置有基板；

所述薄膜晶体管的介电层上方设置有平坦层，且所述平坦层覆盖所述薄膜晶体管的源极和漏极，所述平坦层上设置有第三连接孔，所述第三连接孔位于所述源极或者所述漏极上方，所述第三连接孔中设置有阳极，所述阳极与所述源极或者所述漏极电性连接；

所述平坦层上方设置有像素定义层，所述像素定义层上设置有第四连接孔，且所述第四连接孔位于所述阳极上方，所述第四连接孔中设置有机发光材料，所述有机发光材料与所述阳极接触。

4. 根据权利要求3所述的OLED显示面板，其特征在于，所述基板与所述多晶硅层之间设置有缓冲层，且所述缓冲层包含SiNx和/或SiOy，其中， $x \geq 1, y \geq 1$ 。

5. 一种N型薄膜晶体管的制备方法，其特征在于，包括下述步骤：

在基板上方形成多晶硅层；

图形化所述多晶硅层，形成沟道区，以及位于所述沟道区两侧的源极区和漏极区；

在所述多晶硅层上方形成栅极层，所述栅极层位于所述沟道区上方，且所述栅极层在所述多晶硅层上的投影，与所述源极区和所述漏极区部分重合；

图形化所述栅极层，使所述源极区和所述漏极区上方的栅极层厚度，均小于所述沟道区上方的栅极层厚度；

以所述栅极层作为离子注入掩膜，向所述源极区和所述漏极区进行离子植入，形成两组参杂区，每一组参杂区包括一个重参杂区和与所述重参杂区相连的轻参杂区；

在两个所述重掺杂区上方制备源极和漏极，且所述源极和所述漏极分别与两个所述重掺杂区电性连接。

6. 根据权利要求5所述的N型薄膜晶体管的制备方法，其特征在于，在所述多晶硅层上方形成栅极层之前，还包括下述步骤：

在所述多晶硅层上形成栅极绝缘层；其中，所述栅极绝缘层位于所述多晶硅层与所述栅极层之间；

在基板上方形成多晶硅层之前，还包括下述步骤：

在所述基板上形成缓冲层，其中，所述缓冲层包含 $\text{SiO}_x$ 和/或 $\text{SiNy}$ ,  $x \geq 1$ ,  $y \geq 1$ ；

在基板上方形成多晶硅层，包括下述步骤：

在所述缓冲层上沉积非晶硅层；

采用准分子镭射结晶的方式将所述非晶硅层转化为所述多晶硅层。

7. 根据权利要求5所述的N型薄膜晶体管的制备方法，其特征在于，图形化所述栅极层，包括下述步骤：

在所述栅极层上涂布光阻；

通过半透掩膜板对所述栅极层进行曝光及显影处理，得到光阻半保留部分，所述光阻半保留部分位于所述源极和所述漏极上方；

将所述栅极层位于所述光阻半保留部分的区域进行部分刻蚀；

向所述源极区和所述漏极区进行离子植入，具体为：

采用离子注入技术，向所述源极区和所述漏极区植入磷离子。

8. 根据权利要求6所述的N型薄膜晶体管的制备方法，其特征在于，在两个所述重掺杂区上方制备源极和漏极，包括下述步骤：

在所述栅极绝缘层上形成介电层，且所述介电层覆盖所述栅极层；

图形化所述介电层和所述栅极绝缘层，在所述介电层上形成两个第一连接孔，在所述栅极绝缘层上形成两个第二连接孔，且两个所述第一连接孔分别与两个所述第二连接孔正对，两个所述第二连接孔分别与两个所述重掺杂区正对；

在所述介电层上沉积金属层，且所述金属层均通过两个所述第一连接孔和两个所述第二连接孔，与两个所述重掺杂区电性连接；

图形化所述金属层，形成所述源极和所述漏极；

在所述栅极绝缘层上形成介电层，具体为：

采用等离子体增强化学的气相沉积法，在所述栅极绝缘层上沉积 $\text{SiNx}$ 和/或 $\text{SiOy}$ ，形成所述介电层；

在图形化所述介电层和所述栅极绝缘层之前还包括下述步骤：

对所述介电层进行快速退火处理，其中快速退火的温度为550~600摄氏度，退火时间为5~15分钟；

在所述介电层上沉积金属层，具体为：

采用物理气相沉积的方式，在所述介电层上依次沉积钼、铝、钼金属，形成所述金属层。

9. 一种OLED显示面板的制备方法，其特征在于，包括权利要求5~8任一项所述的N型薄膜晶体管的制备方法，还包括下述步骤：

在介电层上形成平坦层，且所述平坦层覆盖源极和漏极；

图形化所述平坦层，在所述平坦层上形成第三连接孔，所述第三连接孔位于所述源极或者所述漏极上方；

在所述第三连接孔处制备阳极，且所述阳极与所述源极或者所述漏极电性连接；

在所述平坦层上沉积像素定义层，且所述像素定义层覆盖所述阳极；

图形化所述像素定义层，在所述像素定义层上形成第四连接孔，且所述第四连接孔位于所述阳极上方；

在所述第四连接孔处蒸镀有机发光材料，且所述有机发光材料与所述阳极接触。

10. 根据权利要求9所述的OLED显示面板的制备方法，其特征在于，

在所述第三连接孔处制备阳极，具体为：

在所述第三连接孔处沉积铟锡氧化物，并将所述铟锡氧化物图形化形成所述阳极；

所述平坦层和所述像素定义层的材料均为聚酰亚胺。

## N型薄膜晶体管及其制备方法、OLED显示面板及其制备方法

### 技术领域

[0001] 本发明涉及显示技术领域，尤其涉及一种N型薄膜晶体管及其制备方法、OLED显示面板及其制备方法。

### 背景技术

[0002] 传统的方法制作低温多晶硅N型薄膜晶体管时，是在完成多晶硅的结晶和图形定义后，在制作N+区域(即重掺杂区)和N-区域(N-区域又称为LDD:light drain doping,轻掺杂漏结构)，需要使用两次掩膜板分别定义N+和N-区域，再进行两次磷离子的植入，再利用等离子体增强化学的气相沉积法沉积一层栅极绝缘层；传统的方法制作低温多晶硅N型薄膜晶体管工艺流程复杂，制作成本高，并且传统的方法制作出来的N型薄膜晶体管中的栅极层厚度均匀，在该薄膜晶体管处于关态时，任有较大的漏电流，导致该薄膜晶体管的关断与接通不是很灵敏，对显示面板的显示效果造成影响。

### 发明内容

[0003] 为解决上述技术问题，本发明提供一种N型薄膜晶体管及其制备方法、OLED显示面板及其制备方法，可以减小薄膜晶体管的漏电流，改善薄膜晶体管的器件特性。

[0004] 本发明提供的一种N型薄膜晶体管，由下至上包括：多晶硅层、栅极层、源极、漏极；

[0005] 其中，所述多晶硅层包括沟道区，以及所述沟道区两侧的源极区和漏极区，所述栅极层位于所述沟道区上方，且所述栅极层在所述多晶硅层上的投影与所述源极区和所述漏极区部分重合，所述源极区和所述漏极区上方的栅极层厚度，均小于所述沟道区上方的栅极层厚度；

[0006] 所述源极区和所述漏极区均包含重掺杂区和与所述重掺杂区连接的轻掺杂区，所述轻掺杂区均位于所述栅极层下方，所述源极位于所述源极区的重掺杂区上方且与所述源极区的重掺杂区电性连接，所述漏极位于所述漏极区的重掺杂区上方且与所述漏极区的重掺杂区电性连接。

[0007] 优选地，所述重掺杂区和所述轻掺杂区掺杂的离子均为磷离子；

[0008] 所述多晶硅层与所述栅极层之间还设置有栅极绝缘层；

[0009] 所述栅极绝缘层上还设置有介电层，且所述介电层覆盖所述栅极层，所述介电层包含SiNx和/或SiOy，其中， $x \geq 1, y \geq 1$ ；

[0010] 所述介电层上设置有两个第一连接孔，所述栅极绝缘层上设置有两个第二连接孔，两个所述第一连接孔分别与两个所述第二连接孔正对，且两个所述第二连接孔分别与所述源极区的重掺杂区和所述漏极区的重掺杂区正对；

[0011] 所述源极和所述漏极均设置在所述介电层上，且所述源极通过所述第一连接孔和所述第二连接孔，与所述源极区的重掺杂区电性连接，所述漏极通过所述第一连接孔和所述第二连接孔，与所述漏极区的重掺杂区电性连接。

[0012] 本发明还提供一种OLED显示面板，包括上述的N型薄膜晶体管；

- [0013] 所述薄膜晶体管的多晶硅层下方设置有基板；

- [0014] 所述薄膜晶体管的介电层上方设置有平坦层，且所述平坦层覆盖所述薄膜晶体管的源极和漏极，所述平坦层上设置有第三连接孔，所述第三连接孔位于所述源极或者所述漏极上方，所述第三连接孔中设置有阳极，所述阳极与所述源极或者所述漏极电性连接；

- [0015] 所述平坦层上方设置有像素定义层，所述像素定义层上设置有第四连接孔，且所述第四连接孔位于所述阳极上方，所述第四连接孔中设置有有机发光材料，所述有机发光材料与所述阳极接触。

- [0016] 优选地，所述基板与所述多晶硅层之间设置有缓冲层，且所述缓冲层包含SiNx和/或SiOy，其中， $x \geq 1, y \geq 1$ 。

- [0017] 本发明提供一种N型薄膜晶体管的制备方法，包括下述步骤：

- [0018] 在基板上方形成多晶硅层；

- [0019] 图形化所述多晶硅层，形成沟道区，以及位于所述沟道区两侧的源极区和漏极区；

- [0020] 在所述多晶硅层上方形成栅极层，所述栅极层位于所述沟道区上方，且所述栅极层在所述多晶硅层上的投影，与所述源极区和所述漏极区部分重合；

- [0021] 图形化所述栅极层，使所述源极区和所述漏极区上方的栅极层厚度，均小于所述沟道区上方的栅极层厚度；

- [0022] 以所述栅极层作为离子注入掩膜，向所述源极区和所述漏极区进行离子植入，形成两组参杂区，每一组参杂区包括一个重参杂区和与所述重参杂区相连的轻参杂区；

- [0023] 在两个所述重参杂区上方制备源极和漏极，且所述源极和所述漏极分别与两个所述重参杂区电性连接。

- [0024] 优选地，在所述多晶硅层上方形成栅极层之前，还包括下述步骤：

- [0025] 在所述多晶硅层上形成栅极绝缘层；其中，所述栅极绝缘层位于所述多晶硅层与所述栅极层之间；

- [0026] 在基板上方形成多晶硅层之前，还包括下述步骤：

- [0027] 在所述基板上形成缓冲层，其中，所述缓冲层包含SiOx和/或SiNy， $x \geq 1, y \geq 1$ ；

- [0028] 在基板上方形成多晶硅层，包括下述步骤：

- [0029] 在所述缓冲层上沉积非晶硅层；

- [0030] 采用准分子镭射结晶的方式将所述非晶硅层转化为所述多晶硅层。

- [0031] 优选地，图形化所述栅极层，包括下述步骤：

- [0032] 在所述栅极层上涂布光阻；

- [0033] 通过半透掩膜板对所述栅极层进行曝光及显影处理，得到光阻半保留部分，所述光阻半保留部分位于所述源极和所述漏极上方；

- [0034] 将所述栅极层位于所述光阻半保留部分的区域进行部分刻蚀；

- [0035] 向所述源极区和所述漏极区进行离子植入，具体为：

- [0036] 采用离子注入技术，向所述源极区和所述漏极区植入磷离子。

- [0037] 优选地，在两个所述重参杂区上方制备源极和漏极，包括下述步骤：

- [0038] 在所述栅极绝缘层上形成介电层，且所述介电层覆盖所述栅极层；

- [0039] 图形化所述介电层和所述栅极绝缘层，在所述介电层上形成两个第一连接孔，在所述栅极绝缘层上形成两个第二连接孔，且两个所述第一连接孔分别与两个所述第二连接

孔正对，两个所述第二连接孔分别与两个所述重掺杂区正对；

[0040] 在所述介电层上沉积金属层，且所述金属层均通过两个所述第一连接孔和两个所述第二连接孔，与两个所述重掺杂区电性连接；

[0041] 图形化所述金属层，形成所述源极和所述漏极；

[0042] 在所述栅极绝缘层上形成介电层，具体为：

[0043] 采用等离子体增强化学的气相沉积法，在所述栅极绝缘层上沉积SiNx和/或SiOy，形成所述介电层；

[0044] 在图形化所述介电层和所述栅极绝缘层之前还包括下述步骤：

[0045] 对所述介电层进行快速退火处理，其中快速退火的温度为550~600摄氏度，退火时间为5~15分钟；

[0046] 在所述介电层上沉积金属层，具体为：

[0047] 采用物理气相沉积的方式，在所述介电层上依次沉积钼、铝、钼金属，形成所述金属层。

[0048] 本发明还提供一种OLED显示面板的制备方法，包括上述的N型薄膜晶体管的制备方法，还包括下述步骤：

[0049] 在介电层上形成平坦层，且所述平坦层覆盖源极和漏极；

[0050] 图形化所述平坦层，在所述平坦层上形成第三连接孔，所述第三连接孔位于所述源极或者所述漏极上方；

[0051] 在所述第三连接孔处制备阳极，且所述阳极与所述源极或者所述漏极电性连接；

[0052] 在所述平坦层上沉积像素定义层，且所述像素定义层覆盖所述阳极；

[0053] 图形化所述像素定义层，在所述像素定义层上形成第四连接孔，且所述第四连接孔位于所述阳极上方；

[0054] 在所述第四连接孔处蒸镀有机发光材料，且所述有机发光材料与所述阳极接触。

[0055] 优选地，在所述第三连接孔处制备阳极，具体为：

[0056] 在所述第三连接孔处沉积铟锡氧化物，并将所述铟锡氧化物图形化形成所述阳极；

[0057] 所述平坦层和所述像素定义层的材料均为聚酰亚胺。

[0058] 实施本发明，具有如下有益效果：N型薄膜晶体管的轻掺杂区对应的栅极层的厚度较薄，在薄膜晶体管施加工作电压时，该处产生的电场强度也较弱，吸引的电子也较少，因此电阻相对较大，进而起到LDD区域的减小漏电流的作用，从而可以大幅改善该薄膜晶体管的器件特性。

## 附图说明

[0059] 为了更清楚地说明本发明实施例或现有技术中的技术方案，下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍，显而易见地，下面描述中的附图仅仅是本发明的一些实施例，对于本领域普通技术人员来讲，在不付出创造性劳动的前提下，还可以根据这些附图获得其他的附图。

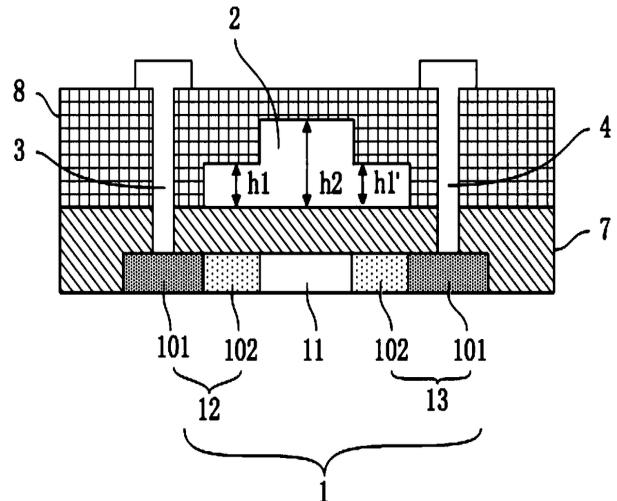

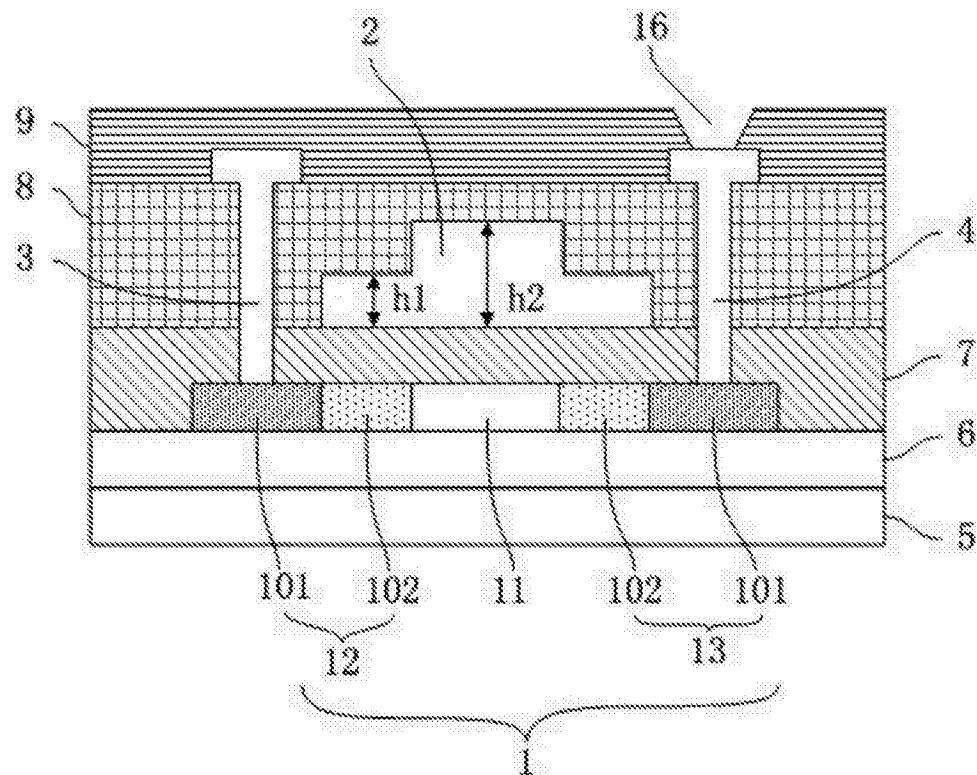

[0060] 图1是本发明提供的N型薄膜晶体管的结构示意图。

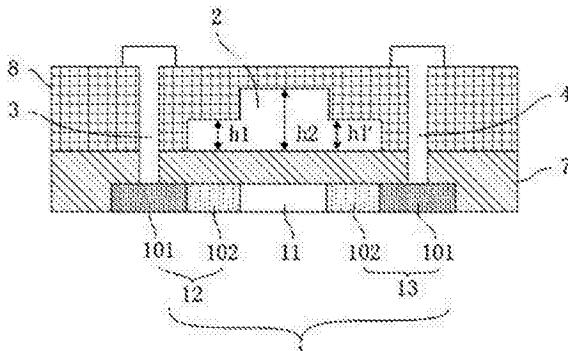

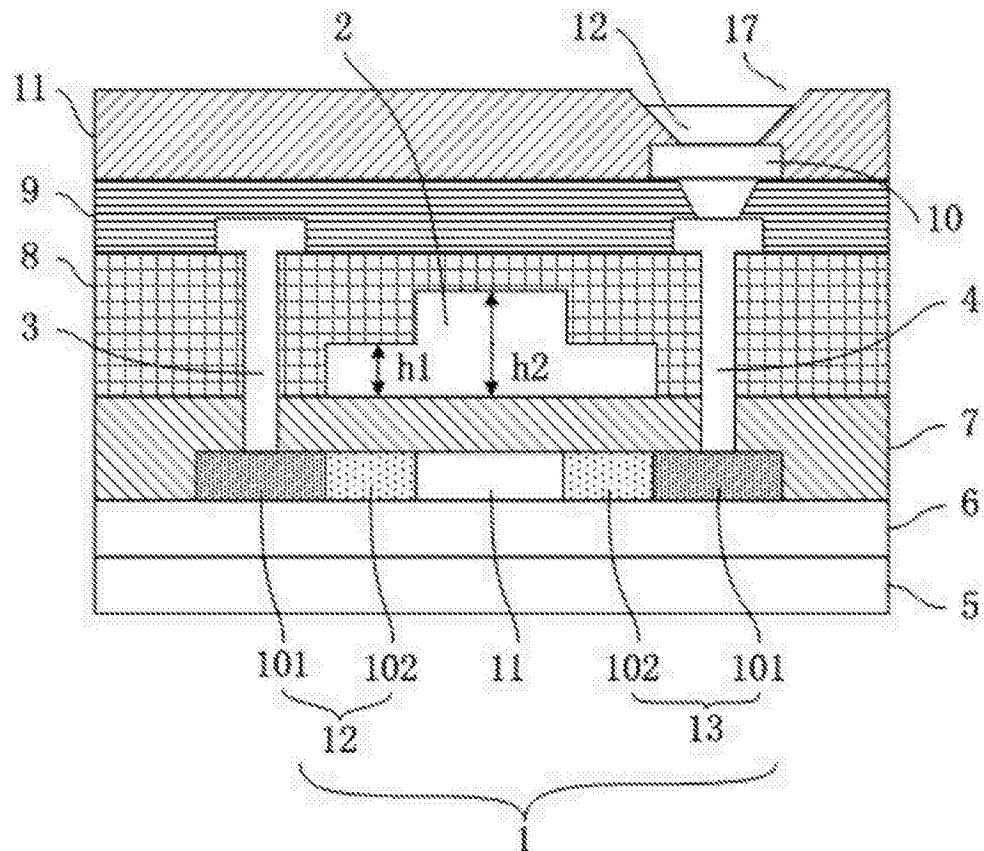

[0061] 图2是本发明提供的N型薄膜晶体管上标注了第一连接孔和第二连接孔的示意图。

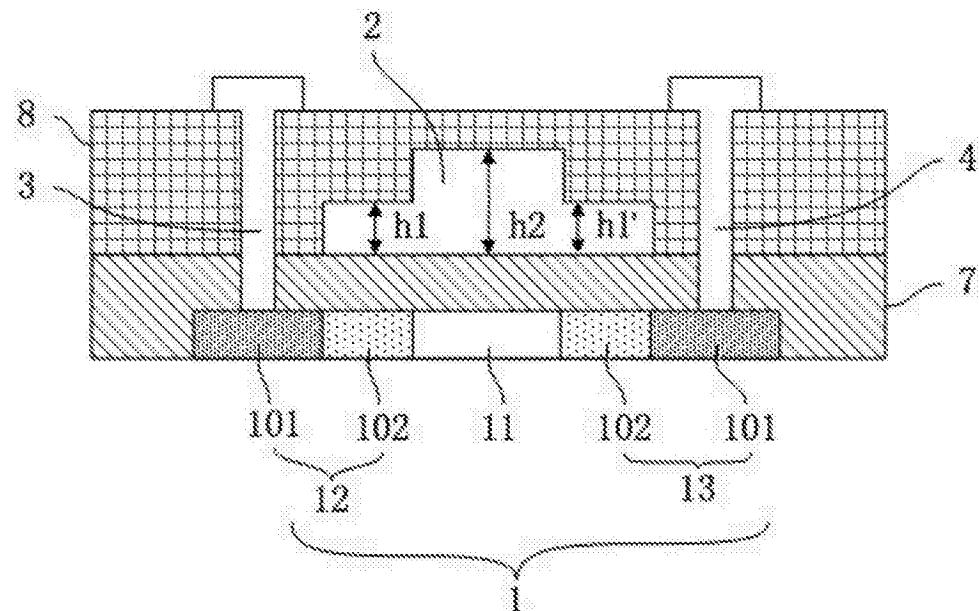

- [0062] 图3是本发明提供的OLED显示面板上标注了第三连接孔的示意图。

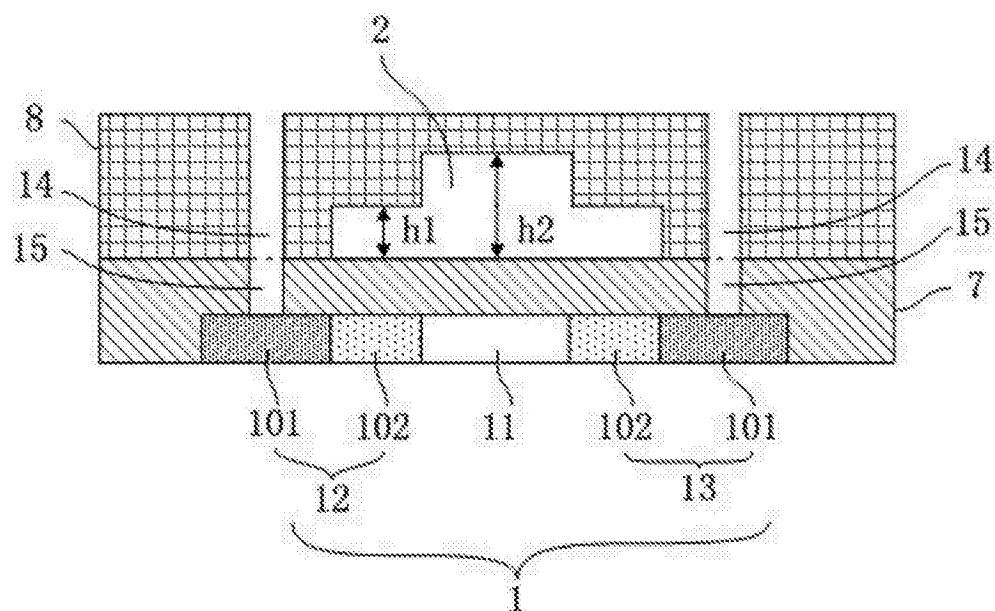

- [0063] 图4是本发明提供的OLED显示面板的结构示意图。

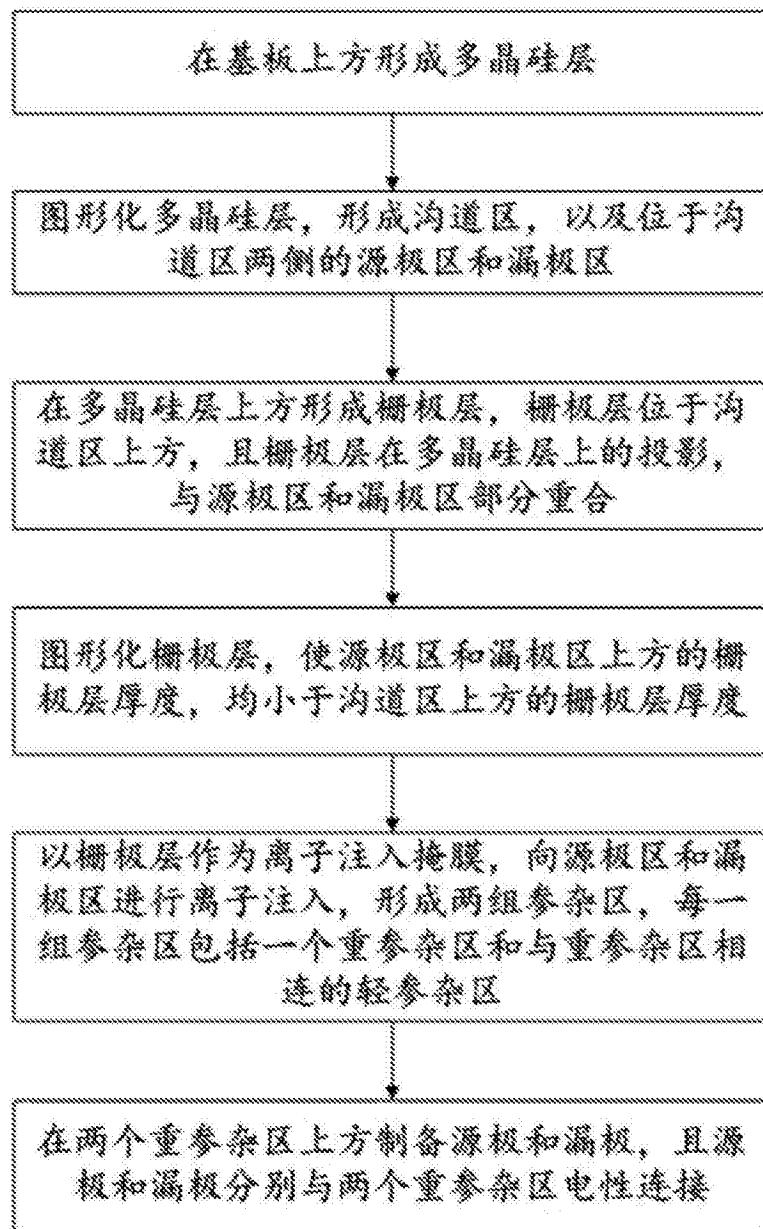

- [0064] 图5是本发明提供的N型薄膜晶体管制备方法的流程图。

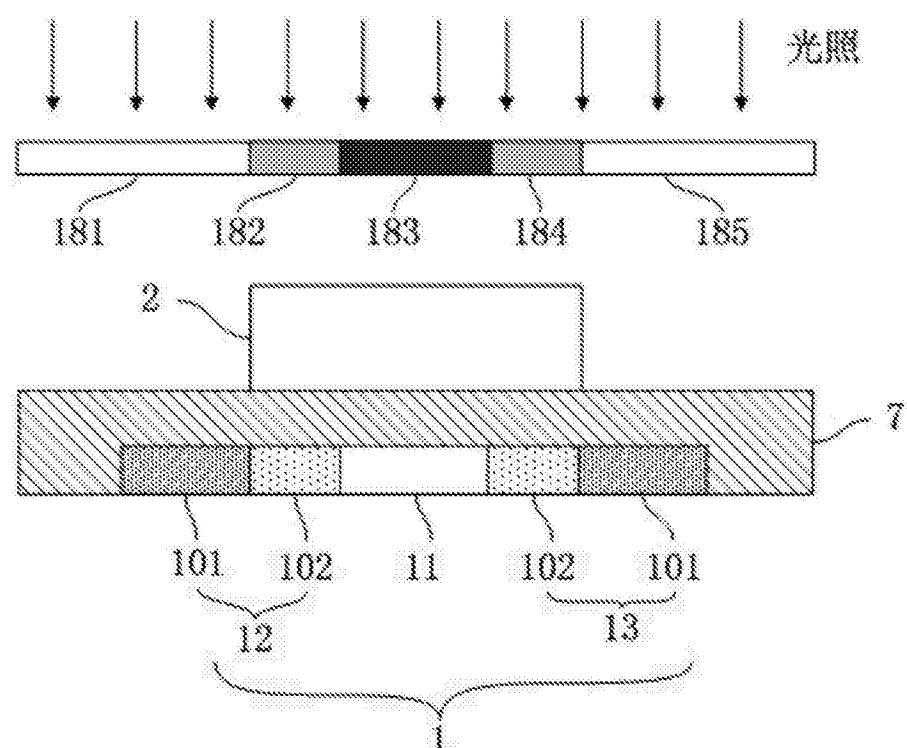

- [0065] 图6是本发明提供的N型薄膜晶体管制备方法中通过半透掩膜板对栅极层进行曝光的示意图。

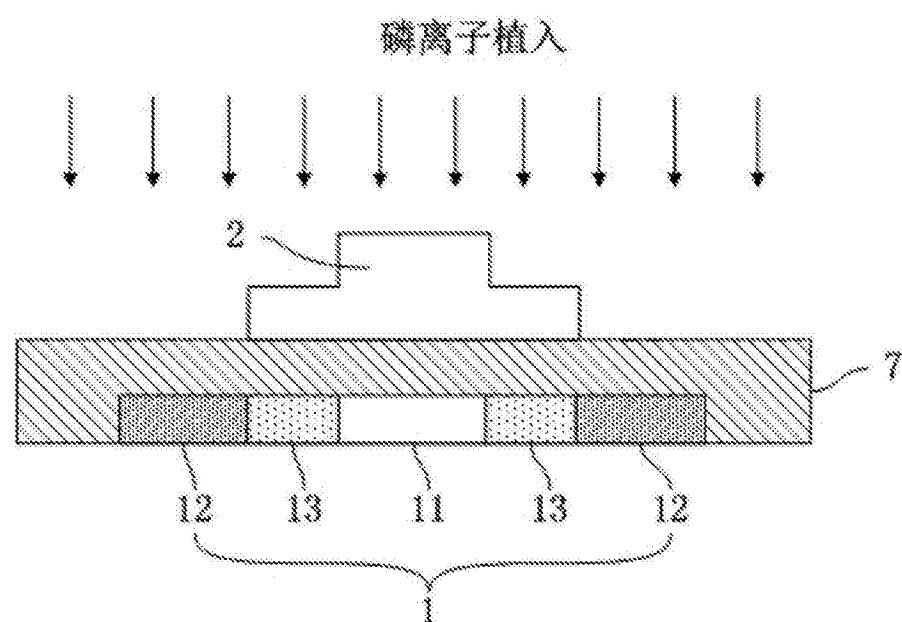

- [0066] 图7是本发明提供的N型薄膜晶体管制备方法中向源极区和漏极区植入磷离子的示意图。

## 具体实施方式

- [0067] 本发明提供一种N型薄膜晶体管，如图1所示，N型薄膜晶体管由下至上包括：多晶硅层1、栅极层2、源极3、漏极4。N型薄膜晶体管即N沟道薄膜晶体管。

- [0068] 其中，多晶硅层1包括沟道区11，以及沟道区11两侧的源极区12和漏极区13，栅极层2位于沟道区11上方，且栅极层2在多晶硅层1上的投影与源极区12和漏极区13部分重合，源极区12和漏极区13上方的栅极层厚度，均小于沟道区11上方的栅极层厚度。如图1中所示，沟道区11上方的栅极层厚度h2，大于源极区12上方的栅极层厚度h1和漏极区13上方的栅极层厚度h1'，其中，h1与h2之间的比值范围，以及h1'与h2之间的比值范围均为1/10~1/5，h1'与h1可相等。

- [0069] 源极区12和漏极区13均包含重掺杂区101和与重掺杂区101连接的轻掺杂区102，源极区12和漏极区13的轻掺杂区102均位于栅极层2下方，源极3位于源极区12的重掺杂区101上方且与源极区12的重掺杂区101电性连接，漏极4位于漏极区13的重掺杂区101上方且与漏极区13的重掺杂区101电性连接。

- [0070] 进一步地，重掺杂区101和轻掺杂区102掺杂的离子均为磷离子；多晶硅层1与栅极层2之间还设置有栅极绝缘层7。

- [0071] 栅极绝缘层7上还设置有介电层8，且介电层8覆盖栅极层2，介电层8包含SiNx和/或SiOy，其中， $x \geq 1, y \geq 1$ 。

- [0072] 如图2所示，介电层8上设置有两个第一连接孔14，栅极绝缘层7上设置有两个第二连接孔15，两个第一连接孔14分别与两个第二连接孔15正对，且两个第二连接孔15分别与源极区12的重掺杂区101和漏极区13的重掺杂区101正对。

- [0073] 源极3和漏极4均设置在介电层8上，且源极3通过第一连接孔14和第二连接孔15，与源极区12的重掺杂区101电性连接，漏极4通过第一连接孔14和第二连接孔15，与漏极区13的重掺杂区101电性连接。

- [0074] 本发明还提供一种OLED显示面板，如图3和图4所示，该OLED显示面板包括上述的N型薄膜晶体管；薄膜晶体管的多晶硅层1下方设置有基板5；薄膜晶体管的介电层8上方设置有平坦层9，且平坦层9覆盖薄膜晶体管的源极3和漏极4，平坦层9上设置有第三连接孔16，第三连接孔16位于源极3或者漏极4上方，第三连接孔16中设置有阳极10，阳极10与源极3或者漏极4电性连接。其中，基板5为玻璃基板。

- [0075] 平坦层9上方设置有像素定义层11，像素定义层11上设置有第四连接孔17，且第四连接孔17位于阳极10上方，第四连接孔17中设置有机发光材料12，有机发光材料12与阳极10接触。其中，有机发光材料12为OLED (Organic Light-Emitting Diode, 有机发光半导体)

发光材料。

[0076] 进一步地，基板5与多晶硅层1之间设置有缓冲层6，且缓冲层6包含SiNx和/或SiOy，其中， $x \geq 1, y \geq 1$ 。

[0077] 本发明还提供一种N型薄膜晶体管的制备方法，如图5所示，该N型薄膜晶体管的制备方法包括下述步骤：

[0078] 在基板5上方形成多晶硅层1；

[0079] 图形化多晶硅层1，形成沟道区11，以及位于沟道区11两侧的源极区12和漏极区13；

[0080] 在多晶硅层1上方形成栅极层2，栅极层2位于沟道区11上方，且栅极层2在多晶硅层1上的投影，与源极区12和漏极区13部分重合；

[0081] 图形化栅极层2，使源极区12和漏极区13上方的栅极层厚度，均小于沟道区11上方的栅极层厚度；

[0082] 以栅极层2作为离子注入掩膜，向源极区12和漏极区13进行离子植入，形成两组参杂区，每一组参杂区包括一个重参杂区101和与重参杂区101相连的轻参杂区102；

[0083] 在两个重参杂区101上方制备源极3和漏极4，且源极3和漏极4分别与两个重参杂区101电性连接(即形成良好的欧姆接触)。其中，重参杂区101一般也称为N+区域，轻参杂区102也称为N-区域或者LDD(Lightly Doped Drain，轻掺杂漏结构)区域。

[0084] 轻参杂区102对应的栅极层2的厚度较薄，在薄膜晶体管施加工作电压时，该处积蓄的电荷相对较少，产生的电场强度也较弱，吸引的电子也较少，因此电阻相对较大，进而起到LDD区域的减小漏电流的作用，从而可以大幅改善该薄膜晶体管的器件特性。并且，上述制备N型薄膜晶体管的方法中，只有一次离子植入的过程，在该次离子植入过程中，栅极层2充当了离子注入掩膜的作用，因此，位于栅极层2下方的部分源极区12和部分漏极区13植入的离子较少，可以作为轻参杂区102，不是位于栅极层2下方的部分源极区12和部分漏极区13植入的离子较多，可以作为重参杂区101；因而，本发明提供的N型薄膜晶体管的制备方法，还能够节省一次给轻参杂区102植入离子的过程，简化了工艺流程，节省制造成本。

[0085] 进一步地，在多晶硅层1上方形成栅极层2之前，还包括下述步骤：

[0086] 在多晶硅层1上形成栅极绝缘层7；其中，栅极绝缘层7位于多晶硅层1与栅极层2之间。

[0087] 在基板5上方形成多晶硅层1之前，还包括下述步骤：

[0088] 在基板5上形成缓冲层6，其中，缓冲层6包含SiOx和/或SiNy， $x \geq 1, y \geq 1$ 。优选地，在基板5上连续沉积SiOx层和SiNy层。缓冲层6可以阻挡部分外部杂质离子的进入。

[0089] 在基板5上方形成多晶硅层1，包括下述步骤：

[0090] 在缓冲层6上沉积非晶硅层；非晶硅也即是无定形硅(a-Si)。

[0091] 采用准分子镭射结晶的方式将非晶硅层转化为多晶硅层1。

[0092] 进一步地，图形化栅极层2，包括下述步骤：

[0093] 在栅极层2上涂布光阻；

[0094] 通过半透掩膜板对栅极层2进行曝光及显影处理，得到光阻半保留部分，

[0095] 光阻半保留部分位于源极和漏极上方；

[0096] 将栅极层2位于光阻半保留部分的区域进行部分刻蚀。

[0097] 其中,如图6所示,半透掩膜板包括透光区181、半透光区182,不透光区183,半透光区182的透光率范围为20%~70%;通过半透掩膜板对栅极层2进行曝光处理时,不透光区183位于沟道区11对应的栅极层2上方,因此,沟道区11上方的栅极层2上涂布的光阻没有被曝光,刻蚀制程中,沟道区11上方的栅极层2不会被刻蚀,最终沟道区11上方的栅极层厚度大于源极区12和漏极区13上方的栅极层厚度。

[0098] 进一步地,向源极区12和漏极区13进行离子植入,具体为:

[0099] 采用离子注入技术,向源极区12和漏极区13植入磷离子;植入磷离子的示意图如图7所示。其中,重参杂区101有大量的磷离子植入,该区域的电阻会很小,与后续制作的源极3和漏极4能够形成良好的欧姆接触。轻参杂区102上方的栅极层厚度较薄,虽然会阻挡磷离子的植入,但是在薄膜晶体管正常工作时,给栅极层2施加电压所产生的电场强度较弱,吸引的电子也较少,电阻相对较大,从而可以起到减小漏电流的作用。

[0100] 进一步地,在两个重参杂区101上方制备源极3和漏极4,包括下述步骤:

[0101] 在栅极绝缘层7上形成介电层8,且介电层8覆盖栅极层2;

[0102] 图形化介电层8和栅极绝缘层7,在介电层8上形成两个第一连接孔14,在栅极绝缘层7上形成两个第二连接孔15,且两个第一连接孔14分别与两个第二连接孔15正对,两个第二连接孔15分别与两个重参杂区101正对;

[0103] 在介电层8上沉积金属层,且金属层均通过两个第一连接孔14和两个第二连接孔15,与两个重参杂区101电性连接;

[0104] 图形化金属层,形成源极3和漏极4。

[0105] 进一步地,在栅极绝缘层7上形成介电层8,具体为:

[0106] 采用等离子体增强化学的气相沉积法,在栅极绝缘层7上沉积SiNx和/或SiOy,形成介电层8。介电层8也即是1LD层(也称为层间绝缘层)。优选地,在栅极绝缘层7上沉积SiNx层和SiOy层。

[0107] 在图形化介电层8和栅极绝缘层7之前还包括下述步骤:

[0108] 对介电层8进行快速退火活化处理,其中快速退火的温度为550~600摄氏度,退火时间为5~15分钟。

[0109] 进一步地,在介电层8上沉积金属层,具体为:

[0110] 采用物理气相沉积的方式,在介电层8上依次沉积钼、铝、钼金属,形成金属层。

[0111] 本发明还提供一种OLED显示面板的制备方法,该OLED显示面板的制备方法包括上述的N型薄膜晶体管的制备方法,还包括下述步骤:

[0112] 在介电层8上形成平坦层9,且平坦层9覆盖源极3和漏极4;

[0113] 图形化平坦层9,在平坦层9上形成第三连接孔16,第三连接孔16位于源极3或者漏极4上方;

[0114] 在第三连接孔16处制备阳极10,且阳极10与源极3或者漏极4电性连接;

[0115] 在平坦层9上沉积像素定义层11,且像素定义层11覆盖阳极10;

[0116] 图形化像素定义层11,在像素定义层11上形成第四连接孔17,且第四连接孔17位于阳极10上方;

[0117] 在第四连接孔17处蒸镀有机发光材料12,且有机发光材料12与阳极10接触。其中,有机发光材料12为OLED发光材料。

- [0118] 进一步地，第三连接孔16位于源极3或者漏极4上方。

- [0119] 在第三连接孔16处制备阳极10，具体为：

- [0120] 在第三连接孔16处沉积铟锡氧化物(即ITO)，并将铟锡氧化物图形化形成阳极10；

- [0121] 平坦层9和像素定义层11的材料均为聚酰亚胺。

- [0122] 上述所说的图形化各膜层，例如金属层、平坦层9、像素定义层11，都是在该膜层上涂布光阻材料，再进行曝光及显影处理，进行刻蚀，完成各膜层的图形化处理过程。

- [0123] 综上所述，本发明提供的N型薄膜晶体管及其制备方法，轻掺杂区102对应的栅极层2的厚度相对较薄，在薄膜晶体管施加工作电压时，该处产生的电场强度也较弱，吸引的电子也较少，因此电阻相对较大，进而起到LDD区域的减小漏电流的作用，从而可以大幅改善该薄膜晶体管的器件特性。并且，上述制备N型薄膜晶体管的方法中，只有一次离子植入的过程，在该次离子植入过程中，栅极层2充当了离子注入掩膜的作用，因此，本发明提供的N型薄膜晶体管的制备方法，还能够节省一次给轻掺杂区102植入离子的过程，简化了工艺流程，节省制造成本。

- [0124] 以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明，不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说，在不脱离本发明构思的前提下，还可以做出若干简单推演或替换，都应当视为属于本发明的保护范围。

图1

图2

图3

图4

图5

图6

图7

|         |                                                      |         |            |

|---------|------------------------------------------------------|---------|------------|

| 专利名称(译) | N型薄膜晶体管及其制备方法、OLED显示面板及其制备方法                         |         |            |

| 公开(公告)号 | <a href="#">CN107819012A</a>                         | 公开(公告)日 | 2018-03-20 |

| 申请号     | CN201710936407.9                                     | 申请日     | 2017-10-10 |

| [标]发明人  | 喻蕾<br>李松杉                                            |         |            |

| 发明人     | 喻蕾<br>李松杉                                            |         |            |

| IPC分类号  | H01L27/32 H01L29/423 H01L21/336 H01L29/786 H01L21/77 |         |            |

| 外部链接    | <a href="#">Espacenet</a> <a href="#">Sipo</a>       |         |            |

**摘要(译)**

本发明提供一种N型薄膜晶体管及其制备方法、OLED显示面板及其制备方法，薄膜晶体管由下至上包括：多晶硅层、栅极层、源极、漏极；其中，多晶硅层包括沟道区，以及沟道区两侧的源极区和漏极区，栅极层位于沟道区上方，且栅极层在多晶硅层上的投影与源极区和漏极区部分重合，源极区和漏极区上方的栅极层厚度，均小于沟道区上方的栅极层厚度；且源极区和漏极区均包含重掺杂区和与重掺杂区连接的轻掺杂区，轻掺杂区均位于栅极层下方，源极位于源极区的重掺杂区上方且与源极区的重掺杂区电性连接，漏极位于漏极区的重掺杂区上方且与漏极区的重掺杂区电性连接。本发明可以减小薄膜晶体管的漏电流，改善薄膜晶体管的器件特性。