(12)发明专利申请

(10)申请公布号 CN 110112205 A

(43)申请公布日 2019.08.09

(21)申请号 201910524464.5

(22)申请日 2019.06.18

(71)申请人 京东方科技股份有限公司

地址 100015 北京市朝阳区酒仙桥路10号

(72)发明人 田宏伟 牛亚男 李栋 刘明

刘政

(74)专利代理机构 中国国际贸易促进委员会专

利商标事务所 11038

代理人 颜镝 王莉莉

(51)Int.Cl.

H01L 27/32(2006.01)

H01L 51/52(2006.01)

H01L 51/56(2006.01)

权利要求书4页 说明书13页 附图9页

(54)发明名称

显示基板及其制造方法、有机发光二极管显示装置

(57)摘要

本公开涉及一种显示基板及其制造方法、有机发光二极管显示装置。显示基板包括：阵列基板，包括显示区域，显示区域包括像素区和围绕像素区的非像素区；凸起结构，沿第一方向位于阵列基板上，且位于非像素区，第一方向为显示基板的出光方向或出光方向的相反方向；第一金属层，沿第一方向位于凸起结构上，并与工作电压端导电连接；第一平坦化层，沿第一方向位于阵列基板上；多个功能层和阴极层，沿第一方向在第一平坦化层上依次设置；其中，阴极层通过过孔与第一金属层电连接。

1. 一种显示基板,包括:

阵列基板,包括显示区域,所述显示区域包括像素区和围绕所述像素区的非像素区;

凸起结构,沿第一方向位于所述阵列基板上,且位于所述非像素区,所述第一方向为所述显示基板的出光方向或所述出光方向的相反方向;

第一金属层,沿所述第一方向位于所述凸起结构上,并与工作电压端导电连接;

第一平坦化层,沿所述第一方向位于所述阵列基板上;

多个功能层和阴极层,沿所述第一方向在所述第一平坦化层上依次设置,

其中,所述阴极层通过过孔与所述第一金属层电连接。

2. 根据权利要求1所述的显示基板,其中,所述过孔设置在所述多个功能层和所述第一平坦化层中的至少一层,且所述过孔在所述阵列基板的正投影与所述凸起结构在所述阵列基板的正投影至少部分重合。

3. 根据权利要求1所述的显示基板,其中,所述阴极层在所述过孔内与所述第一金属层直接接触。

4. 根据权利要求1所述的显示基板,其中,所述多个功能层包括:

第二金属层,沿所述第一方向位于所述第一金属层上,与所述第一金属层电连接,并通过所述过孔与所述阴极层直接接触。

5. 根据权利要求4所述的显示基板,其中,所述多个功能层还包括:

像素定义层,沿所述第一方向位于所述第二金属层上;

有机发光层,沿所述第一方向位于所述像素定义层上;

其中,所述过孔设置在所述像素定义层和所述有机发光层内。

6. 根据权利要求4所述的显示基板,还包括:

阳极层,沿所述第一方向位于所述第一平坦化层上,且与所述第二金属层同层设置。

7. 根据权利要求1所述的显示基板,其中,所述凸起结构相对于所述阵列基板的最大高度为1200nm~3000nm。

8. 根据权利要求1~7任一所述的显示基板,其中,所述阵列基板包括:

衬底;和

薄膜晶体管,位于所述衬底上,所述薄膜晶体管包括栅极层和第一源漏极层,

其中,第一源漏极层与所述第一金属层同层设置。

9. 根据权利要求1~7任一所述的显示基板,还包括:

衬底;

薄膜晶体管,包括栅极层和第一源漏极层;和

层间绝缘层,位于所述栅极层和所述第一源漏极层之间;

其中,所述凸起结构位于所述层间绝缘层上。

10. 根据权利要求1~7任一所述的显示基板,其中,所述阵列基板还包括弯折区域,所述弯折区域设有凹槽和位于凹槽内的填充材料,所述填充材料与所述凸起结构的材料相同。

11. 根据权利要求1~7任一所述的显示基板,其中,所述阵列基板包括:

衬底;

薄膜晶体管,包括栅极层、第二源漏极层和第一源漏极层;

层间绝缘层,位于所述栅极层和所述第二源漏极层之间;和

第二平坦化层,沿所述第一方向位于所述层间绝缘层上,并覆盖所述第二源漏极层;

其中,所述第一源漏极层和所述凸起结构位于所述第二平坦化层上,且所述第一源漏极层的源极和漏极分别与所述第二源漏极层的源极和漏极电连接。

12.根据权利要求11所述的显示基板,其中,所述凸起结构与所述第二平坦化层的材料相同。

13.根据权利要求11所述的显示基板,其中,所述显示基板包括多个凸起结构,位于所述第二平坦化层上;所述阵列基板包括弯折区域,所述弯折区域设有凹槽和位于凹槽内的填充材料,所述多个凸起结构中的一部分与所述第二平坦化层的材料相同,另一部分与所述填充材料的材料相同。

14.一种显示基板的制造方法,包括:

提供包括显示区域的阵列基板,所述显示区域包括像素区和围绕所述像素区的非像素区;

在所述阵列基板的非像素区上形成凸起结构;

在所述凸起结构上形成与工作电压端导电连接的第一金属层;

在所述阵列基板上形成第一平坦化层;

在所述第一平坦化层上依次形成多个功能层和阴极层;

其中,在形成所述阴极层之前,还包括:

在所述多个功能层和所述第一平坦化层中的至少一层形成过孔,以使所述阴极层通过所述过孔与所述第一金属层电连接。

15.根据权利要求14所述的制造方法,其中,在形成所述过孔时,使所述过孔在所述阵列基板的正投影与所述凸起结构在所述阵列基板的正投影至少部分重合。

16.根据权利要求14所述的制造方法,其中,形成所述第一平坦化层的操作包括:

在所述阵列基板上形成平坦化材料层,并使所述平坦化材料层覆盖所述第一金属层;

调整所述平坦化材料层的处理区域的第一材料厚度,以形成所述第一平坦化层,并使所述第一材料厚度小于所述平坦化材料层上位于所述处理区域外周的第二材料厚度,所述处理区域为所述平坦化材料层上位于所述凸起结构在所述平坦化材料层的正投影的至少部分。

17.根据权利要求16所述的制造方法,其中,形成所述过孔的操作包括:

在所述多个功能层和所述第一平坦化层形成过孔,以露出所述第一金属层位于所述过孔底部的部分。

18.根据权利要求14所述的制造方法,其中,形成所述第一平坦化层的操作包括:

在所述阵列基板上形成平坦化材料层,并使所述平坦化材料层覆盖所述第一金属层;

去除所述平坦化材料层的处理区域的材料,以露出所述第一金属层,所述处理区域为所述平坦化材料层上位于所述凸起结构在所述平坦化材料层的正投影的至少部分。

19.根据权利要求18所述的制造方法,其中,形成所述多个功能层的操作包括:

在所述第一金属层上形成与所述第一金属层电连接的第二金属层;

在所述第二金属层上形成像素定义层;

在所述像素定义层上形成有机发光层;

其中,形成所述过孔的操作包括:

在所述有机发光层和所述像素定义层形成过孔,并露出所述第二金属层位于所述过孔底部的部分,以便所述阴极层通过所述过孔与所述第二金属层直接接触。

20.根据权利要求18所述的制造方法,其中,形成所述过孔的操作包括:

在所述多个功能层形成所述过孔,并露出所述第一金属层位于所述过孔底部的部分。

21.根据权利要求19所述的制造方法,还包括:

在所述第一平坦化层上形成阳极层,且所述阳极层与所述第二金属层通过同一构图工艺形成。

22.根据权利要求14~21任一所述的制造方法,其中,提供所述阵列基板的步骤包括:

提供衬底;

在所述衬底上形成薄膜晶体管,所述薄膜晶体管包括栅极层和第一源漏极层,

其中,所述第一源漏极层与所述第一金属层通过同一构图工艺形成。

23.根据权利要求14~21任一所述的制造方法,其中,提供所述阵列基板的步骤包括:

提供衬底;

在所述衬底上形成薄膜晶体管,所述薄膜晶体管包括栅极层和第一源漏极层;

其中,在形成薄膜晶体管时,在所述栅极层上形成层间绝缘层,所述凸起结构形成在所述层间绝缘层上。

24.根据权利要求14~21任一所述的制造方法,其中,所述阵列基板还包括弯折区域,所述制造方法还包括:

在所述弯折区域形成凹槽;

向所述凹槽填入填充材料;

其中,所述凸起结构与所述填充材料通过同一构图工艺形成。

25.根据权利要求14~21任一所述的制造方法,其中,提供所述阵列基板的操作包括:

提供衬底;

在所述衬底上形成薄膜晶体管,所述薄膜晶体管包括栅极层、第二源漏极层和第一源漏极层;

其中,在形成薄膜晶体管时,在所述栅极层上形成层间绝缘层,并在所述层间绝缘层上形成所述第二源漏极层,然后在所述层间绝缘层形成第二平坦化层,并使所述第二平坦化层覆盖所述第二源漏极层;

其中,所述凸起结构和所述第一源漏极层形成在所述第二平坦化层上,且所述第一源漏极层的源极和漏极分别与所述第二源漏极层的源极和漏极电连接。

26.根据权利要求25所述的制造方法,其中,所述凸起结构与所述第二平坦化层通过同一构图工艺形成。

27.根据权利要求14~21任一所述的制造方法,其中,提供所述阵列基板的操作包括:

提供衬底;

在所述衬底上形成薄膜晶体管,所述薄膜晶体管包括栅极层、第二源漏极层和第一源漏极层;

其中,在形成薄膜晶体管时,在所述栅极层上形成层间绝缘层,并在所述层间绝缘层上形成所述第二源漏极层,然后在所述层间绝缘层形成第二平坦化层,并使所述第二平坦化

层覆盖所述第二源漏极层；

其中，所述阵列基板还包括弯折区域，所述制造方法还包括：

在所述弯折区域形成凹槽；

向所述凹槽填入填充材料；

其中，形成所述凸起结构的操作包括：

在所述第二平坦化层上形成多个凸起结构，并且，所述多个凸起结构的一部分与所述填充材料通过同一构图工艺形成，所述多个凸起结构中的另一部分与所述第二平坦化层通过同一构图工艺形成。

28. 一种有机发光二极管显示装置，包括权利要求1～13任一所述的显示基板。

## 显示基板及其制造方法、有机发光二极管显示装置

### 技术领域

[0001] 本公开涉及一种显示基板及其制造方法、有机发光二极管显示装置。

### 背景技术

[0002] 有机电致发光显示器 (Organic Electro Luminescent Display, 简称OLED) 凭借其低功耗、高色饱和度、广视角、薄厚度、可实现柔性化等优异性能, 逐渐成为显示领域的主流, 并可广泛应用于智能手机、平板电脑、电视等终端产品。在这其中, 柔性OLED因其可满足各种特殊结构的需求而逐渐成为OLED中的主流产品。

[0003] IR压降 (IR-drop) 是指出现在电路中电源和地网络中电压下降或升高的现象。随着柔性工艺的发展, 显示尺寸的增大、显示分辨率的提高、线宽的缩小等对于IR-Drop有了显著的影响。为了保证位于像素区域的阴极的透过率, 相关技术中的阴极普遍不会被形成的很厚, 且阴极通常采用从周边到中心的电流传导路径, 这就使得阴极本身的电阻相对更大, 并且该电阻随着显示面积增大会对IR-Drop造成更大的影响。基于不同区域的电压和电流的不同, 各个区域的显示亮度有所不同, 对应的显示效果存在较明显的差异, 影响消费者的观看体验。

[0004] 在相关技术中, 在面对较大面积的显示电路时, 往往采用辅助阴极的方式来克服阴极电阻过大所造成的IR-Drop。

### 发明内容

[0005] 在本公开的一个方面, 提供一种显示基板, 包括:

[0006] 阵列基板, 包括显示区域, 所述显示区域包括像素区和围绕所述像素区的非像素区;

[0007] 凸起结构, 沿第一方向位于所述阵列基板上, 且位于所述非像素区, 所述第一方向为所述显示基板的出光方向或所述出光方向的相反方向;

[0008] 第一金属层, 沿所述第一方向位于所述凸起结构上, 并与工作电压端导电连接;

[0009] 第一平坦化层, 沿所述第一方向位于所述阵列基板上;

[0010] 多个功能层和阴极层, 沿所述第一方向在所述第一平坦化层上依次设置,

[0011] 其中, 所述阴极层通过过孔与所述第一金属层电连接。

[0012] 在一些实施例中, 所述过孔设置在所述多个功能层和所述第一平坦化层中的至少一层, 且所述过孔在所述阵列基板的正投影与所述凸起结构在所述阵列基板的正投影至少部分重合,

[0013] 在一些实施例中, 所述阴极层在所述过孔内与所述第一金属层直接接触。

[0014] 在一些实施例中, 所述多个功能层包括:

[0015] 第二金属层, 沿所述第一方向位于所述第一金属层上, 与所述第一金属层电连接, 并通过所述过孔与所述阴极层直接接触。

[0016] 在一些实施例中, 所述多个功能层还包括:

- [0017] 像素定义层,沿所述第一方向位于所述第二金属层上;

- [0018] 有机发光层,沿所述第一方向位于所述像素定义层上;

- [0019] 其中,所述过孔设置在所述像素定义层和所述有机发光层内。

- [0020] 在一些实施例中,所述显示基板还包括:

- [0021] 阳极层,沿所述第一方向位于所述第一平坦化层上,且与所述第二金属层同层设置。

- [0022] 在一些实施例中,所述凸起结构相对于所述阵列基板的最大高度为1200nm~3000nm。

- [0023] 在一些实施例中,所述阵列基板包括:

- [0024] 衬底;和

- [0025] 薄膜晶体管,位于所述衬底上,所述薄膜晶体管包括栅极层和第一源漏极层,

- [0026] 其中,第一源漏极层与所述第一金属层同层设置。

- [0027] 在一些实施例中,所述显示基板还包括:

- [0028] 衬底;

- [0029] 薄膜晶体管,包括栅极层和第一源漏极层;和

- [0030] 层间绝缘层,位于所述栅极层和所述第一源漏极层之间;

- [0031] 其中,所述凸起结构位于所述层间绝缘层上。

- [0032] 在一些实施例中,所述阵列基板还包括弯折区域,所述弯折区域设有凹槽和位于凹槽内的填充材料,所述填充材料与所述凸起结构的材料相同。

- [0033] 在一些实施例中,所述阵列基板包括:

- [0034] 衬底;

- [0035] 薄膜晶体管,包括栅极层、第二源漏极层和第一源漏极层;

- [0036] 层间绝缘层,位于所述栅极层和所述第二源漏极层之间;和

- [0037] 第二平坦化层,沿所述第一方向位于所述层间绝缘层上,并覆盖所述第二源漏极层;

- [0038] 其中,所述第一源漏极层和所述凸起结构位于所述第二平坦化层上,且所述第一源漏极层的源极和漏极分别与所述第二源漏极层的源极和漏极电连接。

- [0039] 在一些实施例中,所述凸起结构与所述第二平坦化层的材料相同。

- [0040] 在一些实施例中,所述显示基板包括多个凸起结构,位于所述第二平坦化层上;所述阵列基板包括弯折区域,所述弯折区域设有凹槽和位于凹槽内的填充材料,所述多个凸起结构中的一部分与所述第二平坦化层的材料相同,另一部分与所述填充材料的材料相同。

- [0041] 在本公开的一个方面,提供一种显示基板的制造方法,包括:

- [0042] 提供包括显示区域的阵列基板,所述显示区域包括像素区和围绕所述像素区的非像素区;

- [0043] 在所述阵列基板的非像素区上形成凸起结构;

- [0044] 在所述凸起结构上形成与工作电压端导电连接的第一金属层;

- [0045] 在所述阵列基板上形成第一平坦化层;

- [0046] 在所述第一平坦化层上依次形成多个功能层和阴极层;

- [0047] 其中,在形成所述阴极层之前,还包括:

- [0048] 在所述多个功能层和所述第一平坦化层中的至少一层形成过孔,以使所述阴极层通过所述过孔与所述第一金属层电连接。

- [0049] 在一些实施例中,在形成所述过孔时,使所述过孔在所述阵列基板的正投影与所述凸起结构在所述阵列基板的正投影至少部分重合。

- [0050] 在一些实施例中,形成所述第一平坦化层的操作包括:

- [0051] 在所述阵列基板上形成平坦化材料层,并使所述平坦化材料层覆盖所述第一金属层;

- [0052] 调整所述平坦化材料层的处理区域的第一材料厚度,以形成所述第一平坦化层,并使所述第一材料厚度小于所述平坦化材料层上位于所述处理区域外周的第二材料厚度,所述处理区域为所述平坦化材料层上位于所述凸起结构在所述平坦化材料层的正投影的至少部分。

- [0053] 在一些实施例中,形成所述过孔的操作包括:

- [0054] 在所述多个功能层和所述第一平坦化层形成过孔,以露出所述第一金属层位于所述过孔底部的部分。

- [0055] 在一些实施例中,形成所述第一平坦化层的操作包括:

- [0056] 在所述阵列基板上形成平坦化材料层,并使所述平坦化材料层覆盖所述第一金属层;

- [0057] 去除所述平坦化材料层的处理区域的材料,以露出所述第一金属层,所述处理区域为所述平坦化材料层上位于所述凸起结构在所述平坦化材料层的正投影的至少部分。

- [0058] 在一些实施例中,形成所述多个功能层的操作包括:

- [0059] 在所述第一金属层上形成与所述第一金属层电连接的第二金属层;

- [0060] 在所述第二金属层上形成像素定义层;

- [0061] 在所述像素定义层上形成有机发光层;

- [0062] 其中,形成所述过孔的操作包括:

- [0063] 在所述有机发光层和所述像素定义层形成过孔,并露出所述第二金属层位于所述过孔底部的部分,以便所述阴极层通过所述过孔与所述第二金属层直接接触。

- [0064] 在一些实施例中,形成所述过孔的操作包括:

- [0065] 在所述多个功能层形成所述过孔,并露出所述第一金属层位于所述过孔底部的部分。

- [0066] 在一些实施例中,所述制造方法还包括:

- [0067] 在所述第一平坦化层上形成阳极层,且所述阳极层与所述第二金属层通过同一构图工艺形成。

- [0068] 在一些实施例中,提供所述阵列基板的步骤包括:

- [0069] 提供衬底;

- [0070] 在所述衬底上形成薄膜晶体管,所述薄膜晶体管包括栅极层和第一源漏极层,

- [0071] 其中,所述第一源漏极层与所述第一金属层通过同一构图工艺形成。

- [0072] 在一些实施例中,提供所述阵列基板的步骤包括:

- [0073] 提供衬底;

- [0074] 在所述衬底上形成薄膜晶体管，所述薄膜晶体管包括栅极层和第一源漏极层；

- [0075] 其中，在形成薄膜晶体管时，在所述栅极层上形成层间绝缘层，所述凸起结构形成在所述层间绝缘层上。

- [0076] 在一些实施例中，所述阵列基板还包括弯折区域，所述制造方法还包括：

- [0077] 在所述弯折区域形成凹槽；

- [0078] 向所述凹槽填入填充材料；

- [0079] 其中，所述凸起结构与所述填充材料通过同一构图工艺形成。

- [0080] 在一些实施例中，提供所述阵列基板的操作包括：

- [0081] 提供衬底；

- [0082] 在所述衬底上形成薄膜晶体管，所述薄膜晶体管包括栅极层、第二源漏极层和第一源漏极层；

- [0083] 其中，在形成薄膜晶体管时，在所述栅极层上形成层间绝缘层，并在所述层间绝缘层上形成所述第二源漏极层，然后在所述层间绝缘层形成第二平坦化层，并使所述第二平坦化层覆盖所述第二源漏极层；

- [0084] 其中，所述凸起结构和所述第一源漏极层形成在所述第二平坦化层上，且所述第一源漏极层的源极和漏极分别与所述第二源漏极层的源极和漏极电连接。

- [0085] 在一些实施例中，所述凸起结构与所述第二平坦化层通过同一构图工艺形成。

- [0086] 在一些实施例中，提供所述阵列基板的操作包括：

- [0087] 提供衬底；

- [0088] 在所述衬底上形成薄膜晶体管，所述薄膜晶体管包括栅极层、第二源漏极层和第一源漏极层；

- [0089] 其中，在形成薄膜晶体管时，在所述栅极层上形成层间绝缘层，并在所述层间绝缘层上形成所述第二源漏极层，然后在所述层间绝缘层形成第二平坦化层，并使所述第二平坦化层覆盖所述第二源漏极层；

- [0090] 其中，所述阵列基板还包括弯折区域，所述制造方法还包括：

- [0091] 在所述弯折区域形成凹槽；

- [0092] 向所述凹槽填入填充材料；

- [0093] 其中，形成所述凸起结构的操作包括：

- [0094] 在所述第二平坦化层上形成多个凸起结构，并且，所述多个凸起结构的一部分与所述填充材料通过同一构图工艺形成，所述多个凸起结构中的另一部分与所述第二平坦化层通过同一构图工艺形成。

- [0095] 在本公开的一个方面，提供一种有机发光二极管显示装置，包括前述的显示基板。

## 附图说明

- [0096] 构成说明书的一部分的附图描述了本公开的实施例，并且连同说明书一起用于解释本公开的原理。

- [0097] 参照附图，根据下面的详细描述，可以更加清楚地理解本公开，其中：

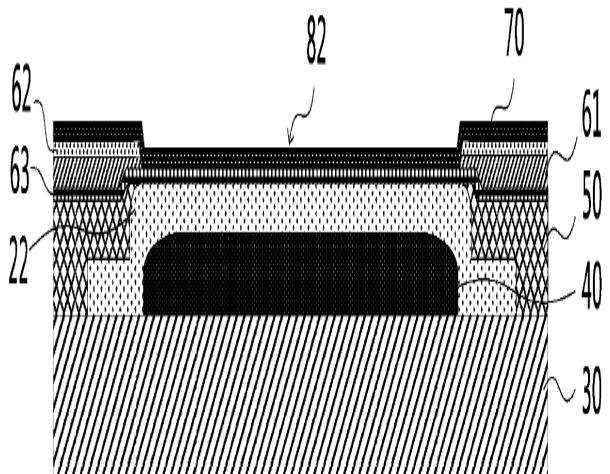

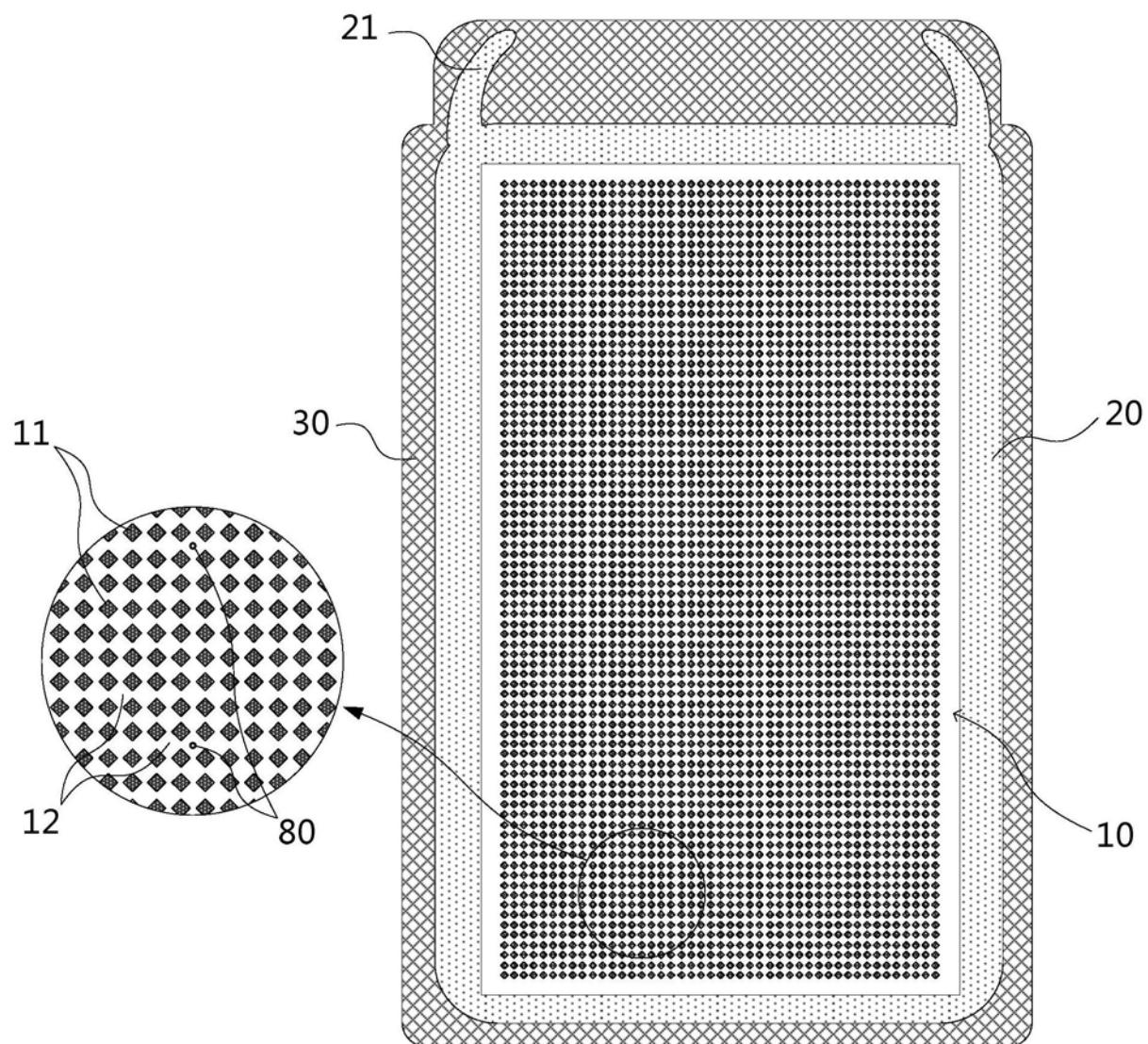

- [0098] 图1是根据本公开显示基板的一个实施例中显示区域及公共电极连接的示意图；

- [0099] 图2-图6分别是根据本公开显示基板的一些实施例的结构示意图；

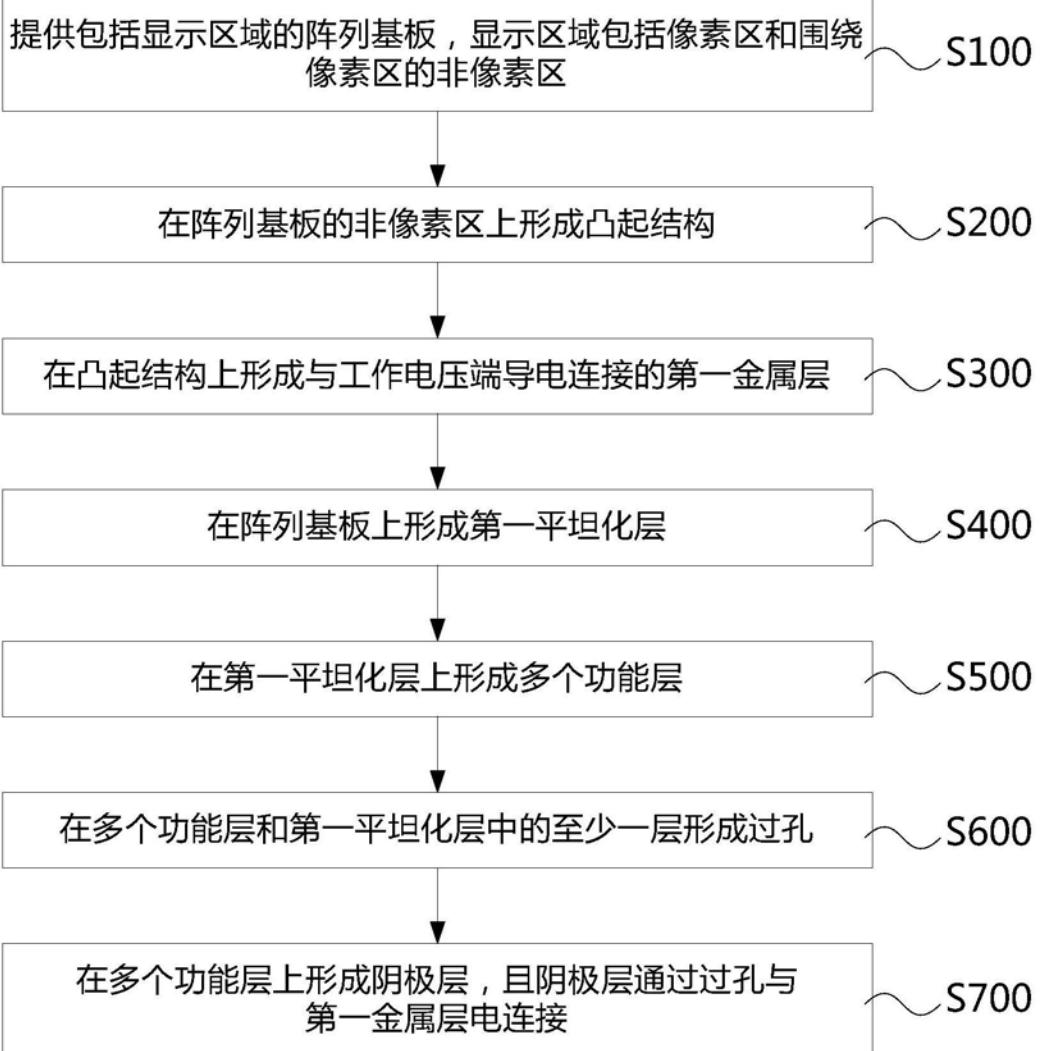

- [0100] 图7是根据本公开显示基板的制造方法的一个实施例的流程示意图；

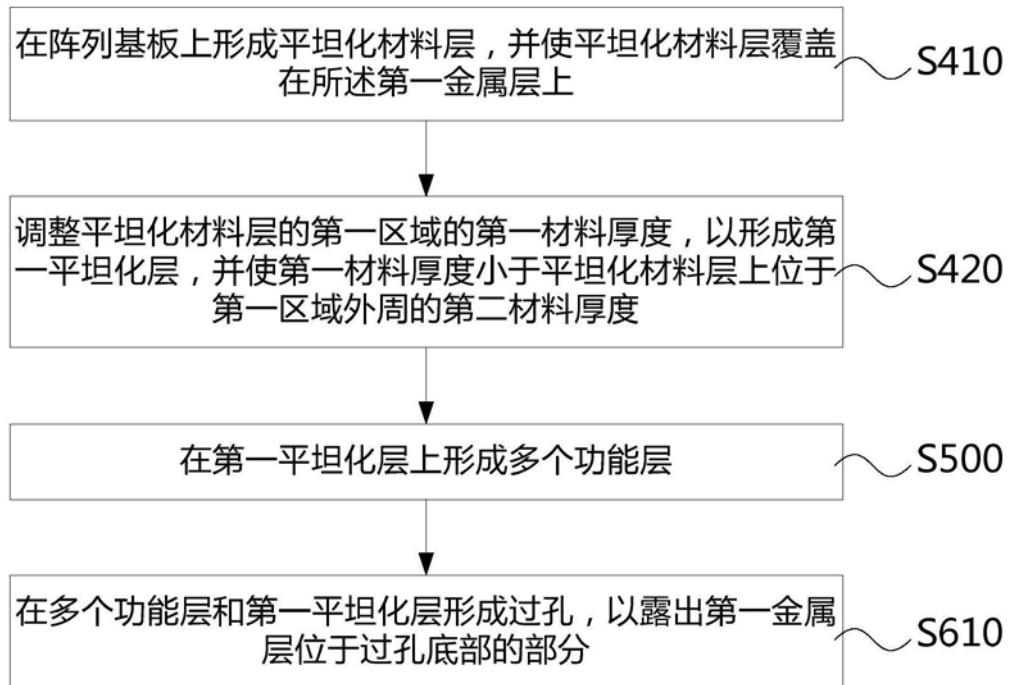

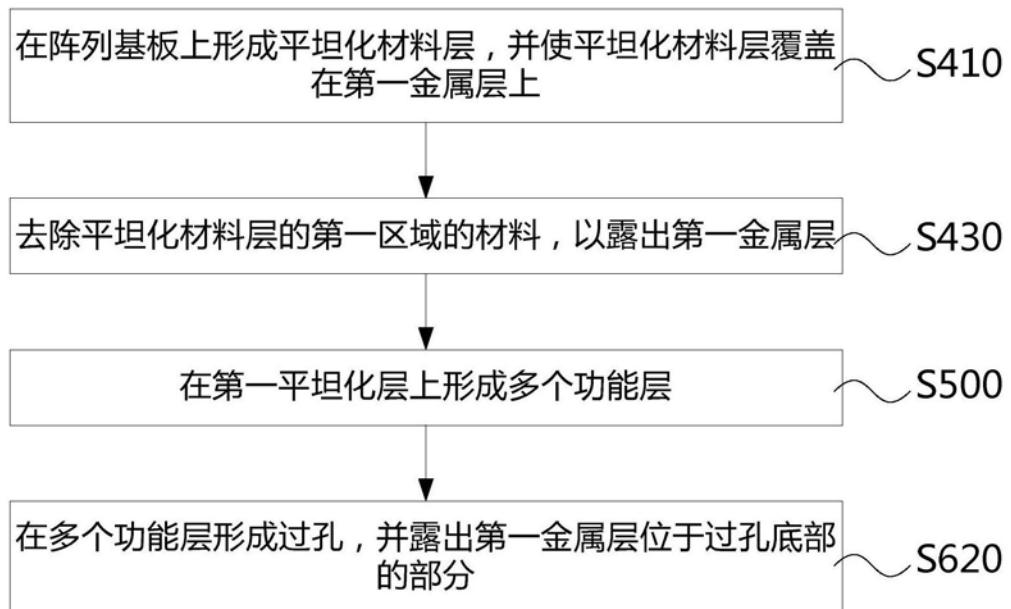

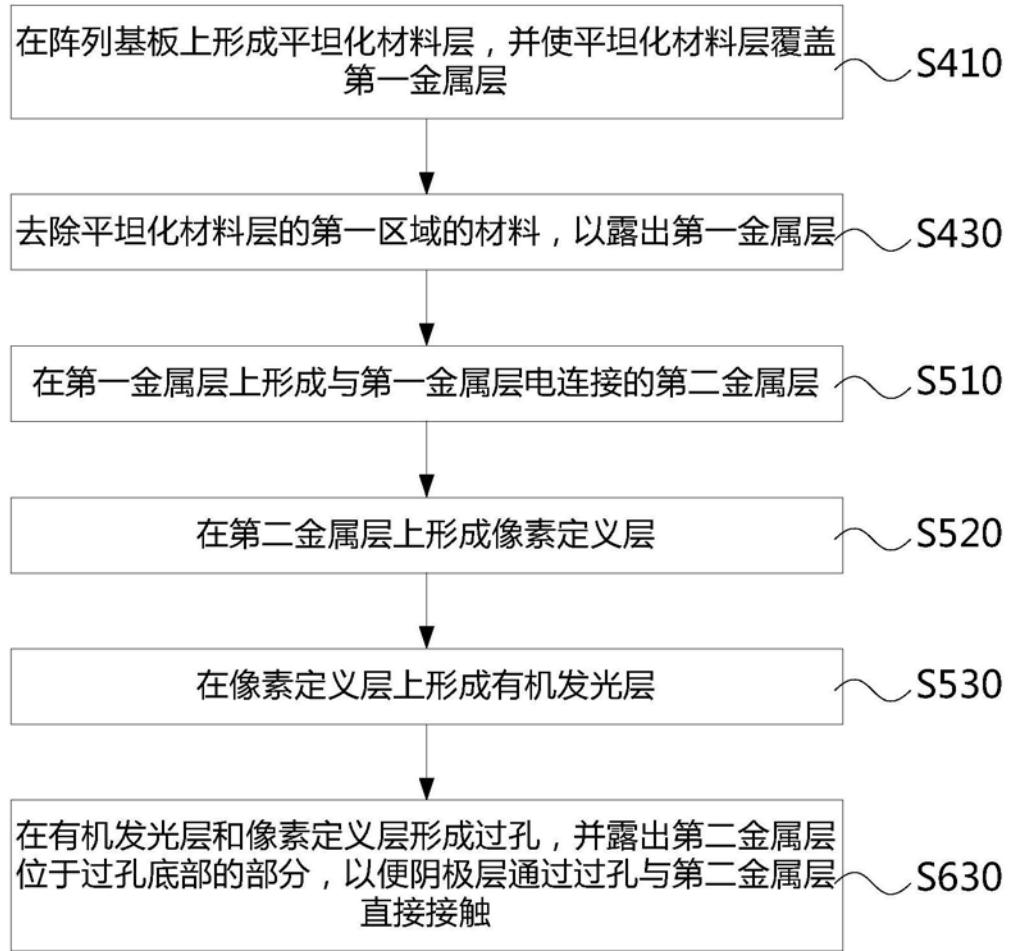

- [0101] 图8-图10分别是根据本公开显示基板的制造方法的一些实施例中从形成第一平坦化层的步骤到形成过孔的步骤的流程示意图；

- [0102] 图11是根据本公开显示基板的制造方法的一个实施例中弯折区域工艺的流程示意图；

- [0103] 图12是根据本公开显示基板的制造方法的另一个实施例的流程示意图；

- [0104] 图13(a)-图13(k)是根据本公开显示基板的一个实施例的制造过程的示意图。

- [0105] 应当明白，附图中所示出的各个部分的尺寸并不是按照实际的比例关系绘制的。此外，相同或类似的参考标号表示相同或类似的构件。

## 具体实施方式

[0106] 现在将参照附图来详细描述本公开的各种示例性实施例。对示例性实施例的描述仅仅是说明性的，决不作为对本公开及其应用或使用的任何限制。本公开可以以许多不同的形式实现，不限于这里所述的实施例。提供这些实施例是为了使本公开透彻且完整，并且向本领域技术人员充分表达本公开的范围。应注意：除非另外具体说明，否则在这些实施例中阐述的部件和步骤的相对布置、材料的组分、数字表达式和数值应被解释为仅仅是示例性的，而不是作为限制。

[0107] 本公开中使用的“第一”、“第二”以及类似的词语并不表示任何顺序、数量或者重要性，而只是用来区分不同的部分。“包括”或者“包括”等类似的词语意指在该词前的要素涵盖在该词后列举的要素，并不排除也涵盖其他要素的可能。“上”、“下”、“左”、“右”等仅用于表示相对位置关系，当被描述对象的绝对位置改变后，则该相对位置关系也可能相应地改变。

[0108] 在本公开中，当描述到特定器件位于第一器件和第二器件之间时，在该特定器件与第一器件或第二器件之间可以存在居间器件，也可以不存在居间器件。当描述到特定器件连接其它器件时，该特定器件可以与所述其它器件直接连接而不具有居间器件，也可以不与所述其它器件直接连接而具有居间器件。

[0109] 本公开使用的所有术语（包括技术术语或者科学术语）与本公开所属领域的普通技术人员理解的含义相同，除非另外特别定义。还应当理解，在诸如通用字典中定义的术语应当被解释为具有与它们在相关技术的上下文中的含义相一致的含义，而不应用理想化或极度形式化的意义来解释，除非这里明确地这样定义。

[0110] 对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论，但在适当情况下，所述技术、方法和设备应当被视为说明书的一部分。

[0111] 为了实现辅助阴极，一些相关技术将显示区域内的阴极层下方的膜层通过激光或其他的方式进行移除，再将阴极层与下方电阻较小且与公共电极端电连接的线路进行连接，从而减少阴极电阻过大造成的IR-Drop。

[0112] 在相关技术中，需要移除阴极层下方较厚的膜层，以便露出需要与阴极层电连接的线路。以激光移除为例，移除的膜层越厚，移除的膜层材料越多，这使得移除过程的生成物也越多，而过多的生成物容易对封装及蒸镀的发光膜层产生不利影响，进而影响显示基板的良率。另一方面，在移除阴极层下方的膜层时，可能造成移除区域与非移除区域之间的

较大段差,在形成阴极层时容易发生断裂,并且也在一定程度上限制了阴极层材料的选择。

[0113] 有鉴于此,本公开实施例提供一种显示基板及其制造方法、有机发光二极管显示装置,能够改善阴极层在过孔部位的爬坡角度。

[0114] 图1是根据本公开显示基板的一个实施例中显示区域及公共电极连接的示意图。

[0115] 参考图1,在一些实施例中,显示基板包括阵列基板30。阵列基板30可包括显示区域10和实现非显示功能的其它区域。阵列基板30的显示区域10可设置多个像素单元,以实现显示功能。显示区域10包括用于设置像素单元的像素区11和围绕像素区11的非像素区12。非像素区12可用于限定像素区11的范围。

[0116] 在图1的显示基板的出光方向上,在阵列基板30的显示区域10的周边可设置负性电源信号层20,该负性电源信号20与显示基板的阴极层电连接,并通过接线端21与工作电压端(例如Vss)电连接。

[0117] 为了降低负性电源信号层20与显示区域10中设置的像素单元的阴极之间的IR-Drop,在一些实施例中可采用辅助阴极的方式来降低负性电源信号层到阴极层的电阻,例如在阵列基板30的显示区域10设置与工作电压端导电的金属层,并在非像素区12内布置多个过孔80来实现阴极层与过孔下方的金属层之间的电连接。通过这种方式,可以减少像素单元的阴极与工作电压端之间的电阻,从而有效地降低IR-Drop。过孔80的数量及设置位置可以根据像素比例进行设计,例如将过孔80与显示区域10中的像素的数量关系设置成1:4到1:400。相邻的过孔80可间隔4~400个像素进行设置。多个过孔80可根据显示区域10的形状按照规则或非规则的分布进行排布。

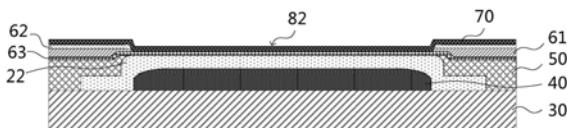

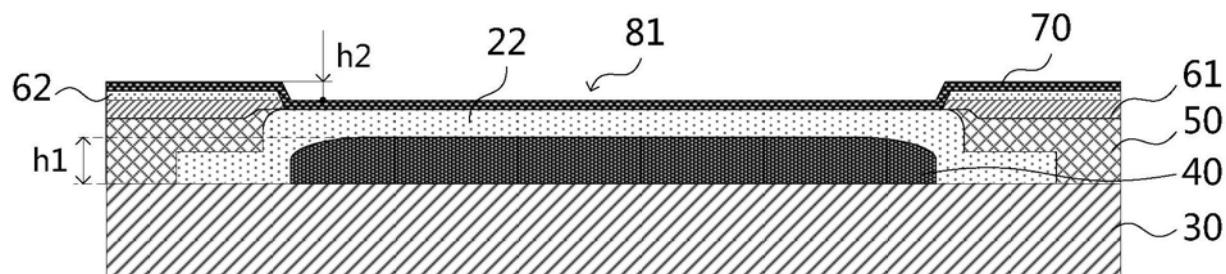

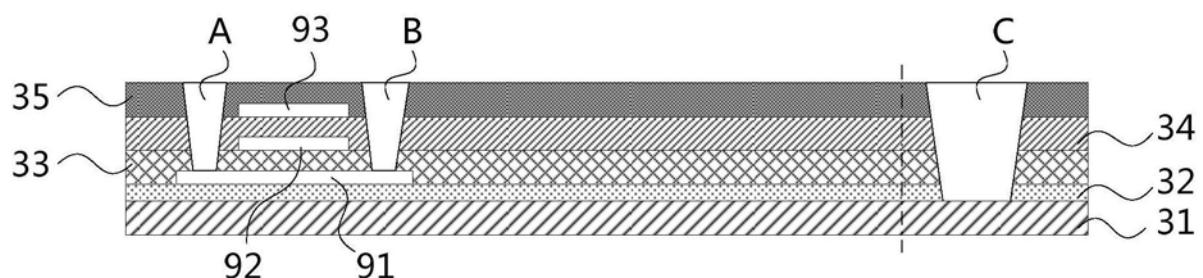

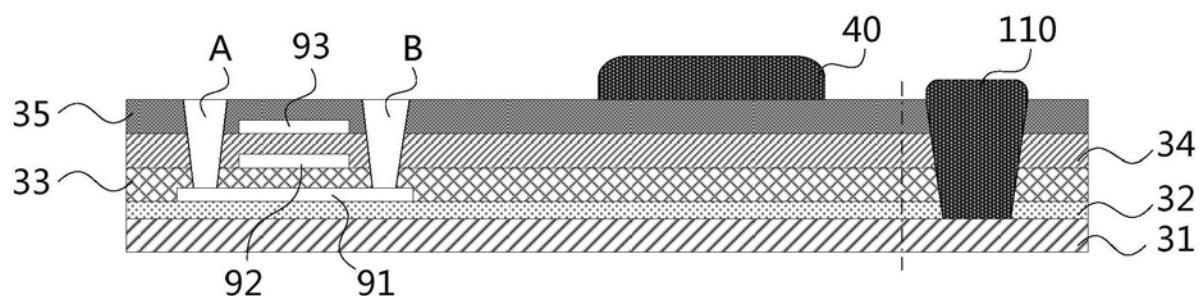

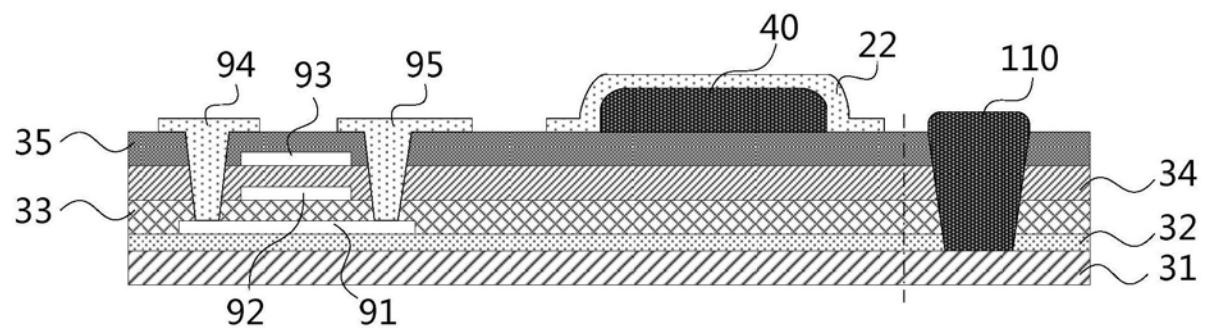

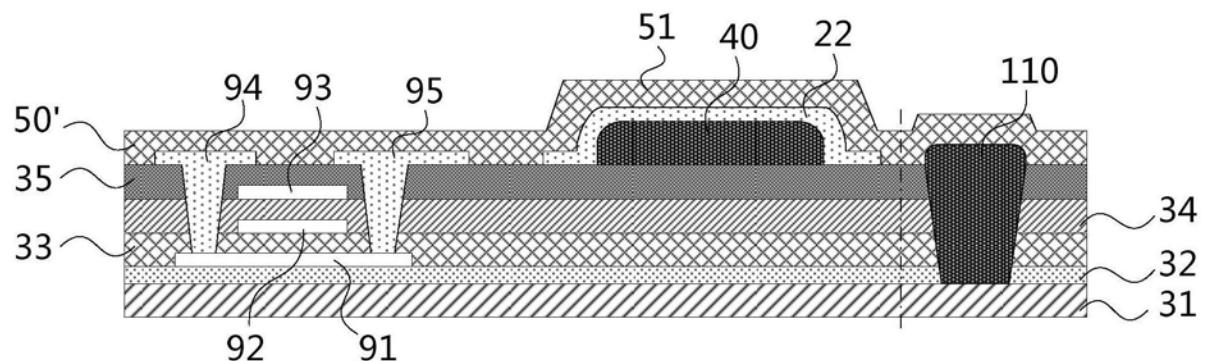

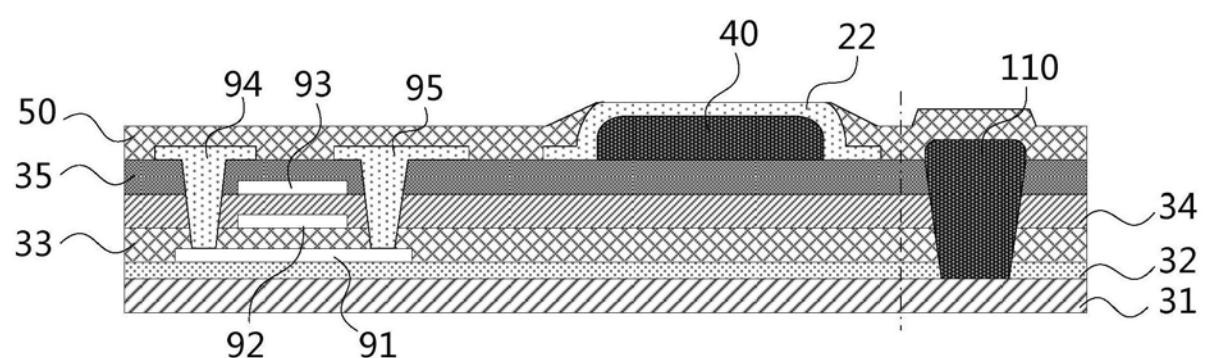

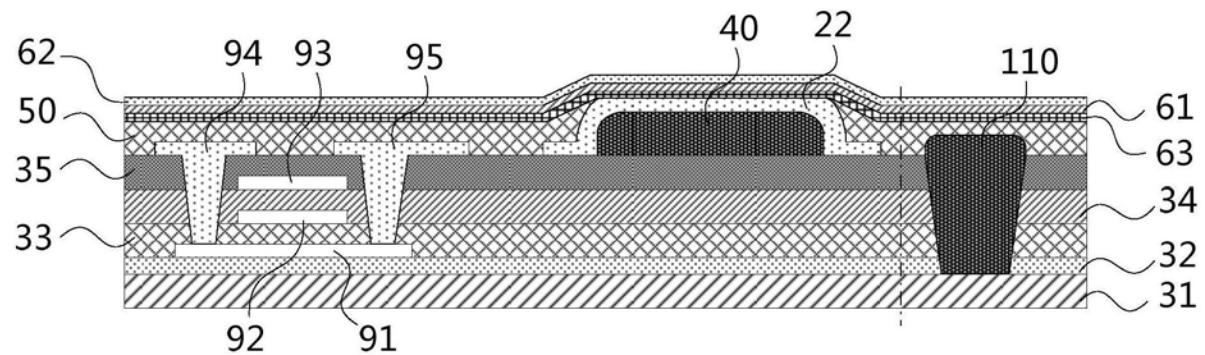

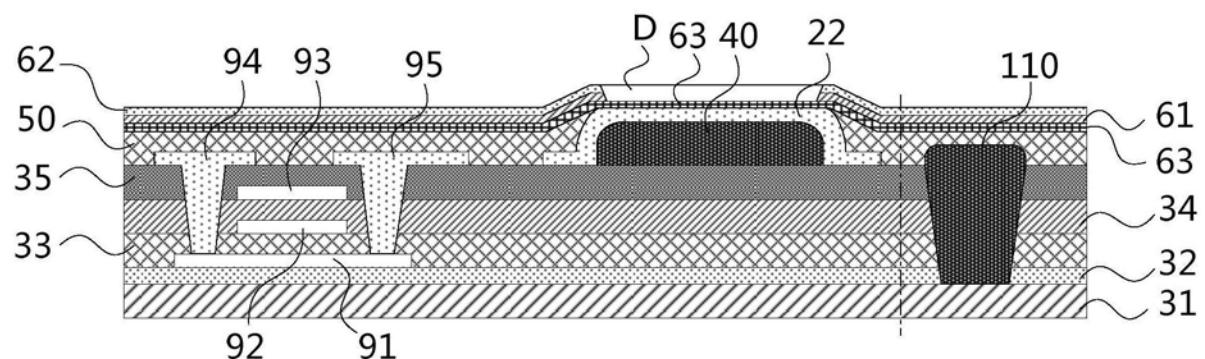

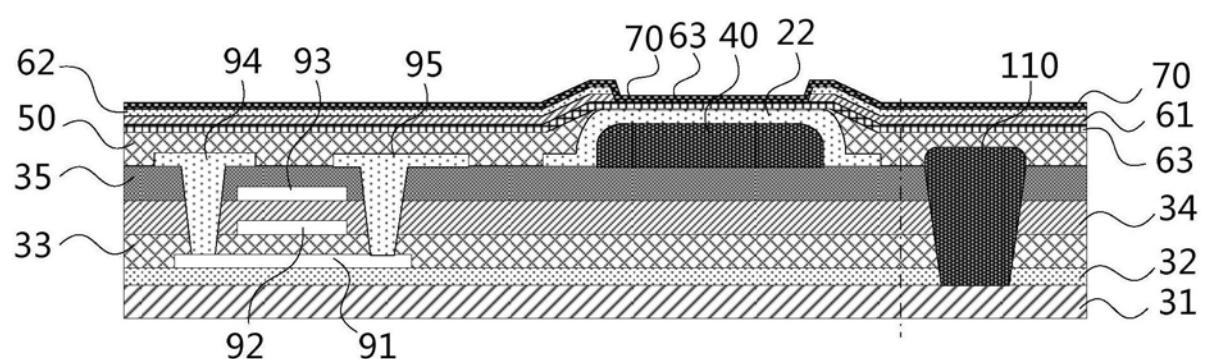

[0118] 图2-图6分别是根据本公开显示基板的一些实施例的结构示意图。

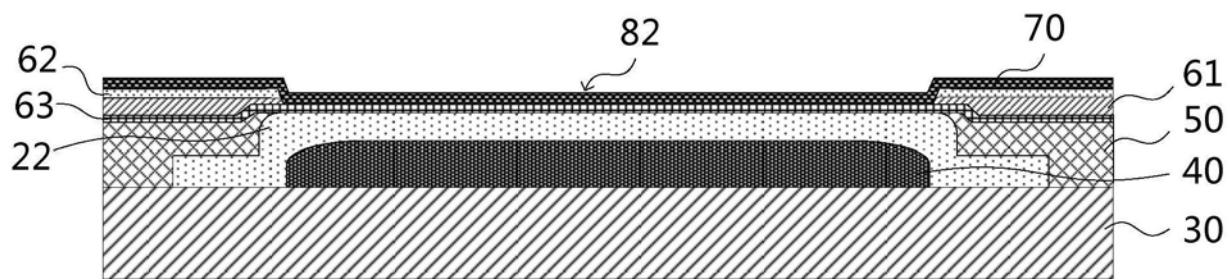

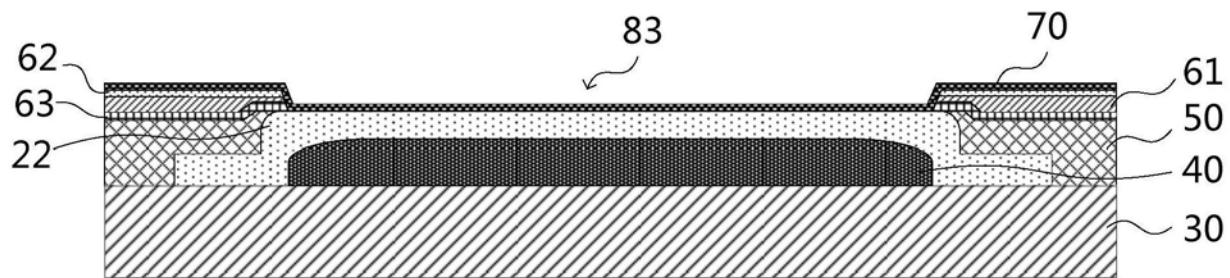

[0119] 参考图2-图4,在一些实施例中,显示基板包括:阵列基板30、凸起结构40、第一金属层22、第一平坦化层50、多个功能层和阴极层70。凸起结构40沿第一方向(即图2-图4中从下到上的竖直方向)位于阵列基板30上,且位于所述非像素区。该第一方向可以为显示基板的出光方向或者显示基板的出光方向的相反方向。例如对于顶发射方式(即从阴极侧出射光)的显示基板来说,第一方向为显示基板的出光方向。而对于底发射方式(即从阳极侧出射光)的显示基板来说,第一方向为显示基板的出光方向的相反方向。

[0120] 凸起结构40相对于阵列基板30向上凸出。凸起结构40的形状可以为圆形、椭圆形或多边形。凸起结构40的材料可以包括硅的氧化物、硅的氮化物、聚酰亚胺中的至少一种。参考图1,凸起结构40的数量可根据分布在显示区域中的过孔80的数量进行确定,例如凸起结构40的数量等于或小于过孔80的数量。凸起结构40在阵列基板30上可沿着与第一方向垂直的至少一个第二方向进行排布。

[0121] 凸起结构40相对于所述阵列基板的最大高度h1可根据阵列基板30上的第一平坦化层的厚度、多个功能层的厚度以及阴极层的爬坡能力中一个或多个因素进行确定,例如可设置h1为1200nm~3000nm。

[0122] 第一金属层22沿第一方向位于所述凸起结构40上,并可作为辅助阴极与工作电压导电连接。参考图2-图4,第一金属层22也可以位于凸起结构40的周边,与凸起结构40上的第一金属层22一体形成。

[0123] 第一平坦化层50可沿第一方向位于所述阵列基板30上,用于为多个功能层的形成提供平坦表面。在不同实施例中,多个功能层的组成可以有所不同。例如,在图2中,多个功

能层包括像素定义层61和有机发光层62。在图3和图4中,多个功能层包括第二金属层63、像素定义层61和有机发光层62。有机发光层62可以包括例如电子注入层、电子阻挡层、电子传输层、发光层、空穴注入层、空穴阻挡层或空穴传输层等发光功能层。多个功能层还可以包括实现其他功能的功能层,例如触控传感器层等。多个功能层和阴极层70可沿第一方向在第一平坦化层50上依次设置。

[0124] 为了使阴极层70与其下方的第一金属层22电连接,参考图2-图4,在一些实施例中,在所述多个功能层和所述第一平坦化层50中的至少一层设有过孔81、82或83。所述阴极层70通过所述过孔81、82或83与所述第一金属层22电连接,以便通过辅助阴极的方式来降低工作电压端到阴极层的电阻。

[0125] 过孔81、82或83在所述阵列基板30的正投影与所述凸起结构40在所述阵列基板30的正投影至少部分重合,即过孔81、82或83在所述阵列基板30的正投影可以与凸起结构40在所述阵列基板30的正投影完全重合,或者只有一部分重合。这里过孔81、82及83在阵列基板30的正投影是指过孔81、82及83的孔壁在阵列基板30的正投影及其围绕的区域。凸起结构40在阵列基板30的正投影是指凸起结构40的整个实体在阵列基板30的正投影。

[0126] 通过这种结构,可使得过孔部位的底部的至少部分形成在凸起结构40的上方,相应可使得该底部相对于多个功能层的最上层(例如图2中的有机发光层62)的高度差相对较小。在形成阴极层70时,过孔部位和过孔周围区域的高度差 $h_2$ 也相对较小,这样就改善了阴极层在过孔部位的爬坡角度,从而使阴极层在形成时不容易在过孔部位发生断裂。

[0127] 在图2中,过孔81从上至下贯穿了有机发光层62、像素定义层61和第一平坦化层50,从而使得阴极层70能够在过孔81内与第一金属层22直接接触。由于位于凸起结构40上方的第一金属层22相比于阵列基板30处于较高的位置,因此在形成第一平坦化层50时,可使得第一平坦化层50在凸起结构40上方的材料更薄,或者移除凸起结构40上方的平坦化层材料而露出第一金属层22。

[0128] 在形成第一平坦化层50时,如果在凸起结构40上方保留较小厚度的平坦化层材料,则在继续形成多个功能层之后,且形成阴极层70之前,可通过激光等方式移除多个功能层和位于凸起结构40上方的平坦化层材料,以便在形成的过孔81的底部露出凸起结构40上方的第一金属层22。

[0129] 在形成第一平坦化层50时,如果凸起结构40上方的平坦化层材料已被移除,则可在继续形成多个功能层之后,且形成阴极层70之前,可通过激光等方式移除多个功能层来形成过孔81,使得过孔81的底部露出凸起结构40上方的第一金属层22。

[0130] 相比于相关技术中需要在形成有机发光层之后,移除阴极层下方较厚的平坦化层材料,本公开的一些实施例在形成第一平坦化层50时减薄或移除凸起结构上方的材料,在形成有机发光层后,可以减少形成过孔时需要移除的平坦化层材料的厚度,或者无需移除凸起结构上方的平坦化层材料,因此可以减少移除过程的生成物,降低生成物对有机发光层的不利影响,从而提高显示基板的良率。

[0131] 在图3和图4中,第二金属层63沿所述第一方向位于所述第一金属层22上,并与所述第一金属层22电连接。参考图3,第二金属层63也可以位于第一金属层22周边的第一平坦化层50上,并与第一金属层22上的第二金属层63一体形成。在一些实施例中,显示基板还包括沿所述第一方向位于所述第一平坦化层50上的阳极层,可用于形成OLED发光面板的阳

极。第二金属层63可以与阳极层同层设置。这样,第二金属层和阳极层在形成时可通过同一构图工艺形成,以简化加工工序。第二金属层和阳极层可采用相同材料,例如包括导电氧化物(例如氧化铟锡和氧化铟锌等)或反射金属(银、铝等)等导电材料。在图3和图4中,像素定义层61沿所述第一方向位于所述第二金属层63上。有机发光层62沿所述第一方向位于所述像素定义层61上。阴极层70沿第一方向位于有机发光层上。阴极层的材料可以包括Li、Ag、Ca、Al、Mg中的至少一种。

[0132] 在图3中,过孔82设置在所述像素定义层61和所述有机发光层62内,所述阴极层70通过所述过孔82与所述第二金属层63直接接触。在形成过孔时保留第二金属层63,一方面可以减少形成过孔时需要移除的阴极层60下方材料厚度,减少移除过程的生成物;另一方面在移除材料时可避免第一金属层被错误移除,从而提高电连接的可靠性。

[0133] 在图4中,过孔83设置在第二金属层63、像素定义层61和有机发光层62内,阴极层70通过过孔83与第一金属层22直接接触,这样能够进一步降低阴极层70与第一金属层22之间的电阻,从而使像素单元的阴极与工作电压端之间的电阻得以减小,从而有效地降低IR-Drop。

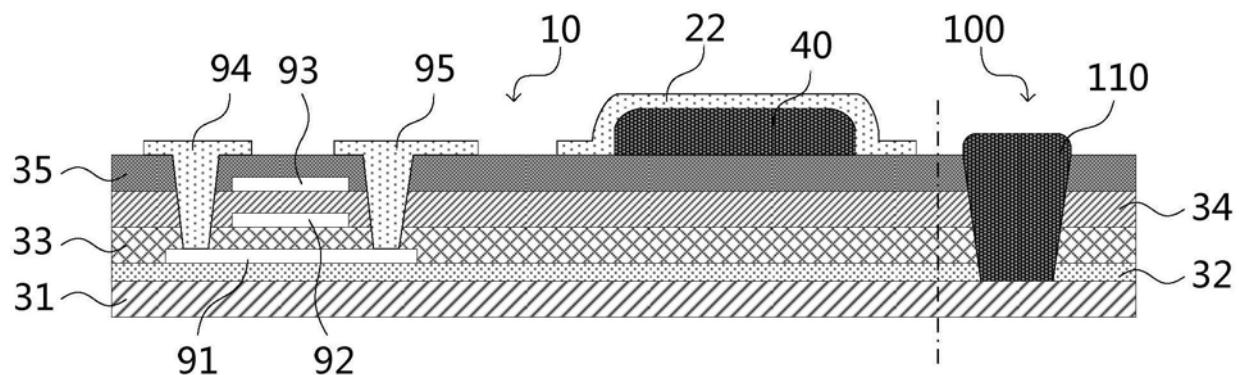

[0134] 参考图5,在一些实施例中,阵列基板包括衬底31和位于衬底31上的薄膜晶体管(Thin Film Transistor, TFT)。薄膜晶体管包括栅极层和第一源漏极层。第一源漏极层可用于构成薄膜晶体管器件的源极(Source Pole)和漏极(Drain Pole)。薄膜晶体管还可以包括有源层91,第一源漏极层中的源极94和漏极95与有源层91连接。第一金属层22可以与第一源漏极层同层设置。这样,第一金属层22和第一源漏极层在形成时可通过同一构图工艺形成,以简化加工工序。

[0135] 在图5中,阵列基板还包括缓冲层32、栅极绝缘层、层间绝缘层35等。沿竖直从下到上的第一方向,阵列基板的缓冲层32设置在衬底31上,有源层91设置在缓冲层32上,第一栅极绝缘层33覆盖在有源层91上,第一栅极层92设置在第一栅极绝缘层33上,第二栅极绝缘层34覆盖在第一栅极层92上,第二栅极层93设置在第二栅极绝缘层34上,层间绝缘层35覆盖在第二栅极层93上。在另一些实施例中,薄膜晶体管可以包括一个栅极层和对应的栅极绝缘层。

[0136] 图5中的凸起结构40可沿第一方向位于层间绝缘层35的表面。第一源漏极层可同样设置在层间绝缘层35的表面,并且第一源漏极层中的源极94和漏极95贯穿层间绝缘层35、第二栅极绝缘层34和第一栅极绝缘层33与有源层91连接。第一源漏极层中的源极94和漏极95可以与第一金属层22同层设置。另外,第一源漏极层中的源极94和漏极95可以与第一金属层22采用相同材料形成,例如钼、铜、铝、金、银或钛等导电材料中的至少一种,并可以通过同一构图工艺形成,以节省加工工序。

[0137] 参考图5,在一些实施例中,阵列基板除了包括显示区域10,还可以包括弯折区域100,用于实现显示基板的可弯折性。在形成上述阵列基板后,可在弯折区域100形成(例如通过曝光-蚀刻工艺)贯穿层间绝缘层35、第二栅极绝缘层34、第一栅极绝缘层33和缓冲层32的凹槽,凹槽的底部露出柔性材质的衬底31。凹槽内可填入填充材料110,该填充材料110可以与凸起结构40通过同一构图工艺形成。例如在基板弯折(Pad-Bending)工艺中,采用半色调(Halftone)工艺来得到Pad-Bending图形的同时,形成凸起结构40。填充材料110和凸起结构40均可采用聚酰亚胺,且相对于阵列基板来说,填充材料110的最大高度为500~

1200nm,而凸起结构40的最大高度为1200~3000nm,大于填充材料相对于阵列基板的最大高度。

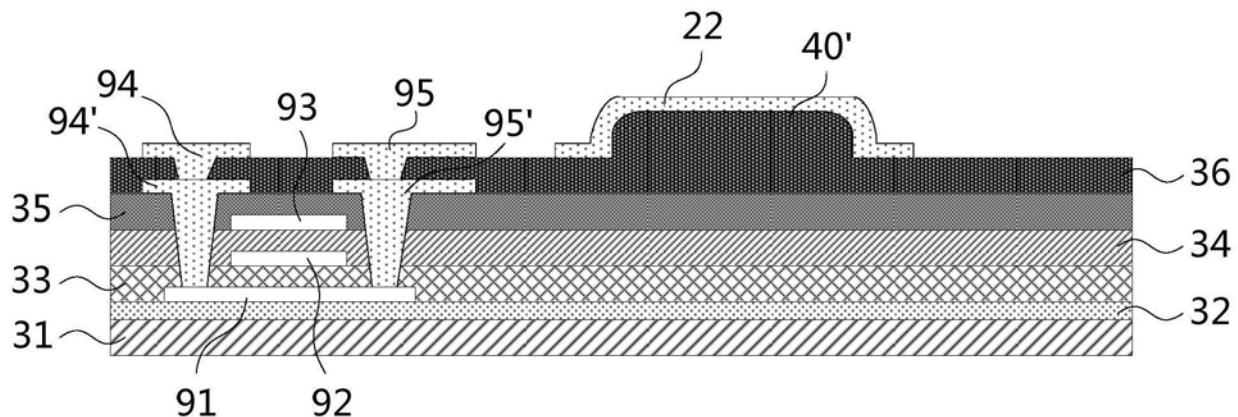

[0138] 参考图6,在一些实施例中,阵列基板包括衬底31、薄膜晶体管、层间绝缘层35和第二平坦化层36。薄膜晶体管包括栅极层、第二源漏极层和第一源漏极层。所述第二源漏极层的源极和漏极分别与所述第一源漏极层的源极和漏极电连接。所述第一源漏极层的源极和漏极均与所述有源层91电连接。

[0139] 在图6中,阵列基板还包括缓冲层32、栅极绝缘层等。沿竖直从下到上的第一方向,阵列基板的缓冲层32设置在衬底31上,有源层91设置在缓冲层32上,第一栅极绝缘层33覆盖在有源层91上,第一栅极层92设置在第一栅极绝缘层33上,第二栅极绝缘层34覆盖在第一栅极层92上,第二栅极层93设置在第二栅极绝缘层34上,层间绝缘层35覆盖在第二栅极层93上。缓冲层32、第一栅极绝缘层33、第二栅极绝缘层34、层间绝缘层35和第二平坦化层36可以采用相同材料,也可以采用不同材料。该材料可以包括硅的氧化物、硅的氮化物、聚酰亚胺中的至少一种。在另一些实施例中,薄膜晶体管可以包括一个栅极层和对应的栅极绝缘层。

[0140] 参考图6,在一些实施例中,第二源漏极层可沿第一方向设置在层间绝缘层35上,即层间绝缘层35位于所述栅极层和所述第二源漏极层之间。第二源漏极层中的源级94'和漏极95'贯穿层间绝缘层35、第二栅极绝缘层34和第一栅极绝缘层33与有源层91连接。第二平坦化层36沿所述第一方向位于所述层间绝缘层35上,并覆盖所述第二源漏极层,而凸起结构40'可设置在第二平坦化层36上。凸起结构40'可以与第二平坦化层36的材料相同。相应的,为了简化工序,可以在形成第二平坦化层36时通过同一构图工艺形成凸起结构40'。

[0141] 在图6中,第一源漏极层可设置在第二平坦化层36上,第一源漏极层的源级94和漏极95贯穿第二平坦化层36分别与第二源漏极层的源极94'和漏极95'连接。第一源漏极层中的源极94和漏极95可以与第一金属层22通过同一构图工艺形成,以节省加工工序。

[0142] 参考图5和图6,在一些实施例中,凸起结构的材料可以与显示基板中的多个部分的材料相同。例如显示基板包括多个凸起结构,位于所述第二平坦化层上。阵列基板包括弯折区域,所述弯折区域设有凹槽和位于凹槽内的填充材料,所述多个凸起结构中的一部分与所述第二平坦化层的材料相同,另一部分与所述填充材料的材料相同。

[0143] 由于凸起结构可与显示基板中的多个部分的材料相同,因此凸起结构可通过显示基板的相应部分的制备工艺一并形成,从而减少显示基板的制备工序,提高制造效率。举例来说,对于在非像素区形成的多个凸起结构,多个凸起结构的一部分可与填入到弯折区域的凹槽内的填充材料通过同一构图工艺形成,多个凸起结构中的另一部分与第二平坦化层通过同一构图工艺形成。

[0144] 图7是根据本公开显示基板的制造方法的一个实施例的流程示意图。

[0145] 参考图7,在一些实施例中,显示基板的制造方法包括步骤S100~S700。在步骤S100中,提供包括显示区域的阵列基板,所述显示区域包括像素区和围绕所述像素区的非像素区。在步骤S200中,在所述阵列基板的非像素区上形成凸起结构。凸起结构相对于所述阵列基板的最大高度可以为1200nm~3000nm。在步骤S300中,在所述凸起结构上形成与工作电压端导电连接的第一金属层。在步骤S400中,在所述阵列基板上形成第一平坦化层。在步骤S500中,在所述第一平坦化层上形成多个功能层。在步骤S600中,在所述多个功能层和

所述第一平坦化层中的至少一层形成过孔。在形成所述过孔时,可使所述过孔在所述阵列基板的正投影与所述凸起结构在所述阵列基板的正投影至少部分重合。在步骤S700中,在所述多个功能层上形成阴极层,且所述阴极层通过所述过孔与所述第一金属层电连接。

[0146] 图8-图10分别是根据本公开显示基板的制造方法的一些实施例中从形成第一平坦化层的步骤到形成过孔的步骤的具体流程示意图。

[0147] 参考图8,在一些实施例中,步骤S400可包括步骤S410和步骤S420。在步骤S410中,在所述阵列基板上形成平坦化材料层,并使所述平坦化材料层覆盖所述第一金属层。在步骤S420,调整所述平坦化材料层的处理区域的第一材料厚度,以形成所述第一平坦化层,并使所述第一材料厚度小于所述平坦化材料层上位于所述处理区域外周的第二材料厚度。所述处理区域为所述平坦化材料层上位于所述凸起结构在所述平坦化材料层的正投影的至少部分。

[0148] 在步骤S500形成多个功能层之后,步骤S600具体包括步骤S610,即在所述多个功能层和所述第一平坦化层形成过孔,以露出所述第一金属层位于过孔底部的部分。由于步骤S420中已将处理区域的材料厚度调整到较小的厚度,相比于相关技术中形成过孔时需要移除较厚的平坦化层,步骤S610形成过孔时需要移除的材料厚度较少,产生的生成物也较少。

[0149] 参考图9,在一些实施例中,步骤S400可包括步骤S410和步骤S430。在步骤S410中,在所述阵列基板上形成平坦化材料层,并使所述平坦化材料层覆盖在所述第一金属层上。在步骤S430,去除所述平坦化材料层的处理区域的材料,以露出所述第一金属层。所述处理区域为所述平坦化材料层上位于所述凸起结构在所述平坦化材料层的正投影的至少部分。

[0150] 在步骤S500形成多个功能层之后,步骤S600具体包括步骤S620,即在所述多个功能层形成过孔,以露出所述第一金属层位于过孔底部的部分。由于步骤S430中已去除处理区域的材料,相比于相关技术中形成过孔时需要移除较厚的平坦化层,步骤S620形成过孔时无需移除第一平坦化层,因此需要移除的材料厚度更少,产生的生成物也更少。

[0151] 参考图10,在一些实施例中,步骤S400可包括步骤S410和步骤S430。在步骤S410中,在所述阵列基板上形成平坦化材料层,并使平坦化材料层覆盖所述第一金属层。在步骤S430,去除所述平坦化材料层的处理区域的材料,以露出所述第一金属层。所述处理区域为所述平坦化材料层上位于所述凸起结构在所述平坦化材料层的正投影的至少部分。

[0152] 在图10中,步骤S500可具体包括步骤S510到步骤S530。在步骤S510中,在所述第一金属层上形成与所述第一金属层电连接的第二金属层。在步骤S520中,在所述第二金属层上形成像素定义层。在步骤S530中,在所述像素定义层上形成有机发光层。

[0153] 在形成多个功能层之后,步骤S600具体包括步骤S630,即在所述有机发光层和所述像素定义层形成过孔,并露出所述第二金属层位于所述过孔底部的部分,以便所述阴极层通过所述过孔与所述第二金属层直接接触。

[0154] 由于步骤S430中已去除处理区域的材料,相比于相关技术中形成过孔时需要移除较厚的平坦化层的材料,步骤S630形成过孔时只需要移除有机发光层和像素定义层,而无需移除第二金属层和第一平坦化层,因此需要移除的材料厚度更少,产生的生成物也更少。另一方面,在移除材料时可避免第一金属层被错误移除,从而提高电连接的可靠性。

[0155] 在一些实施例中,提供阵列基板的步骤可以包括:提供衬底,并在在所述衬底上形

成薄膜晶体管，所述薄膜晶体管包括栅极层和第一源漏极层。薄膜晶体管还可以包括有源层，所述第一源漏极层的源极和漏极可与所述有源层电连接。第一源漏极层可以与图8-图10的实施例中的所述第一金属层通过同一构图工艺形成，以节省加工工序。另外，在形成薄膜晶体管时，可以在所述栅极层上形成层间绝缘层。所述凸起结构可形成在所述层间绝缘层上。

[0156] 在一些实施例中，还可以在所述第一平坦化层上形成阳极层。阳极层可与图9和图10的实施例中的所述第二金属层通过同一构图工艺形成，以节省加工工序。

[0157] 图11是根据本公开显示基板的制造方法的一个实施例中弯折区域工艺的流程示意图。

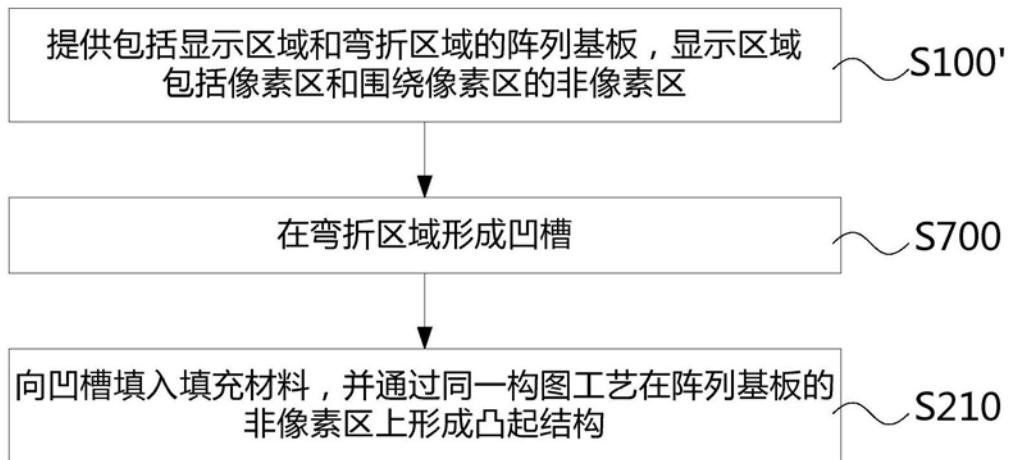

[0158] 参考图11，在一些实施例中，所述阵列基板还包括弯折区域。所述制造方法还可以包括步骤S100'和步骤S700。在步骤S100'中，提供包括显示区域和弯折区域的阵列基板，显示区域包括像素区和围绕像素区的非像素区。步骤S100'可以包括在步骤S100中。在步骤S700中，在所述弯折区域形成凹槽。步骤S200可包括步骤S210，即向凹槽填入填充材料，并通过同一构图工艺在阵列基板的非像素区上形成凸起结构。这样可在填充弯折区域时同时形成凸起结构，从而节省工序。

[0159] 图12是根据本公开显示基板的制造方法的另一个实施例的流程示意图。

[0160] 参考图12，在一些实施例中，提供所述阵列基板的操作可包括：提供衬底，并在所述衬底上形成薄膜晶体管，所述薄膜晶体管包括栅极层、第二源漏极层和第一源漏极层。薄膜晶体管还可以包括有源层，所述第二源漏极层的源极和漏极可与所述有源层电连接。在形成薄膜晶体管时，可在所述栅极层上形成层间绝缘层，并在所述层间绝缘层上形成所述第二源漏极层，然后在所述层间绝缘层形成第二平坦化层，并使所述第二平坦化层覆盖所述第二源漏极层。所述凸起结构和所述第一源漏极层形成在所述第二平坦化层上，且所述第一源漏极层的源极和漏极分别与所述第二源漏极层的源极和漏极电连接。为了节省工序，所述凸起结构可以与所述第二平坦化层通过同一构图工艺形成。在另一些实施例中，凸起结构的形成也可以在第二平坦化层形成之后。

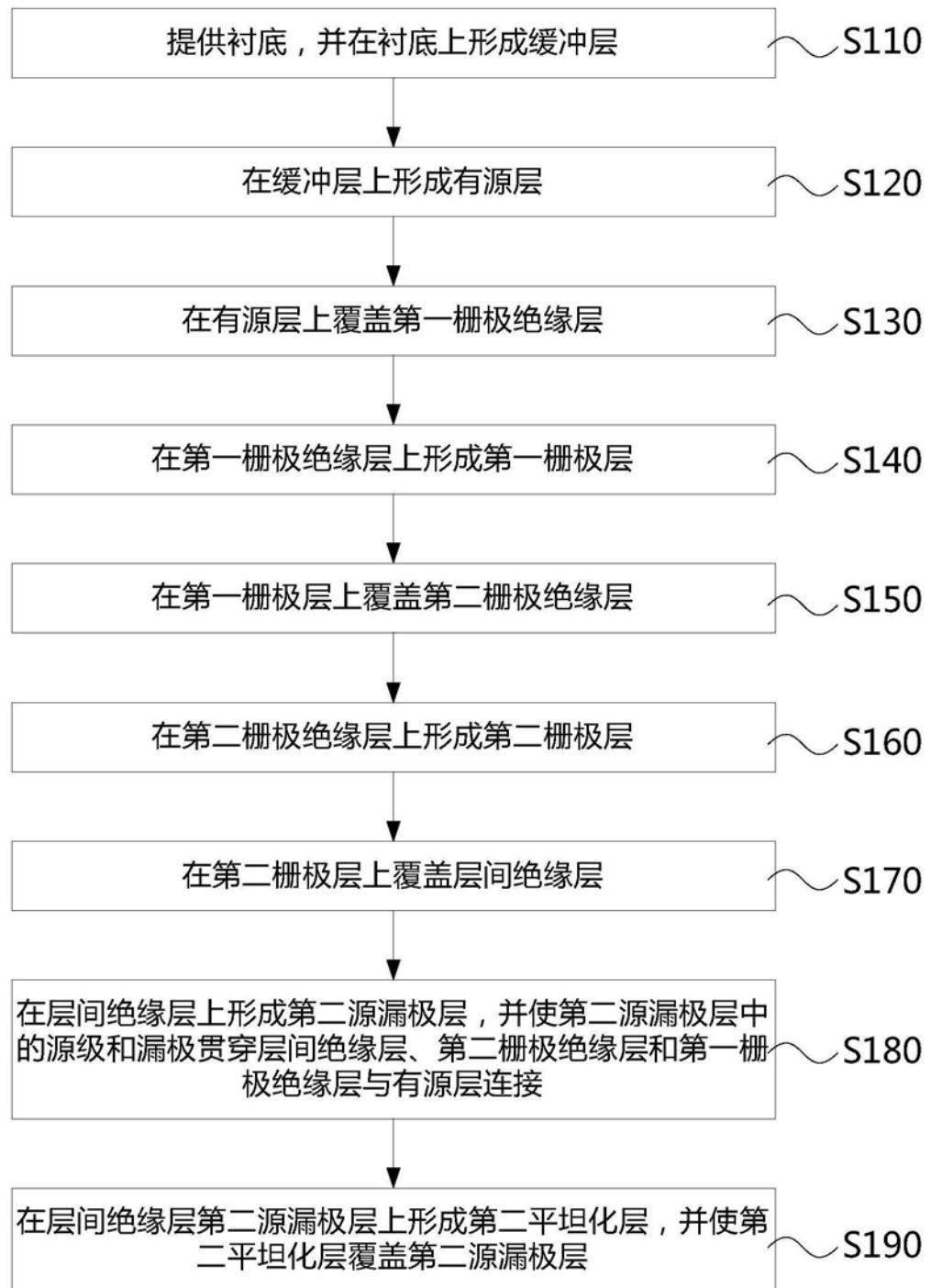

[0161] 举例来说，在图12中，提供阵列基板的步骤包括步骤S110至步骤S190。在步骤S110中，提供衬底，并在衬底上形成缓冲层。在步骤S120中，在缓冲层上形成有源层。在步骤S130中，在有源层上覆盖第一栅极绝缘层。在步骤S140中，在第一栅极绝缘层上形成第一栅极层。在步骤S150中，在第一栅极层上覆盖第二栅极绝缘层。在步骤S160中，在第二栅极绝缘层上形成第二栅极层。在步骤S170中，在第二栅极层上覆盖层间绝缘层。在步骤S180中，在层间绝缘层上形成第二源漏极层，并使第二源漏极层中的源极和漏极贯穿层间绝缘层、第二栅极绝缘层和第一栅极绝缘层与有源层连接。在步骤S190中，在所述层间绝缘层形成第二平坦化层，并使所述第二平坦化层覆盖所述第二源漏极层。

[0162] 步骤S200可以独立于步骤S190，也可以与步骤S190合并，即在形成第二平坦化层时，通过同一构图工艺形成位于阵列基板的非像素区的凸起结构，以节省工序。在另一些实施例中，在所述非像素区形成多个凸起结构时，所述多个凸起结构的一部分与所述填充材料通过同一构图工艺形成，所述多个凸起结构中的另一部分与所述第二平坦化层通过同一构图工艺形成。

[0163] 图13(a)-图13(k)是根据本公开显示基板的一个实施例的制造过程的示意图。

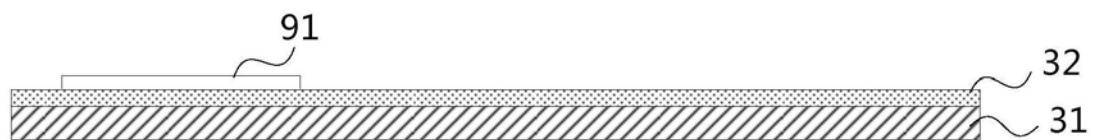

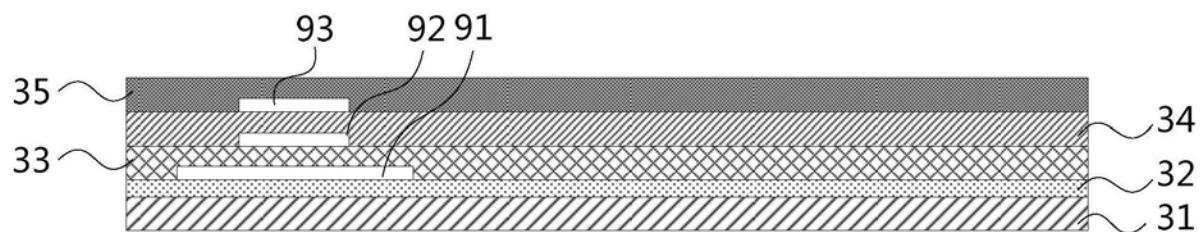

[0164] 下面结合图13 (a) 至图13 (k) 对本公开的一个显示基板实施例的制造过程进行说明。在图13 (a) 中, 提供衬底31。在图13 (b) 中, 在衬底31上形成缓冲层32, 并在缓冲层32上形成有源层91。在图13 (c) 中, 在有源层91上覆盖第一栅极绝缘层33, 第一栅极绝缘层33也覆盖在缓冲层32上。接下来在第一栅极绝缘层33上形成第一栅极层92, 并在第一栅极层92上覆盖第二栅极绝缘层, 第二栅极绝缘层34也覆盖在第一栅极绝缘层33上。然后, 在第二栅极绝缘层34上形成第二栅极层93, 并在第二栅极层93上覆盖层间绝缘层35, 层间绝缘层35也覆盖在第二栅极绝缘层34上。

[0165] 对于需要实现弯折功能的显示基板来说, 其阵列基板可包括显示区域和弯折区域。在图13 (d) 中, 可在显示区域形成贯穿层间绝缘层35、第二栅极绝缘层34和第一栅极绝缘层33的过孔A和B, 并在弯折区域形成贯穿层间绝缘层35、第二栅极绝缘层34、第一栅极绝缘层33和缓冲层32的凹槽C。过孔A、B与凹槽C可在同一工序中形成, 也可在不同工序中形成。

[0166] 在图13 (e) 中, 通过半色调工艺既向凹槽C填入填充材料110作为基板弯折图形, 又在层间绝缘层35的非像素区上形成凸起结构40。填充材料110和凸起结构40均可采用聚酰亚胺, 且相对于层间绝缘层35来说, 填充材料110的最大高度为500~1200nm, 而凸起结构40的最大高度为1200~3000nm。

[0167] 在图13 (f) 中, 在层间绝缘层35上形成第一金属层22和第一源漏极层, 并且使得第一金属层22覆盖在凸起结构40上。在形成显示基板时, 可使第一金属层22与工作电压端导电连接。这样第一源漏极层中的源极94和漏极95分别通过过孔A和B与有源层91电连接, 从而形成了阵列基板中的薄膜晶体管。第一金属层22和第一源漏极层可通过同一构图工艺形成。第一金属层22可以覆盖或不覆盖到弯折区域。

[0168] 在图13 (g) 中, 在层间绝缘层35上形成平坦化材料层50', 并使得平坦化材料层50' 覆盖第一金属层22、第一源漏极层的源极94和漏极95。平坦化材料层50' 可以覆盖或不覆盖到弯折区域。不同位置的平坦化材料层50' 相对于层间绝缘层35的高度有所不同, 其中位于凸起结构40上侧的区域51相比于其他区域更高。

[0169] 在图13 (h) 中, 对平坦化材料层50' 进行处理, 以形成更平坦的第一平坦化层50。在此过程中, 可去除平坦化材料层50' 的处理区域51的材料, 以露出所述第一金属层22。

[0170] 在图13 (i) 中, 在第一平坦化层50上依次形成第二金属层63、像素定义层61和有机发光层62。第二金属层63覆盖在第一金属层22上, 并与第一金属层22直接接触并电连接。在形成第二金属层63时, 可以通过同一构图工艺形成阳极层。

[0171] 在图13 (j) 中, 在像素定义层61和有机发光层62对应于凸起结构40上方的部位形成过孔D, 露出过孔D底部的第二金属层63。此时, 形成过孔时需要移除的材料厚度较薄, 移除时的生成物较少。

[0172] 在图13 (k) 中, 在有机发光层62上形成阴极层70, 阴极层70能够覆盖过孔D的侧壁和底部, 并与第二金属层63直接接触并电连接。这样阴极层70就能够通过各个凸起结构40上方的第二金属层63和第一金属层22与工作电压端建立起电连接, 从而实现辅助阴极的作用。

[0173] 前述的各个显示基板的实施例可应用在用于有机发光二极管显示装置, 相应的, 本公开还提供了包括前述任一种显示基板实施例的有机发光二极管显示装置。该有机发光

二极管显示装置可以为：手机、平板电脑、电视机、显示器、笔记本电脑、数码相框、导航仪等任何具有显示功能的产品或部件。

[0174] 至此，已经详细描述了本公开的各实施例。为了避免遮蔽本公开的构思，没有描述本领域所公知的一些细节。本领域技术人员根据上面的描述，完全可以明白如何实施这里公开的技术方案。

[0175] 虽然已经通过示例对本公开的一些特定实施例进行了详细说明，但是本领域的技术人员应该理解，以上示例仅是为了进行说明，而不是为了限制本公开的范围。本领域的技术人员应该理解，可在不脱离本公开的范围和精神的情况下，对以上实施例进行修改或者对部分技术特征进行等同替换。本公开的范围由所附权利要求来限定。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

31

图13 (a)

图13 (b)

图13 (c)

图13 (d)

图13 (e)

图13 (f)

图13 (g)

图13 (h)

图13 (i)

图13 (j)

图13 (k)

|                |                                                            |         |            |

|----------------|------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示基板及其制造方法、有机发光二极管显示装置                                     |         |            |

| 公开(公告)号        | <a href="#">CN110112205A</a>                               | 公开(公告)日 | 2019-08-09 |

| 申请号            | CN201910524464.5                                           | 申请日     | 2019-06-18 |

| [标]申请(专利权)人(译) | 京东方科技股份有限公司                                                |         |            |

| 申请(专利权)人(译)    | 京东方科技股份有限公司                                                |         |            |

| 当前申请(专利权)人(译)  | 京东方科技股份有限公司                                                |         |            |

| [标]发明人         | 田宏伟<br>牛亚男<br>李栋<br>刘明<br>刘政                               |         |            |

| 发明人            | 田宏伟<br>牛亚男<br>李栋<br>刘明<br>刘政                               |         |            |

| IPC分类号         | H01L27/32 H01L51/52 H01L51/56                              |         |            |

| CPC分类号         | H01L27/3276 H01L27/3279 H01L51/5228 H01L51/56 H01L2227/323 |         |            |

| 代理人(译)         | 王莉莉                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>             |         |            |

### 摘要(译)

本公开涉及一种显示基板及其制造方法、有机发光二极管显示装置。显示基板包括：阵列基板，包括显示区域，显示区域包括像素区和围绕像素区的非像素区；凸起结构，沿第一方向位于阵列基板上，且位于非像素区，第一方向为显示基板的出光方向或出光方向的相反方向；第一金属层，沿第一方向位于凸起结构上，并与工作电压端导电连接；第一平坦化层，沿第一方向位于阵列基板上；多个功能层和阴极层，沿第一方向在第一平坦化层上依次设置；其中，阴极层通过过孔与第一金属层电连接。