(12)发明专利申请

(10)申请公布号 CN 109686313 A

(43)申请公布日 2019.04.26

(21)申请号 201910023117.4

(22)申请日 2019.01.10

(71)申请人 昆山国显光电有限公司

地址 215300 江苏省苏州市昆山市开发区

龙腾路1号4幢

(72)发明人 张元波 韩珍珍 胡思明 吴剑龙

(74)专利代理机构 北京远智汇知识产权代理有

限公司 11659

代理人 张海英

(51)Int.Cl.

G09G 3/3258(2016.01)

权利要求书3页 说明书9页 附图14页

(54)发明名称

一种像素电路、显示面板及像素电路的驱动

方法

(57)摘要

本发明公开了一种像素电路、显示面板及像

素电路的驱动方法。该像素电路包括电压反置单

元，包括第一控制端、第一输入端和第一输出端；

所述第一控制端与所述数据线电连接，所述第一

输入端用于输入电平电压，所述第一输出端与所

述发光单元的阳极电连接；所述电压反置单元用

于根据所述数据线上的信号，在相邻两帧之间

的时间段将所述发光单元的阳极和阴极之间的电

压反向偏置。与现有OLED显示面板中发光单元的

使用寿命较短相比，本发明最大程度地延长了发

光单元反向偏置的时间，延长了发光单元的使用

寿命，最终延长了OLED显示面板的使用寿命。

1.一种像素电路,其特征在于,包括:

驱动单元,包括数据电压输入端、第一扫描信号输入端和驱动输出端,所述数据电压输入端与数据线电连接,所述第一扫描信号输入端与第一扫描线电连接,所述驱动输出端与发光单元的阳极电连接;所述驱动单元还包括第一电平信号输入端,所述第一电平信号输入端与第一电源信号线电连接;所述发光单元的阴极与第二电源信号线电连接;所述驱动单元用于响应所述数据线上的数据电压和所述第一扫描线上的第一扫描信号,在一帧的发光阶段输出驱动信号至所述发光单元的阳极;

电压反置单元,包括第一控制端、第一输入端和第一输出端;所述第一控制端与所述数据线电连接,所述第一输入端用于输入电平电压,所述第一输出端与所述发光单元的阳极电连接;所述电压反置单元用于根据所述数据线上的信号,在相邻两帧之间的时间段将所述发光单元的阳极和阴极之间的电压反向偏置。

2.根据权利要求1所述的像素电路,其特征在于,

所述电压反置单元包括第一晶体管,所述第一晶体管的栅极、第一极和第二极分别作为所述电压反置单元的第一控制端、第一输入端和第一输出端;

在相邻两帧之间的时间段,所述第二电源信号线的电平为高电平;在帧内的时间段,所述第二电源信号线上的电平为低电平。

3.根据权利要求1所述的像素电路,其特征在于,所述电压反置单元包括第二晶体管、第三晶体管和第四晶体管;所述驱动单元还包括第一电平信号输入端,所述第一电平信号输入端与第一电源信号线电连接;

所述第二晶体管的栅极作为所述电压反置单元的第一控制端,所述第二晶体管的第一极与所述发光单元的阳极电连接,所述第二晶体管的第二极与第二电源信号线或参考电压线电连接;

所述第三晶体管的栅极与第一控制信号线电连接,所述第三晶体管的第一极与所述发光单元的阴极电连接,所述第三晶体管的第二极与所述第二电源信号线电连接;

所述第四晶体管的栅极与所述第一控制端电连接,所述第四晶体管的第一极与所述发光单元的阴极电连接,所述第四晶体管的第二极与所述第一电源信号线或所述第一控制信号线电连接。

4.根据权利要求3所述的像素电路,其特征在于,

所述驱动单元包括第五晶体管、第六晶体管、第七晶体管、第八晶体管、第九晶体管、第十晶体管和第一存储电容;所述第七晶体管的栅极与第一扫描线电连接,第一极与参考电压线电连接,第二极与第五晶体管的栅极电连接;所述第六晶体管的栅极与第二扫描线电连接,第一极与数据线电连接,第二极与第五晶体管的第一极电连接;第八晶体管的栅极与第二扫描线电连接,第一极与第五晶体管的第二极电连接,第二极与第五晶体管的栅极电连接;第九晶体管的栅极与发光控制线电连接,第一极与第一电源信号线电连接,第二极与第五晶体管的第一极电连接;第十晶体管的栅极与发光控制线电连接,第一极与五晶体管的第二极电连接,第二极与所述驱动输出端电连接;第一存储电容的第一极与第五晶体管的栅极电连接,第二极与第一电源信号线电连接。

5.根据权利要求4所述的像素电路,其特征在于,

所述电压反置单元包括第十一晶体管和第十二晶体管;所述第十一晶体管的栅极与第

二控制信号线电连接,第一极与第一扫描线电连接,第二极与所述第二晶体管的栅极电连接;第十二晶体管的栅极与第三控制信号线电连接,第一极与所述数据线电连接,第二极与所述第二晶体管的栅极电连接。

6. 根据权利要求4所述的像素电路,其特征在于,所述电压反置单元还包括第十三晶体管;

所述第十三晶体管的第一极与所述驱动输出端电连接,第二极与所述发光单元的阳极电连接,栅极与第一控制信号线电连接。

7. 一种显示面板,其特征在于,包括:多个如权利要求1-6任一项所述的像素电路。

8. 一种像素电路的驱动方法,其特征在于,所述像素电路包括驱动单元和电压反置单元;所述驱动单元包括数据电压输入端、第一扫描信号输入端和驱动输出端,所述数据电压输入端与数据线电连接,所述第一扫描信号输入端与第一扫描线电连接,所述驱动输出端与发光单元的阳极电连接;所述电压反置单元包括第一控制端、第一输入端和第一输出端;所述第一控制端与所述数据线电连接,所述第一输入端用于输入电平电压,所述第一输出端与所述发光单元的阳极电连接;

所述像素电路的驱动方法包括:帧内显示阶段和两帧之间空白阶段;

在所述两帧之间空白阶段,通过所述数据线向所述电压反置单元的第一控制端传输控制信号,以及向所述电压反置单元的第一控制端输入电平电压,控制所述电压反置单元的第一输出端输出所述电平电压,将所述发光单元的阳极和阴极之间的电压反向偏置。

9. 根据权利要求8所述的像素电路的驱动方法,其特征在于,所述驱动单元还包括第一电平信号输入端,所述第一电平信号输入端与第一电源信号线电连接;

所述发光单元的阴极与第二电源信号线电连接;

所述电压反置单元包括第一晶体管,所述第一晶体管的栅极、第一极和第二极分别作为所述电压反置单元的第一控制端、第一输入端和第一输出端;

所述像素电路的驱动方法还包括:

在所述两帧之间空白阶段,通过所述数据线向所述第一晶体管的栅极传输控制信号,以及向所述第一晶体管的第一极输入电平电压,控制所述第一晶体管的第二极输出所述电平电压;

所述电平电压为低电平,所述第二电源信号线上的电平为高电平。

10. 根据权利要求8所述的像素电路的驱动方法,其特征在于,所述电压反置单元包括第二晶体管、第三晶体管和第四晶体管;所述驱动单元还包括第一电平信号输入端,所述第一电平信号输入端与第一电源信号线电连接;

所述第二晶体管的栅极作为所述电压反置单元的第一控制端,所述第二晶体管的第一极与所述发光单元的阳极电连接,所述第二晶体管的第二极与第二电源信号线或参考电压线电连接;

所述第三晶体管的栅极与第一控制信号线电连接,所述第三晶体管的第一极与所述发光单元的阴极电连接,所述第三晶体管的第二极与所述第二电源信号线电连接;

所述第四晶体管的栅极与所述第一控制端电连接,所述第四晶体管的第一极与所述发光单元的阴极电连接,所述第四晶体管的第二极与所述第一电源信号线或所述第一控制信号线电连接;

所述像素电路的驱动方法还包括：

在所述两帧之间空白阶段，通过所述第一控制信号线向所述第三晶体管传输第一控制信号，控制所述第三晶体管关断；通过所述数据线向所述第二晶体管的栅极和所述第四晶体管的栅极传输控制信号，控制所述第二晶体管和所述第四晶体管导通。

## 一种像素电路、显示面板及像素电路的驱动方法

### 技术领域

[0001] 本发明实施例涉及显示技术领域,尤其涉及一种像素电路、显示面板及像素电路的驱动方法。

### 背景技术

[0002] 有机发光二极管(Organic Light-Emitting Diode,OLED)显示面板具有低能耗、生产成本低、自发光、宽视角及响应速度快等优点,目前,在手机、PDA、数码相机等显示领域得到广泛的应用。

[0003] 然而,随着OLED显示面板的使用,其发光单元的发光效率降低,因此,OLED显示面板的发光单元存在使用寿命较低的问题。

### 发明内容

[0004] 本发明提供一种像素电路、显示面板及像素电路的驱动方法,以延长OLED显示面板的发光单元的使用寿命。

[0005] 第一方面,本发明实施例提供了一种像素电路,该像素电路包括:

[0006] 驱动单元,包括数据电压输入端、第一扫描信号输入端和驱动输出端,所述数据电压输入端与数据线电连接,所述第一扫描信号输入端与第一扫描线电连接,所述驱动输出端与发光单元的阳极电连接;所述驱动单元用于响应所述数据线上的数据电压和所述第一扫描线上的第一扫描信号,在一帧的发光阶段输出驱动信号至所述发光单元的阳极;

[0007] 电压反置单元,包括第一控制端、第一输入端和第一输出端;所述第一控制端与所述数据线电连接,所述第一输入端用于输入电平电压,所述第一输出端与所述发光单元的阳极电连接;所述电压反置单元用于根据所述数据线上的信号,在相邻两帧之间的时间段将所述发光单元的阳极和阴极之间的电压反向偏置。

[0008] 进一步地,所述电压反置单元包括第一晶体管,所述第一晶体管的栅极、第一极和第二极分别作为所述电压反置单元的第一控制端、第一输入端和第一输出端;

[0009] 在相邻两帧之间的时间段,所述第二电源信号线的电平为高电平;在帧内的时间段,所述第二电源信号线上的电平为低电平。

[0010] 进一步地,所述电压反置单元包括第二晶体管、第三晶体管和第四晶体管;所述驱动单元还包括第一电平信号输入端,所述第一电平信号输入端与第一电源信号线电连接;

[0011] 所述第二晶体管的栅极作为所述电压反置单元的第一控制端,所述第二晶体管的第一极与所述发光单元的阳极电连接,所述第二晶体管的第二极与第二电源信号线或参考电压线电连接;

[0012] 所述第三晶体管的栅极与第一控制信号线电连接,所述第三晶体管的第一极与所述发光单元的阴极电连接,所述第三晶体管的第二极与所述第二电源信号线电连接;

[0013] 所述第四晶体管的栅极与所述第一控制端电连接,所述第四晶体管的第一极与所述发光单元的阴极电连接,所述第四晶体管的第二极与所述第一电源信号线或所述第一控

制信号线电连接。

[0014] 进一步地,所述驱动单元包括第五晶体管、第六晶体管、第七晶体管、第八晶体管、第九晶体管、第十晶体管和第一存储电容;所述第七晶体管的栅极与第一扫描线电连接,第一极与参考电压线电连接,第二极与第五晶体管的栅极电连接;所述第六晶体管的栅极与第二扫描线电连接,第一极与数据线电连接,第二极与第五晶体管的第一极电连接;第八晶体管的栅极与第二扫描线电连接,第一极与第五晶体管的第二极电连接,第二极与第五晶体管的栅极电连接;第九晶体管的栅极与发光控制线电连接,第一极与第一电源信号线电连接,第二极与第五晶体管的第一极电连接;第十晶体管的栅极与发光控制线电连接,第一极与五晶体管的第二极电连接,第二极与所述驱动输出端电连接;第一存储电容的第一极与第五晶体管的栅极电连接,第二极与第一电源信号线电连接;

[0015] 进一步地,所述电压反置单元包括第十一晶体管和第十二晶体管;所述第十一晶体管的栅极与第二控制信号线电连接,第一极与第一扫描线电连接,第二极与所述第二晶体管的栅极电连接;第十二晶体管的栅极与第三控制信号线电连接,第一极与所述数据线电连接,第二极与所述第二晶体管的栅极电连接。

[0016] 进一步地,所述电压反置单元还包括第十三晶体管;

[0017] 所述第十三晶体管的第一极与所述驱动输出端电连接,第二极与所述发光单元的阳极电连接,栅极与第一控制信号线电连接。

[0018] 第二方面,本发明实施例还提供了一种显示面板,该显示面板包括:多个如本发明任意实施例所述的像素电路。

[0019] 第三方面,本发明实施例还提供了一种像素电路的驱动方法,所述像素电路的驱动方法包括:帧内显示阶段和两帧之间空白阶段;

[0020] 在所述两帧之间空白阶段,通过所述数据线向所述电压反置单元的第一控制端传输控制信号,以及向所述电压反置单元的第一控制端输入电平电压,控制所述电压反置单元的第一输出端输出所述电平电压,将所述发光单元的阳极和阴极之间的电压反向偏置。

[0021] 本发明实施例设置电压反置单元包括第一控制端、第一输入端和第一输出端;第一控制端与数据线电连接,第一输入端用于输入电平电压,第一输出端与发光单元的阳极电连接;电压反置单元用于根据数据线上的信号,在相邻两帧之间的时间段将发光单元的阳极和阴极之间的电压反向偏置。本发明巧妙地利用两帧之间空白阶段对发光单元进行反向偏置,这样设置有两方面优点:一是在帧内时间段数据线需要向像素电路提供数据电压,扫描线需要向像素电路提供扫描信号,而在两帧之间空白阶段数据线和扫描线均处于闲置状态,数据线上的信号变换不会对发光单元的发光状态产生影响,利用数据线向电压反置单元传输控制信号提高了数据线的利用率,减少了显示面板的走线数量,以及多条数据线与显示面板上的每个像素电路电连接,通过驱动芯片可以控制多条数据线同时向显示面板上的多个像素电路同时传输控制信号,从而控制显示面板上多个发光单元的电压同时反向偏置,最大程度地利用两帧之间空白阶段对发光单元进行反向偏置;二是,若在帧内显示阶段对发光单元的电压进行反向偏置,只能利用扫描线对下一行即将被驱动的发光单元进行电压反置,该时间较短,设一帧显示的时间为T,像素行数为m,该时间为T/m,而两帧之间空白阶段的时间较长,增加了对发光单元进行反置的时间调节的灵活性,并且可以根据显示效果确定发光单元进行电压反置的时间,增强了显示效果。基于以上两点,与现有OLED显示

面板中发光单元的使用寿命较短相比,本发明有利于在显示画面不变的情况下对发光单元的电压进行反向偏置,且最大程度地延长了发光单元反向偏置的时间,从而在很大程度上削弱了内建电场的强度,减缓了有机材料的极性化加速,降低了发光单元在产品点亮时的阈值电压增加,减少了发光单元效率降低的速率,进而延长了发光单元的使用寿命,最终延长了OLED显示面板的使用寿命。

## 附图说明

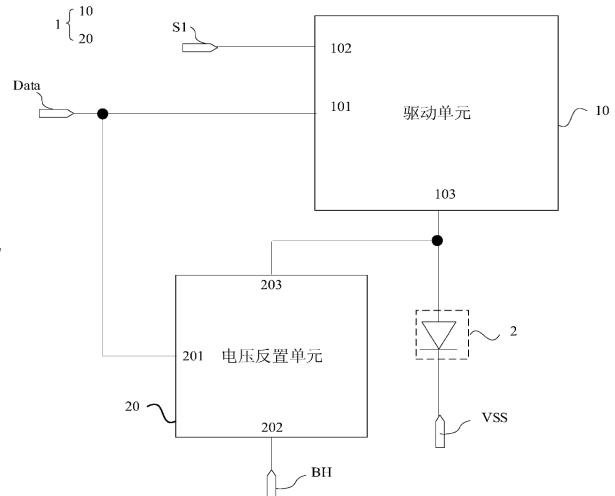

- [0022] 图1为本发明实施例提供的一种像素电路的结构示意图;

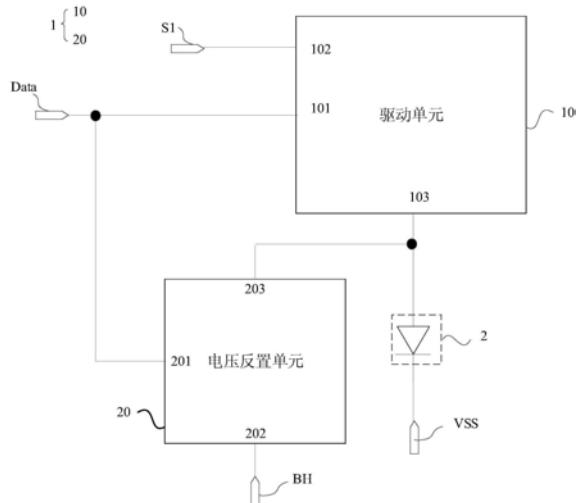

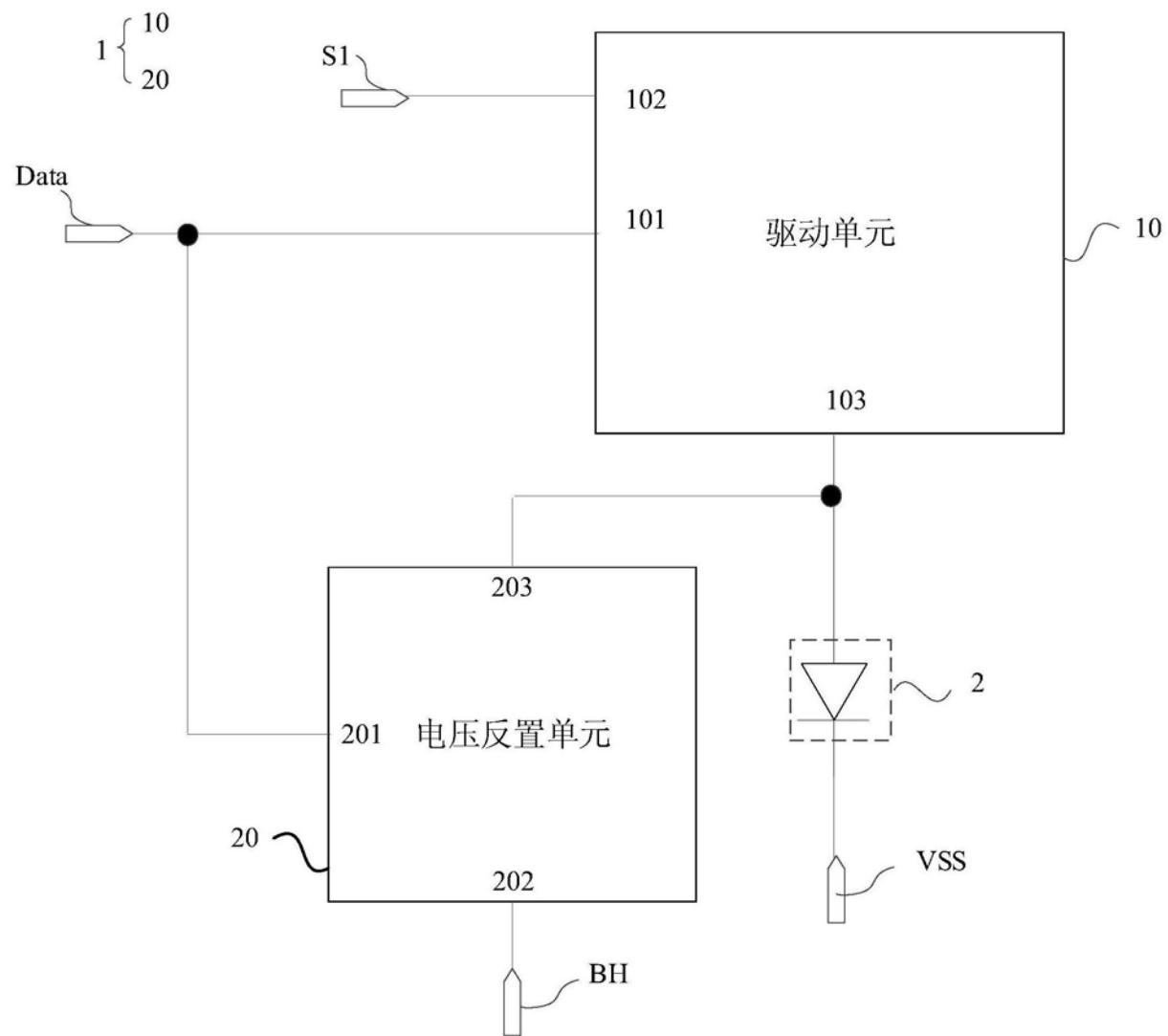

- [0023] 图2为本发明实施例提供的另一种像素电路的结构示意图;

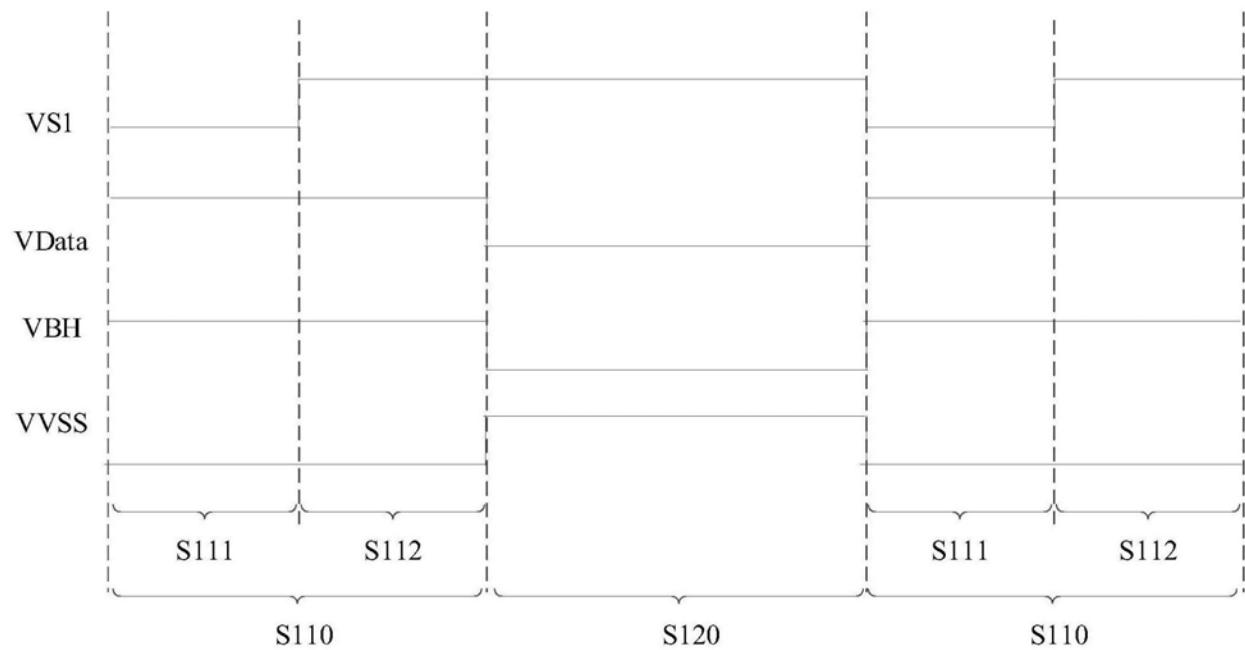

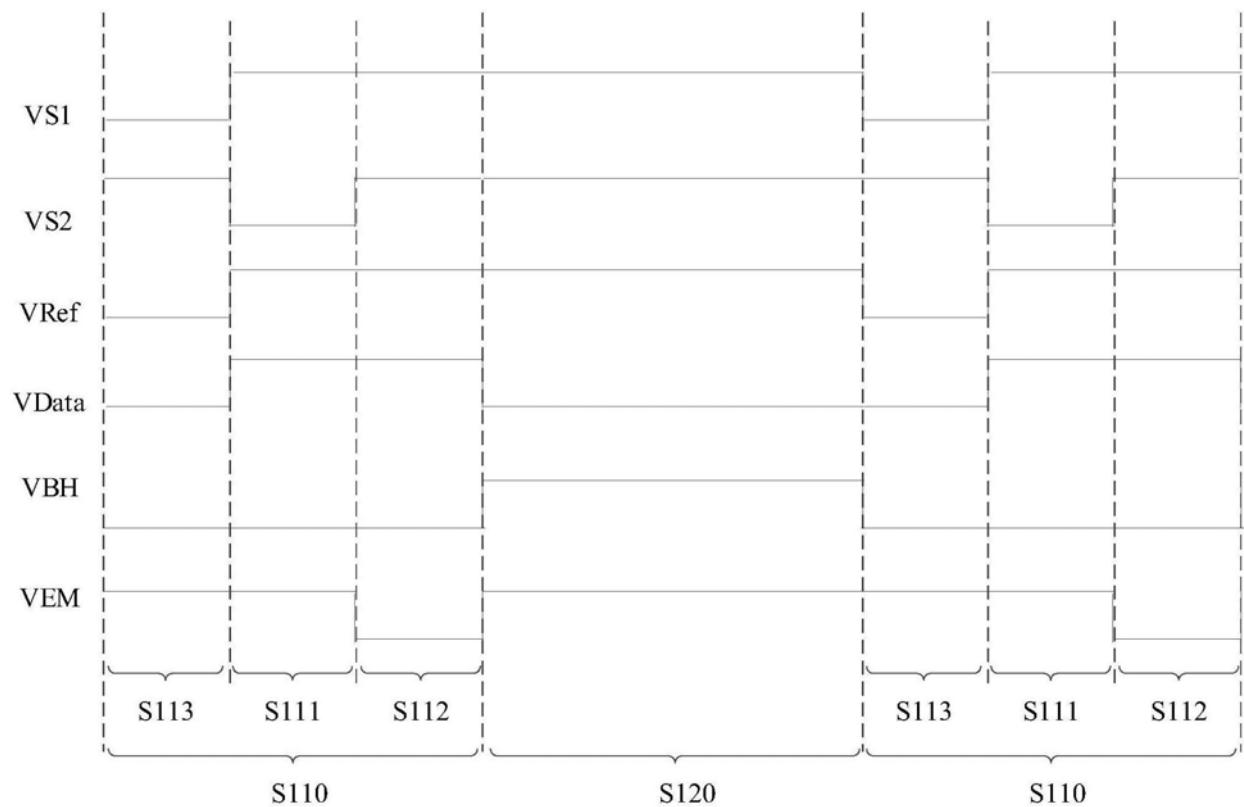

- [0024] 图3为本发明实施例提供的一种像素电路的时序图;

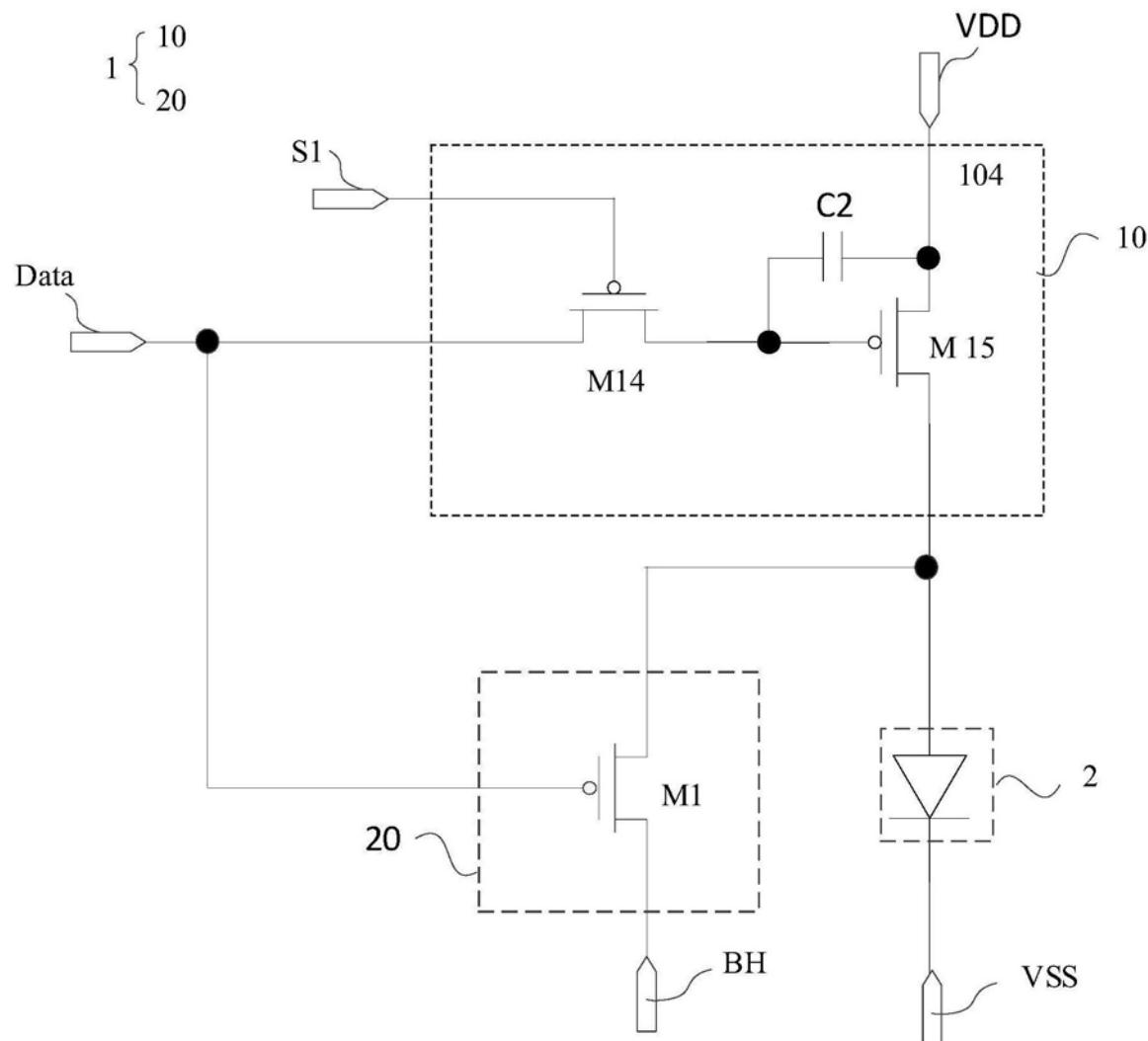

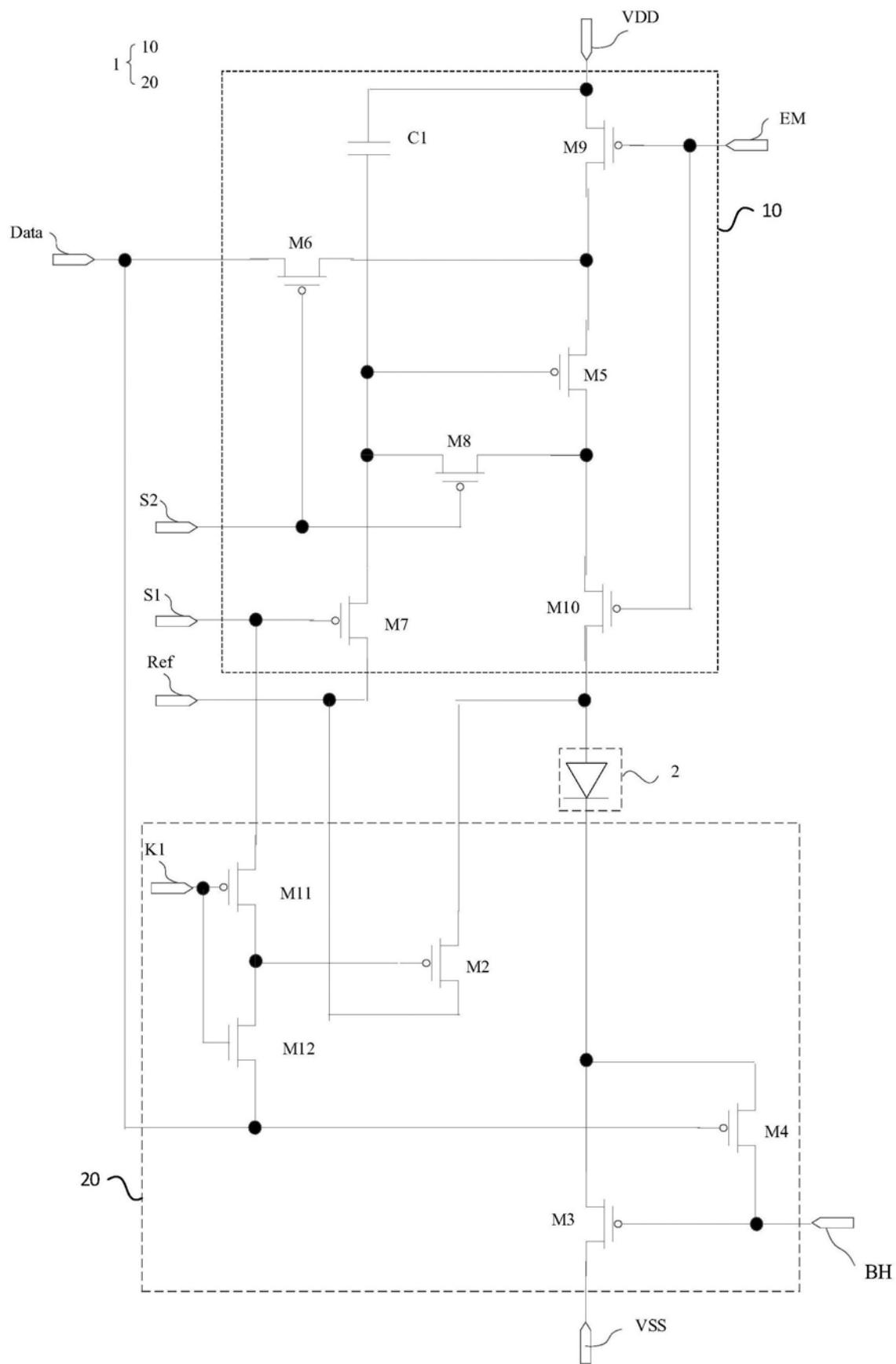

- [0025] 图4为本发明实施例提供的另一种像素电路的结构示意图;

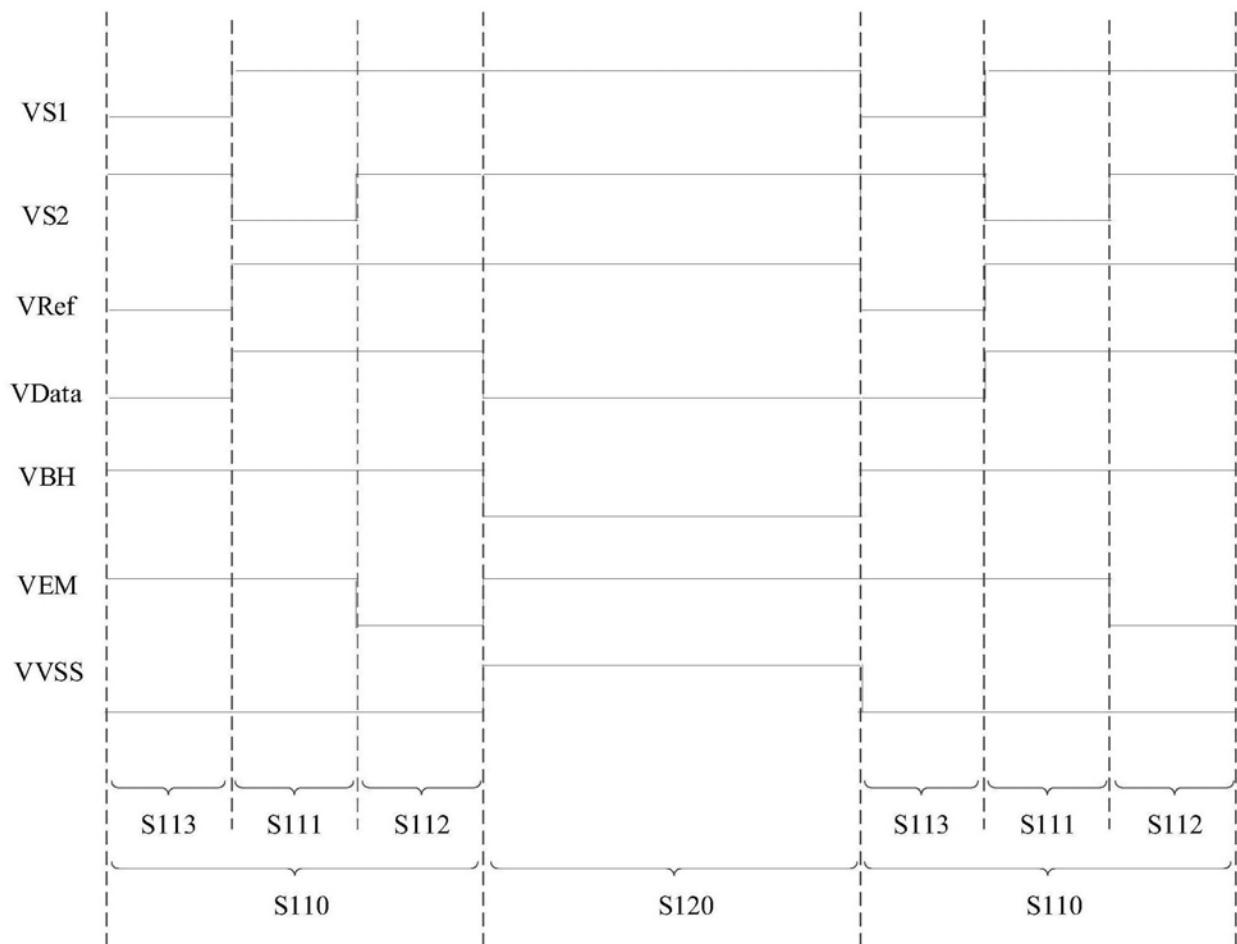

- [0026] 图5为本发明实施例提供的另一种像素电路的时序图;

- [0027] 图6为本发明实施例提供的又一种像素电路的结构示意图;

- [0028] 图7为本发明实施例提供的又一种像素电路的时序图

- [0029] 图8为本发明实施例提供的又一种像素电路的结构示意图;

- [0030] 图9为本发明实施例提供的又一种像素电路的结构示意图;

- [0031] 图10为本发明实施例提供的又一种像素电路的结构示意图;

- [0032] 图11为本发明实施例提供的又一种像素电路的结构示意图;

- [0033] 图12为本发明实施例提供的又一种像素电路的结构示意图;

- [0034] 图13为本发明提供的一种显示面板的结构示意图;

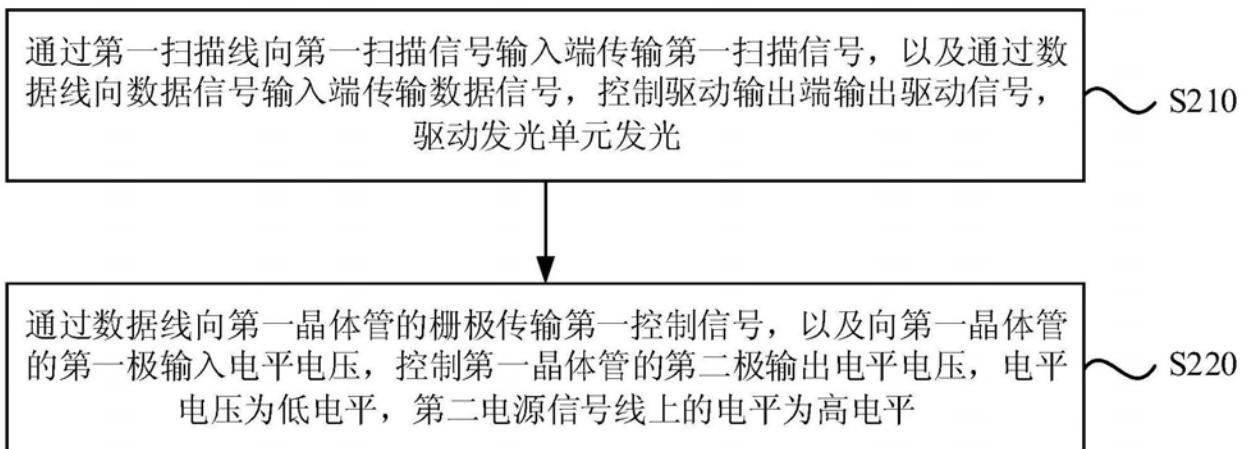

- [0035] 图14为本发明实施例提供的一种像素电路的驱动方法的流程图;

- [0036] 图15为本发明实施例提供的另一种像素电路的驱动方法的流程图;

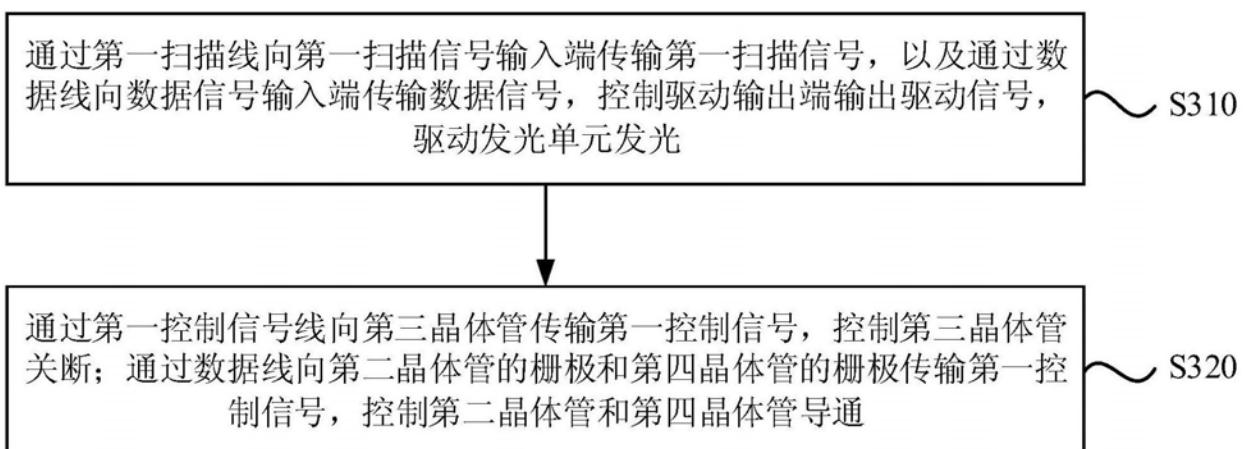

- [0037] 图16为本发明实施例提供的又一种像素电路的驱动方法的流程图。

## 具体实施方式

[0038] 下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的一部分而非全部结构。

[0039] 在现有技术中,像素电路一般包括驱动单元和发光单元,驱动单元包括数据电压输入端、第一扫描信号输入端和驱动输出端,数据电压输入端与数据线电连接,第一扫描信号输入端与第一扫描线电连接,驱动输出端与发光单元的阳极电连接。在帧内显示阶段,第一扫描线输出扫描信号至像素电路,控制数据线上的数据电压写入像素电路,在发光阶段,像素电路根据写入的数据电压产生驱动电流,驱动发光单元发光。发光单元长期处于直流偏置发光状态,有机材料的极性化加速,造成发光单元的内建电场(半导体或者绝缘体中由于内部的作用而形成的电场)随之迅速增强,从而导致发光单元的阈值电压增大,降低了发光单元的发光效率,大幅度缩短了发光单元的使用寿命。为解决这些问题,本发明实施例中,在像素电路中设置电压反置单元,电压反置单元包括第一控制端、第一输入端和第一输出端;第一控制端与数据线电连接,第一输入端用于输入电平电压,第一输出端与发光单元的阳极电连接。电压反置单元用于根据数据线上的信号,在相邻两帧之间的时间段将发光

单元的阳极和阴极之间的电压反向偏置。如此,可以在相邻两帧之间的时间段,利用数据线信号闲置的时间段,向数据线传输控制信号,控制电压反置单元向发光单元的阳极输入低电平,向发光单元的阴极输入高电平,削弱发光单元的内建电场,避免内建电场的迅速增强,提高了发光单元的发光效率,增加了发光单元的使用寿命。下面将以具体的示例进行说明。

[0040] 图1为本发明实施例提供的一种像素电路的结构示意图。参见图1,该像素电路1包括驱动单元10和电压反置单元20。驱动单元10包括数据电压输入端101、第一扫描信号输入端102和驱动输出端103,数据电压输入端101与数据线Data电连接,第一扫描信号输入端102与第一扫描线S1电连接,驱动输出端103与发光单元2的阳极电连接;驱动单元10用于响应数据线Data上的数据电压和第一扫描线S1上的第一扫描信号,在一帧的发光阶段输出驱动信号至发光单元2的阳极。电压反置单元20包括第一控制端201、第一输入端202和第一输出端203;第一控制端201与数据线Data电连接,第一输入端202用于输入电平电压,第一输出端203与发光单元2的阳极电连接;电压反置单元20用于根据数据线Data上的信号,在相邻两帧之间的时间段将发光单元2的阳极和阴极之间的电压反向偏置。

[0041] 该像素电路1的驱动方法为,在帧内显示阶段,通过第一扫描线S1向第一扫描信号输入端102传输第一扫描信号,以及通过数据线Data向数据电压输入端101传输数据电压,控制驱动输出端103输出驱动信号,驱动发光单元2发光;在两帧之间空白阶段,通过数据线Data向电压反置单元20的第一控制端201传输控制信号,以及可以通过第一控制信号线BH向电压反置单元20的第一控制端201输入电平电压,控制电压反置单元20的第一输出端203输出电平电压,将发光单元2的阳极和阴极之间的电压反向偏置。

[0042] 本发明实施例设置电压反置单元20包括第一控制端201、第一输入端202和第一输出端203;第一控制端201与数据线Data电连接,第一输入端202用于输入电平电压,第一输出端203与发光单元2的阳极电连接;电压反置单元20用于根据数据线Data上的信号,在相邻两帧之间的时间段将发光单元2的阳极和阴极之间的电压反向偏置。本发明巧妙地利用两帧之间空白阶段对发光单元2进行反向偏置,这样设置有两方面优点:一是在帧内时间段数据线Data需要向像素电路1提供数据电压,扫描线S1需要向像素电路1提供扫描信号,而在两帧之间空白阶段数据线Data和扫描线S1均处于闲置状态,数据线Data上的信号变换不会对发光单元2的发光状态产生影响,利用数据线Data向电压反置单元20传输控制信号提高了数据线Data的利用率,减少了显示面板的走线数量,以及多条数据线Data与显示面板上的每个像素电路1电连接,通过驱动芯片可以控制多条数据线Data同时向显示面板上的多个像素电路1同时传输控制信号,从而控制显示面板上多个发光单元2的电压同时反向偏置,最大程度地利用两帧之间空白阶段对发光单元2进行反向偏置;二是,若在帧内显示阶段对发光单元2的电压进行反向偏置,只能利用扫描线S1对下一行即将被驱动的发光单元2进行电压反置,该时间较短,设一帧显示的时间为T,像素行数为m,该时间为T/m,而两帧之间空白阶段的时间较长,增加了对发光单元2进行反置的时间调节的灵活性,并且可以根据显示效果确定发光单元2进行电压反置的时间,增强了显示效果。基于以上两点,本发明有利于在显示画面不变的情况下对发光单元2的电压进行反向偏置,且最大程度地延长了发光单元2反向偏置的时间,从而在很大程度上削弱了内建电场的强度,减缓了有机材料的极性化加速,降低了发光单元2在产品点亮时的阈值电压增加,减少了发光单元2效率降低的

速率,进而延长了发光单元2的使用寿命,最终延长了显示面板的使用寿命。

[0043] 需要说明的是,本发明提供的电压反置单元20的设置方式有多种,下面就其中几种进行说明。

[0044] 图2为本发明实施例提供的另一种像素电路的结构示意图。参见图2,在上述各实施例的基础上,可选地,驱动单元10还包括第一电平信号输入端104,第一电平信号输入端104与第一电源信号线VDD电连接,发光单元2的阴极与第二电源信号线VSS电连接。电压反置单元20包括第一晶体管M1,第一晶体管M1的栅极、第一极和第二极分别作为电压反置单元20的第一控制端201、第一输入端202和第一输出端203。在相邻两帧之间的时间段,第二电源信号线VSS的电平为高电平;在帧内的时间段,第二电源信号线VSS上的电平为低电平。

[0045] 具体地,图2中的驱动单元10包括第十四晶体管M14、第十五晶体管M15、和第二存储电容C2。第十四晶体管M14的栅极与第一扫描线S1电连接,第一极与数据线Data电连接;第十五晶体管M15(驱动晶体管)的栅极与第十四晶体管M14的第二极电连接,第一极与第一电源信号线VDD电连接,第二极与发光单元2的阳极电连接;第二存储电容C2的第一极与第十五晶体管M15的栅极电连接,第二极与第十五晶体管M15的第一极电连接。

[0046] 图3为本发明实施例提供的一种像素电路的时序图。参见图2和图3,该像素电路1的工作过程包括帧内显示阶段S110和两帧之间空白阶段S120。其中帧内显示阶段S110包括数据电压写入阶段S111和发光阶段S112,在数据电压写入阶段S111,扫描信号VS1通过扫描线S1传输至第十四晶体管M14的栅极,第十四晶体管M14导通;在第十四晶体管M14导通期间,数据电压VData通过数据线Data和第十四晶体管M14传输至第十五晶体管M15的栅极,与此同时,第二存储电容C2充电至数据电压VData的电位。在发光阶段S112,第二存储电容C2保持充入的电位,使得第十五晶体管M15的栅极和第一极的电压差保持不变,第十五晶体管工作于饱和区,产生驱动电流。该驱动电流传输到发光单元2的阳极,流经发光单元2,传输至第二电源信号线VSS上,发光单元2响应该驱动电流而发光。在两帧之间空白阶段S120,通过数据线Data向第一晶体管M1的栅极传输控制信号(数据电压VData),以及向第一晶体管M1的第一极输入电平电压(例如第一控制信号VBH),第一晶体管M1导通,该电平电压通过第一晶体管M1的第二极输出至发光单元2的阳极,与此同时,通过控制驱动芯片(图2中未示出)输出高电平电压(第二电源信号VVSS)通过第二电源信号线VSS传输至发光单元2的阴极,从而将发光单元2的阳极和阴极之间的电压反向偏置。电压反置单元20这样设置,电路结构简单,仅需增加一根信号线即可实现在两帧之间空白阶段S120对发光单元2的电压的反向偏置。需要说明的,第一控制信号可以为高电平信号(例如,+7V),也可以为低电平信号(例如,-7V),具体可以根据第一晶体管M1的类型进行配置。

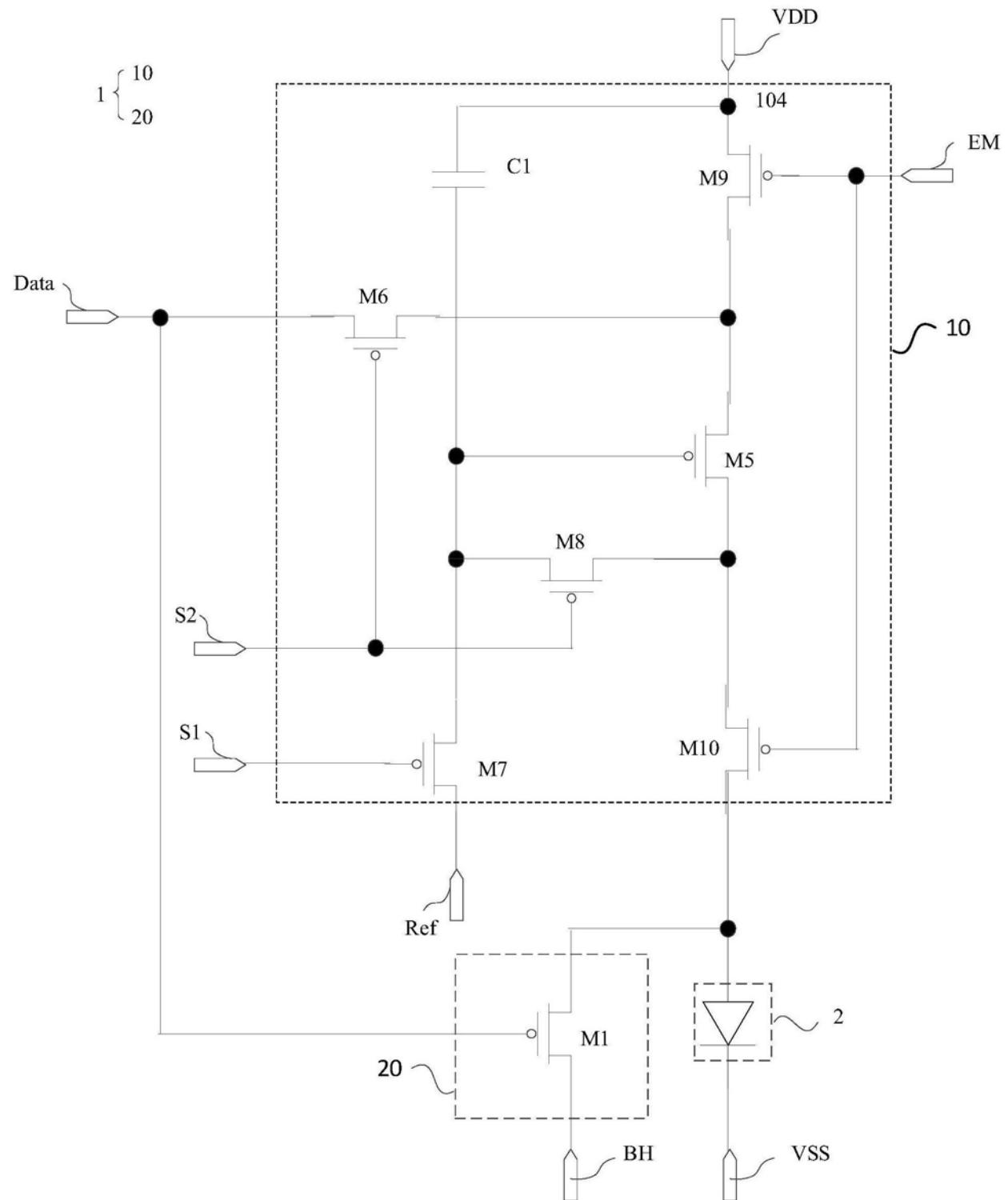

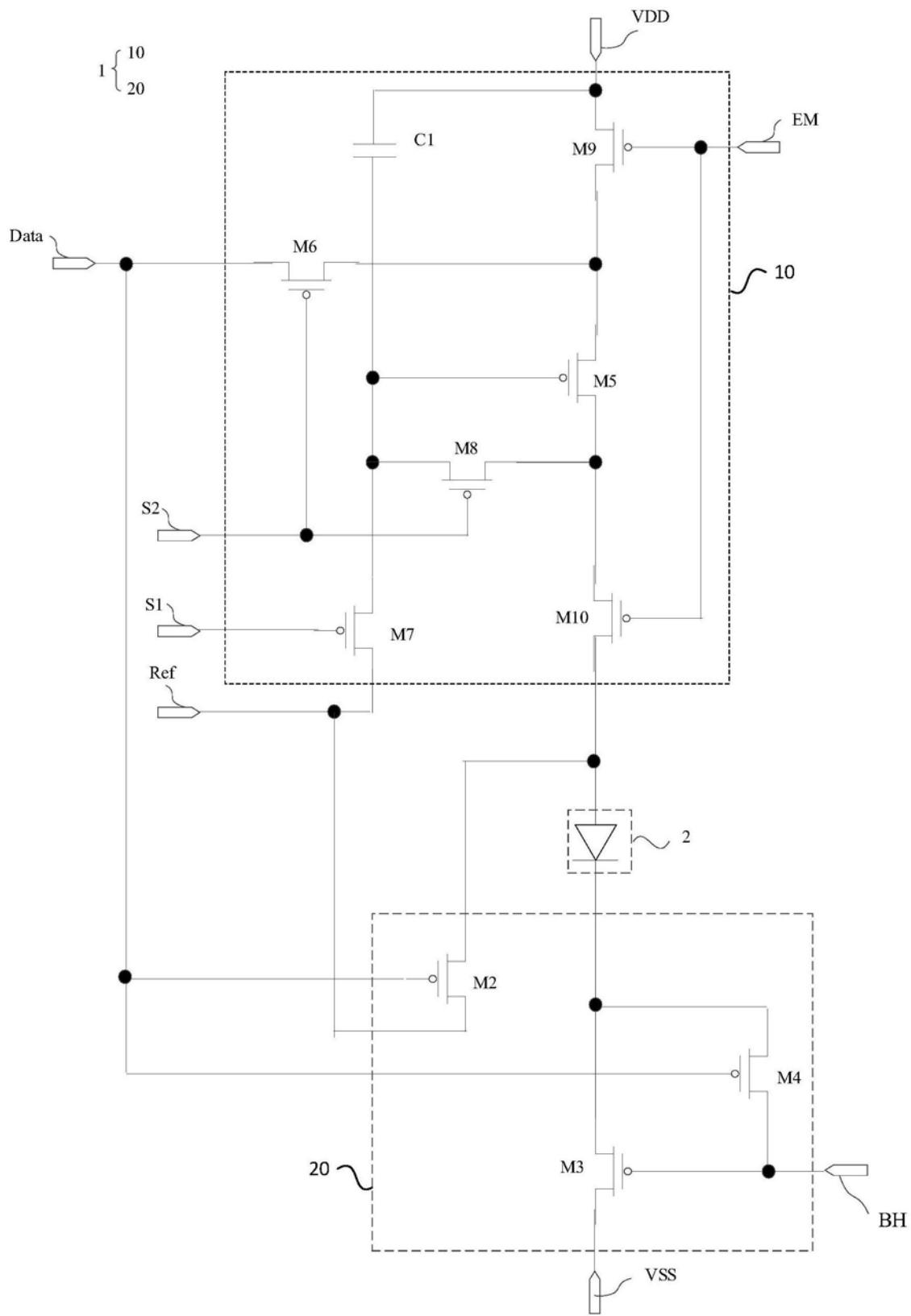

[0047] 需要说明的是,在上述实施例中采用如图2所示的驱动单元10对本发明进行说明,并非对本发明的限定,本发明还可以采用其他形式的像素电路1。图4为本发明实施例提供的另一种像素电路的结构示意图。参见图4,该像素电路1的驱动单元10包括第五晶体管M5(驱动晶体管)、第六晶体管M6、第七晶体管M7、第八晶体管M8、第九晶体管M9、第十晶体管M10和第一存储电容C1;第七晶体管M7的栅极与第一扫描线S1电连接,第一极与参考电压线Ref电连接,第二极与第五晶体管M5的栅极电连接;第六晶体管M6的栅极与第二扫描线S2电连接,第一极与数据线Data电连接,第二极与第五晶体管M5的第一极电连接;第八晶体管M8的栅极与第二扫描线S2电连接,第一极与第五晶体管M5的第二极电连接,第二极与第五晶

体管M5的栅极电连接；第九晶体管M9的栅极与发光控制信号线EM电连接，第一极与第一电源信号线VDD电连接，第二极与第五晶体管M5的第一极电连接；第十晶体管M10的栅极与发光控制信号线EM电连接，第一极与五晶体管的第二极电连接，第二极与驱动输出端103电连接；第一存储电容C1的第一极与第五晶体管M5的栅极电连接，第二极与第一电源信号线VDD电连接。

[0048] 图5为本发明实施例提供的另一种像素电路的时序图。参见图4和图5，该像素电路1的驱动方法包括帧内显示阶段S110和两帧之间空白阶段S120，其中，帧内显示阶段S110包括初始化阶段S113、数据写入阶段S111和发光阶段S112。示例性地，在初始化阶段，第一扫描线S1上的扫描信号VS1为低电平，第七晶体管M7导通，参考电压线Ref上的电压VRef通过导通的第七晶体管M7写入第五晶体管M5的栅极，该电压可以是为低电平，对第五晶体管M5的栅极和第一存储电容C1的第一极的电压进行初始化，保证下一阶段第五晶体管M5导通，数据电压VData能够写入第五晶体管M5的栅极；在数据写入阶段S111，第二扫描线S2上的信号VS2为低电平，第六晶体管M6和第八晶体管M8导通，数据线Data上的数据电压VData依次通过第六晶体管M6、第五晶体管M5和第八晶体管M8写入第五晶体管M5的栅极和第一存储电容C1的第一极，第五晶体管M5的栅极电压逐渐升高，直至第五晶体管M5的栅极电压和源极电压的电压差小于等于第五晶体管M5的阈值电压时，第五晶体管M5截止，第五晶体管M5的栅极电压保持不变；在发光阶段S112，发光控制信号线EM上的信号为低电平，第九晶体管M9和第十晶体管M10导通，第一扫描线S1和第二扫描线S2上的信号为高电平，第六晶体管M6、第七晶体管M7和第八晶体管M8截止。第一存储电容C1充电至数据电压VData，并保持该电位，使得第五晶体管M5的栅极和第一极的电压(即栅源电压)保持不变，根据晶体管的工作原理，第五晶体管M5的第二极输出恒定的驱动信号。在两帧之间空白阶段，通过数据线Data向第一晶体管M1的栅极传输控制信号(数据电压VData)，通过发光控制信号线EM向第九晶体管M9和第十晶体管M10的栅极传输发光控制信号VEM，以及向第一晶体管M1的第一极输入电平电压(例如低电平电压)，第一晶体管M1导通，第九晶体管M9和第十晶体管M10关断，该电平电压通过第一晶体管M1的第二极输出至发光单元2的阳极，与此同时，高电平电压(第二电源信号VVSS)通过第二电源信号线VSS传输至发光单元2的阴极，从而将发光单元2的阳极和阴极之间的电压反向偏置。这样在两帧之间空白阶段将发光单元2的阳极与第一电源电压信号线断开，降低了发光单元2阳极和第一电源电压信号线之间的漏流，从而降低了两帧之间空白阶段像素电路1的功耗。

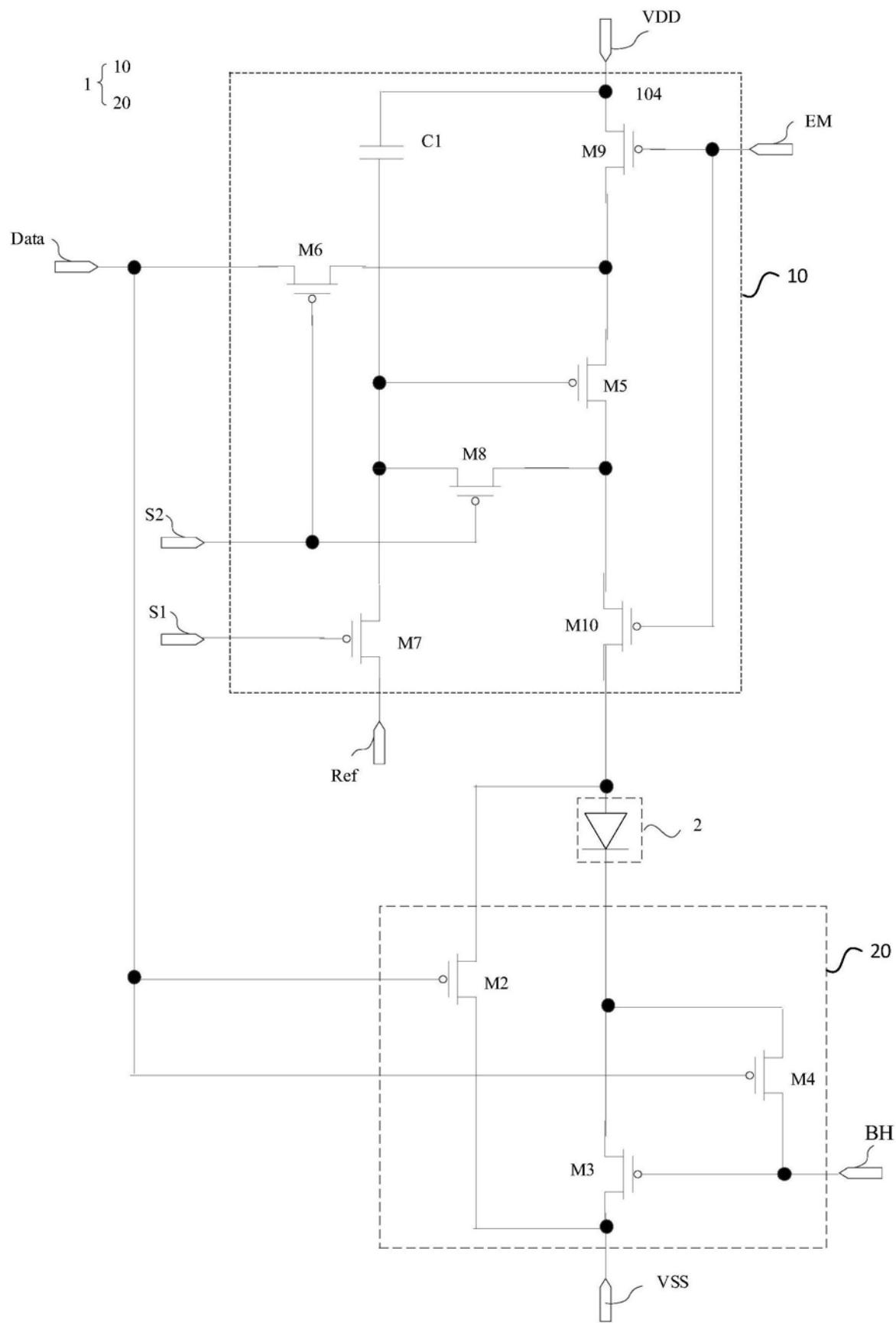

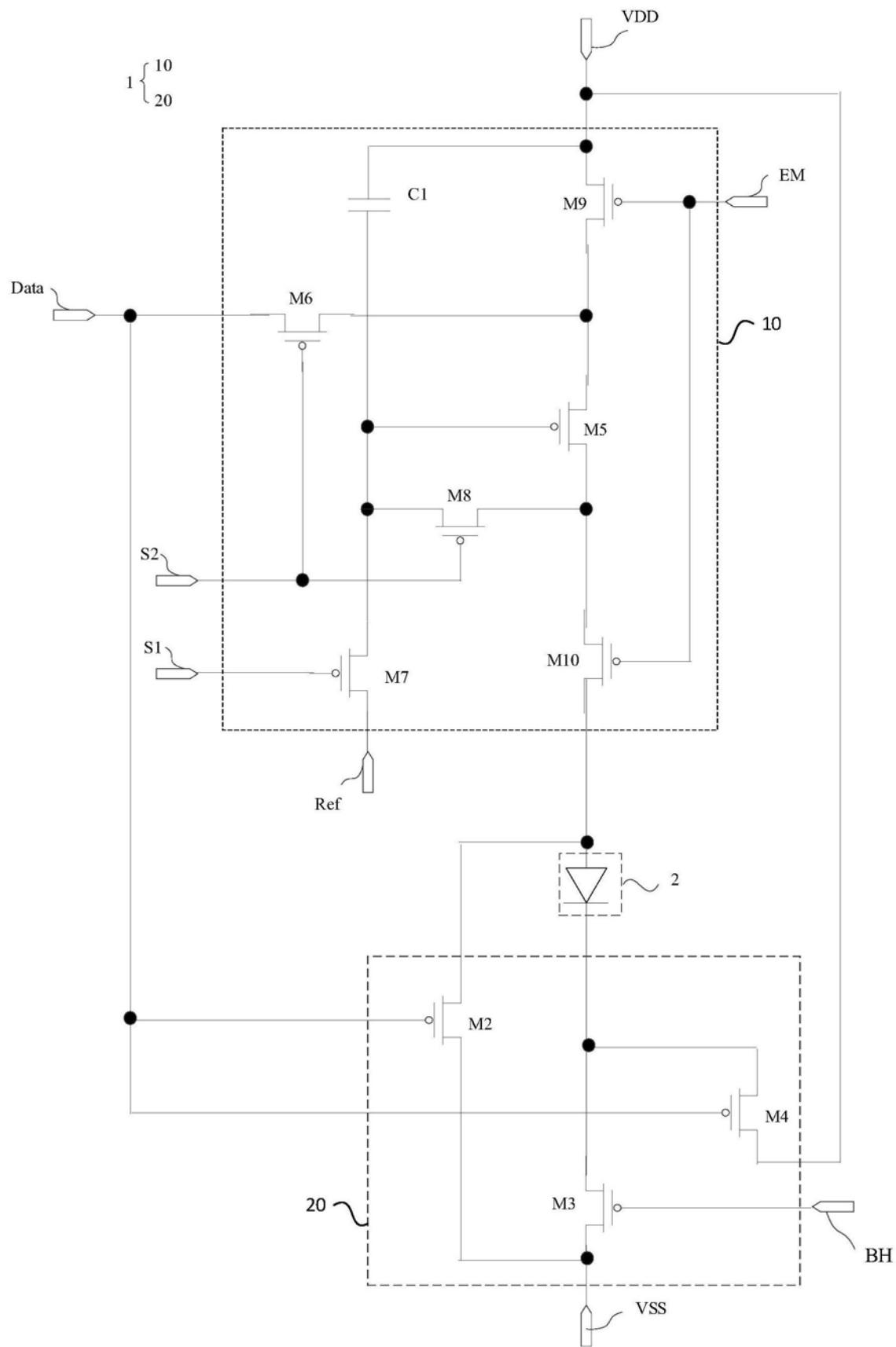

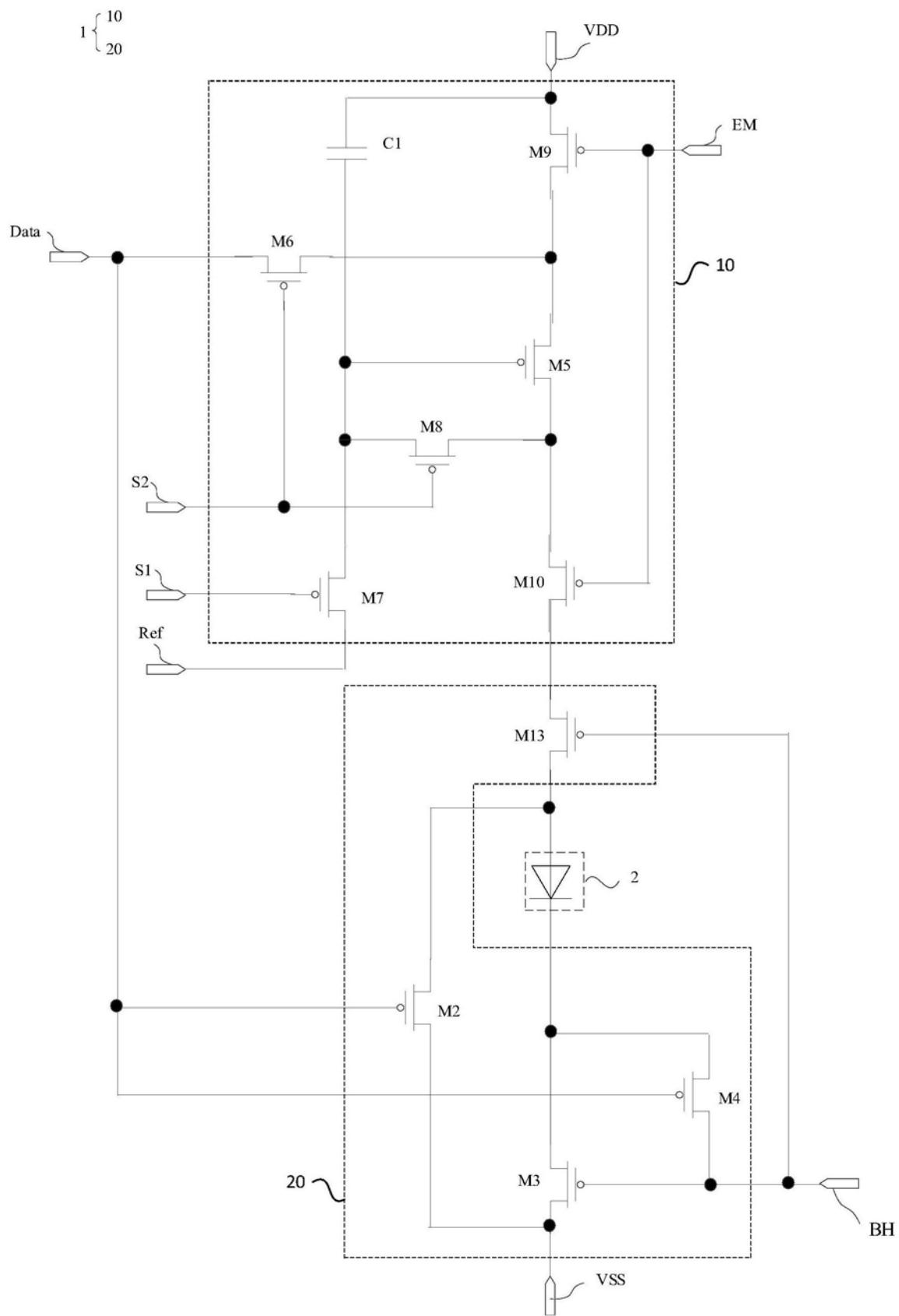

[0049] 图6为本发明实施例提供的又一种像素电路的结构示意图。参见图6，可选地，与上述实施方式不同的是，电压反置单元20包括第二晶体管M2、第三晶体管M3和第四晶体管M4；驱动单元10还包括第一电平信号输入端104，第一电平信号输入端104与第一电源信号线VDD电连接。第二晶体管M2的栅极作为电压反置单元20的第一控制端201，第二晶体管M2的第一极与发光单元2的阳极电连接，第二晶体管M2的第二极与第二电源信号线VSS电连接。第三晶体管M3的栅极与第一控制信号线BH电连接，第三晶体管M3的第一极与发光单元2的阴极电连接，第三晶体管M3的第二极与第二电源信号线VSS电连接。第四晶体管M4的栅极与第一控制端201电连接，第四晶体管M4的第一极与发光单元2的阴极电连接，第四晶体管M4的第二极与第一控制信号线BH电连接。图7为本发明实施例提供的又一种像素电路的时序图。参见图6和图7，在两帧之间空白阶段，通过第一控制信号线BH向第三晶体管M3传输第一

控制信号VBH,控制第三晶体管M3关断;通过数据线Data向第二晶体管M2的栅极和第四晶体管M4的栅极传输控制信号(数据电压VData),控制第二晶体管M2和第四晶体管M4导通。其中,低电平(VVSS)通过第二电源信号线VSS和第二晶体管M2传输至发光单元2的阳极,高电平通过第一控制信号线BH和第四晶体管M4传输至发光单元2的阴极。电压反置单元20这样设置,仅需增加一根信号线,且无需设置驱动芯片在两帧之间的空白阶段向第二电源信号线VSS传输高电平,控制方法较为简单。以及该电压反置单元20可以将各晶体管均设置为P型晶体管和N型晶体管,在显示面板的制作过程中,简化了工艺流程,降低了成本。

[0050] 需要说明的是,图6中第二晶体管M2和第四晶体管M4与各信号线的连接方式有多种,在实际应用中可以根据需要进行设置。例如,图8为本发明实施例提供的又一种像素电路的结构示意图,参见图8,与图6不同的是,第二晶体管M2的第二极与参考电压线Ref电连接,在两帧之间空白阶段,低电平通过参考电压线Ref和第二晶体管M2传输至发光单元2的阳极。又如,图9为本发明实施例提供的又一种像素电路的结构示意图,参见图9,与图6不同的是,第四晶体管M4的第二极与第一电源信号线VDD电连接,在两帧之间空白阶段,高电平通过第一电源信号线VDD和第四晶体管M4传输至发光单元2的阴极。

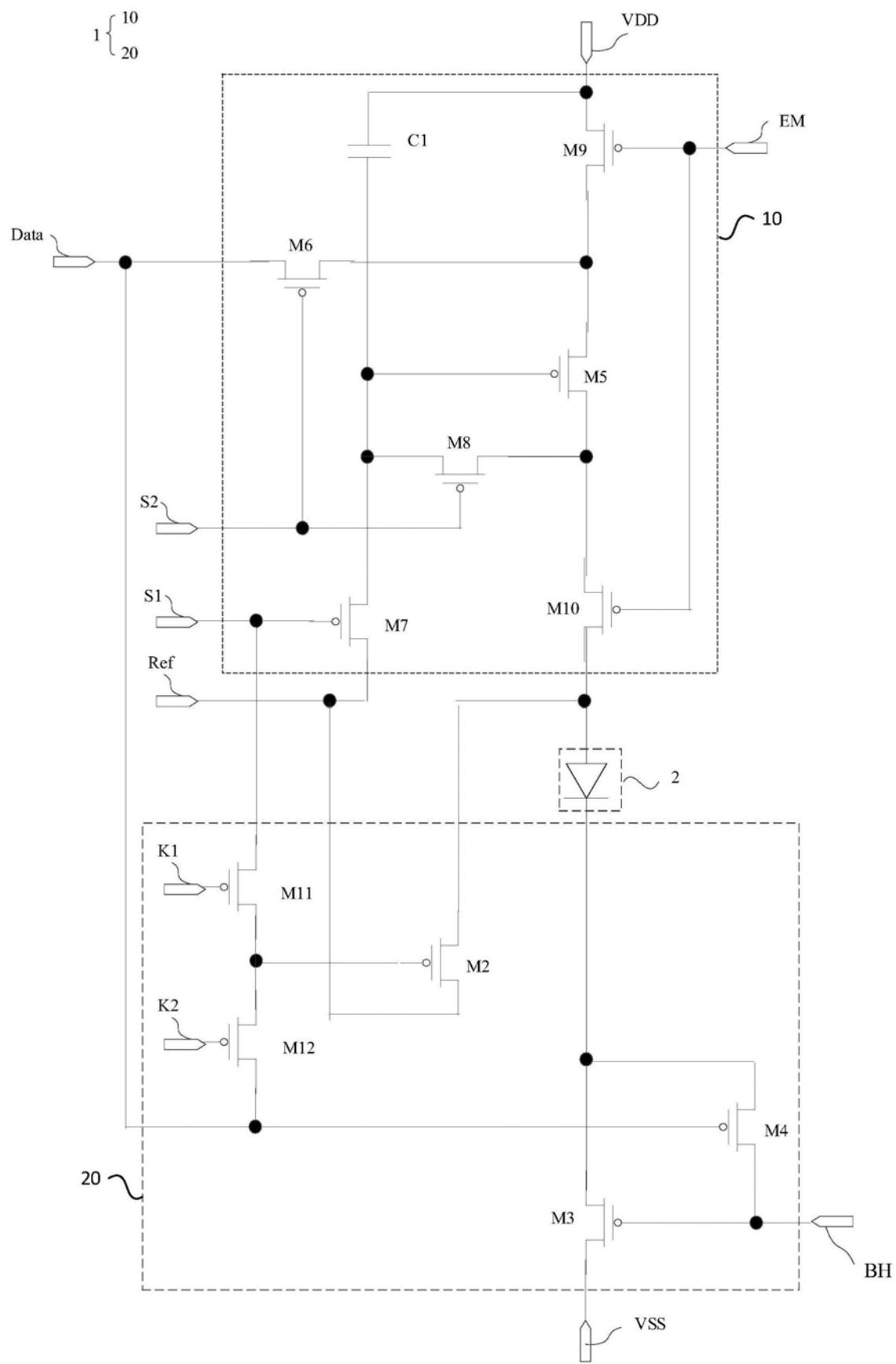

[0051] 图10为本发明实施例提供的又一种像素电路的结构示意图。参见图10,可选地,电压反置单元20包括第十一晶体管M11和第十二晶体管M12;第十一晶体管M11的栅极与第二控制信号线K1电连接,第一极与第一扫描线S1电连接,第二极与第二晶体管M2的栅极电连接;第十二晶体管M12的栅极与第三控制信号线K2电连接,第一极与数据线Data电连接,第二极与第二晶体管M2的栅极电连接。

[0052] 示例性地,在帧内显示阶段的初始化阶段,第二控制信号线K1上的信号控制第十一晶体管M11导通,第三控制信号线K2上的信号控制第十二晶体管M12关断,第一扫描线S1上的信号传输至第二晶体管M2的栅极,使得在帧内显示阶段,第一扫描线S1可以控制第二晶体管M2的开通和关断;第一扫描线S1上的信号控制第二晶体管M2和第七晶体管M7导通,参考电压线Ref上的电压通过导通的第七晶体管M7写入第五晶体管M5的栅极,参考电压可以是为低电平,对第五晶体管M5的栅极和第一存储电容C1的第一极的电压进行初始化,保证下一阶段第五晶体管M5导通,数据电压能够写入第五晶体管M5的栅极,与此同时,参考电压线Ref上的参考电压通过导通的第二晶体管M2传输到发光单元2的阳极,对发光单元2进行初始化。在相邻两帧之间的时间段,第二控制信号线K1上的电平电压控制第十一晶体管M11关断,第三控制信号线K2上的电平电压控制第十二晶体管M12导通,数据线Data上的信号传输至第二晶体管M2的栅极,使得在相邻两帧之间的时间段,数据线Data可以控制第二晶体管M2的导通和关断;通过第一控制信号线BH向第三晶体管M3传输第一控制信号,控制第三晶体管M3关断;通过数据线Data和第十二晶体管向第二晶体管M2的栅极和第四晶体管M4的栅极传输第一控制信号,控制第二晶体管M2和第四晶体管M4导通。其中,低电平通过第二电源信号线VSS和第二晶体管M2传输至发光单元2的阳极,高电平通过第一控制信号线BH和第四晶体管M4传输至发光单元2的阴极。电压反置单元20这样设置,可以使第二晶体管M2不仅可以在帧内显示阶段对发光单元2进行复位,还可以在相邻两帧之间的时间段对发光单元2进行电压反置。

[0053] 需要说明的是,图10中示例性地示出了第十一晶体管M11和第十二晶体管M12均为P型晶体管,并非对本发明的限定,在其他实施方式中,还可以设置第十一晶体管M11和第十

二晶体管M12均为N性晶体。

[0054] 图11为本发明实施例提供的又一种像素电路的结构示意图。参见图11,与上述实施方式不同的是,第十一晶体管M11和第十二晶体管M12为不同类型的晶体管,例如,第十一晶体管M11为P型晶体管,第十二晶体管M12为N型晶体管,或者,第十一晶体管M11为N型晶体管,第十二晶体管M12为P型晶体管。电压反置单元20这样设置,可以将第二控制信号线K1复用为第三控制信号线K2,省去了第三控制信号线K2的设置,使得布线方式更加简单。

[0055] 图12为本发明实施例提供的又一种像素电路的结构示意图。参见图12,在上述各实施例的基础上,可选地,电压反置单元20还包括第十三晶体管M13。第十三晶体管M13的第一极与驱动输出端103电连接,第二极与发光单元2的阳极电连接,栅极与第一控制信号线BH电连接。

[0056] 在帧内显示阶段,通过第一扫描线S1向第一扫描信号输入端102传输第一扫描信号,以及通过数据线Data向数据电压输入端101传输数据电压,控制驱动输出端103输出驱动信号,第一控制信号线BH上的信号控制第十三晶体管M13导通,驱动信号通过第十三晶体管M13传输至发光单元2,驱动发光单元2发光。在两帧之间空白阶段,通过数据线Data向电压反置单元20的第一控制端201传输第一控制信号,以及向电压反置单元20的第一控制端201输入电平电压,控制电压反置单元20的第一输出端203输出电平电压,将发光单元2的阳极和阴极之间的电压反向偏置,与此同时,第一控制信号线BH上的信号控制第十三晶体管M13关断,将发光单元2的阳极与第一电源电压信号线断开,降低了发光单元2阳极和第一电源电压信号线之间的漏流,从而降低了两帧之间空白阶段像素电路1的功耗。

[0057] 综上,本发明实施例巧妙地利用两帧之间空白阶段对发光单元2进行反向偏置,有利于在显示画面不变的情况下对发光单元2的电压进行反向偏置,且最大程度地延长了发光单元2反向偏置的时间,从而在很大程度上削弱了内建电场的强度,减缓了有机材料的极性化加速,降低了发光单元2在产品点亮时的阈值电压增加,减少了发光单元2效率降低的速率,进而延长了发光单元2的使用寿命,最终延长了显示面板的使用寿命。

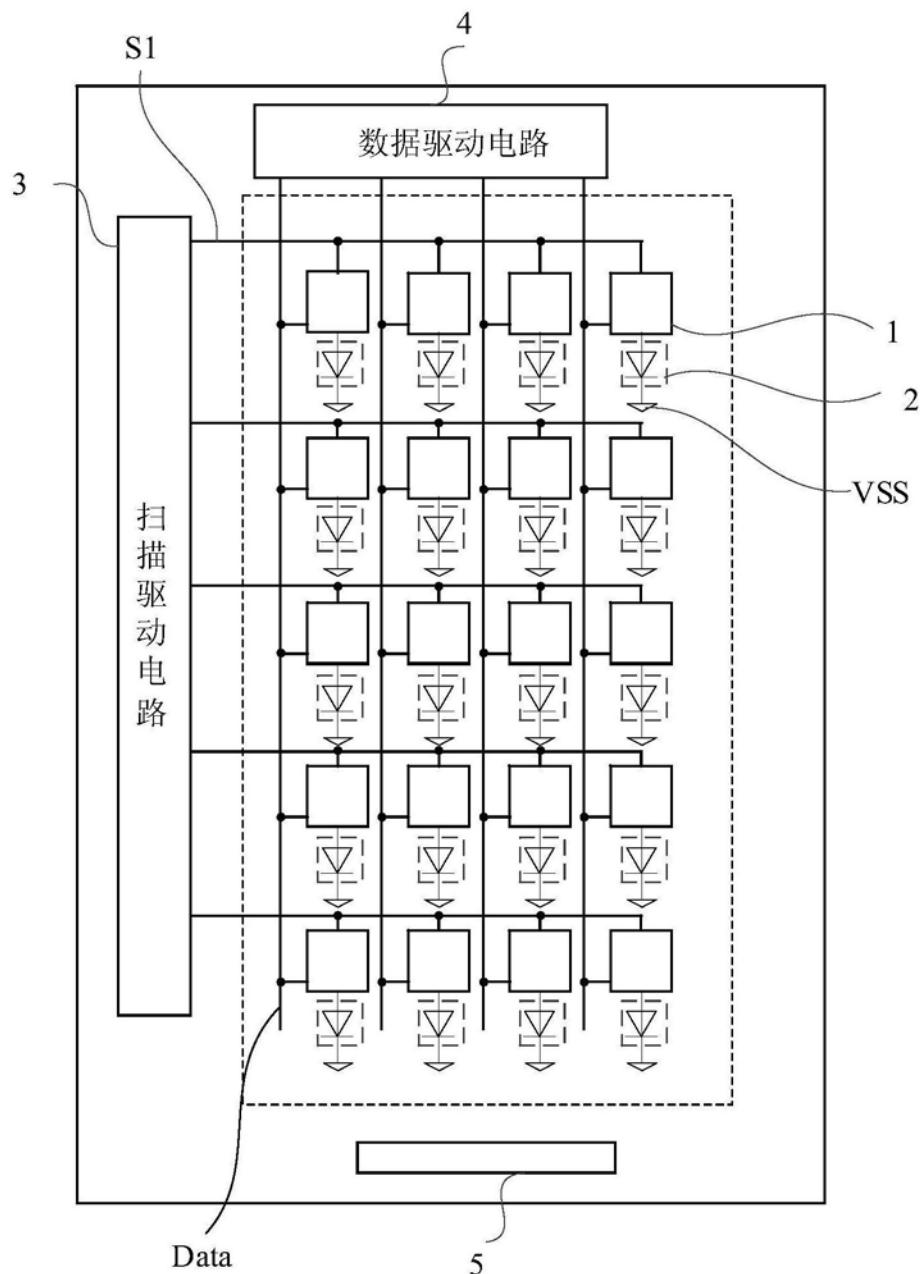

[0058] 本发明实施例还提供了一种显示面板。图13为本发明提供的一种显示面板的结构示意图。参见图13,该显示面板包括本发明任意实施例所提供的像素电路1。该显示面板还可以包括扫描驱动电路3、数据驱动电路4和驱动芯片5,其中扫描驱动电路3通过第一扫描线S1向像素电路1提供扫描信号,数据驱动电路4通过数据线S1向像素电路1提供数据电压,驱动芯片5通过第一控制信号线或第二电源电压信号线向像素电路1提供控制信号及电源电压信号。该显示面板包括本发明任意实施例所提供的像素电路,其技术原理和产生的技术效果类似,这里不再赘述。

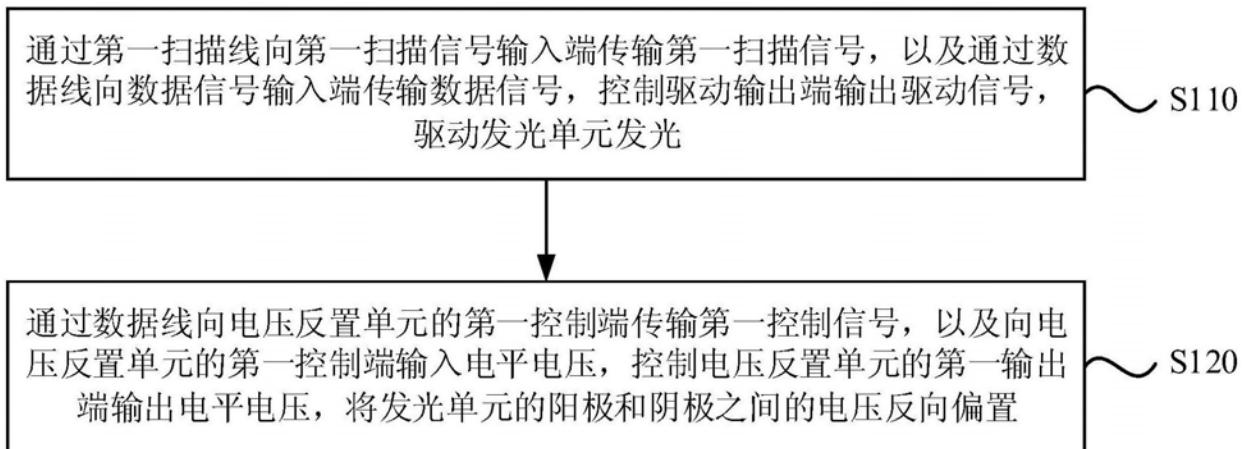

[0059] 本发明实施例还提供了一种像素电路1的驱动方法。图14为本发明实施例提供的一种像素电路的驱动方法的流程图。参见图14,在上述各实施例的基础上,该像素电路1的驱动方法包括:帧内显示阶段S110和两帧之间空白阶段S120。

[0060] 在两帧之间空白阶段S120,通过数据线Data向电压反置单元20的第一控制端201传输控制信号,以及向电压反置单元20的第一控制端201输入电平电压,控制电压反置单元20的第一输出端203输出电平电压,将发光单元2的阳极和阴极之间的电压反向偏置。

[0061] 具体地,在帧内显示阶段S110,通过第一扫描线S1向第一扫描信号输入端102传输第一扫描信号,以及通过数据线Data向数据电压输入端101传输数据电压,控制驱动输出端

103输出驱动信号,驱动发光单元2发光,使显示面板实现正常显示功能。

[0062] 本发明实施例巧妙地利用两帧之间空白阶段对发光单元2进行反向偏置,有利于在显示画面不变的情况下对发光单元2的电压进行反向偏置,且最大程度地延长了发光单元2反向偏置的时间,从而在很大程度上削弱了内建电场的强度,减缓了有机材料的极性化加速,降低了发光单元2在产品点亮时的阈值电压增加,减少了发光单元2效率降低的速率,进而延长了发光单元2的使用寿命,最终延长了显示面板的使用寿命。

[0063] 需要说明的是,根据具体的像素电路1的结构的不同,本发明提供的像素电路1的驱动方法有多种,下面就其中几种进行说明。

[0064] 图15为本发明实施例提供的另一种像素电路的驱动方法的流程图。参见图2和图15,驱动单元10还包括第一电平信号输入端104,第一电平信号输入端104与第一电源信号线VDD电连接;发光单元2的阴极与第二电源信号线VSS电连接;电压反置单元20包括第一晶体管M1,第一晶体管M1的栅极、第一极和第二极分别作为电压反置单元20的第一控制端201、第一输入端202和第一输出端203。

[0065] 该像素电路1的驱动方法包括:帧内显示阶段S210和两帧之间空白阶段S220。

[0066] 在两帧之间空白阶段S220,通过数据线Data向第一晶体管M1的栅极传输控制信号,以及向第一晶体管M1的第一极输入电平电压,控制第一晶体管M1的第二极输出电平电压,电平电压为低电平,第二电源信号线VSS上的电平为高电平。

[0067] 具体地,在帧内显示阶段S210,通过第一扫描线S1向第一扫描信号输入端102传输第一扫描信号,以及通过数据线Data向数据电压输入端101传输数据电压,控制驱动输出端103输出驱动信号,驱动发光单元2发光,使显示面板实现正常显示功能。

[0068] 图16为本发明实施例提供的又一种像素电路的驱动方法的流程图。参见图6和图16,电压反置单元20包括第二晶体管M2、第三晶体管M3和第四晶体管M4;驱动单元10还包括第一电平信号输入端104,第一电平信号输入端104与第一电源信号线VDD电连接;第二晶体管M2的栅极作为电压反置单元20的第一控制端201,第二晶体管M2的第一极与发光单元2的阳极电连接,第二晶体管M2的第二极与第二电源信号线VSS或参考电压线Ref电连接;第三晶体管M3的栅极与第一控制信号线BH电连接,第三晶体管M3的第一极与发光单元2的阴极电连接,第三晶体管M3的第二极与第二电源信号线VSS电连接;第四晶体管M4的栅极与第一控制端201电连接,第四晶体管M4的第一极与发光单元2的阴极电连接,第四晶体管M4的第二极与第一电源信号线VDD或第一控制信号线BH电连接。

[0069] 该像素电路1的驱动方法包括:帧内显示阶段S310和两帧之间空白阶段S320。

[0070] 在两帧之间空白阶段S320,通过第一控制信号线BH向第三晶体管M3传输第一控制信号,控制第三晶体管M3关断;通过数据线Data向第二晶体管M2的栅极和第四晶体管M4的栅极传输第一控制信号,控制第二晶体管M2和第四晶体管M4导通。

[0071] 注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

图12

图13

图14

图15

图16

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种像素电路、显示面板及像素电路的驱动方法                          |         |            |

| 公开(公告)号        | <a href="#">CN109686313A</a>                   | 公开(公告)日 | 2019-04-26 |

| 申请号            | CN201910023117.4                               | 申请日     | 2019-01-10 |

| [标]申请(专利权)人(译) | 昆山国显光电有限公司                                     |         |            |

| 申请(专利权)人(译)    | 昆山国显光电有限公司                                     |         |            |

| 当前申请(专利权)人(译)  | 昆山国显光电有限公司                                     |         |            |

| [标]发明人         | 张元波<br>韩珍珍<br>胡思明<br>吴剑龙                       |         |            |

| 发明人            | 张元波<br>韩珍珍<br>胡思明<br>吴剑龙                       |         |            |

| IPC分类号         | G09G3/3258                                     |         |            |

| CPC分类号         | G09G3/3258                                     |         |            |

| 代理人(译)         | 张海英                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

### 摘要(译)

本发明公开了一种像素电路、显示面板及像素电路的驱动方法。该像素电路包括电压反置单元，包括第一控制端、第一输入端和第一输出端；所述第一控制端与所述数据线电连接，所述第一输入端用于输入电平电压，所述第一输出端与所述发光单元的阳极电连接；所述电压反置单元用于根据所述数据线上的信号，在相邻两帧之间的时间段将所述发光单元的阳极和阴极之间的电压反向偏置。与现有OLED显示面板中发光单元的使用寿命较短相比，本发明最大程度地延长了发光单元反向偏置的时间，延长了发光单元的使用寿命，最终延长了OLED显示面板的使用寿命。