(12)发明专利申请

(10)申请公布号 CN 110085630 A

(43)申请公布日 2019.08.02

(21)申请号 201910101474.8

(22)申请日 2014.10.28

(30)优先权数据

14/494,931 2014.09.24 US

(62)分案原申请数据

201410589411.9 2014.10.28

(71)申请人 苹果公司

地址 美国加利福尼亚州

(72)发明人 蔡宗廷 V·格普塔 林敬伟

(74)专利代理机构 北京市金杜律师事务所

11256

代理人 王茂华 张宁

(51)Int.Cl.

H01L 27/32(2006.01)

权利要求书1页 说明书9页 附图10页

(54)发明名称

硅和半导体氧化物薄膜晶体管显示器

(57)摘要

本发明公开了一种可具有像素电路阵列的电子设备显示器。每个像素电路可包括有机发光二极管和驱动晶体管。每个驱动晶体管可被调节以控制通过有机发光二极管的电流量。每个像素电路可包括存储电容器和一个或多个另外的晶体管诸如开关晶体管。半导体氧化物晶体管和硅晶体管用于形成像素电路的晶体管。存储电容器和晶体管可使用金属层、半导体结构和电介质层来形成。这些层中的一些层可沿显示器的边缘被移除以有利于弯曲。电介质层可具有当数据线延伸到无效边缘区域中时允许阵列中的数据线向基板的表面逐渐降低的阶梯式外形。

1. 一种显示器,包括:

像素阵列,所述阵列中的每个像素包括:

发光二极管;

半导体氧化物开关晶体管,包括半导体氧化物沟道;

多晶硅驱动晶体管,包括多晶硅沟道;以及

存储电容器,耦合在所述半导体氧化物开关晶体管和所述发光二极管之间;以及

缓冲层,所述缓冲层与所述多晶硅沟道重叠并且不与所述半导体氧化物沟道重叠。

2. 根据权利要求1所述的显示器,其中所述电容器包括第一电极和第二电极,以及其中所述第一电极由第一金属层形成。

3. 根据权利要求2所述的显示器,其中所述半导体氧化物开关晶体管包括由所述第一金属层形成的栅极电极。

4. 根据权利要求2所述的显示器,其中所述多晶硅驱动晶体管包括由所述第一金属层形成栅极电极。

5. 根据权利要求4所述的显示器,其中所述第二电极由第二金属层形成,以及其中所述半导体氧化物开关晶体管包括由所述第二金属层形成的栅极电极。

6. 根据权利要求5所述的显示器,还包括:

公共源极-漏极金属层,所述公共源极-漏极金属层形成所述半导体氧化物开关晶体管的源极-漏极端子,并且形成所述多晶硅驱动晶体管的源极-漏极端子。

7. 根据权利要求1所述的显示器,还包括:

另外的缓冲层,所述另外的缓冲层与所述半导体氧化物沟道重叠并且不与所述存储电容器重叠。

8. 一种显示器,包括:

发光二极管的阵列;

硅薄膜晶体管,所述硅薄膜晶体管均耦合至所述发光二极管中的相应发光二极管并且均具有栅极,所述栅极控制被提供至所述发光二极管中的所述相应发光二极管的电流的量;

半导体氧化物薄膜晶体管,所述半导体氧化物薄膜晶体管均具有半导体氧化物沟道并且均提供电压至所述硅薄膜晶体管中的对应硅薄膜晶体管的栅极;以及

缓冲层,所述缓冲层与所述硅薄膜晶体管重叠并且不与所述半导体氧化物沟道重叠。

9. 根据权利要求8所述的显示器,还包括:

存储电容器,耦合在所述半导体氧化物薄膜晶体管中的每个半导体氧化物薄膜晶体管和所述发光二极管中的所述相应发光二极管之间;以及

另外的缓冲层,所述另外的缓冲层与所述半导体氧化物沟道重叠并且不与所述存储电容器重叠。

10. 根据权利要求8所述的显示器,其中所述硅薄膜晶体管包括由第一金属层形成的源极-漏极端子和由第二金属层形成的栅极电极,以及其中所述半导体氧化物薄膜晶体管包括由所述第一金属层形成的源极-漏极端子和由所述第二金属层形成的栅极电极。

## 硅和半导体氧化物薄膜晶体管显示器

[0001] 分案申请说明

[0002] 本申请是申请日为2014年10月28日、申请号为201410589411.9、名称为“硅和半导体氧化物薄膜晶体管显示器”的中国专利申请的分案申请。

### 背景技术

[0003] 本发明整体涉及电子设备，并且更具体地涉及带有具有薄膜晶体管的显示器的电子设备。

[0004] 电子设备通常包括显示器。例如，蜂窝电话和便携式计算机包括用于向用户呈现信息的显示器。

[0005] 显示器诸如有机发光二极管显示器具有基于发光二极管的像素阵列。在这种类型的显示器中，每个像素均包括发光二极管和薄膜晶体管，该薄膜晶体管用于控制向发光二极管施加信号。

[0006] 如果不小心，则显示器的薄膜晶体管电路可表现出过量的晶体管漏电流、不足的晶体管驱动强度、差的面积效率、磁滞、不均匀度和其他问题。因此，期望能够提供改进的电子设备显示器。

### 发明内容

[0007] 电子设备可包括显示器。该显示器可具有形成有效区域的像素。无效边界区域可沿有效区域的边缘部分延伸。该像素可由在基板上的像素电路阵列形成。该基板可由刚性材料形成并且可由在无效区域中弯曲的柔性材料形成。

[0008] 每个像素电路可包括有机发光二极管和耦接至该有机发光二极管的驱动晶体管。每个驱动晶体管可被调节以控制通过其耦接至的有机发光二极管的电流量和因此由该二极管产生的光的量。每个像素电路可包括一个或多个另外的晶体管诸如开关晶体管并且可包括存储电容器。

[0009] 半导体氧化物晶体管和硅晶体管可用于形成像素电路的晶体管。例如，半导体氧化物晶体管可用作开关晶体管并且硅晶体管可以用作驱动晶体管。每个像素电路可具有单一驱动晶体管和一个或多个另外的晶体管。

[0010] 存储电容器和晶体管可使用金属层、半导体结构和电介质层来形成。电介质层可具有当数据线延伸到显示器的无效弯曲边缘区域中时允许像素电路阵列中的数据线向基板的表面逐渐降低的阶梯式外形。电介质层中的一些或全部可在无效边缘区域中移除以有利于弯曲。

### 附图说明

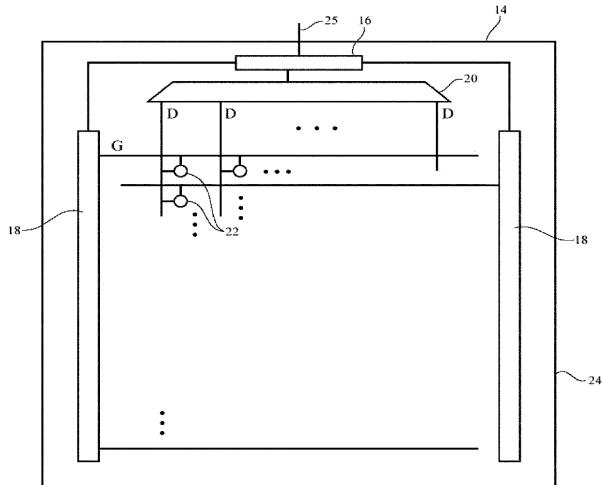

[0011] 图1是根据一个实施例的示例性显示器诸如具有有机发光二极管像素阵列的有机发光二极管显示器的图示。

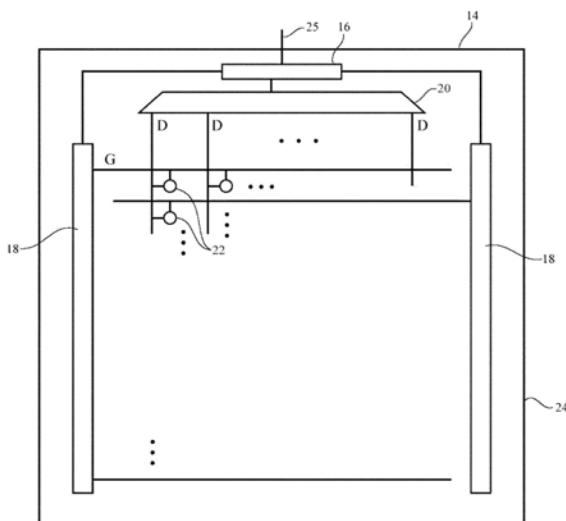

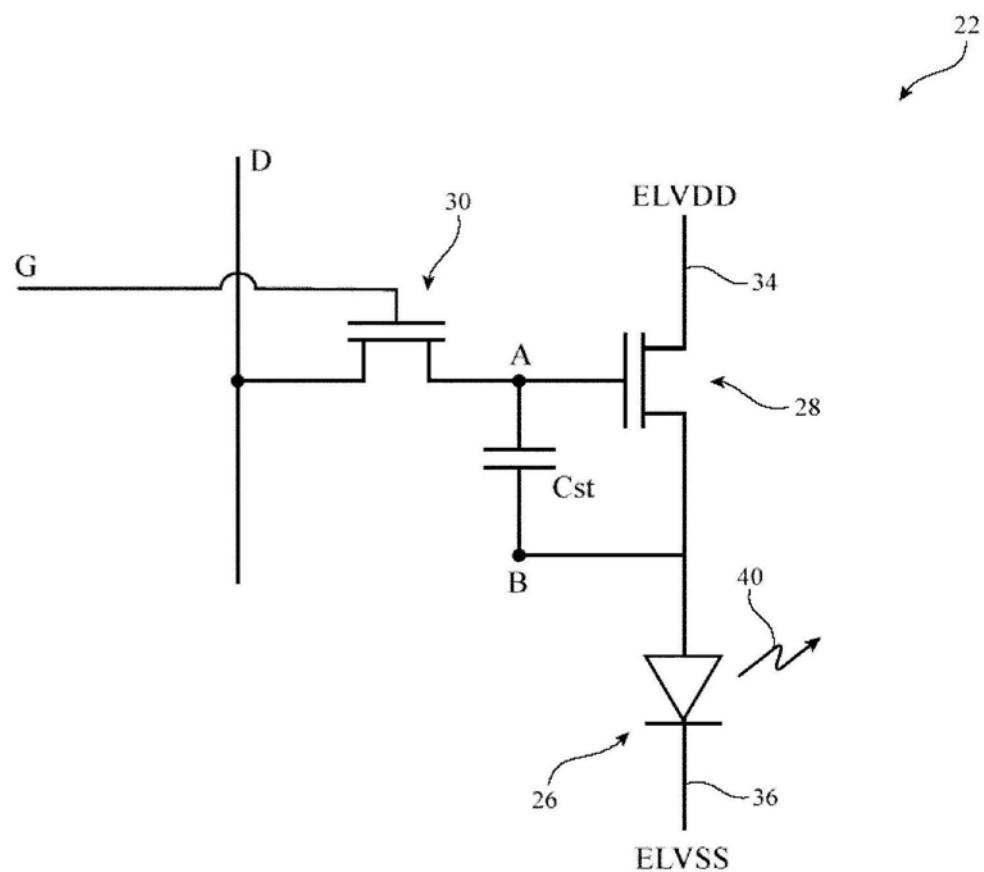

[0012] 图2是根据一个实施例的该类型的示例性有机发光二极管显示器像素的图示，该

示例性有机发光二极管显示器像素可与半导体氧化物薄膜晶体管和硅薄膜晶体管一起用于有机发光二极管。

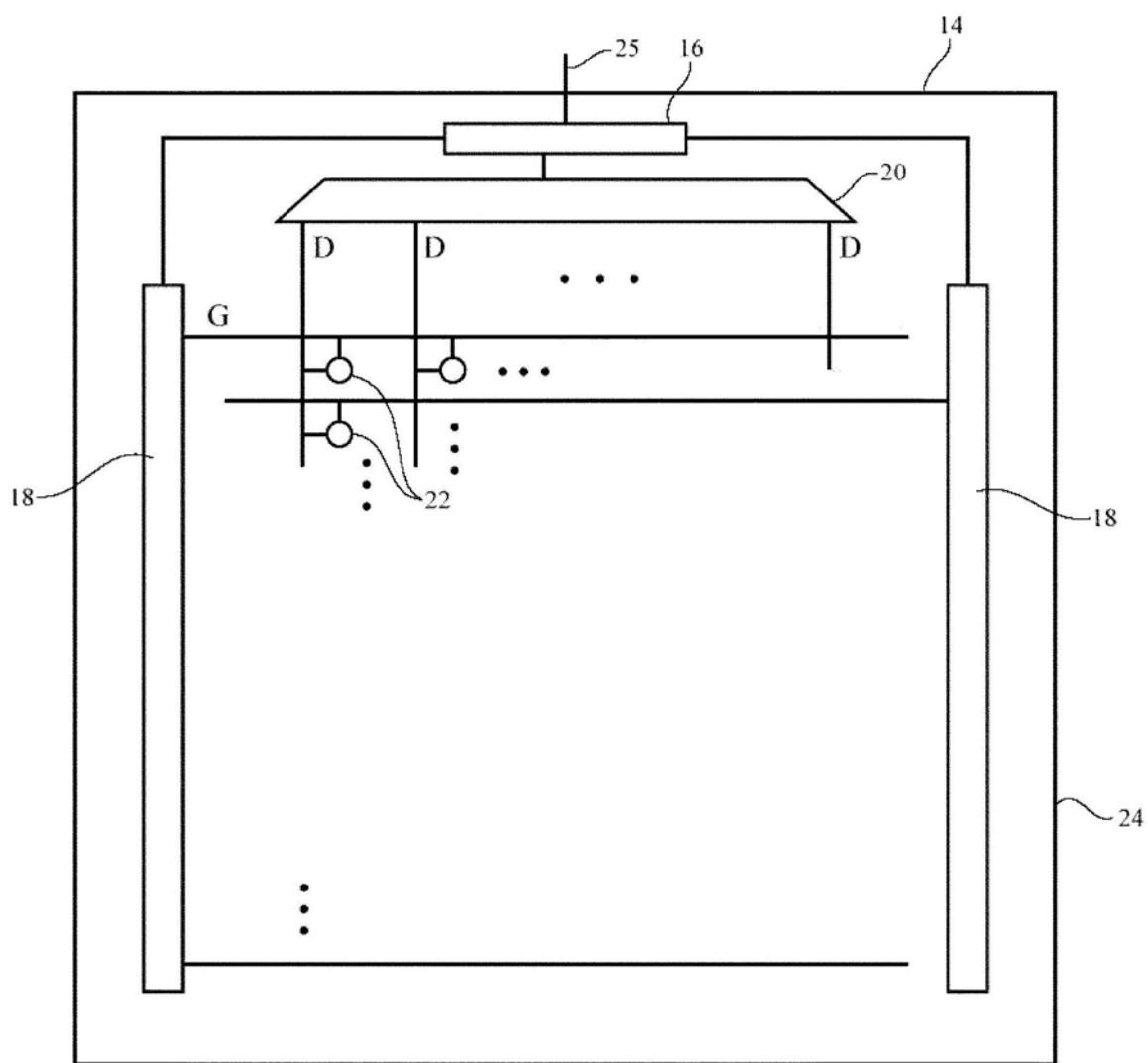

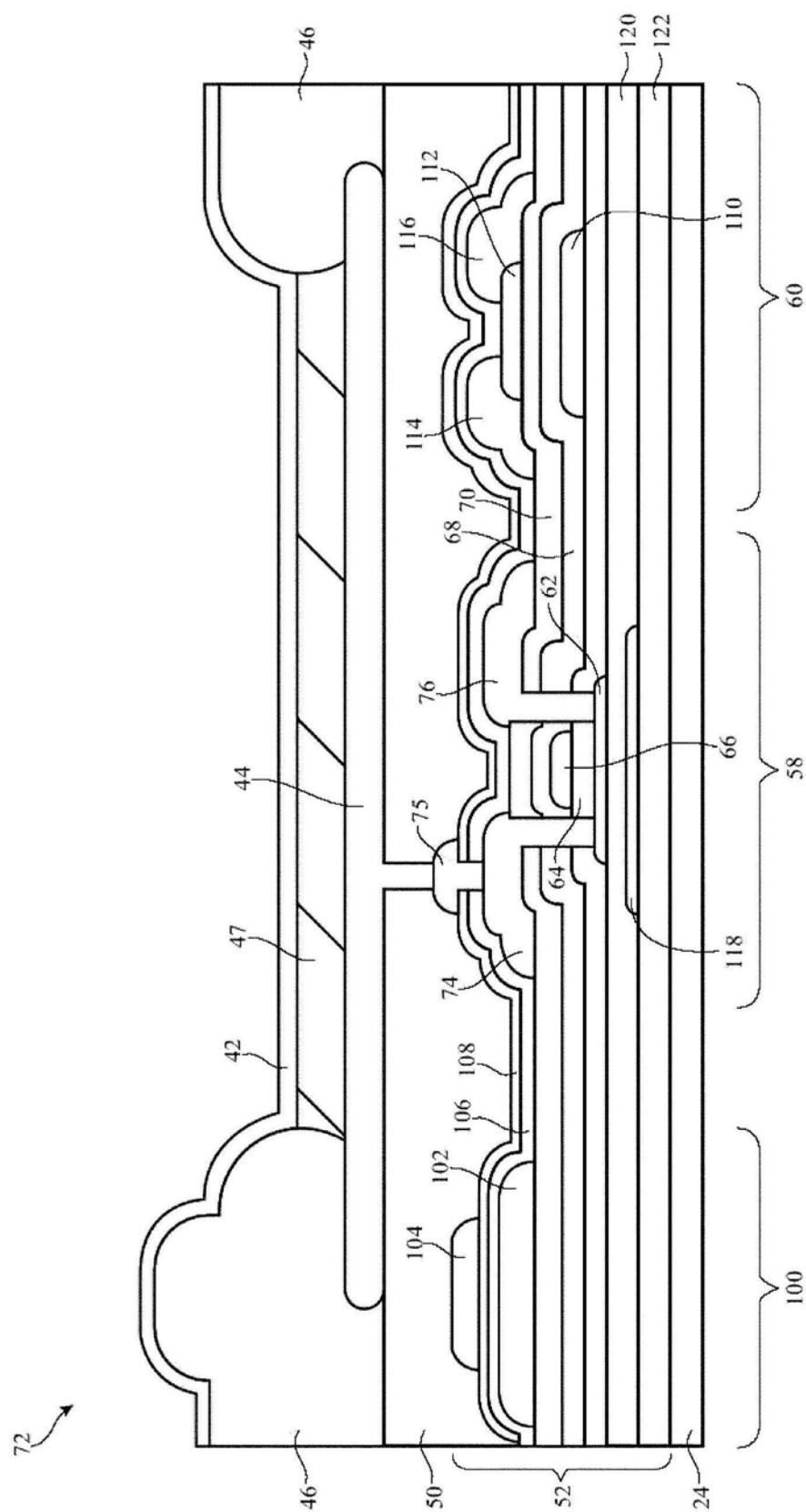

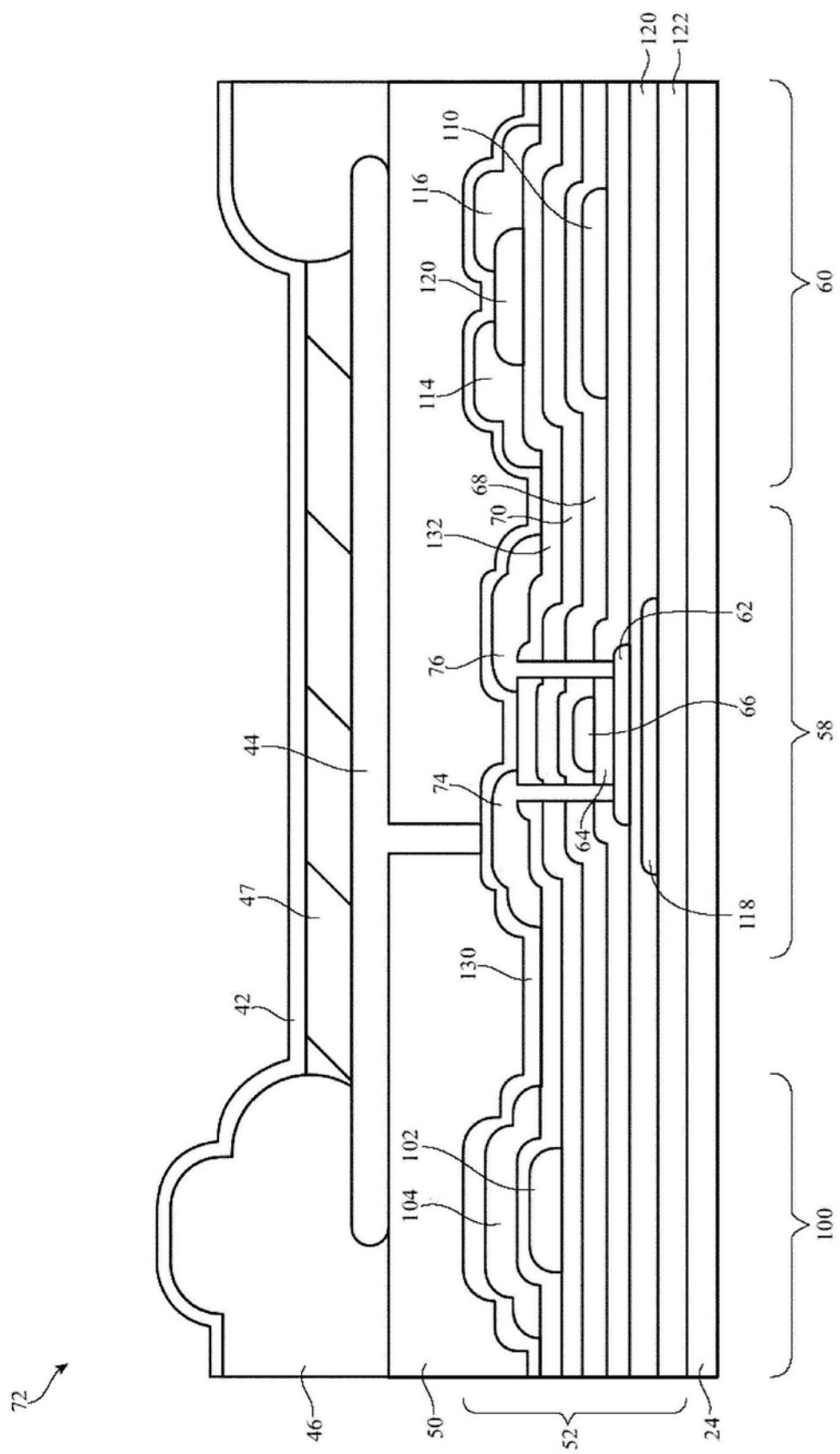

[0013] 图3是根据一个实施例的用于显示器像素的示例性薄膜晶体管结构的横截面侧视图,该显示器像素在其中已经使用底栅极布置来形成半导体氧化物薄膜晶体管的构型中。

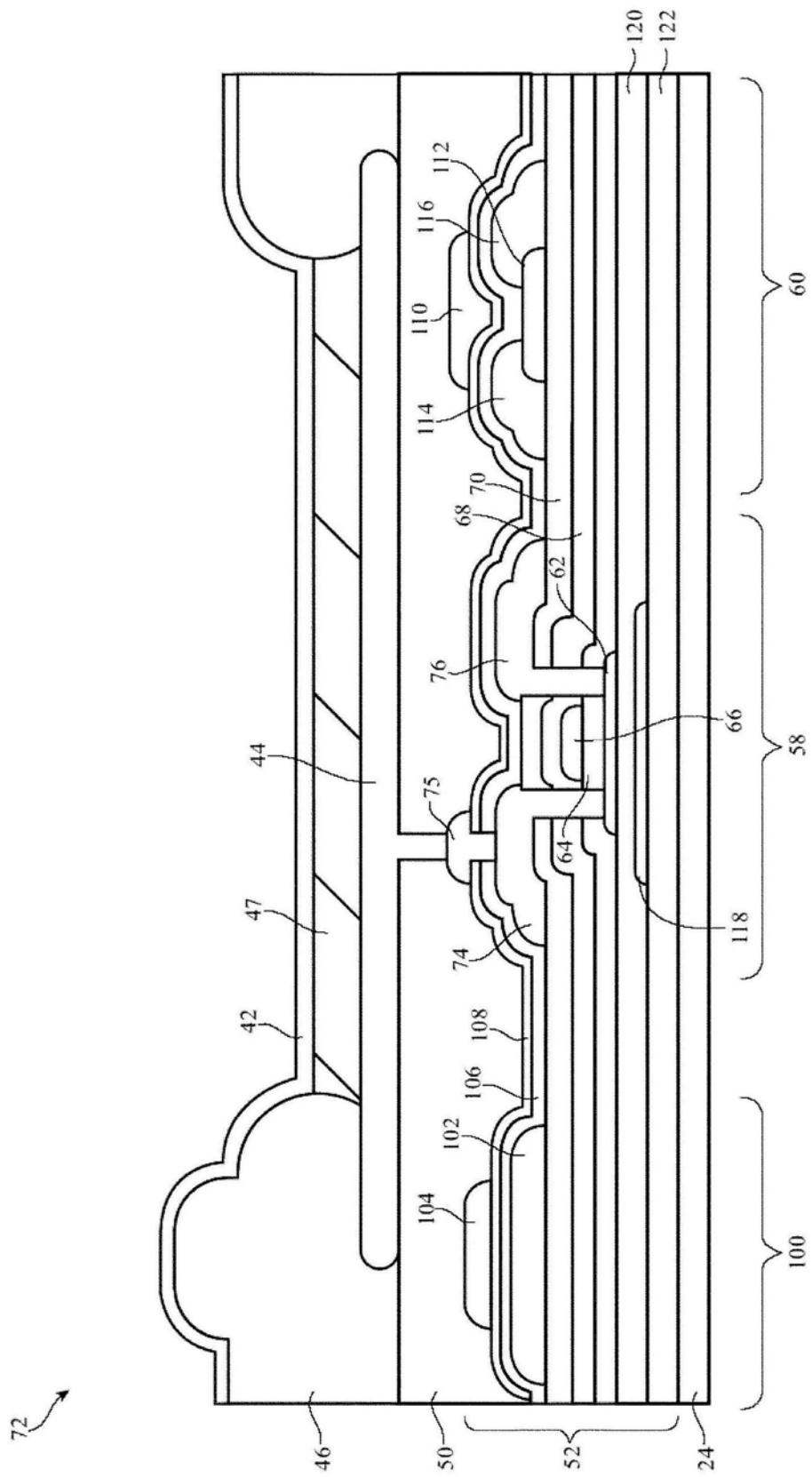

[0014] 图4是根据一个实施例的用于显示器像素的示例性薄膜晶体管结构的横截面侧视图,该显示器像素在其中已经使用顶栅极布置来形成半导体氧化物薄膜晶体管的构型中。

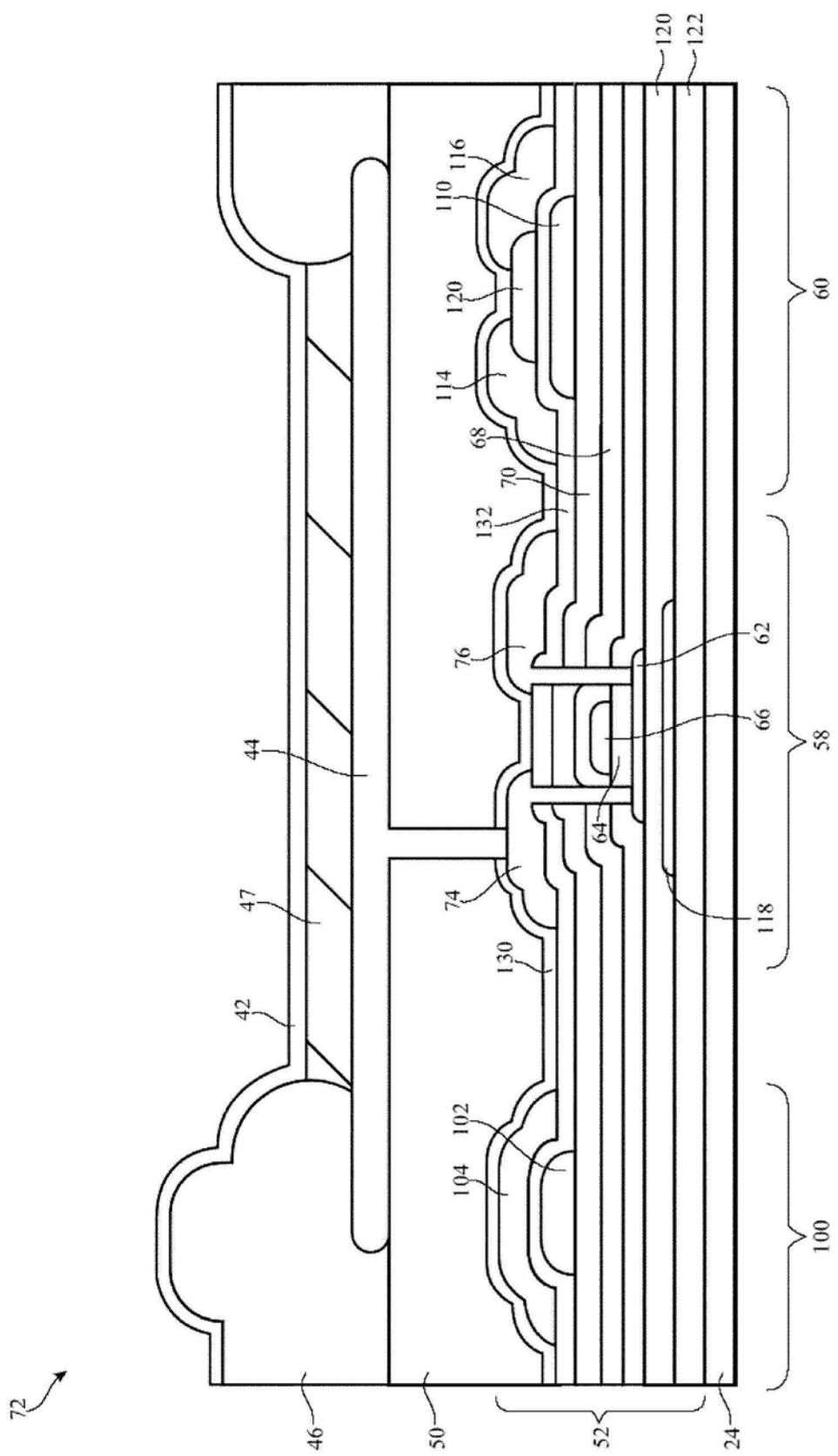

[0015] 图5是根据一个实施例的用于显示器像素的示例性薄膜晶体管结构的横截面侧视图,该显示器像素在其中已经使用底栅极布置来形成半导体氧化物薄膜晶体管并且在其中存储电容器具有第一电极和第二电极的构型中,该第一电极由与半导体氧化物薄膜晶体管的栅极相同的金属层图案化并且该第二电极还形成晶体管源极-漏极。

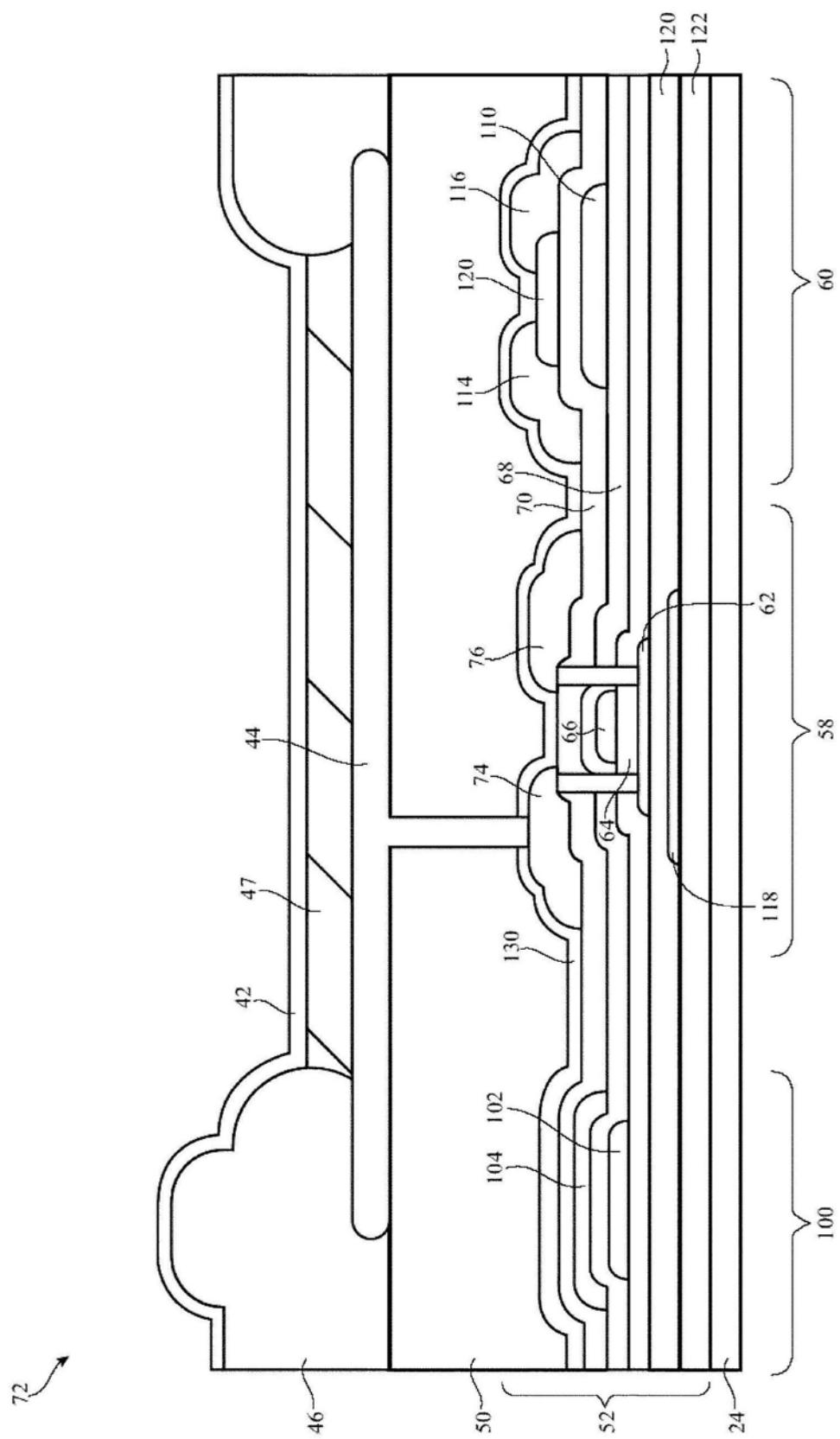

[0016] 图6是根据一个实施例的用于显示器像素的示例性薄膜晶体管结构的横截面侧视图,该显示器像素在其中已经使用底栅极布置来形成半导体氧化物薄膜晶体管并且在其中已经使用下部电极来形成存储电容器的构型中,该下部电极由还用作硅晶体管中的薄膜晶体管栅极金属的金属层图案化。

[0017] 图7是根据一个实施例的用于显示器像素的示例性薄膜晶体管结构的横截面侧视图,该显示器像素在其中已经使用底栅极布置来形成半导体氧化物薄膜晶体管的构型中,该底栅极布置具有插入该半导体氧化物薄膜晶体管的栅极和沟道之间的三层层间电介质。

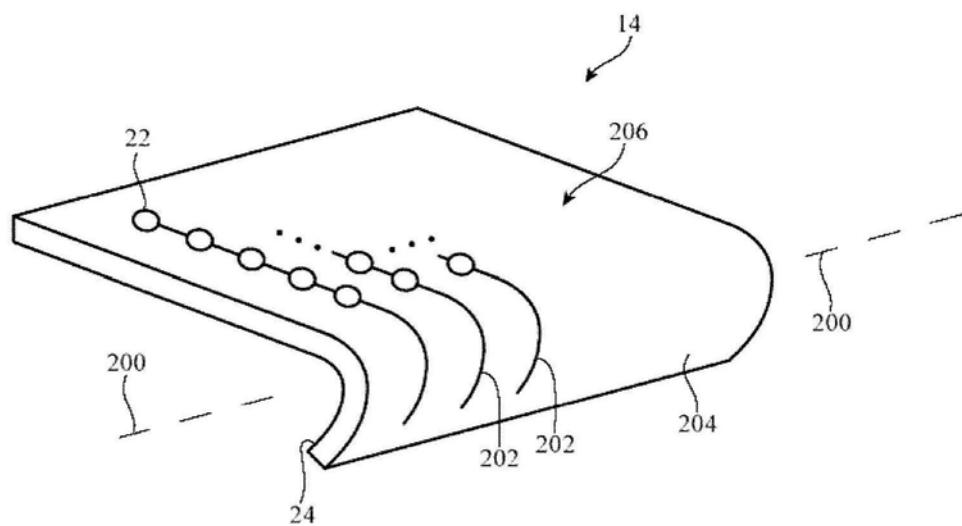

[0018] 图8是根据一个实施例的具有弯曲边缘的示例性显示器的透视图。

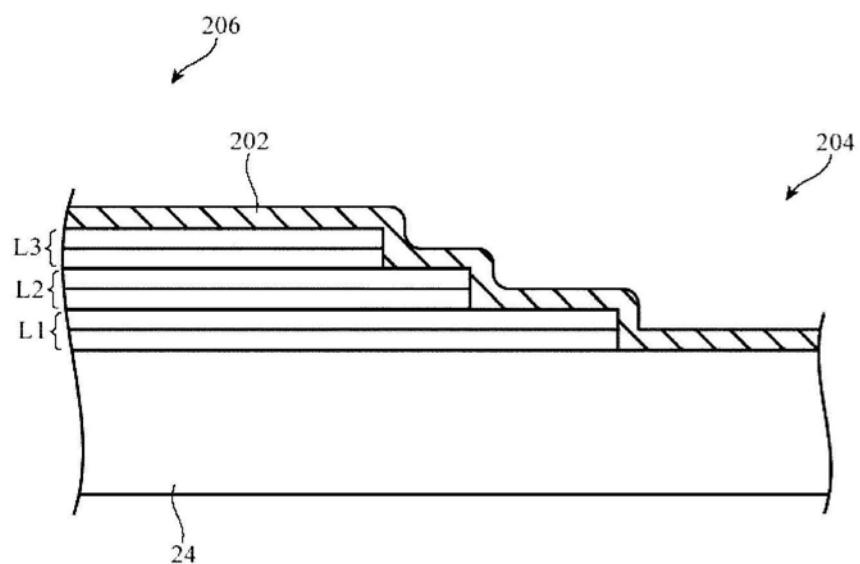

[0019] 图9是根据一个实施例的用于具有弯曲边缘的显示器的示例性阶梯式电介质层的横截面侧视图。

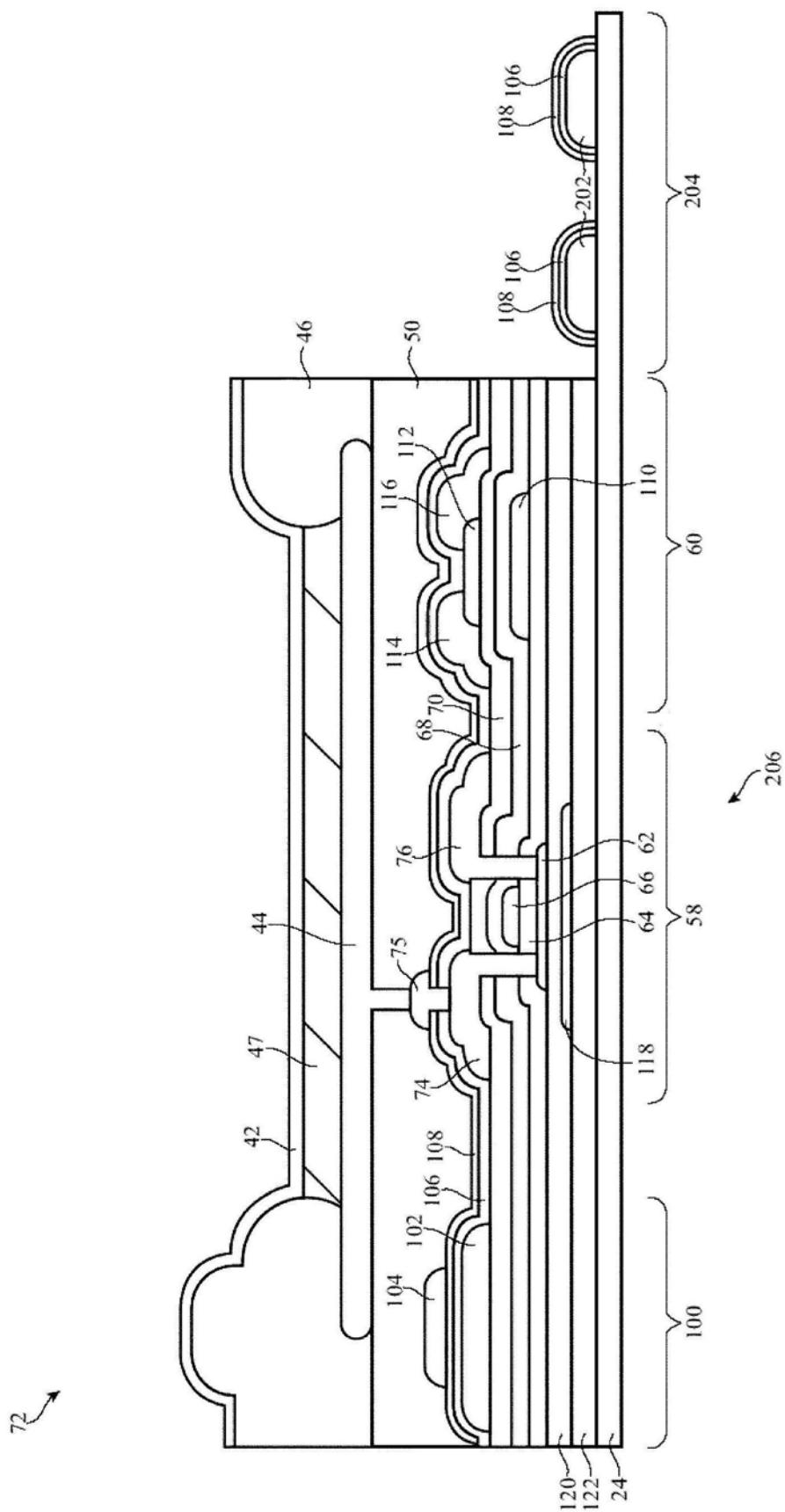

[0020] 图10是根据一个实施例的用于显示器的示例性薄膜晶体管结构的横截面侧视图,该显示器在其中材料的上层已经从显示器移除以有利于显示器在沿显示器的边缘的无效区域中弯曲的构型中。

[0021] 图11是根据一个实施例的用于显示器的示例性薄膜晶体管结构的横截面侧视图,该显示器在其中材料的上层已经从显示器移除以有利于显示器在沿显示器的边缘的弯曲区域中弯曲并且在其中半导体氧化物晶体管结构不与任何富氢氮化硅重叠的构型中。

## 具体实施方式

[0022] 电子设备中的显示器可提供有用于在像素阵列上显示图像的驱动电路。图1中示出了示例性显示器。如图1所示,显示器14可具有一个或多个层诸如基板24。层诸如基板24可由绝缘材料诸如玻璃、塑料、陶瓷和/或其他电介质形成。基板24可以是矩形的或者可具有其他形状。刚性基板材料(例如,玻璃)或柔性基板材料(例如,柔性聚合物片材诸如一层聚酰亚胺或其他材料)可用于形成基板24。

[0023] 显示器14可具有用于为用户显示图像的像素22的阵列(有时称为像素电路)。像素22的阵列可由基板24上的像素结构的行和列形成。在像素22的阵列中可具有任何合适数量的行和列(例如,十个或更多个、一百个或更多个,或者一千个或更多个)。

[0024] 可使用焊料或导电粘合剂将显示驱动电路诸如显示驱动器集成电路16耦接至导电路径诸如基板24上的金属迹线。显示驱动器集成电路16(有时称为定时控制器芯片)可包括用于通过路径25与系统控制电路进行通信的通信电路。路径25可由柔性印刷电路上的迹

线或其他缆线形成。控制电路可位于电子设备中的主逻辑板上,所述电子设备诸如为蜂窝电话、计算机、机顶盒、媒体播放器、便携式电子设备、腕表设备、平板电脑,或正在使用显示器14的其他电子设备。在操作过程中,控制电路可为显示驱动器集成电路16提供与要在显示器14上显示的图像有关的信息。为在显示器像素22上显示图像,当发出时钟信号和其他控制信号以支持薄膜晶体管显示驱动电路诸如栅极驱动电路18和解复用电路20时,显示驱动器集成电路16可将对应的图像数据供应到数据线D。

[0025] 栅极驱动电路18可在基板24上形成(例如,在显示器14的左边缘和右边缘上、仅在显示器14的单个边缘上,或者在显示器14中的其他位置)。解复用器电路20可用于将数据信号从显示驱动器集成电路16解复用到多个对应的数据线D上。根据图1的示例性布置,数据线D通过显示器14竖直延伸。每条数据线D都与显示器像素22的相应列相关联。栅极线G通过显示器14水平延伸。每条栅极线G都与显示器像素22的相应行相关联。栅极驱动电路18可位于显示器14的左侧上、显示器14的右侧上,或位于显示器14的左侧和右侧上,如图1所示。

[0026] 栅极驱动电路18可断言在显示器14中的栅极线G上的栅极信号(有时称为扫描信号)。例如,栅极驱动电路18可以从显示驱动器集成电路16接收时钟信号和其他控制信号,并且可以响应于所接收到的信号,从显示器像素22的第一行中的栅极线信号G开始依次断言栅极线G上的栅极信号。由于每条栅极线被断言,因此在其中栅极线被断言的行中对应的显示器像素将显示在数据线D上显现的显示数据。

[0027] 显示驱动电路16可使用一个或多个集成电路来实现。显示驱动电路诸如解复用器电路20和栅极驱动电路18可使用一个或多个集成电路和/或在基板24上的薄膜晶体管电路来实施。薄膜晶体管可用于形成显示器像素22中的电路。为增强显示器性能,在显示器14中满足所期望标准诸如漏电流、切换速度、驱动强度、均匀度等的薄膜晶体管结构可以使用。一般来讲,在显示器14中的薄膜晶体管可以使用任何合适类型的薄膜晶体管技术(例如,基于硅的、基于半导体氧化物的,等等)形成。

[0028] 根据一种在本文中有时描述为实例的合适布置,显示器14上的一些薄膜晶体管中的沟道区(有效区域)由硅(例如,硅诸如使用低温方法沉积的多晶硅,有时称为LTPS或低温多晶硅)形成,并且在显示器14上的其他薄膜晶体管中的沟道区由半导体氧化物材料(例如,非晶态的氧化铟镓锌,有时称为IGZO)形成。如果需要,则其他类型的半导体可用于形成薄膜晶体管诸如非晶硅、除了IGZO之外的半导体氧化物等。在这种类型的混合显示器构型中,硅晶体管(例如,LTPS晶体管)可在期望的属性诸如切换速度和良好可靠性的情况下使用(例如,用于驱动晶体管以驱动通过像素中的有机发光二极管的电流),然而氧化物晶体管(例如,IGZO晶体管)可在期望低漏电流的情况下使用(例如,当显示器中的显示器像素开关晶体管实施可变刷新率方案或需要低漏电流的其他场景时)。其他注意事项也可被考虑(例如,与功率消耗、占位面积消耗、磁滞、晶体管均匀度等相关的注意事项)。

[0029] 氧化物晶体管诸如IGZO薄膜晶体管通常是n-沟道设备(即,NMOS晶体管),但是如果需要,PMOS设备可以用于氧化物晶体管。硅晶体管也可以使用p-沟道或n-沟道设计制成(即,LTPS设备可以是PMOS或NMOS)。这些薄膜晶体管结构的组合可以为有机发光二极管显示器提供最佳性能。

[0030] 在有机发光二极管显示器中,每个显示器像素都包括相应的有机发光二极管。图2中示出了示例性有机发光二极管显示器像素的示意图。如图2所示,像素22可包括发光二极

管26。可以将正电源电压ELVDD提供给正电源端子34，并且可以将接地电源电压ELVSS提供给接地电源端子36。驱动晶体管28的状态控制流经二极管26的电流量，因此控制来自显示器像素22的发射光40的量。

[0031] 为确保晶体管28保持在数据的连续帧之间的期望状态，显示器像素22可包括存储电容器，诸如存储电容器Cst。在存储电容器Cst上的电压在节点A被施加到晶体管28的栅极以控制晶体管28。可使用一个或多个开关晶体管诸如开关晶体管30将数据加载到存储电容器Cst中。当开关晶体管30关闭时，数据线D从存储电容器Cst隔离，并且在端子A上的栅极电压等于存储在存储电容器Cst中的数据值(即，来自在显示器14上显示的显示数据的先前帧的数据值)。当在与像素22相关联的行中的栅极线G(有时称为扫描线)被断言时，开关晶体管30将被打开并且在数据线D上的新的数据信号将被加载到存储电容器Cst中。在电容器Cst上的新信号在节点A处被施加到晶体管28的栅极，从而调节晶体管28的状态并且调节由发光二极管26发射的光40的对应的量。

[0032] 图2的示例性像素电路仅为电路的一个实例，其可用于显示器14中的像素阵列。例如，每个像素电路可包括任何合适数量的开关晶体管(一个或多个、两个或更多个、三个或更多个等)。如果需要，则有机发光二极管显示器像素22可具有另外的部件(例如，与驱动晶体管串联耦接以帮助实施功能诸如阈值电压补偿等的一个或两个发射启用晶体管)。一般来讲，本文所述的薄膜晶体管结构可与图2的像素电路或者与任何其他合适的像素电路一起使用。例如，本文所述的薄膜晶体管结构可用于六-晶体管像素电路，其具有由两个不同的扫描线控制的三个开关晶体管、与有机发光二极管串联耦接的驱动晶体管，以及由两个相应的发射线控制并且与驱动晶体管和发光二极管串联耦接以实施阈值电压补偿功能的两个发射启用晶体管。用于显示器14中的像素的薄膜晶体管电路还可具有其他数量的开关晶体管(例如，一个或多个、两个或更多个、三个或更多个、四个或更多个等)或其他数量的发射晶体管(无发射晶体管、一个或多个发射晶体管、两个或更多个发射晶体管、三个或更多个发射晶体管、四个或更多个发射晶体管等)。在每个像素电路中的晶体管可由硅晶体管和氧化硅晶体管的任何合适的组合与NMOS晶体管和PMOS晶体管的任何合适的组合形成。图2的像素电路仅为示例性的。

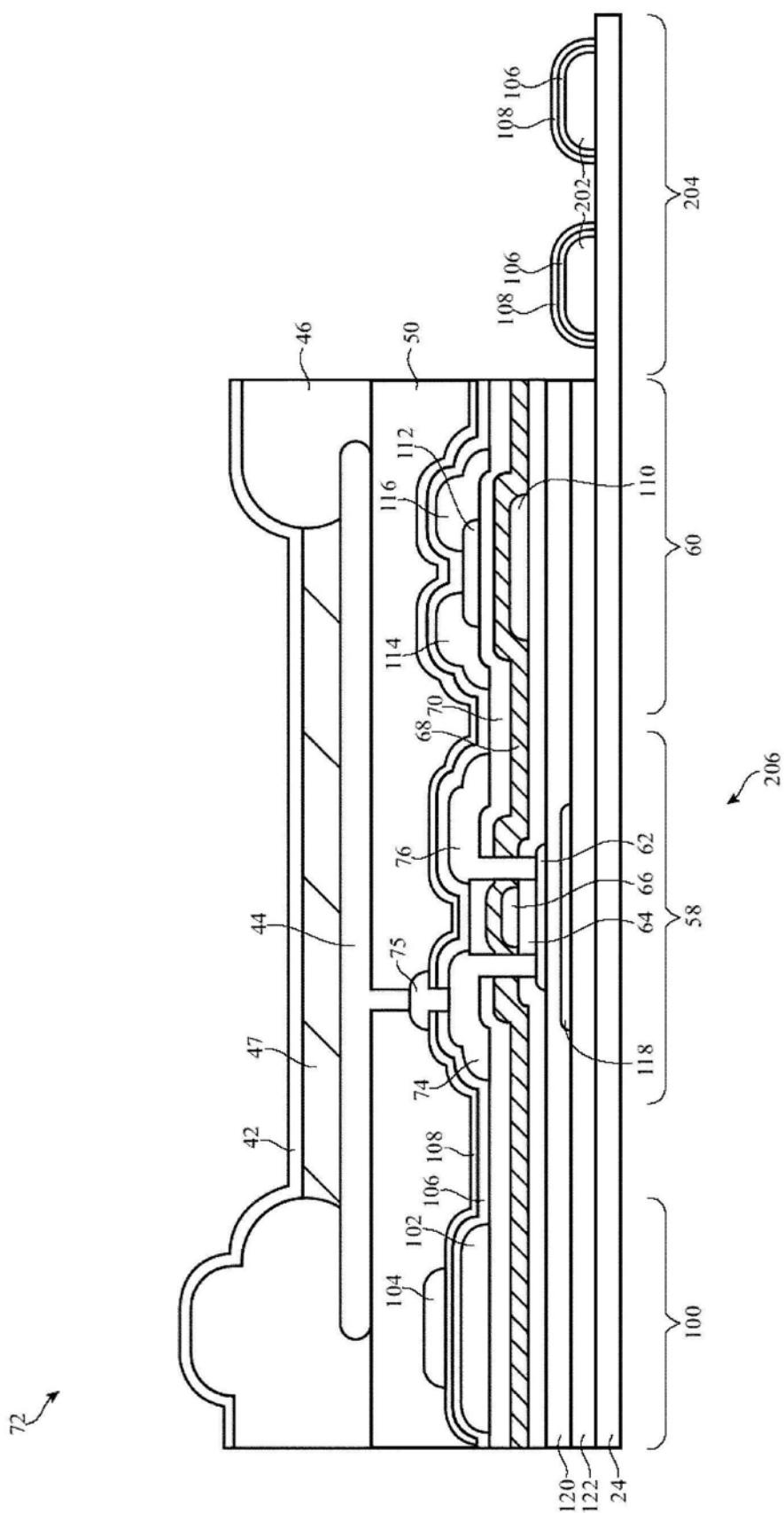

[0033] 图2的有机发光二极管像素诸如像素22或用于显示器14的任何其他合适的像素电路可使用在图3示出的类型的薄膜晶体管结构。在这种类型的结构中，两种不同类型的半导体被使用。如图3所示，像素电路72可包括像素结构诸如发光二极管阴极端子42和发光二极管阳极端子44。有机发光二极管发射材料47可插入阴极42和阳极44之间，从而形成图2的发光二极管26。电介质层46可用于限定像素的布局(例如，发射材料47相对于阳极44对齐)并且有时可以称为像素清晰度层。平面化层50(例如，聚合物层)可在薄膜晶体管结构52的顶部上形成。薄膜晶体管结构52可在基板24上形成。基板24可以是刚性的或柔性的，并且可由玻璃、陶瓷、结晶材料诸如蓝宝石、聚合物(例如，聚酰亚胺的柔性层或其他聚合物材料的柔性片材)等形成。

[0034] 薄膜晶体管结构52可包括硅晶体管诸如硅晶体管58。晶体管58可以是使用“顶栅极”设计形成的LTPS晶体管，并且可用于形成像素22中的任何晶体管(例如，晶体管58可用作驱动晶体管诸如图2的像素22中的驱动晶体管28)。晶体管58可具有由栅极绝缘体层64(例如，氧化硅层或其他无机层)覆盖的多晶硅沟道62。栅极66可由图案化的金属(例如，钼)

形成。栅极66可由一层层间电介质(例如,氮化硅层68和氧化硅层70或其他无机层或有机材料)覆盖。源极-漏极触点74和76可接触多晶硅层62的相对侧以形成硅薄膜晶体管58。

[0035] 栅极66可由金属层GATE形成,源极-漏极端子74和76可由金属层SD形成,并且另外的金属层M3可以用于形成金属通路75以将源极-漏极74耦接至阳极44。

[0036] 电路72还可包括电容器结构诸如电容器结构100(例如,图2的电容器Cst)。电容器结构100可具有下部电极诸如电极102和上部电极诸如电极104。下部电极102可由金属层SD的图案化部分形成。上部电极104可由金属层M3的图案化部分形成。电介质层可使上部电极104和下部电极102分离。电介质层可由高-介电-常数材料诸如二氧化铪或氧化铝形成,并且可由一个或多个其他层形成。在图3的实例中,分离电极102和104的电介质层包括两个钝化层106和108。层106和层108可分别由氧化硅和氮化硅形成。如果需要,其他无机层和/或有机层可以用于形成层106和层108(例如,氧化物层、氮化物层、聚合物层等)。

[0037] 薄膜晶体管结构52可包括半导体氧化物晶体管诸如半导体氧化物晶体管60。在结构60中的薄膜晶体管可以是“底栅极”氧化物晶体管。晶体管60的栅极110可由金属层GATE的一部分形成。晶体管60的半导体氧化物沟道区(沟道112)可由半导体氧化物诸如IGZO形成。层间电介质(例如,层68和70)可插入栅极110和半导体氧化物沟道112之间并且可以用作用于晶体管60的栅极绝缘体层。氧化物晶体管60可具有由金属层SD的图案化部分形成的源极-漏极端子114和116。

[0038] 基板24上的缓冲层122可由一层聚酰亚胺或其他电介质形成。背侧金属层118可在晶体管58下方形成以将晶体管58与缓冲层122中的电荷相屏蔽。缓冲层120可在屏蔽层118之上形成并且可由电介质(例如,有机层诸如聚合物层其他绝缘层)形成。

[0039] 图4中示出了用于像素电路22的另外的示例性薄膜晶体管电路72。在图4的实例中,已经使用“顶栅极”布置来形成氧化物晶体管60。利用该方法,用于晶体管60的栅极110由金属层M3的图案化部分来形成。金属层M3还可以用于形成电容器100的电极104(例如)。金属层SD可用于形成电极102、源极-漏极端子74和76,以及源极-漏极端子114和116。氧化物晶体管60可具有半导体氧化物沟道112。电介质(例如,钝化层106和108和/或高-介电-常数材料或其他绝缘材料)可插入沟道112和栅极110之间。

[0040] 在图5的实例中,电路72的晶体管60是底栅极氧化物晶体管。电介质层132可插入电容器100的上部电极104和下部电极102之间。电介质层132可由无机绝缘体(例如,氧化硅、氮化硅等)形成或者可由聚合物层形成。层132有时可被称为层间电介质层并且可以在层间电介质层68和70的顶部上形成。在电容器100中,层132使电极102和104彼此分离。上部电极104可由金属层SD形成。金属层SD还可用于为硅晶体管58形成源极-漏极74和76,以及为氧化物晶体管60形成源极-漏极114和116。下部电极102可在金属层SD和用于栅极66的栅极金属GATE之间形成沉积的和图案化的金属层。用于形成图5的下部电极102的金属层有时可以称为金属层M2S。除了用于形成电容器100的下部电极102之外,金属层M2S可以用于形成晶体管60的栅极110。

[0041] 在图5的构型中,金属层M2S已经在电介质层68和70上形成。电介质层132插入栅极110和半导体氧化物沟道120之间并且用作用于晶体管60的栅极绝缘体。钝化层诸如电介质层130可在沟道120上方形成以保护沟道120的半导体氧化物界面。电介质层130和电介质层132可各自由氧化硅、氮化硅、氧化铝、氧化铪、单一层、多个次层,或其他绝缘材料形成。

[0042] 图6示出了用于晶体管电路74的另一个示例性构型。在图6的布置中,电路74具有三个金属层。金属层GATE用于为电容器100形成下部电极102并且用于为硅晶体管58形成栅极66。金属层SD用于形成源极-漏极端子74、76、114和116。有时称为金属层G2的另外的金属层插入金属层SD和金属层GATE之间。金属层G2可用于形成电容器100中的上部电极104并且可用于形成氧化物晶体管60中的栅极110。图6的氧化物晶体管60是底栅极晶体管。电介质层70用作用于晶体管60的栅极绝缘体并且插入栅极110和半导体氧化物沟道120之间。钝化层130可以保护沟道区120。在电容器100中,电介质层68插入上部电极104和下部电极102之间。

[0043] 在图7所示的用于电路72的示例性构型中,电容器100的上部电极104由金属层SD形成。金属层SD还可以用于形成硅晶体管58中的源极-漏极74和76以及氧化物晶体管60中的源极-漏极114和116。氧化物晶体管60可具有底栅极构型。氧化物晶体管60的栅极110和硅晶体管58的栅极66可由相同金属层(即,金属层GATE)的相应部分形成。另外的金属层(金属层M2S)可在金属层GATE和金属层SD之间形成。金属层M2S可用于形成电容器100中的下部电极102。电介质层132可插入下部电极102和上部电极104之间。钝化层130可用于保护氧化物晶体管60中的半导体氧化物层120的界面。

[0044] 可期望将显示器14的无效边界区域最小化。像素22为用户显示图像,因此由像素22的阵列占据的显示器14的部分形成显示器14的有效区域。围绕有效区域的显示器14的部分不为用户显示图像并且因此是无效的。用户可见的无效区域的量可通过在有效区域的平面外向下弯曲(例如,以直角或其他合适的角度)基板24的部分而最小化或者消除。为确保显示器14在弯曲期间不被损坏,基板24上的结构可被构造成增强无效区域的弯曲部分中的显示器14的柔韧性。例如,绝缘层诸如无机电介质层和显示器14的其他层(例如,金属层中的一些层)可部分或完全地在无效区域中移除以在弯曲期间阻止应力引起的断裂或者其他损坏(特别是对金属信号线)。

[0045] 例如,考虑图8的显示器14。如图8所示,无效边缘区域204已围绕弯曲轴线200从有效区域206向下弯曲。线202(例如,在显示器14中的数据线或其他金属信号线)横贯轴线200处的弯曲部。为阻止形成断裂或对显示器14的结构的其他损坏,除了线202之外,显示器14的一些或全部结构可在无效区域204中选择性地移除(然而保持在有效区域206中以形成薄膜晶体管电路72诸如图3、4、5、6和7的电路72)。利用该方法,形成线202的金属层可位于在有效区域206中的基板24之上比在无效区域204中更大的距离处。

[0046] 为适应在有效区域206和无效区域204的层之间的高度的不一致,在显示器14的电介质层中可以形成一系列阶梯。该阶梯可以缓慢降低在电介质层上支撑的金属迹线的高度,使得该金属迹线可逐渐改变高度并且不会由于在电介质中的急剧的高度间断而中断。

[0047] 在图9中示出了使得金属线202可以在有效区域206和无效区域204之间顺利过渡的具有阶梯式外形的一组示例性电介质层。如图9所示,显示器14可具有电介质层诸如层L1、L2和L3(参见,例如在图3、4、5和6中的电路72的电介质层)。层L1、L2和L3可由聚合物的一个或多个次层和/或无机层形成(例如,氧化硅、氮化硅、氧化铪、氧化铝等)。在图9的实例中存在三个电介质层L1、L2和L3,但是仅为示例性的。在有效区域206中的图9的左侧上,所有电介质层L1、L2和L3都存在,所以金属线202位于其距基板24的最大距离处。楼梯(阶梯式)电介质外形通过在距有效区域206的相继更大的侧向距离处选择性地移除层L3、L2和L1

而产生。在电介质层中形成的高度阶梯允许金属线202从其最大高度(在有效区域206中)向其在无效区域204中的最小高度过渡。例如,线202可以安置在无效区域204中的基板24的表面上或附近。

[0048] 图10是用于显示器14的示例性薄膜晶体管电路72的横截面侧视图,该显示器在其中材料的上层已从显示器移除以有利于显示器在沿显示器的无效边缘的弯曲区域中弯曲的构型中。在图10的实例中,除了钝化层106和108之外的所有电介质层已从区域204中的基板24移除,所以金属线202(例如,数据线和/或在显示器14中的其他信号线)安置在基板24的表面上。这有利于在区域204中的基板24弯曲。一般来讲,任何合适的薄膜晶体管电路72可与图10的无效区域材料移除方案一起使用(例如,电路诸如图3、4、5、6、7和8等的电路72)。图10的电路仅为示例性的。

[0049] 在图10的示例性构型中,上部电容器电极104已由金属层M3形成。金属层M3还可用于形成通路74以将源极-漏极端子74耦接至阳极44。下部电容器电极102可由金属层SD形成。金属层SD还可以用于形成源极-漏极端子74、76、114和116。钝化层106和108(例如,分别为氮化硅层和氧化硅层)或其他合适的一个或多个电介质层可在半导体氧化物沟道112的顶部上形成。在电容器100中,层106和108之一可被局部移除以减少电介质厚度,从而提高电容器100的电容值。如图10所示,例如,层106可在电极104之下被移除,使得层106不与电容器100重叠,并且使得仅电介质层108插入电容器100的上部电极104和下部电极102之间。电介质层108可由具有大于氧化硅的介电常数的氮化硅形成,所以电介质层108用作电极102和104之间的专用绝缘层可帮助提高电容器100的电容。另外的光刻法掩膜可用于选择性地移除氧化硅层106。该掩膜还可用于为金属线202形成电介质阶梯(参见,例如图9的电介质阶梯)。金属线202可由金属层SD形成。在显示器14的有效区域206中,金属线202可由通过电介质层诸如层122、120、64、68和70支撑的金属层SD的部分来形成(即,可形成图9的示例性层L1、L2和L3的类型的层)。虽然在图9的实例中存在三个高度阶梯,但是可形成一个阶梯、两个阶梯、三个阶梯、或多于三个阶梯。

[0050] 图11的示例性构型类似于图10,但具有带有局部移除的氮化硅钝化层的氧化物晶体管。图10的钝化层106可以是氮化硅层。氮化硅层106可具有高浓度的氢以钝化硅晶体管58的多晶硅层62中的悬空键。为了有效的钝化,氮化硅层106可与晶体管58和硅沟道62重叠。可期望阻止来自氮化硅层106的氢到达半导体氧化物沟道112。这可通过将氮化物层106从晶体管60移除来完成。例如,光刻法掩模可用于图案化氮化硅层106,使得氮化硅层106不存在于半导体氧化物112之下(即,使得不存在与晶体管60重叠的氮化硅层106的部分)。通过确保无氮化硅存在于栅极110和氧化物112之间,晶体管60的性能将不会由于来自层106的氢而劣化。

[0051] 根据一个实施例,提供了一种有机发光二极管显示器,其包括基板、形成基板的有效区域的像素电路阵列,以及基板的无效区域中的电路,每个像素电路包括有机发光二极管、与有机发光二极管串联耦接的硅晶体管、耦接至硅晶体管的存储电容器,以及耦接至存储电容器的半导体氧化物晶体管。

[0052] 根据另一个实施例,基板在无效区域中弯曲。

[0053] 根据另一个实施例,有机发光二极管显示器包括电介质层,该电介质层存在于有效区域中并且电介质层中的至少一些不存在于无效区域中。

[0054] 根据另一个实施例,在每个像素电路中的硅晶体管包括硅沟道,电介质层包括基板和硅沟道之间的缓冲层,并且缓冲层不存在于无效区域中。

[0055] 根据另一个实施例,有机发光二极管显示器包括有效区域中的第一金属层,该第一金属层中的一些形成用于每个像素电路中的硅晶体管的栅极。

[0056] 根据另一个实施例,第一金属层中的一些形成用于每个像素电路中的半导体氧化物晶体管的栅极。

[0057] 根据另一个实施例,有机发光二极管显示器包括第二金属层,该第二金属层在有效区域中是图案化的以形成用于硅晶体管并且用于半导体氧化物晶体管的源极-漏极端子。

[0058] 根据另一个实施例,第二金属层在无效区域中是图案化的以形成在像素电路阵列和无效区域中的电路之间的耦接的数据线。

[0059] 根据另一个实施例,基板是弯曲的柔性基板并且数据线是弯曲的并在基板的表面上形成,使得没有电介质层插入数据线和基板之间。

[0060] 根据另一个实施例,每个像素中的半导体氧化物晶体管包括半导体氧化物沟道。

[0061] 根据另一个实施例,电介质层包括氮化硅层,该氮化硅层与每个像素电路中的硅晶体管的硅沟道重叠,并且不与每个像素电路中的半导体氧化物晶体管的半导体氧化物沟道重叠。

[0062] 根据另一个实施例,存储电容器具有由金属的第二层形成的第一电极并且具有第二电极。

[0063] 根据另一个实施例,电介质层包括另外的氮化硅层,另外的氮化硅层插入每个像素电路中的存储电容器的第一电极和第二电极之间。

[0064] 根据另一个实施例,有机发光二极管显示器包括氧化硅层,该氧化硅层在每个像素电路中与半导体氧化物沟道重叠,并且在每个像素电路的存储电容器中局部移除,使得没有氧化硅层插入存储电容器中的第一电极和第二电极之间。

[0065] 根据另一个实施例,有机发光二极管显示器包括从有效区域向无效区域延伸的数据线,电介质层具有当从有效区域向无效区域过渡时在高度上减小的阶梯式外形,并且数据线在具有阶梯式外形的电介质层上形成。

[0066] 根据另一个实施例,每个像素电路中的半导体氧化物晶体管包括驱动晶体管并且每个像素电路中的硅晶体管包括开关晶体管。

[0067] 根据一个实施例,提供了一种有机发光二极管显示器,其包括有机发光二极管阵列、各自与有机发光二极管中的相应的一个有机发光二极管串联耦接的硅驱动晶体管,以及耦接至硅晶体管的半导体氧化物开关晶体管。

[0068] 根据另一个实施例,半导体氧化物开关晶体管各自具有半导体氧化物沟道,有机发光二极管显示器包括与硅驱动晶体管重叠并且不与半导体氧化物沟道重叠的氮化硅层。

[0069] 根据另一个实施例,有机发光二极管显示器包括耦接至半导体氧化物开关晶体管的存储电容器、和与半导体氧化物沟道重叠并且不与存储电容器重叠的氧化硅层。

[0070] 根据一个实施例,提供了一种有机发光二极管显示器,其包括柔性聚合物基板、基板上的像素电路阵列、柔性聚合物基板上的电介质层和沿循阶梯式外形的电介质层上的数据线。每个像素电路包括有机发光二极管、各自具有半导体氧化物沟道的至少两个半导体

氧化物晶体管、与有机发光二极管串联耦接的至少一个硅晶体管、以及至少一个存储电容器；该柔性聚合物基板上的电介质层具有当从像素电路阵列向邻近像素电路阵列的无效区域过渡时在高度上减小的阶梯式外形；该沿循阶梯式外形的电介质层包括与硅晶体管重叠并且不与半导体氧化物沟道重叠的电介质层。

[0071] 以上内容仅仅是示例性的并且本领域的技术人员可在不脱离所述实施例的范围和实质的情况下做出各种修改。上述实施例可单独实施，也可以任意组合实施。

图1

图2

图3

图4

图5

图6

图7

图8

图9

图10

图11

|                |                                                                                                                                                                   |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 硅和半导体氧化物薄膜晶体管显示器                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">CN110085630A</a>                                                                                                                                      | 公开(公告)日 | 2019-08-02 |

| 申请号            | CN201910101474.8                                                                                                                                                  | 申请日     | 2014-10-28 |

| [标]申请(专利权)人(译) | 苹果公司                                                                                                                                                              |         |            |

| 申请(专利权)人(译)    | 苹果公司                                                                                                                                                              |         |            |

| 当前申请(专利权)人(译)  | 苹果公司                                                                                                                                                              |         |            |

| [标]发明人         | 蔡宗廷<br>V格普塔<br>林敬伟                                                                                                                                                |         |            |

| 发明人            | 蔡宗廷<br>V·格普塔<br>林敬伟                                                                                                                                               |         |            |

| IPC分类号         | H01L27/32                                                                                                                                                         |         |            |

| CPC分类号         | H01L27/1225 H01L27/1251 H01L27/1255 H01L27/3258 H01L27/3262 H01L27/3265 H01L27/3276<br>H01L51/0097 H01L2251/5338 Y02E10/549 H01L29/78651 H01L29/78672 H01L29/7869 |         |            |

| 代理人(译)         | 王茂华<br>张宁                                                                                                                                                         |         |            |

| 优先权            | 14/494931 2014-09-24 US                                                                                                                                           |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                                                                    |         |            |

### 摘要(译)

本发明公开了一种可具有像素电路阵列的电子设备显示器。每个像素电路可包括有机发光二极管和驱动晶体管。每个驱动晶体管可被调节以控制通过有机发光二极管的电流量。每个像素电路可包括存储电容器和一个或多个另外的晶体管诸如开关晶体管。半导体氧化物晶体管和硅晶体管用于形成像素电路的晶体管。存储电容器和晶体管可使用金属层、半导体结构和电介质层来形成。这些层中的一些层可沿显示器的边缘被移除以有利于弯曲。电介质层可具有当数据线延伸到无效边缘区域中时允许阵列中的数据线向基板的表面逐渐降低的阶梯式外形。