(12)发明专利申请

(10)申请公布号 CN 111312162 A

(43)申请公布日 2020.06.19

(21)申请号 201811511113.2

(22)申请日 2018.12.11

(71)申请人 昆山工研院新型平板显示技术中心

有限公司

地址 215300 江苏省苏州市昆山市玉山镇

晨丰路188号3号房

申请人 昆山国显光电有限公司

(72)发明人 盖翠丽

(74)专利代理机构 上海晨皓知识产权代理事务

所(普通合伙) 31260

代理人 成丽杰

(51)Int.Cl.

G09G 3/3208(2016.01)

权利要求书2页 说明书6页 附图3页

(54)发明名称

一种像素电路、显示装置和像素电路的驱动

方法

(57)摘要

本发明实施例涉及显示领域,公开了一种像

素电路、显示装置和像素电路的驱动方法。该像

素电路包括:第一晶体管、第二晶体管、第三晶体

管、存储电容和发光器件;第一晶体管的控制端与

扫描线连接,第一晶体管的第一端与数据线连接,

第一晶体管的第二端分别与存储电容的第一端和第

二晶体管的控制端连接,存储电容的第二端与电源

电压连接;第三晶体管的控制端与控制线连接,第三

晶体管的第一端与电源电压连接,第三晶体管的第二

端与第二晶体管的第一端连接;发光器件的阳极与第

二晶体管的第二端连接,发光器件的阴极接地。使得在像

素电路的存

储电容不变的情况下,通过控制线传输的驱动信

号控制发光器件的亮度,提高了像素电路的发光

亮度的控制。

1. 一种像素电路，其特征在于，包括：第一晶体管、第二晶体管、第三晶体管、存储电容和发光器件；

所述第一晶体管的控制端与扫描线连接，所述第一晶体管的第一端与数据线连接，所述第一晶体管的第二端分别与所述存储电容的第一端和所述第二晶体管的控制端连接，所述存储电容的第二端与电源电压连接；

所述第三晶体管的控制端与控制线连接，所述第三晶体管的第一端与所述电源电压连接，所述第三晶体管的第二端与所述第二晶体管的第一端连接；

所述发光器件的阳极与所述第二晶体管的第二端连接，所述发光器件的阴极接地。

2. 根据权利要求1所述的像素电路，其特征在于，所述第一晶体管和所述第二晶体管为开关管，所述第三晶体管为驱动管。

3. 根据权利要求1-2中任一项所述的像素电路，其特征在于，所述第三晶体管为P型晶体管，优选地，所述第三晶体管为P型薄膜晶体管；

所述第三晶体管的第一端为源极，所述第三晶体管的第二端为漏极。

4. 根据权利要求3所述的像素电路，其特征在于，所述发光器件为有机发光二极管。

5. 一种显示装置，其特征在于，包括如权利要求1-4任一项所述的像素电路。

6. 一种像素电路的驱动方法，应用于如权利要求1-4任一项所述的像素电路，其特征在于，所述像素电路的驱动方法包括：

所述第一晶体管在所述扫描线输出的第一电压信号的控制下处于导通状态；

所述第一晶体管将数据线输出的数据信号传输至存储电容；

所述第一晶体管在所述扫描线输出的第二电压信号的控制下处于关闭状态；

所述第二晶体管在所述存储电容的输出电压信号控制下处于导通状态，通过控制线传输驱动信号至所述第三晶体管，所述第三晶体管根据所述驱动信号驱动所述发光器件；或者，所述第二晶体管在所述存储电容的输出电压信号控制下处于关闭状态；

其中，所述驱动信号包括驱动电流和驱动电压。

7. 根据权利要求6所述的像素电路的驱动方法，其特征在于，所述第一晶体管在所述扫描线输出的第二电压信号的控制下处于关闭状态之前，所述像素电路的驱动方法还包括：

所述第三晶体管在所述控制线输出的控制信号的控制下处于关闭状态，所述发光器件处于熄灭状态。

8. 根据权利要求6所述的像素电路的驱动方法，其特征在于，所述驱动信号用于控制所述发光器件的发光亮度。

9. 根据权利要求6-8任一项所述的像素电路的驱动方法，其特征在于，若所述数据线传输低电压的数据信号；

所述第一晶体管将数据线输出的数据信号传输至存储电容之后，所述像素电路的驱动方法还包括：

控制所述存储电容放电，确定所述第二晶体管的控制端为低电压信号后所述存储电容停止放电。

10. 根据权利要求6-8任一项所述的像素电路的驱动方法，其特征在于，若所述数据线传输高电压的数据信号；

所述第一晶体管将数据线输出的数据信号传输至存储电容之后，所述像素电路的驱动

方法还包括：

控制所述存储电容充电，确定所述第二晶体管的控制端为高电压信号后所述存储电容停止充电。

## 一种像素电路、显示装置和像素电路的驱动方法

### 技术领域

[0001] 本发明实施例涉及显示领域,特别涉及一种像素电路、显示装置和像素电路的驱动方法。

### 背景技术

[0002] 有机发光二极管(Organic Light-Emitting Diode,OLED)作为一种电流型发光器件,因其所具有的自发光、快速响应、宽视觉和可制作在柔性衬底上等特点而被越来越多的应用于高性能显示领域当中。OLED按照驱动方式可分为PMOLED(Passive matrix organic light-emitting diode,无源矩阵有机发光二极管)和AMOLED(Active-matrix organic light-emitting diode,有源矩阵有机发光二极管)。随着平板显示技术的迅猛发展,特别是AMOLED显示屏开始在高端手机、电视等电子显示产品中得到广泛的应用。Micro LED作为新一代显示技术,比现有的OLED技术亮度更高、发光效率更好、但功耗更低。Micro LED作为未来显示的一种解决方案也已成为显示领域研发的热点。

[0003] 然而,发明人发现现有技术中至少存在如下问题:在高端的显示产品中像素驱动电路一般是采用主动阵列,然而主流的主动驱动阵列电路都是模拟信号驱动的,存在电路功耗高、信号容易受到干扰,对驱动器件一致性或者补偿电路的高度依赖等问题。数字驱动的像素电路具有功耗低,信号不易受干扰,对于驱动器件一致性的容忍度高等优点。由于高像素密度的显示产品中像素尺寸较小,因此,在数字驱动电路中像素设计时的存储电容过小,在一帧时间内对信号存储保持率低。

[0004] 需要说明的是,在上述背景技术部分公开的信息仅用于加强对本公开的背景的理解,因此可以包括不构成对本领域普通技术人员已知的现有技术的信息。

### 发明内容

[0005] 本发明实施方式的目的在于提供一种像素电路、显示装置和像素电路的驱动方法,使得在像素电路的存储电容不变的情况下,通过控制线传输的驱动信号控制发光器件的亮度,提高了像素电路的发光亮度的控制。

[0006] 为解决上述技术问题,本发明的实施方式提供了一种像素电路,包括:第一晶体管、第二晶体管、第三晶体管、存储电容和发光器件;

[0007] 第一晶体管的控制端与扫描线连接,第一晶体管的第一端与数据线连接,第一晶体管的第二端分别与存储电容的第一端和第二晶体管的控制端连接,存储电容的第二端与电源电压连接;

[0008] 第三晶体管的控制端与控制线连接,第三晶体管的第一端与电源电压连接,第三晶体管的第二端与第二晶体管的第一端连接;

[0009] 发光器件的阳极与第二晶体管的第二端连接,发光器件的阴极接地。

[0010] 本发明的实施方式还提供了一种显示装置,包括上述的像素电路。

[0011] 本发明的实施方式还提供了一种像素电路的驱动方式,应用于上述的像素电路,

包括：

- [0012] 第一晶体管在扫描线输出的第一电压信号的控制下处于导通状态；

- [0013] 第一晶体管将数据线输出的数据信号传输至存储电容；

- [0014] 第一晶体管在扫描线输出的第二电压信号的控制下处于关闭状态；

- [0015] 第二晶体管在存储电容的输出电压信号控制下处于导通状态，通过控制线传输驱动信号至第三晶体管，第三晶体管根据驱动信号驱动发光器件；或者，第二晶体管在存储电容的输出电压信号控制下处于关闭状态；

- [0016] 其中，驱动信号包括驱动电流和驱动电压。

- [0017] 本发明实施方式相对于现有技术而言，第三晶体管的控制端与控制线连接，在控制线传输的驱动信号的作用通过第二晶体管将驱动信号传输至发光器件，使得发光器件的亮度受驱动信号的控制，在像素电路中存储电容不够的情况下实现对发光器件的亮度的调节，提高了像素电路亮度均一性的控制，提高用户体验。

- [0018] 另外，第一晶体管和第二晶体管为开关管，第三晶体管为驱动管。

- [0019] 该实施方式中，第一晶体管和第二晶体管均为开关管，第二晶体管控制发光器件的数据线输出数据信号的过程中保证发光器件不发光，提高了对发光器件的亮度的控制。

- [0020] 另外，第三晶体管为P型晶体管，优选地，第三晶体管为P型薄膜晶体管；第三晶体管的第一端为源极，第三晶体管的第二端为漏极。

- [0021] 另外，发光器件为有机发光二极管。

- [0022] 该实施方式中，有机发光二极管提高了发光器件的发光效果，进一步提高用户体验。

- [0023] 另外，第一晶体管在扫描线输出的第二电压信号的控制下处于关闭状态之前，像素电路的驱动方法还包括：第三晶体管在控制线输出的控制信号的控制下处于关闭状态，发光器件处于熄灭状态。

- [0024] 另外，驱动信号用于控制发光器件的发光亮度。

- [0025] 另外，若数据线传输低电压的数据信号；第一晶体管将数据线输出的数据信号传输至存储电容之后，像素电路的驱动方法还包括：控制存储电容放电，确定第二晶体管的控制端为低电压信号后存储电容停止放电。

- [0026] 另外，若数据线传输高电压的数据信号；第一晶体管将数据线输出的数据信号传输至存储电容之后，像素电路的驱动方法还包括：控制存储电容充电，确定第二晶体管的控制端为高电压信号后存储电容停止充电。

## 附图说明

- [0027] 一个或多个实施例通过与之对应的附图中的图片进行示例性说明，这些示例性说明并不构成对实施例的限定，附图中具有相同参考数字标号的元件表示为类似的元件，除非有特别申明，附图中的图不构成比例限制。

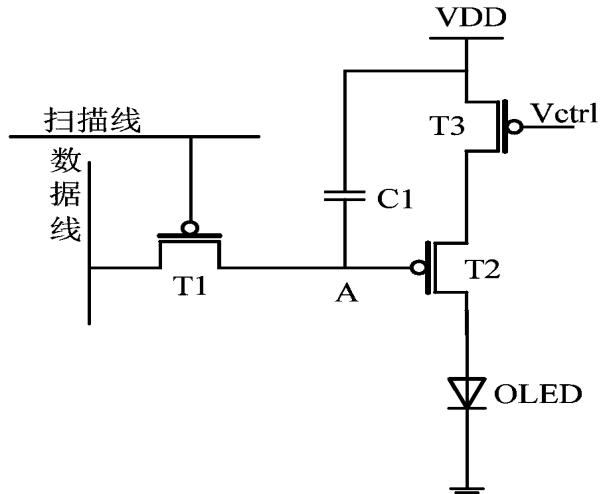

- [0028] 图1是本发明第一实施方式中像素电路的结构示意图；

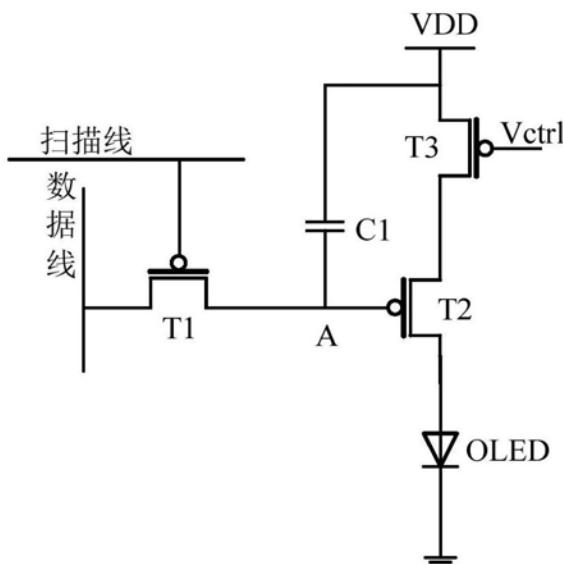

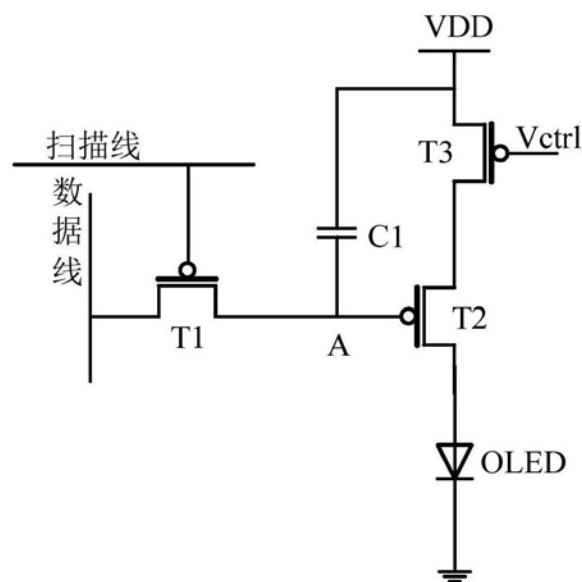

- [0029] 图2是本发明第二实施方式中像素电路的结构示意图；

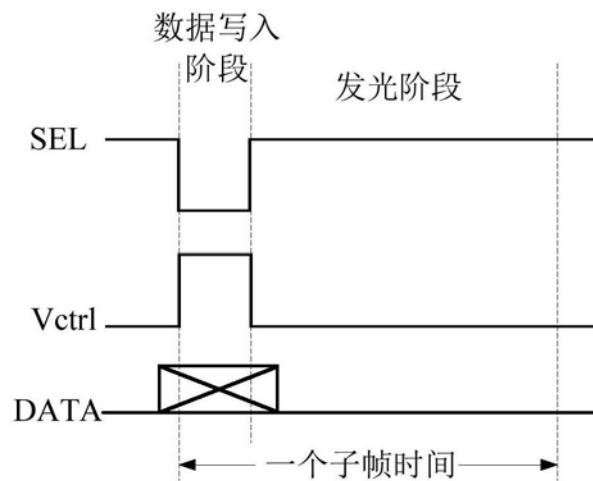

- [0030] 图3是本发明第二实施方式中像素电路的电压时序图；

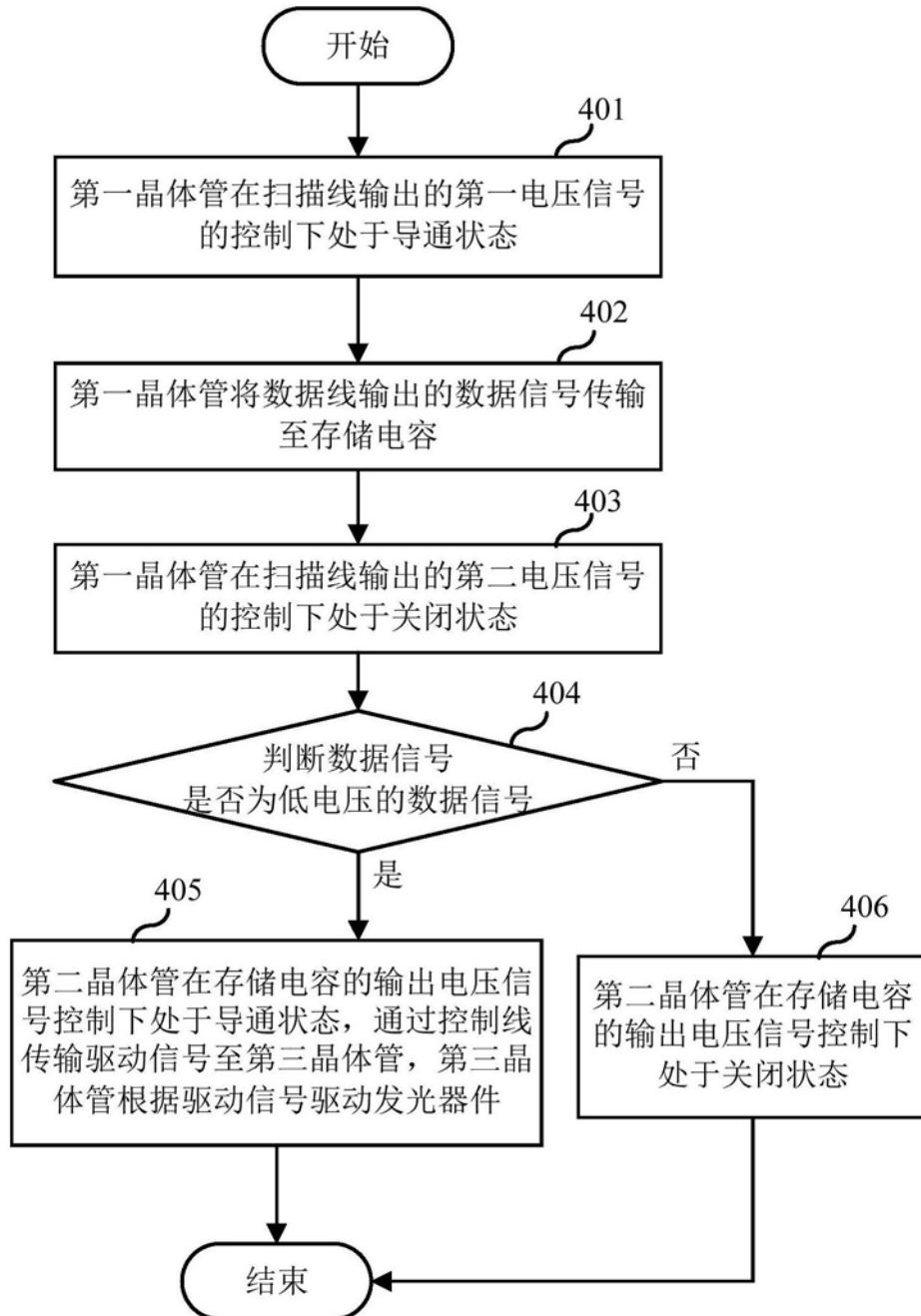

- [0031] 图4是本发明第四实施方式中像素电路的驱动方法的流程图。

## 具体实施方式

[0032] 为使本发明实施例的目的、技术方案和优点更加清楚，下面将结合附图对本发明的各实施方式进行详细的阐述。然而，本领域的普通技术人员可以理解，在本发明各实施方式中，为了使读者更好地理解本申请而提出了许多技术细节。但是，即使没有这些技术细节和基于以下各实施方式的种种变化和修改，也可以实现本申请所要求保护的技术方案。

[0033] 需要说明的是，本发明的说明书和权利要求书及上述附图中的术语“第一”、“第二”等是用于区别类似的对象，而不必用于描述特定的顺序或先后次序。

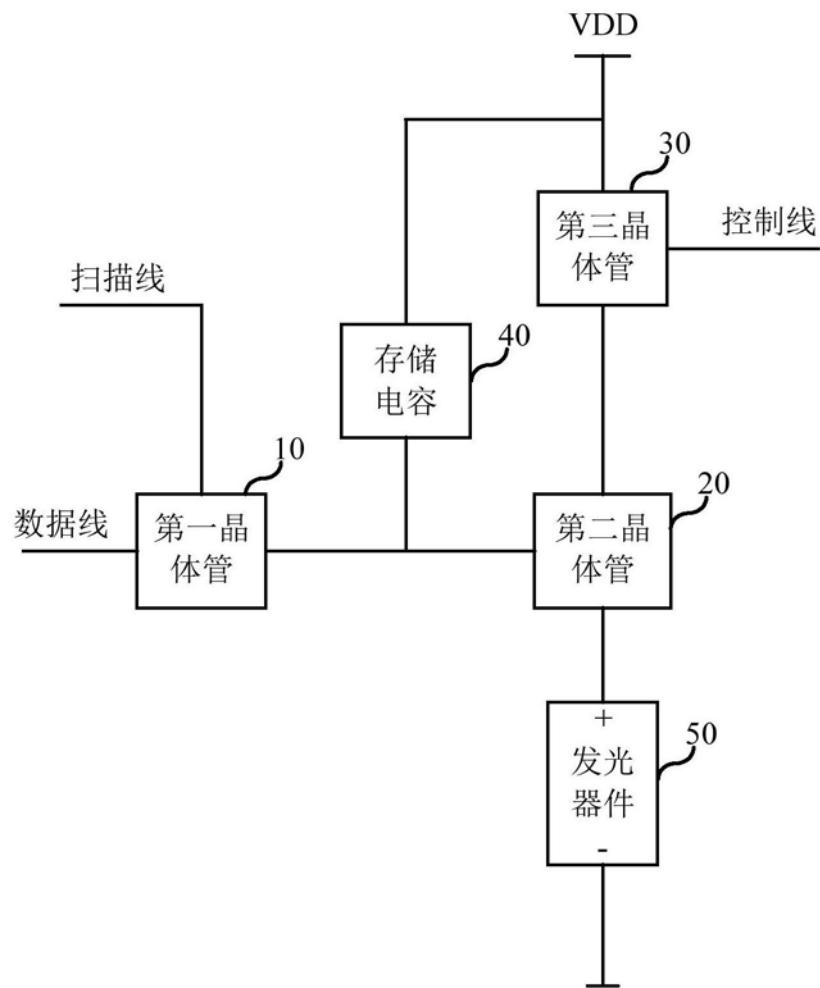

[0034] 本发明的第一实施方式涉及一种像素电路。具体结构如图1所示。包括：第一晶体管10、第二晶体管20、第三晶体管30、存储电容40和发光器件50。

[0035] 第一晶体管10的控制端与扫描线连接，第一晶体管10的第一端与数据线连接，第一晶体管10的第二端分别与存储电容40的第一端和第二晶体管20的控制端连接，存储电容40的第二端与电源电压连接；第三晶体管30的控制端与控制线连接，第三晶体管30的第一端与电源电压连接，第三晶体管30的第二端与第二晶体管20的第一端连接；发光器件50的阳极与第二晶体管20的第二端连接，发光器件50的阴极接地；其中，第三晶体管为P型晶体管。

[0036] 需要说明的是，图示1的像素电路中，第一晶体管10、第二晶体管20和第三晶体管30可以为同一类型的晶体管，例如，第一晶体管10、第二晶体管20和第三晶体管30均为P型薄膜晶体管。或者，第一晶体管和第二晶体管为N型晶体管，第三晶体管为P型晶体管，其中，本实施方式中以图示1中的三个晶体管均为P型薄膜晶体管为例，对电路进行示例性的说明，在其他的具体实施电路中第一晶体管和第二晶体管可以采用其他的种类的晶体管，对晶体管种类不做限定。另外，本实施方式中的发光器件50可以是现有技术中包括LED或OLED在内的多种电流驱动发光器件50，也可为其他类型的发光器件50，本实施方式中以OLED为例说明像素电路的工作原理，具体的实施细节可根据实际使用的发光器件50适应性调整，此处不做限制。

[0037] 具体地说，在像素电路中设置第三晶体管30，且第三晶体管30的控制端与控制线连接，通过第三晶体管30的控制端接收控制线传输的驱动信号，驱动信号用于控制发光器件50的亮度，其中，第三晶体管30为驱动管。

[0038] 具体地说，第一晶体管10和第二晶体管20为开关管，第一晶体管10和第二晶体管20控制端的电压用于控制该晶体管处于导通或关闭的状态。如图1所示，第一晶体管10的控制端与扫描线连接，若第一晶体管10为P型薄膜晶体管，则栅极连接扫描线，可实现通过扫描线传输的电压信号控制第一晶体管10处于导通或关闭的状态，源极或漏极连接数据线均可，具体连接方式不做限制。例如，由于第一晶体管为P型薄膜晶体管，则扫描线传输的低压信号控制第一晶体管处于导通状态，扫描线传输的高压信号控制第一晶体管处于关闭状态。第二晶体管20的控制端与第一晶体管10的第二端连接，即图示中第一晶体管10右侧的一端，若第二晶体管20为P型薄膜晶体管，则栅极连接第一晶体管10的第一端，源极或漏极连接发光器件50的阳极均可，具体的电路连接不做限制。

[0039] 需要说明的是，第三晶体管为P型晶体管，且第三晶体管为驱动管，工作在饱和区，源极提供载流子，使得第三晶体管处于导通状态，因此，设置第三晶体管的源极与电源电压连接，漏极与第二晶体管连接。

[0040] 本实施例中,该像素电路被驱动,在一个发光时间段,包括数据写入阶段和发光阶段。需要说明的是,对发光器件50的控制包括发光和不发光,例如,数字信号“1”表示发光器件50发光,数字信号“0”表示发光器件50不发光,对于数字信号“1”或“0”均包括数据写入阶段和发光阶段,区别之处在于,在数字信号“1”中发光阶段的发光器件50处于发光状态,在数字信号“0”中发光阶段的发光器件50处于熄灭状态。

[0041] 一个具体实施例中,以采用低温多晶硅技术(LTPS, Low Temperature Poly-silicon)工艺制作的像素电路为例,第三晶体管30为P型薄膜晶体管,数字信号“1”时,数据写入阶段时数据线传输的数据信号为低电压,在发光阶段发光器件50处于发光状态;数字信号“0”时,数据写入阶段时数据线传输的数据信号为高电压,在发光阶段发光器件50处于熄灭状态。

[0042] 需要说明的是,本实施方式中第三晶体管30是驱动管,第三晶体管30的控制端与控制线连接,控制线传输驱动信号,第三晶体管30可以一直处于导通状态,在发光阶段控制发光器件50的亮度,使得像素电路在存储电容40的容量有限的情况下实现对发光器件50亮度均一性的控制,这种通过控制端输出的驱动信号控制发光器件50的亮度的方式,提高用户体验,另外,优选地,像素电路中的第一晶体管10、第二晶体管20和第三晶体管30采用相同类型的晶体管,如P型薄膜晶体管,可采用P型LTPS技术制作该像素电路,降低了工艺难度,有利于像素电路的推广和生产。

[0043] 需要说明的是,以上仅为举例说明,并不对本发明的技术方案构成限定。

[0044] 相对于现有技术而言,第三晶体管的控制端与控制线连接,在控制线传输的驱动信号的作用通过第二晶体管将驱动信号传输至发光器件,使得发光器件的亮度受驱动信号的控制,在像素电路中存储电容不够的情况下实现对发光器件的亮度的调节,提高了像素电路亮度均一性的控制,提高用户体验。

[0045] 本发明的第二实施方式涉及一种像素电路,第二实施方式与第一实施方式大致相同,主要区别之处在于:在本发明第二实施方式中具体给出了一种像素电路的结构,如图2所示。

[0046] 第一晶体管、第二晶体管和第三晶体管均以P型薄膜晶体管为例,发光器件为OLED。

[0047] 一个具体实施例中,在一个子帧时间段,具体为将一帧画面在时间上分成多个子帧,每个子帧对应各自的扫描时间,在扫描阶段先进行数据写入再通过驱动晶体管控制发光器件的亮度。如图3所示一个子帧时间段中的电压变化示意,在一个子帧时间段中,图3中的SEL表示扫描线输出的电压信号,Vctrl表示控制端输出的驱动信号,DATA表示写入的数据。在数字信号“1”的状态时,扫描线传输低电压信号至第一晶体管T1,第一晶体管T1处于导通状态,数据线传输低电压的数据信号至存储电容C1,同时Vctrl传输高电压信号至第三晶体管T3的控制端,第三晶体管T3处于关闭状态,表示在数据写入阶段,第三晶体管处于关闭状态,发光器件不发光;发光阶段,扫描线传输高电压信号至第一晶体管T1,第一晶体管T1处于关闭状态,低电压的数据信号控制存储电容C1放电,存储电容C1的第一端处于低电压,第二晶体管处于导通状态,Vctrl为低电压状态,第三晶体管T3处于导通状态,Vctrl输出的驱动信号通过第三晶体管T3控制发光器件的亮度。

[0048] 数字信号“0”的状态时,数据写入阶段,扫描线传输低电压信号至第一晶体管T1,

第一晶体管T1处于导通状态,数据线传输高电压的数据信号至存储电容C1,同时Vctrl1传输高电压信号至第三晶体管T3的控制端,第三晶体管T3处于关闭状态,表示在数据写入阶段,第三晶体管处于关闭状态,发光器件不发光;发光阶段,扫描线传输高电压信号至第一晶体管T1,第一晶体管T1处于关闭状态,存储电容C1的第一端处于高电压,第二晶体管T2处于关闭状态,发光器件不发光。

[0049] 其中,驱动信号用于控制发光器件的亮度。

[0050] 具体地说,图2所示的电路中第三晶体管工作在饱和区,且第三晶体管T3栅极和源极之间的电压Vgs与电源电压VDD和Vctrl相关,其中,VDD是预设置,Vctrl用于控制发光器件的亮度,可保证整个控制面板上的像素电路的亮度的均一性。

[0051] 值得一提的是,在像素电路中每个子帧的时间可以是不相同的,例如,像素电路在显示一帧画面时,该帧画面在时间上会被分成多个子帧,每个子帧完成扫描的时间分别是 $1t$ 、 $1/2t$ 、 $1/4t$ 、 $1/8t$ ……,t表示该帧画面的全部扫描时间,一个具体实施例中,该帧画面的灰阶达到256时,需要8个子帧,第8个子帧的时间为 $1/128t$ 。

[0052] 需要说明的是,以上仅为举例说明,并不对本发明的技术方案构成限定。

[0053] 本发明第三实施方式涉及一种显示装置,包括上述第一或第二实施方式中的像素电路。

[0054] 需要说明的是,显示装置可以为有机发光显示器或其他显示设备,该显示装置中可以包括多个像素单元阵列,每个像素阵列单元包括上述第一或第二实施方式中的像素电路。显示装置可以是手机、平板电脑、电视机、显示器、笔记本电脑、数码相框或导航仪等具有显示功能的产品或部件。

[0055] 具体地说,显示装置上的像素电路均设置在控制面板上,具体像素电路的排列设置方式不做具体限制,显示装置中包括至少一个的像素电路,用于显示装置进行显示。

[0056] 一个具体实施例中,以图2中的像素电路为例,第三晶体管T3与电源电压VDD连接,则第三晶体管的栅极和源极之间的驱动电压表示为: $V_{gs} = VDD - Vctrl$ ;其中,Vgs表示第三晶体管的驱动电压,VDD表示电源电压,Vctrl表示控制端传输的电压值。具体实施例中,通过对像素电路中版图设计,将因版图设计中线路布局或像素电路结构布局对VDD和Vctrl的影响降低,保证在显示装置中的控制板上的像素电路的亮度均一性。

[0057] 不难发现,本实施方式为与第一或第二实施方式相对应的装置实施例,本实施方式可与第一或第二实施方式互相配合实施。第一或第二实施方式中提到的相关技术细节在本实施方式中依然有效,为了减少重复,这里不再赘述。相应地,本实施方式中提到的相关技术细节也可应用在第一或第二实施方式中。

[0058] 本发明第四实施方式涉及一种像素电路的驱动方法。应用于上述第一或第二实施方式中的提到的像素电路,其像素电路的驱动方法的流程如图4所示,包括如下实施步骤:

[0059] 步骤401:第一晶体管在扫描线输出的第一电压信号的控制下处于导通状态。

[0060] 具体地说,第一电压需要根据像素电路中的第一晶体管的类型设置,此处仅是说明第一电压信号控制第一晶体管处于对应的状态,具体根据像素电路中的器件设置,此处不做限制。

[0061] 步骤402:第一晶体管将数据线输出的数据信号传输至存储电容。

[0062] 具体地说,第一晶体管将数据线输出的数据信号传输至存储电容的过程中,数据

信号包含数字信息，且数据信号包括高电压的数据信号和低电压的数据信号，控制存储电容放电或充电，在存储电容充电或放电执行完成之后，扫描线传输第二电压信号控制第一晶体管关闭。

[0063] 需要说明的是，第一晶体管将数据线输出的数据信号传输至存储电容的过程中，第三晶体管的控制线输出的控制信号下处于关闭状态，发光器件处于熄灭状态。也就是说在数据写入阶段，发光器件不发光。

[0064] 步骤403：第一晶体管在扫描线输出的第二电压信号的控制下处于关闭状态。

[0065] 步骤404：判断数据信号是否为低电压的数据信号，若为是，执行步骤405，否则，执行步骤406。

[0066] 步骤405：第二晶体管在存储电容的输出电压信号控制下处于导通状态，通过控制线传输驱动信号至第三晶体管，第三晶体管根据驱动信号驱动发光器件。

[0067] 其中，驱动信号包括驱动电流和驱动电压。

[0068] 具体地说，驱动信号包括驱动电流和驱动电压，根据发光器件的特性设置不同的驱动信号，电流驱动的发光器件设置驱动信号为驱动电流，电压驱动的发光器件设置驱动信号为驱动电压。

[0069] 一个具体实施例中，数据信号为低电压的数据信号，控制存储电容放电，确定第二晶体管的控制端为低电压信号后存储电容停止放电。

[0070] 步骤406：第二晶体管在存储电容的输出电压信号控制下处于关闭状态。

[0071] 一个具体实施例中，数据信号为高电压的数据信号，控制存储电容充电，确定第二晶体管的控制端为高电压信号后存储电容停止充电。

[0072] 需要说明的是，上述具体实现仅为对应步骤的具体细节说明，不做具体限制。

[0073] 上面各种方法的步骤划分，只是为了描述清楚，实现时可以合并为一个步骤或者对某些步骤进行拆分，分解为多个步骤，只要包括相同的逻辑关系，都在本专利的保护范围内；对算法中或者流程中添加无关紧要的修改或者引入无关紧要的设计，但不改变其算法和流程的核心设计都在该专利的保护范围内。

[0074] 不难发现，本实施方式为与第一或第二实施方式相对应的驱动方法实施例，本实施方式可与第一或第二实施方式互相配合实施。第一或第二实施方式中提到的相关技术细节在本实施方式中依然有效，为了减少重复，这里不再赘述。相应地，本实施方式中提到的相关技术细节也可应用在第一或第二实施方式中。

[0075] 本领域的普通技术人员可以理解，上述各实施方式是实现本发明的具体实施例，而在实际应用中，可以在形式上和细节上对其作各种改变，而不偏离本发明的精神和范围。

图1

图2

图3

图4

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种像素电路、显示装置和像素电路的驱动方法                          |         |            |

| 公开(公告)号        | <a href="#">CN111312162A</a>                   | 公开(公告)日 | 2020-06-19 |

| 申请号            | CN201811511113.2                               | 申请日     | 2018-12-11 |

| [标]申请(专利权)人(译) | 昆山工研院新型平板显示技术中心有限公司<br>昆山国显光电有限公司              |         |            |

| 申请(专利权)人(译)    | 昆山工研院新型平板显示技术中心有限公司<br>昆山国显光电有限公司              |         |            |

| 当前申请(专利权)人(译)  | 昆山工研院新型平板显示技术中心有限公司<br>昆山国显光电有限公司              |         |            |

| [标]发明人         | 盖翠丽                                            |         |            |

| 发明人            | 盖翠丽                                            |         |            |

| IPC分类号         | G09G3/3208                                     |         |            |

| CPC分类号         | G09G3/3208 G09G3/3225                          |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

## 摘要(译)

本发明实施例涉及显示领域，公开了一种像素电路、显示装置和像素电路的驱动方法。该像素电路包括：第一晶体管、第二晶体管、第三晶体管、存储电容和发光器件；第一晶体管的控制端与扫描线连接，第一晶体管的第一端与数据线连接，第一晶体管的第二端分别与存储电容的第一端和第二晶体管的控制端连接，存储电容的第二端与电源电压连接；第三晶体管的控制端与控制线连接，第三晶体管的第一端与电源电压连接，第三晶体管的第二端与第二晶体管的第一端连接；发光器件的阳极与第二晶体管的第二端连接，发光器件的阴极接地。使得在像素电路的存储电容不变的情况下，通过控制线传输的驱动信号控制发光器件的亮度，提高了像素电路的发光亮度的控制。