(12) 实用新型专利

(10) 授权公告号 CN 203118410 U

(45) 授权公告日 2013. 08. 07

(21) 申请号 201220601021. 5

(22) 申请日 2012. 11. 14

(30) 优先权数据

10-2012-0029639 2012. 03. 23 KR

(73) 专利权人 三星显示有限公司

地址 韩国京畿道

(72) 发明人 黄荣仁

(74) 专利代理机构 北京英赛嘉华知识产权代理

有限责任公司 11204

代理人 余朦 刘铮

(51) Int. Cl.

G09G 3/32 (2006. 01)

(ESM) 同样的发明创造已同日申请发明专利

权利要求书3页 说明书24页 附图23页

(54) 实用新型名称

像素电路以及有机发光显示装置

(57) 摘要

公开了像素电路和有机发光显示装置。像素电路包括：有机发光二极管；第一PMOS晶体管，连接在第一电源电压与有机发光二极管的阳极之间；第二PMOS晶体管，连接在第一节点与有机发光二极管的阳极之间；第一电容器，连接在第二节点与第一节点之间；第二电容器，连接在第一电源电压与第二节点之间；第三PMOS晶体管，连接在数据线与第二节点之间；第四PMOS晶体管，连接在第三节点与第二节点之间；第三电容器，连接在第三节点与第三PMOS晶体管的栅端之间；以及第五PMOS晶体管，连接在数据线与第三节点之间。根据本实用新型的像素电路和有机发光显示装置能够高速操作、并且可降低功耗。

1. 像素电路,其特征在于包括:

有机发光二极管,所述有机发光二极管的阴极连接至第二电源电压;

第一PMOS晶体管,连接在第一电源电压与所述有机发光显示装置的阳极之间,所述第一PMOS晶体管的栅端连接至第一节点;

第二PMOS晶体管,连接在所述第一节点与所述有机发光二极管的阳极之间,所述第二PMOS晶体管的栅端接收补偿控制信号;

第一电容器,连接在第二节点与所述第一节点之间;

第二电容器,连接在所述第一电源电压与所述第二节点之间;

第三PMOS晶体管,连接在数据线与所述第二节点之间,所述第三PMOS晶体管的栅端接收所述补偿控制信号;

第四PMOS晶体管,连接在第三节点与所述第二节点之间,所述第四PMOS晶体管的栅端接收发射控制信号;

第三电容器,连接在所述第三节点与所述第三PMOS晶体管的栅端之间;以及

第五PMOS晶体管,连接在所述数据线与所述第三节点之间,所述第五PMOS晶体管的栅端连接至扫描线。

2. 如权利要求1所述的电路,其特征在于还包括:

第四电容器,连接在所述有机发光二极管的阳极与阴极之间。

3. 像素电路,其特征在于包括:

有机发光二极管,所述有机发光二极管的阴极连接至第二电源电压;

第一PMOS晶体管,连接在第一电源电压与所述有机发光二极管的阳极之间,所述第一PMOS晶体管的栅端连接至第一节点;

第二PMOS晶体管,连接在所述第一节点与所述有机发光二极管的阳极之间,所述第二PMOS晶体管的栅端接收补偿控制信号;

第一电容器,连接在第二节点与所述第一节点之间;

第二电容器,连接在所述第一电源电压与所述第二节点之间;

第三PMOS晶体管,连接在数据线与所述第二节点之间,所述第三PMOS晶体管的栅端接收所述补偿控制信号;

第四PMOS晶体管,连接在第三节点与所述第二节点之间,所述第四PMOS晶体管的栅端接收发射控制信号;

第三电容器,连接在所述第三节点与维持电源电压之间;以及

第五PMOS晶体管,连接在所述数据线与所述第三节点之间,所述第五PMOS晶体管的栅端连接至扫描线。

4. 如权利要求3所述的电路,其特征在于还包括:

第四电容器,连接在所述有机发光二极管的阳极与阴极之间。

5. 像素电路,其特征在于包括:

有机发光二极管,所述有机发光二极管的阳极连接至第一电源电压;

第一NMOS晶体管,连接在第二电源电压与所述有机发光二极管的阴极之间,所述第一NMOS晶体管的栅端连接至第一节点;

第二NMOS晶体管,连接在所述第一节点与所述有机发光二极管的阴极之间,所述第二

NMOS 晶体管的栅端接收补偿控制信号；

第一电容器，连接在第二节点与所述第一节点之间；

第二电容器，连接在所述第二电源电压与所述第二节点之间；

第三 NMOS 晶体管，连接在数据线与所述第二节点之间，所述第三 NMOS 晶体管的栅端接收所述补偿控制信号；

第四 NMOS 晶体管，连接在第三节点与所述第二节点之间，所述第四 NMOS 晶体管的栅端接收发射控制信号；

第三电容器，连接在所述第三节点与所述第三 NMOS 晶体管的栅端之间；以及

第五 NMOS 晶体管，连接在所述数据线与所述第三节点之间，所述第五 NMOS 晶体管的栅端连接至扫描线。

6. 像素电路，其特征在于包括：

有机发光二极管，所述有机发光二极管的阳极连接至第一电源电压；

第一 NMOS 晶体管，连接在第二电源电压与所述有机发光二极管的阴极之间，所述第一 NMOS 晶体管的栅端连接至第一节点；

第二 NMOS 晶体管，连接在所述第一节点与所述有机发光二极管的阴极之间，所述第二 NMOS 晶体管的栅端接收补偿控制信号；

第一电容器，连接在第二节点与所述第一节点之间；

第二电容器，连接在所述第二电源电压与所述第二节点之间；

第三 NMOS 晶体管，连接在数据线与所述第二节点之间，所述第三 NMOS 晶体管的栅端接收所述补偿控制信号；

第四 NMOS 晶体管，连接在第三节点与所述第二节点之间，所述第四 NMOS 晶体管的栅端接收发射控制信号；

第三电容器，连接在所述第三节点与维持电源电压之间；以及

第五 NMOS 晶体管，连接在所述数据线与所述第三节点之间，所述第五 NMOS 晶体管的栅端连接至扫描线。

7. 有机发光显示装置，其特征在于包括：

像素单元，具有多个像素电路，所述多个像素电路的每个像素电路为如权利要求 1 所述的像素电路；

扫描驱动单元，被配置为向所述像素电路提供扫描信号；

数据驱动单元，被配置为向所述像素电路提供数据信号；

控制信号生成单元，被配置为向所述像素电路提供所述发射控制信号和所述补偿控制信号；

供电单元，被配置为向所述像素单元提供所述第一电源电压和所述第二电源电压；以及

时序控制单元，被配置为控制所述扫描驱动单元、所述数据驱动单元、所述控制信号生成单元和所述供电单元。

8. 有机发光显示装置，其特征在于包括：

像素单元，具有多个像素电路，所述多个像素电路的每个像素电路为如权利要求 3 所述的像素电路；

扫描驱动单元,被配置为向所述像素电路提供扫描信号 ;

数据驱动单元,被配置为向所述像素电路提供数据信号 ;

控制信号生成单元,被配置为向所述像素电路提供所述发射控制信号和所述补偿控制信号 ;

供电单元,被配置为向所述像素单元提供所述第一电源电压、所述第二电源电压和所述维持电源电压 ;以及

时序控制单元,被配置为控制所述扫描驱动单元、所述数据驱动单元、所述控制信号生成单元和所述供电单元。

## 像素电路以及有机发光显示装置

[0001] 相关申请的交叉引用

[0002] 本申请根据 35U.S.C. § 119 要求于 2012 年 3 月 23 日提交到韩国知识产权局的题为“Pixel Circuit, Method of Driving a Pixel Circuit, and Organic Light Emitting Display Device (像素电路、驱动像素电路的方法以及有机发光显示装置)”的第 10-2012-0029639 号韩国专利申请的优先权，该韩国专利申请的全部内容通过引用并入本文。

### 技术领域

[0003] 实施方式涉及像素电路、驱动像素电路的方法以及有机发光显示装置。

### 背景技术

[0004] 在立体(3D)图像显示技术中，立体图像可通过提供三维效果的双眼视差实现。一般地，立体图像可通过分别向左眼和右眼交替地提供左图像和右图像而实现。使用可提供快响应速度和低功耗的有机发光显示装置来作为用于显示立体图像的平板显示装置可能是比较理想的。

### 实用新型内容

[0005] 本实用新型要解决的一个技术问题在于提供一种能够高速操作、并且可降低功耗的像素电路。

[0006] 实施方式指向一种像素电路，该像素电路包括：有机发光二极管，有机发光二极管的阴极连接至第二电源电压；第一 PMOS 晶体管，连接在第一电源电压与有机发光二极管的阳极之间，第一 PMOS 晶体管的栅端连接至第一节点；第二 PMOS 晶体管，连接在第一节点与有机发光二极管的阳极之间，第二 PMOS 晶体管的栅端接收补偿控制信号；第一电容器，连接在第二节点与第一节点之间；第二电容器，连接在第一电源电压与第二节点之间；第三 PMOS 晶体管，连接在数据线与第二节点之间，第三 PMOS 晶体管的栅端接收补偿控制信号；第四 PMOS 晶体管，连接在第三节点与第二节点之间，第四 PMOS 晶体管的栅端接收发射控制信号；第三电容器，连接在第三节点与第三 PMOS 晶体管的栅端之间；以及第五 PMOS 晶体管，连接在数据线与第三节点之间，第五 PMOS 晶体管的栅端连接至扫描线。

[0007] 该电路可被配置为交替地执行用于显示左图像的第一显示操作和用于显示右图像的第二显示操作，第一显示操作和第二显示操作是基于同时发射方法执行的。

[0008] 第一显示操作可包括第一初始数据写入操作、第一复位操作、第一阈值电压补偿操作、第一数据写入操作和第一发射操作，第二显示操作可包括第二初始数据写入操作、第二复位操作、第二阈值电压补偿操作、第二数据写入操作和第二发射操作。

[0009] 该电路可被配置为同时执行第一发射操作和第二初始数据写入操作，并且可被配置为同时执行第二发射操作和第一初始数据写入操作。

[0010] 在执行第一初始数据写入操作的时候，第四 PMOS 晶体管可截止，并且当第五 PMOS

晶体管响应于通过扫描施加的扫描信号而导通时通过数据线施加的第一图像数据可存储在第三电容器中；以及在执行第二初始数据写入操作的时候，第四 PMOS 晶体管可截止，并且当第五 PMOS 晶体管响应于通过扫描线施加的扫描信号而导通时通过数据线施加的第二图像数据可存储在第三电容器中。

[0011] 在执行第一复位操作的时候，第二至第四 PMOS 晶体管可截止，第二电源电压可具有高电压电平，并且第一电源电压可具有低电压电平；以及在执行第二复位操作的时候，第二至第四 PMOS 晶体管可截止，第二电源电压可具有高电压电平，并且第一电源电压可具有低电压电平。

[0012] 在执行第一阈值电压补偿操作的时候，第四 PMOS 晶体管可截止，第二和第三 PMOS 晶体管可导通，第二电源电压可具有高电压电平，并且第一电源电压可具有高电压电平；以及在执行第二阈值电压补偿 操作的时候，第四 PMOS 晶体管可截止，第二和第三 PMOS 晶体管可导通，第二电源电压可具有高电压电平，并且第一电源电压可具有高电压电平。

[0013] 在执行第一数据写入操作的时候，第四 PMOS 晶体管可导通，第二和第三 PMOS 晶体管可截止，第二电源电压可具有高电压电平，并且第一电源电压可具有高电压电平；以及在执行第二数据写入操作的时候，第四 PMOS 晶体管可导通，第二和第三 PMOS 晶体管可截止，第二电源电压可具有高电压电平，并且第一电源电压可具有高电压电平。

[0014] 在执行第一发射操作的时候，第二至第四 PMOS 晶体管可截止，第二电源电压可具有低电压电平，并且第一电源电压可具有高电压电平；以及在执行第二发射操作的时候，第二至第四 PMOS 晶体管可截止，第二电源电压可具有低电压电平，并且第一电源电压可具有高电压电平。

[0015] 第一显示操作还可包括第一偏置截止应用操作，第二显示操作还可包括第二偏置截止应用操作。

[0016] 在执行第一偏置截止应用操作的时候，第四 PMOS 晶体管可截止，第二和第三 PMOS 晶体管可导通，第二电源电压可具有高电压电平，并且第一电源电压可具有低电压电平；以及在执行第二偏置截止应用操作的时候，第四 PMOS 晶体管可截止，第二和第三 PMOS 晶体管可导通，第二电源电压可具有高电压电平，并且第一电源电压可具有低电压电平。

[0017] 该电路还可包括第四电容器，第四电容器连接在有机发光二极管的阳极与阴极之间。

[0018] 实施方式还指向一种像素电路，该像素电路包括：有机发光二极管，有机发光二极管的阳极连接至第二电源电压；第一 PMOS 晶体管，连接在第一电源电压与有机发光二极管的阳极之间，第一 PMOS 晶体管的栅端连接至第一节点；第二 PMOS 晶体管，连接在第一节点与有机发光二极管的阳极之间，第二 PMOS 晶体管的栅端接收补偿控制信号；第一电容器，连接在第二节点与第一节点之间；第二电容器，连接在第一电源电压与第二节点之间；第三 PMOS 晶体管，连接在数据线与第二节点之间，第三 PMOS 晶体管的栅端接收补偿控制信号；第四 PMOS 晶体管，连接在第三节点与第二节点之间，第四 PMOS 晶体管的栅端接收发射控制信号；第三电容器，连接在第三节点与维持电源电压之间；以及第五 PMOS 晶体管，连接在数据线与第三节点之间，第五 PMOS 晶体管的栅端连接至扫描线。

[0019] 该电路可被配置为交替地执行用于显示左图像的第一显示操作和用于显示右图像的第二显示操作，第一显示操作和第二显示操作是基于同时发射方法执行的。

[0020] 第一显示操作可包括第一初始数据写入操作、第一复位操作、第一阈值电压补偿操作、第一数据写入操作和第一发射操作,第二显示操作可包括第二初始数据写入操作、第二复位操作、第二阈值电压补偿操作、第二数据写入操作和第二发射操作。

[0021] 该电路可被配置为同时执行第一发射操作和第二初始数据写入操作,并且可被配置为同时执行第二发射操作和第一初始数据写入操作。

[0022] 第一显示操作还可包括第一偏置截止应用操作,第二显示操作还可包括第二偏置截止应用操作。

[0023] 该电路还可包括第四电容器,第四电容器连接在有机发光二极管的阳极与阴极之间。

[0024] 实施方式还指向一种像素电路,该像素电路包括:有机发光二极管,有机发光二极管的阳极连接至第一电源电压;第一 NMOS 晶体管,连接在第二电源电压与有机发光二极管的阴极之间,第一 NMOS 晶体管的栅端连接至第一节点;第二 NMOS 晶体管,连接在第一节点与有机发光二极管的阴极之间,第二 NMOS 的栅端接收补偿控制信号;第一电容器,连接在第二节点与第一节点之间;第二电容器,连接在第二电源电压与第二节点之间;第三 NMOS 晶体管,连接在数据线与第二节点之间,第三 NMOS 晶体管的栅端接收补偿控制信号;第四 NMOS 晶体管,连接在第三节点与第二节点之间,第四 NMOS 晶体管的栅端接收发射控制信号;第三电容器,连接在第三节点与第三 NMOS 晶体管的栅端之间;以及第五 NMOS 晶体管,连接在数据线与第三节点之间,第五 NMOS 晶体管的栅端连接至扫描线。

[0025] 实施方式还指向一种像素电路,该像素电路包括有机发光二极管,有机发光二极管的阳极连接至第一电源电压;第一 NMOS 晶体管,连接在第二电源电压与有机发光二极管的阴极之间,第一 NMOS 晶体管的栅端连接至第一节点;第二 NMOS 晶体管,连接在第一节点与有机发光二极管的阴极之间,第二 NMOS 晶体管的栅端接收补偿控制信号;第一电容器,连接在第二节点与第一节点之间;第二电容器,连接在第二电源电压与第二节点之间;第三 NMOS 晶体管,连接在数据线与第二节点之间,第三 NMOS 晶体管的栅端接收补偿控制信号;第四 NMOS 晶体管连接在第三节点与第二节点之间,第四 NMOS 晶体管的栅端接收发射控制信号;第三电容器,连接在第三节点与维持电源电压之间;以及第五 NMOS 晶体管,连接在数据线与第三节点之间,第五 NMOS 晶体管的栅端连接至扫描线。

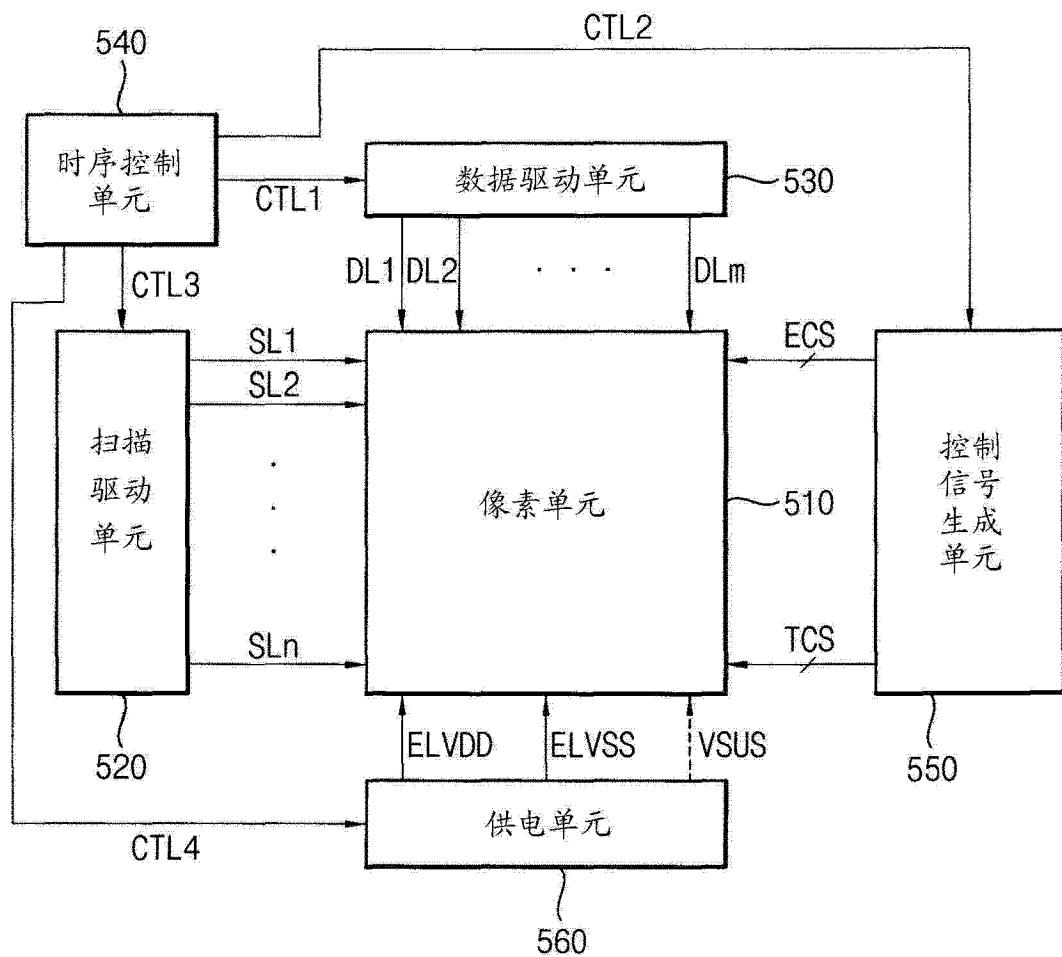

[0026] 实施方式还指向一种有机发光显示装置,该有机发光显示装置包括:像素单元,具有多个像素电路,多个像素电路的每个像素电路是根据一个实施方式的像素电路;扫描驱动单元,被配置为向像素电路提供扫描信号;数据驱动单元,被配置为向像素电路提供数据信号;控制信号生成单元,被配置为向像素电路提供发射控制信号和补偿控制信号;供电单元,被配置为向像素单元提供第一电源电压和第二电源电压;以及及时控制单元,被配置为控制扫描驱动单元、数据驱动单元、控制信号生成单元和供电单元。

[0027] 多个像素电路的每个像素电路可被配置为交替地执行用于显示左图像的第一显示操作和用于显示右图像的第二显示操作,第一显示操作和第二显示操作是基于同时发射方法执行的。

[0028] 第一显示操作可包括第一初始数据写入操作、第一复位操作、第一阈值电压补偿操作、第一数据写入操作和第一发射操作,第二显示操作可包括第二初始数据写入操作、第二复位操作、第二阈值电压补偿操作、第二数据写入操作和第二发射操作,多个像素电路的

每个像素电路可被配置为同时执行第一发射操作和第二初始数据写入操作，并且可被配置为同时执行第二发射操作和第一初始数据写入操作。

[0029] 第一显示操作还可包括第一偏置截止应用操作，第二显示操作还可包括第二偏置截止应用操作。

[0030] 实施方式还指向一种有机发光显示装置，该有机发光显示装置包括：像素单元，具有多个像素电路，多个像素电路的每个像素电路为根据另一实施方式的像素电路；扫描驱动单元，被配置为向像素电路提供扫描信号；数据驱动单元，被配置为向像素电路提供数据信号；控制信号生成单元，被配置为向像素电路提供发射控制信号和补偿控制信号；供电单元，被配置为向像素单元提供第一电源电压、第二电源电压和维持电源电压；以及时序控制单元，被配置为控制扫描驱动单元、数据驱动单元、控制信号生成单元和供电单元。

[0031] 多个像素电路的每个像素电路可被配置为交替地执行用于显示左图像的第一显示操作和用于显示右图像的第二显示操作，第一显示操作和第二显示操作是基于同时发射方法执行的。

[0032] 第一显示操作可包括第一初始数据写入操作、第一复位操作、第一阈值电压补偿操作、第一数据写入操作和第一发射操作，第二显示操作可包括第二初始数据写入操作、第二复位操作、第二阈值电压补偿操作、第二数据写入操作和第二发射操作，多个像素电路的每个像素电路可被配置为同时执行第一发射操作和第二初始数据写入操作，并且可被配置为同时执行第二发射操作和第一初始数据写入操作。

[0033] 第一显示操作还可包括第一偏置截止应用操作，第二显示操作还可包括第二偏置截止应用操作。

[0034] 实施方式还指向驱动像素电路的方法，该方法包括同时执行用于显示左图像的第一显示操作的第一发射操作和用于显示右图像的第二显示操作的第二初始数据写入操作；在完成第一发射操作之后顺序地执行第二显示操作的第二复位操作、第二阈值电压补偿操作和第二数据写入操作；同时执行第二显示操作的第二发射操作和第一显示操作的第一初始数据写入操作；以及在完成第二发射操作之后顺序地执行第一显示操作的第一复位操作、第一阈值电压补偿操作和第一数据写入操作。

[0035] 该方法还可包括在第一显示操作的第一复位操作之前执行第一显示操作的第一偏置截止应用操作；以及在第二显示操作的第二复位操作之前执行第二显示操作的第二偏置截止操作。

[0036] 根据本实用新型实施方式的像素电路可以高速工作，并且可降低功耗和/或基于相同的功耗提高亮度。

## 附图说明

[0037] 通过结合附图详细描述示例性实施方式，对本领域技术人员而言特征将变得显而易见，在附图中：

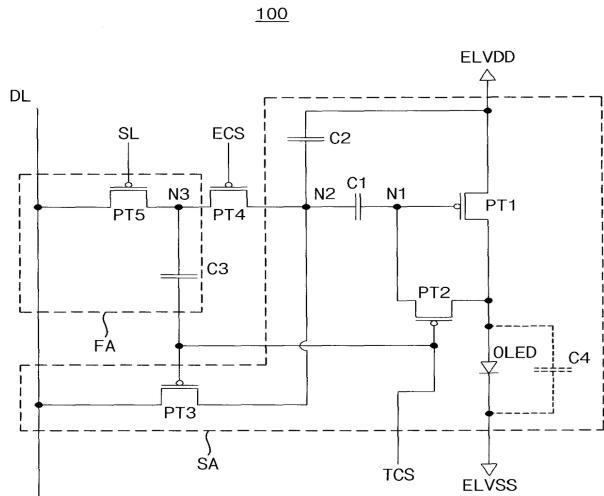

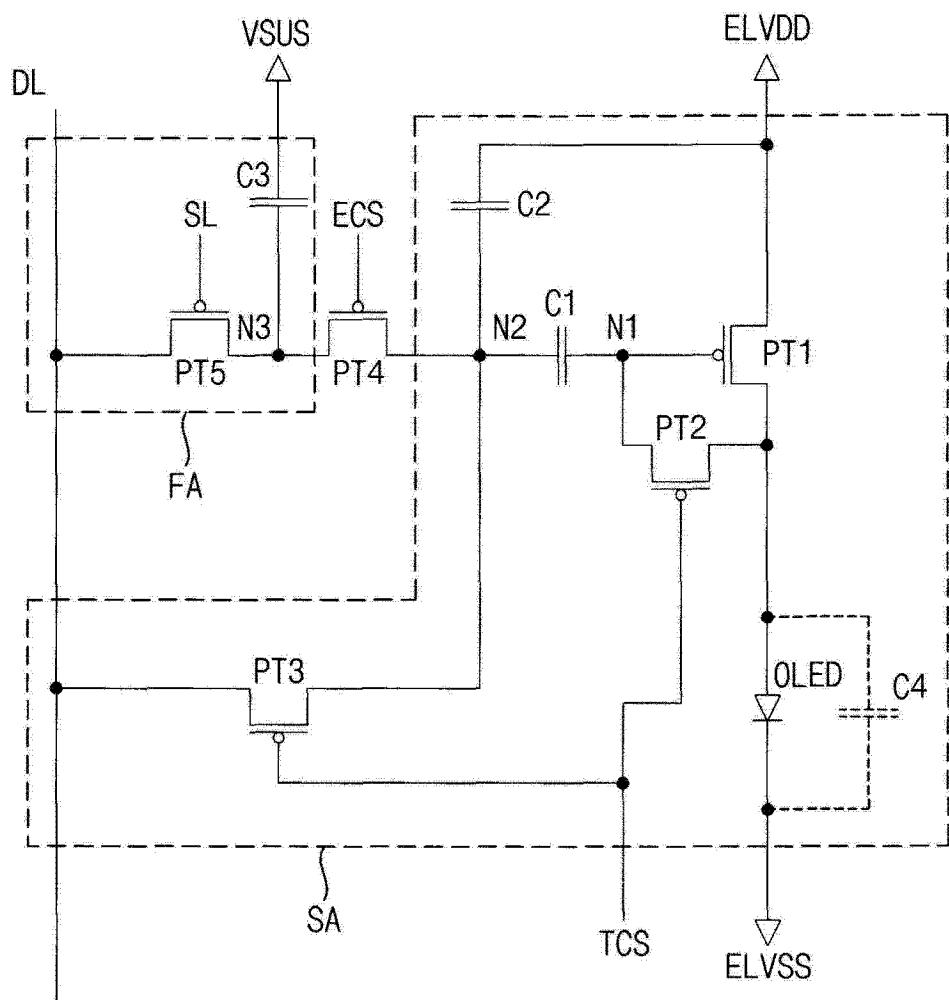

[0038] 图1示出了根据示例性实施方式的像素电路的电路图；

[0039] 图2示出了有机发光显示装置基于同时发射方法实现立体图像的实施例的图示；

[0040] 图3示出了具有图1的像素电路的有机发光显示装置实现立体图像的实施例的图示；

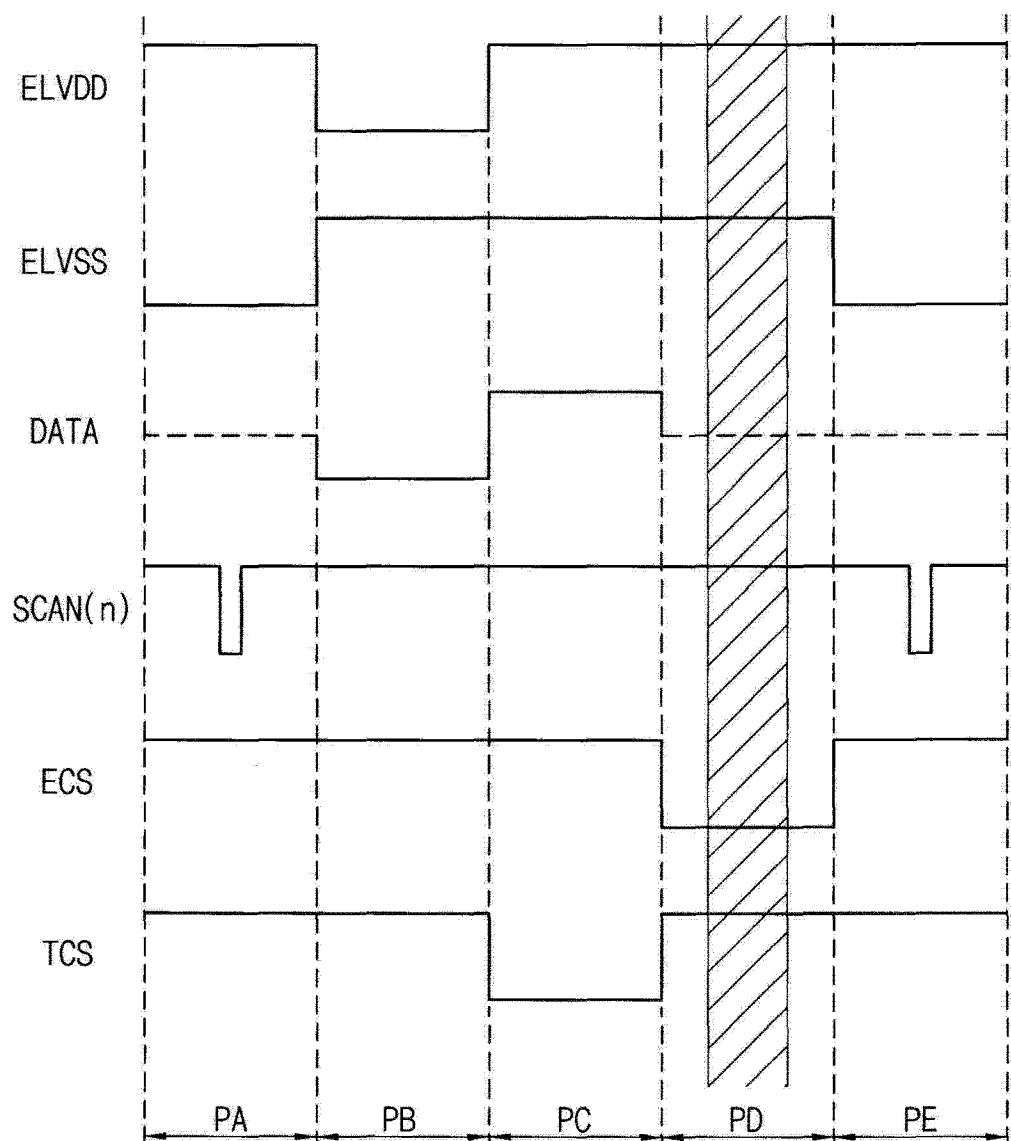

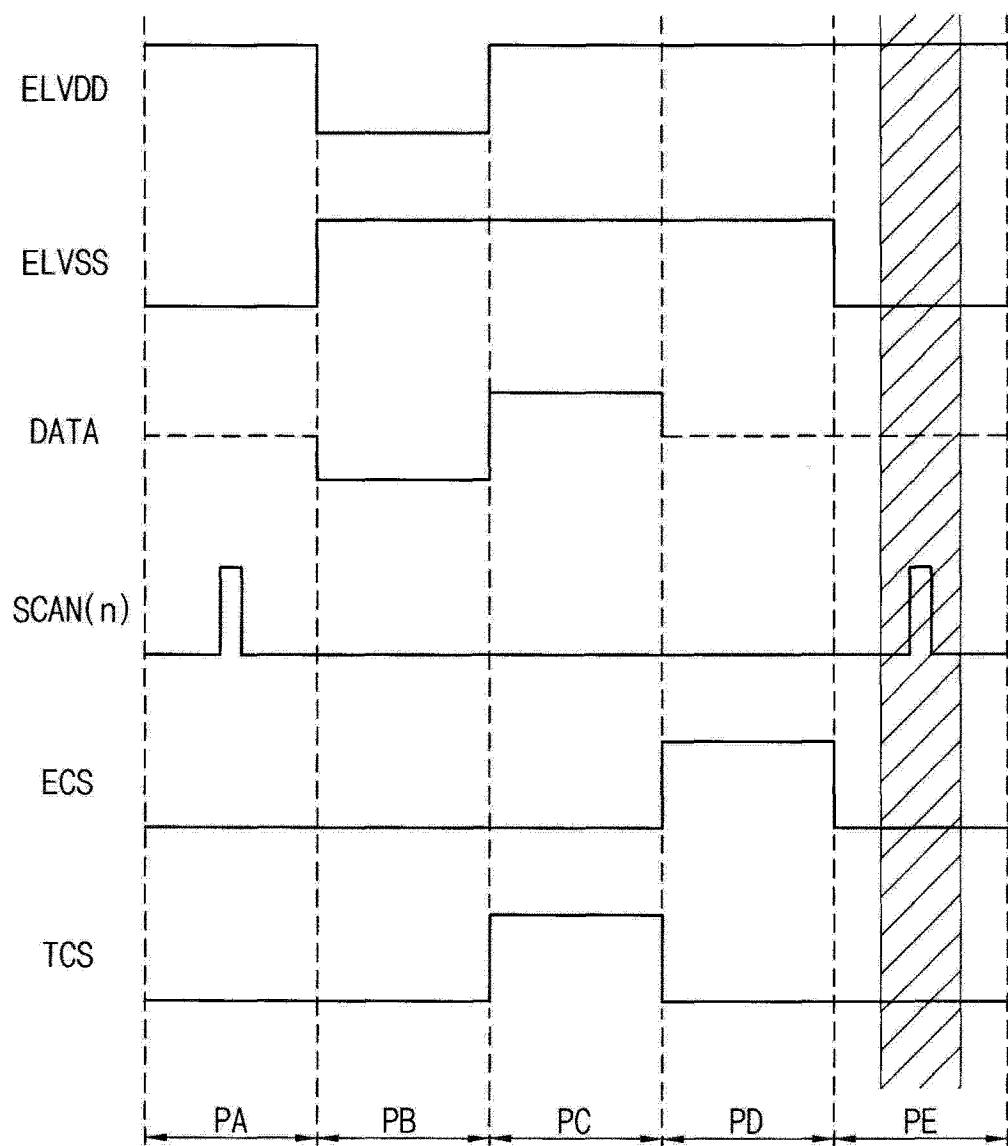

- [0041] 图 4A 至图 4E 示出了图 1 的像素电路的示例性操作的时序图；

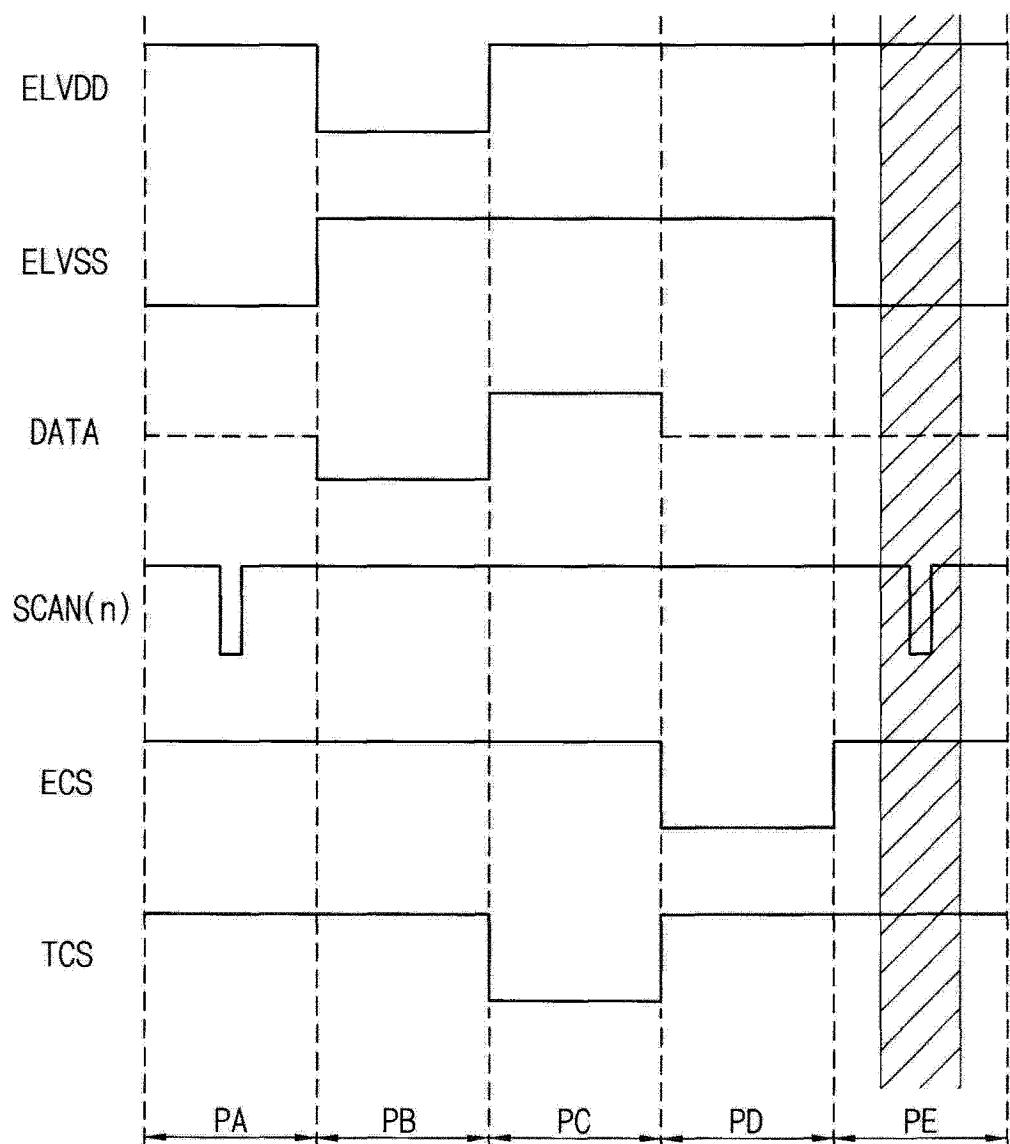

- [0042] 图 5 示出了图 1 的像素电路的另一示例性操作的时序图；

- [0043] 图 6 示出了根据示例性实施方式的像素电路的电路图；

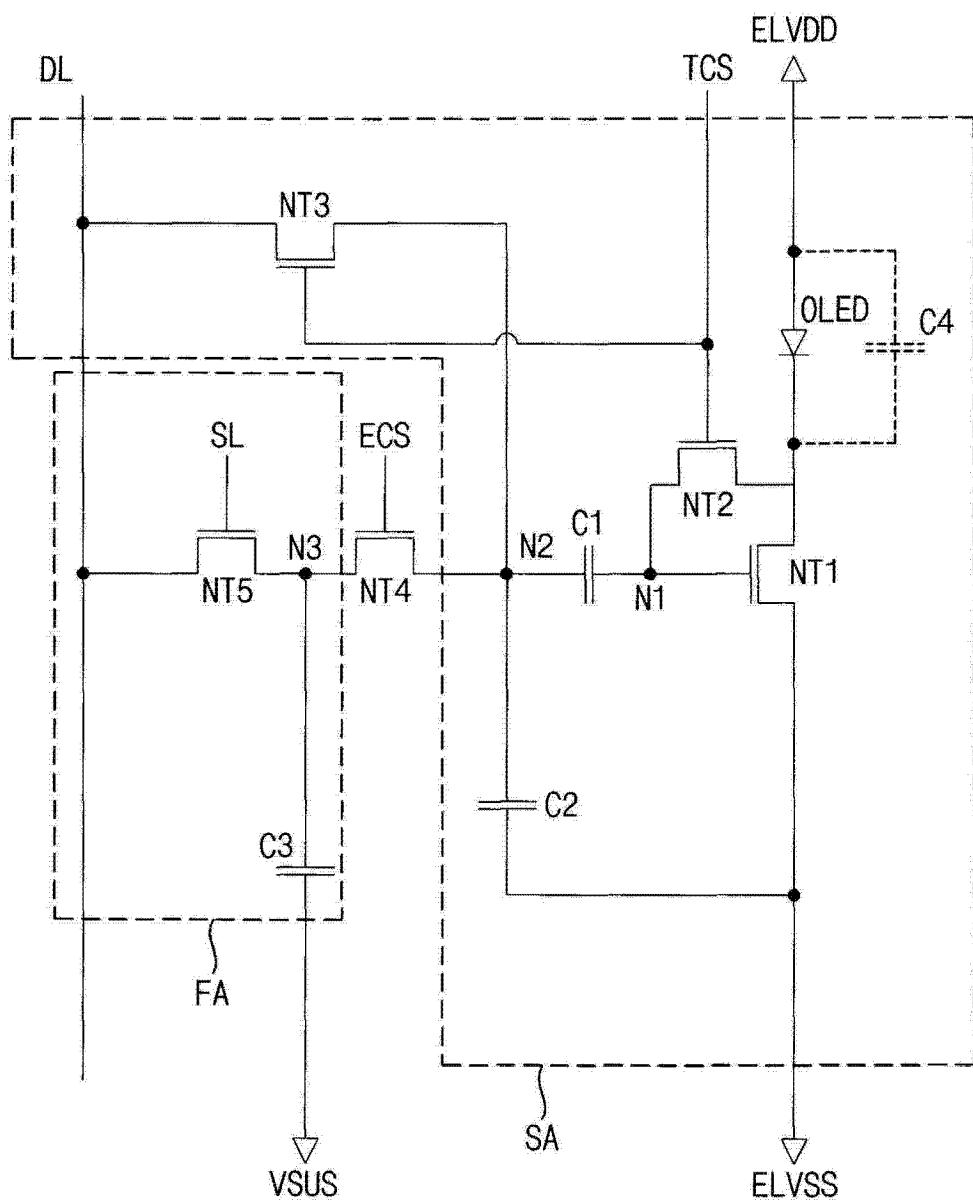

- [0044] 图 7 示出了根据示例性实施方式的像素电路的电路图；

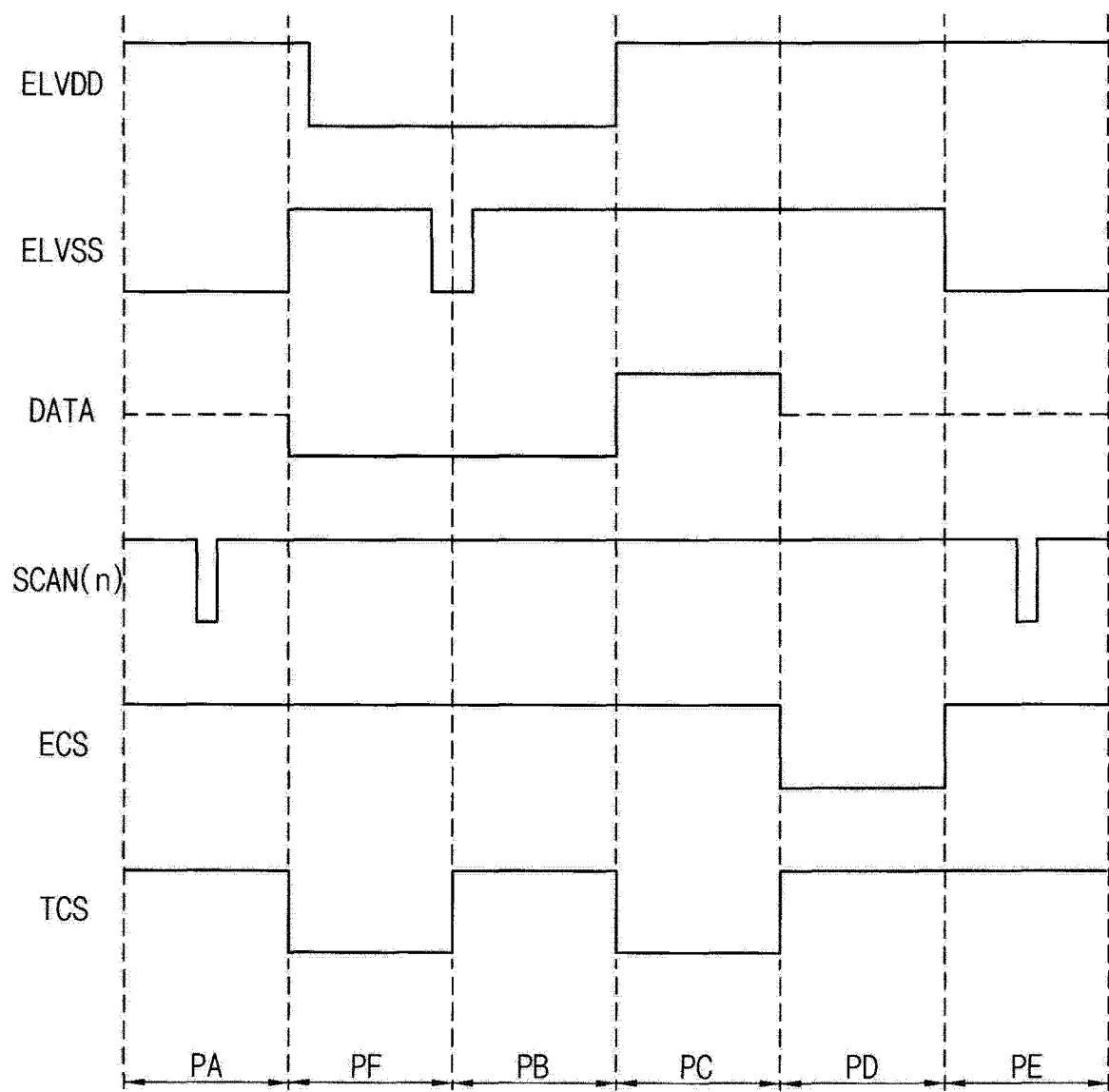

- [0045] 图 8A 至图 8E 是图 7 的像素电路的示例性操作的时序图；

- [0046] 图 9 示出了根据示例性实施方式的像素电路的电路图；

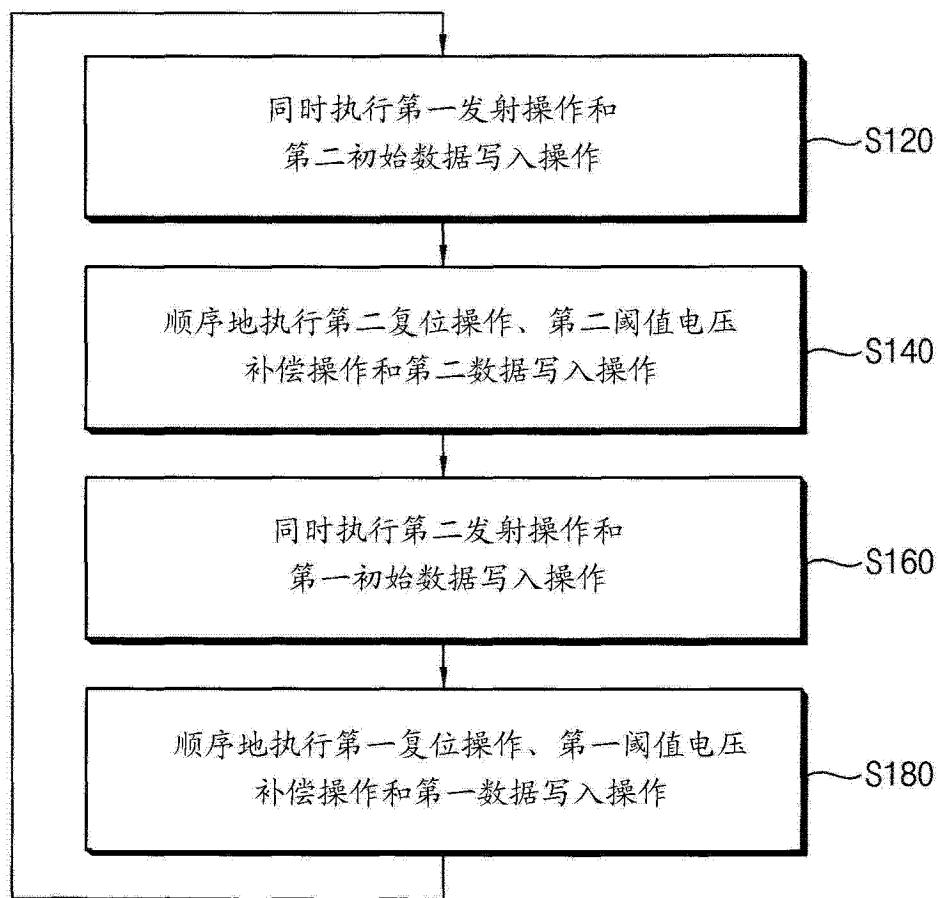

- [0047] 图 10 示出了根据示例性实施方式的驱动像素电路的方法的流程图；

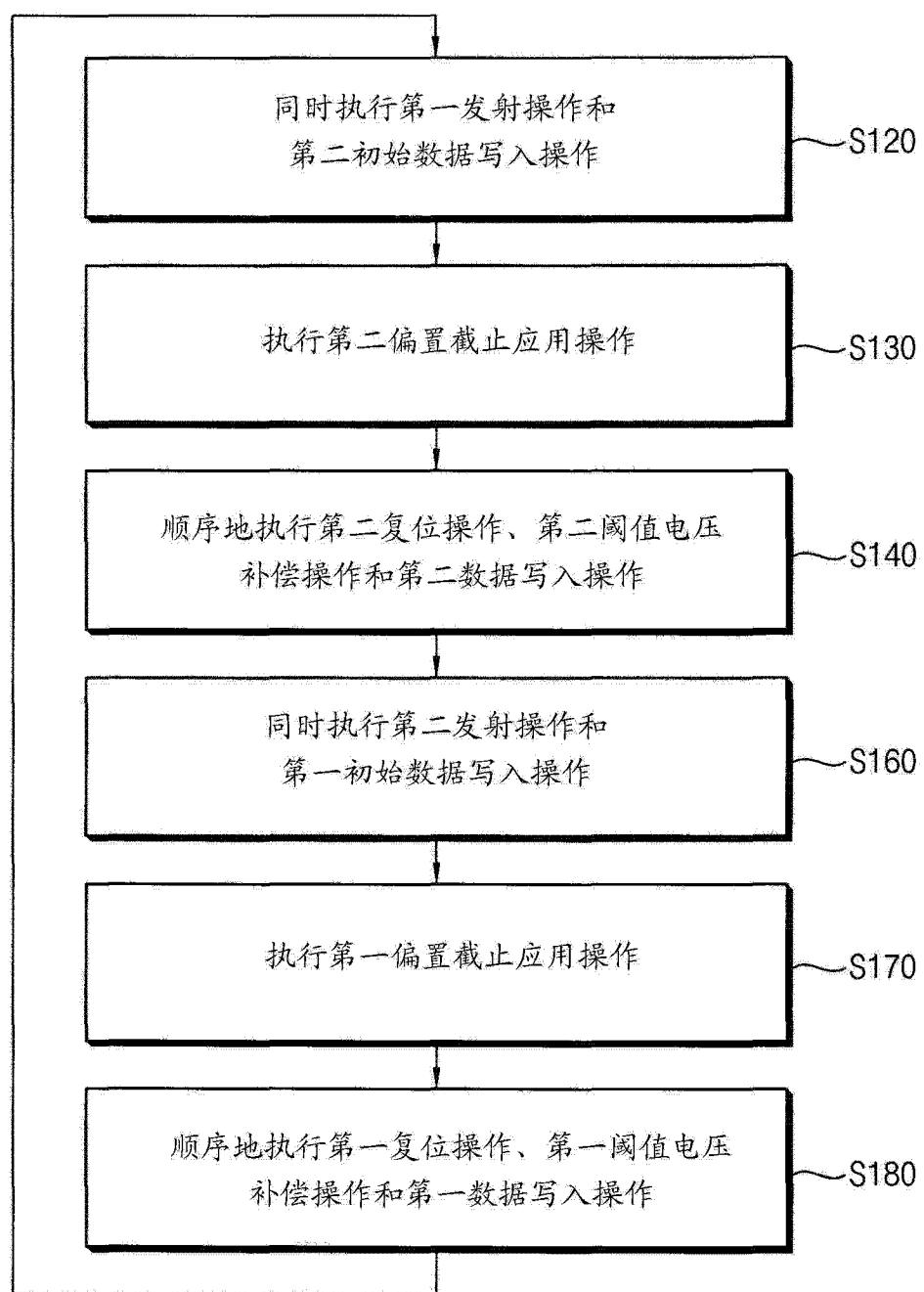

- [0048] 图 11 示出了根据示例性实施方式的驱动像素电路的方法的流程图；

- [0049] 图 12 示出根据示例性实施方式的有机发光显示装置的框图；

- [0050] 图 13 示出了采用快门眼镜方法的立体图像显示系统的图示，其中立体图像显示系统包括图 12 的有机发光显示装置；

- [0051] 图 14 示出了采用视差屏障方法的立体图像显示系统的图示，其中立体图像显示系统包括图 12 的有机发光显示装置；以及

- [0052] 图 15 示出了具有图 12 的有机发光显示装置的电气装置的框图。

### 具体实施方式

[0053] 在下文中将参照附图更充分地描述示例性实施方式，然而，它们可用各种不同形式来体现，并且不应该解释为受在此提出的实施方式的限制。更正确地讲，提供这些实施方案的目的是为了使本文公开的内容是充分和完全的，并且向本领域的普通技术人员完全地传递本实用新型的保护范围。

[0054] 在附图中，为了清楚的目的，层和区域的尺寸可能被夸大。全文中相似的参考标号指示相似的元件。

[0055] 应该理解，尽管在此可能使用术语第一、第二、第三等描述各种元件，但是这些元件不应受到这些术语的限制。上述术语仅仅是被用来使一个元件区别于另一个元件。因此，在下面将讨论的第一元件可以被称为第二元件，而不会背离本发明的教导。如本文所使用的，术语“和 / 或”包括一个或多个列出的关联项的任意和全部组合。

[0056] 应该理解，当提到一个元件“连接(connected)”或“耦接(coupled)”至另一个元件时，它可直接连接或耦接至另一个元件或可能存在中间元件。反之，当提到一个元件“直接连接”或“直接耦接”至另一个元件时，不存在中间元件。用于描述元件之间关系的其它词语应该按类似的方式解释(例如“位于…之间”与“直接位于…之间”，“相邻”与“直接相邻”等)。

[0057] 在此使用的术语仅仅是为了描述具体示例性实施方式的目的，并不是限制本发明概念。如本文所使用的，单数形式“一”和“该”应该还包括复数的含义，除非对该内容做了明确的相反表示。还应该理解术语“包括(comprises)”和 / 或“包括(including)”在本说明书中使用时明确说明了所述的特征、整体、步骤、操作、元件和 / 或组件的存在，但是并不排除一个或多个其它特征、整体、步骤、操作、元件、组件和 / 或它们的组合的存在或添加。

[0058] 除非有相反的限定，在此使用的全部术语(包括技术术语和科学术语)与本领域普通技术人员通常所理解的意思相同。还应该理解，诸如在公共使用的字典中定义的术语应该被解释为具有与它们在相关技术领域的上下文中具有的意思一致，并且不能以理想化或

过于字面化的意义解释,除非在本文明确地如此的定义。

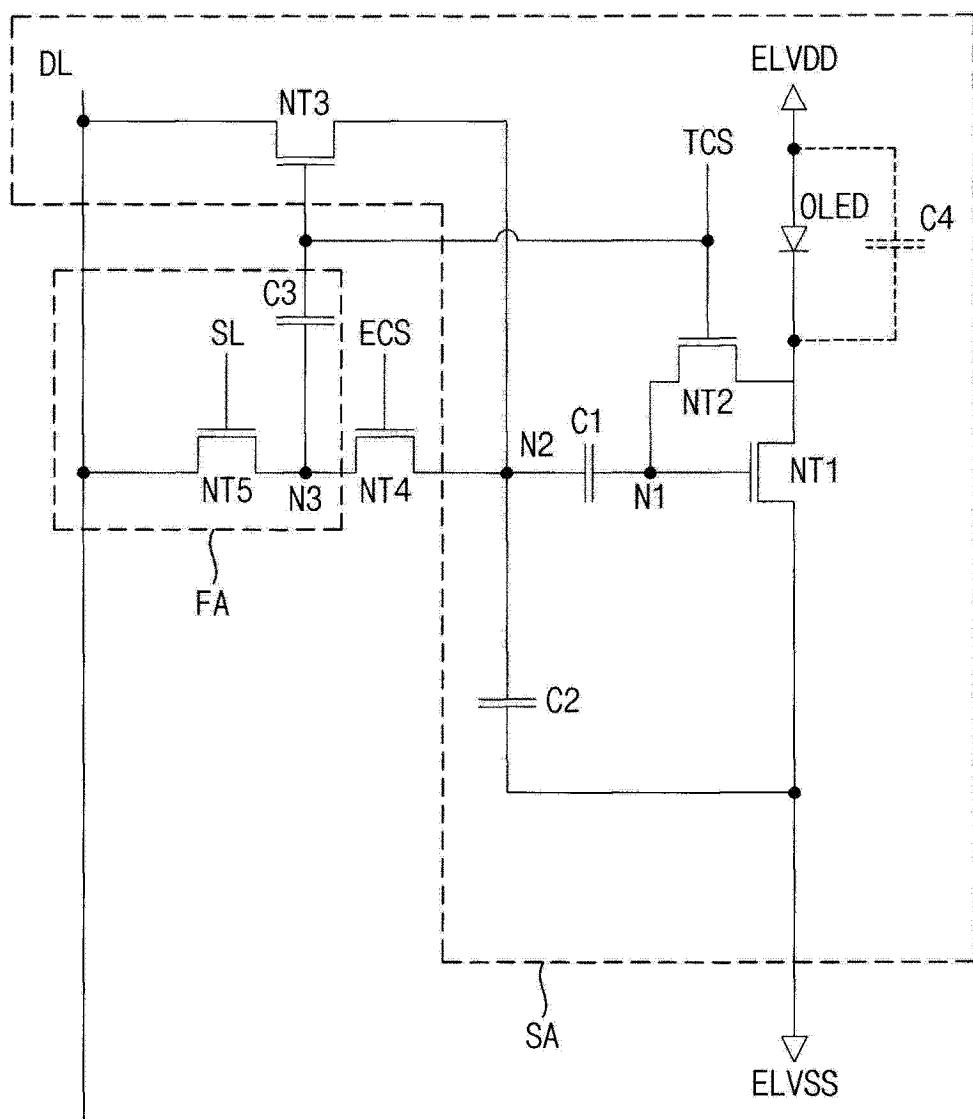

[0059] 图1示出了根据示例性实施方式的像素电路的电路图。

[0060] 参照图1,像素电路100可包括有机发光二极管OLED、第一至第五p沟道金属氧化物半导体(PMOS)晶体管PT1至PT5、以及第一至第三电容器C1至C3。像素电路100可具有5T-3C结构(即,具有5个晶体管和3个电容器的结构)。在示例性实施方式中,像素电路100还可包括第四电容器C4,第四电容器C4连接在有机发光二极管OLED的阳极与阴极之间。第四电容器C4可以是辅助电容器。

[0061] 有机发光二极管OLED可连接在第二电源电压ELVSS与第一PMOS晶体管PT1之间。详细地,有机发光二极管OLED的阴极可连接至第二电源电压ELVSS,并且有机发光二极管OLED的阳极可连接至第一PMOS晶体管PT1的第一端。有机发光二极管OLED可基于受第一PMOS晶体管PT1控制的电流发光。第一PMOS晶体管PT1可连接在第一电源电压ELVDD与有机发光二极管OLED的阳极之间。第一PMOS晶体管PT1的栅端可连接至第一节点N1。第一PMOS晶体管PT1可以是控制流过有机发光二极管OLED的电流的驱动晶体管。如图1所示,在第一节点N1处,第一电容器C1的第一端、第二PMOS晶体管PT2的第一端和第一PMOS晶体管PT1的栅端互相连接。第二PMOS晶体管PT2可连接在第一节点N1与有机发光二极管OLED的阳极之间。第二PMOS晶体管PT2的栅端可接收补偿控制信号TCS。详细地,第二PMOS晶体管PT2的第一端可连接至第一节点N1,并且第二PMOS晶体管PT2的第二端可连接至第一PMOS晶体管PT1的第一端。因此,当第二PMOS晶体管PT2响应于补偿控制信号TCS而导通时,第一PMOS晶体管PT1可为二极管接法(diode-coupled)。

[0062] 第一电容器C1可连接在第一节点N1与第二节点N2之间。详细地,第一电容器C1的第一端可连接至第一节点N1,并且第一电容器C1的第二端可连接至第二节点N2。第一电容器C1可以是阈值电压补偿电容器。如图1所示,在第二节点N2处,第一电容器C1的第二端、第二电容器C2的第一端、第三PMOS晶体管PT3的第一端以及第四PMOS晶体管PT4的第一端互相连接。第二电容器C2可连接在第一电源电压ELVDD与第二节点N2之间。第二电容器C2可以是存储电容器。详细地,第二电容器C2的第一端可连接至第二节点N2,并且第二电容器C2的第二端可连接至第一电源电压ELVDD。第三PMOS晶体管PT3可连接在数据线DL与第二节点N2之间。第三PMOS晶体管PT3的栅端可接收补偿控制信号TCS。详细地,第三PMOS晶体管PT3的第一端可连接至第二节点N2,第三PMOS晶体管PT3的第二端可连接至数据线DL,并且第三PMOS晶体管PT3的栅端可连接至第二PMOS晶体管PT2的栅端。第四PMOS晶体管PT4可连接在第三节点N3与第二节点N2之间。第四PMOS晶体管PT4的栅端可接收发射控制信号ECS。详细地,第四PMOS晶体管PT4的第一端可连接至第二节点N2,并且第四PMOS晶体管PT4的第二端可连接至第三节点N3。如图1所示,在第三节点N3处,第四PMOS晶体管PT4的第二端、第五PMOS晶体管PT5的第一端和第三电容器C3的第一端互相连接。

[0063] 第三电容器C3可连接在第三节点N3与第三PMOS晶体管PT3的栅端之间。详细地,第三电容器C3的第一端可连接至第三节点N3,并且第三电容器C3的第二端可连接至第三PMOS晶体管PT3的栅端。第五PMOS晶体管PT5可连接在数据线DL与第三节点N3之间。第五PMOS晶体管PT5的栅端可连接至扫描线SL。详细地,第五PMOS晶体管PT5的第一端可连接至第三节点N3,第五PMOS晶体管PT5的第二端可连接至数据线,并且第五PMOS

晶体管 PT5 的栅端可连接至扫描线 SL。数据线 DL 可连接至有机发光显示装置的数据驱动单元以提供数据信号(例如左图像数据或右图像数据)。此外,扫描线 SL 可连接至有机发光显示装置的扫描驱动单元以提供扫描信号。如上所述,像素电路 100 可具有包括有机发光二极管 OLED、第一至第五 PMOS 晶体管 PT1 至 PT5、以及第一至第三电容器 C1 至 C3 的 5T-3C 结构。具有像素电路 100 的有机发光显示装置可通过基于同时发射方法交替地显示左图像和右图像来实现立体图像。例如,在左图像由有机发光显示装置的各个像素电路 100 同时显示的时候,右图像数据可被顺序地写入有机发光显示装置的各个像素电路 100。类似地,在右 图像由有机发光显示装置的各个像素电路 100 同时显示的时候,左图像可被顺序地写入有机发光显示装置的各个像素电路 100。

[0064] 如图 1 所示,像素电路 100 可包括第一区 FA 和第二区 SA。在下面的描述中,第一区 FA 包括第三电容器 C3 和第五 PMOS 晶体管 PT5,第二区 SA 包括第一和第二电容器 C1 和 C2 以及第一至第三 PMOS 晶体管 PT1 至 PT3。当第四晶体管 PT4 导通时,第一区 FA 可连接至第二区 SA。当第四 PMOS 晶体管 PT4 截止时,第一区 FA 可与第二区 SA 分离。详细地,当第四 PMOS 晶体管 PT4 导通时,在像素电路 100 中第一区 FA 可连接至第二区 FA。结果,存储在第三电容器 C3 中的数据信号(例如,左图像数据或右图像数据)可转移至第二区 SA。另一方面,当第四 PMOS 晶体管 PT4 截止时,在像素电路 100 中第一区 FA 可与第二区 SA 分离。结果,第一区 FA 和第二区 SA 可执行各自的操作。详细地,可在第二区 SA 中执行发射操作,而在第一区 FA 中执行初始数据写入操作。因此,第一区 FA 的操作可独立于第二区 SA 的操作。例如,当第四 PMOS 晶体管 PT4 响应于发射控制信号 ECS 而截止时,可通过第一和第二 PMOS 晶体管 PT1 和 PT2、第一和第二电容器 C1 和 C2、以及有机发光二极管 OLED (即,第二区 SA 的操作) 显示第一图像(例如,左图像或右图像)。与此同时,当第五 PMOS 晶体管 PT5 响应于通过扫描线 SL 的扫描信号而导通时,可通过数据线 DL 将第二图像数据(例如,右图像数据或左图像数据)存储在第三电容器 C3 中(即,第一区 FA 的操作)。在下文中将详细描述像素电路 100 的操作。

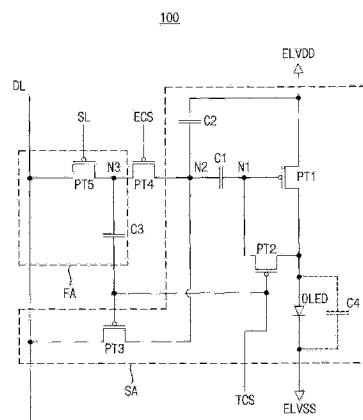

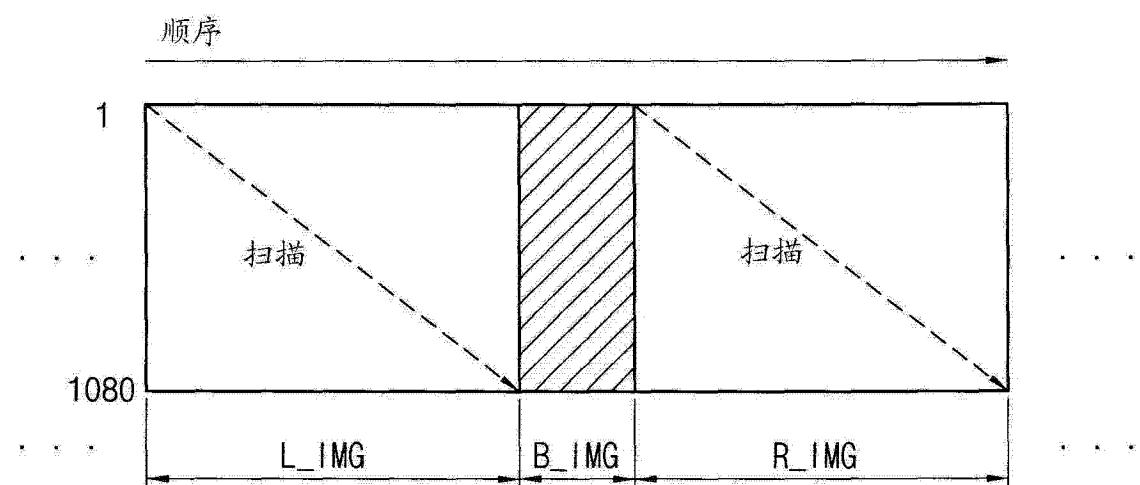

[0065] 图 2 示出了有机发光显示装置基于同时发射方法实现立体图像的实施例的图示。

[0066] 图 2 示出了如何通过基于同时发射方法交替地显示左图像 L\_IMG 和右图像 R\_IMG 来实现立体图像。详细地,可通过分别向左眼和右眼提供左图像 L\_IMG 和右图像 R\_IMG 来实现立体图像。例如,在快门眼镜方法中,可通过在显示左图像 L\_IMG 的时候打开快门眼镜的左快门以及在显示右图像 R\_IMG 的时候打开快门眼镜的右快门来实现立体图像。这里,这些操作可非常快速地执行(例如,重复)以防止观 看者注意到操作之间的时间差。观看者通过顺序地观看左图像 L\_IMG 和右图像 R\_IMG 来看到立体图像。

[0067] 比较起来,对于顺序发射方法,当顺序地显示左图像 L\_IMG 和右图像 R\_IMG 时在左图像 L\_IMG 与右图像 R\_IMG 之间插入黑图像 B\_IMG。黑图像 B\_IMG 被插入以分离右图像 R\_IMG 与左图像 L\_IMG。结果,由于黑图像 B\_IMG,亮度可能降低且功耗可能增加。

[0068] 如图 2 所示,根据一个实施方式的具有图 1 的像素电路 100 的有机发光显示装置可基于同时发射方法显示左图像 L\_IMG 和右图像 R\_IMG。结果,可减少或消除在左图像 L\_IMG 与右图像 R\_IMG 之间显示黑图像 B\_IMG 的时间。此外,图 1 的像素电路 100 具有可通过第四 PMOS 晶体管 PT4 分离的第一区 FA 和第二区 SA 的结构。因此,具有图 1 像素电路 100 的有机发光显示装置可在执行左图像 L\_IMG 的发射操作的时候将右图像数据写入图 1 的像

素电路 100，并且可在执行右图像 R\_IMG 的发射操作的时候将左图像数据写入图 1 的像素电路 100。结果，具有图 1 的像素电路 100 的有机发光显示装置可以高速工作，因此可允许降低具有图 1 的像素电路的有机发光显示装置的工作频率。

[0069] 如上所述，实施方式可通过减少或消除在具有图 1 的像素电路 100 的有机发光显示装置中显示黑图像 B\_IMG 的时间来提高亮度。此外，可在执行左图像 L\_IMG 的发射操作的时候存储右图像数据，并且在执行右图像 R\_IMG 的发射操作的时候存储左图像数据，因此可提高具有图 1 的像素电路 100 的有机发光显示装置的工作速度。

[0070] 顺序地重复(即，显示)60Hz 的左图像 L\_IMG、60Hz 的黑图像 B\_IMG、60Hz 的右图像 R\_IMG 和 60Hz 的黑图像 B\_IMG 的普通有机发光显示装置可使用 240Hz 的工作速度来实现立体图像。相比之下，具有图 1 的像素电路 100 的有机发光显示装置可顺序地重复(即，显示)60Hz 的左图像 L\_IMG 和 60Hz 的右图像 R\_IMG，因此可使用 120Hz 的工作速度来实现立体图像。而且，具有图 1 的像素电路 100 的有机发光显示装置可获得比普通有机发光显示装置大两倍的数据变化时间，可增加寿命(例如，通过将峰值电流减半)，并且可将功耗减半(例如，通过提高亮度)。

[0071] 图 1 的像素电路 100 可顺序地执行初始数据写入操作、复位操作、阈值电压补偿操作、数据写入操作和发射操作以基于同时发射方法显示左图像 L\_IMG 或右图像 R\_IMG (即，一帧)。有机发光显示装置的全部像素电路 100 (通过各个扫描线) 可顺序地执行初始数据写入操作，而有机发光显示装置的全部像素电路 100 可同时执行重置操作、阈值电压补偿操作、数据写入操作和 / 或发射操作。

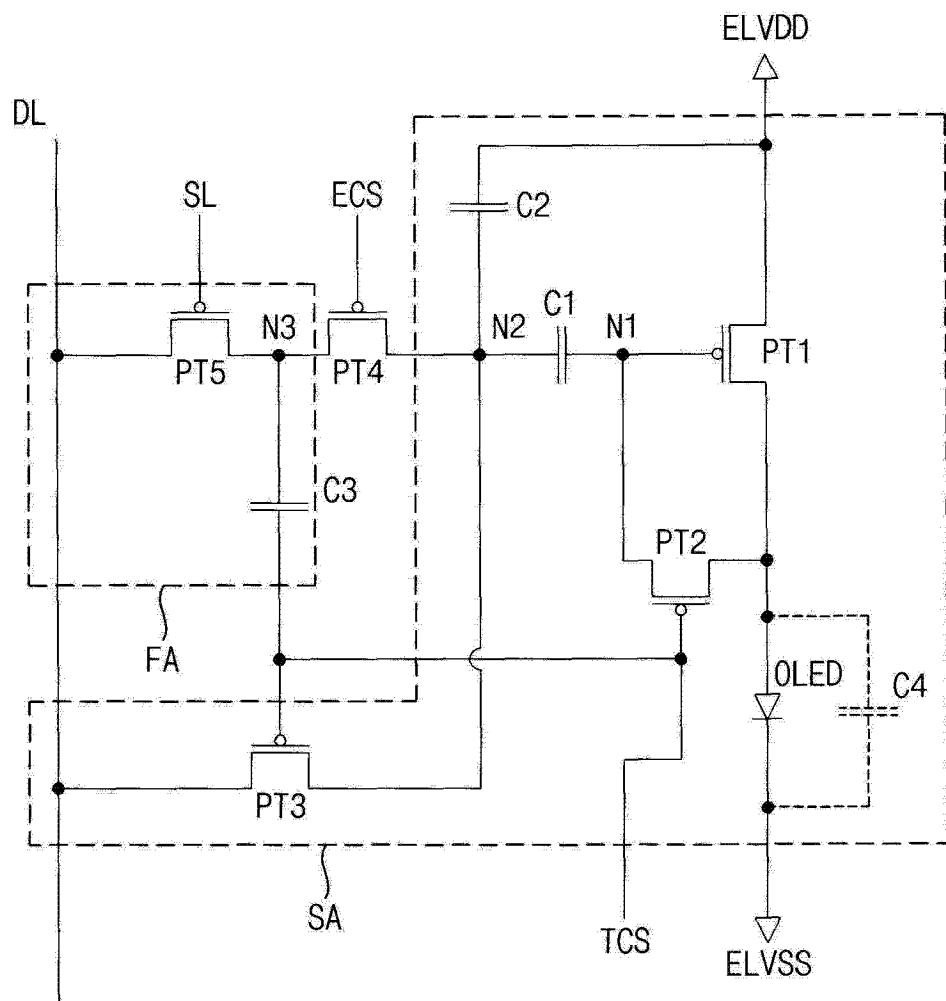

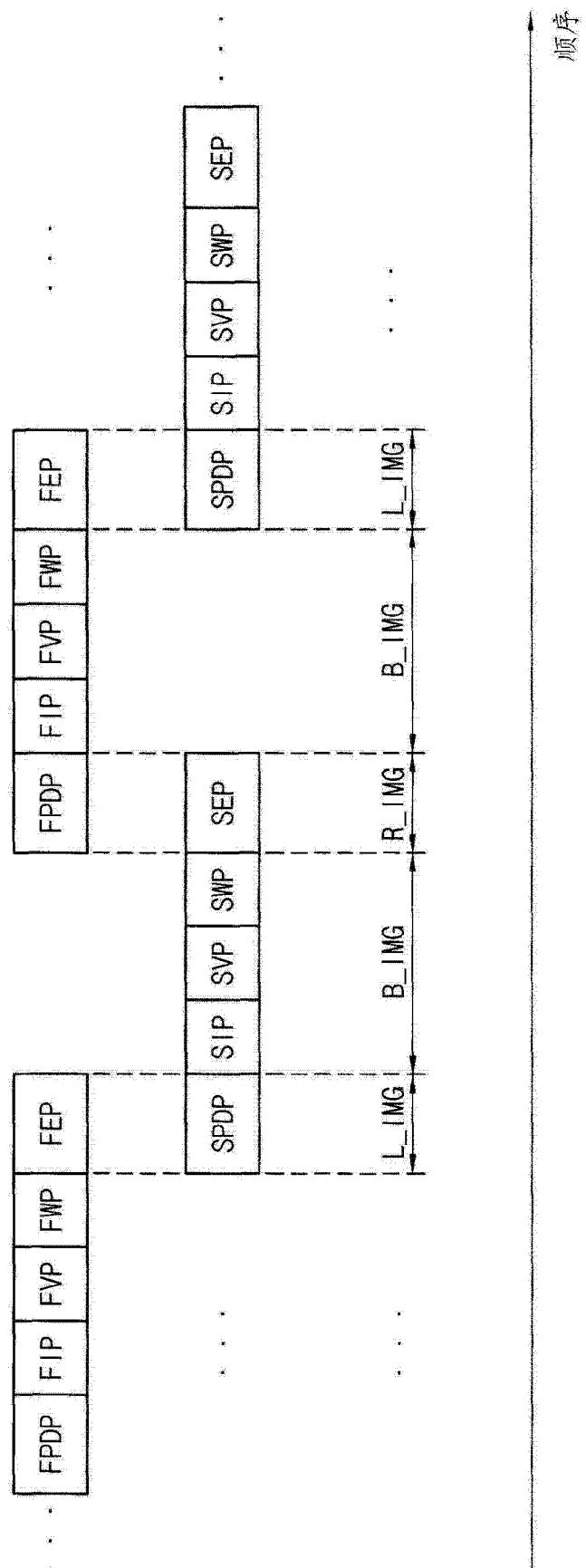

[0072] 图 3 示出了具有图 1 的像素电路的有机发光显示装置实现立体图像的实施例的图示。

[0073] 图 3 示出了如何通过交替地执行用于显示第一图像(例如，左图像 L\_IMG)的第一显示操作和用于显示第二图像(例如，右图像 R\_IMG)的第二显示操作来实现立体图像。可在图 1 的像素电路 100 中基于同时发射方法执行第一显示操作和第二显示操作。

[0074] 用于显示第一图像 L\_IMG 的第一显示操作可包括第一初始数据写入操作 FPDP、第一复位操作 FIP、第一阈值电压补偿操作 FVP、第一数据写入操作 FWP 和第一发射操作 FEP。用于显示第二图像 R\_IMG 的第二显示操作可包括第二初始数据写入操作 SPDP、第二复位操作 SIP、第二阈值电压补偿操作 SVP、第二数据写入操作 SWP 和第二发射操作 SEP。在图 1 的像素电路 100 中可同时执行第一显示操作的第一发射操作 FEP 和第二显示操作的第二初始数据写入操作 SPDP。类似地，在图 1 的像素电路 100 中可同时执行第二显示操作的第二发射操作 SEP 和第一显示操作的第一初始数据写入操作 FPDP。因此，第一显示操作的第一发射操作 FEP 可与第二显示操作的第二初始数据写入操作 SPDP 重叠，并且第二显示操作的第二发射操作 SEP 可与第一显示操作的第一初始数据写入操作 FPDP 重叠。

[0075] 如图 3 所示，观看者可顺序且重复地观看左图像 L\_IMG、黑图像 B\_IMG、右图像 R\_IMG 和黑图像 B\_IMG。这里，由于这些操作可非常快速地执行(即，重复)，观看者注意不到这些操作之间的时间差。观看者可通过顺序且重复地观看左图像 L\_IMG、黑图像 B\_IMG、右图像 R\_IMG 和黑图像 B\_IMG，看到立体图像。为了方便描述，显示 黑图像 B\_IMG 的时间在图 3 中被显示为相对长。但是，实践中显示黑图像 B\_IMG 的时间可以远短于显示左图像 L\_IMG 的时间和显示右图像 R\_IMG 的时间，因为用于显示左图像 L\_IMG 的第一显示操作和用于显

示右图像 R\_IMG 的第二显示操作可基于同时发射方法执行。结果,具有图 1 的像素电路 100 的有机发光显示装置可提高亮度,并且可降低工作频率。在下文中,将参照图 4A 至图 4E 详细描述图 1 的像素电路 100 的操作。

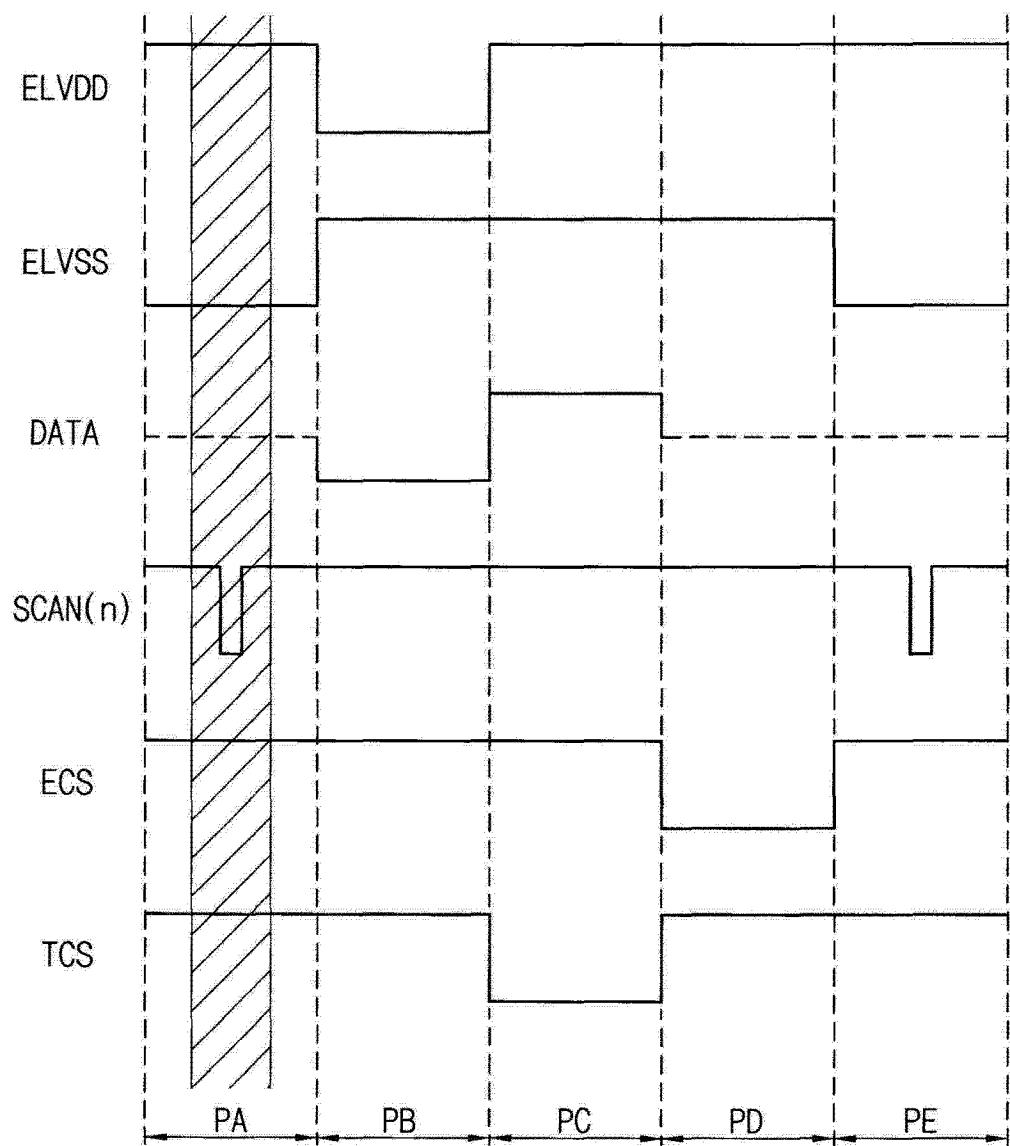

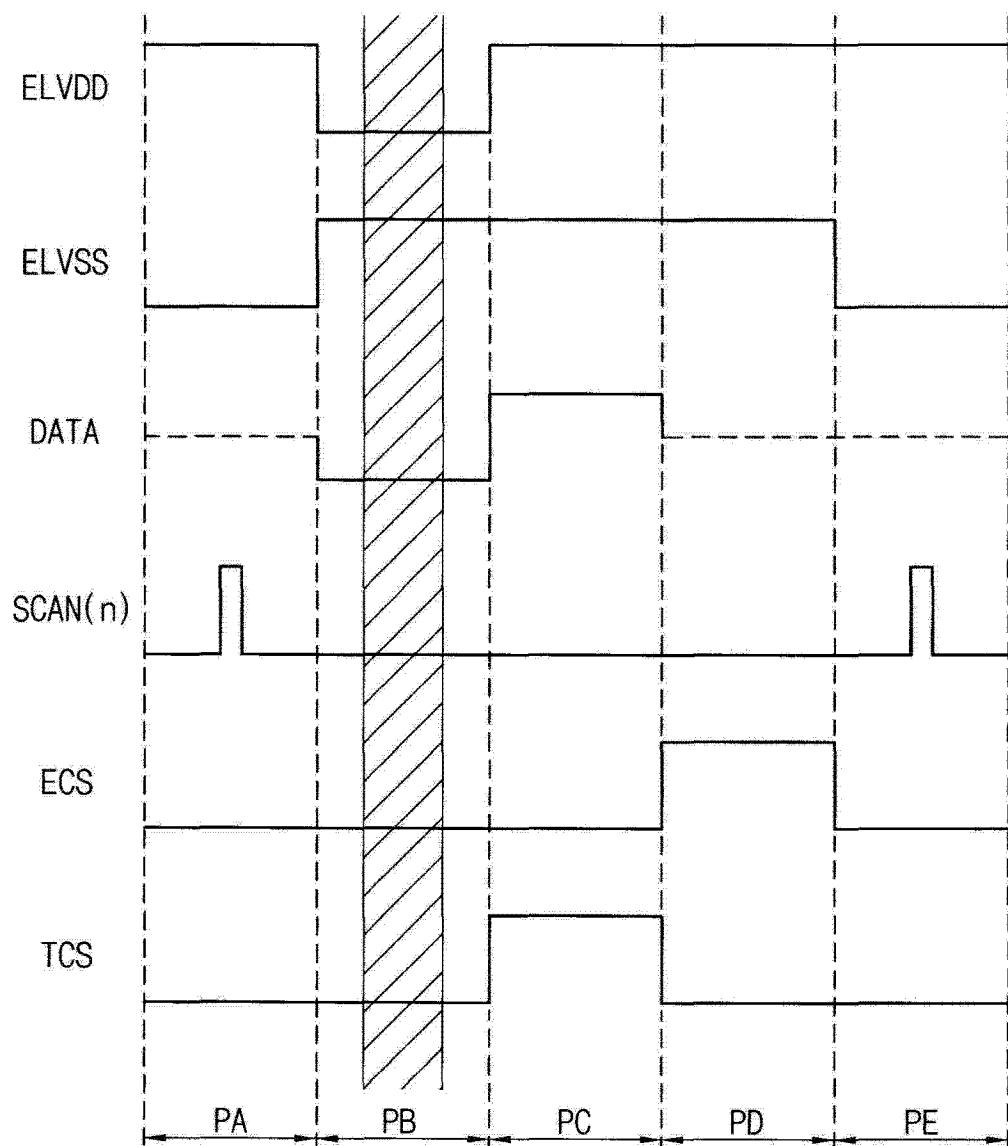

[0076] 图 4A 至图 4E 示出了图 1 的像素电路的示例性操作的时序图。

[0077] 用于显示第一图像(例如,左图像)的第一显示操作可包括第一初始数据写入操作 FPDP、第一复位操作 FIP、第一阈值电压补偿操作 PVP、第一数据写入操作 FWP 和第一发射操作 FEP。类似地,用于显示第二图像(例如,右图像)的第二显示操作可包括第二初始数据写入操作 SPDP、第二复位操作 SIP、第二阈值电压补偿操作 SVP、第二数据写入操作 SWP 和第二发射操作 SEP。

[0078] 为了方便描述,图 4A 至图 4E 专注于用于显示第一图像的第一显示操作。

[0079] 参照图 4A 至图 4E,第一显示操作的第一初始数据写入操作 FPDP、第一复位操作 FIP、第一阈值电压补偿操作 FVP、第一数据写入操作 FWP 和第一发射操作 FEP 可分别对应于第一初始数据写入周期 PA、第一复位周期 PB、第一阈值电压补偿周期 PC、第一数据写入周期 PD 和第一发射周期 PE(类似地,第二初始数据写入操作 SPDP、第二复位操作 SIP、第二阈值电压补偿操作 SVP、第二数据写入操作 SWP 和第二发射操作 SEP 可分别对应于第二初始数据写入周期 PA、第二复位周期 PB、第二阈值电压补偿周期 PC、第二数据写入周期 PD 和第二发射周期 PE)。第一显示操作和第二显示操作在时间上可以是分离的。因此,可将本发明概念应用于采用快门眼镜方法的立体图像显示系统、采用视差屏障的立体图像显示系统等。

[0080] 有机发光显示装置的全部像素电路 100 可通过各个扫描线 SL 顺序地执行初始数据写入操作(即,第一初始数据写入操作 FPDP 或第二初始数据写入操作 SPDP),而有机发光显示装置的全部像素电路 100 可同时执行复位操作(即,第一复位操作 FIP 或第二复位操作 SIP)、阈值电压补偿操作(即,第一阈值电压补偿操作 FVP 或第二阈值电压补偿操作 SVP)、数据写入操作(即,第一数据写入操作 FWP 或第二数据写入操作 SWP)、或发射操作(即,第一发射操作 FEP 或第二发射操作 SEP)。

[0081] 在一个示例性实施方式中,第一电源电压 ELVDD 可具有多个电压电平,第二电源电压 ELVSS 可具有固定的电压电平(例如,0V)。在这种情况下,因为第二电源电压 ELVSS 具有固定的电压电平,所以用于提供第二电源电压 ELVSS 的结构可被简化。然而,因为第一电源电压 ELVDD 具有多个电压电平(例如,可能需要负的电压电平),所以用于提供第一电源电压的结构可能是复杂的。在另一个示例性实施方式中,第一电源电压 ELVDD 可具有多个电压电平,第二电源电压 ELVSS 也可具有多个电压电平。在这种情况下,驱动信号波形可被简化。但是用于提供第一电源电压 ELVDD 的结构和用于提供第二电源电压 ELVSS 的结构可能是复杂的。在又一示例性实施方式中,第一电源电压 ELVDD 可具有固定的电压电平(例如,12V),第二电源电压可具有多个电压电平。在这种情况下,因为第一电源电压 ELVDD 具有固定的电压电平,所以用于提供第一电源电压 ELVDD 的结构可被简化。但是,因为第二电源电压 ELVSS 具有多个电压电平(例如,可能需要正的电压电平),所以用于提供第二电源电压 ELVSS 的结构可能是复杂的。因此,第一电源电压 ELVDD 和第二电源电压 ELVSS 可根据所需的条件确定。为了方便起见,在下面的描述中,第一电源电压 ELVDD 和第二电源电压 ELVSS 具有高电压电平或低电压电平。

[0082] 参照图 4A,可在第一初始数据写入周期 PA 中执行第一初始数据写入操作 FPDP。如

上所述,可同时执行用于显示第一图像的第一显示操作的第一初始数据写入操作 FPD<sub>P</sub> 和用于显示第二图像的第二显示操作的第二发射操作 SEP。因此,在第一初始数据写入周期 PA 中将第一图像数据 DATA 写入各个像素电路 100 的时候可基于存储在各个像素电路 100 中的第二图像数据显示第二图像。详细地,在第一初始数据写入周期 PA 中,第一电源电压 ELVDD 可具有高电压电平,并且第二电源电压 ELVSS 可具有逻辑低电平。此外,发射控制信号 ECS 可具有高电压电平,并且补偿控制信号 TCS 也可具有高电压电平。因此,在图 1 的像素电路 100 中第三和第四 PMOS 晶体管 PT3 和 PT4 可截止。当第四 PMOS 晶体管 PT4 截止时,在图 1 的像素电路 100 中第一区 FA 可与第二区 SA 分离,并且第一区 FA 的操作可独立于第二区 SA 的操作。结果,在第一区 FA 中,当第五 PMOS 晶体管 PT5 响应于通过扫描线 SL 施加的扫描信号而导通时,通过数据线 DL 施加的第一图像数据 DATA 可存储在第三电容器 C3 中。与此同时,在第二区 SA 中,有机发光二极管 OLED 可基于从具有高电压电平的第一电源电压 ELVDD 流向具有低电压电平的第二电源电压 ELVSS 的电流而发光。

[0083] 可将第一电源电压 ELVDD、第二电源电压 ELVSS、发射控制信号 ECS 和补偿控制信号 TCS 同时应用于有机发光显示装置的全部像素电路 100。另一方面,可将第一图像数据 DATA 顺序地应用于有机发光显示装置的全部像素电路 100 (即,当第五 PMOS 晶体管 PT5 响应于具有低电压电平的扫描信号 SCAN(n) 而导通时(见图 1))。参照图 4A,可在全部周期 PA、PB、PC、PD 和 PE 中将第一电源电压 ELVDD、第二电源电压 ELVSS、发射控制信号 ECS 和补偿控制信号 TCS 同时应用于全部像素电路 100,而可仅在第一初始数据写入周期 PA 中将第一图像数据 DATA 顺序地应用于全部像素电路 100。因此,可以为全部像素电路 100 顺序地执行第一显示操作的第一初始数据写入操作 FPD<sub>P</sub>,并且为全部像素电路 100 同时执行第二显示操作的第二发射操作 SEP。

[0084] 如上所述,在具有图 1 的像素电路 100 的有机发光显示装置中,当第二图像(即,右图像或左图像)通过各个像素电路 100 显示的时候,第一图像数据 DATA (即,左图像数据或右图像数据)可存储在各个像素电路 100 的第三电容 C3 中。类似地,当第一图像(即,左图像或右图像)通过各个像素电路 100 显示的时候,第二图像数据 DATA (即,右图像数据或左图像数据)可存储在各个像素电路 100 的第三电容 C3 中。

[0085] 参照图 4B,可在第一复位周期 PB 中执行第一复位操作 FIP。详细地,在第一复位周期 PB 中,第一电源电压 ELVDD 可具有低电压电平,并且第二电源电压 ELVSS 可具有高电压电平。此外,发射控制信号 ECS 可具有高电压电平,并且补偿控制信号 TCS 也可具有高电压电平。因此,在图 1 的像素电路 100 中第三和第四 PMOS 晶体管 PT3 和 PT4 可截止。当第四 PMOS 晶体管 PT4 截止时,在图 1 的像素电路 100 中第一区 FA 可与第二区 SA 分离,并且第一区 FA 的操作可独立于第二区 SA 的操作。第二电源电压 ELVSS 高于第一电源电压 ELVDD。因此,可在第二区 SA 中执行第一复位操作 FIP,并且可将有机发光二极管 OLED 的阳极初始化为具有第二电源电压 ELVSS,从而可在第一复位周期 PB 中初始化和复位图 1 的像素电路 100。可将第一电源电压 ELVDD、第二电源电压 ELVSS、发射控制信号 ECS 和补偿控制信号 TCS 同时应用至有机发光显示装置的全部像素电路 100。因此,参照图 4B,可为有机发光显示装置的全部像素电路 100 同时执行第一显示操作的第一复位操作 FIP。

[0086] 参照图 4C,可在第一阈值电压补偿周期 PC 中执行第一阈值电压补偿操作 FVP。详细地,在第一阈值电压补偿周期 PC 中,第一电源电压 ELVDD 可具有高电压电平,并且第二电

源电压 ELVSS 也可具有高电压电平。此外,发射控制信号 ECS 可具有高电压电平,补偿控制信号 TCS 可具有低电压电平。因此,在图 1 的像素电路 100 中,第二和第三 PMOS 晶体管 PT2 和 PT3 可导通,并且第四和第五 PMOS 晶体管 PT4 和 PT5 可截止。当第四 PMOS 晶体管 PT4 截止时,在图 1 的像素电路 100 中第一区 FA 可与第二区 SA 分离,并且第一区 FA 的操作可独立于第二区 SA 的操作。结果,第一 PMOS 晶体管 PT1 的栅端可具有电压  $ELVDD - V_{th}$ (通过从第一电源电压  $ELVDD$  减去第一 PMOS 晶体管 PT1 的阈值电压  $V_{th}$  产生的)。此外,可将第一电压  $V_0$ (即,特定的高电压)存储在第二电容器 C2 中。可将第一电源电压  $ELVDD$ 、第二电源电压  $ELVSS$ 、发射控制信号 ECS 和补偿控制信号 TCS 同时应用至有机发光显示装置的全部像素电路 100。因此,可为有机发光显示装置的全部像素电路 100 同时执行第一显示操作的第一阈值电压补偿操作 FVP。

[0087] 参照图 4D,可在第一数据写入周期 PD 中执行第一数据写入操作 FWP。详细地,在第一数据写入周期 PD 中,第一电源电压  $ELVDD$  可具有高电压电平,并且第二电源电压  $ELVSS$  也可具有高电压电平。此外,发射控制信号 ECS 可具有低电压电平,并且补偿控制信号 TCS 可具有高电压电平。因此,在图 1 的像素电路中,第四和第五 PMOS 晶体管 PT4 和 PT5 可导通,并且第二和第三 PMOS 晶体管 PT2 和 PT3 可截止。当第四 PMOS 晶体管 PT4 导通时,在图 1 的像素电路 100 中第一区 FA 可连接至第二区 SA,以及当第一区 FA 连接至第二区 SA 时,可将通过第一初始数据写入操作 FPDP 存储在第三存储器 C3 中的第一图像数据转移至第二区 SA。结果,可通过第一图像数据 DATA 改变第一 PMOS 晶体管 PT1 的栅端(即,第一节点 N1)的电压。详细地,当将第一图像数据 DATA 提供至第二区 SA 时,可根据下面的 [ 等式 1] 和 [ 等式 2] 确定第一 PMOS 晶体管 PT1 的栅端(即,节点 N1)的电压。

[0088] [ 等式 1]

$$[0089] V_{eff} = \frac{C_{HOLD}V_{DATA}(C_{ST} + C_{VTH}) \times V_0}{C_{HOLD} + C_{ST} + C_{VTH}}$$

[0090] (其中,  $V_{eff}$  表示与有效数据对应的电压,  $C_{HOLD}$  表示第三电容器 C3 的电容,  $V_{DATA}$  表示与第一图像数据 DATA 对应的电压,  $C_{ST}$  表示第二电容器 C2 的电容,  $C_{VTH}$  表示第一电容器 C1 的电容,以及  $V_0$  表示存储在第二电容器 C2 中的第一电压。)

[0091] [ 等式 2]

$$[0092] V_{G\_TI} = V_{ELVDD} - V_{TH} + (V_{eff} - V_0)$$

[0093] (其中,  $V_{G\_TI}$  表示第一 PMOS 晶体管 PT1 的栅端的电压,  $V_{ELVDD}$  表示与第一电源电压  $ELVDD$  对应的电压,以及  $V_{TH}$  表示第一 PMOS 晶体管 PT1 的阈值电压。)

[0094] 参照图 4E,可在第一发射周期 PE 中执行第一发射操作 FEP。详细地,在第一发射周期 PE 中,第一电源电压  $ELVDD$  可具有高电压电平,并且第二电源电压  $ELVSS$  可具有低电压电平。此外,发射控制信号 ECS 可具有高电压电平,并且补偿控制信号 TCS 也可具有高电压电平。因此,在图 1 的像素电路 100 中第三和第四 PMOS 晶体管 PT3 和 PT4 可截止。当第四 PMOS 晶体管 PT4 截止时,在图 1 的像素电路 100 中第一区 FA 可与第二区 SA 分离,并且第一区 FA 的操作可独立于第二区 SA 的操作。类似于图 4A,第二显示操作的第二初始数据写入操作 SPDP 和第一显示操作的第一发射操作 FEP 可同时执行。因此,在基于存储在各个像素电路 100 中的第一图像数据 DATA 显示第一图像的时候可将第二图像数据写入各个像素电路 100 中。结果,在第一区 FA 中,当第五 PMOS 晶体管 PT5 响应于通过扫描线 SL 施加

的扫描信号而导通时,可将通过数据线 DL 施加的第二图像数据存储在第三存储器 C3 中。与此同时,在第二区 SA 中,有机发光二极管 OLED 可基于从具有高电压电平的第一电源电压 ELVDD 流向具有低电压电平的第二电源电压 ELVSS 的电流发光。

[0095] 可将第一电源电压 ELVDD、第二电源电压 ELVSS、发射控制信号 ECS 和补偿控制信号 TCS 同时应用至有机发光显示装置的全部像素电路 100。另一方面,可将第二图像数据顺序地应用至有机发光显示装置的全部电路(即,当第五 PMOS 晶体管 PT5 响应于具有低电压电平的扫描信号 SCAN[n] 而导通时)。因此,可为全部像素电路 100 同时执行第一显示操作的第一发射操作 FEP,并且可为全部像素电路 100 顺序地执行第二显示操作的第二初始数据写入操作 SPDP。

[0096] 可基于第一 PMOS 晶体管 PT1 的栅端的电压确定流过有机发光二极管 OLED 的电流。也就是说,可基于有效数据 Veff 和存储在第二电容器 C2 中的第一电压 Vo 顺序地确定流过有机发光二极管 OLED 的电流。详细地,有机发光显示装置可基于全部像素电路 100 同时发光的同时发射方法工作。这里,可根据下面的〔等式 3〕确定流过各个像素电路 100 的有机发光二极管 OLED 的电流。

[0097] [等式 3]

$$[0098] I_D = \frac{1}{2} \mu C_{ox} \frac{W}{L} (V_{GS} - V_{TH})^2 = \frac{1}{2} \mu C_{ox} \frac{W}{L} (V_{eff} - V_O)^2$$

[0099] (其中,  $I_D$  表示流过有机发光二极管 OLED 的电流,  $\frac{1}{2} \mu C_{ox} \frac{W}{L}$  是唯一的常数,  $V_{GS}$  表示第一 PMOS 晶体管 PT1 的栅端与源端之间的电压差,  $V_{TH}$  表示第一 PMOS 晶体管 PT1 的阈值电压,  $V_{eff}$  表示与有效数据对应的电压,  $V_O$  表示存储在第二电容器 C2 中的第一电压。)

[0100] 尽管参照图 4A 至图 4E 描述了用于显示第一图像的第一显示操作(即,第一初始数据写入周期 PA、第一复位周期 PB、第一阈值电压补偿周期 PC、第一数据写入周期 PD 和第一发射周期 PE)和用于显示第二图像的第二显示操作(即,第二初始数据写入周期 PA、第二复位周期 PB、第二阈值电压补偿周期 PC、第二数据写入周期 PD、第二发射周期 PE),但是应该理解,为了方便描述,图 4A 至图 4E 中所示出的驱动信号波形被简化了。因此,例如,图 1 的像素电路 100 可基于更复杂的驱动信号波形工作。

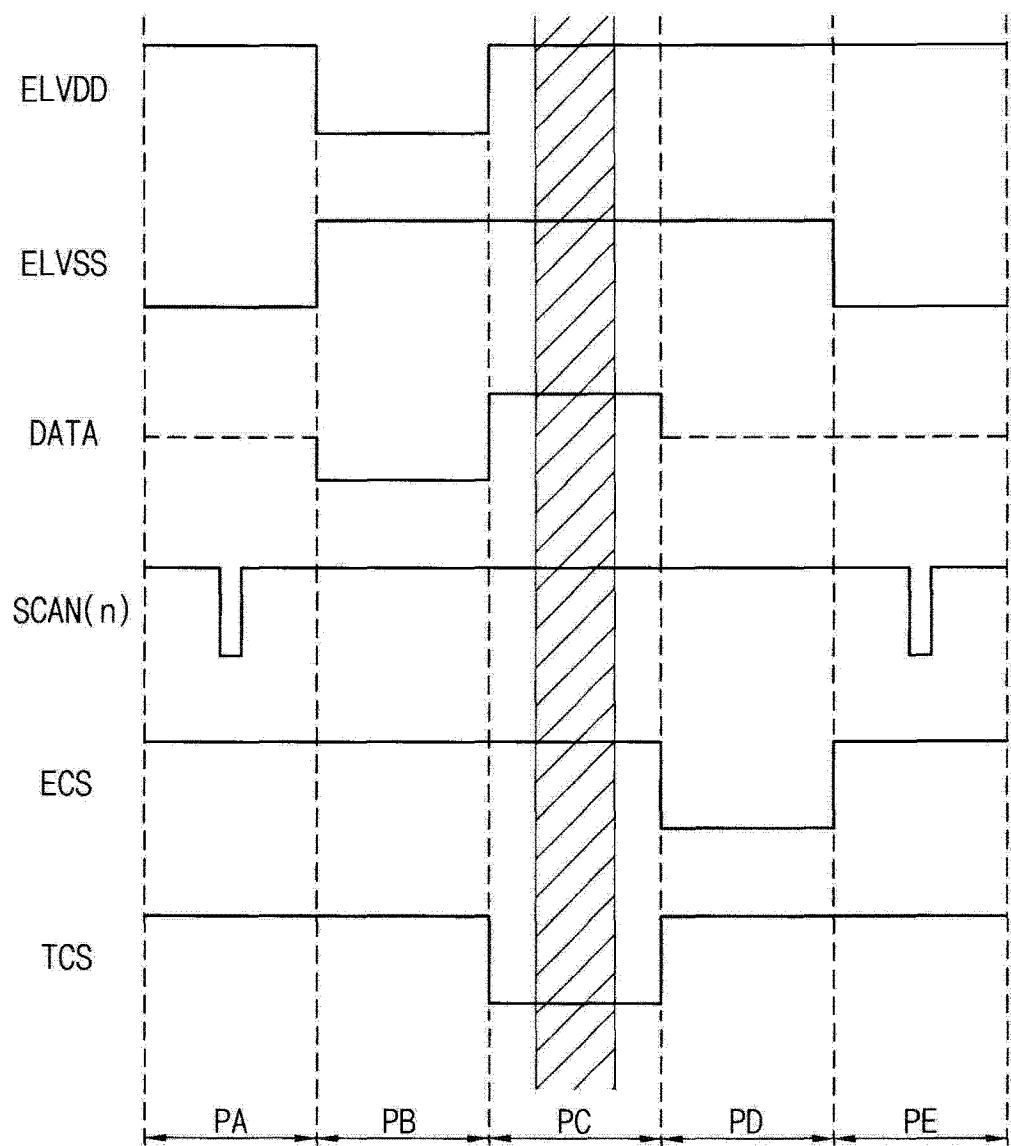

[0101] 图 5 示出了图 1 的像素电路 100 的另一操作示例的时序图。

[0102] 参照图 5,用于显示第一图像(例如,左图像)的第一显示操作的周期可包括第一初始数据写入周期 PA、第一偏置截止(off-bias)应用周期 PF、第一复位周期 PB、第一阈值电压补偿周期 PC、第一数据写入周期 PD 和第一发射周期 PE。类似地,用于显示第二图像(例如,右图像)的第二显示操作的周期可包括第二初始数据写入周期 PA、第二偏置截止应用周期 PF、第二复位周期 PB、第二阈值电压补偿周期 PC、第二数据写入周期 PD 和第二发射周期 PE。为了方便起见,下面对图 5 的描述专注于用于显示第一图像的第一显示操作。如上所述,可根据所需的条件确定第一和第二电源电压 ELVDD 和 ELVSS。但是,为了方便描述,下面将描述第一电源电压 ELVDD 和第二电源电压 ELVSS 具有高电压电平或低电压电平。此外,上面已经描述了第一初始数据写入周期 PA、第一复位周期 PB、第一阈值电压补偿周期 PC、第一数据写入周期 PD 和第一发射周期 PE,下面将不再对它们的详细内容进行描述。

[0103] 如图 5 所示,用于显示第一图像(例如,左图像)的第一显示操作的周期可包括第一

复位周期 PB 之前的第一偏置截止应用周期 PF。第一偏置截止应用周期 PF 可用作通过向图 1 的像素电路 100 应用偏置截止来提高阶跃响应波形的周期。因此,第一偏置截止应用周期 PF 可被设置为减少或防止有机发光显示装置中的串扰。例如,第一偏置截止应用周期 PF 可被设置为防止第一 PMOS 晶体管 PT1 (即,驱动晶体管) 的特征曲线的滞后(即,偏移)。结果,在对第一 PMOS 晶体管 PT1 的阈值电压进行补偿之前,可在第一偏置截止应用周期 PF 中固定(即,可被复位)第一 PMOS 晶体管 PT1 的特征曲线的位置。因此,可固定第一 PMOS 晶体管 PT1 的特征曲线的位置而不管前一帧的数据信号(例如,左图像数据或右图像数据)如何。

[0104] 详细地,在第一偏置截止应用周期 PF 中,发射控制信号 ECS 可具有高电压电平,并且补偿控制信号 TCS 可具有低电压电平。此外,第二电源电压 ELVSS 可具有高电压电平,并且第一电源电压 ELVDD 可具有低电压电平。因此,第四 PMOS 晶体管 PT4 可截止,并且第二和第三 PMOS 晶体管 PT2 和 PT3 可导通。当第四 PMOS 晶体管 PT4 截止时,在图 1 的像素电路 100 中第一区 FA 可与第二区 SA 分离,并且第一区 FA 的操作可独立于第二区 SA 的操作。与此同时,第二区 SA 可执行第一偏置截止应用操作,因为在第二和第三 PMOS 晶体管 PT2 和 PT3 导通的时候第二电源电压 ELVSS 被维持为大于第一电源电压 ELVDD 一段预定时间。

[0105] 尽管图 5 未示出,但是可在第一偏置截止应用周期 PF 与第一复位周期 PB 之间插入第二电源电压 ELVSS 具有高电压电平且第一电源电压 ELVDD 也具有高电压电平的周期。在另一实现中,可在第一偏置截止应用周期 PF 与第一复位周期 PB 之间插入第二电源电压 ELVSS 具有低电压电平且第一电源电压 ELVDD 也具有低电压电平的周期。此周期可防止在执行第一显示操作时第一偏置截止应用操作与第一复位操作之间的干扰。尽管参照图 5 描述了用于显示第一图像的第一显示操作(即,第一初始数据写入周期 PA、第一偏置截止应用周期 PF、第一复位周期 PB、第一阈值电压补偿周期 PC、第一数据写入周期 PD 和第一发射周期 PE)和用于显示第二图像的第二显示操作(即,第二初始数据写入周期 PA、第二偏置截止应用周期 PF、第二复位周期 PB、第二阈值电压补偿周期 PC、第二数据写入周期 PD 和第二发射周期 PE),但是应该理解,为了方便描述简化了图 5 所示的驱动信号波形,因此可使用其它驱动信号波形来操作图 1 的像素电路 100。

[0106] 图 6 示出了根据示例性实施方式的像素电路 200 的电路图。

[0107] 参照图 6,像素电路 200 可包括有机发光二极管 OLED、第一至第五 PMOS 晶体管 PT1 至 PT5、以及第一至第三电容器 C1 至 C3。像素电路 200 可具有 5T-3C 结构(即,具有 5 个晶体管和 3 个电容器的结构)。在示例性实施方式中,像素电路 200 还可包括第四电容器 C4,第四电容器 C4 连接在有机发光二极管的阳极与阴极之间。

[0108] 有机发光二极管 OLED 可连接在第二电源电压 ELVSS 与第一 PMOS 晶体管 PT1 之间。详细地,有机发光二极管 OLED 的阴极可连接至第二电源电压 ELVSS,并且有机发光二极管 OLED 的阳极可连接至第一 PMOS 晶体管 PT1 的第一端。因此,有机发光二极管 OLED 可基于受第一 PMOS 晶体管 PT1 控制的电流而发光。第一 PMOS 晶体管 PT1 可连接在第一电源电压 ELVDD 与有机发光二极管 OLED 的阳极之间。第一 PMOS 晶体管 PT1 的栅端可连接至第一节点 N1。第一 PMOS 晶体管 PT1 可以是对流过有机发光二极管 OLED 的电流进行控制的驱动晶体管。如图 6 所示,在第一节点 N1 处,第一电容器 C1 的第一端、第二 PMOS 晶体管 PT2 的第一端和第一 PMOS 晶体管 PT1 的栅端互相连接。第二 PMOS 晶体管 PT2 可连接在第一节点

N1 与有机发光二极管 OLED 的阳极之间。第二 PMOS 晶体管 PT2 的栅端可接收补偿控制信号 TCS。详细地,第二 PMOS 晶体管 PT2 的第一端可连接至第一节点 N1,并且第二 PMOS 晶体管 PT2 的第二端可连接至第一 PMOS 晶体管 PT1 的第一端。因此,当第二 PMOS 晶体管 PT2 响应于补偿控制信号 TCS 而导通时,第一 PMOS 晶体管 PT1 可为二极管接法。

[0109] 第一电容器 C1 可连接在第一节点 N1 与第二节点 N2 之间。详细地,第一电容器 C1 的第一端可连接至第一节点 N1,并且第一电容器 C1 的第二端可连接至第二节点 N2。第一电容器 C1 可以是阈值电压补偿电容器。如图 6 所示,在第二节点 N2 处,第一电容器 C1 的第二端、第二电容器 C2 的第一端、第三 PMOS 晶体管 PT3 的第一端和第四 PMOS 晶体管 PT4 的第一端互相连接。第二电容器 C2 可连接在第一 电源电压 ELVDD 与第二节点 N2 之间。第二电容器 C2 可以是存储电容器。详细地,第二电容器 C2 的第一端可连接至第二节点 N2,并且第二电容器 C2 的第二端可连接至第一电源电压 ELVDD。第三 PMOS 晶体管 PT3 可连接在数据线 DL 与第二节点 N2 之间。第三 PMOS 晶体管 PT3 的栅端可接收补偿控制信号 TCS。详细地,第三 PMOS 晶体管 PT3 的第一端可连接至第二节点 N2,第三 PMOS 晶体管 PT3 的第二端可连接至数据线 DL,并且第三 PMOS 晶体管 PT3 的栅端可连接至第二 PMOS 晶体管 PT2 的栅端。第四 PMOS 晶体管 PT4 可连接在第三节点 N3 与第二节点 N2 之间。第四 PMOS 晶体管 PT4 的栅端可接收发射控制信号 ECS。详细地,第四 PMOS 晶体管 PT4 的第一端可连接至第二节点 N2,并且第四 PMOS 晶体管 PT4 的第二端可连接至第三节点 N3。如图 6 所示,在第三节点 N3 处,第四 PMOS 晶体管 PT4 的第二端、第五 PMOS 晶体管 PT5 的第一端和第三电容器 C3 的第一端互相连接。

[0110] 第三电容器 C3 可连接在第三节点 N3 与维持电源电压 VSUS 之间。详细地,第三电容器 C3 的第一端可连接至第三节点 N3,并且第三电容器 C3 的第二端可连接至维持电源电压 VSUS。在图 6 中,由于维持电源电压 VSUS 被施加至第三电容器 C3,因此可防止存储在第三电容器 C3 中的数据信号(例如,左图像数据或右图像数据)的波动。也就是说,维持电源电压 VSUS 可以是预定的 DC 电压以防止存储在第三电容器 C3 中的数据信号的波动。第五 PMOS 晶体管 PT5 可连接在数据线 DL 与第三节点 N3 之间。第五 PMOS 晶体管 PT5 的栅端可连接至扫描线 SL。详细地,第五 PMOS 晶体管 PT5 的第一端可连接至第三节点 N3,第五 PMOS 晶体管 PT5 的第二端可连接至数据线 DL,并且第五 PMOS 晶体管 PT5 的栅端可连接至扫描线 SL。数据线 DL 可连接至有机发光显示装置的数据驱动单元以提供数据信号(例如,左图像数据或右图像数据)。此外,扫描线 SL 可连接至有机发光显示装置的扫描驱动单元以提供扫描信号。

[0111] 如上所述,像素电路 200 可具有包括有机发光二极管 OLED、第一至第五 PMOS 晶体管 PT1 至 PT5、以及第一至第三电容器 C1 至 C3 的 5T-3C 结构。具有像素电路 200 的有机发光显示装置可基于同时发射方法通过交替地显示左图像和右图像来实现立体图像。例如,在有机发光显示装置的各个像素电路 200 同时显示左图像的时候,右图像数据可顺序地写入有机发光显示装置的各个像素电路 200 中。类似地,在有机发光显示装置的各个像素电路 200 同时显示右图像的时候,左图像数据可顺序地写入有机发光显示装置的各个像素电路 200 中。

[0112] 如图 6 所示,像素电路 200 可包括第一区 FA 和第二区 SA。在下面的描述中,第一区 FA 包括第三电容器 C3 和第五 PMOS 晶体管 PT5,第二区 SA 包括第一和第二电容器 C1 和

C2、以及第一至第三 PMOS 晶体管 PT1 至 PT3。当第四 PMOS 晶体管 PT4 导通时,第一区 FA 可连接至第二区 SA。当第四 PMOS 晶体管 PT4 截止时,第一区 FA 可与第二区 SA 分离。详细地,当第四 PMOS 晶体管 PT4 导通时,在像素电路 200 中第一区 FA 可连接至第二区 SA。结果,存储在第三电容器 C3 中的数据信号(例如,左图像数据或右图像数据)可转移至第二区 SA。另一方面,当第四 PMOS 晶体管 PT4 截止时,在像素电路 200 中第一区 FA 可与第二区 SA 分离。结果,第一区 FA 和第二区 SA 可执行各自的操作。详细地,在第一区 FA 中执行初始数据写入操作的时候,可在第二区 SA 中执行发射操作。因此,第一区 FA 的操作可独立于第二区 SA 的操作。例如,当第四 PMOS 晶体管 PT4 响应于发射控制信号 ECS 而截止时,可通过第一和第二 PMOS 晶体管 PT1 和 PT2、第一和第二电容器 C1 和 C2、以及有机发光二极管 OLED(即,第二区 SA 的操作)显示第一图像(例如,左图像或右图像)。与此同时,当第五 PMOS 晶体管 PT5 响应于通过扫描线 SL 输入的扫描信号而导通时,通过数据线 DL 输入的第二图像数据(例如,右图像数据或左图像数据)可存储在第三电容器 C3 中(即第一区 FA 的操作)。

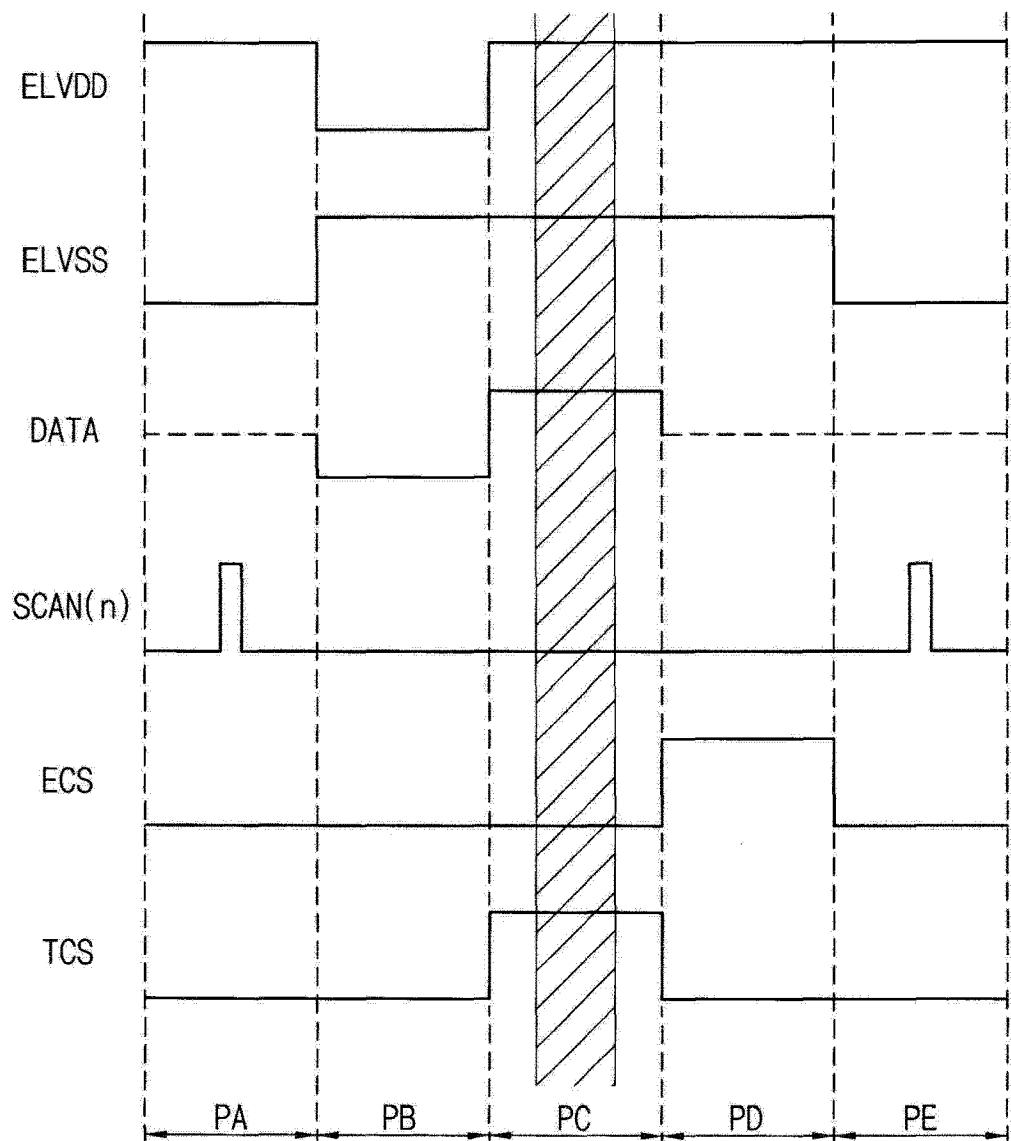

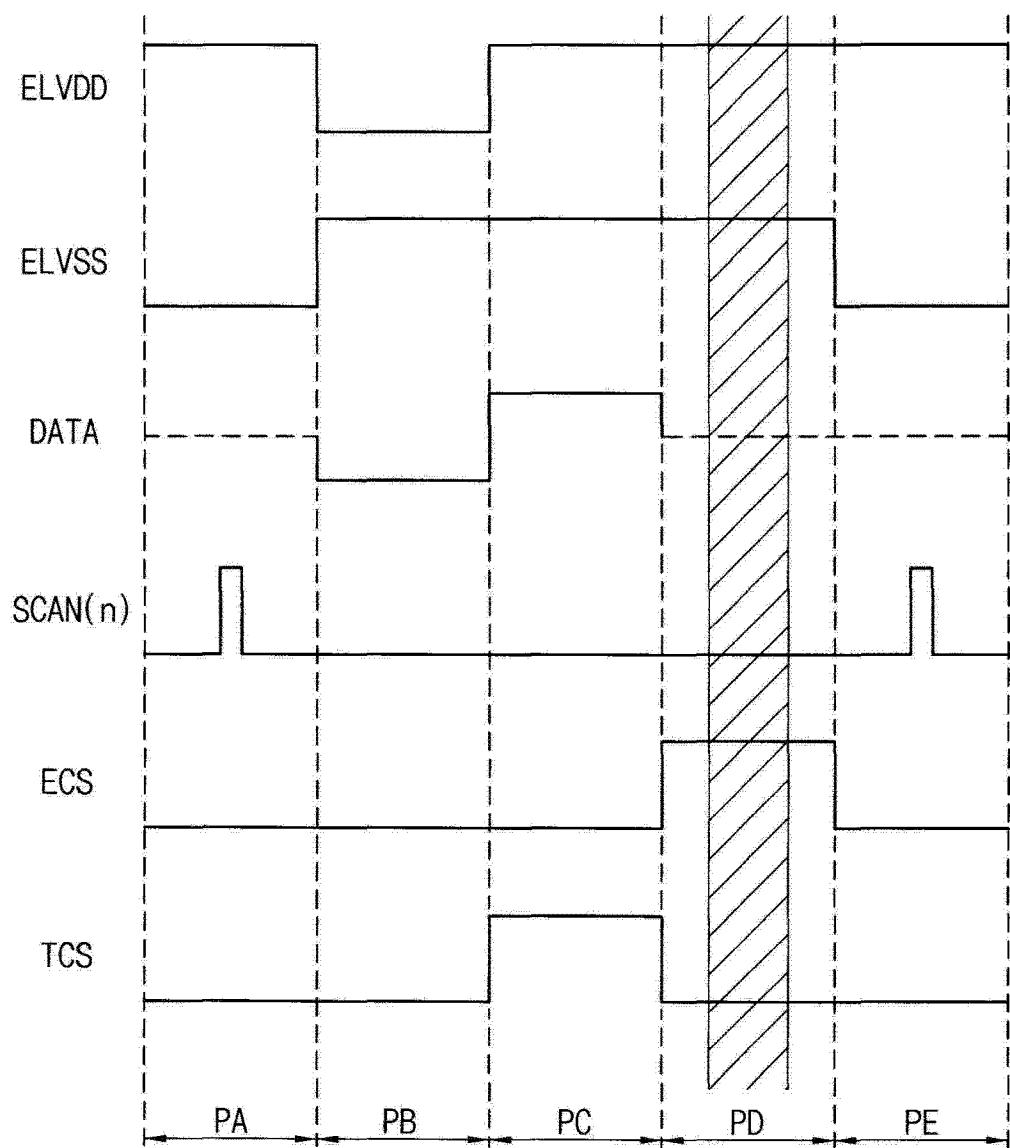

[0113] 图 7 示出了根据示例性实施方式的像素电路 300 的电路图。

[0114] 参照图 7,像素电路 300 可包括有机发光二极管 OLED、第一至第五 n 沟道金属氧化物半导体(NMOS)晶体管 NT1 至 NT5、以及第一至第三电容器 C1 至 C3。像素电路 300 可具有 5T-3C 结构(即,具有 5 个晶体管和 3 个电容器的结构)。在示例性实施方式中,像素电路 300 还可包括第四电容器 C4,第四电容器 C4 连接在有机发光二极管 OLED 的阳极与阴极之间。

[0115] 有机发光二极管 OLED 可连接在第一电源电压 ELVDD 与第一 NMOS 晶体管 NT1 之间。详细地,有机发光二极管 OLED 的阳极可连接至第一电源电压 ELVDD,并且有机发光二极管 OLED 的阴极可连接至第一 NMOS 晶体管 NT1 的第一端。因此,有机发光二极管 OLED 可基于受第一 NMOS 晶体管 NT1 控制的电流而发光。第一 NMOS 晶体管 NT1 可连接在第二电源电压 ELVSS 与有机发光二极管 OLED 的阴极之间。第一 NMOS 晶体管 NT1 的栅端可连接至第一节点 N1。第一 NMOS 晶体管 NT1 可以是对流过有机发光二极管 OLED 的电流进行控制的驱动晶体管。如图 7 所示,在第一节点 N1 处,第一电容器 C1 的第一端、第二 NMOS 晶体管 NT2 的第一端和第一 NMOS 晶体管 NT1 的栅端互相连接。第二 NMOS 晶体管 NT2 可连接在第一节点 N1 与有机发光二极管 OLED 的阴极之间。第二 NMOS 晶体管 NT2 的栅端可接收补偿控制信号 TCS。详细地,第二 NMOS 晶体管 NT2 的第一端可连接至第一节点 N1,并且第二 NMOS 晶体管 NT2 的第二端可连接至第一 NMOS 晶体管 NT1 的第一端。因此,当第二 NMOS 晶体管 NT2 响应于补偿控制信号 TCS 而导通时,第一 NMOS 晶体管 NT1 可为二极管接法。

[0116] 第一电容器 C1 可连接在第一节点 N1 与第二节点 N2 之间。详细地,第一电容器 C1 的第一端可连接至第一节点 N1,并且第一电容器 C1 的第二端可连接至第二节点 N2。第一电容器 C1 可以是阈值电压补偿电容器。如图 7 所示,在第二节点 N2 处,第一电容器 C1 的第二端、第二电容器 C2 的第一端、第三 NMOS 晶体管 NT3 的第一端和第四 NMOS 晶体管 NT4 的第一端互相连接。第二电容器 C2 可连接在第二电源电压 ELVSS 与第二节点 N2 之间。第二电容器 C2 可以是存储电容器。详细地,第二电容器 C2 的第一端可连接至第二节点 N2,并且第二电容器 C2 的第二端可连接至第二电源电压 ELVSS。第三 NMOS 晶体管 NT3 可连接在数据线 DL 与第二节点 N2 之间。第三 NMOS 晶体管 NT3 的栅端可接收补偿控制信号 TCS。详细地,第三 NMOS 晶体管 NT3 的第一端可连接至第二节点 N2,第三 NMOS 晶体管 NT3 的第

二端可连接至数据线 DL，并且第三 NMOS 晶体管 NT3 的栅端可连接至第二 NMOS 晶体管 NT2 的栅端。第四 NMOS 晶体管 NT4 可连接在第三节点 N3 与第二节点 N2 之间。第四 NMOS 晶体管 NT4 的栅端可接收发射控制信号 ECS。详细地，第四 NMOS 晶体管 NT4 的第一端可连接至第二节点 N2，并且第四 NMOS 晶体管 NT4 的第二端可连接至第三节点 N3。如图 7 所示，在第三节点 N3 处，第四 NMOS 晶体管 NT4 的第二端、第五 NMOS 晶体管 NT5 的第一端和第三电容器 C3 的第一端互相连接。

[0117] 第三电容器 C3 可连接在第三节点 N3 与第三 NMOS 晶体管 NT3 的栅端之间。详细地，第三电容器 C3 的第一端可连接至第三节点 N3，并且第三电容器 C3 的第二端可连接至第三 NMOS 晶体管 NT3 的栅端。第五 NMOS 晶体管 NT5 可连接在数据线 DL 与第三节点 N3 之间。第五 NMOS 晶体管 NT5 的栅端可连接至扫描线 SL。详细地，第五 NMOS 晶体管 NT5 的第一端可连接至第三节点 N3，第五 NMOS 晶体管 NT5 的第二端可连接至数据线 DL，并且第五 NMOS 晶体管 NT5 的栅端可连接至扫描线 SL。数据线 DL 可连接至有机发光显示装置的数据驱动单元以提供数据信号(例如，左图像数据或右图像数据)。此外，扫描线 SL 可连接至有机发光显示装置的扫描驱动单元以提供扫描信号。

[0118] 如上所述，像素电路 300 可具有包括有机发光二极管 OLED、第一至第五 NMOS 晶体管 NT1 至 NT5、以及第一至第三电容器 C1 至 C3 的 5T-3C 结构。具有像素电路 300 的有机发光显示装置可基于同时发射方法通过交替地显示左图像和右图像来实现立体图像。例如，在有机发光显示装置的各个像素电路 300 同时显示左图像的时候，右图像数据可顺序地写入有机发光显示装置的各个像素电路 300 中。类似地，在有机发光显示装置的各个像素电路 300 同时显示右图像的时候，左图像数据可顺序地写入有机发光显示装置的各个像素电路 300 中。

[0119] 如图 7 所示，像素电路 300 可包括第一区 FA 和第二区 SA。在下面的描述中，第一区 FA 包括第三电容器 C3 和第五 NMOS 晶体管 NT5，第二区 SA 包括第一和第二电容器 C1 和 C2、以及第一至第三 NMOS 晶体管 NT1 至 NT3。当第四 NMOS 晶体管 NT4 导通时，第一区 FA 可连接至第二区 SA。当第四 NMOS 晶体管 NT4 截止时，第一区 FA 可与第二区 SA 分离。详细地，当第四 NMOS 晶体管 NT4 导通时，在像素电路 300 中第一区 FA 可连接至第二区 SA。结果，存储在第三电容器 C3 中的数据信号(例如，左图像数据或右图像数据)可被转移至第二区 SA。另一方面，当第四 NMOS 晶体管 NT4 截止时，在像素电路 300 中第一区 FA 可与第二区 SA 分离。结果，第一区 FA 和第二区 SA 可执行各自的操作。

[0120] 详细地，可在第二区 SA 中执行发射操作的时候，在第一区 FA 中执行初始数据写入操作。因此，第一区 FA 的操作可独立于第二区 SA 的操作。例如，当第四 NMOS 晶体管 NT4 响应于发射控制信号 ECS 而截止时，可通过第一和第二 NMOS 晶体管 NT1 和 NT2、第一和第二电容器 C1 和 C2、以及有机发光二极管 OLED (即，第二区 SA 的操作)显示第一图像(例如，左图像或右图像)。与此同时，当第五 NMOS 晶体管 NT5 响应于通过扫描线 SL 输入的扫描信号而导通时，通过数据线 DL 输入的第二图像数据(例如，右图像数据或左图像数据)可存储在第三电容器 C3 中(即，第一区 FA 的操作)。在下文中将详细描述像素电路 300 的操作。

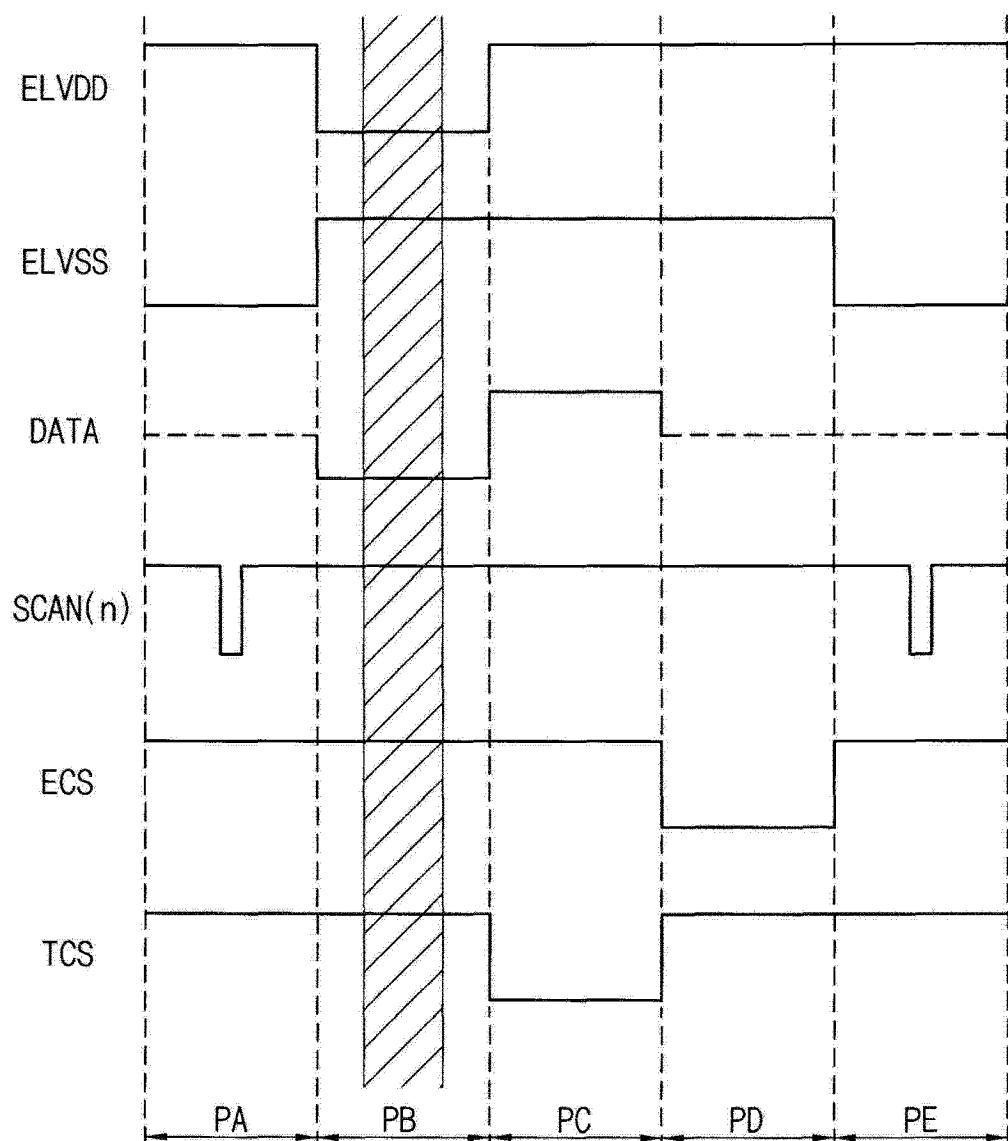

[0121] 图 8A 至图 8E 示出了图 7 的像素电路的示例性操作的时序图。

[0122] 用于显示第一图像(例如，左图像)的第一显示操作可包括第一初始数据写入操作 FPDP、第一复位操作 FIP、第一阈值电压补偿操作 FVP、第一数据写入操作 FWP 和第一发射操

作 FEP。类似地,用于显示第二图像(例如,右图像)的第二显示操作可包括第二初始数据写入操作 SPDP、第二复位操作 SIP、第二阈值电压补偿操作 SVP、第二数据写入操作 SWP 和第二发射操作 SEP。有机发光显示装置的全部像素电路可通过各个扫描线 SL 顺序地执行初始数据写入操作(即,第一初始数据写入操作 FPDP 或第二初始数据写入操作 SPDP)。另一方面,有机发光显示装置的全部像素电路 300 可同时执行复位操作(即,第一复位操作 FIP 或第二复位操作 SIP)、阈值电压补偿操作(即,第一阈值电压补偿操作 FVP 或第二阈值电压补偿操作 SVP)、数据写入操作(即,第一数据写入操作 FWP 或第二数据写入操作 SWP)、或发射操作(即,第一发射操作 FEP 或第二发射操作 SEP)。

[0123] 参照图 8A 至图 8E,第一初始数据写入操作 FPDP、第一复位操作 FIP、第一阈值电压补偿操作 FVP、第一数据写入操作 FWP 和第一发射操作 FEP 可对应于第一初始数据写入周期 PA、第一复位周期 PB、第一阈值电压补偿周期 PC、第一数据写入周期 PD 和第一发射周期 PE。类似地,第二初始数据写入操作 SPDP、第二复位操作 SIP、第二阈值电压补偿操作 SVP、第二数据写入操作 SWP 和第二发射操作 SEP 可对应于第二初始数据写入周期 PA、第二复位周期 PB、第二阈值电压补偿周期 PC、第二数据写入周期 PD 和第二发射周期 PE。为了方便起见,下面对图 8A 至图 8E 的描述将专注于用于显示第一图像的第一显示操作。第一电源电压 ELVDD 和第二电源电压 ELVSS 可根据所需的条件确定。为便于描述起见,下文将描述第一电源电压 ELVDD 和第二电源电压 ELVSS 具有高电压电平或低电压电平的情况。

[0124] 参照图 8A,可在第一初始数据写入周期 PA 中执行第一初始数据写入操作 FPDP。如上所述,用于显示第一图像的第一显示操作的第一初始数据写入操作 FPDP 和用于显示第二图像的第二显示操作的第二发射操作 SEP 可同时执行。因此,在第一初始数据写入周期 PA 中将第一图像数据 DATA 写入各个像素电路 300 的时候可基于存储在各个像素电路 300 中的第二图像数据显示第二图像。详细地,在第一初始数据写入周期 PA 中,第一电源电压 ELVDD 可具有高电压电平,第二电源电压 ELVSS 可具有逻辑低电平。此外,发射控制信号 ECS 可具有低电压电平,补偿控制信号 TCS 也可具有低电压电平。因此,在图 7 的像素电路 300 中第三和第四 NMOS 晶体管 NT3 和 NT4 可截止。当第四 NMOS 晶体管 NT4 截止时,在图 7 的像素电路 300 中第一区 FA 可与第二区 SA 分离,并且第一区 FA 的操作可独立于第二区 SA 的操作。结果,在第一区 FA 中,当第五 NMOS 晶体管 NT5 响应于通过扫描线 SL 施加的扫描信号而导通时,通过数据线 DL 施加的第一图像数据 DATA 可存储在第三电容器 C3 中。与此同时,在第二区 SA 中,有机发光二极管 OLED 可基于从具有高电压电平的第一电源电压 ELVDD 流至具有低电压电平的第二电源电压 ELVSS 的电流发光。

[0125] 如上所述,在具有图 7 的像素电路 300 的有机发光显示装置中,在第二图像(即,右图像或左图像)通过各个像素电路 300 显示的时候,第一图像数据 DATA(即,左图像数据或右图像数据)可存储在各个像素电路 300 的第三电容器 C3 中。类似地,在第一图像(即,左图像或右图像)通过各个像素电路 300 显示的时候,第二图像数据 DATA(即,右图像数据或左图像数据)可存储在各个像素电路 300 的第三电容器 C3 中。

[0126] 参照图 8B,可在第一复位周期 PB 中执行第一复位操作 FIP。详细地,在第一复位周期 PB 中,第一电源电压 ELVDD 可具有低电压电平,第二电源电压 ELVSS 可具有高电压电平。此外,发射控制信号 ECS 可具有低电压电平,补偿控制信号 TCS 也可具有低电压电平。因此,在图 7 的像素电路 300 中第三和第四 NMOS 晶体管 NT3 和 NT4 可截止。当第四 NMOS

晶体管 NT4 截止时,在图 7 的像素电路 300 中第一区 FA 可与第二区分离,并且第一区 FA 的操作可独立于第二区 SA 的操作。由于第二电源电压 ELVSS 高于第一电源电压 ELVDD,可在第二区 SA 中执行第一复位操作 FIP。

[0127] 参照图 8C,可在第一阈值电压补偿周期 PC 中执行第一阈值电压补偿操作 FVP。详细地,在第一阈值电压补偿周期 PC 中,第一电源电压 ELVDD 可具有高电压电平,第二电源电压 ELVSS 也可具有高电压电平。此外,发射控制信号 ECS 可具有低电压电平,并且补偿控制信号 TCS 可具有高电压电平。因此,在图 7 的像素电路 300 中,第二和第三 NMOS 晶体管 NT2 和 NT3 可导通,第四和第五 NMOS 晶体管 NT4 和 NT5 可截止。当第四 NMOS 晶体管 NT4 截止时,在图 7 的像素电路 300 中第一区 FA 可与第二区 SA 分离,并且第一区 FA 的操作可独立于第二区 SA 的操作。当第二和第三 NMOS 晶体管 NT2 和 NT3 导通时,可在第二区 SA 中执行第一阈值电压补偿操作 FVP。

[0128] 参照图 8D,可在第一数据写入周期 PD 中执行第一数据写入操作 FWP。详细地,在第一数据写入周期 PD 中,第一电源电压 ELVDD 可具有高电压电平,第二电源电压 ELVSS 也可具有高电压电平。此外,发射控制信号 ECS 可具有高电压电平,补偿控制信号 TCS 可具有低电压电平。因此,在图 7 的像素电路 300 中,第四和第五 NMOS 晶体管 NT4 和 NT5 可导通,并且第二和第三 NMOS 晶体管 NT2 和 NT3 可截止。当第四 NMOS 晶体管 NT4 导通时,在图 7 的像素电路 300 中第一区 FA 可连接至第二区 SA。当第一区 FA 连接至第二区 SA 时,通过第一初始数据写入操作 FPDP 存储在第三电容器 C3 中的第一图像数据 DATA 可转移至第二区 SA。结果,第一 NMOS 晶体管 NT1 的栅端(即,第一节点 N1)的电压可被第一图像数据 DATA 改变。

[0129] 参照图 8E,可在第一发射周期 PE 执行第一发射操作 FEP。详细地,在第一发射周期 PE 中,第一电源电压 ELVDD 可具有高电压电平,第二电源电压 ELVSS 可具有低电压电平。此外,发射控制信号 ECS 可具有低电压电平,并且补偿控制信号 TCS 也可具有低电压电平。因此,在图 7 的像素电路 300 中第三和第四 NMOS 晶体管 NT3 和 NT4 可截止。当第四 NMOS 晶体管 NT4 截止时,在图 7 的像素电路 300 中第一区 FA 可与第二区 SA 分离,并且第一区 FA 的操作可独立于第二区 SA 的操作。类似于图 8A,第二显示操作的第二初始数据写入操作 SPDP 和第一显示操作的第一发射操作 FEP 可同时执行。因此,在基于存储在各个像素电路 300 中的第一图像数据 DATA 显示第一图像的时候第二图像数据可写入各个像素电路 300 中。结果,在第一区 FA 中,当第五 NMOS 晶体管 NT5 响应于通过扫描线 SL 施加的扫描信号而导通时,通过数据线 DL 施加的第二图像数据可被存储在第三电容器 C3 中。与此同时,在第二区 SA 中,有机发光二极管 OLED 可基于从具有高电压电平的第一电源电压 ELVDD 流至具有低电压电平的第二电源电压 ELVSS 的电流而发光。

[0130] 尽管参照图 8A 至图 8E 描述了用于显示第一图像的第一显示操作(即,第一初始数据写入周期 PA、第一复位周期 PB、第一阈值电压补偿周期 PC、第一数据写入周期 PD 和第一发射周期 PE)和用于显示第二图像的第二显示操作(即,第二初始数据写入周期 PA、第二复位周期 PB、第二阈值电压补偿周期 PC、第二数据写入周期 PD 和第二发射周期 PE),但是应该理解图 8A 至图 8E 所示的驱动信号波形为了方便描述而被简化了。因此,图 7 的像素电路 300 可基于更复杂的驱动信号波形操作。

[0131] 图 9 示出了根据示例性实施方式的像素电路 400 的电路图。

[0132] 参照图 9, 像素电路 400 可包括有机发光二极管 OLED、第一至第五 NMOS 晶体管 NT1 至 NT5、以及第一至第三电容器 C1 至 C3。像素电路 400 可具有 5T-3C 结构(即, 具有 5 个晶体管和 3 个电容器的结构)。在示例性实施方式中, 像素电路 400 还可包括第四电容器 C4, 第四电容器 C4 连接在有机发光二极管 OLED 的阳极与阴极之间。

[0133] 有机发光二极管 OLED 可连接在第一电源电压 ELVDD 与第一 NMOS 晶体管 NT1 之间。详细地, 有机发光二极管 OLED 的阳极可连接至第一电源电压 ELVDD, 有机发光二极管 OLED 的阴极可连接至第一 NMOS 晶体管 NT1 的第一端。有机发光二极管 OLED 可基于受第一 NMOS 晶体管 NT1 控制的电流而发光。第一 NMOS 晶体管 NT1 可连接在第二电源电压 ELVSS 与有机发光二极管 OLED 的阴极之间。第一 NMOS 晶体管 NT1 的栅端可连接至第一节点 N1。第一 NMOS 晶体管 NT1 可以是对流过有机发光二极管 OLED 的电流进行控制的驱动晶体管。如图 9 所示, 在第一节点 N1 处, 第一电容器 C1 的第一端、第二 NMOS 晶体管 NT2 的第一端和第一 NMOS 晶体管 NT1 的栅端互相连接。第二 NMOS 晶体管 NT2 可连接在第一节点 N1 与有机发光二极管 OLED 的阴极之间。第二 NMOS 晶体管 NT2 的栅端可接收补偿控制信号 TCS。详细地, 第二 NMOS 晶体管 NT2 的第一端可连接至第一节点 N1, 并且第二 NMOS 晶体管 NT2 的第二端可连接至第一 NMOS 晶体管 NT1 的第一端。因此, 当第二 NMOS 晶体管 NT2 响应于补偿控制信号 TCS 而导通时, 第一 NMOS 晶体管 NT1 可为二极管接法。

[0134] 第一电容器 C1 可连接在第一节点 N1 与第二节点 N2 之间。详细地, 第一电容器 C1 的第一端可连接至第一节点 N1, 并且第一电容器 C1 的第二端可连接至第二节点 N2。第一电容器 C1 可以是阈值电压补偿电容器。如图 9 所示, 在第二节点 N2 处, 第一电容器 C1 的第二端、第二电容器 C2 的第一端、第三 NMOS 晶体管 NT3 的第一端和第四 NMOS 晶体管 NT4 的第一端互相连接。第二电容器 C2 可连接在第二电源电压 ELVSS 与第二节点 N2 之间。第二电容器 C2 可以是存储电容器。详细地, 第二电容器 C2 的第一端可连接至第二节点 N2, 并且第二电容器 C2 的第二端可连接至第二电源电压 ELVSS。第三 NMOS 晶体管 NT3 可连接在数据线 DL 与第二节点 N2 之间。第三 NMOS 晶体管 NT3 的栅端可接收补偿控制信号 TCS。详细地, 第三 NMOS 晶体管 NT3 的第一端可连接至第二节点 N2, 第三 NMOS 晶体管 NT3 的第二端可连接至数据线 DL, 并且第三 NMOS 晶体管 NT3 的栅端可连接至第二 NMOS 晶体管 NT2 的栅端。第四 NMOS 晶体管 NT4 可连接在第三节点 N3 与第二节点 N2 之间。第四 NMOS 晶体管 NT4 的栅端可接收发射控制信号 ECS。详细地, 第四 NMOS 晶体管 NT4 的第一端可连接至第二节点 N2, 并且第四 NMOS 晶体管 NT4 的第二端可连接至第三节点 N3。如图 9 所示, 在第三节点 N3 处, 第四 NMOS 晶体管 NT4 的第二端、第五 NMOS 晶体管 NT5 的第一端和第三电容器 C3 的第一端互相连接。

[0135] 第三电容器 C3 可连接在第三节点 N3 与维持电源电压 VSUS 之间。详细地, 第三电容器 C3 的第一端可连接至第三节点 N3, 并且第三电容器 C3 的第二端可连接至维持电源电压 VSUS。在图 9 中, 由于维持电源电压 VSUS 被施加至第三电容器 C3, 因此可防止存储在第三电容器 C3 中的数据信号(例如, 左图像或右图像)的波动。也就是说, 维持电源电压 VSUS 可以是预定的直流电压以防止存储在第三电容器 C3 中的数据信号的波动。第五 NMOS 晶体管 NT5 可连接在数据线 DL 与第三节点 N3 之间。第五 NMOS 晶体管 NT5 的栅端可连接至扫描线 SL。详细地, 第五 NMOS 晶体管 NT5 的第一端可连接至第三节点 N3, 第五 NMOS 晶体管 NT5 的第二端可连接至数据线 DL, 并且第五 NMOS 晶体管的栅端可连接至扫描线 SL。数据线

DL 可连接至有机发光显示装置的数据驱动单元以提供数据信号(例如,左图像数据或右图像数据)。此外,扫描线 SL 可连接至有机发光显示装置的扫描驱动单元以提供扫描信号。

[0136] 如上所述,像素电路 400 可具有包括有机发光二极管 OLED、第一至第五 NMOS 晶体管 NT1 至 NT5 和第一至第三电容器 C1 至 C3 的 5T-3C 结构。具有像素电路 400 的有机发光显示装置可基于同时发射方法通过交替地显示左图像和右图像实现立体图像。例如,在通过有机发光显示装置的各个像素电路 400 同时显示左图像的时候,右图像可顺序地写入有机发光显示装置的各个像素电路 400 中。类似地,在通过有机发光显示装置的各个像素电路 400 同时显示右图像的时候,左图像可顺序地写入有机发光显示装置的各个像素电路 400 中。

[0137] 如图 9 所示,像素电路 400 可包括第一区 FA 和第二区 SA。在下面的描述中,第一区 FA 包括第三电容器 C3 和第五 NMOS 晶体管 NT5,第二区 SA 包括第一和第二电容器 C1 和 C2 以及第一至第三 NMOS 晶体管 NT1 至 NT3。当第四 NMOS 晶体管 NT4 导通时,第一区 FA 可连接至第二区 SA。当第四 NMOS 晶体管 NT4 截止时,第一区 FA 可与第二区 SA 分离。详细地,当第四 NMOS 晶体管 NT4 导通时,在像素电路 400 中第一区 FA 可连接至第二区 SA。结果,存储在第三电容器 C3 中的数据信号(例如,左图像数据或右图像数据)可转移至第二区 SA。另一方面,当第四 NMOS 晶体管 NT4 截止时,在像素电路 400 中第一区 FA 可与第二区 SA 分离。结果,第一区 FA 和第二区 SA 可执行各自的操作。详细地,在第一区 FA 中执行初始数据写入操作的时候,可在第二区 SA 中执行发射操作。因此,第一区 FA 的操作可独立于第二区 SA 的操作。例如,当第四 NMOS 晶体管 NT4 响应于发射控制信号 ECS 而截止时,可通过第一和第二 NMOS 晶体管 NT1 和 NT2、第一和第二电容器 C1 和 C2、以及有机发光二极管 OLED(即,第二区 SA 的操作)显示第一图像(例如,左图像或右图像)。与此同时,当第五 NMOS 晶体管 NT5 响应于通过扫描线 SL 输入的扫描信号而导通时,通过数据线 DL 输入的第二图像数据(例如,右图像数据或左图像数据)可存储在第三电容器 C3 中(即,第一区 FA 的操作)。

[0138] 图 10 和图 11 示出了根据示例性实施方式的驱动像素电路的方法的流程图。

[0139] 参照图 10 和图 11,图 10 的方法和图 11 的方法可交替地执行用于显示左图像的第一显示操作和用于显示右图像的第二显示操作。可 基于同时发射方法执行第一和第二显示操作。

[0140] 根据图 10 的方法,可同时执行第一显示操作的第一发射操作和第二显示操作的第二初始数据写入操作(操作 S120)。在完成第一发射操作之后,可顺序地执行第二显示操作的第二复位操作、第二阈值电压补偿操作和第二数据写入操作(操作 S140)。接下来,可同时执行第二显示操作的第二发射操作和第一显示操作的第一初始数据写入操作(操作 S160)。在完成第二发射操作之后,可顺序地执行第一显示操作的第一复位操作、第一阈值电压补偿操作和第一数据写入操作(操作 S180)。

[0141] 根据图 11 的方法,在第二显示操作的第二复位操作之前可执行第二偏置截止应用操作(操作 S130),并且在第一显示操作的第一复位操作之前可执行第一偏置截止应用操作(操作 S170)。对于这些操作,根据示例性实施方式的像素电路可具有包括有机发光二极管、第一至第五 PMOS 晶体管和第一至第三电容器的 5T-3C 结构。在另一种实现中,根据示例性实施方式的像素电路可具有包括有机发光二极管、第一至第五 NMOS 晶体管和第一至第三电容器的 5T-3C 结构。像素电路可以是参照图 1、6、7 和 9 描述的电路。

[0142] 图 12 示出了根据示例性实施方式的有机发光显示装置的框图。

[0143] 参照图 12, 有机发光显示装置 500 可包括像素单元 510、扫描驱动单元 520、数据驱动单元 530、时序控制单元 540、控制信号生成单元 550 和供电单元 560。在一些示例性实施方式中, 扫描驱动单元 520、数据驱动单元 530、时序控制单元 540、控制信号生成单元 550 和供电单元 560 可由集成电路 (IC) 实现。

[0144] 像素电路 510 可经由多个扫描线 SL1 至 SL<sub>n</sub> 连接至扫描驱动单元 520, 可经由多个数据线 DL1 至 DL<sub>m</sub> 连接至数据驱动单元 530, 并且可经由多个控制线连接至控制信号生成单元 550。像素单元 510 可从供电单元 560 接收第一电压电源 ELVDD 和第二电源电压 ELVSS。在示例性实施方式中, 像素单元 510 还可从供电单元 560 接收维持电源电压 VSUS。像素单元 510 可包括多个像素电路。每个像素电路可连接至提供扫描信号的一个扫描线, 可连接至提供数据信号(例如, 左图像数据或右图像数据)的一个数据线, 并且可连接至提供发射控制信号 ECS 和补偿控制信号 TCS 的控制线。此外, 每个像素电路可接收第一电源电压 ELVDD 和第二电源电压 ELVSS。在示例性实施方式中, 每个像素电路还可接收维持电源电压 VSUS。

[0145] 像素电路可位于扫描线 SL1 至 SL<sub>n</sub> 与数据线 DL1 至 DL<sub>m</sub> 的交叉点处。因此, 像素单元 510 可包括  $n*m$  个像素电路(即, 像素电路的数量为  $n*m$ )。时序控制单元 540 可通过生成并向扫描驱动单元 520、数据驱动单元 530、控制信号生成单元 550 和供电单元 560 提供多个时序控制信号 CTL1、CTL2、CTL3 和 CTL4 来控制扫描驱动单元 520、数据驱动单元 530、控制信号生成单元 550 和供电单元 560。

[0146] 如上所述, 各个像素电路可基于第一电源电压 ELVDD、第二电源电压 ELVSS、扫描信号、数据信号、发射控制信号 ECS、补偿控制信号 TCS 和 / 或维持电源电压 VSUS 进行操作。在示例性实施方式中, 每个像素电路可包括有机发光二极管、第一至第五 PMOS 晶体管和第一至第三电容器。在另一示例性实施方式中, 每个像素电路可包括有机发光二极管、第一至第五 NMOS 晶体管和第一至第三电容器。每个像素电路可具有 5T-3C 结构(即, 具有 5 个晶体管和 3 个电容器的结构)。

[0147] 在执行左图像的发射操作的时候, 每个像素电路可存储右图像数据, 并且在执行右图像的发射操作的时候, 每个像素电路可存储左图像数据。有机发光显示装置 500 可通过交替地执行用于显示第一图像(例如, 左图像)的第一显示操作和用于显示第二图像(例如, 右图像)的第二显示操作来实现立体图像。第一显示操作可包括第一初始数据写入操作、第一复位操作、第一阈值电压补偿操作、第一数据写入操作和第一发射操作。第二显示操作可包括第二初始数据写入操作、第二复位操作、第二阈值电压补偿操作、第二数据写入操作和第二发射操作。当第一显示操作和第二显示操作交替执行时, 第一显示操作的第一发射操作和第二显示操作的第二初始数据写入操作同时执行, 并且第二显示操作的第二发射操作和第一显示操作的第一初始数据写入操作同时执行。

[0148] 可通过各个扫描线 SL1 至 SL<sub>n</sub> 为有机发光显示装置 500 的全部像素电路顺序地执行初始数据写入操作(即, 第一初始数据写入操作或第二初始数据写入操作)。另一方面, 可为有机发光显示装置 500 的全部像素电路同时执行复位操作(即, 第一复位操作或第二复位操作)、阈值电压补偿操作(即, 第一阈值电压补偿操作或第二阈值电压补偿操作)、数据写入操作(即, 第一数据写入操作或第二数据写入操作)或发射操作(即, 第一发射操作或第

二发射操作)。如上所述,在有机发光显示装置 500 中,在第二图像数据(即,右图像或左图像)通过有机发光显示装置 500 的各个像素电路同时显示的时候,第一图像数据(即,左图像数据或右图像数据)可顺序地写入有机发光显示装置 500 的各个像素电路中。类似地,在第一图像(即,左图像或右图像)通过有机发光显示装置 500 的各个像素电路同时显示的时候,第二图像数据(即,右图像数据或左图像数据)可顺序地写入有机发光显示装置 500 的各个像素电路中。结果,采用同时发射方法的有机发光显示装置 500 可以高速操作,可降低功耗,并且可提高亮度。

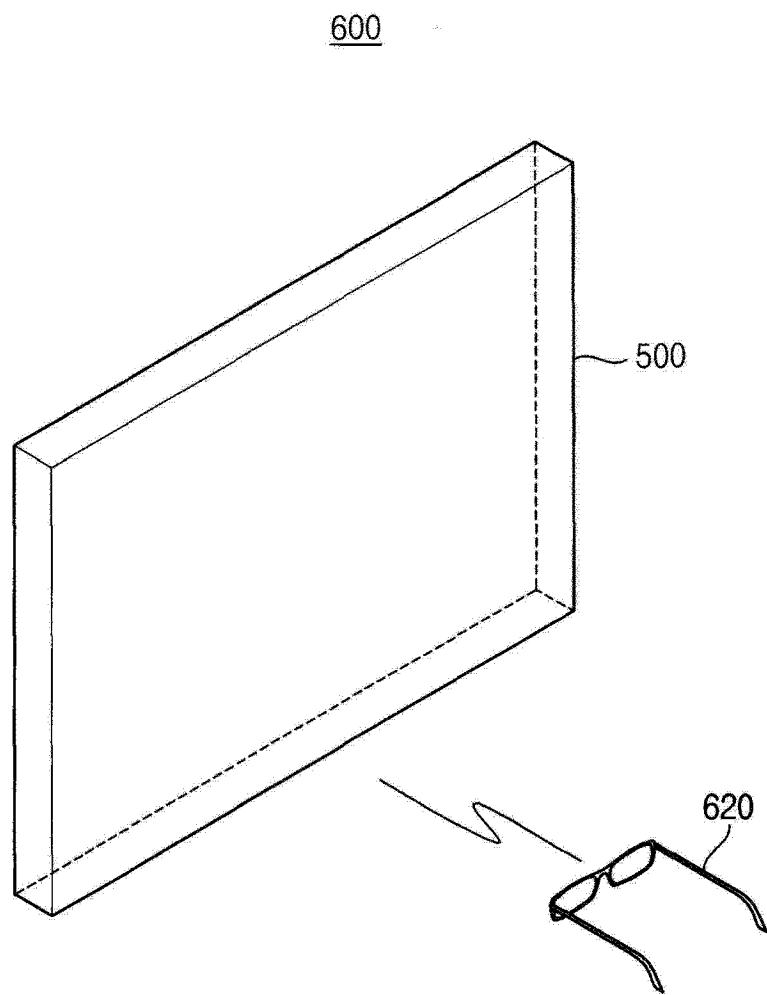

[0149] 图 13 示出了采用快门眼镜方法的立体图像显示系统 600 的图示,其中立体图像显示系统 600 包括图 12 的有机发光显示装置。

[0150] 参照图 13,立体图像显示系统 600 可包括有机发光显示装置 500 和快门眼镜 620。

[0151] 有机发光显示装置 500 可通过交替地显示左图像(即,左图像帧)和右图像(即,右图像帧)实现立体图像。在一些示例性实施方式中,有机发光显示装置 500 可生产用于分别向左眼和右眼交替地提供左图像和右图像的同步信号。因此,左图像和右图像可以与同步信号同步。当有机发光显示装置 500 交替地显示左图像和右图像时,快门眼镜 620 可分别与左图像和右图像同步的方式打开 / 关闭左快门和右快门。例如,快门眼镜 620 可在有机发光显示装置 500 显示左图像时基于同步信号打开左快门,并且在有机发光显示装置 500 显示右图像时基于同步信号打开右快门。在一些示例性实施方式中,有机发光显示装置 500 可通过使用各种有线 / 无线方法向快门眼镜 620 提供同步信号。

[0152] 有机发光显示装置 500 的每个像素电路可具有如上所述包括有机发光二极管、第一至第五 PMOS 晶体管和第一至第三电容器的 5T-3C 结构。在另一种实现中,有机发光显示装置 500 的每个像素电路可具有如上所述包括有机发光二极管、第一至第五 NMOS 晶体管和第一至第三电容器的 5T-3C 结构。在执行左图像数据的发射操作的时候,有机发光显示装置 500 的每个像素电路可存储右图像数据,并且在执行右图像的发射操作的时候,有机发光显示装置 500 的每个像素电路可存储左图像数据。因此,有机发光显示装置 500 可以高速操作,可降低功耗,并且可提高亮度。

[0153] 图 14 示出了采用视差屏障方法的立体图像显示系统 700 的图示,其中立体图像显示系统 700 包括图 12 的有机发光显示装置。

[0154] 参照图 14,立体图像显示系统 700 可包括有机发光显示装置 500 和视差屏障 720。

[0155] 有机发光显示装置 500 可通过交替地显示左图像(即,左图像帧)和右图像(即,右图像帧)实现立体图像。在一些示例性实施方式中,有机发光显示装置 500 可生成用于分别向左眼和右眼交替提供左图像和右图像的同步信号。因此,左图像和右图像可以与同步信号同步。当有机发光显示装置 500 交替地显示左图像和右图像时,视差屏障 720 可允许左图像和右图像交替地通过。详细地,视差屏障 720 可通过改变视差屏障 720 的开放区和阻挡区的位置向左眼和右眼交替地提供左图像和右图像。

[0156] 如上所述,有机发光显示装置 500 的每个像素电路可具有包括有机发光二极管、第一至第五 PMOS 晶体管和第一至第三电容器的 5T-3C 结构,或可具有包括有机发光二极管、第一至第五 NMOS 晶体管和第一至第三电容器的 5T-3C 结构。在此基础上,在执行左图像的发射操作的时候,有机发光显示装置 500 的每个像素电路可存储右图像数据,并且在执行右图像的发射操作的时候,有机发光显示装置 500 的每个像素电路可存储左图像数据。

因此,有机发光显示装置 500 可以高速操作,并且可降低功耗(即,可提高亮度)。

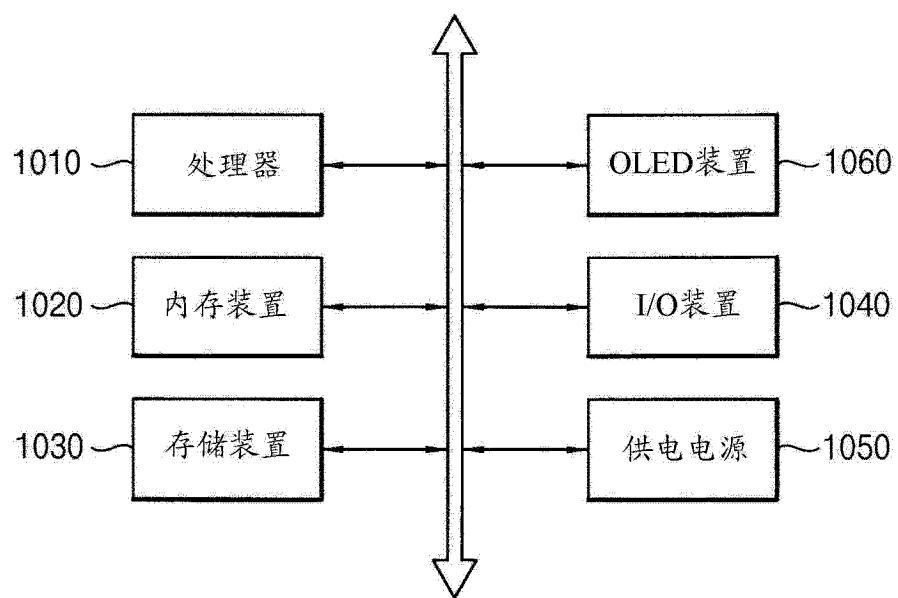

[0157] 图 15 示出了具有图 12 的有机发光显示装置的电气装置 1000 的框图。

[0158] 参照图 15,电气装置 1000 可包括处理器 1010、内存装置(memory device) 1020、存储装置(storage device) 1030、输入 / 输出(I/O)装置 1040、供电电源 1050 和有机发光显示装置 1060。有机发光显示装置 1060 可对应于图 12 的有机发光显示装置 500。此外,电气装置 1000 还可包括用于与视频卡、声卡、存储卡、通用串行总线(USB)装置、其它电气装置等通信的多个端口。

[0159] 处理器 1010 可执行各种计算功能。处理器 1010 可以是微处理器、中央处理单元(CPU)等。处理器 1010 可通过地址总线、控制总线、数据总线等连接至其他部件。而且,处理器 1010 可连接至诸如外设部件互连(PCI)总线的扩展总线。内存装置 1020 可存储数据用于电气装置 1000 的操作。例如,内存装置 1020 可包括至少一个非易失内存装置(诸如可擦可编程只读存储器(EPROM)装置、电可擦除可编程只读存储器(EEPROM)装置、闪存装置、相变随机存取存储器(PRAM)装置、电阻式随机存取存储器(RRAM)装置、纳米浮栅存储器(NFGM)装置、聚合物随机存取存储器(PoRAM)装置、磁性随机存取存储器(MRAM)装置、铁电随机存取存储器(FRAM)装置等)、和 / 或至少一个易失内存装置(诸如,动态随机存取存储器(DRAM)装置、静态随机存取存储器(SRAM)装置、可移动动态随机存取存储器(可移动DRAM)装置等)。存储装置 1030 可以是固态驱动装置、硬盘驱动装置、CD-ROM 装置等。

[0160] I/O 装置 1040 可以是输入装置(诸如键盘、小型键盘、鼠标、触摸屏等)、和 / 或输出装置(诸如,打印机、扬声器等)。在一些示例性实施方式中,有机发光显示装置 1060 可被包括作为 I/O 装置 1040 中的输出装置。供电电源 1050 可为电气装置 1000 的操作供电。有机发光显示装置 1060 可通过总线或其它通信链路与其它部件通信。

[0161] 有机发光显示装置 1060 可如上所述通过分别向左眼和右眼交替地提供左图像(即,左图像帧)和右图像(即,右图像帧)实现立体图像。有机发光显示装置 1060 的每个像素电路可具有包括有机发光二极管、第一至第五 PMOS 晶体管和第一至第三电容器的 5T-3C 结构。在另一种实现中,有机发光显示装置 1060 的每个像素电路可具有包括 有机发光二极管、第一至第五 NMOS 晶体管和第一至第三电容器的 5T-3C 结构。在执行左图像的发射操作的时候,有机发光显示装置 1060 的每个像素电路可存储右图像数据,并且在执行右图像的发射操作的时候,有机发光显示装置 1060 的每个像素电路可存储左图像数据。因此,有机发光显示装置 1060 可以高速操作,可降低功耗,并且可提高亮度。有机发光显示装置 1060 可为如上所述。有机发光显示装置 1060 可被应用于具有立体图像显示装置的适当系统,其中立体图像显示装置例如为采用快门眼镜方法的立体图像显示系统、采用视差屏障方法的立体图像显示系统等。

[0162] 实施方式可应用于具有有机发光显示装置的电气装置。例如,实施方式可应用于电视、计算机监视器、手提电脑、数字照相机、移动电话、智能电话、个人数字助理(PDA)、便携式多媒体播放器(PMP)、MP3 播放器、导航系统、视讯电话等。

[0163] 通过总结和回顾,使用有机发光显示装置实现立体图像的方法可包括在有机发光显示装置上交替地显示左图像和右图像。可分别向左眼和右眼提供左图像和右图像。

[0164] 采用顺序发射方法的一般有机发光显示装置在实现立体图像时可能呈现低亮度和高功耗,这是因为一般有机发光显示装置在交替显示左图像和右图像时在左图像(即,

左图像帧)和右图像(即,右图像帧)之间插入黑图像(即,黑图像帧)以分离右图像与左图像。例如,在实现 60Hz 的立体图像的情况下,可顺序地显示 60Hz 的左图像、60Hz 的黑图像、60Hz 的右图像和 60Hz 的黑图像,从而为一般有机发光显示装置采用 240Hz (即 60Hz+60Hz+60Hz+60Hz) 的快工作速度。此外,当黑图像以上面的方式插到左图像与右图像之间时,发射时间和亮度都可能减半。而且,可能消耗高功率以获得与不插入黑图像的情况相同的亮度。

[0165] 如上所述,示例性实施方式通常涉及立体(3D)图像显示技术。一些示例性实施方式提供像素电路,当包括像素电路的有机发光显示装置基于同时发射方法实现立体图像时,可在左图像发射周期显示左图像的时候存储右图像,并且可在右图像发射周期显示右图像的时候 存储左图像。根据实施方式的像素电路可以高速工作,并且可降低功耗和 / 或基于相同的功耗提高亮度。

[0166] 一些示例性实施方式提供了驱动像素电路的方法,以当包括像素电路的有机发光显示装置基于同时发射方法实现立体图像时,在左图像发射周期显示左图像的同时将右图像数据写入像素电路,并且在右图像发射周期显示右图像的同时将左图像数据写入像素电路。

[0167] 一些示例性实施方式提供了具有像素电路的有机发光显示装置。当根据示例性实施方式的有机发光显示装置基于同时发射方法实现立体图像时,有机发光显示装置可以高速操作,并且可降低功耗。

[0168] 本文中已经公开了示例性实施方式,尽管采用了具体的术语,但是这些术语仅被用作且解释为一般的、描述性的而非用于限制。在一些实例中,对与递交本申请同领域的技术人员而言显而易见的是,基于具体实施方式描述的特征、特点和 / 或元素可单独使用或与基于其他实施方式描述的特征、特点和 / 或元素结合使用,除非特别指出并非如此。由此,本领域技术人员应理解,可进行形式和细节的各种变化而不会背离由权利要求所限定的本实用新型的精神和范围。

100

图 1

图 2

图 3

图 4A

图 4B

图 4C

图 4D

图 4E

图 5

200

图 6

300

图 7

图 8A

图 8B

图 8C

图 8D

图 8E

400

图 9

图 10

图 11

500

图 12

图 13

图 14

1000

图 15

|                |                                                                                                                                                                                                                                                                                                 |         |            |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路以及有机发光显示装置                                                                                                                                                                                                                                                                                  |         |            |

| 公开(公告)号        | <a href="#">CN203118410U</a>                                                                                                                                                                                                                                                                    | 公开(公告)日 | 2013-08-07 |

| 申请号            | CN201220601021.5                                                                                                                                                                                                                                                                                | 申请日     | 2012-11-14 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                                                                                                                                                                                                                                                        |         |            |

| 申请(专利权)人(译)    | 三星显示有限公司                                                                                                                                                                                                                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 三星显示有限公司                                                                                                                                                                                                                                                                                        |         |            |

| [标]发明人         | 黄荣仁                                                                                                                                                                                                                                                                                             |         |            |

| 发明人            | 黄荣仁                                                                                                                                                                                                                                                                                             |         |            |

| IPC分类号         | G09G3/32                                                                                                                                                                                                                                                                                        |         |            |

| CPC分类号         | G09G2300/0852 G09G2310/0216 G09G2310/0262 G09G2310/0251 G09G2300/0866 G09G3/3233 G09G2310/0202 G09G2300/0819 G09G3/003 H04N13/0497 G09G2310/063 H04N13/0438 G09G3/3258 G09G3/3266 G09G3/3275 G09G2300/0469 G09G2300/0809 G09G2310/08 G09G2320/0252 G09G2330/00 H04N13/315 H04N13/341 H04N13/398 |         |            |

| 代理人(译)         | 刘铮                                                                                                                                                                                                                                                                                              |         |            |

| 优先权            | 1020120029639 2012-03-23 KR                                                                                                                                                                                                                                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>                                                                                                                                                                                                                                                  |         |            |

## 摘要(译)

公开了像素电路和有机发光显示装置。像素电路包括：有机发光二极管；第一PMOS晶体管，连接在第一电源电压与有机发光二极管的阳极之间；第二PMOS晶体管，连接在第一节点与有机发光二极管的阳极之间；第一电容器，连接在第二节点与第一节点之间；第二电容器，连接在第一电源电压与第二节点之间；第三PMOS晶体管，连接在数据线与第二节点之间；第四PMOS晶体管，连接在第三节点与第二节点之间；第三电容器，连接在第三节点与第三PMOS晶体管的栅端之间；以及第五PMOS晶体管，连接在数据线与第三节点之间。根据本实用新型的像素电路和有机发光显示装置能够高速操作、并且可降低功耗。