(12)发明专利申请

(10)申请公布号 CN 111384071 A

(43)申请公布日 2020.07.07

(21)申请号 202010218961.5

(22)申请日 2020.03.25

(71)申请人 京东方科技股份有限公司

地址 100015 北京市朝阳区酒仙桥路10号

申请人 福州京东方光电科技有限公司

(72)发明人 曾勇 王洋 邹振游 席文星

余雪

(74)专利代理机构 北京正理专利代理有限公司

11257

代理人 付生辉

(51)Int.Cl.

H01L 27/12(2006.01)

H01L 21/77(2017.01)

H01L 27/32(2006.01)

权利要求书2页 说明书9页 附图3页

(54)发明名称

一种像素结构、阵列基板、显示装置和制作方法

(57)摘要

本发明公开了一种像素结构、阵列基板、显示装置和制作方法，所述像素结构包括层叠设置在衬底上的驱动电路和电致发光显示器件，所述驱动电路包括第一薄膜晶体管和第二薄膜晶体管，其中所述第一薄膜晶体管和第二薄膜晶体管为氧化物薄膜晶体管，所述第二薄膜晶体管包括第一栅绝缘层；设置在所述第一栅绝缘层上的薄膜层，所述薄膜层的介电常数大于预设置的介电常数阈值；以及覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层。本发明提供的实施例通过设置在第二薄膜晶体管的包括第一栅绝缘层、第二栅绝缘层和位于两者之间的薄膜层的三明治结构的栅绝缘层，有效提高像素结构内驱动薄膜晶体管的驱动能力，从而解决现有技术中的问题，具有广泛的应用前景。

A

CN

1. 一种像素结构,包括层叠设置在衬底上的驱动电路和电致发光显示器件,其特征在于,所述驱动电路包括第一薄膜晶体管和第二薄膜晶体管,其中

所述第一薄膜晶体管为氧化物薄膜晶体管,响应于输入的控制信号将输入的数据信号传输至所述第二薄膜晶体管;

所述第二薄膜晶体管为氧化物薄膜晶体管,响应于所述数据信号驱动所述电致发光器件发光,包括

第一栅绝缘层;

设置在所述第一栅绝缘层上的薄膜层,所述薄膜层的介电常数大于预设置的介电常数阈值;以及

覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层。

2. 根据权利要求1所述的像素结构,其特征在于,所述第二薄膜晶体管的第二有源层在所述衬底上的正投影覆盖所述薄膜层在衬底上的正投影。

3. 根据权利要求1所述的像素结构,其特征在于,所述第一薄膜晶体管和第二薄膜晶体管为底栅结构。

4. 根据权利要求1所述的像素结构,其特征在于,所述薄膜层的材料为PZT、SrTiO<sub>3</sub>和BaTiO<sub>3</sub>中的一种。

5. 根据权利要求1所述的像素结构,其特征在于,所述薄膜层的厚度大于100nm且小于300nm。

6. 根据权利要求1所述的像素结构,其特征在于,包括:

衬底;

设置在所述衬底上的所述第一薄膜晶体管的第一栅极;

覆盖所述第一栅极和衬底的栅绝缘层;

设置在所述栅绝缘层上的所述第一薄膜晶体管的第一有源层,所述第一有源层和所述第一栅极相对应;

设置在所述栅绝缘层上的所述第一薄膜晶体管的第一源极和第一漏极、以及所述第二薄膜晶体管的第二栅极,所述第一源极和第一漏极分别与所述第一有源层电连接;

覆盖所述第一源极、第一漏极、第二栅极、第一有源层和栅绝缘层的第一栅绝缘层;

设置在所述第一栅绝缘层上的所述第二薄膜晶体管的薄膜层;

覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层;

设置在所述第二栅绝缘层上的所述第二薄膜晶体管的第二有源层,所述第二有源层在所述衬底上的正投影覆盖所述薄膜层在所述衬底上的正投影;

设置在所述第二栅绝缘层上的所述第二薄膜晶体管的第二源极和第二漏极,所述第二源极和第二漏极分别与所述第二有源层电连接;

覆盖所述第二源极、第二漏极、第二有源层和第二栅绝缘层的平坦化层;

设置在所述平坦化层上的所述电致发光显示器件。

7. 一种阵列基板,其特征在于,包括阵列排布的如权利要求1-6中任一项所述的像素结构。

8. 一种显示装置,其特征在于,包括如权利要求7所述的阵列基板。

9. 一种制作权利要求7所述的阵列基板的制作方法,其特征在于,包括:

在衬底上形成驱动电路,所述驱动电路包括第一薄膜晶体管和第二薄膜晶体管,其中所述第一薄膜晶体管为氧化物薄膜晶体管,响应于输入的控制信号将输入的数据信号传输至所述第二薄膜晶体管;所述第二薄膜晶体管为氧化物薄膜晶体管,响应于所述数据信号驱动所述电致发光器件发光,包括第一栅绝缘层;设置在所述第一栅绝缘层上的薄膜层,所述薄膜层的介电常数大于预设置的介电常数阈值;以及覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层;

在所述驱动电路上形成电致发光器件。

10.根据权利要求9所述的制作方法,其特征在于,包括:

在衬底上形成第一薄膜晶体管的第一栅极;

形成覆盖所述第一栅极和衬底的栅绝缘层;

在所述栅绝缘层上形成所述第一薄膜晶体管的第一有源层,所述第一有源层和所述第一栅极相对应;

在所述栅绝缘层上形成所述第一薄膜晶体管的第一源极和第一漏极、以及第二薄膜晶体管的第二栅极,所述第一源极和第一漏极分别与所述第一有源层电连接;

形成覆盖所述第一源极、第一漏极、第二栅极、第一有源层和栅绝缘层的第一栅绝缘层;

在所述第一栅绝缘层上形成薄膜层;

形成覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层;

在所述第二栅绝缘层上形成所述第二薄膜晶体管的第二有源层,所述第二有源层在所述衬底上的正投影覆盖所述薄膜层在所述衬底上的正投影;

在所述第二栅绝缘层上形成所述第二薄膜晶体管的第二源极和第二漏极,所述第二源极和第二漏极分别与所述第二有源层电连接;

形成覆盖所述第二源极、第二漏极、第二有源层和第二栅绝缘层的平坦化层;

在所述平坦化层上形成电致发光显示器件。

## 一种像素结构、阵列基板、显示装置和制作方法

### 技术领域

[0001] 本发明涉及显示技术领域,特别是涉及一种像素结构、阵列基板、显示装置和制作方法。

### 背景技术

[0002] 电致发光显示器件需要2T1C(两个薄膜晶体管和一个电容)来驱动像素发光。现有技术中,电致发光显示器件主要采用基于低温多晶硅的薄膜晶体管(LTPS)来驱动像素发光,由于LTPS具有非常高的迁移率,因此可以获得足够大的电流驱动发光物质发光。但是,基于LTPS的薄膜晶体管存在以下问题:不均匀且过大的漏电流、不足的驱动强度、较差的面积效率、磁滞以及其它问题。

[0003] 目前,苹果公司为了解决以上问题提出了基于LTP0的像素设计结果,即扫描线薄膜晶体管采用氧化物薄膜晶体管,氧化物薄膜晶体管具有较低的漏电流,能够维持稳定的驱动栅极电压;而驱动薄膜晶体管采用LTPS薄膜晶体管,LTPS具有很高的迁移率,OLED是电流驱动发光,大电流能够使其发出足够强的RGB光源。然而,LTPS制备工艺非常复杂,需要非常高的工艺温度,因此需要制备顶栅的薄膜晶体管结构以避免硅晶化时的高温对其它膜层的影响。然而,这种结构会带来许多问题,例如:需要缓冲层来减少衬底对有源层的影响,部分有源层需要重掺杂来提高导电性以减少有源层和源/漏电极的接触问题等。

### 发明内容

[0004] 为了解决上述问题至少之一,本发明第一个实施例提供一种像素结构,包括层叠设置在衬底上的驱动电路和电致发光显示器件,所述驱动电路包括第一薄膜晶体管和第二薄膜晶体管,其中

[0005] 所述第一薄膜晶体管为氧化物薄膜晶体管,响应于输入的控制信号将输入的数据信号传输至所述第二薄膜晶体管;

[0006] 所述第二薄膜晶体管为氧化物薄膜晶体管,响应于所述数据信号驱动所述电致发光器件发光,包括

[0007] 第一栅绝缘层;

[0008] 设置在所述第一栅绝缘层上的薄膜层,所述薄膜层的介电常数大于预设置的介电常数阈值;以及

[0009] 覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层。

[0010] 进一步的,所述第二薄膜晶体管的第二有源层在所述衬底上的正投影覆盖所述薄膜层在衬底上的正投影。

[0011] 进一步的,所述第一薄膜晶体管和第二薄膜晶体管为底栅结构。

[0012] 进一步的,所述薄膜层的材料为PZT、SrTiO<sub>3</sub>和BaTiO<sub>3</sub>中的一种。

[0013] 进一步的,所述薄膜层的厚度大于100nm且小于300nm。

[0014] 进一步的,包括:

- [0015] 衬底；

- [0016] 设置在所述衬底上的所述第一薄膜晶体管的第一栅极；

- [0017] 覆盖所述第一栅极和衬底的栅绝缘层；

- [0018] 设置在所述栅绝缘层上的所述第一薄膜晶体管的第一有源层，所述第一有源层和所述第一栅极相对应；

- [0019] 设置在所述栅绝缘层上的所述第一薄膜晶体管的第一源极和第一漏极、以及所述第二薄膜晶体管的第二栅极，所述第一源极和第一漏极分别与所述第一有源层电连接；

- [0020] 覆盖所述第一源极、第一漏极、第二栅极、第一有源层和栅绝缘层的第一栅绝缘层；

- [0021] 设置在所述第一栅绝缘层上的所述第二薄膜晶体管的薄膜层；

- [0022] 覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层；

- [0023] 设置在所述第二栅绝缘层上的所述第二薄膜晶体管的第二有源层，所述第二有源层在所述衬底上的正投影覆盖所述薄膜层在所述衬底上的正投影；

- [0024] 设置在所述第二栅绝缘层上的所述第二薄膜晶体管的第二源极和第二漏极，所述第二源极和第二漏极分别与所述第二有源层电连接；

- [0025] 覆盖所述第二源极、第二漏极、第二有源层和第二栅绝缘层的平坦化层；

- [0026] 设置在所述平坦化层上的所述电致发光显示器件。

- [0027] 本发明第二个实施例提供一种阵列基板，包括阵列排布的第一个实施例所述的像素结构。

- [0028] 本发明第三个实施例提供一种显示装置，包括第二个实施例所述的阵列基板。

- [0029] 本发明第四个实施例提供一种制作第二个实施例所述的阵列基板的制作方法，包括：

- [0030] 在衬底上形成驱动电路，所述驱动电路包括第一薄膜晶体管和第二薄膜晶体管，其中所述第一薄膜晶体管为氧化物薄膜晶体管，响应于输入的控制信号将输入的数据信号传输至所述第二薄膜晶体管；所述第二薄膜晶体管为氧化物薄膜晶体管，响应于所述数据信号驱动所述电致发光器件发光，包括第一栅绝缘层；设置在所述第一栅绝缘层上的薄膜层，所述薄膜层的介电常数大于预设置的介电常数阈值；以及覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层；

- [0031] 在所述驱动电路上形成电致发光器件。

- [0032] 进一步的，包括：

- [0033] 在衬底上形成第一薄膜晶体管的第一栅极；

- [0034] 形成覆盖所述第一栅极和衬底的栅绝缘层；

- [0035] 在所述栅绝缘层上形成所述第一薄膜晶体管的第一有源层，所述第一有源层和所述第一栅极相对应；

- [0036] 在所述栅绝缘层上形成所述第一薄膜晶体管的第一源极和第一漏极、以及第二薄膜晶体管的第二栅极，所述第一源极和第一漏极分别与所述第一有源层电连接；

- [0037] 形成覆盖所述第一源极、第一漏极、第二栅极、第一有源层和栅绝缘层的第一栅绝缘层；

- [0038] 在所述第一栅绝缘层上形成薄膜层；

- [0039] 形成覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层；

- [0040] 在所述第二栅绝缘层上形成所述第二薄膜晶体管的第二有源层，所述第二有源层在所述衬底上的正投影覆盖所述薄膜层在所述衬底上的正投影；

- [0041] 在所述第二栅绝缘层上形成所述第二薄膜晶体管的第二源极和第二漏极，所述第二源极和第二漏极分别与所述第二有源层电连接；

- [0042] 形成覆盖所述第二源极、第二漏极、第二有源层和第二栅绝缘层的平坦化层；

- [0043] 在所述平坦化层上形成电致发光显示器件。

- [0044] 本发明的有益效果如下：

- [0045] 本发明针对目前现有的问题，制定一种像素结构、阵列基板、显示装置和制作方法，通过设置在第二薄膜晶体管的包括第一栅绝缘层、第二栅绝缘层和位于两者之间的薄膜层的三明治结构的栅绝缘层，有效提高像素结构内驱动薄膜晶体管的驱动能力，从而弥补了现有技术中存在的问题，具有广泛的应用前景。

## 附图说明

[0046] 为了更清楚地说明本发明实施例中的技术方案，下面将对实施例描述中所需要使用的附图作简单地介绍，显而易见地，下面描述中的附图仅仅是本发明的一些实施例，对于本领域普通技术人员来讲，在不付出创造性劳动的前提下，还可以根据这些附图获得其他的附图。

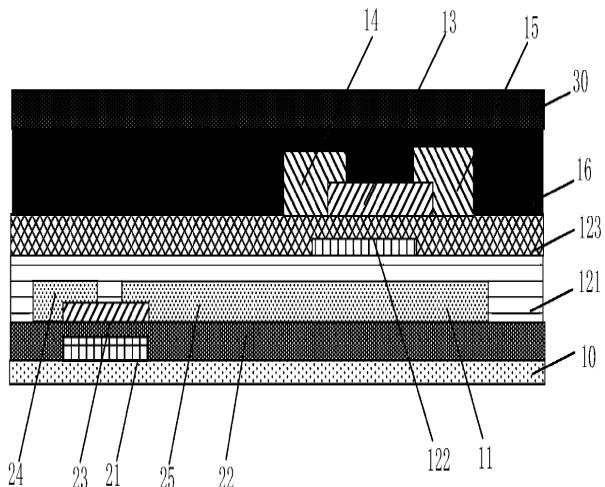

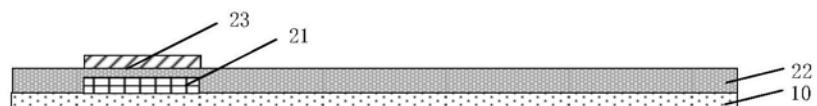

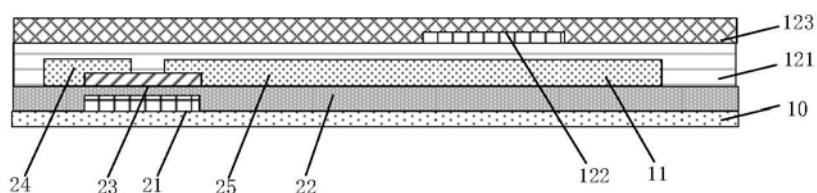

- [0047] 图1示出本发明的一个实施例所述像素结构的结构示意图；

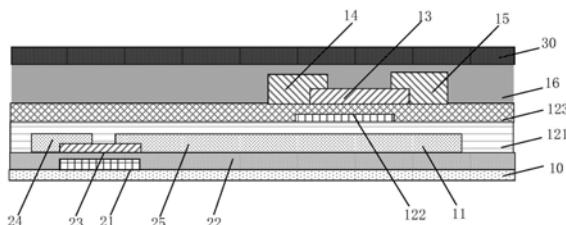

- [0048] 图2示出本发明的一个实施例所述阵列基板的制作流程图；

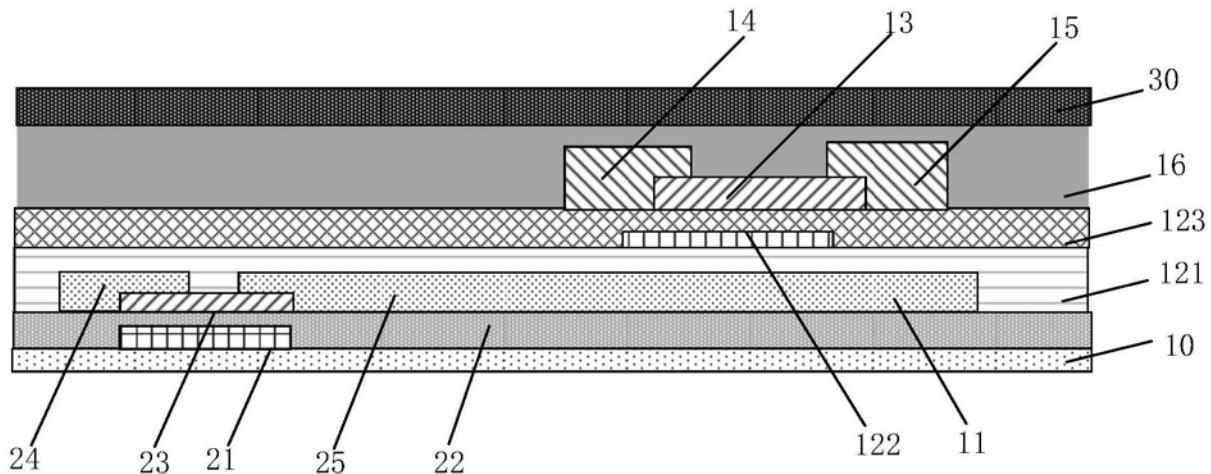

- [0049] 图3a-3j示出本发明的一个实施例所述阵列基板的分阶段制作的示意图。

## 具体实施方式

[0050] 为了更清楚地说明本发明，下面结合优选实施例和附图对本发明做进一步的说明。附图中相似的部件以相同的附图标记进行表示。本领域技术人员应当理解，下面所具体描述的内容是说明性的而非限制性的，不应以此限制本发明的保护范围。

[0051] 需要说明的是，本文中所述的“在……上”、“在……上形成”和“设置在……上”可以表示一层直接形成或设置在另一层上，也可以表示一层间接形成或设置在另一层上，即两层之间还存在其它的层。在本文中，除非另有说明，所采用的术语“位于同一层”指的是两个层、部件、构件、元件或部分可以通过同一构图工艺形成，并且，这两个层、部件、构件、元件或部分一般由相同的材料形成。在本文中，除非另有说明，表述“构图工艺”一般包括光刻胶的涂布、曝光、显影、刻蚀、光刻胶的剥离等步骤。表述“一次构图工艺”意指使用一块掩模板形成图案化的层、部件、构件等的工艺。

[0052] 针对现有技术中存在的缺点和不足之处，如图1所示，本发明的一个实施例提供了一种像素结构，包括层叠设置在衬底10上的驱动电路和电致发光显示器件30，所述驱动电路包括第一薄膜晶体管和第二薄膜晶体管，其中所述第一薄膜晶体管为氧化物薄膜晶体管，响应于输入的控制信号将输入的数据信号传输至所述第二薄膜晶体管；所述第二薄膜晶体管为氧化物薄膜晶体管，响应于所述数据信号驱动所述电致发光器件发光，包括：第一栅绝缘层121；设置在所述第一栅绝缘层121上的薄膜层122，所述薄膜层122的介电常数大

于预设置的介电常数阈值；以及覆盖所述第一栅绝缘层121和薄膜层122的第二栅绝缘层123。

[0053] 本实施例为用于2T1C结构的电致发光显示器件的像素结构，所述第一薄膜晶体管为氧化物薄膜晶体管用于扫描线薄膜晶体管，所述第二薄膜晶体管为氧化物薄膜晶体管用于驱动薄膜晶体管，所述第一薄膜晶体管响应于控制线输入的控制信号导通，将数据线输入的数据信号传输至所述第二薄膜晶体管，所述第二薄膜晶体管响应于所述数据信号导通以驱动电致发光器件发光。本实施例针对现有技术中氧化物薄膜晶体管本身迁移率较低、驱动能力较差的问题，通过设置在第二薄膜晶体管的包括第一栅绝缘层、第二栅绝缘层和位于两者之间的薄膜层的三明治结构的栅绝缘层，有效提高氧化物薄膜晶体管的迁移率，从而提高驱动薄膜晶体管的驱动电流。具体原理如下：

[0054] 薄膜晶体管的源漏电流 $I_d$ 表达式如下所示：

$$[0055] I_d = \frac{\mu_d W C_g}{L} \left[ (V_g - V_{th}) V_d - \frac{V_d^2}{2} \right]$$

[0056] 其中， $\mu_d$ 是薄膜晶体管迁移率， $C_g$ 是栅绝缘层电容， $W/L$ 是薄膜晶体管沟道的宽长比， $V_{th}$ 是薄膜晶体管的阈值电压， $V_g$ 和 $V_d$ 分别是施加在薄膜晶体管的栅极和源/漏电极的电压。

[0057] 由上式可知，薄膜晶体管的源漏电流与有源层迁移率和栅极绝缘层电容成正比，而LTPS形成能够大电流驱动有机发光材料发光主要是因为其具有非常高的迁移率。根据以上公式，本发明为了提高基于氧化物的驱动薄膜晶体管的驱动能力，采用提高栅绝缘层电容的方式实现。

[0058] 其中，所述介电常数阈值数倍于现有常用薄膜材料的介电常数，例如将介电常数阈值设置为20, 50或者更高，在本实施例中，所述薄膜层的材料为PZT、SrTiO<sub>3</sub>和BaTiO<sub>3</sub>中的一种，其中，所述PZT的介电常数6500，所述SrTiO<sub>3</sub>的介电常数 $>10^5$ ，所述BaTiO<sub>3</sub>的介电常数1400。所述薄膜层的厚度大于100nm且小于300nm。

[0059] 值得说明的是，本实施例对薄膜层的材料不做限定，本领域技术人员应当根据实际应用需求选择适当材料的薄膜，以提高栅绝缘层的电容为选择准则，在此不再赘述。

[0060] 同时，本实施例对所述第一薄膜晶体管和第二薄膜晶体管的具体结构不做限定，可以为顶栅结构也可以为底栅结构。

[0061] 考虑到薄膜层可能引起的漏电流，在一个可选的实施例中，所述第二薄膜晶体管的第二有源层在所述衬底上的正投影覆盖所述薄膜层在衬底上的正投影。

[0062] 在本实施例中，当所述第二有源层在所述衬底上的正投影覆盖所述薄膜层在衬底上的正投影时，即所述薄膜层的面积小于等于有源层的面积时，所述薄膜晶体管的栅绝缘层的电容增大，并且不会引起漏电流，有效提高第二薄膜晶体管的性能，从而提高显示装置的显示效果。

[0063] 考虑到简化阵列基板中各薄膜晶体管的制备过程，在一个可选的实施例中，所述第一薄膜晶体管和第二薄膜晶体管为底栅结构。

[0064] 在本实施例中，当作为扫描线薄膜晶体管的第一薄膜晶体管和作为驱动薄膜晶体管的第二薄膜晶体管均为底栅结构时，能够最大限度的共用制作扫描线薄膜晶体管的工艺步骤，例如，所述第二薄膜晶体管的栅极与第一薄膜晶体管的源极和漏极同层设置，所述第

二薄膜晶体管的第一栅绝缘层和第二栅绝缘层与第一薄膜晶体管的层间介质层同层设置。

[0065] 在一个具体的实施例中,所述像素结构包括:

[0066] 衬底10。

[0067] 在本实施例中,在衬底上形成第一薄膜晶体管和第二薄膜晶体管。

[0068] 设置在所述衬底10上的所述第一薄膜晶体管的第一栅极21。

[0069] 在本实施例中,首先在衬底上制作第一薄膜晶体管,所述第一薄膜晶体管为底栅结构,形成第一薄膜晶体管的第一栅极,所述第一栅极的材料可以为Cu、Al、Mo中的一种,也可以为包括Cu、Al、Mo中的至少两种的组合叠层,所述第一栅极的厚度大于100nm且小于500nm。

[0070] 覆盖所述第一栅极21和衬底10的栅绝缘层22。

[0071] 在本实施例中,在第一薄膜晶体管的栅极上形成栅绝缘层,所述栅绝缘层的材料为包括SiNx和Si0x的叠层结构,所述栅绝缘层的厚度大于300nm且小于600nm。

[0072] 设置在所述栅绝缘层22上的所述第一薄膜晶体管的第一有源层23,所述第一有源层23和所述第一栅极21相对应。

[0073] 在本实施例中,在栅绝缘层上形成第一薄膜晶体管的第一有源层,并且第一有源层与第一栅极相对应,第一有源层的材料为IGZO、IZO和IGZTO中的一种,所述第一有源层的厚度为大于10nm且小于100nm。

[0074] 设置在所述栅绝缘层22上的所述第一薄膜晶体管的第一源极24和第一漏极25、以及所述第二薄膜晶体管的第二栅极11,所述第一源极24和第一漏极25分别与所述第一有源层23电连接。

[0075] 在本实施例中,为简化工艺流程步骤,所述第二薄膜晶体管也为底栅结构,所述第二薄膜晶体管的第二栅极与所述第一薄膜晶体管的第一源极和第一漏极同层设置,所述第二栅极的材料可以为Cu、Al、Mo中的一种,也可以为包括Cu、Al、Mo中的至少两种的组合叠层,所述第一栅极的厚度大于100nm且小于500nm。

[0076] 覆盖所述第一源极24、第一漏极25、第二栅极11、第一有源层23和栅绝缘层22的第一栅绝缘层121。

[0077] 在本实施例中,所述第二薄膜晶体管的第一栅绝缘层同时作为第一薄膜晶体管的第一钝化层,所述第一栅绝缘层的材料为包括SiNx和Si0x的叠层结构,所述第一栅绝缘层的厚度大于100nm且小于300nm。

[0078] 设置在所述第一栅绝缘层121上的所述第二薄膜晶体管的薄膜层122。

[0079] 在本实施例中,形成第二薄膜晶体管的薄膜层,所述薄膜层的材料为PZT、SrTiO<sub>3</sub>和BaTiO<sub>3</sub>中的一种,所述薄膜层的厚度大于10nm且小于100nm。同时,考虑到薄膜层过大会产生漏电流,将所述薄膜层设置为与有源层的尺寸相匹配的尺寸,从而确保提高第二薄膜晶体管的栅绝缘层的电容的情况下避免漏电流产生。

[0080] 值得说明的是,所述薄膜层的尺寸与有源层的尺寸相匹配时,在图案化薄膜层材料时可以使用制作有源层的掩膜板,一方面能够确保所述薄膜层的尺寸以避免漏电流产生,另一方面能够降低制作掩膜板的成本。

[0081] 覆盖所述第一栅绝缘层121和薄膜层122的第二栅绝缘层123。

[0082] 在本实施例中,所述第二薄膜晶体管的第二栅绝缘层同时作为第一薄膜晶体管的

第二钝化层,所述第二栅绝缘层的材料为包括SiNx和Si0x的叠层结构,所述第二栅绝缘层的厚度大于100nm且小于300nm.。

[0083] 设置在所述第二栅绝缘层123上的所述第二薄膜晶体管的第二有源层13,所述第二有源层13在所述衬底上的正投影覆盖所述薄膜层122在所述衬底10上的正投影。

[0084] 在本实施例中,第二有源层的材料为IGZO、IZO和IGZTO中的一种,所述第二有源层的厚度为大于10nm且小于100nm。

[0085] 设置在所述第二栅绝缘层123上的所述第二薄膜晶体管的第二源极14和第二漏极15,所述第二源极14和第二漏极15分别与所述第二有源层13电连接。

[0086] 在本实施例中,使用现有工艺步骤继续形成所述第二薄膜晶体管的第二源极和第二漏极。

[0087] 覆盖所述第二源极14、第二漏极15、第二有源层13和第二栅绝缘层122的平坦化层16。

[0088] 在本实施例中,在第一薄膜晶体管和第二薄膜晶体管上形成平坦化层,从而形成所述像素结构的驱动电路。

[0089] 设置在所述平坦化层16上的所述电致发光显示器件30。

[0090] 在本实施例中,在驱动电路上形成电致发光显示器件,从而形成所述像素结构。

[0091] 基于上述像素结构,本申请的一个实施例还提供一种阵列基板,包括阵列排布的上述像素结构。

[0092] 在本实施例中,所述阵列基板利用上述像素结构实现了驱动电路中的扫描薄膜晶体管和驱动薄膜晶体管均为氧化物薄膜晶体管,在提高驱动薄膜晶体管的电流的情况下有效简化阵列基板的制作过程。

[0093] 同时,基于上述阵列基板,本申请的一个实施例还提供一种显示装置,包括上述阵列基板。

[0094] 在本实施例中,所述显示装置包括上述阵列基板,所述显示装置为电致发光二极管显示装置,所述显示装置可以为手机、平板电脑、电视机、显示器、笔记本电脑、数码相框或导航仪等任何具有显示功能的产品或部件。

[0095] 与上述实施例提供的阵列基板相对应,本申请的一个实施例还提供一种制作阵列基板的制作方法,由于本申请实施例提供的制作方法与上述几种实施例提供的阵列基板相对应,因此在前实施方式也适用于本实施例提供的制作方法,在本实施例中不再详细描述。

[0096] 如图2所示,本申请的一个实施例还提供一种制作阵列基板的制作方法,包括:在衬底上形成驱动电路,所述驱动电路包括第一薄膜晶体管和第二薄膜晶体管,其中所述第一薄膜晶体管为氧化物薄膜晶体管,响应于输入的控制信号将输入的数据信号传输至所述第二薄膜晶体管;所述第二薄膜晶体管为氧化物薄膜晶体管,响应于所述数据信号驱动所述电致发光器件发光,包括第一栅绝缘层;设置在所述第一栅绝缘层上的薄膜层,所述薄膜层的介电常数大于预设置的介电常数阈值;以及覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层;在所述驱动电路上形成电致发光器件。

[0097] 本实施例针对现有技术中氧化物薄膜晶体管本身迁移率较低、驱动能力较差的问题,通过设置在第二薄膜晶体管的包括第一栅绝缘层、第二栅绝缘层和位于两者之间的薄膜层的三明治结构的栅绝缘层,有效提高氧化物薄膜晶体管的迁移率,从而提高驱动薄膜

晶体管的驱动电流。

[0098] 在一个具体的实施例中,所述制作方法包括:在衬底上形成第一薄膜晶体管的第一栅极;形成覆盖所述第一栅极和衬底的栅绝缘层;在所述栅绝缘层上形成所述第一薄膜晶体管的第一有源层,所述第一有源层和所述第一栅极相对应;在所述栅绝缘层上形成所述第一薄膜晶体管的第一源极和第一漏极、以及第二薄膜晶体管的第二栅极,所述第一源极和第一漏极分别与所述第一有源层电连接;形成覆盖所述第一源极、第一漏极、第二栅极、第一有源层和栅绝缘层的第一栅绝缘层;在所述第一栅绝缘层上形成薄膜层;形成覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层;在所述第二栅绝缘层上形成所述第二薄膜晶体管的第二有源层,所述第二有源层在所述衬底上的正投影覆盖所述薄膜层在所述衬底上的正投影;在所述第二栅绝缘层上形成所述第二薄膜晶体管的第二源极和第二漏极,所述第二源极和第二漏极分别与所述第二有源层电连接;形成覆盖所述第二源极、第二漏极、第二有源层和第二栅绝缘层的平坦化层;在所述平坦化层上形成电致发光显示器件。

[0099] 在一个具体的实施例中,所述阵列基板的制作步骤如下:

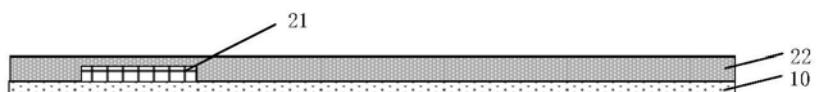

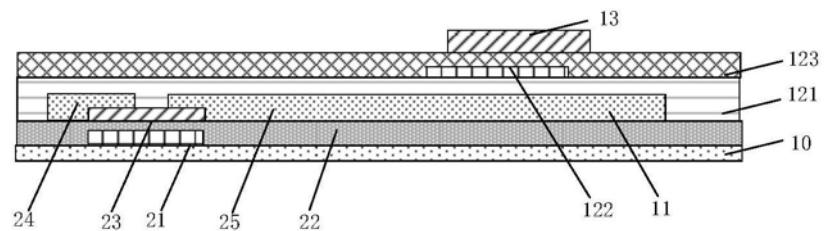

[0100] 第一步,如图3a所示,在衬底10上形成第一薄膜晶体管的第一栅极21。

[0101] 在本实施例中,在衬底上形成第一薄膜晶体管和第二薄膜晶体管,首先在衬底上制作第一薄膜晶体管,所示第一薄膜晶体管为底栅结构,形成第一薄膜晶体管的第一栅极,具体的,在衬底上沉积一层栅极材料层并进行图案化形成第一栅极。

[0102] 所述第一栅极的材料可以为Cu、Al、Mo中的一种,也可以为包括Cu、Al、Mo中的至少两种的组合叠层,所述第一栅极的厚度大于100nm且小于500nm。

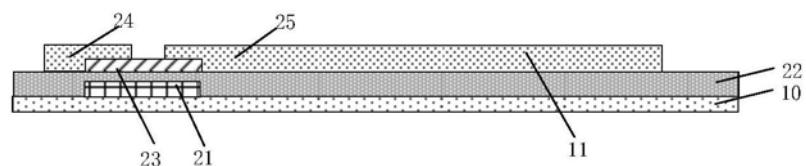

[0103] 第二步,如图3b所示,形成覆盖所述第一栅极21和衬底10的栅绝缘层22。

[0104] 在本实施例中,在第一薄膜晶体管的栅极和衬底上沉积并栅绝缘层,所述栅绝缘层的材料为包括SiNx和Si0x的叠层结构,所述栅绝缘层的厚度大于300nm且小于600nm。

[0105] 第三步,如图3c所示,在所述栅绝缘层22上形成所述第一薄膜晶体管的第一有源层23,所述第一有源层23和所述第一栅极21相对应。

[0106] 在本实施例中,在栅绝缘层上沉积有源层材料层并图案化形成第一薄膜晶体管的第一有源层,并且第一有源层与第一栅极相对应,第一有源层的材料为IGZO、IZO和IGZTO中的一种,所述第一有源层的厚度为大于10nm且小于100nm。

[0107] 第四步,如图3d所示,在所述栅绝缘层22上形成所述第一薄膜晶体管的第一源极24和第一漏极25、以及所述第二薄膜晶体管的第二栅极11,所述第一源极24和第一漏极25分别与所述第一有源层23电连接。

[0108] 在本实施例中,为简化工艺流程步骤,所述第二薄膜晶体管也为底栅结构,所述第二薄膜晶体管的第二栅极与所述第一薄膜晶体管的第一源极和第一漏极同层设置。具体的,在所述栅绝缘层上沉积材料层并图案化形成第一源极、第一漏极和第二栅极,所述第二栅极的材料可以为Cu、Al、Mo中的一种,也可以为包括Cu、Al、Mo中的至少两种的组合叠层,所述第一栅极的厚度大于100nm且小于500nm。

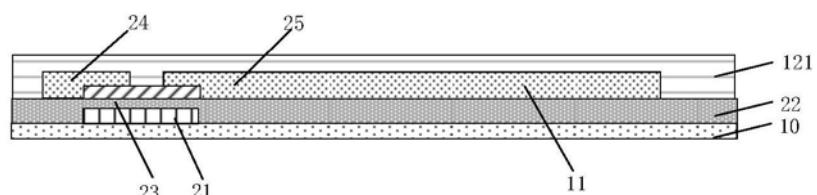

[0109] 第五步,如图3e所示,形成覆盖所述第一源极24、第一漏极25、第二栅极11、第一有源层23和栅绝缘层22的第一栅绝缘层121。

[0110] 在本实施例中,所述第二薄膜晶体管的第一栅绝缘层同时作为第一薄膜晶体管的第一钝化层,具体的,使用沉积工艺形成第一栅极绝缘层。所述第一栅极绝缘层的材料为包括

SiNx和Si0x的叠层结构,所述第一栅绝缘层的厚度大于100nm且小于300nm。

[0111] 第六步,如图3f所示,在所述第一栅绝缘层121上形成所述第二薄膜晶体管的薄膜层122。

[0112] 在本实施例中,形成第二薄膜晶体管的薄膜层,具体的,使用沉积工艺和图案化形成薄膜层,所述薄膜层的材料为PZT、SrTiO<sub>3</sub>和BaTiO<sub>3</sub>中的一种,所述薄膜层的厚度大于10nm且小于100nm。同时,考虑到薄膜层过大会产生漏电流,将所述薄膜层设置为与有源层的尺寸相匹配的尺寸,从而确保提高第二薄膜晶体管的栅绝缘层的电容的情况下避免漏电流产生。

[0113] 第七步,如图3g所示,形成覆盖所述第一栅绝缘层121和薄膜层122的第二栅绝缘层123。

[0114] 在本实施例中,所述第二薄膜晶体管的第二栅绝缘层同时作为第一薄膜晶体管的第二钝化层,具体的,使用沉积工艺形成第二栅极绝缘层,所述第二栅绝缘层的材料为包括SiNx和Si0x的叠层结构,所述第二栅绝缘层的厚度大于100nm且小于300nm。

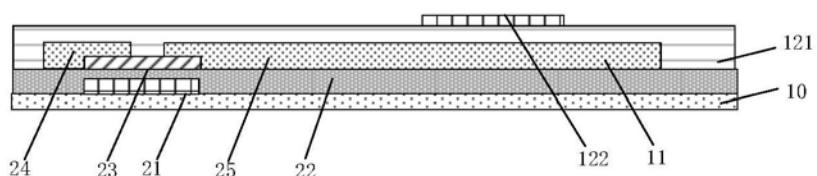

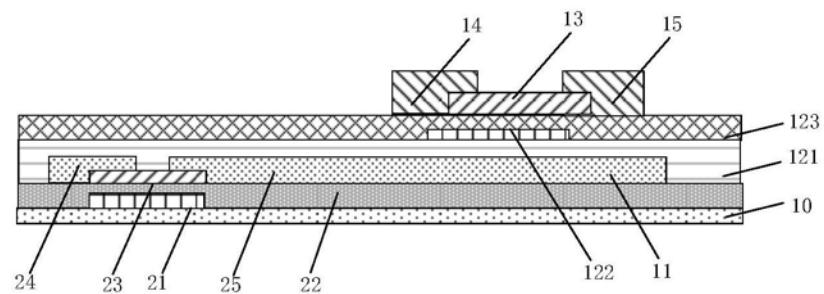

[0115] 第八步,如图3h所示,在所述第二栅绝缘层123上形成所述第二薄膜晶体管的第二有源层13,所述第二有源层13在所述衬底上的正投影覆盖所述薄膜层122在所述衬底10上的正投影。

[0116] 在本实施例中,使用沉积工艺并图案化形成第二有源层,第二有源层的材料为IGZO、IZO和IGZTO中的一种,所述第二有源层的厚度为大于10nm且小于100nm。

[0117] 第九步,如图3i所示,在所述第二栅绝缘层123上形成所述第二薄膜晶体管的第二源极14和第二漏极15,所述第二源极14和第二漏极15分别与所述第二有源层13电连接。

[0118] 在本实施例中,使用现有工艺步骤继续形成所述第二薄膜晶体管的第二源极和第二漏极。

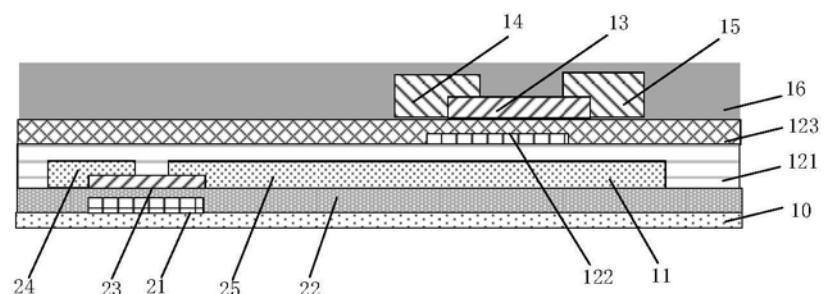

[0119] 第十步,如图3j所示,形成覆盖所述第二源极14、第二漏极15、第二有源层13和第二栅绝缘层122的平坦化层16。

[0120] 在本实施例中,在第一薄膜晶体管和第二薄膜晶体管上形成平坦化层,从而形成所述像素结构的驱动电路。

[0121] 第十一步,如图1所示,在所述平坦化层16上形成所述电致发光显示器件30。

[0122] 在本实施例中,在驱动电路上形成电致发光显示器件,从而形成所述像素结构。

[0123] 至此,完成阵列基板的制作。

[0124] 需要说明的是,在本发明实施例提供的上述制作方法中,形成各膜层结构涉及到的构图工艺,不仅可以包括沉积、光刻胶涂覆、掩模板掩模、曝光、显影、刻蚀、光刻胶剥离等部分或全部的工艺过程,还可以包括其他工艺过程,具体以实际制作过程中形成所需构图的图形为准,在此不做限定。

[0125] 其中,沉积工艺可以为化学气相沉积法、等离子体增强化学气相沉积法或物理气相沉积法,在此不做限定;掩膜工艺中所用的掩膜板可以为半色调掩膜板(Half ToneMask)、单缝衍射掩模板(Single Slit Mask)或灰色调掩膜板(Gray Tone Mask),在此不做限定;刻蚀可以为干法刻蚀或者湿法刻蚀,在此不做限定。

[0126] 本发明针对目前现有的问题,制定一种像素结构、阵列基板、显示装置和制作方法,通过设置在第二薄膜晶体管的包括第一栅绝缘层、第二栅绝缘层和位于两者之间的薄

膜层的三明治结构的栅绝缘层,有效提高像素结构内驱动薄膜晶体管的驱动能力,从而弥补了现有技术中存在的问题,具有广泛的应用前景。

[0127] 显然,本发明的上述实施例仅仅是为清楚地说明本发明所作的举例,而并非是对本发明的实施方式的限定,对于所属领域的普通技术人员来说,在上述说明的基础上还可以做出其它不同形式的变化或变动,这里无法对所有的实施方式予以穷举,凡是属于本发明的技术方案所引伸出的显而易见的变化或变动仍处于本发明的保护范围之列。

图1

在衬底上形成驱动电路，包括第一薄膜晶体管和第二薄膜晶体管，其中所述第一薄膜晶体管和第二薄膜晶体管为氧化物薄膜晶体管，第二薄膜晶体管包括第一栅绝缘层，设置在所述第一栅绝缘层上的薄膜层，所述薄膜层的介电常数大于预设置的介电常数阈值，以及覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层

在所述驱动电路上形成

电致发光显示器件电致发光器件

图2

图3a

图3b

图3c

图3d

图3e

图3f

图3g

图3h

图3i

图3j

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种像素结构、阵列基板、显示装置和制作方法                          |         |            |

| 公开(公告)号        | <a href="#">CN111384071A</a>                   | 公开(公告)日 | 2020-07-07 |

| 申请号            | CN202010218961.5                               | 申请日     | 2020-03-25 |

| [标]申请(专利权)人(译) | 京东方科技集团股份有限公司<br>福州京东方光电科技有限公司                 |         |            |

| 申请(专利权)人(译)    | 京东方科技集团股份有限公司<br>福州京东方光电科技有限公司                 |         |            |

| 当前申请(专利权)人(译)  | 京东方科技集团股份有限公司<br>福州京东方光电科技有限公司                 |         |            |

| [标]发明人         | 曾勇<br>王洋<br>席文星<br>余雪                          |         |            |

| 发明人            | 曾勇<br>王洋<br>邹振游<br>席文星<br>余雪                   |         |            |

| IPC分类号         | H01L27/12 H01L21/77 H01L27/32                  |         |            |

| 代理人(译)         | 付生辉                                            |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a> |         |            |

#### 摘要(译)

本发明公开了一种像素结构、阵列基板、显示装置和制作方法，所述像素结构包括层叠设置在衬底上的驱动电路和电致发光显示器件，所述驱动电路包括第一薄膜晶体管和第二薄膜晶体管，其中所述第一薄膜晶体管和第二薄膜晶体管为氧化物薄膜晶体管，所述第二薄膜晶体管包括第一栅绝缘层；设置在所述第一栅绝缘层上的薄膜层，所述薄膜层的介电常数大于预设置的介电常数阈值；以及覆盖所述第一栅绝缘层和薄膜层的第二栅绝缘层。本发明提供的实施例通过设置在第二薄膜晶体管的包括第一栅绝缘层、第二栅绝缘层和位于两者之间的薄膜层的三明治结构的栅绝缘层，有效提高像素结构内驱动薄膜晶体管的驱动能力，从而解决现有技术中的问题，具有广泛的应用前景。