# (19)中华人民共和国国家知识产权局

# (12)发明专利申请

(10)申请公布号 CN 110706654 A (43)申请公布日 2020.01.17

(21)申请号 201910867287.0

(22)申请日 2019.09.12

(71)申请人 深圳市华星光电半导体显示技术有限公司

地址 518132 广东省深圳市光明新区公明 街道塘明大道9-2号

(72)发明人 田凡 王振岭

(74)专利代理机构 深圳翼盛智成知识产权事务 所(普通合伙) 44300

代理人 黄威

(51) Int.CI.

**G09G** 3/3258(2016.01)

权利要求书3页 说明书6页 附图7页

#### (54)发明名称

一种OLED像素补偿电路及OLED像素补偿方法

#### (57)摘要

本申请公开了一种OLED像素补偿电路及OLED像素补偿方法,该像素补偿电路包括:有机发光二极管、驱动晶体管、第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管、第一电容以及第二电容。本申请通过使用5T2C结构且驱动晶体管DT为双栅极薄膜晶体管的像素内部驱动电路来增大驱动晶体管DT的顶栅电压,进而补偿驱动晶体管DT的阈值电压漂移,从而提升显示面板的亮度均匀性,进而延长产品的使用寿命。

1.一种OLED像素补偿电路,其特征在于,所述OLED像素补偿电路包括:

有机发光二极管,所述有机发光二极管的阳极连接于第三节点,阴极连接于一低电平线;

驱动晶体管,所述驱动晶体管为双栅极薄膜晶体管,用于驱动所述有机发光二极管,所述驱动晶体管的顶栅电性连接第一节点,底栅电性连接第二节点,源极电性连接所述第三节点,漏极电性连接于高电平线;

第一薄膜晶体管,所述第一薄膜晶体管的栅极连接于第一控制信号线,第一端连接于数据线,第二端连接于所述第二节点;

第二薄膜晶体管,所述第二薄膜晶体管的栅极连接于第二控制信号线,第一端连接于 所述数据线,第二端连接于所述第三节点;

第三薄膜晶体管,所述第三薄膜晶体管的栅极连接于第三控制信号线,第一端通过第 一开关连接于恒压电源,第二端连接于所述第一节点;

第四薄膜晶体管,所述第四薄膜晶体管的栅极连接于第四控制信号线,第一端通过所述第一开关连接于所述恒压电源,第二端连接于所述第三节点;

第一电容,所述第一电容连接于所述第二节点和所述第三节点之间;以及

第二电容,所述第二电容连接于所述第一节点和所述第三节点之间。

- 2.根据权利要求1所述的0LED像素补偿电路,其特征在于,当施加至所述驱动晶体管的顶栅的电压逐渐增大时,所述驱动晶体管的栅极与源极之间的压差和电流特性曲线与所述顶栅电压的大小成比例地逐渐减小。

- 3.根据权利要求1所述的OLED像素补偿电路,其特征在于,所述第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管及所述第四薄膜晶体管均为N型晶体管或P型晶体管。

- 4.根据权利要求1所述的0LED像素补偿电路,其特征在于,所述第一控制信号线、第二控制信号线、第三控制信号线、第四控制信号线中的信号以及所述第一开关的开关控制信号均通过外部时序驱动电路提供。

- 5.根据权利要求4所述的OLED像素补偿电路,其特征在于,所述第一控制信号线、第二控制信号线、第三控制信号线、第四控制信号线上的信号以及所述第一开关的开关控制信号被配置如下:所述像素补偿电路依次进入初始化阶段、侦测阶段、阈值电压转存阶段、数据写入阶段以及发光阶段;

在所述初始化阶段,所述第一控制信号线、第三控制信号线以及所述第四控制信号线 为高电平,所述第二控制信号线为低电平,所述第一开关的开关控制信号为闭合;

在所述侦测阶段,所述第一控制信号线和所述第三控制信号线为高电平,所述第二控制信号线和所述第四控制信号线为低电平,所述第一开关的开关控制信号为闭合;

在所述阈值电压转存阶段,所述第一控制信号线和所述第二控制信号线为高电平,所述第三控制信号线和所述第四控制信号线为低电平,所述第一开关的开关控制信号为打开;

在所述数据写入阶段,所述第一控制信号线为高电平,所述第二控制信号线、第三控制信号线以及所述第四控制信号线为低电平,所述第一开关的开关控制信号为打开;

在所述发光阶段,所述第一控制信号线、第二控制信号线、第三控制信号线以及所述第 四控制信号线均为低电平,所述第一开关的开关控制信号为打开。

- 6.根据权利要求5所述的OLED像素补偿电路,其特征在于,所述OLED像素补偿电路还包括外部侦测电路,所述外部侦测电路通过一第二开关与所述第一开关及所述恒压电源并联。

- 7.一种OLED像素补偿方法,其特征在于,所述OLED像素补偿方法包括:

提供OLED像素补偿电路:

其中,所述OLED像素补偿电路包括:

驱动晶体管,所述驱动晶体管为双栅极薄膜晶体管,用于驱动所述有机发光二极管,所述驱动晶体管的顶栅电性连接第一节点,底栅电性连接第二节点,源极电性连接第三节点,漏极电性连接于高电平线;

第一薄膜晶体管,所述第一薄膜晶体管的栅极连接于第一控制信号线,第一端连接于数据线,第二端连接于所述第二节点;

第二薄膜晶体管,所述第二薄膜晶体管的栅极连接于第二控制信号线,第一端连接于 所述数据线,第二端连接于所述第三节点:

第三薄膜晶体管,所述第三薄膜晶体管的栅极连接于第三控制信号线,第一端通过第 一开关连接于恒压电源,第二端连接于所述第一节点;

第四薄膜晶体管,所述第四薄膜晶体管的栅极连接于第四控制信号线,第一端通过所述第一开关连接于所述恒压电源,第二端连接于所述第三节点;

第一电容,所述第一电容连接于所述第二节点和所述第三节点之间;

第二电容,所述第二电容连接于所述第一节点和所述第三节点之间;以及

有机发光二极管,所述有机发光二极管的阳极连接于所述第三节点,阴极连接于一低电平线:

进入初始化阶段;

所述第一控制信号线、第三控制信号线以及所述第四控制信号线提供高电平,所述第一薄膜晶体管、第三薄膜晶体管以及所述第四薄膜晶体管打开,所述第二控制信号线提供低电平,所述第二薄膜晶体管关闭,所述数据线提供预设电位,所述第二节点写入预设电位,所述第一开关闭合,所述第一节点写入所述恒压电源的电压;

进入侦测阶段:

所述第一控制信号线和所述第三控制信号线提供高电平,所述第一薄膜晶体管和所述 第三薄膜晶体管打开,所述第二控制信号线和所述第四控制信号线提供低电平,所述第二 薄膜晶体管和所述第四薄膜晶体管关闭,所述第一开关闭合,所述数据线提供预设电位,所 述驱动晶体管导通,所述第三节点的电压随时间不断升高,所述驱动晶体管的栅极和源极 之间的压差不断降低,当所述驱动晶体管的栅极和源极之间的压差等于所述驱动晶体管的 阈值电压时,所述驱动晶体管截止,此时,所述驱动晶体管的阈值电压存储在所述第一电容 中;

进入阈值电压转存阶段;

所述第一控制信号线和所述第二控制信号线提供高电平,所述第一薄膜晶体管和所述 第二薄膜晶体管打开,所述第三控制信号线和所述第四控制信号线提供低电平,所述第三 薄膜晶体管和所述第四薄膜晶体管关闭,所述第一开关断开,所述数据线提供预设电位,所 述驱动晶体管的源极电压为预设电位,此时,所述驱动晶体管的阈值电压转存在所述第二

#### 电容中;

进入数据写入阶段;

所述第一控制信号线提供高电平,所述第一薄膜晶体管打开,所述第二控制信号线、第 三控制信号线以及所述第四控制信号线提供低电平,所述第二薄膜晶体管、第三薄膜晶体 管以及所述第四薄膜晶体管关闭,所述第一开关断开,所述数据线提供数据信号高电位,所 述数据信号高电位写入在所述第二节点;

#### 进入发光阶段;

所述第一控制信号线、第二控制信号线、第三控制信号线以及所述第四控制信号线均为低电平,所述第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管以及所述第四薄膜晶体管关闭,所述第一开关断开,所述驱动晶体管导通,所述有机发光二极管发光。

- 8.根据权利要求7所述的0LED像素补偿方法,其特征在于,所述恒压电源的电压小于所述有机发光二极管的阈值电压,且所述预设电位与所述恒压电源的电压的差值大于所述驱动晶体管的阈值电压。

- 9.根据权利要求7所述的0LED像素补偿方法,其特征在于,所述第一控制信号线、第二控制信号线、第三控制信号线、第四控制信号线中的信号以及所述第一开关的开关控制信号均通过外部时序驱动电路提供。

- 10.根据权利要求7所述的0LED像素补偿方法,其特征在于,所述0LED像素补偿电路还包括外部侦测电路,所述外部侦测电路通过一第二开关与所述第一开关及所述恒压电源并联,所述外部侦测电路设置为用于输入外部补偿信号。

## 一种0LED像素补偿电路及0LED像素补偿方法

#### 技术领域

[0001] 本申请涉及显示技术领域,尤其涉及一种0LED像素补偿电路及0LED像素补偿方法。

## 背景技术

[0002] OLED (Organic Light Emitting Display,有机发光二极管)显示面板中,由于制造工艺限制,每个驱动晶体管的电气特性存在一定差异,且驱动晶体管在工作过程中不稳定,易受温度、光照等因素影响发生特性漂移,驱动晶体管在空间上的电气特性差异和时间上的特性漂移都会造成显示器显示不均现象。

### 发明内容

[0003] 本申请的目的在于提供一种OLED像素补偿电路及OLED像素补偿方法,以解决显示面板亮度不均的技术问题。

[0004] 为解决上述技术问题,本申请采用的一个技术方案是:提供一种OLED像素补偿电路,所述OLED像素补偿电路包括:有机发光二极管,所述有机发光二极管的阳极连接于第三节点,阴极连接于一低电平线;驱动晶体管,所述驱动晶体管为双栅极薄膜晶体管,用于驱动所述有机发光二极管,所述驱动晶体管的顶栅电性连接第一节点,底栅电性连接第二节点,源极电性连接所述第三节点,漏极电性连接于高电平线;第一薄膜晶体管,所述第一薄膜晶体管的栅极连接于第一控制信号线,第一端连接于断述第二节点;第二薄膜晶体管,所述第二薄膜晶体管的栅极连接于第二控制信号线,第一端连接于所述第二节点;第二薄膜晶体管,所述第三节点;第三薄膜晶体管,所述第三节点;第一节点;第四薄膜晶体管,所述第四薄膜晶体管的栅极连接于第四控制信号线,第一端通过所述第一开关连接于所述恒压电源,第二端连接于所述第三节点;第一电容,所述第一电容连接于所述第二节点和所述第三节点和所述第三节点之间;以及第二电容,所述第二电容连接于所述第一节点和所述第三节点之间。

[0005] 为解决上述技术问题,本申请采用的另一个技术方案是:提供一种OLED像素补偿方法,所述OLED像素补偿方法包括:提供OLED像素补偿电路;其中,所述OLED像素补偿电路包括:驱动晶体管,所述驱动晶体管为双栅极薄膜晶体管,用于驱动所述有机发光二极管,所述驱动晶体管的顶栅电性连接第一节点,底栅电性连接第二节点,源极电性连接第三节点,漏极电性连接于高电平线;第一薄膜晶体管,所述第一薄膜晶体管的栅极连接于第一控制信号线,第一端连接于数据线,第二端连接于所述第二节点;第二薄膜晶体管,所述第二薄膜晶体管的栅极连接于第二控制信号线,第一端连接于所述数据线,第二端连接于所述第三节点;第三薄膜晶体管,所述第三薄膜晶体管的栅极连接于第三控制信号线,第一端通过第一开关连接于恒压电源,第二端连接于所述第一节点;第四薄膜晶体管,所述第四薄膜晶体管的栅极连接于第四控制信号线,第一端通过所述第一开关连接于所述恒压电源,第

二端连接于所述第三节点;第一电容,所述第一电容连接于所述第二节点和所述第三节点 之间:第二电容,所述第二电容连接于所述第一节点和所述第三节点之间:以及有机发光二 极管,所述有机发光二极管的阳极连接于所述第三节点,阴极连接于一低电平线;进入初始 化阶段:所述第一控制信号线、第三控制信号线以及所述第四控制信号线提供高电平,所述 第一薄膜晶体管、第三薄膜晶体管以及所述第四薄膜晶体管打开,所述第二控制信号线提 供低电平,所述第二薄膜晶体管关闭,所述数据线提供预设电位,所述第二节点写入预设电 位,所述第一开关闭合,所述第一节点写入所述恒压电源的电压;进入侦测阶段;所述第一 控制信号线和所述第三控制信号线提供高电平,所述第一薄膜晶体管和所述第三薄膜晶体 管打开,所述第二控制信号线和所述第四控制信号线提供低电平,所述第二薄膜晶体管和 所述第四薄膜晶体管关闭,所述第一开关闭合,所述数据线提供预设电位,所述驱动晶体管 导通,所述第三节点的电压随时间不断升高,所述驱动晶体管的栅极和源极之间的压差不 断降低,当所述驱动晶体管的栅极和源极之间的压差等于所述驱动晶体管的阈值电压时, 所述驱动晶体管截止,此时,所述驱动晶体管的阈值电压存储在所述第一电容中;进入阈值 电压转存阶段;所述第一控制信号线和所述第二控制信号线提供高电平,所述第一薄膜晶 体管和所述第二薄膜晶体管打开,所述第三控制信号线和所述第四控制信号线提供低电 平,所述第三薄膜晶体管和所述第四薄膜晶体管关闭,所述第一开关断开,所述数据线提供 预设电位,所述驱动晶体管的源极电压为预设电位,此时,所述驱动晶体管的阈值电压转存 在所述第二电容中;进入数据写入阶段;所述第一控制信号线提供高电平,所述第一薄膜晶 体管打开,所述第二控制信号线、第三控制信号线以及所述第四控制信号线提供低电平,所 述第二薄膜晶体管、第三薄膜晶体管以及所述第四薄膜晶体管关闭,所述第一开关断开,所 述数据线提供数据信号高电位,所述数据信号高电位写入在所述第二节点;进入发光阶段; 所述第一控制信号线、第二控制信号线、第三控制信号线以及所述第四控制信号线均为低 电平,所述第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管以及所述第四薄膜晶体管关 闭,所述第一开关断开,所述驱动晶体管导通,所述有机发光二极管发光。

[0006] 本申请的有益效果是:区别于现有技术的情况,本申请提供的一种0LED像素补偿电路及像素补偿方法,使用5T2C结构且驱动晶体管为双栅极薄膜晶体管的像素内部驱动电路来补偿阈值电压漂移,从而提升显示面板的亮度均匀性,进而延长产品的使用寿命。

#### 附图说明

[0007] 为了更清楚地说明本申请实施例中的技术方案,下面将对实施例描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本申请的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其它的附图,其中:

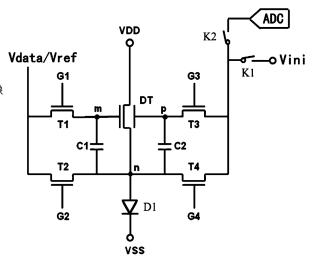

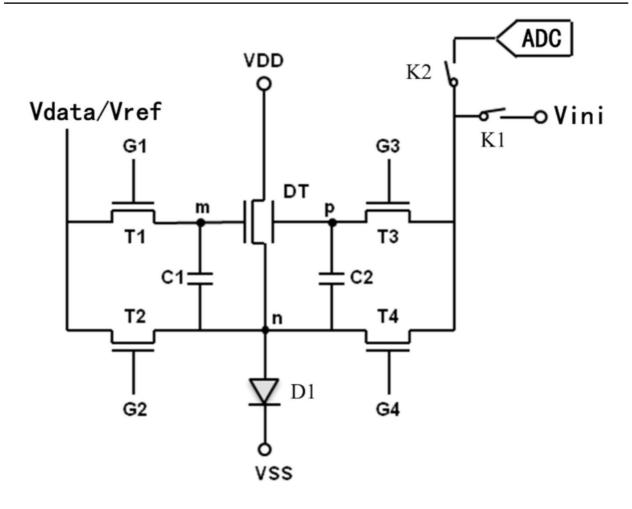

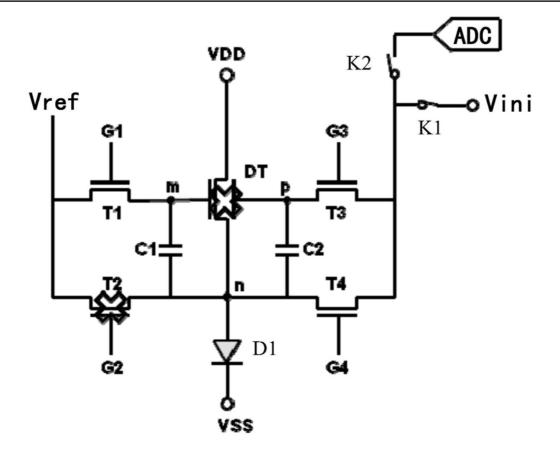

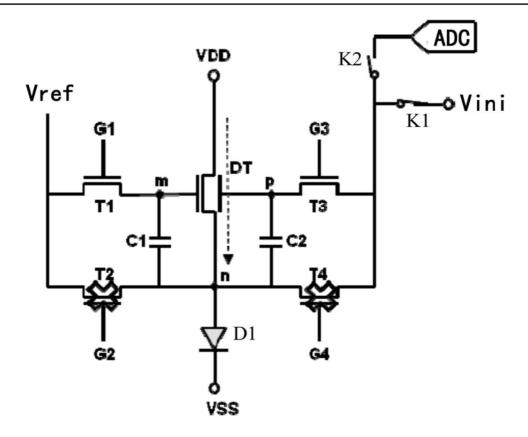

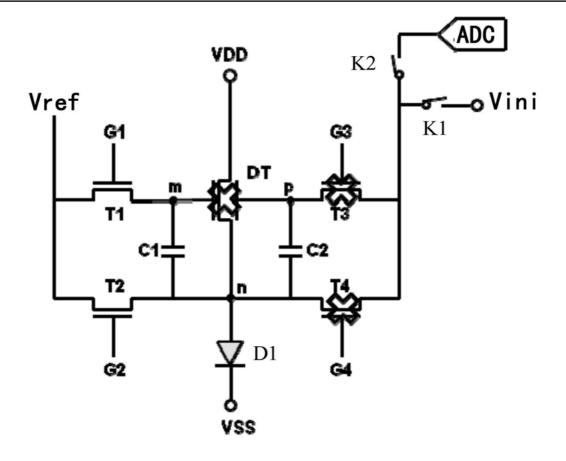

[0008] 图1是本申请的OLED像素补偿电路的电路图;

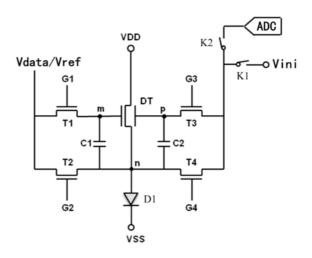

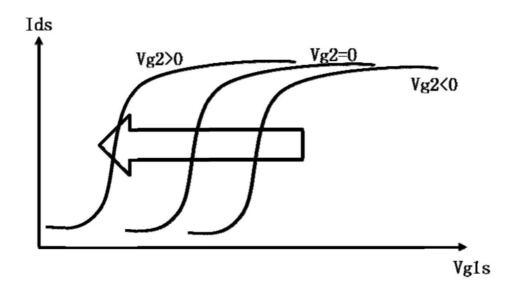

[0009] 图2是图1中的驱动晶体管的工作原理图;

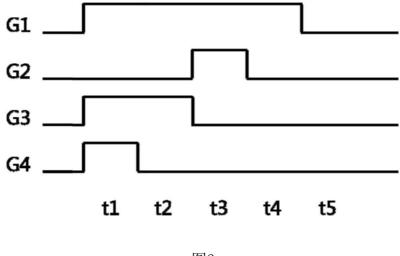

[0010] 图3是本申请的OLED像素补偿电路的时序图:

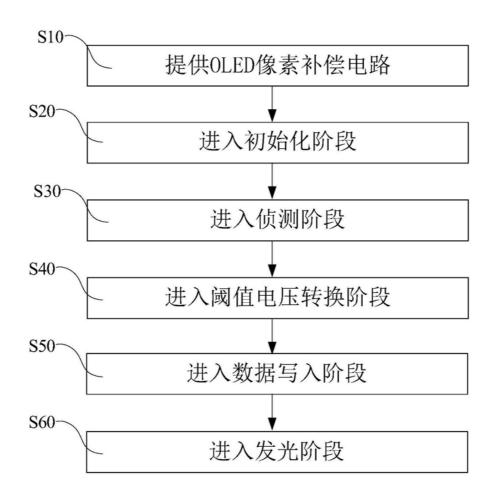

[0011] 图4是本申请的OLED像素补偿方法的流程示意图:

[0012] 图5是本申请的OLED像素补偿电路在初始化阶段的电路示意图:

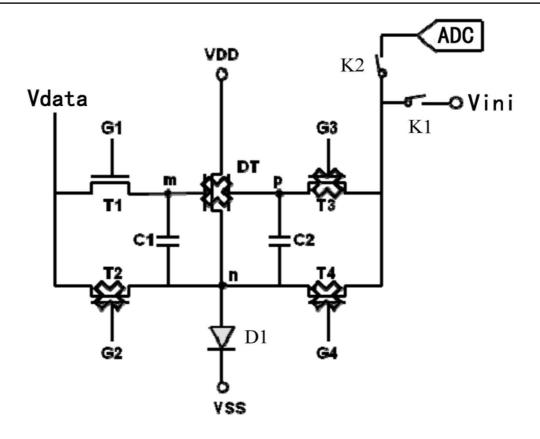

[0013] 图6是本申请的OLED像素补偿电路在侦测阶段的电路示意图:

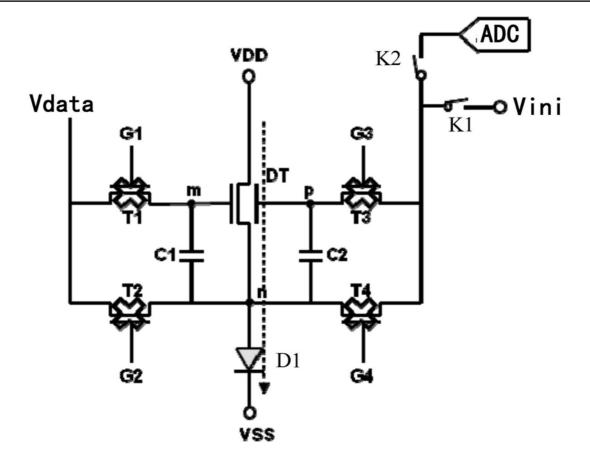

[0014] 图7是本申请的OLED像素补偿电路在阈值电压转存阶段的电路示意图:

[0015] 图8是本申请的OLED像素补偿电路在数据写入阶段的电路示意图:

[0016] 图9是本申请的OLED像素补偿电路在发光阶段的电路示意图。

### 具体实施方式

[0017] 下面将结合本申请实施例中的附图,对本申请实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅是本申请的一部分实施例,而不是全部的实施例。基于本申请中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其它实施例,都属于本申请保护的范围。

[0018] 请参阅图1,图1是本申请的0LED像素补偿电路的电路图。本申请首先提供一种 0LED像素补偿电路,该像素补偿电路包括有机发光二极管D1、驱动晶体管DT、第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3、第四薄膜晶体管T4、第一电容C1以及第二电容C2。有机发光二极管D1的阳极连接于第三节点n,阴极连接于一低电平线VSS。驱动晶体管 DT为双栅极薄膜晶体管,用于驱动有机发光二极管D1,驱动晶体管DT的顶栅电性连接第一节点p,底栅电性连接第二节点m,源极电性连接第三节点n,漏极电性连接于高电平线VDD。第一薄膜晶体管T1的栅极连接于第一控制信号线G1,第一端连接于数据线,第二端连接于第二节点m。第二薄膜晶体管T2的栅极连接于第二控制信号线G2,第一端连接于数据线,第二端连接于第二节点m。第三薄膜晶体管T3的栅极连接于第三控制信号线G3,第一端通过第一开关K1连接于恒压电源Vini,第二端连接于第二节点n。第一电容C1连接于第二节点m和第三节点n之间。第二电容C2连接于第一节点p和第三节点n之间。

[0019] 其中,在本实施例中,高电平线VDD为20V,低电平线VSS为-5V。当然,在其它实施例中,高电平线VDD和低电平线VSS还可以根据需要灵活设置,本申请不做具体限定。

[0020] 本申请通过使用5T2C结构且驱动晶体管DT为双栅极薄膜晶体管的像素内部驱动电路来增大驱动晶体管DT的顶栅电压,进而补偿驱动晶体管DT的阈值电压漂移,从而提升显示面板的亮度均匀性,进而延长产品的使用寿命。

[0021] 如图2所示,图2是图1中的驱动晶体管的工作原理图。其中,在本实施例中,当施加至驱动晶体管DT的顶栅的电压Vg2逐渐增大时,驱动晶体管DT的栅极与源极之间的压差和电流特性曲线与顶栅电压的大小成比例地逐渐减小。即,驱动晶体管DT的栅极与源极之间的压差与顶栅电压呈负相关趋势,顶栅电压越大,驱动晶体管DT的栅极与源极之间的压差越小。故而,在本实施例中,通过增大驱动晶体管DT的顶栅电压,以补偿驱动晶体管DT的阈值电压。

[0022] 其中,在本实施例中,第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3及第四薄膜晶体管T4均可以为N型晶体管或P型晶体管,本申请不做具体限定。

[0023] 其中,第一控制信号线G1、第二控制信号线G2、第三控制信号线G3、第四控制信号 线G4中的信号以及第一开关K1的开关控制信号均通过外部时序驱动电路提供。

[0024] 请参阅图3,图3是本申请的OLED像素补偿电路的时序图。第一控制信号线G1、第二控制信号线G2、第三控制信号线G3、第四控制信号线G4上的信号以及第一开关K1的开关控

制信号相互组合,并依次进入初始化阶段、侦测阶段、阈值电压转存阶段、数据写入阶段以及发光阶段。

[0025] 在初始化阶段,第一控制信号线G1、第三控制信号线G3以及第四控制信号线G4为高电平,第二控制信号线G2为低电平,第一开关K1的开关控制信号为闭合。在侦测阶段,第一控制信号线G1和第三控制信号线G3为高电平,第二控制信号线G2和第四控制信号线G4为低电平,第一开关K1的开关控制信号为闭合。在阈值电压转存阶段,第一控制信号线G1和第二控制信号线G2为高电平,第三控制信号线G3和第四控制信号线G4为低电平,第一开关K1的开关控制信号为打开。在数据写入阶段,第一控制信号线G1为高电平,第二控制信号线G2、第三控制信号线G3以及第四控制信号线G4为低电平,第一开关K1的开关控制信号为打开。在发光阶段,第一控制信号线G1、第二控制信号线G2、第三控制信号线G3以及第四控制信号线G4均为低电平,第一开关K1的开关控制信号为打开。

[0026] 可选地,在本实施例中,如图1所示,OLED像素补偿电路还包括外部侦测电路,外部 侦测电路通过一第二开关K2与第一开关K1及恒压电源V<sub>ini</sub>并联。

[0027] 请结合图1和图3,本申请的0LED像素补偿电路的工作过程如下:

[0028] 在初始化阶段,第一控制信号线G1、第三控制信号线G3以及第四控制信号线G4为高电平,第一薄膜晶体管T1、第三薄膜晶体管T3以及第四薄膜晶体管T4均打开,第二控制信号线G2为低电平,第二薄膜晶体管T2关闭,数据线提供预设电位 $V_{\rm ref}$ ,第二节点m写入预设电位 $V_{\rm ref}$ 。第一开关K1的开关控制信号为闭合,第一开关K1关闭,第一节点p和第三节点n写入恒定电源的电压 $V_{\rm ini}$ 。在本实施例中,恒压电源的电压 $V_{\rm ini}$ 小于有机发光二极管D1的阈值电压 $V_{\rm ini}$ ,且 $V_{\rm ref}$ — $V_{\rm ini}$ > $V_{\rm th}$ —TFT,其中, $V_{\rm th}$ —TFT表示的是驱动晶体管DT的阈值电压。故而,在初始化阶段,OLED不发光。

[0029] 在侦测阶段,第一控制信号线G1和第三控制信号线G3为高电平,第一薄膜晶体管T1和第三薄膜晶体管T3打开,第二控制信号线G2和第四控制信号线G4为低电平,第二薄膜晶体管T2和第四薄膜晶体管T4关闭,数据线提供预设电位 $V_{ref}$ ,第二节点m写入预设电位 $V_{ref}$ ,第一开关K1的开关控制信号为闭合,第一开关K1关闭,第一节点p写入恒定电源的电压 $V_{ini}$ 。由于 $V_{ref}$ — $V_{ini}$ > $V_{th}$ —TFT,故驱动晶体管DT导通,第三节点n的电压随时间不断升高,驱动晶体管DT的栅极和源极之间的压差不断降低,当驱动晶体管DT的栅极和源极之间的压差为 $V_{th}$ —TFT,驱动晶体管DT截止。此时,第三节点n的电压为 $V_{ref}$ — $V_{th}$ —TFT,驱动晶体管DT的阈值电压 $V_{th}$ —TFT 存储在第一电容C1中,第一节点p与第三节点n的压差为 $V_{ini}$ — $(V_{ref}$ — $V_{th}$ —TFT)。

[0030] 在阈值电压转存阶段,第一控制信号线G1和第二控制信号线G2为高电平,第一薄膜晶体管T1和第二薄膜晶体管T2打开,第三控制信号线G3和第四控制信号线G4为低电平,第三薄膜晶体管T3和第四薄膜晶体管T4关闭,数据线提供预设电位 $V_{\rm ref}$ ,第二节点m和第三节点n写入预设电位 $V_{\rm ref}$ 。第一开关K1的开关控制信号为打开,第一开关K1断开。由于在侦测阶段时,第一节点p与第三节点n的压差为 $V_{\rm ini}$ 一( $V_{\rm ref}$ — $V_{\rm th-TFT}$ ),此时,第三节点n的电压为 $V_{\rm ref}$ ,根据电容耦合效应,第一节点p的电压为 $V_{\rm ini}$ + $V_{\rm th-TFT}$ ,驱动晶体管DT的阈值电压 $V_{\rm th-TFT}$ 转存在第二电容C2中。

[0031] 在数据写入阶段,第一控制信号线G1为高电平,第一薄膜晶体管T1打开,第二控制信号线G2、第三控制信号线G3以及第四控制信号线G4为低电平,第二薄膜晶体管T2、第三薄膜晶体管T3以及第四薄膜晶体管T4关闭,数据线提供数据信号高电位V<sub>data</sub>,数据信号高电

位Vdata写入在第二节点m。第一开关K1的开关控制信号为打开,第一开关K1断开。

[0032] 在发光阶段,第一控制信号线G1、第二控制信号线G2、第三控制信号线G3以及第四控制信号线G4均为低电平,第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3以及第四薄膜晶体管T4关闭,第一开关K1的开关控制信号为打开,第一开关K1断开,驱动晶体管DT导通,有机发光二极管D1发光。

[0033] 本申请另一方面提供一种OLED像素补偿方法,如图4所示,图4是本申请的OLED像素补偿方法的流程示意图。OLED像素补偿方法包括如下步骤:

[0034] S10:提供OLED像素补偿电路。

[0035] 其中,OLED像素补偿电路包括有机发光二极管D1、驱动晶体管DT、第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3、第四薄膜晶体管T4、第一电容C1以及第二电容C2。有机发光二极管D1的阳极连接于第三节点n,阴极连接于一低电平线VSS。驱动晶体管DT为双栅极薄膜晶体管,用于驱动有机发光二极管D1,驱动晶体管DT的顶栅电性连接第一节点p,底栅电性连接第二节点m,源极电性连接第三节点n,漏极电性连接于高电平线VDD。第一薄膜晶体管T1的栅极连接于第一控制信号线G1,第一端连接于数据线,第二端连接于第二节点m。第二薄膜晶体管T2的栅极连接于第二控制信号线G2,第一端连接于数据线,第二端连接于第三节点n。第三薄膜晶体管T3的栅极连接于第三控制信号线G3,第一端通过第一开关K1连接于恒压电源Vini,第二端连接于第一节点p。第四薄膜晶体管T4的栅极连接于第四控制信号线G4,第一端通过第一开关K1连接于恒压电源Vini,第二端连接于第三节点n。第一电容C1连接于第二节点m和第三节点n之间。第二电容C2连接于第一节点p和第三节点n之间。

[0036] S20:进入初始化阶段。

[0037] 其中,如图3和图5所示,图5是本申请的0LED像素补偿电路在初始化阶段的电路示意图。第一控制信号线G1、第三控制信号线G3以及第四控制信号线G4为高电平,第一薄膜晶体管T1、第三薄膜晶体管T3以及第四薄膜晶体管T4均打开,第二控制信号线G2为低电平,第二薄膜晶体管T2关闭,数据线提供预设电位 $V_{\rm ref}$ ,第二节点m写入预设电位 $V_{\rm ref}$ 。第一开关K1的开关控制信号为闭合,第一开关K1关闭,第一节点p和第三节点n写入恒定电源的电压 $V_{\rm ini}$ 。在本实施例中,恒压电源的电压 $V_{\rm ini}$ ,小于有机发光二极管D1的阈值电压 $V_{\rm OLED}$ ,且 $V_{\rm ref}$ — $V_{\rm ini}$ > $V_{\rm th-TFT}$ ,其中, $V_{\rm th-TFT}$ 表示的是驱动晶体管DT的阈值电压。故而,在初始化阶段,0LED不发光。

[0038] S30:进入侦测阶段。

[0039] 如图3和图6所示,图6是本申请的0LED像素补偿电路在侦测阶段的电路示意图。第一控制信号线G1和第三控制信号线G3为高电平,第一薄膜晶体管T1和第三薄膜晶体管T3打开,第二控制信号线G2和第四控制信号线G4为低电平,第二薄膜晶体管T2和第四薄膜晶体管T4关闭,数据线提供预设电位 $V_{ref}$ ,第二节点m写入预设电位 $V_{ref}$ ,第一开关K1的开关控制信号为闭合,第一开关K1关闭,第一节点p写入恒定电源的电压 $V_{ini}$ 。由于 $V_{ref}$ — $V_{ini}$ > $V_{th}$ —TFT,故驱动晶体管DT导通,第三节点n的电压随时间不断升高,驱动晶体管DT的栅极和源极之间的压差不断降低,当驱动晶体管DT的栅极和源极之间的压差为 $V_{th}$ —TFT时,驱动晶体管DT截止。此时,第三节点n的电压为 $V_{ref}$ — $V_{th}$ —TFT,驱动晶体管DT的阈值电压 $V_{th}$ —TFT 存储在第一电容C1中,第一节点p与第三节点n的压差为 $V_{ini}$ — $(V_{ref}$ — $V_{th}$ —TFT)。

[0040] S40:进入阈值电压转存阶段。

[0041] 如图3和图7所示,图7是本申请的0LED像素补偿电路在阈值电压转存阶段的电路示意图。第一控制信号线G1和第二控制信号线G2为高电平,第一薄膜晶体管T1和第二薄膜晶体管T2打开,第三控制信号线G3和第四控制信号线G4为低电平,第三薄膜晶体管T3和第四薄膜晶体管T4关闭,数据线提供预设电位 $V_{\rm ref}$ ,第二节点m和第三节点n写入预设电位 $V_{\rm ref}$ 。第一开关K1的开关控制信号为打开,第一开关K1断开。由于在侦测阶段时,第一节点p与第三节点n的压差为 $V_{\rm ini}$ -( $V_{\rm ref}$ - $V_{\rm th}$ -TFT),此时,第三节点n的电压为 $V_{\rm ref}$ ,根据电容耦合效应,第一节点p的电压为 $V_{\rm ini}$ + $V_{\rm th}$ -TFT,驱动晶体管DT的阈值电压 $V_{\rm th}$ -TFT转存在第二电容C2中。

[0042] S50:进入数据写入阶段。

[0043] 如图3和图8所示,图8是本申请的0LED像素补偿电路在数据写入阶段的电路示意图。第一控制信号线G1为高电平,第一薄膜晶体管T1打开,第二控制信号线G2、第三控制信号线G3以及第四控制信号线G4为低电平,第二薄膜晶体管T2、第三薄膜晶体管T3以及第四薄膜晶体管T4关闭,数据线提供数据信号高电位 $V_{\rm data}$ ,数据信号高电位 $V_{\rm data}$ 写入在第二节点m。第一开关K1的开关控制信号为打开,第一开关K1断开。

[0044] S60: 进入发光阶段。

[0045] 如图3和图9所示,图9是本申请的0LED像素补偿电路在发光阶段的电路示意图。第一控制信号线G1、第二控制信号线G2、第三控制信号线G3以及第四控制信号线G4均为低电平,第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3以及第四薄膜晶体管T4关闭,第一开关K1的开关控制信号为打开,第一开关K1断开,驱动晶体管DT导通,有机发光二极管D1发光。

[0046] 其中,第一控制信号线G1、第二控制信号线G2、第三控制信号线G3、第四控制信号 线G4中的信号以及第一开关K1的开关控制信号均通过外部时序驱动电路提供。

[0047] 进一步地,OLED像素补偿电路还包括外部侦测电路,外部侦测电路通过一第二开关K2与第一开关K1及恒压电源并联,外部侦测电路设置为用于输入外部补偿信号。外部补偿电路在需要进行外部补偿时使用,外部补偿电路可以设置在驱动集成电路(integrated circuit,IC)芯片或者驱动系统中,以辅助内部补偿电路来进行阈值电压补偿。

[0048] 综上所述,本申请通过使用5T2C结构且驱动晶体管DT为双栅极薄膜晶体管的像素内部驱动电路来增大驱动晶体管DT的顶栅电压,进而补偿驱动晶体管DT的阈值电压漂移,从而提升显示面板的亮度均匀性,进而延长产品的使用寿命。

[0049] 以上所述仅为本申请的实施例,并非因此限制本申请的专利范围,凡是利用本申请说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其它相关的技术领域,均同理包括在本申请的专利保护范围内。

图1

图2

图3

图4

图5

图6

图7

图8

图9

| 专利名称(译)        | 一种OLED像素补偿电路及OLED像素补偿方法  |         |            |  |

|----------------|--------------------------|---------|------------|--|

| 公开(公告)号        | CN110706654A             | 公开(公告)日 | 2020-01-17 |  |

| 申请号            | CN201910867287.0         | 申请日     | 2019-09-12 |  |

| [标]申请(专利权)人(译) | 深圳市华星光电技术有限公司            |         |            |  |

| [标]发明人         | 田凡<br>王振岭                |         |            |  |

| 发明人            | 田凡<br>王振岭                |         |            |  |

| IPC分类号         | G09G3/3258               |         |            |  |

| CPC分类号         | G09G3/3258 G09G2320/0233 |         |            |  |

| 代理人(译)         | 黄威                       |         |            |  |

| 外部链接           | Espacenet SIPO           |         |            |  |

#### 摘要(译)

本申请公开了一种OLED像素补偿电路及OLED像素补偿方法,该像素补偿电路包括:有机发光二极管、驱动晶体管、第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管、第一电容以及第二电容。本申请通过使用5T2C结构且驱动晶体管DT为双栅极薄膜晶体管的像素内部驱动电路来增大驱动晶体管DT的顶栅电压,进而补偿驱动晶体管DT的顾值电压漂移,从而提升显示面板的亮度均匀性,进而延长产品的使用寿命。