(12)发明专利申请

(10)申请公布号 CN 108269526 A

(43)申请公布日 2018.07.10

(21)申请号 201710005474.9

(22)申请日 2017.01.04

(71)申请人 昆山工研院新型平板显示技术中心

有限公司

地址 215300 江苏省苏州市昆山市昆山高

新区晨丰路188号

(72)发明人 胡思明 杨楠 张九占 宋艳芹

朱晖

(74)专利代理机构 广州华进联合专利商标代理

有限公司 44224

代理人 唐清凯

(51)Int.Cl.

G09G 3/3225(2016.01)

权利要求书2页 说明书4页 附图3页

(54)发明名称

OLED显示装置及其像素电路、像素单元电路

及驱动方法

(57)摘要

本发明涉及一种OLED显示装置及其像素电

路、像素单元电路及驱动方法。该像素单元电

路的第一薄膜晶体管：第一端输入数据信号、第

二端连接第二薄膜晶体管、第三端用于输入第一信

号；第二薄膜晶体管：第二端输入第一电源电压、

第三端用于输入第二信号；第三薄膜晶体管：第

三端通过第一电容与第二薄膜晶体管的第二端

连接；第四薄膜晶体管：第二端通过有机发光二

极管连接第二电源电压、第三端用于输入第三信

号；第五薄膜晶体管：第一端连接第三薄膜晶体

管的第三端、第三端输入第一信号；第二电容的

两端分别连接第一薄膜晶体管的第一端和第五

薄膜晶体管的第一端。该OLED显示装置及其像素

电路、像素单元电路占用的版图面积少，可实现

更高分辨率的屏体显示。

A

CN 108269526

CN

1. 一种像素单元电路，包括第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管、第五薄膜晶体管、第一电容、第二电容以及有机发光二极管；

所述第一薄膜晶体管：第一端输入数据信号、第二端与第二薄膜晶体管的第一端连接、第三端用于输入第一信号；

所述第二薄膜晶体管：第二端用于输入第一电源电压、第三端用于输入第二信号；

所述第三薄膜晶体管：第一端连接第一薄膜晶体管的第二端、第二端连接第四薄膜晶体管的第一端、第三端通过第一电容与第二薄膜晶体管的第二端连接；

所述第四薄膜晶体管：第二端通过所述有机发光二极管连接第二电源电压、第三端用于输入第三信号；其中，所述第四薄膜晶体管的第二端与所述有机发光二极管的阳极连接；

所述第五薄膜晶体管：第一端连接第三薄膜晶体管的第三端、第二端与第四薄膜晶体管的第一端连接、第三端用于输入所述第一信号；

所述第二电容的两端分别连接所述第一薄膜晶体管的第三端和所述第五薄膜晶体管的第一端；

所述第一端和第二端分别为源极或漏极，所述第三端为栅极；所述第一信号、第二信号以及第三信号均为开启或关闭薄膜晶体管的高低电平信号；第一电源电压为正电压，第二电源电压为负电压。

2. 根据权利要求1所述的像素单元电路，其特征在于，所述第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管以及第五薄膜晶体管均为PMOS管。

3. 根据权利要求1所述的像素单元电路，其特征在于，所述第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管以及第五薄膜晶体管均为NMOS管。

4. 一种像素电路，包括多个权利要求1～3任一项所述的像素单元电路。

5. 一种OLED显示装置，包括数据驱动模块、栅极驱动模块以及权利要求4所述的像素电路。

6. 根据权利要求5所述的OLED显示装置，其特征在于，所述栅极驱动模块用于输出所述第一信号、第二信号以及第三信号。

7. 根据权利要求5所述的OLED显示装置，其特征在于，所述栅极驱动模块与所述像素电路集成在OLED显示装置的屏体中。

8. 一种像素单元电路的驱动方法，基于权利要求1所述的像素单元电路，包括：

在第一时段内，设置所述第一信号和第三信号以开启所述第一薄膜晶体管、第四薄膜晶体管以及第五薄膜晶体管，并设置所述第二信号以关闭第二薄膜晶体管；

在接下来的第二时段内，保持开启所述第一薄膜晶体管以及第五薄膜晶体管，保持关闭所述第二薄膜晶体管；并设置所述第三信号以关闭第四薄膜晶体管；

之后，设置所述第一信号以关闭所述第一薄膜晶体管和第五薄膜晶体管，设置所述第二信号以开启第二薄膜晶体管；设置所述第三信号以开启第四薄膜晶体管。

9. 根据权利要求8所述的像素单元电路的驱动方法，其特征在于，所述第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管以及第五薄膜晶体管均为PMOS管；

在第一时段内，设置所述第一信号和第三信号为低电平，设置第二信号为高电平；

在第二时段内，设置所述第一信号为低电平，设置第二信号和第三信号为高电平；

之后，设置所述第一信号为高电平，设置第二信号和第三信号为低电平。

10. 根据权利要求8所述的像素单元电路的驱动方法，其特征在于，所述第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管以及第五薄膜晶体管均为NMOS管；

在第一时段内，设置所述第一信号和第三信号为高电平，设置第二信号为低电平；

在第二时段内，设置所述第一信号为高电平，设置第二信号和第三信号为低电平；

之后，设置所述第一信号为低电平，设置第二信号和第三信号为高电平。

## OLED显示装置及其像素电路、像素单元电路及驱动方法

### 技术领域

[0001] 本发明涉及OLED显示技术领域,特别是涉及一种OLED像素单元电路。

### 背景技术

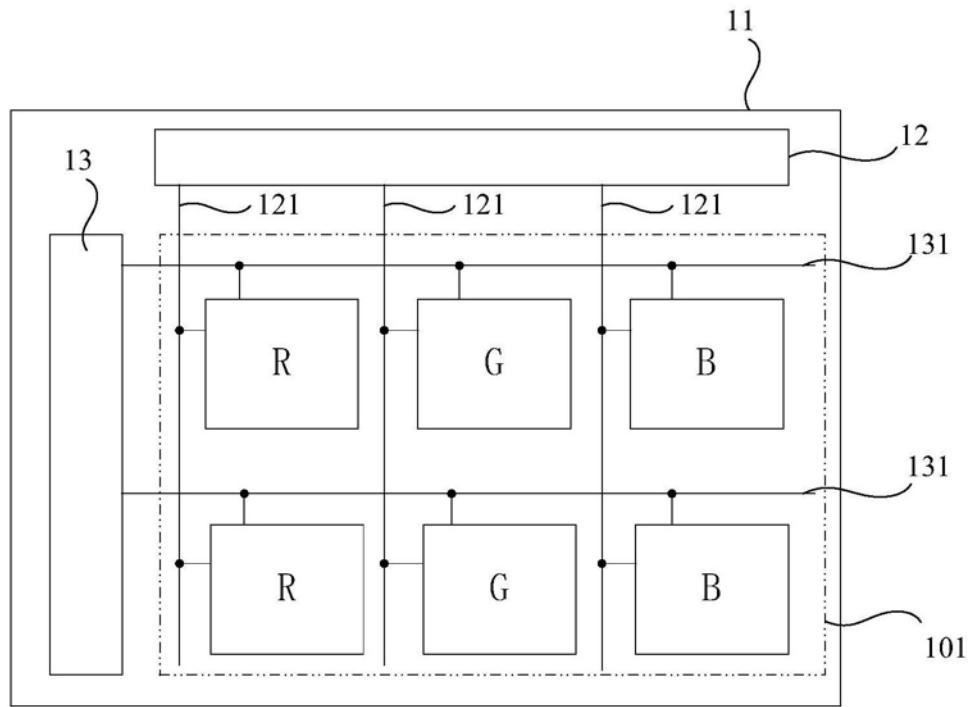

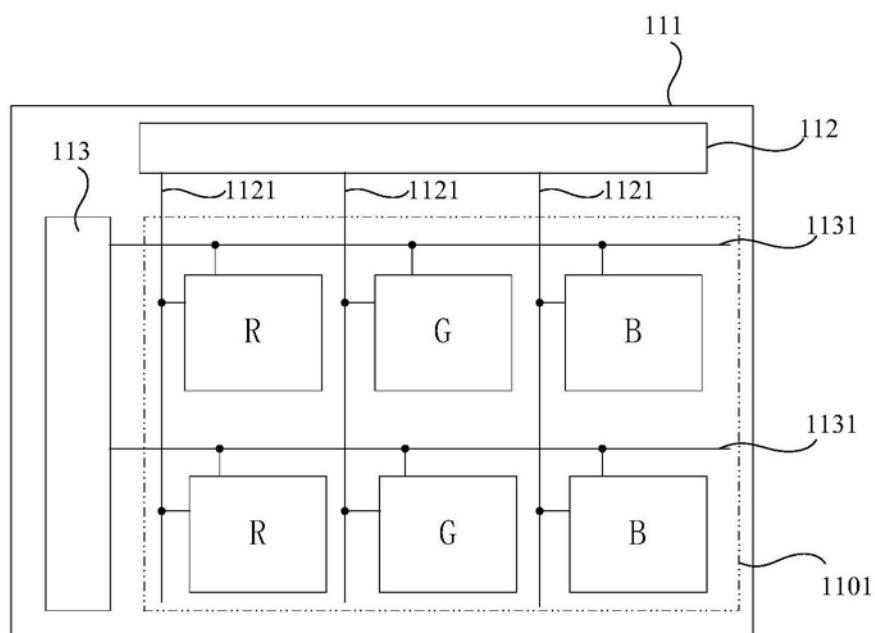

[0002] 图1为OLED显示装置结构示意图。OLED显示装置11包括数据驱动模块12、栅极驱动模块13以及像素电路101。其中像素电路101包括多个像素单元电路R、G、B,每个像素单元电路都与数据驱动模块12的数据线121连接,用于接收数据驱动模块12提供的数据信号;每个像素单元电路都与栅极驱动模块13的扫描线131连接,用于接收栅极驱动模块13提供的扫描信号。像素电路101根据数据驱动模块12提供的数据信号和栅极驱动模块13提供的扫描信号使子像素发光,从而显示图像。

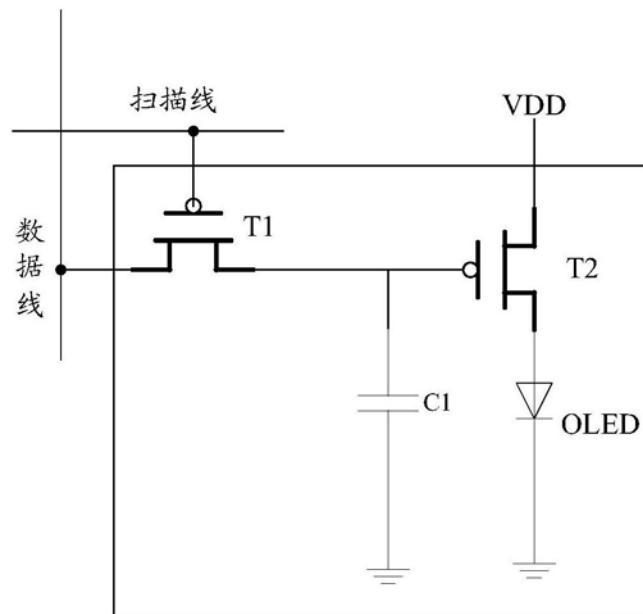

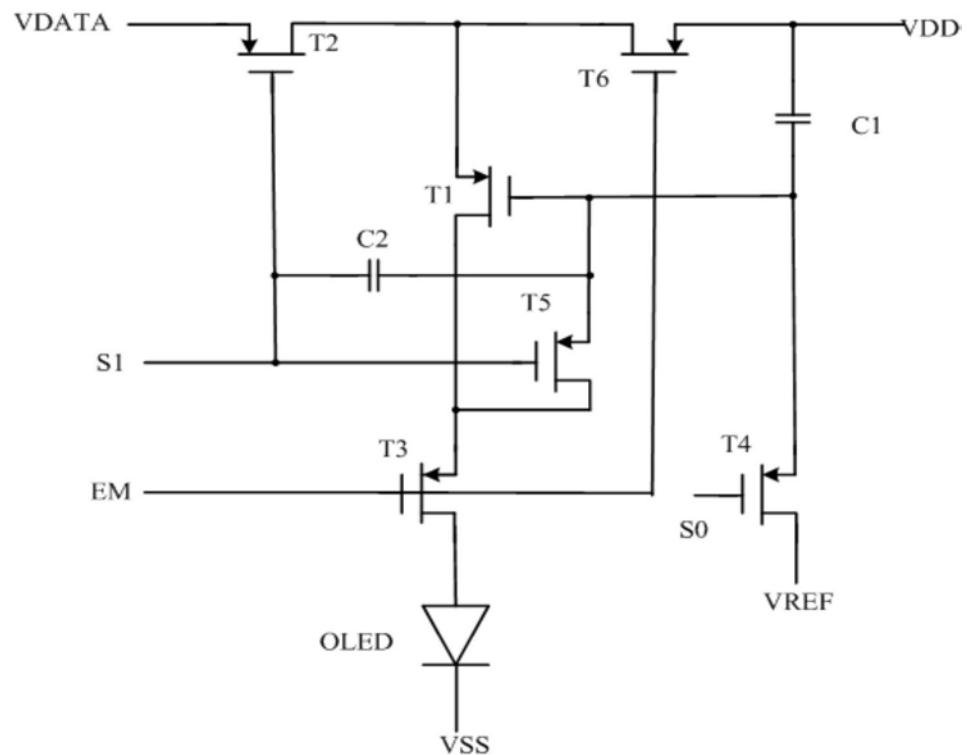

[0003] 传统的OLED显示装置的像素单元电路大多采用2T1C的形式,如图2所示。该像素单元电路中包括两个薄膜晶体管T1、T2和一个电容C1,故称为2T1C电路。该像素单元电路中,流过OLED的电流为:

$$[0004] I_{oled} = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_{th})^2$$

[0005] 但LTPS工艺通常都会带来薄膜晶体管的阈值电压Vth不一致,导致屏体亮度不均。

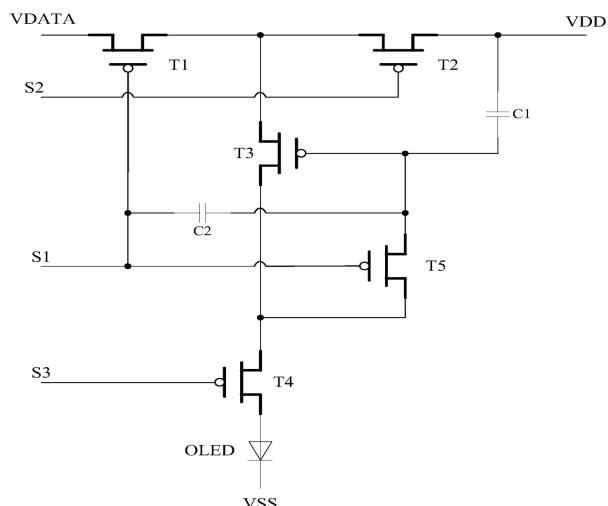

[0006] 一种解决该问题的方案为对薄膜晶体管的阈值电压Vth进行补偿,如图3所示。但该方案采用的器件数量和输入电压信号较多,版图占有的面积较大,实现高分辨率非常困难。

### 发明内容

[0007] 基于此,有必要提供一种可对薄膜晶体管的阈值电压进行补偿的结构简单的像素单元电路。

[0008] 一种像素单元电路,包括第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管、第五薄膜晶体管、第一电容、第二电容以及有机发光二极管;

[0009] 所述第一薄膜晶体管:第一端输入数据信号、第二端与第二薄膜晶体管的第一端连接、第三端用于输入第一信号;

[0010] 所述第二薄膜晶体管:第二端用于输入第一电源电压、第三端用于输入第二信号;

[0011] 所述第三薄膜晶体管:第一端连接第一薄膜晶体管的第二端、第二端连接第四薄膜晶体管的第一端、第三端通过第一电容与第二薄膜晶体管的第二端连接;

[0012] 所述第四薄膜晶体管:第二端通过所述有机发光二极管连接第二电源电压、第三端用于输入第三信号;其中,所述第四薄膜晶体管的第二端与所述有机发光二极管的阳极连接;

[0013] 所述第五薄膜晶体管:第一端连接第三薄膜晶体管的第三端、第二端与第四薄膜晶体管的第一端连接、第三端用于输入所述第一信号;

[0014] 所述第二电容的两端分别连接所述第一薄膜晶体管的第三端和所述第五薄膜晶

体管的第一端；

[0015] 所述第一端和第二端分别为源极或漏极，所述第三端为栅极；所述第一信号、第二信号以及第三信号均为开启或关闭薄膜晶体管的高低电平信号；第一电源电压为正电压，第二电源电压为负电压。

[0016] 在其中一个实施例中，所述第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管以及第五薄膜晶体管均为PMOS管。

[0017] 在其中一个实施例中，所述第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管以及第五薄膜晶体管均为NMOS管。

[0018] 一种像素电路，包括多个上述的像素单元电路。

[0019] 一种OLED显示装置，包括数据驱动模块、栅极驱动模块以及上述的像素电路。

[0020] 在其中一个实施例中，所述栅极驱动模块用于输出所述第一信号、第二信号以及第三信号。

[0021] 在其中一个实施例中，所述栅极驱动模块与所述像素电路集成在OLED显示装置的屏体中。

[0022] 一种像素单元电路的驱动方法，基于上述的像素单元电路，包括：

[0023] 在第一时段内，设置所述第一信号和第三信号以开启所述第一薄膜晶体管、第四薄膜晶体管以及第五薄膜晶体管，并设置所述第二信号以关闭第二薄膜晶体管；

[0024] 在接下来的第二时段内，保持开启所述第一薄膜晶体管以及第五薄膜晶体管，保持关闭所述第二薄膜晶体管；并设置所述第三信号以关闭第四薄膜晶体管；

[0025] 之后，设置所述第一信号以关闭所述第一薄膜晶体管和第五薄膜晶体管，设置所述第二信号以开启第二薄膜晶体管；设置所述第三信号以开启第四薄膜晶体管。

[0026] 在其中一个实施例中，所述第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管以及第五薄膜晶体管均为PMOS管；

[0027] 在第一时段内，设置所述第一信号和第三信号为低电平，设置第二信号为高电平；

[0028] 在第二时段内，设置所述第一信号为低电平，设置第二信号和第三信号为高电平；

[0029] 之后，设置所述第一信号为高电平，设置第二信号和第三信号为低电平。

[0030] 在其中一个实施例中，所述第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管以及第五薄膜晶体管均为NMOS管；

[0031] 在第一时段内，设置所述第一信号和第三信号为高电平，设置第二信号为低电平；

[0032] 在第二时段内，设置所述第一信号为高电平，设置第二信号和第三信号为低电平；

[0033] 之后，设置所述第一信号为低电平，设置第二信号和第三信号为高电平。

[0034] 上述OLED显示装置及其像素电路、像素单元电路及驱动方法可通过设置第一信号、第二信号以及第三信号对阈值电压进行补偿，从而解决屏体亮度不均匀的问题，但电路结构更简单，版图占用的面积也更少，可以应用于更高分辨率屏体的设计。

## 附图说明

[0035] 图1为OLED显示装置结构示意图；

[0036] 图2为2T1C的像素单元电路图；

[0037] 图3为传统的可进行阈值补偿的像素单元电路图；

- [0038] 图4为一实施例的OLED显示装置结构示意图；

- [0039] 图5为一实施例的像素单元电路图；

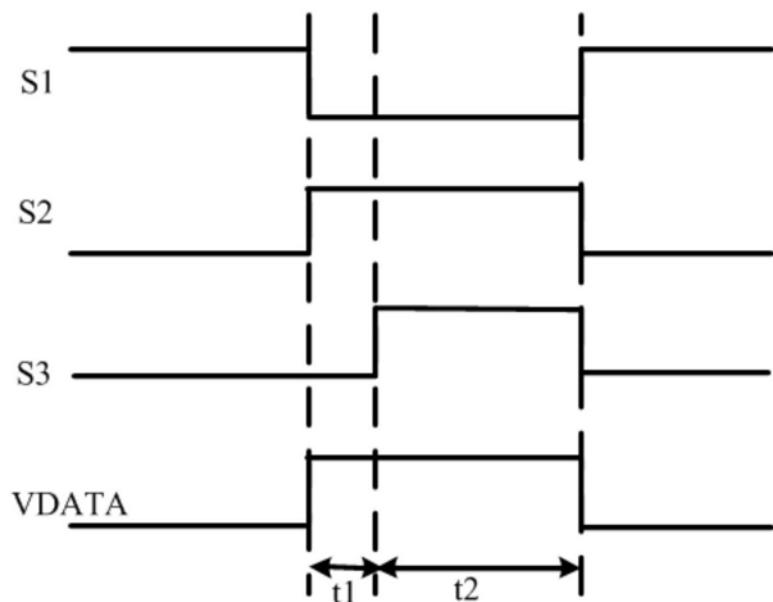

- [0040] 图6为实施例像素单元电路图对应的时序图。

## 具体实施方式

- [0041] 以下结合附图和实施例进行进一步说明。

- [0042] 图4为一实施例的OLED显示装置结构示意图。OLED显示装置111包括数据驱动模块112、栅极驱动模块113以及像素电路1101。其中像素电路1101包括多个像素单元电路R、G、B，每个像素单元电路都与数据驱动模块112的数据线1121连接，用于接收数据驱动模块112提供的数据信号；每个像素单元电路都与栅极驱动模块113的扫描线1131连接，用于接收栅极驱动模块113提供的扫描信号。像素电路1101根据数据驱动模块112提供的数据信号和栅极驱动模块113提供的扫描信号使子像素发光，从而显示图像。

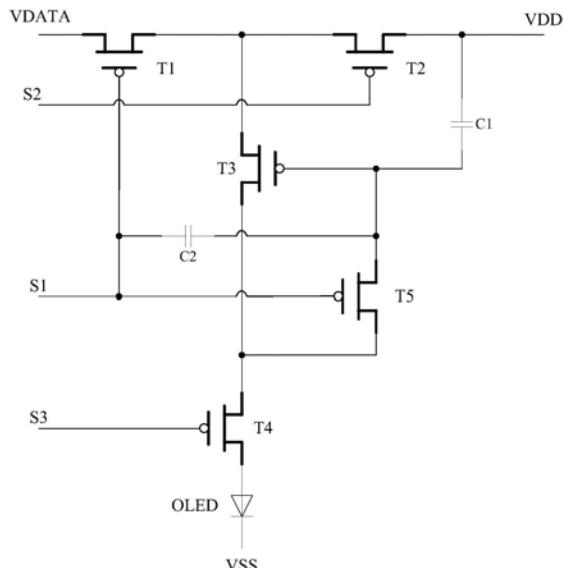

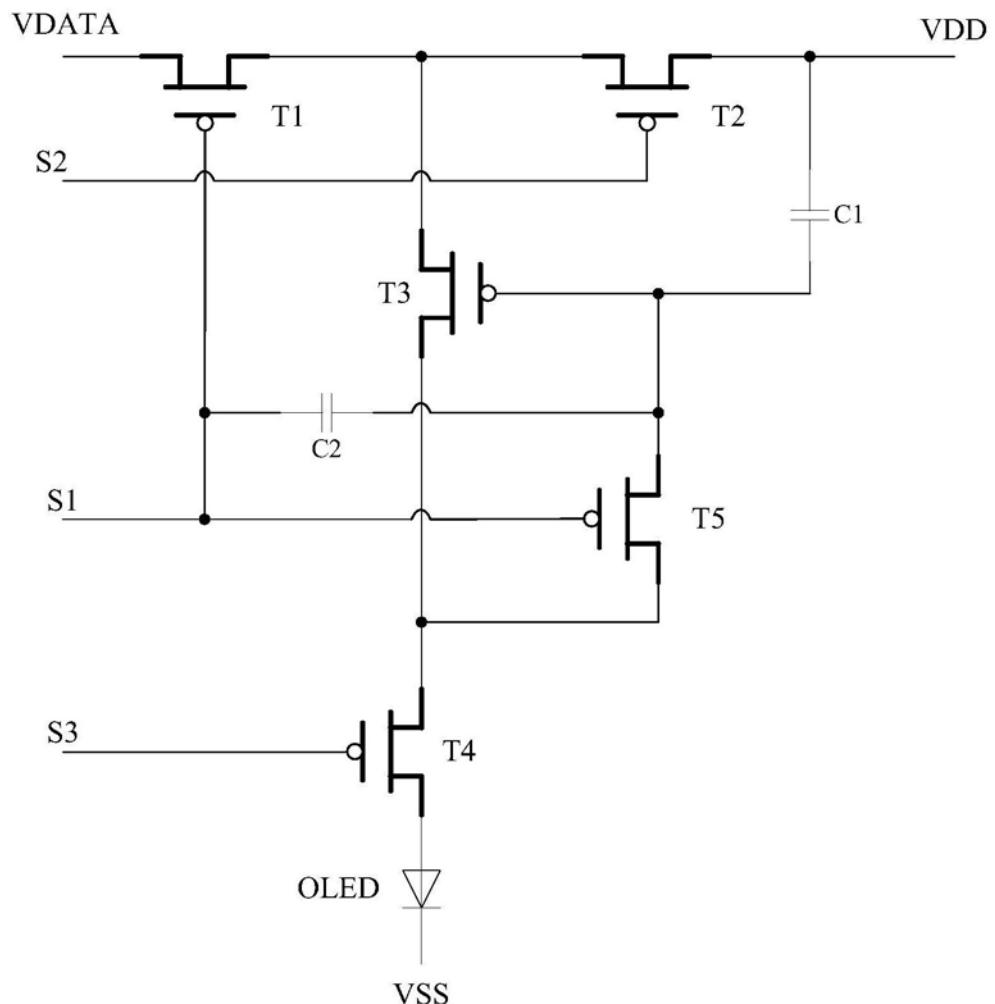

- [0043] 如图5所示，一实施例的像素单元电路包括第一薄膜晶体管T1、第二薄膜晶体管T2、第三薄膜晶体管T3、第四薄膜晶体管T4、第五薄膜晶体管T5、第一电容C1、第二电容C2以及有机发光二极管OLED，以PMOS为例，但是并不限于PMOS，其他器件，比如NMOS亦可。

- [0044] 所述第一薄膜晶体管T1：第一端输入数据信号VDATA、第二端与第二薄膜晶体管T2的第一端连接、第三端用于输入第一信号S1。

- [0045] 所述第二薄膜晶体管T2：第二端用于连接第一电源电压VDD、第三端用于输入第二信号S2。

- [0046] 所述第三薄膜晶体管T3：第一端连接第一薄膜晶体管T1的第二端、第二端连接第四薄膜晶体管T4的第一端、第三端通过第一电容C1与第二薄膜晶体管T2的第二端连接。

- [0047] 所述第四薄膜晶体管T4：第二端连接所述有机发光二极管OLED阳极，OLED阴极连接第二电源电压VSS、第三端用于输入第三信号S3。

- [0048] 所述第五薄膜晶体管T5：第一端连接第三薄膜晶体管T3的第三端、第二端与第四薄膜晶体管T4的第一端连接、第三端用于输入所述第一信号S1。

- [0049] 所述第二电容C2的两端分别连接所述第一薄膜晶体管T1的第三端和所述第五薄膜晶体管T5的第一端；

- [0050] 所述第一端和第二端分别为源极或漏极，所述第三端为栅极；所述第一信号S1、第二信号S2以及第三信号S3均为开启或关闭薄膜晶体管的高低电平信号。栅极驱动模块113可以用来提供上述第一信号S1、第二信号S2以及第三信号S3。

- [0051] 在其中一个实施例中，栅极驱动模块113还可以与像素电路一起集成在显示装置的屏体中，形成GIP结构。

- [0052] 在其中一个实施例中，所述第一薄膜晶体管、第二薄膜晶体管、第三薄膜晶体管、第四薄膜晶体管以及第五薄膜晶体管均为PMOS管。在其他实施例中，也可以都为NMOS管。

- [0053] 基于上述像素单元电路，提供一种像素单元电路的驱动方法，以PMOS晶体管为例，包括：

- [0054] 步骤S100：在第一时段内，设置所述第一信号S1为低电平，设置第二信号S2为高电平，第三信号S3保持不变，为低电平。所述第一薄膜晶体管T1和第五薄膜晶体管T5导通，并设置所述第二信号S2使得第二薄膜晶体管T2截止。利用第二电源电压VSS负压，初始化驱动

薄膜晶体管T3的栅极电压。

[0055] 步骤S200:在接下来的第二时段内,设置第一信号S1和第二信号S2保持不变,设置第三信号S3为高电平。所述第一薄膜晶体管T1以及第五薄膜晶体管T5保持导通,所述第二薄膜晶体管T2保持截止状态;第四薄膜晶体管T4变为截止状态。此时驱动薄膜晶体管T3的栅极电压变为VDATA-Vth,Vth为绝对值。

[0056] 步骤S300:第三阶段,设置所述第一信号S1为高电平,设置第二信号S2和第三信号S3为低电平。所述第一薄膜晶体管T1和第五薄膜晶体管T5由导通变成截止状态,所述第二薄膜晶体管T2由截止变成导通状态;所述第四薄膜晶体管T4由截止变成导通状态,此时完成了驱动晶体管T3的阈值电压补偿,发光二极管OLED的电流为:

$$I_{OLED} = 1/2 \cdot \mu \cdot C_{ox} \cdot W/L \cdot (VDD - VDATA)^2$$

[0058] 根据上述表达式,OLED发光电流与驱动晶体管的阈值电压没有关系,即完成了对驱动晶体管的补偿,采用该电路的屏体将提高整个屏体的显示一致性,提高了显示的质量。

[0059] 同时,该像素电路利用第二电源电压进行初始化,整个电路的输入电压和输入信号线数量较少,电路的晶体管数量较少,因此版图布局使用的面积较少,可以应用于更高分辨率的AMOLED屏体。

[0060] 上述步骤若基于采用NMOS管的结构,则高低电平都采用相反的设置,以对应器件的变化。

[0061] 以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

[0062] 以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

图1

图2

图3

图4

图5

图6

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | OLED显示装置及其像素电路、像素单元电路及驱动方法                     |         |            |

| 公开(公告)号        | <a href="#">CN108269526A</a>                   | 公开(公告)日 | 2018-07-10 |

| 申请号            | CN201710005474.9                               | 申请日     | 2017-01-04 |

| [标]申请(专利权)人(译) | 昆山工研院新型平板显示技术中心有限公司                            |         |            |

| 申请(专利权)人(译)    | 昆山工研院新型平板显示技术中心有限公司                            |         |            |

| 当前申请(专利权)人(译)  | 昆山工研院新型平板显示技术中心有限公司                            |         |            |

| [标]发明人         | 胡思明<br>杨楠<br>张九占<br>宋艳芹<br>朱晖                  |         |            |

| 发明人            | 胡思明<br>杨楠<br>张九占<br>宋艳芹<br>朱晖                  |         |            |

| IPC分类号         | G09G3/3225                                     |         |            |

| CPC分类号         | G09G3/3225 G09G2310/06                         |         |            |

| 其他公开文献         | CN108269526B                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a> |         |            |

**摘要(译)**

本发明涉及一种OLED显示装置及其像素电路、像素单元电路及驱动方法。该像素单元电路的第一薄膜晶体管：第一端输入数据信号、第二端连接第二薄膜晶体管、第三端用于输入第一信号；第二薄膜晶体管：第二端输入第一电源电压、第三端用于输入第二信号；第三薄膜晶体管：第三端通过第一电容与第二薄膜晶体管的第二端连接；第四薄膜晶体管：第二端通过有机发光二极管连接第二电源电压、第三端用于输入第三信号；第五薄膜晶体管：第一端连接第三薄膜晶体管的第三端、第三端输入第一信号；第二电容的两端分别连接第一薄膜晶体管的第一端和第五薄膜晶体管的第一端。该OLED显示装置及其像素电路、像素单元电路占用的版图面积少，可实现更高分辨率的屏体显示。