[19] 中华人民共和国国家知识产权局

[51] Int. Cl<sup>7</sup>

H05B 33/04

H05B 33/02

H05B 33/10

H05B 33/12

## [12] 发明专利申请公开说明书

[21] 申请号 200410104702.0

[43] 公开日 2005 年 7 月 27 日

[11] 公开号 CN 1645975A

[22] 申请日 2004.11.26

[74] 专利代理机构 上海专利商标事务所有限公司

[21] 申请号 200410104702.0

代理人 包于俊

[30] 优先权

[32] 2003.11.27 [33] JP [31] 2003-398084

[32] 2004.6.10 [33] JP [31] 2004-172450

[71] 申请人 东芝松下显示技术有限公司

地址 日本东京

[72] 发明人 佐野浩 炭田祉朗 吉冈达男

[54] 发明名称 显示元件、光学元器件以及光学元器件的制造方法

### [57] 摘要

本发明涉及显示元件、光学元器件以及光学元器件的制造方法。阵列基板 100 具有在基板正面形成的、配置有显示图象用的多个象素的、实质上呈矩形形状的有效部 106。有机 EL 显示装置 1 具有按照至少对阵列基板 100 上的正面的有效部 106 进行覆盖的方式配置的封装组件 300。封装组件 300 由具有实质上相同的图案的、至少两层的、实质上呈矩形形状的缓冲层 311、312、313，以及具有比各缓冲层更大的图案的、按照使其与外部空气隔断的方式对各缓冲层进行覆盖的壁垒层 321、322、323 叠层构成。由有效部 106 的端部处的一条侧边至第一缓冲层 311 的端部处的一条侧边间的最短距离，与至第二缓冲层 312 的端部处的一条侧边间的最短距离不同。

权利要求书 6 页 说明书 36 页 附图 16 页

1. 一种光学元器件，其特征在于，包括

在基板正面形成的、配置有显示图象用的多个象素的、实质上呈矩形形状

5 的有效部，以及

配置成至少对基板正面的所述有效部进行覆盖的封装组件，

所述封装组件由具有实质上相同图案的至少两层的缓冲层，以及具有比各缓冲层更大的图案且对各缓冲层进行覆盖的壁垒层叠层构成，而且由所述有效部端部的一条侧边起到第一缓冲层端部的一条侧边间的最短距离，与到第二缓冲层端部的一条侧边间的最短距离不同。

10 2. 如权利要求 1 所述的光学元器件，其特征在于，

所述有效部具有

形成在呈矩阵状配置在各象素处的、呈独立岛状的第一电极，

与所述第一电极相对配置的、共同形成在全部象素处的第二电极，以及

15 保持在所述第一电极与所述第二电极之间的有机活性层。

3. 如权利要求 1 所述的光学元器件，其特征在于，

所述第二缓冲层配置成覆盖所述第一缓冲层的一个角部。

4. 如权利要求 1 所述的光学元器件，其特征在于，

所述封装组件中的所述缓冲层至少具有三层，包括

20 第一缓冲层，

配置成覆盖所述第一缓冲层的一个角部的第二缓冲层，以及

配置成覆盖所述第二缓冲层的一个角部的第三缓冲层。

5. 如权利要求 1 所述的光学元器件，其特征在于，

所述第二缓冲层配置成使所述第一缓冲层的四个角部相对所述第二缓冲层

25 的角部呈曝露状态。

6. 如权利要求 1 所述的光学元器件，其特征在于，

所述壁垒层由金属材料、金属氧化物材料或陶瓷类材料形成。

7. 如权利要求 1 所述的光学元器件，其特征在于，

所述缓冲层由树脂材料形成。

30 8. 如权利要求 1 所述的光学元器件，其特征在于，

所述缓冲层由树脂材料形成，

所述第一缓冲层和所述第二缓冲层由利用同一图案的掩膜，经过对树脂材料进行蒸镀的工序形成。

9. 一种光学元器件的制造方法，该光学元器件包括在基板主面形成的、配置有显示图象用的多个象素的、实质上呈矩形形状的有效部，以及配置成至少对基板主面上的所述有效部进行覆盖的封装组件，其特征在于，

所述封装组件的制造工序包括

形成具有至少比所述有效部大的图案的、实质上呈矩形形状的第一缓冲层的工序，

- 10 形成具有至少比所述第一缓冲层大的图案、而且覆盖所述第一缓冲层的第一壁垒层的工序，

在所述第一壁垒层上形成具有与所述第一缓冲层实质上相同的图案的第二缓冲层的工序，以及

- 15 形成具有至少比所述第二缓冲层大的图案的、覆盖所述第二缓冲层的第二壁垒层的工序，

由所述有效部端部的一条侧边起到第一缓冲层端部的一条侧边间的最短距离，与到第二缓冲层端部的一条侧边间的最短距离不同。

10. 如权利要求 9 所述的光学元器件的制造方法，其特征在于，

所述有效部具有

- 20 形成在呈矩阵状配置在各象素处的、呈独立岛状的第一电极，

与所述第一电极相对配置、且共同形成在全部象素处的第二电极，以及保持在所述第一电极与所述第二电极之间的有机活性层。

11. 如权利要求 9 所述的光学元器件的制造方法，其特征在于，

形成所述第一缓冲层和所述第二缓冲层的工序，包含利用同一图案的掩膜

- 25 对树脂材料进行蒸镀的蒸镀工序。

12. 如权利要求 11 所述的光学元器件的制造方法，其特征在于，

在分别形成所述第一缓冲层和所述第二缓冲层用的蒸镀工序中，使所述掩膜在不同位置进行位置吻合。

13. 如权利要求 11 所述的光学元器件的制造方法，其特征在于，

在形成所述第一缓冲层用的蒸镀工序中，以基板主面上的第一基准标志为

基准进行位置吻合，并利用所述掩膜对树脂材料进行蒸镀，

在形成所述第二缓冲层用的蒸镀工序中，以相对所述第一基准标志 AM 位于不同位置的第二基准标志为基准进行位置吻合，并利用所述掩膜对树脂材料进行蒸镀。

5 14. 一种形成在基板正面的显示元件，其特征在于，包括

配置成覆盖所述显示元件的封装组件，

所述封装组件由至少两层的缓冲层，以及具有比各缓冲层更大的图案且对各缓冲层进行覆盖的壁垒层叠层构成，

第一缓冲层具有与配置在其上层处的第二缓冲层不同尺寸的图案，

10 所述第二缓冲层叠层成其外侧边缘部在基板正面内位于比所述第一缓冲层的外侧边缘部更内侧或更外侧的位置。

15 15. 一种光学元器件，其特征在于，包括

在基板正面形成的、具有多个显示元件的有效部，以及

配置成至少对基板正面的所述有效部进行覆盖的封装组件，

所述封装组件由至少两层的缓冲层，以及具有比各缓冲层更大的图案且对各缓冲层进行覆盖的壁垒层叠层构成，

第一缓冲层具有与配置在其上层处的第二缓冲层不同尺寸的图案，

所述第二缓冲层叠层成其外侧边缘部在基板正面内位于比所述第一缓冲层的外侧边缘部更内侧或更外侧的位置。

20 16. 如权利要求 15 所述的光学元器件，其特征在于，

所述第一缓冲层具有比所述第二缓冲层更大尺寸的图案，

所述第二缓冲层的外侧边缘部位于基板正面内比所述第一缓冲层的外侧边缘部更内侧的位置。

17. 如权利要求 15 所述的光学元器件，其特征在于，

25 所述第一缓冲层具有比所述第二缓冲层更小尺寸的图案，

所述第二缓冲层的外侧边缘部位于基板正面内比所述第一缓冲层的外侧边缘部更外侧的位置。

18. 如权利要求 15 所述的光学元器件，其特征在于，

所述有效部具有

30 形成在呈矩阵状配置在各像素处的、呈独立岛状的第一电极，

与所述第一电极相对配置的、共同形成在全部象素处的第二电极，以及保持在所述第一电极与所述第二电极之间的有机活性层。

19. 如权利要求 15 所述的光学元器件，其特征在于，所述壁垒层由金属材料、金属氧化物材料或陶瓷类材料形成。

5 20. 如权利要求 15 所述的光学元器件，其特征在于，所述缓冲层由树脂材料形成。

21. 一种光学元器件的制造方法，该光学元器件包括在基板正面形成的、配置有多个象素的有效部，以及配置成至少对基板正面的所述有效部进行覆盖的封装组件，其特征在于，

10 所述封装组件的制造工序包括

形成与所述有效部相对应的第一缓冲层的工序，

形成具有至少比所述第一缓冲层大的图案、而且覆盖所述第一缓冲层的第一壁垒层的工序，

在所述壁垒层上形成与所述有效部相对应的第二缓冲层的工序，以及

15 形成所述第一缓冲层和所述第二缓冲层的工序，包含利用同一图案的掩膜，对树脂材料进行成膜的成膜工序，各个成膜工序按照由基板正面到所述掩膜间的间隔不同进行位置吻合，

第一缓冲层具有与所述第二缓冲层不同尺寸的图案，

20 所述第二缓冲层按照其外侧边缘部位于基板正面内比所述第一缓冲层的外侧边缘部更内侧或更外侧的位置的方式进行叠层设置。

22. 如权利要求 21 所述的光学元器件的制造方法，其特征在于，

形成所述第二缓冲层用的成膜工序中由基板正面到所述掩膜间的间隔，设定成比形成所述第一缓冲层用的所述成膜工序中由基板正面到所述掩膜间的间隔更小，

25 所述第二缓冲层具有比所述第一缓冲层更小尺寸的图案，

所述第二缓冲层叠层成其外侧边缘部在基板正面内位于比所述第一缓冲层的外侧边缘部更内侧或更外侧的位置。

23. 如权利要求 21 所述的光学元器件的制造方法，其特征在于，

形成所述第二缓冲层用的成膜工序中由基板主面到所述掩膜间的间隔，设定成比形成所述第一缓冲层用的所述成膜工序中由基板主面到所述掩膜间的间隔更大，

所述第二缓冲层具有比所述第一缓冲层更大尺寸的图案，

5 所述第二缓冲层的外侧边缘部在基板主面内位于比所述第一缓冲层的外侧边缘部更外侧的位置。

24. 一种光学元器件的制造方法，该光学元器件包括在基板主面形成的多个象素的有效部，以及按照至少对基板主面上的所述有效部进行覆盖的方式配置的封装组件，其特征在于，

10 所述封装组件的制造工序包括

将壁垒层用掩膜安装到形成所述有效部的基板主面用的安装工序，

通过所述壁垒层用掩膜形成至少覆盖所述有效部的第一壁垒层的工序，

在所述第一壁垒层上形成与所述有效部相对应的第一缓冲层的工序，

15 通过所述壁垒层用掩膜形成具有比所述第一缓冲层大的图案的、覆盖所述第一缓冲层的第二壁垒层的工序，

在所述第二壁垒层上形成与所述有效部相对应的第二缓冲层的工序，以及

通过所述壁垒层用掩膜形成具有比所述第二缓冲层大的图案的、覆盖所述第二缓冲层的第三壁垒层的工序，

形成所述第一缓冲层和所述第二缓冲层的工序，包含利用同一图案的掩膜，

20 对树脂材料进行成膜的成膜工序，各个成膜工序按照由基板主面到所述掩膜间的间隔不同进行位置吻合，

所述第一缓冲层具有与所述第二缓冲层不同尺寸的图案，

所述第二缓冲层叠层成其外侧边缘部在基板主面内位于比所述第一缓冲层的外侧边缘部更内侧或更外侧的位置。

25. 一种光学元器件，其特征在于，包括

在基板主面形成的、具有显示图象用的多个象素的显示区域，以及

叠层组件，该叠层组件由配置成覆盖所述显示区域的第一薄膜、覆盖所述第一薄膜的第二薄膜、覆盖所述显示区域且部分覆盖所述第二薄膜的第三薄膜、以及以及覆盖所述第三薄膜的第四薄膜叠层构成，

30 所述第一薄膜与所述第三薄膜的平面形状不同。

26. 一种显示装置，其特征在于，包括

包含在其主表面处的、具有显示图象用的多个象素的显示区域的基板，以及

叠层组件，该叠层组件由配置成覆盖所述显示区域的第一薄膜、覆盖所述

- 5 第一薄膜的第二薄膜、按照与所述第一薄膜不同的图案构成且部分覆盖所述第二薄膜的第三薄膜、以及覆盖所述第三薄膜的第四薄膜叠层构成，

所述第一薄膜和所述第三薄膜的至少一条侧边的端部平面位置不同。

27. 一种显示装置，其特征在于，包括

在基板正面形成的、具有显示图象用的多个象素的显示区域，以及

10 叠层组件，该叠层组件由配置成覆盖所述显示区域的第一薄膜、覆盖所述

- 第一薄膜的第二薄膜、按照与所述第一薄膜相同的图案构成且部分覆盖所述第二薄膜的第三薄膜、以及覆盖所述第三薄膜的第四薄膜叠层构成，

所述第一薄膜和所述第三薄膜的平面位置不同。

## 显示元件、光学元器件以及光学元器件的制造方法

### 5 技术领域

本发明涉及显示元件、光学元器件及光学元器件的制造方法，特别涉及包含有多个诸如自发光元件等等的显示元件的光学元器件及其制造方法。

#### 背景技术

近年来，作为平面显示装置的有机电致发光(EL)显示装置正在受到关注。

10 由于这种有机 EL 显示装置是一种具有自发光元件的显示装置，所以具有视角比较大，不需要背光组件，可以实现薄型化，而且可以抑制电力消耗，响应速度比较快等特征。

由于具有这些特征，有机 EL 显示装置作为取代液晶显示装置的下一代平面显示装置中的主要候选对象，正在引起越来越多的关注。这种有机 EL 显示

15 装置具有由呈矩阵形状配置的作为自发光元件的有机 EL 元件构成的阵列型基板。有机 EL 元件呈在阳极与阴极之间，夹持着包含有具有发光性能的有机化合物的有机活性层的构成形式。

有机 EL 元件在与包含在外部空气中的水分和氧气接触时，其发光性能将急剧恶化。因此，已经有人提出了对阵列型基板上配置有有机 EL 元件的主面

20 与外部空气间的接触实施隔断、封阻的各种技术解决方案。如果举例来说，包含有这些技术的各种技术解决方案中的一个实例，为在有机 EL 元件的表面侧处配置的电极上，叠层形成有机膜和无机膜的膜封装技术（比如说，可以参见非专利文献：柳雄二，“薄型、大型、柔性基板批量生产的对策”，フ ラット

パネル・ディスプレイ 2003，日经 BP 社，2002 年 12 月 27 日，p.264—270）。

25 对有机 EL 元件进行的封装，需要具有良好的台阶状覆盖性，成膜为不包含诸如针孔和龟裂等等缺陷的薄膜。然而，获得完全不存在缺陷的薄膜在实施方面存在困难。因此，难以使有机 EL 元件完全与外部空气隔断，从而难以在长时间里保持良好的工作性能。

#### 发明内容

30 本发明就是解决上述问题用的发明，本发明的目的就是提供一种具有优良

的封装性能，且能够保持良好显示性能的显示元件、光学元器件及光学元器件的制造方法。

作为本发明第一方面的一种光学元器件，可以具有：

在基板正面形成的、配置有显示图象用的多个象素的、实质上呈矩形形状

5 的有效部；以及

按照至少对基板正面的所述有效部进行覆盖的方式配置的封装组件；

所述封装组件由具有实质上相同的图案的、至少两层的缓冲层，以及具有

比所述缓冲层更大的图案且对各缓冲层进行覆盖的壁垒层叠层构成，而且由所

述有效部端部的一条侧边起至第一缓冲层端部的一条侧边间的最短距离，与至

10 第二缓冲层端部的一条侧边间的最短距离不同。

作为本发明第二方面的一种光学元器件的制造方法是具有在基板正面形成

的、配置有显示图象用的多个象素的、实质上呈矩形形状的有效部，以及按照

至少对基板正面的所述有效部进行覆盖的方式配置的封装组件的光学元器件

的制造方法，所述封装组件的制造工序可以包括：

15 对具有至少比所述有效部大的图案的、实质上呈矩形形状的第一缓冲层实

施形成的工序；

对具有至少比所述第一缓冲层大的图案的、覆盖所述第一缓冲层的第一壁

垒层实施形成的工序；

20 在所述第一壁垒层上对具有与所述第一缓冲层实质上相同的图案的第二缓

冲层实施形成的工序；

以及对具有至少比所述第二缓冲层大的图案的、覆盖所述第二缓冲层的第

二壁垒层实施形成的工序；

而且由所述有效部端部的一条侧边起至第一缓冲层端部的一条侧边间的最

短距离，与至第二缓冲层端部的一条侧边间的最短距离不同。

25 作为本发明第三方面的一种显示元件是在基板正面形成的显示元件，可以

具有按照覆盖所述显示元件的方式实施配置的封装组件；

所述封装组件由至少两层的缓冲层，以及具有比各缓冲层更大的图案且对

各缓冲层进行覆盖的壁垒层叠层构成；

第一缓冲层具有与配置在其上层处的第二缓冲层不同尺寸的图案；

30 所述第二缓冲层按照其外侧边缘部位于基板正面内比所述第一缓冲层的外

侧边缘部更内侧或更外侧的位置的方式实施叠层设置。

作为本发明第四方面的一种光学元器件，可以具有：

包括有在基板正面形成的多个显示元件的有效部；

以及按照至少对基板正面的所述有效部进行覆盖的方式配置的封装组件；

5 件；

所述封装组件由至少两层的缓冲层，以及具有比各缓冲层更大的图案且对各缓冲层进行覆盖的壁垒层叠层构成；

第一缓冲层具有与配置在其上层处的第二缓冲层不同尺寸的图案；

所述第二缓冲层按照其外侧边缘部位于基板正面内比所述第一缓冲层的外10侧边缘部更内侧或更外侧的位置的方式实施叠层设置。

作为本发明第五方面的一种光学元器件的制造方法是具有在基板正面形成的、配置有显示图象用的多个象素的有效部，以及按照至少对基板正面的所述有效部进行覆盖的方式配置的封装组件的光学元器件的制造方法，所述封装组件的制造工序可以包括：

15 对与所述有效部相对应的第一缓冲层实施形成的工序；

对具有比所述第一缓冲层大的图案的、覆盖所述第一缓冲层的壁垒层实施形成的工序；

在所述壁垒层上对与所述有效部相对应的第二缓冲层实施形成的工序；

而且形成所述第一缓冲层和所述第二缓冲层的工序，包含利用同一图案的20掩膜，对树脂材料实施成膜的成膜工序，各个成膜工序是按照由基板正面到所述掩膜间的间隔不同的方式实施位置吻合的；

第一缓冲层具有与所述第二缓冲层不同尺寸的图案；

所述第二缓冲层按照其外侧边缘部位于基板正面内比所述第一缓冲层的外侧边缘部更内侧或更外侧的位置的方式实施叠层设置。

25 作为本发明第六方面的一种光学元器件的制造方法是具有在基板正面形成的多个象素的有效部，以及按照至少对基板正面的所述有效部进行覆盖的方式配置的封装组件的光学元器件的制造方法，所述封装组件的制造工序可以包括：

将壁垒层用掩膜安装至形成所述有效部的基板正面用的安装工序；

30 通过所述壁垒层用掩膜对至少覆盖所述有效部的第一壁垒层实施形成的工

序:

在所述第一壁垒层上对与所述有效部相对应的第一缓冲层实施形成的工序;

通过所述壁垒层用掩膜对具有比所述第一缓冲层大的图案的、覆盖所述第5一缓冲层的第二壁垒层实施形成的工序;

在所述第二壁垒层上对与所述有效部相对应的第二缓冲层实施形成的工序;

以及通过所述壁垒层用掩膜对具有比所述第二缓冲层大的图案的、覆盖所述第二缓冲层的第三壁垒层实施形成的工序;

10 而且形成所述第一缓冲层和所述第二缓冲层的工序，包含利用同一图案的掩膜，对树脂材料实施成膜的成膜工序，各个成膜工序是按照由基板主面到所述掩膜间的间隔不同的方式实施位置吻合的；

所述第一缓冲层具有与所述第二缓冲层不同尺寸的图案；

15 所述第二缓冲层按照其外侧边缘部位于基板主面内比所述第一缓冲层的外侧边缘部更内侧或更外侧的位置的方式实施叠层设置。

本发明的其它目的和优点给出在下述的说明中，其中一部分可以通过本说明书明确获知，其它可以通过实施本发明而了解。而且，本发明的各个目的和优点，可以通过参照实施例部分和对下述各部分的组合而获得更加清楚的认识和理解。

20 附图说明

被引入在说明书并构成为说明书一部分的附图，以示意图形式说明着本发明的若干最佳实施例，这些附图与上面给出的综合性描述和下面给出的、对最佳实施例进行的详细描述一起，解释说明着本发明的原理。

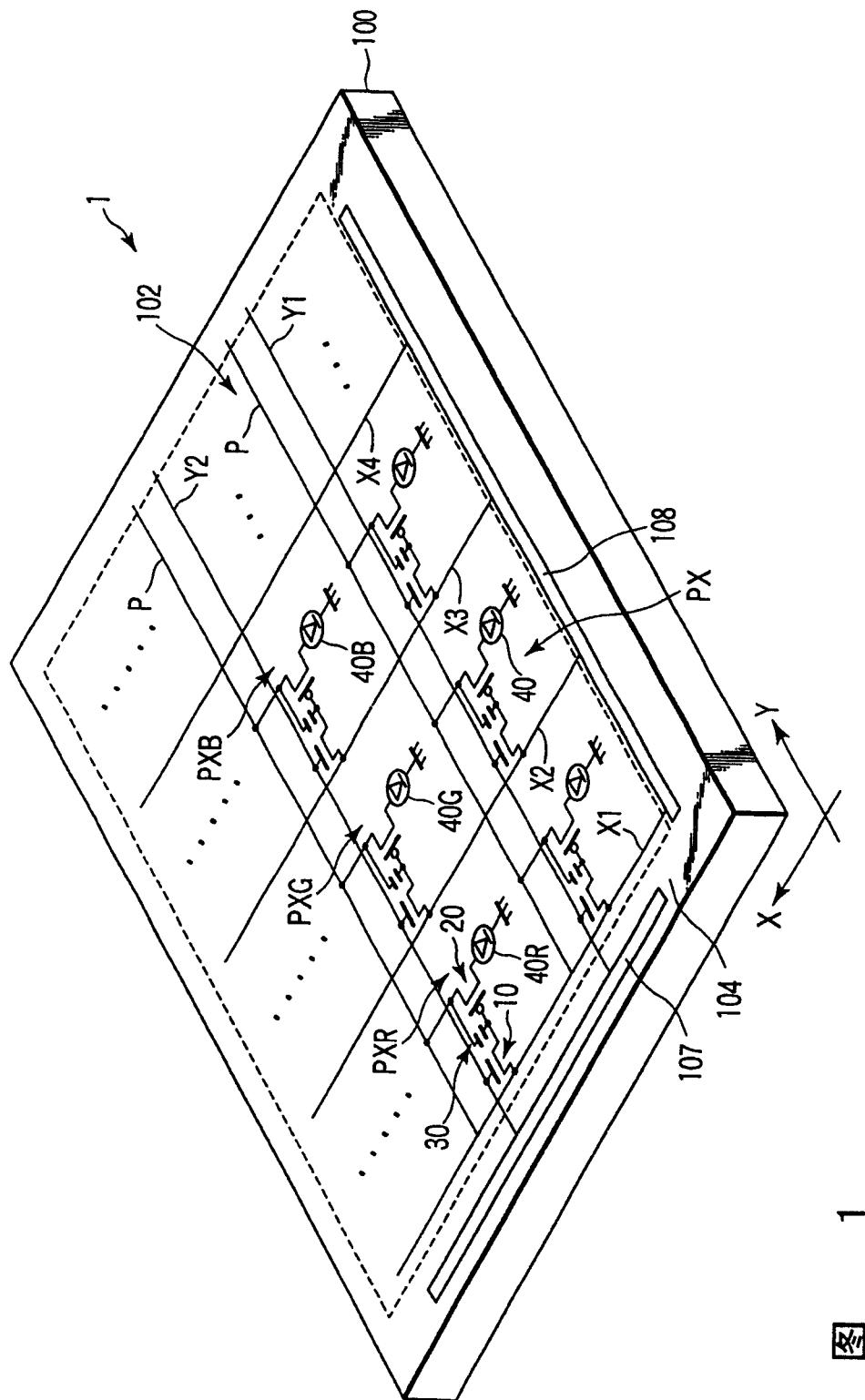

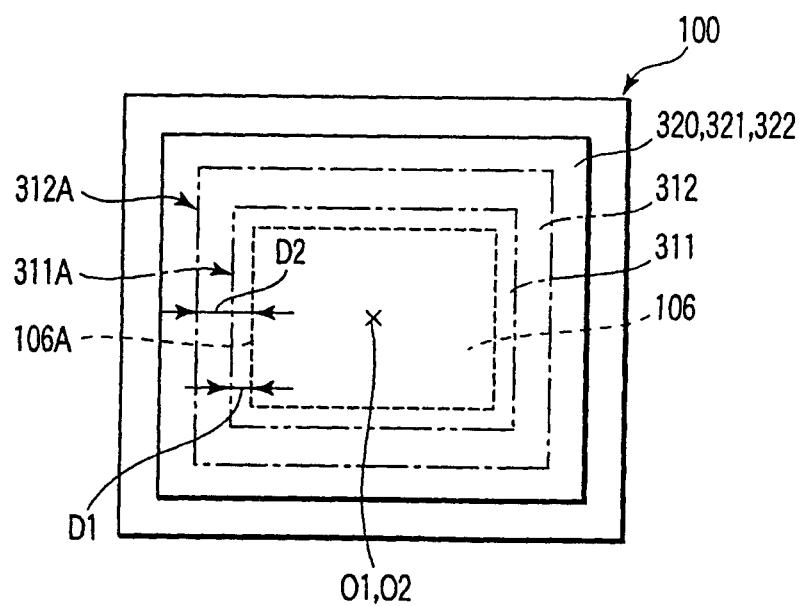

25 图 1 为表示作为本发明一种实施形式的有机 EL 显示装置中的阵列基板的构成形式用的示意图。

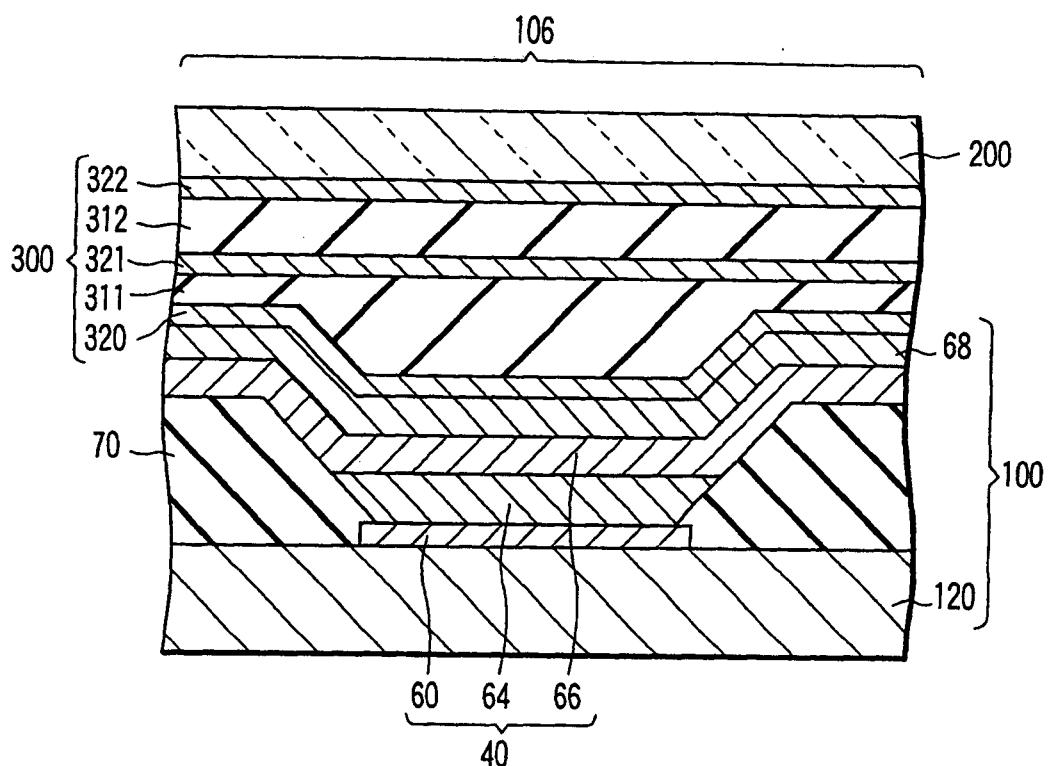

图 2 为表示如图 1 所示的有机 EL 显示装置中的一个象素部分的构成形式用的示意性剖面图。

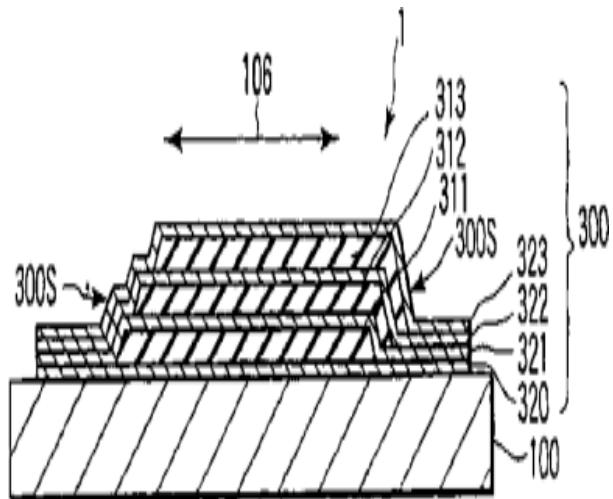

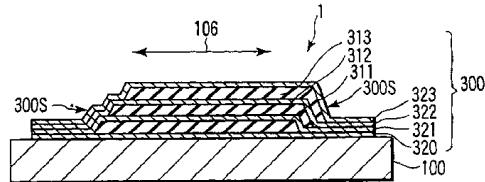

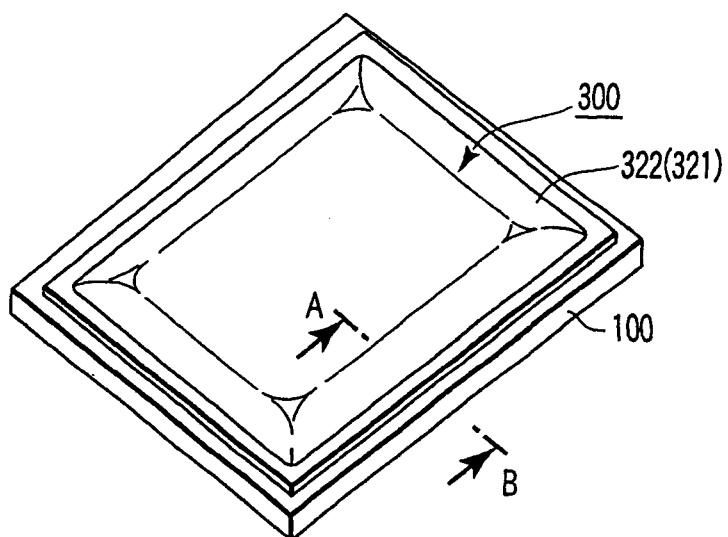

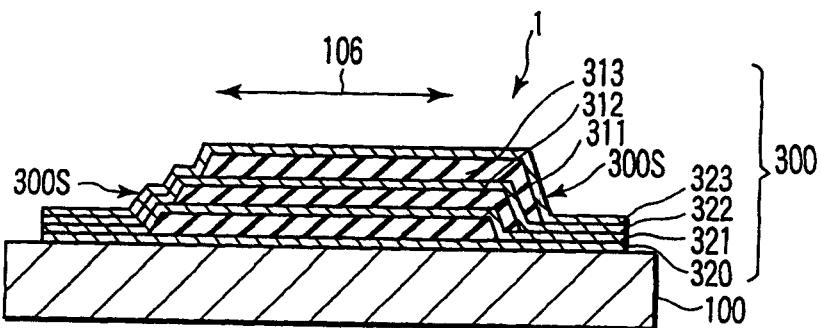

图 3 为表示配置有封装组件的阵列基板的外观用的示意性斜视图。

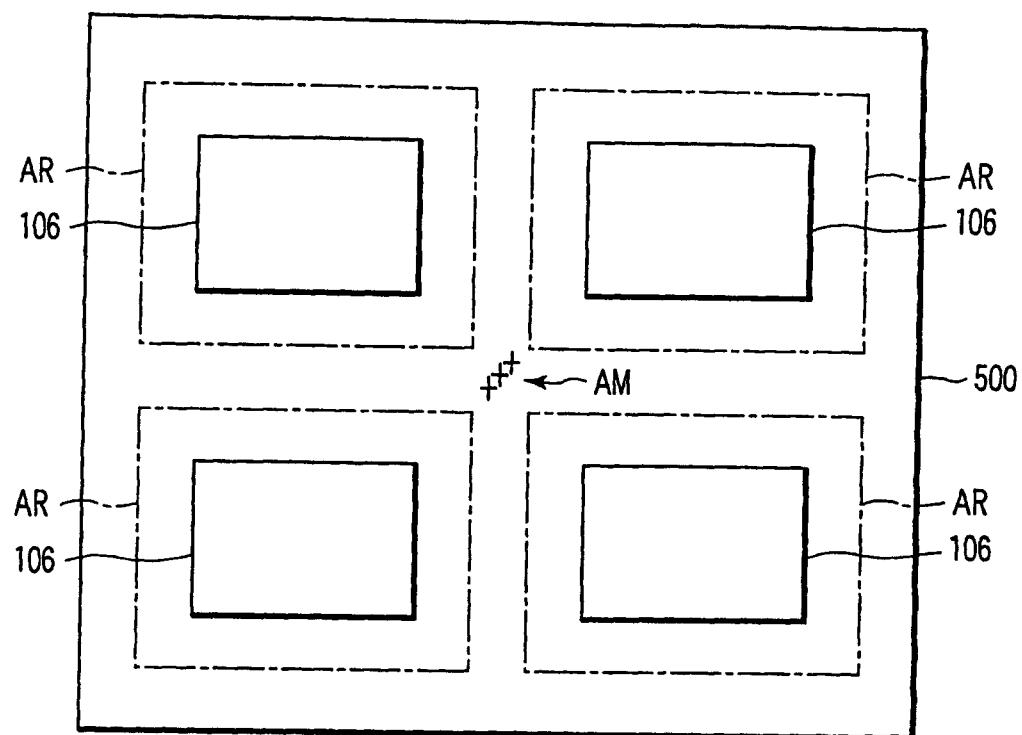

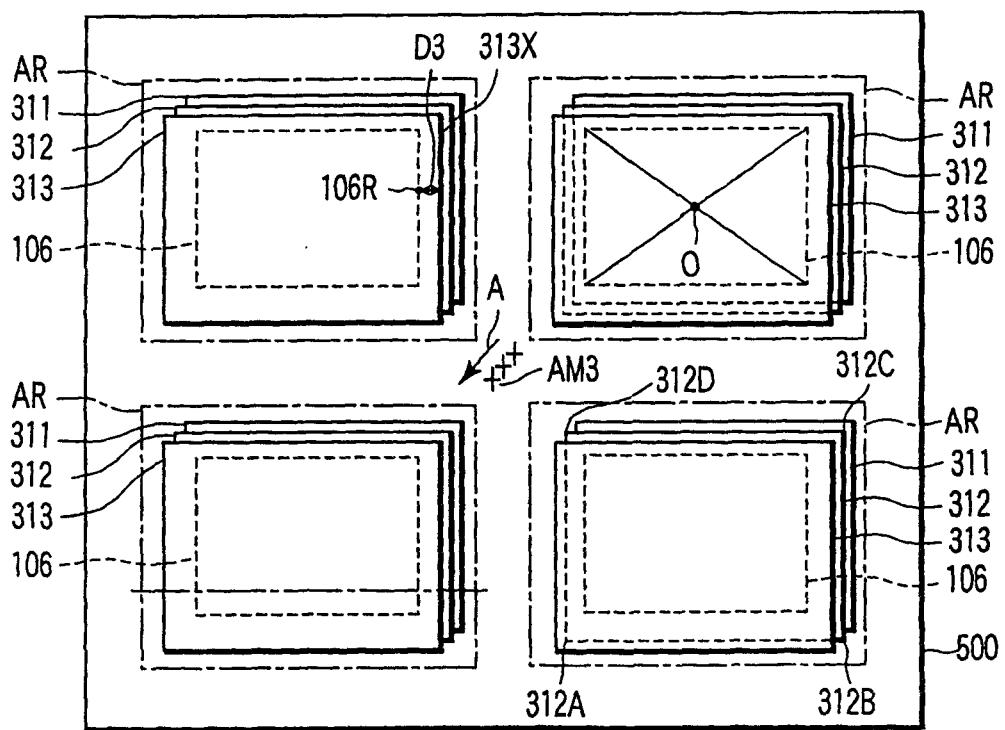

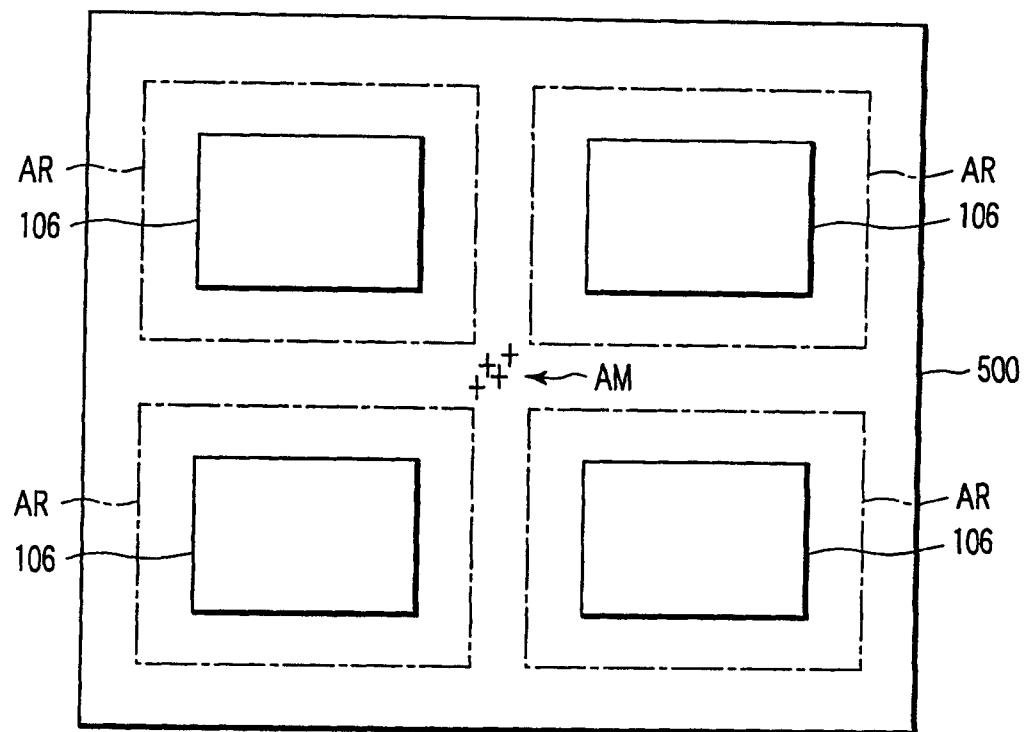

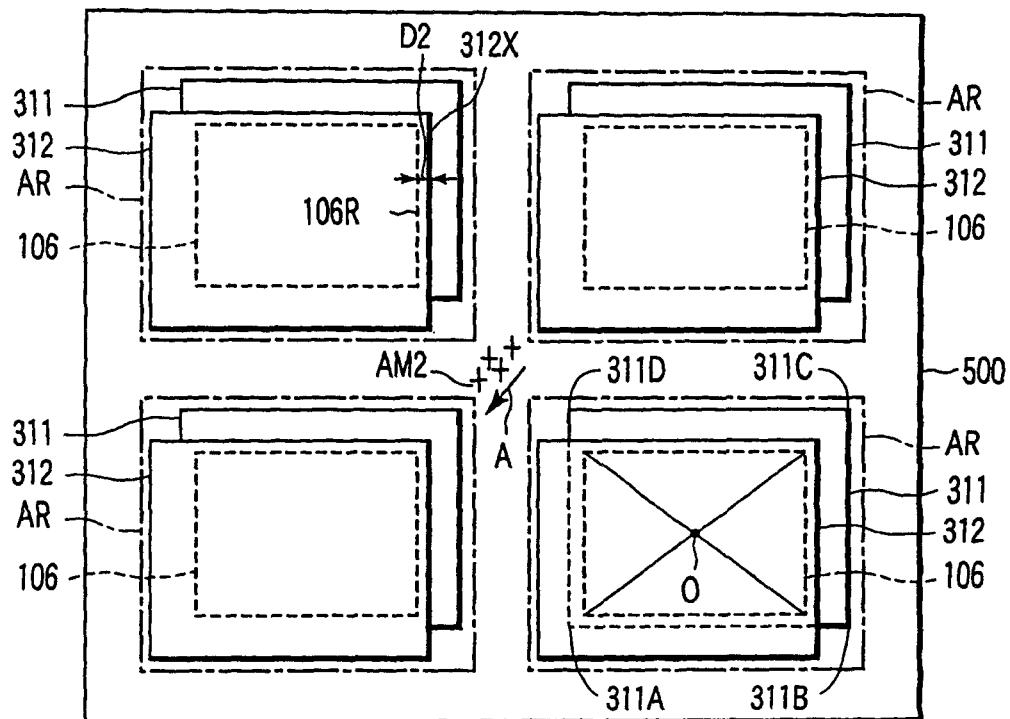

30 图 4A 为说明作为第一实施例的有机 EL 显示装置的制造方法用的示意性平面图。

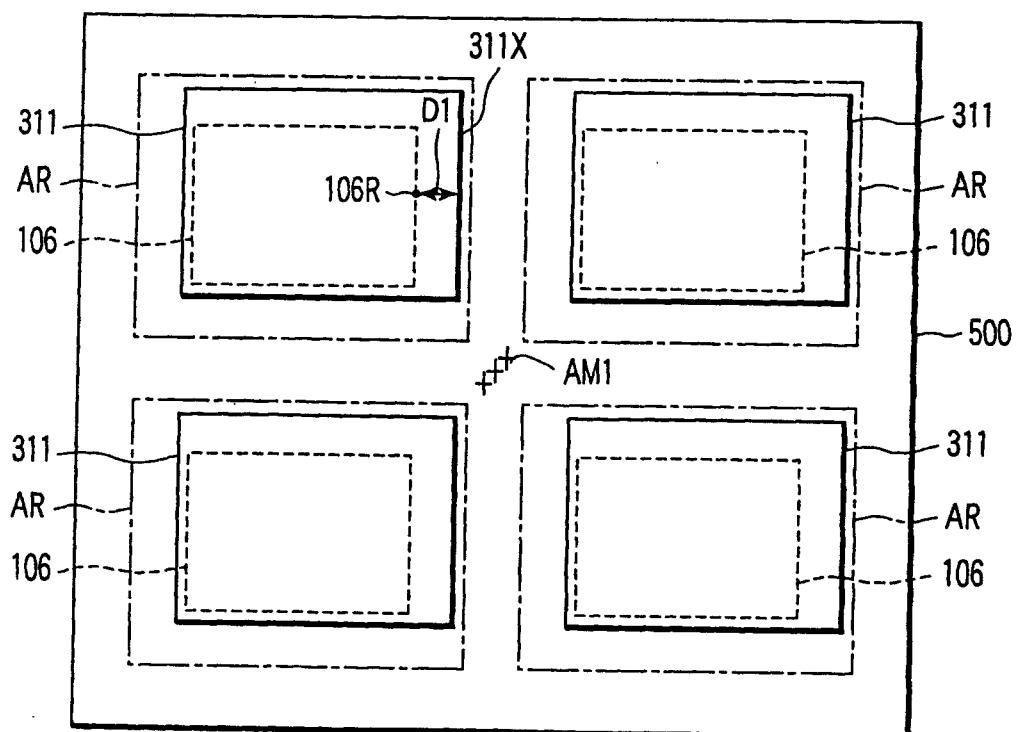

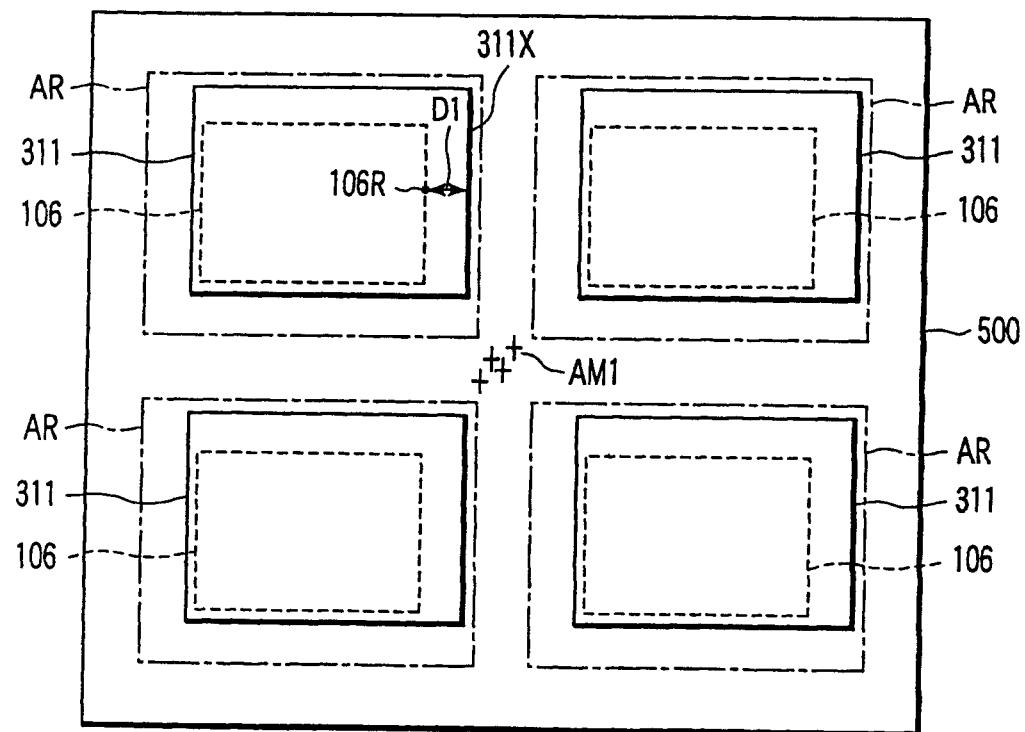

图4B为说明作为第一实施例的有机EL显示装置的制造方法用的示意性平面图。

图4C为说明作为第一实施例的有机EL显示装置的制造方法用的示意性平面图。

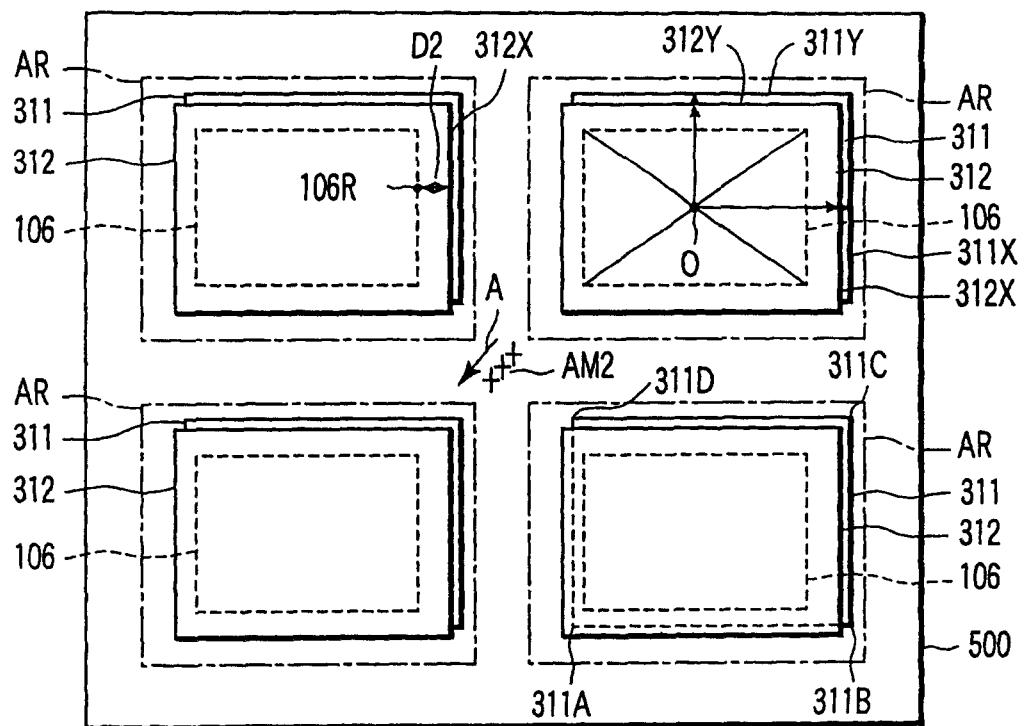

5 图4D为说明作为第一实施例的有机EL显示装置的制造方法用的示意性平面图。

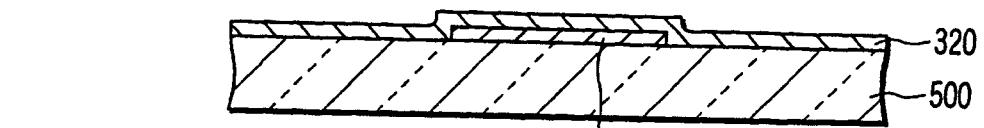

图5A为说明形成封装组件的壁垒层用的制造工序的示意图。

图5B为说明形成封装组件的缓冲层用的制造工序的示意图。

图5C为说明形成封装组件的壁垒层用的制造工序的示意图。

10 图6为表示通过第一实施例和第三实施例制造出的有机EL显示装置的剖面构成形式用的示意图。

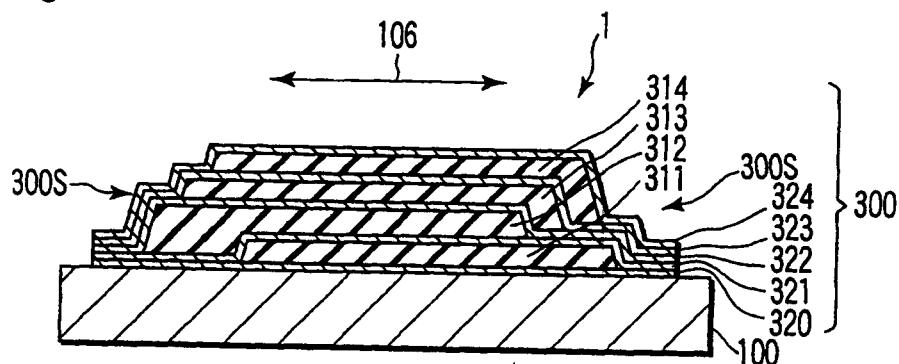

图7为表示通过第二实施例制造出的有机EL显示装置的剖面构成形式用的示意图。

15 图8A为说明第二实施例的有机EL显示装置的制造方法用的示意性平面图。

图8B为说明第二实施例的有机EL显示装置的制造方法用的示意性平面图。

图8C为说明第二实施例的有机EL显示装置的制造方法用的示意性平面图。

20 图8D为说明第二实施例的有机EL显示装置的制造方法用的示意性平面图。

图8E为说明第二实施例的有机EL显示装置的制造方法用的示意性平面图。

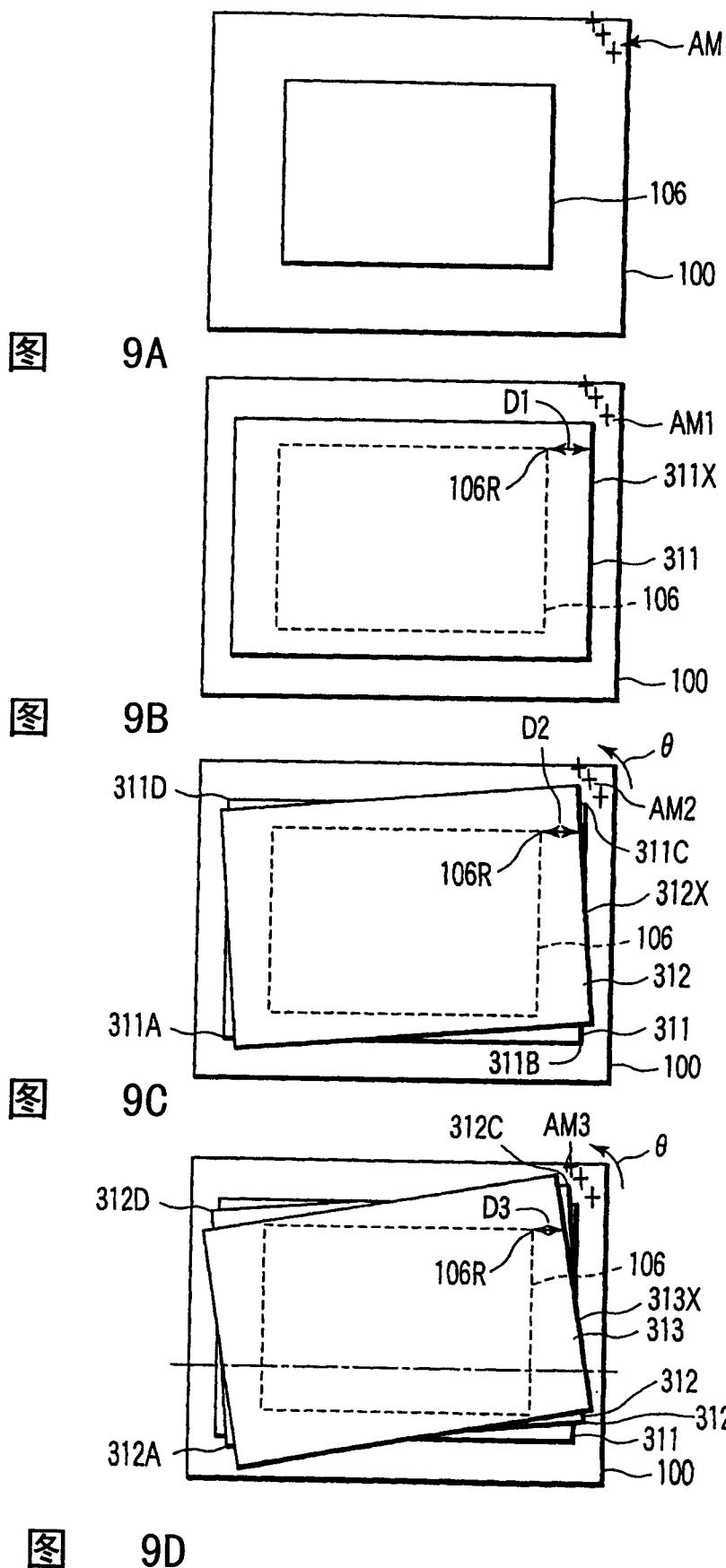

25 图9A为说明第三实施例的有机EL显示装置的制造方法用的示意性平面图。

图9B为说明第三实施例的有机EL显示装置的制造方法用的示意性平面图。

图9C为说明第三实施例的有机EL显示装置的制造方法用的示意性平面图。

30 图9D为说明第三实施例的有机EL显示装置的制造方法用的示意性平面

图。

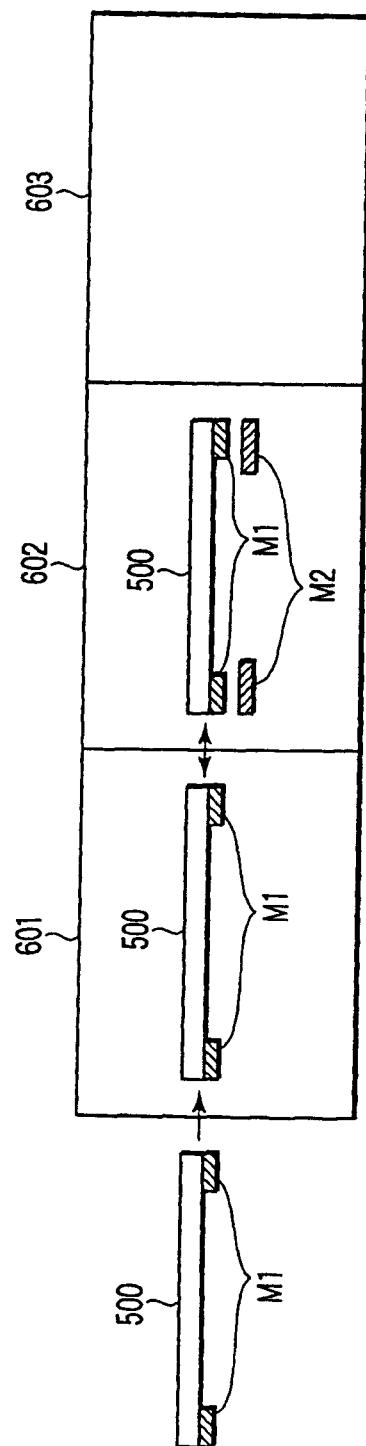

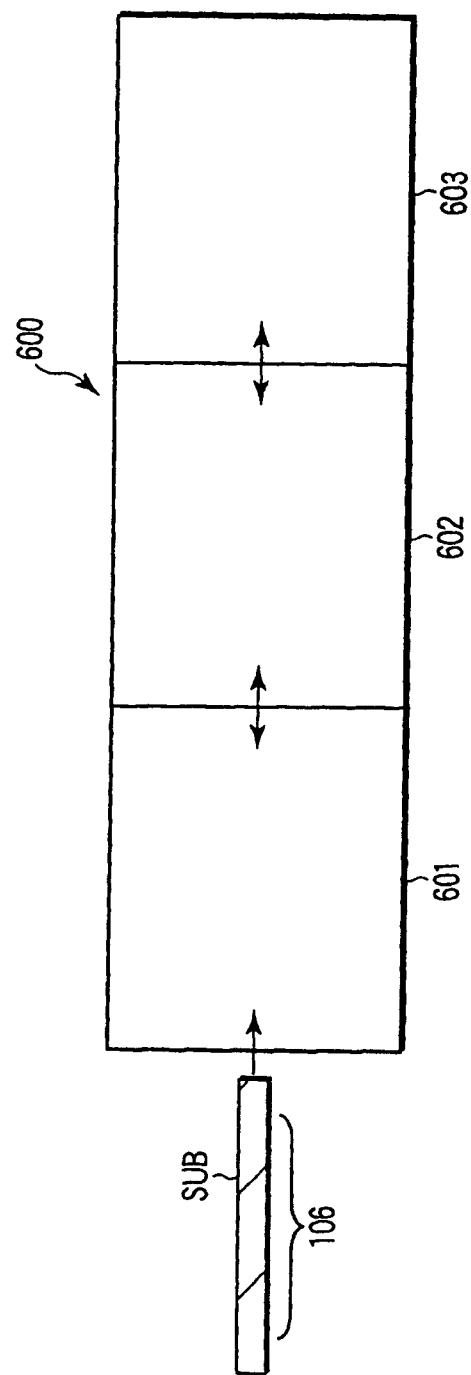

图 10 为表示形成封装组件用的制造装置的构成形式用的示意图。

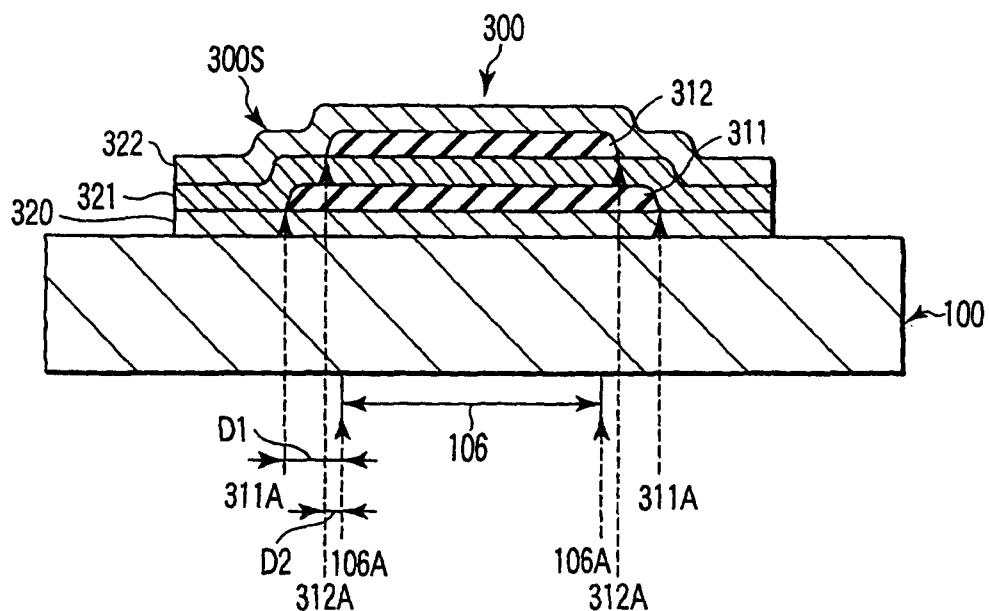

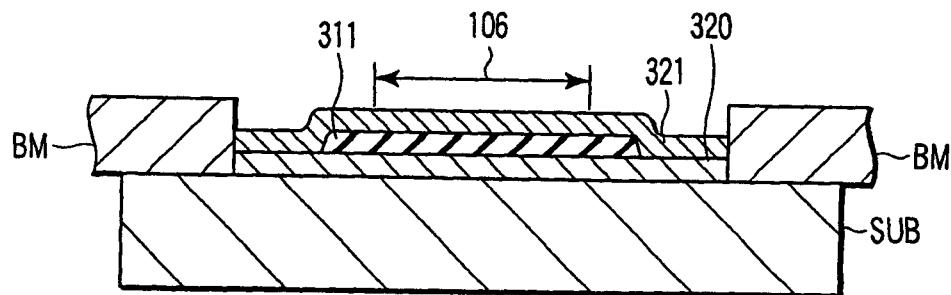

图 11A 为表示沿 A—B 线对如图 3 所示的阵列基板实施剖开时的封装组件的剖面构成形式用的示意图。

5 图 11B 为表示如图 11A 所示的阵列基板和封装组件的平面构成形式用的示意图。

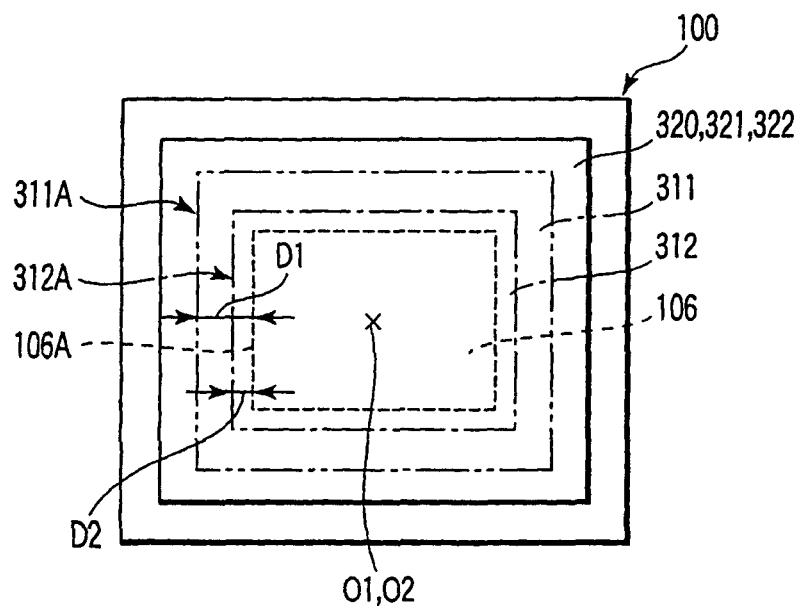

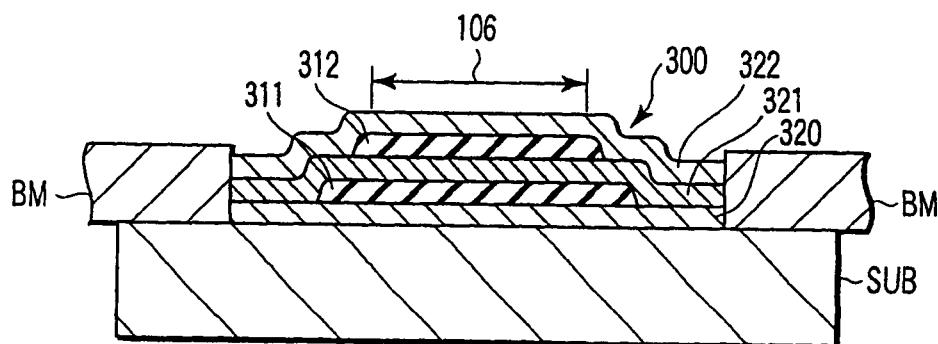

图 12A 为表示沿 A—B 线对如图 3 所示的阵列基板实施剖开时的另一封装组件的剖面构成形式用的示意图。

10 图 12B 为表示如图 12A 所示的阵列基板和封装组件的平面构成形式用的示意图。

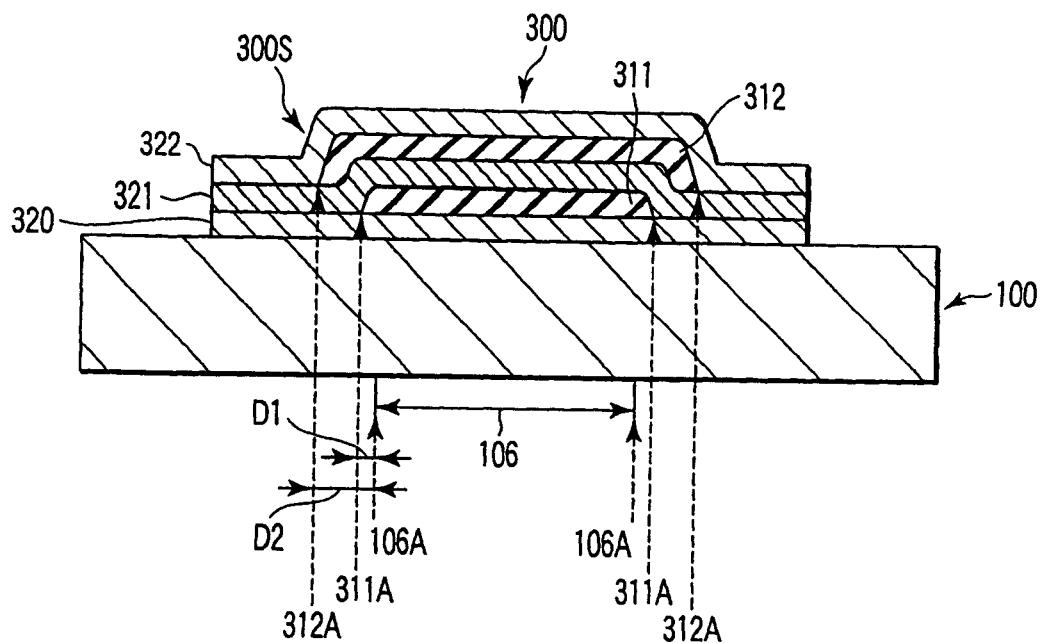

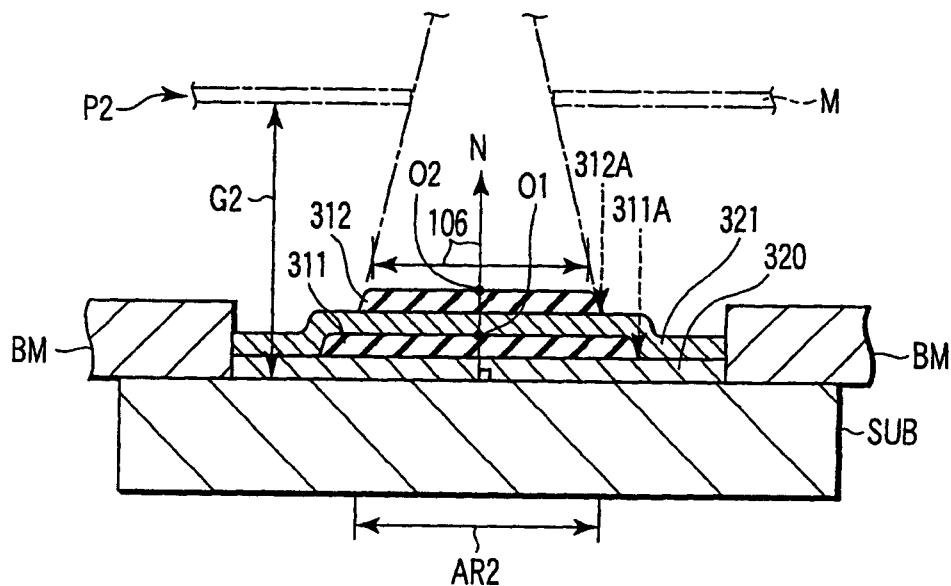

图 13A 为说明有机 EL 显示装置的制造方法用的示意性剖面图。

图 13B 为说明使用在有机 EL 显示装置处的封装组件的第一壁垒层的制造方法用的示意性剖面图。

15 图 13C 为说明使用在有机 EL 显示装置处的封装组件的第一缓冲层的制造方法用的示意性剖面图。

图 13D 为说明使用在有机 EL 显示装置处的封装组件的第二壁垒层的制造方法用的示意性剖面图。

图 13E 为说明使用在有机 EL 显示装置处的封装组件的第二缓冲层的制造方法用的示意性剖面图。

20 图 13F 为说明使用在有机 EL 显示装置处的封装组件的第三壁垒层的制造方法用的示意性剖面图。

图 14 为表示形成封装组件用的制造装置的构成形式用的示意图。

图 15 为表示如图 14 所示的制造装置中的第二腔室的构成形式用的示意图。

具体实施方式

25 下面参考附图，对作为本发明一种实施形式的显示元件、光学元器件和光学元器件的制造方法进行说明。而且在该实施形式中，光学元器件是以诸如有机 EL（电致发光）显示装置等等的自发光型显示装置为例进行说明的。

正如图 1 和图 2 所示，有机 EL 显示元件 1 具有包含着显示图象用的显示区域 102 的阵列基板 100，以及至少对阵列基板 100 上的显示区域 102 实施密封用的封装组件 300。阵列型基板 100 处的显示区域 102，可以由呈矩阵形式配

置的多个象素 PX (R、G、B) 构成。

各象素 PX (R、G、B) 包括有具有对导通象素和断开象素实施电气分离且能够对供给至导通象素处的图像信号实施保持的功能的象素开关 10，依据通过象素开关 10 实施供给的图像信号向显示元件供给出所需要的驱动电流用的 5 驱动型晶体管 20，以及在预定时间里对驱动型晶体管 20 的栅极—源极间电位实施保持用的储存容量元件 30。这种象素开关 10 和驱动型晶体管 20 可以由诸如薄膜晶体管等构成，在这儿利用的是形成在半导体层中的多晶硅。

而且，各象素 PX (R、G、B) 分别具有作为显示元件的有机 EL 元件 40 (R、G、B)。换句话说就是，红色象素 PXR 具有可发射出红色光束的有机 10 EL 元件 40R。绿色象素 PXG 具有可发射出绿色光束的有机 EL 元件 40G。兰色象素 PXB 具有可发射出兰色光束的有机 EL 元件 40B。

各种有机 EL 元件 40 (R、G、B) 的构成形式实质上相同，有机 EL 元件 40 具有在呈矩阵状配置的各象素 PX 处上形成的、呈独立岛状的第一电极 60，与第一电极 60 相对配置的、共同形成在全部象素 PX 处的第二电极 66，以及保 15 持在第一电极 60 与第二电极 66 之间的有机活性层 64。

阵列基板 100 具有沿着象素 PX 的行方向（即图 1 中的 Y 方向）配置的若干条扫描线 Ym (m=1、2、……)，沿着与扫描线 Ym 实质上正交方向（即图 1 中的 X 方向）配置的若干条信号线 Xn (n=1、2、……)，以及向有机 EL 元件 40 的第一电极 60 侧实施电源供给用的电源供给线 P。

20 电源供给线 P 与配置在显示区域 102 周围位置的、图中未示出的第一电极电源线相连接。有机 EL 元件 40 的第二电极 66 侧，与配置在显示区域 102 周围位置的、供给共同电位（在这儿为接地电位）用的、图中未示出的第二电极电源线相连接。

25 阵列基板 100 在沿着显示区域 102 的外侧周部的周边区域 104 处，形成有向扫描线 Ym 分别供给扫描信号用的扫描线驱动回路 107 的至少一部分，以及向信号线 Xn 分别供给图像信号用的信号线驱动回路 108 的至少一部分。所有扫描线 Ym 与扫描线驱动回路 107 相连接。所有信号线 Xn 与信号线驱动回路 108 相连接。

30 在这儿的象素开关 10，配置在扫描线 Ym 与信号线 Xn 的交叉部附近的位置。象素开关 10 的栅极电极与扫描线 Ym 相连接，源极电极与信号线 Xn 相连

接，漏极电极与构成储存容量元件 30 的一侧电极和驱动型晶体管 20 的栅极电极相连接。驱动型晶体管 20 的源极电极与构成储存容量元件 30 的另一侧电极和电源供给线 P 相连接，漏极电极与有机 EL 元件 40 上的第一电极 60 相连接。

正如图 2 所示，阵列基板 100 具有配置在布线基板 120 上的、作为显示元件的有机 EL 元件 40。布线基板 120 可以按照在诸如玻璃基板和塑料薄板等等的绝缘性支撑基板上，配置有象素开关 10、驱动型晶体管 20、储存容量元件 30、扫描线驱动回路 107、信号线驱动回路 108、各种布线（扫描线、信号线、电源供给线等等）的方式构成。

构成有机 EL 元件 40 用的第一电极 60，配置在布线基板 120 的表面绝缘膜上。这种第一电极 60 可以由诸如 ITO (Indium Tin Oxide: 钽・锡・氧化物) 和 IZO (Indium Zinc Oxide: 钽・锌・氧化物) 等等的、具有光透射性的导电材料形成，并且具有作为阳极使用的功能。

有机活性层 64 可以由至少包含具有发光功能的有机化合物的材料构成。这种有机活性层 64 可以呈由形成为各种颜色通用的空穴缓冲层、电子缓冲层以及相对各种颜色形成的有机发光层等等形成的叠层设置形式，也可以呈功能复合型的两层或单层形式。如果举例来说，空穴缓冲层可以配置在阳极与有机发光层之间，并且可以由诸如芳香族氨类电介质、聚噻吩类电介质、聚苯胺类电介质等等的薄膜材料形成。有机发光层可以由具有能够发射出红色、绿色或兰色光束的发光功能的有机化合物形成。对于这些有机发光层采用诸如高分子类发光材料的场合，可以采用诸如 PPV (聚苯乙炔) 和聚二苯并茂类电介质或者它的前驱体等等的薄膜材料形成。

第二电极 66 与有机 EL 元件 40 共同配置在有机活性层 64 上。这种第二电极 66 可以由诸如 Ca (钙)、Al (铝)、Ba (钡)、Ag (银)、Yb (镱) 等等的、具有电子注入功能的金属膜形成，并且具有作为阴极使用的功能。第二电极 66 可以呈、将作为阴极使用功能的金属膜表面用盖覆型金属覆盖的双层构成形式。盖覆型金属可以由诸如铝等等形成。

在该第二电极 66 的表面处，还可以覆盖有作为干燥剂的、具有吸湿性的材料。换句话说就是，有机 EL 元件 40 在与水分接触时，其发光性能将急剧恶化。因此，为了能够保护有机 EL 元件 40 不受到水分影响，在其表面相当的第二电极 66 处还配置有干燥剂 68。这种干燥剂 68 可以为具有吸湿性的材料，比如说

可以由诸如锂 (Li)、钠 (Na)、钾 (K) 等等的碱金属或其其氧化物形成，也可以由诸如锰 (Mg)、钙 (Ca)、钡 (Ba) 等等的碱土金属或其氧化物形成。

阵列基板 100 在显示区域 102 处，还具有至少按照对每个相邻接颜色在象素 PX (R、G、B) 间实施分离的方式设置着的分割壁 70。分割壁 70 可以按照 5 对各象素实施分离的方式设置，在这儿的分割壁 70 是沿着各第一电极 60 的周部边缘呈格子状配置，并且按照使第一电极 60 露出的使得分割壁 70 的开口形状呈圆形或多边形的方式形成的。这种分割壁 70 可以由树脂材料形成，如果举例来说，可以呈由具有亲液性的有机材料形成的第一绝缘层，以及配置在第一绝缘层上的、由具有疏液性的有机材料形成的第二绝缘层形成的叠层结构。

10 具有这种构成形式的有机 EL 元件 40，可以向夹持在第一电极 60 与第二电极 66 之间的有机活性层 64 处注入空穴和电子，通过使它们再次结合的方式形成受激子，从而可以当这些受激子失活时发射出具有预定波长的光。在这儿的 EL 发光，是由阵列基板 100 的下面侧、即第一电极 60 侧发射出的。

15 阵列基板 100 还具有形成在布线基板 120 的主面的有效部 106。这种有效部 106 可以至少包含着对图象实施显示用的显示区域 102，也可以还进一步包含着具备扫描线驱动回路 107 和信号线驱动回路 108 等的周边区域 104。

封装组件 300 如图 2 和图 3 所示，按照至少覆盖有效部 106 的方式，配置在阵列型基板 100 的主面、即形成有机 EL 元件 40 的表面处。这种封装组件 300 的表面呈实质上平坦的构成形式。

20 封装部件 200 如图 2 所示，通过涂覆在封装组件 300 的整个表面处的粘接剂，与封装组件 300 相接。这种封装部件 200 可以由诸如塑料薄板等等的、具有光透射性的绝缘薄膜，以及诸如金刚石类石墨等等形成。

25 封装组件 300 可以由至少两层的缓冲层 311、312、……，以及具有其形成面积比这些缓冲层大的图案并按照将缓冲层与外部空气隔断的方式覆盖各缓冲层的壁垒层 321、322、……叠层构成。位于封装组件 300 中最内侧的层（即最靠近阵列基板 100 的层）最好为壁垒层，所以在这儿的最内层配置的是壁垒层 320。在如图 2 所示的实例中，封装组件 300 不仅具有作为最内层的壁垒层 320，而且还具有作为最外层的壁垒层 322。各个壁垒层最好能够通过其周围部分，按照包含下层缓冲层侧面的方式对其实施整体覆盖。从壁垒层彼此间的密接性能和封装组件的封装性能考虑，最好能够在其周边部也对壁垒层实施叠层设置。

各个缓冲层 311、312、……可以由诸如丙稀类树脂等等的有机材料（树脂材料），形成厚度诸如为 0.1~5 微米（ $\mu\text{m}$ ）左右的薄膜。各个缓冲层 311、312、……至少具有与有效部 106 相等尺寸的，而且最好具有比其更大尺寸的图案。在这儿，形成这些缓冲层 311、312、……的材料可以是能够在粘度比较低的液体状态下实施涂覆，并且能够在对下层凸凹实施吸收的状态下实施硬化的材料。采用这种材料形成的缓冲层 311、312、……，其表面呈平坦化，从而还具有作为平坦化层使用的功能。

如果举例来说，各个壁垒层 320、321、322、……可以由诸如铝和钛等等的金属材料、诸如 ITO 和 IZO 等等的金属氧化物材料或是诸如氧化铝等等陶瓷类材料的无机材料构成，形成厚度为 500 埃~3 微米（ $\mu\text{m}$ ）左右、最好为 200 埃左右的薄膜。对于 EL 发光为由第一电极 60 侧导出的下面发光方式的场合，制作壁垒层 320、321、322、……中至少一层的材料最好具有遮光性和光反射性。对于 EL 发光为由第二电极 66 侧导出的上面发光方式的场合，制作壁垒层 320、321、322、……的材料最好具有光透射性。对于为上面发光方式的场合，制作缓冲层 311、312、……的材料最好也具有光透射性。

下面通过实施例，对这种封装组件 300 的详细构成形式进行说明。

#### （第一实施例）

第一实施例是以能够由一片母模基板切割出与多个显示装置相对应的阵列基板的制造方法为例进行说明的。母模基板具有可以作为阵列基板实施切割制作的多个（比如说为四个）阵列部。

首先如图 4A 所示，在母模基板 500 的正面形成有效部 106。在该第一实施例中，形成有与四个阵列部 AR 相对应的四个实质上呈矩形的有效部 106。换句话说就是，各个有效部 106 是在母模基板 500 上的各阵列部 AR 处，通过诸如重复实施对金属膜和绝缘膜的成膜处理和图案处理等等处理作业的方式形成的，并且具有象素开关 10、驱动型晶体管 20、储存容量元件 30、扫描线驱动回路 107、信号线驱动回路 108，以及诸如信号线 Xn、扫描线 Ym、电源供给线 P 等等各种布线，和分别配置有有机 EL 元件 40 的多个象素 PX。

可以通过形成该有效部 106 的工序，同时形成在随后形成缓冲层时使用的多个基准标志 AM。在该第一实施例中，为了能够叠层形成为三层的缓冲层，形成有在形成各个缓冲层时需要的一个（总共为三个）基准标志 AM。在下面

说明的第一实施例至第三实施例中，为了说明简单，仅仅在图中示出了形成一层缓冲层用的一个基准标志，然而不言而明，也可以配置有形成一层缓冲层用的多个基准标志。换句话说就是，可以配置有形成一层缓冲层用的至少两个基准标志，也可以配置有形成一层缓冲层用的更多个基准标志（比如说配置在母模基板的四个角部附近的位置的基准标志）。通过依据这些个基准标志实施位置吻合的方式，可以提高掩膜与母模基板间的相对位置吻合精度。

这些基准标志 AM 可以在对形成有效部 106 用的金属膜或绝缘膜进行图案处理的时候同时进行。如果举例来说，基准标志 AM 可以在形成扫描线 Ym 时同时实施图案处理，并通过与扫描线 Ym 相同的材料实施形成。而且，这些基准标志 AM 可以形成在诸如位于阵列部 AR 之外的母模基板 500 上，也可以形成在有效部 106 之内。

随后，通过至少对母模基板 500 主面上的有效部 106 进行覆盖的方式，对封装组件 300 实施配置。换句话说就是，可以按照如图 5A 所示的方式，形成使有效部 106 与外部空气隔断的第一壁垒层 320。该第一壁垒层 320 可以通过 15 对金属材料实施蒸镀的方式形成。

如果更具体的讲就是，可以按照如图 10 所示的方式，使形成有效部 106 的母模基板 500，通过图中未示出的保持部件与形成壁垒层用的第一掩膜 M1 形成为一体。该第一掩膜 M1 可以在形成包含着第一壁垒层在内的全部壁垒层时共同的使用，并且可以具有其形状与这些壁垒层的形成区域相对应的开口部。20 这种开口部具有至少比有效部 106 更大的图案，可以呈与诸如阵列部 AR 实质上相等（或略小）的矩形形状。采用这种方式，可以按照实质上相同的同一图案，形成所有壁垒层。

将按照这种方式与第一掩膜 M1 形成为一体的母模基板 500，引导至形成壁垒层用的第一腔室 601 处。在形成母模基板 500 上的有效部 106 的主面，利用第一掩膜 M1 实施金属材料的蒸镀。采用这种方式，可以按照实质上覆盖住整个阵列部 AR 的方式进行配置的方式，形成实质上呈矩形形状的第一壁垒层 320。

随后如图 4B 所示，在第一壁垒层 320 上形成具有至少比有效部 106 更大的图案的第一缓冲层 311。这种第一缓冲层 311 可以采用树脂材料，通过下述工序实施形成。

30 首先如图 10 所示，将与第一掩膜 M1 形成为一体的母模基板 500，引导至

形成缓冲层用的第二腔室 602 处。该第二腔室 602 具有形成缓冲层用的第二掩膜 M2。这种第二掩膜 M2 可以在形成全部缓冲层时共同的使用，并且具有其形状与这些缓冲层的形成区域相对应的开口部。这种开口部具有至少比有效部 106 更大的图案，呈比诸如第一掩膜 M1 的开口部小的矩形形状。采用这种方式，

5 可以按照实质上相同的一同一图案，形成各个缓冲层。

引导至第二腔室 602 处的母模基板 500，可以如图 4B 所示，以与第二掩膜 M2 相对应的第一基准标志 AM1 为基准实施位置吻合作业。随后如图 5B 所示，在第二腔室 602 中，在母模基板 500 上形成有效部 106 的主面，通过第二掩膜 M2 实施树脂材料 311' 的蒸镀。采用这种方式，可以按照实质上覆盖住整个阵

10 列部 AR 上有效部 106 的方式，形成实质上呈矩形形状的第一缓冲层 311。

对于树脂材料 311' 采用的是诸如紫外线硬化型树脂材料等等的感光性树脂材料的场合，可以将实施树脂材料 311' 成膜后的母模基板 500，引导至实施硬化处理用的第三腔室 603 处，使用具有紫外线波长的光源，在预定曝光量下对感光性树脂材料 311' 实施曝光。采用这种方式，可以形成经过硬化处理的

15 第一缓冲层 311。

而且，在第三腔室 603 中，还可以通过实施电子束照射的方式对树脂材料 311' 实施硬化处理。而且，还可以在第二腔室 602 中配置具有能够使树脂材料硬化的感光波长的光源和电子束发生源，在第二腔室 602 中同时进行树脂材料的蒸镀作业和硬化处理作业。还可以在第二腔室 602 中，对可通过气相方式实

20 施聚合的树脂材料实施蒸镀作业，并省略掉硬化处理作业。

在这儿，可以取形成呈矩形形状的有效部 106 的端部的一条侧边为基准位置 106R。在这时，可以将由有效部 106 的一条侧边 106R 起至形成第一缓冲层 311 的端部的一条侧边 311X 间的最短距离取为 D1。这种最短距离在如图 4B 等等的平面图中，定义着由主面的法线方向观察基板时的间隔，在下面的说明中

25 也具有类似含义。

随后如图 5C 所示，按照具有比第一缓冲层 311 更大的图案且使第一缓冲层 311 与外部空气隔断的方式，形成第二壁垒层 321。该第二壁垒层 321 与上述的第一壁垒层 320 实质上相同，并且是在第一腔室 601 中按照与第一壁垒层 320 相同的条件形成的。对于下面说明的第三壁垒层 322 和第四壁垒层 323，也

30 与上述的第一壁垒层 320 实质上相同，按照与第一壁垒层 320 相同的条件形成

的。

随后如图 4C 所示，在第二壁垒层 321 上，形成与第一缓冲层 311 具有实质上相同的图案的第二缓冲层 312。如果举例来说，该第二缓冲层 312 可以采用与第一缓冲层 311 相同的树脂材料实施形成。对这种第二缓冲层 312 实施形成的工序，可以参考上面通过图 10 和图 5B 描述的方式，在第二腔室 602 中进行。

5

在这时，对形成第二缓冲层 312 用的树脂材料进行的蒸镀工序，可以在与形成第一缓冲层 311 时相同的条件下进行，而且可以利用形成第一缓冲层 311 时使用的同一第二掩膜 M2 实施形成。在这一蒸镀工序中，第二掩膜 M2 可以在与形成第一缓冲层 311 时的蒸镀工序中不同的位置实施位置吻合作业。换句话说就是，母模基板 500 以相对第二掩膜 M2 为与第一基准标志 AM1 不同位置的第二基准标志 AM2 为基准实施位置吻合作业，在包含着整个有效部 106 的矩形形状的区域中实施树脂材料的蒸镀作业。

10

15

通过对所蒸镀的树脂材料实施硬化处理的方式，形成按照覆盖整个有效部 106 的方式配置的、实质上呈矩形形状的第二缓冲层 312。在这时，如果由有效部 106 的一条侧边 106R 起至形成第二缓冲层 312 的端部的一条侧边 312X（即与有效部 106 上的一条侧边 106R 最接近的一条侧边）间的最短距离取为 D2 时，该距离 D2 与距离 D1 不同，在本实施形式中的距离 D2 比距离 D1 短。

20

而且，该第二缓冲层 312 也可以按照不使用形成第一缓冲层 311 时的同一第二掩膜 M2 实施形成，可以形成在不与第一缓冲层 311 完全相同的位置，并且可以按照相对第一缓冲层 311 沿一个方向 A（比如说沿有效部 106 的对角方向）偏置的方式实施重叠设置。

25

因此，第二缓冲层 312 当重叠在第一缓冲层 311 上的第一角部 311A 处时（即第二缓冲层 312 按照覆盖第一缓冲层 311 上的第一角部 311A 的方式配置时），将不会重叠在第一缓冲层 311 上的第二角部 311B、第三角部 311C 和第四角部 311D 处（即第二缓冲层 312 按照使第一缓冲层 311 上的其它角部露出的方式配置）。而且，第二缓冲层 312 上的一条侧边 312X 与第一缓冲层 311 上的一条侧边 311X 不相重叠（当然，第二缓冲层 312 上的其它三条侧边也不与第一缓冲层 311 上的其它三条侧边重叠）。

30

随后，按照与参考图 5C 说明过的方式类似的方式，按照具有比第二缓冲

层 312 更大的图案且使第二缓冲层 312 与外部空气隔断的方式，形成第三壁垒层 322。采用这种方式，可以按照覆盖比形成第二缓冲层 312 的区域更大的区域，比如说实质上覆盖整个阵列部 AR 的方式，配置形成实质上呈矩形形状的第三壁垒层 322。

5 随后如图 4D 所示，在第三壁垒层 322 上形成其图案实质上与第一缓冲层 311 相同的第三缓冲层 313。这种第三缓冲层 313 可以采用与第一缓冲层 311 相同的树脂材料形成。对这种第三缓冲层 313 实施形成的工序，可以参考上面通过图 10 和图 5B 描述的方式，在第二腔室 602 中进行。

10 在这时，对形成第三缓冲层 313 用的树脂材料进行的蒸镀工序，可以在与形成第一缓冲层 311 时相同的条件下进行，而且可以利用形成第一缓冲层 311 时使用的同一第二掩膜 M2 实施形成。在这一蒸镀工序中，第二掩膜 M2 可以在与形成第一缓冲层 311 和第二缓冲层 312 时的蒸镀工序中不同的位置实施位置吻合作业。换句话说就是，母模基板 500 以相对第二掩膜 M2 为与第一基准标志 AM1 和第二基准标志 AM2 不同位置的第三基准标志 AM3 为基准实施位置吻合作业，

15 在包含着整个有效部 106 的矩形形状的区域中实施树脂材料的蒸镀作业。

通过对所蒸镀的树脂材料实施硬化处理的方式，形成按照覆盖整个有效部 106 的方式配置的、实质上呈矩形形状的第三缓冲层 313。在这时，如果由有效部 106 的一条侧边 106R 起至形成在第三缓冲层 313 的端部处的一条侧边 313X

20 （即与有效部 106 上的一条侧边 106X 最接近的一条侧边）间的最短距离取为 D3 时，该距离 D3 与距离 D1 和距离 D2 不同，在本实施形式中的距离 D3 比距离 D2 短。

而且，该第三缓冲层 313 也可以按照不使用形成第一缓冲层 311 和第二缓冲层 312 时的同一第二掩膜 M2 实施形成，可以形成在不与第一缓冲层 311 和第二缓冲层 312 完全相同的位置，并且可以按照相对第二缓冲层 312 沿一个方向 A 偏置的方式实施重叠设置。

25

换句话说就是，第一缓冲层 311、第二缓冲层 312 和第三缓冲层 313 按照沿同一个方向 A 偏置的方式实施着叠层设置。因此，第三缓冲层 313 如果重叠在第二缓冲层 312 上的第一角部 312A 处时，将不会重叠在第二缓冲层 312 上的第二角部 312B、第三角部 312C 和第四角部 312D 处（当然，第三缓冲层 313

30

如果重叠在第一缓冲层 311 上的第一角部 311A 处时，将不会重叠在第一缓冲层 311 上的第二角部 311B、第三角部 311C 和第四角部 311D 处）。而且，

5 第三缓冲层 313 上的一条侧边 313X 与第一缓冲层 311 上的一条侧边 311X 和第二缓冲层 312 上的一条侧边 312X 不相重叠（当然，第三缓冲层 313 上的其它三条侧边也不与第一缓冲层 311 上的其它三条侧边和第二缓冲层 312 上的其它三条侧边重叠）。

随后，按照与参考图 5C 说明过的方式类似的方式，按照具有比第三缓冲层 313 更大的图案且使第三缓冲层 313 与外部空气隔断的方式，形成第四壁垒层 323。采用这种方式，可以按照覆盖比形成第三缓冲层 313 的区域更大的区域，

10 比如说实质上覆盖整个阵列部 AR 的方式，配置形成实质上呈矩形形状的第四壁垒层 323。

通过上面所述各工序，形成封装组件 300。

随后，在封装组件 300 的表面处，即在第四壁垒层 323 的整个表面处涂覆

15 粘接剂，与封装部件 200 实施粘接。按照每个阵列部 AR 的单个尺寸对母模基板 500 实施切割。在单个尺寸的切割线上，未配置有封装组件，以便使切削作业容易进行。而且，根据需要还可以在获取 EL 发光的侧表面处，贴覆偏振光板。

利用上述制造工序制造出的显示装置 1，如果沿如图 4D 所示的线 VI—VI

实施切断时，将呈如图 6 所示的剖面形状。换句话说就是，至少在阵列基板 100

20 的有效部 106 处，是通过按照第一壁垒层 320、第一缓冲层 311、第二壁垒层 321、第二缓冲层 312、第三壁垒层 322、第三缓冲层 313 和第四壁垒层 323 的顺序，叠层形成的封装组件 300 实施着封装的。

采用这种方式，可以按照不会受到下层影响的方式，对形成在有效部 106

25 处的有机 EL 元件 40 实施可靠地覆盖。而且，即使在这些缓冲层和壁垒层中的某些个形成有微小间隙，通过这种由若干层形成的叠层构造，也可以延长到达有机 EL 元件处的路径，从而可以获得延长使用寿命的良好技术效果。而且，可以使有机 EL 元件 40 与外部空气隔断，在长时间里保持良好的工作性能。在通过粘接剂将封装部件 200 粘接至封装组件 300 上时，或是通过粘接剂将偏振光板粘接至封装部件 200 上时，可以防止包含在粘接剂中的杂质侵入至有机 EL

30 元件 40 内，从而可以防止有机 EL 元件 40 的性能出现恶化。

而且，各个缓冲层可以利用同一掩膜实施形成，所以在蒸镀树脂材料用的腔室内可以仅准备单一的掩膜。因此，在形成缓冲层用的树脂材料蒸镀工序中，不再需要实施掩膜的替换作业，从而可以提高制造效率。而且，由于不再需要准备价格昂贵的若干种掩膜，所以还可以降低制造成本。

5 对叠层形成的三层缓冲层均是通过同一掩膜形成在完全一致的位置的场合，各个缓冲层的周部边缘在实质上相同位置形成重叠，所以封装组件的周部边缘相对阵列基板 100 的主面，形成为与垂直的法线实质上平行的急剧斜面。对于按照这种方式实施制造的场合，覆盖各个缓冲层的壁垒层的膜厚实质上为缓冲层的 1/1~1/10 左右，所以越是覆盖上层缓冲层的壁垒层越难以对缓冲层的 10 周部边缘进行覆盖，从而会产生覆盖区域不良的问题。而且，当采用光蚀刻工序，通过同一光学掩膜形成三层缓冲层时，首先形成的有机 EL 元件会受到不希望有的、比较大的水分的影响，而且对于诸如由于附着在光学掩膜上的污物的影响，而在缓冲层处形成有诸如针孔等等的微小间隙的场合，由于此时三层缓冲层形成在实质上一致的位置，所以在各缓冲层处的针孔会相互贯穿，从而 15 会使密闭性能显著恶化。

针对这种情况，上述的第一实施例，是使构成封装组件的多个缓冲层按照完全相同的膜厚实施形成的，是按照为该膜厚 10 倍左右的量在沿不同方向彼此偏置的状态下实施叠层设置的。如果举例来说就是，对于这些缓冲层按照 1 微米 ( $\mu\text{m}$ ) 量级的膜厚实施形成的场合，第一缓冲层 311 与第二缓冲层 312 在 20 沿预定方向 A 形成有 10 微米 ( $\mu\text{m}$ ) 左右量级的偏置量的状态下实施重叠，类似的，第二缓冲层 312 与第三缓冲层 313 在沿预定方向 B 形成有 10 微米 ( $\mu\text{m}$ ) 左右量级的偏置量的状态下实施重叠。

而且，第一缓冲层 311、第二缓冲层 312 和第三缓冲层 313 是按照分别覆盖有效部 106 的方式实施配置的，并且是按照相对有效部 106 沿一个方向（比如说沿有效部 106 的对角线方向）形成有偏置量的状态下实施重叠的。采用这种方式，可以使各个缓冲层的各个侧边不在实质上相同的位置重叠，从而可以通过缓慢的斜面 300S 形成封装组件 300 的周部边缘。

因此，即使对于形成覆盖上层缓冲层用的壁垒层的场合，也可以有效地对各缓冲层的周部边缘进行覆盖，从而可以防止覆盖区域不良的现象出现。而且， 30 由于三层缓冲层是在彼此偏置的状态下实施重叠的，所以各缓冲层处的针孔不

会相互贯穿，从而可以防止密闭性能出现恶化。

对于这些缓冲层间的偏置量小于 1 微米 ( $\mu\text{m}$ ) 左右量级的场合，偏置量会被各缓冲层形成时的边缘余量吸收，难以获得使若干缓冲层偏置设置所希望获得的技术效果。对于这些缓冲层间的偏置量大于 100 微米 ( $\mu\text{m}$ ) 左右量级 5 的场合，当叠层设置的缓冲层数目比较多时，由有效部 106 的端部至阵列基板 100 的周部边缘间的外框边缘宽度必须足够的大，这不利于实现窄外框边缘宽度化的需求。因此，在这儿最好使各缓冲层间的偏置量位于 10~100 微米 ( $\mu\text{m}$ ) 左右量级的范围内。而且，各缓冲层间的偏置量可以按照各缓冲层的膜厚、叠层设置的缓冲层的层数、可以实现窄外框边缘宽度化的外框边缘宽度等等，10 实施适当地设定。

而且，各壁垒层是按照覆盖下层缓冲层的侧面的方式形成的，所以可以防止水分沿与阵列型基板平行的方向浸入，并且可以通过周边部防止膜枯干的现象出现。

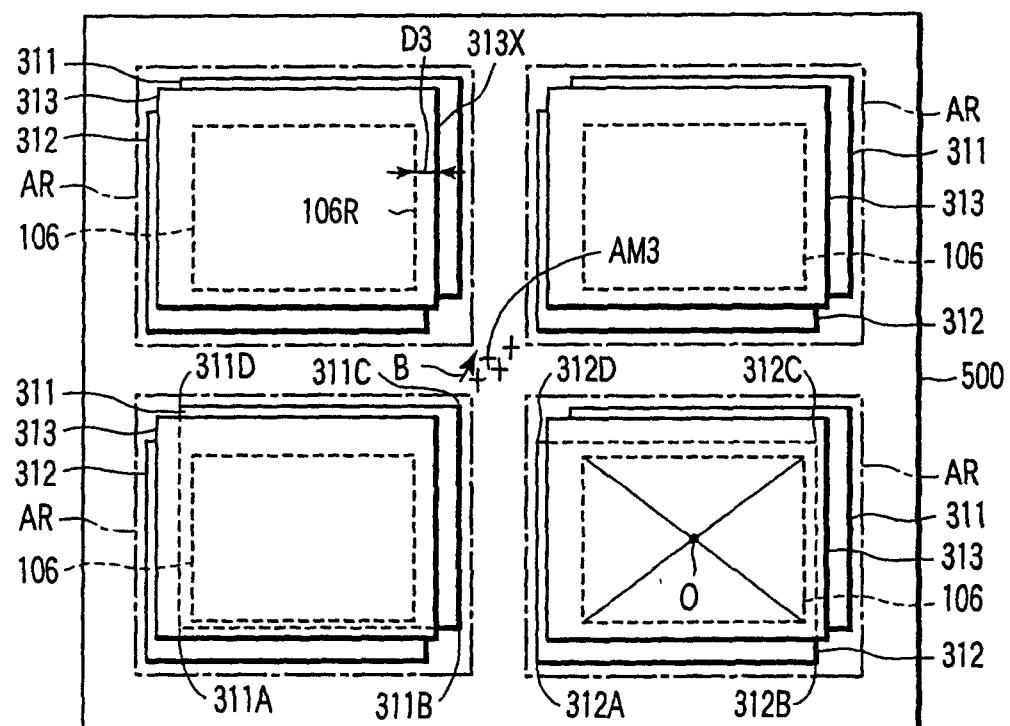

#### (第二实施例)

15 第二实施例是以能够由一片母模基板切割出与多个显示装置相对应的阵列基板的制造方法为例进行说明的。母模基板具有可以作为阵列基板实施切割制作的多个（比如说为四个）阵列部。

首先如图 8A 所示，在母模基板 500 的正面形成有效部 106。该第二实施例与第一实施例相类似，也形成有与四个阵列部 AR 相对应的四个实质上呈矩形的有效部 106。而且，通过形成该有效部 106 的工序，也可以同时形成在随后形成缓冲层时使用的多个基准标志 AM。在该第二实施例中，叠层形成有四层的缓冲层，所以形成有在形成各个缓冲层时所需要四个基准标志 AM。

25 随后，通过至少对母模基板 500 主面上的有效部 106 进行覆盖的方式，对封装组件 300 实施配置。换句话说就是，可以按照第一壁垒层 320、第一缓冲层 311、第二壁垒层 321、第二缓冲层 312、第三壁垒层 322、第三缓冲层 313、第四壁垒层 323、第四缓冲层 314 和第五壁垒层 324 的顺序，叠层形成封装组件 300。

30 第一至第四缓冲层可以按照具有至少比有效部 106 更大的图案的方式实施形成。这些缓冲层与第一实施例中相类似，可以通过诸如树脂材料形成，并且可以通过在第二腔室 602 中进行的树脂材料蒸镀工序，以及根据需要选择的、

在第三腔室 603 中进行的使树脂材料硬化的硬化处理工序实施形成。

第一至第五壁垒层可以按照比各个缓冲层具有更大的图案且使各个缓冲层与外部空气隔断的方式实施形成。这些壁垒层可以在第一腔室 601 中，按照在比形成各缓冲层的区域更大的区域处，即按照具有覆盖实质上整个阵列部 AR 的、实质上呈矩形形状的图案实施形成。

5

在这儿，形成第一缓冲层 311 时的树脂材料蒸镀工序，是在第二腔室 602 中，按照如图 8B 所示的方式，使母模基板 500 相对预定图案的第二掩膜 M2，以第一基准标志 AM1 为基准实施位置吻合作业，在包含整个有效部 106 的矩形区域处实施树脂材料的蒸镀作业。通过这种蒸镀作业，可以按照覆盖住整个有效部 106 的方式，形成实质上呈矩形形状的第一缓冲层 311。在这儿，可以取形成呈矩形形状的有效部 106 的端部的一条侧边为基准位置 106R。在这时，可以将由有效部 106 的一条侧边 106R 起至形成第一缓冲层 311 的端部的一条侧边 311X 间的最短距离取为 D1。

10

15

在形成第二缓冲层 312 时的树脂材料蒸镀工序中，可以利用形成第一缓冲层 311 时的同一第二掩膜 M2，在与形成第一缓冲层 311 时的蒸镀工序中不同的位置实施位置吻合作业。换句话说就是，母模基板 500 可以相对第二掩膜 P2 如图 8C 所示，取与第一基准标志 AM1 不同位置的第二基准标志 AM2 为基准实施位置吻合作业，在包含着整个有效部 106 的矩形形状的区域中实施树脂材料的蒸镀作业。通过这种蒸镀作业，可以按照覆盖住整个有效部 106 的方式，形成实质上呈矩形形状的第二缓冲层 312。

20

在这时，如果由有效部 106 的一条侧边 106R 起至形成第二缓冲层 312 的端部的一条侧边 312X(即与有效部 106 上的一条侧边 106R 最接近的一条侧边)间的最短距离取为 D2 时，该距离 D2 可以与距离 D1 不同，在本实施形式中的距离 D2 比距离 D1 短。

而且，该第二缓冲层 312 也可以按照不使用形成第一缓冲层 311 时的同一第二掩膜 M2 实施形成，可以形成在不与第一缓冲层 311 完全相同的位置，而且可以按照相对第一缓冲层 311 沿一个方向 A(比如说有效部 106 的对角方向)偏置的方式实施重叠设置。

25

因此，第二缓冲层 312 当重叠在第一缓冲层 311 上的第一角部 311A 处时

30 (即第二缓冲层 312 按照覆盖第一缓冲层 311 上的第一角部 311A 的方式配置

时），将不会重叠在第一缓冲层 311 上的第二角部 311B、第三角部 311C 和第四角部 311D 处（即第二缓冲层 312 按照使第一缓冲层 311 上的其它角部露出的方式配置）。而且，第二缓冲层 312 上的一条侧边 312X 与第一缓冲层 311 上的一条侧边 311X 不相重叠（当然，第二缓冲层 312 上的其它三条侧边也不与第一缓冲层 311 上的其它三条侧边重叠）。

在形成第三缓冲层 313 时的树脂材料蒸镀工序中，可以利用形成第一缓冲层 311 时的同一第二掩膜 M2，在与形成第一缓冲层 311 和第二缓冲层 312 时的蒸镀工序中不同的位置实施位置吻合作业。换句话说就是，母模基板 500 可以相对第二掩膜 M2 如图 8D 所示，取与第一基准标志 AM1 和第二基准标志 AM2 不同位置的第三基准标志 AM3 为基准实施位置吻合作业，在包含着整个有效部 106 的矩形形状的区域中实施树脂材料的蒸镀作业。通过这种蒸镀作业，可以按照覆盖住整个有效部 106 的方式，形成实质上呈矩形形状的第三缓冲层 313。

在这时，如果由有效部 106 的一条侧边 106R 起至形成第三缓冲层 313 的端部的一条侧边 313X（即与有效部 106 上的一条侧边 106X 最接近的一条侧边）间的最短距离取为 D3 时，该距离 D3 与距离 D1 和 D2 不同，在本实施形式中的距离 D3 比距离 D1 短且比距离 D2 长。

而且，该第三缓冲层 313 也可以按照不使用形成第一缓冲层 311 和第二缓冲层 312 时的同一第二掩膜 M2 实施形成，可以形成在不与第一缓冲层 311 和第二缓冲层 312 完全相同的位置，而且可以按照相对第二缓冲层 312 沿一个方向 B 偏置的方式实施重叠设置。

因此，第三缓冲层 313 当重叠在第二缓冲层 312 上的第三角部 312C 处时，将不会重叠在第二缓冲层 312 上的第一角部 312A、第二角部 312B 和第四角部 312D 处（在这时，第三缓冲层 313 如果重叠在第一缓冲层 311 上的第一角部 311A 处，将不会重叠在第一缓冲层 311 上的第二角部 311B、第三角部 311C 和第四角部 311D 处）。而且，第三缓冲层 313 上的一条侧边 313X 与第一缓冲层 311 上的一条侧边 311X 和第二缓冲层 312 上的一条侧边 312X 不相重叠（当然，第三缓冲层 313 上的其它三条侧边也不与第一缓冲层 311 上的其它三条侧边和第二缓冲层 312 上的其它三条侧边重叠）。

在形成第四缓冲层 314 时的树脂材料蒸镀工序中，可以利用形成第一缓冲层 311 时的同一第二掩膜 M2，在与形成第一缓冲层 311 第二缓冲层 312 和第三

缓冲层 313 时的蒸镀工序中不同的位置实施位置吻合作业。换句话说就是，母模基板 500 可以相对第二掩膜 M2 如图 8E 所示，取与第一基准标志 AM1、第二基准标志 AM2 和第三基准标志 AM3 不同位置的第四基准标志 AM4 为基准实施位置吻合作业，在包含着整个有效部 106 的矩形形状的区域中实施树脂材料的蒸镀作业。通过这种蒸镀作业，可以按照覆盖住整个有效部 106 的方式，形成实质上呈矩形形状的第四缓冲层 314。

在这时，如果由有效部 106 的一条侧边 106R 起至形成第四缓冲层 314 的端部的一条侧边 314X(即与有效部 106 上的一条侧边 106X 最接近的一条侧边)间的最短距离取为 D4 时，该距离 D4 与距离 D1、D2 和 D3 不同，在本实施形式中的距离 D4 比距离 D1 短且比距离 D3 长。

而且，该第四缓冲层 314 也可以按照不使用形成第一缓冲层 311、第二缓冲层 312 和第三缓冲层 313 时的同一第二掩膜 M2 实施形成，可以形成在不与第一缓冲层 311、第二缓冲层 312 和第三缓冲层 313 完全相同的位置，并且可以按照相对第三缓冲层 313 沿一个方向 C 偏置的方式实施重叠设置。

因此，第四缓冲层 314 当重叠在第三缓冲层 313 上的第二角部 313B 处时，将不会重叠在第一角部 313A、第三角部 313C 和第四角部 313D 处（在这时，第四缓冲层 314 如果重叠在第二缓冲层 312 上的第三角部 312C 处，将不会重叠在第二缓冲层 312 上的第一角部 312A、第二角部 312B 和第四角部 312D。第四缓冲层 314 如果重叠在第一缓冲层 311 上的第一角部 311A 处时，将不会重叠在第一缓冲层 311 上的第二角部 311B、第三角部 311C 和第四角部 311D 处）。而且，第三缓冲层 313 上的一条侧边 313X 与第一缓冲层 311 上的一条侧边 311X 和第二缓冲层 312 上的一条侧边 312X 不相重叠（当然，第三缓冲层 313 上的其它三条侧边也不与第一缓冲层 311 上的其它三条侧边和第二缓冲层 312 上的其它三条侧边重叠）。

通过上面所述各工序，形成封装组件 300。

随后，在封装组件 300 的表面处，即在第五壁垒层 324 的整个表面处涂覆粘接剂，与封装部件 200 实施粘接。按照每个阵列部 AR 的单个尺寸对母模基板 500 实施切割。而且，根据需要还可以在获取 EL 发光的侧表面处，贴覆偏振光板。

利用上述制造工序制造出的显示装置 1，如果沿如图 8E 所示的线 VII—VII

实施切断时，将呈如图 7 所示的剖面形状。换句话说就是，至少在阵列基板 100 的有效部 106 处，是通过按照第一壁垒层 320、第一缓冲层 311、第二壁垒层 321、第二缓冲层 312、第三壁垒层 322、第三缓冲层 313、第四壁垒层 323、第四缓冲层 314 和第五壁垒层 324 的顺序，叠层形成的封装组件 300 实施着封装的。

5

因此，可以获得与第一实施例相同的技术效果。而且在上述第二实施例中，第一缓冲层 311、第二缓冲层 312、第三缓冲层 313 和第四缓冲层 314 是按照分别覆盖有效部 106 的方式实施配置的，并且是按照相对有效部 106 沿四个方向形成有偏置量的状态下实施叠层设置的。采用这种方式，可以使各个缓冲层的

10 各个侧边不在实质上相同的位置实施重叠，从而可以通过缓慢的斜面 300S 形成封装组件 300 的周部边缘。因此，即使叠层设置着的缓冲层的层数增加，也可以在形成覆盖上层缓冲层用的壁垒层时，有效地对各缓冲层的周部边缘进行覆盖，从而可以防止覆盖区域不良的现象出现。

而且，与采用如第一实施例所述的，使若干缓冲层沿同一方向偏置的方式

15 形成叠层构造的场合相比，该第二实施例是沿四个方向分别使缓冲层在彼此偏置的状态下实施叠层设置的，所以可以减小有效部周部边缘的外框边缘宽度，提供出一种更有利于实现窄外框边缘宽度化的构成形式。

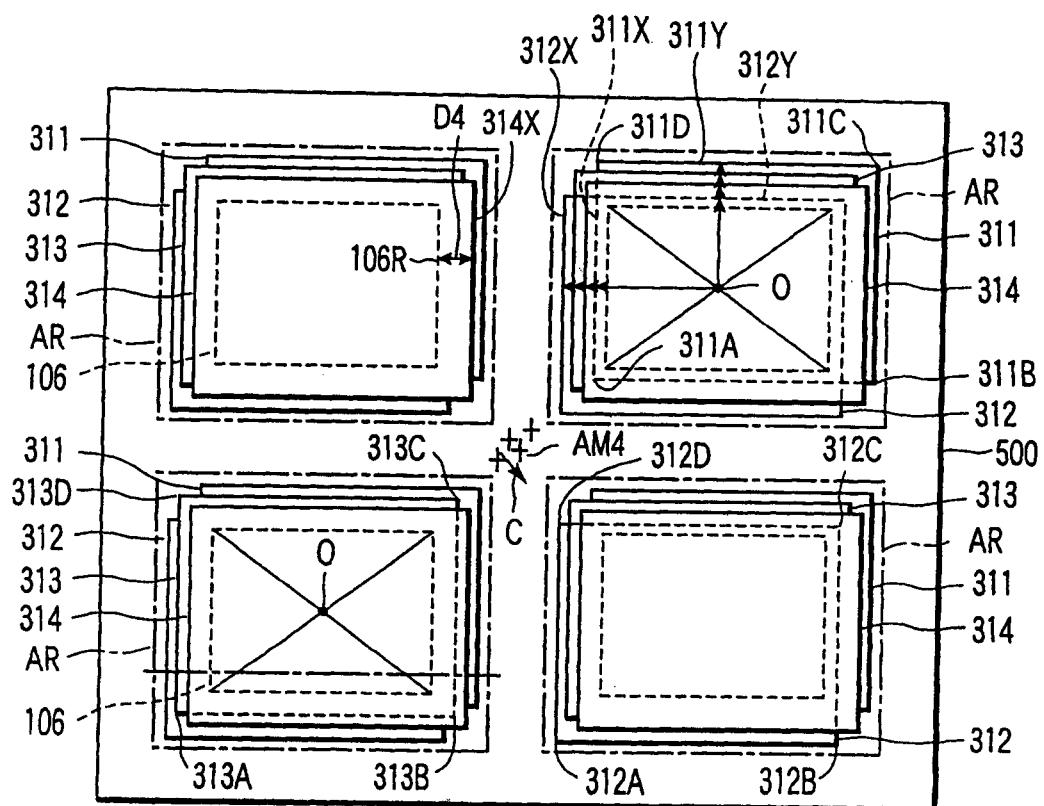

### （第三实施例）

第三实施例是以能够由一片母模基板切割出与 1 个显示装置相对应的阵列

20 基板的制造方法的场合为例进行说明的。而且，不言而明、对于如该第三实施例所述的，由一片基板制造一个阵列基板的场合，可以采用如上述第一实施例所述的、沿一个方向使缓冲层偏置叠层的制造方法，也可以采用如上述第二实施例所述的、沿四个方向使缓冲层偏置叠层的制造方法。

可以首先如图 9A 所示，从基板主面上备有有效部 106 的阵列基板 100。通过形成该有效部 106 的工序，也可以同时形成在随后形成缓冲层时使用的多个基准标志 AM。在该第三实施例中，叠层形成有三层的缓冲层，所以形成有在

25 形成各个缓冲层时所需要三个基准标志 AM。

随后，通过至少对阵列基板 100 主面上的有效部 106 进行覆盖的方式，对

30 封装组件 300 实施配置。换句话说就是，可以按照第一壁垒层 320、第一缓冲层 311、第二壁垒层 321、第二缓冲层 312、第三壁垒层 322、第三缓冲层 313

和第四壁垒层 323 的顺序，叠层形成封装组件 300。

第一至第三缓冲层可以按照具有至少比有效部 106 更大的图案的方式实施形成。这些缓冲层与第一实施例中相类似，可以通过诸如树脂材料形成，并且可以通过在第二腔室 602 中进行的树脂材料蒸镀工序，以及根据需要选择的、

5 在第三腔室 603 中进行的使树脂材料硬化的硬化处理工序实施形成。

第一至第四壁垒层可以按照比各个缓冲层具有更大的图案且使各个缓冲层与外部空气隔断的方式实施形成。这些壁垒层可以在第一腔室 601 中，按照在比形成各缓冲层的区域更大的区域处，即按照具有覆盖实质上整个阵列基板 100 的方式、实质上呈矩形形状的图案实施形成。

10 在这儿，形成第一缓冲层 311 时的树脂材料蒸镀工序，是在第二腔室 602 中，按照如图 9B 所示的方式，使母模基板 500 相对预定图案的第二掩膜 M2，以第一基准标志 AM1 为基准实施位置吻合作业，在包含整个有效部 106 的矩形区域处实施树脂材料的蒸镀作业的。通过这种蒸镀作业，可以按照覆盖住整个有效部 106 的方式，形成实质上呈矩形形状的第一缓冲层 311。在这儿，可以取形成呈矩形形状的有效部 106 的端部的一条侧边为基准位置 106R（在这儿为有效部 106 的一个角部）。在这时，可以将由有效部 106 的一条侧边 106R 起至形成第一缓冲层 311 的端部的一条侧边 311X 间的最短距离取为 D1。

20 在形成第二缓冲层 312 时的树脂材料蒸镀工序中，可以利用形成第一缓冲层 311 时的同一第二掩膜 M2，在与形成第一缓冲层 311 时的蒸镀工序中不同的位置实施位置吻合作业。换句话说就是，母模基板 500 可以相对第二掩膜 M2 如图 9C 所示，取与第一基准标志 AM1 不同位置的第二基准标志 AM2 为基准实施位置吻合作业，在包含着整个有效部 106 的矩形形状的区域中实施树脂材料的蒸镀作业。通过这种蒸镀作业，可以按照覆盖住整个有效部 106 的方式，形成实质上呈矩形形状的第二缓冲层 312。

25 在这时，如果由有效部 106 的一条侧边 106R 起至形成第二缓冲层 312 的端部的一条侧边 312X（即与有效部 106 上的基准位置 106X 最接近的一条侧边）间的最短距离取为 D2 时，该距离 D2 与距离 D1 不同，在本实施形式中的距离 D2 比距离 D1 短。

而且，该第二缓冲层 312 也可以按照不使用形成第一缓冲层 311 时的同一

30 第二掩膜 M2 实施形成，可以形成在不与第一缓冲层 311 完全相同的位置，而

且可以在相对第一缓冲层 311 沿转动方向  $\theta$  偏置的状态下实施重叠。在这儿，第二缓冲层 312 是在相对第一缓冲层 311 沿转动方向  $\theta$  以 5 度偏置的状态下实施重叠的。

因此，第二缓冲层 312 是在使第一缓冲层 311 的四个角部均曝露出来的状态 5 下实施重叠设置的。换句话说就是，第二缓冲层 312 是在与第一缓冲层 311 上的第一角部 311A、第二角部 311B、第三角部 311C 和第四角部 311D 的任何一个都不重合的状态下实施重叠的（第二缓冲层 312 没有覆盖第一缓冲层 311 上的任何一个角部）。而且，第二缓冲层 312 上的一条侧边 312X 与第一缓冲层 311 上的一条侧边 311X 不相重叠（当然，第二缓冲层 312 上的其它三条侧边 10 也不与第一缓冲层 311 上的其它三条侧边重叠）。

在形成第三缓冲层 313 时的树脂材料蒸镀工序中，可以利用形成第一缓冲层 311 时的同一第二掩膜 M2，在与形成第一缓冲层 311 和第二缓冲层 312 时的蒸镀工序中不同的位置实施位置吻合作业。换句话说就是，母模基板 500 可以 15 相对第二掩膜 M2 如图 9D 所示，取与第一基准标志 AM1 和第二基准标志 AM2 不同位置的第三基准标志 AM3 为基准实施位置吻合作业，在包含着整个有效部 106 的矩形形状的区域中实施树脂材料的蒸镀作业。通过这种蒸镀作业，可以按照覆盖住整个有效部 106 的方式，形成实质上呈矩形形状的第三缓冲层 313。

在这时，如果由有效部 106 的一条侧边 106R 起至形成第三缓冲层 313 的端部的一条侧边 313X（即与有效部 106 上的一条侧边 106X 最接近的一条侧边） 20 间的最短距离取为 D3 时，该距离 D2 与距离 D1 和 D2 不同，在本实施形式中的距离 D3 比距离 D1 和距离 D2 短。

而且，该第三缓冲层 313 也可以按照不使用形成第一缓冲层 311 和第二缓冲层 312 时的同一第二掩膜 M2 实施形成，可以形成在不与第一缓冲层 311 和第二缓冲层 312 完全相同的位置，并且可以在相对第二缓冲层 312 沿转动方向 25  $\theta$  偏置的状态下实施重叠。在这儿，第三缓冲层 313 是在相对第二缓冲层 312 沿转动方向  $\theta$  以 5 度偏置的状态下实施重叠的（不言而喻，第三缓冲层 313 是在相对第一缓冲层 311 沿转动方向  $\theta$  以 10 度偏置的状态下实施重叠的）。

因此，第三缓冲层 313 是在使第二缓冲层 312 的四个角部均曝露出来的状态下实施重叠设置的。换句话说就是，第三缓冲层 313 是在与第二缓冲层 312 上的第一角部 312A、第二角部 312B、第三角部 312C 和第四角部 312D 的任何 30

一个都不重合的状态下实施重叠的（在这时，第三缓冲层 313 是在与第一缓冲层 311 上的第一角部 311A、第二角部 311B、第三角部 311C 和第四角部 311D 的任何一个都不重合的状态下实施重叠的）。而且，第三缓冲层 313 上的一条侧边 313X 与第一缓冲层 311 上的一条侧边 311X 和第二缓冲层 312 上的一条侧边 312X 不相重叠（当然，第三缓冲层 313 上的其它三条侧边也不与第一缓冲层 311 上的其它三条侧边和第二缓冲层 312 上的其它三条侧边重叠）。

通过上面所述各工序，形成封装组件 300。

随后，在封装组件 300 的表面处，即在第四壁垒层 323 的整个表面处涂覆粘接剂，与封装部件 200 实施粘接。而且，根据需要还可以在获取 EL 发光的侧表面处，贴覆偏振光板。

利用上述制造工序制造出的显示装置 1，如果沿如图 9D 所示的线 VI—VI 实施切断时，将呈如图 6 所示的剖面形状。换句话说就是，至少在阵列基板 100 的有效部 106 处，是通过按照第一壁垒层 320、第一缓冲层 311、第二壁垒层 321、第二缓冲层 312、第三壁垒层 322、第三缓冲层 313 和第四壁垒层 323 的顺序，叠层形成的封装组件 300 实施着封装的。因此，可以获得与第一实施例相同的技术效果。

正如上面所说明的那样，如果采用第一至第三实施例，将可以提供出一种具有在基板主面形成的、配置有显示图象用的多个象素的、实质上呈矩形形状的有效部，以及按照至少对基板主面上的有效部进行覆盖的方式配置的封装组件的显示装置。这种显示装置的特征在于其封装组件，可以由具有实质上相同的图案的、至少两层的、实质上呈矩形形状的缓冲层，以及具有比各缓冲层更大的图案且按照使各缓冲层与外部空气隔断的方式形成的壁垒层叠层构成，而且由有效部端部的一条侧边起至第一缓冲层端部的一条侧边间的最短距离，与至第二缓冲层端部的一条侧边间的最短距离不同。

如果更严谨地说就是，由有效部 106 的中心（呈矩形形状的有效部的两条对角线间的交叉点）O，至第一缓冲层 311 上彼此正交的两条边 311X 和 311Y 间的最短距离，与至第二缓冲层 312 上彼此正交的两条边 312X 和 312Y 间的最短距离不同（比如说，可以参见图 4C 和图 8E）。

换句话说就是，当在有效部处设计基准位置时，虽然若干缓冲层分别具有相同的图案，然而由基准位置至各缓冲层上的预定一条侧边间的最短距离不同，

所以各缓冲层是按照在基板主面内彼此偏置的位置关系实施叠层设置的。

如果举例来说就是，对于如第一实施例所述的那样，使多个缓冲层在以有效部为基准沿同一方向偏置的状态下实施叠层设置的场合，随后叠层形成的缓冲层，可以重叠在先前形成的缓冲层的一个角部处。如果更严谨地说就是，随

5 后叠层形成的第二缓冲层 312，重叠设置在先前形成的第一缓冲层 311 的一个角部 311A 处，随后叠层形成的第三缓冲层 313，重叠设置在先前形成的第二缓冲层 312 的一个角部 312A 处，由随后叠层形成的缓冲层覆盖的角部 311A 和角部 312A，位于由有效部 106 的中心 O 观察时为相同的对角线方向的位置（比如说，可以参见图 4C 和图 4D）。

10 对于如第二实施例所述的那样，使多个缓冲层在以有效部为基准沿四个方向偏置的状态下实施叠层设置的场合，封装组件至少具有三层缓冲层，在第一缓冲层之后叠层形成的第二缓冲层，重叠设置在先前形成的第一缓冲层的一个角部处，随后叠层形成的第三缓冲层，重叠设置在先前形成的第二缓冲层的一个角部处。如果更严谨地说就是，随后叠层形成的第二缓冲层 312，重叠设置

15 在先前形成的第一缓冲层 311 的一个角部 311A 处，随后叠层形成的第三缓冲层 313，重叠设置在先前形成的第二缓冲层 312 的一个角部 312C 处，随后叠层形成的第四缓冲层 314，重叠设置在先前形成的第三缓冲层 313 的一个角部 313B 处，由随后叠层形成的缓冲层覆盖的角部 311A、角部 312C 和角部 313B，位于由有效部 106 的中心 O 观察时为不同的对角线方向的位置（比如说，可以参见

20 图 8C、图 8D 和图 8E）。

而且对于如第三实施例所述的那样，使多个缓冲层在以有效部为基准沿转动方向偏置的状态下实施叠层设置的场合，随后叠层形成的缓冲层，按照使先前形成的缓冲层的四个角部曝露出来的方式实施重叠设置。如果更严谨地说就是，随后叠层形成的第二缓冲层 312，按照使先前形成的第一缓冲层 311 的四个角部曝露出来的方式实施重叠，随后叠层形成的第三缓冲层 313，按照使先前形成的第二缓冲层 312 的四个角部曝露出来的方式实施重叠（比如说，可以参见图 9B 至图 9D）。

通过采用这种构造方式，可以使各缓冲层的周部边缘不是沿四个方向对齐而叠层设置的，所以可以通过缓慢的斜面形成封装组件的周部边缘，即使对于

30 在上层形成有缓冲层和壁垒层的场合，也可以对这些周部边缘实施可靠地覆盖，

从而可以防止覆盖区域不良的现象出现。而且，由于若干层缓冲层是在彼此偏置的状态下实施重叠的，所以即使对于是通过同一掩膜形成各缓冲层的场合，也可以使各缓冲层处的针孔不相互贯穿，从而可以防止密闭性能出现恶化。因此，可以在长时间里保持稳定且良好的显示性能。

5 而且，形成缓冲层所需要的掩膜，可以按照比缓冲层的层数少的方式准备，所以有利于掩膜的替换作业，从而还可以提高制造效率，降低制造成本。

而且，在上述的第一至第三实施例中，是以构成封装组件的缓冲层为三层的场合和四层的场合为例进行说明的，然而封装组件还可以采用至少两层的缓冲层在彼此偏置的状态下实施叠层的构成形式。对于封装组件由十层以上的缓冲层叠层构成的场合，工序数目比较多，生产性能低下。因此，叠层设置的缓冲层的层数可以在两层以上十层以下，设定为三至五层更好些。

10

而且，在上述的第一至第三实施例中，构成封装组件的全部缓冲层是通过同一图案形成的，然而还可以使若干层中的至少两层缓冲层通过同一图案实施形成。采用这种方式，可以不再需要准备为层数目的掩膜，所以有利于减轻掩

15 膜切换作业的负担，而且通过减少需要准备的掩膜数目，还可以降低制造成本。

而且，在上述的第一至第三实施例中，基础壁垒层和第一至第四壁垒层是按照覆盖整个阵列基板的方式，按实质上相同的图案实施配置的，然而各壁垒层也可以与各缓冲层相类似，在彼此偏置的状态下实施叠层配置。

而且，在上述的第一至第三实施例中，是使掩膜固定设置，通过将阵列基

20 板错开的实施与基准标志相对的掩膜位置吻合作业的，然而还可以使掩膜相对固定设置在阵列型基板侧的基准标志位置实施吻合作业，重要的是要通过基准标志，相对确定掩膜与阵列基板间的位置。

#### (第四实施例)

作为第四实施例的封装组件 300，其中至少一层缓冲层具有与其它缓冲层

25 不同尺寸的图案。因此，至少一层缓冲层的外侧边缘部，是按照在基板主面内位于比其它缓冲层的外侧边缘部更内侧或更外侧的位置叠层设置的。

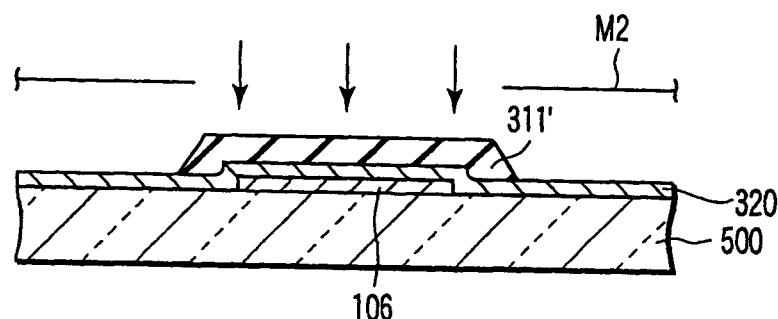

如果举例来说，正如图 11A 和图 11B 所示，封装组件 300 可以具有按照覆盖有效部 106 的方式实施配置的第一壁垒层 320，位于第一壁垒层 320 上的、

30 对应配置在有效部 106 处的第一缓冲层 311，具有比第一缓冲层 311 更大的图案且按照覆盖第一缓冲层 311 的方式实施配置的第二壁垒层 321，位于第二壁

垒层 321 上的、对应配置在有效部 106 处的第二缓冲层 312，以及具有比第二缓冲层 312 更大的图案且按照覆盖第二缓冲层 312 的方式实施配置的第三壁垒层 322。

对于为如图 11A 和图 11B 所示实例の場合，第一缓冲层 311 具有比配置在其上层处的第二缓冲层 312 更大尺寸的图案，且第二缓冲层 312 的外侧边缘部 312A，是按照在基板正面中位于比第一缓冲层 311 的外侧边缘部 311A 更靠近内侧位置的方式实施叠层设置的。

如果更具体的说就是，对配置有封装组件 300 的阵列基板 100 沿其正面的法线方向实施观察时，第二缓冲层 312 的外侧边缘部 312A 位于比第一缓冲层 311 的外侧边缘部 311A 更靠近有效部 106 的端部 106A 的位置。换句话说就是，对于对配置有封装组件 300 的阵列基板 100 从平面上实施观察的場合，由第一缓冲层 311 上的外侧边缘部 311A 至有效部 106 的端部 106A 间的间隔 D1，与由第二缓冲层 312 上的外侧边缘部 312A 至有效部 106 的端部 106A 间的间隔 D2 不同，在本实施形式中的间隔 D1 比间隔 D2 大。

也就是说，第二缓冲层 312 并不是形成在与第一缓冲层 311 完全一致的位置。第二缓冲层 312 上的外侧边缘部 312A 是在相对第一缓冲层 311 上的外侧边缘部 311A 偏置的状态下实施重叠设置的。

对于叠层设置的两层缓冲层形成在完全一致的位置的場合，将如上所述，封装组件 300 的周部边缘相对阵列基板 100 的正面形成为与垂直的法线实质上平行的急剧斜面。对于按照这种方式实施制造的場合，越是覆盖上层缓冲层的壁垒层越难以对缓冲层的周部边缘进行覆盖，从而会产生覆盖区域不良的问题。

因此，构成封装组件的多个缓冲层，是按照完全相同的膜厚实施形成的，并且是在至少缓冲层的膜厚、最好缓冲层膜厚的 10 倍左右的量使外侧边缘部彼此偏置的状态下实施叠层设置的。缓冲层的外侧边缘部的偏置量，可以由诸如 (D1—D2) 限定。

如果举例来说，对于这些缓冲层按照为 10 微米 ( $\mu\text{m}$ ) 左右量级的膜厚实施形成的場合，可以使第一缓冲层 311 上的外侧边缘部 311A 在与第二缓冲层 312 的外侧边缘部 312A 间具有 10 微米 ( $\mu\text{m}$ ) 左右量级的偏置状态下实施重叠设置。各缓冲层间的偏置量与上述的第一至第三实施例相类似，最好为 10~100 微米 ( $\mu\text{m}$ ) 左右量级。

因此，第一缓冲层 311 和第二缓冲层 312 可以分别按照覆盖有效部 106 的方式实施配置，并且在外侧边缘部彼此偏置的状态下实施叠层设置。采用这种方式，可以使各缓冲层上的各个边不在实质上相同的位置实施重叠，从而可以通过缓慢的斜面 300S 形成封装组件 300 的周部边缘。

5 采用这种方式，即使对于形成有覆盖上层缓冲层用的壁垒层的场合，也可以有效地对各缓冲层的外侧边缘部进行覆盖，从而可以防止覆盖区域不良的现象出现。因此，可以防止水分和氧气等等浸入至有机 EL 元件内，从而可以抑制有机 EL 元件的性能恶化，从而可以在长时间里保持稳定且良好的显示性能。

而且，如图 11A 和图 11B 所示的实例，是以封装组件 300 具有两层缓冲层的场合为例进行说明的，对于具有三层以上缓冲层的场合，可以使越上层的缓冲层（越远离阵列型基板 100 的缓冲层）具有越小尺寸的图案。因此，可以使至少一层缓冲层具有与其它缓冲层不同尺寸的图案，并且可以在外侧边缘部彼此偏置的状态下实施叠层设置。采用这种方式，可以通过缓慢的斜面 300S 形成封装组件 300 的周部边缘，从而可以获得与上述相同的技术效果。

15 如图 12A 和图 12B 所示的封装组件 300，可以具有按照覆盖有效部 106 的方式实施配置的第一壁垒层 320，位于第一壁垒层 320 上的、对应配置在有效部 106 处的第一缓冲层 311，具有比第一缓冲层 311 更大的图案且按照覆盖第一缓冲层 311 的方式实施配置的第二壁垒层 321，位于第二壁垒层 321 上的、对应配置在有效部 106 处的第二缓冲层 312，以及具有比第二缓冲层 312 更大的图案且按照覆盖第二缓冲层 312 的方式实施配置的第三壁垒层 322。

对于为如图 12A 和图 12B 所示实例的场合，第一缓冲层 311 具有比配置在其上层处的第二缓冲层 312 更小尺寸的图案，因此第二缓冲层 312 的外侧边缘部 312A，在基板主面内位于比第一缓冲层 311 的外侧边缘部 311A 更靠近外侧的位置实施叠层设置。

25 如果更具体的说就是，对配置有封装组件 300 的阵列基板 100 沿其主面的法线方向实施观察时，第一缓冲层 311 的外侧边缘部 311A 位于比第二缓冲层 312 的外侧边缘部 312A 更靠近有效部 106 的端部 106A 的位置。换句话说就是，对于对配置有封装组件 300 的阵列基板 100 从平面上实施观察的场合，由第一缓冲层 311 上的外侧边缘部 311A 至有效部 106 的端部 106A 间的间隔 D1，与 30 由第二缓冲层 312 上的外侧边缘部 312A 至有效部 106 的端部 106A 间的间隔

D2 不同，在本实施形式中的间隔 D1 比间隔 D2 小。

也就是说，第二缓冲层 312 并不是形成在与第一缓冲层 311 完全一致的位置。第二缓冲层 312 上的外侧边缘部 312A 是在相对第一缓冲层 311 上的外侧边缘部 311A 偏置的状态下实施重叠设置的。与如图 11A 和图 11B 所示的实例 5 相类似，构成封装组件的多个缓冲层是按照完全相同的膜厚实施形成的，并且是按照至少缓冲层的膜厚、最好缓冲层膜厚的 10 倍左右的量使外侧边缘部彼此偏置的状态下实施叠层设置的。缓冲层的外侧边缘部的偏置量，可以由诸如 (D2—D1) 限定。对于需要考虑若干缓冲层偏置叠层设置的技术效果，以及窄 10 外框边缘宽度化的场合，各缓冲层间的偏置量最好位于 10~100 微米 ( $\mu\text{m}$ ) 左右量级的范围内。

采用这种方式，可以使第一缓冲层 311 和第二缓冲层 312 按照分别覆盖有效部 106 的方式实施设置，且在外侧边缘部彼此偏置的状态下实施叠层设置。特别是对于上层缓冲层按照覆盖下层缓冲层的方式实施设置的场合，可以提高 15 封装组件的封装性能。因此，可以防止水分和氧气等等浸入至有机 EL 元件内，从而可以抑制有机 EL 元件的性能恶化，从而可以在长时间里保持稳定且良好的显示性能。

而且，如图 12A 和图 12B 所示的实例，是以封装组件 300 具有两层缓冲层的场合为例进行说明的，对于具有三层以上缓冲层的场合，可以使越上层的缓冲层（越远离阵列型基板 100 的缓冲层）具有越大尺寸的图案。因此，可以使 20 至少一层缓冲层具有与其它缓冲层不同尺寸的图案，在外侧边缘部彼此偏置的状态下实施叠层设置。采用这种方式，可以使上层缓冲层能够可靠地对下层缓冲层进行覆盖，从而可以获得与上述相同的技术效果。

而且，虽然如图 11A 和图 11B、以及图 12A 和图 12B 所示的实例中，所有壁垒层是按照相同尺寸实施形成的，然而本发明并不仅限于这种特定的构成 25 形式，还可以使各层的尺寸不同。

下面，对有机 EL 显示装置的制造方法进行说明。在这儿为了使说明简单，是以具有如图 11A 和图 11B 所示的构成形式的封装组件的有机 EL 显示装置的制造方法为例进行说明的。

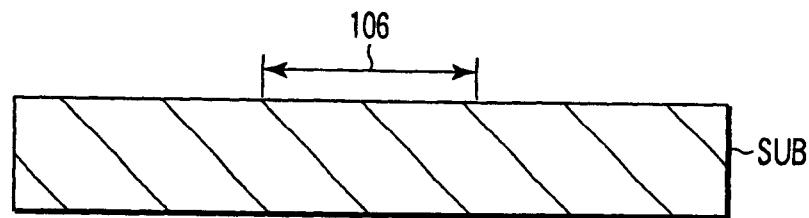

首先如图 13A 所示，制备出在主面上形成有效部 106 的基板 SUB。这种 30 有效部 106 可以通过诸如重复实施对金属膜和绝缘膜的成膜处理和图案处理等

等处理操作的方式形成，具有象素开关 10、驱动型晶体管 20、储存容量元件 30、扫描线驱动回路 107、信号线驱动回路 108，以及诸如信号线 Xn、扫描线 Ym、电源供给线 P 等等的各种布线，和分别具备有机 EL 元件 40 的多个象素 PX。

5 随后，通过至少对位于基板 SUB 的主面上的至少有效部 106 进行覆盖的方式，对封装组件 300 实施配置。

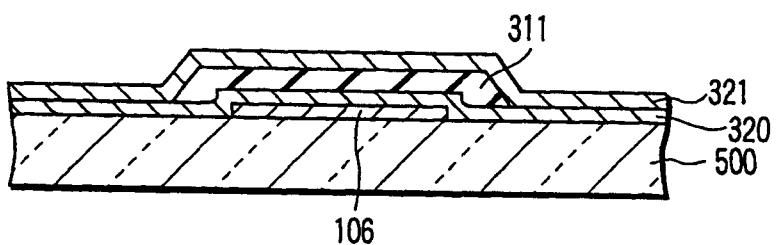

这种封装组件 300 可以通过具有如图 14 所示构成形式的制造装置 600 实施形成。换句话说就是，这种制造装置 600 可以具有对壁垒层实施形成作业用的第一腔室 601，对缓冲层用的树脂材料实施成膜作业用的第二腔室 602，以及对实施成膜后的树脂材料实施硬化作业用的第三腔室 603。

10 利用第一腔室 601，可以通过具有预定形状的开口部的壁垒层用掩膜，对具有作为壁垒层使用功能的金属材料实施蒸镀作业。在这儿使用的壁垒层用掩膜，可以按照相对将有效部 106 朝向蒸镀源侧导入用的基板 SUB 满足预定位置关系实施位置吻合的方式设置在第一腔室 601 内，也可以按照相对形成有效部 106 用的基板 SUB 满足预定位置关系实施位置吻合的方式实施安装。

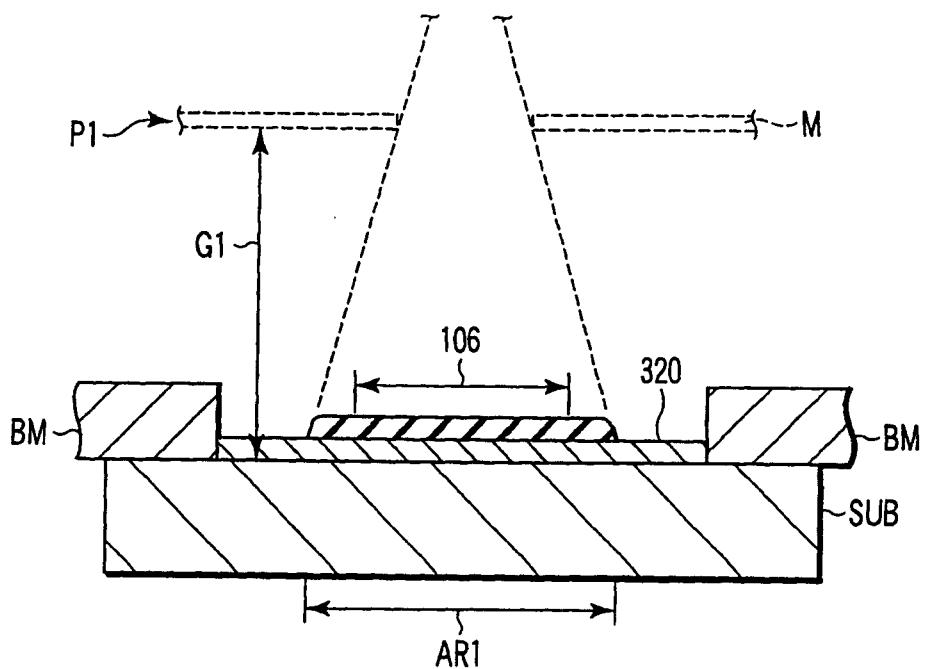

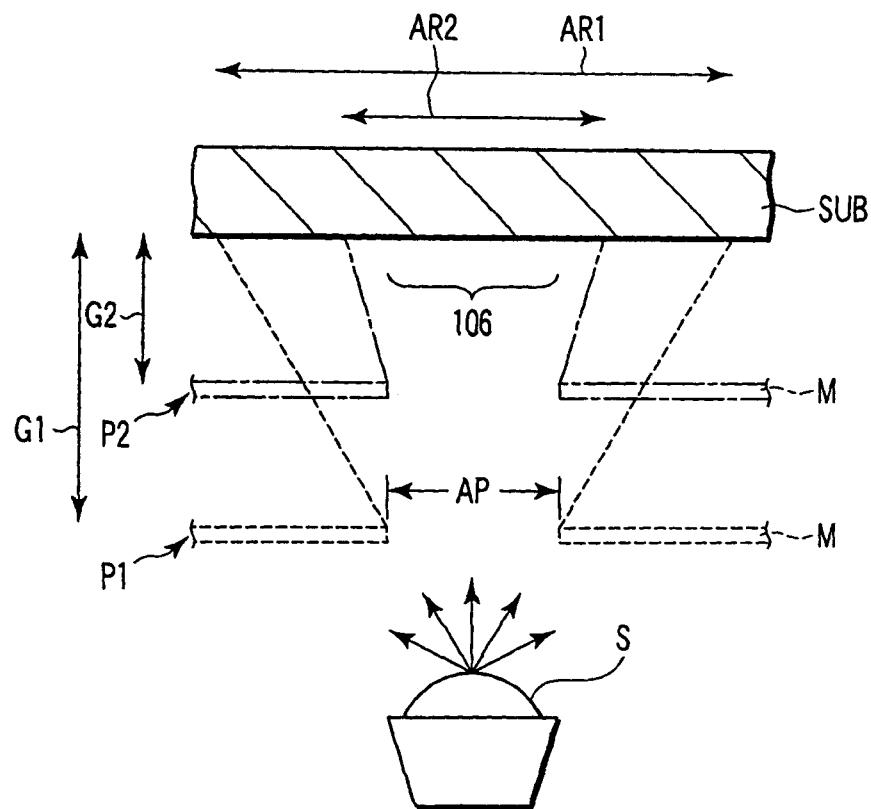

15 利用第二腔室 602，可以通过具有预定形状的开口部的缓冲层用掩膜，对具有作为缓冲层使用功能的树脂材料的液态单体实施蒸发作业。该第二腔室 602 如图 15 所示，在形成缓冲层用的材料源 S 与形成基板 SUB 的有效部 106 的主面之间，配置有缓冲层用掩膜 M。这种缓冲层用掩膜 M 可以在相对基板 SUB 的主面平行的状态下，沿着基板 SUB 的法线方向移动。

20 换句话说就是，该第二腔室 602 在基板 SUB 与缓冲层用掩膜 M 间的间隔比较大时，可以使用比缓冲层用掩膜 M 的开口部 AP 更大的、成膜在基板 SUB 的主面的图案。

对于诸如将缓冲层用掩膜 M 确定在离基板 SUB 的主面比较远的第一位置 P1 处的场合，在基板 SUB 与缓冲层用掩膜 M 之间将形成有比较大的第一间隔 G1。通过在这种第一位置 P1 处配置缓冲层用掩膜 M 的方式，可以限制由材料源 S 飞溅出的树脂材料到达基板 SUB 的主面，并且可以使通过开口部 AP 的树脂材料到达基板 SUB 的主面上的第一区域 AR1 处。采用这种方式，可以使树脂材料在第一区域 AR1 处成膜。

与此相对的是，对于将缓冲层用掩膜 M 确定在离基板 SUB 的主面比较近的第二位置 P2 处的场合，在基板 SUB 与缓冲层用掩膜 M 之间将形成有比较小

的第二间隔 G2。通过在这种第二位置 P2 处配置缓冲层用掩膜 M 的方式，可以限制由材料源 S 飞溅出的树脂材料到达基板 SUB 的主面，并且可以使通过开口部 AP 的树脂材料到达基板 SUB 的主面上的第二区域 AR2。采用这种方式，可以使树脂材料在比第一区域 AR1 小的第二区域 AR2 处成膜。

5 需要进一步指出的是，当对构成封装组件 300 的各缓冲层实施形成时，可以通过具有相同图案的开口部 AP 的掩膜 M 对树脂材料实施成膜作业，通过在各个成膜工序中在由基板 SUB 的主面至掩膜 M 间具有不同间隔的方式实施位置吻合的方式，可以形成出彼此具有不同尺寸的图案的若干缓冲层。因此，在形成具有不同尺寸的图案的若干缓冲层时，不需要制备多个掩膜，所以可以减少制造成本。

10

利用第三腔室 603，可以通过使成膜的单体聚合化的方式，对树脂材料实施硬化作业。对于这种单体采用的是感光性树脂材料（比如说为紫外线硬化型树脂材料）的场合，可以在第三腔室 603 中配置有具有预定波长（比如说为紫外线波长）的光源。在这种第三腔室 603 处，可以通过在预定曝光量下对成膜 15 用单体实施曝光的方式，使单体通过聚合化而被硬化，形成缓冲层。

而且，对于这种单体采用的是电子束硬化型树脂材料的场合，可以在第三腔室 603 中配置有电子束源。在这种第三腔室 603 处，可以通过使用电子束对成膜用单体实施照射的方式，使单体通过聚合化而被硬化，形成缓冲层。

在这儿设置有形成缓冲层使用的成膜用第二腔室 602 和硬化用第三腔室 20 603，然而也可以在第二腔室 602 中配置有具有预定波长的光源和电子束源，从而可以在第二腔室 602 中同时进行成膜作业和硬化处理作业。而且，还可以在第二腔室 602 中，对可通过气相方式实施聚合的树脂材料实施蒸镀作业，并省略掉硬化处理作业（第三腔室）。

在所说明的封装组件 300 的形成过程中，还可以在缓冲层用掩膜相对形成有效部 106 的基板 SUB 满足预定位置关系以实施位置吻合作业的状态下，对其实施安装。

25

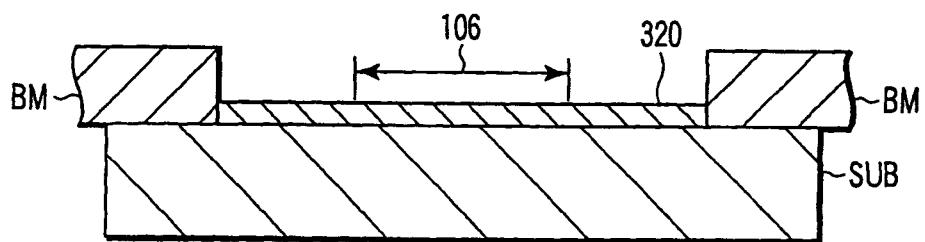

首先如图 13B 所示，在基板 SUB 的主面上，形成使有效部 106 与外部空气隔断的第一壁垒层 320。换句话说就是，将在形成有效部 106 的主面上具有壁垒层用掩膜 BM 的基板 SUB，导入至第一腔室 601。在第一腔室 601 中，通过利用壁垒层用掩膜 BM 对金属材料实施蒸镀的方式，形成第一壁垒层 320。

30

在这时，第一壁垒层 320 形成在基板 SUB 的主面上包含有效部 106 且比有效部 106 的范围大的区域处。

随后如图 13C 所示，按照与有效部 106 对应的方式，在第一壁垒层 320 上形成其图案至少比有效部 106 更大的第一缓冲层 311。换句话说就是，将具有

5 壁垒层用掩膜 BM 的基板 SUB，导入至第二腔室 602 中，使用缓冲层用掩膜 M 在第一位置 P1 处实施位置确定，进而在基板 SUB 的正面与缓冲层用掩膜 M 间形成比较大的第一间隔 G1。对作为树脂材料的、诸如紫外线硬化型树脂材料等等的液态单体实施蒸发作业，利用缓冲层用掩膜 M 在基板正面的第一区域 AR1 处使单体成膜。这种第一区域 AR1 为比位于正下方的第一壁垒层 320 更小的区域，而且为包含着有效部 106 且比有效部 106 更大的区域。

10

随后，将配置有壁垒层用掩膜 BM 的基板 SUB 导入至第三腔室 603。在第三腔室 603 中对成膜在基板 SUB 的正面的单体，在预定曝光量下通过紫外线波长的光束实施曝光。采用这种方式，可以使单体聚合而硬化，形成为第一缓冲层 311。

15 随后如图 13D 所示，在基板 SUB 的正面，与形成第一壁垒层 320 时类似，在第一腔室 601 中形成使第一缓冲层 311 与外部空气隔断的第二壁垒层 321。该第二壁垒层 321 在比位于正下方的第一缓冲层 311 更大的范围内形成。该第二壁垒层 321 是利用安装在基板 SUB 处的壁垒层用掩膜 BM 实施形成的，而且是通过与第一壁垒层 320 相同的图案形成的。采用这种方式，可以通过第二壁垒层 20 321 对整个第一缓冲层 311 进行覆盖。

随后如图 13E 所示，按照与有效部 106 对应的方式，在第二壁垒层 321 上形成其图案至少比有效部 106 更大的第二缓冲层 312。换句话说就是，将具有壁垒层用掩膜 BM 的基板 SUB，导入至第二腔室 602 中。在第二腔室 602 中，使缓冲层用掩膜 M 由第一位置 P1 处起相对基板 SUB 的正面，沿法线方向 N 平行移动，在第二位置 P2 处实施位置确定。采用这种方式，可以在基板 SUB 的正面与缓冲层用掩膜 M 间形成比较小的第二间隔 G2。对诸如紫外线硬化型树脂材料等等的液态单体实施蒸发作业，利用缓冲层用掩膜 M 在基板正面的第二区域 AR2 处使单体成膜。这种第二区域 AR2 为比位于正下方的第二壁垒层 321 更小的区域，而且为包含着有效部 106 且比有效部 106 更大的区域。

25

30 随后，将配置有壁垒层用掩膜 BM 的基板 SUB 导入至第三腔室 603。在第

三腔室 603 中对成膜在基板 SUB 的主面上的单体，在预定曝光量下通过紫外线波长的光束实施曝光。采用这种方式，可以使单体聚合而硬化，形成为第二缓冲层 312。

该第二缓冲层 312 是利用在形成第一缓冲层 311 时使用的同一缓冲层用掩膜 M 实施形成的，所以呈与第一缓冲层 311 类似的形状。而且，第二缓冲层 312 是按照使缓冲层用掩膜 M 由第一位置 P1 处起相对基板 SUB 的正面，沿法线方向 N 平行移动，在第二位置 P2 处实施位置确定的方式形成的，所以其重心 O2 与第一缓冲层 311 的重心 O1 一致（点 O2 位于通过点 O1 的基板正面的法线 N 上）。

该第二缓冲层 312 按照具有比位于它的下层的第一缓冲层 311 更小尺寸的图案的方式形成，因此第二缓冲层 312 的外侧边缘部 312A，在基板正面内位于比第一缓冲层 311 上的外侧边缘部 311A 更为内侧的位置叠层设置。

随后如图 13F 所示，在基板 SUB 的正面，与形成第一壁垒层 320 时类似，在第一腔室 601 中形成使第二缓冲层 312 与外部空气隔断的第三壁垒层 322。该第三壁垒层 322 在比位于正下方的第二缓冲层 312 更大的范围内形成。而且，该第三壁垒层 322 是利用安装在基板 SUB 处的壁垒层用掩膜 BM 实施形成的，所以是通过与第一壁垒层 320 和第二壁垒层 321 相同的图案形成的。采用这种方式，可以通过第三壁垒层 322 对整个第二缓冲层 312 进行覆盖。通过上述工序，可以形成出具有如图 11A 和图 11B 所示构成形式的封装组件 300。在封装组件 300 形成之后，将壁垒层用掩膜 BM 由基板 SUB 处取下。

随后，在封装组件 300 的表面处，即在第二壁垒层 321 的整个表面处涂覆粘接剂，与封装部件 200 实施粘接。而且，根据需要还可以在获取 EL 发光的侧表面处，贴覆偏振光板。

对于在母模基板上形成有多个阵列部の場合，可以随后按照每个阵列部的单个尺寸对母模基板实施切割。采用这种方式，可以由母模基板 SUB 形成安装有封装组件 300 和封装部件 200 的单个的阵列基板 100。而且，对于不是采用母模基板，而是在基板上形成单个阵列部の場合，将不需要实施按照单个尺寸实施切割的工序，对于这种場合，可以利用基板 SUB 直接形成安装有封装组件 300 和封装部件 200 的单个的阵列基板 100。

对于使用上述制造工序制造出的有机 EL 显示装置 1，可以按照不会受到下

层影响的方式，对形成在有效部 106 处的有机 EL 元件 40 实施可靠地覆盖。而且，即使在这些缓冲层和壁垒层中的某些个形成有微小间隙，通过这种由若干层形成的叠层构造，也可以延长到达有机 EL 元件处的路径，从而可以获得延长使用寿命的良好技术效果。因此，可以使有机 EL 元件 40 与外部空气隔断，

- 5 在长时间里保持良好的工作性能。在通过粘接剂将封装部件 200 粘接至封装组件 300 上时，或是通过粘接剂将偏振光板粘接至封装部件 200 上时，可以防止包含在粘接剂中的杂质侵入至有机 EL 元件 40 内，从而可以防止有机 EL 元件 40 的性能出现恶化。

而且，第一缓冲层 311 是按照与配置在其上层处的第二缓冲层 312 具有不同尺寸的图案实施形成的，且第二缓冲层 312 上的外侧边缘部 312A，在基板正面内位于比第一缓冲层 311 上的外侧边缘部 311A 更为内侧或者外侧的位置叠层设置。各个缓冲层可以分别通过利用同一图案的缓冲层用掩膜，对树脂材料分别实施成膜的成膜工序，按照由基板正面到缓冲层用掩膜间的间隔不同的方式实施位置吻合，进而实施形成。

15 对于为如图 11A 和图 11B 所示的封装组件 300，即第二缓冲层 312 具有比位于其下层的第一缓冲层 311 更小尺寸的图案的场合，第二缓冲层 312 上的外侧边缘部 312A，在基板正面内位于比第一缓冲层 311 上的外侧边缘部 311A 更为内侧的位置。采用这种构成形式，可以使通过形成第二缓冲层 312 用的成膜工序形成的、由基板 SUB 的正面至缓冲层用掩膜 M 间的间隔 G2，按照比通过 20 形成第一缓冲层 311 用的成膜工序形成的间隔 G1 小的方式实施设定。

换句话说就是，构成封装组件 300 的各个缓冲层的尺寸呈比上层依次减小的构成形式，所以可以通过各缓冲层的成膜工序，按照由基板正面到缓冲层用掩膜间的间隔依次减小的方式（通过对位于上层的缓冲层进行的成膜工序形成的基板—掩膜间的间隔比通过对位于下层的缓冲层进行的成膜工序形成的基板—掩膜间的间隔小的方式）实施形成。

对于为如图 12A 和图 12B 所示的封装组件 300，即第二缓冲层 312 具有比位于其下层的第一缓冲层 311 更大尺寸的图案的场合，第二缓冲层 312 上的外侧边缘部 312A，在基板正面内位于比第一缓冲层 311 上的外侧边缘部 311A 更为外侧的位置。采用这种构成形式，可以使通过形成第二缓冲层 312 用的成膜 30 工序形成的由基板 SUB 的正面至缓冲层用掩膜 M 间的间隔 G2，按照比通过形

成第一缓冲层311用的成膜工序形成的间隔G1大的方式实施设定。

换句话说就是，可以如图13E所示，在形成第一缓冲层311用的、经过通过缓冲层用掩膜M在第二位置P2处实施位置吻合的成膜工序和硬化工序之后，进行如图13C所示的、通过缓冲层用掩膜M在形成第二缓冲层312的第一位置5 P1处实施位置吻合的成膜工序和硬化工序。

换句话说就是，构成封装组件300的各个缓冲层的尺寸呈比上层依次增大的构成形式，所以可以通过各缓冲层的成膜工序，按照由基板正面到缓冲层用掩膜间的间隔依次增大的方式（通过对位于上层的缓冲层进行的成膜工序形成的基板—掩膜间的间隔比通过对位于下层的缓冲层进行的成膜工序形成的基板—掩膜间的间隔大的方式）实施形成。

10

通过上述说明可知，如果采用本第四实施例，可以提供出一种具有在基板正面形成的、配置有显示图象用的多个象素的、实质上呈矩形形状的有效部，以及按照至少对基板正面的有效部进行覆盖的方式配置的封装组件的光学元器件。这种光学元器件中的封装组件可以具有至少两层的缓冲层，以及具有比缓冲层更大的图案且按照覆盖各个缓冲层的方式形成的壁垒层叠层构成。第一缓冲层具有与配置在其上层处的第二缓冲层不同尺寸的图案，而且第二缓冲层的外侧边缘部，在基板正面内位于比第一缓冲层上的外侧边缘部更为内侧或更为外侧的位置。

15

因此，可以对形成在有效部处的显示元件实施可靠覆盖。对于叠层设置在越上层处的缓冲层具有越小尺寸的图案，且在外侧边缘部彼此偏置的状态下重叠设置的场合，可以通过缓慢的斜面形成封装组件的周部边缘。采用这种方式，可以通过壁垒层对包含着缓冲层外侧边缘部的整个区域实施可靠地覆盖，从而可以防止覆盖区域不良的现象出现。而且，对于叠层设置在越上层处的缓冲层具有越大尺寸的图案，且在外侧边缘部彼此偏置的状态下重叠设置的场合，可以使上层缓冲层按照覆盖下层缓冲层的方式配置，所以可以提高作为封装组件的封装性能。因此，可以确保对外部的杂质和空气的高屏蔽性能，从而可以在长时间里保持稳定且良好的显示性能。

20

25

而且，在上述第四实施例中，为了使由基板正面到缓冲层用掩膜间具有不同间隔，是在第二腔室中使缓冲层用掩膜沿基板正面的法线方向移动的，然而30 本发明并不仅限于此。如果举例来说，还可以使基板沿其法线方向移动，以使

与缓冲层用掩膜间具有不同间隔，或是使基板和缓冲层用掩膜两者均沿基板正面的法线方向移动。

而且，为了使由基板正面到缓冲层用掩膜间具有不同间隔，在这儿是在第二腔室中，使缓冲层用掩膜和基板中的至少一个沿基板法线方向移动至预定位

5 置以实施位置吻合作业的，然而为了对基板正面到缓冲层用掩膜间的间隔实施更高精度的控制，还可以采用在其间插入具有预定高度的分隔器的构成形式。

而且，在上述第四实施例中，是以构成封装组件的缓冲层为两层、壁垒层为三层的场合（可参见图11A和图12A）为例进行说明的，然而本发明对其层数的组合形式并不仅限于该实例。对于封装组件由十层以上的薄膜叠层构成的

10 工序数目比较多，生产性能低下。因此，叠层设置的薄膜层数可以在两层以上十层以下，设定为三至五层更好些。

如果采用如上所述的第一至第四实施例，可以提供出封装性能优良且能够保持良好显示性能的显示元件、光学元器件以及光学元器件的制造方法。

本领域的普通技术人员还可以获知本发明的附加优点和改进形式。因此，

15 本发明的请求保护范围并不仅限于说明书中给出的详细、具体的实施形式。本领域的普通技术人员可以在不脱离本发明的主题和由权利要求限定的范围及等价范围内，获得各种各样的具体实施形式。

1

图

图 2

图 3

图 4A

图 4B

图 4C

图 4D

图 5A

图 5B

图 5C

图 6

图 7

图 8A

图 8B

图 8C

图 8D

图 8E

图 10

图 11A

图 11B

图 12A

图 12B

图 13A

图 13B

图 13C

图 13D

图 13E

图 13F

图 14

图 15

|                |                                                                               |                      |            |

|----------------|-------------------------------------------------------------------------------|----------------------|------------|

| 专利名称(译)        | 显示元件、光学元器件以及光学元器件的制造方法                                                        |                      |            |

| 公开(公告)号        | <a href="#">CN1645975A</a>                                                    | 公开(公告)日              | 2005-07-27 |

| 申请号            | CN200410104702.0                                                              | 申请日                  | 2004-11-26 |

| [标]申请(专利权)人(译) | 东芝松下显示技术股份有限公司                                                                |                      |            |

| 申请(专利权)人(译)    | 东芝松下显示技术有限公司                                                                  |                      |            |

| 当前申请(专利权)人(译)  | 东芝松下显示技术有限公司                                                                  |                      |            |

| [标]发明人         | 佐野浩<br>炭田祉朗<br>吉冈达男                                                           |                      |            |

| 发明人            | 佐野浩<br>炭田祉朗<br>吉冈达男                                                           |                      |            |

| IPC分类号         | H05B33/04 G02F1/13 H01J1/62 H01J63/04 H01L51/52 H05B33/02 H05B33/10 H05B33/12 |                      |            |

| CPC分类号         | H01L51/5237 H01L51/5256 H01L51/5246 H01L51/5253 H01L51/5259                   |                      |            |

| 优先权            | 2003398084 2003-11-27 JP<br>2004172450 2004-06-10 JP                          |                      |            |

| 其他公开文献         | CN100472844C                                                                  |                      |            |

| 外部链接           | <a href="#">Espacenet</a>                                                     | <a href="#">Sipo</a> |            |

**摘要(译)**

本发明涉及显示元件、光学元器件以及光学元器件的制造方法。阵列基板100具有在基板正面形成的、配置有显示图象用的多个象素的、实质上呈矩形形状的有效部106。有机EL显示装置1具有按照至少对阵列基板100上的正面的有效部106进行覆盖的方式配置的封装组件300。封装组件300由具有实质上相同的图案的、至少两层的、实质上呈矩形形状的缓冲层311、312、313，以及具有比各缓冲层更大的图案的、按照使其与外部空气隔断的方式对各缓冲层进行覆盖的壁垒层321、322、323叠层构成。由有效部106的端部处的一条侧边至第一缓冲层311的端部处的一条侧边间的最短距离，与至第二缓冲层312的端部处的一条侧边间的最短距离不同。