## (19) 中华人民共和国国家知识产权局

# (12) 发明专利

(10) 授权公告号 CN 101127188 B (45) 授权公告日 2012.05.02

(21)申请号 200710153394.4

(22)申请日 2002.11.13

(**30**) 优先权数据 348032/2001 2001.11.13 JP

(62)分案原申请数据 02149531.9 2002.11.13

(73) 专利权人 株式会社半导体能源研究所 地址 日本神奈川县厚木市

(72) 发明人 木村肇

(74) 专利代理机构 中国专利代理(香港)有限公司 72001

代理人 张雪梅 王小衡

(51) Int. CI.

G09G 3/30 (2006.01)

G09G 3/32 (2006.01)

**G09G 3/20** (2006.01)

HO5B 33/08 (2006.01)

H05B 33/14 (2006. 01) H01L 51/50 (2006. 01) H01L 27/32 (2006. 01)

**GO9F 9/33**(2006, 01)

审查员 孙大林

权利要求书 3 页 说明书 29 页 附图 22 页

#### (54) 发明名称

显示器件及其驱动方法

#### (57) 摘要

一种具有几乎不会由于退化的EL元件而产生电流值改变的结构的半导体器件被提供。电容元件被配置于驱动TFT栅极和源极之间,视频信号输入到栅电极,然后它处于浮置状态。此时,当驱动TFT的栅极源极电压超过阈值时,驱动TFT被开启。假定EL元件退化并且阳极电位上升,即驱动TFT的源极电位上升,则通过电容元件的耦合处于浮置状态的驱动TFT的栅电极的电位将上升相同量。因此,即使当阳极电位由于EL元件退化而上升,这种上升同样被加到栅电极电位,而允许驱动TFT的栅极源极电压保持不变。

CN 101127188 B

1. 一种包含像素的半导体器件,所述像素包括:

发光元件:

包括微晶半导体膜的第一晶体管;

第一晶体管的源电极电连接到发光元件的一个电极;

电连接在第一晶体管的源电极和栅电极之间的电容器;

电连接到第一晶体管的漏电极的电流供电线;以及

电连接到第一晶体管的漏电极的第二晶体管。

- 2. 权利要求 1 的半导体器件,其中所述像素还包括电连接到第一晶体管的栅电极的第三晶体管,并且其中第一晶体管和第三晶体管具有相同的导电类型。

- 3. 权利要求1的半导体器件,其中第一晶体管的栅电极包含钼。

- 4. 权利要求 1 的半导体器件,其中将所述半导体器件引入选自发光显示器件、数字静态照相机、声音再现装置、膝上型计算机、移动计算机、便携式图像再现装置、护目镜式显示器、摄像机以及移动电话的电子装置。

- 5. 权利要求 1 的半导体器件,其中所述电容器由所述第一晶体管的有源层和作为扫描 线的同一层形成。

- 6. 权利要求 1 的半导体器件,其中所述第一晶体管具有顶部栅极结构或底部栅极结构。

- 7. 权利要求 1 的半导体器件,其中所述发光元件包含有机发光材料,所述有机发光材料通过三重激发产生磷光。

- 8. 权利要求 7 的半导体器件, 其中所述有机发光材料是香豆素色素、Pt 络合物或 Ir 络合物。

- 9. 一种包括像素的半导体器件,所述像素包括:

基片:

基片上的发光元件:

基片上的第一晶体管:

第一晶体管的源电极电连接到发光元件的一个电极:

电连接在第一晶体管的源电极和栅电极之间的电容器;

电连接到第一晶体管的漏电极的电流供电线;

发光元件上的透明元件;以及

电连接到第一晶体管的漏电极的第二晶体管。

- 10. 权利要求 9 的半导体器件,其中所述像素还包括电连接到第一晶体管的栅电极的第三晶体管,并且其中第一晶体管和第三晶体管具有相同的导电类型。

- 11. 权利要求 9 的半导体器件,其中第一晶体管的栅电极包含钼。

- 12. 权利要求 9 的半导体器件,其中将所述半导体器件引入选自发光显示器件、数字静态照相机、声音再现装置、膝上型计算机、移动计算机、便携式图像再现装置、护目镜式显示器、摄像机以及移动电话的电子装置。

- 13. 权利要求 9 的半导体器件,其中所述电容器由所述第一晶体管的有源层和作为扫描线的同一层形成。

- 14. 权利要求 9 的半导体器件,其中所述第一晶体管具有顶部栅极结构或底部栅极结

构。

- 15. 权利要求 9 的半导体器件,其中所述发光元件包含有机发光材料,所述有机发光材料通过三重激发产生磷光。

- 16. 权利要求 15 的半导体器件,其中所述有机发光材料是香豆素色素、Pt 络合物或 Ir 络合物。

- 17. 一种包括像素的半导体器件,所述像素包括:

发光元件:

具有底部栅极结构的第一晶体管;

第一晶体管的源电极电连接到发光元件的一个电极;

电连接在第一晶体管的源电极和栅电极之间的电容器;

电连接到第一晶体管的漏电极的电流供电线;以及

电连接到第一晶体管的漏电极的第二晶体管。

- 18. 权利要求 17 的半导体器件,其中所述像素还包括电连接到第一晶体管的栅电极的第三晶体管,并且其中第一晶体管和第三晶体管具有相同的导电类型。

- 19. 权利要求 17 的半导体器件,其中第一晶体管的栅电极包含钼。

- 20. 权利要求 17 的半导体器件,其中将所述半导体器件引入选自发光显示器件、数字静态照相机、声音再现装置、膝上型计算机、移动计算机、便携式图像再现装置、护目镜式显示器、摄像机以及移动电话的电子装置。

- 21. 权利要求 17 的半导体器件,其中所述电容器由所述第一晶体管的有源层和作为扫描线的同一层形成。

- 22. 权利要求 17 的半导体器件,其中所述发光元件包含有机发光材料,所述有机发光材料通过三重激发产生磷光。

- 23. 权利要求 22 的半导体器件,其中所述有机发光材料是香豆素色素、Pt 络合物或 Ir 络合物。

- 24. 一种声音再现装置,包括:

使用包括像素的发光器件的显示部分,所述像素包括:

发光元件:

第一晶体管:

第一晶体管的源电极电连接到发光元件的一个电极;

电连接到第一晶体管的源电极和栅电极之间的电容器;

电连接到第一晶体管的漏电极的电流供电线:以及

电连接到第一晶体管的漏电极的第二晶体管。

- 25. 权利要求 24 的声音再现装置,其中所述像素还包括电连接到第一晶体管的栅电极的第三晶体管,并且其中第一晶体管和第三晶体管具有相同的导电类型。

- 26. 权利要求 24 的声音再现装置,其中第一晶体管的栅电极包含钼。

- 27. 权利要求 24 的声音再现装置,其中所述电容器由所述第一晶体管的有源层和作为扫描线的同一层形成。

- 28. 权利要求 24 的声音再现装置,其中所述第一晶体管具有顶部栅极结构或底部栅极结构。

- 29. 权利要求 24 的声音再现装置,其中所述发光元件包含有机发光材料,所述有机发光材料通过三重激发产生磷光。

- 30. 权利要求 29 的声音再现装置,其中所述有机发光材料是香豆素色素、Pt 络合物或 Ir 络合物。

- 31. 一种显示器件,包括:

使用包括像素的发光器件的显示部分,所述像素包括:

发光元件:

第一晶体管:

第一晶体管的源电极电连接到发光元件的一个电极;

电连接在第一晶体管的源电极和栅电极之间的电容器;

电连接到第一晶体管的漏电极的电流供电线;以及

电连接到第一晶体管的漏电极的第二晶体管。

- 32. 权利要求 31 的显示器件,其中所述像素还包括电连接到第一晶体管的栅电极的第三晶体管,并且其中第一晶体管和第三晶体管具有相同的导电类型。

- 33. 权利要求 31 的显示器件,其中第一晶体管的栅电极包含钼。

- 34. 权利要求 31 的显示器件,其中所述电容器由所述第一晶体管的有源层和作为扫描线的同一层形成。

- 35. 权利要求 31 的显示器件,其中所述第一晶体管具有顶部栅极结构或底部栅极结构。

- 36. 权利要求 31 的显示器件,其中所述发光元件包含有机发光材料,所述有机发光材料通过三重激发产生磷光。

- 37. 权利要求 36 的显示器件,其中所述有机发光材料是香豆素色素、Pt 络合物或 Ir 络合物。

- 38. 一种包含像素的半导体器件,所述像素包括:

发光元件:

包括单晶半导体膜的第一晶体管;

第一晶体管的源电极电连接到发光元件的一个电极:

电连接在第一晶体管的源电极和栅电极之间的电容器;

电连接到第一晶体管的漏电极的电流供电线;以及

电连接到第一晶体管的漏电极的第二晶体管。

- 39. 权利要求 38 的半导体器件,其中所述像素还包括电连接到第一晶体管的栅电极的第三晶体管,并且其中第一晶体管和第三晶体管具有相同的导电类型。

- 40. 权利要求 38 的半导体器件,其中第一晶体管的栅电极包含钼。

- 41. 权利要求 38 的半导体器件,其中将所述半导体器件引入选自发光显示器件、数字静态照相机、声音再现装置、膝上型计算机、移动计算机、便携式图像再现装置、护目镜式显示器、摄像机以及移动电话的电子装置。

# 显示器件及其驱动方法

[0001] 本发明申请是本发明申请人于 2002 年 11 月 13 日提交的、申请号为 02149531.9、发明名称为"显示器件及其驱动方法"的发明申请的分案申请。

#### 技术领域

[0002] 本发明涉及具有晶体管的一种半导体器件的构成。本发明还涉及包含具有制造于绝缘材料如玻璃和塑料上的薄膜晶体管(此后称作 TFT)的半导体器件的有源矩阵显示器件的构成。此外,本发明涉及采用这样的显示器件的电子装置。

#### 背景技术

[0003] 最近几年,使用发光元件包括电致发光(EL)元件的显示器件的研制已积极展开。发光元件具有高可见度,因为它为自己发光。它不需要在液晶显示器(LCD)中所需要的背光,因此它适合形成不引人注目的外形,并且对视场几乎没有限制。

[0004] 此处,EL元件是一种具有能够通过施加电场得到光发射的光发射层的元件。光发射层具有从单重激发态返回到基态的光发射(荧光),和从三重激发态返回到基态的光发射(磷光)。本发明中,光发射器件可具有上面任何一种光发射形式。

[0005] EL元件被构成,其中光发射层被夹在一对电极(阳极和阴极)之间,形成一般的叠层结构。典型地,阳极/空穴传输层/发射层/电子传输层/阴极的叠层结构是很有名的,它由 Eastman Kodak 公司的 Tang 等人提出。该结构具有相当高的发光效率,它适用于目前研究中的许多 EL 器件。

[0006] 此外,在阳极和阴极之间还有按照空穴注入层/空穴传输层/光发射层/电子传输层,或空穴注入层/空穴传输层/光发射层/电子传输层/电子注入层顺序排列的其它叠层结构。作为用于本发明光发射器件的 EL 元件结构,可采用以上描述的任何结构。此外, 荧光染料可被掺杂到光发射层中。

[0007] 本说明书中,位于阳极和阴极间的所有层在 EL 元件中被总称为 EL 层。因此,空穴注入层,空穴传输层,光发射层,电子传输层和电子注入层都包括在 EL 元件中。由阳极、EL 层和阴极形成的发光元件称为 EL 元件。

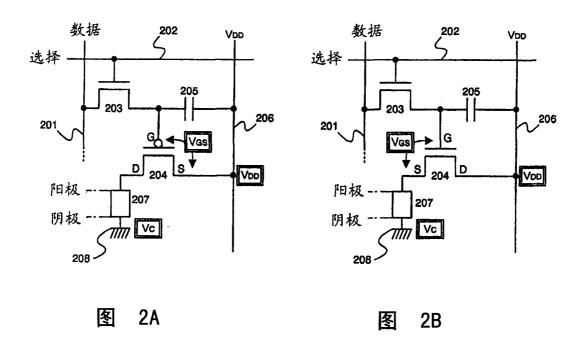

[0008] 图 2A 和 2B 描述了一般发光器件的像素的构成。另外,作为典型的光发射器件,举例说明了一种 EL 显示器件。示于图 2A 和 2B 的像素具有源极信号线 201,栅极信号线 202, 开关 TFT203,驱动 TFT204,电容元件 205,电流供电线 206,EL 元件 207,以及电源线 208。图 2A 中的驱动 TFT204 采用 p- 沟道型,图 2B 中的驱动 TFT204 采用 n- 沟道型。开关 TFT203 是一个用作输入视频信号到像素的开关 TFT,因此极性不被限定。

[0009] 每一部分的连接将被描述。此处,TFT 具有三个极 - 栅极、源极和漏极,但是由于TFT 的结构,源极和漏极彼此不能明显不同。因此,在描述元件间的连接时,源极和漏极其中之一被表示为第一电极,而另外一个被表示为第二电极。当需要描述关于开启、关断 TFT 的每个电极的电位(某种 TFT 的栅极 - 源极电压)时,表示为源极和漏极。

[0010] 此外,本说明书中,处于开的 TFT 是指 TFT 的栅极 - 源极电压超过阈值并且源极和

漏极间有电流的状态。处于关的 TFT 指栅极 - 源极电压下降到低于阈值并且源极和漏极间没有电流的状态。

[0011] 开关TFT 203的栅电极被连接到栅极信号线202,开关TFT 203的第一电极被连接到源极信号线201,而开关TFT203的第二电极被连接到驱动TFT204的TFT的栅电极。驱动TFT204的第一电极被连接到电流供电线206,而驱动TFT204的第二电极被连接到EL元件207的阳极。EL元件207的阳极被连接到电源线208。电流供电线206和电源线208彼此间有电位差。另外,为了保持驱动TFT204的栅极-源极电压,某个固定的电位,例如,可在驱动TFT204的栅电极和电流供电线206间放置电容元件205。

[0012] 当给栅极信号线 202 输入一个脉冲来开启开关 TFT203 时,已被输出到源极信号线 201 的视频信号被输入到驱动 TFT204 的栅电极。驱动 TFT204 的栅极 - 源极电压根据被输入的视频信号的电位确定,并且驱动 TFT204 的源极和漏极间输送的电流(以后被表示为漏极电流)被确定。该电流被提供给 EL 元件 207 来发光。

#### 发明内容

[0013] 利用其体积小重量轻的优点,其中在基片上形成 TFT 并且像素部分和外围电路被安装在一块板内的显示器件被应用于明显增长的移动装置中。同时,TFT 通过许多工艺如膜淀积、通过重复地刻蚀的器件制造、以及用于使半导体具有传导性的杂质元素注入来形成,因此有通过简化工艺使成本减少的艰巨任务。

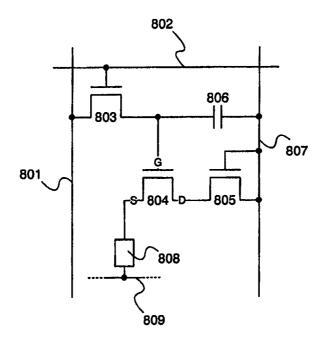

[0014] 然后,当像素部分和外围电路由单极 TFT 构成,注入杂质元素工艺的一部分可被省略。作为通过使用单极 TFT 形成的像素的实例,在发表于 ASIA DISPLAY,315 页 (2001), "基于非晶硅薄膜晶体管的有源矩阵有机光发射显示器件"一文中,提出了如图 8 所示的像素。

[0015] 图 8 所示的像素具有源极信号线 801,栅极信号线 802,开关 TFT803,驱动 TFT804,有源电阻 TFT805,电容元件 806,电流供电线 807, EL 元件 808,以及电源线 809, TFT803 到 805 采用 n- 沟道 TFT。

[0016] 开关TFT803的栅电极被连接到栅极信号线802,开关TFT803的第一电极被连接到源极信号线801,而开关TFT803的第二电极被连接到驱动TFT804的栅电极。驱动TFT804的第一电极被连接到EL元件808的阳极,而驱动TFT804的第二电极被连接到有源电阻TFT805的第一电极。有源电阻TFT805的栅电极和第二电极彼此连接,他们被连接到电流供电线807。EL元件808的阴极被连接到电源线809,和电流供电线807彼此有电位差。电容元件806被配置于驱动TFT804的栅电极和电流供电线807之间,保持施加于驱动TFT804的栅电极的信号电位。

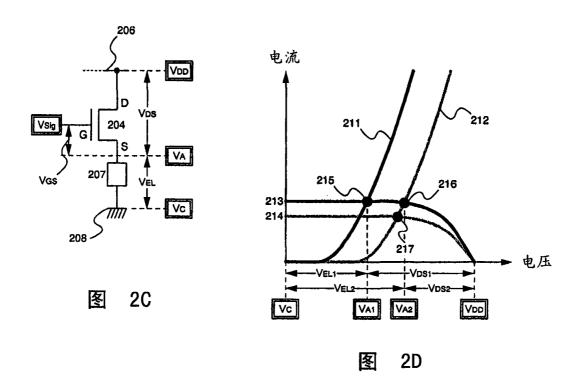

[0017] 如图 2A 和 8 所示,使用 N- 沟道 TFT 作驱动 TFT 的操作将被考虑。图 2C 仅显示了图 2A 和 B 中所示的像素中电流供电线 206 到驱动 TFT 204 到 EL 元件 207 到电源线 208 的构成部分。驱动 TFT 204 被形成为 n- 沟道型,这样被连接到 EL 元件 207 阳极的一侧为源极,而被连接到电流供电线的另一侧为漏极。

[0018] 现在,假设电流供电线 206 的电位为  $V_{DD}$ ,EL 元件 207 的阳极电位为  $V_A$ ,它的阴极电位为  $V_C$ ,并且驱动 TFT204 的栅电极电位为  $V_{Sig}$ 。驱动 TFT204 的源极 – 栅极电压  $V_{GS}$  为  $V_{GS}$  =  $(V_{Sig} - V_A)$ ,EL 元件 207 的阳极 – 阴极电压  $V_{EL}$  为  $V_{EL}$  =  $(V_A - V_C)$ 。

[0019] 图 2D 显示了驱动 TFT204 和 EL 元件 207 的电压 – 电流特性曲线。驱动 TFT204 的电压 – 电流曲线与 EL 元件 207 的电压 – 电流曲线的交点为工作点,它决定被输送通过 EL 元件 207 的电流值和 EL 元件的阳极电位  $V_A$ 。此时,当 EL 元件 207 的电压 – 电流曲线由 211 表示,并且 TFT204 的电压 – 电流曲线用 213 表示时,工作点落在 215,由此电流值和  $V_A = V_{A1}$  被确定。此外,这时驱动 TFT204 的栅极 – 源极电压  $V_{GS}$  被表示为  $V_{GS} = (V_{Sig} - V_{A1})$ 。

[0020] 此处, EL 元件 207 已经退化的情况将被考虑。当 EL 元件 207 已经退化时, 开始发光的电压增加, 曲线向右移动并由 212 表示。此处, 假设驱动 TFT204 在饱和区工作, 以及退化的 EL 元件 207 不引起栅极 – 源极电压改变, 工作点移到 216。更特殊地, 它变为  $V_A = V_2$ 。在这种情况下,即使驱动 TFT204 的源极 – 漏极电压被改变, 电流值没有很大改变, 因此发光没有很大改变。但是, 目前 N- 沟道 TFT 被用作驱动 TFT204,并且被连接到 EL 元件 207 阳极的一侧的是源极。这样, 驱动 TFT204 的栅极 – 源极电压  $V_{GS}$  变小为  $V_{GS} = (V_{Sig} - V_{A2})$ 。所以,驱动 TFT204 的电压 – 电流曲线这时由 214 表示。因此工作点降到 217。更特殊地,退化的 EL 元件 207 引起驱动 TFT204 的源极电位升高和栅极 – 源极电压减小,这样电流值被改变很大,导致发光下降。

[0021] 本发明中,目的是提供一种能够解决如上所描述由退化的 EL 元件所引起问题的 半导体器件,其中 N- 沟道 TFT 被用作驱动 TFT,用于为 EL 元件提供电流。

[0022] 上面所描述的目的的主要点是退化的 EL 元件引起 EL 元件阳极电位,即驱动 TFT 的源极电位升高和由此使驱动 TFT 的栅极 - 源极电压的减小。

[0023] 为了使当 EL 元件退化时电流值不被改变,有必要当退化的 EL 元件引起 EL 元件的阳极电位升高时使驱动 TFT 的栅极 - 源极电压不被改变。

[0024] 在本发明中,采用自举(bootstrap)运行的结构被应用到像素。在驱动 TFT 的栅极和源极间提供一个电容元件,并且在图象信号被输入到栅电极的过程中,源极电位被设定在某个值。图象信号被输入后,栅电极处于浮置状态。此时,如果驱动 TFT 的源极 - 漏极电压超过阈值,驱动 TFT 变为开。但是,如果驱动 TFT 的设定源极电位被释放,电流流向 EL元件,结果阳极电位即驱动 TFT 的源极电位升高。因此处于浮置状态的栅电极的电位,通过置于驱动 TFT 的栅极和源极间的电容元件的耦合,升高相同量。结果,当阳极电位由于 EL元件退化不同地升高时,这种升高可同样加在栅电极电位上,因此可使驱动 TFT 的栅极 - 源极电压保持不变。

[0025] 电容元件(存储电容器)的作用被解释。已输入图象信号的驱动 TFT 的栅极电位被晶体管等的漏泄电流改变,并且驱动 TFT 的源极 - 栅极电压被改变。结果,驱动 TFT 的漏极电流被改变,并且发光减少。因此电容元件需要具有保持电荷使驱动 TFT 的栅极电位在一个恒定值或在预定的显示时期内为几乎恒定值的能力。

[0026] 以下描述本发明的构造。

[0027] 本发明的半导体器件的特征在于包含一个具有发光元件的像素;

[0028] 其中像素具有有两种状态 - 导电和非导电状态的第一和第二开关元件、一个晶体管,一个电容元件以及发光元件:

[0029] 视频信号被输入到第一开关元件的第一电极,并且第一开关元件的第二电极被电连接于晶体管的栅电极;

[0030] 晶体管的第一电极被电连接于第二开关元件的第一电极和发光元件的第一电极,

并且晶体管的第二电极被电连接于第一电源:

[0031] 第二开关元件的第二电极被电连接于第二电源;

[0032] 发光元件的第二电极被电连接于第三电源,并且

[0033] 电容元件被配置于晶体管的栅电极和第一电极之间。

[0034] 本发明的半导体器件的特征在于包含具有发光元件的像素;

[0035] 其中像素具有有两种状态 - 导电和非导电状态的第一、第二和第三开关元件、一个晶体管、一个电容元件以及发光元件:

[0036] 视频信号被输入到第一开关元件的第一电极,并且第一开关元件的第二电极被电连接于晶体管的栅电极:

[0037] 晶体管的第一电极被电连接于第二开关元件的第一电极和发光元件的第一电极,并且晶体管的第二电极被电连接于第一电源;

[0038] 第二开关元件的第二电极被电连接于第二电源;

[0039] 发光元件的第二电极被电连接于第三电源;

[0040] 电容元件被配置于晶体管的栅电极和第一电极之间,并且

[0041] 第三开关元件的第一电极被电连接于晶体管的栅电极,而第三开关元件的第二电极被电连接于晶体管的第一电极、第二电源和第三电源中任何一个。

[0042] 本发明的一种半导体器件的特征在于包含具有发光元件的像素;

[0043] 其中像素具有有两种状态 - 导电和非导电状态的第一、第二和第三开关元件、一个晶体管、一个电容元件以及发光元件:

[0044] 视频信号被输入到第一开关元件的第一电极,并且第一开关元件的第二电极被电连接于晶体管的栅电极;

[0045] 晶体管的第一电极被电连接于第二开关元件的第一电极和发光元件的第一电极, 并且晶体管的第二电极被电连接于第一电源;

[0046] 第二开关元件的第二电极被电连接于第二电源;

[0047] 发光元件的第二电极被电连接于第三电源;

[0048] 电容元件被配置于晶体管的栅电极和第一电极之间,并且

[0049] 第三开关元件的第一电极被电连接于发光元件的第一电极,而第三开关元件的第二电极被电连接于第二电源。

[0050] 本发明的半导体器件包含具有发光元件的像素,

[0051] 其中像素具有有两种状态 - 导电和非导电状态的第一、第二和第三开关元件、一个晶体管、一个电容元件以及发光元件:

[0052] 视频信号被输入到第一开关元件的第一电极,并且第一开关元件的第二电极被电连接于晶体管的栅电极:

[0053] 晶体管的第一电极被电连接于第二开关元件的第一电极和发光元件的第一电极, 并且晶体管的第二电极通过第三开关元件被电连接于第一电源;

[0054] 第二开关元件的第二电极被电连接于第二电源;

[0055] 发光元件的第二电极被电连接于第三电源,并且

[0056] 电容元件被配置于晶体管的栅电极和第一电极之间。

[0057] 在本发明的半导体器件中,当晶体管的电导类型为 N-沟道型时,第一电源的电位

$V_1$ ,第二电源的电位  $V_2$  以及第三电源的电位  $V_3$  可能是  $V_1 > V_2$  和  $V_1 > V_3$ 。

[0058] 在本发明的半导体器件中,第二电源的电位  $V_2$  和第三电源的电位  $V_3$  也可能是  $V_2$   $< V_3$ 。

[0059] 在本发明的半导体器件中,当晶体管的电导类型为 P-沟道型时,第一电源的电位  $V_1$ ,第二电源的电位  $V_2$  以及第三电源的电位  $V_3$  可能是  $V_1 < V_2$  和  $V_1 < V_3$ 。

[0060] 在本发明的半导体器件中,第二电源的电位  $V_2$  以及第三电源的电位  $V_3$  也可能是  $V_2$   $> V_3$ 。

[0061] 本发明的一种半导体器件的特征在于包含具有发光元件的像素;

[0062] 其中像素具有源极信号线、第一和第二栅极信号线、电流供电线、第一、第二和第三晶体管、电容元件以及发光元件;

[0063] 第一晶体管的栅电极被电连接于第一栅极信号线,第一晶体管的第一电极被电连接于第二晶体管的第一电极和发光元件的第一电极,而第一晶体管的第二电极被电连接于与电流供电线彼此间有电位差的第一电源,或不包括该像素的任何一个像素中的第一或第二栅极信号线;

[0064] 第二晶体管的栅电极被电连接于第三晶体管的第一电极,而第二晶体管的第二电极被电连接于电流供电线;

[0065] 第三晶体管的栅电极被电连接于第二栅极信号线,而第三晶体管的第二电极被电连接于源极信号线;

[0066] 发光元件的第二电极被电连接于与电流供电线彼此间有电位差的第二电源,并且

[0067] 电容元件被配置于第二晶体管的栅电极和第一电极之间。

[0068] 本发明的一种半导体器件的特征在于包含具有发光元件的像素;

[0069] 其中像素具有源极信号线、栅极信号线、电流供电线、第一、第二和第三晶体管、电容元件以及发光元件;

[0070] 第一晶体管的栅电极被电连接于栅极信号线,第一晶体管的第一电极被电连接于第二晶体管的第一电极和发光元件的第一电极,而第一晶体管的第二电极被电连接于与电流供电线彼此间有电位差的第一电源,或不包括该像素的任何一个像素中的栅极信号线;

[0071] 第二晶体管的栅电极被电连接于第三晶体管的第一电极,而第二晶体管的第二电极被电连接于电流供电线;

[0072] 第三晶体管的栅电极被电连接于栅极信号线,而第三晶体管的第二电极被电连接于源极信号线;

[0073] 发光元件的第二电极被电连接于与电流供电线彼此间有电位差的第二电源,并且

[0074] 电容元件被配置于第二晶体管的栅电极和第一电极之间。

[0075] 本发明的一种半导体器件的特征在于包含具有发光元件的像素;

[0076] 其中像素具有源极信号线、第一、第二和第三栅极信号线、电流供电线、第一、第二、第三和第四晶体管、电容元件以及发光元件;

[0077] 第一晶体管的栅电极被电连接于第一栅极信号线,第一晶体管的第一电极被电连接于第二晶体管的第一电极和发光元件的第一电极,而第一晶体管的第二电极被电连接于与电流供电线彼此间有电位差的第一电源、在不包括该像素的任何一个像素中的第一、第二和第三栅极信号线以及在该像素中的第二和第三栅极信号线中的任何一个;

[0078] 第二晶体管的栅电极被电连接于第三晶体管的第一电极,而第二晶体管的第二电极被电连接于电流供电线;

[0079] 第三晶体管的栅电极被电连接于第二栅极信号线,而第三晶体管的第二电极被电连接于源极信号线;

[0080] 发光元件的第二电极被电连接于与电流供电线彼此间有电位差的第二电源;

[0081] 电容元件被配置于第二晶体管的栅电极和第一电极之间,并且

[0082] 第四晶体管的栅电极被电连接于第三栅极信号线,第四晶体管的第一电极被电连接于第二晶体管的栅电极,而第四晶体管的第二电极被电连接于第二晶体管的第一电极、第一电源和第二电源中的任何一个。

[0083] 本发明的一种半导体器件的特征在于包含具有发光元件的像素;

[0084] 其中像素具有源极信号线,第一和第二栅极信号线、电流供电线、第一、第二、第三和第四晶体管、电容元件以及发光元件:

[0085] 第一晶体管的栅电极被电连接于第一栅极信号线,第一晶体管的第一电极被电连接于第二晶体管的第一电极和发光元件的第一电极,而第一晶体管的第二电极被电连接于与电流供电线彼此间有电位差的第一电源,在不包括该像素的任何一个像素中的第一和第二栅极信号线以及在该像素中的第二栅极信号线中的任何一个;

[0086] 第二晶体管的栅电极被电连接于第三晶体管的第一电极,而第二晶体管的第二电极被电连接于电流供电线;

[0087] 第三晶体管的栅电极被电连接于第一栅极信号线,而第三晶体管的第二电极被电连接于源极信号线;

[0088] 发光元件的第二电极被电连接于与电流供电线彼此间有电位差的第二电源;

[0089] 电容元件被配置于第二晶体管的栅电极和第一电极之间,并且

[0090] 第四晶体管的栅电极被电连接于第二栅极信号线,第四晶体管的第一电极被电连接于第二晶体管的栅电极,而第四晶体管的第二电极被电连接于第二晶体管的第一电极、第一电源和第二电源中的任何一个。

[0091] 本发明的一种半导体器件的特征在于包含具有发光元件的像素;

[0092] 其中像素具有源极信号线、第一、第二和第三栅极信号线、电流供电线、第一、第二、第三和第四晶体管、电容元件以及发光元件;

[0093] 第一晶体管的栅电极被电连接于第一栅极信号线,第一晶体管的第一电极被电连接于第二晶体管的第一电极和发光元件的第一电极,而第一晶体管的第二电极被电连接于与电流供电线彼此间有电位差的第一电源,在不包括该像素的任何一个像素中的第一、第二和第三栅极信号线以及在该像素中的第二和第三栅极信号线中的任何一个;

[0094] 第二晶体管的栅电极被电连接于第三晶体管的第一电极,而第二晶体管的第二电极被电连接于电流供电线;

[0095] 第三晶体管的栅电极被电连接于第二栅极信号线,而第三晶体管的第二电极被电连接于源极信号线;

[0096] 发光元件的第二电极被电连接于与电流供电线彼此间有电位差的第二电源;

[0097] 电容元件被配置于第二晶体管的栅电极和第一电极之间,并且

[0098] 第四晶体管的栅电极被电连接于第三栅极信号线,第四晶体管的第一电极被电连

接于发光元件的第一电极,而第四晶体管的第二电极被电连接于第一电源。

[0099] 本发明的一种半导体器件的特征在于包含具有发光元件的像素;

[0100] 其中像素具有源极信号线、第一和第二栅极信号线、电流供电线、第一、第二、第三和第四晶体管、电容元件以及发光元件:

[0101] 第一晶体管的栅电极被电连接于第一栅极信号线,第一晶体管的第一电极被电连接于第二晶体管的第一电极和发光元件的第一电极,而第一晶体管的第二电极被电连接于与电流供电线彼此间有电位差的第一电源,在不包括该像素的任何一个像素中的第一、第二和第三栅极信号线以及在该像素中的第二和第三栅极信号线中的任何一个;

[0102] 第二晶体管的栅电极被电连接于第三晶体管的第一电极,而第二晶体管的第二电极被电连接于电流供电线;

[0103] 第三晶体管的栅电极被电连接于第一栅极信号线,而第三晶体管的第二电极被电连接于源极信号线;

[0104] 发光元件的第二电极被电连接于与电流供电线彼此间有电位差的第二电源;

[0105] 电容元件被配置于第二晶体管的栅电极和第一电极之间,并且

[0106] 第四晶体管的栅电极被电连接于第二栅极信号线,第四晶体管的第一电极被电连接于发光元件的第一电极,而第四晶体管的第二电极被电连接于第一电源。

[0107] 本发明的一种半导体器件的特征在于包含具有发光元件的像素;

[0108] 其中像素具有源极信号线、第一、第二和第三栅极信号线、电流供电线,第一、第二、第三和第四晶体管、电容元件以及发光元件;

[0109] 第一晶体管的栅电极被电连接于第一栅极信号线,第一晶体管的第一电极被电连接于第二晶体管的第一电极和发光元件的第一电极,而第一晶体管的第二电极被电连接于与电流供电线彼此间有电位差的第一电源,在不包括该像素的任何一个像素中的第一、第二和第三栅极信号线以及在该像素中的第二和第三栅极信号线中的任何一个;

[0110] 第二晶体管的栅电极被电连接于第三晶体管的第一电极,而第二晶体管的第二电极被电连接于电流供电线;

[0111] 第三晶体管的栅电极被电连接于第二栅极信号线,而第三晶体管的第二电极被电连接于源极信号线;

[0112] 发光元件的第二电极被电连接于与电流供电线彼此间有电位差的第二电源;

[0113] 电容元件被配置于第二晶体管的栅电极和第一电极之间,电容元件保持第二晶体管的栅电极和第一电极之间的电压,并且

[0114] 第四晶体管被配置于第二晶体管的第二电极和电流供电线之间,或第二晶体管的第一电极和发光元件的第一电极之间,并且第四晶体管的栅电极被电连接于第三栅极信号线。

[0115] 本发明的一种半导体器件的特征在于包含具有发光元件的像素;

[0116] 其中像素具有源极信号线、第一和第二栅极信号线、电流供电线、第一、第二、第三和第四晶体管、电容元件以及发光元件:

[0117] 第一晶体管的栅电极被电连接于第一栅极信号线,第一晶体管的第一电极被电连接于第二晶体管的第一电极和发光元件的第一电极,而第一晶体管的第二电极被电连接于与电流供电线彼此间有电位差的第一电源,在不包括该像素的任何一个像素中的第一和第

二栅极信号线以及在该像素中的第二栅极信号线中的任何一个;

[0118] 第二晶体管的栅电极被电连接于第三晶体管的第一电极,而第二晶体管的第二电极被电连接于电流供电线;

[0119] 第三晶体管的栅电极被电连接于第一栅极信号线,而第三晶体管的第二电极被电连接于源极信号线;

[0120] 发光元件的第二电极被电连接于与电流供电线彼此间有电位差的第二电源;

[0121] 电容元件被配置于第二晶体管的栅电极和第一电极之间,电容元件保持第二晶体管的栅电极和第一电极之间的电压,并且

[0122] 第四晶体管被配置于第二晶体管的第二电极和电流供电线之间,或第二晶体管的第一电极和发光元件的第一电极之间,并且第四晶体管的栅电极被电连接于第三栅极信号线。

[0123] 在本发明的半导体器件中,第一和第三晶体管可以是相同的导电类型。

[0124] 在本发明的半导体器件中,包含于像素中的晶体管可以是相同的导电类型。

[0125] 在本发明的半导体器件中,当第二晶体管的一种导电类型为一种 N- 沟道型时,电流供电线的电位  $V_1$ 、第一电源的电位  $V_2$  以及第二电源的电位  $V_3$  是  $V_1 > V_2$  和  $V_1 > V_3$ 。

[0126] 在本发明的半导体器件中,当第二晶体管的导电类型为 N 沟道型时,第一电源的电位  $V_0$  以及第二电源的电位  $V_3$  是  $V_0 > V_3$ 。

[0127] 在本发明的半导体器件中,当第二晶体管的导电类型为 P-沟道型时,电流供电线的电位  $V_1$ 、第一电源的电位  $V_2$  以及第二电源的电位  $V_3$  是  $V_1 < V_2$  和  $V_1 < V_3$ 。

[0128] 在本发明的半导体器件中,当第二晶体管的导电类型为 P- 沟道型时,第一电源的电位  $V_2$  以及第二电源的电位  $V_3$  是  $V_2$  <  $V_3$ 。

[0129] 用于驱动本发明的半导体器件的方法的特征在于具有发光元件的像素被配置,

[0130] 其中像素具有有两种状态 - 导通和非导通状态的第一和第二开关元件,具有一个晶体管,一个电容元件以及发光元件,

[0131] 视频信号被输入到第一开关元件的第一电极,并且第一开关元件的第二电极被电连接于晶体管的栅电极,

[0132] 晶体管的第一电极被电连接于第二开关元件的第一电极和发光元件的第一电极,而晶体管的第二电极被电连接于第一电源,

[0133] 第二开关元件的第二电极被电连接于第二电源,

[0134] 发光元件的第二电极被电连接于第三电源,

[0135] 电容元件被配置于晶体管的栅电极和第一电极之间,

[0136] 用于驱动显示器件的方法包含:

[0137] 第一步导通第一和第二开关元件以输入视频信号到晶体管的栅电极,并固定晶体管的第一电极电位;

[0138] 第二步不导通第一和第二开关元件以使晶体管的栅电极处于浮置状态;以及

[0139] 第三步提供对应于施加到晶体管栅电极电位的电流给发光元件来发射光,

[0140] 其中在第三步,电容元件保持晶体管的栅极-源极电压以使晶体管的第一电极的电位的改变等于晶体管的栅电极的电位改变。

[0141] 用于驱动本发明的半导体器件的方法的特征在于具有发光元件的像素被配置,

[0142] 其中像素具有有两种状态 - 导通和非导通状态的第一、第二和第三开关元件,具有晶体管,电容元件和发光元件,

[0143] 视频信号被输入到第一开关元件的第一电极,并且第一开关元件的第二电极被电连接于晶体管的栅电极,

[0144] 晶体管的第一电极被电连接于第二开关元件的第一电极和发光元件的第一电极,而晶体管的第二电极被电连接于第一电源,

[0145] 第二开关元件的第二电极被电连接于第二电源,

[0146] 发光元件的第二电极被电连接于第三电源,

[0147] 电容元件被配置于晶体管的栅电极和第一电极之间,并且

[0148] 第三开关元件的第一电极被电连接于晶体管的栅电极,而第三开关元件的第二电极被电连接于晶体管的第一电极,第二电源和第三电源中任何一个,

[0149] 用于驱动显示器件的方法包含:

[0150] 第一步导通第一和第二开关元件以输入视频信号到晶体管的栅电极,并固定晶体管的第一电极电位;

[0151] 第二步不导通第一和第二开关元件以使晶体管的栅电极处于浮置状态;

[0152] 第三步提供对应于施加到晶体管栅电极电位的电流给发光元件来发射光;并且

[0153] 第四步导通第三开关元件使得晶体管的栅极 - 源极电压等于或低于阈值电压绝对值,并停止提供电流给发光元件,

[0154] 其中在第三步,电容元件保持晶体管的栅极-源极电压以使晶体管的第一电极的电位的改变等于晶体管的栅电极的电位改变。

[0155] 用于驱动本发明的半导体器件的方法的特征在于具有发光元件的像素被配置,

[0156] 其中像素具有有两种状态 - 导通和非导通状态的第一、第二和第三开关元件,具有晶体管,电容元件和发光元件,

[0157] 视频信号被输入到第一开关元件的第一电极,并且第一开关元件的第二电极被电连接于晶体管的栅电极,

[0158] 晶体管的第一电极被电连接于第二开关元件的第一电极和发光元件的第一电极,而晶体管的第二电极被电连接于第一电源,

[0159] 第二开关元件的第二电极被电连接于第二电源,

[0160] 发光元件的第二电极被电连接于第三电源,

[0161] 电容元件被配置于晶体管的栅电极和第一电极之间,并且

[0162] 第三开关元件的第一电极被电连接于发光元件的第一电极,而第三开关元件的第二电极被电连接于第二电源,

[0163] 用于驱动显示器件的方法包含:

[0164] 第一步导通第一和第二开关元件以输入视频信号到晶体管的栅电极,并固定晶体管的第一电极电位;

[0165] 第二步不导通第一和第二开关元件以使晶体管的栅电极处于浮置状态;

[0166] 第三步提供对应于施加到晶体管栅电极电位的电流给发光元件来发射光;并且

[0167] 第四步导通第三开关元件使得晶体管的栅极-源极电压等于或低于阈值电压绝对值,并停止提供电流给发光元件,

[0168] 其中在第三步,电容元件保持晶体管的栅极-源极电压以使晶体管的第一电极的电位的改变等于晶体管的栅电极的电位改变。

[0169] 用于驱动本发明的半导体器件的方法的特征在于具有发光元件的像素被配置,

[0170] 其中像素具有有两种状态 - 导通和非导通状态的第一、第二和第三开关元件,具有晶体管,电容元件和发光元件,

[0171] 视频信号被输入到第一开关元件的第一电极,并且第一开关元件的第二电极被电连接于晶体管的栅电极,

[0172] 晶体管的第一电极被电连接于第二开关元件的第一电极和发光元件的第一电极,而晶体管的第二电极通过第三开关元件被电连接于第一电源,

[0173] 第二开关元件的第二电极被电连接于第二电源,

[0174] 光发射元件的第二电极被电连接于第三电源,并且

[0175] 电容元件被配置于晶体管的栅电极和第一电极之间,

[0176] 用于驱动显示器件的方法包含:

[0177] 第一步导通第一和第二开关元件以输入视频信号到晶体管的栅电极,并固定晶体管的第一电极电位;

[0178] 第二步不导通第一和第二开关元件以使晶体管的栅电极处于浮置状态;

[0179] 第三步导通第三开关元件以提供对应于施加到晶体管栅电极电位的电流给发光元件来发射光;并且

[0180] 第四步不导通第三开关元件并停止提供电流给发光元件,

[0181] 其中在第三步,电容元件保持晶体管的栅极-源极电压以使晶体管的第一电极的电位的改变等于晶体管的栅电极的电位改变。

#### 附图说明

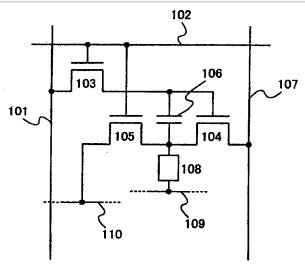

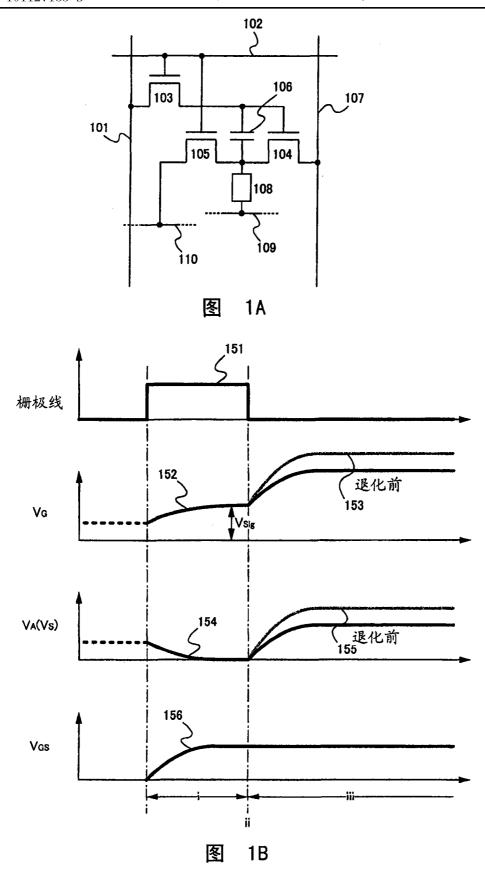

[0182] 图 1A 和 1B 是说明本发明的实施例和其工作的实施例的示意图;

[0183] 图  $2A \sim 2D$  是说明在通过传统结构形成单极 TFT 的情况下的工作示意图;

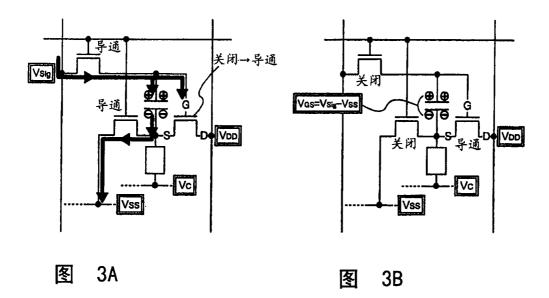

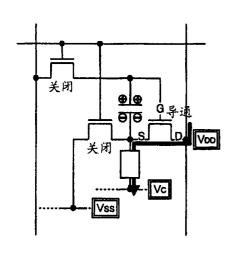

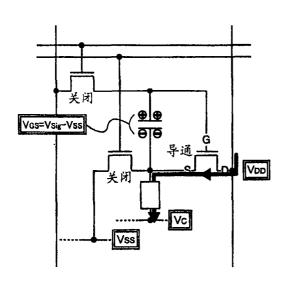

[0184] 图  $3A \sim 3C$  是说明根据图 1A 所示结构的电路的工作示意图;

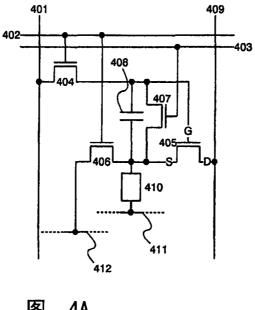

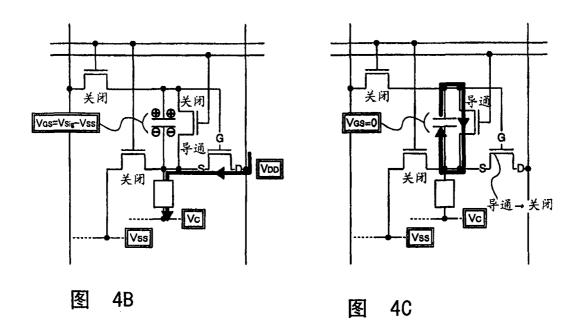

[0185] 图  $4A \sim 4C$  是说明本发明和工作的实施例的示意图;

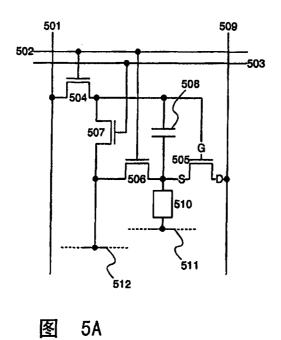

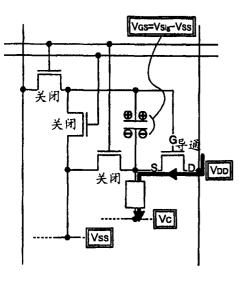

[0186] 图  $5A \sim 5C$  是说明本发明和工作的实施例的示意图;

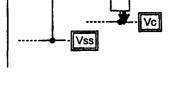

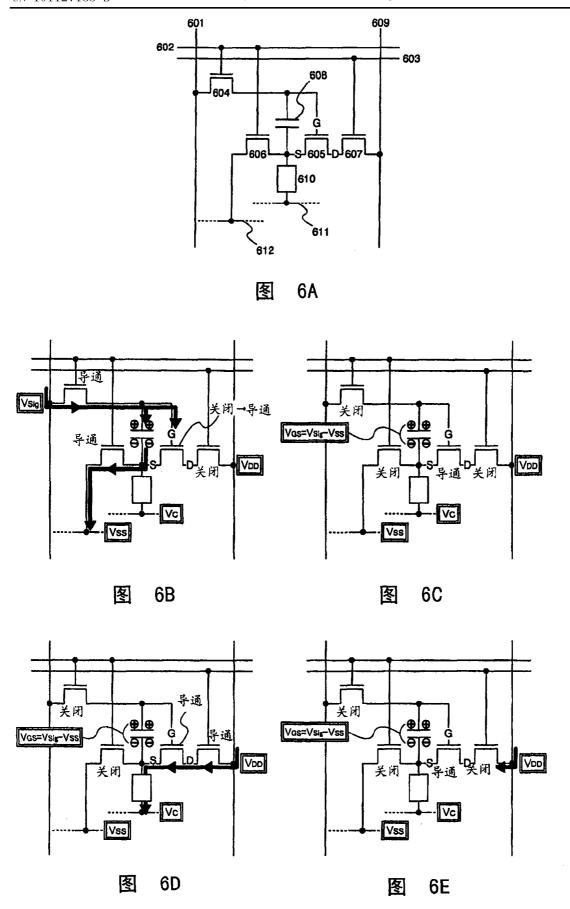

[0187] 图  $6A \sim 6E$  是说明本发明和工作的实施例的示意图;

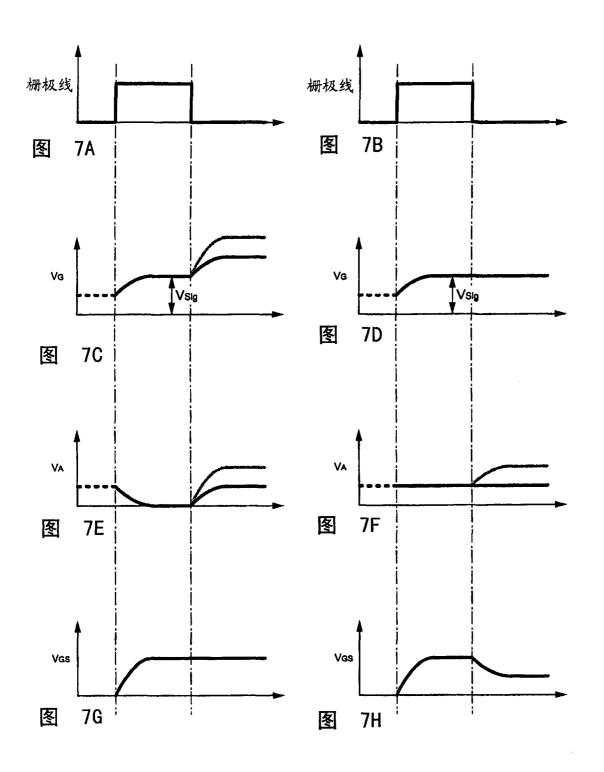

[0188] 图  $7A \sim 7H$  是对比本发明和传统实例在驱动 TFT 的栅电极和源极区周围电位变化的示意图:

[0189] 图 8 介绍由单极 TFT 构造的像素的一个实例的示意图;

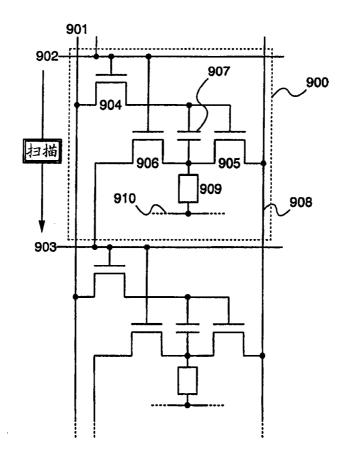

[0190] 图 9 是描述本发明的实施例的示意图;

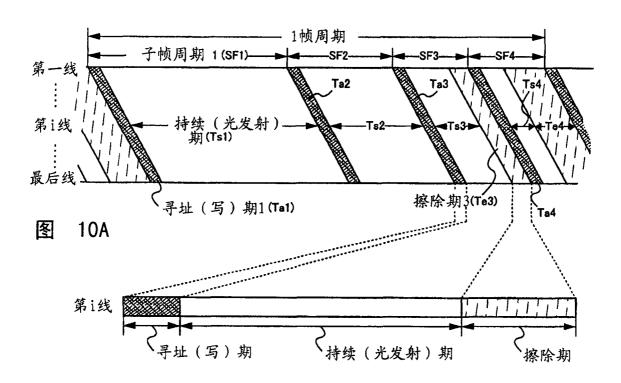

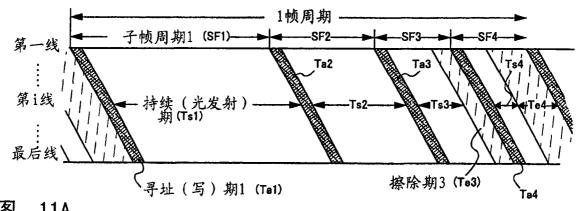

[0191] 图 10A 和 10B 是说明时间灰度等级系统的示意图:

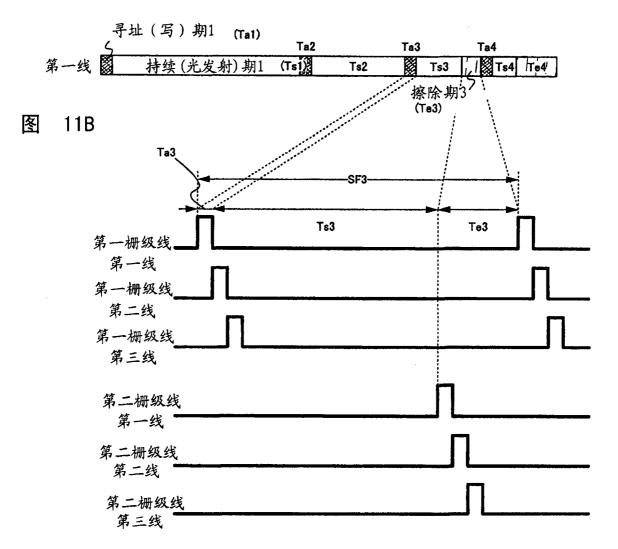

[0192] 图  $11A \sim 11C$  是说明时间灰度等级系统的示意图;

[0193] 图  $12A \sim 12D$  是说明本发明和工作的实施例的示意图;

[0194] 图  $13A \sim 13D$  是说明半导体器件制造工艺的示意图;

[0195] 图  $14A \sim 14C$  是说明半导体器件制造工艺的示意图;

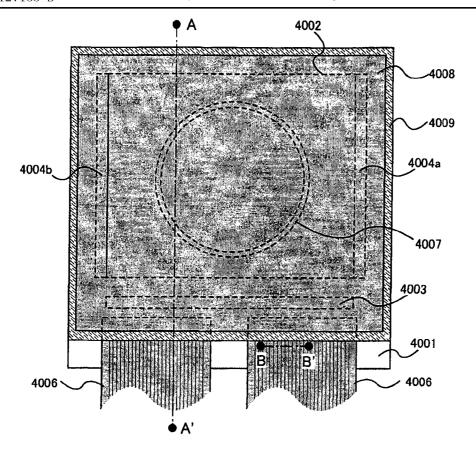

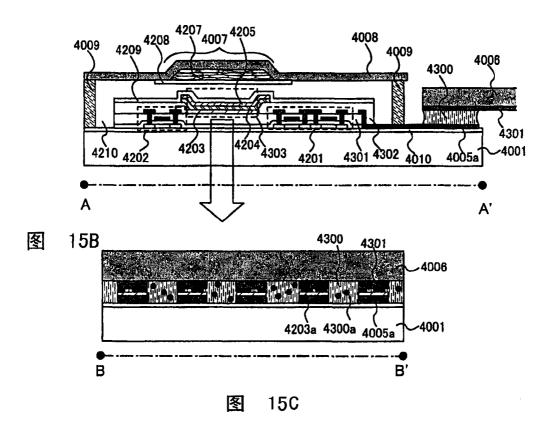

[0196] 图  $15A \sim 15C$  是半导体器件的俯视图和横截面图;

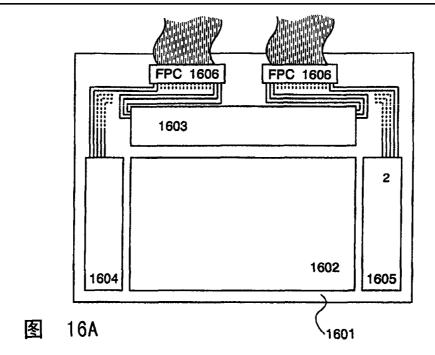

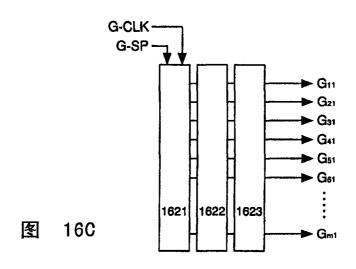

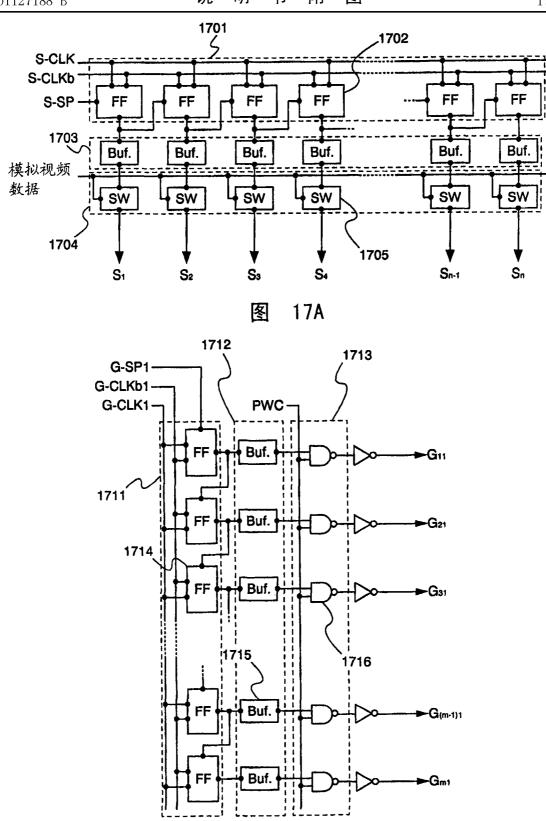

[0197] 图  $16A \sim 16C$  是描述用于利用模拟视频信号的显示器的半导体器件的结构的示意图;

[0198] 图 17A 和 17B 是描述如图  $16A \sim 16C$  所示器件中源极信号线驱动电路和栅极信号线驱动电路实例的示意图;

[0199] 图 18A 和 18B 是描述用于利用数字视频信号的显示器的半导体器件结构的示意图:

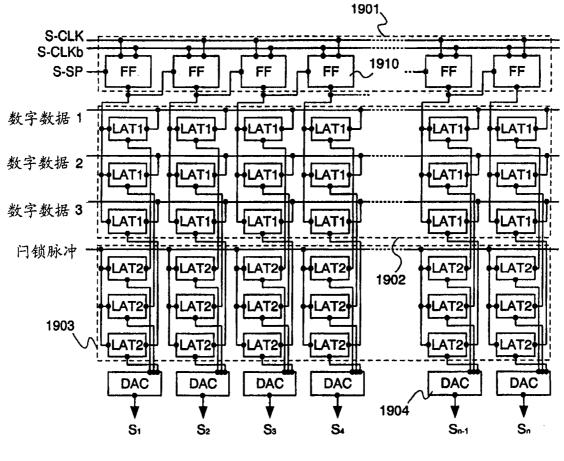

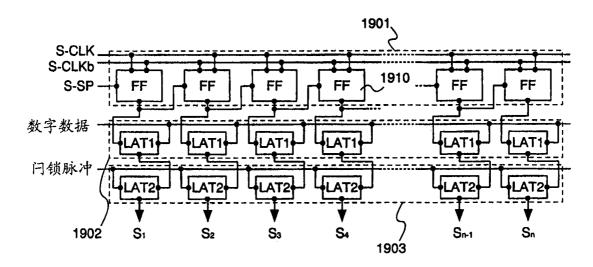

[0200] 图 19A 和 19B 是描述图 18A 和 18B 所示器件中的源极信号线驱动电路实例的示意图;

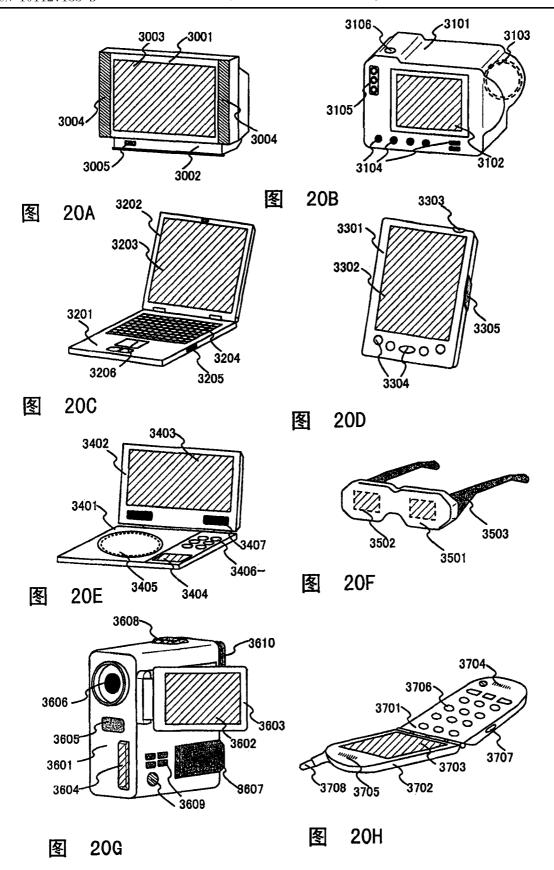

[0201] 图 20A ~ 20H 是描述可适用于本发明的电子器件实例的示意图;

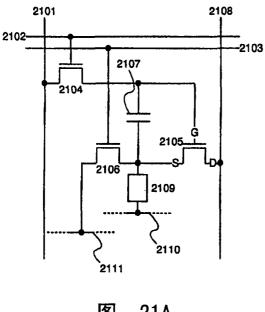

[0202] 图  $21A \sim 21C$  是说明本发明和工作的实施例的示意图;以及

[0203] 图 22 是描述本发明的像素结构的俯视图的示意图。

## 具体实施方式

[0204] [实施例 1]

[0205] 图 1A 表示本发明的一个实施例。本发明的像素具有源极信号线 101,栅极信号线 102,第一、第二和第三 TFT103~105,电容元件 106,电流供电线 107,EL 元件 108,以及电源线 109 和 110。TFT103 的栅电极被连接到栅极信号线 102,TFT103 的第一电极被连接到源极信号线 101,而 TFT103 的第二电极被连接到 TFT104 的栅电极。TFT104 的第一电极被连接到电流供电线 107,而 TFT104 的第二电极被连接到 TFT105 的第一电极和 EL 元件的第一电极。TFT105 的栅电极被连接到栅极信号线 102,而 TFT105 的第二电极被连接到电源线 110。EL 元件 108 的第二电极被连接到电源线 109。电容元件 106 被配置于 TFT104 的栅电极和第二电极之间,用来保持栅极。源极电压。

[0206] 现在,所有 TFT103  $\sim$  105 为 N- 沟道 TFT,并且当栅极 - 源极电压超过阈值时它们被开启。此外,在 EL 元件 108 中,第一电极是阳极,而第二电极为阴极。阳极电位设定为  $V_A$ ,而阴极电位即电源线 109 的电位设定为  $V_C$ 。此外,电流供电线 107 的电位设定为  $V_D$ ,电源线 110 的电位设定为  $V_S$ , 视频信号的电位设定为  $V_S$ ,

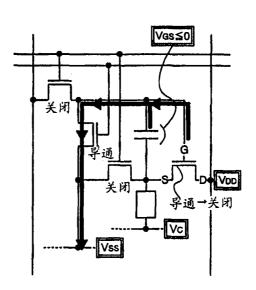

[0207] 电路的工作将用图 1A,1B 和 3A  $\sim$  3C 说明。此处,TFT104 的栅极 (G)、源极 (S),和漏极 (D) 如图 3A 所定义。

[0208] 在某些像素中选择栅极信号线 102 来开启 TFT103 和 105。如图 3A 所示,视频信号从源极信号线 101 被输入到 TFT104 的栅电极,并且电位变为  $V_{sig}$ 。同时,TFT105 导通,这样  $V_A = V_{ss}$ 。此时当设定  $V_{ss} \leq V_c$  时,在书写视频信号时电流不流经 EL 元件 108。但是,设定  $V_{ss} > V_c$ ,则电流可以流经 EL 元件 108。这里关键是  $V_A$  被固定在一固定电位。根据该工作,电容元件 106 的两个电极间的电压转变为  $(V_{sig}-V_{ss})$ 。然后,当栅极信号线 102 的选择期结束,并且 TFT103 和 105 关闭时,储存于电容元件 106 的电荷的迁移路径已不存在,以及 TFT104 的栅极 – 源极电压  $(V_{sig}-V_{ss})$  被保持。(图 3B)。

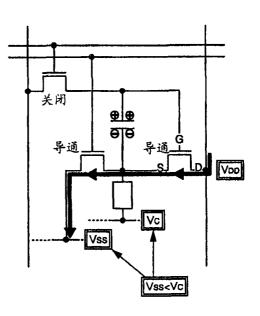

[0209] 此时,当( $V_{\rm sig}$ - $V_{\rm ss}$ )超过 TFT104 的阈值时,TFT104 开启,电流被启动从电流供电线流 107 经 EL 元件,并且启动光发射(图 3C),增加 TFT104 的源极电位。在这一时期,TFT104 的栅电极处于浮置状态,并且电容元件 106 保持 TFT104 的栅极-源极电压。因此,栅电极的电位随源极电位的上升而增加。在这一时期,在 TFT104 和 105 中的半导体层(在源极区

或漏极区)和栅电极间存在电容分量,但是电容元件106的电容值被设定为远远高该于电容分量,由此使TFT104源极电位的增加量几乎等于TFT104栅极电位的增加量。

[0210] 基于该工作,根据退化或不退化的 EL 元件的工作将在图 1B 中考虑。图 1B 图解示出 151 为栅极信号线 102 的电位,152 和 153 为 TFT104 的栅电极的电位  $V_{c}$ ,154 和 155 是 EL 元件 108 的阳极电位  $V_{a}$  即 TFT104 的源极电位,而 156 是 TFT104 的栅极 – 源极电压  $V_{cs}$ 。

[0211] 现在,在图 1B 所示由 i 表示的部分中,栅极信号线 102 被选定在高电位。因此视频信号被写在这部分,并且 TFT104 的栅极电位  $V_G$  升高。同时, TFT105 导通,因此 EL 元件 108 的阳极电位  $V_A$ ,即 TFT104 的源极电位变为等于  $V_{SS}$ 。结果 TFT104 的栅极 – 源极电压  $V_{CS}$  变大。此外,当在这部分中  $V_A = V_{SS} < V_C$  时,无论视频信号值  $V_{Sig}$  为多大,EL 元件 108 不发射光。

[0212] 在由 i i 表示的时刻,栅极信号线 102 的选定是低电位结束,并且 TFT103 和 105 被关闭。此时在电容元件 106 中保持  $V_{GS}=(V_{Sig}-V_A)$ 。

[0213] 随后,进入由 iii 表示的部分,并且光发射被启动。此时,当 TFT104 的栅极 – 源极电位  $V_{cs}$  超过阈值, TFT104 开启以传送漏极电流,发光元件 108 发射光。同时, TFT104 的源极电位也升高。此处如上所述, TFT104 的栅极电位处于浮置状态,因此该电位类似于在 TFT104 的源极电位上升而上升。

[0214] 此处,将考虑 EL 元件 108 已退化的情况。当 EL 元件 108 退化时,如上所述在传送一定值电流经过 EL 元件 108 时,阴极 – 阳极电压变大。结果  $V_A$  上升如 155 所表示。但是,在本发明中,  $V_G$  也由于  $V_A$  的上升而上升,结果表现出  $V_{GS}$  保持不变。

[0215] 另一方面,如图  $7A \sim 7H$  所示,在图 2B 所示传统结构情况下,当视频信号一旦被输入并且电位变为  $V_{\rm Sig}$  时,在此之后 TFT104的栅极电位不被改变。因此,当 EL 元件 207 退化且  $V_{\rm A}$  上升时, TFT204的栅极 – 源极电压变得比退化前小(图 7G 和 7H)。在这种状况下,即使 TFT204在饱和区工作,工作点的电流值也将被改变。因此,当 EL 元件 207 退化且电压 – 电流特性曲线被改变,流经 EL 元件 207 的电流变小导致光发射减小。

[0216] 如上所述,即使在 EL 元件退化时电流值也不被改变,由此本发明可消除 EL 元件退化的影响。

[0217] 此外,电源线的两个电位  $V_{ss}$  和  $V_{c}$  可被任意设定。因此,设定  $V_{ss} < V_{c}$ ,由此反向偏压可以容易地施加到 EL 元件。

[0218] 此外,TFT103和105仅起开关元件的功能是好的,并且因此极性不被限定。更特别地,即使所有构成像素的TFT被设定为单极型,也可以进行正常工作。在图1A中,TFTF103和105被设定为具有相同极性并且只被栅极信号线102控制。但是,使用彼此不同的第一和第二栅极信号线来控制各个TFT是可以的。在这种情况下,TFT103和105彼此可以具有不同的极性。但是,考虑到像素的数字孔径,引线数量尽可能地少是理想的。

[0219] 实施例 2

[0220] 根据图 1A 所示结构,用于通向像素部分的线路,需要五条:源极信号线、栅极信号线、电流供电线  $(V_{DD})$ 、电源线  $(V_{C})$  以及电源线  $(V_{SS})$ 。 在本实施例中,将描述用于引线的线路共享的结构,由此使得用于每个像素的引线的线路数量减少并获得高数字孔径。

[0221] 图 9 描述本实施例的结构。与实施例 1 所不同点仅仅在于 TFT906 的第二电极被连接到电源线  $(V_{ss})$ ,但在本实施例中它被连接到下一行像素中的栅极信号线。假定由虚线

框 900 表示的像素处于第 I 行, TFT906 的第二电极被连接到第 i+1 行的栅极信号线。

[0222] 作为选择栅极信号线的脉冲条件,TFT904的栅极 – 源电压足够大地超过在高电位的阈值是可以接受的。更特别地,电位足够大于阈值达到视频信号  $V_{\rm sig}$  的最大值是可以接受的。同时,电位以低电位安全地关闭 TFT904 为好。因此,处于低电位的电位被设定为等于栅极信号线的  $V_{\rm ss}$ 。

[0223] 当第 i 栅极信号线被选择在高电位并且 TFT904 和 906 被开启时,第 i+1 栅极信号线却不被选择。更特别地,它处于低电位并且电位为  $V_{ss}$ 。因此,与本实施例相似,EL 元件的阳极电位  $V_A$  通过 TFT906 变得等于  $V_{ss}$  因此,当用于引线的线路与本实施例一致被共享,可得到与实施例 1 相同的效果。

[0224] 此外,连接 TFT906 的第二电极的位置不限定于第 i+1 栅极信号线,此时它是一个能够施加固定电位  $V_{ss}$  的位置,同时第 i 栅极信号线被选择在高电位,且 TFT906 导通。例如,它可以是第 i-1 栅极信号线或此外的其它线。当邻近行中的信号线被共享,信号线的脉冲彼此不重叠是理想的。

[0225] 此外,如实施例 1 所描述的, TFT904 和 906 仅起开关元件的功能为好。因此极性不被限定,极性不限于被如图 9 所示的单个栅极信号线 902 所控制。

[0226] 实施例3

[0227] 驱动 TFT 的栅极 - 源极电压被控制,和流经 EL 元件的电流值被用于显示的模拟量控制被称为模拟灰度等级系统。同时,提出数字灰度等级系统,其中 EL 元件只通过两种状态驱动 - 零发光或百分之百发光。在该系统中,只有两个灰度等级,黑和白可被显示,但是它具有几乎不受限于 TFT 特性变化的优点。为了想通过数字灰度等级系统获得多级灰度等级,采用与时间灰度等级系统相结合的驱动方法。时间灰度等级系统是一种通过元件长时间或短时间发光的时间长度表示灰度等级的方法。

[0228] 当数字灰度等级系统与时间灰度等级系统结合时,如图 10A 所示一个帧周期被分成几个子帧周期。每个子帧周期具有寻址(写)期,持续(光发射)期和擦除期,如图 10B 所示。灰度等级被表示出来,其中对应于用于显示的比特数的子帧周期被排列,其中持续(光发射)期的长度在每个子帧周期被设定为 2<sup>(n-1)</sup> : 2<sup>(n-2)</sup> : . . . . : 2 : 1, EL 元件在每个持续(光发射)期被选择发光或不发光,并且当 EL 元件发光时在总时间长度上的不同被利用。当发光时间长则亮度高,而发光时间短则亮度低。此外,图 10A 和 10B 描述了四比特灰度等级的实例,其中一个帧周期被分成四个子帧周期,且 2<sup>4</sup> = 16 灰度等级电平可通过持续(光发射)期的组合表示。此外,灰度等级可以在不特别设定持续期的长度比为二的幂次比时被表示出来。另外,某个子帧周期可以被进一步分割。

[0229] 当利用时间灰度等级系统获得多级灰度等级时,较低比特的持续(光发射)期的长度变得更短。因此后续的寻址期必须紧随持续(光发射)期完成后开始时,与不同子帧周期的寻址(写)期重叠的周期产生。在此情况下,被输入到某个像素的视频信号同时也被输入到不同像素,因此不能进行正常的显示。擦除期被配置用于解决该问题。如图 108 所示,它被配置于 Ts3 和 Ts4 后以便两个不同的寻址(写)期彼此不重叠。相应地,在持续(光发射)期足够长并且两个不同寻址(写)期彼此将不会重叠的 SF1 和 SF2 中不配置擦除期。

[0230] 这样,为了通过将数字灰度等级系统和时间灰度等级系统相结合的方法驱动 EL

元件,可能出现增加光发射被强制停止和配置擦除期的工作的情况。

[0231] 图 4A 描述了增加一个第二栅极信号线 403 和一个擦除 TFT407 到具有实施例 1 所示结构的像素,以响应将数字灰度等级系统和时间灰度等级系统相结合的驱动方法的实例。擦除 TFT407 的栅电极被连接到第二栅极信号线 403,擦除 TFT407 的第一电极被连接到 TFT405 的栅电极和电容元件 408 的第一电极,而擦除 TFT407 的第二电极被连接到 TFT405 的第二电极和电容元件 408 的第二电极。

[0232] 第一栅极信号线 402 被选择以输入视频信号的工作与实施例 1 所示相同,因此此处将其省略。此外,视频信号输入过程中,第二栅极信号线处于低电平且擦除 TFT407 是关闭的。此时  $V_{sig}$  既产生确实开启 TFT405 的电位也产生关闭 TFT405 的电位。

[0233] 此处,从持续(光发射)期到擦除期的工作将用图  $4A \sim 4C$  和图  $11A \sim 11C$  描述。图 11A 与图 10A 所示相同。如图 11B 所示,一个帧周期有四个子帧周期。在具有短持续(光发射)期的子帧周期 SF3 和 SF4 中,他们分别具有擦除期 Te3 和 Te4。此处,在 SF3 中的工作将被举例说明。

[0234] 视频信号输入完成后,对应于 TFT405 的栅极 – 源极电压  $V_{cs}$  的电流传送经 EL 元件 410 以发射光,如图 10B 所示。然后,当计时到达持续(光发射)期的完成时,脉冲被输入到 要处于高电位的第二栅极信号线 403,并且擦除 TFT407 被开启以将 TFT405 的栅极 – 源极电压  $V_{cs}$  设定为零,如图 4C 所示。相应地,TFT405 被关闭,通入 EL 元件的电流被截止,EL 元件 410 被强制停止光发射。

[0235] 工作是如图 11C 所示时间表。擦除期 Te3 是持续(光发射)期 Ts3 之后的周期,一个脉冲被输入到第二栅极信号线 403, EL 元件停止光发射,然后一个脉冲再被输入到第一栅极信号线 402 以开始输入下一个视频信号。

[0236] 此外,在图 4A 所示的结构中,TFT406 的第二电极被连接到电源线 412,但是电源线 412 可被如实施例 2 中所示的邻近行中的栅极信号线所代替。此外,在本实施例中,第二栅极信号线 403 被配置用于控制擦除 TFT407,并且因此 TFT406 的第二电极可被连接到第二栅极信号线 403。

[0237] 虽然 TFT404 和 406 被栅极信号线 402 控制,但可增加一条新的栅极信号线。在这种情况下, TFT404 和 406 可被栅极信号线 402 和新增栅极信号线分别控制。

[0238] 实施例 4

[0239] 图 5A 描述了在不同于实施例 3 中示出的位置配置擦除 TFT 的实施例。在本实施例中,一个擦除 TFT507 被配置于通向电容元件 508 的第一电极的 TFT505 的栅电极和电源线 512 之间。

[0240] 类似实施例 3,有关从视频信号输入到光发射,通过将数字灰度等级系统和时间灰度等级系统结合的方法实施驱动方法是可以接受的。因此,此处省略该描述,而擦除期的工作将被描述。

[0241] 当计时到达持续(光发射)期的结束时,脉冲被输入到第二栅极信号线 503 达到高电平,擦除 TFT507 被开启,并且 TFT505 的栅电极的电位转变为  $V_{ss}$ ,如图 5C 所示。更特别地,在擦除期,TFT505 的栅极 – 源极电压  $V_{cs}$  设定在阈值以下为好。

[0242] TFT505 的源极电位处于至少等于或大于  $V_{ss}$  的电位。因此擦除 TFT507 的工作允许 TFT505 的栅极 – 源极电压  $V_{cs}$  为  $V_{cs}$   $\leq$  0,并且 TFT505 被关闭。相应地,擦除期是 EL 元

件 510 停止光发射的周期。一个脉冲被再次输入到第一栅极信号线 502,并且下一个视频信号再开始被输入。

[0243] 此外,在图 5A 所示的结构中,TFT506 的第二电极被连接到电源线 512,但电源线 512 可被如实施例 2 所示的邻近行中的栅极信号线所取代。另外,在本实施例中,第二栅极信号线 503 被配置用于控制擦除 TFT507。因此,TFT506 的第二电极可被连接到第二栅极信号线 503。

[0244] 虽然 TFT504 和 506 被栅极信号线 502 控制,但是可增加一条新的栅极信号线。在这种情况下,TFT504 和 506 可被栅极信号线 402 和新增栅极信号线分别控制。

[0245] 实施例 5

[0246] 图 6A 描述了在不同于实施例 3 和 4 所示位置配置擦除 TFT 的实例。在本实施例中,擦除 TFT607 被配置于 TFT605 的第一电极和电流供电线之间。

[0247] 电路的工作将被描述。第一栅极信号线 602 被选定在高电平,TFT604 被开启,并且视频信号被从源极信号线 601 输入到像素。同时,TFT606 也被开启使 EL 元件 610 的阳极电位  $V_A$  等于  $V_{ss}$ 。此时,当设定  $V_{ss} \leq V_c$ ,在写视频信号时电流不被传送流经 EL 元件 610,因此 TFT607 处于导通或关闭为好。

[0248] 当视频信号输入完成并且第一栅极信号线 602 不被选择时,TFT605 的栅电极处于浮置状态并且所储存电荷的迁移路径在电容元件 608 中受阻塞。因此,栅极 – 源极电压  $V_{cs}$  在电容元件 608 中被保持。

[0249] 随后,第二栅极信号线 603 被选定在高电平并且 TFT607 被开启,由此电流如图 6D 所示被传送, EL 元件 610 的阳极电位  $V_A$  上升,产生与阴极电位  $V_C$  的电位差,电流被传送以发射光。此外, TFT607 从输入视频信号状态被开启是可以接受的。在此情况下,在第一栅极信号线 602 转变为不被选择的时刻,电流通过 TFT607 和 605 被提供给 EL 元件 610,并且 EL 元件 610 的阳极电位  $V_A$  上升,产生与阴极电位  $V_C$  的电位差,传送电流以发射光。

[0250] 当计时到达持续(光发射)期的结束时,第二栅极信号线603不被选定在低电平,TFT607被关闭,并且从电流供电线609到EL元件610的电流路径被阻塞。因此,电流不流经EL元件610,光发射停止。之后,擦除期是一个脉冲被再次输入到第一栅极信号线602,并且下一个视频信号再开始被输入的周期。

[0251] 此外,在 TFT605 的第一电极和 EL 元件 610 的阳极间配置 TFT607 为好。更特别地,TFT607 被配置于电流供电线 609 和 EL 元件 610 之间的电流路径中,并且在擦除期中提供给 EL 元件 610 的电流可能被切断是可以接受的。

[0252] 虽然 TFT604 和 606 被栅极信号线 602 控制,但是可增加一条新的栅极信号线。在这种情况下,TFT604 和 606 可被栅极信号线 602 和新增栅极信号线分别控制。

[0253] 实施例 6

[0254] 在实施例  $3 \sim 5$  中,增加 TFT 来配置擦除期的实例已被描述,但在本实施例中,将描述不增加擦除 TFT 而进行相同工作的实例。

[0255] 图 21A 描述该结构。该结构几乎类似于实施例 1 所示结构,但不同在于 TFT2104 和 2106 分别被独立的栅极信号线 2102 和 2103 控制。

[0256] 如图 218 所示,在持续(光发射)期,电容元件 2107 固定 TFT2105 的栅极-源极电压,并且与之相伴的电流流经 EL 元件 2109 以发射光。

[0257] 随后,进入擦除期,一个脉冲信号被输入到第二栅极信号线 2103 以开启 TFT2106。此时,被连接到 TFT2106 的第二电极的电源线 2111 的电位被设定为低于 EL 元件 2109 的阴极电位,即电源线 2110 的电位,由此电流不被传送流经 EL 元件 2109。相应地,此时的电流如图 21C 所示被传送。

[0258] 此外,在邻近行的栅极信号线可用作电源线 2111,如其它实施例中所描述的。

[0259] 实施例 7

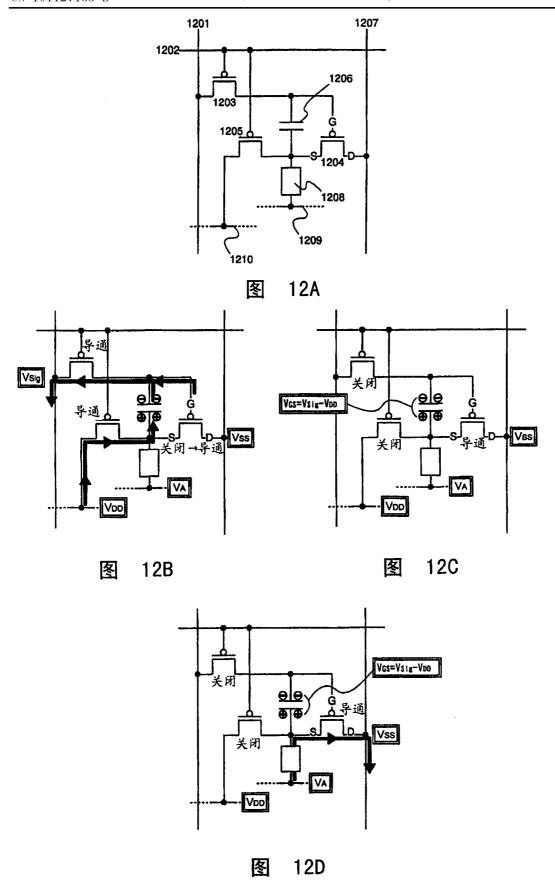

[0260] N-沟道型 TFT 被用作向 EL 元件提供电流的 TFT。但是,本发明可通过用 P-沟道型 TFT 作为驱动 TFT 来完成。图 12A 描述了范例结构。

[0261] 该电路结构与图 1A 中所示的使用 N- 沟道型 TFT 的结构相同。但是,不同点在于 EL 元件 1208 的结构是反向的,被连接于 TFT1204 的第二电极的一侧是阴极,而被连接于电源先 1209 的另一侧是阳极,并且电流供电线 1207 的电位为  $V_{ss}$ ,电源线 1209 的电位为  $V_{h}$ ,而电源线 1210 的电位为  $V_{h}$ ,此处,  $V_{ss} < V_{h}$ ,且  $V_{h} < V_{h}$ 。

[0262] 电路的工作将用图 12B ~ 12D 描述。此外, TFT 的极性为 P- 沟道型, 输入一个低电平到栅电极以开启 TFT, 而输入高电平用以关闭 TFT。

[0263] 在某一行,栅极信号线 1202 被选定在低电平,并且 TFT1203 和 1205 被开启。如图 128 所示,视频信号从源极信号线 1201 被输入到 TFT1204 的栅电极,并且电位变为  $V_{\rm Sig}$ 。同时, TFT1205 是导通的,并且因此 EL 元件 1208 的阴极电位  $V_{\rm C}$  变为  $V_{\rm C} = V_{\rm DD}$ 。此时,当设定  $V_{\rm A} \leq V_{\rm DD}$  时,在写视频信号时,电流不被传送流经 EL 元件 1208。根据该工作,电容元件 1206 的两个电极间的电压,即 TFT1204 的栅极 – 源极电压变为( $(V_{\rm Sig} - V_{\rm DD})$ 。然后,当栅极信号线 1202 的选择期结束处于高电平并且 TFT1203 和 1205 被关闭时,电容元件 1206 中储存的电荷的迁移路径消失,并且 TFT1204 的栅极 – 源极电压( $V_{\rm Sig} - V_{\rm DD}$ )被保持(图 12C)。

[0264] 此处,当  $(V_{\rm sig}-V_{\rm DD})$  低于 TFT1204 的阈值电压时,TFT1204 被开启,电流被传送流经电源线 1209、EL 元件 1208 和电流供电线 1207 以开始光发射(图 12D),并且 TFT1204 的源极电位下降。此时,TFT1204 的栅电极处于浮置状态,而电容元件 1206 保持 TFT1204 的栅极 - 源极电压。因此,栅极电位也随源极电位的减小而下降。

[0265] 在图 12A中,所有构成像素的 TFT 使用 P-沟道型 TFT。但是,TFT1203 和 1205 只起开关元件功能作用为好,如在其它实施例中所描述的。因此,极性不被限定。此外,TFT1203 和 1205 不必只被栅极信号线 1202 驱动。各独立的 TFT 被另一个栅极信号线控制的结构也是可以接受的。

[0266] 实例

[0267] 此后,本发明的实例将被描述。

[0268] [实例 1]

[0269] 在该实例中,将描述一个光发射器件的结构,其中采用模拟视频信号作为显示用视频信号。图 16A 描述了光发射器件的范例结构。器件具有像素部分 1602,在此多个像素在基片 1601 上按矩阵形排列,而且在像素部分周围它具有一个源极信号线驱动电路 1603 和第一和第二栅极信号线驱动电路 1604 和 1605。在图 16A 中使用两个栅极信号线驱动电路。但是,当在如图 1A 所示的像素中使用一条栅极信号线时,则栅极信号线被从两侧同时控制。当在图 4A 和 5A 所示像素中使用两条栅极信号线时,各独立栅极信号线驱动电路控制各自的栅极信号线。

[0270] 被输入到源极信号线驱动电路 1603 和第一及第二栅极信号驱动电路 1604 和 1605 的信号通过一个柔性的印刷电路 (FPC) 1606 被从外侧馈送。

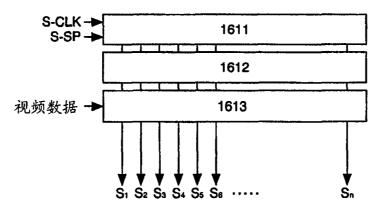

[0271] 图 16B 描述源极信号线驱动电路的范例结构。这是用于使用模拟视频信号作显示视频信号的源极信号线驱动电路,它具有一个移位寄存器 1611、一个缓冲器 1612,以及一个取样电路 1613。虽然没有特地指出,但必要时可增加一个电平移位器。

[0272] 源极信号线驱动电路的工作将被描述。图 17A 表示更详细的结构,因此参考附图。[0273] 移位寄存器 1701 由多个双稳态多谐振荡电路 (FF) 1702 形成,时钟信号 (S-CLK)、反时钟信号 (S-CLKb),以及启动脉冲 (S-SP) 被输入到该电路。响应这些信号的计时,取样脉冲被按顺序地输出。

[0274] 从移位寄存器 1701 输出的取样脉冲经过缓冲器 1703 并被放大,然后被输入到取样电路。取样电路 1704 由多个取样开关 (SW) 1705 形成,取样电路根据输入的取样脉冲计时取样某个列的视频信号。更特别地,当取样脉冲被输入到取样开关时,取样开关 1705 开启。此时视频信号保持的电位被通过取样开关输出到各独立源极信号线。

[0275] 随后,描述栅极信号线驱动电路的工作。图 17B 描述了图 16C 中所示的第一和第二栅极信号线驱动电路 1604 和 1605 的更详细的范例结构。第一栅极信号线驱动电路具有一个移位寄存器电路 1711,和一个缓冲器 1712,它响应时钟信号 (G-CLK1)、反时钟信号 (G-CLKb1),以及启动脉冲 (G-SP1) 被驱动。第二栅极信号线驱动电路 1605 也可同样被构造。

[0276] 从移位寄存器到缓冲器的工作与源极信号线驱动电路相同。被缓冲器放大的取样脉冲各自选择独立的栅极信号线。第一栅极信号线驱动电路按顺序选择第一栅极信号线  $G_{11}$ 、 $G_{21}$ 、...  $G_{m1}$ ,而第二栅极信号线驱动电路按顺序选择第二栅极信号线  $G_{12}$ 、 $G_{22}$ 、...  $G_{m2}$ 。第三栅极信号线驱动电路,图中未示出,也像第一和第二栅极信号线驱动电路一样,按顺序选择第三栅极信号线  $G_{13}$ 、 $G_{23}$ 、...  $G_{m3}$ 。在被选择行中,视频信号被写在像素中以根据实施例中所描述的程序发射光。

[0277] 此外,作为移位寄存器的实例,此处显示了由多个 D 双稳态多谐振荡电路形成的移位寄存器。但是通过一个解码器选择信号线的结构也是可以接受的。

[0278] [实例 2]

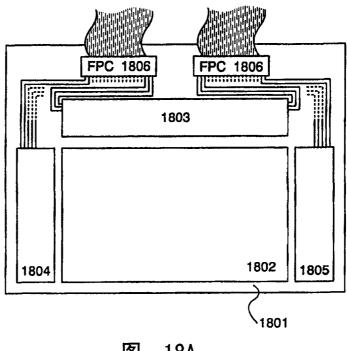

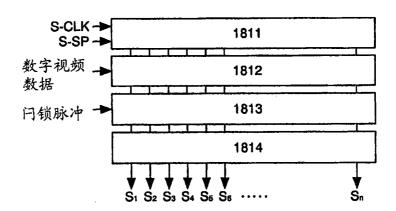

[0279] 在本实例中,将描述其中使用数字视频信号作为显示用视频信号的光发射器件的结构。图 18A 描述了光发射器件的范例结构。该器件具有像素部分 1802,在此多个像素在基片 1801 上按矩阵形排列,而且在像素部分周围它具有一个源极信号线驱动电路 1803 和第一和第二栅极信号线驱动电路 1804 和 1805。在图 18A 中使用两个栅极信号线驱动电路。但是,当在如图 1A 所示的像素中使用一条栅极信号线时,栅极信号线被从两侧同时控制。当在图 4A 和 5A 所示像素中使用两条栅极信号线时,独立的栅极信号线驱动电路控制各自的栅极信号线。

[0280] 被输入到源极信号线驱动电路 1803 以及第一和第二栅极信号线驱动电路 1804 和 1805 的信号通过一个柔性的印刷电路 (FPC) 1806 被从外侧馈送。

[0281] 图 18B 描述源极信号线驱动电路的范例结构。这是用于使用数字视频信号作为显示用视频信号的源极信号线驱动电路,它具有一个移位寄存器 1811、一个第一闩锁电路 1812、一个第二闩锁电路 1813,以及一个 D/A 转换器电路 1814。虽然图中没有特地示出,但

必要时可增加一个电平移位器。

[0282] 第一和第二栅极信号线驱动电路 1804 和 1805 是实例 1 中所示结构为好,因此此处省略图示和描述。

[0283] 源极信号线驱动电路的工作将被描述。图 19A 示出更详细的结构,因此参考附图。

[0284] 移位寄存器 1901 由多个双稳态多谐振荡电路 (FF) 1910 形成,时钟信号 (S-CLK)、反时钟信号 (S-CLKb),以及启动脉冲 (S-SP) 被输入到该电路。响应这些信号的计时,取样脉冲被按顺序输出。

[0285] 从移位寄存器 1901 输出的取样脉冲被输入到第一闩锁电路 1902。数字视频信号被输入到第一闩锁电路 1902。响应输入取样脉冲的计时,数字视频信号被保留在每一阶段。此处,数字视频信号按三比特被输入。在每个比特的视频信号被保留在单独的第一闩锁电路中。此处,三个第一闩锁电路由一个取样脉冲平行操作。

[0286] 当第一闩锁电路 1902 完成将数字视频信号保留直到最后阶段时,闩锁脉冲在水平回扫期被输入到第二闩锁电路 1903,并且保留在第一闩锁电路 1902 中的数字视频信号立即被传输到第二闩锁电路 1903。之后,保留在第二闩锁电路 1903 中的一行数字视频信号同时被输入到 D/A 转换器电路 1904。

[0287] 当保留在第二闩锁电路 1903 的数字视频信号被输入到 D/A 转换器电路 1904 的同时,移位寄存器 1901 再次输出取样脉冲。随之重复该操作以处理一个帧的视频信号。

[0288] D/A 转换器电路 1904 将输入的数字视频信号从数字转换为模拟信号,并输出到源极信号线作为具有模拟电压的视频信号。

[0289] 上述工作在一个水平周期的所有阶段进行。因此视频信号被输出到全部源极信号线。

[0290] 此外,如实例 1 所述,使用解码器取代移位寄存器来选择信号线的结构也是可接受的。

[0291] 「实例 3]

[0292] 在实例 2 中,数字视频信号通过 D/A 转换器电路被从数字转换到模拟信号,并且被写入像素中。本发明的半导体器件也可通过时间灰度等级系统表示灰度等级。在此情况下,不需要 D/A 转换器电路,如图 19B 所示,并且通过由 EL 元件长时间或短时间发射光的时间长度决定的表达式控制灰度等级。因此,每个比特视频信号不需进行平行处理。因此,第一和第二闩锁电路以一比特为好。此时,每个比特的数字视频信号被依次输入,按顺序保存在闩锁电路中并被写入像素中。当然,必要比特数的闩锁电路平行排列是可以接受的。

[0293] 实例 4

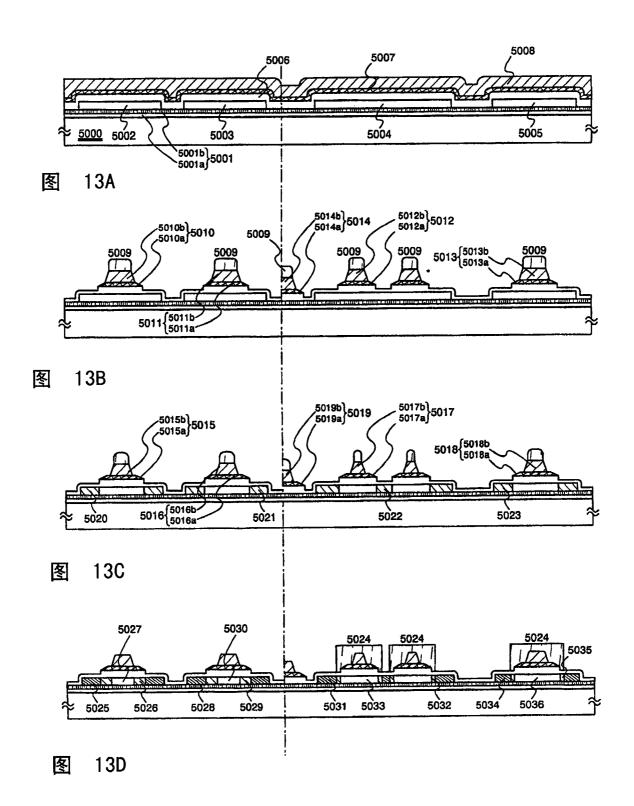

[0294] 在本说明书中,一个其上具有驱动器电路、具有用于开关的 TFT 和用于驱动的 TFT 的像素部分的基片被形成,为方便起见,该基片被称为有源矩阵基片。在本实例中,通过使用单极 TFT 制造的有源基片将参考图 13A ~ 14C 被描述。

[0295] 在其表面上形成绝缘膜的石英基片、硅基片、金属基片或不锈基片被用作基片 5000。此外,具有热阻的塑料基片,它可承受本制造工艺中的处理温度,可被使用。在本实例中,由玻璃诸如钡硼硅酸盐玻璃或铝硼硅酸盐玻璃制成的基片 5000 被使用。

[0296] 其次,在基片 5000 上形成由绝缘膜诸如氧化硅膜、氮化硅膜或氮氧化硅膜制成的基底膜 5001。在本实例中,一双层结构被用于基底膜 5001。然而绝缘膜的单层结构或其中

两层或多层绝缘膜叠层的结构也可以使用。

[0297] 在本实例中,作为基底膜 5001 的第一层,厚度为  $10 \text{nm} \sim 200 \text{nm}$  (优选  $50 \text{nm} \sim 100 \text{nm}$ ) 的氦氧化硅膜 5001 a 通过使用  $\text{SiH}_4$ 、 $\text{NH}_3$  和  $\text{N}_2\text{O}$  作反应气体的等离子体 CVD 法被形成。在本实例中,厚度 50 nm 的氦氧化硅膜 5001 a 被形成。其次,作为基底膜 5001 的第二层,厚度为  $50 \text{nm} \sim 200 \text{nm}$  (优选  $100 \text{nm} \sim 150 \text{nm}$ ) 的氦氧化硅膜 5001 b 通过使用  $\text{SiH}_4$  和  $\text{N}_2\text{O}$  作反应气体的等离子体 CVD 法被形成。在本实例中,厚度 100 nm 的氦氧化硅膜 5001 b 被形成。[0298] 顺序地,在基底膜 5001 L 形成半导体层  $5002 \sim 5005$ 。半导体层  $5002 \sim 5005$  形成如下。即厚度为  $25 \text{nm} \sim 80 \text{nm}$  (优选  $30 \text{nm} \sim 60 \text{nm}$ ) 的半导体膜通过已知方法(如溅射法、LPCVD 法或等离子体 CVD 法)形成。其次,半导体膜通过已知结晶化法(如激光结晶化法、使用 RTA 或退火炉的热结晶化法、使用促进结晶化的金属元素的热结晶化法等)被结晶化。然后,所得结晶半导体膜被作成预定形状图案以形成半导体层  $5002 \sim 5005$ 。注意无定形半导体膜、微晶半导体膜、结晶半导体膜、具有无定形结构的化合物半导体膜如非晶硅锗膜等可被用作半导体膜、

[0299] 在本实例中,通过等离子体 CVD 法形成厚度 55nm 的非晶硅膜。含有镍的溶液被吸附在非晶硅膜上,并且在 500℃进行 1 小时的脱水处理,然后于 550℃进行 4 小时热结晶化以形成结晶硅膜。之后,使用光刻技术的图案加工工艺被实施以形成半导体层 5002~5005。

[0300] 注意, 当通过激光结晶化法形成结晶半导体膜时, 优选使用进行连续振荡或脉冲振荡的气体或固体激光器。准分子激光器、YAG 激光器、YVO<sub>4</sub> 激光器、YLF 激光器、YA1O<sub>3</sub> 激光器、玻璃激光器、红宝石激光器、Ti:蓝宝石激光器等可被用作前者气体激光器。此外, 使用晶体如 YAG、YVO<sub>4</sub>、YLF 或 YA1O<sub>3</sub> 的激光器, 其中添加 Cr、Nd、Er、Ho、Ce、Co、Ti 或 Tm, 可用作后者固体激光器。激光器的基波根据掺杂材料而变化, 并且具有 1 μ m 领域的基波的激光被得到。通过使用非线性光学元件可获得基波的谐波。注意, 为了在无定形半导体膜的结晶化过程中获得具有大晶粒尺寸的晶体, 优先使用能够进行连续振荡的固体激光器, 并且采用基波的二次到四次谐波。典型地, 采用 Nd: YVO<sub>4</sub> 激光器(1064nm 基波)的二次谐波(532nm)和三次谐波(355nm)。

[0301] 并且从具有 10W 功率输出的连续振荡  $YVO_4$  激光器发射的激光通过非线性光学元件被转换成谐波。此外,有一种将一个  $YVO_4$  晶体和一个非线性光学元件放置在一个谐振器并发射谐波的方法。优选地,通过光学系统和辐照被处理物体在辐照表面上形成具有矩形或椭圆形状的激光。此时,要求具有约  $0.01MW/cm^2 \sim 100MW/cm^2$  (优选  $0.1MW/cm^2 \sim 100MW/cm^2$ ) 的能量密度。半导体膜相对于激光以约  $10cm/s \sim 2000cm/s$  的速度被移动来被激光辐照。

[0302] 并且当上述激光器被使用时,优选从激光振荡器发射的激光束通过光学系统被线性聚光并辐照到半导体膜。结晶化条件被适当设定。当使用准分子激光器时,优选脉冲振荡频率设定为 300Hz,和激光能量密度设定为  $100 \text{mJ/cm}^2 \sim 700 \text{mJ/cm}^2$ (典型地  $200 \text{mJ/cm}^2 \sim 300 \text{mJ/cm}^2$ )。此外,当使用 YAG 激光器时,优选使用二次谐波,脉冲振荡频率被设定为到  $1 \text{Hz} \sim 300 \text{Hz}$ ,和激光能量密度设定为  $300 \text{mJ/cm}^2 \sim 1000 \text{mJ/cm}^2$ (典型地  $350 \text{mJ/cm}^2 \sim 500 \text{mJ/cm}^2$ )。宽度在  $100 \, \mu \text{m} \sim 1000 \, \mu \text{m}$ (优选  $400 \, \mu \text{m}$ )的线性聚光的激光束被辐照扫过基片整个表面。此时,关于线性激光束的重叠比率可被设定为  $50\% \sim 98\%$ 。

[0303] 但是,在本实例中,非晶硅膜被使用促进结晶化的金属元素结晶化,以至金属元素保留在结晶硅膜中。因此,在结晶硅膜上形成厚 50nm~100nm的非晶硅膜,进行热处理(使用 RTA 法或退火炉热处理)使金属元素扩散进入非晶硅膜,并且热处理后通过腐蚀去除非晶硅膜。结果,包含在结晶硅膜中的金属元素可被减少或去除。

[0304] 注意,形成半导体层  $5002 \sim 5005$  后,为了控制 TFT 的阈值可进行少量杂质元素 (硼或磷)添加。

[0305] 其次,覆盖半导体层  $5002 \sim 5005$  的栅极绝缘膜 5006 被形成。栅极绝缘膜 5006 通过等离子体 CVD 法或溅射法由包含硅的膜厚  $40 \text{nm} \sim 150 \text{nm}$  的绝缘膜形成。在本实例中,通过等离子体 CVD 法形成厚 115 nm 的氦氧化硅膜作为栅极绝缘膜 5006。当然,栅极绝缘膜 不限于氦氧化硅膜。另一种包含硅的绝缘膜可被用作单层或叠层结构。

[0306] 注意,当氧化硅膜被用作栅极绝缘膜 5006 时,等离子体 CVD 法被采用, TEOS(四乙基正硅酸脂)和  $0_2$  被混合,反应压力被设定为 40Pa,基片温度被设定为 300  $\mathbb{C}$   $\sim$  400  $\mathbb{C}$  。然后,在高频 (13.56MHz) 功率密度 0.5W/cm²  $\sim$  0.8W/cm² 下可发生放电形成氧化硅膜。之后,当对通过上述步骤形成的氧化硅膜在 400  $\mathbb{C}$   $\sim$  500  $\mathbb{C}$  下进行热退火时,作为栅极绝缘膜 5006 可获得优选性能。

[0307] 其次,具有  $20 \text{nm} \sim 100 \text{nm}$  膜厚的第一导电膜 5007 和具有  $100 \text{nm} \sim 400 \text{nm}$  膜厚的第二导电膜 5008 被叠加在栅极绝缘膜 5006 上。在本实例中,膜厚 30 nm 且由 100 nm 程 100 nm 程 100 nm 程 100 nm 不 100 nm 程 100 nm 不 1

[0308] 在本实例中,作为第一导电膜 5007 的 TaN 膜通过溅射法使用 Ta 靶在含氮气氛中形成。作为第二导电膜 5008 的 W 膜通过溅射法使用 W 靶形成。此外,它可通过热 CVD 法使用六氟化钨(WF<sub>6</sub>)形成。在任何情况下,当他们被用作栅电极时,有必要减少电阻,W 膜电阻率被设定为  $20~\mu$  Ω cm 或更低是理想的。当晶体颗粒被增大,W 膜的电阻率可能被减小。但是,如果大量杂质元素如氧存在于 W 膜中,则结晶化被抑制,结果使电阻率增加。因此,在本实例中,考虑到杂质在膜形成时不能从气相进入膜中,W 膜通过溅射法采用高纯 W (纯度99.9999%)作靶形成。这样可获得  $9~\mu$  Ω cm  $\sim 20~\mu$  Ω cm 的电阻率。

[0309] 注意,在本实例中,TaN膜被用作第一导电膜5007,而W膜被用作第二导电膜5008。但是,构成第一导电膜5007和第二导电膜5008的材料不特别限定。第一导电膜5007和第二导电膜5008各自可从Ta、W、Ti、Mo、Al、Cu、Cr和Nd中选择一种元素形成,或由主要包含上述元素的合金材料或化合物形成。此外,它们可由一种以添加杂质元素如磷或AgPdCu合金的多晶硅膜为代表的半导体膜形成。

[0310] 其次,由抗蚀剂制成的掩模 5009 被通过光刻法形成,并且进行用于形成电极和引线的第一刻蚀工艺。该第一刻蚀工艺在第一刻蚀条件和第二刻蚀条件下进行(图 13B)。

[0311] 在本实例中,作为第一刻蚀条件,采用 ICP(感应耦合等离子体)刻蚀法。此外, $CF_4$ 、 $Cl_2$ 和  $0_2$ 被用作刻蚀气体,并且各气体流速比设定为 25: 25: 10(sccm)。具有 500W 和 13.56MHz 的 RF 功率被供给线圈型电极使处于 1.0Pa 压强下产生等离子体,由此进行刻蚀。具有 150W 和 13.56MHz 的 RF 功率被供给基片一侧(样品台),为其施加实际上的负自偏压。W 膜在这种第一刻蚀条件下被刻蚀,结果第一导电层 5007 的末端部分被作成斜坡形。[0312] 随后,不将由抗蚀剂制成的掩模 5009 移走,把刻蚀条件变为第二刻蚀条件。 $CF_4$ 和  $Cl_2$ 被用作刻蚀气体,并且各气体流量比设定为 30: 30(sccm)。具有 500W 和 13.56MHz 的

RF 功率被供给线圈型电极以在 1. 0Pa 压强下产生等离子体,由此进行约 15 秒的刻蚀。具有 20W 和 13. 56MHz 的 RF 功率被供给基片一侧(样品台),为其施加实际上的负自偏压。在第二刻蚀条件下,第一导电膜 5007 和第二导电膜 5008 都被刻蚀到相同程度。注意,为了进行刻蚀并不留残留物在栅极绝缘膜 5006 上,优选刻蚀时间增加约 10%~ 20%的速率。

[0313] 在上述第一刻蚀工艺中,当由抗蚀剂制成的掩模的形状制作合适时,第一导电膜5007的末端部分和第二导电膜5008的末端部分通过施加到基片一侧的偏压的作用变为斜坡形。这样,从第一导电层5007和第二导电层5008制成的第一形状导电层5010~5014通过第一刻蚀工艺被形成。关于绝缘膜5006,未被第一形状导电层5010~5014覆盖的区域被刻蚀约20nm~50nm,以便形成较薄区域。

[0314] 其次,不去掉由抗蚀剂制成的掩模 5009 (图 13C) 进行第二刻蚀工艺。在第二刻蚀工艺中, $SF_6$ 、 $Cl_2$  和  $0_2$  被用作刻蚀气体,并且有关气体流速比被设定为 24 : 12 : 24 (sccm)。 具有 700W 和 13. 56MHz 的 RF 功率被供给线圈型电极使处于 1. 3Pa 压强下产生等离子体,由此进行约 25 秒的刻蚀。具有 10W 和 13. 56MHz 的 RF 功率被供给基片一侧(样品台),为其施加实际上的负自偏压。这样,W 膜被有选择地刻蚀形成第二形状导电层 5015  $\sim$  5019。此时第一导电层 5015a  $\sim$  5018a 几乎没有被刻蚀。

[0315] 然后不去掉由抗蚀剂制成的掩模 5009 而进行第一掺杂工艺,以添加低浓度杂质元素,用于为半导体层 5002 ~ 5005 提供 N-型电导。第一掺杂工艺优选通过离子掺杂法或离子注入法进行。至于离子掺杂法的条件,剂量设定为  $1\times10^{13}$  原子 / cm²,并且加速电压设定为 40KeV ~ 80KeV。在本实例中,剂量设定为  $5.0\times10^{13}$  原子 / cm²,并且加速电压设定为 40KeV ~ 80KeV。在本实例中,剂量设定为  $5.0\times10^{13}$  原子 / cm²,且加速电压设定为 50KeV。作为用于提供 N-型电导的杂质元素,优选使用属于 15 族的元素,典型地,使用磷 (P) 或砷 (As)。在本实例中,使用磷 (P)。在此情况下,第二形状导电层  $5015\sim5019$  成为提供 N-型电导的杂质元素的掩模。因此第一杂质区 (N--区)  $5020\sim5023$  被自对准形成。然后,提供 N-型电导的杂质元素以  $1\times10^{18}$  原子 / cm³  $\sim1\times10^{20}$  原子 / cm³ 的浓度范围被添加到第一杂质区  $5020\sim5023$ 。

[0316] 随后,去掉抗蚀剂制成的掩模 5009 后,形成一个新的抗蚀剂掩模 5024,并且在高于第一掺杂工艺的加速电压下进行第二掺杂工艺。在离子掺杂法条件下,剂量设定为  $1\times10^{13}$  原子  $/\text{cm}^2\sim3\times10^{15}$  原子  $/\text{cm}^2$ ,并且加速电压设定为  $60\text{KeV}\sim120\text{KeV}$ 。在本实例中,剂量设定为  $3.0\times10^{15}$  原子  $/\text{cm}^2$ ,且加速电压设定为 65KeV。在第二掺杂工艺中,第二导电层  $5015b\sim5018b$  被用作杂质元素的掩模,这样进行掺杂使杂质元素被添加到位于第一导电层  $5015a\sim5018a$  的斜坡部分下的半导体层中。

[0317] 作为上述第二掺杂工艺的结果,用于提供 N-型电导的杂质元素以  $1\times10^{18}$  原子 / cm³ ~  $5\times10^{19}$  原子 / cm³ 浓度范围被添加到与第一导电层重叠的第二杂质区 (N-区;Lov区)5026、5029。此外,用于提供 N-型电导的杂质元素以  $1\times10^{19}$  原子 / cm³ ~  $5\times10^{21}$  原子 / cm³ 浓度范围被添加到第三杂质区 (N+区)5025、5028、5031 和 5034。经过第一和第二掺杂工艺,在半导体层  $5002\sim5005$  内形成了未添加杂质元素区域或添加少量杂质元素区域。在本实例中,没有完全添加杂质元素的区域或添加示踪杂质元素的区域称为沟道区 5027、5030、5033 和 5036。此外,存在通过上述第一掺杂工艺形成的第一杂质区 (N-区)5020 ~ 5023 中的被第二掺杂工艺中的抗蚀剂 5024 覆盖的区域。在本实例中,它们继续被称作第一杂质区 (N-区;LDD区)5032、5035。

[0318] 注意,在本实例中,第二杂质区 (N-区)5026 和第三杂质区 (N+区)5025、5028、5031 和5034 只通过第二掺杂工艺形成。但是,本发明不限于此。掺杂工艺条件可适当改变,并且可进行多次掺杂工艺以形成这些区域。

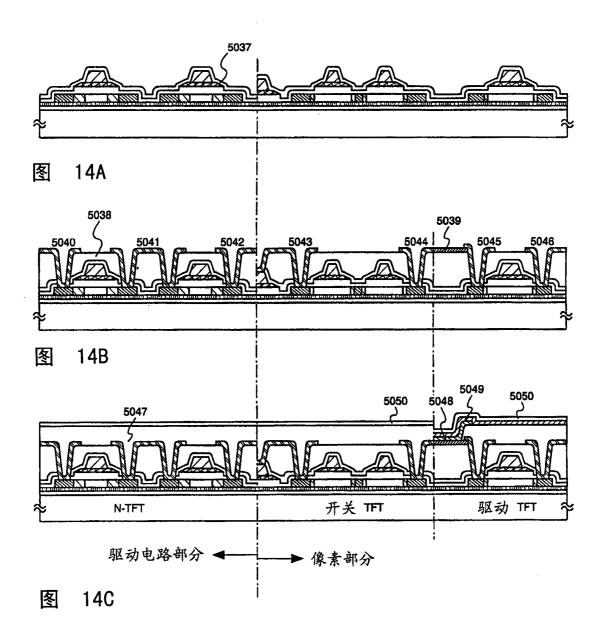

[0319] 其次,如图 14A 所示,去掉抗蚀剂制成的掩模 5024 并形成第一层间绝缘膜 5037。 厚度为 100nm ~ 200nm 的含硅绝缘膜通过等离子体 CVD 法或溅射法被形成,作为第一层间绝缘膜 5037。在本实例中,通过等离子体 CVD 法形成膜厚 100nm 的氮氧化硅膜。当然第一层间绝缘膜 5037 不限于氮氧化硅膜,因此,另一种含硅绝缘膜可被用作单层或叠层结构。

[0320] 其次,进行热处理,用于半导体层结晶性的恢复和添加到半导体层的杂质元素的激活。这种热处理通过热退火法利用退火炉进行。热退火法优选在氮气氛中进行,其中氧浓度为 1ppm 或更小,优选 0. 1ppm 或更小在  $400\,^{\circ}$ ~  $700\,^{\circ}$ 0。在本实例中,为激活工艺进行  $410\,^{\circ}$ 1 小时的热处理。注意,除热退火法外,可使用激光退火法或快速热退火法(RTA 法)。

[0321] 热处理也可在第一层间绝缘膜 5037 形成之前进行。但是,如果构成第一导电层 5015a~5019a和第二导电层 5015b~5019b的材料对热敏感,优选形成用于保护引线等的 第一层间绝缘膜 5037(主要含硅的绝缘膜,如氮化硅膜)之后再进行热处理,如同本实例一样。

[0322] 如上所述,当热处理是在第一层间绝缘膜 5037(主要含硅的绝缘膜,如氮化硅膜) 形成后进行时,半导体层的氢化也可与激活处理工艺同时进行。在氢化步骤中,半导体层的悬空键被包含于第一层间绝缘膜中的氢终止。

[0323] 注意,可进行不同于用于激活工艺的热处理的用于氢化的热处理。

[0324] 此处,无论第一层间绝缘膜 5037 存在与否,半导体层可被氢化。作为另一些氢化方法,可采用利用等离子体激发氢的方法 (等离子体氢化)或在含氢  $3\% \sim 100\%$ 的气氛中进行  $300 \sim 450\%$ ,1 小时  $\sim 12$  小时的热处理的方法。

[0325] 其次,第二层间绝缘膜 5038 在第一层间绝缘膜 5037 上形成。无机绝缘膜可被用作第二层间绝缘膜 5038。例如由 CVD 法形成的氧化硅膜、通过 SOG(在玻璃上旋涂)法等施加的氧化硅膜可被使用。此外,有机绝缘膜可被用作第二层间绝缘膜 5038。例如,由聚酰亚胺、聚酰胺、BCB 苯并环丁烯 (benzocyclobutene)、丙烯酸类 (acrylic)等构成的膜可被使用。另外,有一种由丙烯酸类膜和氧化硅膜构成的叠层结构可被使用。

[0326] 在本实例中,厚度为 1. 6 im 的丙烯酸类膜被形成。当第二层间绝缘膜 5038 被形成之后,由形成于基片 5000 上的 TFT 引起的不平度降低,表面可被调平。特别地,第二层间绝缘膜 5038 具有很强的拉平趋向。因此可获得良好的平整膜。

[0327] 其次,利用干法或湿法刻蚀,第二层间绝缘膜 5038、第一层间绝缘膜 5037,以及栅极绝缘膜 5006 被刻蚀形成通向杂质区 5025、5028、5031 和 5034 的接触孔。

[0328] 其次,由透明导电膜构成的像素电极 5039 被形成。氧化铟和氧化锡的化合物(氧化铟锡:ITO)、氧化锌和氧化铟的化合物、氧化锌、氧化锡、氧化铟等可被用于透明导电膜。此外,可使用添加镓的透明导电膜。像素电极对应于 EL 元件的阳极。

[0329] 在本实例中,厚度为 110nm 的 IT0 膜被形成,并被进行图案化形成像素电极 5039。 [0330] 其次,电连接于有关杂质区的引线  $5040 \sim 5046$  被形成。注意,在本实例中,膜厚为 100nm 的 Ti 膜、膜厚 350nm 的铝膜以及膜厚 100nm 的 Ti 膜通过溅射法被形成一个连续的叠层,并且最终的叠层膜被按照预定形状进行图案加工,以便形成引线  $5040 \sim 5046$ 。

[0331] 当然,它们不限于三层结构。单层结构、双层结构、由四层或更多层构成的叠层结构可被使用。引线材料不限于 A1 和 Ti,因此其它导电膜可被使用。例如,在 TaN 膜上形成 AL 膜或 Cu 膜,其上再形成 Ti 膜,然后最终的叠层膜被图案加工形成引线。

[0332] 此处, 像素电极 5039 上的一部分和引线 5045 的一部分彼此重叠, 以便产生引线 5045 和像素电极 5039 间的电连接。

[0333] 通过上述步骤,如图 14B 所示,包含 N- 沟道 TFT 的驱动电路部分和包含开关 TFT 及驱动 TFT 的像素部分可在同一基片上被形成。

[0334] 在驱动电路部分的 N-沟道 TFT 包含与构成栅电极一部分的第一导电层 5015a 重叠的低浓度杂质区 5026 (Lov 区) 和分别作为源极区或漏极区的高浓度杂质区 5025。

[0335] 像素部分的 N- 沟道开关 TFT 包含在栅电极之外形成的低浓度杂质区 5032(Loff区) 和分别作为源极区或漏极区的高浓度杂质区 5031。

[0336] 其次,形成第三层间绝缘膜 5047。无机绝缘膜或有机绝缘膜可被用作第三层间绝缘膜 5047。由 CVD 法形成的氧化硅膜、通过 SOG(在玻璃上旋涂)法施加的氧化硅膜,或由溅射法等形成的氮氧化硅膜可被用作无机绝缘膜。此外,丙烯酸类树脂膜等可被用作有机绝缘膜。

[0337] 下面将描述第二层间绝缘膜 5038 和第三层间绝缘膜 5047 的组合实例。

[0338] 有一种组合,其中由丙烯酸类和溅射法形成的氮氧化硅膜被用作第二层间绝缘膜5038,而由溅射法形成的氮氧化硅膜被用作第三层间绝缘膜5047。此外有一种组合,其中由SOG法形成的氧化硅膜被用作第二层间绝缘膜5038,并且由SOG法形成的氧化硅膜被用作第三层间绝缘膜5047。此外有一种组合,其中由SOG法形成的氧化硅膜和由等离子体CVD法形成的氧化硅膜组成的叠层膜被用作第二层间绝缘膜5038,而由等离子体CVD法形成的氧化硅膜被用作第三层间绝缘膜5047。此外,有一种组合,其中丙烯酸类被用作第二层间绝缘膜5038,并且丙烯酸类被用作第三层间绝缘膜5047。此外有一种组合,其中丙烯酸类膜和由等离子体CVD法法形成的氧化硅膜组成的叠层膜被用作第二层间绝缘膜5038,而由等离子体CVD法形成的氧化硅膜被用作第三层间绝缘膜5047。此外有一种组合,其中由等离子体CVD法形成的氧化硅膜被用作第三层间绝缘膜5038,而丙烯酸类被用作第三层间绝缘膜5047。

[0339] 在对应于第三层间绝缘膜 5047 中的像素电极 5039 的位置处形成一个开口部分。第三层间绝缘膜作为堤坝(bank)。当在形成开口部分时使用湿法刻蚀,它可以容易地形成为具有斜坡形的侧壁。如果凹槽部分的侧壁不是足够柔软,EL 元件的逐步退化成为突出问题。因此需要注意。

[0340] 碳颗粒或金属颗粒可能被添加到第三层间绝缘膜 5047 中以减少电阻率,由此抑制静电产生。此时,优选所添加的碳颗粒或金属颗粒的量被调节,以使电阻率为  $1\times10^6\Omega$ m  $\sim 1\times10^{12}\Omega$ m (优选  $1\times10^8\Omega$ m  $\sim 1\times10^{10}\Omega$ m)。

[0341] 其次,EL层 5048 被在暴露于第三层间绝缘膜 5047 的凹槽部分的像素电极 5039 上形成。

[0342] 已知的有机光发射材料或无机光发射材料可以被用作 EL 层 5048。

[0343] 基于低分子量的有机光发射材料,基于高分子量的有机光发射材料,或基于中分子量的有机光发射材料可任意用作有机光发射材料。注意在本说明书中,基于中分子量的

有机光发射材料表示没有升华特性并且其中分子数量为 20 或更少或分子链的长度为 10 im 或更小的有机光发射材料。

[0344] EL层 5048 一般具有叠层结构。典型地,具有"空穴输运层,光发射层,和电子输运层"组成的叠层结构,它由 Estman Koda k公司地 Tang 等提出。除此之外,可使用一种结构,其中"空穴注入层,空穴输运层,光发射层,和电子输运层"或"空穴注入层,空穴输运层,光发射层,和电子输运层"或"空穴注入层,空穴输运层,光发射层,电子输运层和电子注入层"按此顺序被叠放在阳极上。光发射层可能掺杂荧光颜料等。

[0345] 在本实例中,EL层 5048 通过蒸发法利用基于低分子量的有机光发射材料被形成。特别地,一种叠层结构被使用,其中厚度 20nm 的铜酞化菁 (CuPc) 膜被提供作为空穴注入层,并在其上提供厚度为 70nm 的三-8- 羟基喹啉铝化合物 (A1 $q_3$ ) 膜作为光发射层。发光颜色可通过向 A1 $q_3$  中添加荧光颜料如喹吖啶酮 (quinacridon)、二萘嵌苯或 DCM1 加以控制。

[0346] 注意图 14C 中只有一个像素被示出。但是,可使用一种结构,其中对应于多色,例如 R(红色),G(绿色)B(蓝色)中各有关颜色的 EL层 5048 被分别形成。

[0347] 作为利用基于高分子量的有机光发射材料的实例,EL层 5048 也可通过一种叠层结构被构造,其中厚度为 20nm 的聚噻吩 (PEDOT) 膜通过旋涂法被作为空穴注入层被提供,其上提供厚度约 100nm 的对亚苯亚乙烯 (paraphenylenevinylene) (PPV) 膜作为光发射层。当使用  $\pi$  共轭系统 PPV 聚合物时,从红色到蓝色的光发射波长可被选择。此外,无机材料如碳化硅可被用作电子输运层和电子注入层。

[0348] 注意 EL 层 5048 不限于具有其中的空穴注入层、空穴输运层、光发射层、电子输运层、电子注入层等各不相同的叠层结构的层。换言之,EL 层 5048 可以具有一种叠层结构,其中构成空穴注入层、空穴输运层、光发射层、电子输运层、电子注入层等的材料被相混合。

[0349] 例如,EL层 5048 可具有一种结构,其中由构成电子输运层的材料(此后称为电子输运材料)和构成光发射层的材料(此后称为光发射材料)组成的混合层被置于电子输运层和光发射层之间。

[0350] 其次,在EL层 5048上提供由导电膜制成的像素电极 5049。在本实例情况下,一种铝和锂的合金膜可被用作导电膜。当然,已知的 MgAg 膜(镁和银的合金膜)可被使用。像素电极 5049 对应于EL元件的阴极。由属于元素周期表中第一族和第二族的一种元素构成的导电膜或其中添加这些元素的导电膜可随意被用作阴极材料。

[0351] 当像素电极 5049 被形成时, EL 元件被完成。注意, EL 元件表示由像素电极(阳极)5039、EL 层 5048 和像素电极(阴极)5049 构成的元件。

[0352] 提供完全覆盖 EL 元件的钝化膜 5050 是有效的。单层绝缘膜如碳膜、氮化硅膜或 氮氧化硅膜或这些膜组合成的叠层膜可被用作钝化膜 5050。

[0353] 优选具有良好覆盖能力的膜作为钝化膜 5050,使用碳膜,特别是 DLC(类金刚石碳)膜和 CN 膜是有效的。DLC 膜可在从室温到 100℃温度范围内被形成。这样,可以很容易地在具有低热阻的 EL 层 5047 上形成一种膜。此外 DLC 膜对氧有高的阻挡效应,因而可以抑制 EL 层的氧化。

[0354] 注意,第三层间绝缘膜 5047 形成后,利用多反应室型(或连续型)成膜装置,在不暴露大气情况下,连续进行直到形成钝化膜 5050 的所有步骤是有效的。

[0355] 注意,实际上当完成直到如图 14C 所示状态时,为了不暴露大气,优选利用保护膜

(叠层膜、紫外线固化树脂膜等)或具有高气密性和低放气性的透明密封部件进行封装(密封)。此时,当被密封部件包围的内部部分被形成惰性气氛或在内部放入吸湿材料(例如氧化钡),则EL元件的可靠性被改善。

[0356] 而且当气密度被通过诸如封装的工艺增加后,附接一个连接器(柔性印刷电路: FPC),用于和从形成于具有外部信号终端的基片 5000 上的元件或电路引出的终端连接,以使它作为产品被完成。

[0357] 而且根据本实例描述的步骤,制造半导体器件要求的光掩模的数量可被减少。结果工艺被减少并且对降低制造成本和提高产量有贡献。

[0358] 「实例 5]

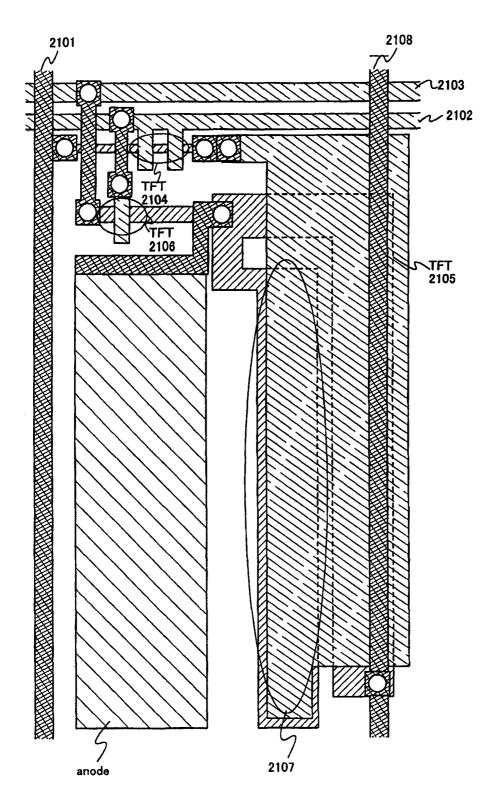

[0359] 在本实例中,通过图 15A ~ 15C 将描述根据本发明制造半导体器件的一个实例。

[0360] 图 15A 是一个通过密封部件密封其中形成 TFT 元件的基片而获得的半导体器件的俯视图。图 15B 是沿图 15A 中 A-A'线的截面图。图 15C 是沿图 15A 中 B-B'线的截面图。

[0361] 密封部件 4009 被提供以包围提供在基片 4001 上的像素部分 4002,源极信号线驱动电路 4003,以及第一和第二栅极信号线驱动电路 4004a 和 4004b。此外,在像素部分 4002、源极信号线驱动电路 4003 以及第一和第二栅极信号线驱动电路 4004a 和 4004b 上提供密封部件 4008。这样像素部分 4002、源极信号线驱动电路 4003 以及第一和第二栅极信号线驱动电路 4004a 和 4004b 被用基片 4001、密封部件 4009 和密封部件 4008 密封。

[0362] 而且提供于基片 4001 上的像素部分 4002、源极信号线驱动电路 4003 以及第一和第二栅极信号线驱动电路 4004a 和 4004b 各有多个 TFT。在图 15B 中,典型示出包含于源极信号线驱动电路 4003 的 TFT (注意此处示出一个 N- 沟道 TFT 和一个 P- 沟道 TFT) 4201 和包含于像素部分 4002 中的 TFT4202,二者形成于基底膜 4010 上。

[0363] 层间绝缘膜(平面化膜)4301 形成于 TFT4201 和 4202 上,其上形成与 TFT4202 的漏极电连接的像素电极(阳极)4203。具有大功函数的透明导电膜被用作像素电极 4203。氧化铟和氧化锡的化合物、氧化锌和氧化铟的化合物、氧化锌、氧化锡或氧化铟等可被用于透明导电膜。此外,可使用添加镓的透明导电膜。

[0364] 在像素电极 4203 上形成绝缘膜 4302。在像素电极 4203 上的绝缘膜 4302 中形成 开口部分。在开口部分中,有机光发射层 4204 被形成于像素电极 4203 上。已知的有机光发射材料或无机光发射材料可被用作有机光发射层 4204。此外,有机光发射材料包括基于低分子量(单体系统)材料和基于高分子量(聚合物系统)材料,并且可使用其中任何一种材料。

[0365] 优选已知的蒸发技术或施加法技术作为形成有机光发射层 4204 的方法。此外,通过随意组合空穴注入层、空穴输运层、光发射层、电子输运层、电子注入层获得的叠层结构或单层结构优选用作有机光发射层结构。

[0366] 由具有光屏蔽特性的导电膜(典型地主要包含铝、铜、或银的导电膜或导电膜与另一种导电膜的叠层膜)制成的阴极 4205 被形成于有机光发射层 4204 上。此外,存在于阴极 4205 和有机光发射层 4204 间界面的水分和氧被减少到最小是理想的。因此,需要一种器件,其中有机光发射层 4204 在氦气氛或稀有气体中被形成,且阴极 4205 不暴露于氧和湿气中被形成。在本实例中,通过使用多反应室型(组合工具型 cluster tool type) 成膜装置形成上述膜是可能的。预定电压被提供给阴极 4205。

[0367] 通过上述步骤,由像素电极(阳极)4203、有机光发射层 4204 以及阴极 4205 构成的发光元件 4303 被形成。在绝缘膜 4302 上形成覆盖发光元件 4303 的保护膜 4209。保护膜 4209 有效防止氧、湿气等渗入发光元件 4303。

[0368] 参考数 4005a 表示与电源相连的引线,它与 TFT4202 的第一电极连接。引线 4005a 从密封部件 4009 和基片 4001 之间通过,并通过各向异性导电膜 4300 与 FPC4006 的 FPC 引线 4301 电连接。

[0369] 玻璃材料、金属部件(典型地,不锈部件)、陶瓷部件、塑料部件(包括塑料膜)可被用作封接部件4008。FRP(玻璃纤维增强塑料)板、PVF(聚氟乙烯)膜、Mylar膜、聚酯膜或丙烯酸类膜可被用作塑料部件。此外,具有一种结构的薄片可被使用,该结构中铝箔被夹在PVT膜和聚脂(Mylar)膜之间。

[0370] 注意,当来自发光元件的光的辐射方向朝向覆盖部件一侧时,要求覆盖部件是透明的。在此情况下,透明材料如玻璃板、塑料板聚酯膜或丙烯酸类膜可被使用。

[0371] 并且除惰性气体如氮气或氩气以外,紫外线固化树脂或热固型树脂可被用于填充剂 4210。PVC(聚氯乙烯)、丙烯酸衍生物、聚酰亚胺、环氧树脂、硅树脂、PVB(聚乙烯醇缩丁醛)或 EVA(乙烯乙酸乙烯酯)可被使用。在本实例中,氮被用做填充剂。

[0372] 并且为了将填充剂 4210 暴露到吸湿材料(优选氧化钡)或能吸收氧的材料,在基片 4001 一侧中的密封部件 4008 的表面提供一个凹形部分 4007,并且放置由 4207 表示的吸湿材料或能吸收氧的材料。为防止具有吸湿特性或能吸收氧的材料 4207 飞出,具有吸湿特性或能吸收氧的材料 4207 通过凹形覆盖部件 4208 被固定在凹形部分 4007 中。注意凹形覆盖部件 4208 被形成细网状,并且被构造成能透过空气或湿气但不能透过具有吸湿特性或能吸收氧的材料 4207。当具有吸湿特性或能吸收氧的材料 4207 被提供时,发光元件 4303 的退化可被抑制。

[0373] 如图 15C 所示,在引线 4005a 上形成导电膜 4203a,以使它与像素电极 4203 形成的同时与引线 4005a 接触。

[0374] 而且各向异性导电膜 4300 具有导电添充剂 4300a。当基片 4001 和 FPC4006 通过 热压彼此键合时,位于基片 4001 上的导电膜 4203a 和位于 FPC4006 上的 FPC 引线 4301 彼此通过导电添充剂 4300a 电连接。

[0375] 「实例 6]

[0376] 在本实例中,通过使用有机光发射材料,其三重激发产生的磷光可用于发射光,外部光发射量子效率可得到显著改善。结果,发光元件的功耗可被减少,其寿命可被延长,并且重量可减轻。

[0377] 下面是外部光发射量子效率通过使用三重激发被改善的报告(T. Tsutsui, C. Adachi, S. saito, 有机分子系统中的光化学过程, ed. K. Honda, (Elsevier Sci. Pub., Tokyo, 1991) 437页)。

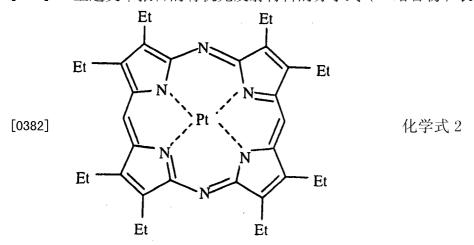

[0378] 上述文章报告的有机光发射材料的分子式(香豆素色素)表示如下:

[0380] (M. A. Baldo, D. F. O' Brien, Y. You, A. Shoustikov, S. Sibley, M. E. Thompson, S. R. Forrest, Nature 395(1998) p. 151)

[0381] 上述文章报告的有机光发射材料的分子式(Pt 络合物)表示如下:

[0383] (M. A. Baldo, S. Lamansky, P. E. Burrows, M. E. Thompson, S. R. Forrest, Appl. Phys. Lett, 75 (1999) p. 4.)

[0384] (T. Tsutsui, M. -J. Yang, M. Yahiro, K. Nakamura, T. Watanabe, T. Tsuji, Y. Fukuda, T. Wakimoto, S. Mayaguchi, Jpn, Appl. Phys., 38 (12B) (1999) L1502)

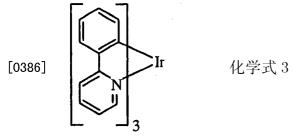

[0385] 上述文章报告的有机光发射材料的分子式(Ir 络合物)表示如下:

[0387] 如上所述,如果来自三重激发的磷光能被投入实际应用,原则上可实现外部光发射量子效率达到使用来自单重激发荧光情况下的 3 ~ 4 倍。

[0388] [实例 7]

[0389] 使用发光元件的光发射器件是自发射型,与液晶显示器相比,呈现更优秀的图象显示分辨能力。此外,光发射器件具有更宽的视角。因此光发射器件可被用于不同的电子装置中的显示部分。

[0390] 使用本发明光发射器件的这些电子装置包括摄像机、数字照相机、护目镜式显示器(头置显示器)、导航系统、声音复制系统(汽车声频设备和组合音响设备)、膝上型计算机、游戏机、便携式信息终端(移动计算机、移动电话、便携式游戏机、电子记事本等)、包括记录媒介(更特别地,一种能复制记录媒介如数字视盘(DVD)等等,并且包括用于显示复制图象的显示器的设备)等。特殊地,在便携式信息终端情况下,优选使用光发射器件,因为可能被从一个倾斜方向观看的便携式信息终端常常要求具有宽的视角。图 20 分别表示出这种电子装置的各种特例。

[0391] 图 20A 表示一种光发射显示器件,它包括机壳 3001、支撑台 3002、显示部分 3003、扬声器部分 3004、视频输入终端 3005 等。本发明可用于显示部分 3003。光发射器件为自

发射型,因此不需要背光。因此它的显示部分可具有比液晶显示器薄的厚度。光发射显示器件包括用于显示信息的整个显示器件,如个人计算机、TV广播接收机和广告显示器。

[0392] 图 20B 图解示出一种数字静态照相机,它包括主体 3101、显示部分 3102、图象接收部分 3103、操作键 3104、外部连接端口 3105、快门 3106 等。根据本发明的光发射器件可被用作显示部分 3102。

[0393] 图 20C 图解示出一种膝上型计算机,它包括主体 3201、机壳 3202、显示部分 3203、键盘 3204、外部连接端口 3205、定位鼠标 3206 等。根据本发明的光发射器件可被用作显示部分 3203。

[0394] 图 20D 图解示出一种移动计算机,它包括主体 3301、显示部分 3302、开关 3303、操作键 3304、红外端口 3305 等。根据本发明的光发射器件可被用作显示部分 3302。

[0395] 图 20E 图解示出一种包括记录媒介(更特别地,DVD 复制装置)的便携式图象复制装置,它包括主体 3401、机壳 3402、显示部分 A3403、另一个显示部分 B3404、记录媒介(DVD等)读出部分 3405、操作键 3406、扬声器部分 3407 等。显示部分 A3403 主要用于显示图象信息,而显示部分 B3404 主要用于显示字符信息。根据本发明的光发射器件可被用作显示部分 A3403 和 B3404。包括记录媒介的图象复制装置进一步包括游戏机等。

[0396] 图 20F 图解示出一种护目镜式显示器(头置显示器),它包括主体 3501、显示部分 3502、镜臂部分 3503 等。根据本发明的光发射器件可被用作显示部分 3502。

[0397] 图 20G 图解示出一种摄像机,它包括主体 3601、显示部分 3602、机壳 3603、外部连接端口 3604、遥控接收部分 3605、图象接收部分 3606、电池 3607、声音输入部分 3608、操作键 3609、目镜 3610 等。根据本发明的光发射器件可被用作显示部分 3602。

[0398] 图 20H 图解示出一种移动电话,它包括主体 3701、机壳 3702、显示部分 3703、声音输入部分 3704、声音输出部分 3705、操作键 3706、外部连接端口 3707、天线 3708 等。根据本发明的光发射器件可被用作显示部分 3703。注意显示部分 3703 通过在黑色背景下显示白色字符可减少移动电话的功耗。

[0399] 将来当从有机光发射材料可发射亮度较亮的光时,根据本发明的光发射器件将适用于前投式和后投式投影仪,其中包含输出图象信息的光被透镜装置等放大而投影。

[0400] 前面提到的电子装置更可能被用于显示通过电信路径如因特网、CATV(电缆电视系统)传播的信息,以及特别地可能用于显示活动图像信息。光发射器件适合显示活动图像,因为有机光发射材料可呈现高响应速度。

[0401] 光发射器件的发光部分消耗能量,因此通过其中光发射部分变得尽可能小的方式来显示信息是所希望的。因此,当光发射器件被应用于主要显示字符信息的显示部分,例如便携式信息终端,以及更特别地的便携式电话或声音再生装置的显示部分时,理想的是驱动光发射器件以使字符信息通过光发射部分形成而非发射部分对应于背景。

[0402] 如上面提到的,本发明可不同地被应用于各领域广泛的电子装置中。本实例中的电子装置可通过利用具有由实例 1 ~ 6 结构自由组合所得结构的光发射器件获得。

[0403] 「实例 8]

[0404] 在本实例中,用图 22 描述图 21A 所示像素结构的俯视图。

[0405] 在图 22 中,通过对区域中的同一层进行图案加工形成 TFT 来形成多个有源层。然后,通过对同一层的图案加工,形成第一栅极线 2102、第二栅极线 2103 以及各个 TFT 的栅电

极。随后,源极信号线 2101 和电流供电线 2108 通过对同一层的图案加工被形成。最后,EL元件(发光元件)的第一电极(此处为阳极)被形成。

[0406] 然后,一个选择 TFT2104 被配置,其第一栅极线 2102 的一部分为栅电极。TFT2104 被形成具有双栅极结构,其中两个栅电极在一个有源层中形成,由此它比在一个有源层中形成一个栅电极的单栅极结构有更可靠的选择(开关)。此外 TFT2104 也可被形成具有多栅极结构,其中在一个有源层中形成三个或更多栅电极。

[0407] 此外,为了减少 TFT 中的变化,TFT2105 的沟道长度(L)被设定得较长。另外,L 进一步加长,由此可使 TFT 的饱和区是平的。

[0408] 除此之外, 栅电极通过接触被连接于第二栅电极线 2103 的 TFT 2106 被形成。另外, 由有源层和作为扫描线的同一层所形成的电容元件被配置。

[0409] 对于每个 TFT 这样的构造是可采用的, 栅电极被置于半导体膜(沟道形成区)上的顶部栅极结构或与此相反的底部栅极结构被使用, 和补偿结构或 GOLD 结构被用于杂质区(源区或漏区)。

[0410] 根据本发明,在由单极TFT、作为器件电特性特别优秀的N-沟道TFT构成的半导体器件中,形成这样一种构造,以至不会由于EL元件的退化而产生驱动TFT的栅极-源极电压变化,由此,即使EL元件退化也几乎不会使发光减少。此外,本发明提出的构造既不必是复杂构造也不必增加形成像素的元件数量。因此它可被应用而不引起诸如数字孔径减少的缺点。因此是非常有用的。

[0411] 虽然本发明已结合优选实施例被描述,但本发明并不应限于这些实施例。例如,在本发明中使用的晶体管可以是其中的有源层由结晶半导体或非晶半导体构成的薄膜晶体管(TFT)、单晶晶体管或使用有机半导体材料作为其有源层的晶体管中的任何一种。例如通过使用 SOI 技术形成的晶体管可被用作单晶薄膜晶体管,而包含多晶硅或非晶硅的薄膜晶体管可被用作薄膜晶体管。

图

3C

**4A** 图

5B

冬

图 5C

附

冬

图 8

图 9

图 10B

图 11A

11C 冬

图 15A

图 16B

图 17B

18A 图

图 18B

图 19A

图 19B

图 21A

图 21B

21C 图

图 22

| 专利名称(译)        | 显示器件及其驱动方法                                                                                                                                                                                                       |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 公开(公告)号        | CN101127188B                                                                                                                                                                                                     | 公开(公告)日 | 2012-05-02 |

| 申请号            | CN200710153394.4                                                                                                                                                                                                 | 申请日     | 2002-11-13 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                                                                     |         |            |

| 申请(专利权)人(译)    | 株式会社半导体能源研究所                                                                                                                                                                                                     |         |            |

| 当前申请(专利权)人(译)  | 株式会社半导体能源研究所                                                                                                                                                                                                     |         |            |

| [标]发明人         | 木村肇                                                                                                                                                                                                              |         |            |

| 发明人            | 木村肇                                                                                                                                                                                                              |         |            |

| IPC分类号         | G09G3/30 G09G3/32 G09G3/20 H05B33/08 H05B33/14 H01L51/50 H01L27/32 G09F9/33 H04M1/73                                                                                                                             |         |            |

| CPC分类号         | G09G2330/08 G09G2310/061 G09G2300/0842 H01L27/3244 G09G2310/027 G09G2330/10 H01L27 /1255 G09G3/3266 G09G2300/0426 G09G2320/043 G09G2310/0251 G09G3/3233 H04W52/027 G09G2310/0256 G09G3/2022 G09G3/3291 Y02D70/00 |         |            |

| 代理人(译)         | 张雪梅                                                                                                                                                                                                              |         |            |

| 审查员(译)         | 孙大林                                                                                                                                                                                                              |         |            |

| 优先权            | 2001348032 2001-11-13 JP                                                                                                                                                                                         |         |            |

| 其他公开文献         | CN101127188A                                                                                                                                                                                                     |         |            |

| 外部链接           | Espacenet SIPO                                                                                                                                                                                                   |         |            |

## 摘要(译)

一种具有几乎不会由于退化的EL元件而产生电流值改变的结构的半导体器件被提供。电容元件被配置于驱动TFT栅极和源极之间,视频信号输入到栅电极,然后它处于浮置状态。此时,当驱动TFT的栅极源极电压超过阈值时,驱动TFT被开启。假定EL元件退化并且阳极电位上升,即驱动TFT的源极电位上升,则通过电容元件的耦合处于浮置状态的驱动TFT的栅电极的电位将上升相同量。因此,即使当阳极电位由于EL元件退化而上升,这种上升同样被加到栅电极电位,而允许驱动TFT的栅极源极电压保持不变。