(12) 发明专利

(10) 授权公告号 CN 1892767 B

(45) 授权公告日 2011.08.10

(21) 申请号 200610106206.8

(56) 对比文件

(22) 申请日 2006.07.04

US 2004/0070558 A1, 2004.04.15, 权利

要求 1, 说明书 0010 节, 0016 节, 0027-0034

节, 0037-0043 节, 0051 节, 说明书附图 1-3.

JP 2001-184015 A, 2001.07.06,

(30) 优先权数据

2005-194600 2005.07.04 JP

审查员 毕淑影

(73) 专利权人 株式会社半导体能源研究所

地址 日本神奈川

(72) 发明人 吉田泰则 木村肇 山崎舜平

(74) 专利代理机构 中国国际贸易促进委员会专

利商标事务所 11038

代理人 王永刚

(51) Int. Cl.

G09G 3/30 (2006.01)

G09G 3/20 (2006.01)

H05B 33/08 (2006.01)

H05B 33/14 (2006.01)

权利要求书 2 页 说明书 33 页 附图 35 页

(54) 发明名称

显示器件及其驱动方法

(57) 摘要

本发明的目的是提供一种显示器件及其驱动方法,在进行面积灰度级显示的EL显示器件中,实现图像质量改善且使图像质量稳定化。为了解决上述问题,在一个像素中设置分别具有发出几乎相同颜色的光的发光元件的多个子像素;以及具有与像素相同数量的子像素的多个监视用像素,其中,监视用像素的发光元件和像素的发光元件同时制作,并且,监视用像素的发光元件的电极在每个子像素中分别连接到不同的恒流源,而且,还设置差动放大电路以便根据监视用像素中的发光元件的电极的电位变化,使像素的发光元件的电极的电位对每个子像素进行变化。

1. 一种显示器件，包括：

包括至少两个第一子像素的第一像素，其中每个所述第一子像素具有发光元件；

包括至少两个第二子像素的监视像素，其中每个所述第二子像素具有发光元件；以及

电路，其用于按照所述监视像素中的每个所述第二子像素的所述发光元件的电位变化，改变施加到所述第一像素中的每个所述第一子像素的所述发光元件的电位，

其中，所述第一像素中的所述第一子像素的所有所述发光元件的颜色相同，

所述监视像素中的所述第二子像素的所有所述发光元件的颜色相同，

所述第一像素中的每个所述第一子像素连接到每个不同的驱动晶体管，

所述第一像素中的所述第一子像素执行面积灰度等级，并且

当施加了电压时所述第一子像素中的一个第一子像素的所述发光元件与所述第一子像素中的另一个第一子像素的所述发光元件具有不同的发光特性。

2. 根据权利要求 1 的显示器件，

其中，所述第一像素以及所述监视像素中的所述第一子像素和第二子像素中的每一个包括选择晶体管、与所述发光元件连接的驱动晶体管和用于保持电压的电容器，并且

所述选择晶体管和所述驱动晶体管由非晶硅形成。

3. 根据权利要求 2 的显示器件，

其中，设置有用于将负电压施加到所述驱动晶体管的栅电极的预充电电路。

4. 根据权利要求 3 的显示器件，

其中，通过所述预充电电路施加到所述驱动晶体管的栅电极的电位等于或高于施加到每个所述第一子像素的所述发光元件的电压的低电位侧的电位，且等于或低于将每个所述第一子像素的所述驱动晶体管的源电极电位和每个所述第一子像素的所述驱动晶体管的阈值电压值相加而得到的电位。

5. 根据权利要求 1 的显示器件，

其中，所述电路为运算放大器电路。

6. 根据权利要求 1 的显示器件，

其中，所述电路为缓冲放大器电路。

7. 一种显示器件，包括：

包括至少两个第一子像素的第一像素，其中每个所述第一子像素具有相同发光颜色的至少一个发光元件；

包括至少两个第二子像素的监视像素，其中每个所述第二子像素具有相同发光颜色的至少一个发光元件；以及

电路，其用于按照所述监视像素中的每个所述第二子像素的所述发光元件的电位变化，改变施加到所述第一像素中的每个所述第一子像素的所述发光元件的电位，

其中，所述监视像素中的每个所述第二子像素的所述发光元件与所述第一像素中的每个所述第一子像素的所述发光元件同时制作，

所述第一像素中的所述第一子像素的所有所述发光元件的颜色相同，

所述监视像素中的所述第二子像素的所有所述发光元件的颜色相同，

所述第一像素中的每个第一子像素连接到每个不同的驱动晶体管，

所述第一像素中的所述第一子像素执行面积灰度等级，并且

当施加了电压时所述第一子像素中的一个第一子像素的所述发光元件与所述第一子像素中的另一个第一子像素的所述发光元件具有不同的发光特性。

8. 根据权利要求 7 的显示器件，

其中，所述第一像素以及所述监视像素中的所述第一子像素和第二子像素中的每一个包括选择晶体管、与所述发光元件连接的驱动晶体管和用于保持电压的电容器，并且，

所述选择晶体管和所述驱动晶体管由非晶硅形成。

9. 根据权利要求 8 的显示器件，

其中，设置有用于将负电压施加到所述驱动晶体管的栅电极的预充电电路。

10. 根据权利要求 9 的显示器件，

其中，通过所述预充电电路施加到所述驱动晶体管的栅电极的电位等于或高于施加到每个所述第一子像素的所述发光元件的电压的低电位侧的电位，且等于或低于将每个所述第一子像素的驱动晶体管的源电极电位和每个所述第一子像素的驱动晶体管的阈值电压值相加而得到的电位。

11. 根据权利要求 7 的显示器件，

其中，所述电路为运算放大器电路。

12. 根据权利要求 7 的显示器件，

其中，所述电路为缓冲放大器电路。

13. 一种显示器件，包括：

以矩阵方式布置有第一像素的像素部分，其中每个所述第一像素包括第一发光元件连接到第一驱动晶体管的第一子像素、至少两个第二发光元件并联连接在一起并连接到第二驱动晶体管的第二子像素；

监视像素，包括第三发光元件连接到第三驱动晶体管的第三子像素、至少两个第四发光元件并联连接在一起并连接到第四驱动晶体管的第四子像素；以及

电路，其用于按照所述监视像素中的所述第三发光元件以及所述第四发光元件的电位变化，改变施加到所述第一像素中的所述第一发光元件以及所述第二发光元件的电位，

其中，所述第一发光元件和所述第三发光元件具有等同的特性，并且所述第二发光元件和所述第四发光元件具有等同的特性，

所述第一像素中的所述第一子像素和所述第二子像素执行面积灰度等级，并且

当施加了电压时所述第一发光元件与所述第二发光元件具有不同的发光特性。

14. 根据权利要求 13 的显示器件，

其中，所述电路为运算放大器电路。

15. 根据权利要求 13 的显示器件，

其中，所述电路为缓冲放大器电路。

## 显示器件及其驱动方法

### 技术领域

[0001] 本发明涉及使用发光元件构成像素的显示器件及其驱动方法。

### 背景技术

[0002] 对使用电致发光 (Electro Luminescence) 元件 (下文中也称作“发光元件”) 形成像素的平板型显示器件的开发不断展开。尽管是平板状的屏幕,但由于像素的发光元件自身发光,所以该显示器件被认为具有比液晶显示器件更宽的视角。另外,与液晶显示器件相比能够做到更薄而轻之类的优点受人关注。

[0003] 在使用发光元件形成像素的情况下,作为控制像素的亮度的方法,已知控制流过发光元件中的电流值或电压值的模拟灰度等级方法(例如,参照专利文件1)。另外,还已知控制发光元件的发光时间的时间灰度等级方法(例如,参照专利文件2)。除此以外,还已知将一个像素分割为多个区域并控制被分割的每个像素的发光状态的面积灰度等级方法(例如,参照专利文件3)。

[0004] 专利文件1 日本专利申请公开 2003-288055 号公报

[0005] 专利文件2 日本专利申请公开 2002-123219 号公报

[0006] 专利文件3 日本专利申请公开 2001-184015 号公报

[0007] 然而,发光元件的亮度有由于温度变化或随着发光时间的推移而变化之类的问题。在采用面积灰度等级方法的显示器件中,这种亮度退化显著地表现为图像质量的退化,所以被视为应当加以解决的问题。

### 发明内容

[0008] 因此,本发明的目的就是,在使用发光元件来进行面积灰度级显示的显示器件中,谋求图像质量改善且使图像质量稳定化。

[0009] 本发明的要点在于:在具有由发光元件构成的像素的显示器件的一部分上设置与上述像素相同结构的发光元件作为监视用发光元件,并考虑该监视元件的变动来修正提供给发光元件的电压或电流。

[0010] 本发明提供一种显示器件,包括:多个监视用发光元件;检测多个监视用发光元件所具有的电极的电位变化的监视线;以及,在所述多个监视用发光元件的任何一个短路时,以电气方式切断通过监视线而提供给已短路的监视用发光元件的电流的单元。

[0011] 本发明还提供一种显示器件,其中在一个显示用像素中具有多个由几乎相同发光颜色的发光元件形成的子像素,并且具有与所述显示用像素相同结构的监视用像素。设置在该像素中的发光元件和设置在监视用像素中的发光元件具有相同的结构,优选的是在制造工序中同时进行制作。监视用像素内的发光元件对每个子像素分别连接到不同的恒流源。而且,显示装置具有差动放大电路,其用于根据监视用像素内的该发光元件的电位变化,对每个子像素改变施加到显示用像素的发光元件上的电位。

[0012] 通过设置具有与设置在像素中的发光元件相同结构的监视用发光元件,就可以抑

制由于环境温度的改变和随时间进展的退化而导致的亮度不均匀性。由此，就可以实现图像质量改善且使图像质量稳定化。

### 附图说明

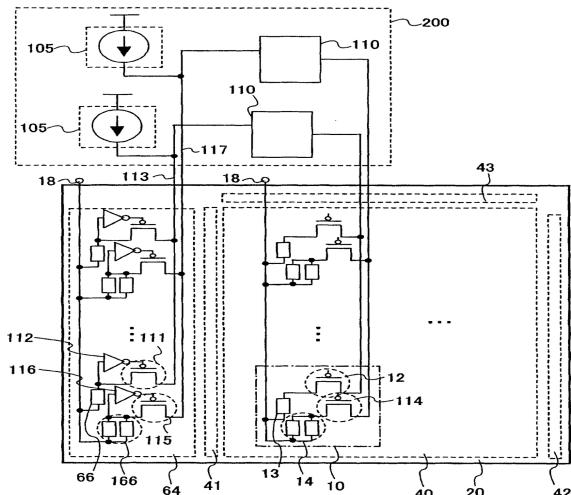

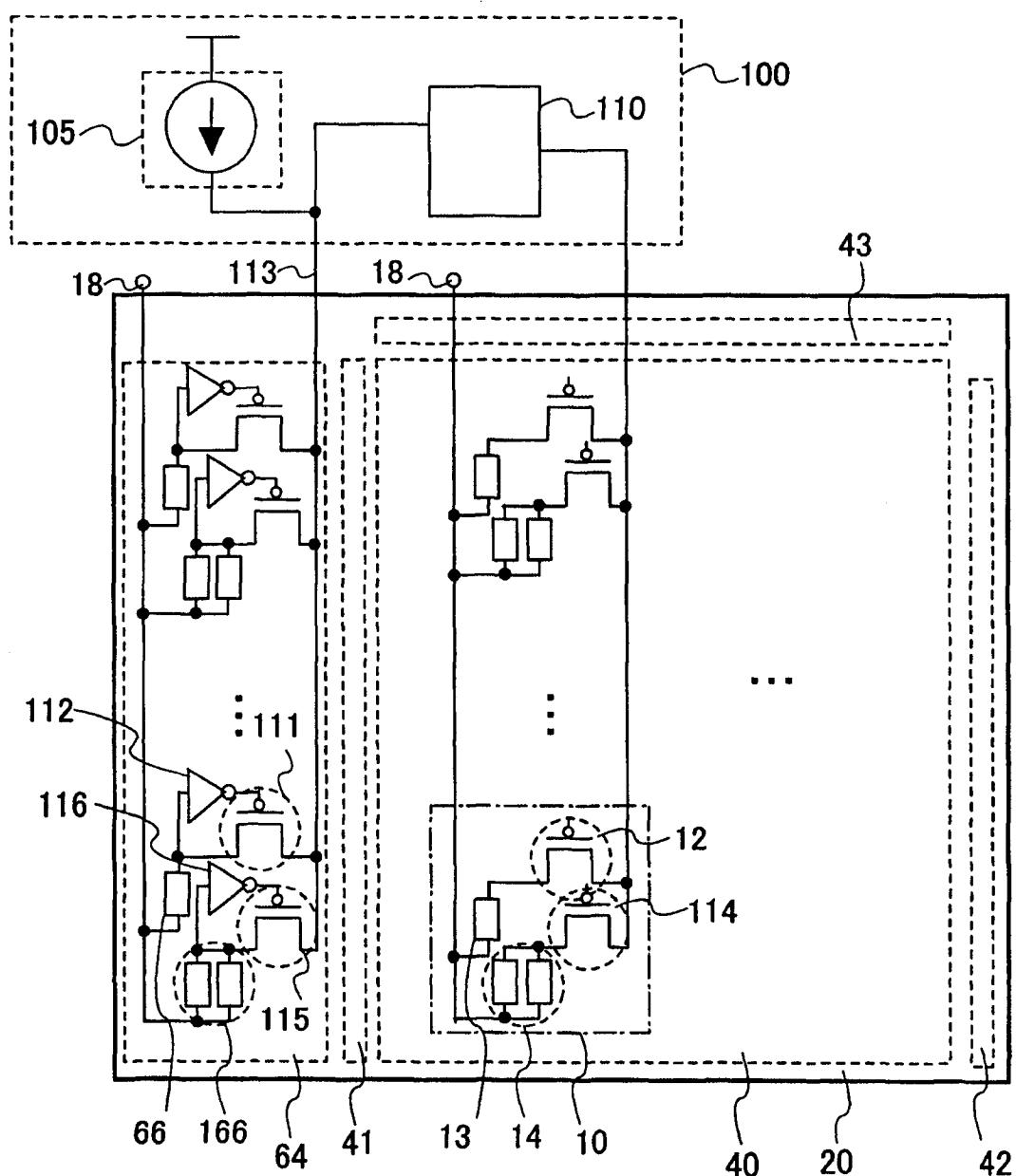

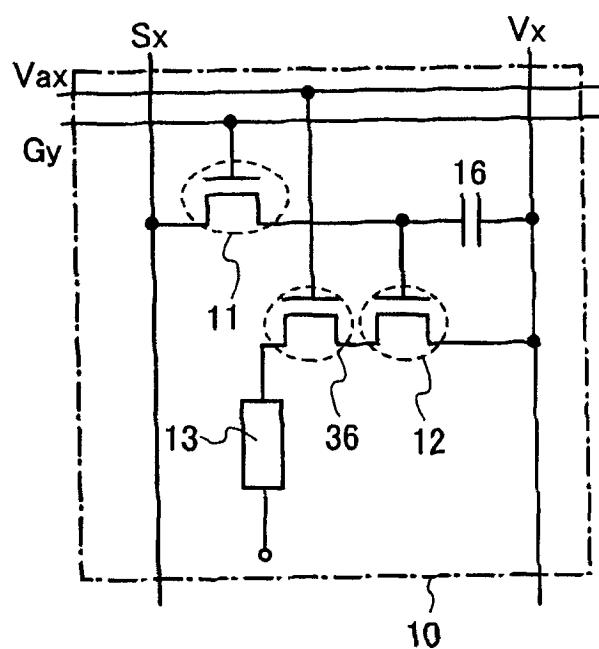

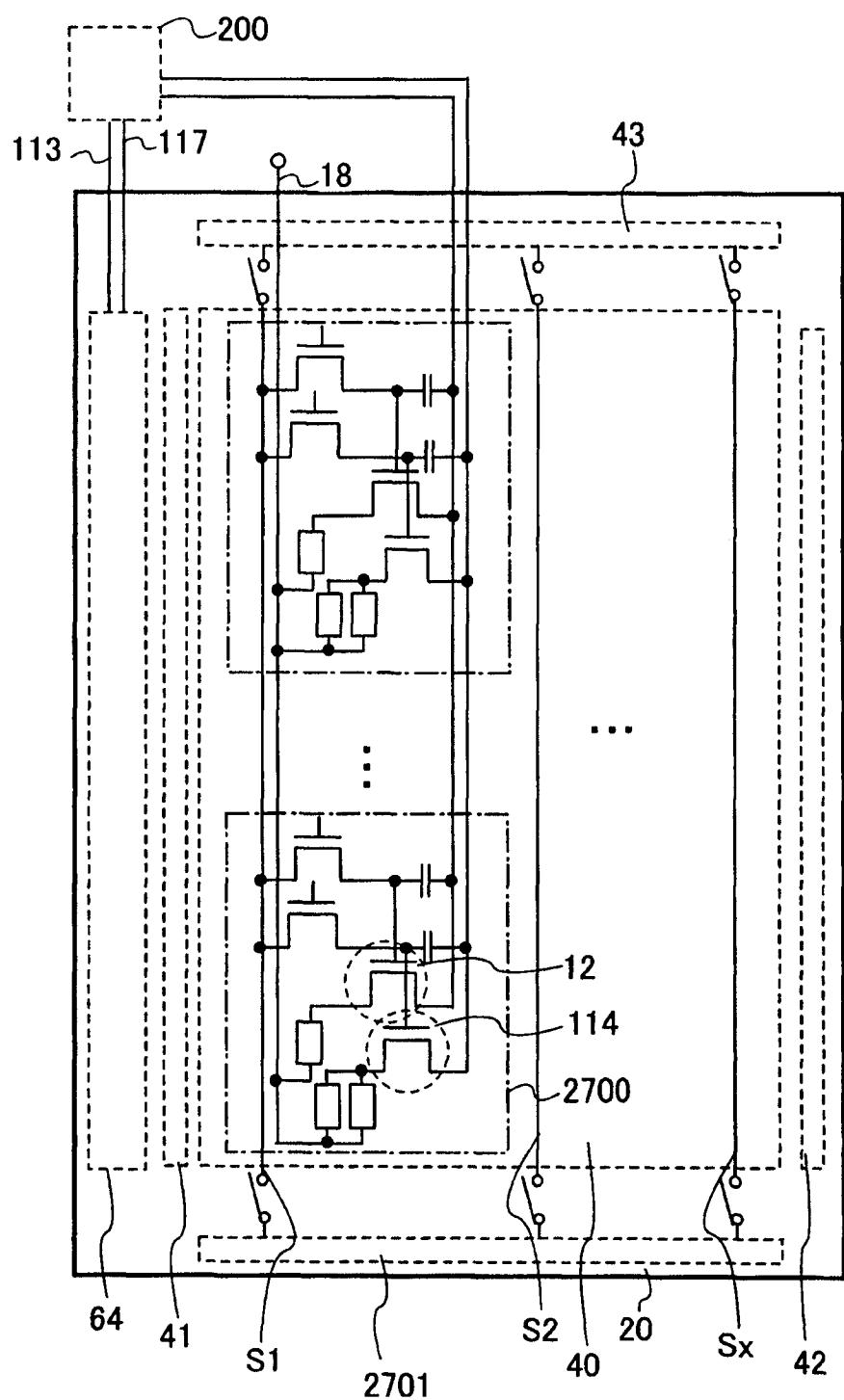

- [0013] 图 1 是表示本发明的显示器件的图；

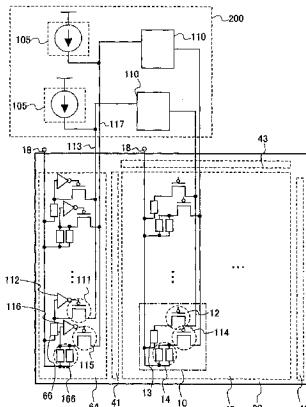

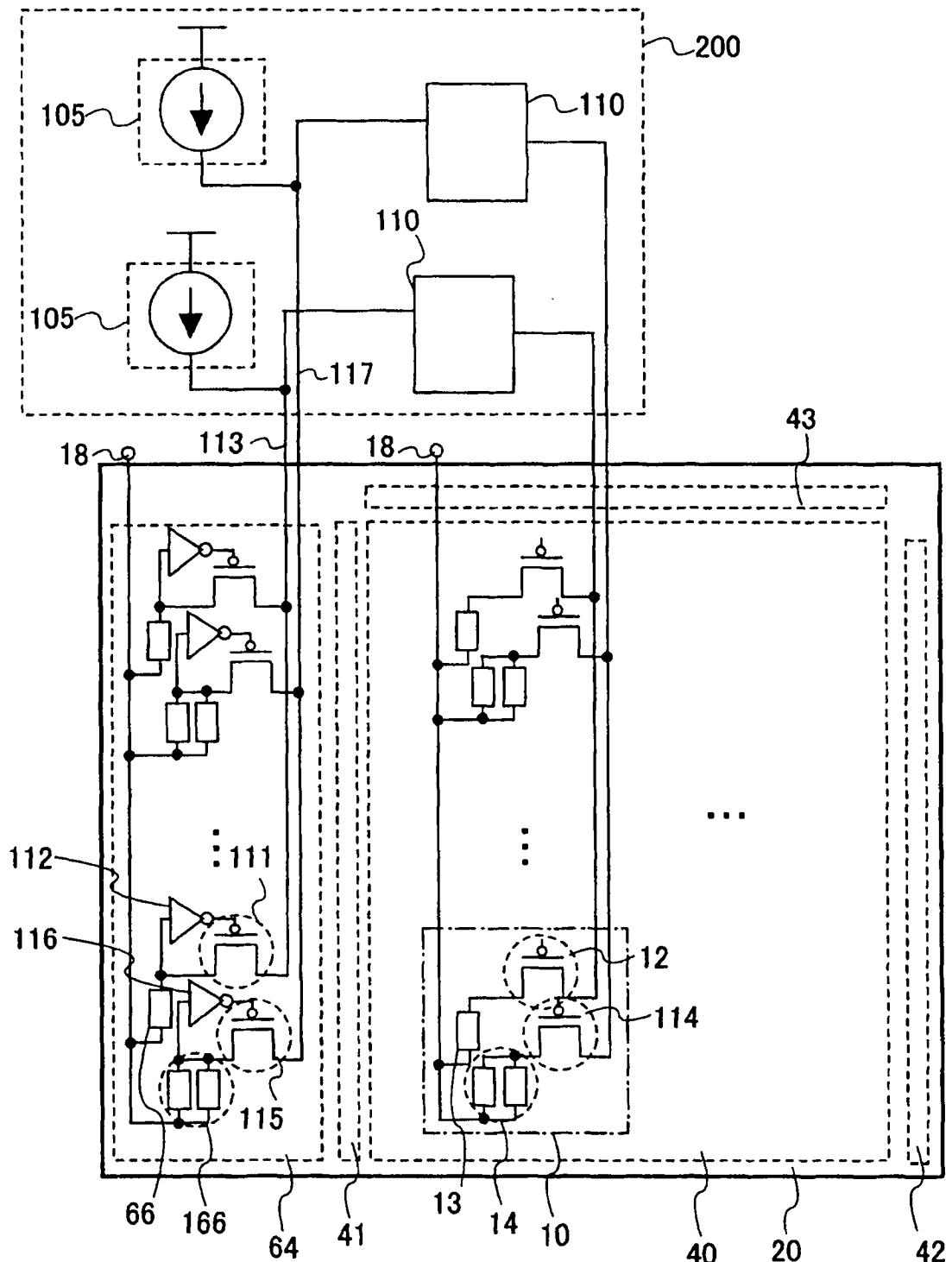

- [0014] 图 2 是表示本发明的显示器件的图；

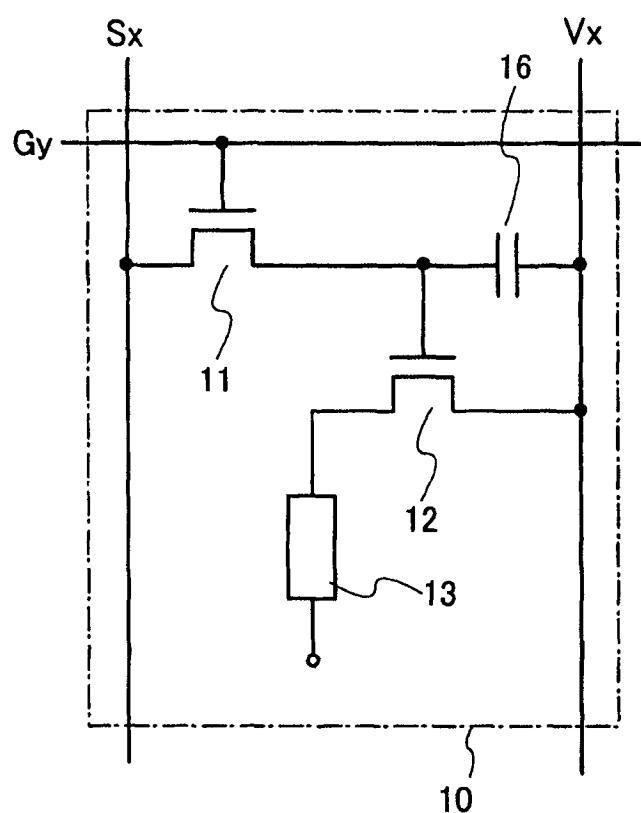

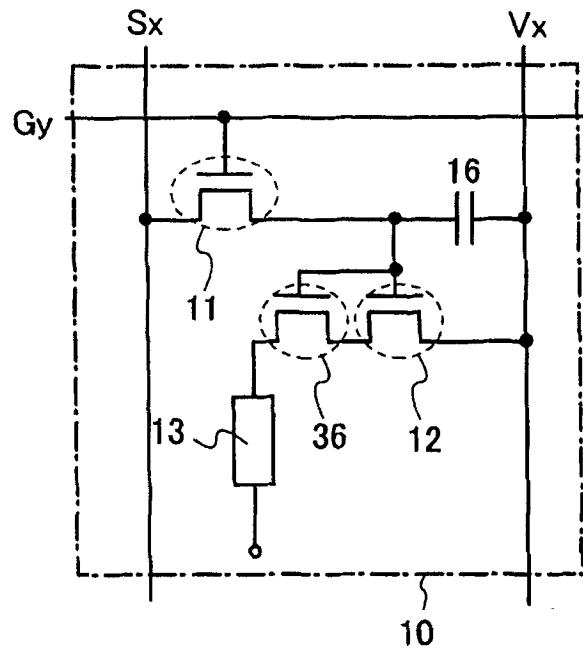

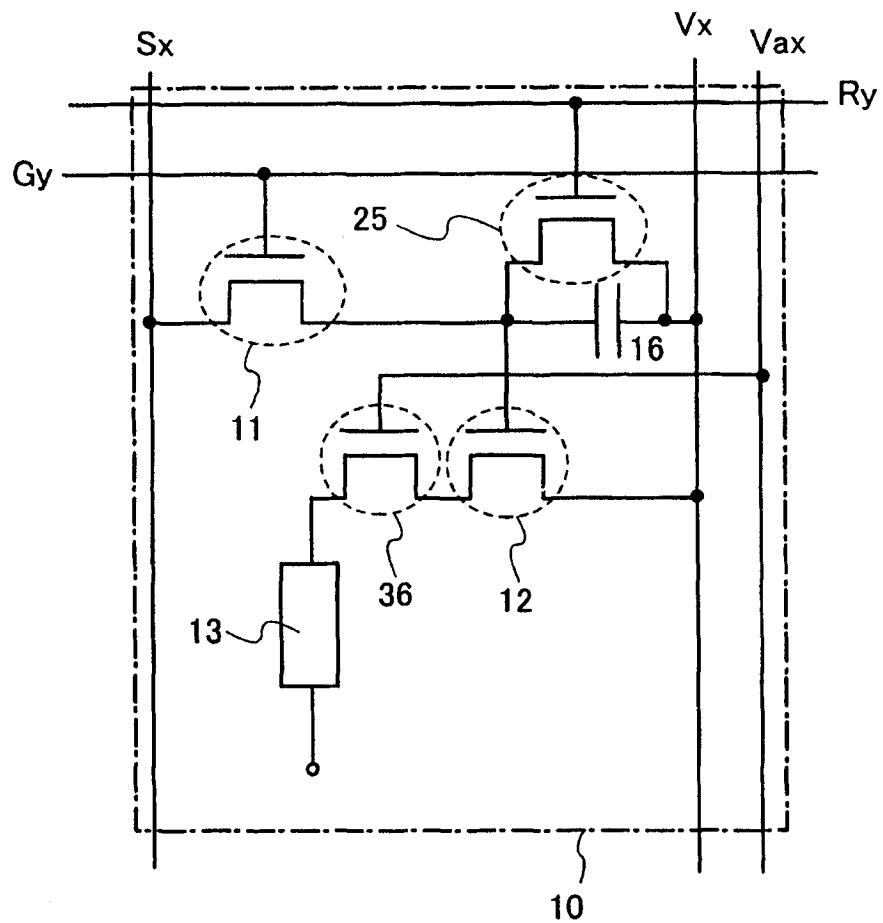

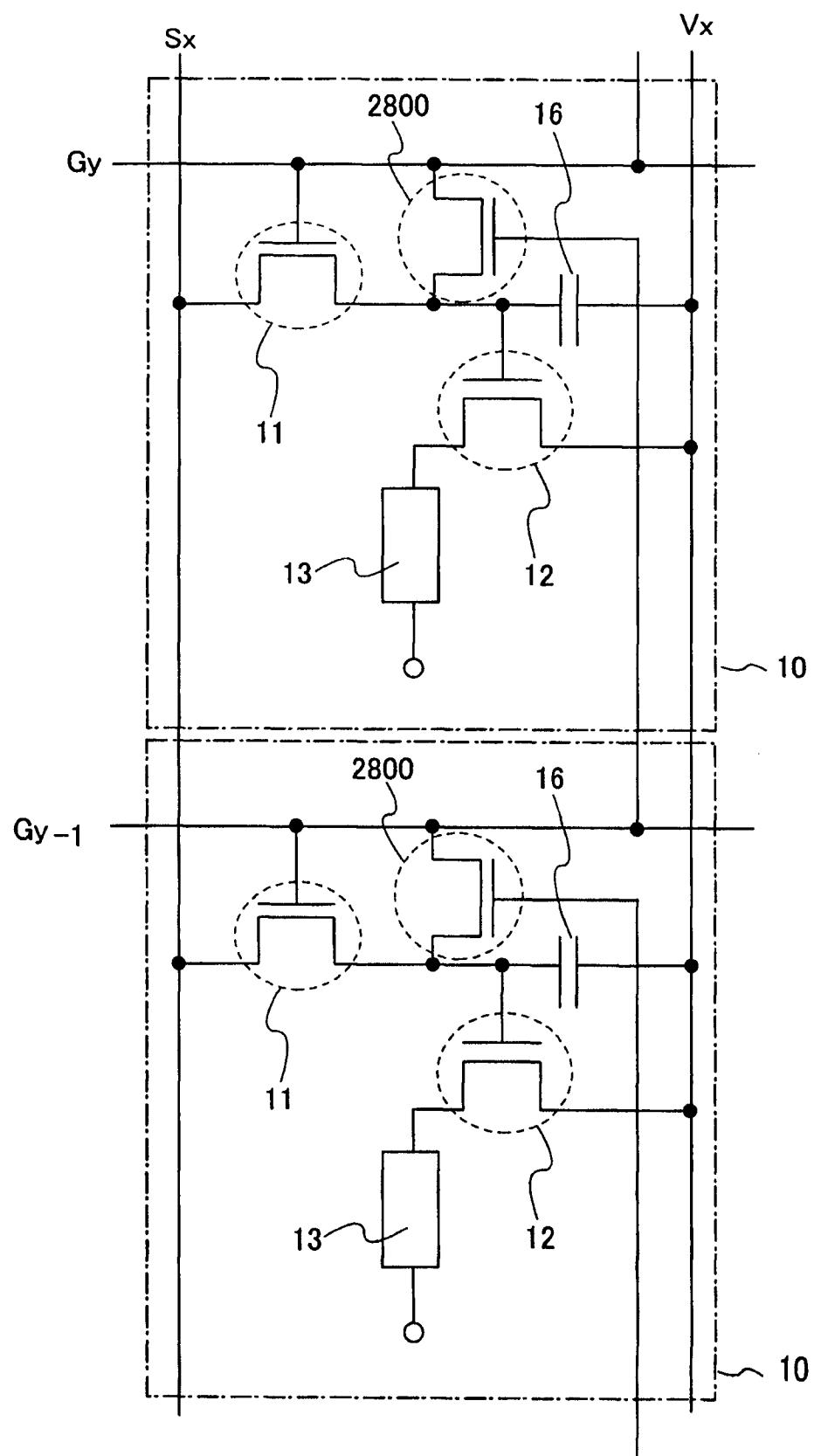

- [0015] 图 3 是表示本发明的像素的等效电路的图；

- [0016] 图 4 是表示本发明的像素的布局的图；

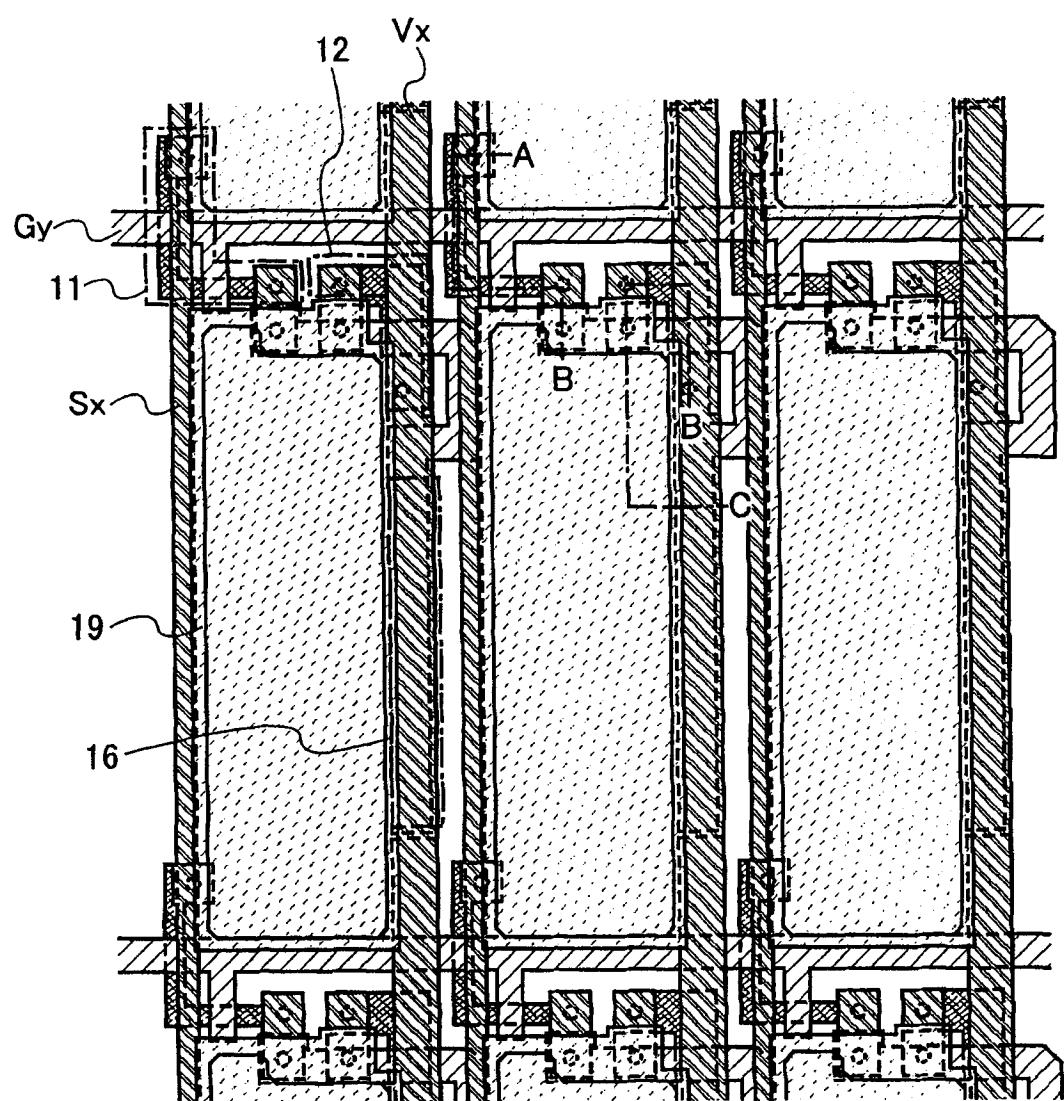

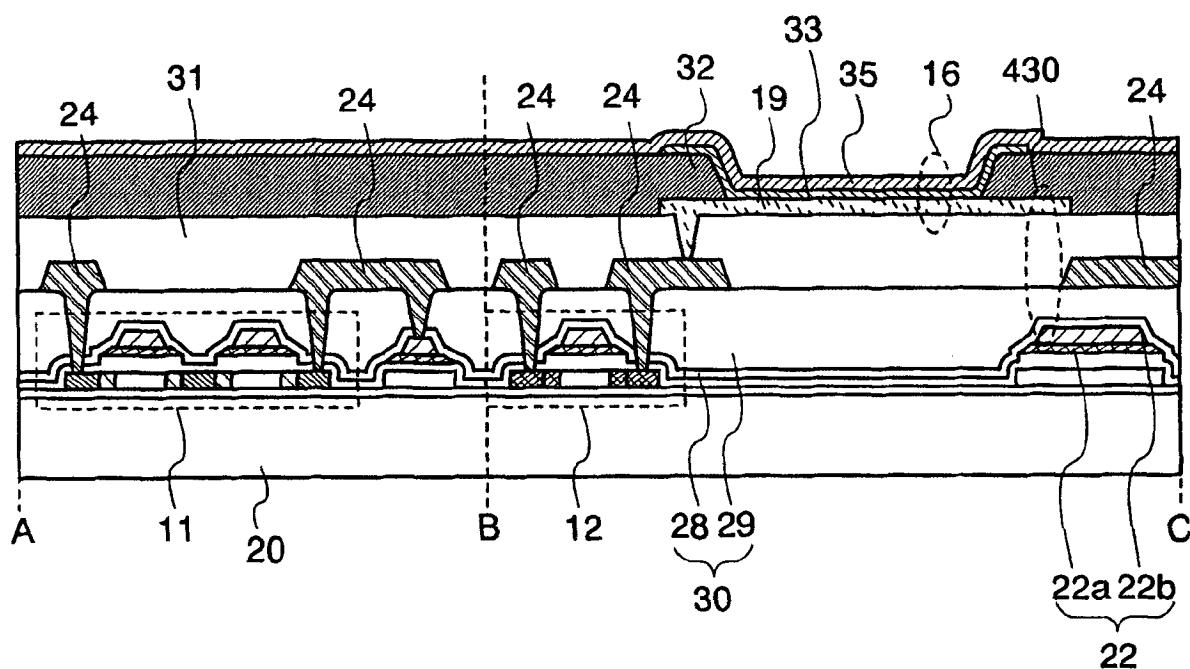

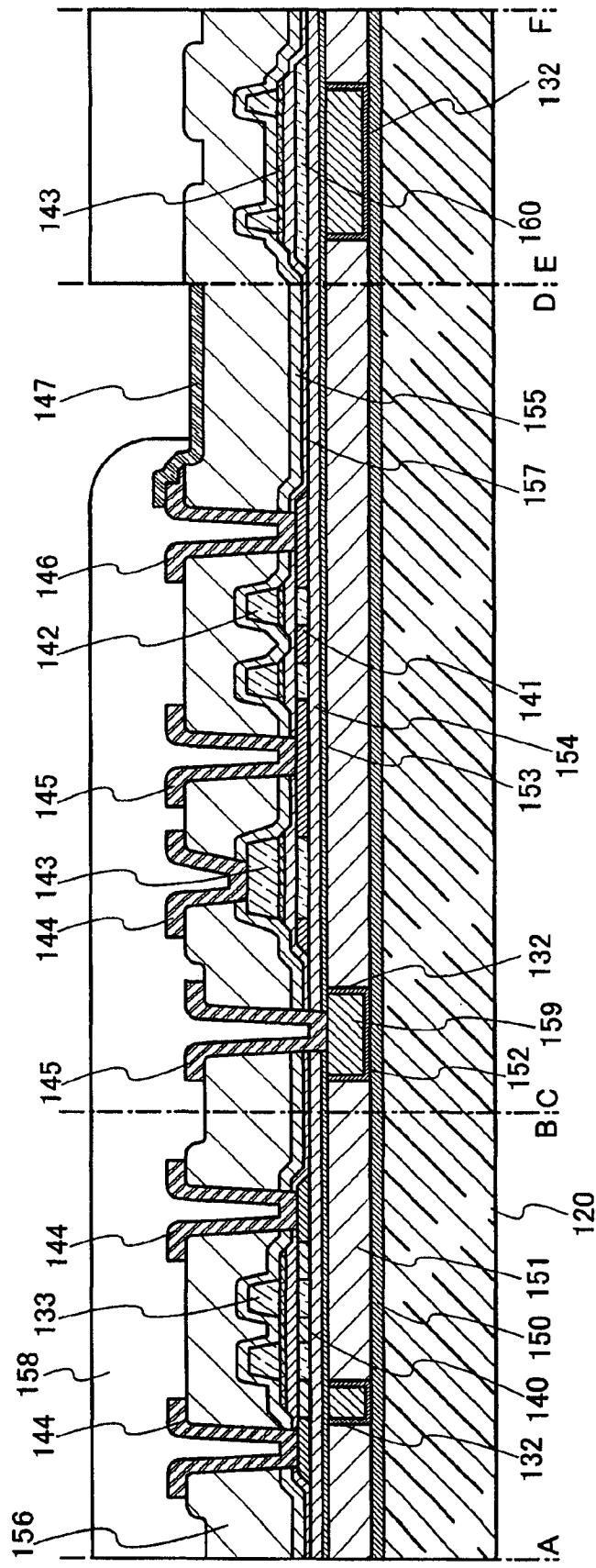

- [0017] 图 5 是表示本发明的像素的截面的图；

- [0018] 图 6A 和 6B 是表示本发明的监视电路的图；

- [0019] 图 7A 和 7B 是表示本发明的监视电路的图；

- [0020] 图 8A 和 8B 是表示本发明的监视电路的图；

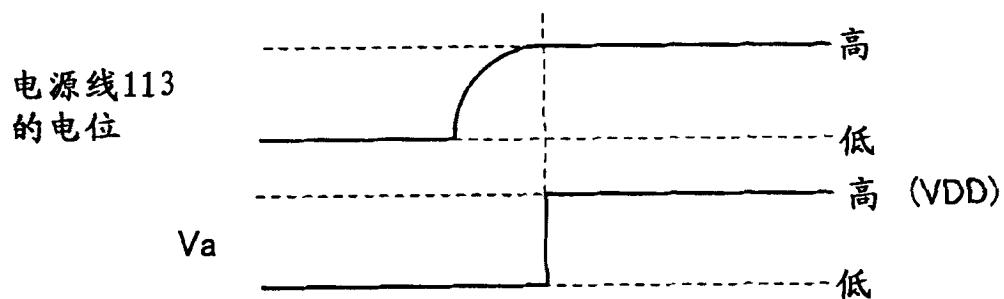

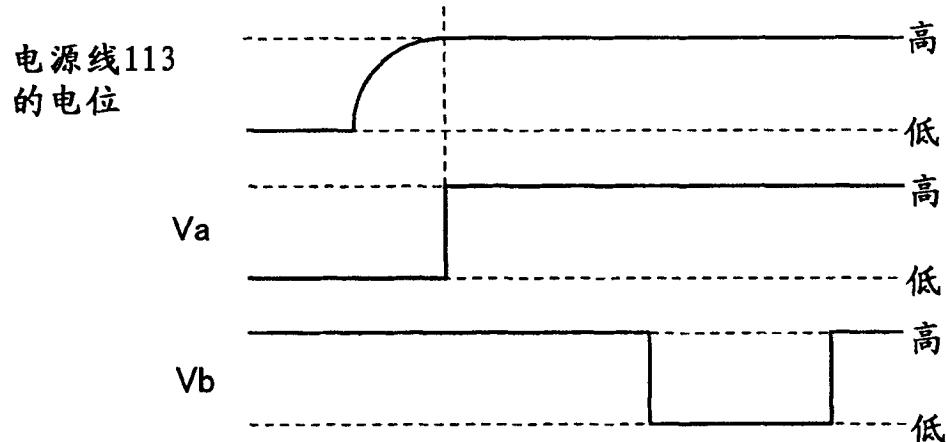

- [0021] 图 9A 和 9B 是表示本发明的定时图的图；

- [0022] 图 10 是表示本发明的像素的等效电路的图；

- [0023] 图 11A 至 11C 是表示本发明的像素的等效电路的图；

- [0024] 图 12 是表示本发明的像素的等效电路的图；

- [0025] 图 13 是表示本发明的面板的图；

- [0026] 图 14 是表示本发明的定时图的图；

- [0027] 图 15A 和 15B 是表示本发明的定时图的图；

- [0028] 图 16A 至 16F 是表示本发明的电子器具的图；

- [0029] 图 17A 至 17C 是表示可以适用本发明的显示器件的一个例子；

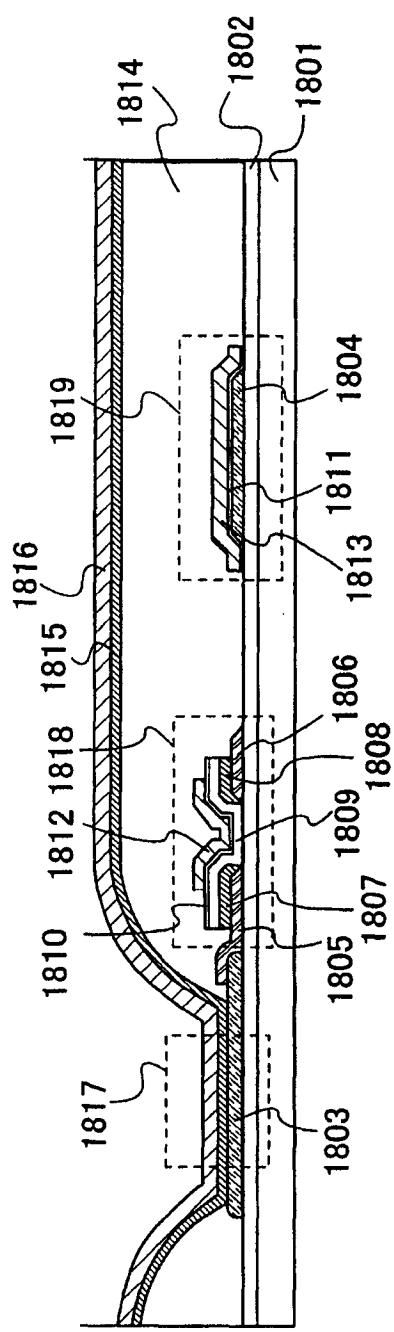

- [0030] 图 18A 和 18B 是表示可以适用本发明的显示器件的一个例子；

- [0031] 图 19A 和 19B 是表示可以适用本发明的显示器件的一个例子；

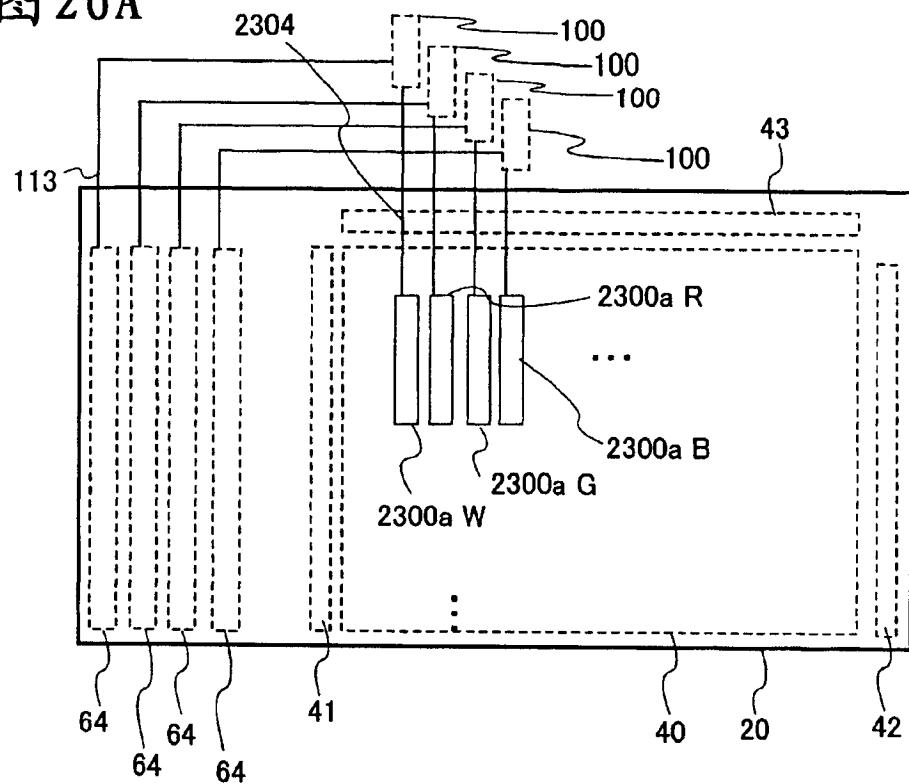

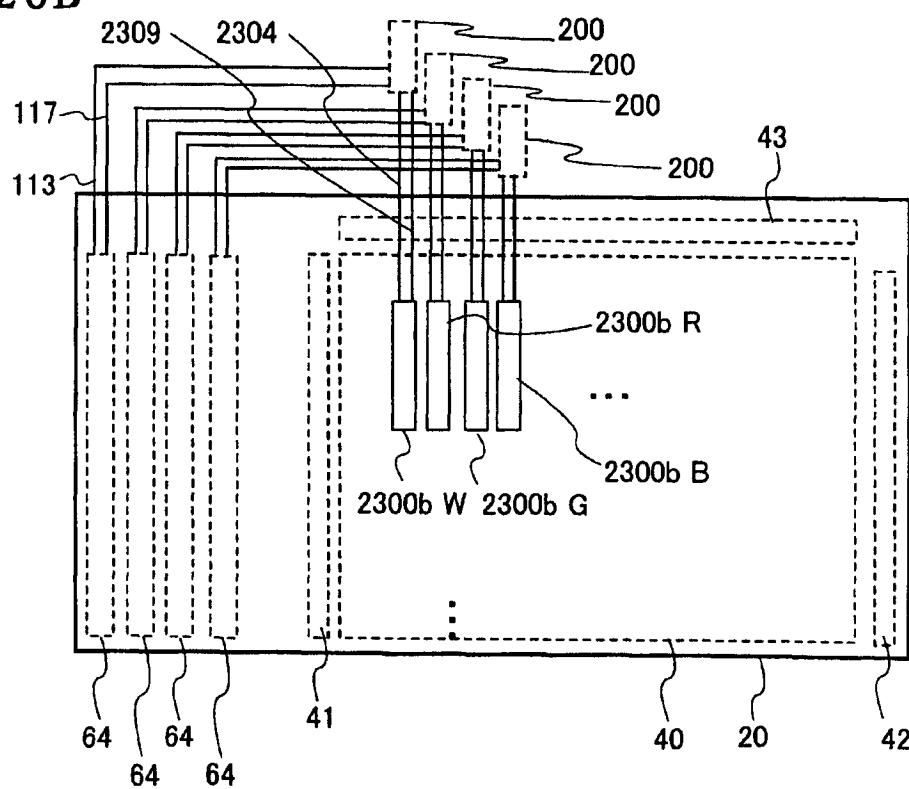

- [0032] 图 20A 和 20B 是表示可以适用本发明的显示器件的一个例子；

- [0033] 图 21 是表示可以适用本发明的显示器件的一个例子；

- [0034] 图 22A 至 22E 是表示可以适用本发明的显示器件的一个例子；

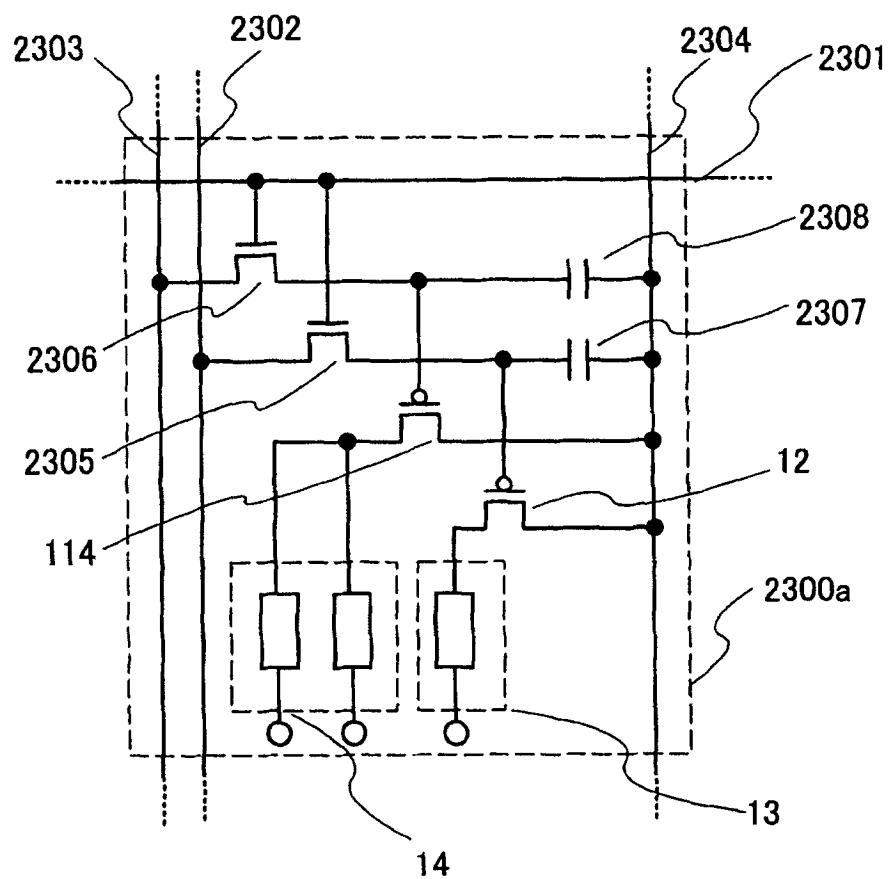

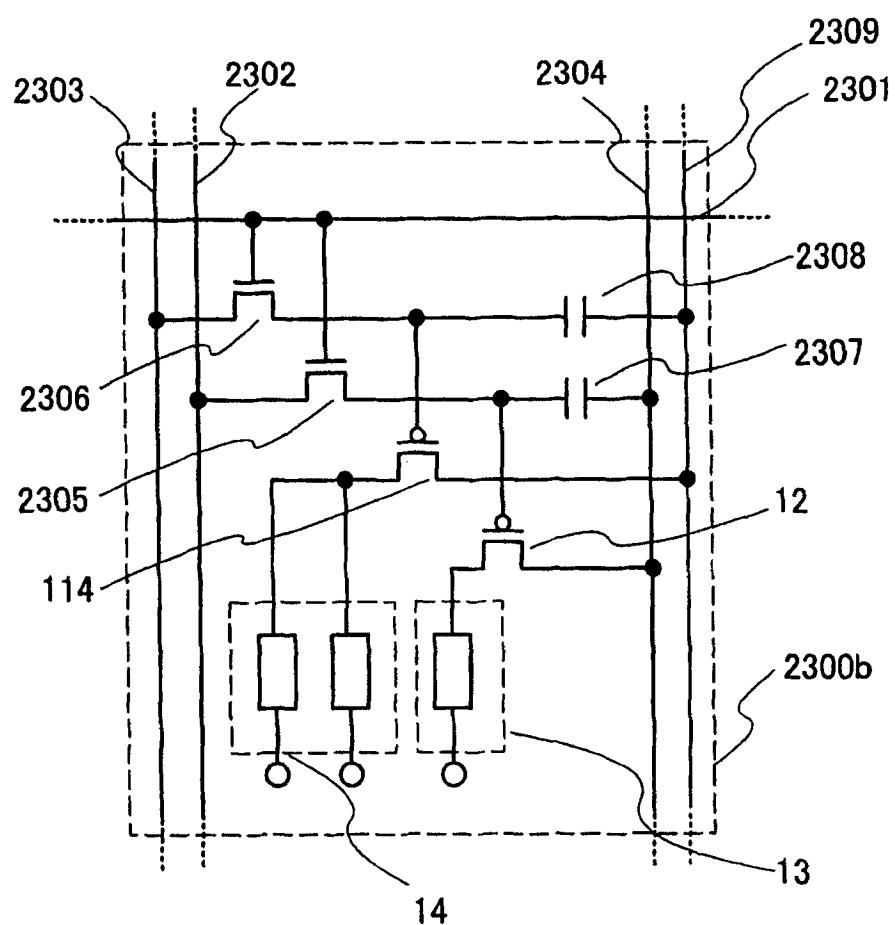

- [0035] 图 23A 和 23B 是表示本发明的像素的等效电路的图；

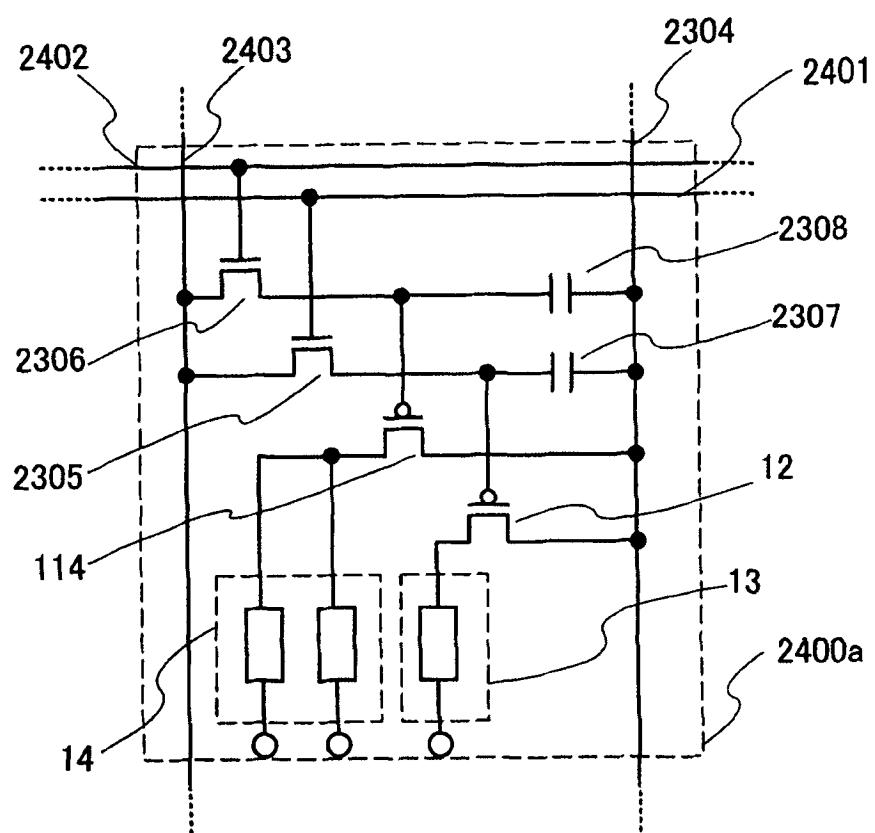

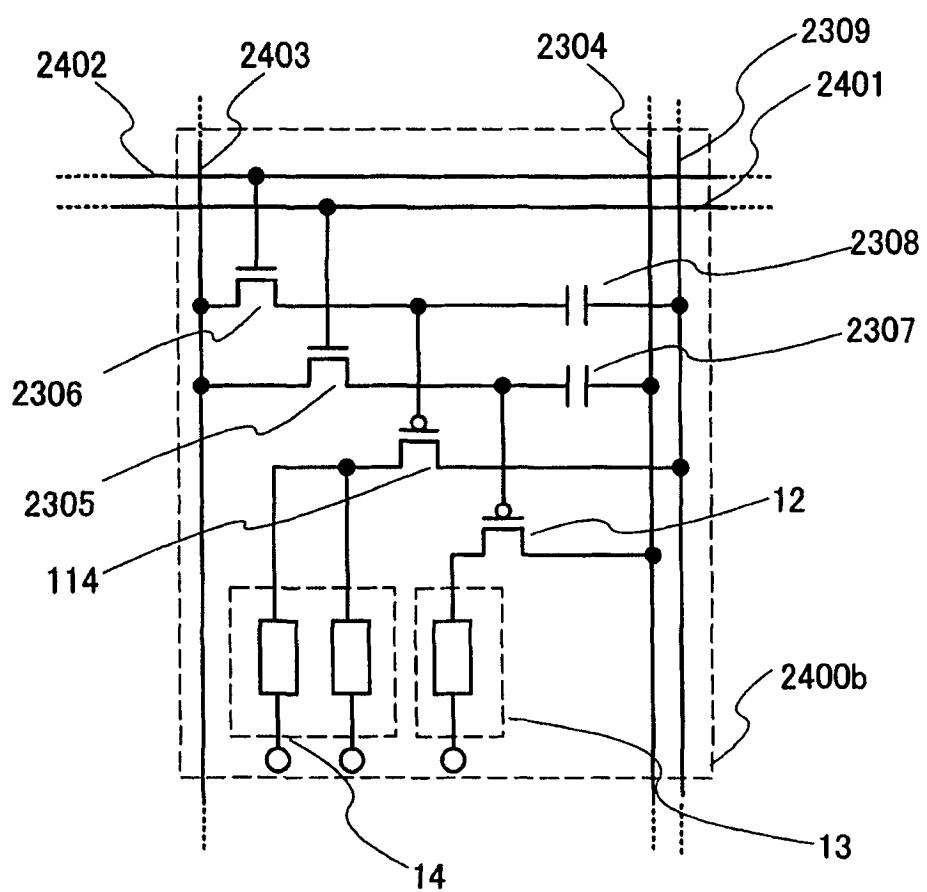

- [0036] 图 24A 和 24B 是表示本发明的像素的等效电路的图；

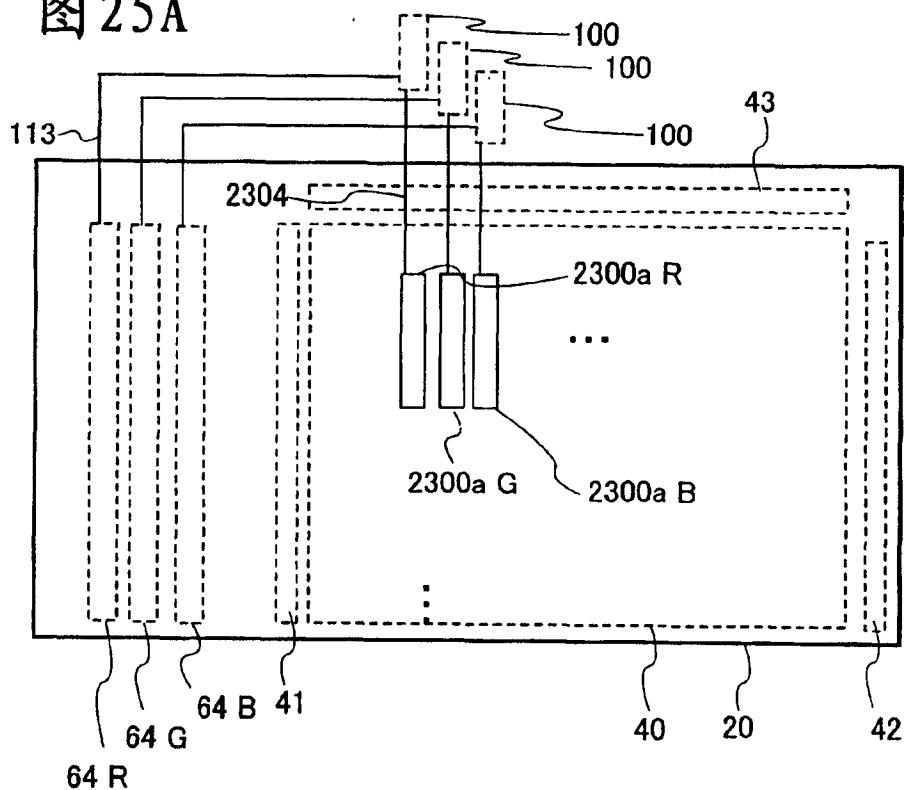

- [0037] 图 25A 和 25B 是表示本发明的显示器件的图；

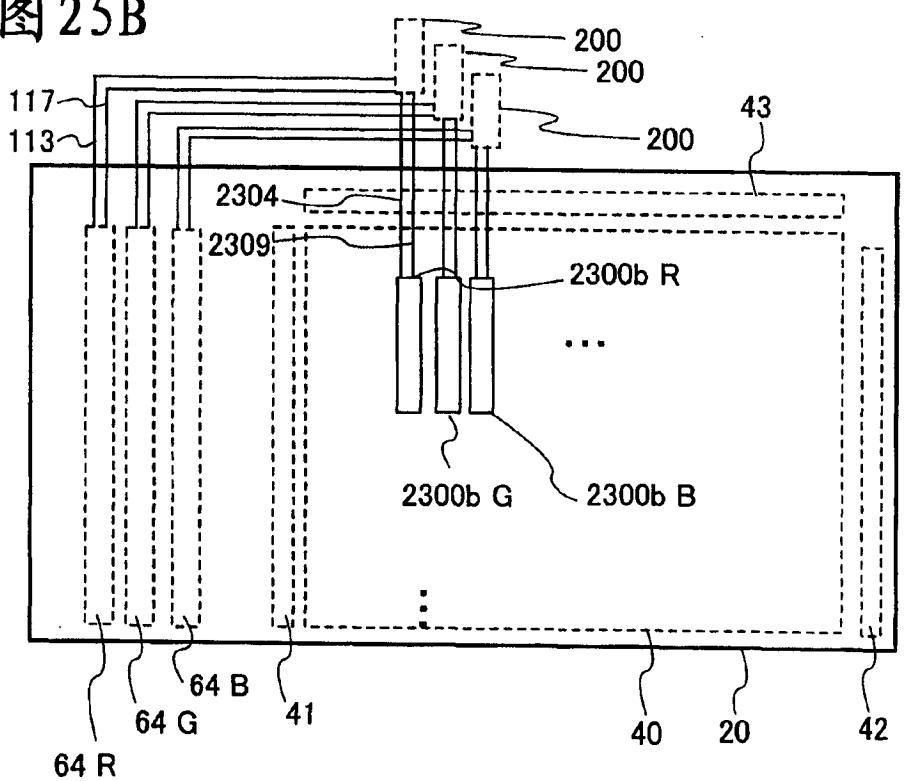

- [0038] 图 26A 和 26B 是表示本发明的显示器件的图；

- [0039] 图 27 是表示本发明的显示器件的图；

- [0040] 图 28 是说明适于将负方向电压施加到驱动晶体管的栅极的像素结构的图；

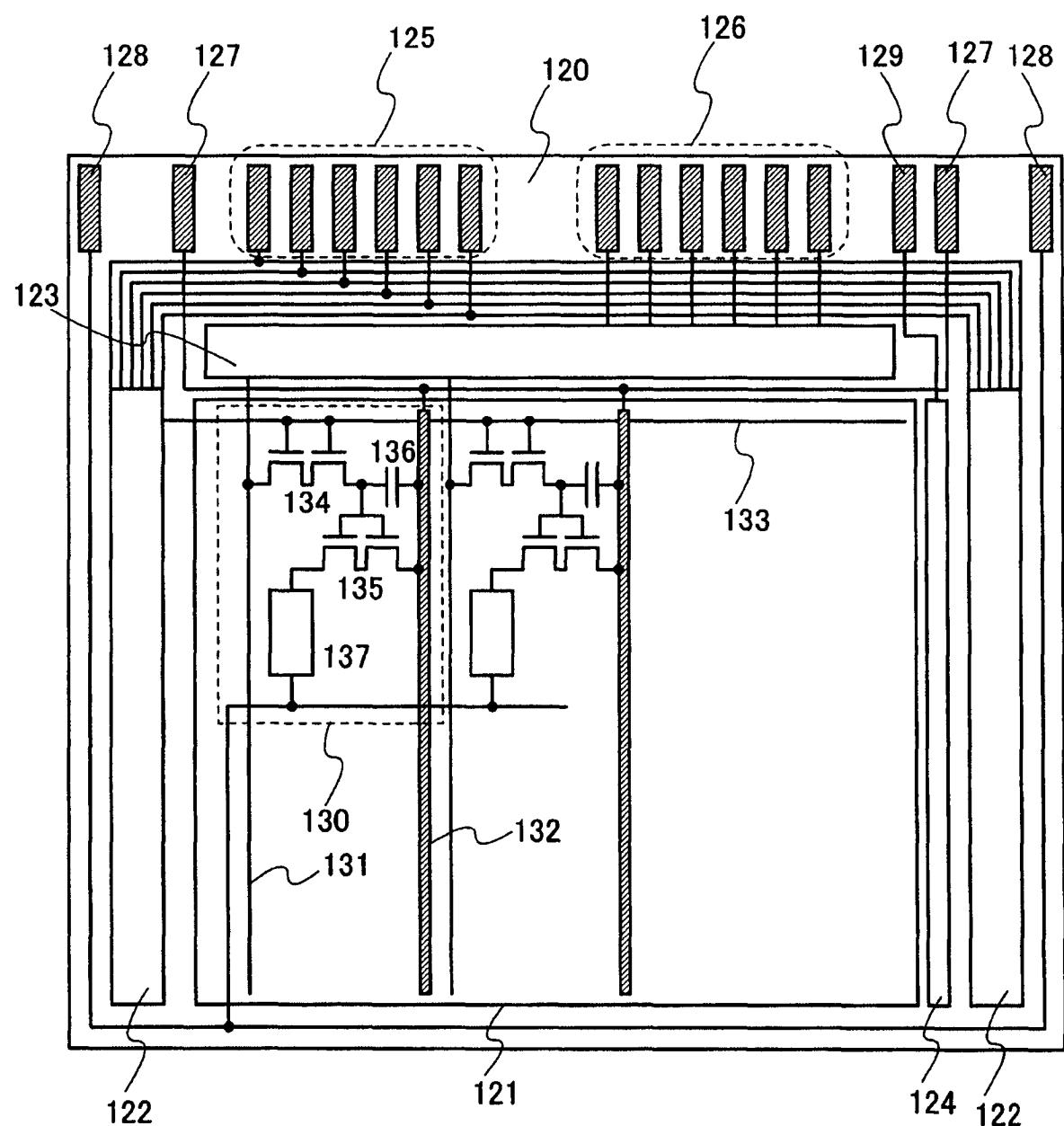

- [0041] 图 29 是说明本发明的显示面板的结构的图；

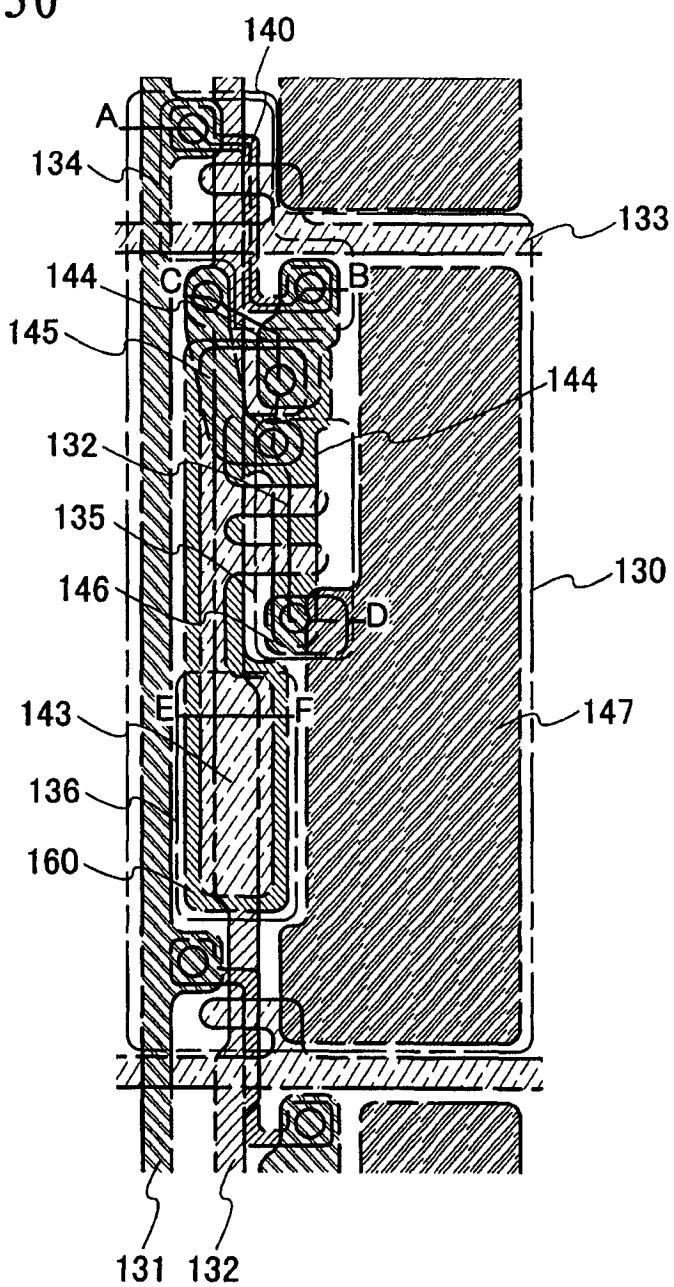

- [0042] 图 30 是说明本发明的显示面板的子像素的结构的图；

- [0043] 图 31 是说明本发明的显示面板的子像素的结构的图；

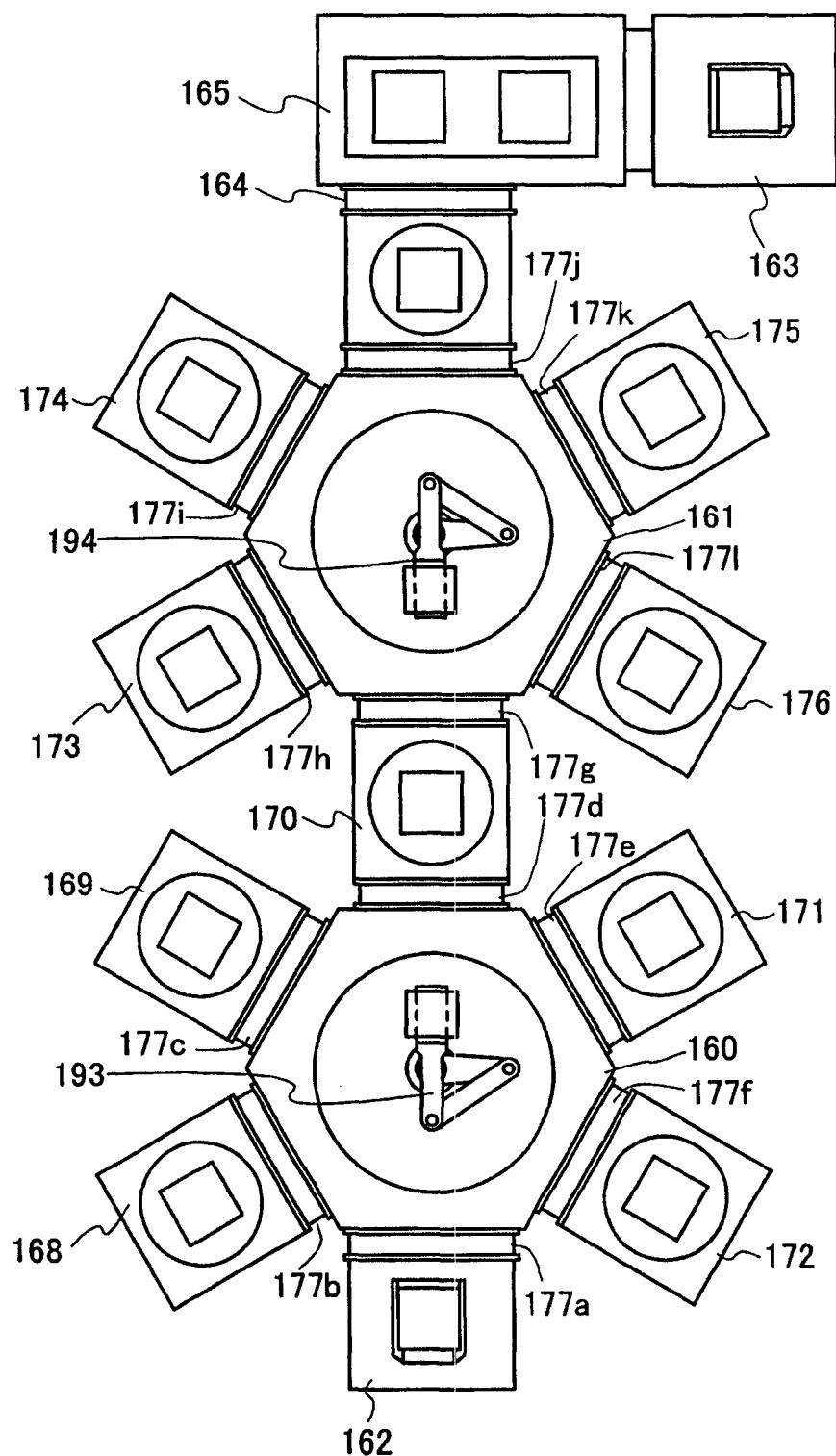

- [0044] 图 32 是表示用于形成 EL 层的蒸镀设备的结构的图；

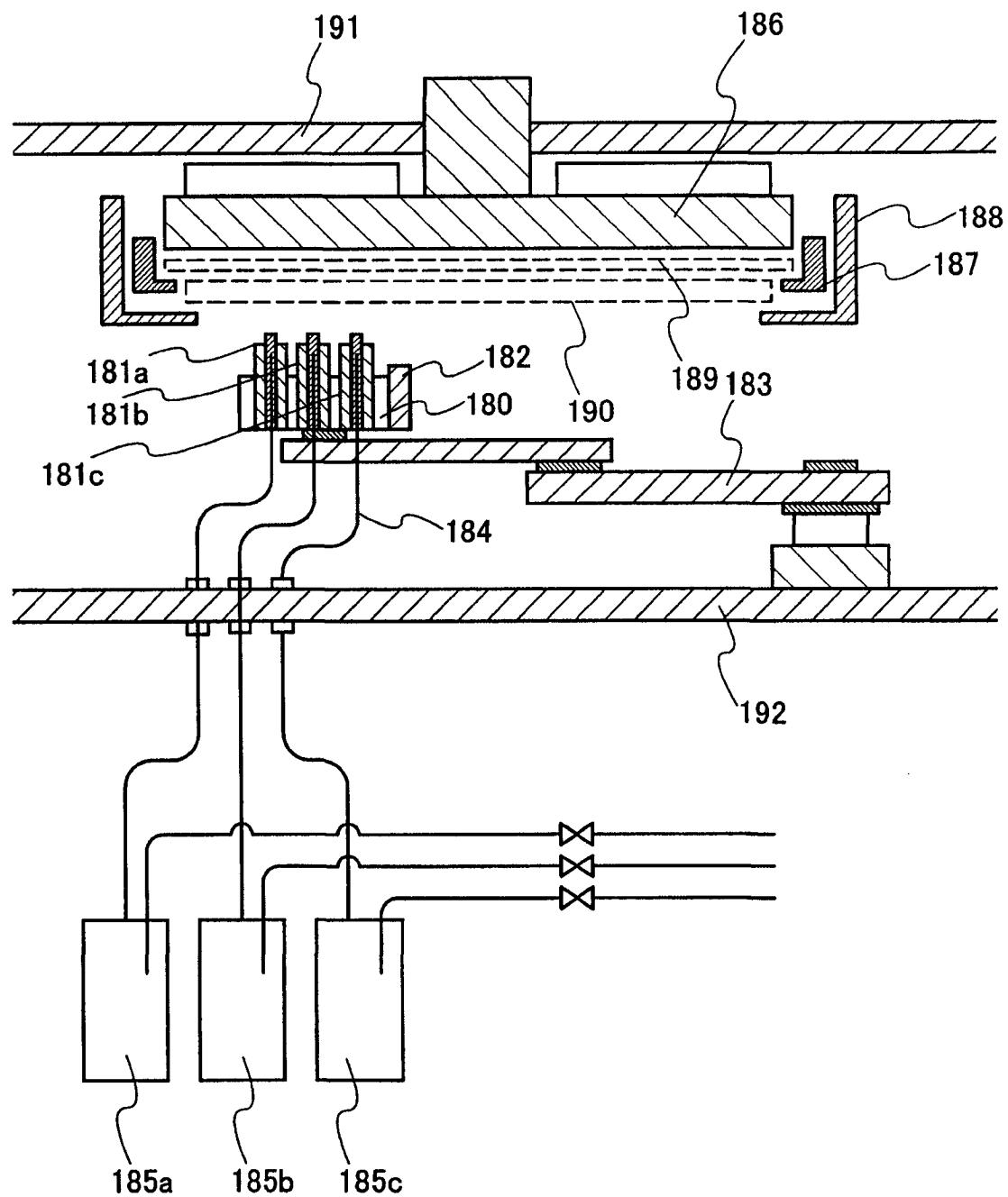

- [0045] 图 33 是表示用于形成 EL 层的蒸镀设备的结构的图。

## 具体实施方式

[0046] 下面将参考附图来详细描述本发明的实施方式。但本发明可以以多种不同的方式来实施，并且只要是本领域技术人员，就很容易了解一个事实，就是可以将本发明的形式和内容更改而不脱离本发明的宗旨和范围。所以，对本发明的解释并不局限于本实施方式中所记载的内容。而且，在用于说明实施方式的全部附图中对相同的部分或者具有同样功能的部分将使用相同的附图标记，并省略相关的重复说明。

[0047] 注意，在本说明书中，各个元件之间的连接是指以电气方式进行连接。因此，在具有连接结构的元件之间有可能通过半导体元件或开关元件等来进行连接。

[0048] 另外，在本说明书中，晶体管的源电极和漏电极是为了在晶体管的结构上方便地区别栅电极之外的电极而采用的名称。在本发明中，当对晶体管的极性没有限制的结构的情况下，若考虑到其极性，源电极和漏电极的名称将会变化。因此，有时将源电极或漏电极记载为一个电极及另一个电极中的某一个。

[0049] (实施方式 1)

[0050] 在本实施方式中，参照附图来说明具有监视用发光元件的面板的结构。

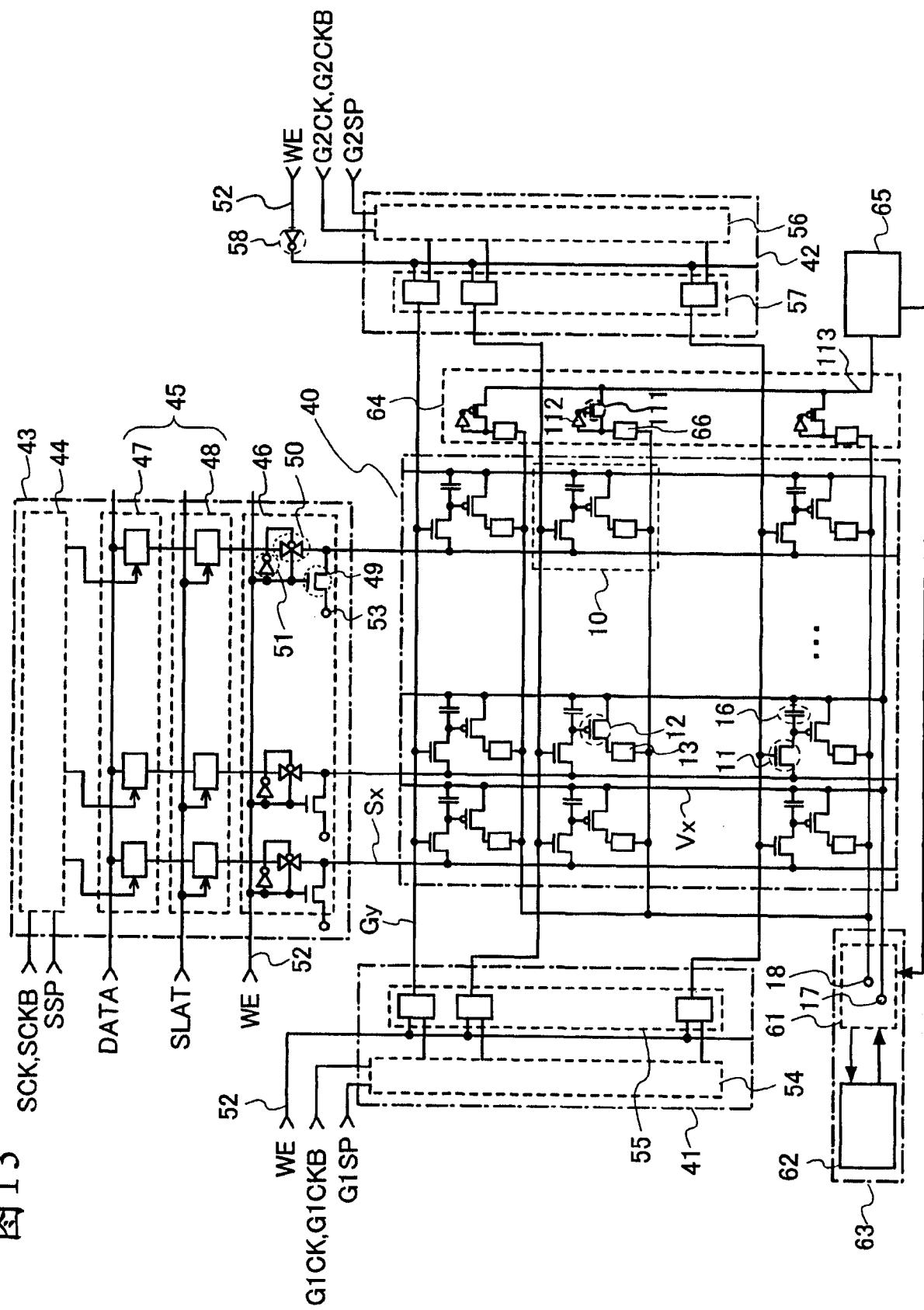

[0051] 图1表示出面板的结构，其中设置有像素部分40、信号线驱动电路43、第一扫描线驱动电路41、第二扫描线驱动电路42以及监视电路64。该面板通过使用绝缘衬底20而形成。

[0052] 像素部分40设置有多个像素10，在各像素中都设置有第一发光元件13以及连接到第一发光元件13并具有控制电流供应之功能的第一驱动用晶体管12。第一发光元件13连接到电源18。另外，在各像素中还可以设置有与所述第一驱动用晶体管12和第一发光元件13处于相同的连接关系的第二驱动晶体管114和第二发光元件14。第二驱动晶体管114和第二发光元件14还可以与第一驱动用晶体管12和第一发光元件13共用电源，并且，并联连接在一起。这里，第二发光元件14还可以是如图1所示那样将具有和第一发光元件相同或几乎相同功能的两个发光元件并联连接的构成。但是，并不局限于此，也可以如第一发光元件13那样使用一个发光元件。另外，还可以采用将三个或更多个发光元件并联连接的结构，而且，这些多个发光元件也可以不具有相同的功能。例如，该多个发光元件可以具有与第一发光元件13不同的发光面积。也就是说，只要在一个像素中，将第二驱动晶体管114和第二发光元件14与第一驱动用晶体管12和第一发光元件13并联连接即可。注意，在下面的实施方式中将举例说明像素10的具体结构。

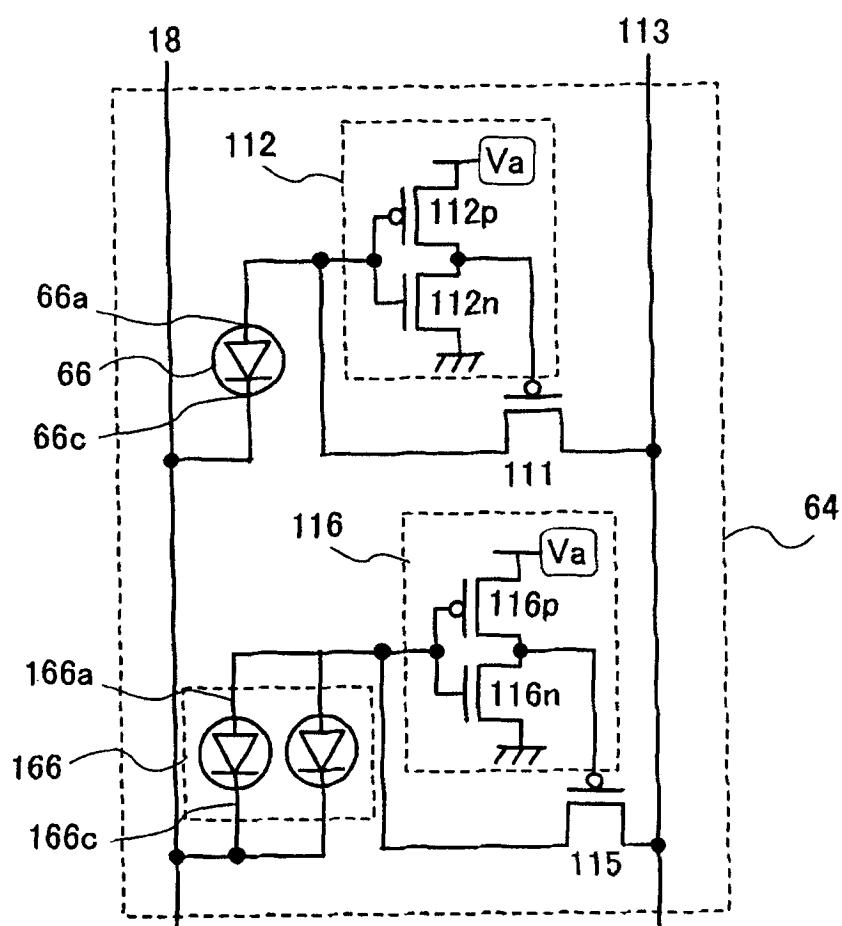

[0053] 监视电路64包括第一监视用发光元件66、连接到第一监视用发光元件66的第一监视控制用晶体管111、以及第一反相器112。该第一反相器112的输出端子连接到第一监视控制用晶体管111的栅电极。并且，第一反相器112的输入端子连接到第一监视控制用晶体管111的源电极和漏电极中的一方以及第一监视用发光元件66上。恒流源105通过电源线113连接到第一监视控制用晶体管111。监视电路64的其他监视控制用晶体管具有用于控制从电源线113向多个监视用发光元件的各自的电流供给的功能。由于电源线113连接到多个监视用发光元件所有的电极上，该电源线113就可具有监视该电极电位之变化的功能。另外，恒流源105只要具有向电源线113提供恒定电流的功能即可。另外，与像素10相同，监视电路64还可以具有使用相同的电源且与第一监视控制用晶体管111、第一监视用发光元件66以及第一反相器112并联连接的第二监视控制用晶体管115、第二监视用发光元件166以及第二反相器116。

[0054] 第一监视用发光元件 66 按照与第一发光元件 13 相同的制作条件、以相同的工序来制造,从而也具有相同的结构。因此,它们对于环境温度的改变和随时间进展的退化具有相同或者几乎相同的特性。该第一监视用发光元件 66 与电源 18 相连接。在这里,由于与第一发光元件 13 连接的电源和连接到第一监视用发光元件 66 的电源为同一电位,因此,采相同的附图标记表示为电源 18。注意,虽然在本实施方式中,设第一监视控制用晶体管 111 的极性为 p 沟道型来进行说明,但是本发明并不限定于此,也可以采用 n 沟道型。在这种情况下,使外围电路结构适当地进行变更。

[0055] 关于第二监视用发光元件 166、第二监视控制用晶体管 115 和第二反相器 116 也同样如此,第二监视用发光元件 166 按照与第二发光元件 14 相同的制作条件、以相同的工序来制造,从而也具有相同的结构。因此,它们对于环境温度的改变和随时间进展的退化具有相同或者几乎相同的特性。该第二监视用发光元件 166 与电源 18 相连接。在这里,由于与第二发光元件 14 连接的电源和连接到第二监视用发光元件 166 的电源为同一电位,因此,采用相同的附图标记记载为电源 18。注意,虽然在本实施方式中,设第二监视控制用晶体管 115 的极性为 p 沟道型来进行说明,但是本发明并不限定于此,也可以采用 n 沟道型。在这种情况下,使外围电路结构适当地进行变更。

[0056] 这种设置监视电路 64 的位置并不限定于此,还可以设置在信号线驱动电路 43 和像素部分 40 之间,或者在第一扫描线驱动电路 41 或第二扫描线驱动电路 42 和像素部分 40 之间。

[0057] 在监视电路 64 和像素部分 40 之间设置有缓冲放大器电路 110。该缓冲放大器电路是指具有输入和输出为相同电位,高输入阻抗以及高输出电流容量之类的特性的电路。因此,只要是具有这种特性的电路,电路结构就可以适当地决定。

[0058] 在这种结构中,缓冲放大器电路具有伴随第一监视用发光元件 66 和第二监视用发光元件 166 的其中一方电极电位的变化,而改变施加到像素部分 40 所有的第一发光元件 13 和第二发光元件 14 的电压的功能。

[0059] 在这种结构中,既可以在相同的绝缘衬底 20 也可以在不同的衬底上设置控制电路 100 内的恒流源 105 和缓冲放大器电路 110。

[0060] 在前述的结构中,从恒流源 105 向第一监视用发光元件 66 和第二监视用发光元件 166 提供恒定电流。当在这种状态下发生环境温度变化或者随时间的退化时,第一监视用发光元件 66 和第二监视用发光元件 166 的电阻值改变。例如,当发生随时间的退化时,第一监视用发光元件 66 和第二监视用发光元件 166 的电阻值增加。于是,由于提供给第一监视用发光元件 66 和第二监视用发光元件 166 的电流值是恒定的,所以第一监视用发光元件 66 和第二监视用发光元件 166 的两端之间的电位差改变。具体而言,在第一监视用发光元件 66 和第二监视用发光元件 166 所有的两个电极之间的电位差改变。此时,由于连接到电源 18 的电极的电位被固定,所以连接到恒流源 105 的电极的电位改变。该电极的电位变化通过电源线 113 被提供给缓冲放大器电路 110。

[0061] 换言之,将上述电极的电位变化输入给缓冲放大器电路 110 的输入端子。又,将从缓冲放大器电路 110 的输出端子输出的电位通过第一驱动用晶体管 12 和第二驱动晶体管 114 提供给第一发光元件 13 和第二发光元件 14。具体而言,被输出的电位作为第一发光元件 13 和第二发光元件 14 所具有的一个电极的电位而提供。

[0062] 通过这样,将与环境温度的变化以及随时间的退化相应的第一监视用发光元件 66 和第二监视用发光元件 166 中的变化反馈给第一发光元件 13 和第二发光元件 14。其结果,第一发光元件 13 和第二发光元件 14 就能够以与环境温度变化以及随时间的退化相应的亮度来点亮。因此,就能够提供一种显示器件,其能够进行不依赖于环境温度变化以及随时间的退化的变化的显示。

[0063] 进而,由于设置了多个第一监视用发光元件 66 和第二监视用发光元件 166,所以能够将它们电位的变化平均化后提供给第一发光元件 13 和第二发光元件 14。换言之,在本发明中,最好是能够通过设置多个第一监视用发光元件 66 和第二监视用发光元件 166 来使电位变化平均化。另外,通过设置多个第一监视用发光元件 66 和第二监视用发光元件 166,就可以做好对于其中发生短路等情况的监视用发光元件进行替换的准备。

[0064] 此外,除了连接到第一监视用发光元件 66 和第二监视用发光元件 166 的第一监视控制用晶体管 111 和第二监视控制用晶体管 115 之外,优选还设置第一反相器 112 和第二反相器 116。这是考虑到由于第一监视用发光元件 66 和第二监视用发光元件 166 中的缺陷(包括初始缺陷和随时间的缺陷)导致的、监视电路 64 的工作不良而设置的。例如,考虑如下情况:当恒流源 105 和第一监视控制用晶体管 111 以及第二监视控制用晶体管 115 不通过其他晶体管等而进行连接时,在多个监视用发光元件之中的某个第一监视用发光元件 66 和第二监视用发光元件 166 因制作工序中的不良等而在该监视用发光元件所具有的阳极和阴极之间导致短路。于是,来自恒流源 105 的电流就通过电源线 113 更多地被提供到已短路的第一监视用发光元件 66 和第二监视用发光元件 166。由于多个监视用发光元件分别并联连接,所以,当较多电流被提供给短路了的第一监视用发光元件 66 和第二监视用发光元件 166 时,对其他的监视用发光元件就不能提供预定的恒定电流。结果,就不能将第一监视用发光元件 66 和第二监视用发光元件 166 的适当的电位变化提供给第一发光元件 13 和第二发光元件 14。

[0065] 这种监视用发光元件的短路就使该监视用发光元件的阳极电位和阴极电位变得相同。例如,在发光元件的制造过程中,有时因阳极和阴极之间的灰尘等而引起短路。此外,除了阳极和阴极之间的短路,还有可能由于扫描线和阳极之间发生短路,而使监视用发光元件发生短路。

[0066] 因此,在本实施方式中,除了第一监视控制用晶体管 111 和第二监视控制用晶体管 115 之外,还设置有第一反相器 112 和第二反相器 116。第一监视控制用晶体管 111 和第二监视控制用晶体管 115 停止向已短路的第一监视用发光元件 66 和第二监视用发光元件 166 供给电流,以便防止上述那样的因第一监视用发光元件 66 和第二监视用发光元件 166 的短路等导致的过量电流的供给。也就是说以电气方式将已短路的监视用发光元件和监视线断开。

[0067] 第一反相器 112 和第二反相器 116 具有当多个监视用发光元件中的任何一个短路时,输出使监视控制用晶体管关断的电位的功能。此外,第一反相器 112 和第二反相器 116 具有当多个监视用发光元件中的任何一个都不短路时,输出使监视控制用晶体管导通的电位的功能。

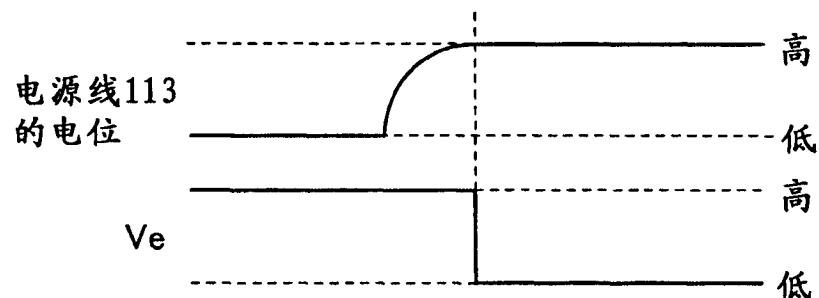

[0068] 利用图 6 来说明监视电路 64 的详细动作。如图 6A 所示,在第一监视用发光元件 66 所包含的电极中,在假定高电位侧为阳极电极 66a 且低电位侧为阴极电极 66c 时,阳极电

极 66a 连接到第一反相器 112 的输入端子，并且阴极电极 66c 连接到电源 18，为固定电位。因此，当第一监视用发光元件 66 所包含的阳极和阴极之间发生短路时，阳极电极 66a 的电位接近阴极电极 66c 的电位。其结果，由于将接近阴极电极 66c 的电位的低电位提供给第一反相器 112，故第一反相器 112 所包含的 p 沟道型晶体管 112p 导通。于是，从第一反相器 112 输出高电位侧的电位 (Va)，并成为第一监视控制用晶体管 111 的栅极电位。换言之，输入到第一监视控制用晶体管 111 的栅极的电位是 Va，第一监视控制用晶体管 111 关断。

[0069] 同样，在第二监视用发光元件 166 所包含的电极中，在假定高电位侧为阳极电极 166a 且低电位侧为阴极电极 166c 时，阳极电极 166a 连接到第二反相器 116 的输入端子，并且阴极电极 166c 连接到电源 18，为固定电位。因此，当第二监视用发光元件 166 所包含的阳极和阴极之间发生短路时，阳极电极 166a 的电位靠近阴极电极 166c 的电位。其结果，由于将靠近阴极电极 166c 的电位的低电位提供给第二反相器 116，故第二反相器 116 所包含的 p 沟道型晶体管 116p 导通。于是，从第二反相器 116 输出高电位侧的电位 (Va)，并成为第二监视控制用晶体管 115 的栅极电位。换言之，输入到第二监视控制用晶体管 115 的栅极的电位是 Va，第二监视控制用晶体管 115 关断。

[0070] 注意，作为高电位 (High) 的 VDD 被设定为与阳极电位相同或比阳极电位更高。此外，第一反相器 112 和第二反相器 116 的低电位 (Low)、电源 18 的电位、电源线 113 的低电位侧的电位以及施加到 Va 的低电位侧的电位可以使之全部具有相同的电位。一般来说，较低侧的电位是接地电位。但是不局限于此，确定较低侧的电位，使其与较高侧的电位具有预定的电位差即可。预定的电位差可以根据发光材料的电流、电压、亮度特性或器件的规格来确定。

[0071] 在此，应该注意的是在第一监视用发光元件 66 和第二监视用发光元件 166 中流过恒定电流的顺序。此时，需要在第一监视控制用晶体管 111 和第二监视控制用晶体管 115 导通的状态下，开始在电源线 113 中流过恒定电流。在本实施方式中，如图 6B 所示，将 Va 保持为 Low 不变，开始在电源线 113 中流过电流。然后，对于 Va 进行设定以便在电源线 113 的电位达到饱和状态之后成为 VDD。其结果，即使在第一监视控制用晶体管 111 和第二监视控制用晶体管 115 导通的状态下，也可以对附带于电源线 113 的电容元件和寄生电容进行充电。

[0072] 另一方面，当第一监视用发光元件 66 和第二监视用发光元件 166 没有短路时，由于阳极电极 66a 和阳极电极 166a 的电位被提供给第一反相器 112 和第二反相器 116，所以 n 沟道型晶体管 112n 和 116n 导通。于是，从第一反相器 112 和第二反相器 116 输出低电位侧的电位，因此，第一监视控制用晶体管 111 和第二监视控制用晶体管 115 导通。

[0073] 根据上述结构，就可以防止将来自恒流源 105 的电流提供给已短路的监视用发光元件。从而，在存在多个监视用发光元件的情况下，当在监视用发光元件中发生了短路时，通过切断向已短路的监视用发光元件的电流供给，就可以将电源线 113 的电位变化抑制到最小限度。其结果，就可以将适当的第一监视用发光元件 66 和第二监视用发光元件 166 的电位变化提供到第一发光元件 13 和第二发光元件 14。

[0074] 注意，在本实施方式中，恒流源 105 只要是能够提供恒定电流的电路就可以，例如，可以使用晶体管来制作恒流源。此外，尽管本实施方式中以监视电路 64 包括多个监视用发光元件、监视控制用晶体管和反相器的方式进行了说明，但本发明并不局限于此。例

如,只要具有当监视用发光元件短路时就检测该情况,并切断通过监视线提供到已短路的监视用发光元件的电流的功能,就可以使用任何电路作为反相器。具体而言,只要具有使监视控制用晶体管关断,以便切断提供到已短路的监视用发光元件的电流的功能即可。

[0075] 此外,本实施方式中,使用多个监视用发光元件。在此情况下,即使监视元件中的某一个发生动作不良,通过其他监视元件进行工作,就可以监视由于环境温度的变化和随时间经过的退化而引起的发光元件的特性变化,来修正像素 10 的发光元件的亮度。

[0076] 在本实施方式中,为了防止电位变动而设置缓冲放大器电路 110。从而,只要是如缓冲放大器电路 110 那样能够防止电位改动的电路,也可以不是该缓冲放大器电路 110 而使用其他的电路。也就是说,当将第一监视用发光元件 66 和第二监视用发光元件 166 的一个电极电位传送到第一发光元件 13 和第二发光元件 14 之际,在第一监视用发光元件 66 和第一发光元件 13 与第二监视用发光元件 166 和第二发光元件 14 之间设置用于防止电位变动的电路时,作为这样的电路并不局限于上述缓冲放大器电路 110,也可以使用具有任何结构的电路,诸如运算放大器电路等。

[0077] 这里,将用图 2 来说明本实施方式之中的其他电路结构。图 2 所示的电路结构,在每个像素 10 和监视电路 64 中的元件配置上与图 1 相同,但是电源的连接方法与图 1 不同。也就是说,不仅是图 1 中所示的共同电源线 113 还追加电源线 117,以对每个子像素通过独立的电源来进行驱动。如此,在本实施方式中,还可以将电源线按每个子像素独立地进行连接。此时,还可以将恒流源 105 和缓冲放大器电路 110 独立配置在各个电源中。

[0078] 如此,作为对每个子像素配置电源线、连接到该电源线的控制电路 200 内的恒流源 105 以及缓冲放大器电路 110 的优点,可举出通过对每个子像素设定流过监视元件的电流值就可以提高修正精度。在使用本实施方式所示那样的子像素来进行面积灰度级显示时,第一发光元件 13 和第二发光元件 14 可以具有不同的特性。例如,在给两者的子像素上施加相同电压的情况下,使一方的子像素的发光元件的亮度设定为另一方的子像素的两倍时,能够显示亮度比为 0、1、2、3 的 4 种灰度级,而无须改变驱动电压或发光占空比。这样,在使各个子像素中的发光元件具有不同的特性时,因它们退化或温度而引起的特性变化的情形在双方未必相同。因此,通过组合具有不同的特性的元件而引起的特性就变化非常复杂。为了更准确地进行修正,按特性类似的元件进行分组比较有效果。如果在每个子像素中配置电源线、与该电源线连接的恒流源 105 和缓冲放大器电路 110,并且使第一监视用发光元件 66 和第二监视用发光元件 166 具有与像素 10 相同的特性,就可以实现进一步准确的修正。

[0079] 注意,虽然在本实施方式中,只表示采用两个子像素的情况,但子像素的数量并不局限于此。只要并联连接起来,几个子像素都可以。

[0080] (实施方式 2)

[0081] 在本实施方式中,将说明与上述实施方式不同的,当监视用发光元件短路时关断监视控制用晶体管的电路结构及其动作。注意,虽然在实施方式 1 中用包括子像素的像素电路进行了说明,但本实施方式中将说明当配置在各子像素中的监视用发光元件短路时关断监视控制用晶体管的电路结构,所以,在此说明每一个像素中的电路,而省略重复的说明。

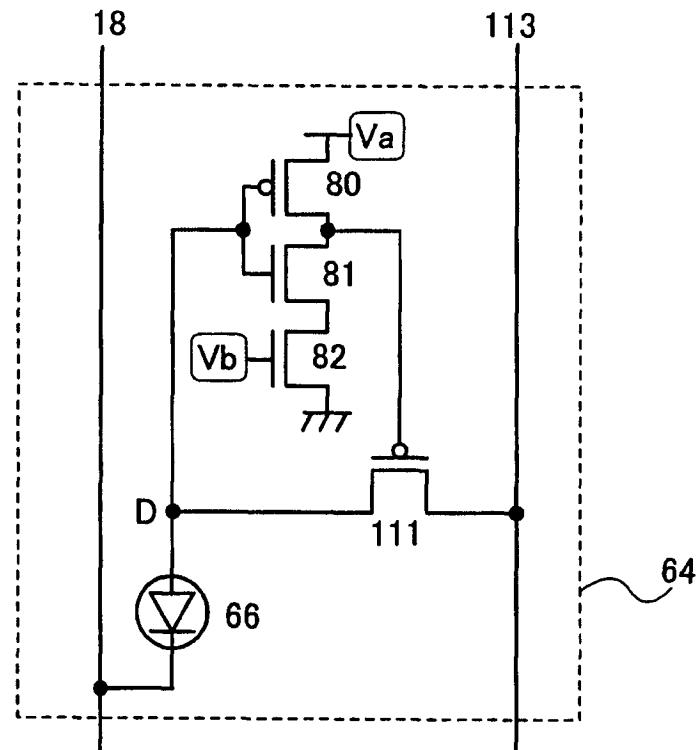

[0082] 图 7A 所示的监视电路 64 包括 p 沟道型的第一晶体管 80、具有与第一晶体管 80 共

用栅电极且与第一晶体管 80 并联连接的 n 沟道型的第二晶体管 81、与第二晶体管 81 串联连接的 n 沟道型的第三晶体管 82。监视用发光元件 66 连接到第一和第二晶体管 80、81 的栅电极。监视控制用晶体管 111 的栅电极连接到第一和第二晶体管 80、81 的互相连接起来的电极。其他结构与图 6A 所示的监视电路 64 一样。但是,在此只表示包括监视控制用晶体管 111 和监视用发光元件 66 的子像素。

[0083] 另外,设第一 p 沟道型晶体管 80 的高电位侧的电位为 Va,第三 n 沟道型晶体管 82 的栅电极电位为 Vb。而且,使电源线 113 的电位、以及 Va、Vb 的电位如图 7B 所示那样进行动作。

[0084] 首先,使附随于电源线 113 的电容元件和寄生电容成为完全进行了充电的状态,之后,使 Va 的电位为 High。在监视用发光元件 66 短路了的情况下,使监视用发光元件 66 的阳极电位,即点 D 的电位,降低到和监视用发光元件 66 的阴极相同的程度。于是,低电位即 Low 电位被输入到第一和第二晶体管 80、81 的栅电极,n 沟道型的第二晶体管 81 关断,p 沟道型的第一晶体管 80 导通。而且,第一晶体管 80 的一方的电位、即较高侧的电位被输入到监视控制用晶体管 111 的栅电极,使监视控制用晶体管 111 关断。其结果,来自电源线 113 的电流就不被供给到已短路的监视用发光元件 66 中。

[0085] 此时,在因短路状态微小而使阳极电位略微降低的情形中,有可能难以控制第一和第二晶体管 80、81 中的某一个为导通或关断。因此,如图 7A 所示,将 Vb 的电位供给到第三晶体管 82 的栅电极。也就是说,如图 7B 所示,当 Va 为 High 期间,使 Vb 的电位为 Low。于是,n 沟道型的第三晶体管 82 关断。其结果,一旦阳极电位为比 VDD 降低第一晶体管的阈值电压的电位时,就可以使第一晶体管 80 导通,而且可以使监视控制用晶体管 111 关断。

[0086] 这样,通过控制 Vb 的电位,即使在阳极电位略微降低时也可以正确地使监视控制用晶体管 111 关断。注意,在监视用发光元件正常工作时,使监视控制用晶体管 111 为导通这样来进行控制。也就是说,由于阳极电位与电源线 113 的高电位几乎相同,所以第二晶体管 81 导通。其结果,低电位被施加到监视控制用晶体管 111 的栅电极,从而导通。

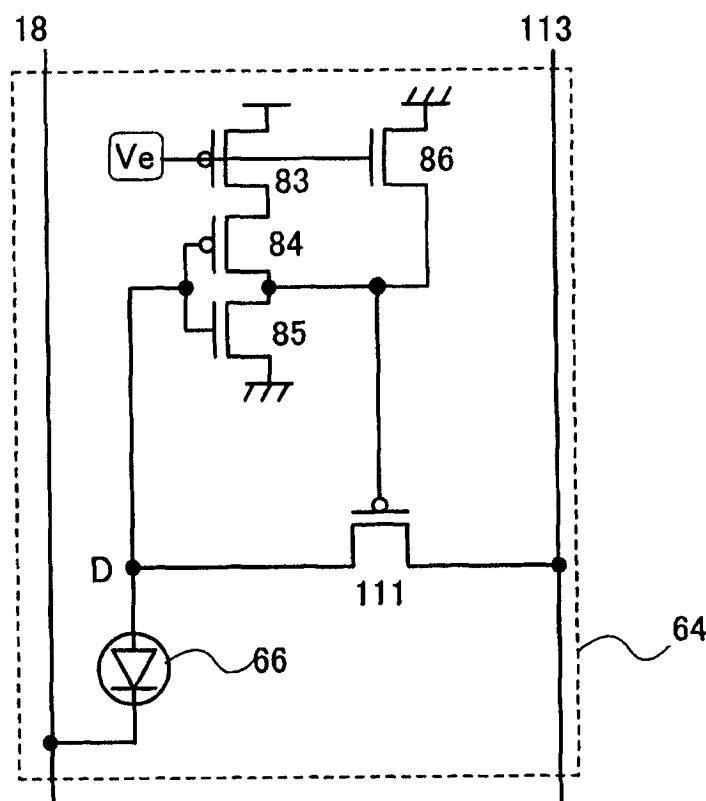

[0087] 如图 8A 所示,监视电路 64 包括 p 沟道型的第一晶体管 83、与第一晶体管 83 串联连接的 p 沟道型的第二晶体管 84、与第二晶体管 84 共用栅电极的 n 沟道型的第三晶体管 85、与第一晶体管共用栅电极且与第一晶体管并联连接的 n 沟道型的第四晶体管 86。监视用发光元件 66 连接到第二和第三晶体管 84、85 的栅电极。监视控制用晶体管 111 的栅电极连接到第二和第三晶体管 84、85 的互相连接起来的电极。而且,监视控制用晶体管 111 的栅电极连接到第四晶体管 86 的一个电极。其他结构与图 6 所示的监视电路 64 一样。

[0088] 首先,在将附随于电源线 113 的电容元件和寄生电容完全充电之后,使 Ve 的电位为 Low。在监视用发光元件 66 已短路的情况下,监视用发光元件 66 的阳极电位,即点 D 的电位,降低到和监视用发光元件 66 的阴极相同的程度。于是,低电位即 Low 被输入到第二和第三晶体管 84、85 的栅电极,从而 n 沟道型的第三晶体管 85 关断,p 沟道型的第二晶体管 84 导通。另外,当 Ve 的电位为 Low 时,第一晶体管 83 导通,第四晶体管 86 关断。而且,第一晶体管 83 的较高侧的电位经由第二晶体管 84 被输入到监视控制用晶体管 111 的栅电极,从而关断。其结果,来自电源线 113 的电流不被供给到已短路的监视用发光元件 66 中。这样,通过控制栅电极的电压 Ve,就可以正确地使监视控制用晶体管 111 关断。

[0089] (实施方式 3)

[0090] 可以将反向电压施加到发光元件和监视用发光元件。由此,在本实施方式中将说明施加反向电压的情况。

[0091] 反向电压是指在以发光元件13和监视用发光元件66发光时所施加的电压为正向电压的情况下,施加使正向电压的较高侧的电位和较低侧的电位反转而得到的电压。如果用监视用发光元件66具体地说明则是:为了反转阳极电极66a和阴极电极66c的电位,使施加到电源线113的电位低于电源18的电位。

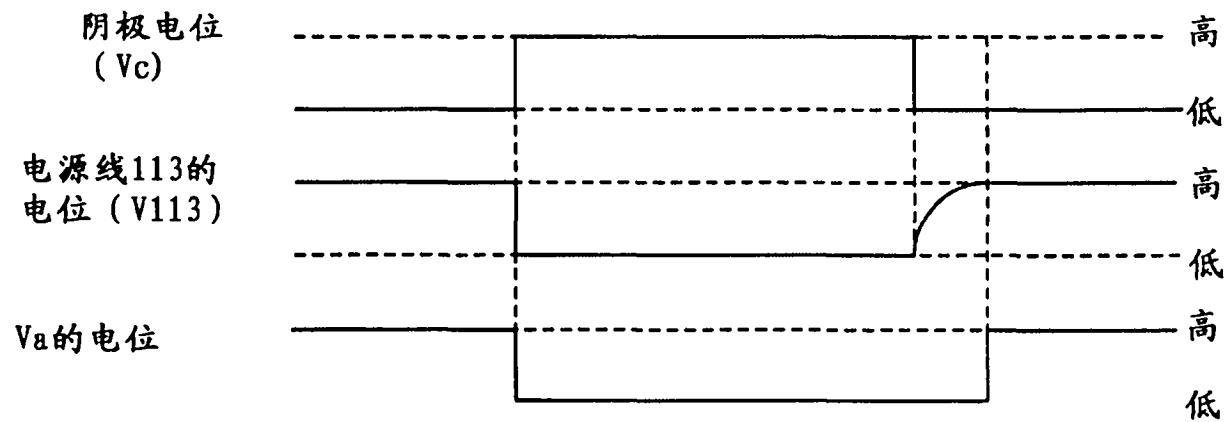

[0092] 具体来说,如图14所示,设阳极电极66a的电位(阳极电位:Va)和阴极电极66c的电位(阴极电位:Vc)为Low电位。与此同时,将电源线113的电位(V113)也进行反转。这个阳极电位和阴极电位反相的期间称作反向电压施加期间。而且,在经过预定的反向电压施加期间后,返回阴极电位,并将恒定电流流过电源线113,以完成充电,也就是说,在电压饱和之后,返回电位。此时,电源线113的电位呈曲线状返回,这是由于以恒定电流对多个监视用发光元件充电,进而对寄生电容充电的缘故。

[0093] 优选的是,将阳极电位反转,接着将阴极电位反转为好。然后,在经过预定的反向电压施加期间后,返回阳极电位,接着返回阴极电位。然后,在与阳极电位反相的同时,将电源线113的电位充电到High。

[0094] 在此反向电压施加期间中,驱动用晶体管12和监视控制用晶体管111必须变为导通。

[0095] 对发光元件施加反向电压的结果是,能够使发光元件13还有监视用发光元件66的缺陷状况改善,使可靠性提高。此外,发光元件13和监视用发光元件66可能具有阳极和阴极短路的初始缺陷,这是由于异物的粘连、由阳极或阴极中的微小凸起产生的针孔、以及发光层的不均匀而引起。当这样的初始缺陷发生时,不能根据信号进行点亮或者不点亮,且大部分电流流过短路了的元件。其结果,就发生图像显示不能良好地进行之类的问题。另外,这种缺陷还有可能在任意的像素中产生。

[0096] 因此,如本实施方式所示,若向发光元件13还有监视用发光元件66施加反向电压则将在已短路的部分流过局部电流,从而该短路部分发热,可以使其氧化或碳化。其结果,可以使已短路的部分绝缘化,而在该部分以外的区域流过电流,就可以作为发光元件13或监视用发光元件66正常地进行工作。如此,即使存在初始缺陷,也可以通过如上述那样地施加反向电压而消除该缺陷。注意,优选在出厂之前进行这种短路部分的绝缘化。

[0097] 另外,不仅是初始缺陷,而且还有随着时间的推移而新发生阳极与阴极之间的短路。这种缺陷也称作累进性缺陷。因此,如本发明中所示,通过定期向发光元件13和监视用发光元件66施加反向电压,即使发生累进性缺陷,也可以消除这种缺陷,而作为发光元件13或监视用发光元件66正常地进行工作。

[0098] 另外,通过施加反向电压可以防止图像的烧印痕(荧光屏的图像保留)。图像的烧印痕是由于发光元件13的退化状态而产生的,但通过施加反向电压可以降低退化程度。其结果,可以防止图像的烧印痕。

[0099] 一般来说,发光元件13和监视用发光元件66的退化在初期进展较大,但随着时间的推移其退化进度渐渐变小。也就是说,在像素中退化过一次的发光元件13和监视用发光元件66不容易产生进一步的退化。其结果,在每个发光元件13之间发生不均匀。因此,可在出厂之前,或在不显示图像时等,使所有发光元件13和监视用发光元件66点亮,从而使其

中没有产生退化的元件产生退化,以使所有元件的退化状态平均化。也可以在发光器件中设置这样的使所有元件发光的结构。

[0100] (实施方式 4)

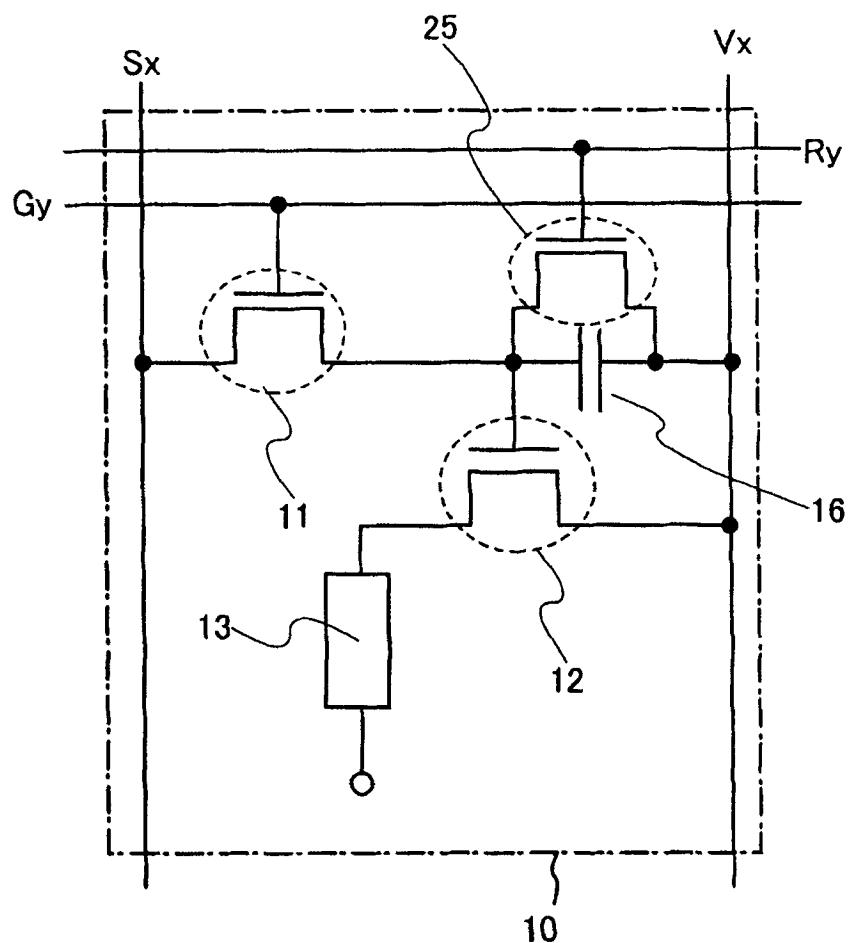

[0101] 在本实施方式中,将说明像素电路以及其结构的一个实例。图 3 表示可以适用于本发明的像素部分的像素电路。在像素部分 40 中呈矩阵状设置有数据线 Sx、栅极线 Gy、电源线 Vx,且在它们的交叉点上设置有像素 10。像素 10 包括开关用晶体管 11、驱动用晶体管 12、电容元件 16、发光元件 13。

[0102] 说明该像素中的连接关系。在数据线 Sx 和栅极线 Gy 的交叉处设置开关用晶体管 11,开关用晶体管 11 的一个电极与信号线 Sx 相连接而开关用晶体管 11 的栅电极与栅极线 Gy 相连接。驱动用晶体管 12 的一个电极连接到电源线 Vx 而其栅电极连接到开关用晶体管 11 的另一个电极。设置电容元件 16 以保持驱动用晶体管 12 的栅源间的电压。在本实施方式中,电容元件 16 的一个电极连接到 Vx 而其另一个电极连接到驱动用晶体管 12 的栅电极。注意,在驱动用晶体管 12 的栅极电容大而漏电流小等情况下就没有必要设置电容元件 16。发光元件 13 连接到驱动用晶体管 12 的另一个电极。

[0103] 说明这种像素的驱动方法。首先,当开关用晶体管 11 导通时,从信号线 Sx 输入视频信号。按照视频信号在电容元件 16 中累积电荷。当在电容元件 16 中累积的电荷超出驱动用晶体管 12 的栅源间的电压 ( $V_{gs}$ ) 时,驱动用晶体管 12 导通。于是,向发光元件 13 提供电流以进行点亮。这时,能够使驱动用晶体管 12 在线性区或饱和区进行工作。如果工作在饱和区,就可以提供恒定电流。如果工作在线性区,就可以以低电压使其工作,并能够谋求低电力消耗化。

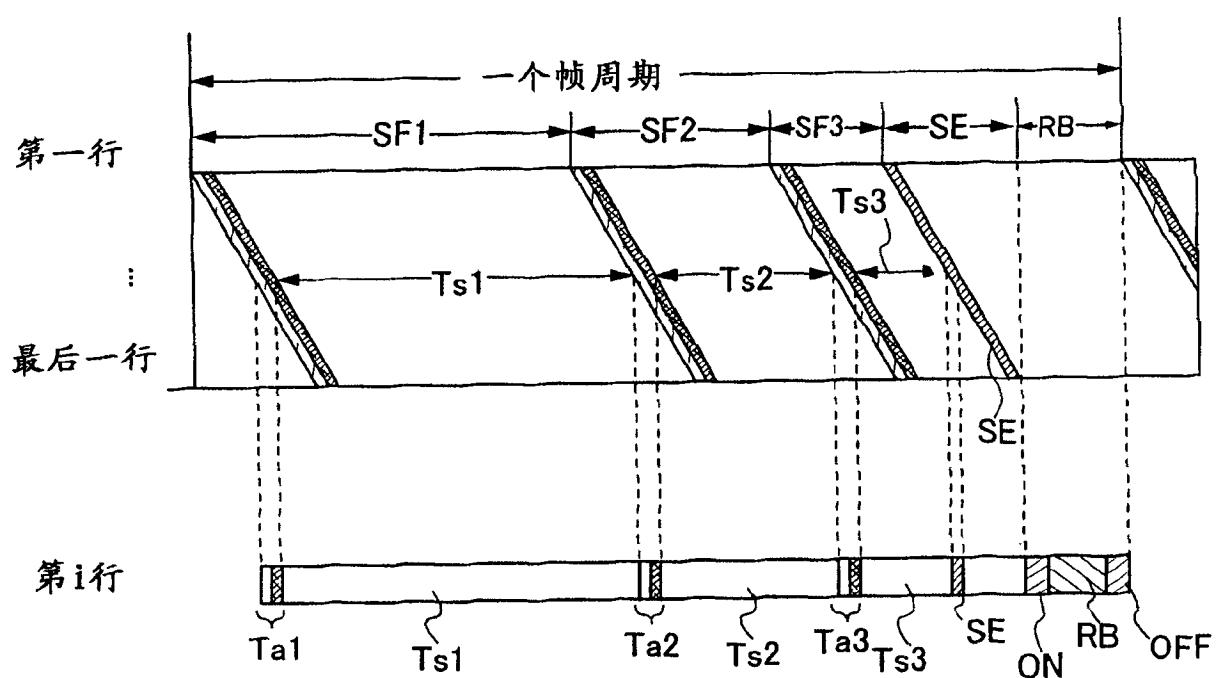

[0104] 下文中,使用定时图来说明像素的驱动方法。图 9A 是在一秒钟进行 60 帧的图像改写的情况下一个帧周期的定时图。在该定时图中,纵坐标表示扫描线(从第一行到最后一行)而横坐标表示时间。

[0105] 一个帧周期包括  $m$ ( $m$  是 2 或更大的自然数)个子帧周期 SF1、SF2、…、SF $m$ ,每个子帧周期 SF1、SF2、…、SF $m$  分别包括写入工作周期 Ta1、Ta2、…、Ta $m$ 、显示周期(点亮周期) Ts1、Ts2、…、Ts $m$ 、和反向电压施加周期。在本实施方式中,如图 9A 所示,一个帧周期设有子帧周期 SF1、SF2 和 SF3,以及反向电压施加周期(RB)。而且,在每个子帧周期中,写入工作周期 Ta1 ~ Ta3 按顺序进行,后面分别跟着显示周期 Ts1 到 Ts3。

[0106] 在图 9B 所记载的定时图中示出着眼于某一行(第  $i$  行)时的写入工作周期、显示周期和反向电压施加周期。在写入工作周期和显示周期交替出现之后出现反向电压施加周期。具有写入工作周期和显示周期的周期称作正向电压施加周期。

[0107] 写入工作周期 Ta 可以分成多个工作周期。在本实施方式中,使其分成两个工作周期,其中一个进行删除工作,另一个进行写入工作。为了这样设置删除工作和写入工作,而输入 WE(Write Erase) 信号。在以下的实施方式将说明其他删除工作和写入工作以及信号的细节。另外,紧接在反向电压施加周期之前设置使所有像素的开关用晶体管同时导通的周期,亦即,使所有扫描线导通的周期(导通周期)。

[0108] 紧接在反向电压施加周期之后设置使所有像素的开关用晶体管同时关断的周期,亦即,使所有扫描线关断的周期(关断周期)为好。另外,紧接在反向电压施加周期之前设置删除周期(SE)。该删除周期可以通过与上述删除工作同样的工作来进行。在删除周期,

按顺序删除紧接在删除周期之前的子帧周期，即在本实施方式中的 SF3 所写入的数据的动作顺次进行。这是因为，在导通周期，在最后一行的像素的显示周期结束之后开关用晶体管一齐导通，从而第一行等的像素就具有不必要的显示周期。

[0109] 如此，通过诸如扫描线驱动电路以及信号线驱动电路等驱动电路来进行用于设置导通周期、关断周期和删除周期的控制。注意，向发光元件 13 施加反向电压的定时，即反向电压施加周期并不限于图 9A 和 9B 所示的定时。那就是说，不需要对每个帧设置反向电压施加周期，也不需要在一帧的后半部分中设置反向电压施加周期。只要至少在紧接施加周期 (RB) 之前提供导通周期并且只要至少在紧接施加周期 (RB) 之后提供关断周期即可。另外，使发光元件的阳极电压和阴极电压相反的顺序也并不限于图 9A 和 9B 所示的顺序。也就是说，也可以在阴极电极的电位提高之后，使阳极电极的电位下降。

[0110] 图 4 示出图 3 中所示的像素电路的布局示例。首先，形成构成开关用晶体管 11 和驱动用晶体管 12 的半导体膜。然后，经由作为栅绝缘膜发挥功能的绝缘膜而形成第一导电膜。该导电膜可以用作开关用晶体管 11 和驱动用晶体管 12 的栅电极，另外还可以用作栅极线 Gy。这时，开关用晶体管 11 优选为双栅结构。

[0111] 然后，经由作为层间绝缘膜发挥功能的绝缘膜而形成第二导电膜。该导电膜可以用作开关用晶体管 11 和驱动用晶体管 12 的漏极布线和源极布线，另外还可以用作信号线 Sx 和电源线 Vx。这时，可以通过第一导电膜、用作层间绝缘膜的绝缘膜以及第二导电膜的叠层构造来形成电容元件 16。驱动用晶体管 12 的栅电极和开关用晶体管的另一电极通过接触孔连接起来。

[0112] 然后，在设置于像素中的开口部分中形成第一电极 19(像素电极)。该像素电极连接到驱动用晶体管 12 的另一电极。这时，在第二导电膜和像素电极之间设置有绝缘膜等的情况下，就需要通过接触孔进行连接。在没有设置绝缘膜等的情况下，像素电极可以直接连接到驱动用晶体管 12 的另一电极。

[0113] 在图 4 所示出的布局中，为了确保高开口率，有时第一导电膜和像素电极重叠起来。在这种区域中，有时会出现耦合电容。该耦合电容是不希望的电容。

[0114] 图 5 表示图 4 所示的 A-B 和 B-C 的截面图例。在绝缘衬底 20 上经由基底膜形成有半导体膜。在绝缘衬底 20 中可以采用诸如钡硼硅酸盐玻璃和铝硼硅酸盐玻璃等玻璃衬底、石英衬底、不锈钢衬底等。此外，由诸如此以 PET(聚对苯二甲酸乙二醇酯)、PEN(聚萘二甲酸乙二醇酯)为代表的塑料或丙烯酸等具有挠性的合成树脂制成的衬底与其它衬底相比较通常具有耐热稳定较低的倾向，但只要可以承受制造过程中的处理温度就可以使用。在基底膜中可以使用诸如氧化硅、氮化硅以及氮氧化硅等绝缘膜。

[0115] 在基底膜上形成非晶体半导体膜。设非晶体半导体膜的膜厚为 25nm 到 100nm(优选为 30nm 到 60nm)。另外，除了硅之外，硅锗也可以用于非晶半导体。

[0116] 接着，根据需求使非晶体半导体膜结晶，以形成晶体半导体膜。进行结晶化的方法能够使用加热炉、激光辐射、或者从灯发出的光的照射(此后称作灯退火)或者将它们组合起来。例如，通过向非晶体半导体膜掺杂金属元素并使用加热炉进行热处理来形成晶体半导体膜。因为可以在低温下使半导体膜结晶，所以优选添加金属元素。将这样形成的晶体半导体膜加工成预定的形状。预定的形状是指如在图 4 中所示成为开关用晶体管 11 和驱动用晶体管 12 的形状。

[0117] 接着,形成用作栅绝缘膜的绝缘膜。形成厚度为10nm到150nm并且优选为20nm到40nm的该绝缘膜以便覆盖半导体膜。例如,可以使用氮化硅膜、氧化硅膜等,还可以采用单层结构或叠层结构。

[0118] 然后,经由栅绝缘膜形成用作栅电极的第一导电膜。尽管栅电极既可以是单层结构也可以是叠层结构,但在本实施方式中使用由导电膜22a和22b构成的叠层结构。各导电膜22a和22b用从Ta、W、Ti、Mo、Al和Cu中选择出的元素或以上述元素为主要成分的合金材料或化合物材料形成即可。在本实施方式中,顺次形成厚度为10nm到50nm,例如30nm的氮化钽膜作为导电膜22a,形成厚度为200nm到400nm,例如370nm的钨膜作为导电膜22b。

[0119] 接着,以栅电极作为掩模添加杂质元素。这时,除高浓度杂质区外还可以形成低浓度杂质区。这称作LDD(轻掺杂漏极)结构。特别地,将低浓度杂质区与栅电极重叠的结构称作GOLD(栅漏重叠的LDD)结构。特别是,n沟道型晶体管优选采用具有低浓度杂质区的结构。

[0120] 随后,形成用作层间绝缘膜30的绝缘膜28和29。绝缘膜28只要是包含氮的绝缘膜即可,并且在本实施方式中,通过等离子体CVD法形成厚度为100nm的氮化硅膜。

[0121] 此外,能够通过使用有机材料或无机材料形成绝缘膜29。作为有机材料能够使用聚酰亚胺、丙烯酸、聚酰胺、聚酰亚胺酰胺、抗蚀剂、苯并环丁烯、硅氧烷以及聚硅氮烷。硅氧烷是指由硅(Si)和氧(O)的结合物形成的骨架结构,硅氧烷以聚合物材料为起始材料来形成,该聚合物材料至少包含氢作为取代基、或至少包含氟、烷基或芳香族碳氢化合物之中的至少一种作为取代基。另外聚硅氮烷是指包含具有硅(Si)和氮(N)的结合的聚合物材料。作为无机材料能够使用含有氧或氮的绝缘膜,诸如氧化硅( $\text{SiO}_x$ )、氮化硅( $\text{SiN}_x$ )、氧化氮化硅( $\text{SiO}_x\text{N}_y$ )( $x > y$ )以及氮氧化硅( $\text{SiN}_x\text{O}_y$ )( $x > y$ )( $x, y = 1, 2, \dots$ )等。另外,绝缘膜29可以具有这些绝缘膜的叠层结构。特别是,当通过使用有机材料来形成绝缘膜29时,虽然平整性增高但另一方面水分和氧却被有机材料所吸收。为了防止该情况,在有机材料上形成含有无机材料的绝缘膜为好。优选的是若在无机材料中使用含氮的绝缘膜,就可以防止诸如Na的碱离子侵入。优选的是若在绝缘膜29中使用有机材料就可以增高平整性。

[0122] 在层间绝缘膜30中形成接触孔。然后,形成第二导电膜,其用作开关用晶体管11和驱动用晶体管12的源极布线和漏极布线24、信号线Sx以及电源线Vx。作为第二导电膜可以使用由诸如铝(Al)、钛(Ti)、钼(Mo)、钨(W)或硅(Si)的元素构成的膜或者使用了这些元素的合金膜。在本实施方式中,通过堆叠厚度分别为60nm、40nm、300nm和100nm的钛膜、氮化钛膜、钛铝合金膜以及钛膜而形成第二导电膜。然后,形成绝缘膜31以便覆盖第二导电膜。作为绝缘膜31可以使用上述的层间绝缘膜30的材料。通过这样设置绝缘膜31就可以增高水平率。

[0123] 而且,在设于绝缘膜31的开口部分中形成第一电极19(像素电极)。为了在开口部分中增高像素电极的台阶覆盖性(step coverage),在开口部分的末端面以具有多个曲率半径的方式使之带有圆状为好。在第一电极19中可以使用诸如铟锡氧化物(ITO:Indium Tin Oxide)、通过将2%到20%的氧化锌(ZnO)混合到氧化铟中获得的IZO(铟锌氧化物:Indium Zinc Oxide)、通过将2%到20%的氧化硅( $\text{SiO}_2$ )混合到氧化铟中获得的ITO-SiO<sub>x</sub>、有机铟以及有机锡等作为具有透光性的材料。作为具有遮光性的材料,除了银(Ag)以外还可以使用从钽、钨、钛、钼、铝以及铜中选择出的元素或以上述元素为主要成分的合金材料。

或化合物材料。此时,当通过使用有机材料形成绝缘膜 31 以增高平整性时,由于像素电极的形成表面的平整性得以改进,从而可以施加恒定电压进而能够防止短路。

[0124] 在第一导电膜与像素电极重叠的区域 430 中可能出现耦合电容。该耦合电容是不希望的电容。

[0125] 随后,形成隔壁 32,通过蒸镀法或喷墨法形成发光层 33。发光层 33 具有有机材料或无机材料,并适当组合电子注入层 (EIL)、电子传输层 (ETL)、发光层 (EML)、空穴传输层 (HTL)、空穴注入层 (HIL) 等而构成。注意,各层之间的界限不一定是清晰明确的,并且还有构成各层的材料彼此部分地混合而使得界面变得模糊的情况。另外,发光层的结构并不限于上述叠层结构。

[0126] 可以使用无机材料作为形成发光层 33 的母体材料。作为无机材料优选使用锌、镉、镓等金属材料的硫化物、氧化物和氮化物。例如,作为硫化物可以使用硫化锌 (ZnS)、硫化镉 (CdS)、硫化钙 (CaS)、硫化钇 (Y<sub>2</sub>S<sub>3</sub>)、硫化镓 (Ga<sub>2</sub>S<sub>3</sub>)、硫化锶 (SrS)、硫化钡 (BaS) 等。作为氧化物可以使用氧化锌 (ZnO)、氧化钇 (Y<sub>2</sub>O<sub>3</sub>) 等。另外,作为氮化物可以使用氮化铝 (AlN)、氮化镓 (GaN)、氮化铟 (InN) 等。进而,还可以使用硒化锌 (ZnSe)、碲化锌 (ZnTe) 等。此外,也可以使用诸如硫化钙镓 (CaGa<sub>2</sub>S<sub>4</sub>)、硫化锶镓 (SrGa<sub>2</sub>S<sub>4</sub>)、硫化钡镓 (BaGa<sub>2</sub>S<sub>4</sub>) 等三元混晶。

[0127] 作为杂质元素,可以使用形成通过利用金属离子的内层电子迁移而获得发光中心的材料,诸如锰 (Mn)、铜 (Cu)、钐 (Sm)、铽 (Tb)、铒 (Er)、铥 (Tm)、铕 (Eu)、铈 (Ce)、镨 (Pr) 等金属元素。另外,也可以添加诸如氟 (F) 或氯 (Cl) 等卤族元素作为电荷补偿。

[0128] 另外,作为利用施主 - 受主复合的发光中心,可以使用包括第一杂质元素和第二杂质元素的发光材料。作为第一杂质元素,可以使用诸如铜 (Cu)、银 (Ag)、金 (Au)、铂 (Pt) 等金属元素、或硅 (Si) 等。作为第二杂质元素,可以使用氟 (F)、氯 (Cl)、溴 (Br)、碘 (I)、硼 (B)、铝 (Al)、镓 (Ga)、铟 (In)、铊 (Tl) 等。

[0129] 发光材料通过固相反应法,即,称量母体材料和杂质元素,然后在研钵中将其混合到一起,并在电炉中进行加热而产生反应的方法,以将杂质元素添加在母体材料中。例如,分别称量母体材料、第一杂质元素或含有第一杂质元素的化合物、以及第二杂质元素或含有第二杂质元素的化合物,并在研钵中将其混合在一起后,用电炉进行加热而焙烧。焙烧温度优选为 700°C 至 1500°C。这是因为,在温度过低时不能进行固相反应,而在温度过高时母体材料将会分解。注意,虽然也可以在粉末状态下进行焙烧,但优选的是在球粒状态下进行焙烧。

[0130] 另外,作为当利用固相反应时的杂质元素,可以将由第一杂质元素和第二杂质元素构成的化合物组合起来使用。在此情况下,由于杂质元素容易扩散,并且固相反应容易进行,因此,可以获得均匀的发光材料。而且,由于不混入多余的杂质元素,因此可以获得高纯度的发光材料。作为由第一杂质元素和第二杂质元素构成的化合物,例如,可以使用氟化铜 (CuF<sub>2</sub>)、氯化铜 (CuCl)、碘化铜 (CuI)、溴化铜 (CuBr)、氮化铜 (Cu<sub>3</sub>N)、磷化铜 (Cu<sub>3</sub>P)、氟化银 (AgF)、氯化银 (AgCl)、碘化银 (AgI)、溴化银 (AgBr)、氯化金 (AuCl<sub>3</sub>)、溴化金 (AuBr)、氯化铂 (PtCl<sub>2</sub>) 等。另外,也可以使用含有第三杂质元素以代替第二杂质元素的发光材料。

[0131] 作为第三杂质元素,例如,可以使用锂 (Li)、钠 (Na)、钾 (K)、铷 (Rb)、铯 (Cs)、氮 (N)、磷 (P)、砷 (As)、锑 (Sb)、铋 (Bi) 等。这些杂质元素的浓度只要相对于母体材料被设定

为 0.01 至 10mol% 即可，优选为 0.1 至 5mol% 的范围内。

[0132] 作为具有高电气导电性的发光材料，可以使用如下材料，即采用上述材料作为母体材料并添加包含上述第一杂质元素、第二杂质元素和第三杂质元素的发光材料。这些杂质元素的浓度相对于母体材料设定为 0.01 至 10mol% 即可，优选为 0.1 至 5mol% 的范围内。

[0133] 作为由第二杂质元素和第三杂质元素构成的化合物，例如，可以使用诸如氟化锂 (LiF)、氯化锂 (LiCl)、碘化锂 (LiI)、溴化锂 (LiBr)、氯化钠 (NaCl) 的卤化碱、氮化硼 (BN)、氮化铝 (AlN)、铝锑 (AlSb)、镓磷 (GaP)、镓砷 (GaAs)、铟磷 (InP)、铟砷 (InAs)、铟锑 (InSb) 等。

[0134] 使用上述材料作为母体材料并且使用包含上述第一杂质元素、第二杂质元素和第三杂质元素的发光材料的发光层，能够进行发光，而无需由高电场进行了加速的热电子。也就是说，由于没有必要给发光元件施加高电压，所以可以获得能够以低驱动电压进行工作的发光元件。另外，由于能够以低驱动电压进行发光，所以可以获得耗电也得以降低的发光元件。此外，进一步还可以包含用作其他发光中心的元素。

[0135] 另外，可以使用上述材料作为母体材料，并且使用包含第二杂质元素、第三杂质元素和利用金属离子的内层电子迁移而获得的发光中心的发光材料。在此情况下，用作发光中心的金属离子优选为相对于母体材料为 0.05 至 5 原子%。另外，第二杂质元素的浓度优选为相对于母体材料为 0.05 至 5 原子%。另外，第三杂质元素的浓度优选为相对于母体材料为 0.05 至 5 原子%。具有这种结构的发光材料能够以低电压进行发光。从而，可以获得能够以低驱动电压进行发光的发光元件，所以可以获取耗电被降低的发光元件。另外，进一步还可以包含用作其他发光中心的元素。通过使用这种发光材料，就可以抑制发光元件的亮度退化。另外，也可以使用晶体管来实现低电压驱动。

[0136] 而且，通过蒸镀法形成第二电极 35。根据像素结构，发光元件的第一电极 19（像素电极）和第二电极 35 用作阳极或阴极。作为阳极材料优选使用具有高功函数（功函数为 4.0eV 或更高）的金属、合金、导电化合物以及它们的混合物等。作为阳极材料的具体例子，除使用 ITO、通过将 2% 到 20% 的氧化锌 (ZnO) 混合到氧化铟中获得的 IZO 外、还可以使用金 (Au)、铂 (Pt)、镍 (Ni)、钨 (W)、铬 (Cr)、钼 (Mo)、铁 (Fe)、钴 (Co)、铜 (Cu)、钯 (Pd)、或者金属材料的氮化物 (TiN) 等。

[0137] 另一方面，作为阴极材料优选使用具有低功函数（功函数为 3.8eV 或更低）的金属、合金、导电化合物及其混合物。作为阴极材料的具体例子，除使用属于元素周期表第一族或第二族的元素，即诸如 Li 和 Cs 等碱金属、诸如 Mg、Ca 和 Sr 等碱土金属、以及含它们的合金 (Mg : Ag、Al : Li) 或化合物 (LiF、CsF、CaF<sub>2</sub>) 外，还可以使用包括稀土类金属的过渡金属而形成。然而，因为需要阴极具有透光性，所以将这些金属或包含它们的合金形成得极薄，并且通过堆叠诸如 ITO 等金属（包括合金）而形成。

[0138] 接下来，还可以形成保护膜以覆盖第二电极 35。作为保护膜，可以使用氮化硅膜或 DLC 膜。通过这种方式，就可以形成显示器件的像素。

[0139] （实施方式 5）

[0140] 将参照图 29 到图 31 来说明本发明的显示器件中的像素和驱动电路的结构。

[0141] 图 29 表示了涉及本发明的显示面板的结构。该显示面板在衬底 120 上包括配置

有多个子像素 130 的像素部分 121、控制扫描线 133 的信号的扫描线驱动电路 122、控制数据线 131 的信号的数据线驱动电路 123。另外，还可以设置监视电路 124，其用于修正包括在子像素 130 中的发光元件 137 的亮度变化。发光元件 137 和包括在监视电路 124 中的发光元件具有相同的结构。发光元件 137 的结构采用在一对电极之间夹着含有产生场致发光的材料的层的形式。

[0142] 在衬底 120 的边缘部分上具有从外部电路将信号输入到扫描线驱动电路 122 中的输入端子 125、从外部电路将信号输入到数据线驱动电路 123 中的输入端子 126、以及从外部电路将信号输入到监视电路 124 中的输入端子 129。

[0143] 在子像素 130 中包括连接到数据线 131 的晶体管 134 以及串联地插入到电源线 132 和发光元件 137 之间进行连接的晶体管 135。晶体管 134 的栅极连接到扫描线 133，在被扫描信号选择时，将数据线 131 的信号输入到子像素 130。被输入的信号提供到晶体管 135 的栅极中，并且使保持电容部分 136 充电。根据该信号，电源线 132 和发光元件 137 变为导通状态，从而发光元件 137 发光。

[0144] 为了使设置在子像素 130 中的发光元件 137 发光，有必要从外部电路供给电力。设置在像素部分 121 的电源线 132 通过输入端子 127 连接到外部电路。由于电源线 132 因盘绕的布线长度而发生电阻损耗，所以优选将多个输入端子 127 设置在衬底 120 的边缘部分上。在衬底 120 的两端部分上设置输入端子 127，以在像素部分 121 的面内使亮度不均匀不显著的方式进行配置。也就是说，防止在画面中一侧很亮而在另一侧很暗。另外，发光元件 137 具有一对电极，其中与和电源线 132 连接的电极相反侧的电极被形成为多个子像素 130 共同使用的共用电极。这里，提供多个端子 128 以便减少该电极的电阻损耗。

[0145] 接着，将参照图 30 和图 31 详细地说明子像素 130 的一个例子。注意，图 30 示出了子像素 130 的俯视图，并且图 31 示出了相应于图 30 中所示的截面线 A-B、C-D、E-F 的纵截面图。

[0146] 扫描线 133 和数据线 131 由不同的层形成，且夹着绝缘层 155 以及 156 进行交叉。在夹有栅绝缘层 157 且与半导体层 141 相交叉的部分上，扫描线 133 作为晶体管的栅电极发挥作用。在此情况下，通过使晶体管 134 按照半导体层 141 的配置方式，将扫描线 133 分支以在多处设置与半导体层 141 交叉的部分，就可以获得所谓多栅晶体管，其中一对源极和漏极之间串联布置多个沟道形成区域。

[0147] 与晶体管 135 连接的电源线 132 具有低电阻是所希望的，因此优选使用电阻率低的 Al 和 Cu 等。在形成 Cu 布线的情况下，可以和阻挡层组合而形成在绝缘层中。图 31 表示在衬底 120 上并且在半导体层 141 的下层形成电源线的例子。在衬底 120 的表面上形成阻挡层 150，以防止包含在衬底 120 中的碱金属等杂质渗出。电源线 132 在形成于绝缘层 151 的开孔中由阻挡层 152 和 Cu 层 159 形成。阻挡层 152 由钽 (Ta)、氮化钽 (TaN)、氮化钨 (WN)、氮化钛 (TiN) 等形成。在通过溅射法形成种子层 (seed layer) 后，通过电镀法淀积 1 μm 到 5 μm 厚的 Cu 层 159，并且通过化学机械抛光进行平整化处理。那就是说，通过采用镶嵌工序，就可以获取嵌入在绝缘层 151 中的形状。

[0148] 在绝缘层 151 上形成有对于半导体层 140、141 的基底绝缘层。基底绝缘层的结构没有特别的限制，但优选由氮化硅层 153 和氧化硅层 154 形成。此外，作为绝缘层的结构，除了栅绝缘层 157 之外，使用氧化硅或氮化硅等在半导体层 140、141 上形成绝缘层 156，并

用作保护膜。

[0149] 电源线 132 和晶体管 135 通过形成穿过上述绝缘层的接触孔并使用布线 145 而连接到一起。另外，栅电极 142 通过布线 144 连接到晶体管 134 上。晶体管 134 和 135 的栅电极还可以是由多个层层叠而形成的。例如，可以考虑到和栅绝缘层的粘附度和电阻率来组合第一导电层和第二导电层，也可以采用如下结构：改变上层和下层的形状（例如设为具有帽舌的帽子型的形状），以便可以以自对准方式在半导体层上形成源区域和漏区域以及低浓度杂质（LDD）区域。

[0150] 另外，优选是将栅电极 142 延伸而设置的保持电容部分 136 的电容电极 143，通过利用第一导电层和第二导电层的组合来设置基于第一导电层的薄膜部分，并向位于其下层的半导体层添加具有一导电型的杂质以降低电阻。也就是说，保持电容部分 136 是由将栅电极 142 延伸而设置的保持电容部分 136 的电容电极 143、晶体管 135 的半导体层 141 延伸而成的半导体层 160、以及夹在两者之间的栅绝缘层 157 而形成的，但是，通过将一导电型的杂质添加到半导体层 160 中以进行低电阻化，就可以使其有效地工作。

[0151] 发光元件的像素电极还可以直接接触于晶体管 135 的半导体层 141，但是，也可以如附图 31 所示那样，通过布线 146 连接到半导体层。在此情况下，优选的是通过在布线 146 的端部上设置多个台阶形状，就能够增加和像素电极 147 接触的面积。这种台阶形状可以通过使用狭缝（slit）或半透光膜等消光手段的光掩模而形成。像素电极 147 的边缘端部被隔壁层 158 覆盖。

[0152] 由于使用低电阻材料如 Cu 等形成电源线，因此本实施方式所示的显示面板特别是在屏幕尺寸大型化时很有效。例如，当屏幕尺寸为 13 英寸级时，对角线的长度为 340mm，但是，当屏幕尺寸为 60 英寸级时，对角线的长度为 1500mm 或更大。在这样的情况下，布线电阻不能忽视，因此优选使用诸如 Cu 等的低电阻材料作为布线。另外，考虑到布线延迟，也可以与此同样形成数据线和扫描线。

[0153] 另外，可以自由地与实施方式 1 至 4 所述的内容组合地实施本实施方式所述的内容。

[0154] （实施方式 6）

[0155] 本实施方式中将参照附图说明当制造显示面板时所使用的蒸镀设备。

[0156] 通过在用晶体管形成像素电路和 / 或驱动电路的元件衬底上形成 EL 层以制造显示面板。该 EL 层在其至少一部分中包含产生场致发光的材料而形成。EL 层还可以由多个具有不同作用的层构成。此时，EL 层有可能由被称作空穴注入传输层、发光层、电子注入传输层等的具有不同作用的层结合来构成。

[0157] 图 32 示出了用于在形成有晶体管的元件衬底上形成 EL 层的蒸镀设备的结构。在该蒸镀设备中，多个处理室连结到载运室 160 和 161。该处理室包括供给衬底的装载室 162、回收衬底的卸载室 163、另外还包括加热处理室 168、等离子体处理室 172、蒸镀 EL 材料的成膜处理室 169 至 175、形成导电膜的成膜处理室 176，该导电膜用作发光元件的一个电极并且包含铝或以铝作为主要成分。另外，载运室和各处理室之间设置有闸门阀 177a 至 177i，以可以独立控制各处理室的压力，从而防止处理室之间的相互污染。

[0158] 从装载室 162 导入到载运室 161 的衬底通过自由转动的机械臂方式的载运装置 193 移入到预定的处理室。而且，通过载运装置 193 将衬底从某个处理室载运到其他处理

室。载运室 160 和载运室 161 通过成膜处理室 170 连结起来,在此,通过载运装置 193 和载运装置 194 执行衬底的授受。

[0159] 连结到载运室 160 和载运室 161 的各处理室被保持减压状态。从而,在该蒸镀设备中,不接触大气的情况下,连续地对衬底进行 EL 层的成膜处理。EL 层的成膜处理结束后的显示面板有可能因水蒸气等导致退化,所以在本蒸镀设备中,将密封处理室 165 连结到载运室 161,该密封处理室 165 用来在接触大气之前执行密封处理以保持显示面板的质量。密封处理室 165 被设定为大气压或近于大气压的减压状态,因此,在载运室 161 和密封处理室 165 之间还设置有中间室 164。中间室 164 是为了授受衬底且缓冲各室之间的压力而被设置的。

[0160] 在装载室 162、卸载室 163、载运室以及成膜处理室中设置有保持室内减压状态的排气装置。作为排气装置,可以使用各种真空泵诸如干燥泵、涡轮分子泵或扩散泵等。

[0161] 在图 32 所示的蒸镀设备中,根据发光元件的叠层结构,可以适当地组合连结到载运室 160 和载运室 161 的处理室的数量及其结构。以下,表示其组合的一个实例。

[0162] 在加热处理室 168 中,首先对形成有下部电极和绝缘隔壁等的衬底执行加热以进行除气处理。在等离子体处理室 172 中,对基底电极的表面进行用稀有气体或氧等离子的处理。该等离子体处理是为了使表面清净化,并使表面的状态、表面的物理性或化学性状态(例如,功函数等)稳定化。

[0163] 成膜处理室 169 是用于形成与发光元件的一个电极相接触的电极缓冲层的处理室。电极缓冲层具有载流子注入性(空穴注入或电子注入),并且抑制发生发光元件的短路和暗点缺陷。典型的是,通过使用有机无机混合材料形成电极缓冲层,其电阻率为  $5 \times 10^4 \Omega$  至  $1 \times 10^6 \Omega \text{ cm}$ ,其厚度为 30nm 至 300nm。另外,成膜室 171 是形成空穴传输层的处理室。

[0164] 根据单色发光的情况或白色发光的情况,发光元件中的发光层具有不同的结构。优选是按照上述结构将成膜处理室也配置在蒸镀设备中。例如,当在显示面板上形成功能颜色不同的三种发光元件时,有必要形成对应于各发光颜色的发光层。在此情况下,可以将成膜处理室 170 用于形成第一发光层,将成膜处理室 173 用于形成第二发光层,并将成膜处理室 174 用于形成第三发光层。通过对每个发光层区分成膜处理室,就可以防止因不同的发光材料导致的相互污染,而且可以提高成膜处理时的生产量。

[0165] 另外,还可以在成膜处理室 170、成膜处理室 173、成膜处理室 174 中各自按顺序蒸镀发光色不同的三种 EL 材料。此时,通过使用阴影掩模并按照要蒸镀的区域偏移该掩模来进行蒸镀。

[0166] 当形成白色发光的发光元件时,以纵方向层叠发光颜色不同的发光层来形成。此时,通过按顺序将元件衬底在成膜处理室中移动,就对每个发光层进行成膜。另外,也可以在同一成膜处理室中连续形成不同的发光层。

[0167] 在成膜处理室 176 中,在 EL 层上形成电极。可以使用电子激光蒸镀法或溅射法形成该电极,但优选采用电阻加热蒸镀法。

[0168] 一直到电极形成才结束的元件衬底经过中间室 164 移入到密封处理室 165。密封处理室 165 中填充有氦、氩、氖或氮等惰性气体,在该气氛下,在元件衬底的形成 EL 层的一侧粘贴密封板来实现密封。在完成密封的状态下,元件衬底和密封板之间既可以填充惰性气体,也可以填充树脂材料。密封处理室 165 中包括描画密封材料的分配器、用于在元件衬

底对面固定密封板的固定载台和机械臂等机械要素、以及填充树脂材料的分配器或旋涂器等。

[0169] 图 33 表示成膜处理室的内部结构。成膜处理室被保持在减压状态下。图 33 中夹在上面板 191 和底面板 192 之间的内侧是室内，并表示了被保持成减压状态的室内。

[0170] 在处理室中提供有一个或多个蒸发源。这是因为，在形成具有不同组成的多个层，或共同蒸镀不同的材料的情况下，优选设置多个蒸发源的缘故。在图 33 中，蒸发源 181a、181b、181c 安装在蒸发源支架 180。蒸发源支架 180 被多铰链式机械臂 183 保持。多铰链式机械臂 183 通过伸缩其铰链可以在可移动的范围内将蒸发源支架 180 的位置自由地移动。另外，还可以将距离传感器 182 设置在蒸发源支架 180 中，监测蒸发源 181a 至 181c 和衬底 189 之间的间隔，以控制当蒸镀时的最佳间隔。此时，可以在多铰链式机械臂中采用能够沿着上下方向（Z 轴方向）变位的多铰链式机械臂。

[0171] 衬底载台 186 和衬底卡盘 187 成对地固定衬底 189。衬底载台 186 还可以构成为内置有加热器以能够加热衬底 189。通过利用衬底卡盘 187 的紧缓将衬底 189 固定在衬底载台 186 上而移入和送出。当进行蒸镀时，还可以根据需求而使用对应于要蒸镀的图案具有开口部分的阴影掩模 190。这时，阴影掩模 190 设置在衬底 189 和蒸发源 181a 至 181c 之间。阴影掩模 190 通过掩模卡盘 188 与衬底 189 紧密接触或保持一定间隔地被固定。在需要给阴影掩模 190 定位时，通过将照相机配置在处理室中，并将用于沿着 X-Y-θ 方向微动的定位装置提供在掩模卡盘 188 上以进行定位。蒸发源 181 中还附加有将蒸镀材料连续供应到蒸发源的蒸镀材料供应装置。该蒸镀材料供给装置包括：配置在离开蒸发源 181 的位置的蒸镀材料供应源 185a、185b、185c、以及用于连接于两者之间的材料供给管 184。典型的是，对应蒸发源 181 设置材料供给源 185a、185b、185c。在图 33 的情况下，材料供应源 185a 和蒸发源 181a 相对应。关于材料供应源 185b 和蒸发源 181b、材料供应源 185c 和蒸发源 181c 也同样如此。

[0172] 作为蒸镀材料的供应方法可以采用诸如气流传送方式和气雾剂方式等。气流传送方式是通过气流传送蒸镀材料的微粉末的方法，即，使用惰性气体等将蒸镀材料传送到蒸发源 181。气雾剂方式是如下方法：传送将蒸镀材料溶解或分散在熔剂中而成的原料液，接着通过喷雾器将其变为气雾状，一边使气雾中的溶剂气化一边进行蒸镀。这两种方法都在蒸发源 181 中设置加热装置，以使被传送的蒸镀材料蒸发而成膜在衬底 189 上。在图 33 的情况下，材料供应管 184 由可以柔軟地进行弯曲并具有在减压状态下也不变形程度的刚度的细管而构成。

[0173] 当采用气流传送方式或气雾剂方式时，可以使成膜处理室内设为大气压或更低的减压状态，优选为 133Pa 至 13300Pa，而进行成膜即可。在成膜处理室中填充有氦、氩、氖、氪、氙或氮等惰性气体，或在供应该气体（同时进行排气）的同时，可以调节其压力。另外，在形成氧化膜的成膜处理室中，还可以通过导入氧或一氧化二氮等的气体以制造氧气气氛。另外，在蒸镀有机材料的成膜处理室中，还可以通过导入氢等的气体以制造还原气氛。

[0174] 作为其他蒸镀材料的供应方法，还可以使用如下结构：通过在材料供应管 184 中设置螺旋而向蒸发源连续推出蒸镀材料。

[0175] 根据本实施方式的蒸镀设备，即使是大屏幕的显示面板也可以均匀性好地连续形成膜。此外，由于蒸发源不需要每次用完蒸镀材料都补给蒸镀材料，从而可以提高生产能

力。

[0176] 另外,可以自由地与实施方式 1 至 5 所述的内容组合而实施本实施方式所述的内容。

[0177] (实施方式 7)

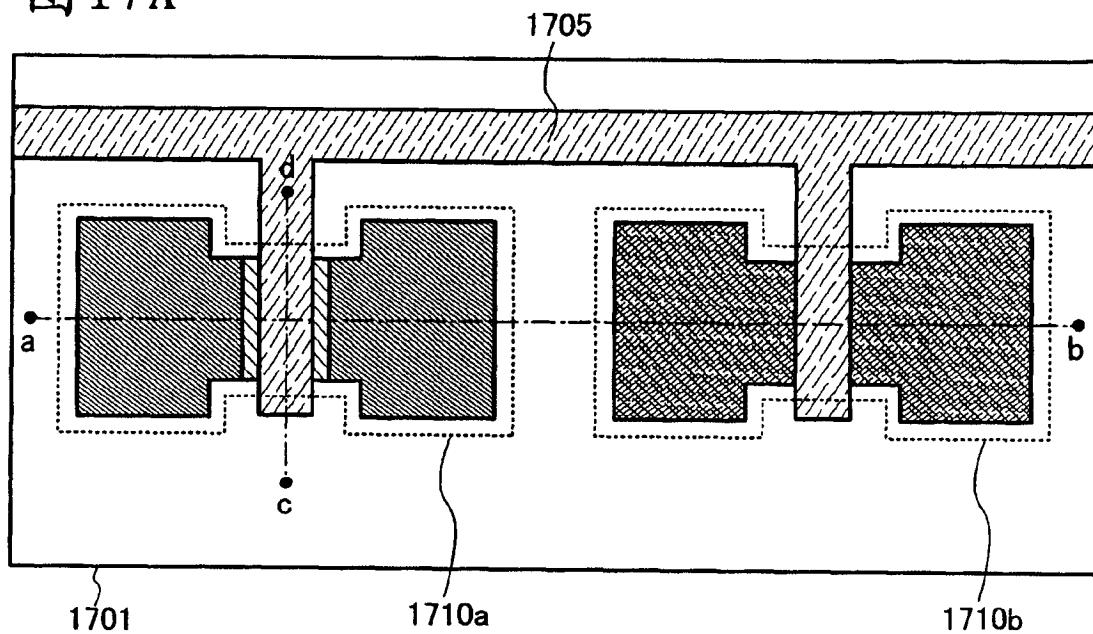

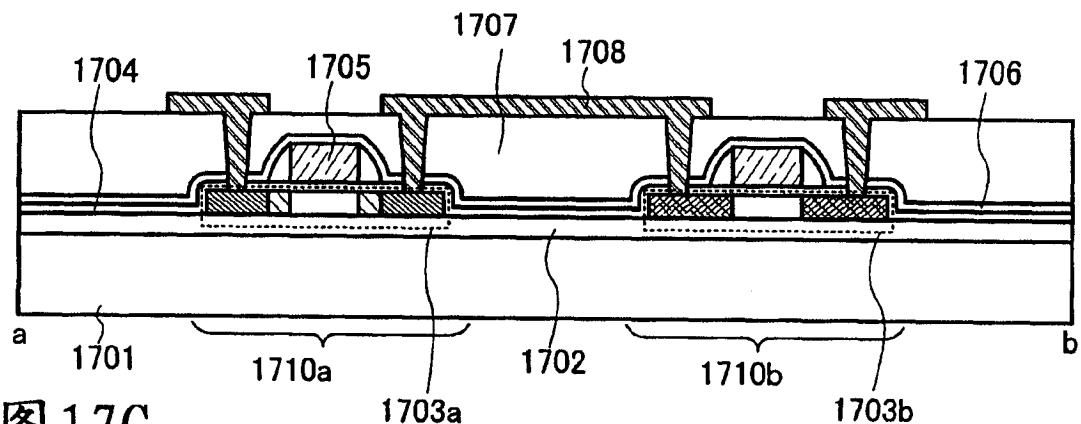

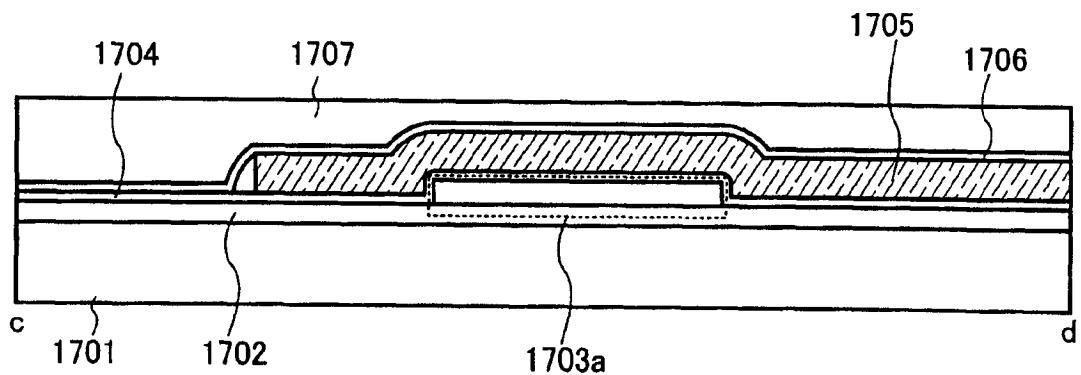

[0178] 在本实施方式中,将说明可以适用本发明的显示器件的制造方法。可以适用本发明的显示器件也可以组合使用由微波激励的高密度等离子的方法。图 17 示出了其一个实例。注意,在图 17 中,图 17B 相当于沿图 17A 的 a-b 之间的截面图,而图 17C 相当于沿图 17A 的 c-d 之间的截面图。

[0179] 图 17 所示的显示器件包括:中间夹着绝缘膜 1702 设置在衬底 1701 上的半导体膜 1703a 和 1703b;中间夹着栅绝缘膜 1704 设置在该半导体膜 1703a 和 1703b 上的栅电极 1705;覆盖栅电极而设置的绝缘膜 1706 和 1707;与半导体膜 1703a 和 1703b 的源区域或漏区域电连接且设置在绝缘膜 1707 上的导电膜 1708。注意,图 17 示出了设置 n 型薄膜晶体管 1710a 和 p 型薄膜晶体管 1710b 的情况,其中,半导体膜 1703a 的一部分用作 n 型薄膜晶体管 1710a 的沟道区域,半导体膜 1703b 的一部分用作 p 型薄膜晶体管 1710b 的沟道区域。但是,不限制于这种结构。例如,虽然在图 17 中将 LDD 区域设置在 n 型薄膜晶体管 1710a 而不在 p 型薄膜晶体管 1710b 上设置 LDD 区域,但是,既可以采用两者都设置有 LDD 区域的结构也可以采用两者都没有设置 LDD 区域的结构。

[0180] 衬底 1701 可以使用诸如硼硅酸钡玻璃和硼硅酸铝玻璃的玻璃衬底、石英衬底、陶瓷衬底、含有不锈钢的金属衬底等。除此以外,还可以使用由以聚对苯二甲酸乙二醇酯 (PET)、聚乙烯萘酯 (PEN) 和聚醚砜 (PES) 为代表的塑料和丙烯酸类具有弯曲性的合成树脂构成的衬底。通过使用有弯曲性的衬底,可以制造能够折弯的显示器件。由于这样的衬底其尺寸和形状没有很大的限制,所以作为衬底 1701 通过使用例如一边为 1m 以上的矩形衬底,就可以显著提高生产性。与使用圆形硅衬底的情形相比,这种优点有着巨大优势。

[0181] 为了防止由于 Na 等碱金属及碱土类金属从衬底 1701 向半导体膜 1703a、1703b 中扩散而导致对半导体元件的特性产生恶劣影响,设置用作基底膜的绝缘膜 1702。作为绝缘膜 1702 可被设置得具有诸如氧化硅 ( $\text{SiO}_x$ )、氮化硅 ( $\text{SiN}_x$ )、氧氮化硅 ( $\text{SiO}_x\text{N}_y$ ) ( $x > y$ ) 或氮氧化硅 ( $\text{SiN}_x\text{O}_y$ ) ( $x > y$ ) 等包含氧或氮的绝缘膜的单层结构或其叠层结构。例如,在设置具有双层结构的绝缘膜 1702 的情况下,氮氧化硅膜可被设为第一层的绝缘膜,而氧氮化硅膜可被设为第二层的绝缘膜为好。此外,在设置具有三层结构的绝缘膜 1702 的情况下,氧氮化硅膜可被设为第一层的绝缘膜、氮氧化硅膜可被设为第二层的绝缘膜、氧氮化硅膜可被设为第三层的绝缘膜为好。

[0182] 对非晶体半导体通过溅射法、LPCVD 法、等离子体 CVD 法等使用以硅 (Si) 为主要成分的材料来形成非晶体半导体膜,接着,通过结晶方法例如激光结晶法、RTA 或者利用退火炉热结晶或利用促进结晶化的金属元素的热结晶来使得该非晶体半导体膜结晶化,以获得半导体膜 1703a 和 1703b。

[0183] 可以使用氧化硅 ( $\text{SiO}_x$ )、氮化硅 ( $\text{SiN}_x$ )、氧氮化硅 ( $\text{SiO}_x\text{N}_y$ ,  $x > y$ ) 或氮氧化硅 ( $\text{SiN}_x\text{O}_y$ ) ( $x > y$ ) 等包含氧或氮的绝缘膜的单层结构或它们的叠层结构来设置栅绝缘膜 1704。

[0184] 可以通过溅射法、等离子体 CVD 法等设置绝缘膜 1706 以使其具有诸如氧化硅

( $\text{SiO}_x$ )、氮化硅 ( $\text{SiN}_x$ )、氧氮化硅 ( $\text{SiO}_x\text{N}_y$ ,  $x > y$ ) 或氮氧化硅 ( $\text{SiN}_x\text{O}_y$ ,  $x > y$ ) 等包含氧或氮的绝缘膜或诸如 DLC(类金刚石碳) 等含碳膜的单层结构或其叠层结构。

[0185] 绝缘膜 1707 可以被设置得具有由诸如氧化硅 ( $\text{SiO}_x$ ) 膜、氮化硅 ( $\text{SiN}_x$ ) 膜、氮氧化硅 ( $\text{SiO}_x\text{N}_y$ ,  $x > y$ ) 膜或氧氮化硅 ( $\text{SiN}_x\text{O}_y$ ,  $x > y$ ) 膜等包含氧或氮的绝缘膜或诸如 DLC(金刚石状碳) 膜的含碳膜、以及诸如环氧、聚酰亚胺、聚酰胺、聚乙烯基苯、苯并环丁烯、或丙烯酸的有机材料、硅氧烷树脂等组成的单层结构或者其叠层结构。注意，硅氧烷树脂相当于包含 Si-O-Si 结合的树脂。硅氧烷由硅 (Si) 和氧 (O) 结合构成其骨架结构。作为取代基，使用至少含有氢的有机基 (例如烷基、芳烃)。作为取代基还可以使用氟基。或者，作为取代基可以使用氟基和至少含有氢的有机基。注意，图 17 所示的显示器件还可以不设置绝缘膜 1706 而直接设置绝缘膜 1707 以覆盖栅电极 1705。

[0186] 作为导电膜 1708 可以使用由选自 Al、Ni、C、W、Mo、Ti、Pt、Cu、Ta、Au、Mn 中的一种元素或含有多种该元素的合金构成的单层或叠层结构。例如，作为由含有多种上述元素的合金组成的导电膜，可以使用含有 C 和 Ti 的 Al 合金、含有 Ni 的 Al 合金、含有 C 和 Ni 的 Al 合金、含有 C 和 Mn 的 Al 合金等。另外，在采用叠层结构的情况下，可以通过 Al 和 Ti 的叠层来进行设置。

[0187] 另外，在图 17 中，n 型薄膜晶体管 1710a 包括和栅电极 1705 的侧面接触的侧壁，并且形成有通过选择性地将赋予 n 型导电性的杂质添加到半导体膜 1703a 中而成的源区域和漏区域、以及设置在侧壁的下方的 LDD 区域。而且，p 型薄膜晶体管 1710b 具有和栅电极 1705 的侧面接触的侧壁，并且形成有通过选择性地将赋予 p 型导电性的杂质添加到半导体膜 1703b 中而成的源区域和漏区域。

[0188] 注意，在本发明的显示器件中，通过采用等离子体处理对于上述衬底 1701、绝缘膜 1702、半导体膜 1703a 和 1703b、栅绝缘膜 1704、绝缘膜 1706 或绝缘膜 1707 中的至少某一层进行氧化或氮化，而使半导体膜或绝缘膜氧化或氮化。如此，通过采用等离子体处理对半导体膜或绝缘膜进行氧化或氮化，就可以改善该半导体膜或绝缘膜的表面性质，并可以形成与由 CVD 法或溅射法形成的绝缘膜相比更致密的绝缘膜。因此，就可以抑制发生针孔等的缺陷而提高显示器件的特性等。

[0189] 另外，等离子体处理在电子密度为  $1 \times 10^{11} \text{ cm}^{-3}$  或更高至  $1 \times 10^{13} \text{ cm}^{-3}$  或更低，并且等离子体的电子温度为 0.5eV 或更高至 1.5eV 或更低的条件下进行。由于等离子体的电子密度为高密度，并且在形成于衬底 1701 之上的被处理物 (在此，半导体膜 1703a、1703b) 附近的电子温度较低，所以可以防止等离子体给被处理物带来的损伤。此外，由于等离子体的电子密度为  $1 \times 10^{11} \text{ cm}^{-3}$  以上的高密度，使用等离子体处理使被照射物氧化或氮化而形成的氧化物或氮化膜比起通过 CVD 法和溅射法等形成的薄膜来，膜厚度等在均匀性上表现出色，并且可以形成致密的膜。此外，由于等离子体的电子温度很低为 1.5eV 或更低，所以与以往的等离子体处理以及热氧化法相比，可以在更低的温度下进行氧化或氮化处理。例如，即使在比玻璃的扭变点再低 100 度以上的温度下进行等离子体处理，也可以充分进行氧化或氮化处理。注意，用于形成等离子体的频率可以采用微波 (2.45GHz) 等的高频率。

[0190] 接下来，对将非晶硅 (a-Si:H) 膜用于晶体管的半导体层的情况进行说明。图 18 表示顶部栅极晶体管的情况，图 19 和图 20 表示底部栅极晶体管的情况。

[0191] 图 18A 表示具有将非晶硅用于半导体层的顶部栅极结构的晶体管的横截面。基底

膜 1802 形成在衬底 1801 上, 像素电极 1803 进一步形成在基底膜 1802 上。另外, 由与像素电极 1803 相同的材料制成的第一电极 1804 形成在与像素电极 1803 同一层中。玻璃衬底、石英衬底、陶瓷衬底等可以用作衬底。另外, 作为基底膜 1802, 可以使用氮化铝 (AlN)、氧化硅 ( $\text{SiO}_2$ )、氧氮化硅 ( $\text{SiO}_x\text{N}_y$ ) 等的单层或者它们的叠层。

[0192] 此外, 布线 1805 和布线 1806 形成在基底膜 1802 上, 像素电极 1803 的端部由布线 1805 覆盖。在布线 1805 和布线 1806 上, 形成具有 N 型导电性的 N 型半导体层 1807 和 N 型半导体层 1808。另外, 在布线 1805 和布线 1806 之间, 半导体层 1809 形成在基底膜 1802 上。而且, 半导体层 1809 的一部分延伸至 N 型半导体层 1807 和 N 型半导体层 1808 上。注意, 由具有非晶体性诸如非晶硅 (a-Si:H) 和微晶半导体 ( $\mu$ c-Si:H) 等的半导体膜形成该半导体层。另外, 棚绝缘膜 1810 形成在半导体层 1809 上。另外, 由与棚绝缘膜 1810 相同材料制成且在同一层上形成的绝缘膜 1811 也形成在第一电极 1804 上。注意, 作为棚绝缘膜 1810, 可以使用氧化硅膜或氮化硅膜等。

[0193] 另外, 在棚绝缘膜 1810 上, 形成栅电极 1812。在由与栅电极相同的材料制成且在同一层上形成的第二电极 1813 夹着绝缘膜 1811 形成在第一电极 1804 上。形成将绝缘膜 1811 夹在第一电极 1804 和第二电极 1813 之间的电容器 1819。此外, 形成覆盖像素电极 1803 的端部、驱动晶体管 1818 和电容器 1819 的层间绝缘膜 1814。

[0194] 含有有机化合物的层 1815 和相对电极 1816 形成在层间绝缘膜 1814 和位于其开口部分的像素电极 1803 上。在将含有有机化合物的层 1815 夹在像素电极 1803 和相对电极 1816 之间的区域中, 形成发光元件 1817。

[0195] 另外, 也可以如图 18B 所示用第一电极 1820 形成如图 18A 所示的第一电极 1804。第一电极 1820 由与布线 1805 和 1806 同层的相同材料形成。此外, 图 19 表示使用具有底部栅极结构的晶体管的显示器件的面板的局部横截面图, 其中非晶硅被用于半导体层。

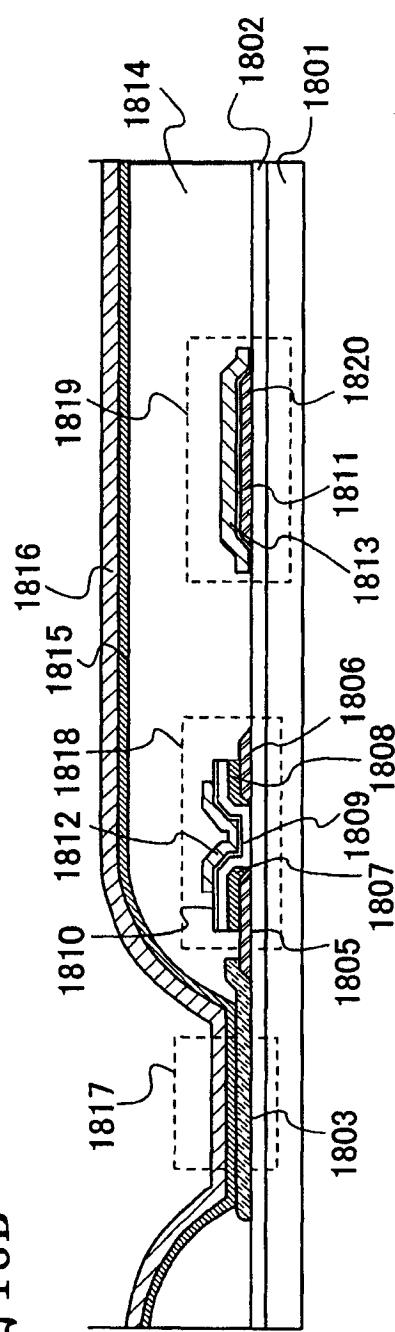

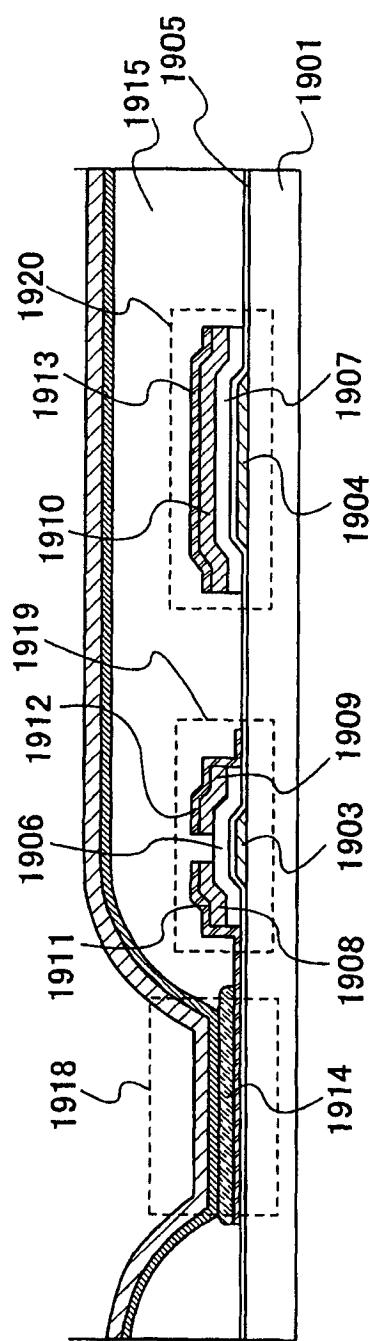

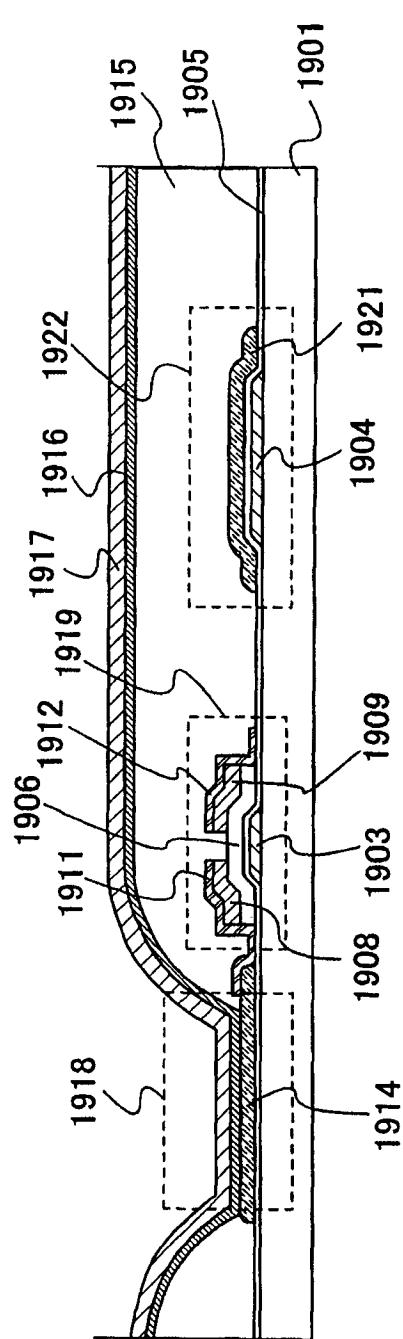

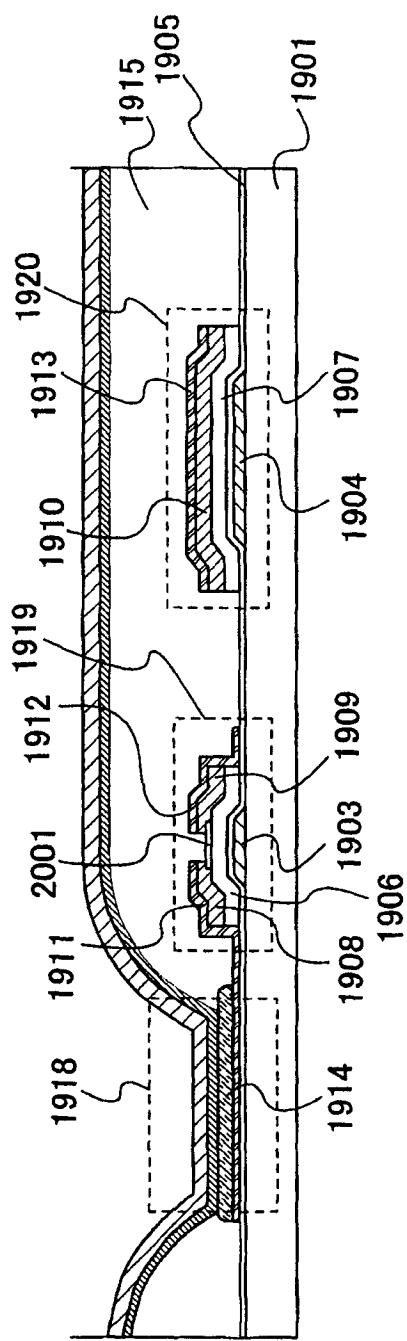

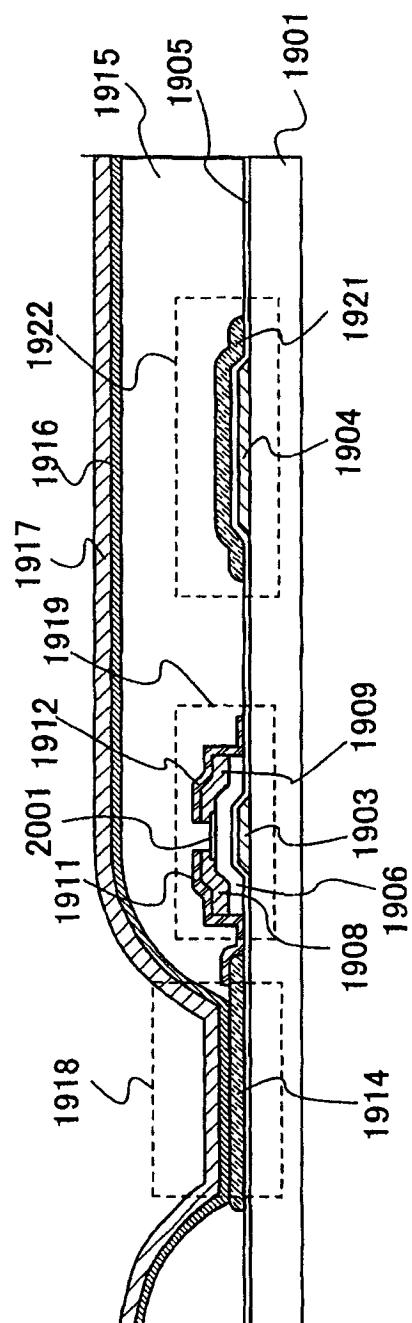

[0196] 棚电极 1903 形成在衬底 1901 上。另外, 由与棚电极 1903 相同材料制成的第一电极 1904 形成在同一层中。在棚电极 1903 的材料中可以使用添加了磷的多晶硅。除了多晶硅外, 也可以使用作为金属和硅的化合物的硅化物。

[0197] 此外, 形成棚绝缘膜 1905, 以覆盖棚电极 1903 和第一电极 1904。作为棚绝缘膜 1905, 使用氧化硅膜或氮化硅膜等。在棚绝缘膜 1905 上, 形成半导体层 1906。由与该半导体层 1906 相同材料制成的半导体层 1907 形成在同一层中。

[0198] 在半导体层 1906 上, 形成具有 N 型导电性的 N 型半导体层 1908 和 1909, 而 N 型半导体层 1910 形成在半导体层 1907 上。在 N 型半导体层 1908 和 1909 上, 分别形成布线 1911 和 1912, 而在 N 型半导体层 1910 上, 形成由与布线 1911 和 1912 相同材料制成且在同一层中的半导体层 1913。形成由半导体层 1907、N 型半导体层 1910 和导电层 1913 构成的第二电极。注意, 形成具有将棚绝缘膜 1905 夹在该第二电极和第一电极 1904 之间的结构的电容元件 1920。

[0199] 此外, 布线 1911 的一个端部延伸, 与该延伸的布线 1911 的上部接触而形成像素电极 1914。以覆盖像素电极 1914 的端部、驱动晶体管 1919 和电容元件 1920 的方式形成绝缘层 1915。

[0200] 发光层 1916 和相对电极 1917 形成在像素电极 1914 和绝缘层 1915 上, 在将发光层 1916 夹在像素电极 1914 和相对电极 1917 之间的区域中, 形成发光元件 1918。

[0201] 也可以不设置作为电容元件的第二电极之一部分的半导体层 1907 和 N 型半导体层 1910。也就是说，第二电极可以是导电层 1913，电容元件可以具有将栅绝缘膜夹在第一电极 1904 和导电层 1913 之间的结构。

[0202] 在图 19A 中，通过在形成布线 1911 之前形成像素电极 1914，就可以形成如图 19B 所示的具有将栅绝缘膜 1905 夹在由像素电极 1914 形成的第二电极 1921 和第一电极 1904 之间的结构的电容元件 1922。注意，在图 19 中，虽然对反转交错的沟道蚀刻结构的晶体管进行了描述，但是不言而喻，也可以是沟道保护结构的晶体管。将参考图 20A 和 20B 对沟道保护结构的晶体管的情况进行描述。

[0203] 如图 20A 所示的沟道保护型结构的晶体管不同于图 19A 所示的沟道蚀刻结构的驱动晶体管 1919 之处就在于：在由半导体层 1906 的沟道形成的区域上设置作为蚀刻掩模的绝缘体 2001，在其他相同的之处使用相同的附图标记。同样，图 20B 所示的沟道保护型结构的晶体管不同于图 19B 所示的沟道蚀刻结构的驱动晶体管 1919 之处就在于：在由半导体层 1906 的沟道形成的区域上设置作为蚀刻掩模的绝缘体 2001，在其他相同之处使用相同的附图标记。

[0204] 当将非晶半导体膜用于形成像素的晶体管的半导体层（沟道形成区、源区域、漏区域等）时，可以缩减制造成本。注意，可以应用本发明像素结构的晶体管结构和电容元件结构并不限于上述结构，还可以使用各种结构的晶体管结构和电容元件结构。

[0205] 当制造上述显示器件时，在光蚀刻工序中还可以使用其透光率有坡度的光掩模（半色调掩模）。以下，将说明应用使用了半色调掩模时的本发明的显示器件的制造方法。

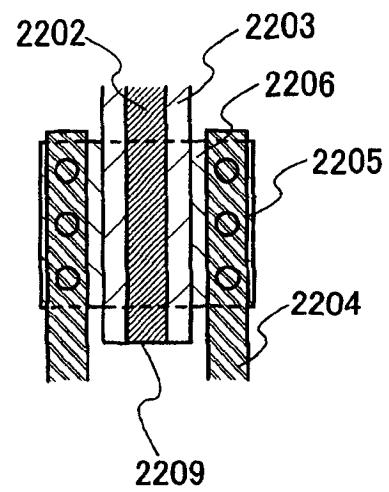

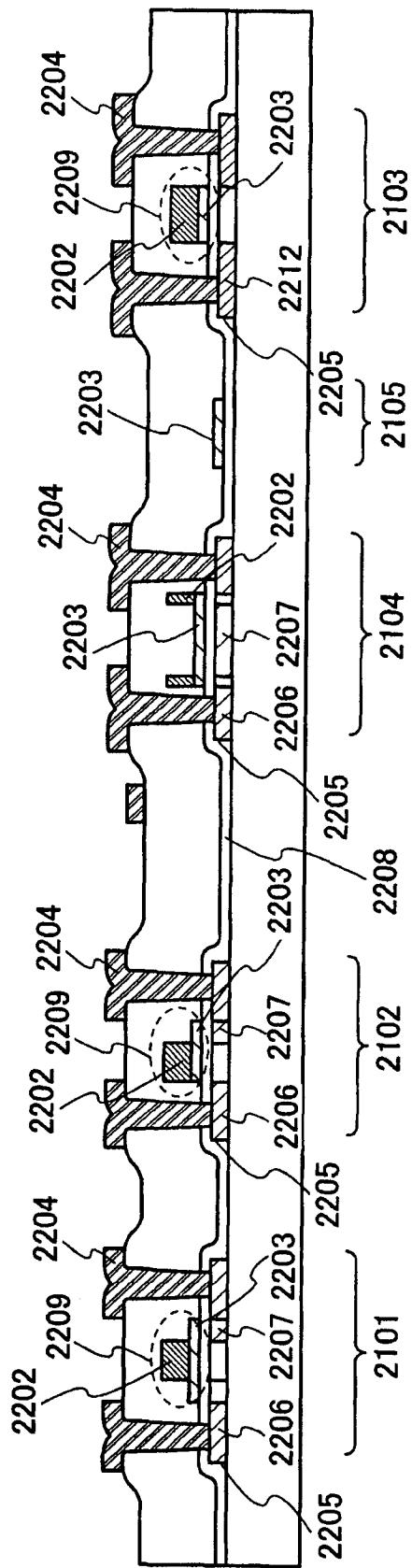

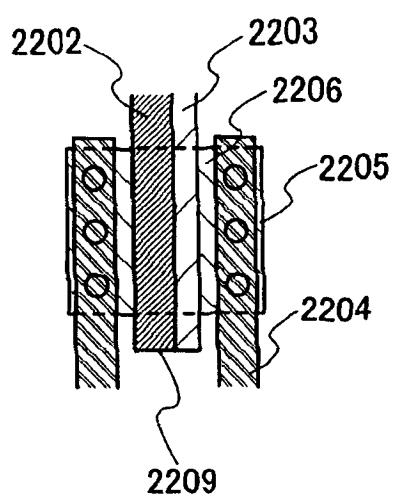

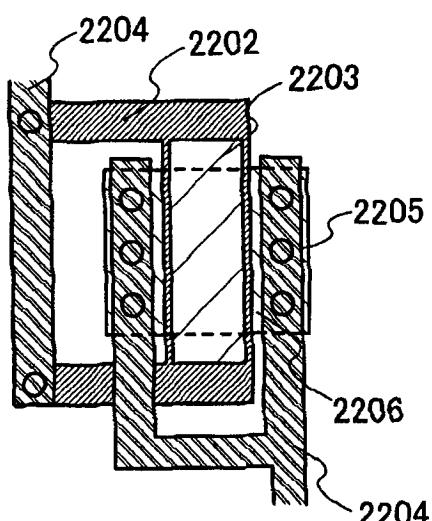

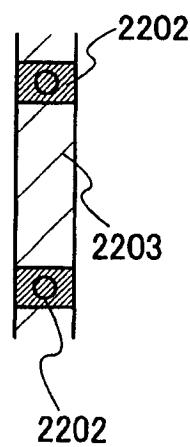

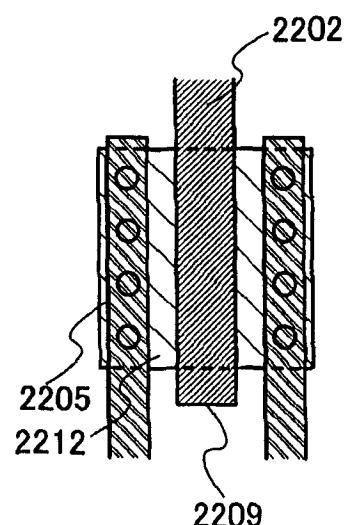

[0206] 晶体管除了可以使用形成在单晶衬底上的 MOS 晶体管以外还可以用薄膜晶体管（TFT）而构成。图 21 是表示构成电路的晶体管的截面结构的图。图 21 描述了 n 沟道型晶体管 2101、n 沟道型晶体管 2102、电容元件 2104、电阻元件 2105、p 沟道型晶体管 2103。每个晶体管包括半导体层 2205、栅绝缘层 2208、栅电极 2209。栅电极 2209 由第一导电层 2203 和第二导电层 2202 的叠层结构形成。另外，图 22A 至 22D 是对应于图 21 所示的晶体管、电容元件和电阻元件的俯视图，可以同时参照这些附图。

[0207] 在图 21 中，n 沟道型晶体管 2101 沿着沟道长度方向（载流子的流动方向）在栅电极的两边的半导体层 2205 中形成有杂质区域 2207。该也被称作低浓度漏区（LDD）的杂质区域 2207，与构成和布线 2204 接触的源区域或漏区域的杂质区域 2206 的杂质浓度相比，以更低浓度被添加杂质。在构成 n 沟道型晶体管 2101 的情况下，杂质区域 2206 和杂质区域 2207 添加有磷等赋予 n 型的杂质。LDD 是用作抑制热电子退化或短沟道效应的部件而形成的。

[0208] 如图 22A 所示，在 n 沟道型晶体管 2101 的栅电极 2209 中，第一导电层 2203 广泛地形成在第二导电层 2202 的两侧。在此情况下，第一导电层 2203 的膜厚度形成为比第二导电层的膜厚度更薄。第一导电层 2203 的厚度形成为能够透过由 10 至 100kV 的电场进行了加速的种子离子的厚度。杂质区域 2207 被形成为重叠于栅电极 2209 的第一导电层 2203。那就是说，形成与栅电极 2209 重叠的 LDD 区域。该结构是，通过在栅电极 2209 中将第二导电层 2202 作为掩模，经过第一导电层 2203 添加具有一导电性的杂质，以自对准方式形成杂质区域 2207。也就是说，以自对准方式形成了与栅电极重叠的 LDD 区域。

[0209] 在图 21 中，n 沟道型晶体管 2102 在栅电极的一侧的半导体层 2205 中形成有以低

于杂质区域 2206 的杂质浓度添加杂质的杂质区域 2207。如图 22B 所示,在 n 沟道型晶体管 2102 的栅电极 2209 中,第一导电层 2203 广泛地形成在第二导电层 2202 的单侧。在此也同样地,通过将第二导电层 2202 作为掩模,经过第一导电层 2203 添加具有一导电性的杂质,就可以自对准方式形成 LDD 区域。

[0210] 在单侧具有 LDD 的晶体管适用于在源电极和漏电极之间只施加正电压或只施加负电压的晶体管为好。具体地,可以适用于构成反相器电路、NAND 电路、NOR 电路、锁存电路之类的逻辑门的晶体管、或者构成传感放大器、恒电压产生电路、VOC 之类的模拟电路的晶体管。

[0211] 在图 21 中,电容元件 2104 将栅绝缘层 2208 夹在第一导电层 2203 和半导体层 2205 之间而形成。在形成电容元件 2104 的半导体层 2205 上具有杂质区域 2206 和杂质区域 2207。杂质区域 2207 形成在半导体层 2205 的与第一导电层 2203 重叠的位置上。另外,杂质区域 2206 与布线 2204 形成接触。由于杂质区域 2207 可以经过第一导电层 2203 来添加一导电型的杂质,所以能够将包含在杂质区域 310 和杂质区域 2207 中的杂质浓度设为相同,还可设为不同。总之,在电容元件 2104 中使半导体层 2205 用作电极,因此,优选添加一导电型的杂质以进行低电阻化。另外,如图 22C 所示,通过利用第二导电层 2202 作为辅助电极,就可以充分地使第一导电层 2203 作为电极发挥作用。如此,通过采用将第一导电层 2203 和第二导电层 2202 组合的复合电极结构,就可以以自对准方式形成电容元件 2104。

[0212] 在图 21 中,电阻元件 2105 由第一导电层 2203 形成。第一导电层 2203 形成为具有大约 30nm 至 150nm 程度的厚度,从而能够通过适当地设定该幅度和长度来构成电阻元件。

[0213] 在图 21 中,p 沟道型晶体管 2103 在半导体层 2205 中具有杂质区域 2212。该杂质区域 2212 形成与布线 2204 形成接触的源区域和漏区域。栅电极 2209 的结构是第一导电层 2203 和第二导电层 2202 重叠的结构。p 沟道型晶体管 2103 是没有设置 LDD 的具有单漏极结构的晶体管。当形成 p 沟道型晶体管 2103 时,将赋予 p 型的杂质如硼等添加在杂质区域 2212 中。另一方面,如果给杂质区域 2212 添加磷,就可以形成具有单漏极结构的 n 沟道型晶体管。

[0214] 还可以对半导体层 2205 及栅绝缘层 2208 的一方或双方进行使用由微波激励的高密度等离子体处理,以进行氧化或氮化处理,其中,高密度等离子体处理的条件如下:电子温度为 2eV 或更低、离子能量为 5eV 或更低、电子密度大约为  $10^{11}$  至  $10^{13}\text{cm}^{-3}$ 。此时,通过使衬底温度设为 300°C 至 450°C 且在氧化气氛中 ( $\text{O}_2$ 、 $\text{N}_2\text{O}$  等) 或氮化气氛中 ( $\text{N}_2$ 、 $\text{NH}_3$  等) 执行处理,就可以降低半导体层 2205 和栅绝缘层 2208 的界面的缺陷能级。通过对栅绝缘层 2208 进行该处理,就可以谋求该绝缘层致密化。就是说,可以抑制电荷缺陷发生并抑制晶体管的阈值电压变动。另外,在以低于 3V 的电压驱动晶体管时,可以将通过该等离子体处理被氧化或氮化的绝缘层适用于栅绝缘层 2208。另外,在晶体管的驱动电压为 3V 或更大的情形中,可以组合用该等离子体处理形成在半导体层 2205 的表面上的绝缘层和用 CVD 法(等离子体 CVD 法或热 CVD 法)淀积的绝缘层,而形成栅绝缘层 2208。此外,同样地,该绝缘层也可以利用于电容元件 2104 的介电层。此时,用该等离子体处理形成的绝缘层被形成为 1nm 至 10nm 的厚度,并且是致密的膜,所以可以形成具有大电荷容量的电容元件。

[0215] 如参照图 21 和图 22 所说明那样,通过组合厚度不同的导电层,就可以形成具有各种结构的元件。通过使用设置了衍射光栅图案或由半透明膜构成的具有光强度降低功能的

辅助图案的光掩模或中间掩模,就可以形成只形成有第一导电层的区域和层叠有第一导电层和第二导电层的区域。也就是说,在光蚀刻工序中,曝光光抗蚀剂时,调节光掩模的透过光量,以使被显影的抗蚀剂掩模具有不同的厚度。此时,可以在光掩模或中间掩模中提供比分辨率界限更窄的狭缝,以形成具有上述复杂形状的抗蚀剂。另外,在显影后,可以进行大约200°C的烘焙以使由光抗蚀剂材料形成的掩模图案变形。

[0216] 另外,通过使用设置了衍射光栅图案或由半透明膜构成的具有光强度降低功能的辅助图案的光掩模或中间掩模,就可以连续形成只形成有第一导电层的区域和层叠有第一导电层和第二导电层的区域。如图22A所示,可以选择性地将只形成有第一导电层的区域形成在半导体层上。这样的区域在半导体层上很有效,但在其外的区域中(与栅电极连续的布线区域)不是必需的。通过使用上述光掩模或中间掩模,就可以在布线部分中不制造只有第一导电层的区域,所以能够实际上提高布线密度。

[0217] 在图21和图22的情形中,第一导电层使用诸如钨(W)、铬(Cr)、钽(Ta)、氮化钽(TaN)或钼(Mo)等的高熔点金属或以高熔点金属作为主要成分的合金或化合物形成为30nm至50nm的厚度。而且,第二导电层使用诸如钨(W)、铬(Cr)、钽(Ta)、氮化钽(TaN)或钼(Mo)等的高熔点金属或以高熔点金属作为主要成分的合金或化合物形成为300nm至600nm的厚度。例如,第一导电层和第二导电层分别使用不同的导电材料,以便在后面进行的蚀刻工序中得到蚀刻速率差。作为一个实例,能够使用TaN作为第一导电层,使用钨膜作为第二导电层。

[0218] 本实施方式示出了,通过使用设置了衍射光栅图案或由半透明膜构成的具有光强度降低功能的辅助图案的光掩模或中间掩模,可以通过相同的工序分开制作具有不同电极结构的晶体管、电容元件以及电阻元件。由此,就可以根据电路的特性作成形态不同的元件,而无须增加工序,以实现集成化。

[0219] (实施方式8)

[0220] 在本实施方式中将说明可以应用于本发明的像素结构。注意,省略与图3相同结构的说明。图10示出一种像素结构,其特征是除了图3中示出的像素结构之外还在电容元件16的两端设置第三晶体管25。第三晶体管25的功能是在预定周期内使累积在电容元件16中的电荷放电。该第三晶体管25也称作删除用晶体管。由连接第三晶体管25的栅电极的删除用栅极线Ry来控制预定周期。

[0221] 例如,在设置多个子帧周期的情况下,在短子帧周期由第三晶体管25使电容元件16的电荷放电。其结果,就可以提高占空比。

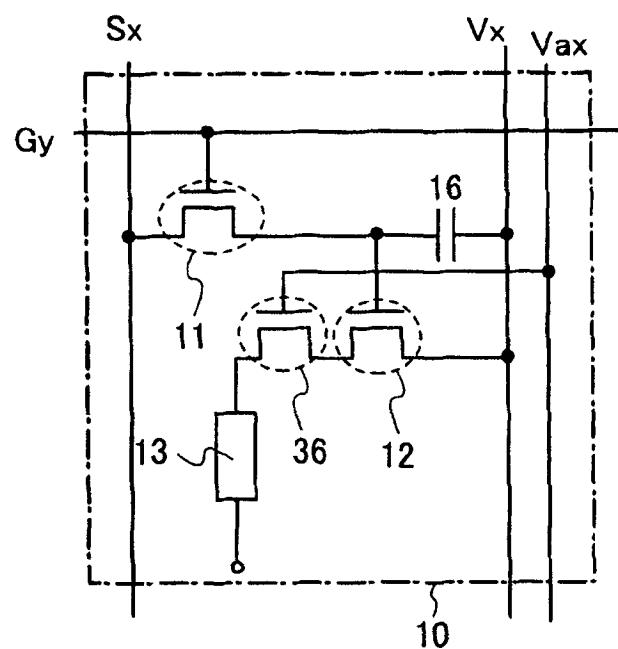

[0222] 图11A示出一种像素结构,其特征是除了图3中示出的像素结构之外还在驱动用晶体管12和发光元件13之间设置第四晶体管36。在第四晶体管36的栅电极上连接有具有固定电位的第二电源线Vax。所以,可以不依赖于驱动用晶体管12和第四晶体管36的栅源间的电压地使提供给发光元件13的电流恒定。该第四晶体管36也称作电流控制用晶体管。图11B示出不同于图11A的像素结构,其特征在于,具有固定电位的第二电源线Vax与栅极线Gy并行地设置。图11C示出不同于图11A和图11B的像素结构,其特征在于,第四晶体管36的具有固定电位的栅电极连接到驱动用晶体管12的栅电极。如图11C中所示,在不用新设置电源线的像素结构中,可以维持开口率。

[0223] 图12示出一种像素结构,其特征是对图11A示出的像素结构添加设置图10示出

的删除用晶体管 25。借助于删除用晶体管就可以使电容元件 16 的电荷放电。不用说,可以对图 11B 或 11C 示出的像素结构添加设置删除用晶体管。

[0224] 在此,将说明在一个像素中设置多个子像素时的像素电路。虽然没有图示出,当在一个像素中设置多个子像素并分别独立地驱动时,按照子像素的数量准备数据线、扫描线和电源线,并且分别配置一个像素部分的元件即可。但是,在数据线、扫描线和电源线之中能够在子像素之间共同使用的也可以共同使用。以下描述共同使用时的电路实例。

[0225] 图 23A 示出了一个像素电路图,其中,在子像素之间共同使用与驱动晶体管的源区域或漏区域中的一方连接的电源线和扫描线。图 23B 示出了只共同使用扫描线的像素电路图。图中的第一驱动用晶体管 12、第一发光元件 13、第二驱动晶体管 114、第二发光元件 14 是与图 1 所示相同的。在图 23A 中,除了上述结构之外,还由扫描线 2301、第一数据线 2302、第二数据线 2303、电源线 2304、第一选择晶体管 2305、第二选择晶体管 2306、第一电容元件 2307、第二电容元件 2308 构成。在图 23B 中除了上述结构外还添加有第二电源线 2309。

[0226] 第一子像素由第一选择晶体管 2305、第一电容元件 2307、第一驱动用晶体管 12、第一发光元件 13 构成。同样,第二子像素由第二选择晶体管 2306、第二电容元件 2308、第二驱动晶体管 114、第二发光元件 14 构成。

[0227] 由于进行扫描的定时在子像素间也可以相同,所以可以如图 23 所示那样在子像素之间共同使用扫描线,而分别使用不同的数据线。如果共同使用扫描线,就能够在像素电路的布局上提供裕度,从而可以提高像素的开口率。另外,也可以实现成品率的提高。

[0228] 图 24A 示出了在子像素中通过数据线 2403 来共同使用电源线和数据线的像素电路图,其中,电源线与驱动晶体管的源区域或漏区域中的一方连接,而数据线与选择晶体管的源区域或漏区域中的一方连接。图 24B 示出了只共同使用数据线的像素电路图。如图 24 所示的扫描线 2401、2402 那样,还可以通过分别使用不同的扫描线而在子像素之间改变扫描定时,以共同使用数据线。如果共同使用数据线,就能够提供像素电路的布局裕度,从而可以提高像素的开口率。另外,也可以实现成品率的提高。此外,由于数据线的寄生电容较小,所以伴随数据线的充放电导致的耗电量减小。

[0229] 如上所述,通过在子像素之间共同使用布线来进行面积灰度级显示,与没有子像素的情况相比就可以实现多灰度等级化而不会减少像素开口率和成品率。注意,当不共同使用电源线时,如实施方式 1 所述那样具有可以在每个子像素中利用监视用发光元件进行退化以及温度的修正,并且还可以降低由于流经电源线中的电流电压下降而导致的电压变动等、特别的效果,所以对于电源线不共同使用的情况也一并进行了记述。

[0230] 接下来,将说明采用了本发明的能够全色显示的显示器件的像素电路。由于在具有以 R、G、B 进行颜色区分的像素的显示器件中由于发光像素的退化或温度导致的特性变化对发光元件的每个发光色不同,所以也可以如图 25 那样按每种颜色分别应用本发明的结构。

[0231] 图 25A 示出了将本发明适用于将图 23A 所示的像素 2300a 中的发光元件以 R、G、B 进行了颜色区分的显示器件上的结构。此时,还可以对监视电路 64 也同样进行颜色区分,以对每个 R、G、B 修正由于退化或温度导致的特性变化。这里的像素结构也可以不用图 23A 的结构,而用与图 24A 所示的像素 2400a 相同的结构。

[0232] 图 25B 示出了将本发明适用于将图 23B 所示的像素 2300b 中的发光元件以 R、G、B 进行了颜色区分的显示器件上的结构。此时,还可以对监视电路 64 也同样进行颜色区分,以对每个 R、G、B 修正由于退化或温度的影响导致的特性变化。这里的像素可以不用图 23B 的结构,而用与图 24B 所示的像素 2400b 相同的结构。另外,作为用于实现全色显示的像素结构,还可以采用如图 26 所示的将一个像素分成三个或更多个像素的结构。此时,也可以按已分割的数量配置监视电路 64,以在每个发光元件中修正由于退化或温度导致的特性变化。

[0233] 图 26A 示出了将本发明适用于将图 23A 所示的像素中的发光元件以 W、R、G、B 进行了颜色区分的显示器件上的结构。此时,还可以对监视电路 64 也同样进行颜色区分,以对每个 W、R、G、B 修正由于退化或温度导致的特性变化。这里的像素结构可以不用图 23A 的结构,而用与图 24A 相同的结构。

[0234] 图 26B 示出了将本发明适用于将图 23B 所示的像素中的发光元件以 W、R、G、B 进行了颜色区分的显示器件上的结构。此时,还可以对监视电路 64 也同样进行颜色区分,以对每个 W、R、G、B 修正由于退化或温度导致的特性变化。这里的像素结构可以不用图 23B 的结构,而用与图 24B 相同的结构。

[0235] 注意,虽然在图 25 和图 26 中描述了已分割的所有像素具有相同数量的电源线的例子,但并不局限于此。例如,在图 26 的结构中,也可以是仅 W 像素采用图 23A 所示的结构,而剩余的 R、G、B 三者都采用图 23B 所示的结构。像这样,经过颜色区分的各个像素电路既可以采用相互不同的像素结构,也可以自由地选择其结构。

[0236] (实施方式 9)

[0237] 本实施方式中将说明在由使用非晶硅的晶体管构成的显示器件中适用本发明时的像素结构以及将亮度信息写入到像素中的写入方法。

[0238] 使用非晶硅的半导体集成器件在其制造工序上难以构成一体地形成有不同导电型的晶体管的、所谓的 CMOS 电路。即使可能构成 CMOS 电路,其制造工序也与只形成单一导电型的晶体管的情况相比不可避免地复杂化,所以不能有效地利用在使用非晶硅时的最大优点、即通过简单的制造工序而实现低成本。因此,当设计使用非晶硅的半导体集成器件时,需要考虑到只使用单一导电型的晶体管来构成电路。

[0239] 另外,与使用块状硅和多晶硅的晶体管不同,使用非晶硅的晶体管,因连续工作而引起的随时间的退化,尤其是阈值的增加是很明显的。该阈值增加的主要原因在于,由于将正方向电压连续施加到晶体管的栅电极上,而被捕获到栅绝缘膜中的电荷量增加,并且沟道部分的缺陷密度增大。作为抑制发生这些现象而防止晶体管的阈值转移的方法,例如有设置将负方向电压施加到栅电极上的期间的方法。

[0240] 图 27 示出了一种显示器件的结构,其防止当使用非晶硅时的晶体管的随时间的退化。在图 27 中使用与图 2 相同的附图标记的部分表示具有相同或几乎相同的功能的部分。其中,附图标记 2700 是像素电路、2701 是预充电电路、S1 至 Sx 传输对像素写入的亮度信号的数据线。数据线 S1 至 Sx 通过开关连接到信号线驱动电路 43 以及预充电电路 2701。每个数据线提供有两个开关,但该两个开关不会同时导通,而至少其中一个导通。另外,将构成像素电路 2700 的晶体管的导电型都设为 N 沟道型来进行说明。

[0241] 在信号线驱动电路 43 工作而将预定电压写入到像素中之前,预充电电路 2701 工

作。也就是说，首先配置在数据线 S1 至 Sx 上的开关之中预充电电路 2701 一侧的开关导通，从而写入到像素中的电压先设定为预充电电路 2701 所决定的电压，然后配置在数据线 S1 至 Sx 上的开关切换，从而信号线驱动电路 43 所决定的电压写入到像素中。

[0242] 在此，由预充电电路 2701 所决定的预充电电压优选为等于或低于使驱动用晶体管 12 和 114 关断的电压，且等于或高于电源 18 的电位。其理由在于：如上所述，在使用非晶硅的晶体管中，为了防止因随时间的退化引起的阈值电压转移，而设置将负方向电压施加到栅电极上的期间是有效的，但是还因为如果将在预充电期间中向像素写入的电压设定为低于使驱动用晶体管 12 和 114 关断的电压，就可以设置使所有驱动晶体管的栅电压为负方向电压的期间，从而可以降低驱动晶体管的随时间的退化而引起的阈值电压转移。而且，由于过度降低预充电电压时，也将导致耗电量的增大和电源电路的高成本化，所以预充电电压优选为等于相对电极一侧的电源 18 的电位或更高。

[0243] 注意，预充电电路 2701 的目的是将恒定电压施加到所有驱动晶体管的栅电极，因而，不需要在电路中具有电气性元件，也可以采用将外部输入电源传送到数据线 S1 至 Sx 的布线。

[0244] 接下来，将用图 28 说明适于向驱动晶体管的栅极施加负方向电压的像素结构。图 28 是沿着数据线的方向相邻的两个像素的电路图，其结构在图 3 所示的像素电路上添加有负方向电压施加用晶体管 2800。负方向电压施加用晶体管 2800 的栅电极连接到前一个像素的扫描线，并且负方向电压施加用晶体管 2800 的源电极和漏电极中的一方连接到该像素的扫描线，负方向电压施加用晶体管 2800 的源电极和漏电极中的另一方连接到驱动用晶体管 12 的栅电极。

[0245] 图 28 所示的像素不需要使用任何特别的驱动方法，而只通过与使用图 3 时完全相同地进行驱动，就可以实现给驱动用晶体管 12 的栅电极施加负方向电压的驱动。在该像素的前一个像素被选择时，该像素的晶体管 2800 导通。于是，由于这时的该像素的扫描线电位是低电位，因此驱动用晶体管 12 的栅电极的电位通过晶体管 2800 变为低电位。此时，向驱动用晶体管 12 的栅电极施加负方向电压。在该像素被选择时，晶体管 2800 的栅电极为低电位，并且源电极或漏电极为比该栅电极高的电位，所以晶体管 2800 关断。从而，在该像素被选择时进行数据写入，而晶体管 2800 不妨碍写入工作。如上所述，通过使用图 28 所示的像素，就可以大幅度提高晶体管的可靠性，而不受晶体管 2800 的写入时间的限制，又无须添加用于施加负电荷的特别的外围驱动电路。

[0246] 这里，优选的是，扫描线的低电位侧电位设定为在像素中的电极可取的电位中最底，而且扫描线的高电位侧电位设定为在像素中的电极可取的电位中最高，以便确实地使晶体管 2800 开启和关闭。

[0247] 注意，图 28 所示的像素电路的目的在于，在将数据写入到该像素之前，给驱动用晶体管 12 的栅电极提供十分低的电位。从而，在不背离该目的的情况下，可以将添加的晶体管的电极连接到任何部分。例如，晶体管 2800 的栅电极可以连接于该像素的前两个的扫描线，也可以连接到专门设置的扫描线。另外，晶体管 2800 的源电极或漏电极中的一方，例如可以连接到相对电极，也可以连接到电源线。此外，对于添加晶体管 2800 的原来像素当然不局限于具有图 3 所示的结构。例如，既可以是使用子像素的图 23 所示的像素，也可以是图 24 所示的像素。进而，还可以采用添加了删除用晶体管的图 10 所示的像素，也可以使

用添加了栅电位固定的晶体管的图 11、12 所示的像素。只要按照所述目的,即,在写入数据之前将低电位写入到驱动晶体管的栅电极即可,被添加晶体管的原来像素的结构上没有限制。

[0248] (实施方式 10)

[0249] 在本实施方式中,将说明具有上述实施方式所示的像素电路的面板的整体结构。

[0250] 如图 13 所示,本发明的显示器件包括以矩阵状配置多个上述像素 10 的像素部分 40、第一扫描线驱动电路 41、第二扫描线驱动电路 42 以及信号线驱动电路 43。可以使第一扫描线驱动电路 41 和第二扫描线驱动电路 42 夹着像素部分 40 彼此面对地进行配置,或者可以在像素部分 40 的上下左右四方中的一方配置第一扫描线驱动电路 41 和第二扫描线驱动电路 42。

[0251] 信号线驱动电路 43 包括脉冲输出电路 44、锁存器 45 以及选择电路 46。锁存器 45 具有第一锁存器 47 和第二锁存器 48。选择电路 46 具有晶体管 49 和模拟开关 50 作为开关组件。在各列中对应于信号线设置晶体管 49 和模拟开关 50。另外,在本实施方式中,在各列中设置反相器 51 用于生成 WE 信号的反相信号。注意,当 WE 信号的反相信号由外部提供时,则也可以不设置反相器 51。

[0252] 晶体管 49 的栅电极连接到选择信号线 52,并且其一个电极连接到信号线而另一电极连接到电源 53。在第二锁存器 48 和各条信号线之间设置模拟开关 50。换言之,模拟开关 50 的输入端子连接到第二锁存器 48 而输出端子连接到信号线。模拟开关 50 的两个控制端子之一连接到选择信号线 52 而另一端子通过反相器 51 连接到选择信号线 52。电源 53 的电位为关断像素所具有的驱动用晶体管 12 的电位,在驱动用晶体管 12 的极性是 n 沟道型时设电源 53 的电位为 Low,而在驱动用晶体管 12 为 p 沟道型时则设电源 53 的电位为 High。

[0253] 第一扫描线驱动电路 41 包括脉冲输出电路 54 和选择电路 55。第二扫描线驱动电路 42 包括脉冲输出电路 56 和选择电路 57。分别向脉冲输出电路 54 和 56 输入启动脉冲 (G1SP, G2SP)。还分别向脉冲输出电路 54 和 56 输入时钟脉冲 (G1CK, G2CK) 和其反相的时钟脉冲 (G1CKB, G2CKB)。

[0254] 选择电路 55 和 57 连接到选择信号线 52,但是包括在第二扫描线驱动电路 42 中的选择电路 57 通过反相器 58 连接到选择信号线 52。换言之,通过选择信号线 52 输入到选择电路 55 和 57 的 WE 信号处于彼此反相了的关系。

[0255] 选择电路 55 和 57 各个包括三态缓冲电路。当从选择信号线 52 发送的信号处于 H(高)电平时三态缓冲电路进入工作状态,并且当信号处于 L(低)电平时进入高阻抗状态。包括在信号线驱动电路 43 中的脉冲输出电路 44、包括在第一扫描线驱动电路 41 中的脉冲输出电路 54 以及包括在第二扫描线驱动电路 42 中的脉冲输出电路 56 具有由多个触发电路构成的移位寄存器或译码器电路。如果译码器电路用作脉冲输出电路 44、54 和 56,就可以随机地选择信号线或扫描线。通过随机地选择信号线或扫描线,就可以抑制当采用时间灰度等级方式时出现的伪轮廓的发生。

[0256] 此外信号线驱动电路 43 的结构并不限于前面提到的结构,还可以设置电平移动器或缓冲器。另外,第一扫描线驱动电路 41 和第二扫描线驱动电路 42 的结构也并不限于前面提到的结构,还可以设置电平移动器或缓冲器。此外,信号线驱动电路 43、第一扫描线

驱动电路 41、以及第二扫描线驱动电路 42 还可以分别包括保护电路。

[0257] 此外，在本发明中还可以设置保护电路。保护电路可以形成为包括多个电阻元件。例如，p 沟道型晶体管可以用作多个电阻元件。可以在信号线驱动电路 43、第一扫描线驱动电路 41、或第二扫描线驱动电路 42 中分别设置保护电路，优选的是，设置在像素部分 40 和信号线驱动电路 43、第一扫描线驱动电路 41、或第二扫描线驱动电路 42 之间。借助于这种保护电路就可以防止元件由于静电而引起的退化或破坏。

[0258] 另外在本实施方式中，显示器件包括电源控制电路 63。电源控制电路 63 具有用于向发光元件 13 供应电源的电源电路 61 和控制器 62。电源电路 61 包括第一电源 17，该第一电源 17 通过驱动用晶体管 12 和电源线 Vx 连接到发光元件 13 的像素电极。另外电源电路 61 还包括第二电源 18，该第二电源 18 通过连接到相对电极的电源线连接到发光元件 13。

[0259] 这种电源电路 61，当向发光元件 13 施加正向电压使得发光元件 13 中流过电流而发光时，设定第一电源 17 的电位高于第二电源 18 的电位。另一方面，当向发光元件 13 施加反向电压时，设定第一电源 17 的电位低于第二电源 18 的电位。可以通过从控制器 62 向电源电路 61 提供预定的信号来进行这种电源的设定。

[0260] 在本实施方式中，特征是发光器件还包括监视电路 64 和控制电路 65。控制电路 65 包括恒定电流源 105 和缓冲放大器电路 110。另外监视电路 64 包括监视用发光元件 66、监视控制用晶体管 111 以及反相器 112。

[0261] 按照监测电路 64 的输出，控制电路 65 向电源控制电路 63 提供用于修正电源电位的信号。根据从控制电路 65 提供的信号，电源控制电路 63 修正提供给像素部分 40 的电源电位。具有上述结构的本发明的显示器件可以抑制由于环境温度的变化和随时间进展的退化而引起的电流值的变动，使得可靠性增加。进而，通过使用监视控制用晶体管 111 和反相器 112，就可以防止来自恒流源 105 的电流流过已短路的监视用发光元件 66 中，从而可以将正确的电流值的变动提供给发光元件 13。

[0262] (实施方式 11)

[0263] 在本实施方式中将参照附图说明具有上述结构的本发明的显示器件的工作过程。

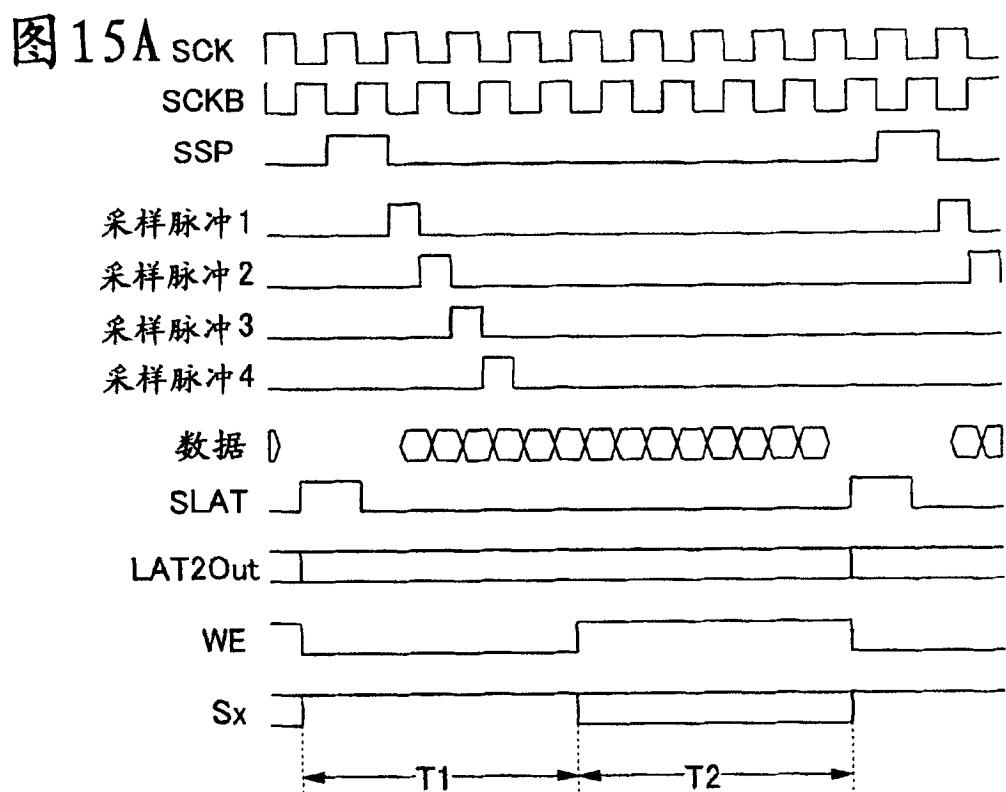

[0264] 首先，将利用图 15A 来说明信号线驱动电路 43 的工作过程。脉冲输出电路 44 被输入时钟信号（下文中称作 SCK）、时钟反相信号（下文中称作 SCKB）和启动脉冲（下文中称作 SSP）。根据这些信号的定时，将采样脉冲输出到第一锁存器 47。输入有数据的第一锁存器 47 依据采样脉冲被输入的定时从第一列到最后一列保持视频信号。当锁存脉冲被输入时，将保持在第一锁存器 47 中的视频信号一齐传送到第二锁存器 48。

[0265] 此处，说明各周期中的选择电路 46 的工作过程，其中设从选择信号线 52 传输的 WE 信号在 L 电平时的周期为 T1，WE 信号在 H 电平时的周期为 T2。周期 T1 和 T2 相当于水平扫描周期的半个周期，将周期 T1 称为第一子栅极选择周期而将周期 T2 称为第二子栅极选择周期。

[0266] 在周期 T1 中（第一子栅极选择周期），从选择信号线 52 传送的 WE 信号是 L 电平，晶体管 49 为导通状态而模拟开关 50 为非导通状态。于是，多个数据线 S1 到 Sn 经由被配置在各列中的晶体管 49 电连接到电源 53。即，多个信号线 Sx 具有与电源 53 相同的电位。这时，被选择的像素 10 所具有的开关用晶体管 11 被导通，电源 53 的电位经由该开关用晶

体管 11 传输到驱动用晶体管 12 的栅电极。于是,驱动用晶体管 12 成为关断状态,没有电流在发光元件 13 的两个电极之间流过而不发光。如此,不管输入到信号线 Sx 的视频信号的状态如何,电源 53 的电位都被传输到驱动用晶体管 12 的栅电极,该开关用晶体管 11 成为关断状态,强制性地使发光元件 13 不发光,这种工作过程被称为删除动作。此时,若沿着使像素的驱动晶体管关断的方向充分加大电源 53 的电位,则由于与写入数据时相比相反的偏压被施加到驱动晶体管的栅电极,所以提高晶体管的可靠性,从而这是优选的。

[0267] 在周期 T2 中(第二子栅极选择周期),从选择信号线 52 传输的 WE 信号是 H 电平,晶体管 49 为关断状态而模拟开关 50 为导通状态。于是,保持在第二锁存器 48 的一行视频信号同时传输到每个信号线 Sx。这时,像素 10 中的开关用晶体管 11 被导通,视频信号经由该开关用晶体管 11 传输到驱动用晶体管 12 的栅电极。于是,根据被输入的视频信号,驱动用晶体管 12 被导通或关断,发光元件 13 的第一和第二电极彼此具有不同的电位或相同的电位。更详细而言,当驱动用晶体管 12 被导通时,发光元件 13 的第一和第二电极彼此具有不同的电位,因此电流流入发光元件 13。于是,发光元件 13 点亮。注意,流入发光元件 13 的电流与流动在驱动用晶体管 12 的源漏间的电流相同。

[0268] 另一方面,当驱动用晶体管 12 被关闭时,发光元件 13 的第一和第二电极具有相同的电位,没有电流流入发光元件 13。即,发光元件 13 不发光。如此,驱动用晶体管 12 根据视频信号而成为导通状态或关断状态,发光元件 13 的第一和第二电极的电位彼此成为不同电位或相同电位,这种工作过程被称为写入动作。

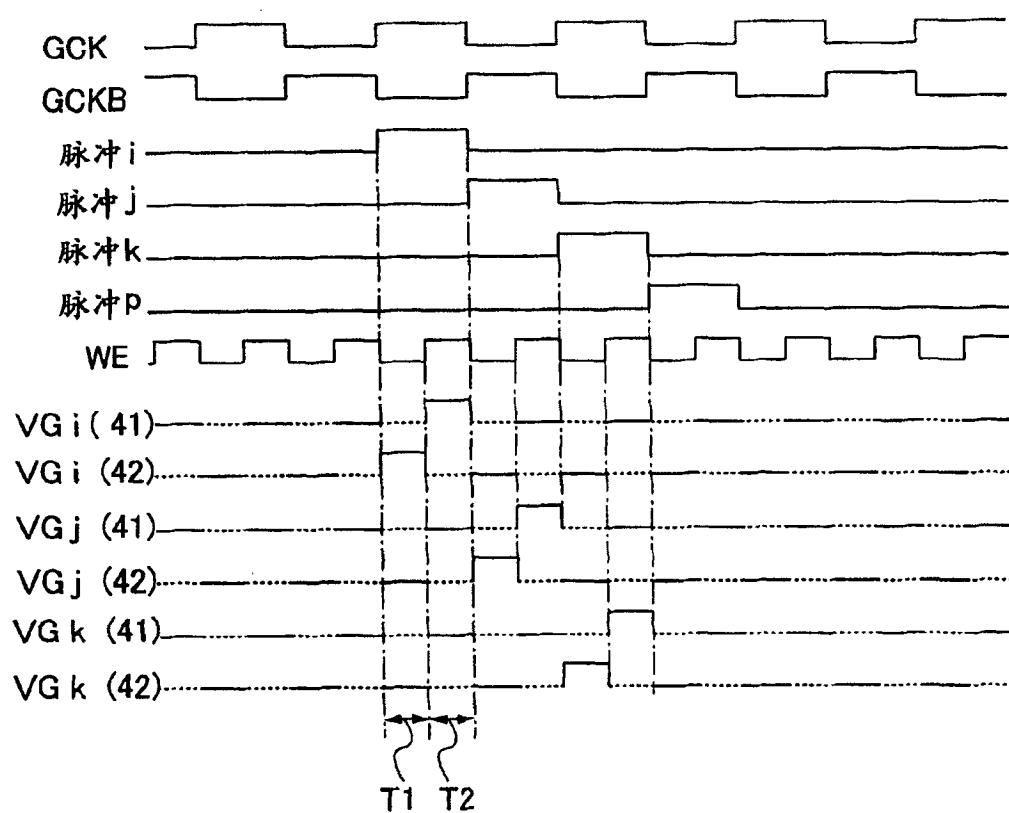

[0269] 接下来,说明第一扫描线驱动电路 41 和第二扫描线驱动电路 42 的工作过程。脉冲输出电路 54 被输入 G1CK、G1CKB 和 G1SP,根据这些信号的定时,将脉冲顺次输出到选择电路 55。脉冲输出电路 56 被输入 G2CK、G2CKB 和 G2SP。根据这些信号的定时,将脉冲顺次输出到选择电路 57。图 15B 示出了给选择电路 55 和 57 的第 i、j、k 和 p 行(i、j、k 和 p 是自然数,满足  $1 \leq i, j, k, p \leq n$ )的各行所提供的脉冲的电位。

[0270] 在此,与信号线驱动电路 43 的工作过程的说明同样地,说明各周期中的第一扫描线驱动电路 41 包含的选择电路 55 和第二扫描线驱动电路 42 包含的选择电路 57 的工作过程,其中设从选择信号线 52 传输的 WE 信号在 L 电平时的周期为 T1,WE 信号在 H 电平时的周期为 T2。注意,图 15B 的定时图中,将从第一扫描线驱动电路 41 传输了信号的栅极线 Gy(y 是自然数,满足  $1 \leq y \leq n$ )的电位表示为 VGy(41),而将从第二扫描线驱动电路 42 传输了信号的栅极线的电位表示为 VGy(42)。而且,VGy(41) 和 VGy(42) 可以通过相同的扫描线 Gy 来提供。

[0271] 在周期 T1 中(第一子栅极选择周期),从选择信号线 52 传送的 WE 信号是 L 电平。于是,第一扫描线驱动电路 41 中的选择电路 55 被输入 L 电平的 WE 信号,因此选择电路 55 进入浮置状态。另一方面,第二扫描线驱动电路 42 中的选择电路 57 被输入通过使 WE 信号反相获得的 H 电平信号,因此选择电路 57 进入工作状态。即,选择电路 57 传输 H 电平信号(行选择信号)到第 i 行的栅极线 Gi,因此栅极线 Gi 具有与 H 电平信号相同的电位。即,第 i 行的栅极线 Gi 被第二扫描线驱动电路 42 选择。结果,像素 10 中的开关用晶体管 11 成为导通状态。然后,信号线驱动电路 43 中的电源 53 的电位传输到驱动用晶体管 12 的栅电极,因此驱动用晶体管 12 成为关断状态,发光元件 13 的两个电极具有相同的电位。即,在此周期内,进行使发光元件 13 不发光的删除动作。

[0272] 在周期 T2 中（第二子栅极选择周期），从选择信号线 52 传送的 WE 信号是 H 电平。于是，第一扫描线驱动电路 41 中的选择电路 55 被输入 H 电平的 WE 信号，因此选择电路 55 处于工作状态。即，选择电路 55 传输 H 电平信号到第 i 行的栅极线 Gi，因此栅极线 Gi 具有与 H 电平信号相同的电位。即，第 i 行的栅极线 Gi 被第一扫描线驱动电路 41 选择。结果，像素 10 中的开关用晶体管 11 成为导通状态。然后，视频信号从信号线驱动电路 43 中的第二锁存器 48 传输到驱动用晶体管 12 的栅电极，因此驱动用晶体管 12 成为导通或关断状态，发光元件 13 的两个电极具有不同或相同的电位。即，在这个周期中，进行使发光元件 13 发光或不发光的写入动作。另一方面，第二扫描线驱动电路 42 中的选择电路 57 被输入 L 电平信号，因此它处于浮置状态。

[0273] 如此，栅极线 Gy 在周期 T1（第一子栅极选择周期）中被第二扫描线驱动电路 42 选择，而在周期 T2（第二子栅极选择周期）中被第一扫描线驱动电路 41 选择。即，第一扫描线驱动电路 41 和第二扫描线驱动电路 42 以互补的方式控制栅极线。然后，在第一子栅极选择周期和第二子栅极选择周期中的一个内进行删除动作，而在另一个内进行写入动作。

[0274] 注意，在第一扫描线驱动电路 41 选择第 i 行的栅极线 Gi 的周期内，第二扫描线驱动电路 42 处于不工作状态（选择电路 57 处于浮置状态），或传输行选择信号到除第 i 行外的其它行的栅极线。同样，在第二扫描线驱动电路 42 传输行选择信号到第 i 行的栅极线的周期内，第一扫描线驱动电路 41 处于浮置状态，或传输行选择信号到除第 i 行外的其它行的栅极线。

[0275] 执行上述动作的本发明，能够将发光元件 13 强制关断，因此，可以提高占空比。进而，尽管能够将发光元件 13 强制关断，也不需要设置用于释放电容元件 16 的电荷的 TFT。因此，就可以实现高开口率。若实现高开口率，就能够使发光元件的亮度随着发光面积的增加而减小。即，由于能够减小驱动电压故能够减小功耗。

[0276] 注意，本发明不限于上述将栅极选择周期分成两半的实施方式。栅极选择周期也可以分成三个或更多的周期。

[0277] （实施方式 12）

[0278] 本发明也可以应用到进行恒定电流驱动的显示器件。在本实施方式中，将说明使用监视用发光元件 66 检测随时间的变化程度，并根据其检测结果对视频信号或电源电位进行修正，由此来补偿发光元件随时间的变化的情况。

[0279] 在本实施方式中，设置第一和第二监视用发光元件。第一监视用发光元件由第一恒流源提供恒定电流，而第二监视用发光元件由第二恒流源提供恒定电流。通过改变从第一恒流源供给的电流值和从第二恒流源供给的电流值，使流到第一和第二监视用发光元件的总电流量不同。于是，在第一和第二监视用发光元件之间产生不同的随时间变化。

[0280] 第一和第二监视用发光元件连接到运算电路，在该运算电路中计算出第一监视用发光元件和第二监视用发光元件的电位差。将通过运算电路计算出的电压值提供给视频信号产生电路。在视频信号产生电路中基于从运算电路提供的电压值来修正提供给每个像素的视频信号。通过上述构造，就能够补偿发光元件随时间的变化。此外，优选在各监视用发光元件和运算电路之间设置用于防止缓冲放大器电路等的电位波动的电路。另外，在本实施方式中，作为具有恒定电流驱动的构造的像素，例如有使用电流镜电路的像素等。

[0281] （实施方式 13）

[0282] 本发明可以应用到无源矩阵型显示器件。无源矩阵型显示器件包括形成在衬底上的像素部分、设置在该像素部分外围的列信号线驱动电路、行信号线驱动电路、和用于控制驱动电路的控制器。像素部分包括被配置于列方向上的各列信号线、被配置于行方向上的行信号线、以及被配置成矩阵状的多个发光元件。可以在形成了该像素部分的衬底上设置监视电路 64。

[0283] 在本实施方式的显示器件中能够利用监视电路 64 根据温度的变化或随时间的变化，来修正输入到列信号线驱动电路的图像数据，或者由恒压源产生的电压，因此可以提供能够减少由温度的变化和随时间的变化这两者所引起的影响的发光器件。

[0284] (实施方式 14)

[0285] 作为配备有包括发光元件的像素部分的电子器具可列举出：电视机装置（有时只称之为电视或电视接收机）、数字照相机、数字摄像机、便携式电话装置（有时只称之为便携式电话机或手机）、PDA 等便携式信息终端、便携式游戏机、用于计算机的监视器、计算机、汽车用立体声系统等音响重放装置和家用游戏机等配备有记录介质的图像重放装置。关于它们的具体例子将参考图 16 说明。

[0286] 图 16A 中所示的便携式信息终端器件包括主体 9201、显示部分 9202 等。本发明的显示器件可应用于显示部分 9202。即，根据用监视用发光元件校正供应到发光元件的电源电位的本发明，可以提供便携式信息终端器件，其中由于环境温度的改变和随时间的改变导致的发光元件中电流值变化所造成的影响可被抑制。

[0287] 图 16B 中所示的数字摄像机包括显示部分 9701 和 9702 等。本发明的显示器件可应用于显示部分 9701。根据用监视用发光元件校正供应到发光元件的电源电位的本发明，可以提供数字摄像机，其中由于环境温度的改变和随时间的改变导致的发光元件中电流值变化所造成的影响可被抑制。

[0288] 图 16C 中所示的便携式电话机包括主体 9101、显示部分 9102 等。本发明的显示器件可应用于显示部分 9102。根据用监视用发光元件校正供应到发光元件的电源电位的本发明，可以提供便携式电话机，其中由于环境温度的改变和随时间的改变导致的发光元件中电流值变化所造成的影响可被抑制。

[0289] 图 16D 中所示的便携式电视机装置包括主体 9301、显示部分 9302 等。本发明的显示器件可应用于显示部分 9302。根据用监视用发光元件校正供应到发光元件的电源电位的本发明，可以提供便携式电视机装置，其中由于环境温度的改变和随时间的改变导致的发光元件中电流值变化所造成的影响可被抑制。这种电视机装置可广泛地适用于搭载在便携式电话等的便携式信息终端中的小型结构、能搬运的中型结构、或者大型结构（例如 40 英寸或更大）。

[0290] 图 16E 中所示的便携式计算机包括主体 9401、显示部分 9402 等。本发明的显示器件可应用于显示部分 9402。根据用监视用发光元件校正供应到发光元件的电源电位的本发明，可以提供便携式计算机，其中由于环境温度的改变和随时间的改变导致的发光元件中电流值变化所造成的影响可被抑制。

[0291] 图 16F 中所示的电视机装置包括主体 9501、显示部分 9502 等。本发明的显示器件可应用于显示部分 9502。根据用监视用发光元件校正供应到发光元件的电源电位的本发明，可以提供电视机装置，其中由于环境温度的改变和随时间的改变导致的发光元件中电

流值变化所造成的影响可被抑制。

图 1

图 2

图 3

图 4

图 5

图 6A

图 6B

图 7A

图 7B

图 8A

图 8B

图 9A

图 9B

图 10

图 11A

图 11B

图 11C

图 12

图 13

图 14

图 15B

图 16A

图 16B

图 16C

图 16D

图 16F

图 16E

图 17A

图 17B

图 17C

图 18A

图 18B

图 19A

图 19B

图 20A

图 20B

图 21

图 22A

图 22B

图 22C

图 22D

图 22E

图 23A

图 23B

图 24A

图 24B

图 25A

图 25B

图 26A

图 26B

图 27

图 28

图 29

图 30

图 31

图 32

图 33

|                |                                                                            |         |            |

|----------------|----------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示器件及其驱动方法                                                                 |         |            |

| 公开(公告)号        | <a href="#">CN1892767B</a>                                                 | 公开(公告)日 | 2011-08-10 |

| 申请号            | CN200610106206.8                                                           | 申请日     | 2006-07-04 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                               |         |            |

| 申请(专利权)人(译)    | 株式会社半导体能源研究所                                                               |         |            |

| 当前申请(专利权)人(译)  | 株式会社半导体能源研究所                                                               |         |            |

| [标]发明人         | 吉田泰则<br>木村肇<br>山崎舜平                                                        |         |            |

| 发明人            | 吉田泰则<br>木村肇<br>山崎舜平                                                        |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H05B33/08 H05B33/14                                      |         |            |

| CPC分类号         | G09G2300/0452 G09G2310/0251 G09G2320/029 G09G2330/10 G09G3/3233 G09G3/2022 |         |            |

| 代理人(译)         | 王永刚                                                                        |         |            |

| 优先权            | 2005194600 2005-07-04 JP                                                   |         |            |

| 其他公开文献         | CN1892767A                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                             |         |            |

### 摘要(译)

本发明的目的是提供一种显示器件及其驱动方法，在进行面积灰度级显示的EL显示器件中，实现图像质量改善且使图像质量稳定化。为了解决上述问题，在一个像素中设置分别具有发出几乎相同颜色的光的发光元件的多个子像素；以及具有与像素相同数量的子像素的多个监视用像素，其中，监视用像素的发光元件和像素的发光元件同时制作，并且，监视用像素的发光元件的电极在每个子像素中分别连接到不同的恒流源，而且，还设置差动放大电路以便根据监视用像素中的发光元件的电极的电位变化，使像素的发光元件的电极的电位对每个子像素进行变化。