## [12] 发明专利申请公开说明书

[21] 申请号 200410045244.8

[43] 公开日 2005年2月23日

[11] 公开号 CN 1584964A

[22] 申请日 2004.6.4

[74] 专利代理机构 北京市柳沈律师事务所

[21] 申请号 200410045244.8

代理人 王志森 黄小临

[71] 申请人 友达光电股份有限公司

地址 台湾省新竹市

[72] 发明人 叶信宏 曾戎骏

权利要求书3页 说明书5页 附图6页

[54] 发明名称 数据驱动电路及其有机发光二极管

显示器

## [57] 摘要

本发明有关于一种数据驱动电路，特别有关于一种设置多个模拟取样存储电路共享一组数字/模拟转换器，当由到对应的取样信号启动时，对应的模拟取样存储电路会导通以进行存储取样的操作，如此可避免使用数字锁存器当分辨率增加而造成横向布局面积增加时所造成的线路布局上的困难。

1. 一种数据驱动电路，包括：

多个移位缓存器，每一移位缓存器在一对应周期中依序输出一取样信号；

5 多条数据信号线，该多条数据信号线在一第一周期传输多组第一数字数据，在一第二周期时传输多组第二数字数据；

一数字/模拟转换器，接收该多组第一数字数据并转换成一第一模拟转换数据，及接收该等第二数字数据并转换成一第二模拟转换数据；

10 多个模拟取样存储电路，每一模拟取样存储电路在该第一周期时，由其中一对应的取样信号启动而导通，及一第一信号启动存储对应的该第一模拟转换数据；在该第二周期时，由一第二信号启动读出该第一模拟转换数据所对应的一第一模拟数据，并由该取样信号启动而导通及该第二信号启动存储该第二模拟转换数据；在一第三周期时，由该第一信号启动读出该第二模拟转换数据所对应的一第二模拟数据；以及

15 多个像素，每一像素分别接收其所对应的该第一模拟数据及对应的该第二模拟数据。

2. 如权利要求1所述的数据驱动电路，其中该每一模拟取样存储电路包括：

20 一电流源，连接该数字/模拟转换器与一恒定电压源之间，并由对应的该取样信号控制而导通；

一第一存储电容，设置在该恒定电压源与一第一节点之间；

一第二存储电容，设置在该恒定电压源与该第一节点之间；

一第一晶体管，具有一输入端连接该恒定电压源，一控制端连接该第一存储电容及该第二存储电容，及一输出端；

25 一第一开关，设置在该第一存储电容与该第一节点之间，在该第一周期由该第一信号启动而导通，在该第二周期由该第一信号禁止而关断；

一第二开关，设置在该第一存储电容与该第一晶体管控制端之间，在该第一周期由该第二信号禁止而关断，在该第二周期由该第二信号启动而导通；

30 一第三开关，设置在该第二存储电容与该第一节点之间，在该第一周期由该第二信号禁止而关断，在该第二周期由该第二信号启动而导通；及

一第四开关，设置在该第二存储电容与该第一晶体管控制端之间，在该第一周期由该第一信号启动而导通，在该第二周期由该第一信号禁止而关断。

5 3. 如权利要求 2 所述的数据驱动电路，该电流源包括一晶体管，该晶体管具有一输入端连接该恒定电压源，一控制端连接该第一节点，及一输出端连接该数字/模拟转换器上；

一第六开关，设置在该第一节点与该晶体管的输出端之间，并由对应的该取样信号控制导通；及

10 10 一第五开关，设置在该晶体管的输出端与数字/模拟转换器之间，并由该对应的该取样信号控制导通。

4. 如权利要求 3 所述的数据驱动电路，其中该第一到第六开关为一开关晶体管或一传输选通元件。

5. 一有机发光二极管显示器，包括：

多个像素，以阵列型式排列；

15 一扫描驱动电路，依序驱动该多个像素中的一行像素；

一种数据驱动电路，包括：

多个移位缓存器，每一移位缓存器在对应周期中依序输出一取样信号；

多条数据信号线，该多条数据信号线在一第一周期传输多组第一数字数据，在一第二周期时传输多组第二数字数据；

20 一数字/模拟转换器，接收该多组第一数字数据并转换成一第一模拟转换数据，及接收该等第二数字数据并转换成一第二模拟转换数据；以及

25 多个模拟取样存储电路，每一模拟取样存储电路在该第一周期时，由其中一对应的取样信号启动而导通，及一第一信号启动存储对应的该第一模拟转换数据；在该第二周期时，由一第二信号启动读出该第一模拟转换数据所对应的一第一模拟数据，并由该取样信号启动而导通及该第二信号启动存储该第二模拟转换数据；在一第三周期时，由该第一信号启动读出该第二模拟转换数据所对应的一第二模拟数据到对应像素中。

6. 如权利要求 5 所述的有机发光二极管显示器，其中每一模拟取样存储电路包括：

30 一电流源，连接该数字/模拟转换器与一恒定电压源之间，并由对应的该取样信号控制而导通；

一第一存储电容，设置在该恒定电压源与一第一节点之间；

一第二存储电容，设置在该恒定电压源与该第一节点之间；

一第一晶体管，具有一输入端连接该恒定电压源，一控制端连接该第一存储电容及该第二存储电容，及一输出端；

5 一第一开关，设置在该第一存储电容与该第一节点之间，在该第一周期由该第一信号启动而导通，在该第二周期由该第一信号禁止而关断；

一第二开关，设置在该第一存储电容与该第一晶体管控制端之间，在该第一周期由该第二信号禁止而关断，在该第二周期由该第二信号启动而导通；

10 一第三开关，设置在该第二存储电容与该第一节点之间，在该第一周期由该第二信号禁止而关断，在该第二周期由该第二信号启动而导通；及

一第四开关，设置在该第二存储电容与该第一晶体管控制端之间，在该第一周期由该第一信号启动而导通，在该第二周期由该第一信号禁止而关断。

15 7. 如权利要求 6 所述的有机发光二极管显示器，该电流源包括一晶体管，该晶体管具有一输入端连接该恒定电压源，一控制端连接该第一节点，及一输出端连接该数字/模拟转换器上；

一第六开关，设置在该第一节点与该晶体管的输出端之间，并由一对应的该取样信号控制导通；及

一第五开关，设置在该晶体管的输出端与数字/模拟转换器之间，并由该对应的该取样信号控制导通。

20 8. 如权利要求 7 所述的有机发光二极管显示器，其中该第一到第六开关为一开关晶体管或一传输选通元件。

## 数据驱动电路及其有机发光二极管显示器

## 5 技术领域

本发明有关于一种数据驱动电路，特别有关于一种通过共享数字/模拟转换电路，可避免使用数字锁存器当分辨率增加而造成横向布局面积增加时所造成的线路布局上的困难。

## 10 背景技术

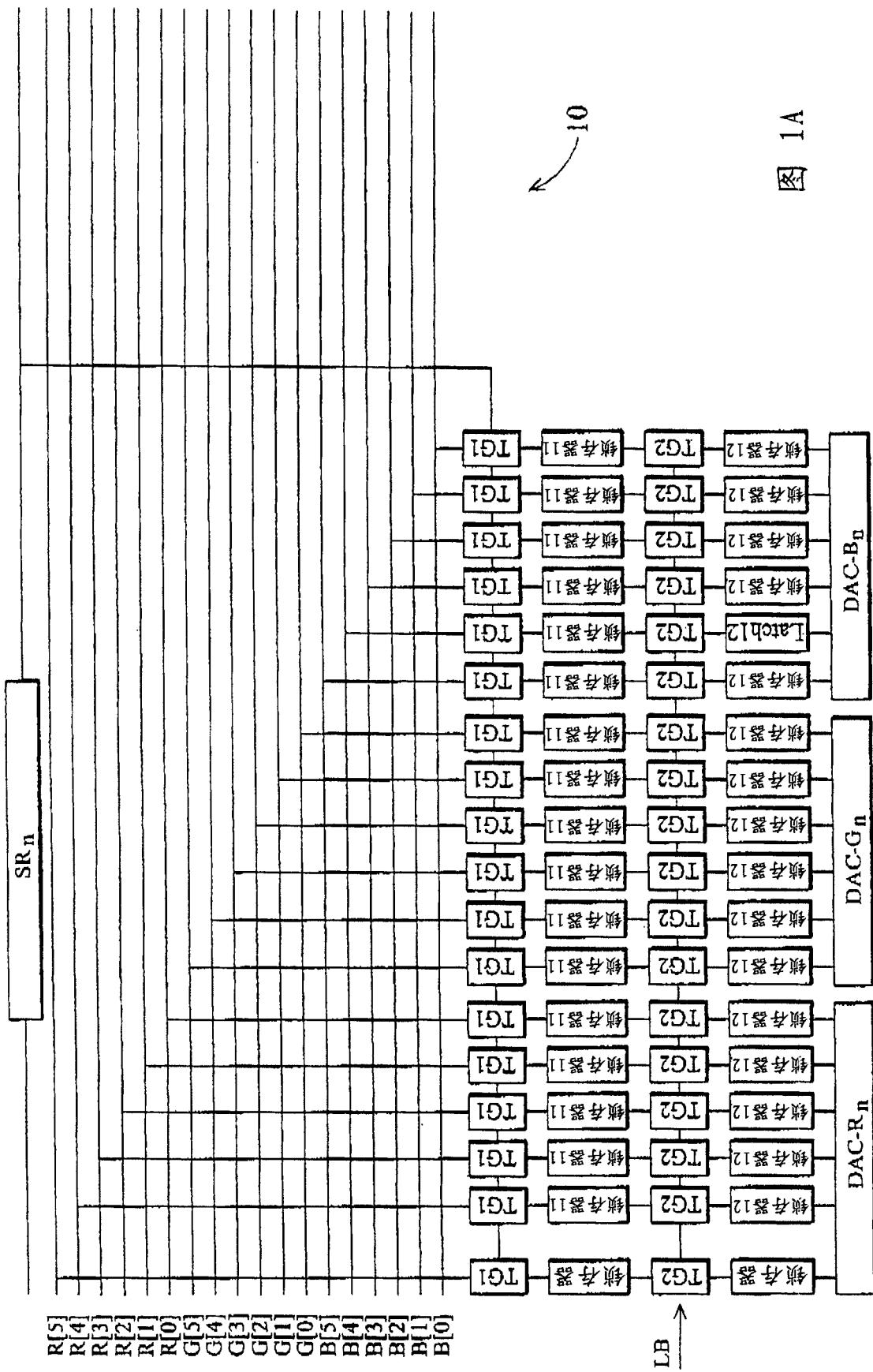

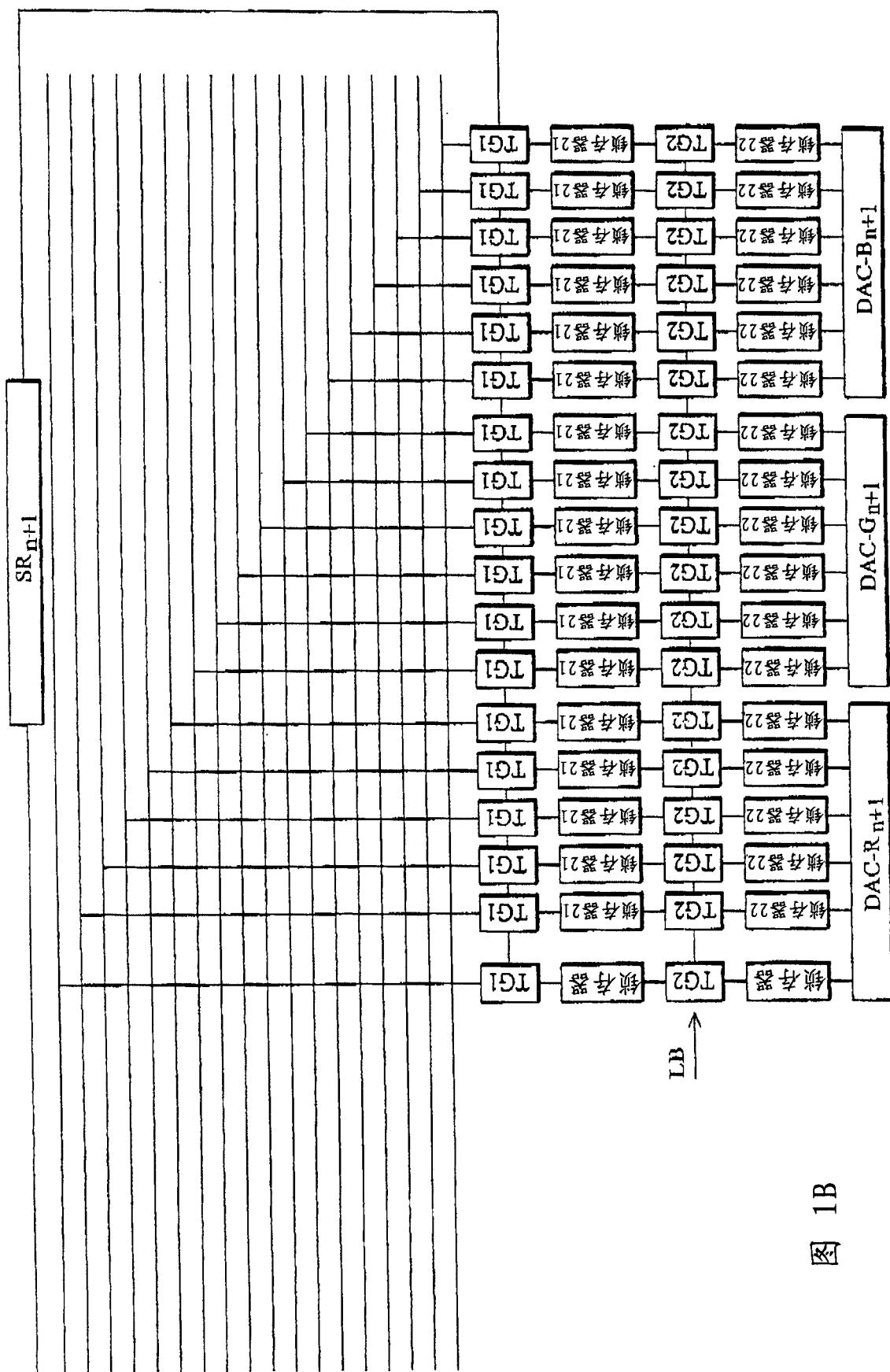

传统有源矩阵有机发光二极管(OLED)显示器的数字型数据驱动器，使用存储缓存器(数字锁存器)，在一信号线周期中作为线路缓冲器(linebuffer)用以存储数字图像信号。图1A及1B显示传统上操作在一次一条信号线模式下的一6位数字型数据驱动结构10。在该结构下，在一水平描扫周期中，依序的加载多组数字图像信号，首先先加载一组数字图像信号经信号线R[5]~B[0]由移位缓存器SR<sub>n</sub>的取样信号控制输出到对应的第一级锁存器11(Latch11)中，接着再加载下一组数字图像信号经信号线R[5]~B[0]由缓存器SR<sub>n+1</sub>的取样信号控制输出到对应的第一级锁存器21(Latch21)中。之后，通过(linebuffer)“LB”信号的控制，所有存在第一级锁存器11(Latch11)、锁存器21(Latch21)中的数字图像信号R[5]~B[0]会写入第二级锁存器12(Latch12)、锁存器22(Latch22)中，同时被放进数字/模拟转换器DAC-R<sub>n</sub>、DAC-G<sub>n</sub>、DAC-B<sub>n</sub>中。

由于分辨率增加，数据位数会跟着增加，所以很占布局面积的存储缓存器，以及数字/模拟转换器的数目也会随着增加。然而在传统排列方式下，数字型驱动器在横向上的布局是比较受限的。因此，当分辨率增加造成存储缓存器及数字/模拟转换器的数目增加时，将会增加线路布局上的困难度。

## 发明内容

有鉴于此，本发明的目的在于提供一种数据驱动电路，通过设置多个模拟取样存储电路代替传统数字锁存器，且共享一数字/模拟转换器，可避免由于分辨率增加时，因为所需要的横向布局面积增加，所造成的线路布局上的

困难度。

为实现上述优点，及根据本发明的目的，本发明提供一种数据驱动电路，包括有多个移位缓存器，每一移位缓存器在一对周期中依序输出一取样信号；多条数据信号线，该多条数据信号线在一第一周期传输多组第一数字数据，5 在一第二周期时传输多组第二数字数据；一数字/模拟转换器，接收该多组第一数字数据并转换成对应的第一模拟转换数据，及接收该等第二数字数据并转换成对应的第二模拟转换数据；多个模拟取样存储电路，每一模拟取样存储电路在该第一周期时，由其中一对对应的取样信号启动而导通及一第一信号启动存储该第一模拟转换数据；在该第二周期时，由一第二信号启动读出该10 第一模拟转换数据的对应第一模拟数据，及接收该取样信号启动而导通及该第二信号启动存储该第二模拟转换数据；及在一第三周期时，由该第一信号启动读出该第二模拟转换数据的对应第二模拟数据；以及多个像素，每一像素分别接收其所对应的第一模拟数据以及对应的第二模拟数据。

本发明还提出一有机发光二极管 (OLED) 显示器，包括：多个像素，以阵列15 型式排列；一扫描驱动电路，依序驱动该多个像素中的一行像素；一数据驱动电路，包括：多个移位缓存器，每一移位缓存器在一对周期中依序输出一取样信号；多条数据信号线，该多条数据信号线在一第一周期传输多组第一数字数据，在第二周期时传输多组第二数字数据；一数字/模拟转换器，接收该多组第一数字数据并转换成一第一模拟转换数据，及接收该等第二数字数据并转换成一第二模拟转换数据；以及多个模拟取样存储电路，每一模拟取样存储20 电路在该第一周期时，由其中一对对应的取样信号启动而导通及一第一信号启动存储对应的第一模拟转换数据；在该第二周期时，由一第二信号启动读出该第一模拟转换数据的对应第一模拟数据，并由该取样信号启动而导通及该第二信号启动存储该第二模拟转换数据；及在一第三周期时，由该第一信号启动25 读出该第二模拟转换数据的对应第二模拟数据到对应像素中。

#### 附图说明

为了让本发明的上述和其它目的、特征、和优点能更明显易懂，下文特举一较佳实施例，并配合所附图示，作详细说明如下：

30 图 1A 及 1B 显示传统数字型数据驱动结构；

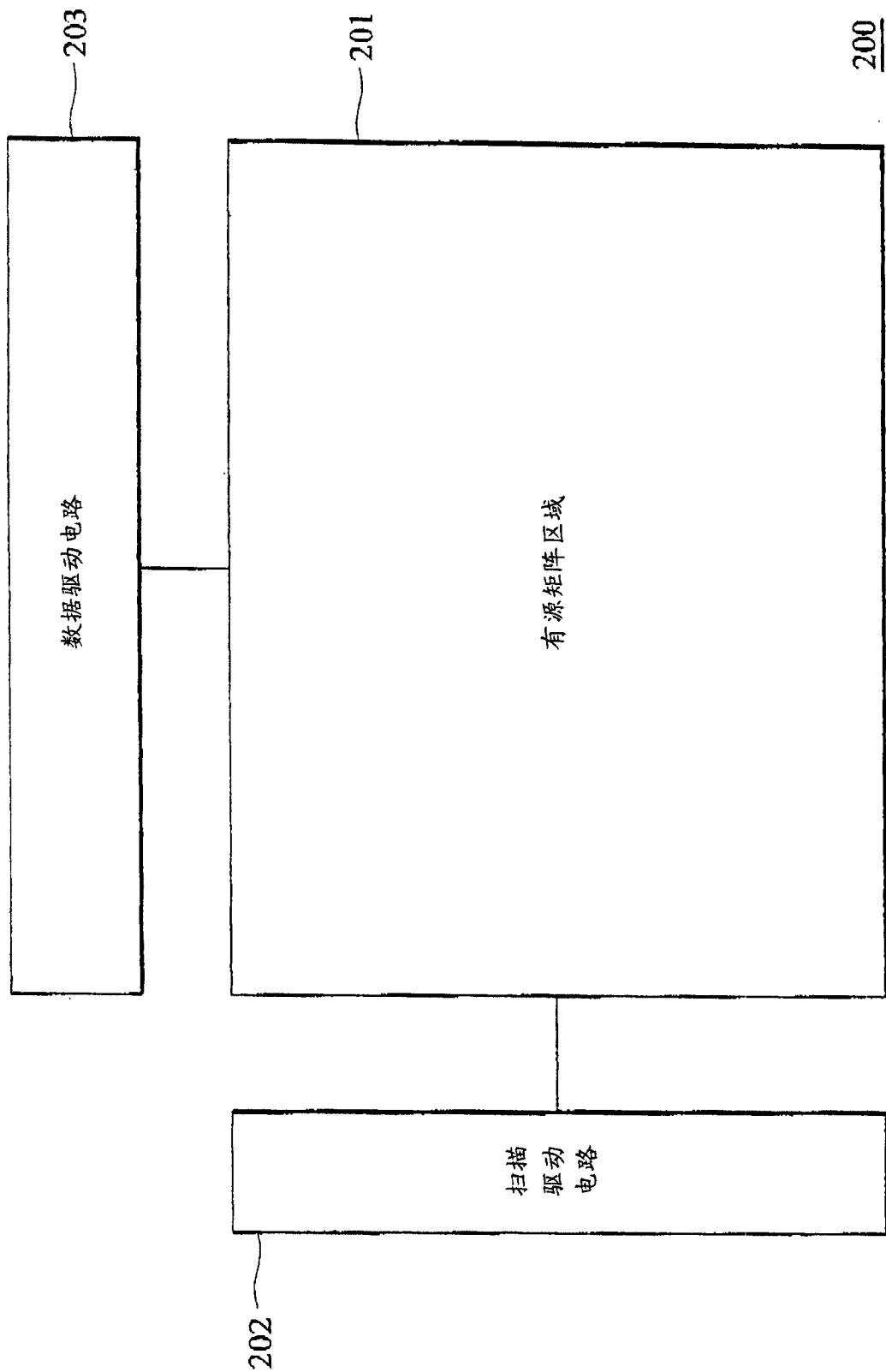

图 2 中所示为适用本发明数据驱动电路的一有机发光二极管 (OLED) 显示器;

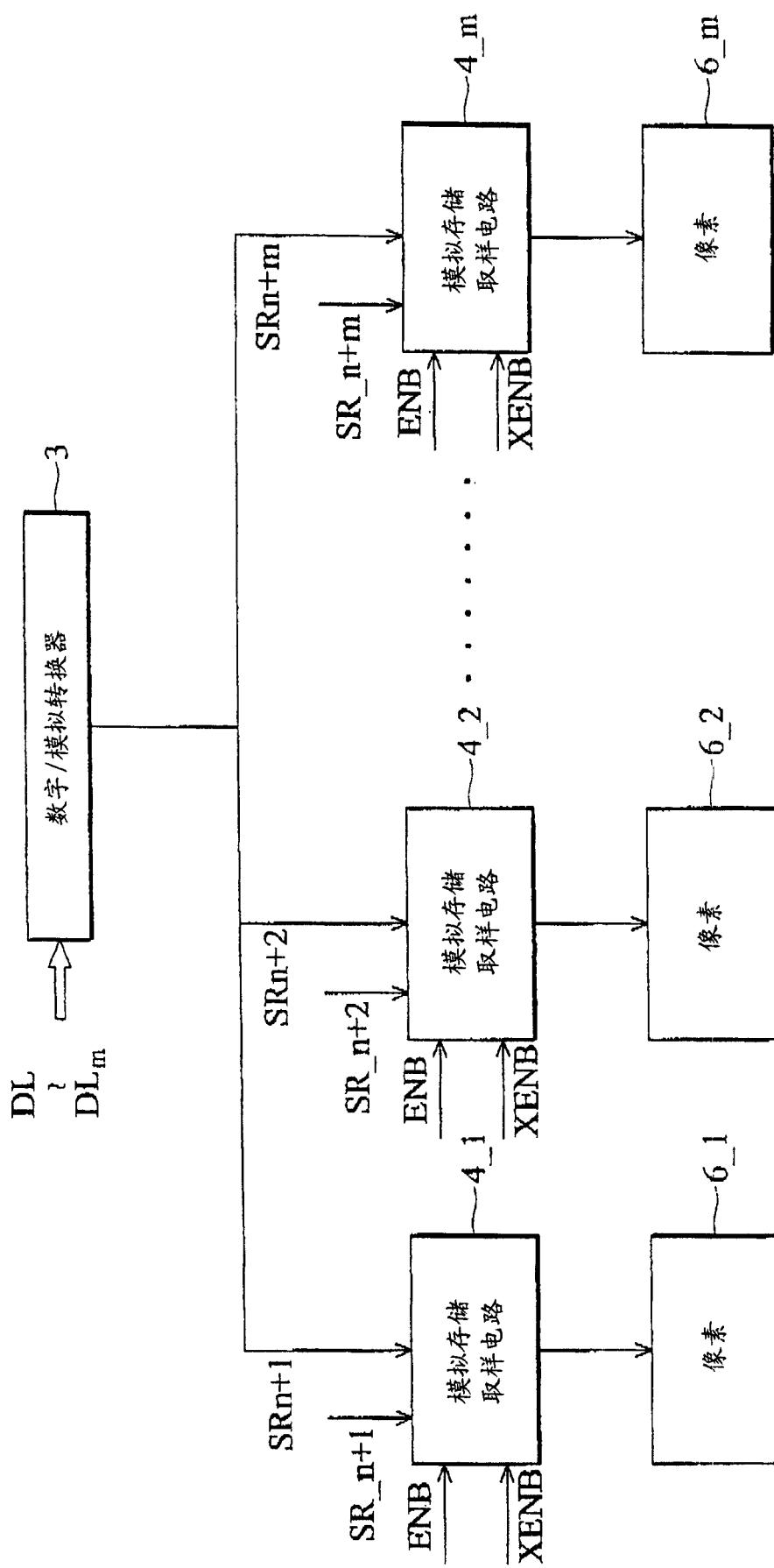

图 3 中所示为数据驱动电路的方块示意图;

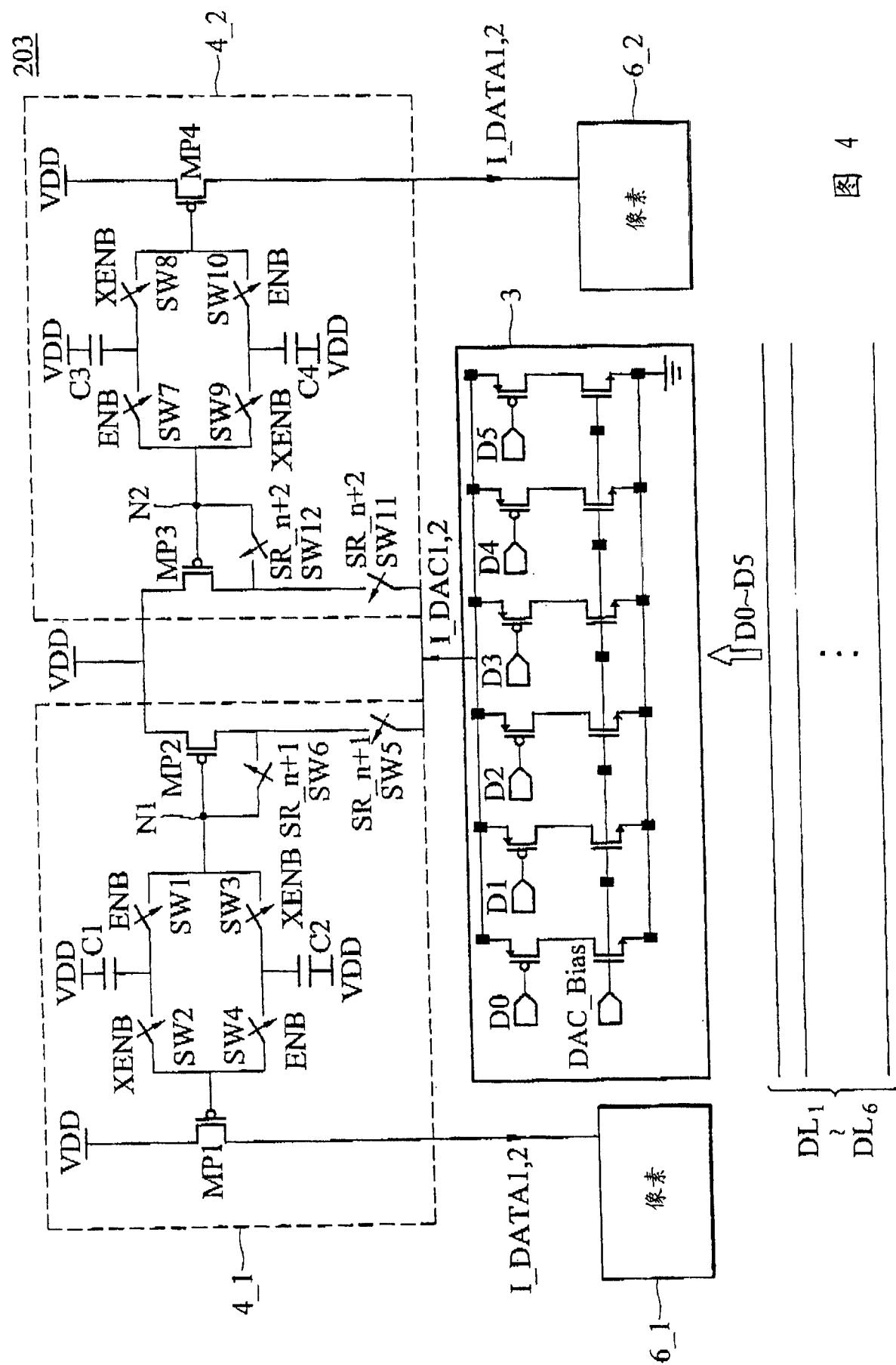

图 4 为数据驱动电路的详细电路图;

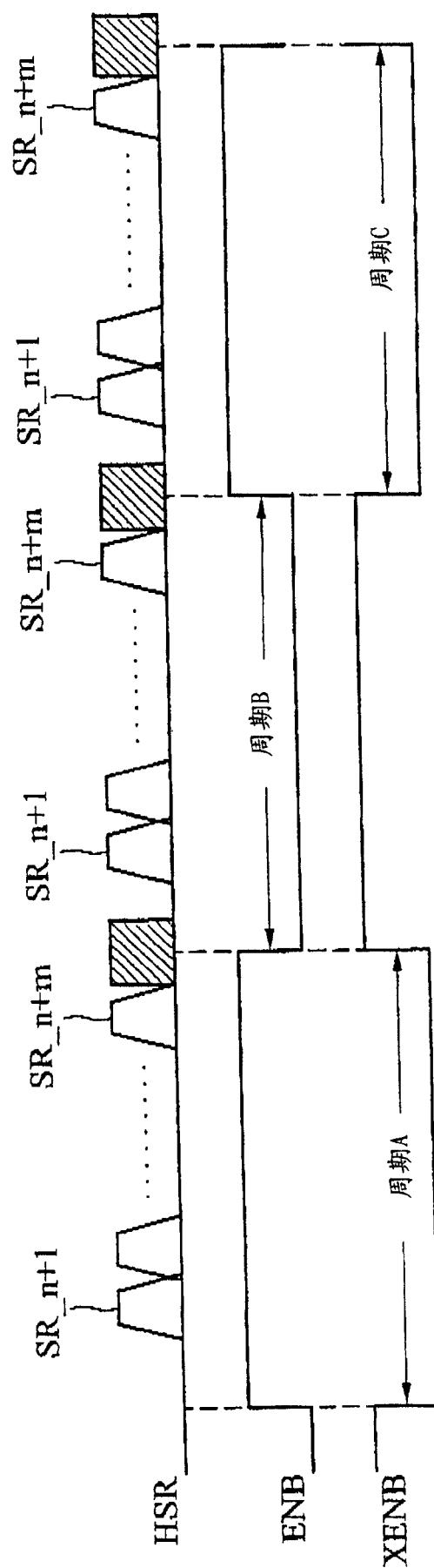

5 图 5 为数据驱动电路的操作时序图;

相关符号说明:

数字型数据驱动结构~10; 移位缓存器~SR<sub>n</sub>; 数字图像信号~R[5] ~ B[0]; 第一级锁存器 11~Latch11; 第二级锁存器 12~Latch12; 数字/模拟转换器~DAC-R<sub>n</sub>、DAC-G<sub>n</sub>、DAC-B<sub>n</sub>; 移位缓存器~SR<sub>n+1</sub>; 第一级锁存器 21~Latch21; 第二级锁存器 22~Latch22; 数字/模拟转换器~DAC-R<sub>n+1</sub>、DAC-G<sub>n+1</sub>、DAC-B<sub>n+1</sub>; 有机发光二极管 (OLED) 显示器~200; 有源矩阵区域~201; 扫描驱动电路~202; 数据驱动电路~203; 多条数据驱动信号线~DL1~DL<sub>m</sub>; 数字/模拟转换器~3; 多个模拟取样存储电路~4\_1~4\_~m; 像素~6\_1~6\_~m; 开关~SW1~SW12; 晶体管 MP1~MP3; 电压源~Vdd; 存储电容~C1、C2; 节点~N1; 第一信号~ENB; 第二信号~XENB; 模拟转换数据~I\_DAC1、I\_DAC2; 取样信号~SR\_n+1~SR\_n+~m; 模拟数据~I\_DATA2、I\_DATA2

### 具体实施方式

如图 2 中所示, 为适用本发明的数据驱动电路的一有机发光二极管 (OLED) 显示器 200。如图 2 中所示, 有机发光二极管 (OLED) 显示器 200 至少具有一由多个像素所排成的有源矩阵区域 201、一扫描驱动电路 202 以及一数据驱动电路 203。扫描驱动电路 202, 用以依序地驱动有源矩阵区域 201 中的一行像素。数据驱动电路 203, 用以输出数据信号到对应像素。

图 3 所示为图 2 中数据驱动电路 203 的方块示意图, 数据驱动电路 203 包括多条数据驱动信号线 DL1~DL<sub>m</sub>、一数字/模拟转换器 3、多个模拟取样存储电路 4\_1~4\_~m、及多个像素 6\_1~6\_~m。

多条数据信号线 DL1~DL<sub>m</sub>, 用以传输数字数据; 数字/模拟转换器 3, 连接该多条数据信号线 DL1~DL<sub>m</sub>, 以将数字数据并转换成对应的模拟转换数据, 例如对应的电流数据; 多个模拟取样存储电路 4\_1~4\_~m, 连接到数字/模拟转换器 3, 可由对应的一取样信号 SR\_n+1~SR\_n+~m 启动而导通, 并在一周期中, 由一第一信号 ENB 或一第二信号 XENB 的控制而存储接收到的模拟转换数据,

及一第二信号 XENB 或一第一信号 ENB 的控制读出前一周期的模拟转换数据的对应模拟数据；多个像素 6\_1~6\_m，连接到对应的模拟取样存储取样电路 4\_1~4\_m 以接收读出的模拟数据。

图 4 中举一实施例，该数据驱动电路 203 中的多条数据信号线 DL1~DL6 5 传递一 6 位的数据 D0~D65 到一 6 位的数字/模拟转换器 3 中，数据驱动电路 203 包括二模拟取样存储取样电路 4\_1 及 4\_2。

模拟取样存储电路 4\_1 包括有一用以当作电流源的晶体管 MP2，设置在一恒定电压源 VDD 以及数字/模拟转换器 3 之间。在晶体管 MP2 的栅极及漏极间设有一开关 SW6(第六开关)，及在漏极及数字/模拟转换器 3 间设有开关 SW5(第五开关)，开关 SW5 及开关 SW6 会由取样信号 SR\_n+1 的启动而导通。10

二存储电容 C1 以及 C2，并联的设置在电压源 VDD 以及一第一节点 N1 间，在存储电容 C1 以及第一节点 N1 间设有一开关 SW1(第一开关)，在存储电容 C2 以及第一节点 N1 间设有一开关 SW3(第三开关)，开关 SW1 会由一第一信号 ENB 15 的控制呈导通或关断的状态；开关 SW3 则由一第二信号 XENB 的控制而呈导通或关断的状态。一当作电流源的晶体管 MP1，设置在电压源 VDD 以及一像素 6\_1 之间，晶体管 MP1 的栅极经由开关 SW2(第二开关)以及开关 SW4(第四开关)分别连接到存储电容 C1 以及存储电容 C2，其中开关 SW2 会由第二信号 XENB 的控制而呈导通或关断的状态；开关 SW4 则由一第一信号 ENB 的控制而呈导通或关断的状态。

20 模拟取样存储电路 4\_2 具有用以当作电流源的晶体管 MP3、MP4，二存储电容 C3 及 C4，以及开关 SW7~SW10 以及 SW11、SW12。其电路构造与模拟取样存储电路 4\_1 相同，在此不再赘述。

实际操作时，由于模拟取样存储电路 4\_1 与模拟取样存储电路 4\_2 的操作相同，以模拟取样存储电路 4\_1 为例，请一并参阅图 4、5，其中图 5 为数据驱动电路 203 的操作时序图。首先，在周期 A(第一周期)时，多个信号线 DL1~DL6 会传递一组数字数据 D0~D5(第一数字数据)到数字模拟/转换器 3 中以转换成对应的模拟转换数据 I\_DAC1(第一模拟转换数据)，例如为一电流数据。同时，例如一取样信号 SR\_n+1 控制开关 SW5 及 SW6 导通，第一信号 ENB 启动而导通开关 SW1 及 SW4，模拟转换数据 I\_DAC1 即经开关 SW5、SW6 及 25 SW1 存储到存储电容 C1 中。

30 接着进入周期 B(第二周期)，第一信号 ENB 禁止而关断开关 SW1 及 SW4，

第二信号 XENB 启动而导通开关 SW3 及开关 SW2, 因此存储电容 C1 中的模拟转换数据 I\_DAC1 即流到晶体管 MP1 的栅极, 以控制晶体管 MP1 传输对应的模拟数据 I\_DATA1 到像素 6\_1 中。同时, 另一组数字数据 D0~D5 (第二数字数据) 到数字模拟 / 转换器 3 中转换成对应的模拟转换数据 I\_DAC2 (第二模拟转换数据), 5 当取样信号 SR\_n+1 控制开关 SW5 及 SW6 导通, 模拟转换数据 I\_DAC2 (第二模拟转换数据) 即经开关 SW5、SW6 及 SW3 存储到存储电容 C2 中。

进入周期 C (第三周期) 时, 第一信号 ENB 启动而导通 SW1、SW4, 使存储电容 C2 中的模拟转换数据连接到晶体管 MP1 的栅极, 以控制晶体管 MP1 传输对应的模拟数据 I\_DATA2 到像素 6\_1 中。

10 模拟取样存储电路 4\_2 与模拟存储取样电路 4\_1 的操作原理相同, 在此不再赘述, 不同的是其由到同一对应周期中的 SR\_n+2 取样信号启动时才会导通开关 SW11 及 SW12。

综上所述, 虽然本发明已以一较佳实施例公开如上, 然其并非用以限定本发明, 任何本领域技术人员, 在不脱离本发明的精神和范围的情况下, 可 15 进行各种更动与修改, 因此本发明的保护范围当视所提出的权利要求限定的范围为准。

图 1A

图 1B

图 2

图 3

图 4

图 5

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 数据驱动电路及其有机发光二极管显示器                             |         |            |

| 公开(公告)号        | <a href="#">CN1584964A</a>                     | 公开(公告)日 | 2005-02-23 |

| 申请号            | CN200410045244.8                               | 申请日     | 2004-06-04 |

| [标]申请(专利权)人(译) | 友达光电股份有限公司                                     |         |            |

| 申请(专利权)人(译)    | 友达光电股份有限公司                                     |         |            |

| 当前申请(专利权)人(译)  | 友达光电股份有限公司                                     |         |            |

| [标]发明人         | 叶信宏<br>曾戎骏                                     |         |            |

| 发明人            | 叶信宏<br>曾戎骏                                     |         |            |

| IPC分类号         | G09G3/3275 G09G3/32                            |         |            |

| 代理人(译)         | 王志森                                            |         |            |

| 其他公开文献         | CN100342418C                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a> |         |            |

### 摘要(译)

本发明有关于一种数据驱动电路，特别有关于一种设置多个模拟取样存储电路共享一组数字/模拟转换器，当由到对应的取样信号启动时，对应的模拟取样存储电路会导通以进行存储取样的操作，如此可避免使用数字锁存器当分辨率增加而造成横向布局面积增加时所造成的线路布局上的困难。