## [12] 发明专利申请公开说明书

[21] 申请号 02105240.9

[43] 公开日 2002 年 8 月 28 日

[11] 公开号 CN 1366344A

[22] 申请日 2002.1.18 [21] 申请号 02105240.9

[30] 优先权

[32] 2001.1.18 [33] JP [31] 10868/01

[32] 2001.12.7 [33] JP [31] 374905/01

[71] 申请人 夏普公司

地址 日本大阪市

[72] 发明人 冈本成继

[74] 专利代理机构 中国专利代理(香港)有限公司

代理人 郑立柱 梁永

权利要求书 3 页 说明书 17 页 附图页数 16 页

[54] 发明名称 存储器一体型显示元件

[57] 摘要

一种存储器一体型显示元件，在显示元件的各像素中，存储器电路由 2 个互补型的反相器连接成环状而构成，根据选择期间经选择电路供给的数据电位 存储是否点亮有机发光二极管。另一反相器的输出端直接连接于上述有机发光二极管，该反相器的两个 TFT 驱动该有机发光二极管。由此，即使产生制造偏差等，也能以相同的亮度电平点亮/熄灭有机发光二极管。结果即使因制造偏差 等在构成像素的元件的特性中产生偏差，也能以相同亮度电平点亮光学调制元件。

ISSN 1008-4274

# 权利要求书

1. 一种存储器一体型显示元件 (1·1h~1i), 光学调制元件 (12) 和存储表示对该光学调制元件的输入的 2 值数据的存储器元件(11)设置在像素(4·4a~4i)

5 上, 其特征在于:

上述存储器元件 (11) 由至少 2 个反相器(11a·11b)连接成环状而构成,

上述各个反相器(11a、11b)中输出为上述存储器元件 (11) 的输出端的输出反相器 (11a、11b) 的输出直接连接于上述光学调制元件 (12) 的一端。

2. 根据权利要求 1 所述的存储器一体型显示元件 (1·1h~1i), 上述光学调

10 制元件 (12), 发光强度根据电流量改变的电流驱动型光学调制元件 (12)。

3. 根据权利要求 1 所述的存储器一体型显示元件 (1·1h~1i), 上述光学调

制元件 (12) 是有机发光二极管存储器一体型显示元件 (1·1h~1i)。

4. 根据权利要求 1、2 或 3 所述的存储器一体型显示元件 (1·1h~1i), 具

有上述存储器元件 (11) 具有向光学调制元件 (12) 施加电压期间, 在电压施

15 加结束后释放存储在该光学调制元件 (12) 上的电荷的电荷释放装置 (p1、n2、

p3、n4)。

5. 根据权利要求 1、2、3 或 4 所述的存储器一体型显示元件 (1·1h~1i),

上述输出反相器(11a、11b)是互补型反相器(11a、11b)的存储器一体型显示元件

(1·1h~1i)。

20 6. 根据权利要求 5 所述的存储器一体型显示元件 (1·1h~1i), 上述互补型

反相器(11a、11b)包括连接于第一电源线 (Lh、Lr) 的 p 型晶体管 (p1、p3) 和

连接于第二电源线 (Lg、Ll) 的 n 型晶体管 (n2、n4), 上述光学调制元件 (12)

的阳极连接于上述输出反相器(11a、11b)的输出端, 阴极连接于上述第二电源线

(Lg、Ll) 的存储器一体型显示元件 (1·1h~1i)。

25 7. 根据权利要求 5 所述的存储器一体型显示元件 (1·1h~1i), 上述互补型

反相器(11a、11b)包括连接于第一电源线 (Lh、Lr) 的 p 型晶体管 (p1、p3) 和

连接于第二电源线 (Lg、Ll) 的 n 型晶体管 (n2、n4), 上述光学调制元件 (12)

的阳极连接于上述输出反相器(11a、11b)的输出端, 阴极连接于上述第二电源线

(Lg、Ll), 并且

30 上述 n 型晶体管 (n2、n4) 的断开电阻值相对 p 型晶体管 (p1、p3) 的接

通电阻值的比率设定成 K 时，上述的光学调制元件（12）的接通电阻值的 p 型晶体管（p1、p3）的断开电阻值的比率设定为约  $(K+1)^{1/2}/K$  的存储器一体型显示元件（1.1h~1i）。

8. 根据权利要求 5 所述的存储器一体型显示元件（1.1h~1i），上述互补型反相器(11a、11b)包括连接于第一电源线（Lh、Lr）的 p 型晶体管（p1、p3）和连接于第二电源线（Lg、Ll）的 n 型晶体管（n2、n4），上述光学调制元件（12）的阳极连接于上述输出反相器(11a、11b)的输出端，阴极连接于上述第二电源线（Lg、Ll），并且

设上述 n 型晶体管（n2、n4）的断开电阻值相对 p 型晶体管（p1、p3）的接通电阻值的比率为 K、上述光学调制元件（12）的点亮亮度的偏差量为基准值的±x%以内时，

上述 p 型晶体管（p1、p3）的接通电阻值相对上述光学调制元件（12）的接通电阻值的平均值的比率设定为从  $(K+1)^{1/2} \cdot (1-x/100)/K$  到  $(K+1)^{1/2} \cdot (1+x/100)/K$  的范围内的存储器一体型显示元件（1.1h~1i）。

- 15 9. 根据权利要求 5 所述的存储器一体型显示元件（1.1h~1i），上述互补型反相器(11a、11b)包括连接于第一电源线（Lh、Lr）的 p 型晶体管（p1、p3）和连接于第二电源线（Lg、Ll）的 n 型晶体管（n2、n4），上述光学调制元件（12）的阴极连接于上述输出反相器(11a、11b)的输出端，阳极连接于上述第一电源线（Lh、Lr）的存储器一体型显示元件（1.1h~1i）。

- 20 10. 根据权利要求 5 所述的存储器一体型显示元件（1.1h~1i），上述互补型反相器(11a、11b)包括连接于第一电源线（Lh、Lr）的 p 型晶体管（p1、p3）和连接于第二电源线（Lg、Ll）的 n 型晶体管（n2、n4），上述光学调制元件（12）的阴极连接于上述输出反相器(11a、11b)的输出端，阳极连接于上述第一电源线（Lg、Ll），并且

25 上述 p 型晶体管（p1、p3）的断开电阻值相对上述 n 型晶体管（n2、n4）的接通电阻值的比率为 K 时，

上述 n 型晶体管（n2、n4）的接通电阻值相对上述光学调制元件（12）的接通电阻值的比率设定为约  $(K+1)^{1/2}/K$  的存储器一体型显示元件（1.1h~1i）。

- 30 11. 根据权利要求 5 所述的存储器一体型显示元件（1.1h~1i），上述互补型反相器(11a、11b)包括连接于第一电源线（Lh、Lr）的 p 型晶体管（p1、p3）

和连接于第二电源线 (Lg、Ll) 的 n 型晶体管 (n2、n4)，上述光学调制元件 (12) 的阴极连接于上述输出反相器(11a、11b)的输出端，阳极连接于上述第一电源线 (Lh、Lr)，并且

上述 p 型晶体管 (p1、p3) 的断开电阻值相对上述 n 型晶体管 (n2、n4)

- 5 的接通电阻值的比率为 K、上述光学调制元件 (12) 的点亮亮度的偏差量为基准值的±x%以内时，

n 型晶体管 (n2、n4) 的接通电阻值相对上述光学调制元件 (12) 的接通电阻值的平均值的比率设定为从  $(K+1)^{1/2} \cdot (1-x/100)/K$  到  $(K+1)^{1/2} \cdot (1+x/100)/K$  的范围内。

- 10 12. 根据权利要求 1、2 或 3 所述的存储器一体型显示元件 (1·1h~1i)，由多个包括上述光学调制元件 (12) 和存储器元件 (11) 的副像素 (41·42) 构成 1 个像素单位。

13. 根据权利要求 1、2 或 3 所述的存储器一体型显示元件 (1·1h~1i)，共用上述存储器元件 (11) 的电源电极之一和上述光学调制元件 (12) 的阳极或 15 阴极。

14. 根据权利要求 1、2 或 3 所述的存储器一体型显示元件 (1·1h~1i)，上述存储器元件 (11) 的第一电源电极和第二电源电极，以及上述光学调制元件 (12) 的阳极和阴极分开形成的存储器一体型显示元件 (1·1h~1i)。

15. 根据权利要求 1、2 或 3 所述的存储器一体型显示元件 (1i)，具有多 20 个数据信号线 (2) 和与上述各数据信号线 (2) 大致正交的多个选择信号线 (3)，

对数据信号线 (2) 和选择信号线 (3) 的每一组合设置上述存储器元件 (11)，与自身对应的选择信号线 (3) 指示选择时，存储与自身对应的数据信号线 (2) 所示的 2 值数据，并且，

- 经上述数据信号线 (2) 或选择信号线 (3) 之一的基准线 (2、3) 相邻的 25 存储器元件 (11) 之间以及光学调制元件 (12) 之间对于该基准线 (2、3) 线对称地布置，该存储器元件 (11) 之间或光学调制元件 (12) 之间共用电源线的存储器一体型显示元件 (1·1h~1i)。

# 说 明 书

## 存储器一体型显示元件

### 5 技术领域

本发明涉及在像素内配置存储器元件的存储器一体型显示元件。

### 背景技术

平板型显示装置中，作为光学调制元件，使用 OLED（有机发光二极管）等自发光元件和液晶元件等，在各像素中配置寻址用的 TFT（薄膜晶体管）栅10 的有源矩阵方式的显示装置得到广泛使用。

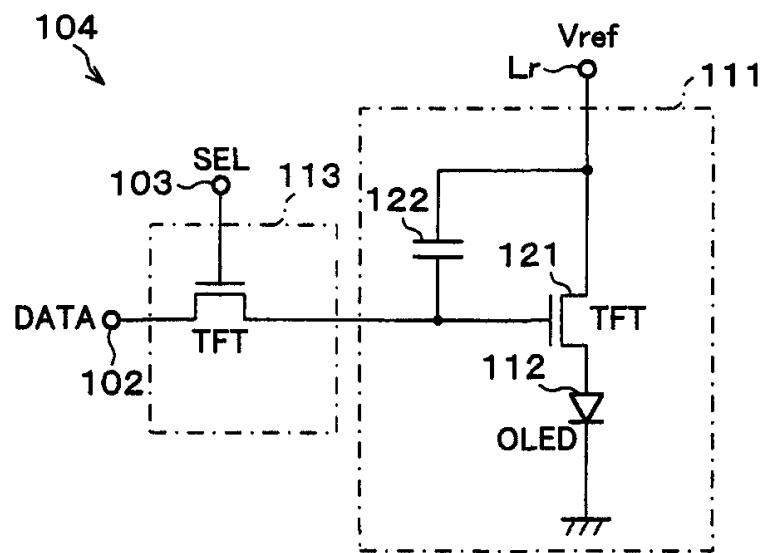

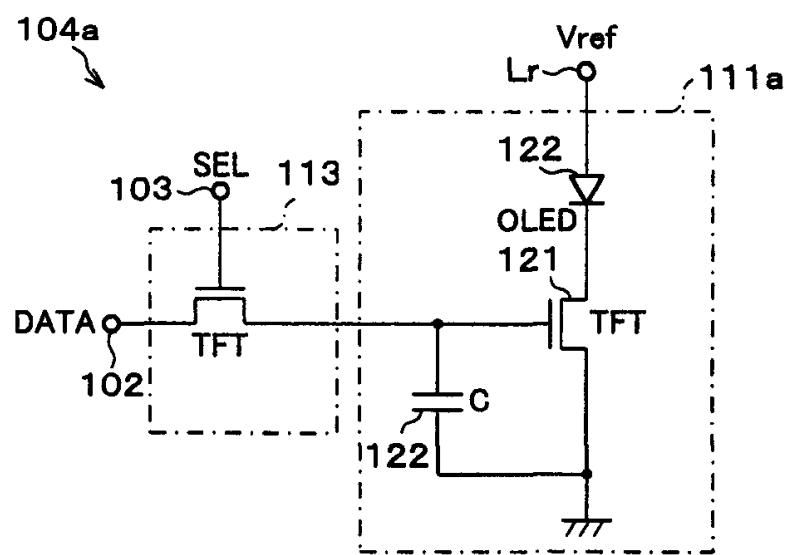

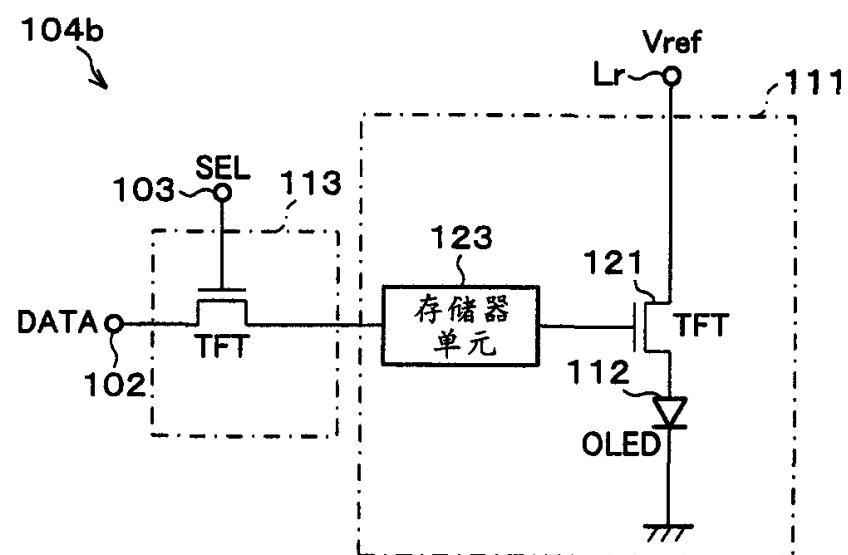

这里，有源矩阵方式的显示装置中，设置多个数据线和与各数据线正交的多个选择线，数据线和选择线的各交叉点上配置像素。使用作为光学调制元件的 OLED 的情况为例，则如图 18 所示，像素 104 中，选择模块 113 是仅在选择导线 103 在输出选择电平的选择信号 SEL 期间（选择期间）导通，连接数据线15 102 和驱动 OLED112 的驱动模块 111。

另一方面，驱动模块 111 中，施加基准电位 Vref 的电源线 Lr 和 OLED112 之间设置 TFT121。该 TFT121 的栅极上连接作为存储器元件的电容器 122，选择期间的数据信号 DATA 由电容器 122 保持，在非选择期间还向 TFT121 的栅极施加。如图 19 所示的像素 104a 所示，TFT121 和电源线 Lr 之间设置20 OLED112。

但是，这些像素 104（104a）中，将数据信号 DATA 存储为模拟量，因此，如图 20 所示，选择期间中施加的数据信号 DATA 的信号电平在非选择期间因电路内的泄漏电流等而慢慢降低。

因此，周期地设置选择期间的同时，需要例如通过设定电容器 122 的电容25 值等将电容器 122 保持的电位的时间变化率调整到该周期的电位降低量不影响显示的程度。电容器 122 需要的电容量由显示灰度数决定，但由于像素 104（104a）内可形成的电容值有限，可显示的灰度数或选择期间受到限制。

因此，特开平 10-161564（公开日：1998 年 6 月 19 日）中提出一种显示装置，在使用电压驱动型的 EL 元件作为光学调制元件的结构中，替代设置电容器30 122，而用掺杂了杂质离子的氮化硅膜形成 TFT121 的栅绝缘膜，使 TFT121 具

有 EEPROM 功能。另外，特许第 2775040 号公报（登记日：1998 年 5 月 1 日）中，公开一种结构，将电压驱动型的液晶用作光学调制元件，用强介电电容器保持数据信号 DATA。这些结构中，与如图 18 和 19 所示的结构不同，由于可抑制电位电平的降低，数据信号 DATA 可长时间保持。

5 作为与上述模拟量保持数据信号 DATA 的结构不同的结构，在例如特开平 8-194205 号公报（公开日：1996 年 7 月 30 日）、特开平 11-119698 号公报（公开日：1999 年 4 月 30 日）中，公开的结构如图 21 所示的像素 104b 所示，替代电容器 122 的设置的存储器元件 123 保持光学调制元件的点亮/未点亮的 2 值，由面积调制来进行灰度显示。该结构中，由于保持 2 值，与保持模拟量的

10 情况相比，数据信号 DATA 可长时间保持。

### 发明内容

本发明的目的是实现存储器一体型显示元件，即使因制造偏差等而在构成像素的元件的特性中产生偏差，也能按相同的亮度电平点亮光学调制元件。

为达到上述目的，本发明的存储器一体型显示元件中光学调制元件和存储

15 表示对该光学调制元件的输入的 2 值数据的存储器元件设置在像素上，上述存

储器元件由至少 2 个反相器连接成环状而构成，上述各个反相器中输出为上述

存储器元件的输出端的输出反相器的输出直接连接于上述光学调制元件的一

端。

根据上述结构，由于存储器元件的输出反相器驱动光学调制元件，与存储

20 器元件和光学调制元件经驱动用开关元件连接的已有技术相比，对光学调制元

件的驱动不造成障碍，可将开关元件数目仅仅减少驱动用开关元件部分。

由于不插入驱动用开关元件部分，即使产生制造偏差也不会随着驱动用开

关元件的特性变化而使光学调制元件的亮度电平变化，能够以相同亮度电平点

亮光学调制元件。

25 上述已有技术的结构中，形成很多像素时，因制造偏差等在驱动光学调制

元件的驱动用开关元件（TFT121）的阈值特性中产生偏差时，光学调制元件的

亮度产生偏差，画面内，应为相同电平的像素的亮度确彼此不同，担心发生明

显的色斑的问题。

尤其，作为电流驱动型的光学调制元件的 LED（发光二极管）中，由于具

30 有根据施加电压的指数函数的发光特性，上述阈值的特性产生偏差时，向 LED

流入的电流变化大，从而与电压驱动型的液晶元件等相比，产生明显的亮度偏差。

与此相反，本发明中，成为存储器元件的输出端的输出反相器的输出直接连接于上述光学调制元件的一端，因此，即使制造偏差产生了，光学调制元件

5 的亮度也不会随着驱动用开关元件的特性变化而使电平变化，能够以相同亮度电平点亮光学调制元件。

本发明的存储器一体型显示元件中，上述输出反相器是互补型反相器，例如 CMOS（互补 MOS）反相器。

该结构中，存储器元件例如存储熄灭/点亮等的 2 值之一时，构成上述互补

10 型反相器的开关元件（例如，p 型晶体管和 n 型晶体管的组合等）中之一导通。由此，在某显示状态中，即使在光学调制元件中存储电荷，该剩余电荷经导通的开关元件快速释放，光学调制元件快速向下面的显示状态移动。因此，显示错误产生或光学调制元件的烧坏、恶化可被抑制。

本发明的存储器一体型显示元件结构中还具有作为上述输出反相器的互补型的反相器，上述互补型的反相器包括连接于第一电源线的 p 型晶体管和连接于第二电源线的 n 型晶体管，上述光学调制元件的阳极连接于上述输出反相器的输出端，阴极连接于上述第二电源线，并且上述 n 型晶体管的断开电阻值相对 p 型晶体管的接通电阻值的比率设定为 K、上述光学调制元件的点亮亮度的偏差量为基准值的  $\pm x\%$  以内时，上述 p 型晶体管的接通电阻值相对上述光学

20 调制元件的接通电阻值的平均值的比率设定为从  $(K+1)^{1/2} \cdot (1-x/100)/K$  到  $(K+1)^{1/2} \cdot (1+x/100)/K$  的范围内。

上述连接中，各电阻值如上设定时，p 型晶体管和光学调制元件为导通状态，n 型晶体管为截断状态时的输出反相器和光学调制元件的消耗功率大致最小。另一方面，光学调制元件截断状态与导通状态相比，电阻值变得非常大。

25 由于 p 型晶体管为截断状态，n 型晶体管为导通状态，向光学调制元件施加的电压大致为 0，与导通状态时相比，输出反相器和光学调制元件的消耗功率小。因此，如上所述，通过设定各电阻值，存储器一体型显示元件的消耗功率降低。

本发明的存储器一体型显示元件在上述输出反相器为互补型的反相器的结构中，上述互补型反相器包括连接于第一电源线的 p 型晶体管和连接于第二

30 电源线的 n 型晶体管，上述光学调制元件的阴极连接于上述输出反相器的输出

端，阳极连接于上述第二电源线，并且上述 p 型晶体管的断开电阻值相对上述 n 型晶体管的接通电阻值的比率为 K、上述光学调制元件的点亮亮度的偏差量为基准值的±x%以内时，n 型晶体管的接通电阻值相对上述光学调制元件的接通电阻值的平均值的比率设定为从  $(K+1)^{1/2} \cdot (1-x/100)/K$  到  $(K+1)^{1/2} \cdot (1+x/100)/K$  的范围内。

上述连接中，各电阻值如上设定时，n 型晶体管和光学调制元件为导通状态，p 型晶体管为截断状态时的输出反相器和光学调制元件的消耗功率大致最小。另一方面，与阴极和第二电源线连接时一样，光学调制元件截断状态时消耗功率非常小。因此，如上所述，通过设定各电阻值，存储器一体型显示元件的消耗功率降低。

本发明的其他目的、特征和优点通过下面所示的记载可变得非常明了。本发明的优点通过下面参考附图的说明可更清楚。

#### 附图说明

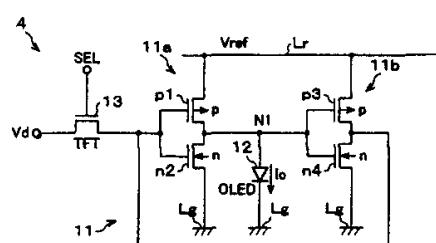

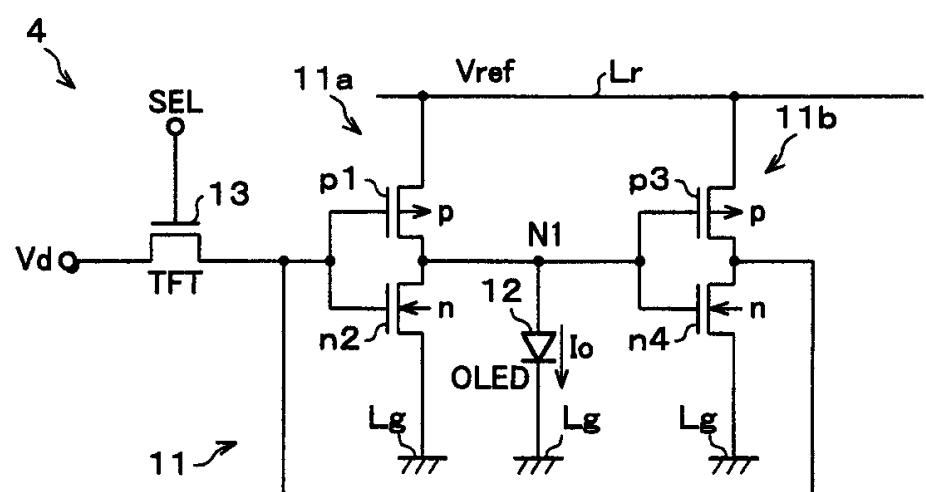

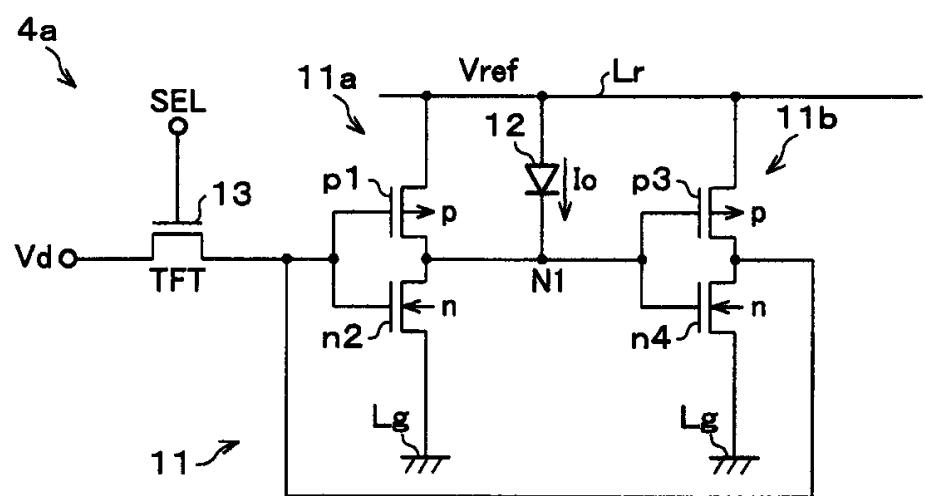

图 1 是表示本发明的一个实施例，表示像素的部件结构的电路图；

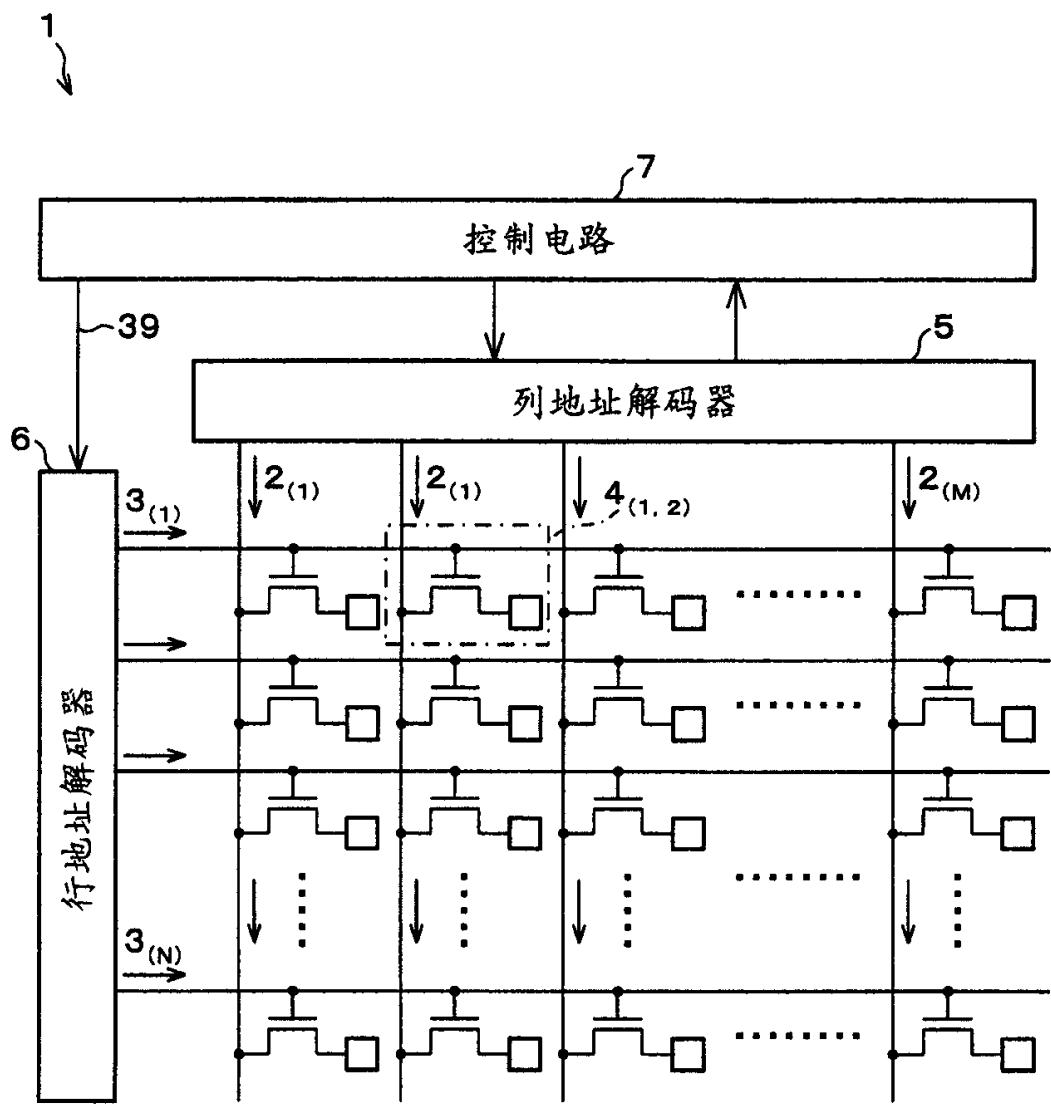

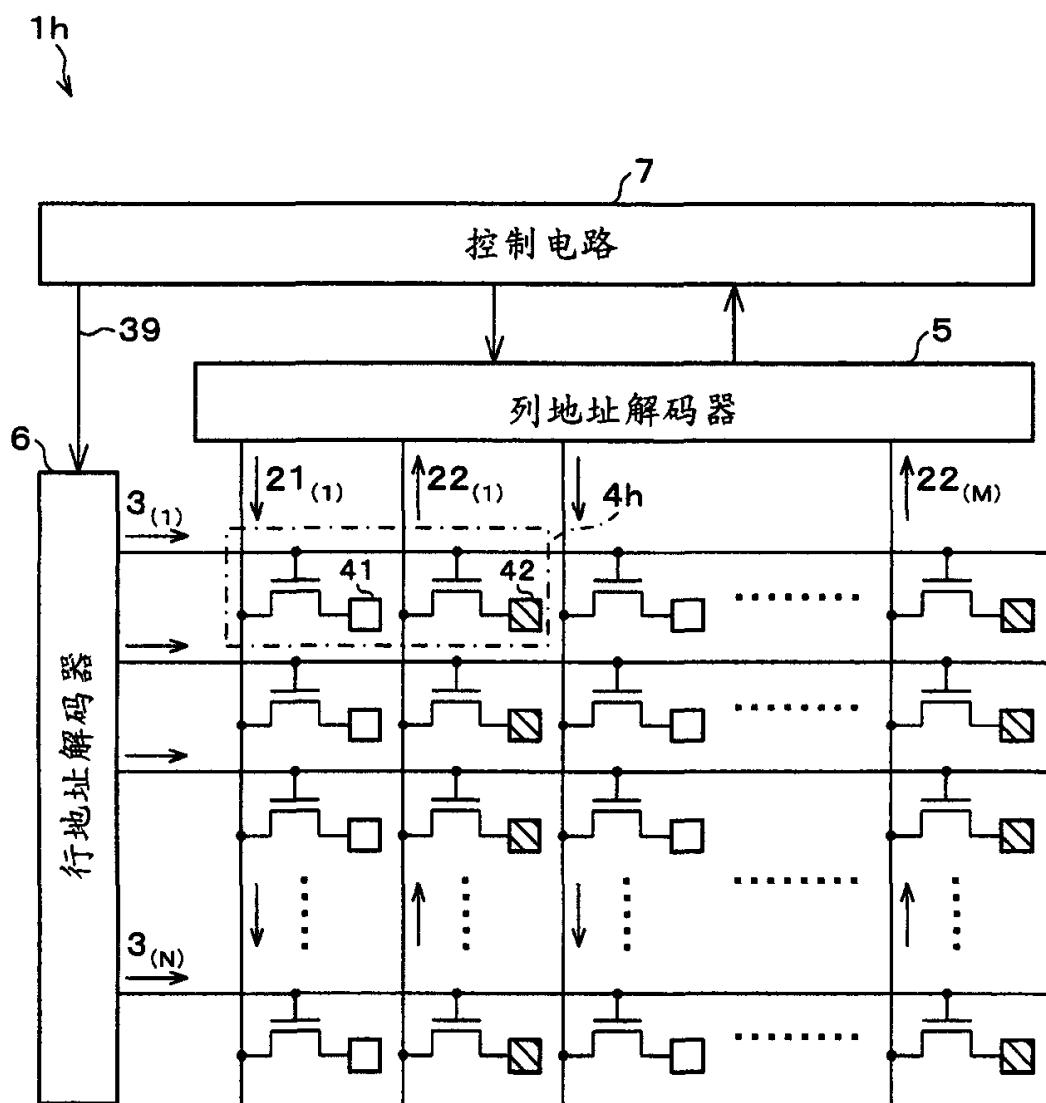

图 2 是包含上述像素的显示元件的部件结构的框图；

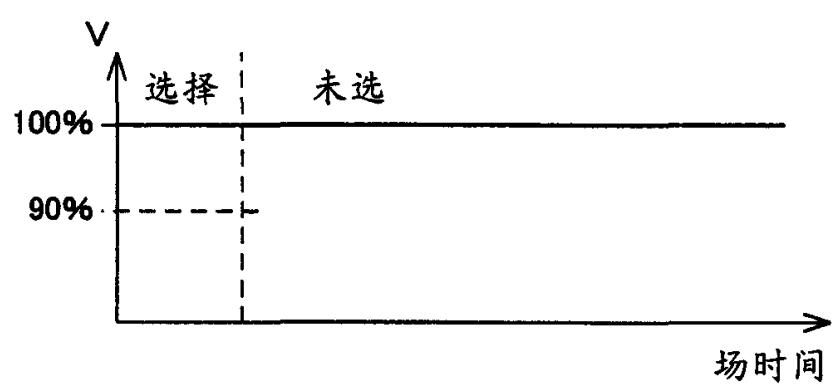

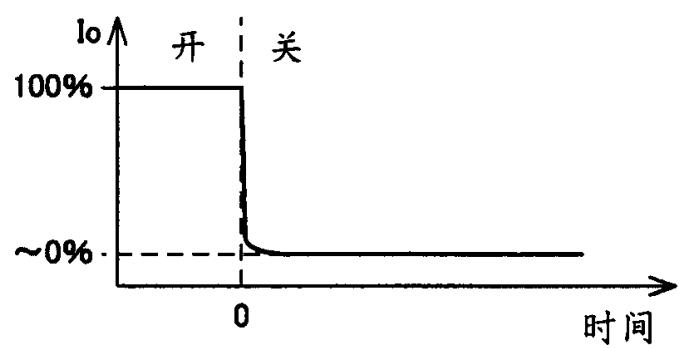

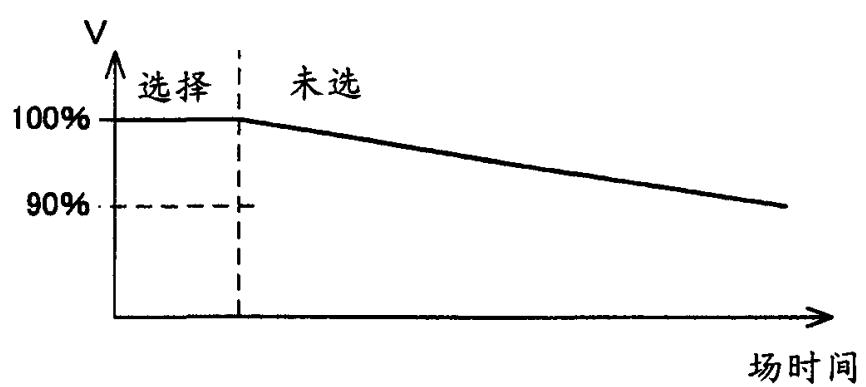

图 3 是表示上述像素中存储器元件保持的电位随时间变化的曲线；

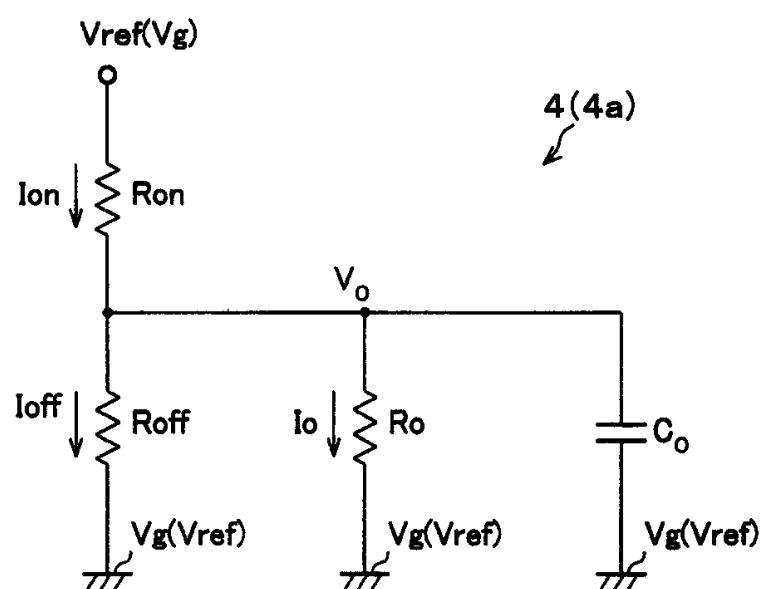

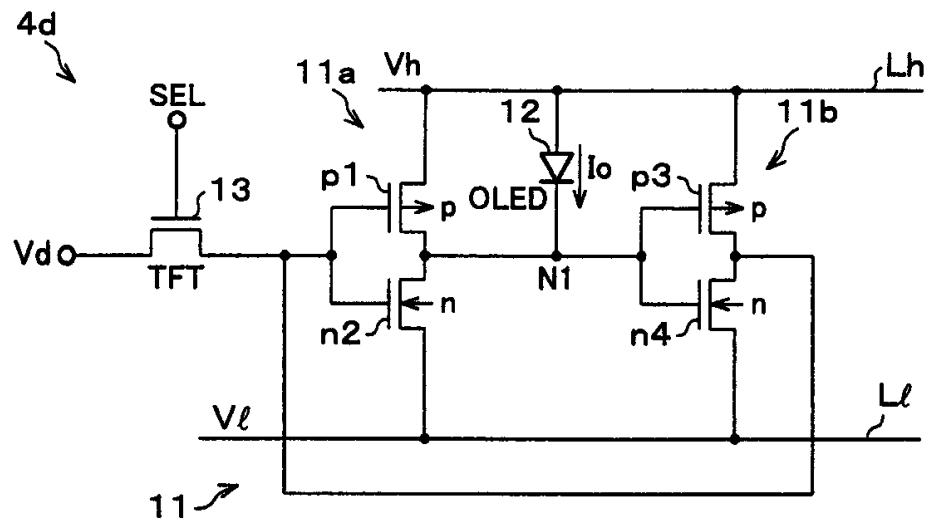

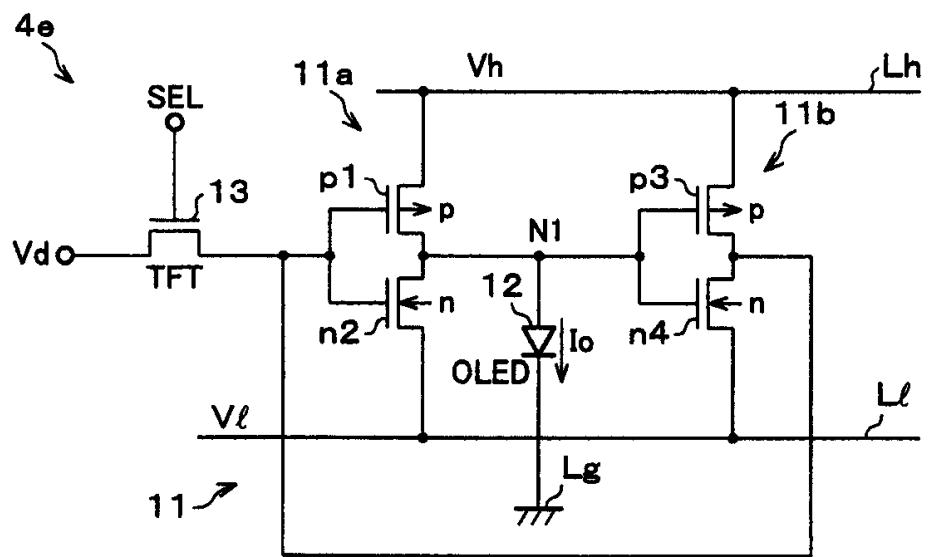

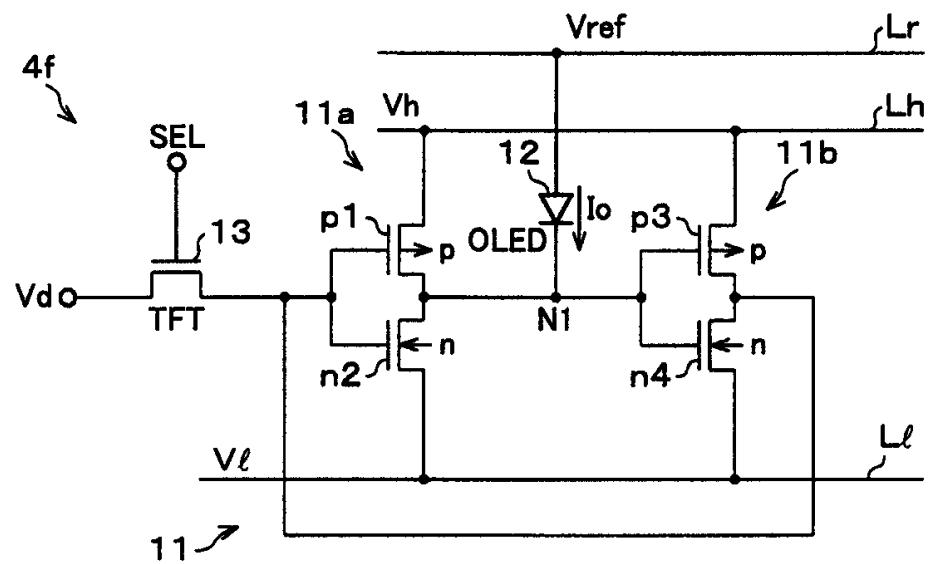

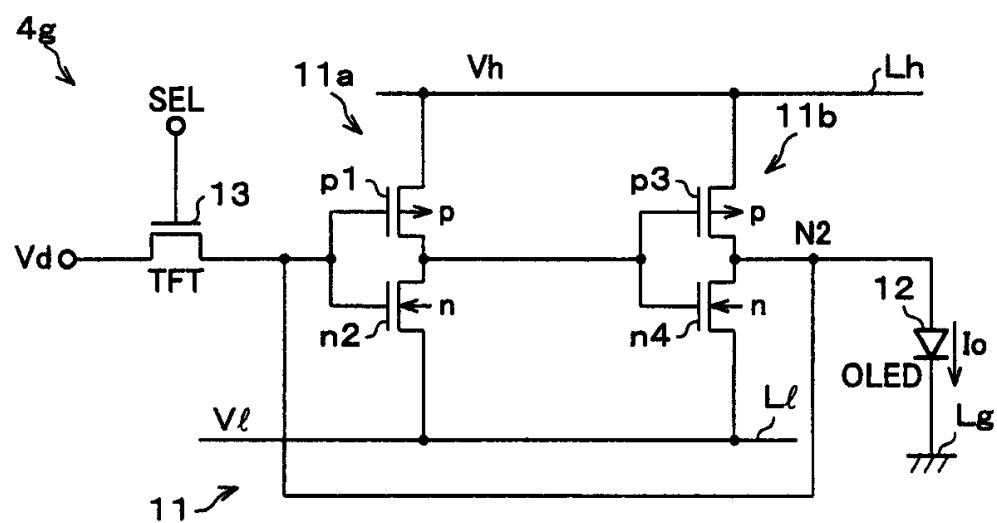

图 4 是表示上述像素的等效电路的电路图；

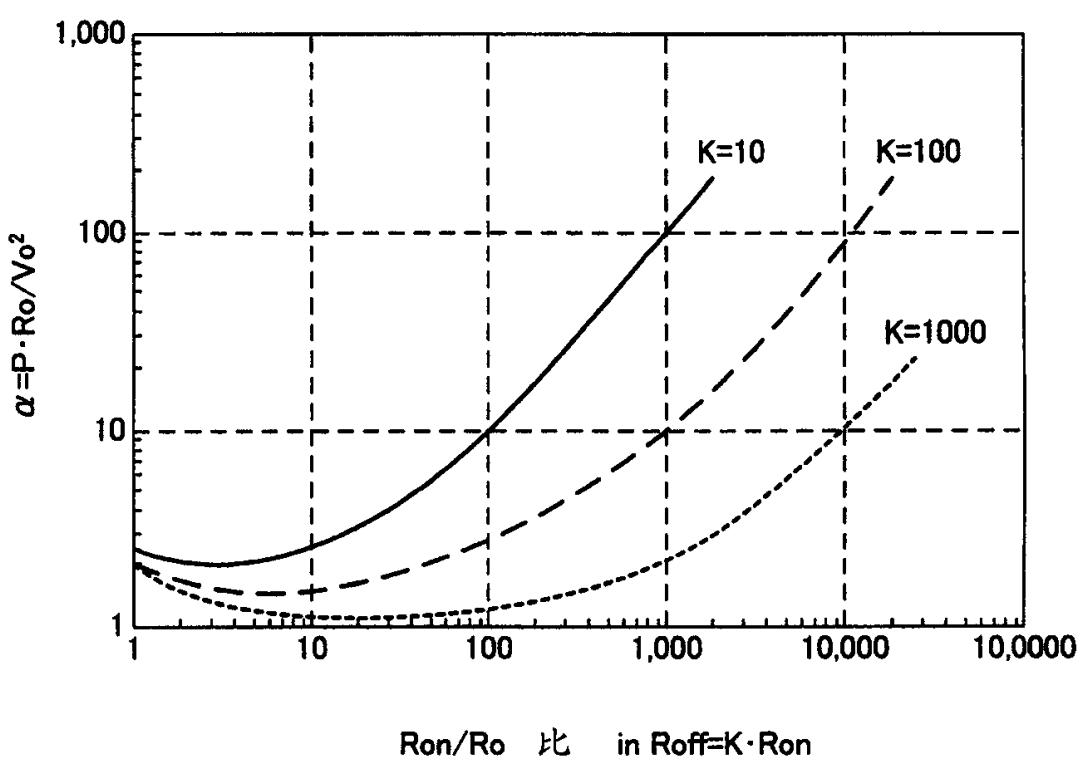

图 5 是将 TFT 的接通电阻值与断开电阻值的比率设定在某数值时表示上述像素的消耗功率和断开电阻值的关系的曲线；

图 6 是表示 TFT 的接通电阻值与断开电阻值的组合与上述消耗功率的关系的说明图；

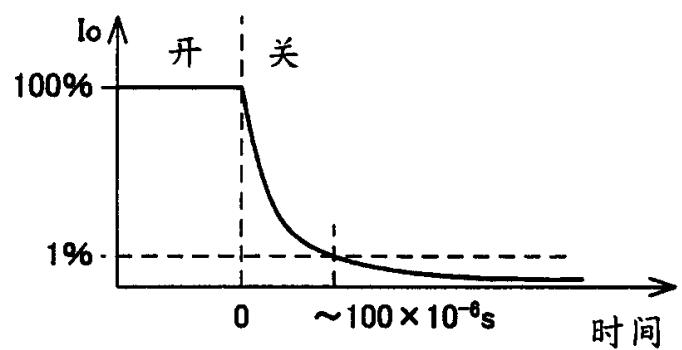

图 7 是表示在图 21 所示已有技术中在 LED (OLED) 中剩余的电流特性的曲线；

图 8 是表示图 1 所示像素中在 OLED 中剩余的电流特性的曲线；

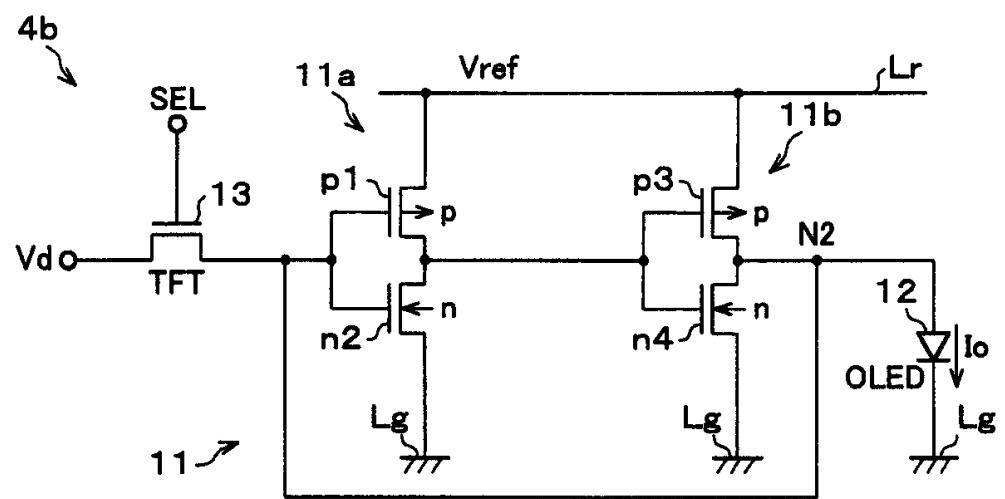

图 9 是表示上述实施例的变形例、表示像素的部件结构的电路图；

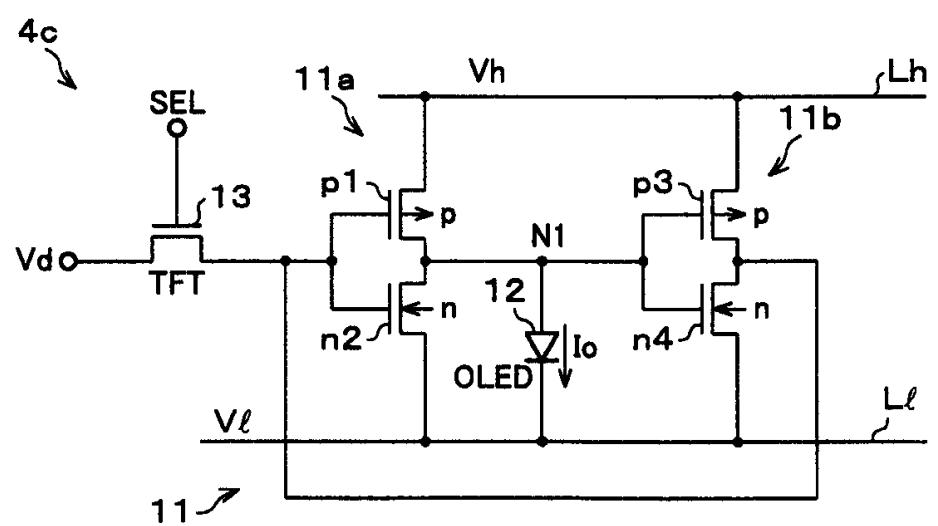

图 10 是表示上述实施例的另一变形例、表示像素的部件结构的电路图；

图 11 是表示上述实施例的再一变形例、表示像素的部件结构的电路图；

图 12 是表示上述实施例的又一变形例、表示像素的部件结构的电路图；

图 13 是表示上述实施例的另外一变形例、表示像素的部件结构的电路图；

图 14 是表示上述实施例的再一变形例、表示像素的部件结构的电路图；

图 15 是表示上述实施例的另外一变形例、表示像素的部件结构的电路图；

图 16 是表示上述实施例的另外的变形例、表示像素的部件结构的框图；

图 17 是表示上述实施例的再一变形例、表示像素的部件结构的电路图；

图 18 是表示已有技术、表示像素的部件结构的框图；

5 图 19 是表示另一已有技术、表示像素的部件结构的电路图；

图 20 是表示上述像素中存储器元件保持的电位随时间变化的曲线；

图 21 是表示再一已有技术、表示像素的部件结构的框图。

#### 具体实施方式

根据图 1 到图 7 说明本发明的一个实施例，如下所述。即，本实施例的显

10 示元件 1 是将作为光学调制元件的 OLED（有机发光二极管）排列成矩阵状的

显示元件，如图 2 所示，具有彼此平行配置的多个数据线  $2_{(1)} \sim 2_{(M)}$ 、与上述数

据线  $2_{(1)} \sim 2_{(m)}$  各分别大致正交地排列的多个选择线  $3_{(1)} \sim 3_{(N)}$ 、数据线  $2_{(1)} \sim$

$2_{(M)}$  与选择线  $3_{(1)} \sim 3_{(N)}$  的交叉点上配置的像素  $4_{(1,1)} \sim 4_{(N,M)}$ 、与各数据线  $2_{(1)} \sim$

$2_{(M)}$  连接的列地址解码器 5 和驱动各选择线  $3_{(1)} \sim 3_{(N)}$  的行地址解码器 6 以及控

15 制两个解码器 5,6 的控制电路 7。

具体如后所述，上述各像素  $4_{(ij)}$  具有作为存储元件的存储该像素  $4_{(ij)}$  为接

通（ON）状态还是截断（OFF）状态的存储器电路 11（后述），该存储器电路

11 构成为向自身连接的选择线  $3_{(j)}$  施加行地址解码器 6 预先设定的选择电平的

20 电位期间（选择期间），经自身连接的数据线  $2_{(j)}$  连接于列地址解码器 5，从列

地址解码器 5 访问（读写）存储器电路 11 的内容。该存储器电路 11 在选择期

间以外的非选择期间中从数据线  $2_{(j)}$  断开，保持在选择期间写入的值（ON 或

OFF 状态），继续向作为光学调制元件的 OLED12 施加。

这里，各像素  $4_{(ij)}$  不具有存储器电路 11 时，或者具有采样保持电路等模

拟方式的存储器电路时，如图 20 所示，在选择期间施加的电压在非选择期间连

25 续降低。因此，相反，即使像素  $4_{(ij)}$  的显示状态相同，也需要例如规定的周期

等，到电压降低影响显示的期间再次选择像素  $4_{(ij)}$  来恢复选择电位。其结果，

担心每单位时间应选择的像素  $4_{(ij)}$  的数目增多，每单位时间选择 1 个像素  $4_{(ij)}$

的时间（占空比）降低。

与此相反，本实施例的各像素  $4_{(ij)}$  具有存储接通（ON）状态还是截断（OFF）

30 状态的存储器电路 11，因此如图 3 所示，表示选择期间施加的状态的电压在非

选择期间被继续保持。其结果是如果像素  $4_{ij}$  的显示状态不改变，就不需要选择该像素  $4_{ij}$ 。结果，即使是像素数目多、分辨率高的显示元件 1，仍可抑制占空比的降低。由于仅更新必须的部分即可，因此无论显示状态有无变更，消耗功率都比向全部像素写入时减少。下面尤其是在矩阵的位置指定不重要的情况下，将任意像素  $4_{ij}$  统称像素 4。

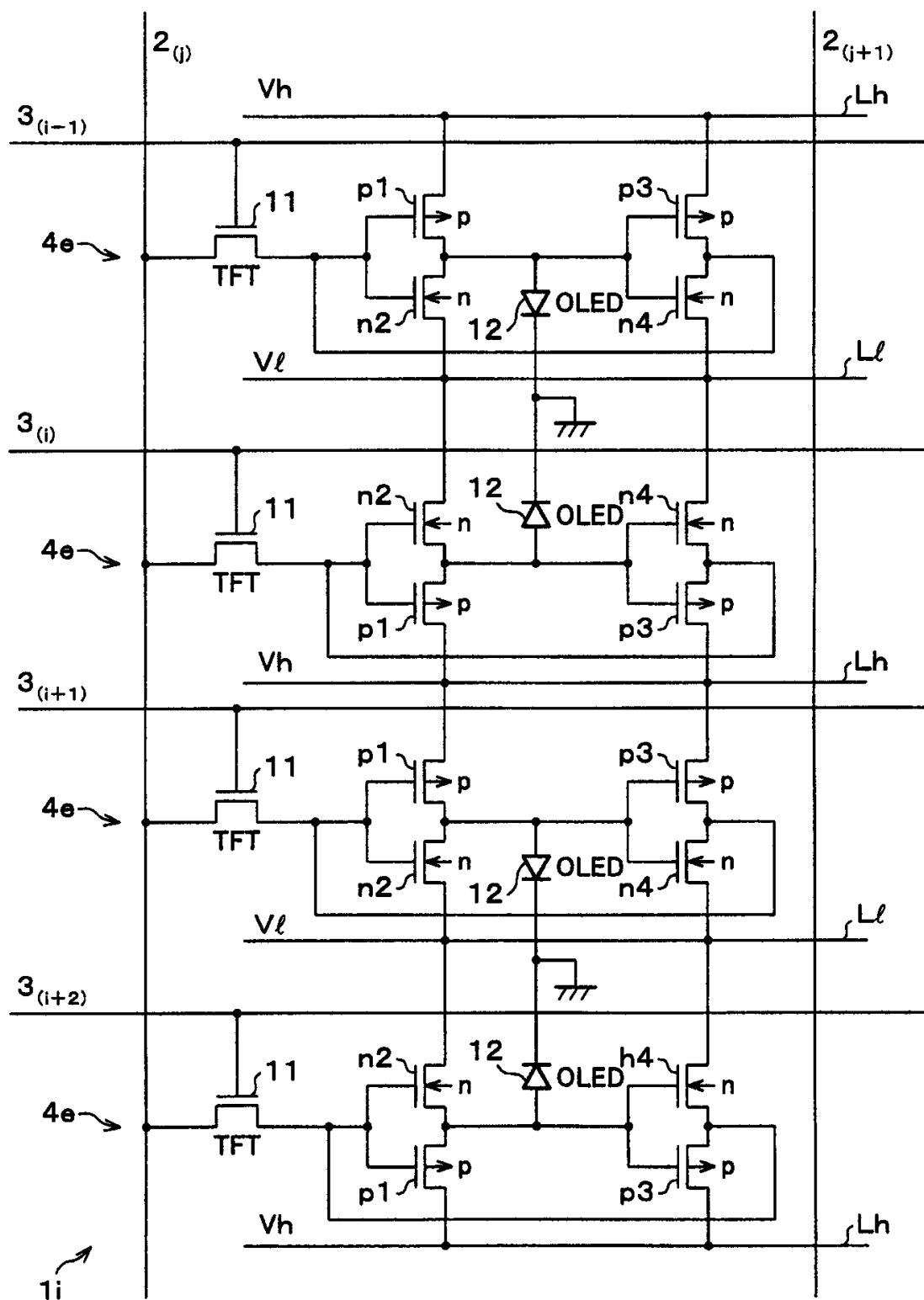

更具体说，本发明的像素 4 如图 1 所示包括将 CMOS 结构的反相器 11a·11b 连接成环状而构成的静态 RAM 所构成的存储器电路 11、向作为该存储器电路 11 的输出端例如反转输出端（反相器 11a 的输出端）N1 连接阳极端子并将阴极接地的 OLED12。另外，存储器电路 11 的输入端（反相器 11a 的输入）经选择电路 13 连接于和像素 4 对应的数据线 2，选择电路 13 导通时可施加数据线 2 的数据电位 Vd。该选择电路 13 例如由薄膜晶体管（TFT）等构成，通过与像素 4 对应的选择线 3 施加的选择信号 SEL 控制导通/截断。

上述反相器 11a 由互补动作的 p 型和 n 型 TFT p1·n2 构成，成为输入端的两个 TFT p1·n2 的栅极连接于上述选择电路 13 并且成为输出端的两个 TFT p1·n2 的漏极连接于下一级的反相器 11b。另外 TFTp1 的源极连接于施加预定的基准电位  $Vref[V]$  的电源线（第一电源线）Lr 并且 TFTn2 的源极连接于地线（第二电源线）Lg。

另一方面，在上述反相器 11a 上纵向连接的下一级的反相器 11b 也由互补动作的 p 型和 n 型 TFT p3·n4 构成，成为输入端的两个 TFT p3·n4 的栅极连接于上述反相器 11a 的输出端（两个 TFT p1·n2 的漏极）的同时并且成为输出端的两个 TFT p3·n4 的漏极反馈到反相器 11a 的输入端（两个 TFT p1·n2 的栅极）。两个 TFT p3·n4 的源极与反相器 11a 同样连接于电源线 Lr 和地线 Lg。

图 1 的结构中，反相器 11a 的输出端 N1 上连接 OLED12，因此反相器 11a 与权利要求记载的输出反相器对应。反相器 11a 的 TFTp1 与 p 型晶体管对应，25 TFTn2 与 n 型晶体管和电荷适当装置对应。

本实施例中，例如，用同一电平的层在平面内作成 OLED12 和存储器电路 11，将 OLED12 的阴极用铝等导电性高的布线形成，存储器电路 11 的地线 Lg 和 OLED12 的地线 Lg 作为共用电极一体形成，但也可独立形成。但是，某像素 4 的 OLED12 和存储器电路 11 不具有公共电极时，例如在形成存储器电路 30 11 等的基板的相对侧上经绝缘膜等形成 OLED12 的地线等，将 OLED12 的地线

与存储器电路 11 的地线、电源线在不同的层内形成，并且各像素 4 的 OLED12 的地线可为共用电极。任一情况下，像素 4 的 OLED12 的地线与该像素 4 的存储器电路 11 的地线和/或其他像素 4 的 OLED12 的地线作为公共电极形成可简化布线的占据面积和制造工序，并且提高像素 4 的数值孔径。

- 5 上述结构中，选择期间中，选择电路 13 导通，存储器电路 11 的输入端上施加数据线 2 的电位（数据电位  $V_d$ ）。由此，存储器电路 11 的各反相器 11a(11b)中，两个 TFT p1·n2(n4·p3)的一侧导通，反转输出端 N1 的电位为与基准电位  $V_{ref}$  或地电平的 2 个值中与数据电位  $V_d$  对应的值。列地址解码器 5 的电流驱动能力设定得比反相器 11b 的电流驱动能力高很多，因此反转输出端 N1 的电位不限于至此在存储器电路 11 存储的值，为与数据电位  $V_d$  对应的值。

10

上述存储器电路 11 中，两个反相器 11a·11b 连接成环状，因此两个反相器 11a·11b 中，两个 TFT p1·n2(n4·p3)的导通/截断状态在选择期间结束后、选择电路 13 截断期间（非选择期间中）仍维持。其结果反转输出端 N1 的电位保持基准电位  $V_{ref}$  或地电位  $V_g$  的 2 个值中与选择电路 13 的截断时刻相同的电位。因此，OLED12 的点亮/熄灭由选择期间施加的数据电位  $V_d$  控制，该数据电位  $V_d$  表示接通状态（反转输出端 N1 为基准电位  $V_{ref}$ ）时，OLED12 在非选择期间中继续点亮。表示断开状态（反转输出端 N1 为地电位  $V_g$ ）时，可继续熄灭。

15

上述中，说明的是列地址解码器 5 向由行地址解码器 6 选择的像素 4 的存储器电路 11 写入表示点亮/熄灭的数据的情况，但是选择期间中经数据线 2 连接存储器电路 11 和列地址解码器 5，因此可读出存储器电路 11 的内容。此时，列地址解码器 5 用非常大的输入阻抗的输入电路将存储器电路 11 的内容判定为不变更反相器 11b 反馈的电位电平的程度，因此不变更存储器电路 11 的内容，可读出存储器电路 11 的内容。

20

读出数据时，包含数据读出中的像素 4... 中，各个存储器电路 11 存储自身的显示状态，因此不造成任何障碍地继续显示画面。上述显示元件 1 中，各数据线  $2_{(1)} \sim 2_{(M)}$  彼此独立设置，列地址解码器 5 中，对数据线  $2_{(1)} \sim 2_{(M)}$  访问的电路也彼此独立设置。因此列地址解码器 5 可同时向所有选择中的像素 4 写入，从全部这些像素可同时读出数据。另外，向某像素  $4_{(ij)}$  的写入的同时，可从其他像素  $4_{(ik)}$  的存储器电路 11 读出内容。

25

30 这里，OLED12 为接通状态时，在驱动 OLED12 的反相器 11a 中，TFTp1

导通、TFTn2 截断，因此向 OLED12 供给电流的电路的等效电路如图 4 所示为连接于基准电位  $V_{ref}$  的电阻  $R_{on}$  经电阻  $R_{off}$ 、电阻  $R_o$  和电容  $C_o$  的并联电路接地的电路。图 4 的等效电路中，TFTp3-n4 的栅极为输入端的下一级的反相器 11b 与上述电阻  $R_{on}$ 、 $R_{off}$ 、电阻  $R_o$  和电容  $C_o$  相比，输入阻抗高、不影响消耗功率的分析，因此图中略去。图 4 的电阻  $R_{on}$  和  $R_{off}[\Omega]$  与 TFTp1 的接通电阻以及 TFTn2 的断开电阻对应。另外，电阻  $R_o[\Omega]$  和电容  $C_o[F]$  与 OLED12 的电阻分量和电容分量对应。

上述等效电路中，像素 4 的消耗功率  $P[W]$  按下式（1）表示

$$P = V_{ref}^2 / (R_{on} + R_{off} \cdot R_o / (R_{off} + R_o)) \quad \dots\dots\dots(1)$$

另一方面，向 OLED12 施加的电压  $V_o$  在 OLED12 接通状态下设定成希望的亮度值，因此不管 TFTp1-n1 的电阻值如何，当施加电压  $V_o$  为一定值时，需要设定基准电位  $V_{ref}$  使得基准电位  $V_{ref}$  的电阻  $R_{on}$  和  $R_{off}$  产生的分压值为规定电压  $V_o$ 。

这里，TFTp1 的接通电阻值  $R_{on}$  对于 OLED12 的接通电阻值  $R_o$  的相对值 A ( $=R_{on}/R_o$ )、TFTn2 的断开电阻  $R_{off}$  对于 OLED12 的接通电阻值  $R_o$  的相对值 B ( $=R_{off}/R_o$ ) 并通过  $V_o = V_{ref} \cdot (R_{off} \cdot R_o / (R_{off} + R_o)) / (R_{on} + R_{off} \cdot R_o / (R_{off} + R_o))$  替代上式（1）时，下式（2）成立：

$$P \cdot R_o / V_o^2 = (A + (B / (B + 1))) / (B / (B + 1))^2 = \alpha \quad \dots\dots\dots(2)$$

式（2）中，电阻值  $R_o$  和电压  $V_o$  固定，因此消耗功率 P 与式（2）的右侧的代用标记  $\alpha$  成正比变化，参数  $\alpha$  最小时，消耗功率最小。

另外，分辨改变上述相对值 A 和 B 时的参数  $\alpha$  的值例，如图 6 所示，相对值 A 小并且相对值 B 大时，消耗功率 P 降低。例如，n 型 TFTn2 的断开电阻值  $R_{off}$  为 OLED12 的接通电阻值  $R_o$  的 1000 倍时，p 型的 TFTp1 的接通电阻值  $R_{on}$  为电阻值  $R_o$  的 0.2 倍以下，则可充分避免发光部（OLED12）以外的无用功率浪费。

这里，n 型 TFT 的断开电阻的比率对 p 型的 TFT 的接通电阻的比率由制造方法、材质或 TFT 的尺寸、结构等限制，因此 n 型 TFT 的断开电阻对 p 型的 TFT 的接通电阻的比率为 K ( $=B/A$ ) 时，对于几个 K 图示出表示消耗功率 P 的参数  $\alpha$  与上述相对值 A 的关系时，如图 5 所示。图 5 中，表示出 n 型 TFT 的断开电阻为 p 型的 TFT 的接通电阻的 10 倍、100 倍和 1000 倍时 ( $K=10, 100, 1000$ )

的情况。

将  $B=K \cdot A$  代入上式 (2)，算出参数  $\alpha$  最小时的相对值  $A$  的值，则如下式所示成立：

$$d\alpha/dA = 1 - ((K+1)/K^2) \cdot (1/A^2) = 0 \dots\dots(3)$$

5 如下式 (4) 所示，为：

$$A = (K+1)^{1/2}/K \dots\dots(4)$$

其结果例如  $K=100$  时，TFTp1 的接通电阻  $R_{on}$  设定成 OLED12 的接通电阻  $R_o$  的 0.10 倍左右， $K=1000$  时，将电阻  $R_{on}$  设定到电阻  $R_o$  的 0.032 倍左右，可使像素 4 的消耗功率最小。从该最佳值的偏离产生的消耗功率增大若在例如 10 为百分之几的左右的许可范围内，则设定成从上述值稍微偏离也可以。

下面，作为许可范围的例子说明设定各像素 4 的亮度使得亮度变化（偏差）相对设计值为  $\pm x\%$  的情况。这里，OLED12 的电流—亮度特性大致为线状。因此，对各像素 4 施加的电压一定时，亮度变动对设计值为  $\pm x\%$  时，电流相对流向 OLED12 的电流平均值的变动值也为  $\pm x\%$ ，功率相对 OLED12 消耗的功率 15 平均值的变动值也为  $\pm x\%$ 。另外，施加电压一定时，OLED12 的接通电阻的偏差以  $R_o$  为平均值，近似具有  $\pm x\%$  的偏差时，上述式 (1) 为下式 (5) 所示：

$$P = V_{ref}^2 / (R_{on} + R_{off} \cdot R_o \cdot X / (R_{off} + R_o \cdot X)) \dots\dots(5)$$

上式 (5) 中， $X$  表示 OLED12 的接通电阻的变动， $X = 1 \pm x/100$ 。

如上述所示，向 OLED12 施加的电压  $V_o$  设定成大致为一定值，因此与上 20 式 (1) 和式 (2) 同样，通过相对值  $A = R_{on}/R_o$ 、 $B = R_{off}/R_o$  并通过  $V_o = V_{ref} \cdot (R_{off} \cdot R_o \cdot X / (R_{off} + R_o \cdot X)) / (R_{on} + R_{off} \cdot R_o \cdot X / (R_{off} + R_o \cdot X))$  替代上述式 (5)，得到下式 (6)：

$$P \cdot R_o / V_o^2 = (A + (B \cdot X / (B + X))) / (B / (B + X))^2 = \alpha \dots\dots(6)$$

另外，与上述式 (3) 一样，将  $B=K \cdot A$  代入上式 (6)，则算出参数  $\alpha$  最小 25 时的相对值  $A$  的值，则如下式所示成立：

$$d\alpha/dA = 1/X^2 - ((K+1)/K^2) \cdot (1/A^2) = 0 \dots\dots(7)$$

如下式 (8) 所示，为：

$$A = (K+1)^{1/2} \cdot (1 \pm x/100) / K \dots\dots(8)$$

此时，像素 4 的消耗功率  $P$  最小。

30 因此，相对值  $A$  在如下所示范围内时，各像素 4 的点亮亮度的偏差量保持

在基准值 $\pm x$  以内。

$$\begin{aligned} (K+1)^{1/2} \cdot (1-x/100)/K &\leq A \leq (K+1)^{1/2} \cdot \\ &\quad (1+x/100)/ \\ K &\quad \cdots (9) \end{aligned}$$

同样，相对值 B 满足如下所示时，各像素 4 的点亮亮度的偏差量保持在基准值 $\pm x$  以内。

$$\begin{aligned} (K+1)^{1/2} \cdot (1-x/100) &\leq B \leq (K+1)^{1/2} \cdot \\ &\quad (1+x/100) \cdots (10) \end{aligned}$$

- 上述结构中，与图 21 所示的已有技术不同，成为光学调制元件的 OLED12

5 直接连接于存储器电路 11 的输出端（反转输出端 N1），替代图 21 所示的驱动

用的 TFT121 而存储器电路 11 的 TFTp1 接通驱动 OLED12。因此，与图 21 所

示结构相比，仅将元件数目减少 TFT121 的部分，提高像素 4 的数值孔径。

- 图 21 的结构中，由于像素从接通状态向断开状态移动，即使 TFT121 被截

断，由于 LED112 的电容分量，接通状态期间存储在 LED112 的阳极的电荷也

10 不快速释放，如图 7 所示，TFT121 截断后，电流也流向 LED112。

- 这里，像素的光学调制元件为液晶时，由于剩余电荷，即使向光学调制元

件施加的电压稍有变动，像素中产生的色度变化、显示烧坏或光学调制元件的

恶化多半不是问题。但是，光学调制元件在 LED 或 OLED 时，发光强度根据电

流变化，根据施加电压的指数函数变化，因此即使电压稍稍变动，也会担心

15 产生大的亮度偏差。

- 因此，前场为接通（亮）状态、下一场为断开（暗）状态时，在一定期间

(图 7 的例子中为 100 微秒) 中像素中剩余残留光。尤其，通过电荷存储产

生参与光时，像素数多，在高频驱动的显示元件中，产生显示错误，像素显示偏

离希望的亮度，色度变化。OLED (LED) 上存储电荷时，成为烧坏、元件恶化

20 的原因。

与此相反，图 1 所示结构中，存储器电路 11 是将反相器 11a・11b 形成为

环状的静态 RAM，用互补动作的 TFTp1・n2 驱动 OLED12。因此，像素 4 从接

通状态移动到断开状态时，随着 TFTp1 的截断，TFT n2 导通。其结果接通状态

期间，即使在 OLED12 的阳极上存储电荷，该电荷也经 TFTn2 释放到地线 Lg。

因此，作为光学调制元件，不限于使用电流驱动型的 OLED12，如图 8 所示，实现陡直的光学响应特性。由此，原理上不产生剩余电荷引起的暗显示的灰度错误，可抑制剩余电荷引起的色度的变化、显示烧坏或 OLED12 的恶化。

本实施例中，如上所述，TFTp1 的接通电阻  $R_{on}$  和 TFTn2 的断开电阻  $R_{off}$  设定。因此，通过 TFT 的电阻值和 OLED12 的电阻值的平衡，不管是否使用担心像素 4 内白白消耗功率的光学调制元件，即电流动作型 OLED12，都可降低 OLED12 接通状态时的消耗功率 P。断开状态时，由于 OLED12 截断，各反相器 11a·11b 的 TFTp1~n4 移动到恒定状态下后，电源线 Lr 和地线 Lg 之间不流过电流。因此断开状态的像素 4 的消耗功率保持低值。

但是，图 1 所示的像素 4 中，说明的是 OLED12 设置在存储器电路 11 的反转输出端 N1 和地线之间的情况，但如图 9 所示的像素 4a 那样，反转输出端 N1 和电源线 Lr 之间也可设置 OLED12。

此时，OLED12 与像素 4 相反，存储器电路 11 将反转输出端 N1 维持在地电平期间，即在 TFTp1 截断、TFTn2 导通期间点亮。OLED12 将反转输出端 N1 维持在基准电位  $V_{ref}$  期间，即在 TFTp1 导通、TFTn2 截断期间熄灭。该例中，OLED12 在熄灭时 TFTp1 导通，因此该 TFTp1 与权利要求的范围内记载的电荷释放装置对应。

OLED12 点亮时，向 OLED12 供给电流的电路的等效电路如图 4 ( ) 表示，为更换像素 4 的等效电路的地线 Lg 和电源线 Lr 的电路，因此 TFTn2 的接通电阻为  $R_{on}$ 、TFTp1 的断开电阻为  $R_{off}$  时，像素 4 的消耗功率 P 如上式 (1) 到式 (4) 所示原封适用。因此，p 型 TFT 的断开电阻值  $R_{off}$  对 n 型 TFT 的接通电阻值  $R_{on}$  的比率 A 设定到  $(K+1)^{1/2}/K$ ，则像素 4a 的消耗功率 P 可设定到最小值。

即使该结构，成为光学调制元件的 OLED12 直接连接于存储器电路 11 的输出端（反转输出端 N1），存储器电路 11 的 TFTn2 接通驱动 OLED12，因此与图 1 的像素 4 同样，可减少元件数，提高像素 4a 的数值孔径。

像素 4a 从接通状态向断开状态移动时，随着 TFTn2 的截断，TFTp1 导通。其结果，接通状态期间，即使 OLED12 的阴极上存储电荷，该电荷通过 TFTp1 释放到电源线 Lr。因此，与图 1 的像素 4 同样，作为光学调制元件，不管是否使用电流驱动型的 OLED12，如图 8 所示，可实现陡直的光学响应特性，由此，

可抑制剩余电荷引起的色度的变化、显示烧坏或 OLED12 的恶化。

本实施例中，如上所述，设定 TFTn2 的接通电阻 Ron 和 TFTp1 的断开电阻 Roff。因此，不管是否使用电流动作型的 OLED12，都可降低像素 4a 的消耗功率 P。

5 图 1 和图 9 中，

作为存储器电路 11 的输出端，说明了将 OLED12 连接于反转输出端 N1 的情况，但如图 10 的像素 4b 所示，反馈线部分的非反转输出端 N2（反相器 11b 的输出端）上连接 OLED12 的情况下也得到同样的效果。

OLED12 与图 9 同样设置在输出端和电源线 Lr 之间，但图 10 中，与图 1

10 同样，表示出在输出端和地线 Lg 之间设置的情况。图 10 的结构中，反相器 11b 的输出端连接于 OLED12，OLED12 熄灭时 TFTn4 导通，因此反相器 11b 对应于权利要求范围记载的输出反相器，TFTp3 对应 p 型晶体管、TFTn4 对应 n 型晶体管和电荷释放装置。

另一方面，图 1、图 9 和图 10 中，说明了向像素 4·4a·4b 供给基准电位 Vref

15 和地电平的情况，但如图 11（图 12）所示像素 4c(4d)所示，代替其可供给正负电源电压 Vh·Vl。此时，通过作为第一和第二电源线的电源线 Lh 和 Ll 施加的正负电源电位 Vh·Vl 驱动存储器电路 11，因此除像素 4~4b 的效果外，可更稳定地动作存储器电路 11。此时，与图 1,图 9 和图 10 的结构相比，电源的电位电平从基准电位 Vref 和地电平变更到正负电源电位 Vh 和 Vl，但若电位差相同，

20 消耗功率相同，因此各 TFT 的接通电阻值 Ron 和 Roff 与上述同样地设定，使得可将消耗功率 P 设定到最小。

如图 13 到图 15 所示的像素 4f 到 4g 那样，由正负电源电压 Vh·Vl 驱动存储器电路 11 的同时，向 OLED12 的一端（与存储器电路 11 的输出端不同的端部）施加与两电源电位 Vh·Vl 不同的电位。图 13 是图 1 所示的像素 4 中将 OLED12

25 的阴极和存储器电路 11 的电源电极分离开的结构，OLED12 的阴极接地。图 14 所示的像素 4f 与图 9 所示的像素 4a 对应，向 OLED12 的阳极施加基准电位 Vref。另外，图 15 所示的像素 4g 与图 10 所示的像素 4b 对应，将 OLED12 的阴极接地。

这些结构中，除像素 4~像素 4d 的效果外，由于 OLED12 的电极和存储器

30 电路 11 的电极分离，因特性改善等理由可用不同方法分别制造或施加不同的电

压。由于各电极分离，在 OLED12 的上层或下层等与存储器电路 11 的电极不同的层上可配置 OLED12 的电极。因此，与在同一层上形成电极的情况相比，可提高数值孔径。使 OLED12 的两个电极中至少之一为透明电极，则通过透明电极可发光显示更好。

但是，图 2 所示的显示元件 1 中，各像素 4<sub>(ij)</sub> 分别具有 1 个 OLED12，基于在存储器电路 11 中存储的值（2 值）来点亮或熄灭各个 OLED12。与此相反，图 16 所示的显示元件 1h 中，各像素 4 被分割为多个副像素 41·42，根据副像素 41·42 的点亮/熄灭组合来作灰度显示。上述副像素 41（42）是与上述各像素 4~4g 之一相同的结构，各副像素 41·42 的灰度电平可设定成通过例如调整 OLED12 的发光面积、供给电源电平等、组合各副像素 41·42 的点亮/熄灭组合来使像素 4h 的亮度为希望的灰度的亮度电平。

图 16 中，作为一例，表示出组合行方向（沿着选择线 3<sub>(j)</sub> 的方向）上相邻的 2 个副像素 41<sub>(ij)</sub>·42<sub>(ij)</sub> 来构成 1 个像素 4h<sub>(ij)</sub>，通过向副像素 41<sub>(ij)</sub> 供给数据电位 Vd 的数据线 21<sub>(j)</sub> 和向副像素 42<sub>(ij)</sub> 供给数据电位 Vd 的数据线 22<sub>(j)</sub> 驱动像素 4h<sub>(ij)</sub> 时的情况虽然已作了图示，但当然，分割像素 4h 的副像素的个数根据需要的灰度数可设定到期望的值。各副像素相邻配置以看作 1 个像素，则可沿着选择线 3，也可以沿着数据线 2（21.22），各副像素沿着选择线 3 配置而连接于同一选择线 3 时，则仅选择该选择线 3 就可访问所有副像素的各存储器电路 11，因此可缩短访问时间。该例中，表示出向副像素 41 的存储器电路 11 写入、从副像素 42 的存储器电路 11 读出数据的情况也如图示。

这里，图 2 和图 16 的例子中，为说明简便，说明各像素 4（4h）在相同方向上形成的情况，但如本实施例所示，各像素 4~4h 具有存储器电路 11，除数据线 2 和选择线 3 外，还将供给基准电位 Vref 和地电平或电源电位 Vh·Vl 等的电源线连接于各像素 4~4h 时，如图 17 所示的显示元件 1i 那样，希望各像素 4~4h 或各副像素 41·42 线对称地配置较好。图 17 中，例示出将图 13 所示的像素 4e 相对选择线 3 线对称地配置的情况。沿着选择线 3 交互形成供给电源电位 Vh 的电源线 Lh 和供给电源电位 Vl 的电源线 Ll。

该结构中，像素 4e 相对作为基准线的选择线 3 线对称地配置，因此沿着该电源线 Lh 的选择线 3 上相邻的像素 4e·4e 中，连接于该电源线 Lh 的元件（TFTp1·p3）比同方向形成时配置在相邻的位置上，在两像素 4e·4e 之间共用电

源线 Lh。同样，沿着电源线 L1 的选择线 3 上相邻的像素 4e·4e 之间可共用电源线 L1。其结果像素数（数据线 2 的根数和选择线 3 的根数）相等时，显示元件 1i 上形成的必要的电源线数目大致降低 1/2，可提高数值孔径。上面说明了相对选择线 3 线对称地配置的情况，但由于可在相对数据线 2 线对称地配置并且夹持数据线 2 配置的像素之间共用电源线（地线），可得到同样的效果。

如上所述，本发明的存储器一体型显示元件（1·1h~1i）中光学调制元件（OLED12）和存储表示对该光学调制元件的输入的 2 值数据的存储器元件（11）设置在像素（4·4a~4i）上，上述存储器元件由至少 2 个反相器（11a·11b）连接成环状而构成，上述各个反相器中输出为上述存储器元件的输出端的输出反相器（11a 或 11b）的输出直接连接于上述光学调制元件的一端。存储器元件的输出端和光学调制元件通过例如连接存储器元件的输出端和光学调制元件的阳极，或者连接存储器元件的输出端和光学调制元件的阴极等而相互连接。这里，根据光学调制元件的材料的光学特性、与基板的材质的兼容性等选择其中之一的连接。

根据上述结构，由于存储器元件的输出端和光学调制元件直接连接，存储器元件和光学调制元件与经驱动用开关元件连接的已有技术相比，可将开关元件的数目减少驱动用的开关元件的部分。成为输出端的输出反相器驱动光学调制元件，因此即使去除驱动用开关，也不会产生故障，可驱动光学调制元件。

由于不插入驱动用开关元件，例如，使用电流驱动型的 LED（发光二极管）作为光学调制元件的情况下，相对施加电压变动而言亮度变化的特性陡直的情况下，例如即使产生制造偏差，光学调制元件的亮度电平不随驱动用开关元件的特性变化而产生变化，能够以相同亮度电平点亮光学调制元件。

尤其，在将光学调制元件和存储器元件构成的像素排列成矩阵状的情况下，上述亮度电平的变化，应以相同显示状态显示的像素之间的显示状态的偏差，显示品质恶化，但上述结构中，亮度电平的偏差不产生，因此可防止该显示品质的恶化。

希望本发明的存储器一体型显示元件除上述结构外还具有在电压施加结束后将在上述存储器元件向光学调制元件施加电压期间在该光学调制元件上存储的电荷释放出去的电荷释放装置（TFTp1、n2、p3 或 n4）。

该结构中，存储器元件产生的电压施加结束后，电荷释放装置释放在光学

调制元件上存储的电荷，光学调制元件比设置电荷释放装置的情况强，可向下一显示状态移动。如使用电流驱动型的光学调制元件的情况一样，即使在剩余电荷容易改变光学调制元件的显示状态，容易降低存储器一体型显示元件的显示品质的情况下，也可防止显示错误发生。另外，像 OLED（有机发光二极管）

5 一样，使用由于剩余电荷而容易将光学调制元件烧坏或恶化的光学调制元件的情况下，由于电荷释放装置释放电荷，可抑制烧坏或恶化的光学调制元件。

本发明的存储器一体型显示元件中，上述输出反相器例如即使是 CMOS（互补 MOS）反相器这样的互补型反相器也可以。

该结构中，存储器元件例如存储熄灭/点亮等的 2 值之一时，构成上述互补

10 型的反相器的开关元件（例如 p 型晶体管和 n 型晶体管的组合等）中的一个导通。由此，在某显示状态下，即使在光学调制元件上存储电荷，该剩余电荷经导通的开关元件快速释放出去，光学调制元件快速移动到下一显示状态。因此，与设置电荷释放装置的情况相同，显示错误的产生或光学调制元件的烧坏和恶化可被抑制。

15

另外，本发明的存储器一体型显示元件中除上述结构外，上述互补型反相器包括连接于第一电源线（Lh 或 Lr）的 p 型晶体管（TFTp1 或 p3）和连接于第二电源线（Lg 或 Ll）的 n 型晶体管（TFTn2 或 n4），上述光学调制元件的阳极连接于上述输出反相器的输出端，阴极连接于上述第二电源线的同时，并且设上述 n 型晶体管的断开电阻值相对 p 型晶体管的接通电阻值的比率为 K 时，

20 上述 p 型晶体管的接通电阻值相对上述光学调制元件的接通电阻值的比率设定大约为  $(K+1)^{1/2}/K$ 。

25

本发明的存储器一体型显示元件中除上述结构外，上述互补型反相器包括连接于第一电源线（Lh 或 Lr）的 p 型晶体管（TFTp1 或 p3）和连接于第二电源线（Lg 或 Ll）的 n 型晶体管（TFTn2 或 n4），上述光学调制元件的阳极连接于上述输出反相器的输出端，阴极连接于上述第二电源线的同时，并且设上述 n 型晶体管的断开电阻值相对 p 型晶体管的接通电阻值的比率为 K、上述光学调制元件的点亮亮度的偏差量为基准值的  $\pm x\%$  以内时，上述 p 型晶体管的接通电阻值相对上述光学调制元件的接通电阻值的平均值的比率设定为从  $(K+1)^{1/2} \cdot (1-x/100)/K$  到  $(K+1)^{1/2} \cdot (1+x/100)/K$  的范围内。

30

上述连接中，各电阻值如上设定时，p 型晶体管和光学调制元件为导通状

态，n型晶体管为截断状态时的输出反相器和光学调制元件的消耗功率大致为最小。另一方面，光学调制元件为截断状态时，与导通状态相比，电阻值变得非常大。由于p型晶体管截断、n型晶体管导通，向光学调制元件施加的电压大致为0，与导通状态相比，输出反相器和光学调制元件的消耗功率小。因此，

5 如上所述，通过设定各电阻值，存储器一体型显示元件的消耗功率可降低。

另一方面，本发明的存储器一体型显示元件在上述输出反相器为互补型的反相器的结构中，上述互补型反相器包括连接于第一电源线(Lh或Lr)的p型晶体管(TFTp1或p3)和连接于第二电源线(Lg或Ll)的n型晶体管(TFTn2或n4)，上述光学调制元件的阴极连接于上述输出反相器的输出端，阳极连接于上述第二电源线的同时，并且设上述p型晶体管的断开电阻值相对n型晶体管的接通电阻值的比率为K时，上述n型晶体管的接通电阻值相对上述光学调制元件的接通电阻值的比率设定大约为(K+1)<sup>1/2</sup>/K。

10

15

本发明的存储器一体型显示元件中除上述结构外，上述互补型反相器包括连接于第一电源线(Lh或Lr)的p型晶体管(TFTp1或p3)和连接于第二电源线(Lg或Ll)的n型晶体管(TFTn2或n4)，上述光学调制元件的阴极连接于上述输出反相器的输出端，阳极连接于上述第二电源线，并且设上述p型晶体管的断开电阻值相对n型晶体管的接通电阻值的比率为K、上述光学调制元件的点亮亮度的偏差量为基准值的±x%以内时，上述p型晶体管的接通电阻值相对上述光学调制元件的接通电阻值的平均值的比率设定为从(K+1)<sup>1/2</sup>·(1-x/100)/K到(K+1)<sup>1/2</sup>·(1+x/100)/K的范围内。

20

上述连接中，各电阻值如上设定时，n型晶体管和光学调制元件为导通状态，p型晶体管为截断状态时的输出反相器和光学调制元件的消耗功率大致为最小。另一方面，与阴极连接于第二电源线的情况同样，光学调制元件为截断状态时的消耗功率非常小。因此，如上所述，通过设定各电阻值，存储器一体

25 型显示元件的消耗功率可降低。

本发明的存储器一体型显示元件在上述结构中，由多个包括上述光学调制元件和存储器元件的副像素(41·42)构成1个像素单位。该结构中，1个像素单位由多个副像素构成，通过组合各副像素的光学调制状态(2值)可对1个像素单位的亮度电平附加灰度。其结果，存储器元件，如不管是否仅存储点亮/未点亮等的2值，可将像素的灰度表现数设定大于2。即使通过时分驱动来表

30

现灰度的情况下，通过组合时分驱动和像素分割驱动，可相对减少时分驱动数，将存储器一体型显示元件的驱动频率设定得较低。

本发明的存储器一体型显示元件除上述结构外，共用上述存储器元件的电源电极之一和上述光学调制元件的阳极或阴极。这样，与分别设置电极的情况

5 相比，可减少电极的总体面积，提高存储器一体型显示元件的数值孔径。

另一方面，本发明的存储器一体型显示元件替代共用电极，分别形成了上述存储器元件的第一电源电极和第二电源电极，以及上述光学调制元件的阳极和阴极。该结构中，在存在特性改善等理由的情况下，可向各电极分别施加电压。

10 不管是否共用电极，向存储器元件的各电源电极施加的电压电平和存储器元件的输出电平一致就可以。例如，二者之间具有规定的电位差等情况下二者不一致也可以。不一致时，向各电源电极施加的电压电平通过存储器元件调整，使得输出光学调制元件的显示适当的电压电平。

本发明的存储器一体型显示元件在上述结构之外还具有多个数据信号线

15 (2… ) 和与上述各数据信号线大致正交的多个选择信号线 (3… )，上述的存储器元件设置了与数据信号线和选择信号线的每一组合设置上述存储器元件，与自身对应的选择信号线指示选择时，存储与自身对应的数据信号线所示的 2 值数据，并且，经数据信号线或选择信号线之一的基准线相邻的存储器元件之间以及光学调制元件之间对于该基准线线对称地布置，该存储器元件之间或光学

20 调制元件之间最好能够共用电源线。

该结构中，经基准线相邻的存储器元件之间和光学调制元件之间线对称地配置，该存储器元件之间或光学调制元件之间共用电源线，可减少存储器一体型显示元件需要的电源线数目。这样，减少存储器一体型显示元件需要的电极根数，可实现数值孔径高的存储器一体型显示元件。

25 发明的详细说明中作出的具体实施形式和实施例目的是使本发明的技术内容更明白，不限定于该具体的例子，不应作狭义的解释，在本发明的精神和下面记载的权利要求的范围内，可实施各种变更。

## 说 明 书 附 图

1

图 2

图 3

图 4

图 5

图 6

涉及功耗的参数 $\alpha$ 相对于电阻(相对值)A和电阻(相对值)B的组合的值

|      | B      |        |       |       |       |       |       |       |       |       |       |       |       |       |       |       |

|------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| A    | 20,000 | 10,000 | 5,000 | 2,000 | 1,000 | 500   | 200   | 100   | 50.0  | 20.0  | 10.0  | 5.00  | 2.00  | 1.00  |       |       |

| 0.01 | 1.010  | 1.010  | 1.010 | 1.011 | 1.011 | 1.012 | 1.015 | 1.020 | 1.030 | 1.061 | 1.112 | 1.214 | 1.523 | 2.040 |       |       |

| 0.02 | 1.020  | 1.020  | 1.020 | 1.021 | 1.021 | 1.022 | 1.025 | 1.030 | 1.041 | 1.072 | 1.124 | 1.229 | 1.545 | 2.080 |       |       |

| 0.05 | 1.050  | 1.050  | 1.050 | 1.051 | 1.051 | 1.052 | 1.056 | 1.061 | 1.072 | 1.105 | 1.161 | 1.272 | 1.613 | 2.200 |       |       |

| 0.10 | 1.100  | 1.100  | 1.100 | 1.101 | 1.101 | 1.102 | 1.106 | 1.112 | 1.124 | 1.160 | 1.221 | 1.344 | 1.725 | 2.400 |       |       |

| 0.20 | 1.200  | 1.200  | 1.200 | 1.201 | 1.201 | 1.203 | 1.207 | 1.214 | 1.228 | 1.271 | 1.342 | 1.488 | 1.950 | 2.800 |       |       |

| 0.50 | 1.500  | 1.500  | 1.500 | 1.501 | 1.501 | 1.502 | 1.504 | 1.510 | 1.520 | 1.540 | 1.601 | 1.705 | 1.920 | 2.625 | 4.000 |       |

| 1.00 | 2.000  | 2.000  | 2.000 | 2.001 | 2.001 | 2.002 | 2.003 | 2.006 | 2.015 | 2.030 | 2.060 | 2.153 | 2.310 | 2.640 | 3.750 | 6.000 |

| 2.00 | 3.000  | 3.000  | 3.000 | 3.001 | 3.001 | 3.003 | 3.005 | 3.010 | 3.025 | 3.050 | 3.101 | 3.255 | 3.520 | 4.080 | 6.000 | 10.00 |

| 5.00 | 6.001  | 6.001  | 6.002 | 6.006 | 6.011 | 6.022 | 6.055 | 6.111 | 6.222 | 6.563 | 7.150 | 8.400 | 12.75 | 22.00 |       |       |

| 10.0 | 11.00  | 11.00  | 11.00 | 11.01 | 11.02 | 11.04 | 11.11 | 11.21 | 11.42 | 12.08 | 13.20 | 15.60 | 24.00 | 42.00 |       |       |

| 20.0 | 21.00  | 21.00  | 21.00 | 21.02 | 21.04 | 21.08 | 21.21 | 21.41 | 21.83 | 23.10 | 25.30 | 30.00 | 46.50 | 82.00 |       |       |

| 50.0 | 51.01  | 51.01  | 51.02 | 51.05 | 51.10 | 51.20 | 51.51 | 52.02 | 53.04 | 56.18 | 61.60 | 73.20 | 114.0 | 202.0 |       |       |

| 100  | 101.0  | 101.0  | 101.0 | 101.1 | 101.2 | 101.4 | 102.0 | 103.0 | 105.1 | 111.3 | 122.1 | 145.2 | 226.5 | 402.0 |       |       |

| 200  | 201.0  | 201.0  | 201.1 | 201.2 | 201.4 | 201.8 | 203.0 | 205.0 | 209.1 | 221.6 | 243.1 | 289.2 | 451.5 | 802.0 |       |       |

图 7

图 8

图 9

图 10

图 11

图 12

图 13

冬 14

图 15

图 16

图 17

图 18

图 19

图 20

图 21

|                |                                                                                     |         |            |

|----------------|-------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 存储器一体型显示元件                                                                          |         |            |

| 公开(公告)号        | <a href="#">CN1366344A</a>                                                          | 公开(公告)日 | 2002-08-28 |

| 申请号            | CN02105240.9                                                                        | 申请日     | 2002-01-18 |

| [标]申请(专利权)人(译) | 夏普株式会社                                                                              |         |            |

| 申请(专利权)人(译)    | 夏普公司                                                                                |         |            |

| 当前申请(专利权)人(译)  | 夏普公司                                                                                |         |            |

| [标]发明人         | 冈本成继                                                                                |         |            |

| 发明人            | 冈本成继                                                                                |         |            |

| IPC分类号         | H01L51/50 G09F9/30 G09G3/00 G09G3/20 G09G3/30 G09G3/32 H01L27/32 H01L27/15 G09F9/33 |         |            |

| CPC分类号         | G09G3/3258 G09G3/2074 G09G2300/0857 G09G2330/021                                    |         |            |

| 代理人(译)         | 郑立柱<br>梁永                                                                           |         |            |

| 优先权            | 2001010868 2001-01-18 JP<br>2001374905 2001-12-07 JP                                |         |            |

| 其他公开文献         | CN1241162C                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                      |         |            |

### 摘要(译)

一种存储器一体型显示元件,在显示元件的各像素中,存储器电路由2个互补型的反相器连接成环状而构成,根据选择期间经选择电路供给的数据电位存储是否点亮有机发光二极管。另一反相器的输出端直接连接于上述有机发光二极管,该反相器的两个TFT驱动该有机发光二极管。由此,即使产生制造偏差等,也能以相同的亮度电平点亮/熄灭有机发光二极管。结果即使因制造偏差等在构成像素的元件的特性中产生偏差,也能以相同亮度电平点亮光学调制元件。