(12) 发明专利申请

(10) 申请公布号 CN 102832228 A

(43) 申请公布日 2012. 12. 19

(21) 申请号 201210299566. X

G09G 3/20(2006. 01)

(22) 申请日 2004. 06. 17

(30) 优先权数据

172009/2003 2003. 06. 17 JP

(62) 分案原申请数据

200410049570. 6 2004. 06. 17

(71) 申请人 株式会社半导体能源研究所

地址 日本神奈川县厚木市

(72) 发明人 山崎舜平 小山润

(74) 专利代理机构 中国专利代理(香港)有限公司 72001

代理人 叶晓勇 王忠忠

(51) Int. Cl.

H01L 27/32(2006. 01)

H01L 27/12(2006. 01)

G09G 3/32(2006. 01)

权利要求书 5 页 说明书 15 页 附图 22 页

(54) 发明名称

显示器件和电子设备

(57) 摘要

一种显示器件，其中降低了由于晶体管特性的改变而引起的亮度改变，并防止了由于电阻值的改变而引起的图像质量退化。本发明包括其沟道部分由非晶半导体或有机半导体构成的晶体管，连接到该晶体管的源电极或漏电极的连接布线，具有包括像素电极、电致发光层和反向电极的叠层结构的发光元件，环绕像素电极端部的绝缘层，和形成在和晶体管的栅电极、连接布线、或像素电极相同的层上的辅助布线。而且，连接布线连接到像素电极，且辅助布线通过提供在绝缘层中的开口部分连接到反向电极。

1. 一种显示器件,包括:

在基板上的晶体管,该晶体管包括源极、漏极和沟道区;

在所述晶体管上的第一绝缘层;

在所述第一绝缘层之上且电连接到所述源极或所述漏极中的一个的连接布线;

在所述第一绝缘层之上且电连接到所述连接布线的像素电极;

在所述第一绝缘层上的辅助布线;

在所述第一绝缘层上的第二绝缘层;

在所述像素电极上且在所述第二绝缘层中的第一开口部分;

在所述辅助布线上且在所述第二绝缘层中的第二开口部分;

在所述像素电极上且在所述第一开口部分中的电致发光层;以及

在所述电致发光层上的反向电极,

其中,所述辅助布线通过所述第二开口部分电连接到所述反向电极,并且

其中,所述连接布线的材料不同于所述像素电极的材料。

2. 根据权利要求 1 所述的显示器件,其中,所述基板包括柔性基板。

3. 根据权利要求 1 所述的显示器件,其中,所述显示器件并入到从由便携式终端、便携式游戏机、目镜类显示器、监视器、摄像机和个人计算机构成的组中选择的一个。

4. 根据权利要求 1 所述的显示器件,还包括在所述反向电极上并与之接触的保护层。

5. 根据权利要求 1 所述的显示器件,其中,所述沟道区包括非晶半导体。

6. 一种显示器件,包括:

在基板上的栅电极;

在所述栅电极上的栅绝缘层;

在所述栅绝缘层之上且具有一个导电型的第一半导体区;

在所述栅绝缘层之上且具有所述一个导电型的第二半导体区;

在所述栅绝缘层之上且在所述第一半导体区和所述第二半导体区之间的沟道区;

在所述第一半导体区和所述第二半导体区之上的第一绝缘层;

在所述第一绝缘层之上且电连接到所述第一半导体区和所述第二半导体区中的一个的连接布线;

在所述第一绝缘层之上且电连接到所述连接布线的像素电极;

在所述第一绝缘层之上的辅助布线;

在所述第一绝缘层之上的第二绝缘层;

在所述像素电极之上且在所述第二绝缘层中的第一开口部分;

在所述辅助布线上且在所述第二绝缘层中的第二开口部分;

在所述像素电极之上且在所述第一开口部分中的电致发光层;以及

在所述电致发光层上的反向电极,

其中,所述辅助布线通过所述第二开口部分电连接到所述反向电极,并且

其中,所述连接布线的材料不同于所述像素电极的材料。

7. 根据权利要求 6 所述的显示器件,其中,所述基板包括柔性基板。

8. 根据权利要求 6 所述的显示器件,其中,所述显示器件并入到从由便携式终端、便携式游戏机、目镜类显示器、监视器、摄像机和个人计算机构成的组中选择的一个。

9. 根据权利要求 6 所述的显示器件, 还包括在所述反向电极上并与其接触的保护层。

10. 根据权利要求 6 所述的显示器件, 其中, 所述沟道区包括非晶半导体。

11. 一种显示器件, 包括:

在基板之上的栅电极;

在所述栅电极之上的栅绝缘层;

在所述栅绝缘层之上的第一 N 型半导体区;

在所述栅绝缘层之上的第二 N 型半导体区;

在所述栅绝缘层之上且在所述第一 N 型半导体区和所述第二 N 型半导体区之间的沟道区;

在所述第一 N 型半导体区和所述第二 N 型半导体区之上的第一绝缘层;

在所述第一绝缘层之上且电连接到所述第一 N 型半导体区和所述第二 N 型半导体区中的一个的连接布线;

在所述第一绝缘层之上且电连接到所述连接布线的像素电极;

在所述第一绝缘层之上的辅助布线;

在所述第一绝缘层之上的第二绝缘层;

在所述像素电极之上且在所述第二绝缘层中的第一开口部分;

在所述辅助布线之上且在所述第二绝缘层中的第二开口部分;

在所述像素电极之上且在所述第一开口部分中的电致发光层; 以及

在所述电致发光层上的反向电极,

其中, 所述辅助布线通过所述第二开口部分电连接到所述反向电极, 并且

其中, 所述连接布线的材料不同于所述像素电极的材料。

12. 根据权利要求 11 所述的显示器件, 其中, 所述基板包括柔性基板。

13. 根据权利要求 11 所述的显示器件, 其中, 所述显示器件并入到从由便携式终端、便携式游戏机、目镜类显示器、监视器、摄像机和个人计算机构成的组中选择的一个。

14. 根据权利要求 11 所述的显示器件, 还包括在所述反向电极上并与其接触的保护层。

15. 根据权利要求 11 所述的显示器件, 其中, 所述沟道区包括非晶半导体。

16. 一种显示器件, 包括:

在基板之上的栅电极;

在所述栅电极之上的栅绝缘层;

在所述栅绝缘层之上且具有一个导电型的第一半导体区;

在所述栅绝缘层之上且具有所述一个导电型的第二半导体区;

在所述栅绝缘层之上且在所述第一半导体区和所述第二半导体区之间的沟道区;

在所述第一半导体区和所述第二半导体区之上的第一绝缘层;

在所述第一绝缘层之上且电连接到所述第一半导体区和所述第二半导体区中的一个的连接布线;

在所述第一绝缘层之上且电连接到所述连接布线的像素电极;

在所述第一绝缘层之上的辅助布线;

在所述第一绝缘层之上的第二绝缘层;

在所述像素电极之上且在所述第二绝缘层中的第一开口部分；

在所述辅助布线之上且在所述第二绝缘层中的第二开口部分；

在所述像素电极之上且在所述第一开口部分中的电致发光层；以及

在所述电致发光层上的反向电极，

其中，所述辅助布线通过所述第二开口部分电连接到所述反向电极，

其中，所述反向电极延伸到所述第二开口部分中以提供在所述辅助布线上的所述反向电极，并且

其中，所述连接布线的材料不同于所述像素电极的材料。

17. 根据权利要求 16 所述的显示器件，其中，所述基板包括柔性基板。

18. 根据权利要求 16 所述的显示器件，其中，所述显示器件并入到从由便携式终端、便携式游戏机、目镜类显示器、监视器、摄像机和个人计算机构成的组中选择的一个。

19. 根据权利要求 16 所述的显示器件，还包括在所述反向电极上并与之接触的保护层。

20. 根据权利要求 16 所述的显示器件，其中，所述沟道区包括非晶半导体。

21. 一种显示器件，包括：

在基板之上的晶体管，该晶体管包括源极、漏极、沟道区和栅绝缘层；

在所述栅绝缘层之上的辅助布线；

在所述辅助布线和所述晶体管之上的第一绝缘层；

在所述第一绝缘层之上且电连接到所述源极和所述漏极中的一个的连接布线；

在所述第一绝缘层之上且电连接到所述连接布线的像素电极；

环绕所述像素电极的端部并在其之上的第二绝缘层；

在所述像素电极之上的电致发光层；

在所述电致发光层上的反向电极；以及

在所述辅助布线之上且在所述第一绝缘层和所述第二绝缘层之中的开口，

其中，所述辅助布线通过所述开口电连接到所述反向电极，并且

其中，所述连接布线的材料不同于所述像素电极的材料。

22. 根据权利要求 21 所述的显示器件，其中，所述基板包括柔性基板。

23. 根据权利要求 21 所述的显示器件，其中，所述显示器件并入到从由便携式终端、便携式游戏机、目镜类显示器、监视器、摄像机和个人计算机构成的组中选择的一个。

24. 根据权利要求 21 所述的显示器件，还包括在所述反向电极上并与之接触的保护层。

25. 根据权利要求 21 所述的显示器件，其中，所述沟道区包括非晶半导体。

26. 一种显示器件，包括：

在基板之上的栅电极；

在所述栅电极之上的栅绝缘层；

在所述栅绝缘层之上且具有一个电导型的第一半导体区；

在所述栅绝缘层之上且具有所述一个电导型的第二半导体区；

在所述栅绝缘层之上且在所述第一半导体区和所述第二半导体区之间的沟道区；

在所述栅绝缘层之上的辅助布线；

在所述辅助布线、所述第一半导体区和所述第二半导体区之上的第一绝缘层；

在所述第一绝缘层之上且电连接到所述第一半导体区和所述第二半导体区中的一个的连接布线；

在所述第一绝缘层之上且电连接到所述连接布线的像素电极；

环绕所述像素电极的端部并在其上的第二绝缘层；

在所述像素电极之上的电致发光层；

在所述电致发光层上的反向电极；以及

在所述辅助布线之上且在所述第一绝缘层和所述第二绝缘层中的开口，

其中，所述辅助布线通过所述开口电连接到所述反向电极，并且

其中，所述连接布线的材料不同于所述像素电极的材料。

27. 根据权利要求 26 所述的显示器件，其中，所述基板包括柔性基板。

28. 根据权利要求 26 所述的显示器件，其中，所述显示器件并入到从由便携式终端、便携式游戏机、目镜类显示器、监视器、摄像机和个人计算机构成的组中选择的一个。

29. 根据权利要求 26 所述的显示器件，还包括在所述反向电极上并与之接触的保护层。

30. 根据权利要求 26 所述的显示器件，其中，所述沟道区包括非晶半导体。

31. 一种显示器件，包括：

在基板之上的栅电极；

在所述栅电极之上的栅绝缘层；

在所述栅绝缘层之上的第一 N 型半导体区；

在所述栅绝缘层之上的第二 N 型半导体区；

在所述栅绝缘层之上且在所述第一 N 型半导体区和所述第二 N 型半导体区之间的沟道区；

在所述栅绝缘层之上的辅助布线；

在所述辅助布线、所述第一 N 型半导体区和所述第二 N 型半导体区之上的第一绝缘层；

在所述第一绝缘层之上且电连接到所述第一 N 型半导体区和所述第二 N 型半导体区中的一个的连接布线；

在所述第一绝缘层之上且电连接到所述连接布线的像素电极；

环绕所述像素电极的端部并在其上的第二绝缘层；

在所述像素电极之上的电致发光层；

在所述电致发光层上的反向电极；以及

在所述辅助布线之上且在所述第一绝缘层和所述第二绝缘层中的开口，

其中，所述辅助布线通过所述开口电连接到所述反向电极，并且

其中，所述连接布线的材料不同于所述像素电极的材料。

32. 根据权利要求 31 所述的显示器件，其中，所述基板包括柔性基板。

33. 根据权利要求 31 所述的显示器件，其中，所述显示器件并入到从由便携式终端、便携式游戏机、目镜类显示器、监视器、摄像机和个人计算机构成的组中选择的一个。

34. 根据权利要求 31 所述的显示器件，还包括在所述反向电极上并与之接触的保护

层。

35. 根据权利要求 31 所述的显示器件，其中，所述沟道区包括非晶半导体。

36. 一种显示器件，包括：

在基板之上的栅电极；

在所述栅电极之上的栅绝缘层；

在所述栅绝缘层之上且具有一个电导型的第一半导体区；

在所述栅绝缘层之上且具有所述一个电导型的第二半导体区；

在所述栅绝缘层之上且在所述第一半导体区和所述第二半导体区之间的沟道区；

在所述栅绝缘层之上的辅助布线；

在所述辅助布线、所述第一半导体区和所述第二半导体区之上的第一绝缘层；

在所述第一绝缘层之上且电连接到所述第一半导体区和所述第二半导体区中的一个的连接布线；

在所述第一绝缘层之上且电连接到所述连接布线的像素电极；

环绕所述像素电极的端部并在其上的第二绝缘层；

在所述像素电极之上的电致发光层；

在所述电致发光层上的反向电极；以及

在所述辅助布线之上且在所述第一绝缘层和所述第二绝缘层之中的开口，

其中，所述辅助布线通过所述开口电连接到所述反向电极，

其中，所述反向电极延伸到所述开口以提供在所述辅助布线上的所述反向电极，并且

其中，所述连接布线的材料不同于所述像素电极的材料。

37. 根据权利要求 36 所述的显示器件，其中，所述基板包括柔性基板。

38. 根据权利要求 36 所述的显示器件，其中，所述显示器件并入到从由便携式终端、便携式游戏机、目镜类显示器、监视器、摄像机和个人计算机构成的组中选择的一个。

39. 根据权利要求 36 所述的显示器件，还包括在所述反向电极上并与之接触的保护层。

40. 根据权利要求 36 所述的显示器件，其中，所述沟道区包括非晶半导体。

## 显示器件和电子设备

### 技术领域

[0001] 本发明涉及包括自发光元件和其沟道部分由非晶半导体或有机半导体形成的晶体管的显示器件。

### 背景技术

[0002] 近年来,包括发光元件的显示器件已经得到了积极的发展。除了常规液晶显示器件的优势之外,发光显示器件具有诸如响应快、优良的动态显示和宽视角的特征。因此,作为下一代平板显示器,发光显示器件吸引了众多的注意。

[0003] 发光显示器件包括多个像素,每个像素具有发光元件和至少两个晶体管。在每个像素中,与发光元件串联连接的晶体管控制发光元件的发光或不发光。对于晶体管,在很多情况下采用具有高场效应迁移率的多晶半导体(多晶硅)。发光元件具有其中将电致发光层夹在一对电极之间的结构。具体来说,在构图的第一导电层(第一电极)上形成电致发光层,然后形成第二导电层(第二电极)以便覆盖电致发光层的整个表面。

### 发明内容

[0004] 使用多晶硅的晶体管由于晶界中的晶体缺陷而易于引起特性的变化。因此,即使输入相同的信号电压时,每个像素中晶体管的漏电流也会不同,造成亮度的变化。

[0005] 由于前述原因,本发明提供一种显示器件,其中抑制了由晶体管特性的变化而引起亮度的变化。

[0006] 优选的是,对形成在电致发光层上的第二导电层(第二电极)进行加热以降低电阻。然而,电致发光层具有低的耐热性且不能承受高的热处理。因此,由于不同的电阻值,施加到一对电极之间的电压在发光元件的边缘和中心之间也不同,从而引起图像质量退化。

[0007] 由于前述原因,本发明提供一种显示器件,其中防止了由于电阻值不同引起的图像质量退化。

[0008] 为了解决前述问题,本发明采取以下措施。

[0009] 根据本发明的显示器件包括受控于晶体管的发光元件,该晶体管的沟道部分由非晶半导体(典型的是非晶硅,a-Si :H)或有机半导体构成。由于这种晶体管具有很小的场效应迁移率等的变化,因此可以抑制由于晶体管特性的变化而引起的显示器件的亮度变化。而且,非晶半导体适于制造从几英寸到几十英寸尺寸范围的大平板,并且由于没有结晶步骤并需要少量的掩模,其制造工艺是具有成本效益的。

[0010] 根据本发明的显示器件包括辅助导电层(布线),其连接到形成在电致发光层上的导电层。结果,可以在没有热处理的情况下降低导电层的电阻,并由此可以防止显示器件图像质量的退化。由于随着平板尺寸增大,电阻值成为问题,因此通过采用本发明可以非常有效地制造具有几十英寸尺寸的大平板。

[0011] 根据本发明的显示器件包括基板,其包括像素部分和排列在像素部分外围的驱动器电路,以及附着在基板上的驱动器 IC。像素部分包括包含夹在一对电极之间的发光材料

的发光元件,以及其沟道部分由非晶半导体构成的多个晶体管。形成在基板上的驱动器电路包括其沟道部分由非晶半导体构成的N型晶体管(下文中有时表示为a-Si:HTFT)和其沟道部分由有机半导体构成的P型晶体管(下文中有时表示为有机TFT)。有机TFT对应于包括诸如并五苯的低分子量有机化合物、诸如PEDOT(聚噻吩)和PPV(聚亚苯基亚乙烯基)的高分子量有机化合物等的晶体管。a-Si:HTFT和有机TFT可以形成在和像素部分的相同基板上,并可以配置为使用该CMOS电路作为单元电路、移位寄存器、缓冲器等。此外,可以仅用N型晶体管或P型晶体管形成驱动器电路。在这种情况下,可以仅用a-Si:HTFT或有机TFT形成驱动器电路。

[0012] 根据本发明的显示器件包括发光元件,其包括夹在连接到阳极线的第一电极和连接到阴极线的第二电极之间的发光材料。显示器件还包括其沟道部分由非晶半导体构成的晶体管。显示器件还包括反向偏置电压施加电路,其转换阳极线和阴极线彼此的电位以向发光元件施加反向偏置电压。根据这种结构,可以防止发光元件随时间退化,从而得到具有提高的可靠性的显示器件。

[0013] 根据本发明的显示器件包括其包含夹在一对电极之间的发光材料的发光元件、其栅电极连接到具有恒定电位的第一电源线上的第一晶体管、和其栅电极连接到信号线的第二晶体管。发光元件、第一晶体管和第二晶体管串联连接在具有和低电位电压相同电位的第二电源和具有和高电位电压相同电位的第三电源之间。而且,每个第一晶体管和第二晶体管具有由非晶半导体构成的沟道部分。在这种显示器件中,第二晶体管工作在线性区,由此,在发光元件中流过的电流量不受第一晶体管 $V_{GS}$ 的微小变化的影响。换言之,在发光元件中流过的电流量通过在饱和区工作的第一晶体管确定。因此,根据具有前述结构的本发明,可以提供一种显示器件,其中抑制了由于晶体管特性的变化而引起的亮度变化,并提高了图像质量。

[0014] 通过采用前述结构,本发明可以提供一种显示器件,其中抑制了由于晶体管特性的变化而引起的亮度变化。而且,在根据本发明的显示器件中,可以无需热处理而降低导电层的电阻,并防止图像质量退化。此外,根据本发明的显示器件包括其沟道部分由非晶半导体构成的晶体管,由此可以实现大尺寸且廉价的显示器件。

## 附图说明

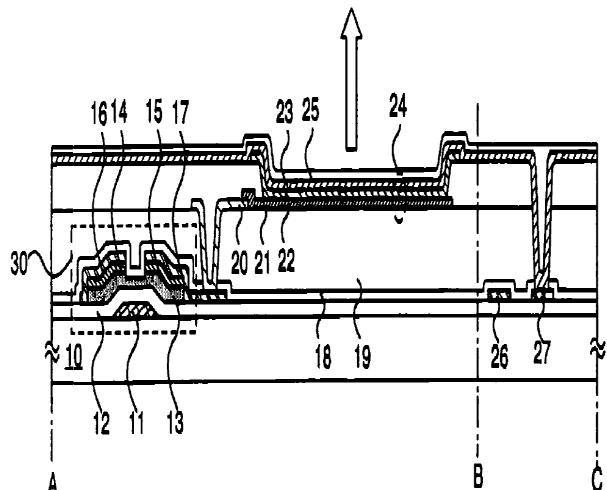

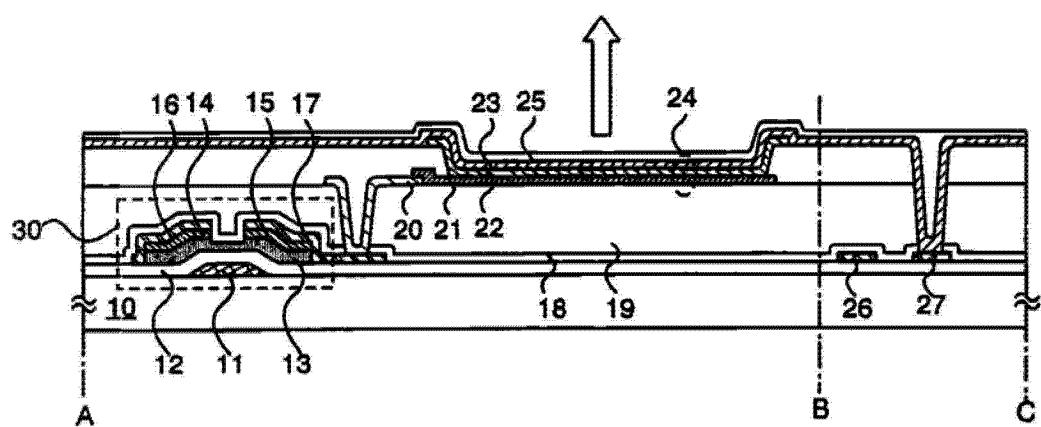

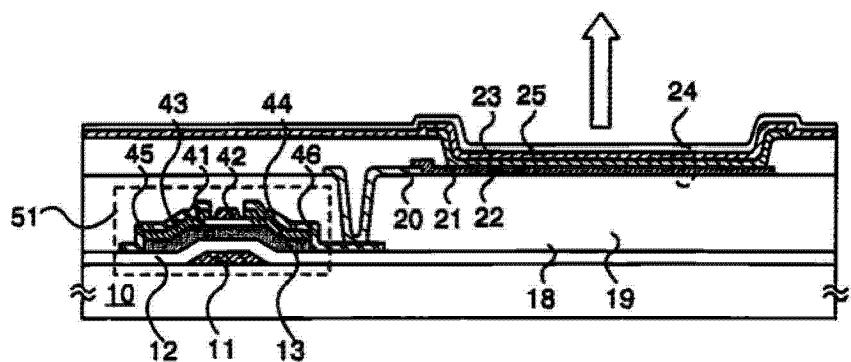

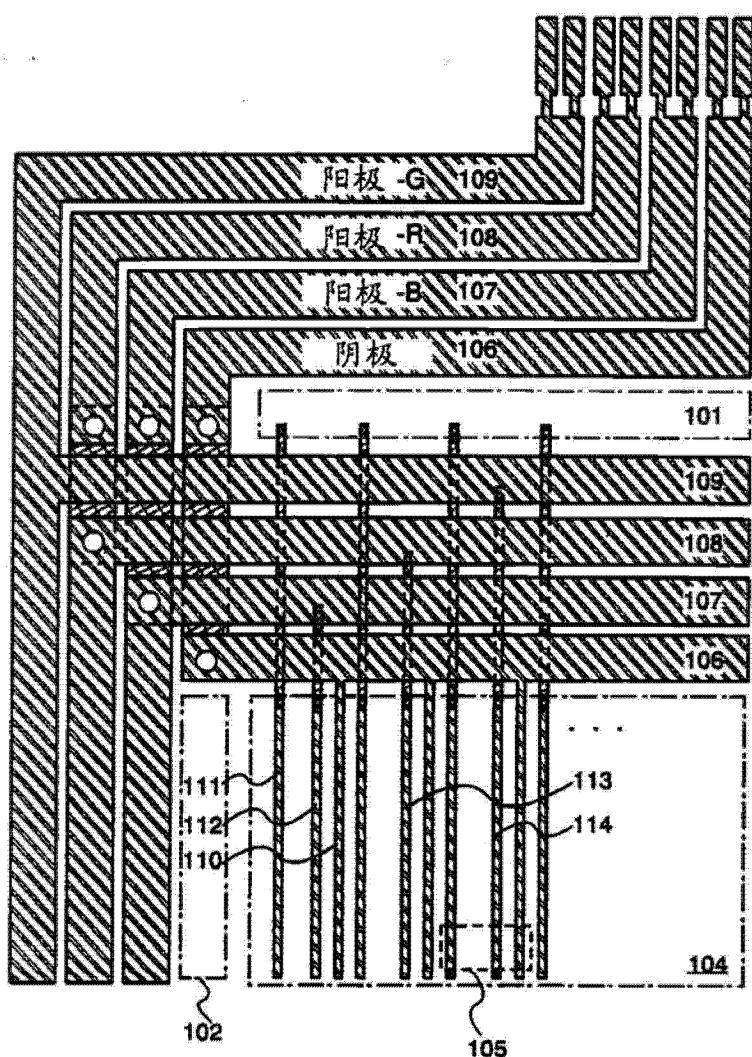

[0015] 图1A至1C是使用非晶半导体用于沟道部分的晶体管(沟道保护型和沟道蚀刻型)、发光元件和连接到发光元件其中一个电极上的辅助布线的横截面图。

[0016] 图2是使用非晶半导体用于沟道部分的晶体管(双栅极型)、发光元件和连接到发光元件其中一个电极上的辅助布线的横截面图。

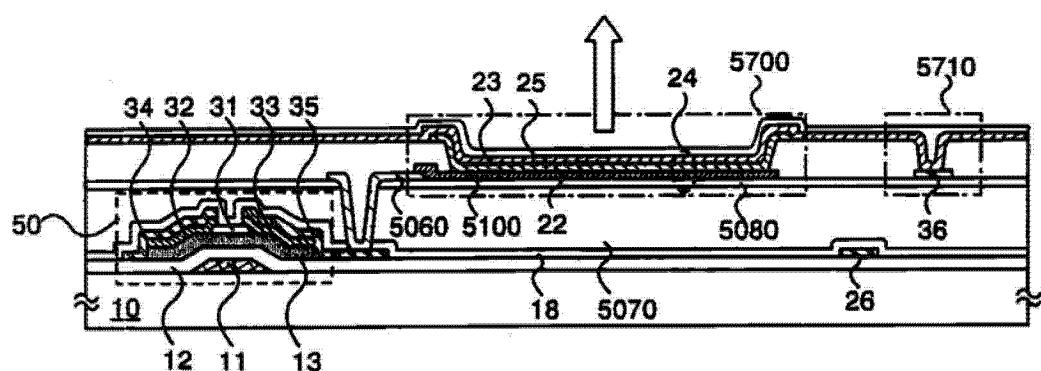

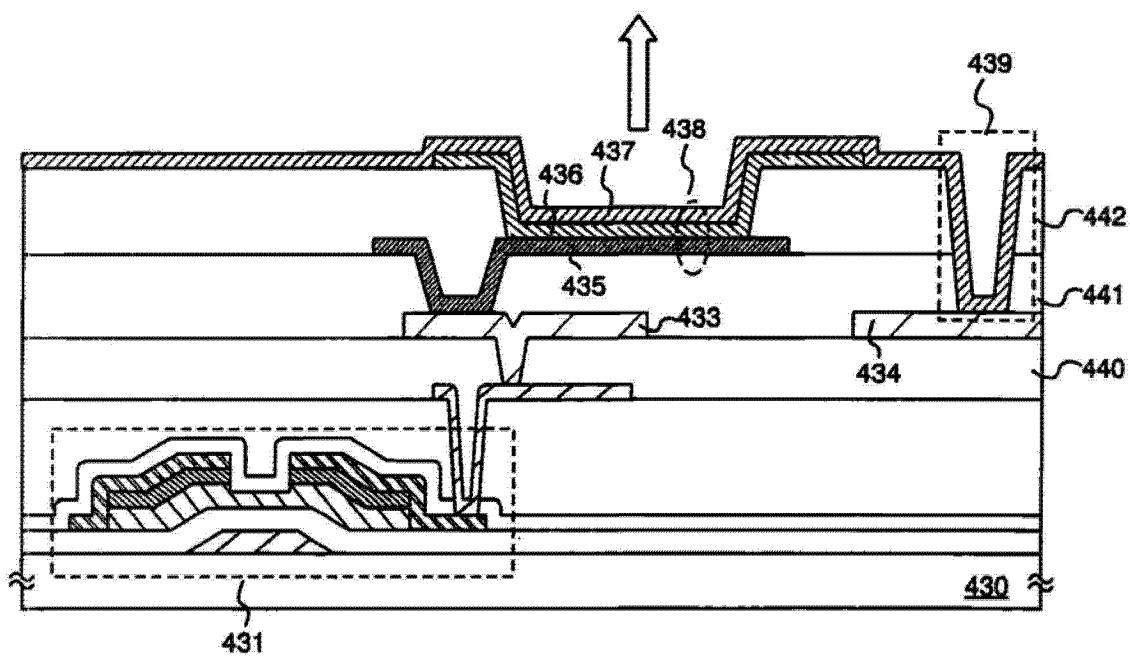

[0017] 图3A和3B是使用非晶半导体用于沟道部分的晶体管、发光元件和连接到发光元件其中一个电极上的辅助布线的横截面图。

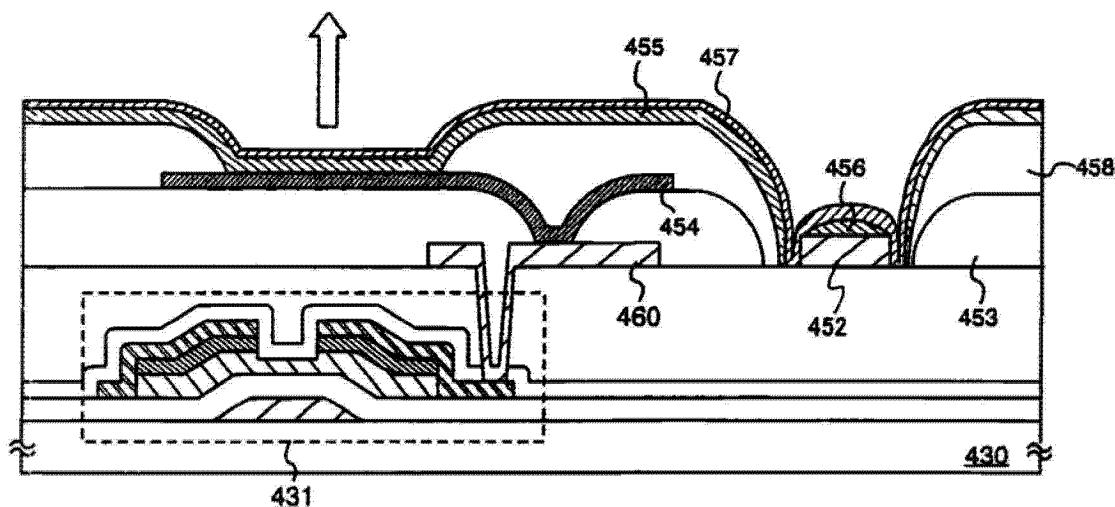

[0018] 图4A和4B是示出阳极线、阴极线和辅助布线排列的平板的顶视图。

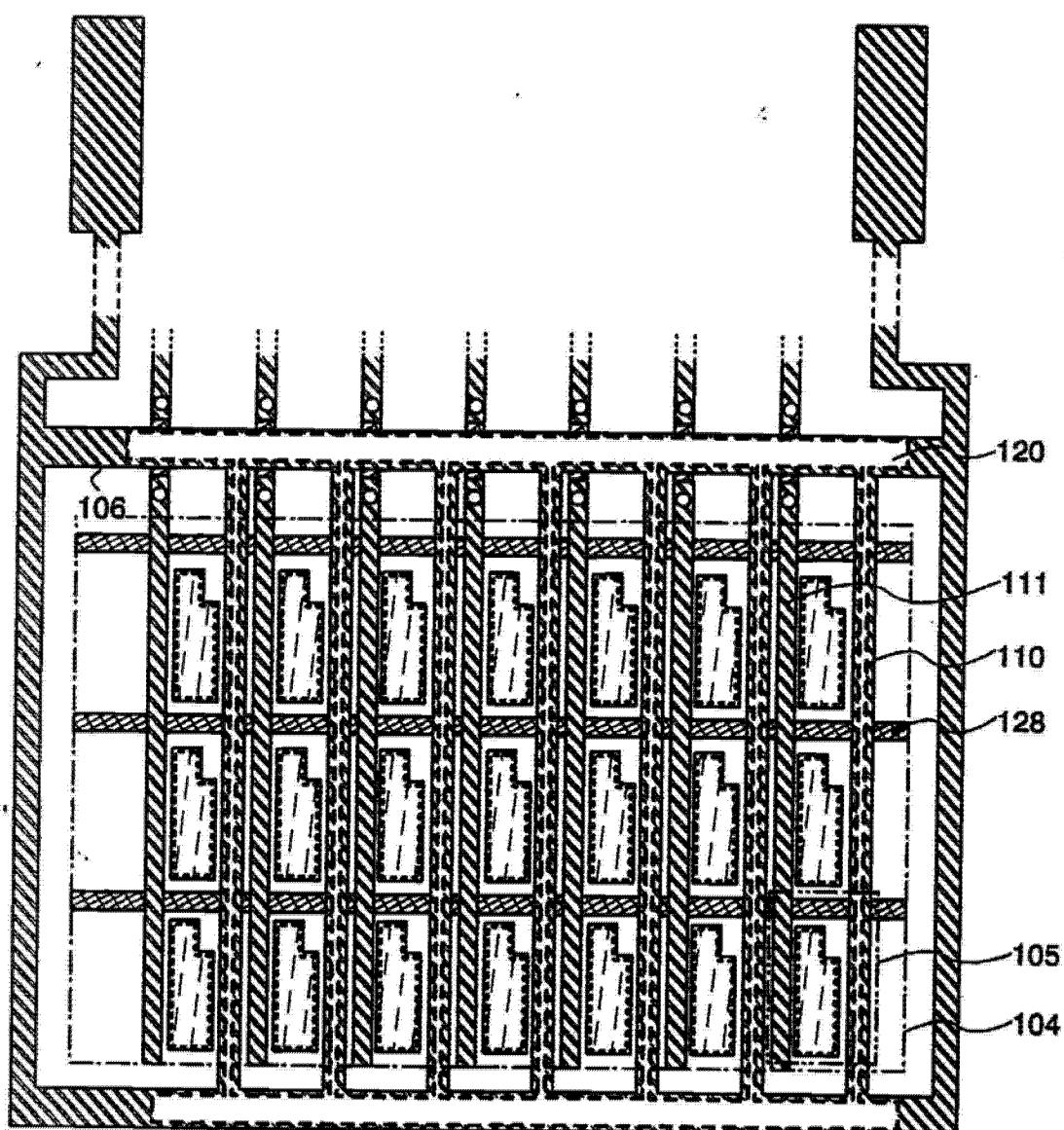

[0019] 图5是示出开口部分和阳极线、阴极线以及辅助布线的排列的图。

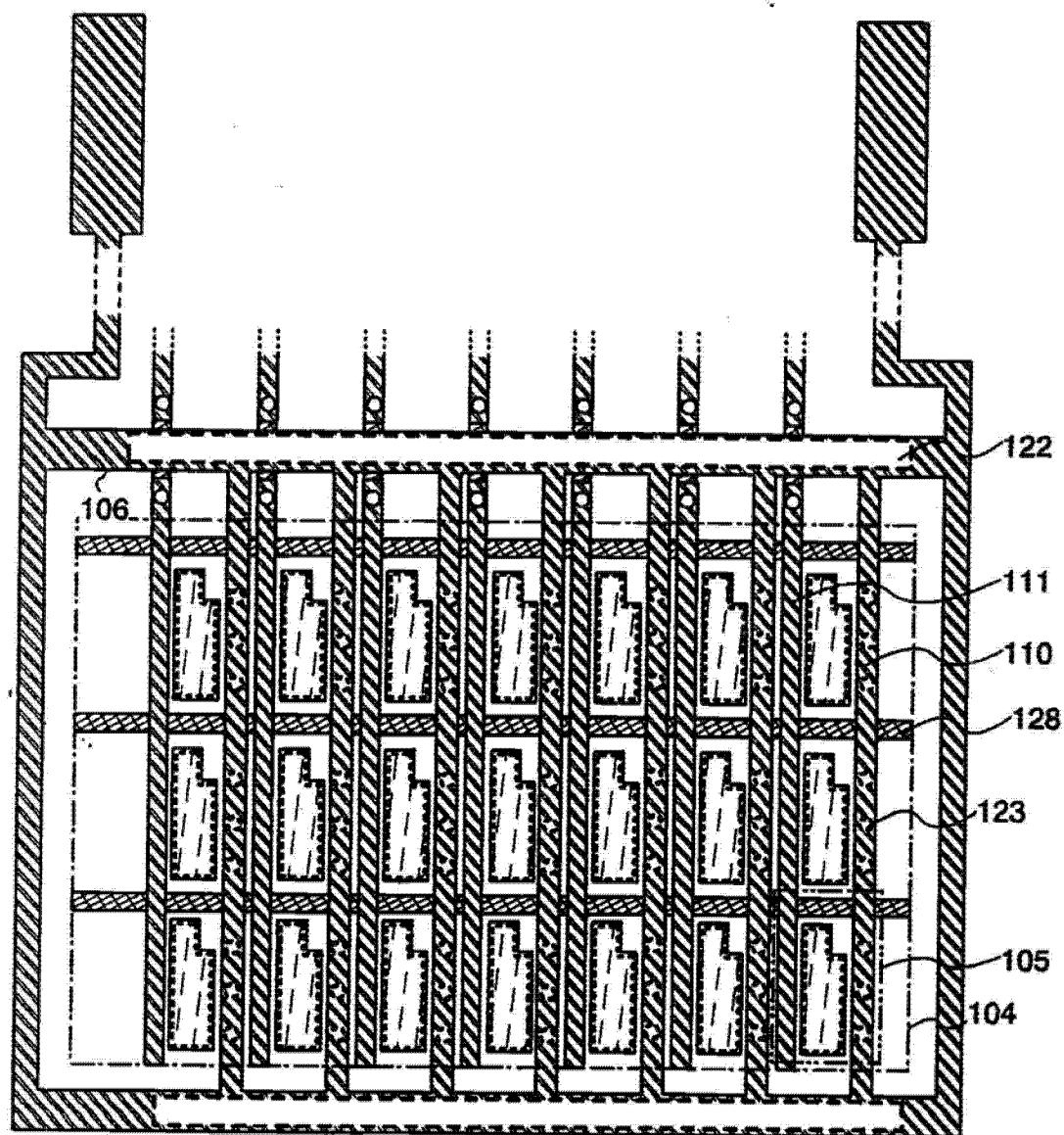

[0020] 图6是示出开口部分和阳极线、阴极线以及辅助布线的排列的图。

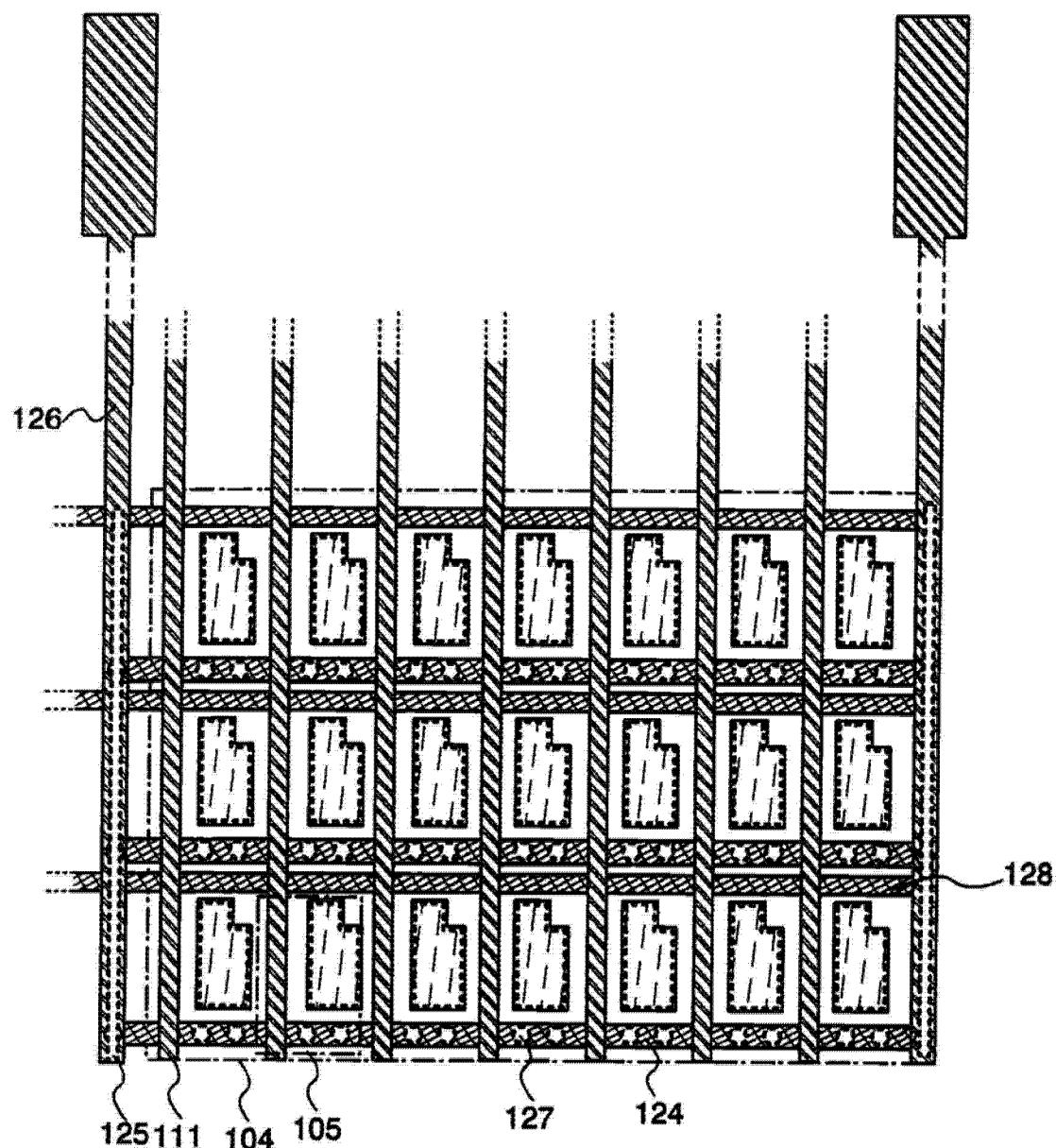

[0021] 图7是示出开口部分和阳极线、阴极线以及辅助布线的排列的图。

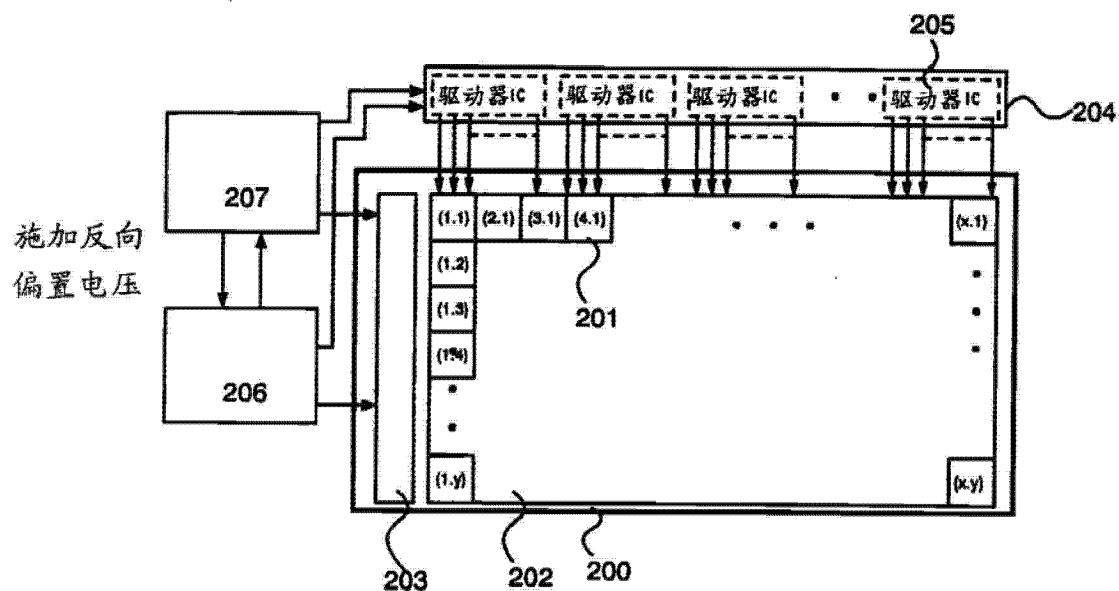

[0022] 图8A和8B是安装驱动器IC的平板的顶视图。

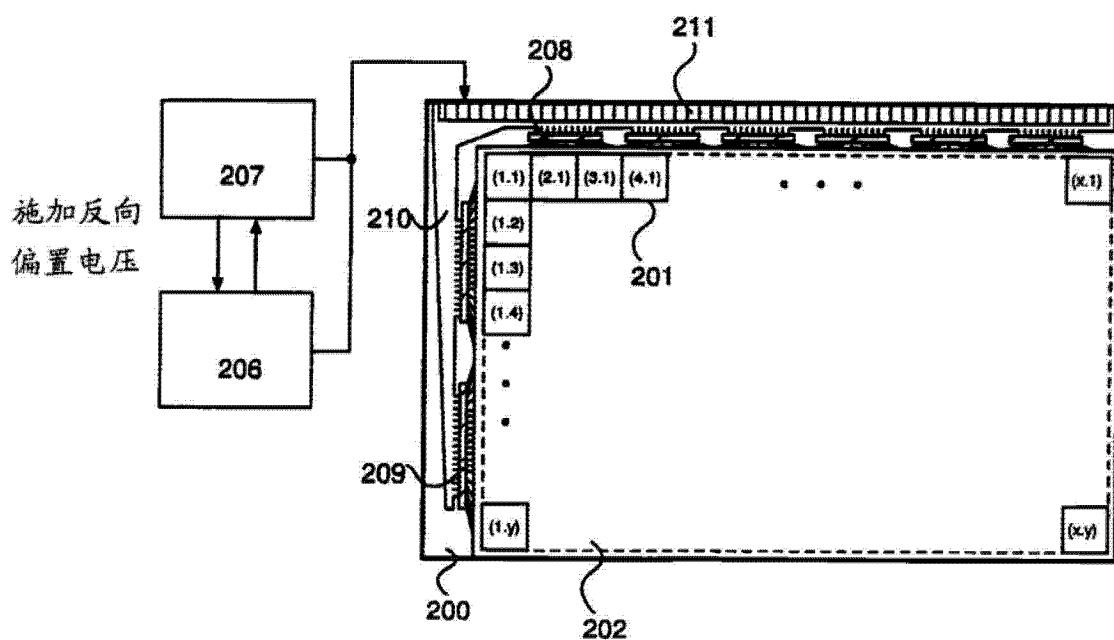

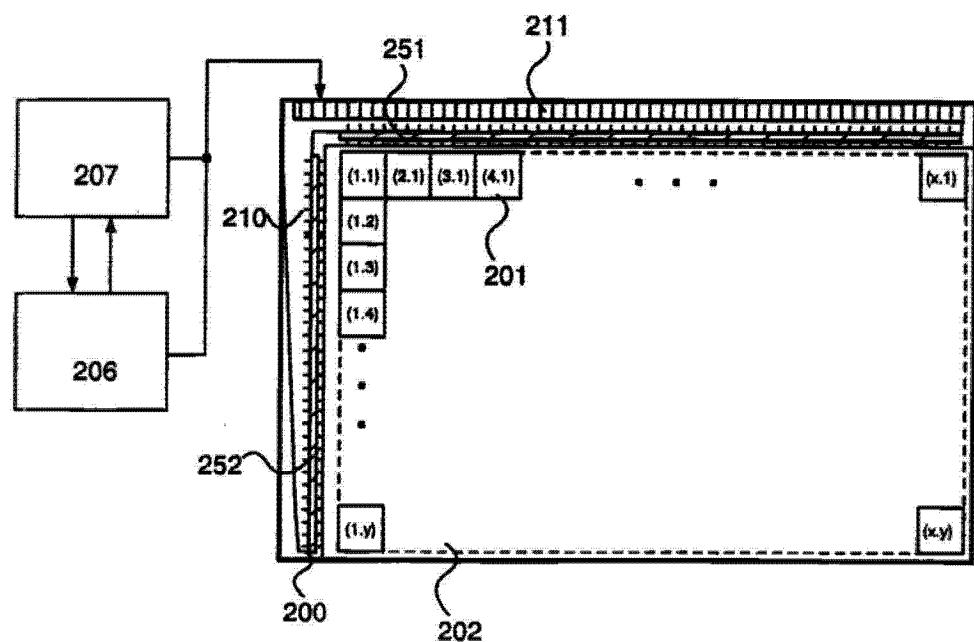

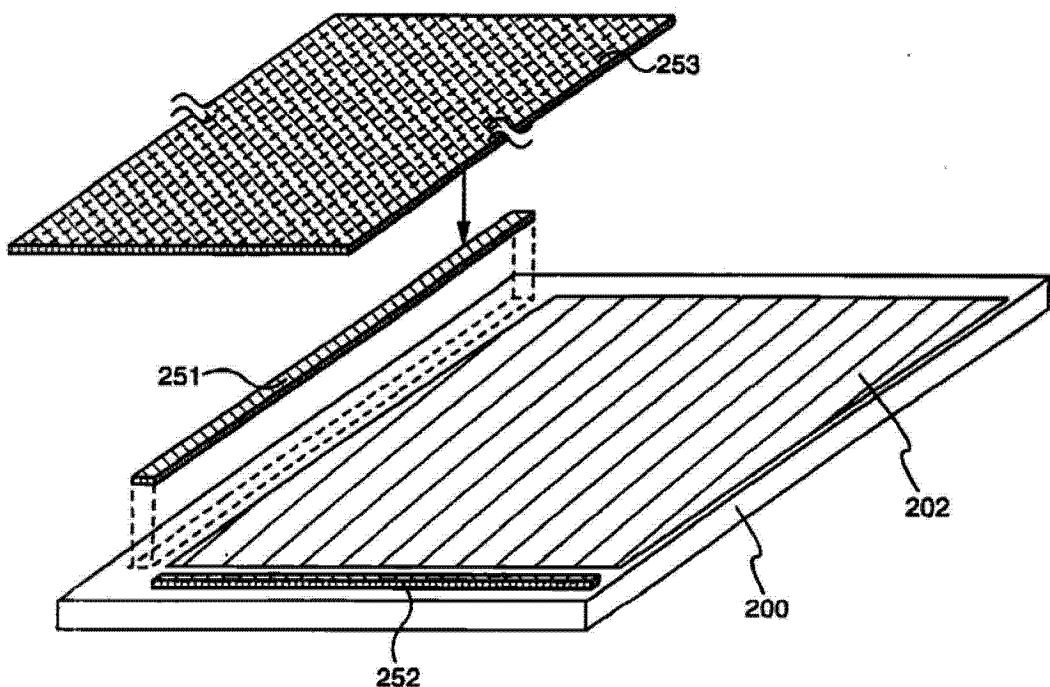

- [0023] 图 9A 是安装线性驱动器 IC 的平板的顶视图,且图 9B 是其透视图。

- [0024] 图 10A 示出了等效电路。

- [0025] 图 10B 是用有机晶体管和 a-Si 晶体管形成的 CMOS 电路的横截面图。

- [0026] 图 11A 至 11F 是包括发光元件和用非晶半导体用于沟道部分的晶体管的像素的电路图。

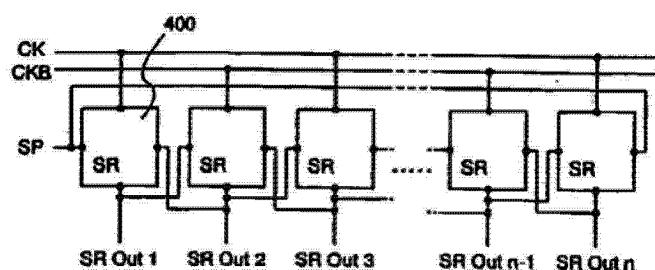

- [0027] 图 12A 和 12B 是仅用 N 型晶体管构成的移位寄存器的电路图。

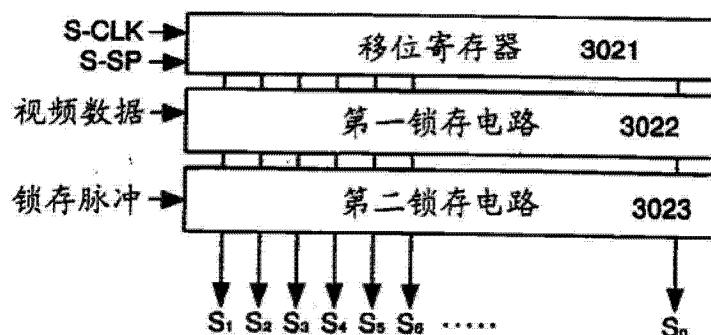

- [0028] 图 13A 和 13B 是表示时间灰度级的时序图。

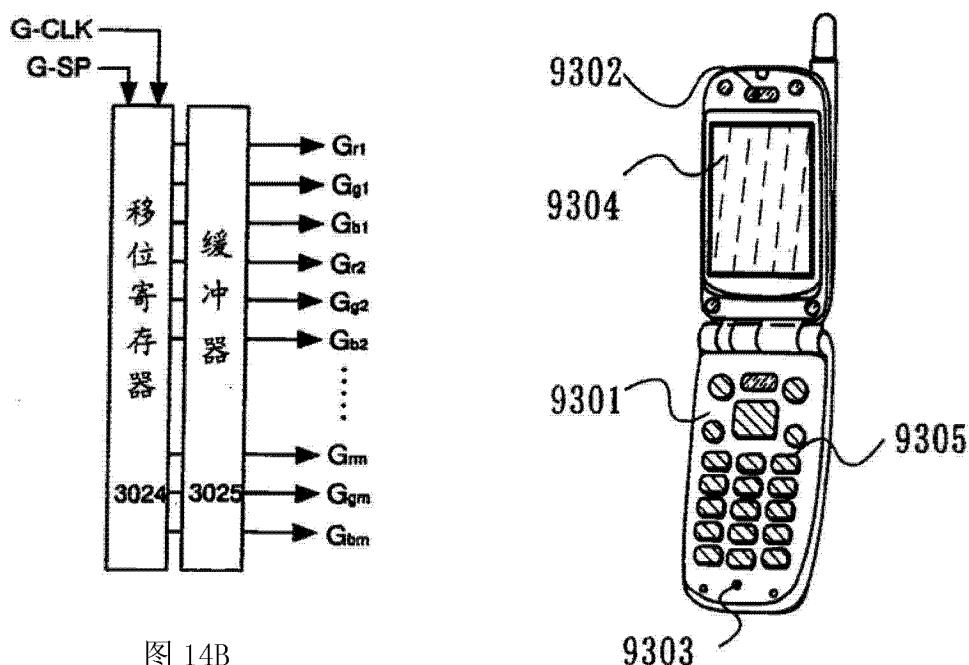

- [0029] 图 14A 和 14B 是表示信号线驱动器电路和扫描线驱动器电路的结构的示意图。

- [0030] 图 15A 至 15D 是表用本发明的电子设备的图。

- [0031] 图 16A 至 16D 是采用本发明的电子设备的图。

- [0032] 图 17A 至 17D 是阈值补偿电路的示意图。

- [0033] 图 18A 至 18D 是发光元件叠层结构的图。

- [0034] 图 19A 和 19B 是发光元件叠层结构的图。

- [0035] 图 20 是像素电路(3TFT/ 单元)的版图。

- [0036] 图 21 是像素电路(3TFT/ 单元)的版图。

- [0037] 图 22 是像素电路(4TFT/ 单元)的版图。

- [0038] 图 23 是像素电路(4TFT/ 单元)的版图。

## 具体实施方式

### 实施方式 1

[0040] 参考图 4A 和 4B,阐释了平板上布线的排列,特别是具有和高电位电压 VDD 相同电位的电源线(下文称为阳极线)和具有和低电位电压 VSS 相同电位的电源线(下文称为阴极线)的排列。要指出的是,图 4A 和 4B 仅示出了像素部分 104 中排列成列的布线。

[0041] 图 4A 是包括基板 100 的平板的顶视图。在基板 100 上,设置其中排列成矩阵的多个像素 105 的像素部分 104、排列在像素部分 104 外围的信号线驱动器电路 101、以及扫描线驱动器电路 102 和 103。驱动器电路的数目没有专门的限制,并且可以根据像素 105 的配置而改变。而且,驱动器电路不必整体地形成在基板 100 上,并且可以通过 COG 等将驱动器 IC 附着在基板 100 上。

[0042] 将像素部分 104 中排列成列的信号线 111 连接到信号线驱动器电路 101。并且,将排列成列的电源线 112 至 114 连接到阳极线 107 至 109 的任何一个。类似地,将排列成列的辅助布线 110 连接到阴极线 106 上。将阳极线 107 至 109 和阴极线 106 引导在像素部分 104 和排列在其外围的驱动器电路周围,并连接到 FPC 的端子上。

[0043] 阳极线 107 至 109 中的每一个与每个 RGB 相对应。当在阳极线 107 至 109 的每一个上施加不同的电位时,可以补偿每种颜色之间亮度的变化。也就是说,通过使用多个阳极线,可以解决即使施加相同电流时,由每种颜色中发光元件的电致发光层的电流密度差异引起每种颜色中亮度变化的问题。要指出的是,这里将电致发光层划分成 RGB 的颜色,但本发明不限于此。当不考虑通过每个像素中的电流密度差异的方法来显示单色图像或显示彩色图像时,例如,通过使用白色发光元件与滤色器组合,则不需要多个阳极线且单一信号阳极线就足够了。

[0044] 图 4B 是简单表示掩模版图的示意图。阳极线 107 至 109 以及阴极线 106 排列在信号线驱动器电路 101 周围，并且阳极线 107 至 109 连接到像素部分 104 中排列成列的电源线 112 至 114。如图 4B 所示，阴极线 106 和辅助布线 110 形成在相同的导电层上。

[0045] 形成阴极线 106 和辅助布线 110 之后，形成功能元件的第一导电层(第一电极)，然后在其上形成绝缘层(也称为堤(bank))。随后，在位于阴极线 106 和辅助布线 110 上的绝缘层中形成开口部分。开口部分暴露阴极线 106 和辅助布线 110，此时形成电致发光层。选择性地形成电致发光层以便不覆盖位于阴极线 106 和辅助布线 110 上的开口部分。然后，形成第二导电层(第二电极)以便覆盖整个电致发光层、阴极线 106 和辅助布线 110。根据这些步骤，将第二导电层电连接到阴极线 106 和辅助布线 110 上，这是本实施方式的重要特征之一。根据这个特征，可以降低形成以便覆盖电致发光层的第二导电层的电阻，因此，可以防止由于第二导电层的电阻值引起的图像质量退化。由于随着平板尺寸增大电阻值成为问题，因此这一特征在制造具有几十英寸尺寸的大平板中非常有效。

[0046] 虽然在本实施方式中将第二导电层连接到阴极线，但是本发明不限于此。可以将第二导电层连接到阳极线上，并且在这种情况下设置发光元件的反向电极作为阳极。

[0047] 而且，辅助布线 110 不必如图 4A 和 4B 所示形成在和排列成列的信号线相同的层上，且可以形成在和排列成行的扫描线相同的层上。可以成列地以点状或线形、或者以点状和线形提供在辅助电极 110 和第二导电层之间形成接触(连接)的开口部分。也可以成行地以点状或线形、或者以点状和线形提供。它们的一些示例在下文中示出，并参考图 5 至 7 描述其掩模版图。要指出的是，图 5 至 7 是简化图，其中像素 105 仅包括像素电极且未示出电源线 112。

[0048] 参考图 5，阐释了其中在相同导电层上形成辅助布线 110 和信号线 111、且通过以线形形成的开口部分 120 将辅助布线 110 连接到第二导电层的结构。在图 5 中，像素部分 104 包括排列成矩阵的多个像素 105，以及排列成列的信号线 111 和辅助布线 110，以及排列成行的扫描线 128。辅助布线 110 连接到阴极线 106。要指出的是，虽然辅助布线 110 和阴极线 106 形成在相同的导电层上，但在这里将排列在像素部分 104 中的布线称为辅助布线 110，而将排列在其他区域中的布线成为阴极线 106。

[0049] 线形开口部分 120 形成在辅助布线 110 和阴极线 106 上。辅助布线 110 和阴极线 106 通过开口部分 120 连接到第二导电层。在这种情况下，辅助布线 110 通过线形开口部分 120 连接到第二导电层。

[0050] 参考图 6，下文阐释了其中在阴极线 106 上形成线形开口部分 122、并在辅助布线 110 上形成点状开口部分 123 的结构。该结构与图 5 中所示的不同在于，通过点状开口部分 123 将辅助布线 110 连接到第二导电层。

[0051] 参考图 7，下文阐释了其中在相同导电层上形成辅助布线 124 和扫描线 128、并通过点状开口部分 127 将辅助布线 124 连接到第二布线的结构。在图 7 中，像素部分 104 包括排列成矩阵的多个像素 105，以及排列成列的信号线 111、排列成行的扫描线 128 和辅助布线 124。辅助布线 124 连接到阴极线 126。辅助布线 124 和阴极线 126 形成在不同导电层上并通过开口部分 127 相互连接。

[0052] 线形开口部分 125 形成在阴极线 126 之上，点状开口部分 127 形成在辅助布线 124 之上。阴极线 126 和辅助布线 124 通过这些开口部分 125 和 127 连接到第二导电层。在这

种情况下,辅助布线 124 通过点状开口部分 127 连接到第二导电层。

[0053] 如上所述,辅助布线可以形成在和排列成列的布线(例如信号线)相同的导电层上,如图 5 和 6 所示;或者可以形成在和排列成行的布线(例如扫描线)相同的导电层上,如图 7 所示。这些结构不需要额外的掩模等,因此,可以避免诸如生产成本增加和可靠性下降的问题。而且,在辅助布线和第二导电层之间形成接触的点状开口部分排列在像素边缘的情况下,可以抑制孔径比的降低而得到更明亮的图像。

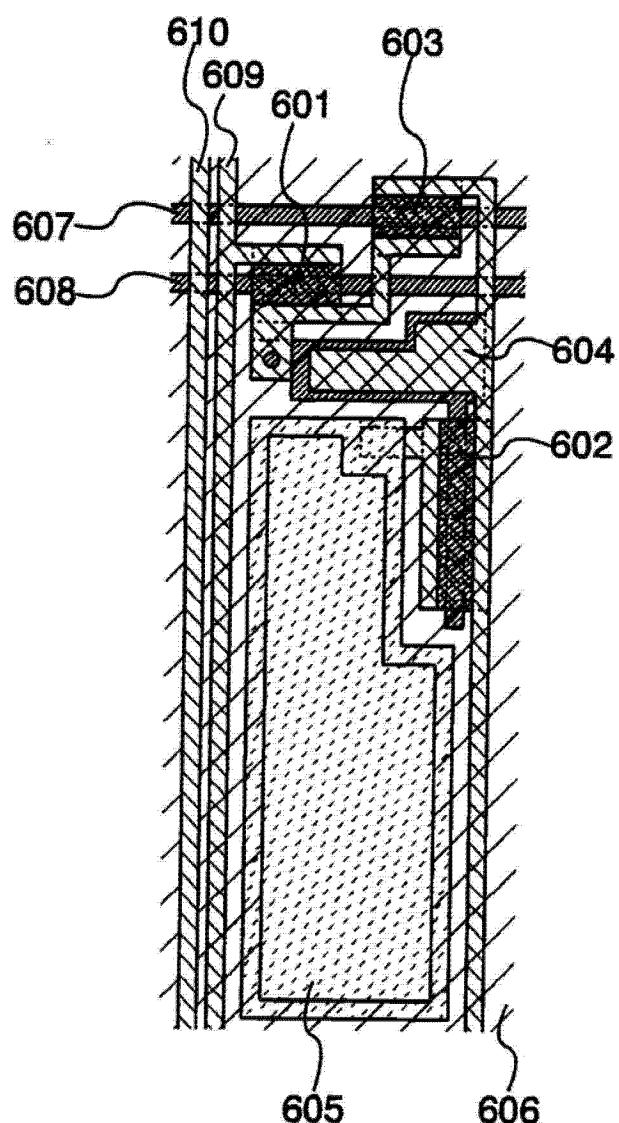

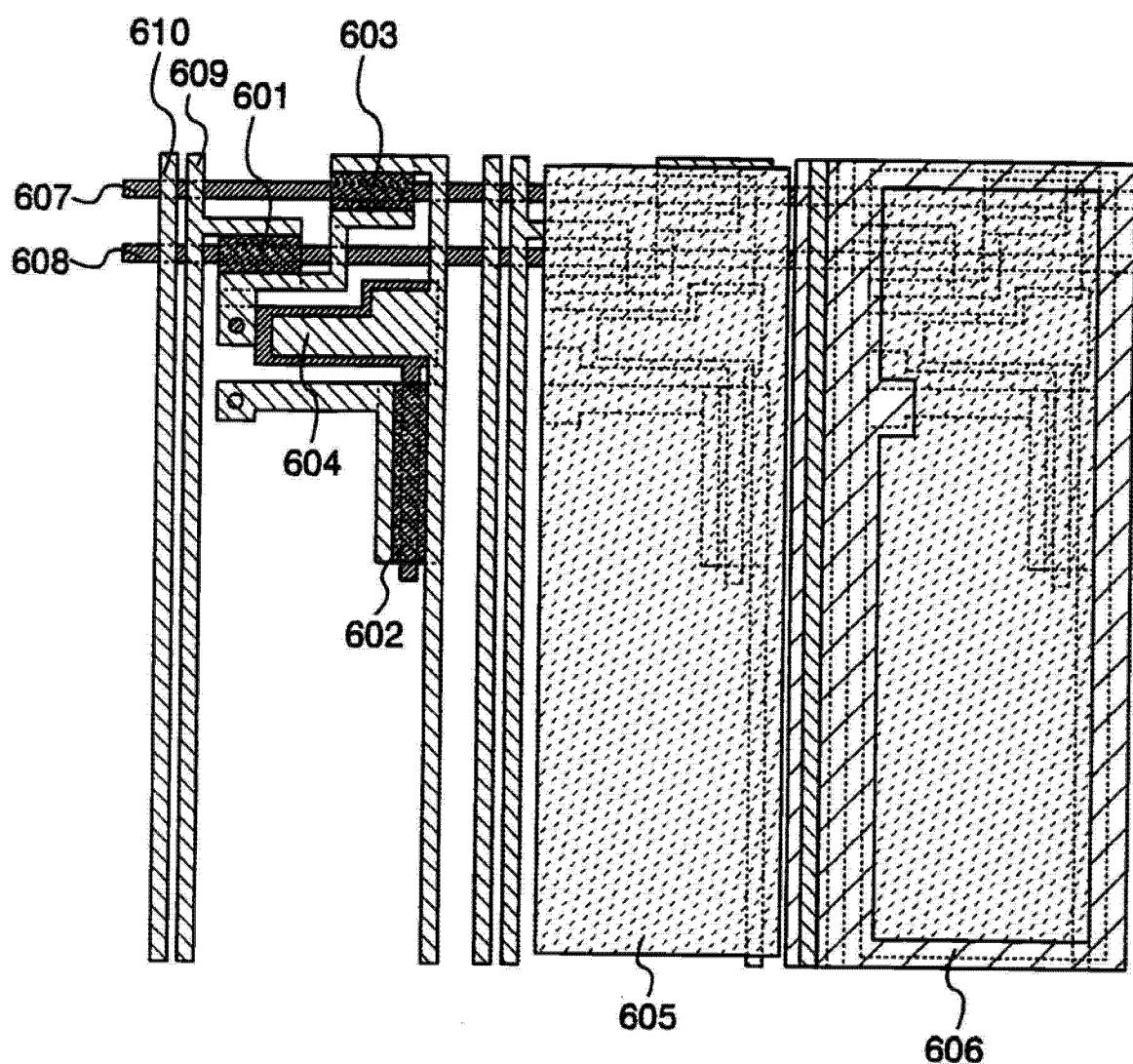

[0054] 参考图 1A 至 1C、2 和 3A 以及 3B,接下来阐释驱动晶体管、发光元件以及提供在具有绝缘表面的基板上的辅助布线的截面结构和掩模版图。

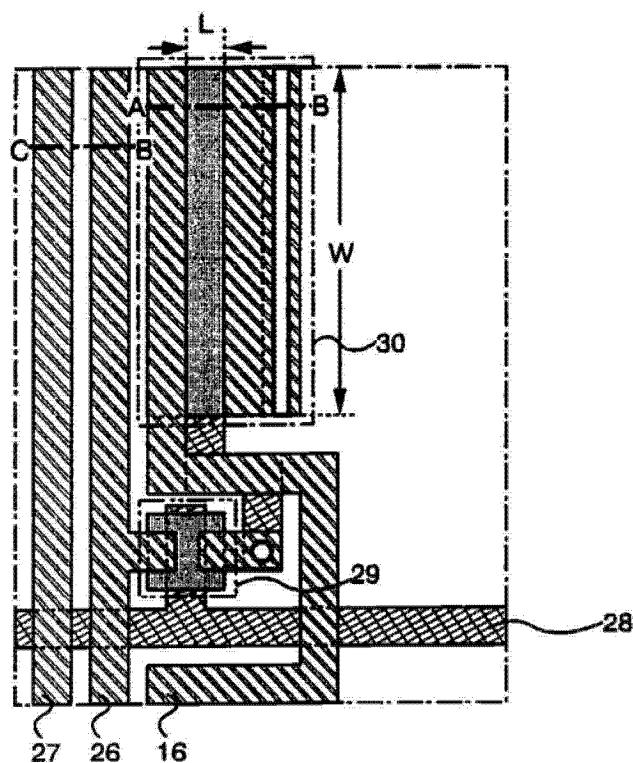

[0055] 图 1C 示出了一个像素的掩模版图。在图 1C 所示的像素中,作为电源线的导体 16、作为信号线的导体 26 和作为辅助布线的导体 27 排列成列,且作为扫描线的导体 28 排列成行。像素还包括开关晶体管 29 和驱动晶体管 30。

[0056] 图 1A 是沿图 1C 掩模版图中的线 A-B-C 的横截面图。在图 1A 中,在具有绝缘表面的基板 10 上形成栅电极 11,并在其上形成栅绝缘层 12。然后,依次层叠非晶半导体、N 型半导体和导体,然后将其同时构图以形成非晶半导体 13、N 型半导体 14 和 15,以及导体 16 和 17。随后,形成绝缘体 18 和 19,并在预定区域中形成开口部分以便部分地暴露导体 17 后形成导体 20。然后,形成导体 21(第一电极、像素电极)、电致发光层 22 和导体 23(第二电极、反向电极)以便与导体 20 电连接。导体 21、电致发光层 22 和导体 23 的重叠区域对应于发光元件 24。然后,在整个表面上形成保护层 25。

[0057] 注意,和导体 16 和 17 的同时形成导体 26 和 27。导体 26 和 27 分别对应于信号线和辅助布线。在形成导体 23(第二电极、反向电极)之前通过暴露导体 27,导体 23 可以层叠在导体 27 上,从而降低导体 23 的电阻。要指出的是,在图 1A 的横截面中,作为辅助布线的导体 27 形成在与导体 16 和 17 相同的导电层上。

[0058] 图 1B 示出了驱动晶体管 50 和发光元件 24 的截面结构。在图 1B 中,在具有绝缘表面的基板 10 上形成栅电极 11,并在其上形成栅绝缘层 12。在形成非晶半导体 13 之后,形成作为蚀刻停止层的绝缘体 31。随后,依次层叠 N 型半导体和导体,然后将其同时构图以形成 N 型半导体 32 和 33 以及导体 34 和 35。然后,形成绝缘体 18、5070 和 5080,并在预定区域中形成开口部分以便部分地暴露导体 35 之后,形成由导体构成的连接布线 5060。然后,形成包括导体 21、电致发光层 22 和导体 23 的发光元件 24,然后形成保护层 25。

[0059] 注意,和导体 34 和 35 的同时形成导体 26,并和连接布线 5060 的同时形成导体 36。导体 26 对应信号线且导体 36 对应辅助布线。在形成导体 23(反向电极)之前通过暴露导体 36,导体 23 可以层叠在导体 36 上,从而降低导体 23 的电阻。要指出的是,在图 1B 的横截面图中,作为辅助布线的导体 36 形成在与导体 20 相同的层上。

[0060] 图 2 是驱动晶体管 51 和发光元件 24 的横截面图。在图 2 中,在具有绝缘表面的基板 10 上形成栅电极 11,并在其上形成栅绝缘层 12。在形成非晶半导体 13 之后,形成作为蚀刻停止层的绝缘体 41,然后形成栅电极 42。随后,依次层叠 N 型半导体和导体,并将其同时构图以形成 N 型半导体 43 和 44 以及导体 45 和 46。然后,形成绝缘体 18 和 19,在预定区域中形成开口部分以便部分地暴露导体 46 之后,形成导体 20。然后,在形成保护层 25 之前,形成包括导体 21、电致发光层 22 和导体 23 的发光元件 24。作为辅助布线的导体 36 电连接到导体 23。

[0061] 图 3A 是驱动晶体管 431 和发光元件 438 的横截面图。驱动晶体管 431 形成在具有绝缘表面的基板 430 上，并在其上形成绝缘体 440。在预定区域中形成开口部分之后，在绝缘体 440 上形成导体 433 和 434。随后，形成作为像素电极的导体 435，然后形成绝缘体 442。在绝缘体 441 和 442 的预定区域中形成开口部分 439 之后，在绝缘体 442 上形成电致发光层 436，并在其上形成作为反向电极的导体 437。以这种方式，图 3A 中层叠了四层绝缘体。

[0062] 图 3B 是驱动晶体管 431 和发光元件 459 的横截面图。驱动晶体管 431 形成在具有绝缘表面的基板 430 上，然后形成电连接于驱动晶体管 431 的布线 460 和辅助布线 452。在形成绝缘体 453 之后，在绝缘体 453 的预定区域中形成开口部分。随后，形成作为像素电极的导体 454，在其上形成绝缘体 458，然后，在绝缘体 458 的预定区域中形成开口部分。之后，在导体 454 上形成电致发光层 455 和 456，并在其上形成作为反向电极的导体 457。导体 454、电致发光层 455 和 457、以及导体 457 的重叠区域对应发光元件 459。

[0063] 在图 3B 中，通过气相淀积形成辅助布线 452 上的电致发光层 456，且其膜厚度薄，因此，辅助布线 452 的侧面不会覆盖有电致发光层 456。利用该结构，导体 457 电连接到辅助布线 452 的侧面。

[0064] 如图 1A 至 1C、2 和 3A 以及 3B 所示，本发明的显示器件包括发光元件和具有非晶半导体的晶体管。优选的是，为了提高电流容量，将与发光元件串联连接的驱动晶体管的沟道宽度 W/ 沟道长度 L 设置在 1 到 100 (更优选为 5 到 20) 范围内。具体说来，期望沟道长度 L 在 5 到 15  $\mu\text{m}$  范围内，且沟道宽度 W 在 20 到 1200  $\mu\text{m}$  范围内 (更优选为 40 到 600  $\mu\text{m}$ )。注意，根据上述沟道长度 L 和沟道宽度 W，晶体管占据更大的像素面积。因此，发光元件期望地在基板的相反方向中发射光，即，顶部发射。

[0065] 有三种主要类型的使用非晶半导体用于沟道部分的晶体管：沟道蚀刻型(图 1A、图 3A 和 3B)、沟道保护型(图 1B) 和双栅极型(图 2)。本发明可以使用任何一种。

[0066] 包括在发光元件中的一对电极中的一个对应阳极，另一个对应阴极。阳极和阴极优选由金属、合金、电导体化合物或其混合物构成。而且，用具有高功函数的材料作阳极，而用具有低功函数的材料作阴极。电致发光层夹在阳极和阴极之间，且由选自多种有机材料或无机材料中的至少一种材料构成。电致发光层中的发光包括当激发的单重态返回到基态时产生的发光(荧光)和当激发的三重态返回到基态时产生的发光(磷光)。

[0067] 绝缘层可以由有机材料或无机材料构成。然而，当使用有机材料时，由于其具有高吸湿性，优选提供诸如氮化硅膜的阻挡膜。在有机材料中，与其他有机材料例如丙烯和聚酰亚胺相比，抗蚀剂材料廉价、具有小直径的接触孔、并具有低吸湿性，因此，它不需要阻挡膜。然而，当将抗蚀剂材料着色时，优选将其用于顶部发射显示器件。具体说来，借助旋转器涂敷通过在溶剂(甲基醚丙二醇乙酸酯；PGMEA)中溶解甲酚树脂等获得的溶液来形成抗蚀剂材料。

[0068] 根据本发明采用上述结构，减少了晶体管特性中的变化，由此，可以提供这样的显示器件，其中减少了由于晶体管特性的变化而引起的亮度变化。而且，根据本发明采用非晶半导体，可以有效地制造从几英寸到几十英寸尺寸范围内的大平板，由于没有结晶步骤并且需要小数目的掩模，而引起生产成本的降低。此外，根据制造步骤中的热处理温度，可以在诸如塑料的轻薄且廉价的柔性基板上形成非晶半导体。因此，可以拓宽显示器件的应用

范围。

[0069] 辅助布线有助于降低第二导电层的电阻,而造成功率消耗的降低。通过设置辅助布线,可以防止由于布线电阻引起的缺陷布线和灰度级,还可以抑制电压下降,从而向发光元件施加恒定电压。因此,可以提供提高了图像质量的显示器件。本实施方式中所述的结构在具有几十英寸尺寸的大平板的制造中是有效的。这是由于随着平板尺寸的增大,电阻值会成为问题。

[0070] 实施方式 2

[0071] 参考附图描述本发明的实施方式。

[0072] 图 8A 是包括具有绝缘表面的基板 200 的平板的顶视图。在基板 200 上,形成扫描线驱动器电路 203 和包括排列成矩阵的多个像素 201 的像素部分 202。多个驱动器 IC 205 附着在基板 200 上,且多个驱动器 IC 205 对应信号线驱动器电路 204。扫描线驱动器电路 203 和信号线驱动器电路 204 连接到电源电路 206 和控制器 207。

[0073] 电源电路 206 为平板提供电源,并特别地连接到设置在像素部分 202 中的电源线。电源线也称为阳极线或阴极线。阳极线具有和高电位电压 VDD 相同的电位,阴极线具有和低电位电压 VSS 相同的电位。控制器 207 为信号线驱动器电路 204 和扫描线驱动器电路 203 提供时钟、反时钟(clock back)、启动脉冲和视频信号。如本实施方式中,在信号线驱动器电路 204 包括多个驱动器 IC 205 的情况下,控制器 207 还确定将哪个视频信号提供给每个驱动器 IC,即,它将信号分类。

[0074] 虽然在图 8 中只有扫描线侧的驱动器电路整体地形成在基板上,但是本发明不限于此,并且根据驱动器电路的工作频率,信号线侧的驱动器电路也可以整体地形成在相同的基板上。然而,优选的是,扫描线侧的驱动器电路整体地形成在基板上,而信号线侧的驱动器电路以驱动器 IC 形成。据此,扫描线驱动器电路和信号线驱动器电路可以分开工作,这是由于信号线驱动器电路在 50MHz 或更高的频率(例如 65MHz 或更高)下工作,而扫描线驱动器电路在其百分之一的频率下工作,即大约 100kHz。在这种方式中,根据每个驱动器电路的工作频率,可以选择将驱动器电路整体地形成在基板上,或将驱动器 IC 附着在基板上。

[0075] 图 8B 是包括具有绝缘表面的基板 200 的平板的顶视图。在基板 200 上形成包括排列成矩阵的多个像素 201 的像素部分 202。通过 COG 将信号线侧的驱动器 IC 209 和扫描线侧的驱动器 IC 208 附着在基板 200 上。这些驱动器 IC 208 和 209 以连接布线 210 连接到外部输入端 211,并通过外部输入端 211 连接到电源电路 206 和控制器 207。虽然,在图 8B 中通过 COG 将驱动器 IC 附着在基板上,但本发明不限于此。可以通过 TAB 将驱动器 IC 附着到基板上,或通过 FPC 连接到基板上来取代附着于其上。而且,驱动器 IC 的长侧和短侧的长度以及所安装的驱动器 IC 的数量没有专门的限制。

[0076] 每个像素 201 包含包括夹在一对电极之间的发光材料的发光元件,和其沟道部分由非晶半导体或有机半导体构成的晶体管。发光元件的第一电极连接到阳极线,且其第二电极连接到阴极线。根据本发明,在发光元件不发光期间,阳极线和阴极线的电位相互转换,从而对发光元件施加反向偏置电压。通过从控制器 207 向电源电路 206 提供的预定信号来确定向发光元件施加反向偏置电压的时序。因此,在本发明中,电源电路 206 和控制器 207 共同被称为反向偏置电压施加电路。

[0077] 当本发明的显示器件用于显示具有多级灰度级的图像时,时间灰度级是可应用的。这是由于在发光元件不发光期间通过施加反向偏置电压,可以在不影响灰度级显示的情况下施加反向偏置电压。

[0078] 通常,将所有像素中阳极线和阴极线之一或二者共同连接。因此,反向偏置电压不得不同时向所有像素施加。因此为了向发光元件施加反向偏置电压,可以添加半导体元件。该半导体元件对应晶体管或二极管,并且允许任意地施加反向偏置电压,例如每个像素或每根线。具体地,一旦半导体元件导通,就向发光元件施加反向偏置电压。也就是说,当半导体元件导通时,发光元件电连接到具有比发光元件的反向电极更低电位的布线,由此向发光元件施加反向偏置电压。当施加反向偏置电压时,发光元件必然不发光。然而,根据前述结构,可以在任意时序下向任意像素施加反向偏置电压,因此,可以实现灰度级显示而没有任何问题。该结构适用于其他用于实现多级灰度级的驱动方法,例如模拟驱动方法以及时间灰度级。

[0079] 根据采用上述结构的本发明,可以防止发光元件随时间的退化,得到具有提高了可靠性和长寿命元件的显示器件。该实施方式可以与前述实施方式组合实现。

#### [0080] 实施方式 3

[0081] 在本实施方式中,将参考 10A 和 10B 描述 CMOS 电路的截面结构,该 CMOS 电路包括其沟道部分由非晶半导体构成的 N 型晶体管和其沟道部分由有机半导体构成的 P 型晶体管。

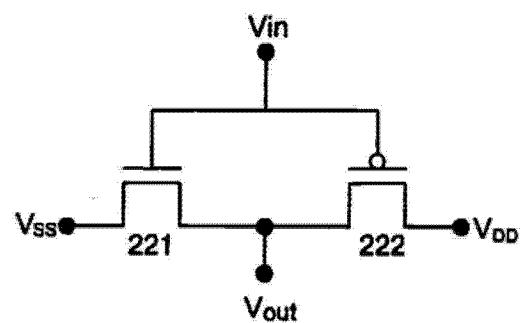

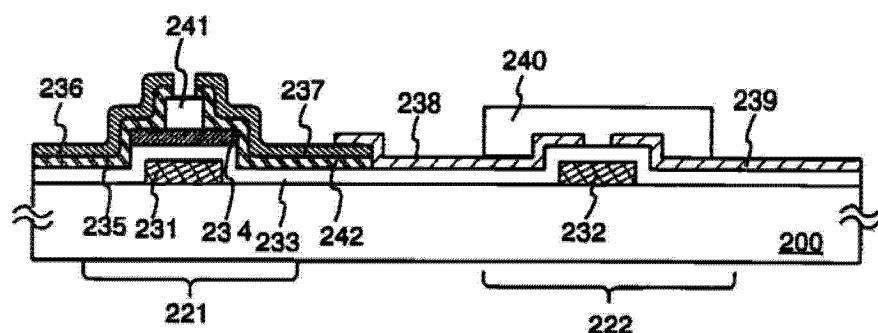

[0082] 图 10A 是包括串联连接的 P 型晶体管 221 和 N 型晶体管 222 的等效电路图,且其一端具有和 VDD 相同的电位,而另一端具有和 VSS 相同的电位。图 10B 是这些晶体管的横截面图。在图 10B 中,在基板 200 上形成导体 231 和 232,并在其上形成氮化硅 233。然后,在氮化硅 233 上形成非晶半导体 234,并在其上形成另一氮化硅 241。在氮化硅 241 上,依次层叠 N 型半导体和导体,然后将其同时构图以形成 N 型半导体 235 和 242 以及电极 236 和 237。随后,形成电极 238 和 239,并在其后形成用作沟道层的有机半导体 240。对于有机半导体 240,可以使用诸如并五苯的低分子量有机化合物、诸如 PEDOT 和 PPV 的高分子量有机化合物等,并且可以通过使用金属掩模的气相淀积来构图并五苯。以这种方式,完成包括其沟道部分由非晶半导体 234 构成的 N 型晶体管和其沟道部分由有机半导体 240 构成的 P 型晶体管的 CMOS 电路。

[0083] CMOS 电路是形成移位寄存器、缓冲器等的时钟控制反向器等的单元电路。因此,虽然由于工作频率,本实施方式的 CMOS 电路优选用作扫描线侧的驱动器电路,但该 CMOS 电路可以用作驱动器电路和像素电路。具体说来,期望用本实施方式的 CMOS 电路形成扫描线侧的驱动器电路,并用驱动器 I C 形成信号线侧的驱动器电路。虽然用本实施方式中的 CMOS 电路形成驱动器电路,但本发明不限于此。不必说,可以仅用 N 型晶体管(a-Si :HTFT)或 P 型晶体管(有机 TFT)形成驱动器电路。

[0084] 本实施方式可以与前述实施方式组合实现。

#### [0085] 实施方式 4

[0086] 本发明提供一种包括多个像素的显示器件,每个像素包括具有夹在一对电极之间的发光材料的发光元件,并包括其沟道部分由非晶半导体或有机半导体构成的晶体管。下文中参考图 11A 至 11F 阐释像素的结构。

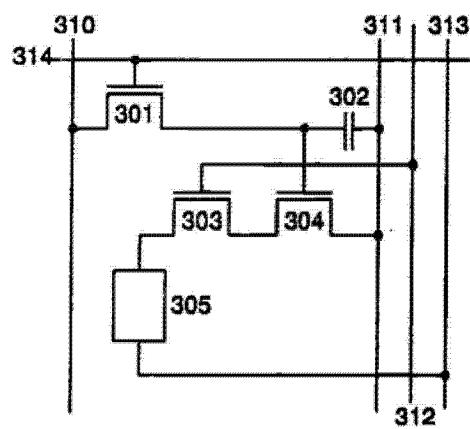

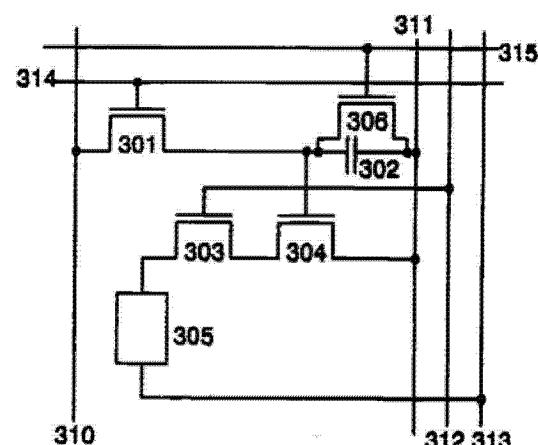

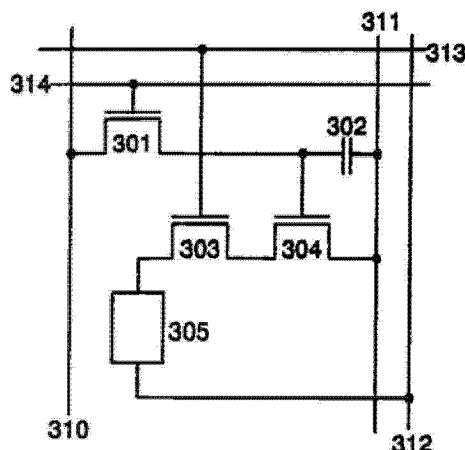

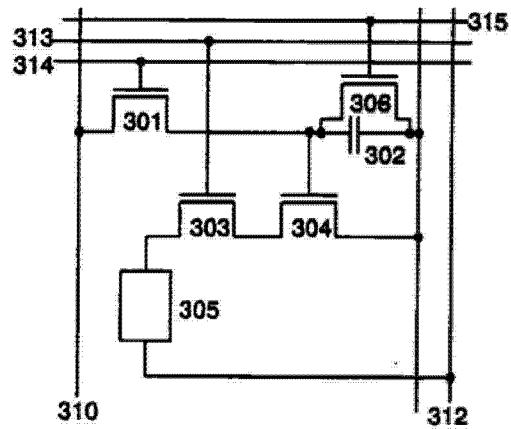

[0087] 在图 11A 所示的像素中,信号线 310 和电源线 311 至 313 排列成列,且扫描线 314 排列成行。像素还包括用于开关的晶体管 301、用于驱动的晶体管 303、用于电流控制的晶体管 304、电容 302 和发光元件 305。

[0088] 图 11C 所示的像素具有与图 11A 所示的相同的结构,除了晶体管 303 的栅电极连接到排列成行的电源线 313 上。也就是说,图 11A 和 11C 中的像素都示出了相同的等效电路图。然而,在电源线 313 排列成列(图 11A)的情况和在电源线 313 排列成行(图 11C)的情况之间,电源线形成在不同的导电层上。为了使用于形成连接到图 11A 和图 11C 中晶体管 303 栅电极的布线的层之间的区别清楚,将两个像素各在图 11A 和 11C 中示出。

[0089] 在图 11A 和 11C 中,像素中的晶体管 303 和 304 串联连接,且晶体管 303 的沟道长度  $L_3$ /沟道宽度  $W_3$  与晶体管 304 的沟道长度  $L_4$ /沟道宽度  $W_4$  的比率设置为  $L_3/W_3:L_4/W_4=5$  到 6000 :1。例如,当  $L_3$ 、 $W_3$ 、 $L_4$  和  $W_4$  分别等于 500  $\mu\text{m}$ 、3  $\mu\text{m}$ 、3  $\mu\text{m}$  和 100  $\mu\text{m}$  时,可以将  $L_3/W_3:L_4/W_4$  设置为 6000 :1。

[0090] 晶体管 303 工作在饱和区并控制在发光元件 305 中流过的电流量,而晶体管 304 工作在线性区并控制是否向发光元件 305 提供电流。考虑到制造步骤,这些晶体管 303 和 304 优选地具有相同的电导率。对于晶体管 303,可以使用耗尽型晶体管以及增强型晶体管。根据具有前述结构的本发明,由于晶体管 304 工作在线性区,因此晶体管 304 的  $V_{GS}$  中的微小变化不影响在发光元件 305 中流过的电流量。也就是说,在发光元件 305 中流过的电流量由工作在饱和区的晶体管 303 确定。因此,可以提供一种显示器件,其中减小了由于晶体管特性的变化而引起的亮度变化并提高了图像质量。

[0091] 图 11A 至 11D 中的晶体管 301 控制输入到像素的视频信号。当晶体管 301 导通并向像素输入视频信号时,视频信号被保持在电容 302 中。虽然图 11A 至 11D 中的像素包括电容 302,但是本发明不限于此。当栅极电容等可以取代电容保持视频信号时,不必提供电容 302。

[0092] 发光元件 305 包括夹在一对电极之间的电致发光层。像素电极和反向电极(阳极和阴极)具有电位差,以便向发光元件 305 施加正向偏置电压。电致发光层由选自多种有机材料或无机材料的至少一种材料构成。电致发光层中的发光包括当激发的单重态返回到基态时产生的发光(荧光)和当激发的三重态返回到基态时产生的发光(磷光)。

[0093] 图 11B 所示的像素具有与图 11A 所示的相同的结构,除了增加了晶体管 306 和扫描线 315。类似地,图 11D 所示的像素具有与图 11C 所示的相同的结构,除了增加了晶体管 306 和扫描线 315。

[0094] 通过增加的扫描线 315 控制晶体管 306 开 / 关。当晶体管 306 导通时,释放保持在电容 302 中的电荷,由此将晶体管 304 关断。也就是说,通过设置晶体管 306 可以强制地停止向发光元件 305 提供电流。因此,通过采用图 11B 和 11D 所示的结构,在信号写入所有像素之前,可以使发光周期与写周期同时开始或在写周期之后立刻开始,从而提高占空比。

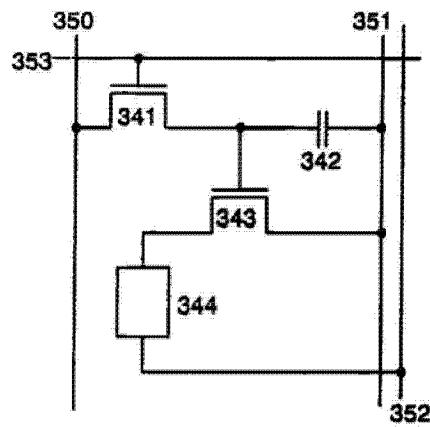

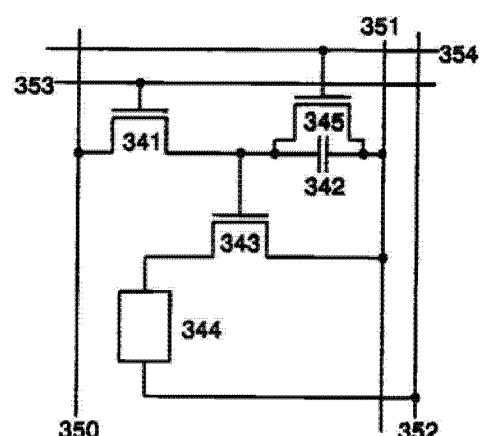

[0095] 在图 11E 所示的像素中,信号线 350 排列成列,且电源线 351 和 352 以及扫描线 353 排列成行。像素还包括开关晶体管 341、驱动晶体管 343、电容 342 和发光元件 344。图 11F 所示的像素具有与图 11E 所示的相同的结构,除了增加了晶体管 345 和扫描线 354。要指出的是,图 11F 的结构由于晶体管 345 还可以提高占空比。

[0096] 本实施方式可以与前述实施方式组合实现。

[0097] 实施例 1

[0098] 包括一对电极之间的发光材料的发光元件和包括非晶半导体或有机半导体的晶体管是本发明的基本元件，并且发光元件和晶体管提供在每个像素中。当在每个像素中提供包括非晶半导体的晶体管的情况下，通过 COG 或 TAB 将驱动器 IC 通常安装在基板上，或通过 FPC 连接到基板上。下文中描述的是其中将多个驱动器 IC 形成在矩形基板上并安装在基板上的实施例。

[0099] 图 9A 是在扫描线侧和信号线侧分别包括驱动器 IC 251 和 252 的平板的顶视图。其他元件与图 8B 所示平板的元件相同，因此在此省略其阐释。

[0100] 图 9B 是附着在基板上的驱动器 IC 的透视图。多个驱动器电路以及用于连接多个驱动器电路的输入和输出端形成在基板 253 上。当使用每个驱动器电路及其相应的输入和输出端作为单元，而将基板 253 分隔成条或矩形时，获得多个驱动器 IC。然后，将驱动器 IC 附着在基板 200 上以完成显示器件。在图 9B 中，将作为扫描线驱动器电路的驱动器 IC 252 和作为信号线驱动器电路的驱动器 IC 251 安装在基板上。

[0101] 优选的是，信号线和扫描线具有与驱动器 IC 的输出端相同的间距。据此，不必在像素部分 202 的端部每隔几块就提供引线，导致了制造步骤中提高的产量。而且，通过在矩形基板 253 上形成驱动器 IC，可以大量地生产它们，而导致提高的生产率。因此，作为基板 253，例如大基板，优选使用在长度上具有约 300 到 1000mm 的边的基板。与在圆形硅晶片上形成 IC 芯片的情况相比，其提供了极大的优点。然而，当将基板 253 分隔开以便使驱动器 IC 的长边具有与像素部分 202 的垂直或水平方向相同的长度时，可以减少驱动器 IC 的数量并且可以提高可靠性。

[0102] 这些驱动器 IC 优选地由结晶半导体构成，且结晶半导体优选地通过辐射连续波激光获得。由此，作为产生激光的振荡器，期望使用连续波固体激光器或连续波气体激光器。当辐射连续波激光时，晶粒界面在激光的扫描方向中延伸。利用这种特性，构图半导体层以便晶粒界面方向平行于沟道长度方向。由此，可以获得使用具有足够电特性的结晶半导体作为有源层的薄膜晶体管。

[0103] 优选的是，设置在信号线侧且设置在扫描线侧的驱动器 IC 具有不同的结构，具体地，它们在薄膜晶体管的栅绝缘层厚度上不同。由此可以独立地操作信号(数据)线驱动器电路和扫描线驱动器电路。具体地，在形成信号线驱动器电路的薄膜晶体管中，栅绝缘层的厚度设置为 20 到 70nm 且沟道长度设置为 0.3 到 1 μm。另一方面，在形成扫描线驱动器电路的薄膜晶体管中，栅绝缘层的厚度设置为 150 到 250nm 且沟道长度设置为 1 到 2 μm。在这种方式中，可以获得包括其每一个具有与每个驱动器电路相应的工作频率的驱动器 IC 的显示器件。本实施方式可以与前述实施方式组合实现。

[0104] 实施例 2

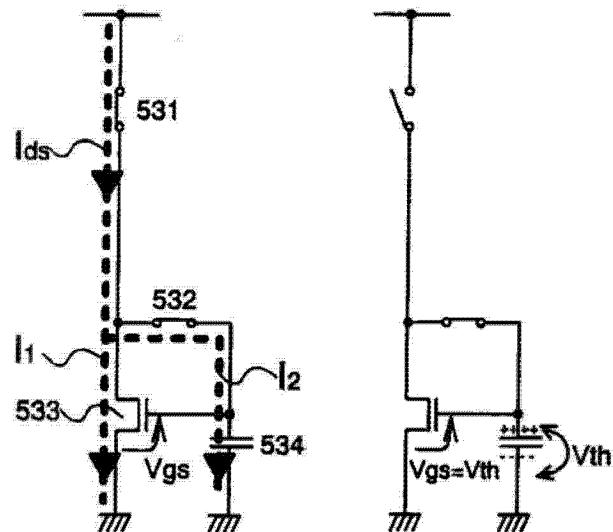

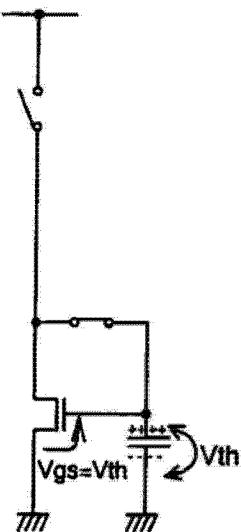

[0105] 包括一对电极之间的发光材料的发光元件和包括非晶半导体或有机半导体的晶体管是本发明的基本元件，并且发光元件和晶体管提供在每个像素中。在这种包括非晶半导体的晶体管中，电特性(阈值电压、场效应迁移率等)随时间而改变。因此，参考阈值电压，在下文中描述阈值补偿电路。

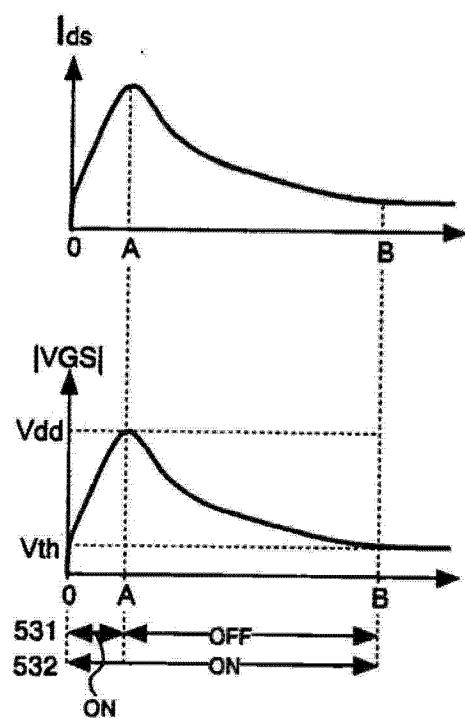

[0106] 参考图 17A 至 17D 阐释阈值补偿电路。图 17A 是包括由晶体管等构成的开关 531 和 532、晶体管 533 和电容 534 的等效电路。简要描述该电路的工作。

[0107] 当开关 531 和 532 接通时(图 17A),电流  $I_{ds}$  从开关 531 提供到晶体管 533,并从开关 531 和 532 提供到电容 534。 $I_{ds}$  被分成  $I_1$  和  $I_2$ ,且满足  $I_{ds}=I_1+I_2$ 。当电流开始流动时,电荷未保持在电容 534 中,晶体管被关断,由此,满足  $I_2=0$  且  $I_{ds}=I_1$ 。然而,随着电荷被保持在电容 534 中,电容 534 两电极之间的电位开始不同。当电极之间的电位差等于  $V_{th}$  时,晶体管 533 导通,且  $I_2$  大于 0。由于此时满足  $I_{ds}=I_1+I_2$ ,因此  $I_1$  逐渐地减小,尽管电流继续流动。电容 534 继续保持电荷直到电极之间的电位差等于  $V_{dd}$  为止。当电极之间的电位差等于  $V_{dd}$  时,  $I_2$  停止流动,且由于晶体管 533 导通,满足  $I_{ds}=I_1$ (图 17C 和 17D,点 A)。

[0108] 随后,开关 531 被关断(图 17B)。由此,保持在电容 534 中的电荷通过开关 532 在晶体管 533 的方向中流动以被放电。该操作持续到晶体管 533 被关断为止。也就是说,电容 534 保持有具有与晶体管 533 的阈值电压相同电位的电荷(图 17C 和 17D,点 B)。

[0109] 以该方式,可以将电容两电极之间的电位差设置为与晶体管的阈值电压相同。将信号电压输入到晶体管的栅电极,同时保持晶体管的  $V_{GS}$ 。由此,将加到信号电压上的保持在电容中的  $V_{GS}$  输入到晶体管的栅电极。换言之,即使当晶体管的阈值电压存在变化时,信号电压和晶体管的阈值电压也将恒定地输入到晶体管。因此,可以降低晶体管阈值电压的变化。

[0110] 通过采用阈值补偿电路,可以降低用于驱动发光元件的驱动晶体管阈值电压的变化,还可以降低由于阈值电压的这种变化而引起的亮度的变化,并且可以获得提高了图像质量的显示器件。要指出的是,本实施方式的阈值补偿电路可以应用于图 11A 至 11F 所示的像素电路中。在这种情况下,可以提供阈值补偿电路以便补偿具有对其输入信号电压的栅电极的驱动晶体管的阈值电压。

[0111] 虽然在本实施例中作为示例示出了用于阈值电压的补偿器,本发明还可以包括用于其他电特性的补偿器。例如,可以提供用于场效应迁移率的补偿器。本实施例可以与前述实施方式和实施例组合实现。

#### [0112] 实施例 3

[0113] 为了形成发光元件,任意地组合空穴注入层、空穴传输层、空穴阻挡层、电子传输层等。然而,电子注入层优选地由已知为适于仅传输电子的材料的浴铜灵(BCP)形成,其掺杂有锂(Li),这是由于当浴铜灵掺杂有锂时,可以急剧提高电子注入特性。

[0114] 而且,苯并恶唑衍生物(BzOS)和吡啶衍生物是具有良好的电子传输特性的材料且在淀积时不易结晶。此外,当包含碱金属、碱土金属和过渡金属中的至少一种时,这些材料可以具有极佳的电子注入特性。因此,在包括位于一对电极之间的发光材料的发光元件中,包括在发光材料中的部分层优选由苯并恶唑衍生物或吡啶衍生物构成。

[0115] 也就是说,当电子注入层由包括苯并恶唑衍生物或吡啶衍生物和碱金属、碱土金属和过渡金属中的至少一种的用于发光元件的电子注入特性的合成物构成时,电子可以更容易从起阴极作用的电极注入。此外,由于吡啶衍生物在淀积时不会有效地结晶,因此可以提供比以往具有优越特性和更长寿命的发光元件以及使用该发光元件的显示器件。本实施例可以与前述实施方式和实施例组合实现。

#### [0116] 实施例 4

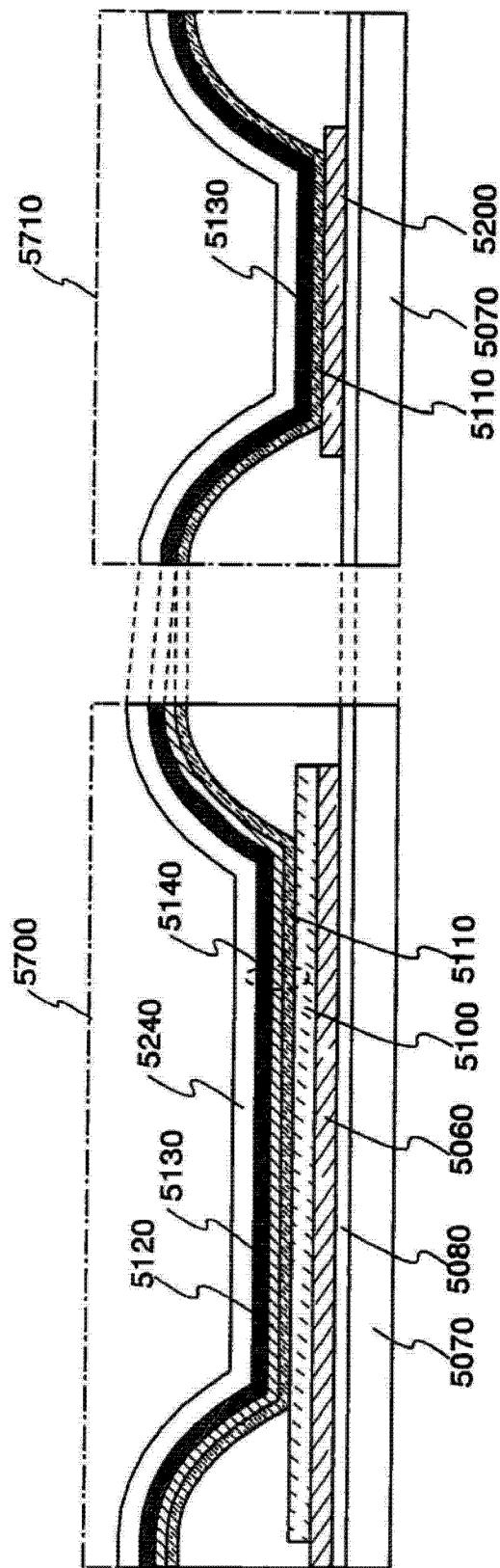

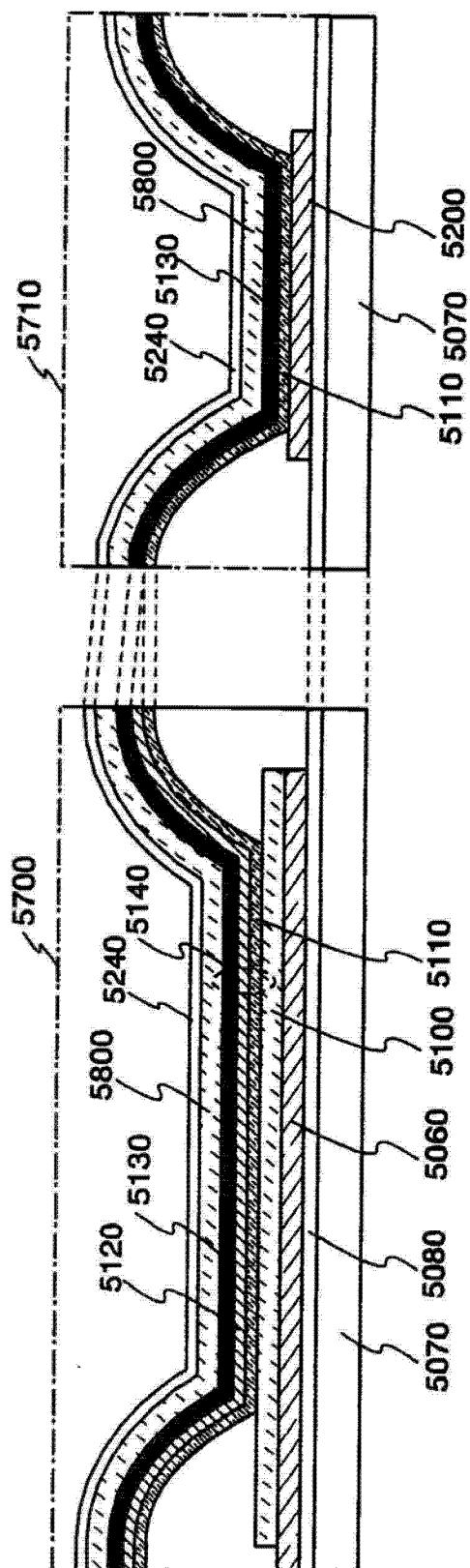

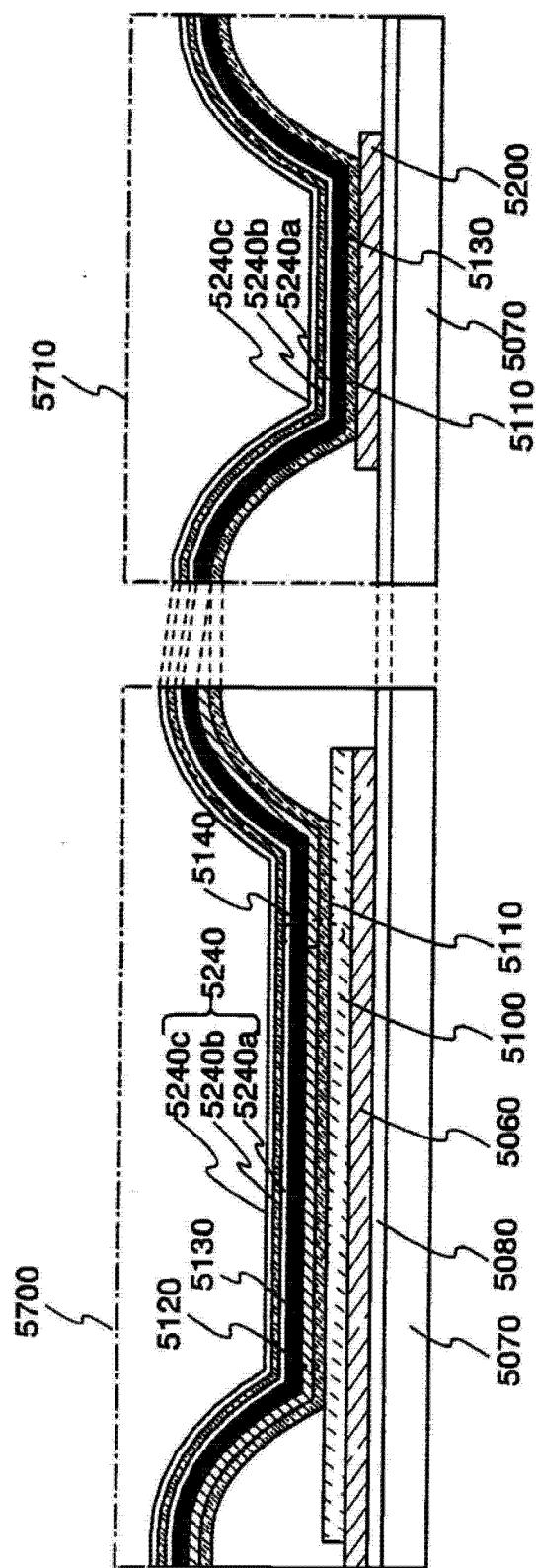

[0117] 在本实施例中,描述发光元件的叠层结构。要指出的是,在此参考图 1B 中由虚线包围的区域 5700 和 5710 的放大图进行描述。图 18A、18C 和 19A 与区域 5700 的放大图相

应,而图 18B、18D 和 19B 与区域 5710 的放大图相应。图 1B 的截面结构与图 18A 至 18D 以及图 19A 和 19B 的截面结构的相同之处在于它们包括绝缘体 5070 和 5080、连接布线 5060 和像素电极 5100,但是它们的不同之处在于将在下文中通过使用不同的参考数字描述的其他元件。

[0118] 在图 18A 和 18B 中,在绝缘体 5070 上形成绝缘层 5080,并在其上形成连接布线 5060。连接布线 5060 电连接到驱动晶体管的源电极或漏电极。在绝缘体 5080 上,还形成通过构图与连接布线 5060 相同的导体而获得的辅助布线 5200。然后,形成像素电极 5100 以便与连接布线 5060 连接,并在像素电极 5100 上,依次层叠空穴注入层 5110、发光层 5120 和电子注入层 5130。最后,形成保护层 5240。像素电极 5100、空穴注入层 5110、发光层 5120 和电子注入层 5130 的重叠区域对应发光元件 5140。

[0119] 通过使用金属掩模形成发光层 5120,以便暴露部分辅助电极 5200 而不完全覆盖开口部分。因此,在开口部分中,空穴注入层 5110 和电子注入层 5130 依次层叠在辅助布线 5200 上。注意,本发明不限于该结构,可以通过以金属掩模的方式形成空穴注入层 5110 和发光层 5120,仅使电子注入层 5130 在辅助布线 5200 上。

[0120] 虽然在图 18A 和 18B 中来自发光元件 5140 的光在基板的方向中发射,但还可以采用其中光在基板的相反方向中发射的结构。

[0121] 在图 18C 和 18D 中,形成像素电极 5100 以便与连接布线 5060 连接。在像素电极 5100 上,依次层叠空穴注入层 5110、发光层 5120、电子注入层 5130 和透明导电层 5800。最后,形成保护层 5240。当作为反向电极的电子注入层 5130 具有增大的电阻时,形成以便与电子注入层 5130 连接的透明导电层抑制了电压下降。

[0122] 通过金属掩模的方式形成发光层 5120,以便暴露部分辅助布线 5200 而不完全覆盖开口部分。因此,在开口部分中,空穴注入层 5110、电子注入层 5130 和透明导电层 5800 依次层叠在辅助布线 5200 上。要指出的是,本发明不限于该结构,可以通过金属掩模的方式形成空穴注入层 5110 和发光层 5120,仅有电子注入层 5130 和透明导电层 5800 形成在辅助布线 5200 上。可选择的,通过借助金属掩模的方式形成空穴注入层 5110、发光层 5120 和电子注入层 5130,仅有透明导电层 5800 形成在辅助布线 5200 上。

[0123] 图 18A 和 18B 所示的保护层 5240 可以具有无机绝缘层和有机绝缘层的叠层结构。参考图 19A 和 19B 描述这种情况下的截面结构。

[0124] 在图 19A 和 19B 中,保护层 5240 具有叠层结构,其中形成无机绝缘层 5240a 以便与电子注入层 5130 接触,并依次在无机绝缘层 5240a 上层叠有机树脂层 5240b 和无机绝缘层 5240c。当无机绝缘层 5240a 和 5240a 由氮化硅、氮氧化硅、氧化铝或氮化铝等形成时,可以防止湿气和氧气被发光元件 5140 吸收而加速其退化。而且,在无机绝缘层 5240a 和无机绝缘层 5240c 之间提供的具有较小内部应力的有机树脂层 5240b 可以防止保护层 5240 被应力剥落。对于有机树脂层 5240b,可以使用聚酰亚胺、聚酰胺、聚酰亚胺酰胺等。

[0125] 通过使用金属掩模形成发光层 5120,以便暴露部分辅助布线 5200 而不完全覆盖开口部分。因此,在开口部分中,空穴注入层 5110、电子注入层 5130、无机绝缘层 5240a、有机树脂层 5240b 和无机绝缘层 5240c 依次层叠在辅助布线 5200 上。要指出的是,本发明不限于该结构,可以通过借助金属掩模的方式形成空穴注入层 5110 和发光层 5120,在辅助布线 5200 上依次层叠电子注入层 5130、无机绝缘层 5240a、有机树脂层 5240b 和无机绝缘层

5240c。本实施例可以与前述实施方式和实施例组合实现。

[0126] 实施例 5

[0127] 包括一对电极之间的发光材料的发光元件和包括非晶半导体或有机半导体的晶体管是本发明的基本元件，并且发光元件和晶体管提供在每个像素中。在每个像素中提供这种晶体管的情况下，形成在相同基板上的驱动器电路还优选地用包括非晶半导体或有机半导体的晶体管形成。然而，包括非晶半导体的晶体管不能应用于 P 型晶体管。因此，在本实施例中，描述仅用 N 型晶体管形成的移位寄存器。

[0128] 在图 12A 中，以 400 表示的块对应于用于输出单级取样脉冲的脉冲输出电路。用 n 个脉冲输出电路形成移位寄存器。图 12B 示出了脉冲输出电路 400 的详细结构，其包括 N 型晶体管 401 至 406 和电容 407。可以通过应用自举法，仅用 N 型晶体管构成脉冲输出电路 400。日本专利特许公开 No. 2002-335153 中详细披露了该操作。

[0129] 虽然在本实施例中仅用 N 型晶体管构成驱动器电路，但本发明不限于此。可以使用其沟道部分包括有机半导体的 P 型晶体管用于形成驱动器电路。本实施例可以与前述实施方式和实施例组合实现。

[0130] 实施例 6

[0131] 在通过数字驱动法操作本发明显示器器件的情况下，优选将时间灰度级用于显示具有多级灰度级的图像。在本实施例中，描述时间灰度级。图 13A 是时序图，其纵坐标表示扫描线，横坐标表示时间。图 13B 是第 j 行扫描线的时序图。

[0132] 在此，显示器件具有大约 60Hz 的帧频率。即，每秒进行 60 次图像的写入，一个写图像的周期成为帧周期。在时间灰度级中，将帧周期分成多个子帧周期。在很多情况下划分数量等于位的数量，为了简单在此描述这种情况。也就是说，在本实施例中作为示例示出 5 位灰度级，将帧周期分成五个子帧周期 SF1 至 SF5。每个子帧周期包括用于将视频信号写入像素的地址周期 Ta，和用于使像素发光或不发光的维持周期 Ts。维持周期 Ts1 至 Ts5 的比率设置为  $Ts1 : \dots : Ts5 = 16 : 8 : 4 : 2 : 1$ 。换言之，当显示具有 n 位灰度级的图像时，维持周期的比率为  $2^{(n-1)} : 2^{(n-2)} : \dots : 2^1 : 2^0$ 。

[0133] 具有比写周期更短的发光周期的子帧周期（在此为子帧周期 SF5）具有擦除周期 Te5。在擦除周期 Te5 期间，为了在发光周期之后不立刻开始下一周期，重置已经写入像素的视频信号并强行重置发光元件。

[0134] 当必须增加位的数量时，可以增加子帧的数量。子帧周期的顺序不必从最高有效位排列到最低有效位，可以在帧周期内随机排列。而且，每个帧周期可以改变子帧周期的顺序。本实施例可以与前述实施方式和实施例组合实现。

[0135] 实施例 7

[0136] 在本实施例中，参考图 14A 和 14B 描述信号线驱动器电路和扫描线驱动器电路的结构示例。

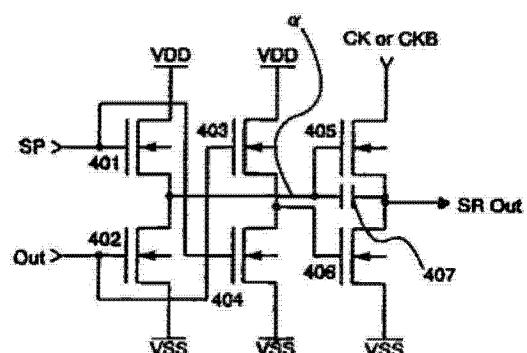

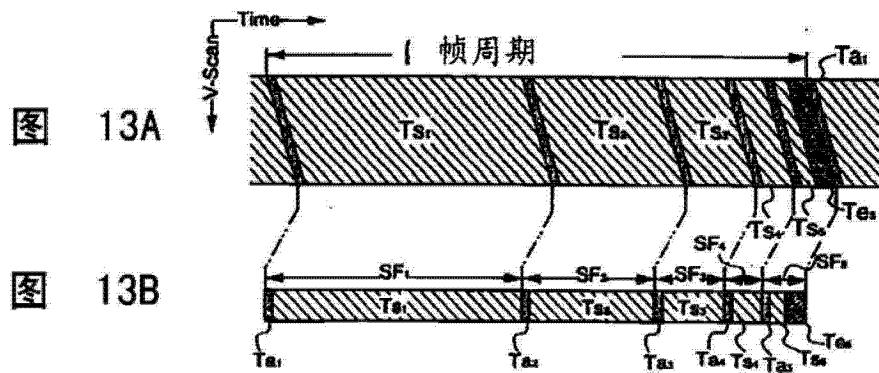

[0137] 如图 14A 所示，信号线驱动器电路包括移位寄存器 3021、第一锁存电路 3022 和第二锁存电路 3023。同时，如图 14B 所示，扫描线驱动器电路包括移位寄存器 3024 和缓冲器 3025。图 14A 和 14B 中的结构仅仅是示例。例如，可以将电平移动器或缓冲器增加到信号线驱动器电路中，并且可以在扫描线驱动器电路中的移位寄存器 3024 和缓冲器 3025 之间设置电平移动器。通过增加电平移动器，可以改变逻辑电路部分和缓冲器部分的电压幅度。

本实施例可以与前述实施方式和实施例组合实现。

[0138] 实施例 8

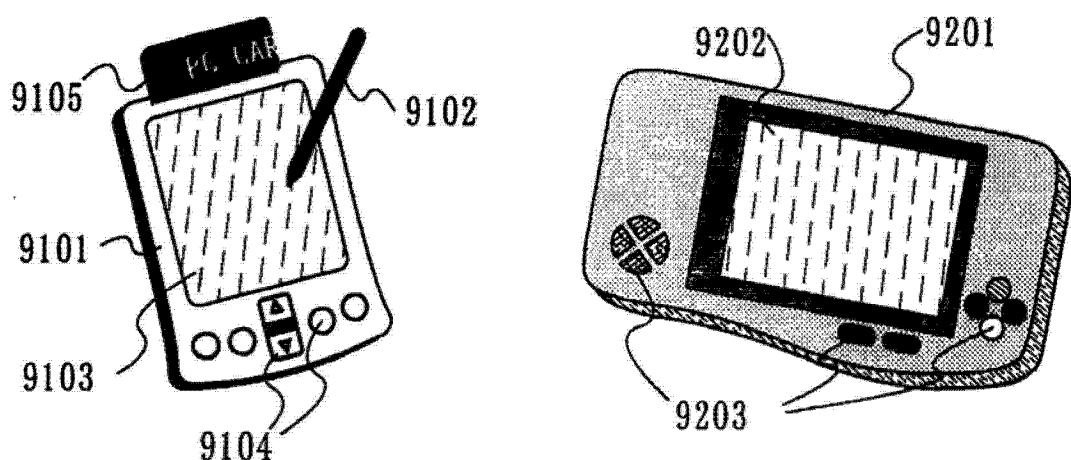

[0139] 本发明可以应用于各种电子设备,例如摄像机、数字照相机、目镜类显示器、导航系统、诸如汽车音频系统的音频再现设备、笔记本个人电脑、游戏机、便携式信息终端(移动计算机、移动电话、便携式游戏机、电子图书等)、提供有记录介质的图像再现设备,例如家庭视频游戏机(特别是,能够再现例如 DVD 的记录介质并具有用于显示再现图像的显示器的设备)。这种电子设备的详细示例在图 15A 至 15D 以及 16A 和 16D 中示出。

[0140] 图 15A 示出了包括主体 9301、音频输出部分 9302、音频输入部分 9303、显示部分 9304、操作开关 9305 等的便携式终端。图 15B 示出了包括主体 9101、触屏笔 9102、显示部分 9103、操作键 9104、外部接口 9105 等的 PDA。图 15C 示出了包括主体 9201、显示部分 9202、操作键 9203 等的便携式游戏机。图 15D 示出了包括主体 9501、显示部分 9502、臂部分 9503 等的目镜型显示器。

[0141] 图 16A 示出了具有约 40 英寸尺寸的大液晶电视,其包括显示部分 9401、外壳 9402、音频输出部分 9403 等。图 16B 示出了包括外壳 9601、音频输出部分 9602、显示部分 9603 等的监视器。图 16C 示出了包括显示部分 9701 和 9702 等的数字照相机。图 16D 示出了包括外壳 9801、显示部分 9802 和键盘 9803 等的笔记本个人计算机。

[0142] 在前述电子设备中,可以将本发明的显示器件应用于包括显示部分 9304、9103、9202、9502、9401、9603、9701、9702 和 9802 的平板中。本实施例可以于前述实施方式和实施例组合实现。

[0143] 实施例 9

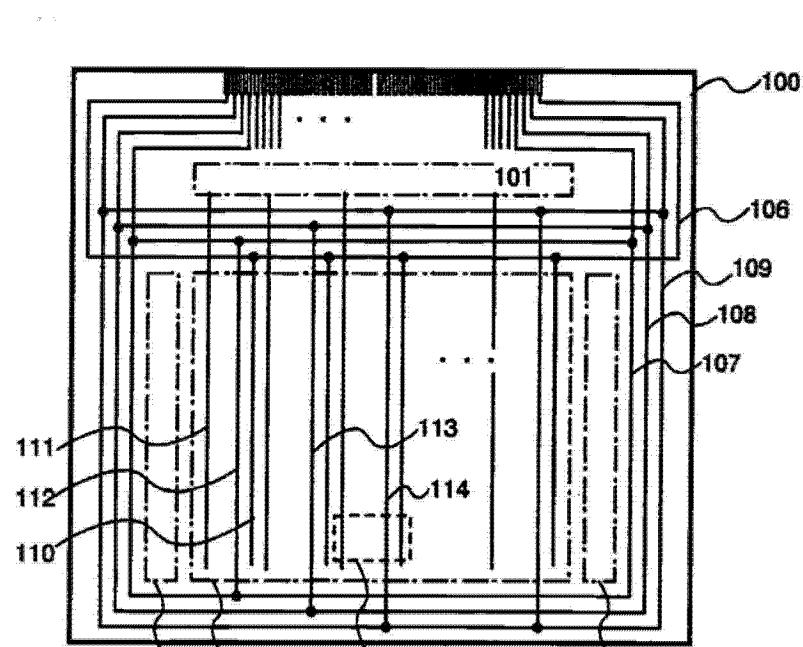

[0144] 在本实施例中,阐释了实施例 4 中所描述的像素电路的版图示例。下文中描述的版图示例包括发光元件的像素电极和环绕像素电极端部的绝缘层。在图 21 至 23 所示的版图示例中,示出了彼此相邻的三个像素,其中一个像素表示在形成晶体管和电容之后立即的版图,另一像素表示在形成像素电极之后立即的版图,其余像素表示在形成作为堤的绝缘层之后立即的版图。

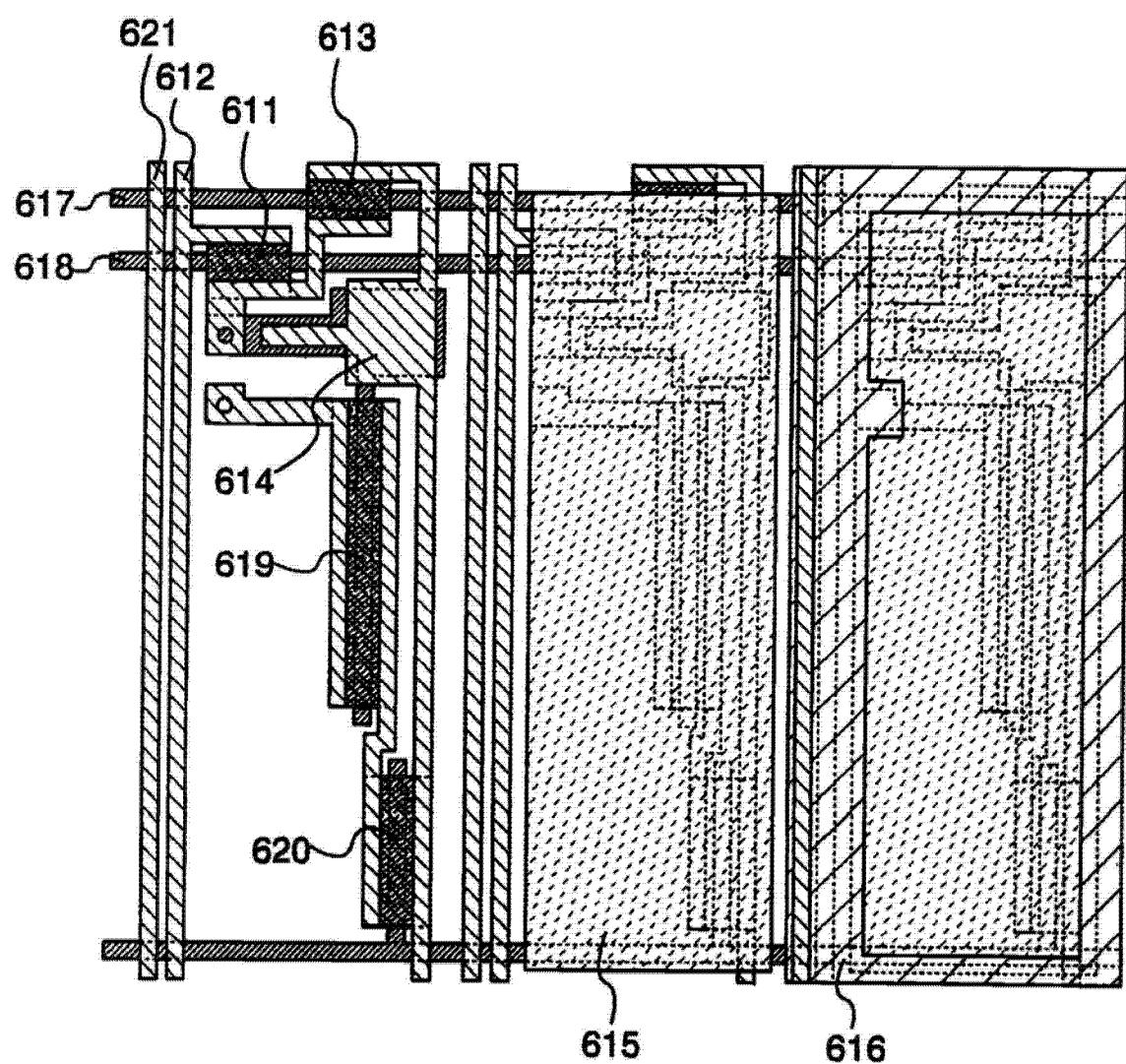

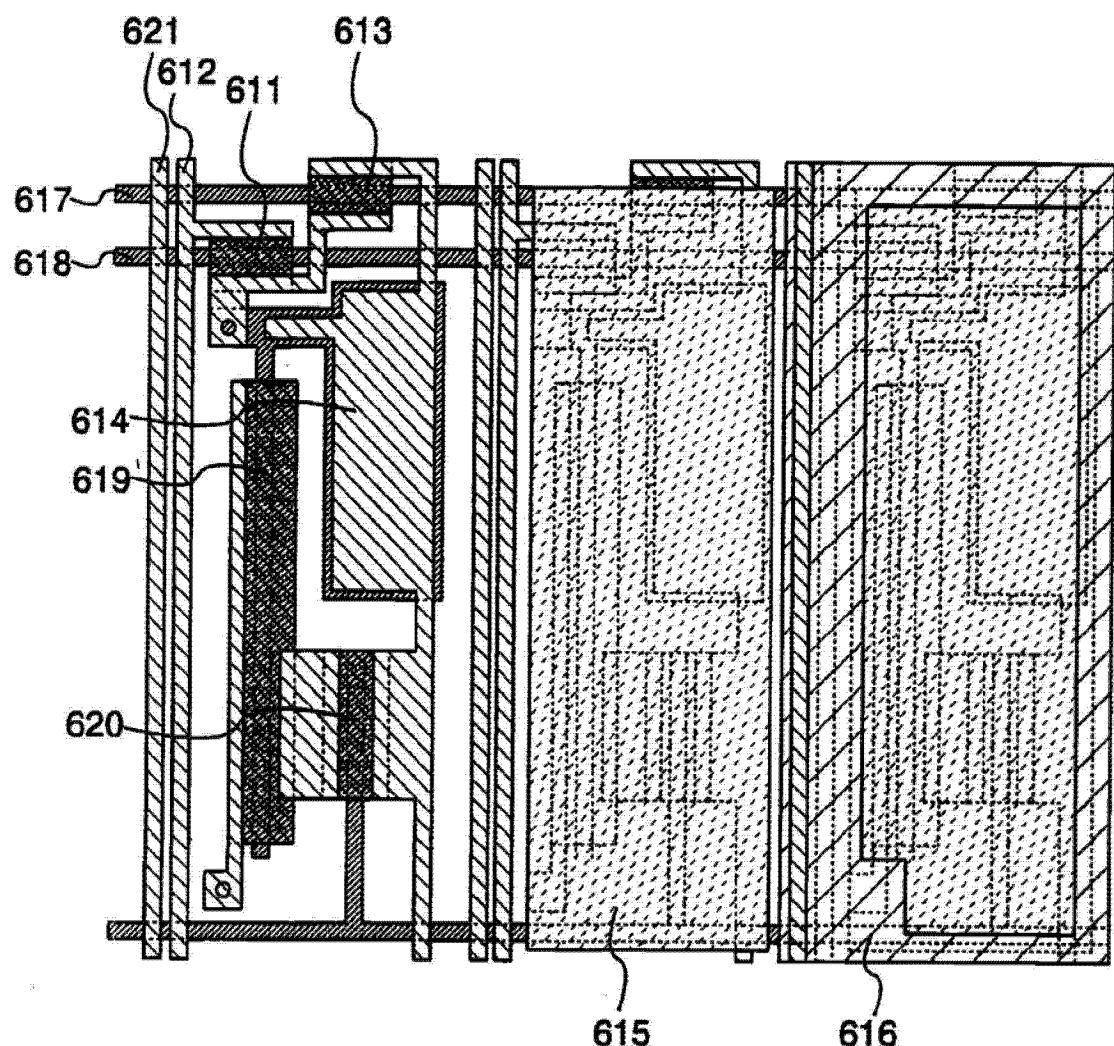

[0145] 第一和第二版图示例示出了具有三个晶体管(3TFT/单元)的像素。像素包括开关晶体管 601、驱动晶体管 602、擦除晶体管 603、电容 604、排列成列的信号线 609 和辅助布线 610,以及排列成行的扫描线 607 和 608(图 20 和 21)。像素还包括包含在发光元件中的像素电极 605 和绝缘层 606。绝缘层 606 提供在相邻像素电极 605 之间,并具有开口部分以暴露辅助布线 610 和像素电极 605。辅助布线 610 通过提供在绝缘层 606 中的开口部分连接到反向电极。提供电致发光层以便通过绝缘层 606 中的开口部分与像素电极 605 接触,并提供反向电极以便与电致发光层接触。

[0146] 在图 20 所示的版图示例中,可以采用顶部发射、底部发射和双发射。另一方面,在图 21 所示的版图示例中,由于像素电极 605 提供在晶体管 601 至 603 之上,因此优选采用顶部发射。在图 21 中还可以采用双发射。在那种情况下,为了遮蔽晶体管 601 至 603,绝缘层 606 可以由屏蔽材料形成。

[0147] 第三和第四版图示例示出了具有四个晶体管(4TFT/单元)的像素。像素包括用于开关的晶体管 611、用于驱动的晶体管 619、用于电流控制的晶体管 620、用于擦除的晶体管 613、电容 614、排列成列的信号线 612 和辅助布线 621,以及排列成行的扫描线 617 和 618

(图 22 和 23)。像素还包括包含在发光元件中的像素电极 615 和绝缘层 616。绝缘层 616 具有开口部分以便暴露辅助布线 621 和像素电极 615。辅助布线 621 通过提供在绝缘层 616 中的开口部分连接到反向电极。而且，提供电致发光层以便通过绝缘层 616 中的开口部分与像素电极 615 接触，并提供反向电极以便与电致发光层接触。根据这种结构，像素电极 615 提供在晶体管 601、603、611、613、619 和 620 上以产生提高的孔径比。因此，在该结构中优选采用顶部发射。要指出的是，在图 22 中示出的版图示例中还可以采用双发射。在那种情况下，绝缘层 616 可以由屏蔽材料形成，以便遮蔽晶体管 611、613、619 和 620。

[0148] 在上述结构中，晶体管 601 至 603、611、613、619 和 620 包括用于沟道部分的非晶半导体或有机半导体。辅助布线 610 和 621 形成在和晶体管 601 至 603、611、613、619 和 620 的栅电极相同的层中，或形成在和连接到晶体管 601 至 603、611、613、619 和 620 的源电极或漏电极的连接布线相同的层中，或形成在和像素电极 605 和 615 相同的层中。

[0149] 本申请是基于 2003 年 6 月 17 日向日本专利局申请的日本专利申请序列号 No. 2003-172009，在此引入其内容作为参考。

[0150] 虽然已经参考附图以实施方式和实施例的方式全面描述了本发明，应当理解，各种变化和改进对本领域技术人员来说是显而易见的。因此，除非这种变化和改进脱离下文限定的本发明的范围，否则都应被包括其内。

图 1A

图 1B

图 1C

图 2

图 3A

图 3B

图 4A

图 4B

图 5

图 6

图 7

图 8A

图 8B

图 9A

图 9B

图 10A

图 10B

图 11A

图 11B

图 11C

图 11D

图 11E

图 11F

图 12A

图 12B

图 14A

图 14B

图 15A

图 15B

图 15C

图 15D

图 16A

图 16C

图 16B

图 16D

图 17A

图 17B

图 17C

图 17D

图 18B

图 18A

图 18C      图 18D

图 19A

图 19B

图 20

图 21

图 22

图 23

|                |                                                                                                                                                                                                                                                                                          |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示器件和电子设备                                                                                                                                                                                                                                                                                |         |            |

| 公开(公告)号        | <a href="#">CN102832228A</a>                                                                                                                                                                                                                                                             | 公开(公告)日 | 2012-12-19 |

| 申请号            | CN201210299566.X                                                                                                                                                                                                                                                                         | 申请日     | 2004-06-17 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                                                                                                                                                                             |         |            |

| 申请(专利权)人(译)    | 株式会社半导体能源研究所                                                                                                                                                                                                                                                                             |         |            |

| 当前申请(专利权)人(译)  | 株式会社半导体能源研究所                                                                                                                                                                                                                                                                             |         |            |

| [标]发明人         | 山崎舜平<br>小山润                                                                                                                                                                                                                                                                              |         |            |

| 发明人            | 山崎舜平<br>小山润                                                                                                                                                                                                                                                                              |         |            |

| IPC分类号         | H01L27/32 H01L27/12 G09G3/32 G09G3/20 G09F9/30 G09G3/00 H01L21/00 H01L29/76 H01L31/036<br>H01L31/112 H01L51/52                                                                                                                                                                           |         |            |

| CPC分类号         | G09G2300/0842 H01L27/3276 G09G2300/0866 G09G2300/0417 H01L51/5203 G09G2300/0426<br>G09G2300/0465 G09G2300/0861 G09G2320/043 G09G2310/0251 G09G2310/0286 G09G3/3233<br>G09G2320/0223 G09G2310/0256 G09G3/2022 H01L27/283 H01L27/156 H01L29/78669 H01L29<br>/78696 H01L51/0545 H01L51/0562 |         |            |

| 代理人(译)         | 王忠忠                                                                                                                                                                                                                                                                                      |         |            |

| 优先权            | 2003172009 2003-06-17 JP                                                                                                                                                                                                                                                                 |         |            |

| 其他公开文献         | <a href="#">CN102832228B</a>                                                                                                                                                                                                                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                                                                                                                                                                                           |         |            |

## 摘要(译)

一种显示器件，其中降低了由于晶体管特性的改变而引起的亮度改变，并防止了由于电阻值的改变而引起的图像质量退化。本发明包括其沟道部分由非晶半导体或有机半导体构成的晶体管，连接到该晶体管的源电极或漏电极的连接布线，具有包括像素电极、电致发光层和反向电极的叠层结构的发光元件，环绕像素电极端部的绝缘层，和形成在和晶体管的栅电极、连接布线、或像素电极相同的层上的辅助布线。而且，连接布线连接到像素电极，且辅助布线通过提供在绝缘层中的开口部分连接到反向电极。