(12) 发明专利申请

(10) 申请公布号 CN 102569342 A

(43) 申请公布日 2012.07.11

(21) 申请号 201110373008.9

(22) 申请日 2005.12.02

(30) 优先权数据

2004-353457 2004.12.06 JP

(62) 分案原申请数据

200580041540.3 2005.12.02

(71) 申请人 株式会社半导体能源研究所

地址 日本神奈川县

(72) 发明人 吉田泰则 木村肇 前川慎志

中村理 山崎舜平

(74) 专利代理机构 上海专利商标事务所有限公司 31100

代理人 杨洁

(51) Int. Cl.

H01L 27/32 (2006.01)

权利要求书 3 页 说明书 43 页 附图 29 页

(54) 发明名称

显示装置

(57) 摘要

本发明提供一种可执行多灰度彩色显示的有源矩阵EL显示装置。特别地，本发明通过可选择性地形成图案的制造方法低成本地提供大的有源矩阵EL显示装置。像素部分中的电源线通过可选择性地形成图案的制造方法排列成矩阵。此外，通过可选择性地形成图案的制作方法在相邻布线之间设置更长距离，可减小布线间的电容。

## 1. 一种半导体装置,包括:

基板;

在所述基板之上的薄膜晶体管,其中所述薄膜晶体管包括源极和漏极;

与所述源极和所述漏极之一电连接的电源线;

与所述源极和所述漏极的另一个电连接的电极;

其中所述电源线包括第一电源线和第二电源线,

其中所述第一电源线与所述第二电源线相交,以及

其中所述电源线包括氧化铟锡。

2. 如权利要求 1 所述的半导体装置,其特征在于,所述第一电源线包括氧化铟锡。

3. 如权利要求 1 所述的半导体装置,其特征在于,所述薄膜晶体管包括包含硅的半导体层。

4. 如权利要求 1 所述的半导体装置,其特征在于,所述薄膜晶体管包括包含锗的半导体层。

5. 如权利要求 1 所述的半导体装置,其特征在于,所述电极包括氧化铟锡。

6. 如权利要求 1 所述的半导体装置,其特征在于,所述半导体装置是有源矩阵 EL 显示装置。

7. 如权利要求 1 所述的半导体装置,其特征在于,还包括与所述第一电源线基本平行的信号线。

8. 如权利要求 1 所述的半导体装置,其特征在于,所述薄膜晶体管包括多晶半导体。

9. 如权利要求 1 所述的半导体装置,其特征在于,所述电源线被排列为矩阵。

10. 如权利要求 2 所述的半导体装置,其特征在于,所述第一电源线与所述第二电源线电连接。

## 11. 一种半导体装置,包括:

基板;

在所述基板之上的薄膜晶体管,其中所述薄膜晶体管包括源极和漏极;

与所述源极和所述漏极之一电连接的电源线;

与所述源极和所述漏极的另一个电连接的第一电极;

在所述第一电极之上的绝缘层,其中所述绝缘层与所述第一电极的一部分重叠;

在所述第一电极之上的场致发光层;

在所述场致发光层之上的第二电极,

其中所述电源线包括第一电源线和第二电源线,

其中所述第一电源线与所述第二电源线相交,以及

其中所述电源线包括氧化铟锡。

12. 如权利要求 11 所述的半导体装置,其特征在于,所述第一电源线包括氧化铟锡。

13. 如权利要求 11 所述的半导体装置,其特征在于,所述薄膜晶体管包括包含硅的半导体层。

14. 如权利要求 11 所述的半导体装置,其特征在于,所述薄膜晶体管包括包含锗的半导体层。

15. 如权利要求 11 所述的半导体装置,其特征在于,所述第一电极包括氧化铟锡。

16. 如权利要求 11 所述的半导体装置,其特征在于,所述绝缘层包括聚酰亚胺。

17. 如权利要求 11 所述的半导体装置,其特征在于,所述半导体装置是有源矩阵 EL 显示装置。

18. 如权利要求 11 所述的半导体装置,其特征在于,还包括与所述第一电源线基本平行的信号线。

19. 如权利要求 11 所述的半导体装置,其特征在于,所述薄膜晶体管包括多晶半导体。

20. 如权利要求 11 所述的半导体装置,其特征在于,所述电源线排列为矩阵。

21. 如权利要求 12 所述的半导体装置,其特征在于,所述第一电源线与所述第二电源线电连接。

22. 一种半导体装置,包括:

基板;

在所述基板之上的薄膜晶体管,其中所述薄膜晶体管包括源极和漏极;

与所述源极和所述漏极之一电连接的电源线;

与所述源极和所述漏极的另一个电连接的第一电极;

在所述第一电极之上的绝缘层,其中所述绝缘层与所述第一电极的一部分重叠;

在所述第一电极之上的场致发光层;

在所述场致发光层之上的第二电极,

其中所述电源线包括第一电源线和第二电源线,

其中所述第一电源线与所述第二电源线相交,

其中所述电源线包括氧化铟锡,以及

其中所述绝缘层包括氧化硅。

23. 如权利要求 22 所述的半导体装置,其特征在于,所述第一电源线包括氧化铟锡。

24. 如权利要求 22 所述的半导体装置,其特征在于,所述薄膜晶体管包括包含硅的半导体层。

25. 如权利要求 22 所述的半导体装置,其特征在于,所述薄膜晶体管包括包含锗的半导体层。

26. 如权利要求 22 所述的半导体装置,其特征在于,所述第一电极包括氧化铟锡。

27. 如权利要求 22 所述的半导体装置,其特征在于,所述半导体装置是有源矩阵 EL 显示装置。

28. 如权利要求 22 所述的半导体装置,其特征在于,还包括与所述第一电源线基本平行的信号线。

29. 如权利要求 22 所述的半导体装置,其特征在于,所述薄膜晶体管包括多晶半导体。

30. 如权利要求 22 所述的半导体装置,其特征在于,所述电源线排列为矩阵。

31. 如权利要求 23 所述的半导体装置,其特征在于,所述第一电源线与所述第二电源线电连接。

32. 一种半导体装置,包括:

基板;

在所述基板之上的薄膜晶体管,其中所述薄膜晶体管包括源极和漏极;

与所述源极和所述漏极之一电连接的电源线;

与所述源极和所述漏极的另一个电连接的发光元件；

其中所述电源线包括第一电源线和第二电源线，

其中所述第一电源线与所述第二电源线相交，以及

其中所述电源线包括氧化铟锡。

33. 如权利要求 32 所述的半导体装置，其特征在于，所述第一电源线包括氧化铟锡。

34. 如权利要求 32 所述的半导体装置，其特征在于，所述薄膜晶体管包括包含硅的半导体层。

35. 如权利要求 32 所述的半导体装置，其特征在于，所述薄膜晶体管包括包含锗的半导体层。

36. 如权利要求 32 所述的半导体装置，其特征在于，所述发光元件的电极包括氧化铟锡。

37. 如权利要求 32 所述的半导体装置，其特征在于，所述发光元件直接与所述源极和所述漏极的另一个连接。

38. 如权利要求 32 所述的半导体装置，其特征在于，所述半导体装置是有源矩阵 EL 显示装置。

39. 如权利要求 32 所述的半导体装置，其特征在于，还包括与所述第一电源线基本平行的信号线。

40. 如权利要求 32 所述的半导体装置，其特征在于，所述薄膜晶体管包括多晶半导体。

41. 如权利要求 32 所述的半导体装置，其特征在于，所述电源线被排列为矩阵。

42. 如权利要求 33 所述的半导体装置，其特征在于，所述第一电源线与所述第二电源线电连接。

## 显示装置

[0001] 本申请是申请日为 2007 年 6 月 4 日,申请号为 200580041540.3(国际申请号为 PCT/JP2005/022608),名为“显示装置”申请的分案申请。”

### 技术领域

[0002] 本发明涉及其中在基板上形成 EL(场致发光)元件的电子显示器(电光装置),尤其涉及使用半导体元件(使用半导体薄膜的元件)的显示装置。此外,本发明还涉及在显示部分中使用 EL 显示装置的电子设备。

### 背景技术

[0003] 近年来,在基板上形成薄膜晶体管(在本说明书中以下称为 TFT)的技术对有源矩阵显示装置的应用已得到了有力地推动和开发。具体地,使用诸如多晶硅等多晶半导体膜的 TFT 在场效应迁移率(也称为迁移率)方面比使用诸如非晶硅等非晶半导体膜的常规 TFT 更高,这允许快速工作。因此,通常由基板外的驱动电路控制的像素现在可由在与像素相同的基板上形成的驱动电路来控制。

[0004] 在使用这样的多晶半导体膜的有源矩阵显示装置中,各种电路和元件可在同一基板上形成。因此,有多方面的优点,诸如制造成本的下降、显示装置尺寸的缩小、成品率的提高以及生产量的降低。

[0005] 此外,已起动了对将 EL 元件用作自发光元件的有源矩阵 EL 显示装置的研究。EL 显示装置也称为有机 EL 显示器(OELD)或有机发光二极管(OLED)。

[0006] EL 元件具有其中一对电极(阳极和阴极)将一 EL 层夹在中间的结构,该 EL 层通常具有叠层结构。通常,有由 Eastman Kodak 公司的 Tang 等人提出的“空穴输送层、发光层和电子输送层”的叠层结构。该结构具有相当高的发光效率,并用于正在研究和开发中的大多数 EL 显示装置。

[0007] 此外,也可采用空穴注入层、空穴输送层、发光层和电子输送层的叠层结构,或者空穴注入层、空穴输送层、发光层、电子输送层和阳极上的电子注入层的叠层结构。发光层可用磷光颜料等掺杂。

[0008] 在本说明书中,设置在阴极和阳极之间的所有层都统称为 EL 层。因此,空穴注入层、空穴输送层、发光层、电子输送层和电子注入层等都被包括在 EL 层中。

[0009] 当从该对电极向具有上述结构的 EL 层施加预定电压时,载流子在发光层中重组并发光。在本说明书中,当 EL 元件发光时,称为 EL 元件被驱动。此外,在本说明书中,由阳极、EL 层和阴极构成的发光元件被称为 EL 元件。

[0010] 注意,在本说明书中,EL 元件可利用因单重激发态引起的发光(磷光)和因三重激发态引起的发光(荧光)。

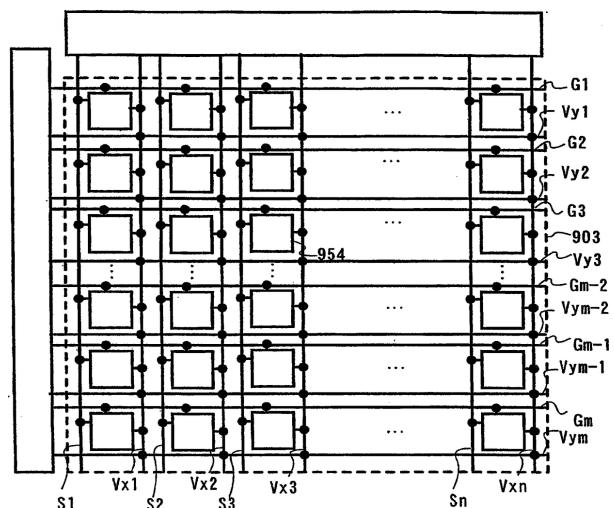

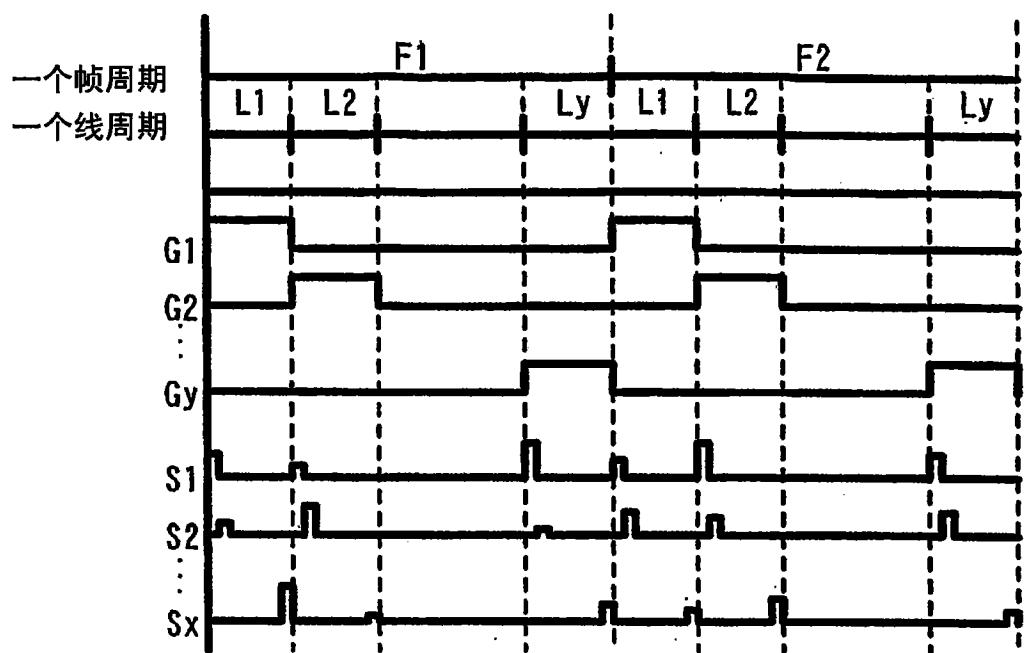

[0011] EL 显示装置可通过模拟驱动方法(模拟驱动)和数字驱动方法(数字驱动)来驱动。首先,参照图 1 和 2 对 EL 显示装置的模拟驱动进行描述。

[0012] 图 1 示出模拟驱动 EL 显示装置的像素部分 100 的结构。各自有来自栅极信号线

驱动电路的选择信号输入的栅极信号线 (G1 ~ Gy) 连接到每一像素的开关 TFT101 的栅电极。每一像素的开关 TFT 101 的源极区和漏极区之一连接到有模拟视频信号输入的源极信号线 (也称为数据信号线) (S1 ~ Sx) 中的每一条, 另一个则连接到每一像素的驱动 TFT 104 的栅电极和电容器 108。

[0013] 每一像素的驱动 TFT 104 的源极区和漏极区之一连接到电源线 (V1 ~ Vx) 中的每一条, 而另一个则连接到 EL 元件 106。电源线 (V1 ~ Vx) 中的每一条的电位称为电源电位。电源线 (V1 ~ Vx) 中的每一条连接到每一像素的电容器 108。

[0014] EL 元件 106 具有阳极、阴极和设置在阳极和阴极之间的 EL 层。在 EL 元件 106 的阳极连接到驱动 TFT 104 的源极区或漏极区的情形中, EL 元件 106 的阳极是像素电极而其阴极是反电极。在 EL 元件 106 的阴极连接到驱动 TFT 104 的源极区或漏极区的情形中, EL 元件 106 的阳极是反电极而其阴极是像素电极。

[0015] 在本说明书中, 反电极的电位被称为反电位。向反电极施加反电位的电源被称为反电源。像素电极的电位与反电极的电位之间的电位差是施加于 EL 层的 EL 驱动电压。

[0016] 图 2 示出图 1 所示的通过模拟方法驱动的 EL 显示装置的时序图。从选择一条栅极信号线直到选择一条不同的栅极信号线的周期称为一个线周期 (L)。从显示一个图像直到显示下一个图像的周期对应于一个帧周期 (F)。在图 1 的 EL 显示装置的情形中有 y 条栅极信号线, 因此在一个帧周期中设置 y 个线周期 (L1 ~ Ly)。

[0017] 电源线 V1 ~ Vx 被保持在某电源电位。作为反电极电位的反电位也被保持为某电位。反电位和电源电位具有使 EL 元件发光的电位差。

[0018] 在第一线周期 (L1) 中, 栅极信号线 G1 输入有来自栅极信号线驱动电路的选择信号。然后, 模拟视频信号被依次输入到源极信号线 S1 ~ Sx。由于所有连接到栅极信号线 G1 的开关 TFT 都导通, 因此输入到源极信号线 S1 ~ Sx 的模拟视频信号通过开关 TFT 输入到驱动 TFT 的栅电极。

[0019] 流过驱动 TFT 的沟道形成区的电流量受其栅极电压控制。

[0020] 在此, 对其中驱动 TFT 的源极区连接到电源线、而其漏极区连接到 EL 元件的一个示例进行描述。

[0021] 当驱动 TFT 的源极区连接到电源线时, 像素部分中的每个像素都输入有相同的电位。此时, 当向源极信号线输入模拟信号时, 信号电压的电位与驱动 TFT 的源极区的电位之间的电位差变成栅极电压。流向 EL 元件的电流取决于驱动 TFT 的栅极电压。在此, EL 元件的亮度与在 EL 元件的相对电极之间流动的电流成正比。这样, EL 元件取决于模拟视频信号的电压发光。

[0022] 重复上述操作, 并且当模拟视频信号被输入到所有源极信号线 (S1 ~ Sx) 时, 第一个线周期 (L1) 结束。要注意, 直到模拟视频信号全部输入的周期以及水平回扫线周期一起可以是一个线周期。然后, 在第二个线周期 (L2) 中, 栅极信号线 G2 输入有一选择信号。与第一线周期 (L1) 的情形相似, 模拟视频信号被依次输入源极信号线 (S1 ~ Sx)。

[0023] 当向所有栅极信号线 (G1 ~ Gy) 输入选择信号时, 所有线周期 (L1 ~ Ly) 结束。当所有线周期 (L1 ~ Ly) 结束时, 一个帧周期结束。在一个帧周期中, 所有像素执行显示以形成一个图像。要注意, 全部线周期 (L1 ~ Ly) 与一个垂直回扫线周期一起可以是一个帧周期。

[0024] 如上所述,由 EL 元件发出的光的量受模拟视频信号控制。通过控制发光量,执行灰度显示。该方法是所谓的模拟驱动方法,其中灰度显示通过改变输入到源极信号线的模拟视频信号的电压来执行。

[0025] 然后,对 EL 显示装置的数字驱动进行描述。在一数字灰度方法中,驱动 TFT104 的栅极 - 源极电压  $V_g$  分两级工作:在没有电流流向 EL 元件 106 的区域中(等于发光起动电压或更低),或者在有最大电流流入的区域中(等于亮度饱和电压或更高)。即,EL 元件发光或不发光。

[0026] EL 显示器主要采用其中诸如 TFT 的阈值等特性的变化不易于影响显示的数字灰度显示方法。然而,在数字灰度方法的情形中,本身仅可显示两个灰度电平。因此,提出了要结合另一种方法采用数字灰度方法的多种技术,以执行多灰度显示。

[0027] 这些技术之一是一种组合使用面积灰度方法和数字灰度方法的方法。面积灰度方法是通过控制发光部分的面积来显示灰度的方法。即,一个像素被分成多个子像素,且发光的子像素的数量和面积受到控制以显示一灰度。该方法的缺点在于在子像素的数量不能增加时不能容易地实现高分辨率和多灰度显示。非专利文献 1、2 等公开了该面积灰度方法。

[0028] 另一种实现多灰度显示的方法是组合使用时间灰度方法和数字灰度方法的一种方法。该时间灰度方法是通过利用发光时间差来显示灰度的方法。即,一个帧周期被分成多个子帧周期,且灰度通过控制发光的子帧周期的数量和长度来显示(参见专利文献 1)。

[0029] 非专利文献 3 公开了组合使用数字灰度方法、面积灰度方法和时间灰度方法的情形。

[0030] 接着,对通过数字灰度方法显示灰度的情形中的恒定电流驱动和恒定电压驱动进行描述。

[0031] 恒定电流驱动是当 EL 元件 106 发光时使驱动 TFT 104 在饱和区中工作、并向所有像素提供恒定电流的一种驱动方法。该驱动方法的优点在于即使在 EL 元件 106 退化且 V-I 特性改变也可向 EL 元件 106 提供恒定电流,这导致 EL 显示装置的寿命延长。

[0032] 另一方面,恒定电压驱动是当 EL 元件 106 发光时使驱动 TFT 104 在线性区中工作、并向所有像素提供恒定电压的一种驱动方法。该驱动方法的优点在于即使在驱动 TFT 104 的特性改变时也可向 EL 元件 106 施加恒定电压,这导致像素的亮度没有变化和较高的显示质量。

[0033] [ 非专利文献 1]

[0034] Euro Display 99 会后新闻 :P71 :“TFT-LEPD with Image Uniformity by Area Ratio Gray Scale”

[0035] [ 非专利文献 2]

[0036] IEDM 99 :P107 :“Technology for Active Matrix Light Emitting Polymer Displays”

[0037] [ 非专利文献 3]

[0038] IDW '99 :P171 :“Low-Temperature Poly-Si TFT Driven Light-Emitting-Polymer Displays and Digital Gray Scale for Uniformity”

[0039] [ 专利文献 1]

[0040] 日本专利公开 No. 2001-324958

## 发明内容

[0041] 本发明提供一种可低成本制造且成品率良好的高分辨率大 EL 显示装置。因此, 存在以下问题。

[0042] 首先, 对组合使用数字灰度方法和时间灰度方法作为 EL 显示装置的驱动方法的情形中的问题进行描述。在组合使用数字灰度方法和时间灰度方法的情形中, 一个帧周期被分成多个子帧周期, 并且发光的子帧周期的数量和长度受到控制以显示一灰度。即, 与通过模拟灰度方法显示一个图像所花的时间相比, 在组合使用数字灰度方法和时间灰度方法的情形中, 只能花几个子帧部分的时间来显示一个图像, 这需要驱动器电路以与模拟灰度方法相比相当快的速度来工作。

[0043] 其次, 限制了驱动电路的工作频率。如果一个帧被分成太多的子帧或者分辨率太高, 则不能提供足够的写入时间。即, 组合使用数字灰度方法和时间灰度方法时的问题之一是写入时间不足。据此, 需要提供尽可能长的写入时间。

[0044] 然后, 对寄生电容增大的问题进行描述。显示装置越大且分辨率越高, 则显示装置具有布线越长的像素部分。此外, 跨接布线的布线数增加, 这导致像素部分中布线的寄生电容增大。

[0045] 当寄生电容增大时, 通过布线传输的电信号的波形的钝度也增大。波形的钝度会阻碍信号的正确传输并降低显示质量。即, 制造高分辨率大 EL 显示装置时的问题之一是寄生电容的增大。据此, 寄生电容需要尽可能地小。

[0046] 然后, 对低成本制造中的问题进行描述。目前, TFT 和使用 TFT 的电子电路通常通过在基板上层叠诸如半导体、绝缘体和导体等各种薄膜, 并通过光刻技术适当地形成预定图案来制造。光刻技术是通过利用光来将诸如由在称为光掩模的在透光平面表面上不透光的材料构成的电路等图案转移到基板上的一种技术。该技术广泛用于半导体集成电路等的制造步骤。

[0047] 使用光刻技术的制造步骤甚至仅对由称为光刻胶的光敏有机树脂材料形成的掩模图案也需要许多步骤, 诸如曝光、显影、烘干以及剥离等。因此, 当光刻步骤的数量增加时, 制造成本必然增加。

[0048] 然后, 对布线电阻的问题进行描述。首先, 对将模拟驱动方法用作 EL 显示装置的驱动方法的情形进行描述。

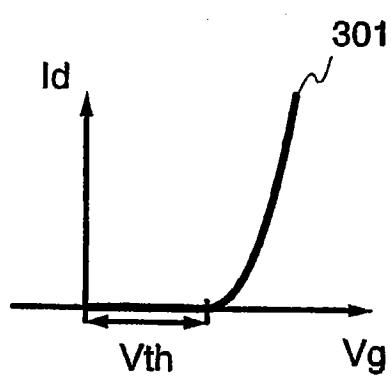

[0049] 图 3 是示出驱动 TFT 在饱和区中 ( $V_{ds} > V_g - V_{th}$ ) 的特性的曲线图。在此,  $V_{ds}$  是源极 - 漏极电压,  $V_g$  是栅极 - 源极电压, 而  $V_{th}$  是阈值电压。参考标号 301 指  $I_d - V_g$  特性 (或  $I_d - V_g$  曲线)。此处,  $I_d$  表示漏极电流。根据该曲线图, 可知道 因任何栅极电压而流动的电流的量。

[0050] 在模拟驱动方法中, 驱动 TFT 在饱和区中工作, 且栅极电压被改变以改变其漏极电流。

[0051] 在开关 TFT 导通时通过源极信号线输入到像素的模拟视频信号被施加到驱动 TFT 的栅电极。这样, 驱动 TFT 的栅极电压改变。此时, 漏极电流根据  $I_d - V_g$  特性按与栅电压 1 : 1 的比例设置。这样, 预定漏极电流根据输入到驱动 TFT 的栅电极的模拟视频信号的电

压被提供给 EL 元件。EL 元件发光,其发光量与所提供的电流的量相一致。

[0052] 如上所述,EL 元件的发光量受模拟视频信号控制,灰度显示根据该模拟视频信号来执行。

[0053] 在此,即使从源极信号线输入了相同的信号,每一像素的驱动 TFT 的栅极电压在驱动 TFT 的源极区的电位变化时还是会变化。在此,驱动 TFT 的源极区的电位从电源线施加。然而,电源线的电位由于布线电阻引起的电位降而取决于在像素部分中的位置改变。

[0054] 此外,在电源线的布线电阻较小的情形、显示装置相对较小的情形、或者流过电源线的电流相对较小的情形中,因布线电阻引起的电位降而导致电源线电位改变并不具有太多的效果,但除上述情形之外仍有显著的效果,特别是在显示装置相对较大的情形中。

[0055] 特别地,当显示装置较大时,从外部输入端到像素部分的每一电源线的距离中会有较大变化,因此电源线引线部分中布线长度就会存在较大变化。因此,因电源线引线部分的电位降导致电源线电位的变化变大。

[0056] 因上述因素引起的电源线电位的变化影响每一像素中 EL 元件的亮度并改变显示亮度,这导致显示不均匀。

[0057] 在下文中,对电源线电位中的变化的具体示例进行描述。

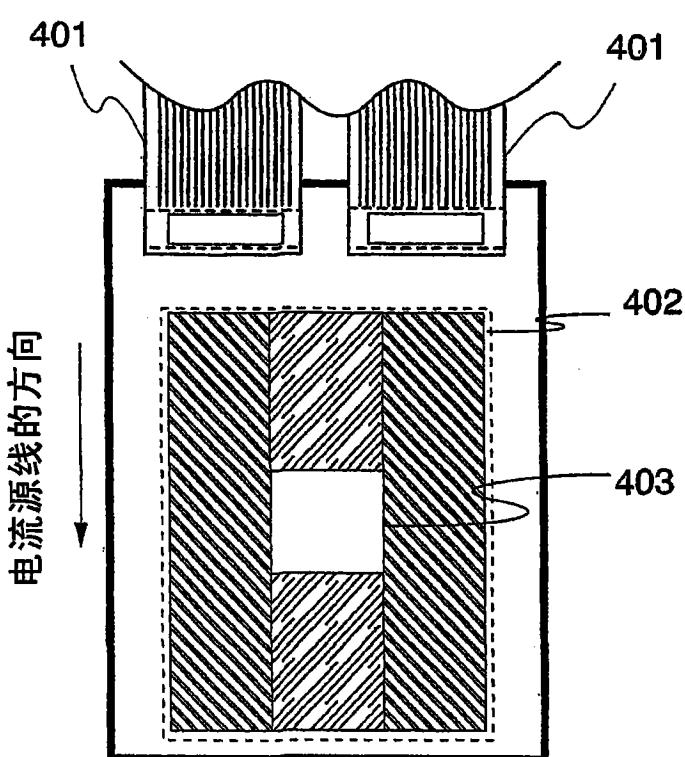

[0058] 如图 4 所示,当在显示屏中显示白框或黑框时,发生称为串扰的现象。这是框上下的部分与框旁边的部分之间发生亮度差的现象。

[0059] 串扰是一不同电流流到框上、下、旁边的像素中的驱动 TFT 104 的现象。该差异是因平行于源极信号线 S1 和 S2 排列的电源线 V1 和 V2 引起的。

[0060] 在如图 4 所示白框在显示屏的一部分中显示的情形中,对于显示白框的像素的电源线与仅向不显示白框的像素供应电源的电源线相比由于布线电阻而具有更大的电位降,因为电流通过显示白框的像素中的驱动 TFT 的源极和漏极被提供给 EL 元件。因此,白框上下部分比不显示白框的其它像素暗。

[0061] 在此,在显示装置的显示屏较小的情形中,该问题不会发生。然而,随着显示装置的显示屏越来越大,流向 EL 元件的电流的总量与显示屏的面积成比例地增加。

[0062] 例如,当比较流向显示屏对角线为 4 英寸的显示装置和显示屏对角线为 20 英寸的显示装置中的 EL 元件的电流总量时,后一显示屏是前者的 25 倍,因而提供给 EL 元件的电流的总量也约为 25 倍大。

[0063] 因此,前述电位降在具有大显示屏的显示装置中相当成问题。

[0064] 例如,假设显示屏对角线为 20 英寸的显示装置的布线长度为 700 毫米、宽度为 10 毫米、且薄层电阻为  $0.5 \Omega$ ,则当电流为 1A 时,会发生 10V 的电位降并且不能进行正常的显示。

[0065] 然后,对采用恒压驱动以及数字驱动方法作为 EL 显示装置的驱动方法的情形中的布线电阻问题进行描述。

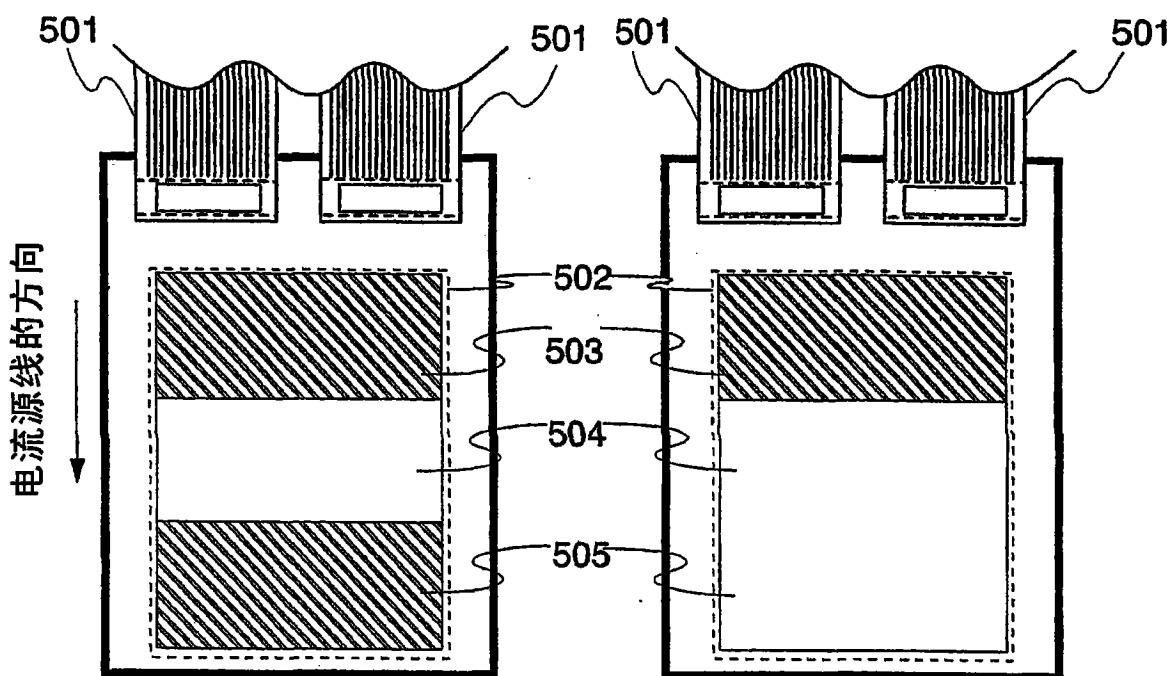

[0066] 当采用恒压驱动时,恒定电压被施加于每一像素中的 EL 元件 106。因此,可获得能显示相当高质量图像的 EL 显示装置,且其像素的亮度不受驱动 TFT 104 特性变化的影响。然而,如果布线电阻较高,则不可能满足进行恒压驱动的必要条件,即向每一像素中的 EL 元件 106 提供恒定电压。对此将参照图 5A 和 5B 进行描述。

[0067] 图 5A 示出其中全部像素的 1/3 同时发光的面板。图 5B 示出全部像素的 2/3 同时

发光的面板。

[0068] 当图 5A 和 5B 之间的不同数量的像素同时发光时,在发光时不同电流值被提供给像素部分中的电源线 (V1 ~ Vx)。在此,如果在像素部分中的电源线 (V1 ~ Vx) 中有布线电阻,则电压根据电流量下降。即,在电流值不同的图 5A 和 5B 中,对每个像素施加的电压不同。当施加不同电压时,EL 元件的亮度在如图 5A 所示的显示时和如图 5B 的显示时之间有所不同。

[0069] 这样,当每个像素的亮度取决于所显示图像的发光率改变时,它在通过时间灰度方法显示灰度时会受到不利影响。例如,显示三个灰度电平的情形由图 5A 和 5B 中的面板连续显示相同时段。此时,假设显示区域 503 显示灰度 0,显示区域 504 显示灰度 2,而显示区域 505 显示灰度 1。然而,有了布线电阻,显示区域 505 显示低于 1 的灰度,因为图 5A 每个像素的亮度比图 5B 的高。这样,有了布线电阻,在用数字驱动方法进行恒压驱动的情形中不能显示期望灰度。

[0070] 当电源线 (V1 ~ Vx) 的布线电阻越高时,该亮度差异越大。显示装置越大,则电源线越长,从而使得布线电阻越高。即,制造高分辨率大 EL 显示装置时的问题之一是布线电阻的增大。据此,布线电阻需要尽可能地低。

[0071] 本发明鉴于上述问题而作出,以提供能进行清晰的多灰度彩色显示的有源矩阵 EL 显示装置。本发明还提供使用这样的有源矩阵 EL 显示装置的高功能电子装置。

[0072] 本发明提供可低成本制造且成品率良好的高分辨率大 EL 显示装置。据此,本发明的配置如下所述。

[0073] 本发明的一种配置包括一种显示装置,它包括:绝缘表面上的多条源极信号线、多条栅极信号线、成列的多条电源线、成排的多条电源线、以及排列成矩阵的多个像素,其中该多个像素的每一个都包括开关薄膜晶体管、驱动薄膜晶体管、以及发光元件,其中该多个像素的每一个连接到成列的多条电源线之一、以及成排的多条电源线之一,且其中绝缘薄膜在多条源极信号线、多条栅极信号线、成列的多条电源线以及成排的多条电源线的至少之一下的部分中形成。

[0074] 本发明的另一种配置包括一种制造显示装置的方法,包括以下步骤:在绝缘表面上形成多条源极信号线;形成多条栅极信号线;形成排列成矩阵的多个像素,并且所述多个像素的每一个包括开关薄膜晶体管、驱动薄膜晶体管、以及发光元件;形成成列的多条电源线;形成成排的多条电源线;以及通过微滴排放法或印刷法将多个像素的每一个连接到成列的多条电源线之一和成排的多条电源线之一。

[0075] 本发明的又一种配置包括一种制造显示装置的方法,包括以下步骤:在绝缘表面上形成源极信号线;形成栅极信号线;形成电源线;形成包括开关薄膜晶体管、驱动薄膜晶体管、以及发光元件的像素;通过微滴排放法或印刷法在源极信号线、栅极信号线以及电源线的至少之一下的部分中形成一绝缘薄膜。

[0076] 在前述发明中,多条源极信号线、多条栅极信号线以及多条电源线之一通过溅射法或 CVD 法形成。

[0077] 在此,CVD 法包括等离子体 CVD 法 (RF 等离子体 CVD 法、微波 CVD 法、电子回旋共振 CVD 法、热丝 CVD 法等)、LPCVD 法,以及热 CVD 法。

[0078] 本发明是一种使用根据本发明上述配置的显示装置的个人计算机。

- [0079] 本发明是一种使用根据本发明上述配置的显示装置的电视机。

- [0080] 本发明是一种使用根据本发明上述配置的显示装置的诸如视频摄像机等摄像机。

- [0081] 本发明是一种使用根据本发明上述配置的显示装置的图像再现设备。

- [0082] 本发明是一种使用根据本发明上述配置的显示装置的头戴式显示器。

- [0083] 本发明是一种使用根据本发明上述配置的显示装置的便携式信息终端。

- [0084] 根据本发明,可提供可低成本制造且成品率良好的高分辨率大EL显示装置。此外,当可获得足够的信号写入时间时,信号可准确地输入到像素,由此可显示更清晰的图像。此外,作为可降低布线电阻的效应,可减少因布线电阻引起的图像质量缺陷。

## 附图说明

- [0085] 图1是示出EL显示装置的像素电路的示图。

- [0086] 图2是示出模拟驱动的驱动定时的示图。

- [0087] 图3是示出驱动TFT的特性的示图。

- [0088] 图4是通过框显示出串扰的示图。

- [0089] 图5A和5B是示出因电源线的布线电阻引起的电位效应的示图。

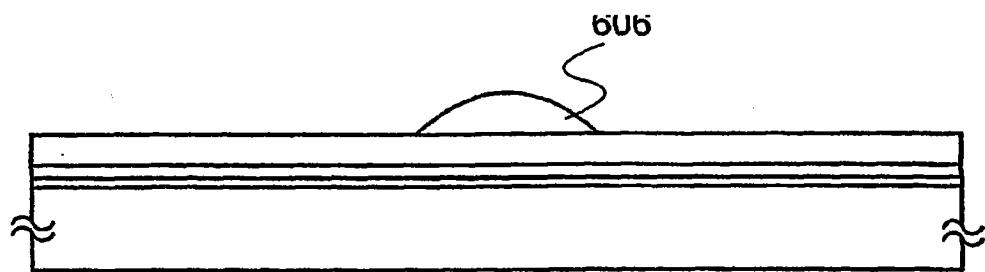

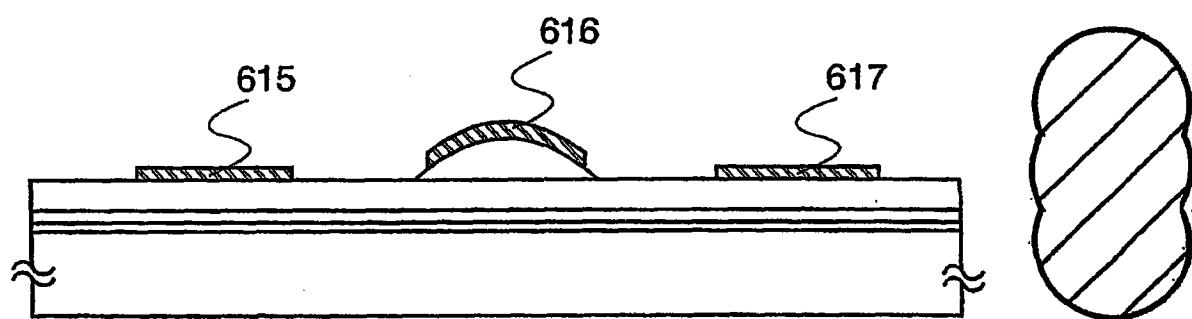

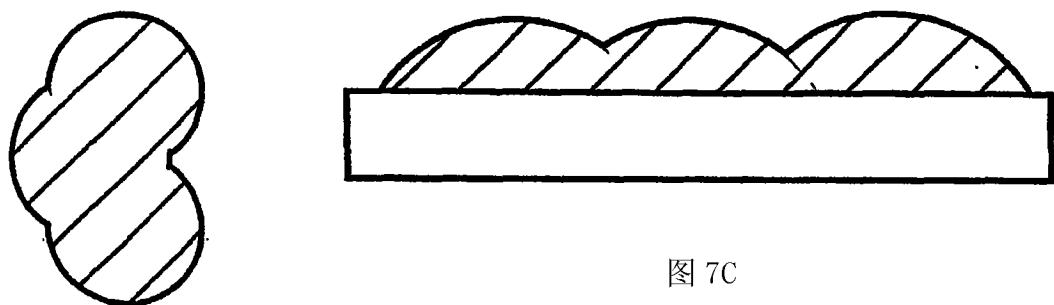

- [0090] 图6A-6C是示出降低布线之间的寄生电阻的结构的示图。

- [0091] 图7A-7D是示出引起布线电阻的变化的形状的示图。

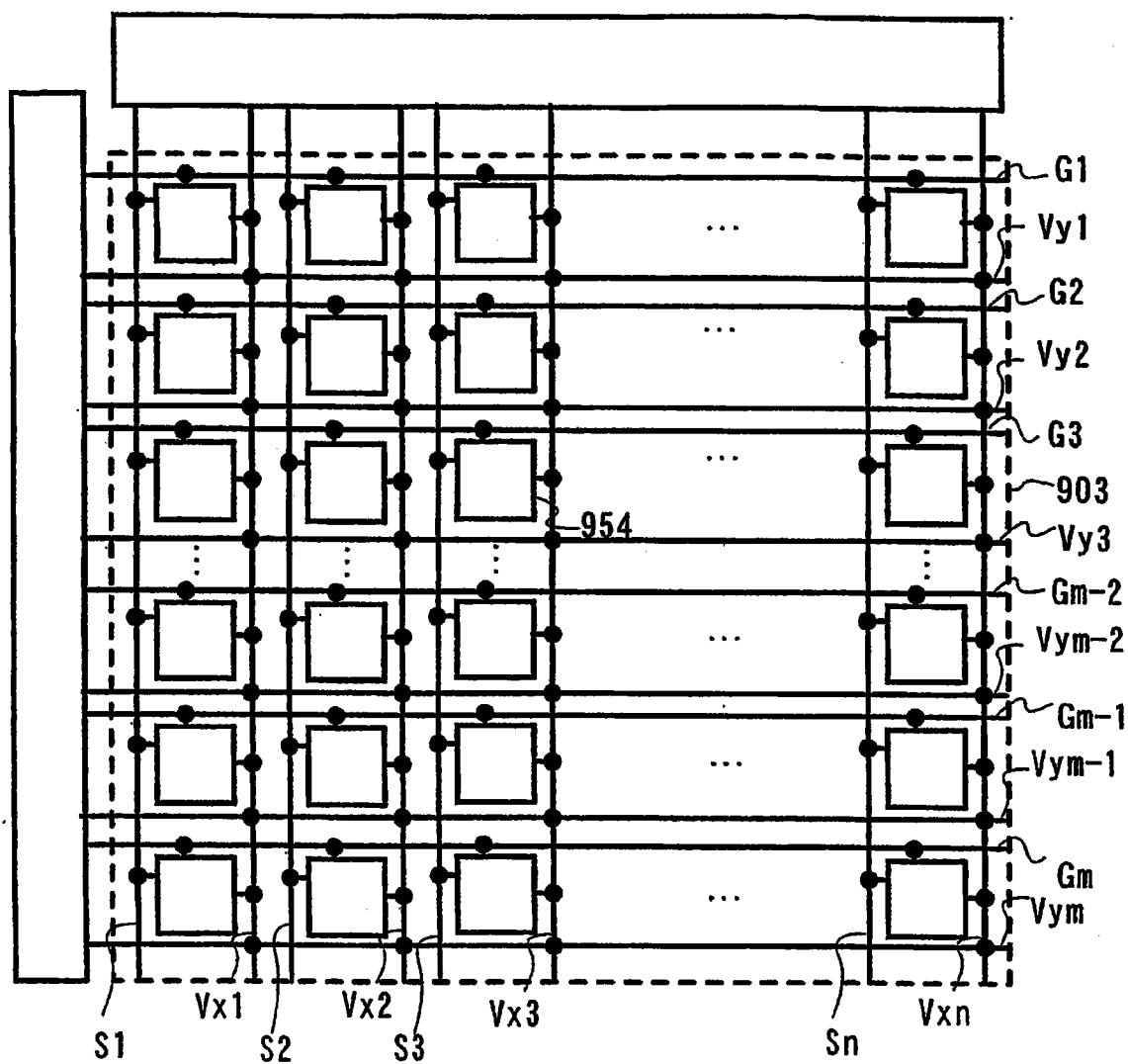

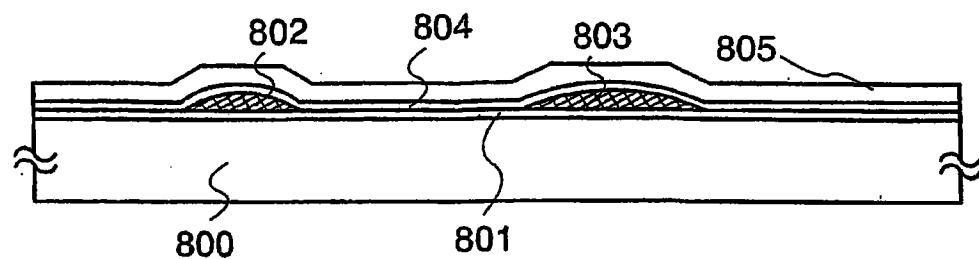

- [0092] 图8是示出本发明实施方式1的示图。

- [0093] 图9是示出本发明实施方式2的示图。

- [0094] 图10是示出本发明实施方式3的示图。

- [0095] 图11是示出本发明实施方式4的示图。

- [0096] 图12是示出本发明实施方式5的示图。

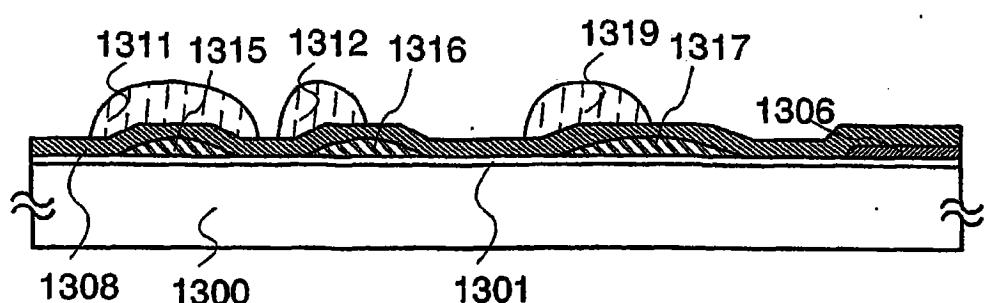

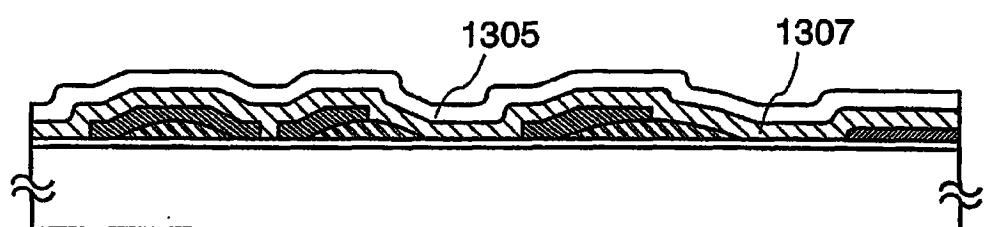

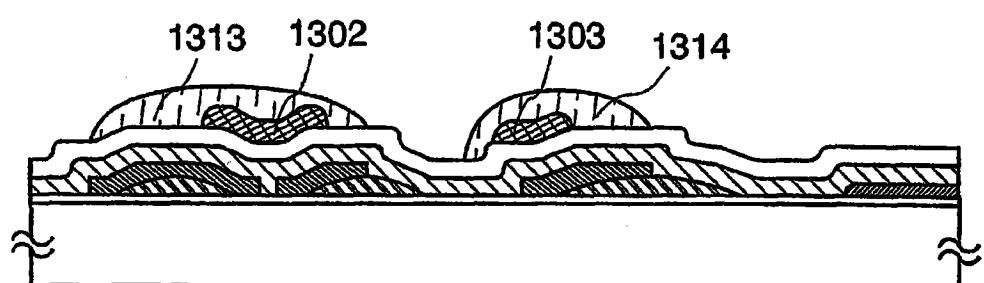

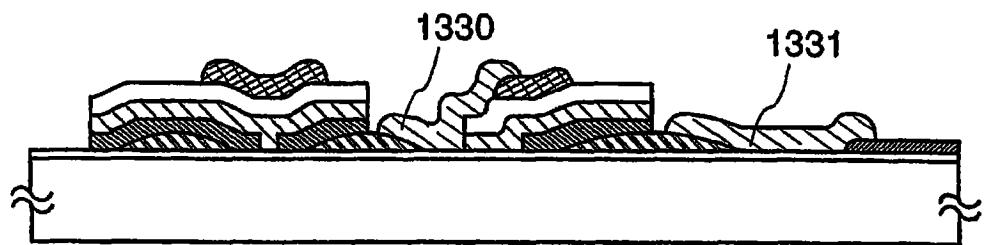

- [0097] 图13A-13D是示出可应用本发明的显示装置的制造方法的视图。

- [0098] 图14A和14B是示出可应用本发明的显示装置的制造方法的视图。

- [0099] 图15是示出可应用于本发明的微滴排放设备的配置的视图。

- [0100] 图16A是可应用于本发明的显示装置的像素部分的平面俯视图,而图16B是其电路图。

- [0101] 图17是示出可应用于本发明的显示装置的视图。

- [0102] 图18A-18D是示出可应用本发明的显示装置的制造方法的视图。

- [0103] 图19A和19B是示出可应用本发明的显示装置的制造方法的视图。

- [0104] 图20A-20D是示出可应用本发明的显示装置的制造方法的视图。

- [0105] 图21是示出可应用本发明的显示装置的制造方法的视图。

- [0106] 图22A-22D是示出可应用本发明的显示装置的制造方法的视图。

- [0107] 图23A和23B是示出可应用本发明的显示装置的制造方法的视图。

- [0108] 图24A-24D是示出可应用本发明的显示装置的制造方法的视图。

- [0109] 图25A和25B是示出可应用本发明的显示装置的制造方法的视图。

- [0110] 图26A-26D是示出可应用本发明的显示装置的制造方法的视图。

- [0111] 图27是示出可应用本发明的显示装置的制造方法的视图。

- [0112] 图28A-28D是示出可应用本发明的显示装置的制造方法的视图。

- [0113] 图 29A 和 29B 是示出可应用本发明的显示装置的制造方法的视图。

- [0114] 图 30A-30C 是示出可应用本发明的显示装置的制造方法的视图。

- [0115] 图 31 是作为可应用本发明的半导体装置的一种模式的面板的平面俯视图。

- [0116] 图 32 是示出本发明一电子设备的主要配置的框图。

- [0117] 图 33 是示出应用本发明的一电子设备的视图。

- [0118] 图 34A-34C 是示出可应用本发明的电子设备的视图。

- [0119] 图 35A-35C 是示出可应用本发明的电子设备的视图。

## 具体实施方式

[0120] 尽管本发明将参照附图通过各实施方式进行全面的描述,但可以理解各种改变和更改对本领域技术人员是显而易见的。因此,除非这样的改变和更改背离了本发明的范围,否则它们应当被解释为包含在内。注意,在各实施方式中等同部分或具有等同功能的部分由相同的标号表示,并略去其详细描述。

[0121] 用于本发明的晶体管不排他性地限于某一类型。它可以是使用以非晶硅或多晶硅为代表的非单晶硅半导体薄膜的薄膜晶体管 (TFT)、通过使用半导体基板或 SOI (绝缘体上硅) 基板形成的 MOS 晶体管、结型晶体管、双极晶体管、使用有机半导体的晶体管、碳纳米管等。此外,其上安装晶体管的基板不排他性地限于某一类型。它可以是单晶基板、SOI 基板、玻璃基板等。

### [实施方式 1]

[0123] 参照图 13A-16B、图 8 以及图 6A-6C 对本发明一实施方式进行描述。首先,本发明的目的之一是低成本地制造 EL 显示装置。据此,通过减少光刻步骤的数量来制造 TFT。

[0124] 作为减少光刻步骤的数量的一种方法,提出了一种用于制造显示装置的方法,其中制造显示面板所需图案的一个或多个,诸如用于形成布线层的导电层或用于形成预定图案的电极或掩模层,通过可选择性地形成图案的方法来形成。作为可选择性地形成图案的方法,提出了一种微滴排放法(取决于系统也称为喷墨法),它可通过选择性地排放为具体目的而混合的混合物的微滴排放来形成预定图案。此外,通过采用用于转移或绘制图案的方法,例如印刷法(用于通过丝网印刷、胶印等形成图案的方法)等,可实现成本的降低。即,低成本制造 EL 显示装置时的问题之一是大量的光刻步骤。据此,光刻步骤的数量需要尽可能地少,这样可选择性地形成图案的方法就有效了。

[0125] 因此,在该实施方式中,EL 显示装置通过如下所述的作为可选择性地形成图案的 EL 显示装置的制造方法之一的微滴排放法来制造。注意,这仅仅是一个示例,且该实施方式并不限于该方法。

[0126] 首先,参照图 13A-14B 对显示装置的制造方法作出描述,该显示装置包括沟道保护型薄膜晶体管,其栅电极、源极或漏极布线通过改进粘性的手段来制造。

[0127] 用以改进粘性的基底膜 801 在基板 800 上形成,作为预先基础处理。基板 800 由诸如钡硼硅酸盐玻璃和铝硼硅酸盐玻璃等玻璃基板、石英基板、硅基板、金属基板、不锈钢基板、或对本实施方式中的步骤的处理温度有耐热性的塑料基板构成。基板 800 的表面可通过 CMP(化学机械抛光)法等通过抛光来平坦化。绝缘层可在基板 800 上形成。该绝缘层使用各自包含硅的氧化物材料和氮化物材料通过诸如 CVD 法、等离子体 CVD 法、溅射法、

或旋涂法以单层或叠层形成。该绝缘层并非必需设置,但对阻挡来自基板 800 的污染物等是有效的。在形成防止来自玻璃基板的污染的基底层的情形中,形成基底膜 801 作为对通过微滴排放法在基底层上形成的导电层 802 和 803 的预处理。

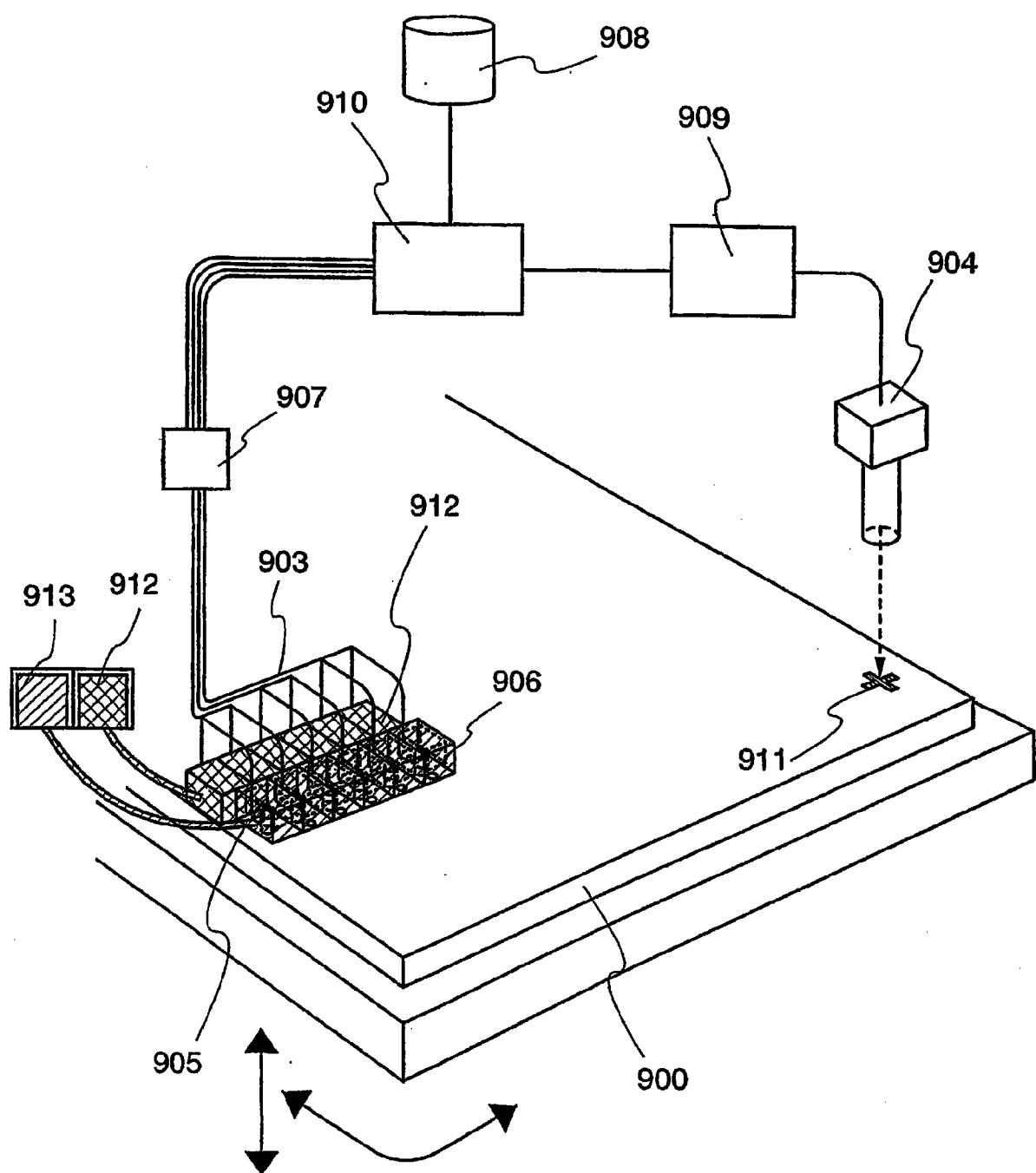

[0128] 图 15 示出用于形成图案的微滴排放设备的一种模式。微滴排放单元 903 的每一个头 905 连接到控制单元 907。计算机 910 控制控制单元 907,由此可绘出编程图案。绘制的时间可例如基于在基板 900 上形成的标记 911 来确定。或者,可基于基板 900 的边缘来确定基点。这由诸如 CCD 等图像拾取单元 904 检测,并通过图像处理单元 909 转换成数字信号。计算机 910 识别该数字信号并生成发送给控制单元 907 的控制信号。当然,基于哪一控制信号被发送到控制单元 907,有关要在基板 900 上形成的图案的数据存储在存储器介质 908 中,因而可单独控制微滴排放单元 903 的每一个头 905。使用一个头可排放并绘制导电材料、有机材料、无机材料等中的每一种。在诸如层间膜等宽广区域中进行绘制的情形中,可排放相同的材料以同时从多个喷嘴绘制以改进生产量。在使用大基板的情形中,头 905 自由地在基板上扫描,并自由地设置要绘制的区域,由此多个相同的图案可绘制在一个基板上。

[0129] 在本实施方式中,具有光催化功能的物质被用作具有改进粘性功能的基底膜。该光催化物质可通过诸如浸涂法、旋涂法等溶胶法、微滴排放法、或离子镀法、离子束法、CVD 法、溅射法、RF 磁控管溅射法、等离子体喷射法、或阳极氧化法等形式形成。此外,取决于其形成方法,光催化物质不需要像膜一样具有连续性。在光催化物质由包括多种金属的氧化物半导体形成的情形中,光催化物质可通过混合和熔化构成元素的盐来形成。在通过诸如浸涂法或旋涂法等涂覆方法形成光催化物质的情形中有必要去除溶剂时,可烘干或干燥溶剂。具体地,可在预定温度(例如 300°C 或以上)下加热,较佳地在包括氧气的气氛中加热。例如,在包括氧气和氮气的气氛中将银(Ag)用作导电浆来进行烘干,然后分解诸如可热固化树脂等有机材料。因此,可获得不包含有机材料的银。因此,可提高 Ag 的表面平坦度。

[0130] 根据热处理,光催化物质可具有预定晶体结构。例如,它具有锐钛矿相或金红石锐钛矿混合相。锐钛矿相优先地在低温阶段形成。因此,光催化物质在不具有预定晶体结构时还可被加热。此外,光催化物质可多次地形成,以在通过涂覆方法形成的情形中获得预定的膜厚。

[0131] 在本实施方式中描述通过溅射法形成具有预定晶体结构的  $TiO_x$ (通常为  $TiO_2$ )晶体作为光催化物质的情形。溅射将钛金属管用作靶并使用氩气和氧气来进行。此外,可引入氮气。气氛包括大量氧气且成型压力被设置成较高以形成具有高度光催化活性的  $TiO_x$ 。较佳的是在加热设有待处理对象的沉积室或基板时形成  $TiO_x$ 。

[0132] 如此形成的  $TiO_x$  即使在它是极薄的膜(约  $1nm \sim 1\mu m$ )时也具有光催化功能。

[0133] 此外,较佳的是通过溅射法、气相沉积法等形式由诸如 Ti(钛)、W(钨)、Cr(铬)、Ta(钽)、Ni(镍)或 Mo(钼)等金属材料或其氧化物制成的基底膜 801。

[0134] 基底膜 801 可被形成为  $0.01 \sim 10nm$  厚。只要它被形成得相当薄,就不必具有层结构。当高熔点金属材料被用作基底膜时,较佳的是在将导电层 802 和 803 形成为栅电极层之后通过执行以下两个步骤之一来处理露在该表面上的基底膜。

[0135] 第一种方法是绝缘不与导电层 802 和 803 重叠的基底膜 801,并形成绝缘层的步骤。换言之,氧化并绝缘不与导电层 802 和 803 重叠的基底膜 801。当基底膜 801 用此方法

氧化和绝缘时,较佳的是将基底膜 801 形成为  $0.01 \sim 10\text{nm}$  厚,从而可容易地氧化基底膜。注意,氧化可通过暴露于氧气气氛或热处理来进行。

[0136] 第二种方法是将导电层 802 和 803 用作掩模来通过蚀刻去除基底膜 801 的步骤。当采用该步骤时,对基底膜 801 的厚度没有限制。

[0137] 可选择地,用于对成型区(成型面)进行等离子体处理的方法可被用作另一预先基础处理。等离子体处理将空气、氧气或氮气用作处理气体来进行,且压力从数十到数千托(133000 帕),较佳地从 100 托(13300 帕)到 1000 托(133000 帕),更佳地从 700 托(93100 帕)到 800 托(106400 帕),即大气压或接近大气压的压力,并在这样的条件下施加脉冲电压。此时,等离子体密度被设为  $1 \times 10^{10}$  到  $1 \times 10^{14}\text{m}^{-3}$ ,由此实现所谓的电晕放电或辉光放电。通过采用将空气、氧气或氮气用作处理气体的等离子体处理,可与材料无关地进行表面改性。因此,可对任何材料进行表面改性。

[0138] 作为另一种方法,可形成用作粘合剂的有机材料物质以改进要通过微滴排放法形成的图案与其成型区之间的粘性。可使用有机材料(有机树脂材料)(聚酰亚胺或丙烯酸树脂)或硅氧烷。注意,硅氧烷由硅(Si)和氧(O)的键形成的骨架构成,其中包括至少含有氢的有机基(诸如烷基或芳香烃)作为取代基。或者,氟基可被用作取代基。再或者,氟基或至少含有氢的有机基可被用作取代基。

[0139] 随后,排放含有导电材料的混合物,并且形成用作栅电极的导电层 802 和 803。

[0140] 微滴排放单元是对具有用于排放微滴的单元,诸如具有混合物排放口的喷嘴或设有一个或多个喷嘴的头的统称。包括在微滴排放单元内的喷嘴的直径被设置在  $0.02 \sim 100\mu\text{m}$ (有利地为  $30\mu\text{m}$  或以下)的范围内,并且要从喷嘴排放的混合物的量被设置在  $0.001 \sim 100\text{pL}$ (有利地为  $10\text{pL}$  或以下)的范围内。要排放的混合物的量与喷嘴的直径成正比地增加。此外,较佳的是待处理对象与喷嘴的排放口之间的距离尽可能地短,以便于在期望位置滴落微滴。该距离有利地被设置在约  $0.1 \sim 3\text{mm}$  的范围内(更佳地,  $1\text{mm}$  或以下)。

[0141] 对于要从排放口排放的混合物,使用溶解或分散在溶剂中的导电材料。导电材料对应于诸如 Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W 或 Al 等金属,诸如 Cd 或 Zn 等金属的硫化物,Fe、Ti、Si、Ge、Zr 或 Ba 的氧化物,或卤化银的微粒或分散纳米粒子。此外,它对应于用作透光导电膜的氧化铟锡(ITO)、含有氧化硅的氧化铟锡(ITSO)、有机铟、有机锡、氧化锌、氮化钛等。然而,对于要从排放口排放的混合物,较佳的是考虑电阻率来使用从溶解或分散在溶剂中的金、银和铜中选择的任何材料。更佳的是使用具有低电阻值的银或铜。当使用银或铜时,可另外设置阻挡膜,用作对杂质的一种措施。氮化硅膜或硼化镍(NiB)可被用作阻挡膜。

[0142] 另外,可使用具有通过用另一导电材料涂敷导电材料的周边形成的多层的粒子。例如,可使用具有其中用硼化镍(NiB)、然后用银等涂敷铜的三层结构的粒子。对于这样的溶剂,可使用诸如乙酸丁酯和乙酸乙酯等酯、诸如异丙醇和乙醇等醇、诸如甲基乙基甲酮和丙酮等有机溶剂等。混合物的粘度较佳地是  $50\text{mPa} \cdot \text{s}$ (cps) 或以下。这是因为防止混合物变干,或者将混合物流畅地从排放口排放。混合物的表面张力较佳地是  $40\text{N/m}$  或以下。注意,混合物的粘度等可根据要使用的溶剂和预期用途来适当地调节。例如,其中 ITO、有机铟或有机锡溶解或分散在溶剂中的混合物的粘度是  $5 \sim 50\text{mPa} \cdot \text{s}$ ,其中银溶解或分散在溶剂中的混合物的粘度是  $5 \sim 20\text{mPa} \cdot \text{s}$ ,而其中金溶解或分散在溶剂中的混合物的粘度是  $10 \sim$

20mPa • S。

[0143] 导电层可通过层叠多种导电材料来形成。此外,导电层可将银用作导电材料通过微滴排放法来形成,然后它可用铜等镀层。镀层可用电镀或化学(无电)镀层法来进行。镀层可通过将基板表面浸入充满具有镀层材料的溶液的容器中来进行。可涂覆具有镀层材料的溶液,使得在倾斜(或垂直)放置基板时溶液在基板表面流动。当镀层通过垂直放置基板来涂敷溶液而进行时,有处理设备尺寸可变小的优点。

[0144] 导电材料粒子的直径最好尽可能的小,以防止喷嘴阻塞并制造高清晰度的图案,尽管这取决于每一喷嘴的直径、图案的期望形状等。较佳地,导电材料粒子的直径为0.1 μm或以下。混合物通过诸如电解法、雾化法、或除湿法等公知方法形成,且粒子大小通常约为0.01 ~ 10 μm。注意,当采用气体蒸镀法时,受分散剂保护的纳米分子小至约7nm。当粒子的每个表面都用涂层覆盖时,纳米分子不附着在溶剂中并在室温下均匀分散在溶剂中,且显示出与液体相似的性质。因此,较佳的是使用涂层。

[0145] 当排放混合物的步骤在降低压力下进行时,混合物溶液被蒸发,直到所排放的混合物落在待处理对象上,且因而可略去后来的干燥和烘干混合物的步骤。较佳的是在降低压力下执行该步骤,因为氧化物膜等未在导体表面上形成。在排放混合物之后,执行干燥和/或烘干步骤中的任一步或两者。每一干燥和烘干步骤是热处理的一个步骤。例如,在100°C下干燥3分钟,并在从200到350°C的温度下烘干15分钟到30分钟,每一步骤都具有不同的目的、温度和持续时间。干燥和烘干步骤通过激光照射、快速热退火、加热炉等在常压或降低压力下进行。注意,热处理的定时并不受特别的限制。基板可预先加热,以有利地进行干燥和烘干步骤。此时基板的温度取决于基板的材料等,但通常为100 ~ 800°C(较佳地,为200 ~ 350°C)。根据这些步骤,纳米粒子彼此接触,并且熔合和焊接通过淬火和收缩周边树脂、以及蒸发混合物中的溶液或化学地去除分散剂来加速。

[0146] 连续波或脉冲波气体激光器或固体激光器可用于激光照射。受激准分子激光器等可作为气体激光器给出,且使用掺杂有Cr、Nd等的YAG或YVO<sub>4</sub>的晶体的激光器可作为固体激光器给出。注意,较佳的是使用相关于激光的吸收比的连续波激光器。此外,可使用其中组合使用脉冲波和连续波的所谓的混合激光照射法。然而,较佳的是通过激光照射进行的热处理可取决于基板800的耐热性在几微妙到几十秒内瞬时执行,使该基板800不受损。通过使用在惰性气体气氛中发光以用紫外线到红外光进行照射的红外线灯等或卤素灯来快速升温或加热达几微妙到几分钟,可进行快速热退火(RTA)。由于该处理是瞬时地进行的,因此实质上仅可加热上表面上的薄膜而不会影响下层薄膜。换言之,即使是诸如塑料基板等具有低耐热性的基板也不会受影响。

[0147] 此外,上述形成基底膜801的步骤作为预先基础处理对通过微滴排放法形成的导电层进行,然而该处理步骤可在形成导电层之后进行。

[0148] 随后,在导电层802和803上形成栅绝缘层(参见图13A)。该栅绝缘层可由诸如硅的氧化物或氮化物材料等公知材料形成,并且可以是叠层或单层。例如,可以是氮化硅膜、氧化硅膜和氮化硅膜的三层叠层,或者可以是这些或氧氮化硅膜的单层,或是这两层的叠层。在本实施方式中,氮化硅膜被用作绝缘层804,而氮氧化硅膜被用作栅绝缘层805。较佳地使用具有致密膜质量的氮化硅膜。在将银、铜等用于通过微滴排放法形成的导电层的情形中,在其上形成氮化硅膜或NiB膜作为阻挡膜在防止杂质扩散以及平坦化表面中是有

效的。注意,诸如氩气等稀有气体元素较佳地包括在反应气体中,并较佳地混合于要形成的绝缘膜中以便于形成在较低膜形成温度下几乎没有栅极漏电流的致密绝缘膜。

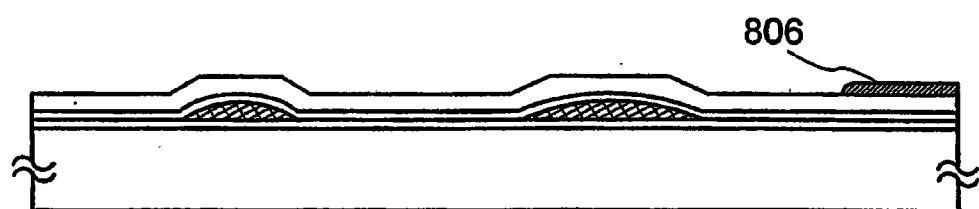

[0149] 随后,导电层(也称为第一电极)806通过在栅绝缘膜上选择性地排放含有导电材料混合物来形成(参见图13B)。在从基板800一侧发光时或在制造透光型EL显示面板时,导电层806能以包含氧化铟锡(ITO)、含有氧化硅的氧化铟锡(ITSO)、氧化锌(ZnO)、氧化锡(SnO<sub>2</sub>)等的混合物的预定图案并通过烘干它来形成。

[0150] 较佳地,导电层806通过溅射法由氧化铟锡(ITO)、含有氧化硅的氧化铟锡(ITSO)、氧化锌(ZnO)等形成。更佳的是使用理由其中ITO含有2~10重量%的氧化硅的靶通过溅射法形成的含有氧化硅的氧化铟锡。此外,可使用利用通过将2~20重量%的氧化锌混合到含有氧化硅的氧化铟中获得的靶而形成的氧化物导电材料。掩模层可通过微滴排放法来形成,并在通过溅射法形成导电层(第一电极)806之后蚀刻成具有期望图案。在该实施方式中,导电层806通过微滴排放法由透光导电材料形成。具体地,它由氧化铟锡或由ITO和氧化硅构成的ITSO形成。尽管未示出,但与形成导电层802和803的情形相似,光催化物质可在形成了导电层806的区域中形成。光催化物质可改进粘性,并且导电层806可形成为成一细线的期望图案。导电层806变成用作像素电极的第一电极。

[0151] 在本实施方式中,描述了由氮化硅膜、氧氮化硅膜(氧化硅膜)和由氮化硅制成的氮化硅膜的三层构成的栅绝缘层的一个示例。由含有氧化硅的氧化铟锡形成的导电层(第一电极)806较佳地形成为与包括在栅绝缘层805内的氮化硅形成的绝缘层紧密接触。因此,可提高在场致发光层中产生的光向外发射的速率。

[0152] 此外,含有诸如Ag(银)、Au(金)、Cu(铜)、W(钨)或Al(铝)等金属粒子作为其主要成分的混合物可在所产生光被发射到基板800的相对侧时、或在制造反射型EL显示面板时使用。作为另一种方法,第一电极层可通过由溅射法形成透光导电膜或反光导电膜、由微滴排放法形成掩模图案、并另外进行蚀刻过程来形成。

[0153] 导电层(第一电极)806可通过CMP法抛光、或通过聚乙烯醇的多孔体清洗来抛光,以使其表面平坦化。此外,导电层(第一电极)806的表面可用紫外光照射,或可在通过CMP法抛光后用氧等离子体来处理。

[0154] 半导体层可通过一公知方法(溅射法、LP(低压)CVD法、等离子体CVD法等)形成。对半导体层的材料没有特别限制,但半导体层较佳地由硅、锗硅(SiGe)合金等形成。

[0155] 半导体层由非晶半导体(通常为氢化非晶硅)或结晶半导体(通常为多晶硅)作为材料形成。多晶硅包括:将通过800℃或更高的处理温度形成的多晶硅作为主要材料的所谓的高温多晶硅、将通过600℃或更低的处理温度形成的多晶硅作为主要材料的所谓的低温多晶硅、以及通过添加例如促进结晶的元素等来结晶的结晶硅。

[0156] 此外,作为另一物质,也可使用在半导体层的一部分中含有晶相的半非晶半导体或半导体。半非晶半导体表示具有非晶结构和结晶结构(包括单晶和多晶)的中间结构、并具有在自由能方面稳定的第三态的半导体,以及具有短程有序和晶格畸变的结晶半导体。通常,含有硅作为主要成分的半导体层具有晶格畸变,其中拉曼频谱被移至低于520cm<sup>-1</sup>的低频侧。此外,至少1原子%或以上的氢或卤素被包含其中以将悬挂键封端。在此,如上所述的这种半导体被称为半非晶半导体(下文中称为“SAS”)。该SAS也称为所谓的微晶半导体(通常称为微晶硅)。

[0157] SAS 可通过对硅源气体进行辉光放电分解（等离子体 CVD）来获得。SiH<sub>4</sub> 作为典型的硅源气体给出。也可使用 Si<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>Cl<sub>2</sub>、SiHCl<sub>3</sub>、SiCl<sub>4</sub>、SiF<sub>4</sub> 等。此外，可混合 GeF<sub>4</sub> 或 F<sub>2</sub>。通过用氢气或氦气和从氦气、氩气、氪气和氖气中选出的一种或多种稀有气体的混合物稀释的硅源气体可便于形成 SAS。氢气与硅源气体的稀释比就流量比而言较佳地在 2 ~ 1000 倍的范围内。尽管 SAS 通过辉光放电分解的形成较佳地在降低压力下进行，但该形成还可通过利用大气压下的放电来进行。通常，形成可在 0.1 ~ 133Pa 的压力范围内进行。用于产生辉光排放的电源频率在 1 ~ 120MHz 的范围内，较佳地在 13 ~ 60MHz 的范围内。可适当地设置高频电源。用于加热基板的温度较佳地为 300 °C 或以下，并可采用 100 ~ 200 °C 范围内的温度。对于主要在形成薄膜时要包含的杂质元素，从诸如氧气、氮气或碳等大气组分得到的杂质较佳地浓度为  $1 \times 10^{20} \text{ cm}^{-3}$  或以下，并且特别地，氧气的浓度是  $5 \times 10^{19} \text{ cm}^{-3}$  或以下，较佳地为  $1 \times 10^{19} \text{ cm}^{-3}$  或以下。此外，通过允许含有诸如氦、氩、氪、或氖等稀有气体元素来促进晶格畸变，可增强 SAS 的稳定性，由此形成令人满意的 SAS。此外，由基于氢的气体形成的 SAS 层可层叠在由基于氟的气体形成的 SAS 层上，作为半导体层。

[0158] 当结晶半导体层被用作半导体层时，可采用公知方法（激光结晶法、热结晶法、使用诸如镍等促进结晶的元素的热结晶法等）作为用于制造结晶半导体层的方法。在不引入促进结晶的元素的情形中，在用激光照射非晶硅膜之前通过在氮气氛中在 500 °C 的温度下加热非晶硅膜达一个小时来放出氢气，直到非晶硅膜中所含的氢浓度变成  $1 \times 10^{20} \text{ 原子 / cm}^3$  或以下。这是因为当用激光照射含有许多氢的非晶硅膜时膜会被损坏。

[0159] 对将金属元素引入非晶半导体层的方法没有特别的限制，只要它是能使金属元素在非晶半导体层表面或内部存在的方法即可。例如，可采用溅射法、CVD 法、等离子体处理法（包括等离子体 CVD 法）、吸收法、或涂敷金属盐溶液的方法。在其中，使用溶液的方法是简便的，并且在金属元素的简单浓度调节方面是有用的。较佳的是氧化物膜通过氧气气氛中的 UV 光照射、热氧化法、用臭氧水或包括羟基的过氧化氢处理等形成，以便于改进非晶半导体层表面的润湿度并在非晶半导体层的整个表面上散布水溶液。

[0160] 此外，可组合热处理和激光照射以使非晶半导体层结晶。热处理和 / 或激光照射可独立进行许多次。

[0161] 使用有机材料的有机半导体可被用作半导体。低分子量材料、高分子量材料等被用于有机半导体，且此外可使用诸如有机颜料、导电高分子量材料等材料。

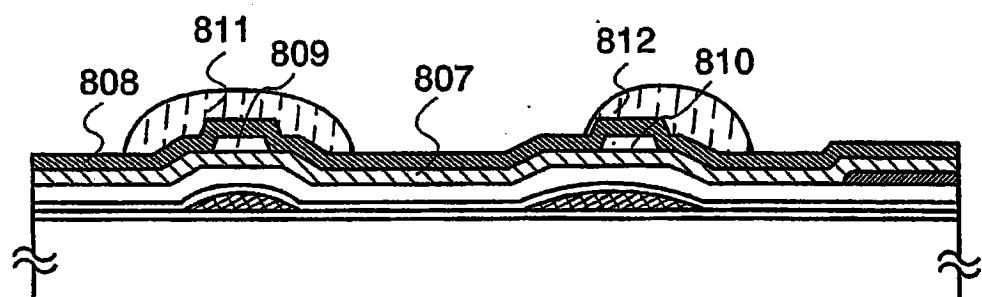

[0162] 在本实施方式中非晶半导体被用作半导体。形成作为非晶半导体层的半导体层 807，并且绝缘膜通过例如等离子体 CVD 法形成并选择性地蚀刻成在期望区域中具有期望形状，以便于形成沟道保护膜 809 和 810。此时，沟道保护膜 809 和 810 可通过将栅电极用作掩模将基板的背面曝光来形成。此外，聚酰亚胺、聚乙烯醇等可通过微滴排放法滴落，作为沟道保护膜。因此，可略去曝光步骤。然后，N 型半导体层 808 通过等离子体 CVD 法等使用具有一种导电性的半导体层（例如 N 型非晶半导体层）形成。具有一种导电性的半导体层可按需形成。

[0163] 由一种或多种无机材料（氧化硅、氮化硅、氧氮化硅、氮氧化硅等）、光敏或非光敏有机材料（有机树脂材料）（聚酰亚胺、丙烯酸、聚酰胺、聚酰亚胺酰胺（polyimide amide）、抗蚀剂、苯并环丁烯等）、具有低介电常数的低 k 材料等或其叠层形成的膜可被用作沟道保护膜。此外，可使用其中骨架结构通过硅（Si）和氧（O）的键配置、且至少包含氢作为取代

基（例如烷基或芳香烃）的材料。或者，氟基可被用作取代基。另外可选择地，氟基和至少含有氢的有机基可被用作取代基。诸如等离子体 CVD 法或热 CVD 法等气相生长法或溅射法可被用作将无机材料用作沟道保护膜的制造方法。此外，在使用有机材料的情形中，可采用微滴排放法或印刷法（用于形成图案的方法，诸如丝网印刷或胶印）。可使用通过涂敷法获得的绝缘膜、SOG 膜等。

[0164] 随后，形成由诸如抗蚀剂或聚酰亚胺等绝缘体形成的掩模层 811 和 812。然后，半导体层 807 和 N 型半导体层 808 通过使用掩模层 811 和 812 来同时图形化。

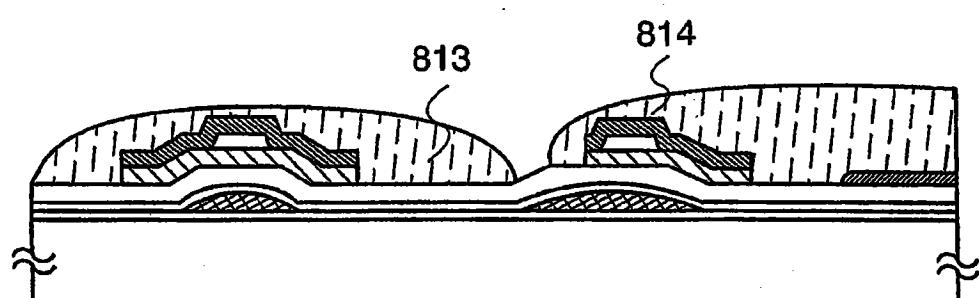

[0165] 然后，由诸如抗蚀剂或聚酰亚胺等绝缘体形成的掩模层 813 和 814 通过微滴排放法来形成（参见图 13D）。通孔 818 使用掩模 813 和 814 通过蚀刻工艺在栅绝缘层 804 和 805 的一部分中形成，并且置于其下层一侧并用作栅极电极层的导电层的一部分暴露。等离子体蚀刻（干法蚀刻）或湿法蚀刻可被用作蚀刻工艺。然而，等离子体蚀刻适于大基板。诸如  $CF_4$ 、 $NF_3$ 、 $Cl_2$  或  $BCl_3$  等基于氟或基于氯的气体被用作蚀刻气体，并且可适当添加诸如 He 或 Ar 等惰性气体。此外，当应用大气压放电蚀刻工艺时可执行局部放电过程，并且掩模层无需完全在基板上形成。

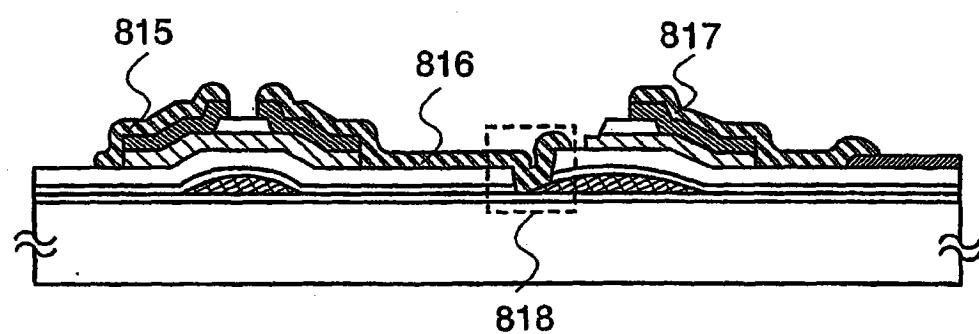

[0166] 导电层 815、816 和 817 通过在去除掩模层 813 和 814 之后排放含有导电材料的混合物来形成。然后，N 型半导体将导电层 815、816 和 817 用作掩模来图形化，以形成 N 型半导体层（参见图 14A）。导电层 815、816 和 817 用作布线层。注意，上述在导电层 815、816 和 817 与栅绝缘层 805 接触的部分中选择性地形成光催化物质等的预先基础处理可在形成导电层 815、816 和 817 之前进行，尽管并未示出。因此，导电层可形成为具有令人满意的粘性。

[0167] 形成基底膜的上述步骤可作为对要通过微滴排放法形成的导电层的预先基础处理来执行。此外，处理步骤可在形成导电层之后执行。显示装置的可靠性可得到改进，因为各层之间的粘性根据该步骤得以改进。

[0168] 导电层 817 用作源极布线层或漏极布线层，并被形成为与之前形成的第一电极电连接。此外，作为源极布线层或漏极布线层的导电层 816、以及作为栅电极层的导电层 803 在栅极绝缘层 805 中形成的通孔 818 中彼此电连接。含有诸如 Ag（银）、Au（金）、Cu（铜）、W（钨）或 Al（铝）等金属粒子作为其主要成分的混合物可被用作形成布线层的导电材料。此外，透光氧化铟锡（ITO）、含有氧化硅的氧化铟锡（ITSO）、有机铟、有机锡、氧化锌、氮化钛等可组合使用。

[0169] 在栅绝缘层 804 和 805 的一部分中形成通孔 818 的步骤可在形成导电层 815、816 和 817 之后进行，将导电层 815、816 和 817 用作掩模以形成通孔 818。然后，导电层在通孔 818 中形成，且作为栅电极层的导电层 816 和导电层 803 彼此电连接。在该情形中，优点在于多个步骤可得到简化。

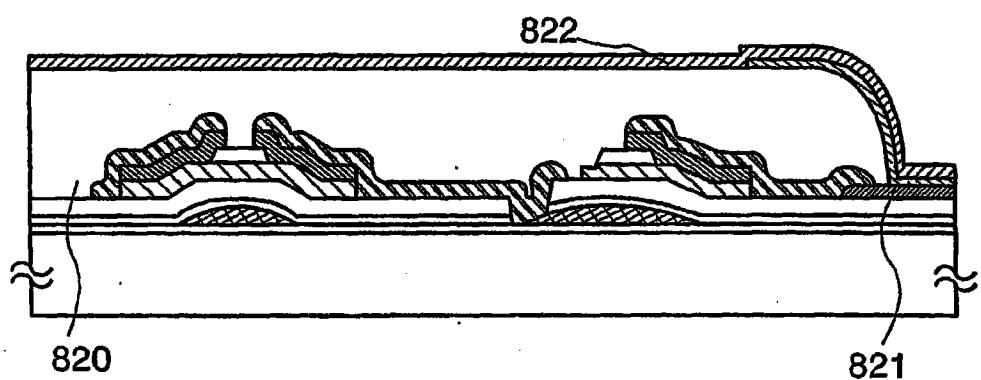

[0170] 随后，形成要成为分隔壁的绝缘层 820。尽管未示出，但由氮化硅或氮氧化硅形成的保护层可全部在绝缘层 820 下形成，以覆盖薄膜晶体管。在通过旋涂法或浸渍法全部形成绝缘层之后，如图 14B 所示通过蚀刻工艺在绝缘层 820 中形成一开口。当绝缘层 820 通过微滴排放法形成时不必进行蚀刻过程。当诸如绝缘层 820 等较宽区域通过微滴排放法形成时，它通过从微滴排放设备的喷嘴的多个排放口中排放混合物、并通过绘制以使得多条线彼此重叠来形成。因此，改进了生产量。

[0171] 绝缘层 820 被形成为具有与其中像素要根据作为第一电极的导电层 806 形成的位置相对应的通孔。绝缘层 820 可通过使用诸如氧化硅、氮化硅、氧氮化硅、氧化铝、氮化铝、或氧氮化铝、丙烯酸、异丁烯酸、丙烯酸或异丁烯酸的衍生物等无机绝缘材料；诸如聚酰亚胺、芳族聚酰胺或聚苯并咪唑等耐热高分子量材料；或包括含有硅、氧和氢的化合物中的 Si-O-Si 键，并通过将硅氧烷材料用作起始材料而形成的无机硅氧烷，或其中与硅键合的氢被诸如甲基或苯基等有机基取代的基于有机硅氧烷的绝缘材料来形成。较佳的是通过使用诸如丙烯酸或聚酰亚胺等光敏或非光敏材料来形成绝缘层 820，因为其侧面变成曲率半径连续变化且上层薄膜不中断地形成的形状。

[0172] 根据上述步骤，完成了用于 EL 显示面板的 TFT 基板，其中底栅型（也称为逆向交错型）沟道保护 TFT 和第一电极（第一电极层）在基板 800 上连接。

[0173] 在形成场致发光层 821 之前，绝缘层 820 内或其表面所吸收的湿气通过在 200℃ 大气压下进行热处理来去除。此外，在降低压力下在 200 ~ 400℃ 的温度下，较佳地在 250 ~ 350℃ 的温度下进行热处理，且场致发光层 821 较佳地通过真空气相沉积法或微滴排放法在不暴露于大气的情况下在降低压力下形成。

[0174] 发出红 (R)、绿 (G) 和蓝 (B) 光的材料使用相应的气相沉积掩模通过气相沉积法等选择性地形成为场致发光层 821。发出红 (R)、绿 (G) 和蓝 (B) 光的材料（低分子量或高分子量材料等）可通过微滴排放法类似于滤色片来形成。该情形是较佳的，因为 RGB 可以在不使用掩模的情况下单独沉积。作为第二电极的导电层 822 层叠在场致发光层 821 上，因而完成了使用发光元件的具有显示功能的显示装置（参见图 14B）。

[0175] 有效的是设置钝化膜以覆盖第二电极，尽管未示出。钝化膜由含有氮化硅 (SiN)、氧化硅 (SiO<sub>2</sub>)、氧氮化硅 (SiO<sub>x</sub>N<sub>y</sub> : x > y > 0)、氮氧化硅 (SiN<sub>x</sub>O<sub>y</sub> : x > y > 0)、氮化铝 (AlN)、氧氮化铝 (AlO<sub>x</sub>N<sub>y</sub> : x > y > 0)、氮成分比氧成分多的氮氧化铝 (AlN<sub>x</sub>O<sub>y</sub> : x > y > 0)、氧化铝、金刚石型碳 (DLC) 的绝缘膜、或含氮碳膜 (CN<sub>x</sub>) 形成，并且可使用绝缘膜的单层或组合叠层。例如，可使用含氮碳膜 (CN<sub>x</sub>) 和氮化硅 (SiN) 或有机材料的叠层，并且可使用诸如苯乙烯聚合物等高分子量材料的叠层。也可使用硅氧烷树脂。硅氧烷由硅 (Si) 和氧 (O) 的键形成的骨架构成，其中至少含有氢的有机基（诸如烷基或芳香烃）被包括作为取代基。可选择地，氟基可被用作取代基。此外可选择地，氟基和至少含有氢的有机基可被用作取代基。

[0176] 在该情形中，具有令人满意的覆盖率的膜较佳地被用作钝化膜，并且使用碳膜（具体地，DLC 膜）是有效的。因为 DLC 膜可在从室温到 100℃ 或以下范围内的温度下形成，所以它可容易地在具有低耐热性的场致发光层上形成。DLC 膜可通过等离子体 CVD 法（通常为 RF 等离子体 CVD 法、微波 CVD 法、电子回旋共振 (ECR) CVD 法、热丝 CVD 法等）、燃烧火焰法、溅射法、离子束气相沉积法、激光气相沉积法等形成。作为用于薄膜形成的反应气体，使用氢气和碳氢化合物气体（例如 CH<sub>4</sub>、C<sub>2</sub>H<sub>2</sub>、C<sub>6</sub>H<sub>6</sub> 等）。气体通过辉光放电来离子化，并且离子被加速以与施加了负自偏压的阴极碰撞，由此形成膜。此外，CN 膜可通过将 C<sub>2</sub>H<sub>4</sub> 气体和 N<sub>2</sub> 气体用作反应气体来形成。DLC 膜对氧具有高阻挡效应，并可抑制场致发光层的氧化。因此，在以下密封步骤中可防止场致发光层被氧化的问题。

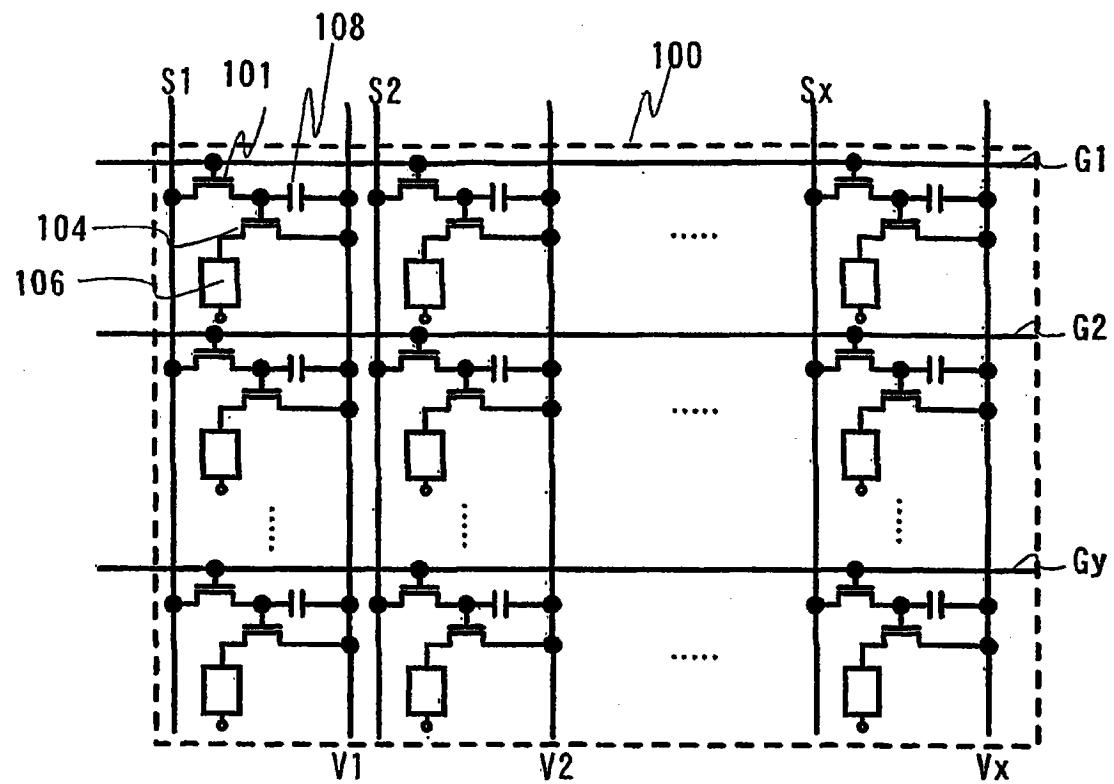

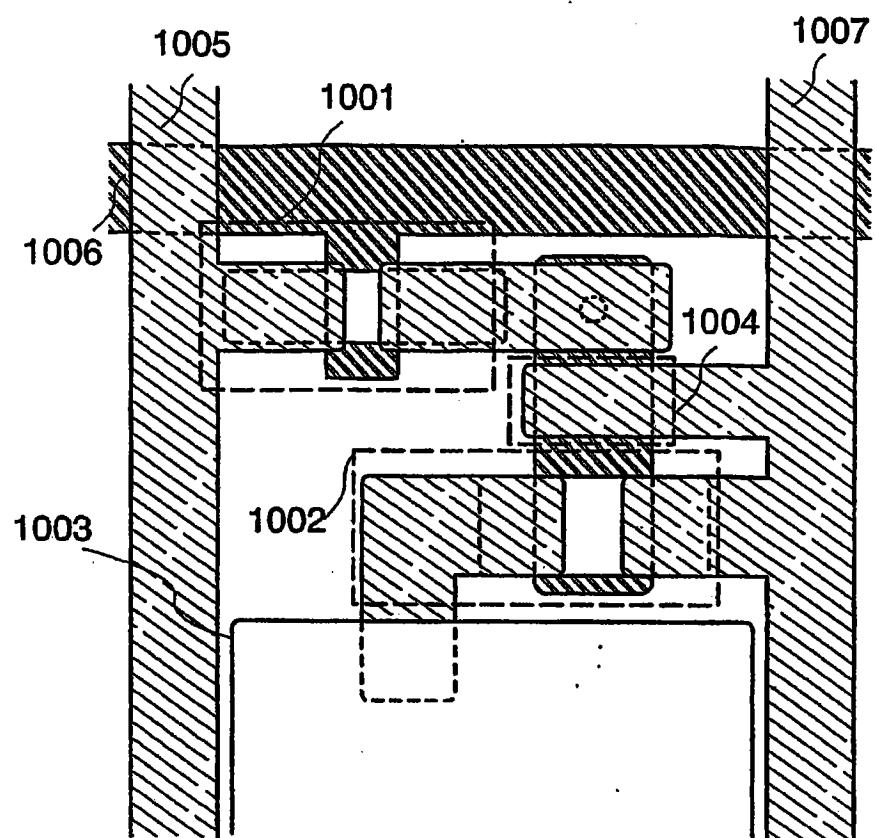

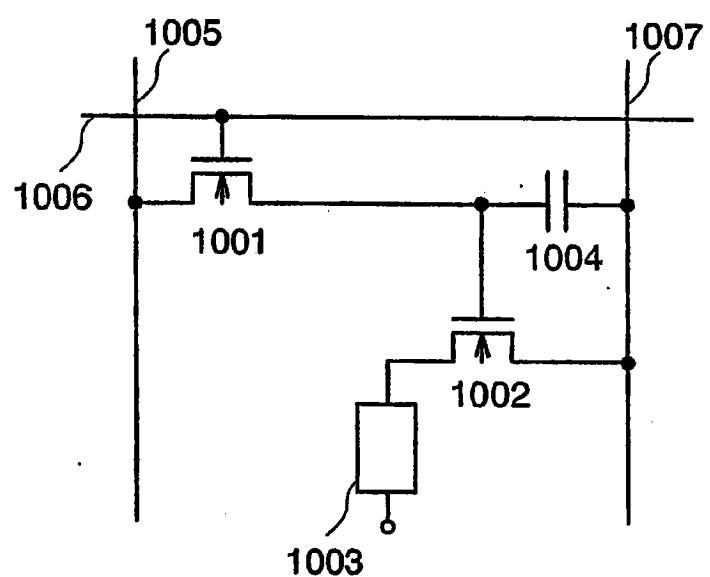

[0177] 图 16A 是本实施方式的显示装置的像素部分的平面俯视图，而图 16B 示出其电路图。参考标号 1001 和 1002 表示 TFT，1003 表示发光元件，1004 表示电容器，1005 表示源

极线,1006 表示栅极线,并且 1007 表示电源线。TFT 1001 是控制与信号线的连接的晶体管(下文中也称为“开关晶体管”或“开关 TFT”)。TFT 1002 是控制流向发光元件的电流的晶体管(下文中也称为“驱动晶体管”或“驱动 TFT”),而驱动 TFT 与发光元件串联连接。电容器 1004 保持作为驱动 TFT 的 TFT 1002 的源极 - 栅极电压。

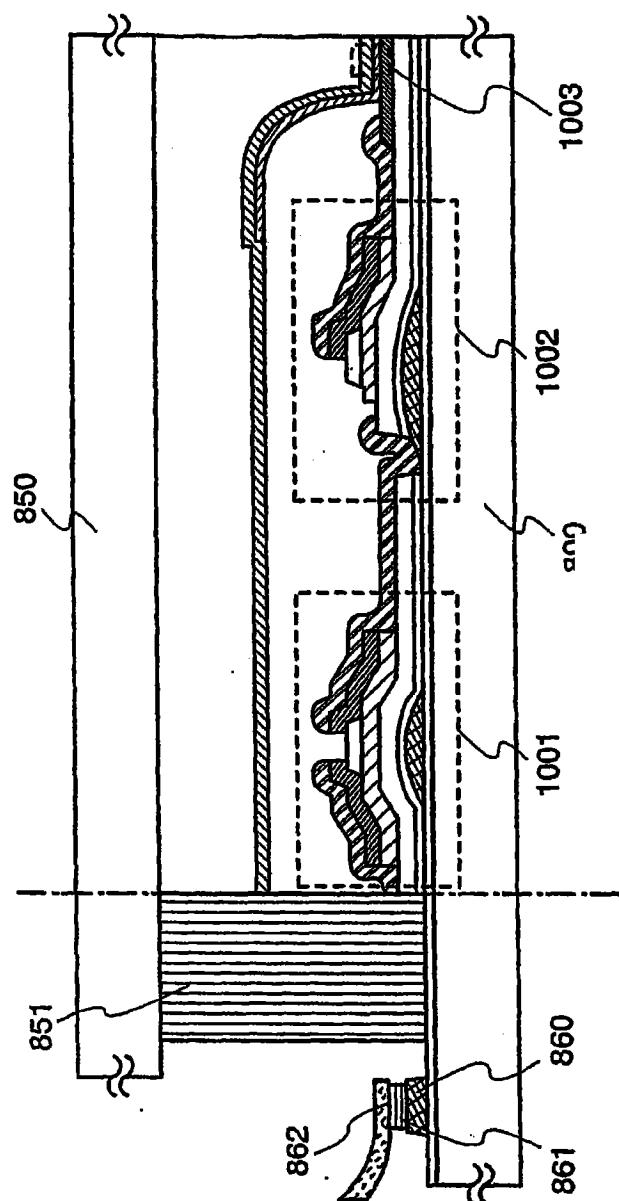

[0178] 图 17 是本实施方式的显示装置的详细示图。具有开关 TFT 1001 和作为连接到发光元件 1003 的驱动 TFT 的 TFT 1002 的基板 800 通过密封材料 851 紧固于密封基板 850。提供给在基板 800 上形成的每一电路的各个信号从一端部供应。

[0179] 栅极布线层 806 以与导电层 802 和 803 相同的步骤在端部形成。当然,与导电层 802 和 803 相似,光催化物质在栅极布线层 860 的形成区中形成。当光催化物质通过微滴排放法形成时,可改进栅极布线层 860 与基底形成区之间的粘性。当通孔 818 在栅极绝缘层 805 中形成时,同时可执行暴露栅极布线层 860 的蚀刻。柔性印刷电路(FPC)862 可通过各向异性导电层 868 连接到栅极布线层 860。

[0180] 注意,用玻璃基板密封发光元件 1003 的情形在前述显示装置中示出。密封处理是用于保护发光元件免于受潮的处理。采用用覆盖材料机械密封的方法、用可热固化树脂或可 UV 固化树脂密封的方法、以及用诸如金属氧化物或氮化物等具有高阻挡性的薄膜密封的方法的任一种。玻璃、陶瓷、塑料或金属可被用作覆盖材料,并且要求覆盖材料在光射向覆盖材料一侧时透光。覆盖材料和其上形成发光元件的基板使用诸如可热固化树脂或可紫外线固化树脂等密封材料来彼此附连。通过热处理或紫外光照射处理固化树脂来形成密封空间。在密封空间内提供以氧化钡为代表的吸湿材料也是有效的。吸湿材料可被设置在与之相接触的密封材料上或被设置在分隔壁的周边,以便于不阻挡来自发光元件的光。此外,覆盖材料与其上形成发光元件的基板之间的空间可用可热固化树脂或可紫外线固化树脂填充。在该情形中,将以氧化钡为代表的吸湿材料添加到可热固化树脂或可紫外线固化树脂中是有效的。

[0181] 如上所述,通过不应用利用光掩模的曝光步骤,在本实施方式中可略去该步骤。此外,即使在使用一边超过 1000 毫米的第五代或以后玻璃基板时,EL 显示面板也可通过微滴排放法在基板上直接形成各图案来容易地制造。

[0182] 此外,可制造粘性和抗剥离性得到改进的高可靠性显示装置。

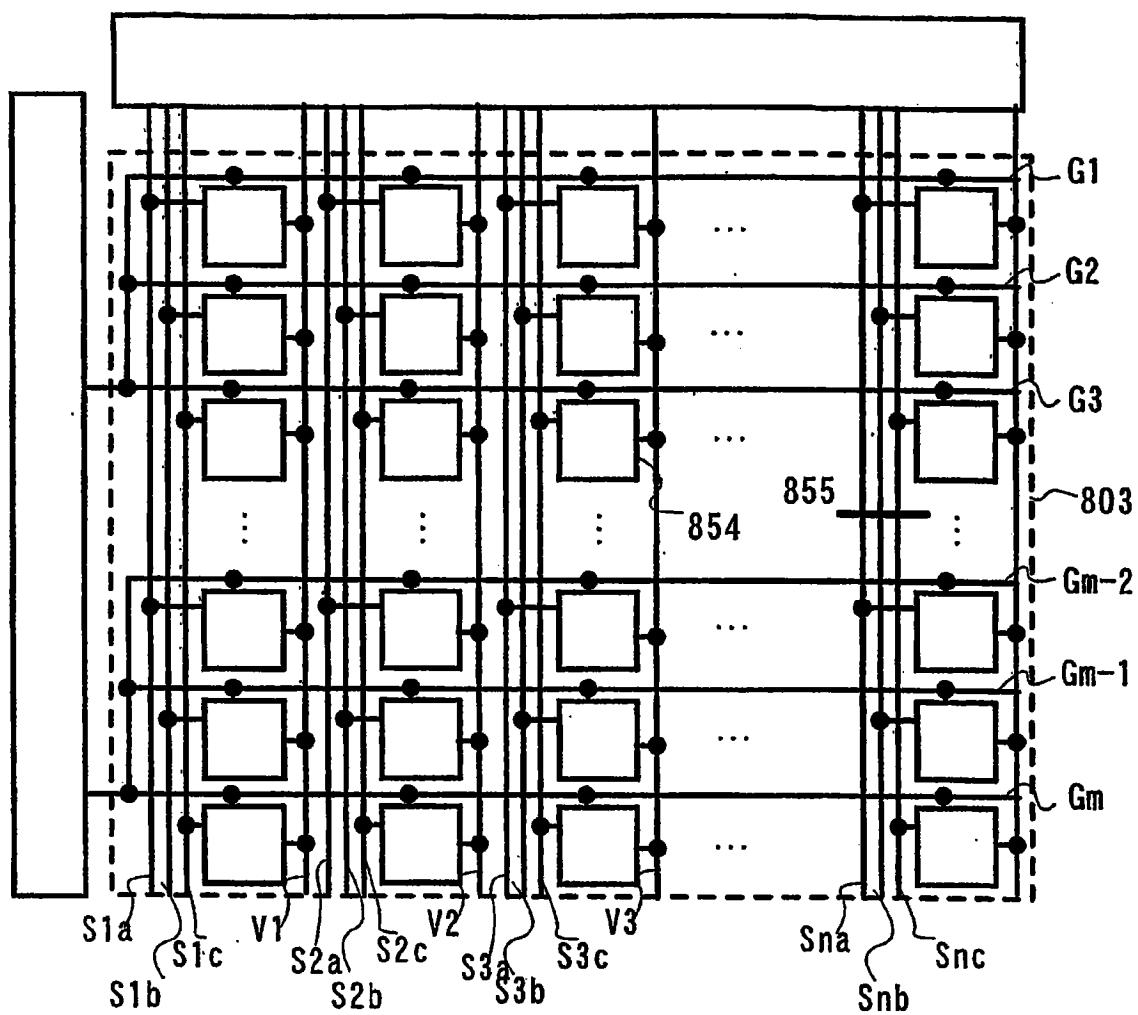

[0183] 图 8、16A 和 16B 示出本实施方式的整个像素部分的电路图。在本实施方式中,对一列垂直像素设置多条源极信号线。在图 8 中,描述对一列垂直像素设置三条源极信号线的示例。

[0184] 要注意,源极信号线的数目并不限于三条,且可按需设置。

[0185] 图 8 中每一像素的电路 854 被描述为如图 16A 和 16B 中所示的电路。然而,这仅是一个示例,且每一像素中的电路并不限于图 16A 和 16B 中的电路。

[0186] 第一行、第一列的像素包括栅极信号线 G1、作为三条源极信号线之一的源极信号线 S1a、电源线 V1、开关 TFT 1001、驱动 TFT 1002、EL 元件 1003、以及电容器 1004。

[0187] 描述了像素与电路之间的连接。栅极信号线 G1 与开关 TFT 1001 的栅电极相连,且作为三条源极信号线之一的源极信号线 S1a 与开关 TFT 1001 的源电极或漏电极相连,电源线 V1 与驱动 TFT 1002 的源电极或漏电极以及电容器 1004 的一个电极相连。电容器 1004 的另一个电极连接到开关 TFT 1001 的源电极和漏电极中的另一个、以及驱动 TFT 1002 的

栅电极。驱动 TFT 1002 的源电极和漏电极的另一个与 EL 元件 1003 相连。

[0188] 另外,第二行、第一列的像素包括栅极信号线 G2、作为三条源极信号线之一的源极信号线 S1b、电源线 V1、开关 TFT 1001、驱动 TFT 1002、EL 元件 1003、以及电容器 1004。

[0189] 第二行、第一列的像素与第一行、第一列的像素的不同之处在于:使用 G2 代替 G1,且使用 S1b 代替 S1a。

[0190] 第三行、第一列的像素包括栅极信号线 G3、作为三条源极信号线之一的源极信号线 S1c、电源线 V1、开关 TFT 1001、驱动 TFT 1002、EL 元件 1003、以及电容器 1004。

[0191] 第三行、第一列的像素与第一行、第一列的像素的不同之处在于:使用 G3 代替 G1,且使用 S1c 代替 S1a。

[0192] 此外,在上述三个像素列中, G1、G2 和 G3 电连接。

[0193] 另外,第一列的各像素是前述结构的重复。

[0194] 此外,第二列的各像素与前述结构的不同之处在于:使用 V2 代替 V1,使用 S2a 代替 S1a,且使用 S2c 代替 S1c。

[0195] 另外,第 n 列的各像素与前述结构的不同之处在于:使用 Vn 代替 V1,使用 Sna 代替 S1a,且使用 Snc 代替 S1c。

[0196] 此外,V1 ~ Vn 都彼此电连接。

[0197] 然后,对如何操作图 8 的电路进行描述。首先,栅极信号线 G1、G2 和 G3 同时接通。当栅极信号线 G1、G2 和 G3 接通时,信号从源极信号线 S1a、S1b、S1c、...、Sna、Snb 和 Snc 写入像素。然后,栅极信号线 G4、G5 和 G6 同时接通。当栅极信号线 G4、G5 和 G6 接通时,信号从源极信号线 S1a、S1b、S1c、...、Sna、Snb 和 Snc 写入像素。重复这些操作直到栅极信号线 Gm-2、Gm-1 和 Gm。一个图像的信号可通过前述操作写入。

[0198] 当以三条栅极信号线作为一个组来工作的方式工作时,栅极信号线接通时间是仅有一条信号线的电路的时间的三倍。即,可解决写入时间需要尽可能地长的困难。

[0199] 然而,在如图 8 所示连接的情形中,布线之间的寄生电容可在一些情形下增大。

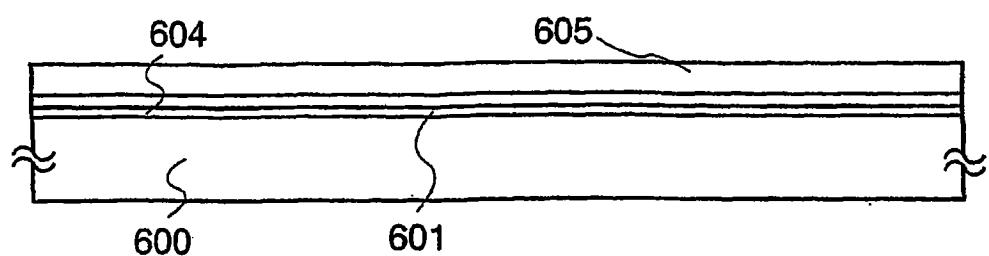

[0200] 因此,除图 8 的结构外,通过利用可选择性地形成图案的方法的优点还可设计一种工艺。为了描述该工艺,图 6A ~ 6C 被称为示出沿线的横截面 855 的示图。

[0201] 图 6A ~ 6C 示出应用于基板的工艺,在前述 TFT 形成步骤中在该基板上形成了栅绝缘层 805(图 13A)。在横截面 855 中没有半导体层,因此,导电层通常在形成栅绝缘层 605 后形成(图 6A)。然而,在本实施方式中,其上形成三条源极信号线的绝缘层的一部分在形成栅绝缘层 605 之后通过微滴排放法进一步形成为一图案(图 6B)。然后,如上所述地形成导电层以形成一图案(图 6C)。

[0202] 通过执行这一过程,三条源极信号线被形成为具有和没有绝缘层 606。在该结构中,布线之间的距离比没有绝缘层 606 的情形中长,且因而可减小布线之间的寄生电容。即,可解决要求寄生电容尽可能地小的问题。此外,在本实施方式的结构中,布线越长,则效应越大。

[0203] 在本实施方式中,要注意可自由确定绝缘层的位置、数量、形状等,只要该绝缘层被选择性地形成为使同一层的布线之间的距离保持较长。此外,在选择性形成的绝缘层上形成的布线不限于源极信号线。绝缘层可通过相似方法形成为栅极信号线或电源线,并可减小寄生电容。

[0204] [实施方式 2]

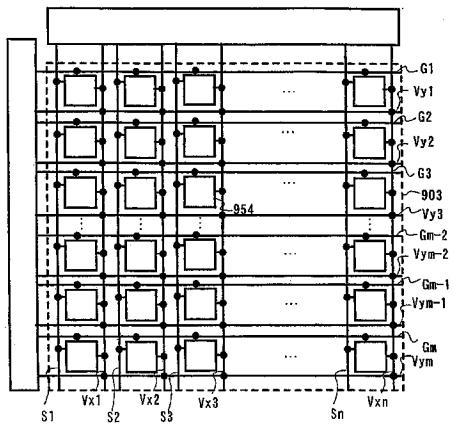

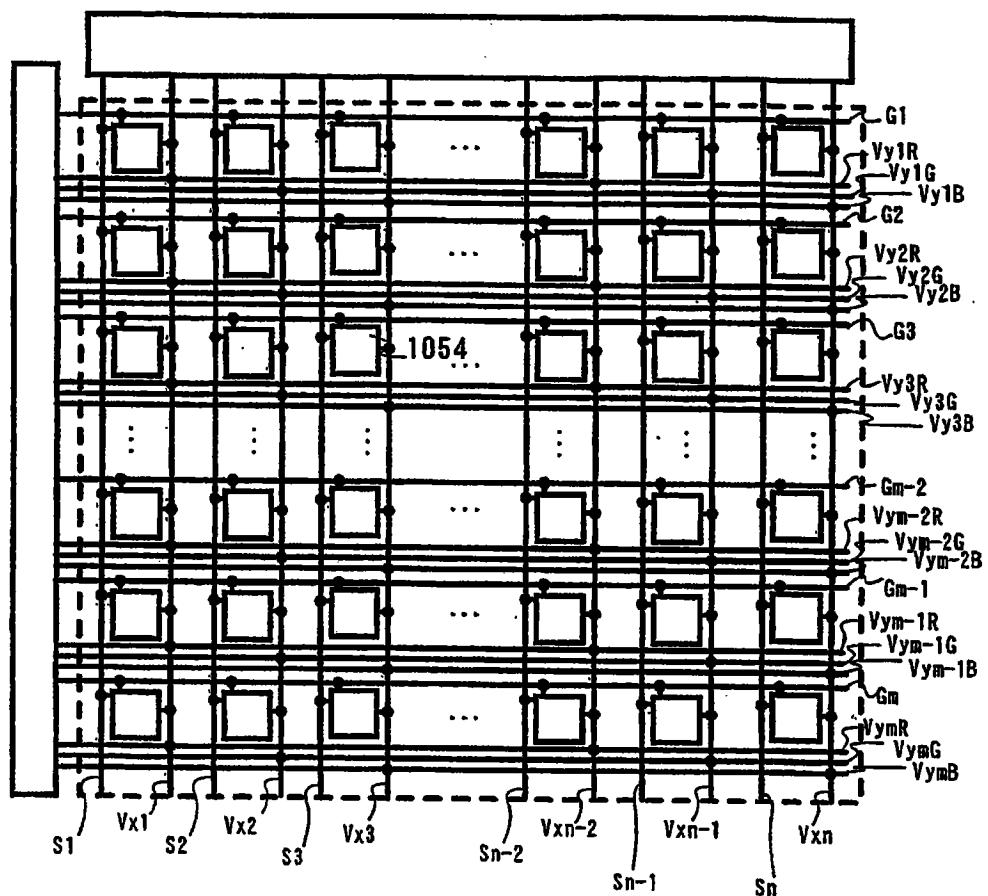

[0205] 参照图 9、16A 和 16B 对本发明一实施方式进行描述。

[0206] 在图 9 中,每一像素中的电路 954 被描述为如图 16A 和 16B 中所示的电路。然而,这仅是一个示例,且每一像素中的电路并不限于图 16A 和 16B 中的电路。

[0207] 像素部分的第一行、第一列的像素包括栅极信号线 G1、源极信号线 S1、电源线 Vx1、电源线 Vy1、开关 TFT 1001、驱动 TFT 1002、EL 元件 1003、以及电容 器 1004。

[0208] 描述了像素与电路之间的连接。栅极信号线 G1 与开关 TFT 1001 的栅电极相连,源极信号线 S1 与开关 TFT 1001 的源电极或漏电极相连,电源线 Vx1 与驱动 TFT 1002 的源电极或漏电极以及电容器 1004 的一个电极相连。电源线 Vy1 与电源线 Vx1 相连,且电容器 1004 的另一个电极连接到开关 TFT 1001 的源电极或漏电极中的另一个、以及驱动 TFT 1002 的栅电极。驱动 TFT 1002 的源电极或漏电极中的另一个与 EL 元件 1003 相连。

[0209] 像素部分的第二行、第一列的像素包括栅极信号线 G2、源极信号线 S 1、电源线 Vx1、电源线 Vy2、开关 TFT 1001、驱动 TFT 1002、EL 元件 1003、以及电容器 1004。

[0210] 像素部分的第二行、第一列的像素与第一行、第一列的像素的不同之处在于:使用 G2 代替 G1,且使用 Vy2 代替 Vy1。

[0211] 此外,像素部分的第 m 行、第一列的像素包括栅极信号线 Gm、源极信号线 S1、电源线 Vx1、电源线 Vym、开关 TFT 1001、驱动 TFT 1002、EL 元件 1003、以及电容器 1004。

[0212] 此外,像素部分的第一行、第 n 列的像素与第一行、第一列的像素的不同之处在于:使用 Sn 代替 S1,且使用 Vxn 代替 Vx1。

[0213] 此外,像素部分的第 m 行、第 n 列的像素与第一行、第一列的像素的不同之处在于:使用 Sn 代替 S1,使用 Vxn 代替 Vx1,使用 Gm 代替 G1,且使用 Vym 代替 Vy1。

[0214] 另外,Vx1 ~ Vxn 以及 Vy1 ~ Vyn 都彼此电连接。

[0215] 在本实施方式中,像素部分中的电源线不仅是平行于源极信号线 (S1 ~ Sn) 设置的布线 (Vx1 ~ Vxn),而且是在垂直方向或几乎垂直方向上设置的布线 (Vy1 ~ Vym),由此电压从每一方向提供给像素的驱动 TFT 1002 的源极区或漏极区。设置在垂直方向或几乎垂直方向上的电源线 (Vy1 ~ Vym) 连接到每个像素的电源线 (Vx1 ~ Vxn),且这些电源线排列成矩阵。因此,流过 EL 元件 1003 的电流不仅在平行于源极信号线 (S1 ~ Sn) 的方向上提供,而且在垂直方向上提供。因此,可解决本发明中要解决的问题之一,即布线电阻需要尽可能地低。

[0216] 因为布线电阻可以较低,所以减少了当 EL 显示装置由模拟驱动方法驱动时发生的串扰。此外,可减少 EL 显示装置由数字驱动方法和恒压驱动方法组合操作时发生的灰度显示缺陷。

[0217] 然而,本实施方式的目的之一是与实施方式 1 相似地以低成本制造 EL 显示装置。因此,EL 显示装置可通过微滴排放法经由 EL 显示装置制造工艺来制造,微滴排放法是能够选择性地形成图案的 EL 显示装置制造方法之一。

[0218] 在此,对将微滴排放法用于制造 EL 显示装置时的成本降低时的问题进行描述。

[0219] 图 7A ~ 7D 是通过微滴排放法形成为布线的导电层的平面俯视图 (A 和 B) 以及截面图 (C 和 D)。当通过排放含有导电材料的混合物而形成导电层时,取决于要排放的导电材料的特性、基底的抗水性、排放位置的误差等,该导电层可以不在期望位置形成期望形状

(参见图 7B 和 7D)。

[0220] 在此,布线的电阻在使用相同导电材料时取决于布线的长度和横截面的面积。在如图 7B 和 7D 所示未获得期望形状的情形中,布线的电阻变得比设计值高。即,通过微滴排放法形成的布线与通过光刻法形成的布线相比在布线电阻上有更多变化。

[0221] 有了较高的布线电阻,在使用模拟驱动方法的情形中发生串扰,而在如上所述在数字驱动方法中使用恒压驱动的情形中灰度显示中出现缺陷。当布线电阻变化时,像素的显示缺陷取决于电源线而不同。这可被容易地观察为显示不均。

[0222] 即,将微滴排放法用于降低成本的问题之一是布线电阻的变化。据此,需要布线电阻的变化尽可能地小。

[0223] 在此,对可减少因微滴排放法引起的布线电阻的变化的实施方式进行描述。

[0224] 这可通过考虑当电源线排列成矩阵时所有布线电阻并联连接来描述。即,当布线电阻并联连接时,直到某一像素的电源线的电阻值取决于所有电源线的电阻值,并取决于非矩阵排列情形中存在的电阻的位置而变小。

[0225] 即,根据本实施方式,可解决在使用微滴排放法的情形中布线电阻的变化需要尽可能小的目的,并且可减小电源线的布线电阻。

[0226] 注意,在本实施方式中布线并不需要设置成彼此平行,而是可在任何方向上设置。此外,电源线并不需要是每个像素只有一条,而是可按需设置。此外,电源线不需要在全部像素部分中都排列成矩阵,而是可在像素部分的一部分中排列成矩阵。

[0227] 此外,本实施方式可结合实施方式 1 自由地实现。

[0228] [实施方式 3]

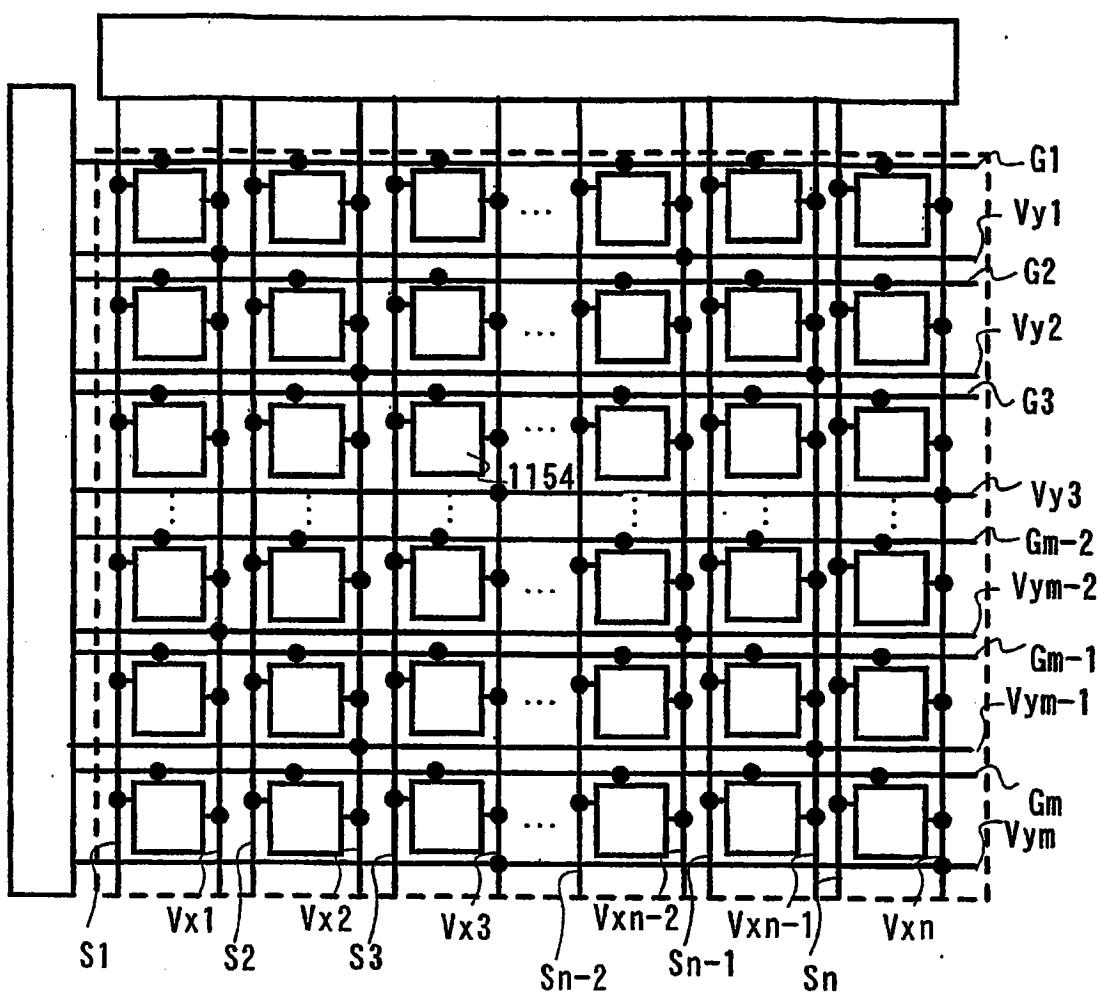

[0229] 参照图 10、16A 和 16B 对本发明一实施方式进行描述。

[0230] 在图 10 中,每一像素中的电路 1054 被描述为如图 16A 和 16B 中所示的电路。然而,这仅是一个示例,且每一像素中的电路并不限于图 16A 和 16B 中的电路。

[0231] 像素部分的第一行、第一列的像素包括栅极信号线 G1、源极信号线 S1、电源线 Vx1、电源线 Vy1R、开关 TFT 1001、驱动 TFT 1002、EL 元件 1003、以及电容器 1004。

[0232] 描述了像素与电路之间的连接。栅极信号线 G1 与开关 TFT 1001 的栅电极相连,源极信号线 S1 与开关 TFT 1001 的源电极或漏电极相连,电源线 Vx1 与驱动 TFT 1002 的源电极或漏电极以及电容器 1004 的一个电极相连。电源线 Vy1R 与电源线 Vx1 相连,且电容器 1004 的另一个电极连接到开关 TFT 1001 的源电极或漏电极中的另一个、以及驱动 TFT 1002 的栅电极。驱动 TFT 1002 的源电极或漏电极中的另一个与 EL 元件 1003 相连。

[0233] 此外,像素部分的第二行、第一列的像素包括栅极信号线 G2、源极信号线 S1、电源线 Vx1、电源线 Vy2R、开关 TFT 1001、驱动 TFT 1002、EL 元件 1003、以及电容器 1004。

[0234] 像素部分的第二行、第一列的像素与第一行、第一列的像素的不同之处在于:使用 G2 代替 G1,且使用 Vy2R 代替 Vy1R。

[0235] 此外,像素部分的第三行、第一列的像素与第一行、第一列的像素的不同之处在于:使用 G3 代替 G1,且使用 Vy3R 代替 Vy1R。

[0236] 另外,像素部分的第一列的像素是上述三行的结构的重复。

[0237] 此外,像素部分的第一行、第二列的像素与第一行、第一列的像素的不同之处在于:使用 S2 代替 S1,使用 Vx2 代替 Vx1,且使用 Vy1G 代替 Vy1R。

[0238] 另外,像素部分的第二行、第二列的像素与第一行、第二列的像素的不同之处在于:使用 G2 代替 G1,且使用 Vy2G 代替 Vy1G。

[0239] 此外,像素部分的第三行、第二列的像素与第一行、第二列的像素的不同之处在于:使用 G3 代替 G1,且使用 Vy3G 代替 Vy1G。

[0240] 另外,第二列的像素是上述三行的结构的重复。

[0241] 此外,像素部分的第一行、第三列的像素与第一行、第一列的像素的不同之处在于:使用 S3 代替 S1,使用 Vx3 代替 Vx1,且使用 Vy1B 代替 Vy1R。

[0242] 另外,像素部分的第二行、第三列的像素与第一行、第三列的像素的不同之处在于:使用 G2 代替 G1,且使用 Vy2B 代替 Vy1B 使用。

[0243] 此外,像素部分的第三行、第三列的像素与第一行、第三列的像素的不同之处在于:使用 G3 代替 G1,且使用 Vy3B 代替 Vy1B。

[0244] 另外,第三列的像素是上述三行的结构的重复。

[0245] 此外, Vy1R ~ VymR 彼此全部电连接。

[0246] 此外, Vy1G ~ VymG 彼此全部电连接。

[0247] 此外, Vy1B ~ VymB 彼此全部电连接。

[0248] 在本实施方式中,像素部分中的电源线不仅是平行于源极信号线 (S1 ~ Sn) 设置的布线 (Vx1 ~ Vxn),而且是在垂直方向或几乎垂直方向上设置的布线 (Vy1R ~ VymB),由此电压从每一方向分别提供给每一 R、G 和 B 像素的驱动 TFT1002 的源极区或漏极区。设置在垂直方向或几乎垂直方向上的电源线 (Vy1 ~ Vym) 连接到每一 R、G 和 B 像素的电源线 (Vx1 ~ Vxn),且这些电源线排列成矩阵。因此,流过 EL 元件 1003 的电流不仅在平行于源极信号线 (S1 ~ Sn) 的方向上提供,而且在垂直方向上提供。因此,可解决本发明中要解决的问题之一,即布线电阻需要尽可能地低。此外,不同的电压电平可施加于独立连接的 R、G 和 B 像素。

[0249] 因为布线电阻可以较低,所以减少了当 EL 显示装置由模拟驱动方法驱动时发生的串扰。此外,可减少 EL 显示装置由数字驱动方法和恒压驱动方法组合操作时发生的灰度显示缺陷。

[0250] 然而,本实施方式要解决的问题之一是与实施方式 1 和 2 相似地以低成本制造 EL 显示装置。因此,EL 显示装置可通过微滴排放法经由 EL 显示装置制造工艺来制造,微滴排放法是能够选择性地形成图案的 EL 显示装置制造方法之一。

[0251] 在通过微滴排放法形成布线的情形中,如上所述布线电阻发生变化。根据本实施方式,可减少因微滴排放法引起的布线电阻的变化。

[0252] 这可通过考虑当电源线排列成矩阵时所有布线电阻并联连接来描述。即,当布线电阻并联连接时,直到某一像素的电源线的电阻值取决于所有电源线的电阻值,并取决于非矩阵排列情形中存在的电阻的位置而变小。

[0253] 即,根据本实施方式,可解决在使用微滴排放法的情形中布线电阻的变化需要尽可能小的问题,并且可减小电源线的布线电阻。

[0254] 注意,在本实施方式中布线并不需要设置成彼此平行,而是可在任何方向上设置。此外,电源线并不需要是每个像素只有一条,而是可按需设置。此外,电源线不需要在全部像素部分中都排列成矩阵,而是可在像素部分的一部分中排列成矩阵。

[0255] 此外,本实施方式可结合实施方式 1 和 2 自由地实现。

[0256] [ 实施方式 4]

[0257] 参照图 11、16A 和 16B 对本发明一实施方式进行描述。

[0258] 在图 11 中,每一像素中的电路 1154 被描述为如图 16A 和 16B 中所示的电路。然而,这仅是一个示例,且每一像素中的电路并不限于图 16A 和 16B 中的电路。

[0259] 像素部分的第一行、第一列的像素包括栅极信号线 G1、源极信号线 S1、电源线 Vx1、电源线 Vy1、开关 TFT 1001、驱动 TFT 1002、EL 元件 1003、以及电容器 1004。

[0260] 描述了像素与电路之间的连接。栅极信号线 G1 与开关 TFT 1001 的栅电极相连,源极信号线 S1 与开关 TFT 1001 的源电极或漏电极相连。电源线 Vx1 与驱动 TFT 1002 的源电极或漏电极以及电容器 1004 的一个电极相连。电源线 Vy1 与电源线 Vx1 相连,且电容器 1004 的另一个电极连接到开关 TFT 1001 的源电极或漏电极中的另一个、以及驱动 TFT 1002 的栅电极。驱动 TFT 1002 的源电极或漏电极中的另一个与 EL 元件 1003 相连。

[0261] 此外,像素部分的第二行、第一列的像素与第一行、第一列的像素的不同之处在于:使用 G2 代替 G1,且可具有其中 Vx1 不连接到另一电源线以便于使每一 R、G 和 B 的电源线电隔离的配置。

[0262] 此外,像素部分的第三行、第一列的像素与第一行、第一列的像素的不同之处在于:使用 G3 代替 G1,且可具有其中 Vx1 不连接到另一电源线以便于使每一 R、G 和 B 的电源线电隔离的配置。

[0263] 另外,像素部分的第四行、第一列的像素与第一行、第一列的像素的不同之处在于:使用 G4 代替 G1,且使用 Vy4 代替 Vy1。

[0264] 此外,像素部分的第五行、第一列的像素与第四行、第一列的像素的不同之处在于:使用 G5 代替 G4,且可具有其中 Vx1 不连接到另一电源线以便于使每一 R、G 和 B 的电源线电隔离的配置。

[0265] 此外,像素部分的第六行、第一列的像素与第四行、第一列的像素的不同之处在于:使用 G6 代替 G4,且可具有其中 Vx1 不连接到另一电源线以便于使每一 R、G 和 B 的电源线电隔离的配置。

[0266] 另外,第一列的像素是上述三行的结构的重复。

[0267] 此外,像素部分的第一行、第二列的像素与第一行、第一列的像素的不同之处在于:使用 S2 代替 S1,使用 Vx2 代替 Vx1,且可具有其中 Vx2 不连接到另一电源线以便于使每一 R、G 和 B 的电源线电隔离的配置。

[0268] 另外,像素部分的第二行、第二列的像素与第一行、第二列的像素的不同之处在于:使用 G2 代替 G1,且可具有其中 Vx2 不连接到另一电源线 Vy2 的配置。

[0269] 此外,像素部分的第三行、第二列的像素与第一行、第二列的像素的不同之处在于:使用 G3 代替 G1,且可具有其中 Vx2 不连接到另一电源线以便于使每一 R、G 和 B 的电源线电隔离的配置。

[0270] 另外,第二列的像素是上述三行的结构的重复。

[0271] 此外,像素部分的第一行、第三列的像素与第一行、第一列的像素的不同之处在于:使用 S3 代替 S1,使用 Vx3 代替 Vx1,且可具有其中 Vx3 不连接到另一电源线以便于使每一 R、G 和 B 的电源线电隔离的配置。

[0272] 另外,像素部分的第二行、第三列的像素与第一行、第三列的像素的不同之处在于:使用 G2 代替 G1,且可具有其中 Vx3 不连接到另一电源线的配置。

[0273] 此外,第三行、第三列的像素与第一行、第三列的像素的不同之处在于:使用 G3 代替 G1,且可具有其中 Vx3 不连接到另一电源线 Vy3 以便于使每一 R、G 和 B 的电源线电隔离的配置。

[0274] 另外,第三列的像素是上述三行的结构的重复。

[0275] 像素部分中其余的列具有其中重复第一~第三列的配置的配置

[0276] 此外, Vx1, Vx4, …, Vx(3i-2), Vy1, Vy4, …, 和 Vy(3j-2) 彼此全部电连接 (i, j 都是自然数)。

[0277] 此外, Vx2, Vx5, …, Vx(3i-1), Vy2, Vy5, …, 和 Vy(3j-1) 彼此全部电连接 (i, j 都是自然数)。

[0278] 此外, Vx3, Vx6, …, Vx(3i), Vy3, Vy6, …, 和 Vy(3j) 彼此全部电连接 (i, j 都是自然数)。

[0279] 在本实施方式中,像素部分中的电源线不仅是平行于源极信号线 (S1 ~ Sn) 设置的布线 (Vx1 ~ Vxn),而且是在垂直方向或几乎垂直方向上设置的布线 (Vy1 ~ Vym),由此电压从每一方向分别提供给 R、G 和 B 像素的驱动 TFT 1002 的源极区或漏极区。设置在垂直方向或几乎垂直方向上的电源线 (Vy1 ~ Vym) 连接到每一 R、G 和 B 像素的电源线 (Vx1 ~ Vxn),且这些电源线排列成矩阵。因此,流过 EL 元件 1003 的电流不仅在平行于源极信号线 (S1 ~ Sn) 的方向上提供,而且在垂直方向上提供。因此,可解决本发明中要解决的问题之一,即布线电阻需要尽可能地低。此外,不同的电压电平可施加于独立连接的 R、G 和 B 像素。

[0280] 此外,当一条电源线被设置成与每一像素中的栅极信号线平行时,布线电阻 可在不显著降低孔径比并增大布线之间的寄生电容的情况下降低。

[0281] 因为布线电阻可以较低,所以减少了当 EL 显示装置由模拟驱动方法驱动时发生的串扰。此外,可减少 EL 显示装置由数字驱动方法和恒压驱动方法组合操作时发生的灰度显示缺陷。

[0282] 然而,本实施方式要解决的问题之一是与实施方式 1、2 和 3 相似地以低成本制造 EL 显示装置。因此,EL 显示装置可通过微滴排放法经由 EL 显示装置制造工艺来制造,微滴排放法是能够选择性地形成图案的 EL 显示装置制造方法之一。

[0283] 在通过微滴排放法形成布线的情形中,如上所述布线电阻发生变化。根据本实施方式,可减少因微滴排放法引起的布线电阻的变化。

[0284] 这可通过考虑当电源线排列成矩阵时所有布线电阻并联连接来描述。即,当布线电阻并联连接时,直到某一像素的电源线的电阻值取决于所有电源线的电阻值,并取决于非矩阵排列情形中存在的电阻的位置而变小。

[0285] 即,根据本实施方式,可解决在使用微滴排放法的情形中布线电阻的变化需要尽可能小的问题,并且可减小电源线的布线电阻。

[0286] 注意,在本实施方式中布线并不需要设置成彼此平行,而是可在任何方向上设置。此外,电源线并不需要是每个像素只有一条,而是可按需设置。此外,电源线不需要在全部像素部分中都排列成矩阵,而是可在像素部分的一部分中排列成矩阵。

[0287] 此外,本实施方式可结合实施方式 1、2 和 3 自由地实现。

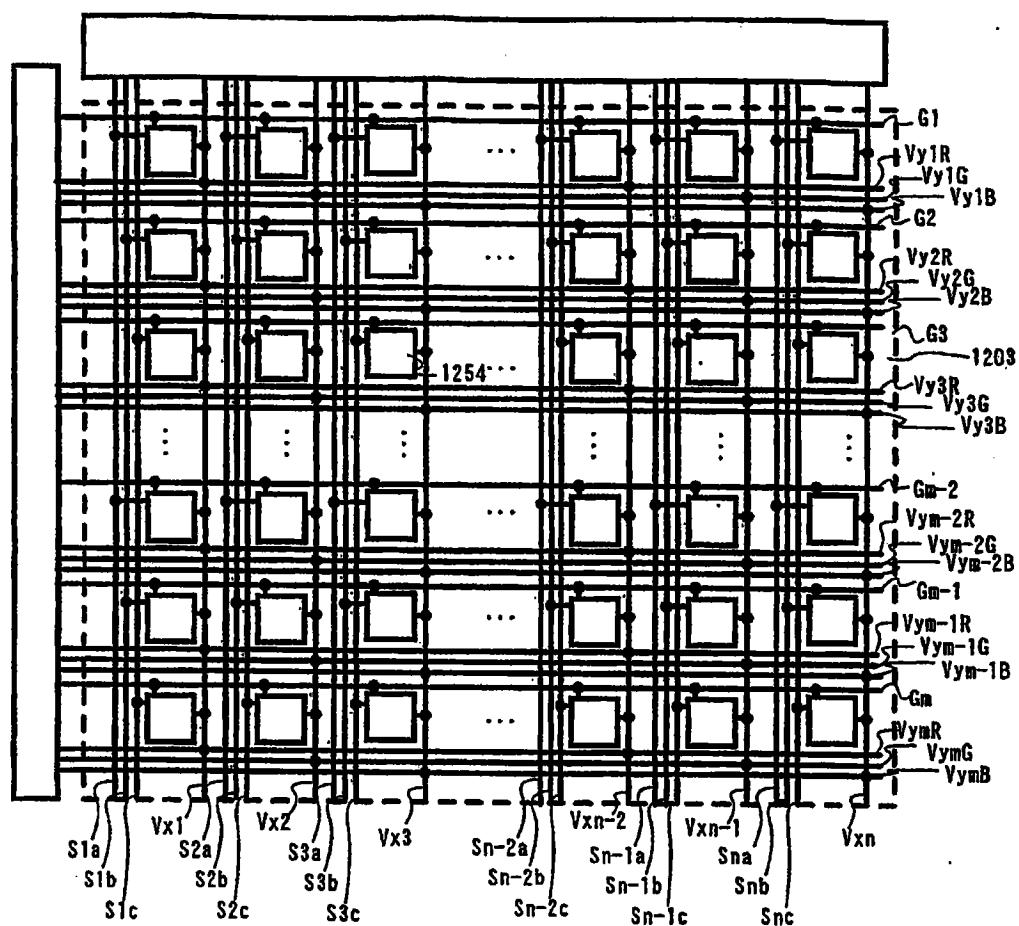

[0288] [ 实施方式 5]

[0289] 本实施方式是实施方式 1 和实施方式 2、3 或 4 的组合。在此参照图 12、16A 和 16B 描述一种配置。

[0290] 图 12 和 16 示出本实施方式的整个像素部分的电路图。在本实施方式中,对一个垂直像素列设置多条源极信号线。在图 8 中,描述对一个垂直像素列设置三条源极信号线的情形。

[0291] 注意,源极信号线的数量并不限于三条,并可按需设置。

[0292] 在图 12 中,每一像素中的电路 1254 被描述为如图 16A 和 16B 中所示的电路。然而,这仅是一个示例,且每一像素中的电路并不限于图 16 中的电路。

[0293] 第一行、第一列的像素包括栅极信号线 G1、作为三条源极信号线之一的源极信号线 S1a、电源线 Vx1、开关 TFT 1001、驱动 TFT 1002、EL 元件 1003、以及电容器 1004。

[0294] 描述了像素与电路之间的连接。栅极信号线 G1 与开关 TFT 1001 的栅电极相连,作为三条源极信号线之一的源极信号线 S1a 与开关 TFT 1001 的源电极或漏电极相连,电源线 Vx1 与驱动 TFT 1002 的源电极或漏电极以及电容器 1004 的一个电极相连。电源线 Vy1R 与电源线 Vx1 相连,且电容器 1004 的另一个电极连接到开关 TFT 1001 的源电极或漏电极中的另一个、以及驱动 TFT 1002 的栅电极。驱动 TFT 1002 的源电极或漏电极中的另一个与 EL 元件 1003 相连。

[0295] 此外,像素部分的第二行、第一列的像素包括栅极信号线 G2、作为三条源极信号线之一的源极信号线 S1b、电源线 Vx1、电源线 Vy2R、开关 TFT 1001、驱动 TFT 1002、EL 元件 1003、以及电容器 1004。

[0296] 第二行、第一列的像素与第一行、第一列的像素的不同之处在于:使用 G2 代替 G1,使用 S1b 代替 S1a,且使用 Vy2R 代替 Vy1R。

[0297] 第三行、第一列的像素包括栅极信号线 G3、作为三条源极信号线之一的源极信号线 S1c、电源线 Vx1、电源线 Vy3R、开关 TFT 1001、驱动 TFT 1002、EL 元件 1003、以及电容器 1004。

[0298] 像素部分的第三行、第一列的像素与第一行、第一列的像素的不同之处在于:使用 G3 代替 G1,使用 S1c 代替 S1a,且使用 Vy3R 代替 Vy1R 使用。

[0299] 此外,在上述三个像素列中,G1、G2 和 G3 电连接。

[0300] 另外,第一列的像素是上述结构的重复。

[0301] 此外,第二列的像素与上述结构的不同之处在于:使用 Vx2 代替 Vx1,使用 S2a 代替 S1a,使用 S2b 代替 S1b,使用 S2c 代替 S1c,使用 Vy1G 代替 Vy1R 使用,使用 Vy2G 代替 Vy2R,且使用 Vy3G 代替 Vy3R。

[0302] 此外,第三列的像素与上述结构的不同之处在于:使用 Vx3 代替 Vx1,使用 S3a 代替 S1a,使用 S3b 代替 S1b,使用 S3c 代替 S1c,使用 VynB 代替 Vy1R,使用 Vy2B 代替 Vy2R,且使用 Vy3B 代替 Vy3R。

[0303] 另外,第三列之后的像素列是上述结构的重复。

[0304] 此外,Vy1R ~ VymR 彼此全部电连接。

[0305] 此外,Vy1G ~ VymG 彼此全部电连接。

[0306] 此外, Vy1B ~ VymB 彼此全部电连接。

[0307] 根据本实施方式,可解决实施方式 1 中所述的写入时间需要尽可能地长的问题。此外,可解决寄生电容需要尽可能地小的问题。

[0308] 此外,根据本实施方式,可解决实施方式 2、3 或 4 中所述的布线电阻需要尽可能地低的问题。另外,可解决布线电阻的变化需要尽可能地小的问题。

[0309] 另外,根据本实施方式,当使用可选择性地形成图案的微滴排放法时,EL 显示装置可低成本地制造。

[0310] [ 实施方式 6 ]

[0311] 参照图 18A ~ 19F 对本发明一实施方式进行描述。在本实施方式中,沟道蚀刻型薄膜晶体管被用作薄膜晶体管。因此,在此略去对相同部分或具有类似功能的部分的描述。

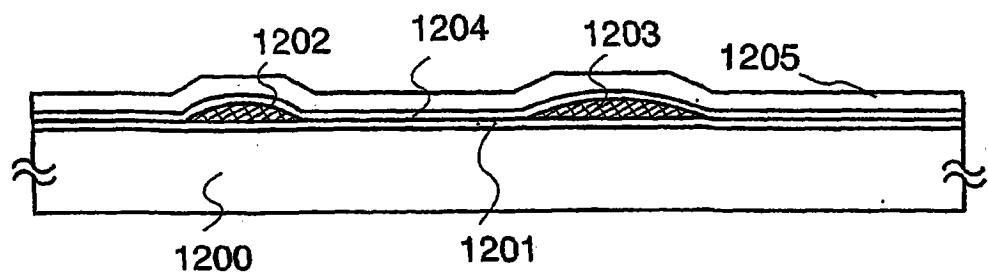

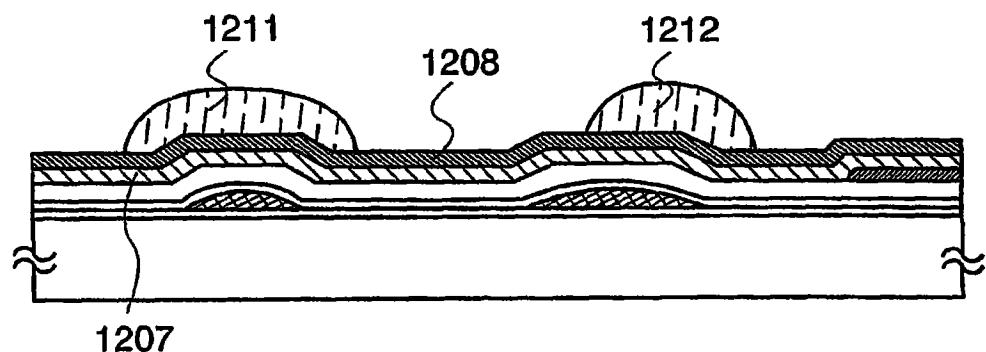

[0312] 具有改进粘性功能的基底膜 1201 在基板 1200 上形成(参见图 18A)。绝缘层可在基板 1200 上形成。该绝缘层被用作基底膜且并非必需设置,但有阻挡来自基板 1200 的污染物等的效果。在形成基底层以便防止来自玻璃基板的污染的情形中,形成基底膜 801 作为对通过微滴排放法在基底层上形成的导电层 1202 和 1203 的预处理。

[0313] 在本实施方式中,具有光催化功能的物质被用作具有改进粘性的功能的基底膜。

[0314] 在本实施方式中,对通过溅射法形成具有预定晶体结构的 Ti0x 晶体作为光催化物质的情形进行描述。通过将金属钛管用作靶并使用氩气和氧气来进行溅射。此外,也可引入氦气。为了形成具有高度光催化活性的 Ti0x,在相当高压下使用含有大量氧气的空气。此外, Ti0x 较佳地在加热沉积腔室或要在其上形成待处理对象的基板时形成。

[0315] 以此方式形成的 Ti0x 即使在相当薄的薄膜形式中也具有光催化功能。

[0316] 较佳的是通过溅射法或气相沉积法使用诸如 Ti(钛)、W(钨)、Cr(铬)、Ta(钽)、Ni(镍) 和 Mo(钼) 等金属材料或其氧化物来形成基底膜 1201。基底膜 1201 可被形成为 0.01 ~ 10nm 厚,且只要它被形成得相当薄,就不必具有层结构。在将高熔点金属材料用作基底膜的情形中,较佳的是在将导电层 1202 和 1203 形成为栅电极层之后通过执行以下两个步骤之一来处理露在该表面上的基底膜。

[0317] 第一种方法是绝缘不与导电层 1202 和 1203 重叠的基底膜 1201 以形成绝缘层的步骤。换言之,氧化并绝缘不与导电层 1202 和 1203 重叠的基底膜 1201。当基底膜 1201 用此方法氧化和绝缘时,较佳的是将基底膜 1201 形成为 0.01 ~ 10nm 厚,从而可容易地氧化基底膜。注意,氧化可通过暴露于氧气或通过热处理来进行。

[0318] 第二种方法是将导电层 1202 和 1203 用作掩模来通过蚀刻去除基底膜 1201 的步骤。当采用该步骤时,对基底膜 1201 的厚度没有限制。

[0319] 可选择地,用于对成型区(成型表面)进行等离子体处理的方法可被用作另一预先基础处理。等离子体处理将空气、氧气或氮气用作处理气体来进行,且压力从数十到数千托(133000 帕),较佳地从 100 托(13300 帕)到 1000 托(133000 帕),更佳地从 700 托(93100 帕)到 800 托(106400 帕),即大气压或接近大气压的压力,并在这样的条件下施加脉冲电压。此时,等离子体密度被设为  $1 \times 10^{10}$  到  $1 \times 10^{14} \text{ m}^{-3}$ ,由此实现所谓的电晕放电或辉光放电。通过采用将空气、氧气或氮气用作处理气体的等离子体处理,可与材料无关地进行表面改性。因此,可对任何材料进行表面改性。

[0320] 作为另一种方法,可形成用作粘合剂的有机材料物质以改进要通过微滴排放法形

成的图案与其成型区之间的粘性。有机材料（有机树脂材料）（聚酰亚胺或丙烯酸）由硅（Si）和氧（O）的键形成的骨架构成，其中至少含有氢的有机基（诸如烷基或芳香烃）被包括作为取代基。或者，氟基可被用作取代基。再或者，氟基或至少含有氢的有机基可被用作取代基。

[0321] 随后，排放含有导电材料的混合物，并且形成用作栅电极的导电层 1202 和 1203。这些导电层 1202 和 1203 通过微滴排放法来形成。在本实施方式中，银被用作导电材料，但也可使用银、铜等的叠层。可选择地，也可使用单层铜。

[0322] 此外，进行形成基底膜 1201 的前述步骤作为对要通过使用微滴排放法形成的导电层的预先基础处理，然而，该处理步骤可在形成该导电层之后执行。

[0323] 随后，在导电层 1202 和 1203 上形成栅绝缘膜（参见图 18A）。该栅绝缘膜可由诸如硅的氧化物或氮化物材料等公知材料形成，并且可以是叠层或单层。

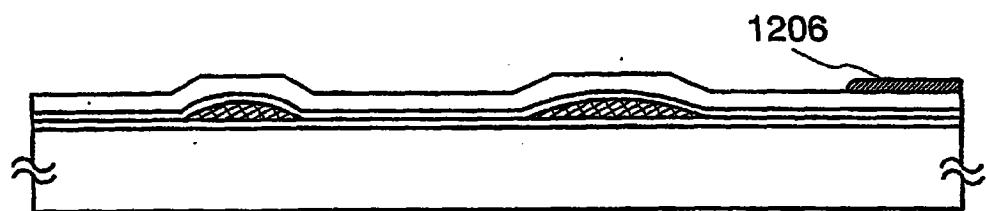

[0324] 随后，导电层（也称为第一电极）1206 通过在栅绝缘膜上选择性地排放含有导电材料的混合物来形成（参见图 18B）。在从基板 1200 一侧发光时或在制造透光 EL 显示面板时，导电层 1206 能以包含氧化铟锡（ITO）、含有氧化硅的氧化铟锡（ITSO）、氧化锌（ZnO）、氧化锡（SnO<sub>2</sub>）等的混合物的预定图案并通过烘干它来形成。尽管未示出，但与形成导电层 1202 和 1203 的情形相似，光催化物质可在形成了导电层 1206 的区域中形成。使用光催化物质可改进粘性，并且导电层 1206 可被形成为成一细线的期望图案。导电层 1206 变成用作像素电极的第一电极。

[0325] 半导体层可通过一公知方法（溅射法、LPCVD 法、等离子体 CVD 法等）形成。对半导体层的材料中没有特定限制，但半导体层较佳地由硅、锗硅（SiGe）合金等形成。

[0326] 半导体层由非晶半导体（通常为氢化非晶硅）、半非晶半导体、其半导体层局部具有晶相的半导体、结晶半导体（通常为多晶硅）或有机半导体作为材料来形成。

[0327] 在本实施方式中，非晶半导体被用作半导体。形成半导体层 1207，且具有一种导电性的半导体层（例如 N 型半导体层 1208）通过等离子体 CVD 法等形成（参见图 12C）。具有一种导电性的半导体层可按需形成。

[0328] 随后，形成各自由诸如抗蚀剂和聚酰亚胺等绝缘体形成的掩模层 1211 和 1212，然后，半导体层 1207 和 N 型半导体层 1208 通过使用掩模层 1211 和 1212 来同时图案化。

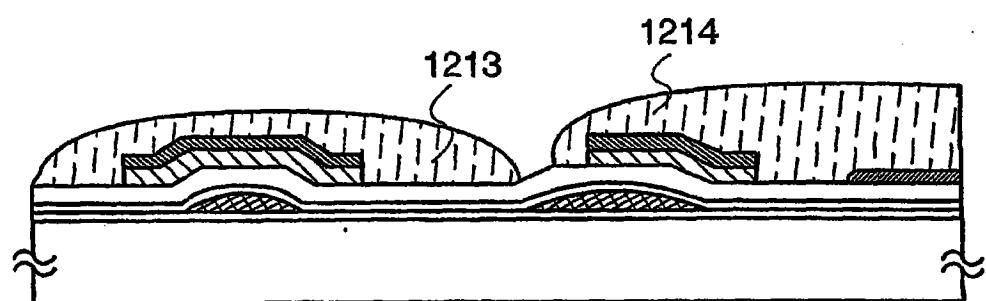

[0329] 然后，由诸如抗蚀剂和聚酰亚胺等绝缘体形成的掩模层 1213 和 1214 通过微滴排放法来形成（参见图 18D）。通过使用掩模层 1213 和 1214，通孔 1218 通过蚀刻工艺在栅绝缘层 1204 和 1205 的一部分中形成，从而暴露置于其下层一侧并用作栅电极层的导电层的一部分。

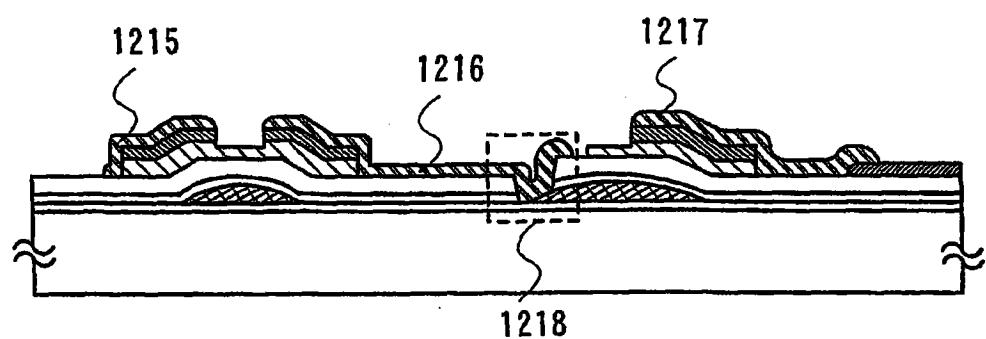

[0330] 在去除掩模层 1213 和 1214 之后，导电层 1215、1216 和 1217 通过排放含有导电材料的混合物来形成，并且 N 型半导体将导电层 1215、1216 和 1217 用作掩模来图案化，以形成 N 型半导体层（参见图 19A）。注意，在形成导电层 1215、1216 和 1217 之前，光催化物质可在导电层 1215、1216 和 1217 与栅绝缘层 1205 接触的部分中选择性地形成。因此，导电层可被形成为具有令人满意的粘性。

[0331] 导电层 1217 用作源极布线层或漏极布线层，并被形成为与预先形成的作为第一电极的导电层 1206 电连接。此外，作为源极布线层或漏极布线层的导电层 1216、以及作为栅电极层的导电层 1203 通过在栅绝缘层 1205 中形成的通孔 1218 彼此电连接。

[0332] 在栅绝缘层 1204 和 1205 的一部分中形成通孔 1218 的步骤可在形成导电层 1215、1216 和 1217 之后进行,且导电层 1215、1216 和 1217 作为掩模成为布线层。然后,导电层在通孔 1218 中形成,且作为栅电极层的导电层 1216 和导电层 1203 电连接。在该情形中,优点在于制造步骤可得到简化。

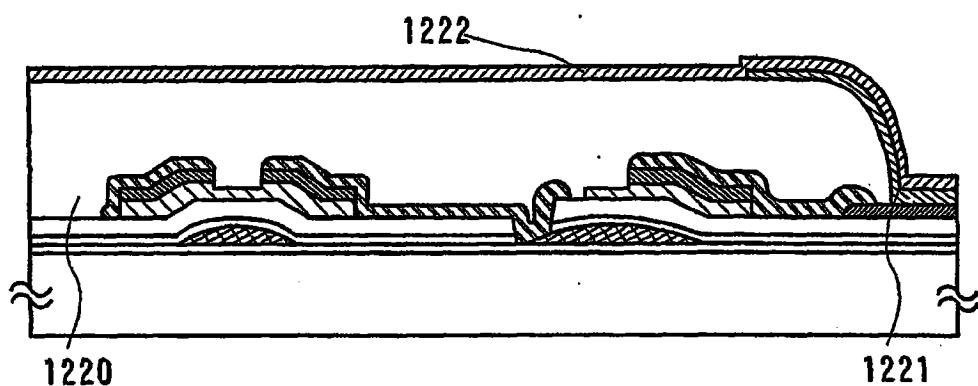

[0333] 随后,形成要成为分隔壁的绝缘层 1220。在绝缘层通过旋涂法或浸渍法完全形成之后,如图 19B 所示通过蚀刻工艺在绝缘层 1220 中形成一开口。当绝缘层 1220 通过微滴排放法形成时不必进行蚀刻过程。

[0334] 绝缘层 1220 被形成为带有具有与其中像素要与作为第一电极的导电层 1206 相对应地形成的位置来设置的开口部分的通孔。

[0335] 根据上述步骤,完成了 TFT 基板,其中底栅型(也称为逆向交错型)沟道保护型 TFT 和作为第一电极的导电层 1206 在基板 1200 上连接。

[0336] 通过在作为第一电极的导电层 1206 上层叠场致发光层 1221 并在其上层叠导电层 1222,完成了使用发光元件的、具有显示功能的显示装置(参见图 19B)。

[0337] 如上所述,通过不应用使用光掩模的曝光步骤,在本实施方式中可略去该步骤。此外,即使在使用一边超过 1000 毫米的第五代或以后玻璃基板时,EL 显示面板也可通过微滴排放法在基板上直接形成各种图案来容易地制造。

[0338] 此外,可制造粘性和抗剥离性得到改进的高度可靠的显示装置。

[0339] [ 实施方式 7 ]

[0340] 参照图 20A ~ 21 对本发明一实施方式进行描述。本实施方式与实施方式 1 的不同之处在于:顶栅(也成为正向交错)型薄膜晶体管被用作薄膜晶体管。因此,在此略去对相同部分或具有类似功能的部分的描述。

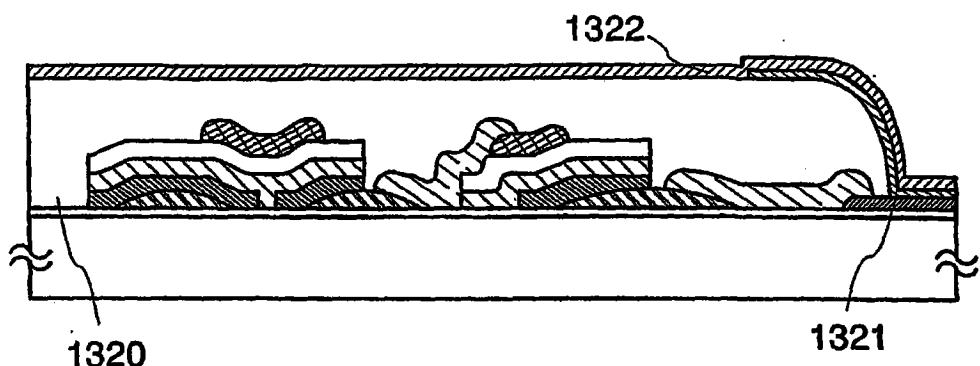

[0341] 具有改进粘性功能的基底膜 1301 在基板 1300 上形成(参见图 20A)。注意,绝缘层可在基板 1300 上形成。该绝缘层并非必需设置,但有阻挡来自基板 1300 的污染物等的效果。在如本实施方式中使用正向交错薄膜晶体管的情形中,半导体层与基板直接接触,因此不需要基底层。在形成基底层以便防止来自玻璃基板的污染的情形中,基底膜 1301 通过微滴排放法在基底层上形成,作为对其成型区中的导电层 1302 和 1303 的预处理。

[0342] 在本实施方式中,具有光催化功能的物质被用作具有改进粘性的功能的基底膜。

[0343] 在本实施方式中,对通过溅射法形成具有预定晶体结构的 TiO<sub>x</sub> 作为光催化物质的情形进行描述。通过将金属钛管用作靶并使用氩气和氧气来进行溅射。此外,也可引入氦气。为了形成具有高度光催化活性的 TiO<sub>x</sub>,在相当高压下使用含有大量氧气的空气。此外,TiO<sub>x</sub> 较佳地在加热沉积腔室或在其上形成元件的基板时形成。

[0344] 以此方式形成的 TiO<sub>x</sub> 即使在相当薄的薄膜形式中也具有光催化功能。

[0345] 较佳的是使用诸如 Ti(钛)、W(钨)、Cr(铬)、Ta(钽)、Ni(镍) 和 Mo(钼) 等金属材料或其氧化物来形成基底膜 1301。基底膜 1301 可被形成为 0.01 ~ 10nm 厚,并且只要它被形成得相当薄,就不必具有层结构。在将高熔点材料用作基底膜的情形中,较佳的是在将导电层 1315、1316 和 1317 形成为源极布线层或漏极布线层之后通过执行以下两个步骤之一来处理露在该表面上的基底膜。

[0346] 第一种方法是绝缘不与导电层 1315、1316 和 1317 重叠的基底膜 1301 以形成绝缘层的步骤。换言之,氧化并绝缘不与导电层 1315、1316 和 1317 重叠的基底膜 1301。当基

底膜 1301 用此方法氧化和绝缘时, 较佳的是将基底膜 1301 形成为 0.01 ~ 10nm 厚, 从而可容易地氧化基底膜。注意, 氧化可通过暴露于氧气氛或通过热处理来进行。

[0347] 第二种方法是将用作源极布线层或漏极布线层的导电层 1315、1316 和 1317 用作掩模来通过蚀刻去除基底膜 1301 的步骤。当采用该步骤时, 对基底膜 1301 的厚度没有限制。

[0348] 可选择地, 用于对成型区 (成型表面) 进行等离子体处理的方法可被用作另一预先基础处理。等离子体处理将空气、氧气或氮气用作处理气体来进行, 且压力从数十到数千托 (133000 帕), 较佳地从 100 托 (13300 帕) 到 1000 托 (133000 帕), 更佳地从 700 托 (93100 帕) 到 800 托 (106400 帕), 即大气压或接近大气压的压力, 并在这样的条件下施加脉冲电压。此时, 等离子体密度被设置为  $1 \times 10^{10}$  到  $1 \times 10^{14} \text{ m}^{-3}$ , 由此实现所谓的电晕放电或辉光放电。通过采用将空气、氧气或氮气用作处理气体的等离子体处理, 可与材料无关地进行表面改性。因此, 可对任何材料进行表面改性。

[0349] 作为另一种方法, 可形成用作粘合剂的基于有机材料的物质以改进要通过微滴排放法形成的图案与其成型区之间的粘性。有机材料 (有机树脂材料) (聚酰亚胺或丙烯酸) 由硅 (Si) 和氧 (O) 的键形成的骨架构成, 其中至少含有氢的有机基 (诸如烷基或芳香烃) 被包括作为取代基。或者, 氟基可被用作取代基。再或者, 氟基或至少含有氢的有机基可被用作取代基。

[0350] 随后, 排放含有导电材料的混合物, 并且形成用作源极布线层或漏极布线层的导电层 1315、1316 和 1317。这些导电层 1315、1316 和 1317 通过微滴排放法来形成。

[0351] 作为用于形成导电层 1315、1316 和 1317 的导电材料, 可使用含有诸如 Ag (银)、Au (金)、Cu (铜)、W (钨) 和 Al (铝) 等金属粒子作为其主要成分的混合物。具体地, 较佳的是考虑到电阻率, 通过使用溶解或分散在溶剂中的金、银和铜的任一种形成电阻率较低的源极布线层或漏极布线层。更佳的是使用具有低电阻的银或铜。对于这样的溶剂, 可使用诸如乙酸丁酯等酯、诸如异丙醇等醇、诸如丙酮等有机溶剂等。表面张力和粘性通过控制溶液的浓度并添加表面活性剂来适当地控制。

[0352] 随后, 导电层 (也称为第一电极) 1306 通过选择性地排放含有导电材料的混合物来形成 (参见图 20A)。在从基板 1300 一侧发光时或在制造透光 EL 显示面板时, 导电层 1306 能以包含氧化铟锡 (ITO)、含有氧化硅的氧化铟锡 (ITSO)、氧化锌 (ZnO)、氧化锡 (SnO<sub>2</sub>) 等的混合物的预定图案并烘干它来形成。尽管未示出, 但与形成导电层 1315、1316 和 1317 的情形相似, 光催化物质可在形成了导电层 1306 的区域中形成。使用光催化物质可改进粘性, 并且导电层 1306 可被形成为成一细线的期望图案。导电层 1306 变成用作像素电极的第一电极。

[0353] 此外, 上述形成基底膜 1301 的步骤作为对通过微滴排放法形成的导电层的预先基础处理来进行, 然而该处理步骤可在形成导电层 1315、1316 和 1317 之后进行。例如, 通过在其上形成氧化钛膜和 N 型半导体层 (尽管未示出), 导电层与 N 型半导体层之间的粘性得到改进。

[0354] 在导电层 1315、1316 和 1317 的整个表面上形成 N 型半导体层之后, 设置在导电层 1315 与 1316 之间以及导电层 1316 和 1317 之间的 N 型半导体层使用由诸如抗蚀剂和聚酰亚胺等绝缘体形成的掩模层 1311、1312 和 1319 通过蚀刻来去除。可按需形成具有一种导

电性的半导体层。然后,由非晶半导体(下文中成为 AS)或 SAS 形成的半导体层 1307 通过气相法或溅射法来形成。在采用等离子体 CVD 法的情形中,AS 通过将 SiH<sub>4</sub> 用作半导体材料气体或 SiH<sub>4</sub> 和 H<sub>2</sub> 的混合气体来形成。SAS 由其中用 H<sub>2</sub> 稀释 SiH<sub>4</sub> 3-1000 倍的混合气体来形成。当 SAS 由以上类型的气体形成时,半导体层在一表面侧具有令人满意的结晶度。SAS 适于其中栅电极在半导体层的上层形成的顶栅型 TFT。

[0355] 随后,栅绝缘层 1305 通过等离子体 CVD 法或溅射法被形成为具有单层或叠层结构。具体地,由氮化硅形成的绝缘层、由氧化硅形成的绝缘层、以及由氮化硅形成的绝缘层的三层叠层是一较佳结构。

[0356] 然后,栅电极层 1302 和 1303 通过微滴排放法来形成。含有诸如 Ag(银)、Au(金)、Cu(铜)、W(钨) 或 Al(铝) 等金属粒子作为其主要成分的混合物可用作形成栅电极层 1302 和 1303 的导电材料。

[0357] 半导体层 1307 和栅绝缘层 1305 使用通过微滴排放法形成的掩模层 1313 和 1314 在与源极布线层和漏极布线层(导电层 1315、1316 和 1317)相对应的位置中形成。换言之,半导体层和栅绝缘层被形成为跨接在导电层 1315 和 1316 上。

[0358] 随后,导电层 1330 和 1331 通过微滴排放法来形成。导电层 1316 和栅电极层 1303、以及导电层 1317 和作为第一电极的导电层 1306 彼此电连接。

[0359] 源极布线层或漏极布线层以及栅电极层可在不使用导电层 1330 的情况下直接通过栅电极层相连。在该情形中,在栅绝缘层 1305 中形成通孔,且作为源极布线或漏极布线的导电层 1316 和 1317 的一部分在形成导电层 1316 和 1317 之前曝光。然后,栅电极层 1302、1303 和导电层 1331 通过微滴排放法来形成。此时,栅电极层 1303 是同样用作导电层 1330 的布线,并连接到导电层 1316。干法蚀刻或湿法蚀刻都可用于蚀刻,然而作为干法蚀刻的等离子体蚀刻是更佳的。

[0360] 随后,形成要成为分隔壁的绝缘层 1320。尽管未示出,但由氮化硅或氮氧化硅形成的保护层可完全在绝缘层 1320 之下形成以覆盖薄膜晶体管。在绝缘层通过旋涂法或浸渍法完全形成之后,如图 21 所示通过蚀刻工艺在绝缘层 1320 中形成一开口。当绝缘层 1320 通过微滴排放法形成时不必进行蚀刻过程。在通过微滴排放法形成诸如绝缘层 1320 等宽广区域时,可通过从微滴排放设备的喷嘴的多个排放口中排放混合物并进行绘制以使多条线彼此重叠来形成以改进生产量。

[0361] 绝缘层 1320 被形成为具有与其中像素要根据作为第一电极的导电层 1306 形成的位置相对应的通孔。

[0362] 根据上述步骤完成 TFT 基板,其中顶栅型(也称为逆向交错型)TFT 和作为第一电极层的导电层 1306 在基板 1300 上连接。

[0363] 在形成场致发光层 1321 之前,绝缘层 1320 内或其表面所吸收的湿气通过在 200℃ 大气压下进行热处理来去除。此外,在降低压力下在 200 ~ 400℃(较佳地 250 ~ 350℃)的温度下进行热处理,且场致发光层 1321 较佳地通过真空气相沉积法或微滴排放法在不暴露于大气的情况下在降低压力下形成。

[0364] 场致发光层 1321 和导电层 1322 层叠在作为第一电极的导电层 1306 上,然后完成使用发光元件的具有显示功能的显示装置(参见图 21)。

[0365] 如上所述,通过不应用使用光掩模的曝光步骤,在本实施方式中可略去该步骤。此

外,即使在使用一边超过 1000 毫米的第五代或以后玻璃基板时,EL 显示面板也可通过微滴排放法在基板上直接形成各种图案来容易地制造。

[0366] 此外,可制造粘性和抗剥离性得到改进的高度可靠的显示装置。

[0367] [ 实施方式 8 ]

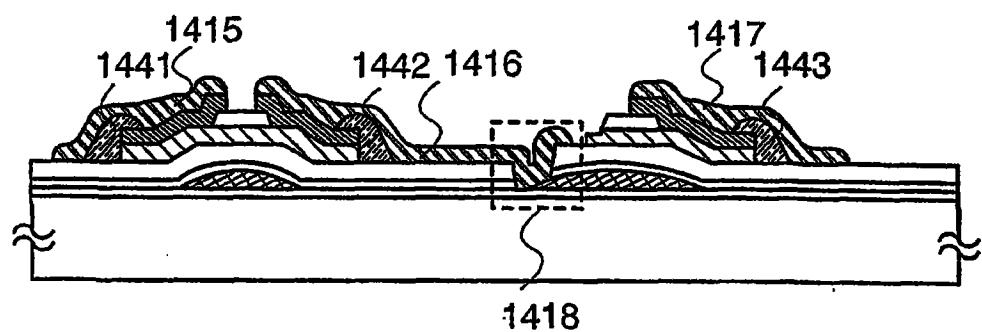

[0368] 参照图 22A ~ 23B 对本发明一实施方式进行描述。本实施方式与实施方式 1 的不同之处在于薄膜晶体管与第一电极不同地连接。因此,略去对相同部分或具有类似功能的部分的描述。

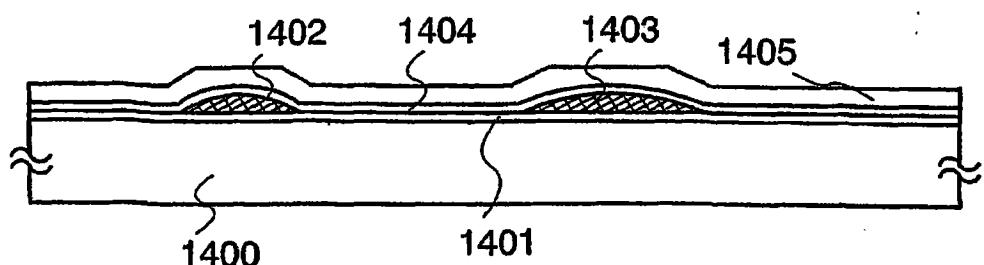

[0369] 用于改进粘性的基底膜 1401 在基板 1400 上形成,作为预先基础处理。在本实施方式中,对通过溅射法形成具有预定晶体结构的 Ti0x 作为光催化物质的情形进行描述。通过将金属钛管用作靶并使用氩气和氧气来进行溅射。此外,也可引入氦气。大气含有大量氧气且成型压力被设置为较高,以形成具有高度光催化活性的 Ti0x。此外,Ti0x 较佳地在加热沉积腔室或其上形成待处理对象的基板时形成。

[0370] 以此方式形成的 Ti0x 即使在相当薄的薄膜形式中也具有光催化功能。

[0371] 此外,较佳的是通过溅射法或气相沉积法等形成由诸如 Ti(钛)、W(钨)、Cr(铬)、Ta(钽)、Ni(镍) 或 Mo(钼) 等金属材料或其氧化物形成的基底膜 1401,作为另一预先基本处理。基底膜 1401 可被形成为 0.01 ~ 10nm 厚。只要它形成得相当薄,就不必具有层结构。在将高熔点金属材料用作基底膜的情形中,较佳的是在将导电层 1402 和 1403 形成为栅电极层之后通过执行以下两个步骤之一来处理露在该表面上的基底膜。

[0372] 第一种方法是绝缘不与导电层 1402 和 1403 重叠的基底膜 1401 以形成绝缘层的步骤。换言之,氧化并绝缘不与导电层 1402 和 1403 重叠的基底膜 1401。当基底膜 1401 用此方法氧化和绝缘时,较佳的是将基底膜 1401 形成为 0.01 ~ 10nm 厚,从而可容易地氧化基底膜。注意,氧化可通过暴露于氧气或通过热处理来进行。

[0373] 第二种方法是将导电层 1402 和 1403 用作掩模来通过蚀刻去除基底膜 1401 的步骤。当采用该步骤时,对基底膜 1401 的厚度没有限制。

[0374] 可选择地,用于对成型区(成型表面)进行等离子体处理的方法可被用作另一预先基础处理。等离子体处理将空气、氧气或氮气用作处理气体来进行,且压力从数十到数千托(133000 帕),较佳地从 100 托(13300 帕)到 1000 托(133000 帕),更佳地从 700 托(93100 帕)到 800 托(106400 帕),即大气压或接近大气压的压力,并在这样的条件下施加脉冲电压。此时,等离子体密度被设为  $1 \times 10^{10}$  到  $1 \times 10^{14} \text{ m}^{-3}$ ,由此实现所谓的电晕放电或辉光放电。通过采用将空气、氧气或氮气用作处理气体的等离子体处理,可与材料无关地进行表面改性。因此,可对任何材料进行表面改性。

[0375] 作为另一种方法,可形成用作粘合剂的有机材料物质以改进要通过微滴排放法形成的图案与其成型区之间的粘性。可使用有机材料(有机树脂材料)(聚酰亚胺或丙烯酸),或其中骨架结构由硅(Si)和氧(O)的键构成,且至少含有氢作为取代基或含有氟基、烷基以及芳香烃中的至少一种作为取代基的材料。

[0376] 随后,排放含有导电材料的混合物,并且形成后来用作栅电极的导电层 1402 和 1403。这些导电层 1402 和 1403 通过微滴排放法来形成。在本实施方式中,银被用作一种导电材料,但也可使用银、铜等的叠层。可选择地,也可使用单层铜。

[0377] 此外,进行形成基底膜 1401 的前述步骤作为对要通过使用微滴排放法形成的导

电层的预先基础处理,然而,该处理步骤可在形成该导电层之后执行。

[0378] 随后,在导电层 1402 和 1403 上形成栅绝缘膜(参见图 22A)。该栅绝缘膜可由诸如硅的氧化物或氮化物材料等公知材料形成,并且可以是叠层或单层。

[0379] 半导体层可通过一公知方法(溅射法、LPCVD 法、等离子体 CVD 法等)形成。对半导体层的材料没有特定限制,但半导体层较佳地由硅、锗硅(SiGe)合金等形成。

[0380] 半导体层将非晶半导体(通常为氢化非晶硅)、半非晶半导体、其半导体层部分地具有晶相的半导体、结晶半导体(通常为多晶硅)或有机半导体用作材料。

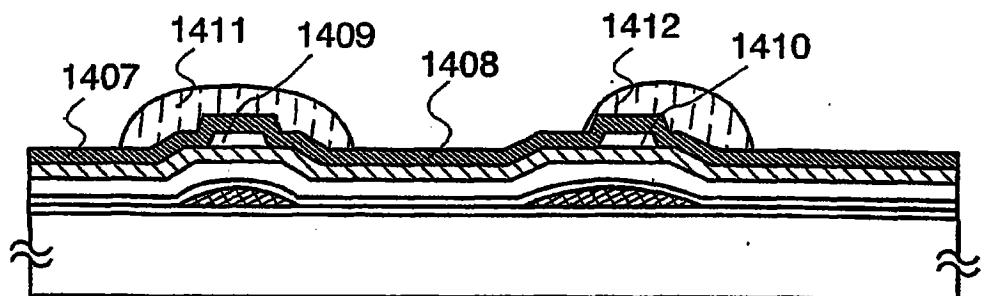

[0381] 在本实施方式中,非晶半导体被用作半导体。形成半导体层 1407,并且绝缘膜通过例如等离子体 CVD 法形成并选择性地蚀刻在期望区域具有期望形状,以便于形成沟道保护膜 1409 和 1410。此外,沟道保护膜可通过微滴排放法或印刷法(可形成图案的方法,诸如丝网印刷或胶印)使用聚酰亚胺、聚乙烯醇等形成。然后,具有一种导电性的半导体层(例如 N 型非晶半导体层 1408)通过等离子体 CVD 法等形成。具有一种导电性的半导体层可按需形成。

[0382] 随后,形成由诸如抗蚀剂或聚酰亚胺等绝缘体形成的掩模层 1411 和 1412。然后,半导体层 1407 和 N 型半导体层 1408 通过使用掩模层 1411 和 1412 来同时图案化。

[0383] 然后,由诸如抗蚀剂或聚酰亚胺等绝缘体形成的掩模层 1413 和 1414 通过微滴排放法来形成(参见图 22C)。通过使用掩模 1413 和 1414,通过蚀刻工艺在栅绝缘层 1404 和 1405 的一部分中形成通孔 1418,并暴露置于其下层一侧并用作栅电极层的导电层的一部分。等离子体蚀刻(干法蚀刻)或湿法蚀刻可被用作蚀刻工艺。此外,当应用大气压放电蚀刻工艺时可执行局部放电过程,并且掩模层无需完全在基板上形成。

[0384] 在去除掩模层 1413 和 1414 之后,导电层 1415、1416 和 1417 通过排放含有导电材料的混合物来形成。然后,N 型半导体层将导电层 1415、1416 和 1417 用作掩模来图案化(参见图 22D)。注意,在形成导电层 1415、1416 和 1417 之前,可在导电层 1415、1416 和 1417 要与栅绝缘层 1405 接触的部分中进行选择性地形成光催化物质等的前述预先基础处理(尽管未示出)。因此,导电层可被形成为对层叠的上下层具有令人满意的粘性。

[0385] 此外,形成作为布线层的导电层 1415、1416 和 1417 以覆盖 N 型半导体层和如图 22D 所示的半导体层。该半导体层被蚀刻。因此,布线层可能不能覆盖陡峭阶梯并且会断开。因此,形成绝缘层 1441、1442 和 1443 以减少阶梯,并且该阶梯被修平。在采用微滴排放法时,绝缘层 1441、1442 和 1443 可在无掩模等的情况下选择性地形成。该阶梯可被绝缘层 1441、1442 和 1443 修平,且覆盖这些绝缘层的布线层可被形成为具有令人满意的覆盖率而无诸如断裂等缺陷。绝缘层 1441、1442 和 1443 可由诸如氧化硅、氮化硅、氧氮化硅、氧化铝、氮化铝、或氧氮化铝、丙烯酸、甲基丙烯酸、丙烯酸和甲基丙烯酸的衍生物等无机绝缘材料;诸如诸如聚酰亚胺、芳族聚酰胺或聚苯并咪唑等耐热高分子量材料;或包括含有硅、氧和氢的化合物中的 Si-O-Si 键,并通过将基于硅氧烷的材料用作起始材料而形成的无机硅氧烷,或其中与硅键合的氢被诸如甲基或苯基等有机基取代的基于有机硅氧烷的绝缘材料来形成。

[0386] 随后,导电层(也称为第一电极)1406 通过在要与用作源极布线层或漏极布线层的导电层 1417 相接触的栅绝缘膜上选择性地排放含有导电材料的混合物来形成(参见图 23A)。在从基板 1400 一侧发光时或在制造透光 EL 显示面板时,导电层 1406 可通过形成包

含氧化铟锡 (ITO)、含有氧化硅的氧化铟锡 (ITSO)、氧化锌 (ZnO)、氧化锡 (SnO<sub>2</sub>) 等的混合物的预定图案、并烘干它来形成。尽管未示出,但诸如形成光催化物质等预先基础处理可类似于形成导电层 1402 和 1403 的情形在要形成导电层 1406 的区域中进行。该预先基础处理可改进粘性,并且导电层 1406 可被形成为成一细线的期望图案。该导电层 1406 变成用作像素电极的第一电极。

[0387] 此外,作为源极布线层或漏极布线层的导电层 1416、以及作为栅电极层的导电层 1403 在栅绝缘层 1405 中形成的通孔 1418 中彼此电连接。含有诸如 Ag(银)、Au(金)、Cu(铜)、W(钨) 或 Al(铝) 等金属粒子作为其主要成分的混合物可被用作形成布线层的导电材料。此外,透光氧化铟锡 (ITO)、含有氧化硅的氧化铟锡 (ITSO)、有机铟、有机锡、氧化锌、氮化钛等可组合使用。

[0388] 在形成导电层 1415、1416、1417 和 1406 之后,可将导电层 1415、1416、1417 和 1406 用作掩模来形成通孔 1418。然后,导电层在通孔 1418 中形成,且导电层 1416 和作为栅电极层的导电层 1403 彼此电连接。

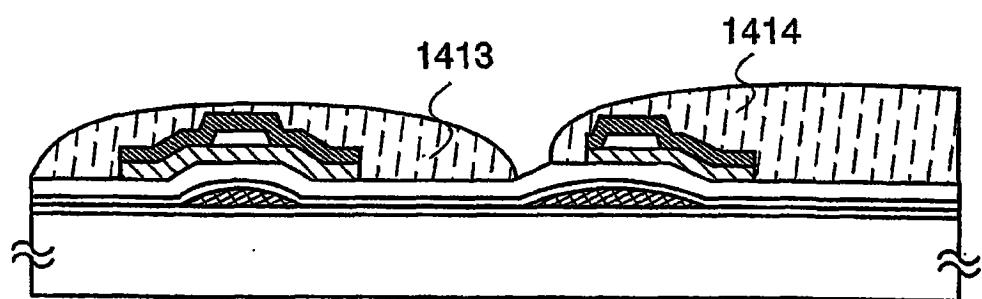

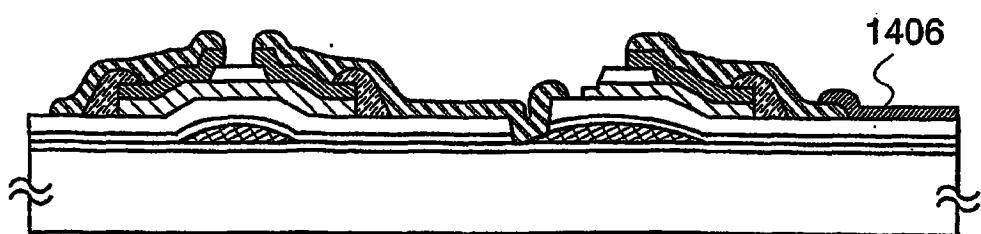

[0389] 随后,形成要成为分隔壁的绝缘层 1420。尽管未示出,由氮化硅或氮氧化硅形成的保护层可完全在绝缘层 1420 下形成,以覆盖薄膜晶体管。在绝缘层通过旋涂法或浸渍法完全形成之后,如图 23B 所示通过蚀刻工艺在绝缘层 1420 中形成一开口。当绝缘层 1420 通过微滴排放法形成时不必进行蚀刻过程。当诸如绝缘层 1420 等较宽区域通过微滴排放法形成时,它通过从微滴排放设备的喷嘴的多个排放口中 排放混合物、并通过绘制以使多条线彼此重叠形成,来改进生产量。

[0390] 绝缘层 1420 被形成为具有与其中像素要根据作为第一电极的导电层 1406 形成的位置相对应的通孔。

[0391] 根据上述步骤完成 TFT 基板,其中底栅型(也称为逆向交错型)沟道保护 TFT 和导电层(第一电极层)1406 在基板 1400 上连接。

[0392] 通过在作为第一电极的导电层 1406 上层叠场致发光层 1421 和导电层 1422,完成了使用发光元件的、具有显示功能的显示装置(参见图 23B)。

[0393] 如上所述,通过不应用使用光掩模的曝光步骤,在本实施方式中可略去该步骤。此外,即使在使用一边超过 1000 毫米的第五代或以后的玻璃基板时,EL 显示面板也可通过微滴排放法在基板上直接形成各种图案来容易地制造。

[0394] 此外,可制造粘性和抗剥离性得到改进的高度可靠的显示装置。

[0395] [实施方式 9]

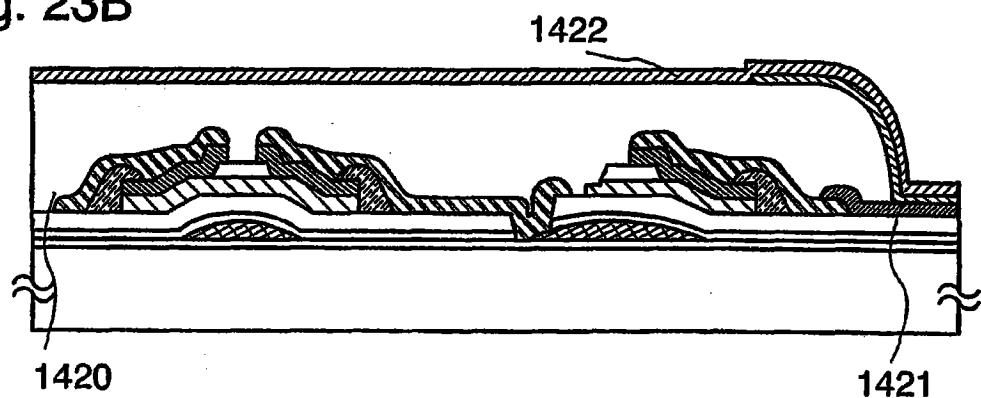

[0396] 参照图 24A ~ 25B 对本发明一实施方式进行描述。本实施方式与实施方式 6 的不同之处在于薄膜晶体管与第一电极不同地连接。因此,略去对相同部分或具有类似功能的部分的描述。

[0397] 用于改进粘性的基底膜 1501 在基板 1500 上形成,作为预先基础处理。在本实施方式中,对通过溅射法形成具有预定晶体结构的 TiO<sub>x</sub> 作为光催化物质的情形进行描述。通过将金属钛管用作靶并使用氩气和氧气来进行溅射。此外,也可引入氦气。为了形成具有高度光催化活性的 TiO<sub>x</sub>,使用含有大量氧气的大气以及相当高的压力。此外, TiO<sub>x</sub> 较佳地在加热沉积腔室或其上形成待处理对象的基板时形成。

[0398] 以此方式形成的 TiO<sub>x</sub> 即使在相当薄的薄膜形式中也具有光催化功能。

[0399] 较佳的是使用诸如 Ti(钛)、W(钨)、Cr(铬)、Ta(钽)、Ni(镍) 和 Mo(钼) 等金属材料或其氧化物来形成基底膜 1501。基底膜 1501 可被形成 0.01 ~ 10nm 厚, 并且只要它形成得相当薄, 就不必具有层结构。在将高熔点材料用作基底膜的情形中, 较佳的是在将导电层 1502 和 1503 形成为栅电极层之后通过执行以下两个步骤之一来处理露在该表面上的基底膜。

[0400] 第一种方法是绝缘不与导电层 1502 和 1503 重叠的基底膜 1501 并形成绝缘层的步骤。换言之, 氧化并绝缘不与导电层 1502 和 1503 重叠的基底膜 1501。当基底膜 1501 用此方法氧化和绝缘时, 较佳的是将基底膜 1501 形成为 0.01 ~ 10nm 厚, 从而可容易地氧化基底膜。注意, 氧化可通过暴露于氧气气或通过热处理来进行。

[0401] 第二种方法是将导电层 1502 和 1503 用作掩模来通过蚀刻去除基底膜 1501 的步骤。当采用该步骤时, 对基底膜 1501 的厚度没有限制。

[0402] 可选择地, 用于对成型区(成型表面)进行等离子体处理的方法可被用作另一预先基础处理。等离子体处理将空气、氧气或氮气用作处理气体来进行, 且压力从数十到数千托(133000 帕), 较佳地从 100 托(13300 帕)到 1000 托(133000 帕), 更佳地从 700 托(93100 帕)到 800 托(106400 帕), 即大气压或接近大气压的压力, 并在这样的条件下施加脉冲电压。此时, 等离子体密度被设为  $1 \times 10^{10}$  到  $1 \times 10^{14} \text{ m}^{-3}$ , 由此实现所谓的电晕放电或辉光放电。通过采用将空气、氧气或氮气用作处理气体的等离子体处理, 可与材料无关地进行表面改性。因此, 可对任何材料进行表面改性。

[0403] 作为另一种方法, 可形成用作粘合剂的基于有机材料的物质以改进要通过微滴排放法形成的图案与其成型区之间的粘性。有机材料(有机树脂材料)(聚酰亚胺或丙烯酸)由硅(Si)和氧(O)的键形成的骨架构成, 其中至少含有氢的有机基(诸如烷基或芳香烃)被包括作为取代基。或者, 氟基可被用作取代基。再或者, 氟基或至少含有氢的有机基可被用作取代基。

[0404] 随后, 排放含有导电材料的混合物, 并且形成后来用作栅电极的导电层 1502 和 1503。这些导电层 1502 和 1503 通过微滴排放法来形成。在本实施方式中, 银被用作一种导电材料, 但也可使用银、铜等的叠层, 也可使用单层铜。

[0405] 执行形成基底膜 1501 的上述步骤作为对要通过使用微滴排放法形成的导电层的预先基础处理, 然而, 该处理步骤可在形成导电层 1502 之后执行。

[0406] 随后, 在导电层 1502 和 1503 上形成栅绝缘膜(参见图 24A)。该栅绝缘膜可由诸如硅的氧化物或氮化物材料等公知材料形成, 并且可以是叠层或单层。

[0407] 半导体层可通过一公知方法(溅射法、LPCVD 法、等离子体 CVD 法等)形成。对半导体层的材料没有特定限制, 但半导体层较佳地由硅、锗硅(SiGe)合金等形成。

[0408] 半导体层将非晶半导体(通常为氢化非晶硅)、半非晶半导体、其半导体层部分地具有晶相的半导体、结晶半导体(通常为多晶硅)或有机半导体用作材料。

[0409] 在本实施方式中, 非晶半导体被用作半导体。形成导电层 1507, 然后具有一种导电性的半导体层(例如 N 型非晶半导体层 1508)通过等离子体 CVD 法等形成。具有一种导电性的半导体层可按需形成。

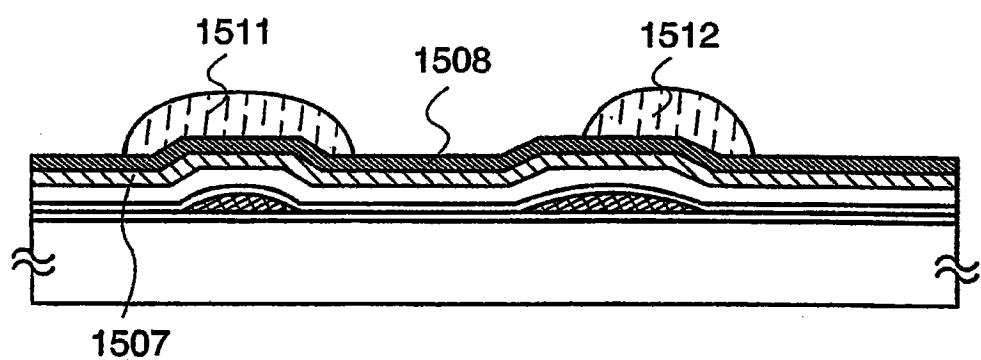

[0410] 随后, 形成由诸如抗蚀剂或聚酰亚胺等绝缘体形成的掩模层 1511 和 1512。然后, 半导体层 1507 和 N 型半导体层 1508 通过使用掩模层 1511 和 1512 来同时图案化(参见图

24B)。

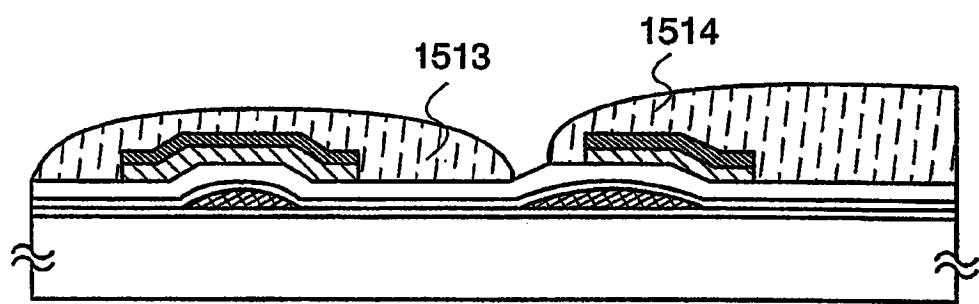

[0411] 然后,由诸如抗蚀剂或聚酰亚胺等绝缘体形成的掩模层 1513 和 1515 通过使用微滴排放法来形成(参见图 24C)。使用掩模 1513 和 1515,通过蚀刻工艺在栅绝缘层 1504 和 1505 的一部分中形成通孔 1518,并暴露置于其下层一侧并用作栅电极层的导电层 1503 的一部分。等离子体蚀刻(干法蚀刻)或湿法蚀刻可被用作蚀刻工艺。此外,当应用大气压放电蚀刻工艺时可执行局部放电过程,并且掩模层无需完全在基板上形成。

[0412] 在去除掩模层 1513 和 1514 之后,导电层 1515、1516 和 1517 通过排放含有导电材料的混合物来形成。然后,N型半导体层将导电层 1515、1516 和 1517 用作掩模来图案化,以形成 N型半导体层(参见图 24D)。注意,在形成导电层 1515、1516 和 1517 之前,可在导电层 1515、1516 和 1517 要与栅绝缘层 1505 接触的部分中进行选择性地形成光催化物质等的前述预先基础处理(尽管未示出)。因此,导电层可形被成为对层叠的上下层具有令人满意的粘性的粘性。

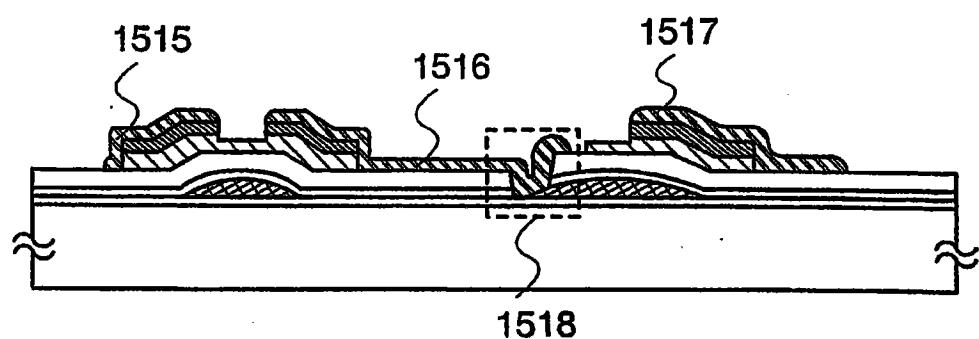

[0413] 随后,导电层(也称为第一电极)1506 通过在要与用作源极布线层或漏极布线层的导电层 1517 相接触的栅绝缘膜上选择性地排放含有导电材料的混合物来形成(参见图 25A)。在从基板 1500 一侧发光时或在制造透光 EL 显示面板时,导电层 1506 可通过形成包含氧化铟锡(ITO)、含有氧化硅的氧化铟锡(ITSO)、氧化锌(ZnO)、氧化锡(SnO<sub>2</sub>)等的混合物的预定图案、并烘干它来形成。尽管未示出,但诸如形成光催化物质等预先基础处理可类似于形成导电层 1502 和 1503 的情形在要形成导电层 1506 的区域中进行。该预先基础处理可改进粘性,并且导电层 1506 可被形成为成一细线的期望图案。该导电层 1506 变成用作像素电极的第一电极。

[0414] 此外,作为源极布线层或漏极布线层的导电层 1516、以及作为栅电极层的导电层 1503 在栅绝缘层 1505 中形成的通孔 1518 中彼此电连接。含有诸如 Ag(银)、Au(金)、Cu(铜)、W(钨)或 Al(铝)等金属粒子作为其主要成分的混合物可被用作形成布线层的导电材料。此外,透光氧化铟锡(ITO)、含有氧化硅的氧化铟锡(ITSO)、有机铟、有机锡、氧化锌、氮化钛等可组合使用。

[0415] 在形成导电层 1515、1516、1517 和 1506 之后,可执行将导电层 1515、1516、1517 和 1506 用作掩模来形成通孔 1518 的步骤。然后,在通孔 1518 中形成导电层,且导电层 1516 和作为栅电极层的导电层 1503 彼此电连接。

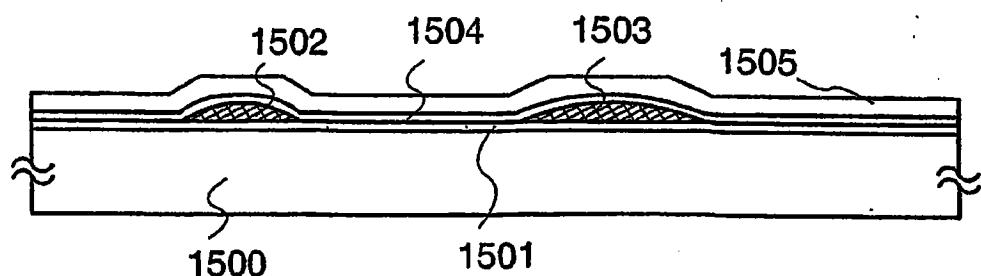

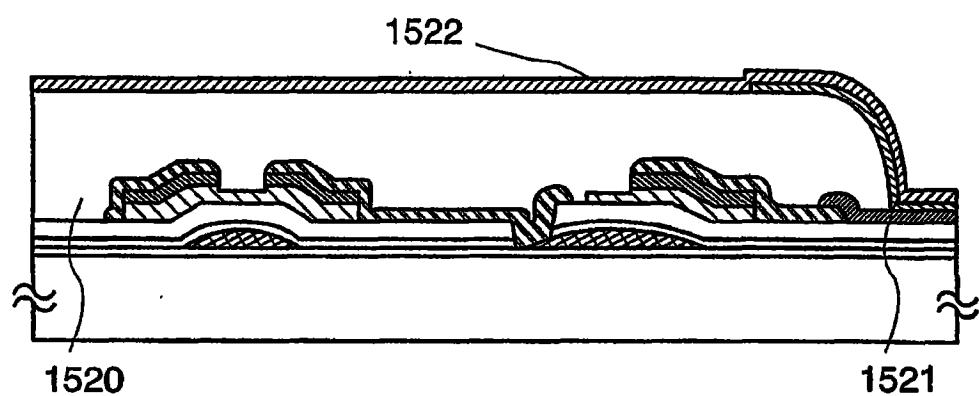

[0416] 随后,形成要成为分隔壁的绝缘层 1520。尽管未示出,但由氮化硅或氮氧化硅形成的保护层可完全在绝缘层 1520 下形成,以覆盖薄膜晶体管。在绝缘层 1520 通过旋涂法或浸渍法完全形成之后,如图 25B 所示通过蚀刻工艺在该绝缘层中形成一开口。当绝缘层 1520 通过微滴排放法形成时不必进行蚀刻过程。当诸如绝缘层 1520 等较宽区域通过微滴排放法形成时,它通过从微滴排放设备的喷嘴的多个排放口中排放混合物、并通过绘制以使多条线彼此重叠形成,来改进生产量。

[0417] 绝缘层 1520 被形成为具有与其中像素要根据作为第一电极的导电层 1506 形成的位置相对应的通孔。

[0418] 根据上述步骤完成 TFT 基板,其中底栅型(也称为逆向交错型)TFT 和导电层(第一电极层)1506 在基板 1500 上连接。

[0419] 通过在作为第一电极的导电层 1506 上层叠场致发光层 1521 和导电层 1522,完成

使用发光元件的、具有显示功能的显示装置(参见图25B)。

[0420] 如上所述,通过不应用使用光掩模的曝光步骤,在本实施方式中可略去该步骤。此外,即使在使用一边超过1000毫米的第五代或以后的玻璃基板时,EL显示面板也可通过微滴排放法在基板上直接形成各种图案来容易地制造。

[0421] 此外,可制造粘性和抗剥离性得到改进的高度可靠的显示装置。

[0422] [实施方式10]

[0423] 参照图26A~27对本发明一实施方式进行描述。本实施方式与实施方式7的不同之处在于薄膜晶体管与第一电极不同地连接。因此,略去对相同部分或具有类似功能的部分的描述。

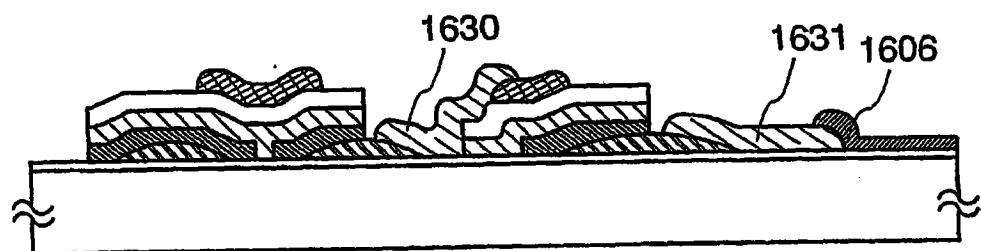

[0424] 具有改进粘性功能的基底膜1601在基板1600上形成(参见图26A)。绝缘层可在基板1600上形成。该绝缘层并非必需设置,但有阻挡来自基板1600的污染物等的效果。在如本实施方式中使用交错薄膜晶体管的情形中,因为半导体层与基板直接接触,所以基底层是有效的。在形成基底层以便防止来自玻璃基板的污染的情形中,基底膜1601通过微滴排放法形成,作为导电层1615、1616和1617的成型区中的预处理。

[0425] 在本实施方式中,具有光催化功能的物质被用作具有改进粘性功能的基底膜1601。

[0426] 在本实施方式中,对通过溅射法形成具有预定晶体结构的Ti0x作为光催化物质的情形进行描述。通过将金属钛管用作靶并使用氩气和氧气来进行溅射。此外,也可引入氦气。为了形成具有高度光催化活性的Ti0x,使用含有大量氧气的大气以及相当高的压力。此外,Ti0x较佳地在加热沉积腔室或其上形成元件的基板时形成。

[0427] 以此方式形成的Ti0x即使在相当薄的薄膜形式中也具有光催化功能。

[0428] 较佳的是使用诸如Ti(钛)、W(钨)、Cr(铬)、Ta(钽)、Ni(镍)和Mo(钼)等金属材料或其氧化物来形成基底膜1601。基底膜1601可被形成为0.01~10nm厚,并且只要它被形成得相当薄,就不必具有层结构。在将高熔点材料用作基底膜的情形中,较佳的是在将导电层1615、1616和1617形成为源极布线层或漏极布线层之后通过执行以下两个步骤之一来处理露在该表面上的基底膜。

[0429] 第一种方法是绝缘不与要成为源极布线层或漏极布线层的导电层1615、1616和1617重叠的基底膜1601并形成绝缘层的步骤。换言之,氧化并绝缘不与要成为源极布线层或漏极布线层的导电层1615、1616和1617重叠的基底膜1601。当基底膜1601用此方法氧化和绝缘时,较佳的是将基底膜1601形成为0.01~10nm厚,从而可容易地氧化基底膜。注意,氧化可通过暴露于氧气或通过热处理来进行。

[0430] 第二种方法是将要成为源极布线层或漏极布线层的导电层1615、1616和1617用作掩模来通过蚀刻去除基底膜1601的步骤。当采用该步骤时,对基底膜1601的厚度没有限制。

[0431] 可选择地,用于对成型区(成型表面)进行等离子体处理的方法可被用作另一预先基础处理。等离子体处理将空气、氧气或氮气用作处理气体来进行,且压力从数十到数千托(133000帕),较佳地从100托(13300帕)到1000托(133000帕),更佳地从700托(93100帕)到800托(106400帕),即大气压或接近大气压的压力,并在这样的条件下施加脉冲电压。此时,等离子体密度被设为 $1\times10^{10}$ 到 $1\times10^{14}\text{m}^{-3}$ ,由此实现所谓的电晕放电或辉

光放电。通过采用将空气、氧气或氮气用作处理气体的等离子体处理,可与材料无关地进行表面改性。因此,可对任何材料进行表面改性。

[0432] 作为另一种方法,可形成用作粘合剂的有机材料物质以改进要通过微滴排放法形成的图案与其成型区之间的粘性。可使用有机材料(有机树脂材料)(聚酰亚胺或丙烯酸),或其中骨架结构通过硅(Si)和氧(O)的键构成、且其中至少含有氢作为取代基、或者含有氟基、烷基和芳香烃的至少之一作为取代基的材料。

[0433] 随后,排放含有导电材料的混合物,并且形成要成为源极布线层或漏极布线层的导电层1615、1616和1617。这些导电层1615、1616和1617通过微滴排放法来形成。

[0434] 作为用于形成导电层1615、1616和1617的导电材料,可使用含有诸如Ag(银)、Au(金)、Cu(铜)、W(钨)和Al(铝)等金属粒子作为其主要成分的混合物。具体地,较佳的是考虑到电阻率,通过使用溶解或分散在溶剂中的金、银和铜的任一材料形成电阻率较佳地较低的源极布线层或漏极布线层。更佳的是使用具有低电阻的银或铜。此外,可使用具有通过用另一导电材料涂敷导电材料的周边而形成的多层的粒子。例如,可使用具有其中用硼化镍(NiB)涂覆铜、然后在其上涂银等的三层结构的粒子。对于这样的溶剂,可使用诸如乙酸丁酯等酯、诸如异丙醇等醇、诸如丙酮等有机溶剂等。表面张力和粘性通过控制溶液的浓度并添加表面活性剂来适当地控制。

[0435] 上述形成基底膜1601的步骤作为对通过微滴排放法形成的导电层的预先基础处理来进行,然而该处理可在形成导电层1615、1616和1617之后进行。例如,通过在其上形成氧化钛膜和N型半导体层(尽管未示出),导电层与N型半导体层之间的粘性得到改进。

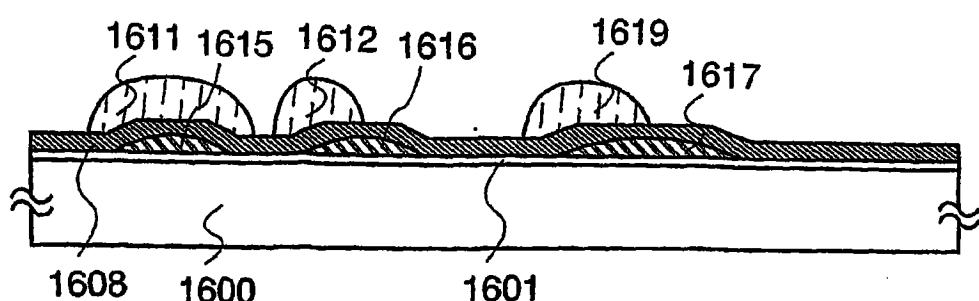

[0436] 在导电层1615、1616和1617的整个表面上形成N型半导体层之后,设置在导电层1615与1616之间以及导电层1616和1617之间的N型半导体层使用由诸如抗蚀剂和聚酰亚胺等绝缘体形成的掩模层1611、1612和1619通过蚀刻来去除。可按需形成具有一种导电性的半导体层。然后,由AS或SAS形成的半导体层1607通过气相法或溅射法形成。在采用等离子体CVD法的情形中,AS通过将SiH<sub>4</sub>用作半导体材料气体或SiH<sub>4</sub>和H<sub>2</sub>的混合气体来形成。SAS由用H<sub>2</sub>稀释SiH<sub>4</sub>3-1000倍的混合气体形成。当SAS由以上类型的气体形成时,半导体层在其一表面侧具有令人满意的结晶度。SAS适用于其中栅电极在半导体层的上层形成的顶栅型TFT。

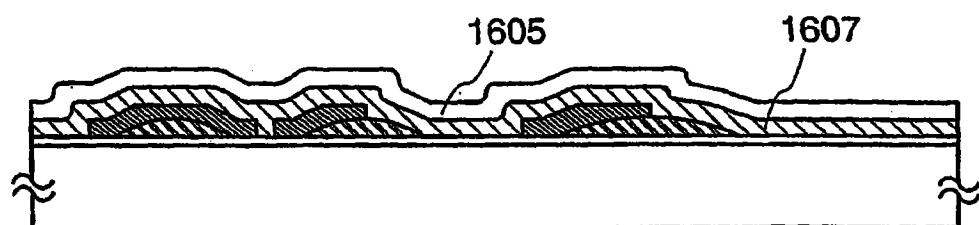

[0437] 随后,栅绝缘层1605通过等离子体CVD法或溅射法形成为具有单层或叠层结构(参见图26B)。由氮化硅形成的绝缘层、由氧化硅形成的绝缘层、以及由氮化硅形成的绝缘层的三层叠层是一较佳结构。

[0438] 然后,作为栅电极层的导电层1602和1603通过微滴排放法形成(参见图26C)。含有诸如Ag(银)、Au(金)、Cu(铜)、W(钨)或Al(铝)等金属粒子作为其主要成分的混合物可用作形成栅电极层1602和1603的导电材料。

[0439] 半导体层1607和栅绝缘层1605使用通过微滴排放法形成的掩模层1616和1614在与源极布线层和漏极布线层(导电层1615、1616和1617)相对应的位置中形成。换言之,半导体层和栅绝缘层被形成为跨接在导电层1615和1616上。

[0440] 随后,导电层1630和1631通过微滴排放法形成,并与导电层1616和导电层1603电连接。

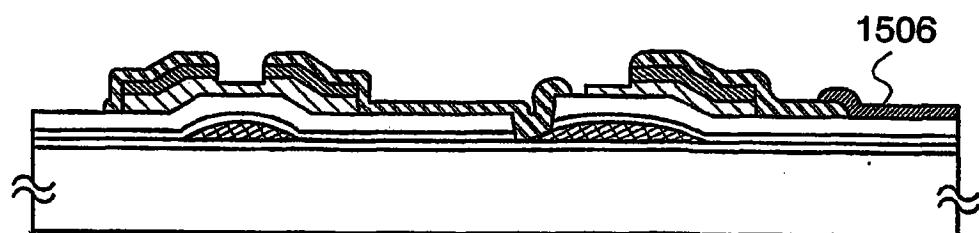

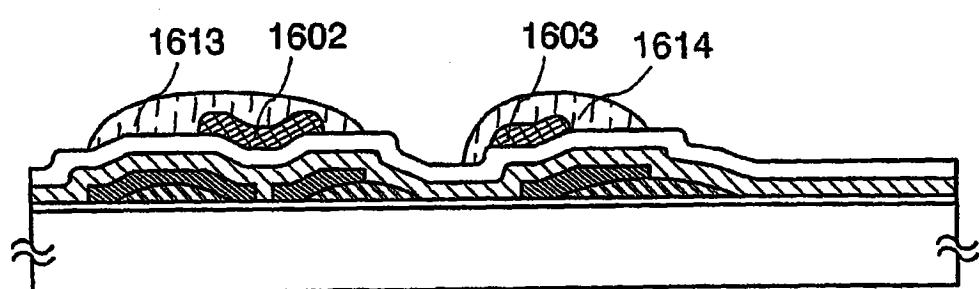

[0441] 随后,导电层(也称为第一电极)1606通过选择性地排放含有导电材料的混合物

来形成,以与导电层 1631 相接触。可选择地,导电层 1606 可具有与导电层 1617 直接接触的结构。在从基板 1600 一侧发光时或在制造透光 EL 显示面板时,导电层 1606 可通过形成包含氧化铟锡 (ITO)、含有氧化硅的氧化铟锡 (ITSO)、氧化锌 (ZnO)、氧化锡 (SnO<sub>2</sub>) 等的混合物的预定图案、并烘干它来形成。尽管未示出,但诸如形成光催化物质等预先基础处理可类似于形成导电层 1615、1616 和 1617 的情形在要形成导电层 1606 的区域中进行。使用光催化物质可改进粘性,并且导电层 1606 可被形成为成一细线的期望图案。该导电层 1606 变成用作像素电极的第一电极。

[0442] 源极布线层或漏极布线层以及栅电极层可在不使用导电层 1630 的情况下直接通过栅电极层相连。在该情形中,在栅极绝缘层 1605 中形成通孔,且作为源极布线或漏极布线的导电层 1616 和 1617 的一部分在形成导电栅电极层 1602 和 1603 之前曝光。然后,导电栅电极层 1602、1603 和导电层 1631 通过微滴排放法形成。此时,导电层 1603 是也用作导电层 1630 的布线,并连接到导电层 1616。干法蚀刻或湿法蚀刻都可用于蚀刻,然而作为干法蚀刻的等离子体蚀刻是更佳的。

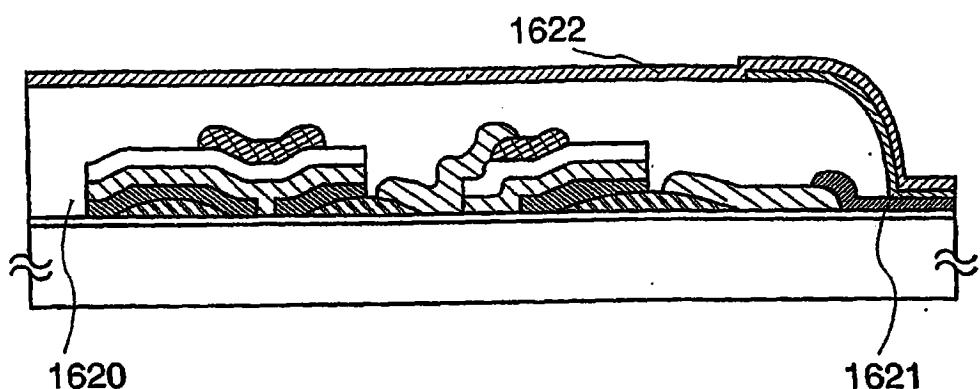

[0443] 随后,形成要成为分隔壁的绝缘层 1620。尽管未示出,由氮化硅或氮氧化硅形成的保护层可完全在绝缘层 1620 之下形成以覆盖薄膜晶体管。在绝缘层 1620 通过旋涂法或浸渍法全部形成之后,如图 27 所示通过蚀刻工艺在该绝缘层中形成一开口。当绝缘层 1620 通过微滴排放法形成时不必执行蚀刻过程。在通过微滴排放法形成诸如绝缘层 1620 等宽广区域时,可通过从微滴排放设备的喷嘴的多个排放口中排放混合物、并通过绘制以使多条线彼此重叠来形成,以改进生产量。

[0444] 绝缘层 1620 被形成为具有与其中像素要根据作为第一电极的导电层 1606 形成的位置相对应的通孔。

[0445] 根据上述步骤完成 TFT 基板,其中顶栅型(也称为交错型)TFT 和导电层 1606 在基板 1600 上连接。

[0446] 在形成场致发光层 1621 之前,绝缘层 1620 内或其表面所吸收的湿气通过在 200℃ 在大气压下进行热处理来去除。此外,在降低压力下在 200 ~ 400℃(较佳地 250 ~ 350℃)的温度下进行热处理,且场致发光层 1621 较佳地通过真空气相沉积法或微滴排放法在不暴露于大气的情况下在降低压力下形成。

[0447] 通过将场致发光层 1621 和导电层 1622 层叠在作为第一电极的导电层 1606 上,完成使用发光元件的具有显示功能的显示装置(参见图 27)。

[0448] 如上所述,通过不应用使用光掩模的曝光步骤,在本实施方式中可略去该步骤。此外,即使在使用一边超过 1000 毫米的第五代或以后的玻璃基板时,EL 显示面板也可通过微滴排放法在基板上直接形成各种图案来容易地制造。

[0449] 此外,可制造粘性和抗剥离性得到改进的高度可靠的显示装置。

[0450] [实施方式 11]

[0451] 参照图 28A ~ 29B 对本发明一实施方式进行描述。本实施方式与实施方式 1 的不同之处在于作为穿过栅电极层 805 的布线层的导电层 816 与作为栅电极层的导电层 803 不同地连接。因此,略去对相同部分或具有类似功能的部分的描述。

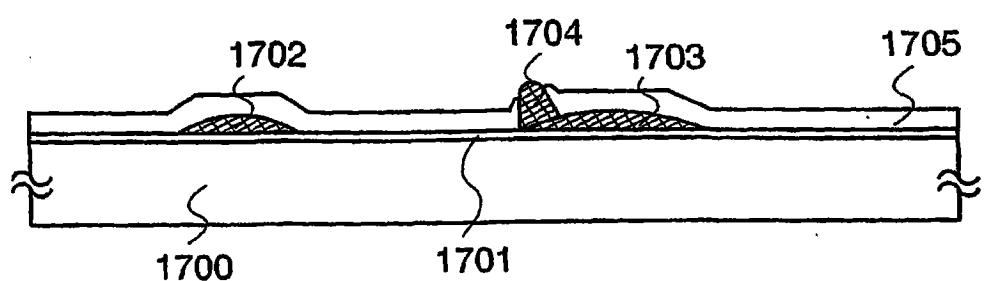

[0452] 改进粘性的基底膜 1701 在基板 1700 上形成(参见图 28A)。注意,绝缘层可在基板 1700 上形成。

[0453] 在本实施方式中,具有光催化功能的物质被用作具有改进粘性功能的基底膜 1701。

[0454] 在本实施方式中,对通过溅射法形成具有预定晶体结构的 Ti0x 作为光催化物质的情形进行描述。通过将金属钛管用作靶并使用氩气和氧气来进行溅射。此外,也可引入氦气。大气含有大量氧气,且成型压力被设置成较高,以形成具有高度光催化活性的 Ti0x。此外, Ti0x 较佳地在加热沉积腔室或其上形成待处理对象的基板时形成。

[0455] 以此方式形成的 Ti0x 即使在相当薄的薄膜形式中也具有光催化功能。

[0456] 较佳的是通过溅射法、气相沉积法等使用诸如 Ti(钛)、W(钨)、Cr(铬)、Ta(钽)、Ni(镍) 和 Mo(钼) 等金属材料或其氧化物来形成基底膜 1701,作为预先基本处理。该基底膜可被形成为 0.01 ~ 10nm 厚,并且只要它形成得相当薄,就不必具有层结构。在将高熔点材料用作基底膜的情形中,较佳的是在将导电层 1702 和 1703 形成为栅电极层之后通过执行以下两个步骤之一来处理露在该表面上的基底膜。

[0457] 第一种方法是绝缘不与导电层 1702 和 1703 重叠的基底膜 1701 并形成绝缘层的步骤。换言之,氧化并绝缘不与导电层 1702 和 1703 重叠的基底膜 1701。当基底膜 1701 用此方法氧化和绝缘时,较佳的是将基底膜 1701 形成为 0.01 ~ 10nm 厚,从而可容易地氧化基底膜。注意,氧化可通过暴露于氧气气或通过热处理来进行。

[0458] 第二种方法是将导电层 1702 和 1703 用作掩模来通过蚀刻去除基底膜 1701 的步骤。当采用该步骤时,对基底膜 1701 的厚度没有限制。

[0459] 可选择地,用于对成型区(成型表面)进行等离子体处理的方法可被用作另一预先基础处理。等离子体处理将空气、氧气或氮气用作处理气体来进行,且压力从数十到数千托(133000 帕),较佳地从 100 托(13300 帕)到 1000 托(133000 帕),更佳地从 700 托(93100 帕)到 800 托(106400 帕),即大气压或接近大气压的压力,并在这样的条件下施加脉冲电压。此时,等离子体密度被设为  $1 \times 10^{10}$  到  $1 \times 10^{14} \text{ m}^{-3}$ ,由此实现所谓的电晕放电或辉光放电。通过采用将空气、氧气或氮气用作处理气体的等离子体处理,可与材料无关地进行表面改性。因此,可对任何材料进行表面改性。

[0460] 作为另一种方法,可形成用作粘合剂的有机材料物质以改进要通过微滴排放法形成的图案与其成型区之间的粘性。可使用有机材料(有机树脂材料)(聚酰亚胺或丙烯酸树脂),或其中骨架结构通过硅(Si)和氧(O)的键构成、且其中至少含有氢作为取代基、或者含有氟基、烷基和芳香烃的至少之一作为取代基的材料。

[0461] 随后,排放含有导电材料的混合物,并且形成要成为源极布线层或漏极布线层的导电层 1702 和 1703。这些导电层 1702 和 1703 通过微滴排放法来形成。

[0462] 用作支柱的导体 1704 通过在形成导电层 1703 之后局部地排放含有导电材料的混合物来形成。导体 1704 通过沉积所排放的混合物来较佳地形成为圆柱形,从而在使用圆柱形导体 1704 时下层中的图案和上层中的图案容易彼此接触。导体 1704 可由与导电层 1703 相同的材料形成,或可由不同材料形成。它可通过排放要层叠的混合物来形成。

[0463] 在形成导电层 1703 之后,可对导电层 1703 执行上述预先基础处理,以再次改进粘性。此外,较佳的是在形成作为支柱的导体 1704 之后类似地执行预先基础处理。当执行诸如形成诸如 Ti0x 等光催化物质的预先基本处理时,各层可具有令人满意的粘合。

[0464] 随后,在导电层 1702 和 1703 上形成栅绝缘膜(参见图 28A)。

[0465] 然后,导电层(也称为第一电极)1706通过在栅绝缘膜上选择性地排放含有导电材料的混合物来形成(参见图28B)。尽管未示出,但光催化物质可类似于形成导电层1702和1703的情形在要形成导电层1706的区域中形成。该光催化物质可改进粘性,并且导电层1706可被形成为成一细线的期望图案。该导电层1706变成用作像素电极的第一电极。

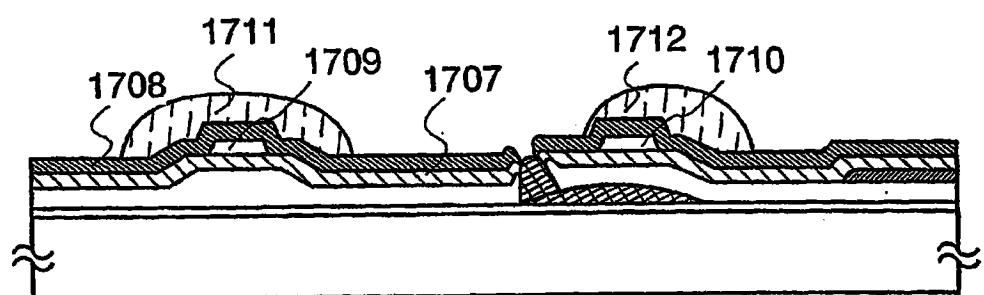

[0466] 在本实施方式中,非晶半导体被用作半导体。形成作为非晶半导体层的导电层1707,并且绝缘膜通过例如等离子体CVD法形成并被选择性地蚀刻成在期望区域具有期望形状,以便于形成沟道保护膜1709和1710。此时,沟道保护膜1709和1710可通过将栅电极用作掩模曝光基板的背面来形成。此外,聚酰亚胺、聚乙烯醇等可通过微滴排放法滴落,作为沟道保护膜。因此,可略去曝光步骤。然后,具有一种导电性的半导体层(例如使用N型非晶半导体层的例如N型非晶半导体层1708)通过等离子体CVD法等形成(参见图28C)。具有一种导电性的半导体层可按需形成。

[0467] 随后,形成由诸如抗蚀剂或聚酰亚胺等绝缘体形成的掩模层1711和1712,并且半导体层1707和N型半导体层1708通过使用掩模层1711和1712来同时图案化。

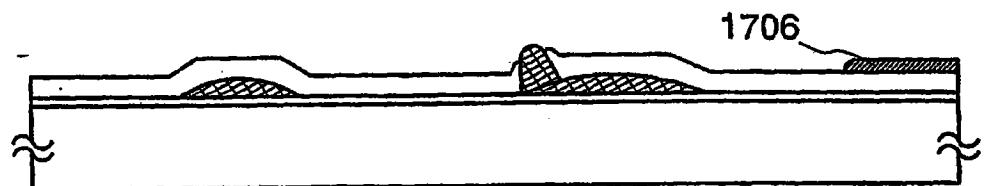

[0468] 在本实施方式中,要通过用作支柱的导体1704连接到作为栅电极层的导电层1703的导体穿过栅电极层1705,并存在于栅绝缘层1705上。因此,可略去在栅绝缘层中开通孔的步骤。

[0469] 导电层1715、1716和1717通过排放含有导电材料的混合物来形成。然后,N型半导体层将导电层1715、1716和1717用作掩模来图案化。注意,在形成导电层1715、1716和1717之前,光催化物质可在导电层1715、1716和1717与栅绝缘层1705接触的部分中选择性地形成,尽管并未示出。因此,导电层可被形成为具有令人满意的粘性。

[0470] 导电层1717用作源极布线层或漏极布线层,并被形成为与预先形成的第一电极电连接。作为源极布线层或漏极布线层的导电层1716可通过导体1704与作为栅电极层的导电层1703电连接(参见图29A)。当绝缘层等残留在用作支柱的导体1704上时,它可通过蚀刻等去除。

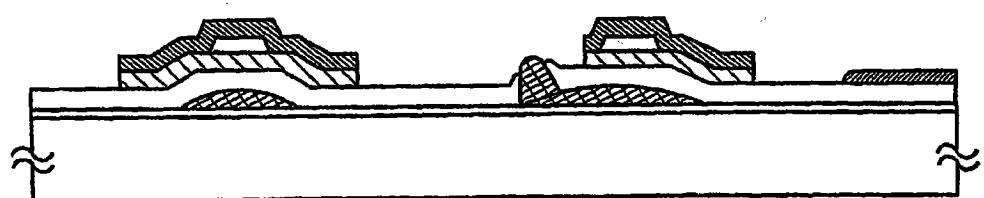

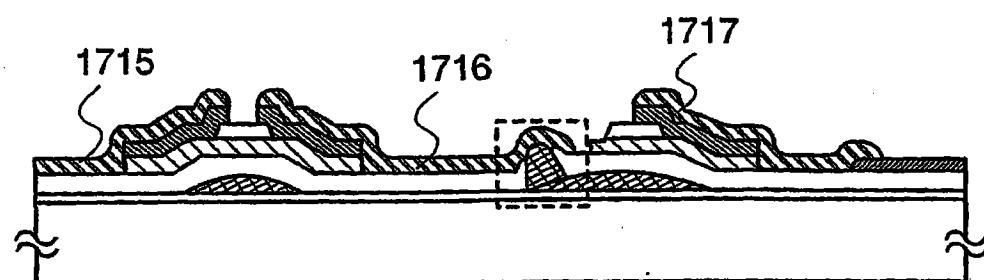

[0471] 随后,形成作为分隔壁的绝缘层1720。

[0472] 绝缘层1720被形成有具有与其中像素要根据作为第一电极的导电层1706形成的位置相对应的通孔。

[0473] 根据上述步骤完成用于EL显示面板的TFT基板,其中底栅型(也称为逆向交错型)沟道保护型TFT和第一电极在基板1700上连接。

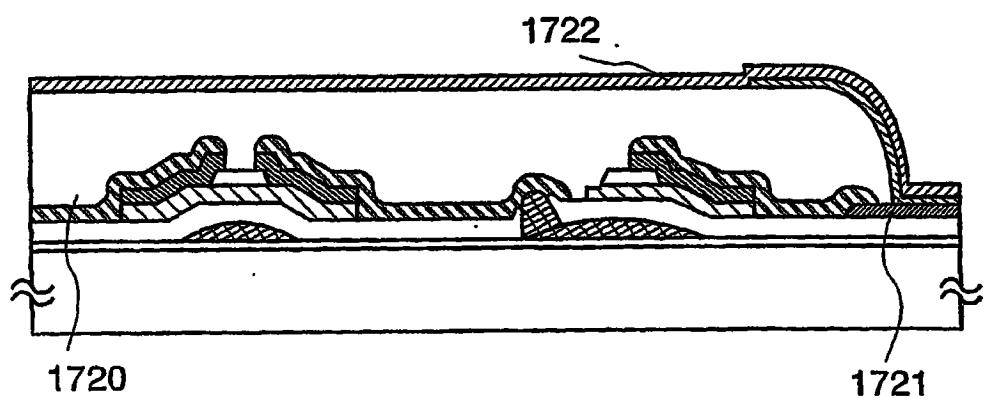

[0474] 场致发光层1721和导电层1722层叠在作为第一电极的导电层1706上,然后完成使用发光元件的、具有显示功能的显示装置(参见图29B)。

[0475] 如上所述,通过不应用使用光掩模的曝光步骤,在本实施方式中可略去该步骤。此外,即使在使用一边超过1000毫米的第五代或以后的玻璃基板时,EL显示面板也可通过微滴排放法在基板上直接形成各种图案来容易地制造。

[0476] 此外,可制造粘性和抗剥离性得到改进的高度可靠的显示装置。在本实施方式中将支柱用于通孔的连接方法可组合以上实施方式自由地实现。

[0477] [实施方式12]

[0478] 薄膜晶体管可通过应用本发明来形成,并且显示装置可通过使用薄膜晶体管来形成。在将发光元件用作显示元件以及将N型晶体管用作驱动发光元件的晶体管的情形

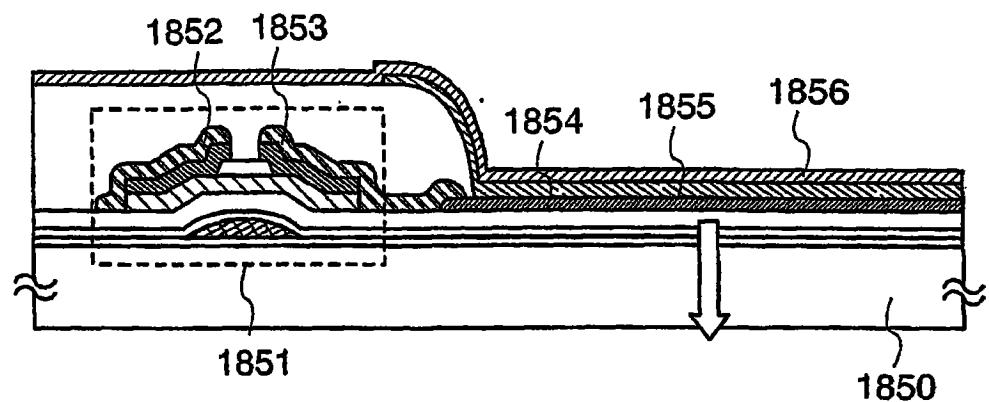

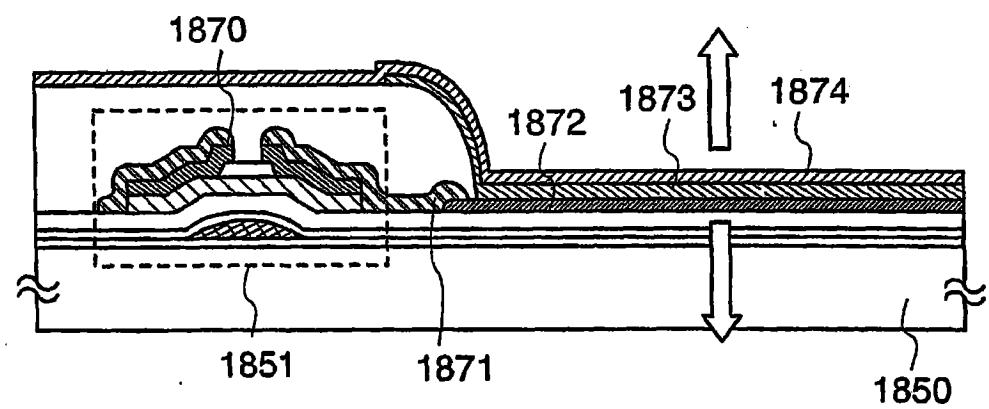

中,从发光元件发出的光是底部发光、顶部发光、以及双端发光中的任一种。在此,参照图 30A ~ 30C 描述任何情形的发光元件的叠层结构。

[0479] 在本实施方式中使用作为通过应用本发明在实施方式 1 中形成的沟道保护薄膜晶体管的晶体管 1851。

[0480] 首先,参照图 30A 描述从基板 1850 一侧发光的情形,即底部发光的情形。在该情形中,源极布线或漏极布线 1852 和 1853、第一电极 1854、场致发光层 1855、以及第二电极 1856 依次层叠以与晶体管 1851 电连接。然后,参照图 30B 描述从基板 1850 的相对一侧发光的情形,即顶部发光的情形。源极布线或漏极布线 1861 和 1862、第一电极 1863、场致发光层 1864、以及第二电极 1865 依次层叠以与晶体管 1851 电连接。即使第一电极 1863 发光,在上述结构中光也由布线 1862 反射并射向基板 1850 的相对一侧。注意,在此结构中不需要对第一电极 1863 使用透光材料。最后,参照图 30C 描述向基板 1850 一侧及其相对一侧发光的情形,即双端发光的情形。源极布线或漏极布线 1870 和 1871、第一电极 1872、场致发光层 1873、以及第二电极 1874 依次层叠以与晶体管 1851 电连接。此时,双端发光在第一电极 1872 和第二电极 1874 都由透光材料形成、或被形成得足够薄以透光时实现。

[0481] 发光元件具有其中场致发光层夹在第一电极和第二电极之间的结构。有必要根据功函来选择第一电极和第二电极的材料。取决于像素结构,第一电极和第二电极两者都可以是阳极或阴极。因为在本实施方式中驱动 TFT 的极性是 N 沟道型,所以第一电极较佳地是阴极,而第二电极较佳地是阳极。当驱动 TFT 的极性是 P 沟道型时,第一电极较佳地是阳极,而第二电极较佳地是阴极。

[0482] 当第一电极是阳极时,场致发光层较佳地通过从阳极侧起依次层叠 HIL(空穴注入层)、HTL(空穴输送层)、EML(发光层)、ETL(电子输送层)、以及 EIL(电子注入层)来形成。当第一电极是阴极时,场致发光层的结构相反。较佳地是从阴极侧起依次层叠 EIL(电子注入层)、ETL(电子输送层)、EML(发光层)、HTL(空穴输送层)、HIL(空穴注入层)、以及作为第二电极的阳极。注意,该场致发光层可具有单层结构或组合结构、以及叠层结构。

[0483] 显示红色(R)、绿色(G) 和蓝色(B) 的发光性的材料可通过气相沉积法使用相应的气相沉积掩模等来选择性地形成场致发光层。显示红色(R)、绿色(G) 和蓝色(B) 的发光性的材料(诸如低分子量材料或高分子量材料) 可通过微滴排放法形成,因为在该情形中无需使用类似于滤色片的掩模就可分开执行 RGB 的着色,所以该微滴排放法是较佳的。

[0484] 具体地, CuPc 或 PEDOT 被用作 HIL,  $\alpha$ -NPD 被用作 HTL, BCP 或  $\text{Alq}_3$  被用作 ETL, BCP:Li 或  $\text{CaF}_2$  被用作 EIL。此外,掺杂有对应于 R、G 和 B 的相应发光色的掺杂物(在 R 的情形中为 DCM 等、在 G 的情形中为 DMQD 等) 的  $\text{Alq}_3$  可被用作例如 EML。

[0485] 注意,场致发光层并不限于以上材料。例如,空穴注入性质可通过共同蒸镀诸如氧化钼( $\text{MoO}_x$ : $x = 2 \sim 3$ ) 和  $\alpha$ -PND 或红荧烯、而不使用 CuPc 或 PEDOT 来增强。有机材料(包括低分子量材料或高分子量材料) 或有机材料和无机材料的合成材料可被用作场致发光层的材料。

[0486] 此外,尽管未在图 30A ~ 30C 中示出,滤色片可在基板 1850 的对置基板上形成。该滤色片可通过微滴排放法形成,在该情形中光等离子体处理可作为前述预先基础处理来进行。由于本发明的基底膜,滤色片可被形成为具有令人满意的粘性的期望图案。高清晰度显示可使用滤色片来进行。这是因为滤色片可在 RGB 的每一放射光谱中将宽峰调节为尖

峰。

[0487] 形成示出每一 RGB 发光性的材料的情形如上所述,然而全色显示也可通过形成示出单色发光性的材料并组合使用该材料和滤色片或色彩转换层来进行。例如,在形成示出白色或橘色发光性的场致发光层的情形中,全色显示可通过单独设置滤色片、色彩转换层、或滤色片和色彩转换层的组合来进行。例如,滤色片或色彩转换层可在第二基板(密封基板)上形成,然后可附连到基板上。如上所述,示出单色发光性的材料、滤色片和色彩转换层都可通过微滴排放法形成。

[0488] 毋庸多言,可进行单色发光的显示。例如,区域色彩型显示装置可通过使用单色发光性来形成。无源矩阵显示部分适用于主要可显示文本和符号的区域色彩型。

[0489] 在上述结构中具有低功函的材料可用作阴极,例如 Ca、Al、CaF、MgAg、AlLi 等是较佳的。场致发光层可以是单层型、叠层型、以及各层之间没有界面的混合层型的任一种。可使用以下材料的任一种:单态材料、三态材料、其组合材料、包括 低分子量材料、高分子量材料和中间分子量材料的有机材料、以电子注入性质优越的氧化钼为代表的无机材料、以及有机材料和无机材料的复合材料。第一电极 1854、1863 和 1872 通过使用透光的透光导电膜,例如其中氧化铟混有 2 ~ 20 重量% 的氧化锌(ZnO)、以及 ITO 或 ITSO 的透光导电膜来形成。注意,在氧气气氛中的等离子体处理或真空气氛中的热处理较佳地在形成第一电极 1854、1863 和 1872 之前进行。分隔壁(也称为堤)通过使用含硅材料、有机材料或复合材料形成。此外,可使用多孔膜。注意,较佳的是通过使用诸如丙烯酸或聚酰亚胺等光敏或非光敏材料来形成分隔壁,因为其侧面变成曲率半径连续变化且上层薄膜不中断地形成的形状。本实施方式可组合以上实施方式自由的实现。

[0490] [实施方式 13]

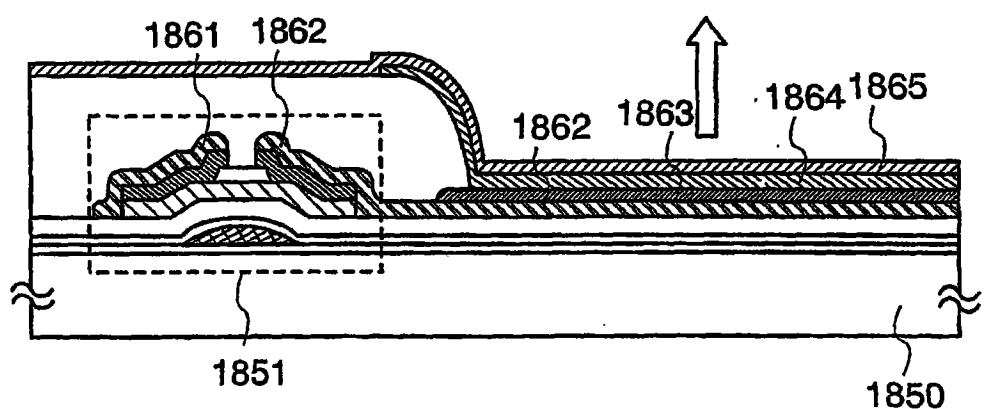

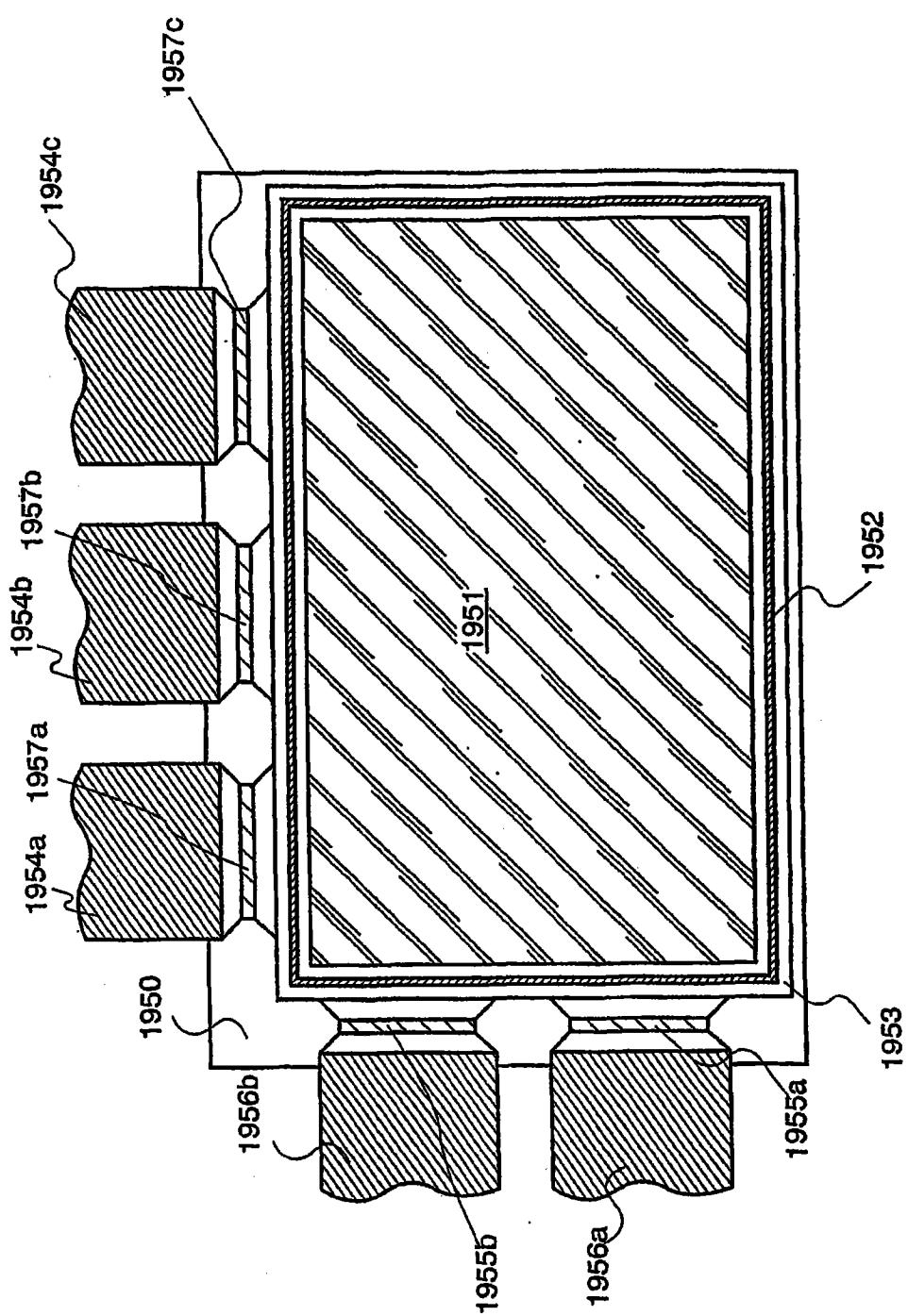

[0491] 参照图 31 描述作为应用了本发明的显示装置的一种模式的面板的外观。

[0492] 在如图 31 所示的面板中,其中驱动电路在像素部分 1951 周围形成的驱动 IC 通过 COG(玻璃上芯片)法安装。毋庸多言,驱动 IC 也可通过 TAB(载带自动接合)法安装。

[0493] 基板 1950 用密封材料 1952 固定到对置基板 1953。像素部分 1951 可将 EL 元件用作显示介质。驱动 IC 1955a 和 1955b、以及驱动 IC 1957a、1957b 和 1957c 各自可以是通过使用单晶半导体形成的集成电路、或通过使用利用多晶半导体制造的 TFT 形成等效的集成电路。信号或功率通过 FPC 1954a、1954b 和 1954c 以及 FPC1956a 和 1956b 被分别提供给驱动 IC 1955a 和 1955b,以及驱动 IC 1957a、1957b 和 1957c。

[0494] [实施方式 14]

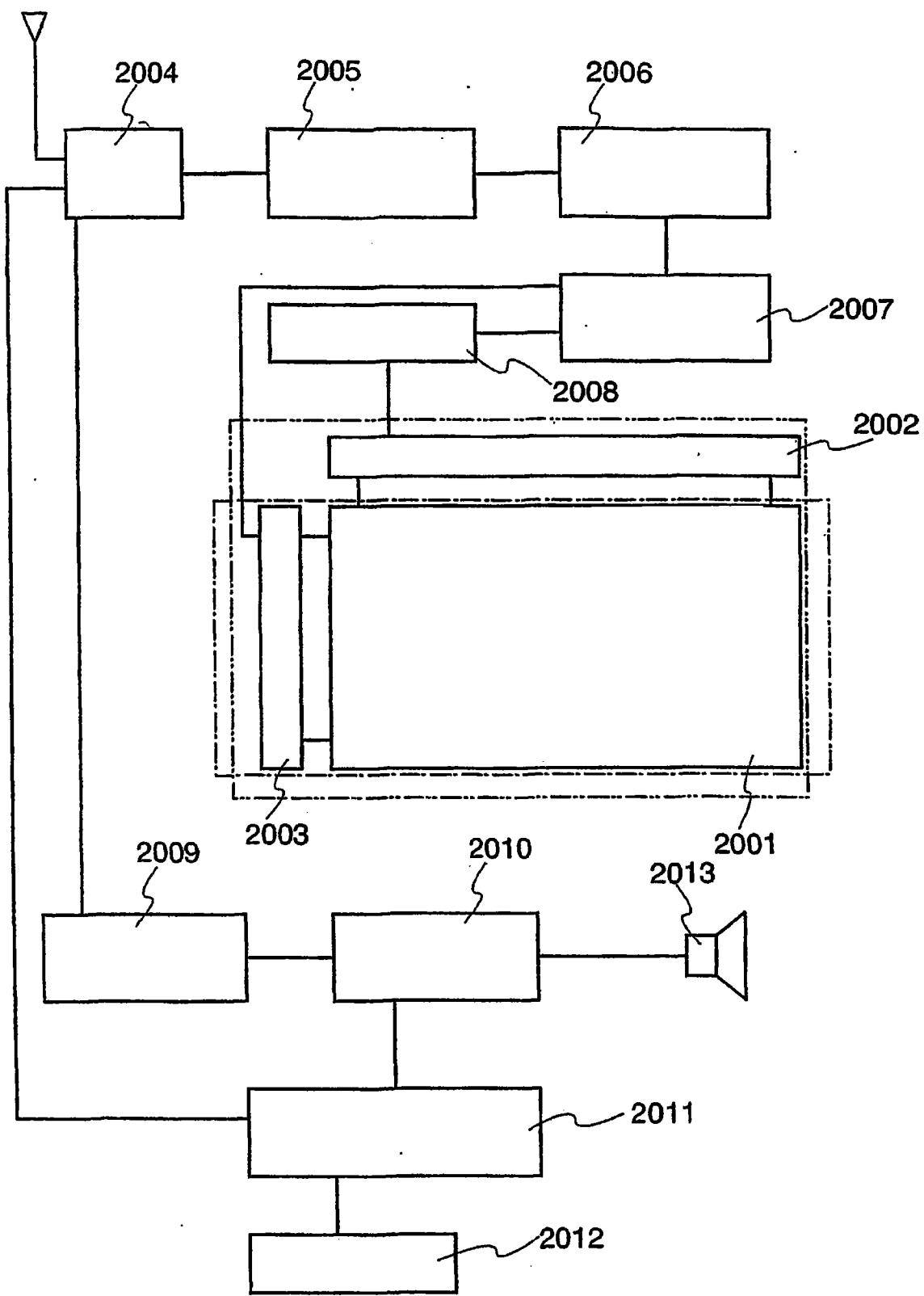

[0495] EL 电视机可通过使用根据本发明形成的显示装置来完成。图 32 是示出 EL 电视机的主要结构的框图。与如图 31 所示的结构一样,EL 显示面板包括外壳,其中扫描线驱动电路和信号线驱动电路通过 COG 法安装在像素部分 1951 及其周边,其中只形成一个像素部分并且扫描线驱动电路和信号线驱动电路通过 TAB 法安装,以及其中 TFT 使用 SAS 形成、像素部分和扫描线驱动电路集成在基板上、并且信号线驱动电路作为驱动 IC 分开安装,然而,可采用任一模式。

[0496] 另一外部电路可由以下构成:放大由调谐器 2004 接收的信号中的视频信号的视频信号放大电路 2005;将要从中输出的信号转换成与红、绿和蓝的每一种颜色相对应的色度信号的视频信号处理电路 2006;以及转换视频信号以输入到视频信号输入侧的驱动 IC

等的控制电路 2007。控制电路 2007 向扫描线侧和信号线侧输出信号。在数字驱动的情形中,信号分配电路 2008 可被设置在信号线侧,并且输入数字信号可被分成  $m$  个部分并提供。

[0497] 由调谐器 2004 接收的信号中的音频信号被发送给音频信号放大电路 2009,并通过音频信号处理电路 2010 提供给扬声器 2013。控制电路 2011 接收来自输入部分 2012 的有关接收站(接收频率)或音量的控制数据,并将该信号发送给调谐器 2004 和音频信号处理电路 2010。

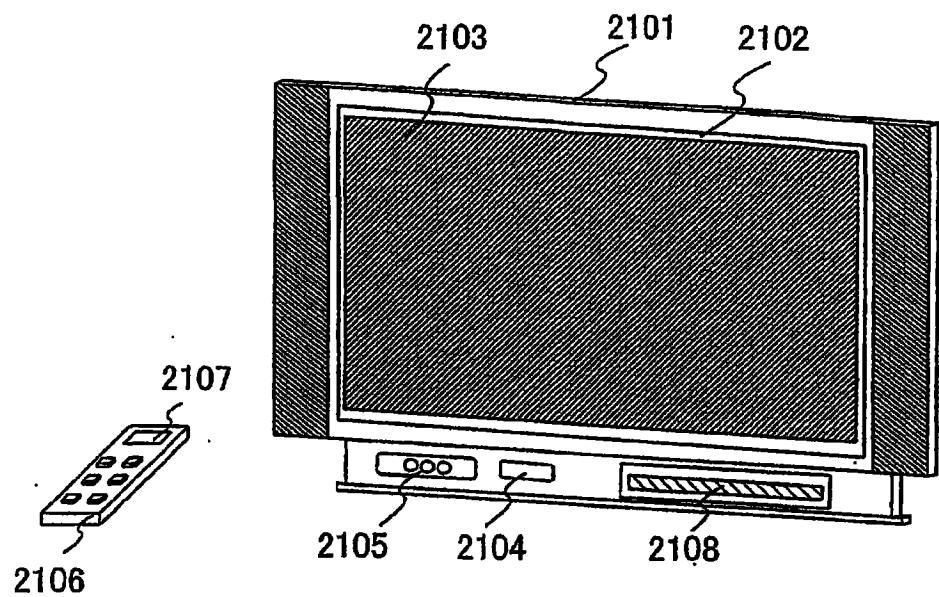

[0498] 电视机可通过将包括这样的外部电路的 EL 模块结合到如图 33 所示的外壳 2101 中来完成。显示屏 2021 通过使用 EL 显示模块来形成,并且扬声器 2202、操作开关 2024 等可被设置为附件设备。这样,电视机可根据本发明完成。

[0499] 此外,外部进入的光的反射光可通过使用波片和偏振片来阻挡。 $\lambda/4$  片或  $\lambda/2$  片被用作波片并可被设计成能控制光。模块具有 TFT 元件基板、发光元件、密封基板(密封材料)、波片( $\lambda/4$  片或  $\lambda/2$  片)以及偏振片的叠层结构,并且从发光元件所发出的光穿过其中并射向偏振片一侧外部。波片和偏振片可被设置在光所射向的一侧。在向两侧发光的双端发射发光显示装置的情形中,波片和偏振片可被设置在两侧。此外,防反射膜可被设置在偏振片外。因此,可显示高清晰度的精确图像。

[0500] 使用 EL 元件的显示面板 2102 被结合在外壳 2101 中。不仅普通的 TV 广播可通过接收器 2105 接收,而且可通过调制解调器 2104 有线或无线地连接到一通信网络来实现单向数据通信(从发送器到接收器)或双向数据通信(在发送器和接收器之间、或接收器之间)。电视机可通过装在外壳中的开关来操作、或通过单独提供的遥控单元 2106 来操作,并且显示要输出的信息的显示部分 1207 可包括在遥控单元中。

[0501] 此外,除主屏幕 2103 外,电视机还可具有由显示频道或音量的第二显示面板构成的子屏幕 2108。该主屏幕 2103 和子屏幕 2108 可通过使用 EL 显示面板来形成。可选择地,主屏幕 2103 可通过具有较佳视角的 EL 显示面板来形成,而子屏幕 2108 可通过使用能以上述结构低功耗地显示的液晶显示面板来形成。此外,在给予低功耗优先级的情形中,主屏幕 2103 可通过使用液晶显示面板来形成,而子屏幕 2108 可通过使用会闪烁的 EL 显示面板来形成。即使在使用大基板时,高度可靠的显示装置也可通过应用本发明来形成,并且使用大量的 TFT 或电子部件。

[0502] 毋庸多言,本发明并不限于电视机并可用于各种应用,特别是大显示媒体,诸如火车站、机场等的信息显示板等、或街上的广告显示板、以及个人计算机的监视器。

[0503] [实施方式 15]

[0504] 可通过应用本发明来制造各种显示装置。也就是说,本发明可应用于其中显示装置结合在显示部分中的各种电子设备。

[0505] 这些电子设备可给出如下:诸如视频摄像机和数码相机等摄像机、投影仪、头戴式显示器(护目镜型显示器)、汽车导航系统、车载音响、个人计算机、游戏机、便携式信息终端(移动计算机、蜂窝式电话、电子书等)、包括记录介质的图像再现设备(具体地,能再现诸如数字多功能盘(DVD)并具有能显示再现图像的显示器的记录介质的设备)等。其示例如图 34A ~ 34C 所示。

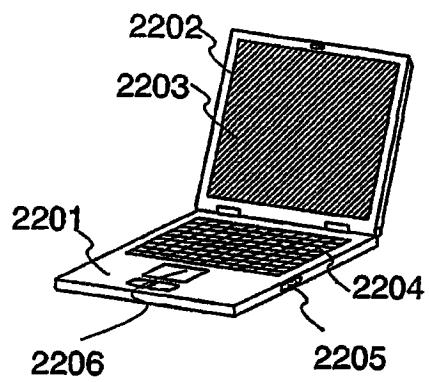

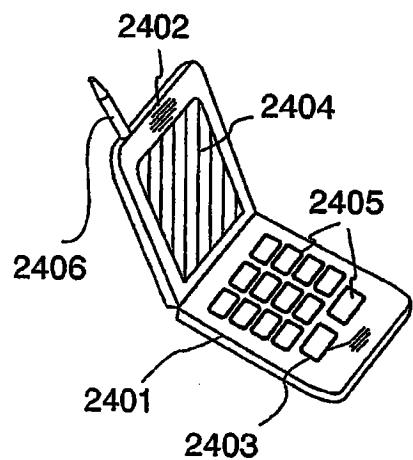

[0506] 图 34A 示出一膝上型个人计算机,它包括主体 2201、外壳 2202、显示部分 2203、键

盘 2204、外部连接端口 2205、定点鼠标 2206 等。本发明用于制造显示部分 2203。当应用本发明时,可低成本地制造具有高显示质量的显示部分的膝上型个人计算机。

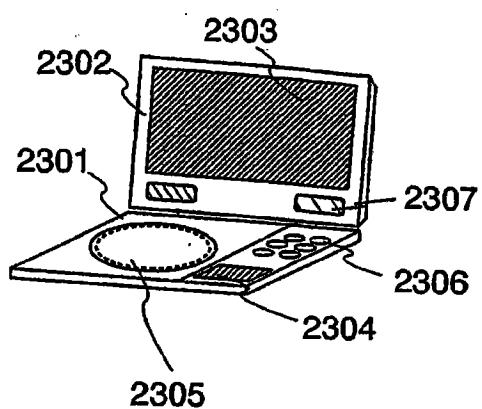

[0507] 图 34B 示出包括图像显示部分的一图像再现设备(具体地, DVD 再现设备), 它包括主体 2301、外壳 2302、显示部分 A 2303、显示部分 B 2304、记录介质(DVD 等)读取部分 2305、操作键 2306、扬声器部分 2307 等。显示部分 A 2303 主要显示图像数据, 而显示部分 B 2304 主要显示文本数据。本发明用于制造显示部分 A2303 和显示部分 B 2304。当应用本发明时, 可低成本地制造具有高显示质量的图像显示部分的图像再现设备。

[0508] 图 34C 示出蜂窝式电话, 它包括主体 2401、音频输出部分 2402、音频输入部分 2403、显示部分 2404、操作开关 2405、天线 2406 等。当根据本发明制造的显示装置应用于显示部分 2404 时, 可低成本地制造具有高显示质量的显示部分的蜂窝式电话。

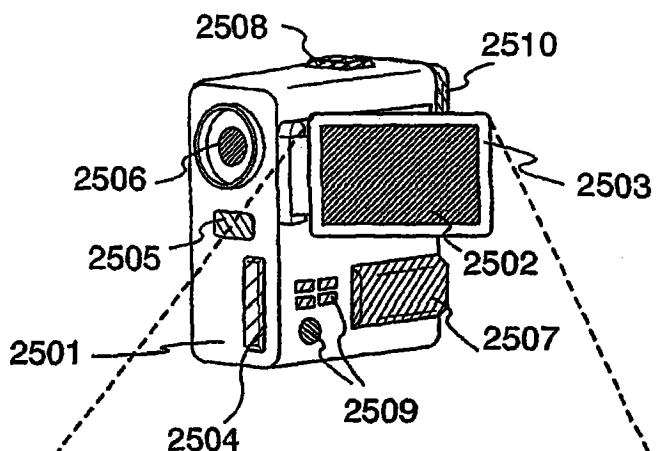

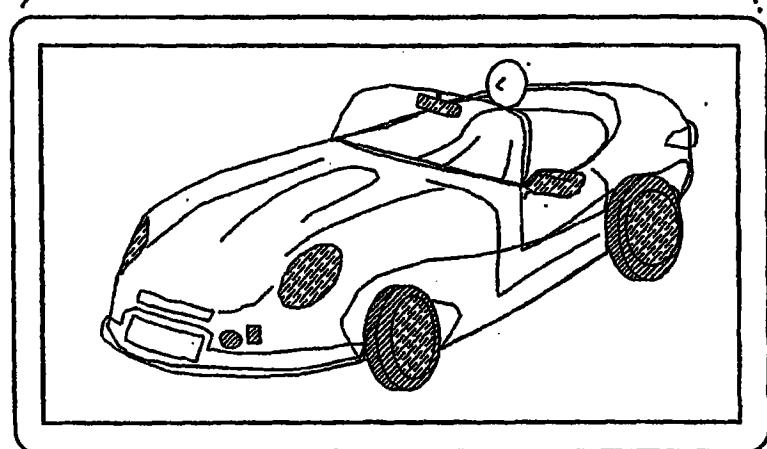

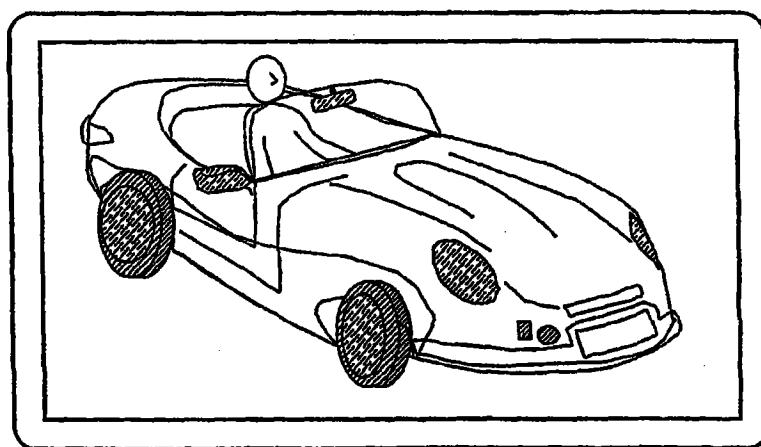

[0509] 图 35A 示出视频摄像机, 它包括主体 2501、显示部分 2502、外壳 2503、外部连接端口 2504、遥控接收部分 2505、图像接收部分 2506、电池 2507、音频输入部分 2508、操作键 2509、目镜部分 2510 等。本发明可应用于作为双端发射发光显示装置的显示部分 2502。图 35B 和 35C 示出在显示部分 2502 中显示的图像。图 35B 示出所拍摄的图像, 而图 35C 示出从正在拍摄的车辆一侧看到的图像。因为本发明的显示装置是透光型的, 从而可在两侧显示图像, 所以所拍摄的图像也可从主体侧看到。因此, 拍摄自身的照片也是方便的。此外, 本发明可应用于数码视频摄像机等、以及可获得相似效果的视频摄像机。通过将根据本发明制造的显示装置应用于显示部分 2502, 可低成本地制造诸如视频摄影机和数码相机等具有高显示质量的图像显示部分的摄像机。本实施例可组合以上实施方式自由实现。

[0510] 本申请基于 2004 年 12 月 6 日向日本特许厅提交的日本优先权申请 No. 2004-353457, 其全部内容通过引用结合于此。 100 : 像素部分(显示区域), 101 : 开关 TFT, 104 : 驱动 TFT, 106 : EL 元件, 108 : 电容器, 503 : 像素部分(显示区域), 504 : 像素部分(显示区域), 505 : 像素部分(显示区域), 605 : 栅绝缘层, 606 : 绝缘层, 800 : 基板, 801 : 基底膜, 802 : 导电层, 803 : 导电层, 804 : 绝缘层, 805 : 栅绝缘层, 806 : 导电层, 807 : 半导体层, 808 : N 型半导体层, 809 : 沟道保护膜, 811 : 掩模层, 813 : 掩模层, 815 : 导电层, 816 : 导电层, 817 : 导电层, 818 : 通孔, 820 : 绝缘层, 821 : 场致发光层, 822 : 导电层, 850 : 密封基板, 851 : 密封材料, 854 : 每一像素中的电路, 860 : 栅极布线层, 861 : 各向异性导电层, 862 : 柔性印刷电路(FPC), 900 : 基板, 903 : 微滴排放单元, 904 : 图像拾取单元, 905 : 头, 907 : 控制单元, 908 : 存储介质, 909 : 图像处理单元, 910 : 计算机, 911 : 标记, 954 : 每一像素中的电路, 1001 : TFT(开关 TFT), 1002 : TFT(驱动 TFT), 1003 : 发光元件(EL 元件), 1004 : 电容器, 1005 : 源极信号线, 1006 : 栅极信号线, 1007 : 电源线, 1054 : 每一像素中的电路, 1154 : 每一像素中的电路, 1200 : 基板, 1201 : 基底膜, 1202 : 导电层, 1203 : 导电层, 1205 : 栅绝缘层, 1206 : 导电层, 1207 : 半导体层, 1208 : N 型半导体层, 1211 : 掩模层, 1213 : 掩模层, 1215 : 导电层, 1216 : 导电层, 1217 : 导电层, 1218 : 通孔, 1220 : 绝缘层, 1221 : 场致发光层, 1222 : 导电层, 1254 : 每一像素中的电路, 1300 : 基板, 1301 : 基底膜, 1302 : 栅电极层, 1303 : 栅电极层, 1305 : 栅绝缘层, 1306 : 导电层, 1307 : 半导体层, 1311 : 掩模层, 1313 : 掩模层, 1315 : 导电层, 1316 : 导电层, 1317 : 导电层, 1320 : 绝缘层, 1321 : 场致发光层, 1322 : 导电层, 1330 : 导电层, 1331 : 导电层, 1400 : 基板, 1401 : 基底膜, 1402 : 导电层, 1403 : 导电层, 1405 : 栅绝缘层, 1406 : 导电层, 1407 : 半导体层, 1408 : N 型半导体层, 1409 : 沟道保护膜, 1411 : 掩模层, 1413 : 掩模

层,1415 :导电层,1416 :导电层,1417 :导电层,1418 :通孔,1420 :绝缘层,1421 :场致发光层,1422 :导电层, 1441 :绝缘层,1500 :基板,1501 :基底膜,1502 :导电层,1503 :导电层,1505 :栅绝缘层,1506 :导电层,1507 :半导体层,1508 :N型半导体层,1511 :掩模层,1513 :掩模层,1515 :导电层,1516 :导电层,1517 :导电层,1518 :通孔,1520 :绝缘层,1521 :场致发光层,1522 :导电层,1600 :基板,1601 :基底膜,1602 :导电层,1603 :导电层,1605 :栅绝缘层,1606 :导电层,1607 :半导体层,1611 :掩模层,1613 :掩模层,1615 :导电层,1616 :导电层,1617 :导电层,1620 :绝缘层,1621 :场致发光层,1622 :导电层,1630 :导电层,1631 :导电层,1700 :基板,1701 :基底膜,1702 :导电层,1703 :导电层,1704 :导体,1705 :栅绝缘层,1706 :导电层,1707 :半导体层,1708 :N型半导体层,1709 :沟道保护膜,1711 :掩模层,1715 :导电层,1716 :导电层,1717 :导电层,1720 :绝缘层,1721 :场致发光层,1722 :导电层,1850 :基板,1851 :晶体管,1852 :源极布线或漏极布线,1853 :源极布线或漏极布线,1854 :电极,1855 :场致发光层,1856 :电极。1861 :源极布线或漏极布线,1862 :源极布线或漏极布线,1863 :电极,1864 :场致发光层,1865 :电极,1870 :源极布线或漏极布线,1871 :源极布线或漏极布线,,1872 :电极,1873 :场致发光层,1874 :电极,1950 :基板,1951 :像素部分,1952 :密封材料,1953 :对置基板,1954a :FPC,1954b :FPC,1954c :FPC,1955a :驱动 IC ;1955b :驱动 IC,1956a :FPC,1956b :FPC,1957a :驱动 IC,1957b :驱动 IC,1957c :驱动 IC,2001 :EL 显示面板,2002 :源极信号线驱动电路,2003 :栅极信号线驱动电路,2004 :调谐器,2005 :视频信号放大电路,2007 :控制电路,2008 :信号分配电路,2009 :音频信号放大电路,2010 :音频信号放大电路,2011 :控制单元,2012 :输入部分,2013 :扬声器,2021 :显示屏,2022 :扬声器,2024 :操作开关,2101 :外壳,2102 :显示面板,2103 :主屏幕,2104 :调制解调器,2105 :接收器,2106 :遥控单元,21107 :显示部分,2108 :子显示器,2201 :主体,2202 :外壳,2203 :显示部分,2204 :键盘,2205 :外部连接端口,2206 :定点鼠标,2301 :主体,2302 :外壳,2303 :显示部分 A,2304 :显示部分 B, 2306 :操作键,2307 :扬声器部分,2401 :主体,2402 :音频输出部分,2403 :音频输入部分,2404 :显示部分,2405 :操作开关,2406 :天线,2501 :主体,2502 :显示部分,2503 :外壳,2504 :外部连接端口,2505 :遥控接收部分,2506 :接收部分,2507 :电池,2508 :音频输入部分,2509 :操作键。

图 1

图 2

图 3

图 4

图 5A

图 5B

图 6A

图 6B

图 6C

图 7A

图 7C

图 7B

图 7D

图 8

图 9

图 10

图 11

图 12

图 13A

图 13B

图 13C

图 13D

图 14A

图 14B

图 15

图 16A

图 16B

图 17

图 18A

图 18B

图 18C

图 18D

图 19A

图 19B

图 20A

图 20B

图 20C

图 20D

图 21

图 22A

图 22B

图 22C

图 22D

图 23A

Fig. 23B

图 23B

图 24A

图 24B

图 24C

图 24D

图 25A

图 25B

图 26A

图 26B

图 26C

图 26D

图 27

图 28A

图 28B

图 28C

图 28D

图 29A

图 29B

图 30A

图 30B

图 30C

图 31

图 32

图 33

图 34A

图 34B

图 34C

图 35A

图 35B

图 35C

|                |                                                                                                                                            |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示装置                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">CN102569342A</a>                                                                                                               | 公开(公告)日 | 2012-07-11 |

| 申请号            | CN201110373008.9                                                                                                                           | 申请日     | 2005-12-02 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 株式会社半导体能源研究所                                                                                                                               |         |            |

| 当前申请(专利权)人(译)  | 株式会社半导体能源研究所                                                                                                                               |         |            |

| [标]发明人         | 吉田泰则<br>木村肇<br>前川慎志<br>中村理<br>山崎舜平                                                                                                         |         |            |

| 发明人            | 吉田泰则<br>木村肇<br>前川慎志<br>中村理<br>山崎舜平                                                                                                         |         |            |

| IPC分类号         | H01L27/32                                                                                                                                  |         |            |

| CPC分类号         | H01L27/3248 H01L27/1214 H01L27/3276 H01L21/288 H01L21/76838 H01L27/156 H01L27/1285<br>H01L27/1292 G09G3/32 G09G3/36 H01L27/124 H01L51/0508 |         |            |

| 代理人(译)         | 杨洁                                                                                                                                         |         |            |

| 优先权            | 2004353457 2004-12-06 JP                                                                                                                   |         |            |

| 其他公开文献         | CN102569342B                                                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>                                                                                             |         |            |

### 摘要(译)

本发明提供一种可执行多灰度彩色显示的有源矩阵EL显示装置。特别地，本发明通过可选择性地形成图案的制造方法低成本地提供大的有源矩阵EL显示装置。像素部分中的电源线通过可选择性地形成图案的制造方法排列成矩阵。此外，通过可选择性地形成图案的制作方法在相邻布线之间设置更长距离，可减小布线间的电容。