## [12] 发明专利说明书

专利号 ZL 200510064215.0

[45] 授权公告日 2010 年 3 月 3 日

[11] 授权公告号 CN 100593185C

[22] 申请日 2005.4.12

[74] 专利代理机构 北京纪凯知识产权代理有限公司

[21] 申请号 200510064215.0

代理人 程伟

[30] 优先权

[32] 2004.4.12 [33] JP [31] 2004-117332

[32] 2005.3.28 [33] JP [31] 2005-092566

[32] 2005.3.28 [33] JP [31] 2005-092588

[32] 2005.3.30 [33] JP [31] 2005-096835

[73] 专利权人 三洋电机株式会社

地址 日本大阪

[72] 发明人 池田恭二

[56] 参考文献

CN1437178A 2003.8.20

JP2003223138A 2003.8.8

审查员 潘光虎

权利要求书 4 页 说明书 16 页 附图 31 页

[54] 发明名称

有机 EL 像素电路

[57] 摘要

本发明是通过控制驱动晶体管的控制端的电位以使与该晶体管的控制端的电位对应的驱动电流供给至有机 EL 组件。又在驱动晶体管与前述有机 EL 组件之间插入配置驱动控制晶体管，以使前述驱动电流导通或截止 (on-off)。并且，设置短路晶体管，且通过该短路晶体管以控制是否将驱动晶体管予以二极管连接。再者，通过选择晶体管，控制是否将来自数据线的数据信号供给至前述驱动晶体管的控制端。再者，在该选择晶体管与前述驱动晶体管的控制端之间配置电容，同时通过电位控制晶体管使该电容的前述选择晶体管与预定的电源之间的连接予以导通或截止。

1. 一种用于有机 EL 面板的像素电路，具有：

将与控制端的电位对应的驱动电流供给至有机 EL 组件的驱动晶体管；

插入配置于预定的电源与前述有机 EL 组件之间，且使前述驱动电流导通或截止的驱动控制晶体管；

用于控制是否使前述驱动晶体管为二极管连接的短路晶体管；

用于控制是否将来自数据线的数据信号供给至前述驱动晶体管的控制端的选择晶体管；

插入配置于该选择晶体管与前述驱动晶体管的控制端之间的电容；

使该电容的前述选择晶体管侧与前述预定的电源之间的连接予以导通或截止的电位控制晶体管；以及

连接在前述选择晶体管的控制端，且用于控制前述选择晶体管的导通截止的控制线，

该控制线也连接在前述电位控制晶体管的控制端，并且前述选择晶体管与前述电位控制晶体管在一方导通时另一方即截止。

2. 如权利要求 1 所述的用于有机 EL 面板的像素电路，其中，

前述驱动晶体管将 2 个被控制端的一端连接在正电源，而另一端则连接在前述驱动控制晶体管。

3. 如权利要求 2 所述的用于有机 EL 面板的像素电路，其中，

前述电位控制晶体管使前述电容的前述选择晶体管侧与前述正电源之间的连接予以导通或截止。

4. 如权利要求 2 所述的用于有机 EL 面板的像素电路，其中，

前述驱动晶体管为 p 沟道晶体管。

5. 如权利要求 1 所述的用于有机 EL 面板的像素电路，其中，

前述驱动晶体管将 2 个被控制端的一端连接在前述驱动控制晶体管，而将另一端连接在前述有机 EL 组件。

6. 如权利要求 5 所述的用于有机 EL 面板的像素电路，其中，前述电位控制晶体管使前述电容的前述选择晶体管侧与前述正电源之间的连接予以导通或截止。

7. 如权利要求 5 所述的用于有机 EL 面板的像素电路，其中，前述驱动晶体管为 n 沟道晶体管。

8. 如权利要求 1 所述的用于有机 EL 面板的像素电路，其中，具有连接在前述选择晶体管的控制端，且用于控制前述选择晶体管的导通截止的控制线，该控制线也连接有前述短路晶体管的控制端，并且前述选择晶体管与前述短路晶体管同时导通或截止。

9. 如权利要求 1 所述的用于有机 EL 面板的像素电路，其中，具有连接在前述选择晶体管的控制端，且用于控制前述选择晶体管的导通或截止的控制线，该控制线也连接有前述短路晶体管及前述电位控制晶体管的控制端，以及前述选择晶体管与前述短路晶体管同时导通截止，而前述选择晶体管与前述电位控制晶体管在一方导通时另一方即截止。

10. 如权利要求 1 所述的用于有机 EL 面板的像素电路，其中，前述驱动控制晶体管通过发光设定线控制导通截止，前述电位控制晶体管使前述电容的前述选择晶体管侧与前述发光设定线之间的连接导通或截止。

11. 如权利要求 10 所述的用于有机 EL 面板的像素电路，其中，具有连接在前述选择晶体管的控制端，且用于控制前述选择晶体管的导通截止的控制线，此控制线也连接在前述电位控制晶体管的控制端，并且前述选择晶体管与前述电位控制晶体管互补式地导通或截止。

12. 如权利要求 11 所述的用于有机 EL 面板的像素电路，其中，前述控制线也连接在前述短路晶体管的控制端，并且前述选择晶

体管与前述短路晶体管同时导通截止。

13. 如权利要求 10 所述的用于有机 EL 面板的像素电路，其中，具有连接在前述选择晶体管的控制端，且用于控制前述选择晶体管的导通截止的控制线，

前述发光设定线在通过前述控制线使选择晶体管导通之后，设定成使驱动控制晶体管截止的电压，并在通过前述控制线使选择晶体管截止之后，设定成使驱动控制晶体管导通的电压。

14. 一种有机 EL 面板的像素电路的驱动方法，其中前述像素电路包括：

将与控制端的电位对应的驱动电流供给至有机 EL 组件的驱动晶体管；

插入配置在预定的电源与前述有机 EL 组件之间，且使前述驱动电流导通截止的驱动控制晶体管；

用于控制是否使前述驱动晶体管为二极管连接的短路晶体管；

用于控制是否将来自数据线的数据信号供给至前述驱动晶体管的控制端的选择晶体管；

插入配置在该选择晶体管与前述驱动晶体管的控制端之间的电容；以及

使该电容的前述选择晶体管侧与前述预定的电源之间的连接导通截止的电位控制晶体管；以及

连接在前述选择晶体管的控制端，且用于控制前述选择晶体管的导通截止的控制线，该控制线也连接在前述电位控制晶体管的控制端，并且前述选择晶体管与前述电位控制晶体管在一方导通时另一方即截止；

前述驱动方法具有：

使选择晶体管及短路晶体管导通，并使电位控制晶体管截止，同时在将前述电容的选择晶体管侧的电压设为数据信号的电压的状态下，相对于驱动晶体管的被控制端一方的电压，将驱动晶体管的控制端电压设定成差异有相当于驱动晶体管的阈值电压的电压的复位步骤；以及

使选择晶体管、短路晶体管截止，并使电位控制晶体管导通，以将驱动晶体管的控制端电压设定成数据信号的电压以及与驱动晶体管的阈值电压对应的电压，且使驱动控制晶体管导通，以使来自驱动晶体管的驱动电流流通于有机 EL 组件的发光步骤。

15. 如权利要求 14 所述的有机 EL 面板的像素电路的驱动方法，其中，

作为前述复位步骤之前的步骤，是将前述选择晶体管及短路晶体管设为导通，电位控制晶体管设为截止，前述驱动控制晶体管设为导通，以使前述驱动晶体管的控制端的电荷释出的放电步骤。

## 有机 EL 像素电路

### 技术领域

本发明涉及一种对应数据信号以控制供给至有机 EL 组件的驱动电流的有机 EL 像素电路。

### 背景技术

将属于自发光组件的电致发光 (Electroluminescence; 以下称 EL) 组件作为发光组件使用在各像素的 EL 显示装置除具有自发光型的优点外，还具有较薄且消耗电力较小等优点，故正作为一种取代液晶显示装置 (LCD) 及 CRT 等显示装置的显示装置而受到瞩目。

而在将个别控制 EL 组件的薄膜晶体管 (TFT) 等开关组件设置在各像素，且依每像素控制 EL 组件的有源矩阵型 (active matrix type) EL 显示装置中，尤能进行高精细的显示。

在此有源矩阵型 EL 显示装置中，在基板上向行 (row, 水平) 方向延伸有多条栅极线，并向列 (column, 垂直) 方向延伸有多条数据线及电源线，而各像素具备有机 EL 组件、选择 TFT、驱动用 TFT 及保持电容。通过选择栅极线以使选择 TFT 导通 (ON)，并将数据线上的数据电压 (电压视频 (video) 信号) 充电至保持电容，且以该电压使驱动 TFT 导通以使来自电源线的电力流通于有机 EL 组件。

然而，在此种像素电路中，当配置成矩阵状的像素电路的驱动 TFT 的阈值电压 (threshold voltage) 不均时，辉度即变成不均，而有显示品质降低的问题。再者，就构成整体显示面板的像素电路的 TFT 而言，难以使其特性相同，而难以防止其导通截止 (ON OFF) 的阈值不均的情形。

于是，希望防止在驱动 TFT 中阈值的不均对于显示造成的影响。

在此，在有关用于防止对于 TFT 的阈值电压的变动的影响的电路方面，以往已有各种的提案 (例如日本特表 2002-514320 号公报)。

然而，在此提案中，必须要有用于补偿阈值变动的电路。因此，使用此种电路时，即会有像素电路的组件数增加的问题，也有开口率

变小的问题。而且，在追加供补偿之用的电路时，也会有必须变更用于驱动像素电路的周边电路的问题。

## 发明内容

本发明提供一种能够有效补偿驱动晶体管的阈值电压的变动的像素电路。

依据本发明，在使选择晶体管导通的状态下，通过使短路晶体管导通，即可将驱动晶体管的控制端电压设定成与数据电压及驱动晶体管的阈值电压对应的电压。因此，不须驱动晶体管的阈值电压的变动，即可将与数据电压对应的驱动电流供给至有机EL组件。

并且，电位控制晶体管的一端连接在发光设定线。由于发光设定线被设定来自预定电源的电压，因此该电压基本上不会受到流动于有机EL组件的电流等的影响而呈稳定。于是，即可正确地设定驱动晶体管的控制端电压。

并且，由于将驱动晶体管设定成n沟道晶体管，因此晶体管的特性优异，而晶体管的有源层也可通过非晶硅予以形成。再者，即使将电容器插入选择晶体管与驱动晶体管的控制端之间，仍可利用与将传统的选择晶体管直接连接在p沟道驱动晶体管的控制端时相同极性的数据信号。

## 附图说明

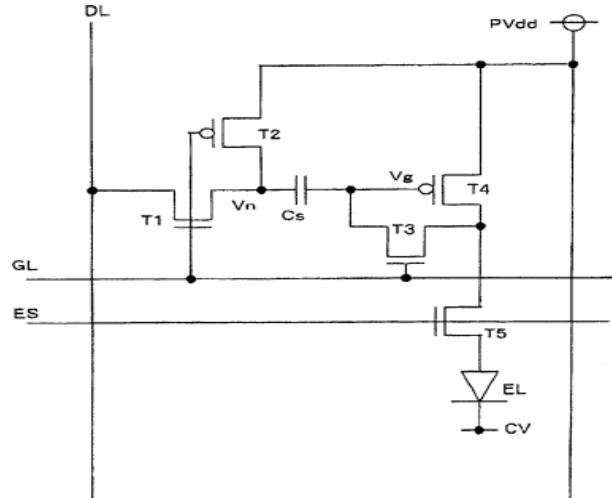

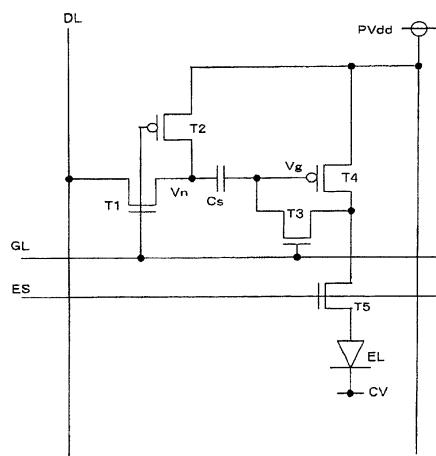

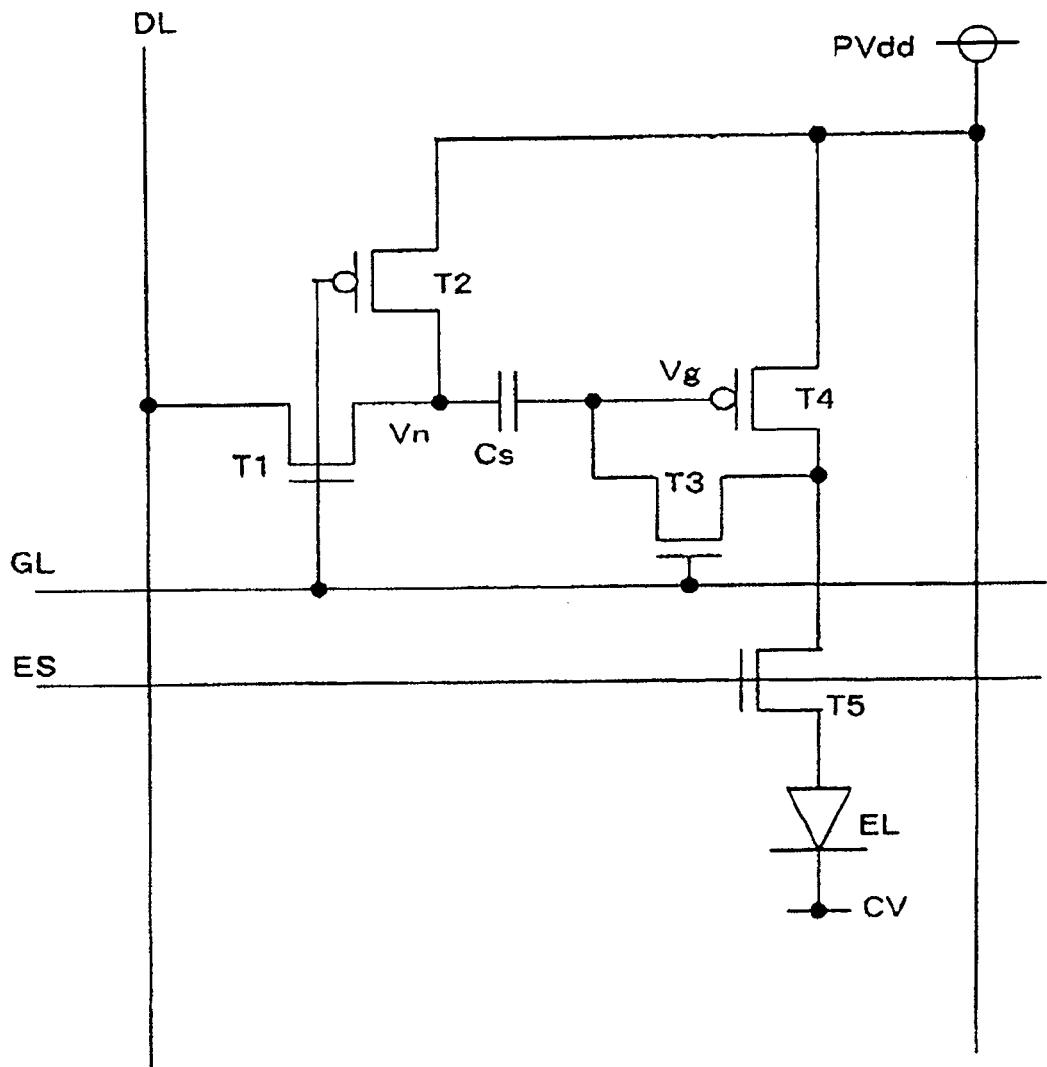

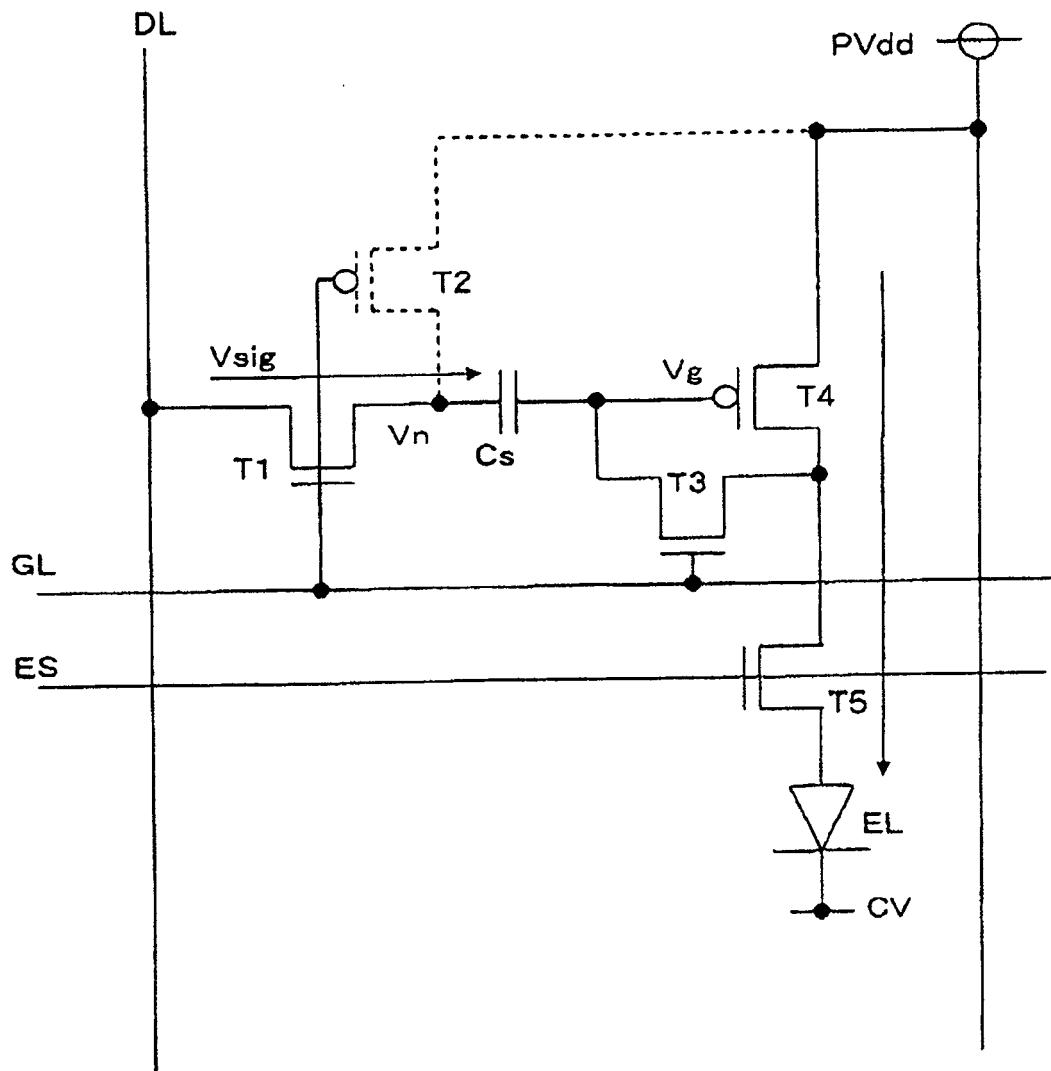

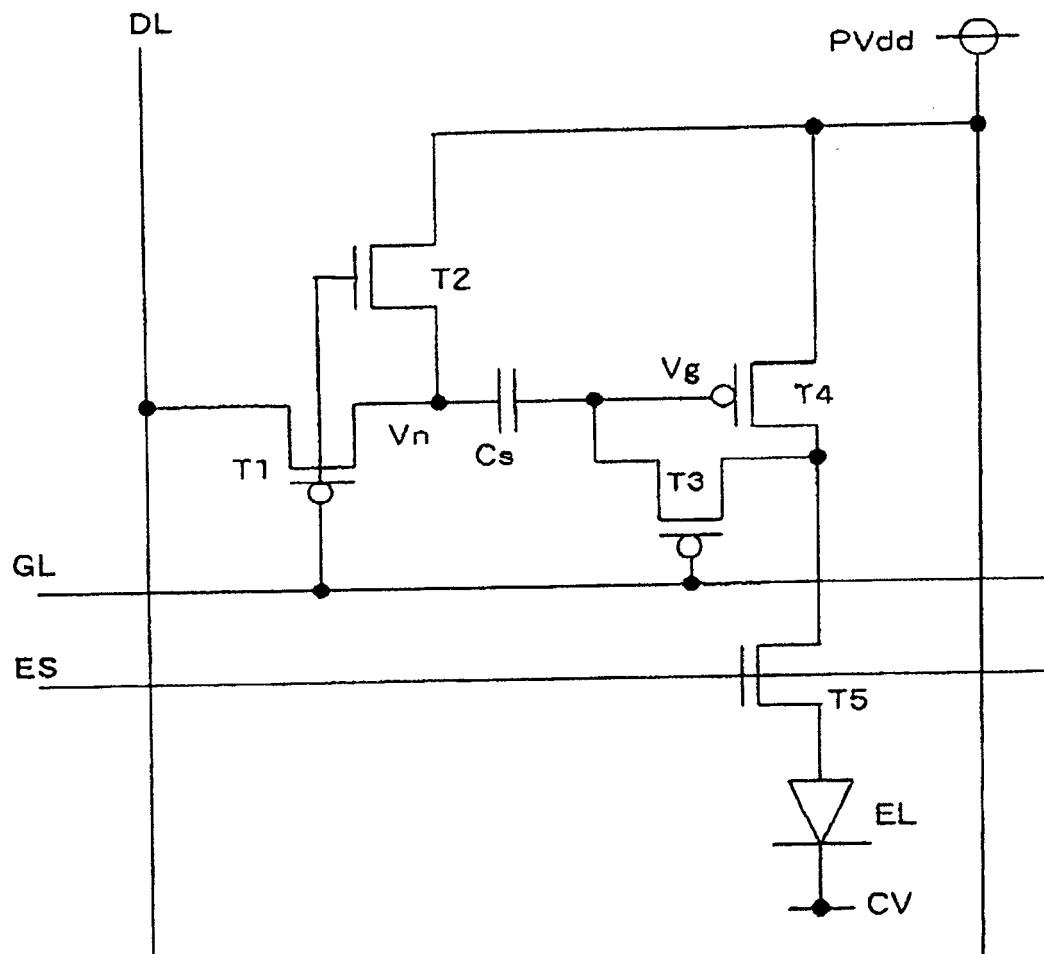

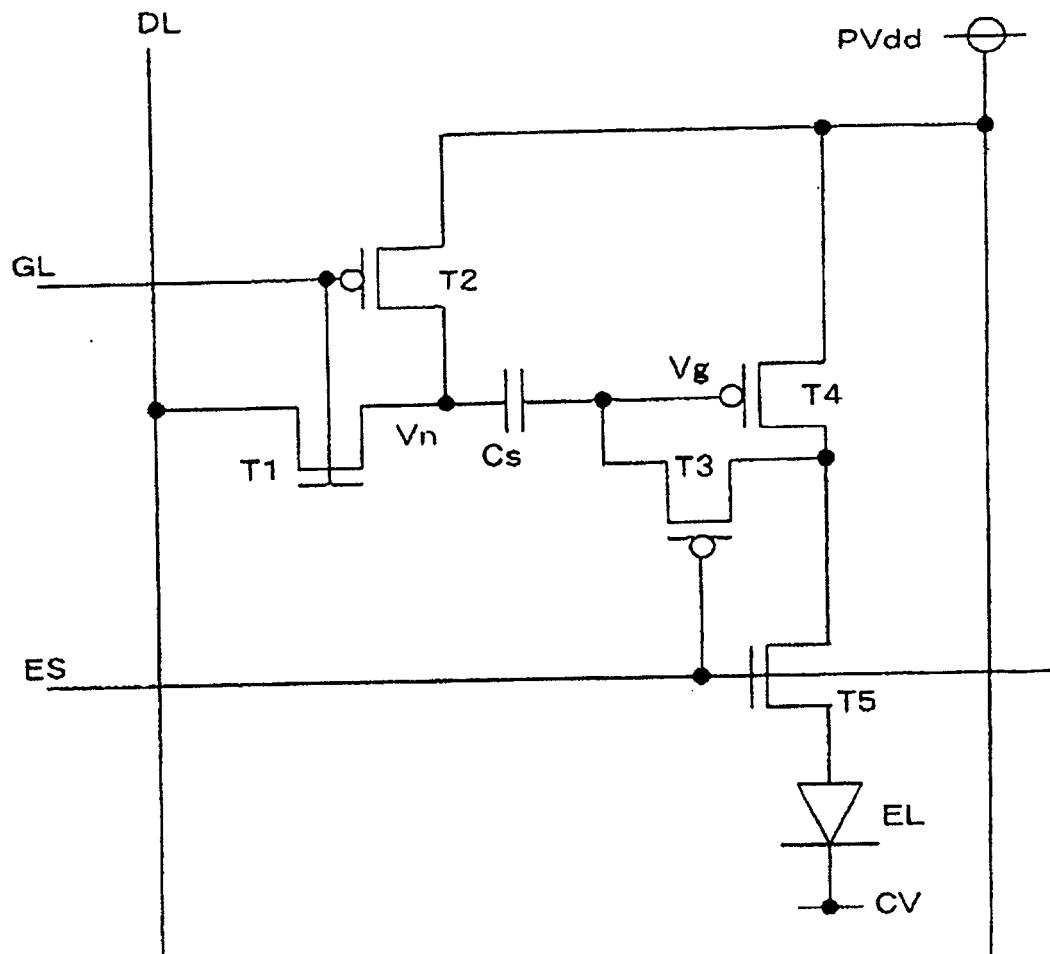

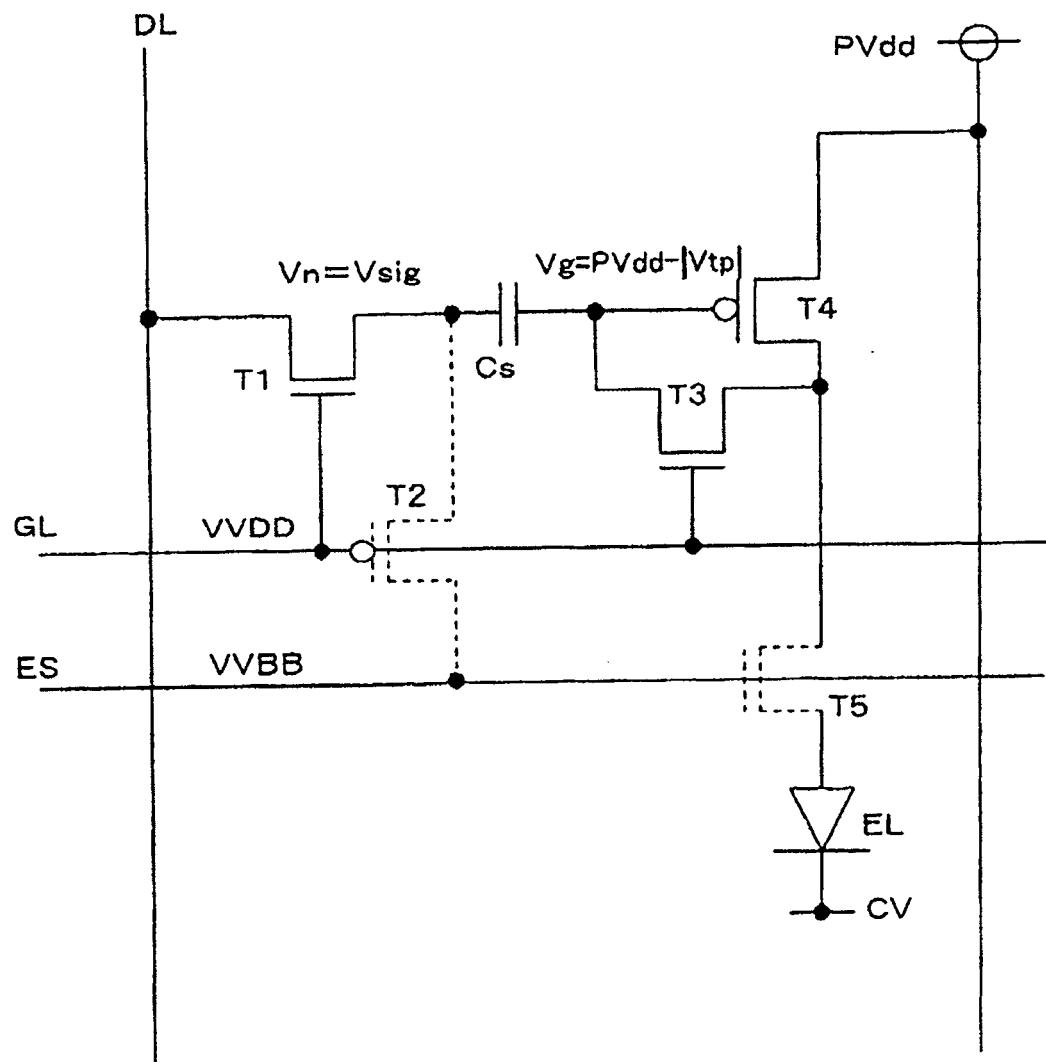

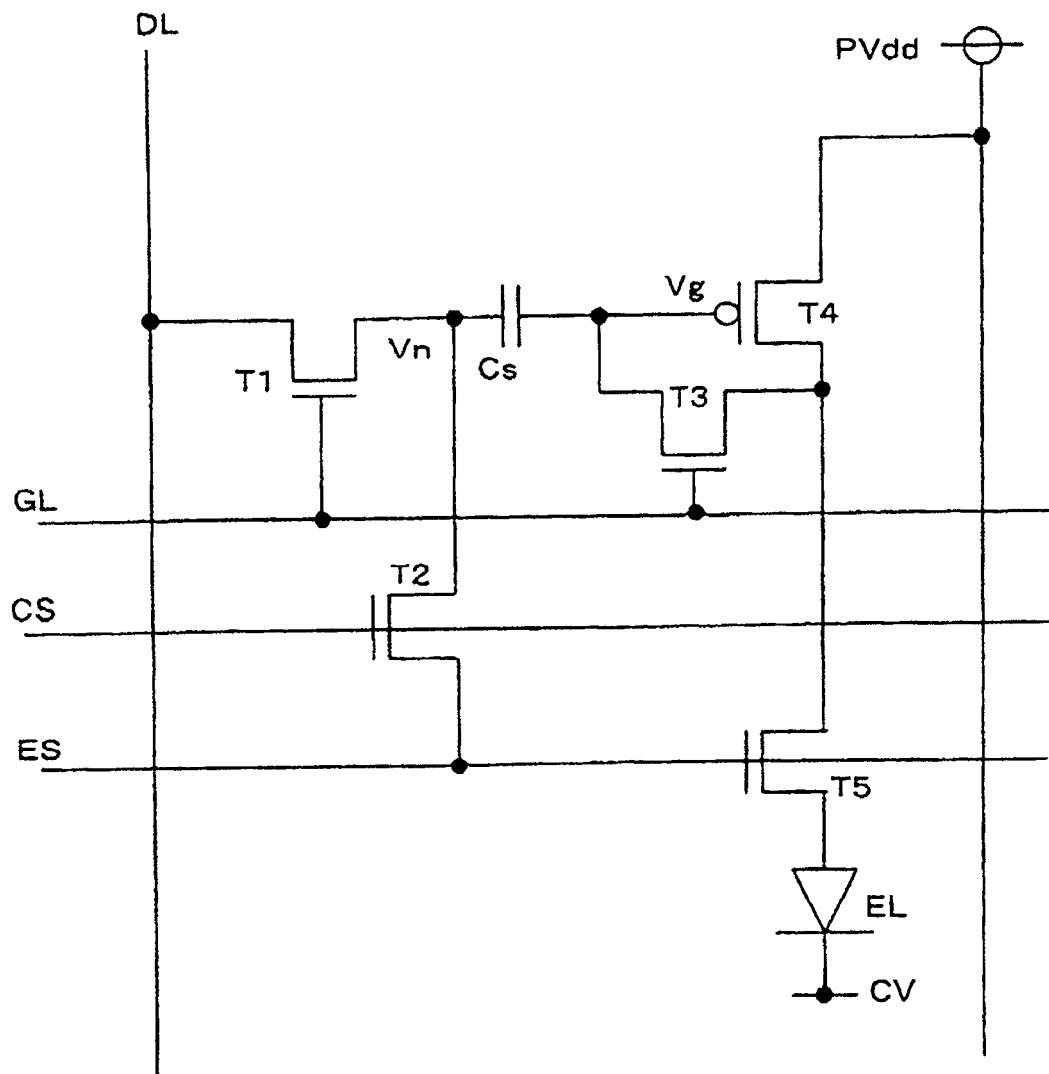

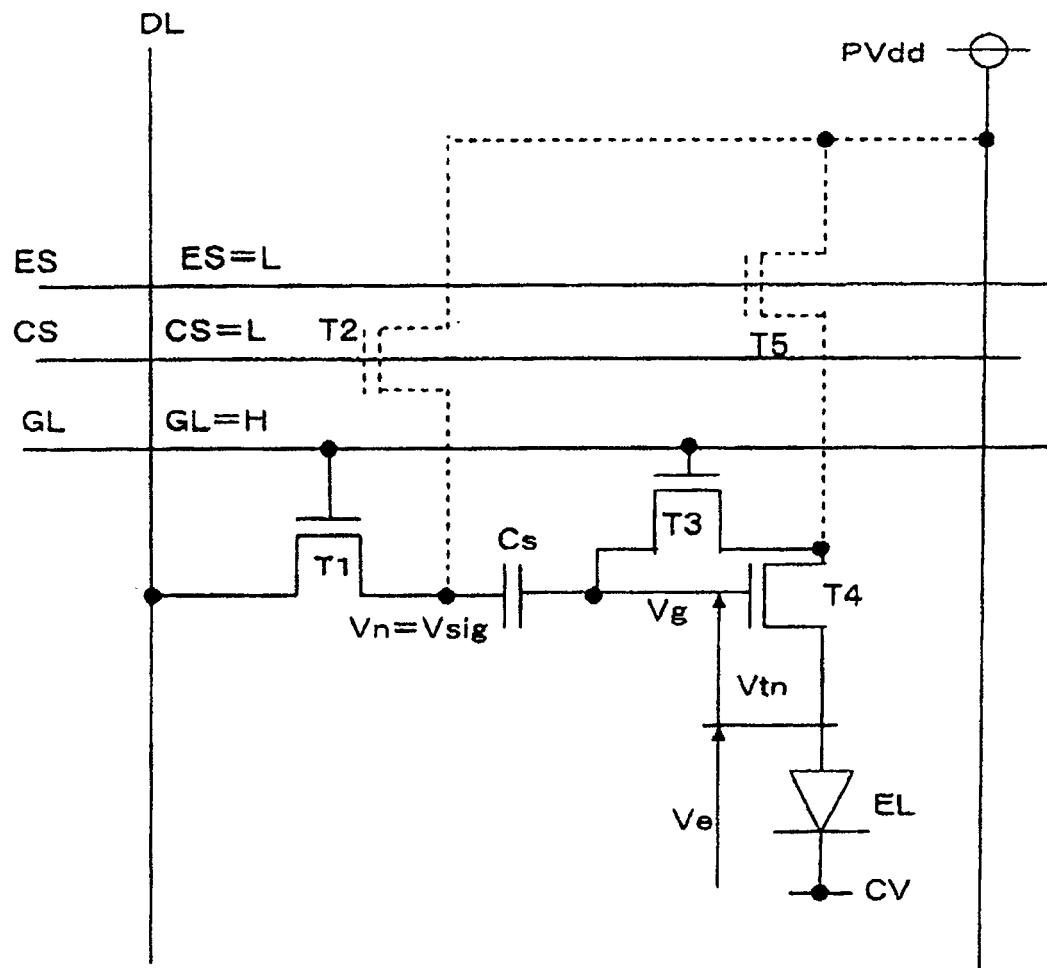

图1为表示实施例的像素电路的构成图；

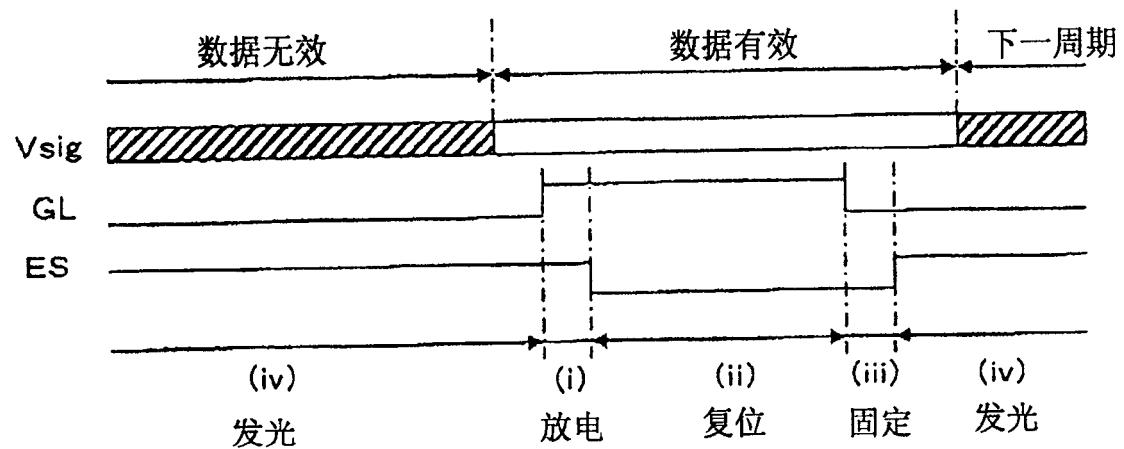

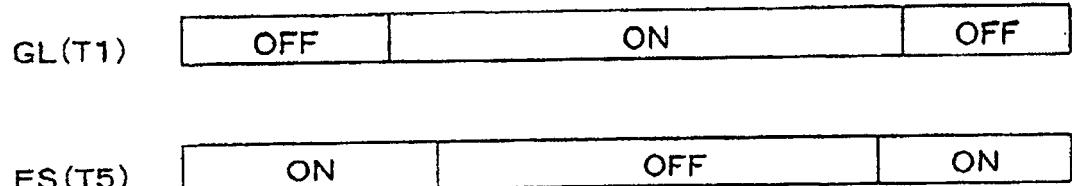

图2为说明动作的条形图；

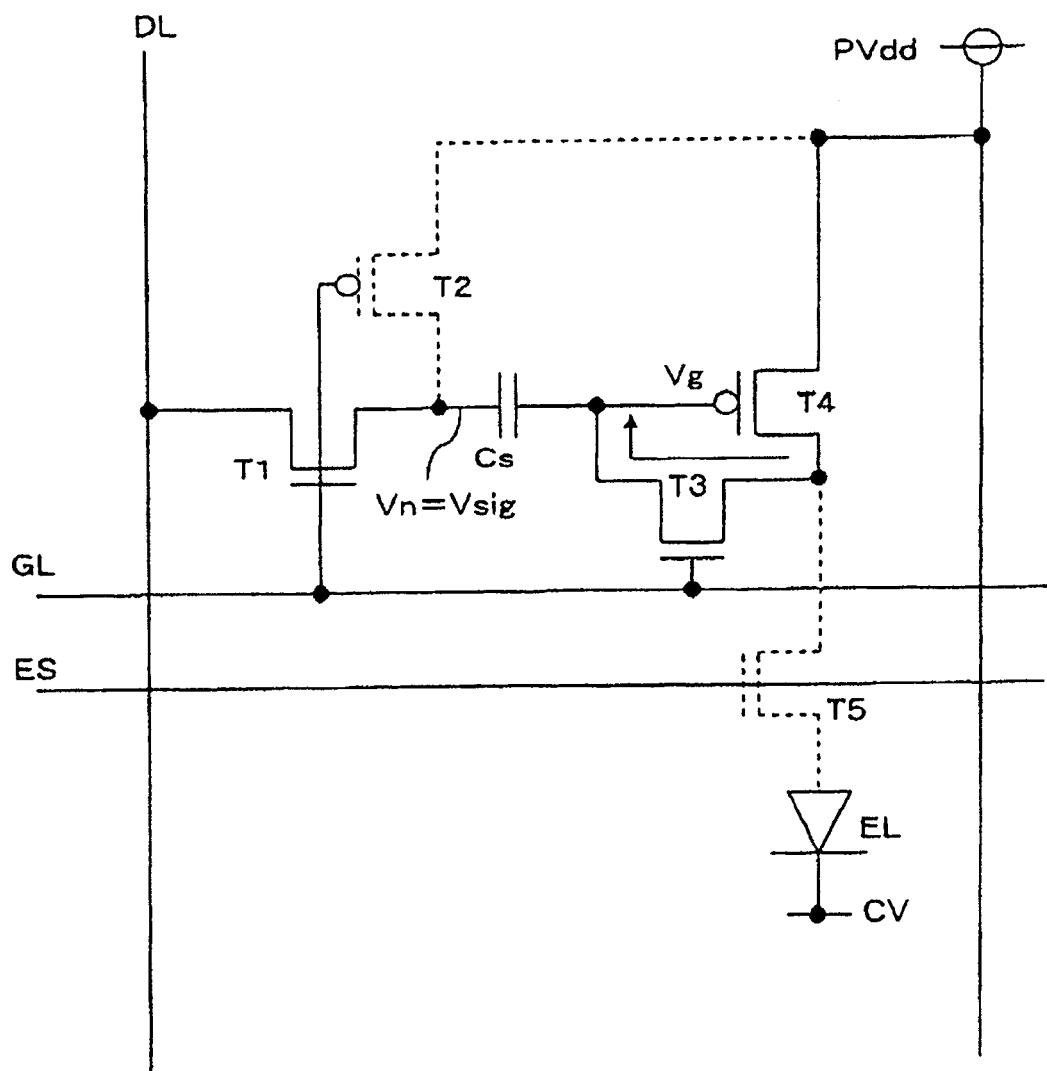

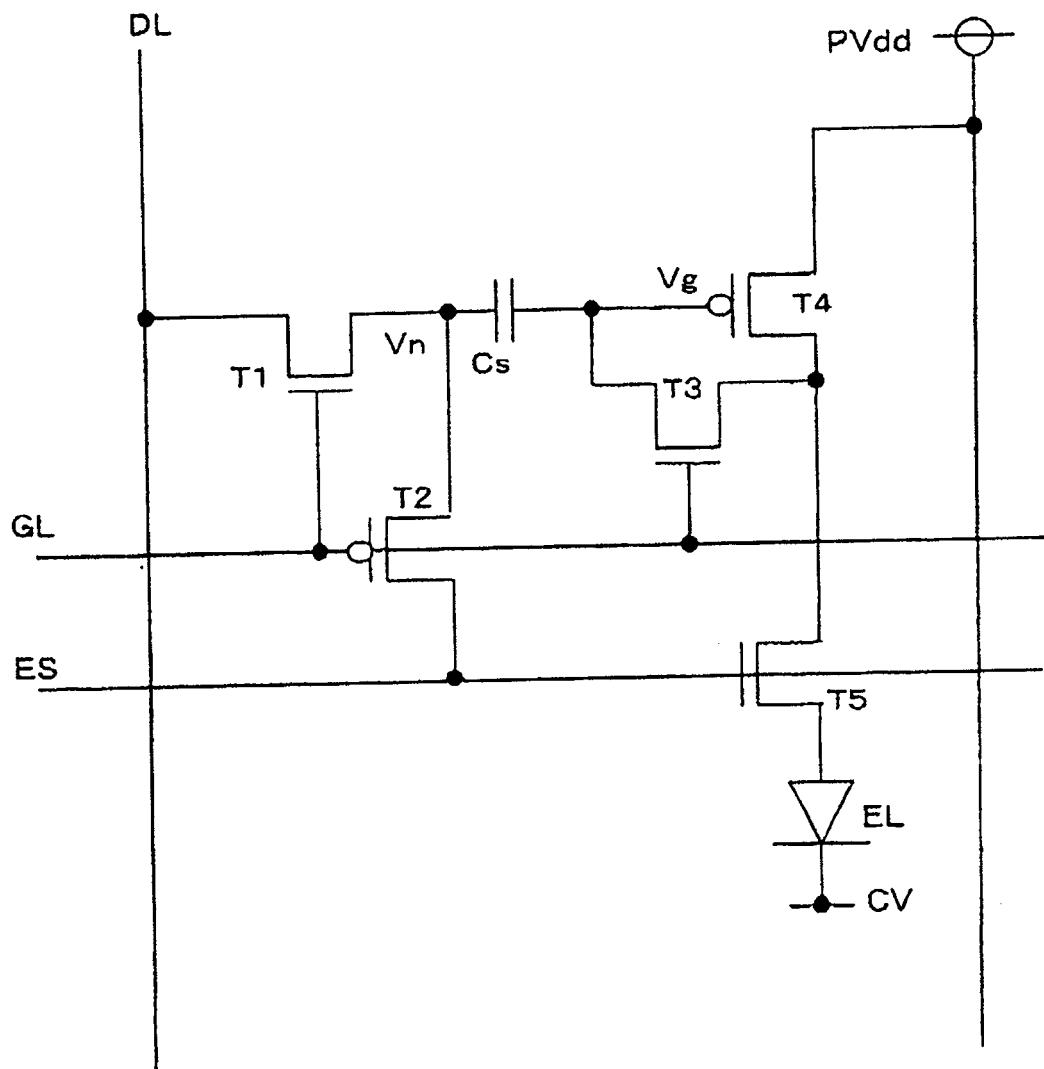

图3为说明放电(discharge)步骤的图；

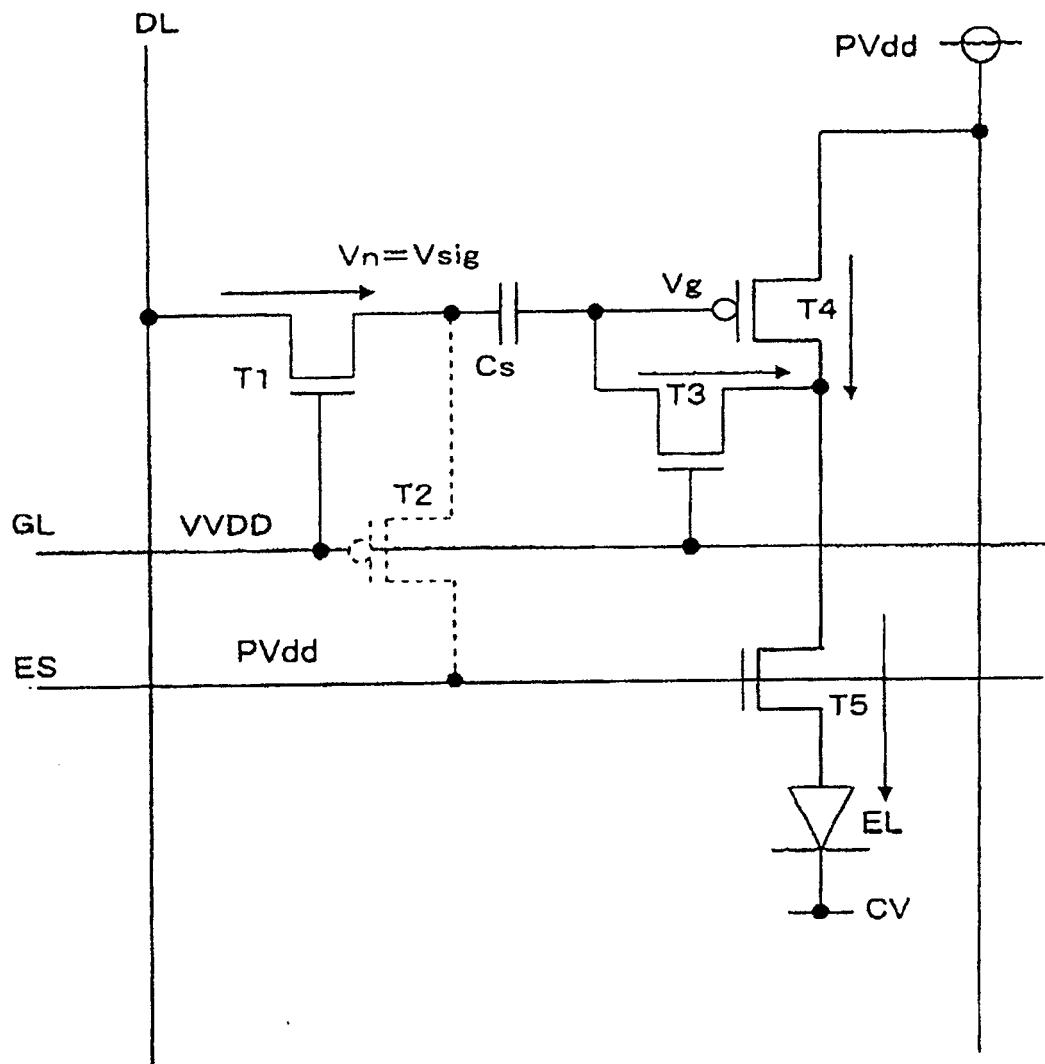

图4为说明复位(reset)步骤的图；

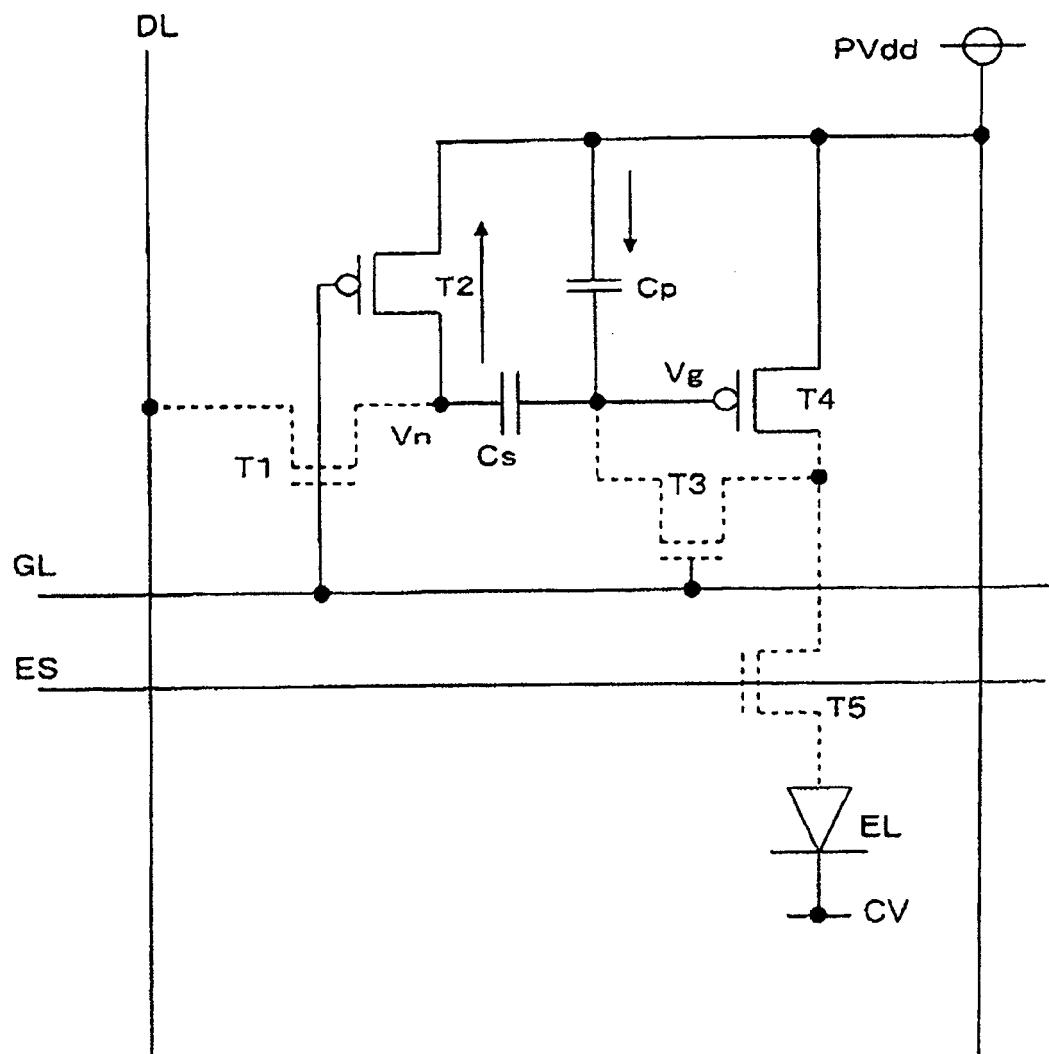

图5为说明电位固定步骤的图；

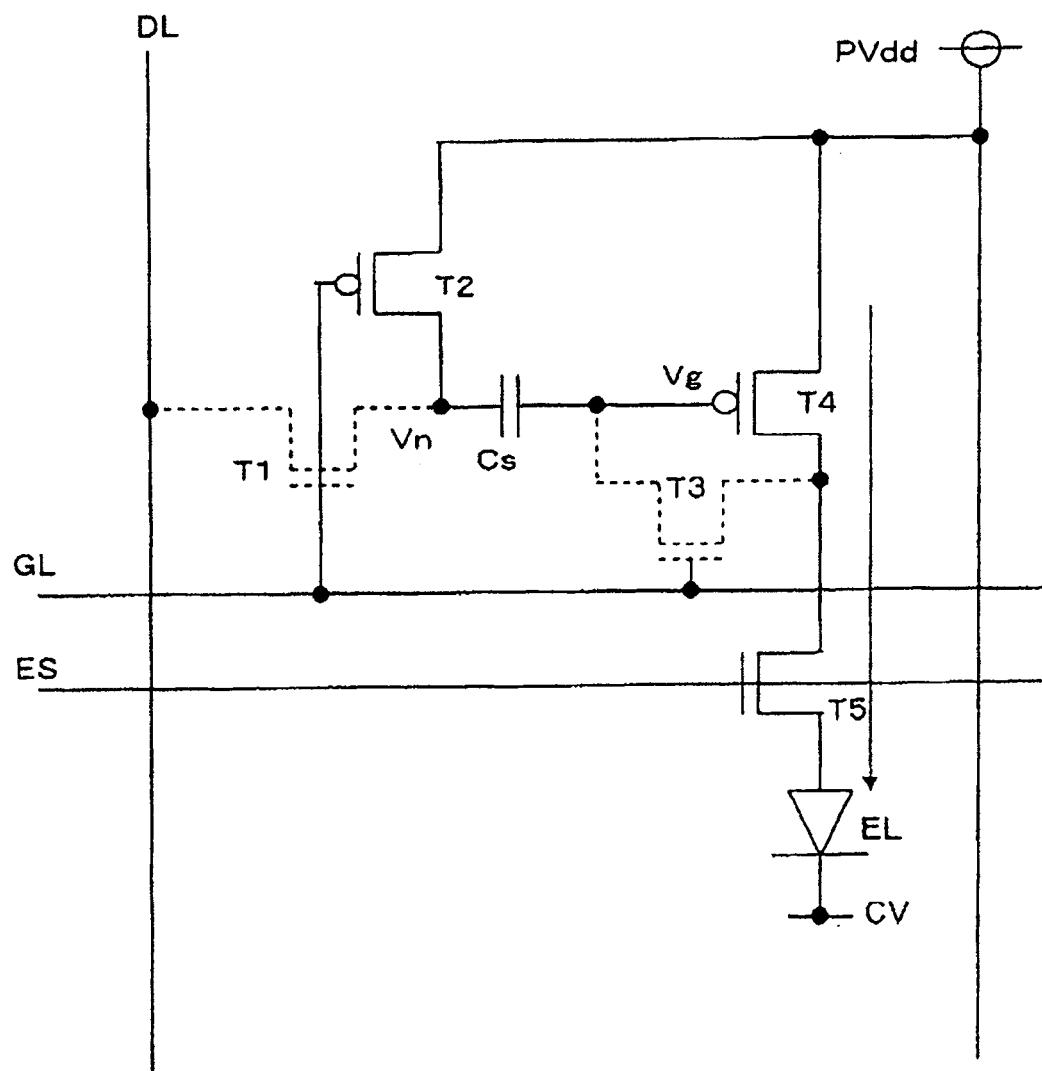

图6为说明发光步骤的图；

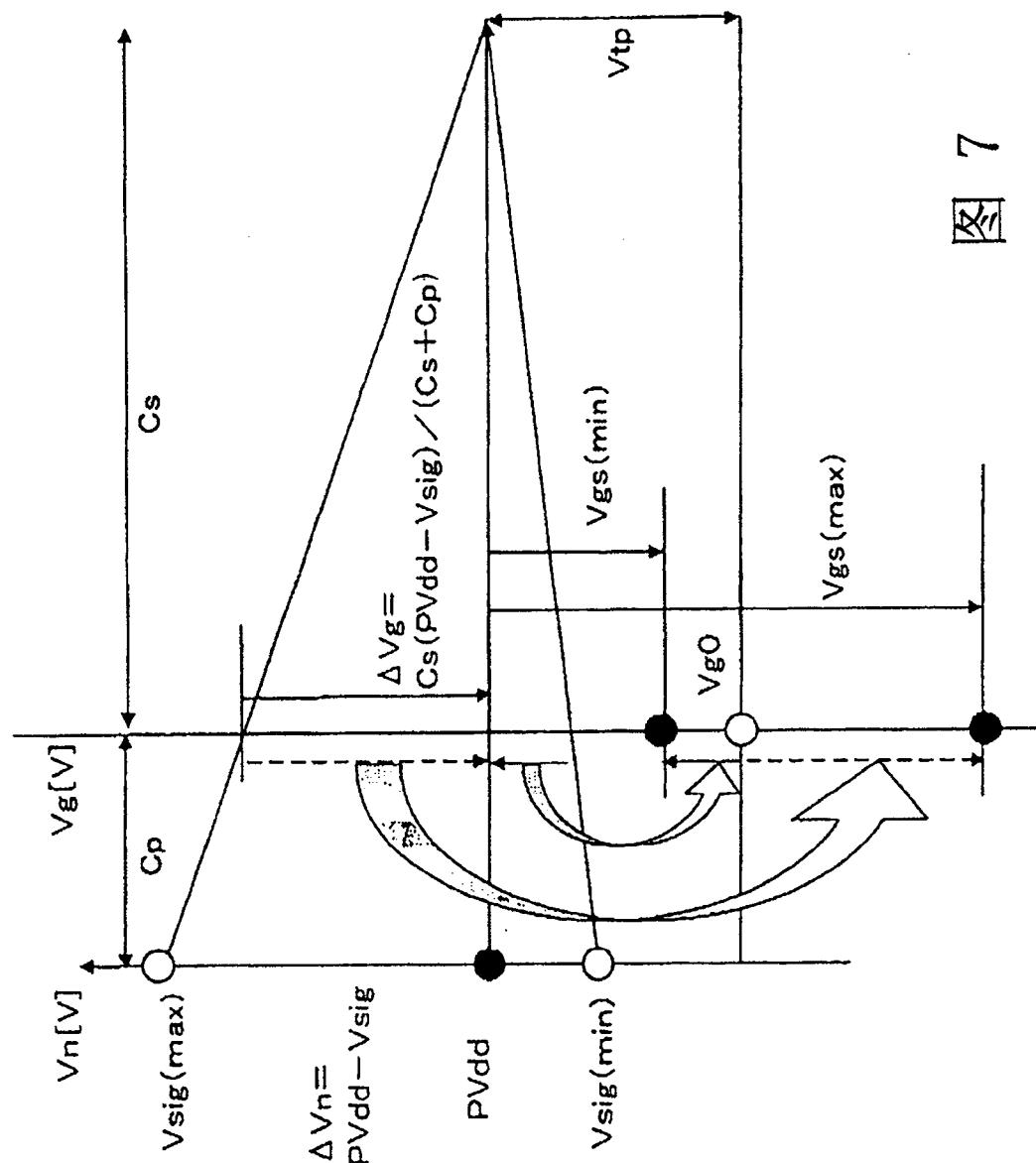

图7为说明从复位起在电位固定步骤中的电位变化的状态图；

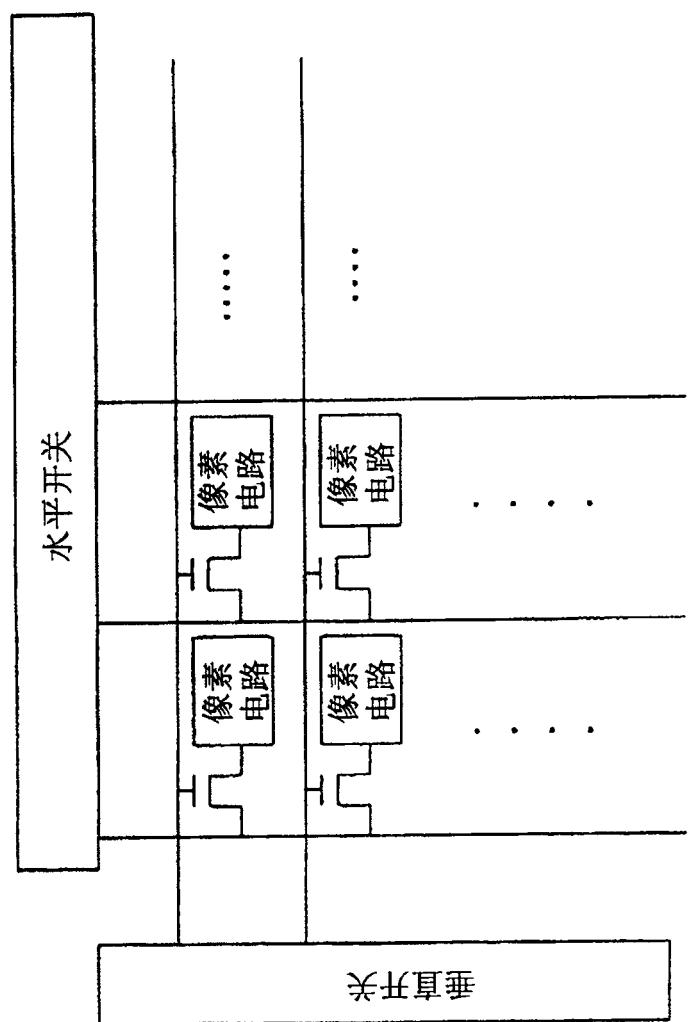

图8为表示面板的整体构成图；

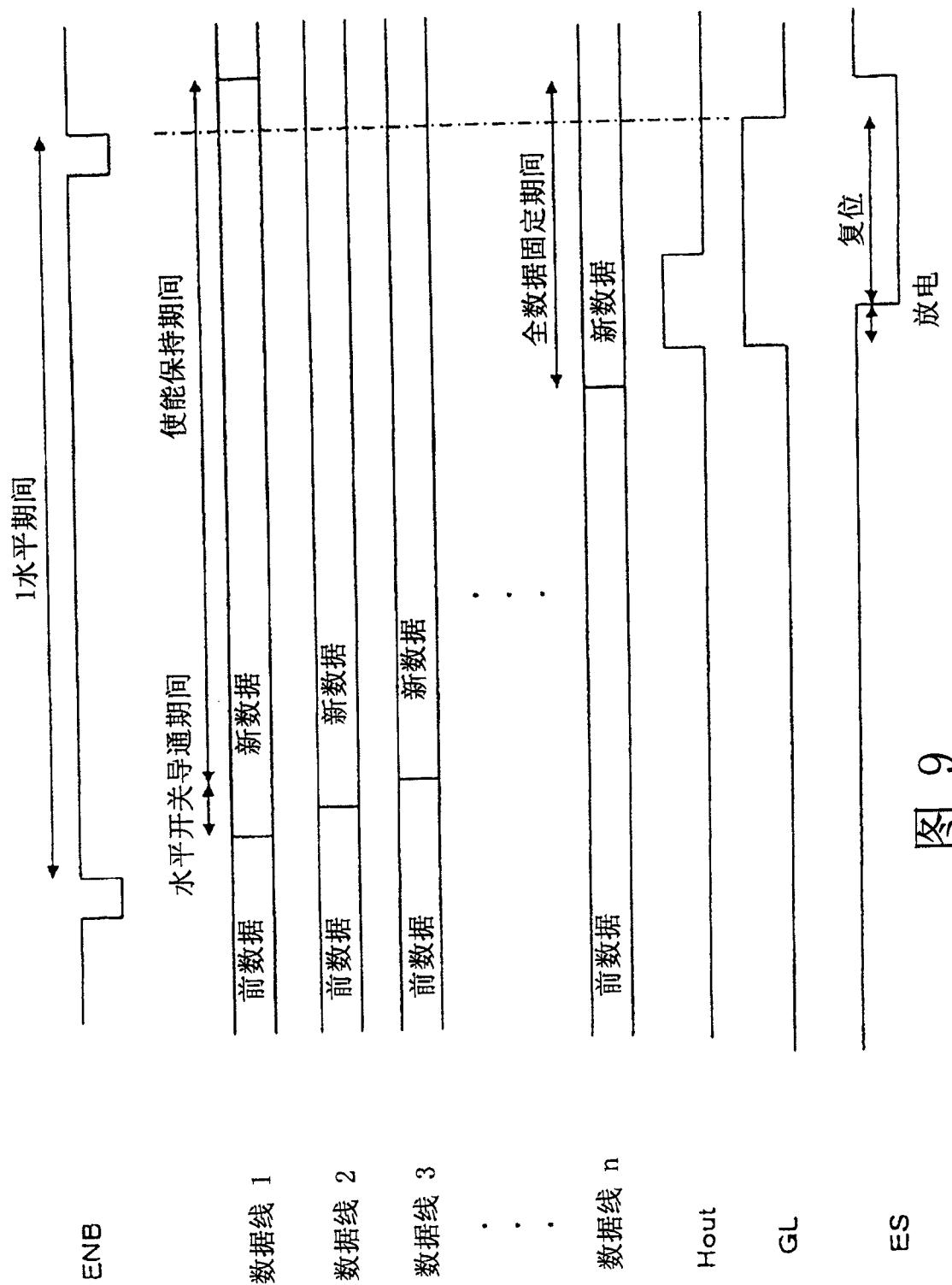

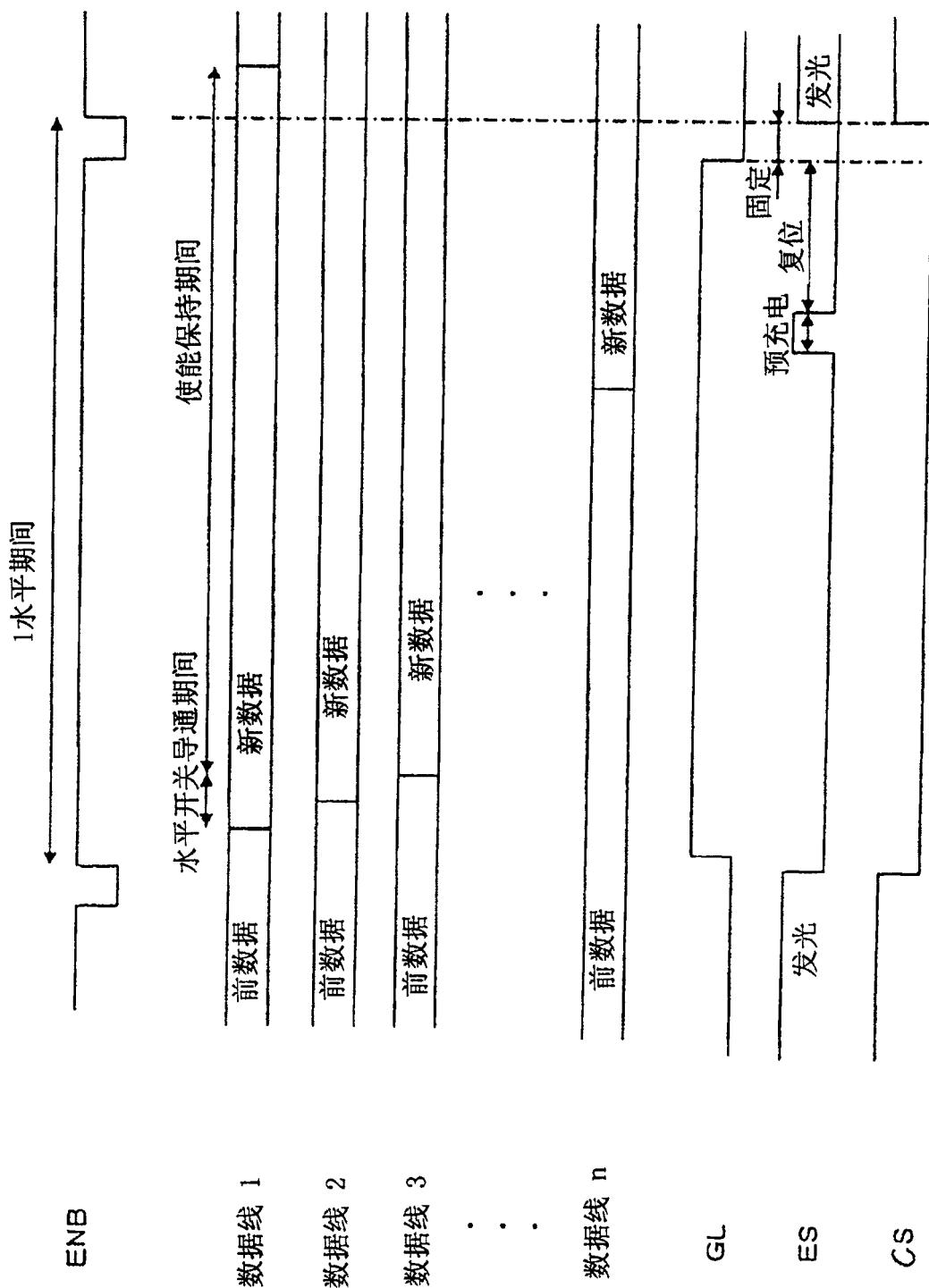

图9为表示数据设定的时序例图；

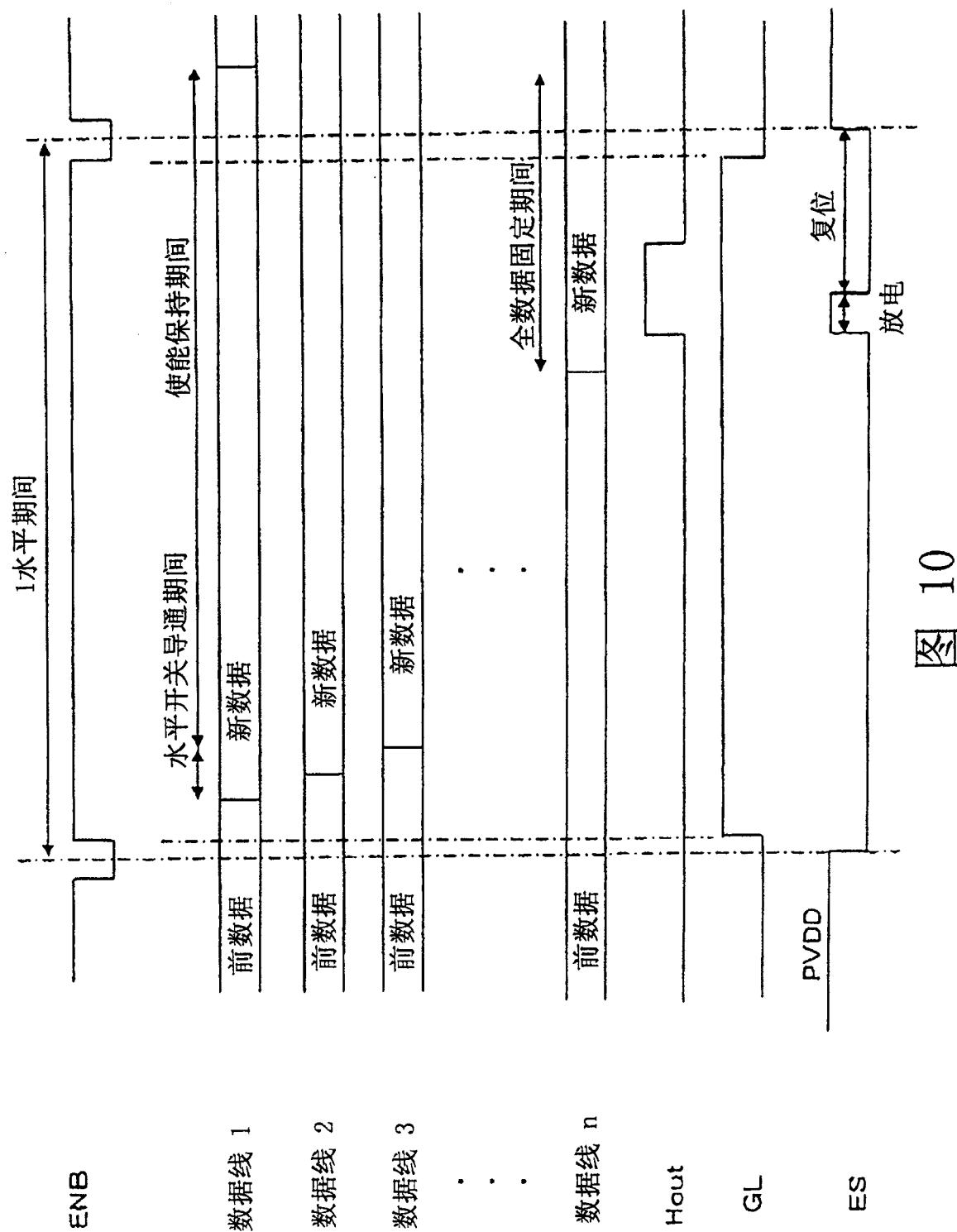

图10为表示数据设置的另一时序例图；

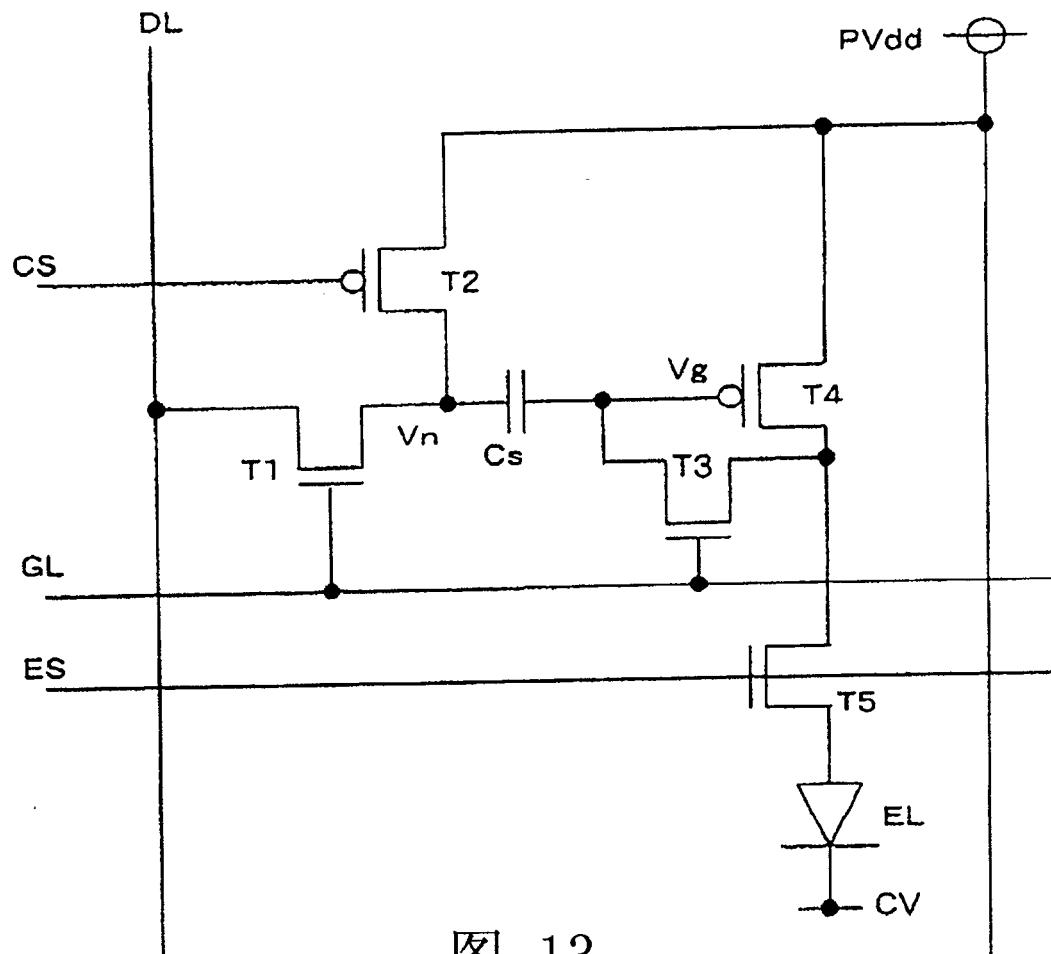

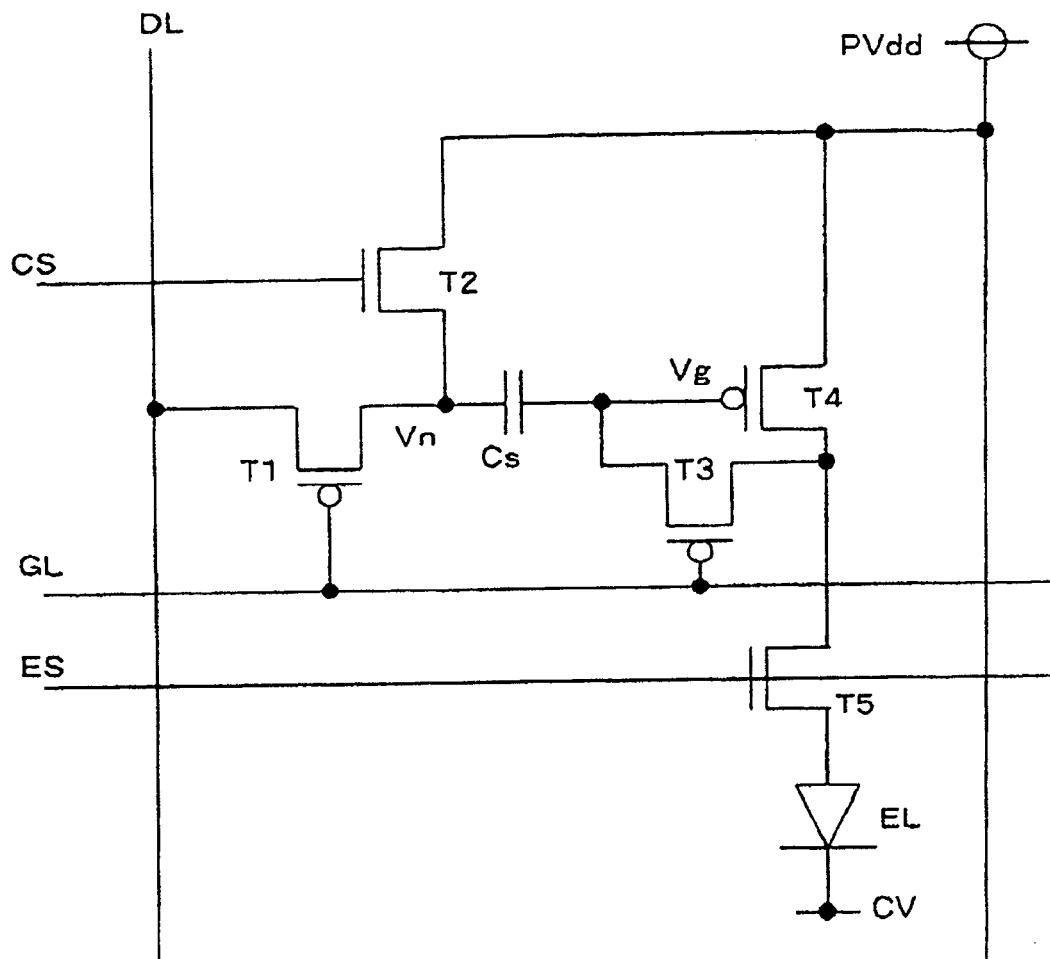

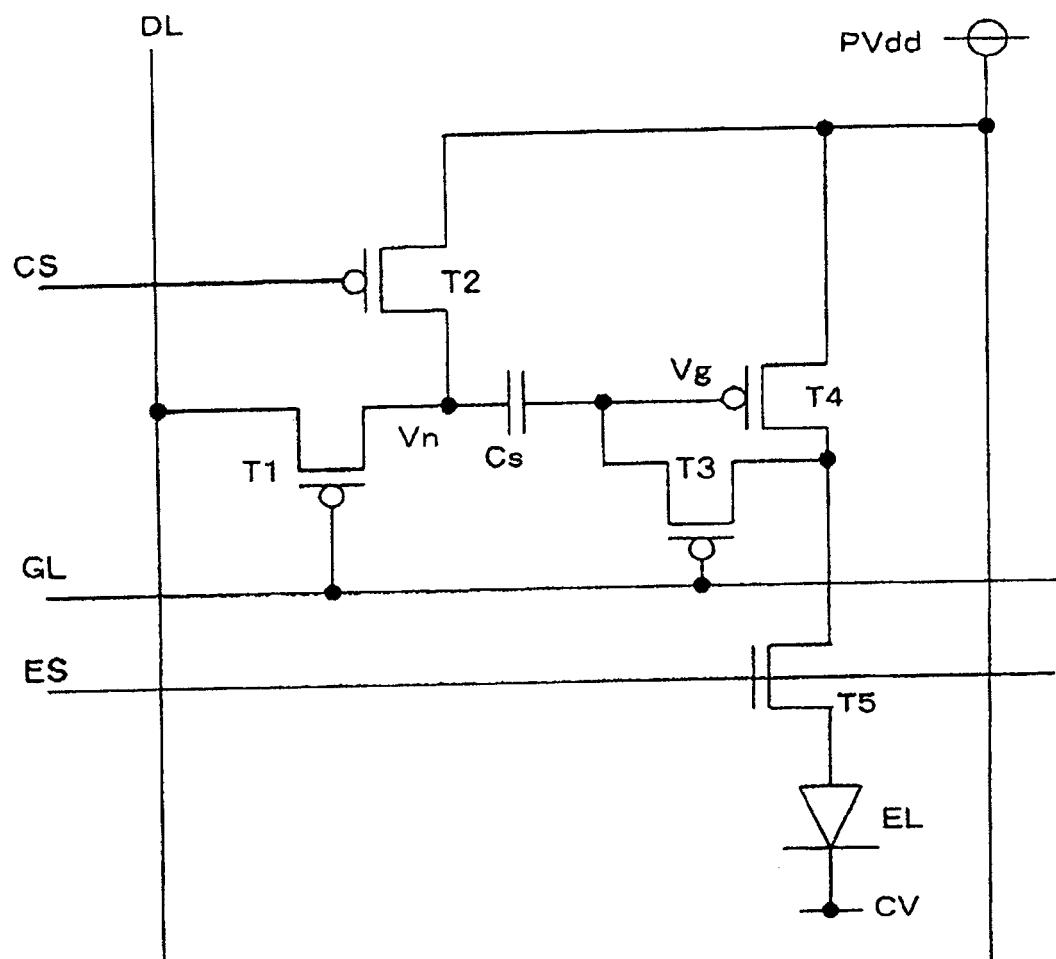

图11为说明变形例1的构成图；

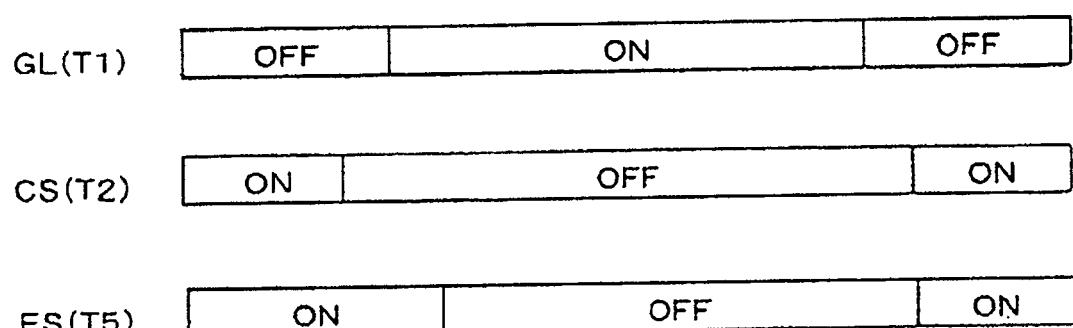

- 图 12 为表示变形例 1 的驱动状态图；

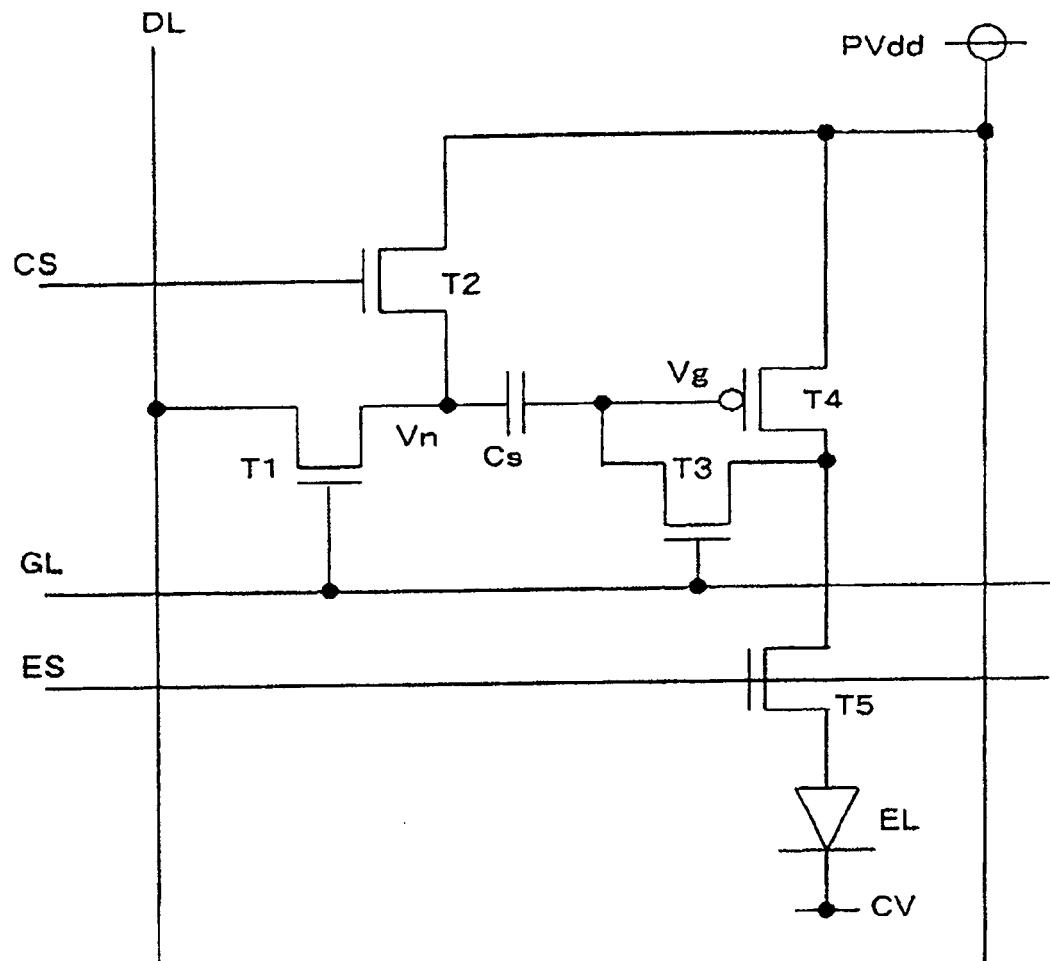

图 13 为说明变形例 2 的构成图；

图 14 为表示变形例 2 的驱动状态图；

图 15 为表示变形例 2 的另一构成图；

图 16 为表示变形例 2 的又一构成图；

图 17 为表示变形例 2 的再一构成图；

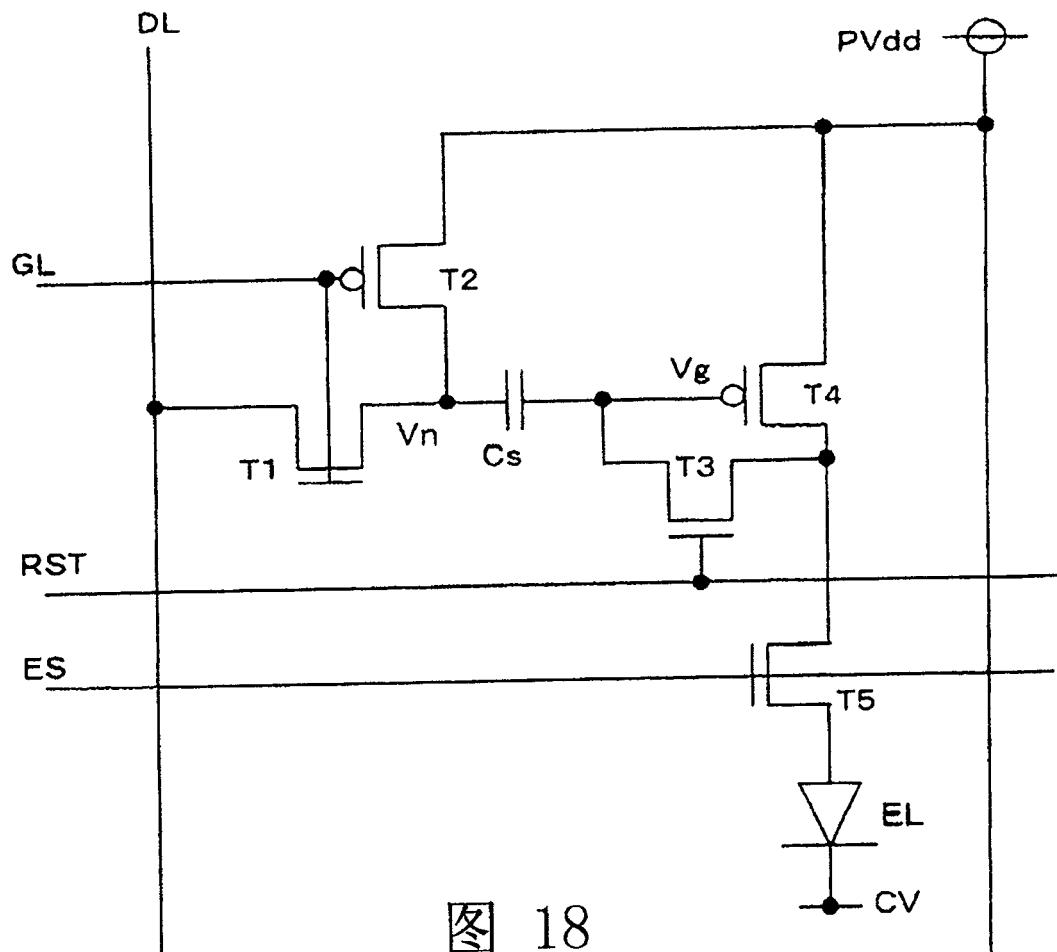

图 18 为表示实施例 3 的构成图；

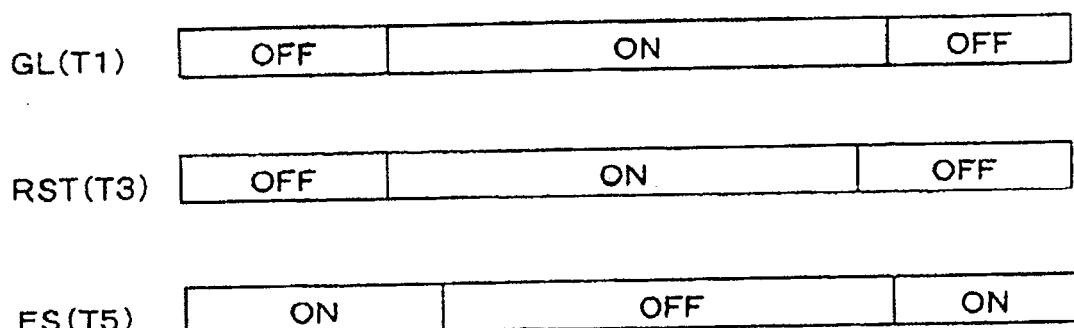

图 19 为表示变形例 3 的驱动状态图；

图 20 为表示变形例 4 的构成图；

图 21 为表示变形例 4 的驱动状态图；

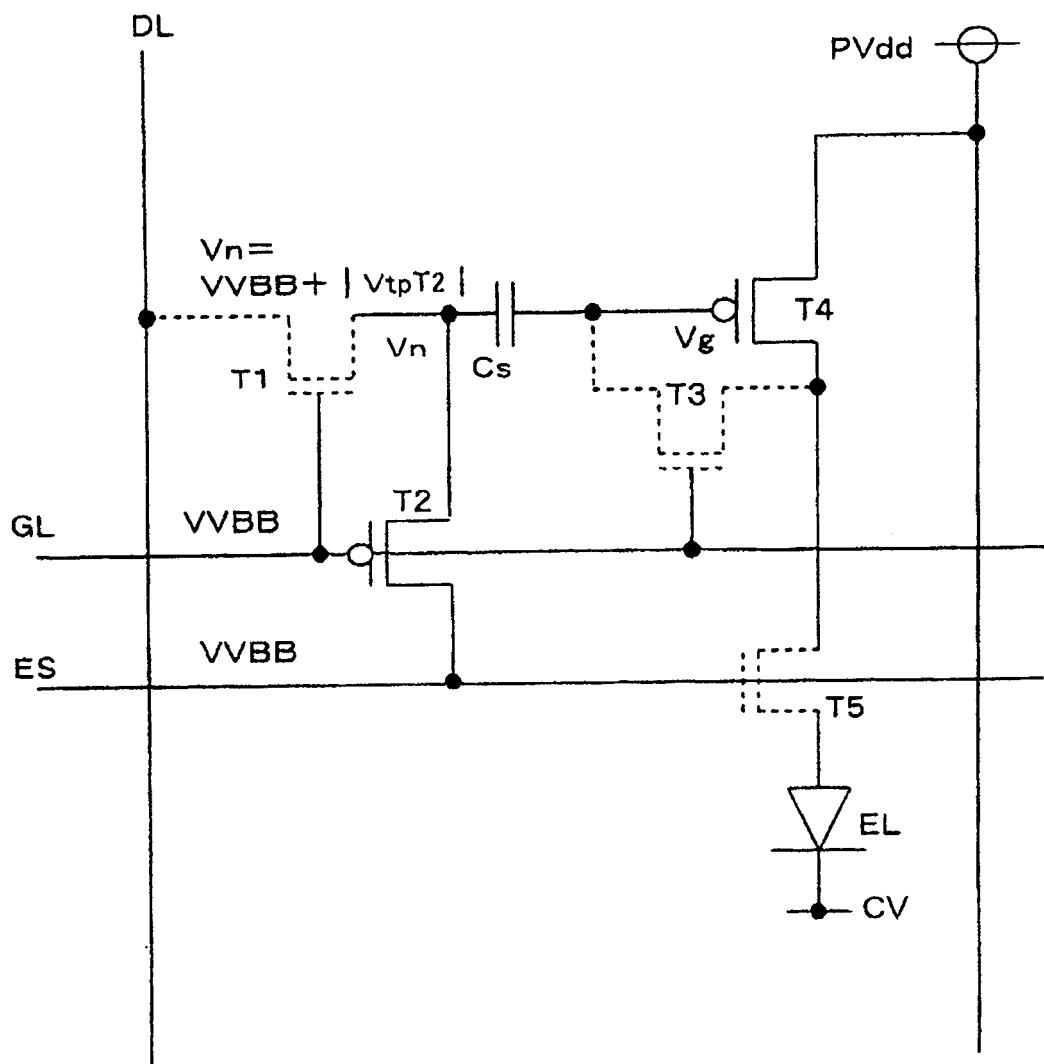

图 22 为表示实施例 5 的像素电路的构成图；

图 23 为说明变形例 5 的放电步骤图；

图 24 为说明变形例 5 的复位步骤图；

图 25 为说明变形例 5 的电位固定步骤图；

图 26 为说明变形例 5 的发光步骤图；

第 27 图为说明变形例 6 的构成图；

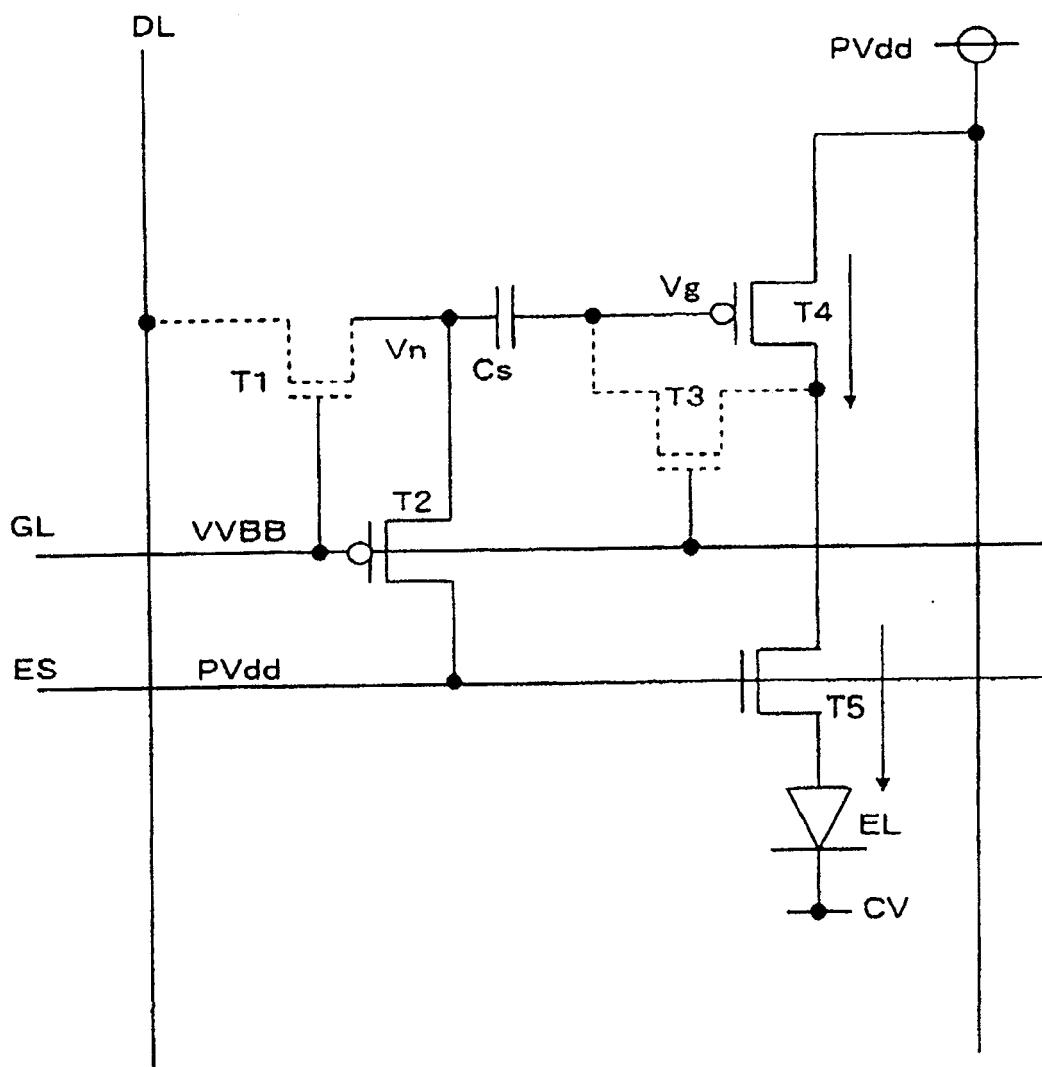

图 28 为表示变形例 7 的像素电路的构成图；

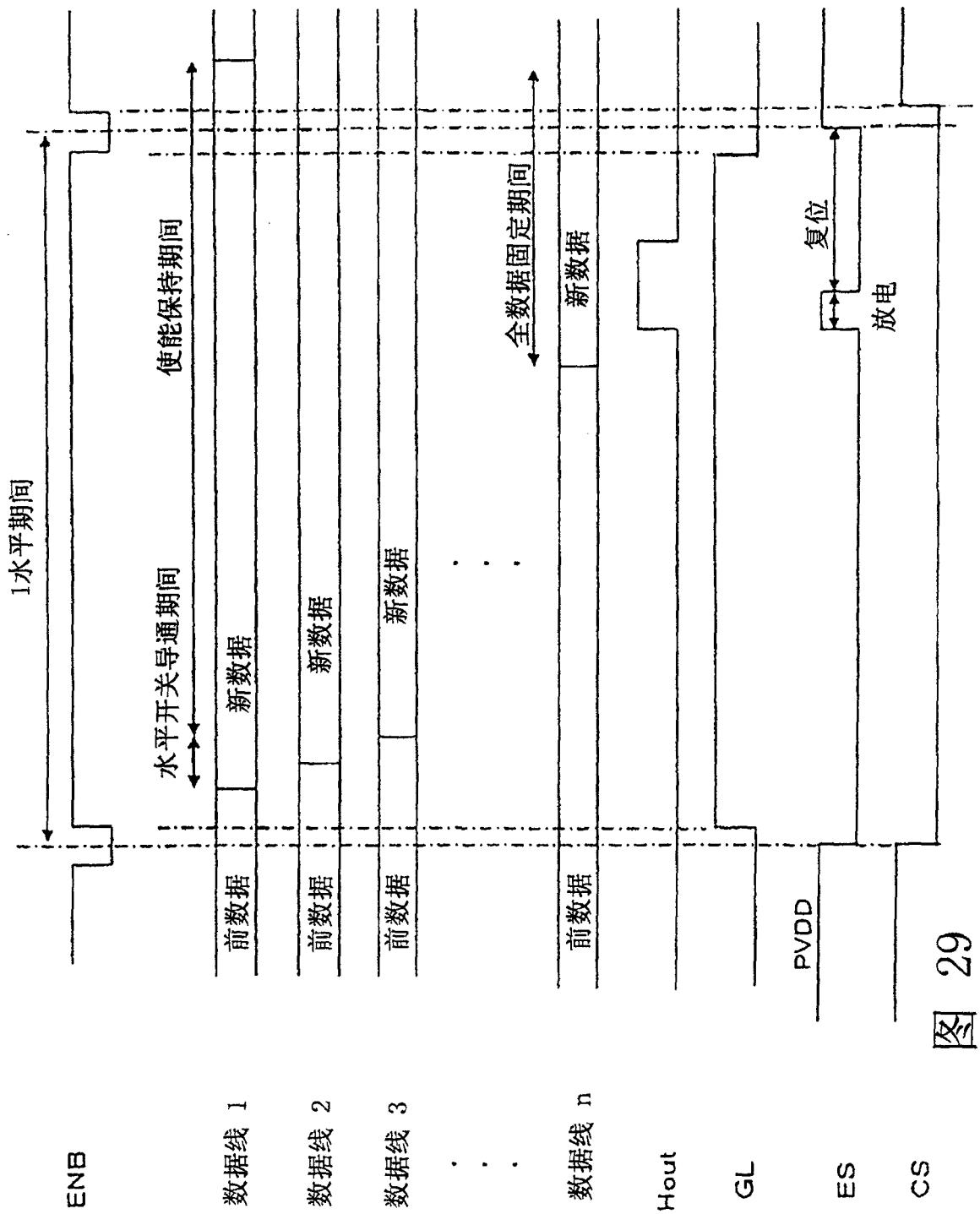

图 29 为说明变形例 7 的动作条图；

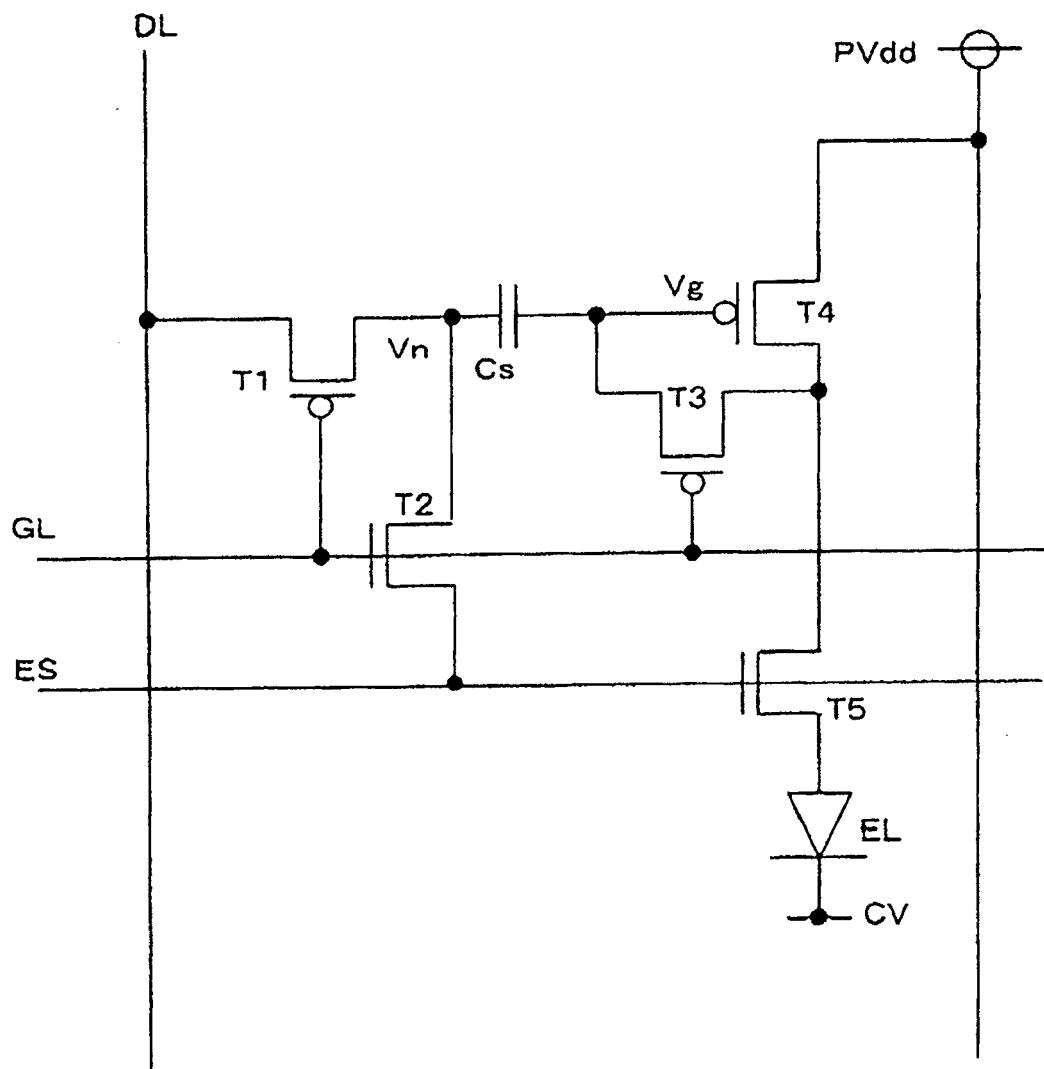

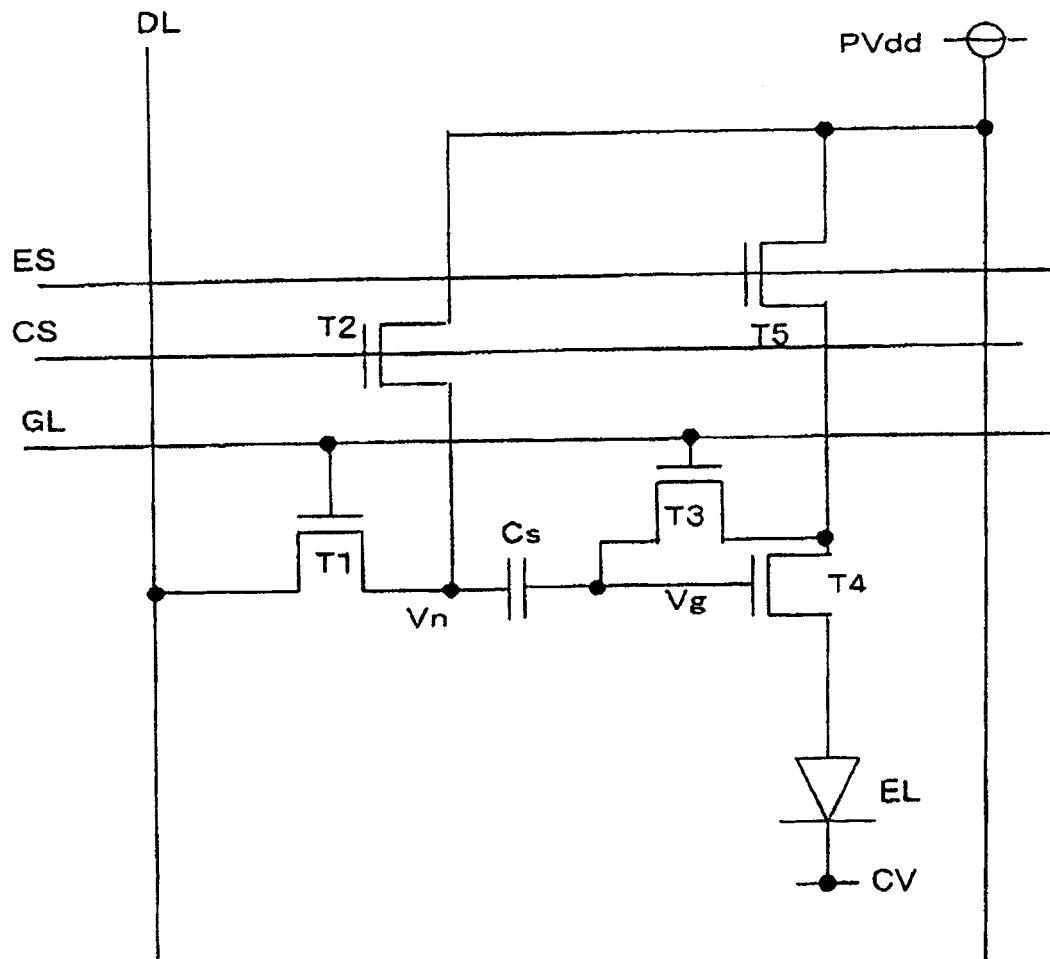

图 30 为表示变形例 8 的像素电路的构成图；

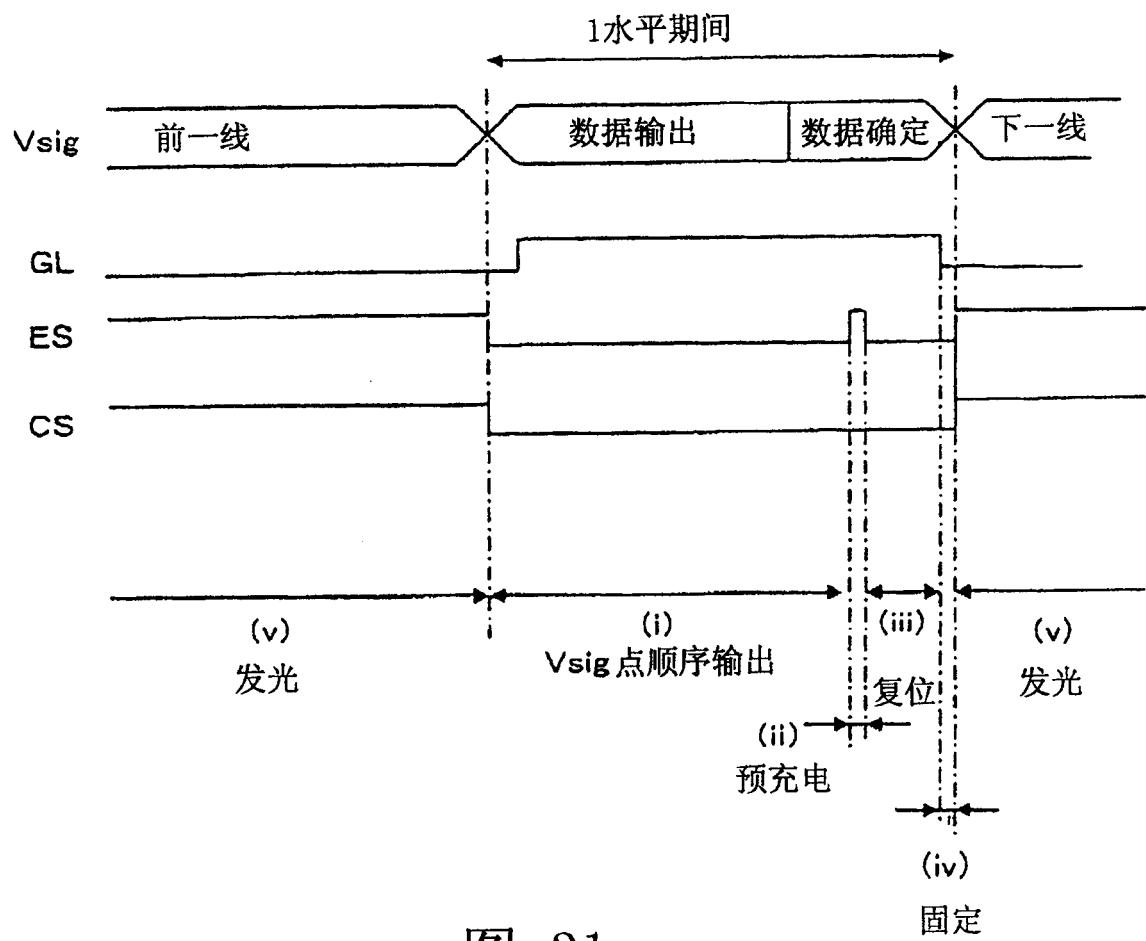

图 31 为说明变形例 8 的动作条图；

图 32 为说明变形例 8 的数据的写入图；

图 33 为说明变形例 8 在发光时的图；

图 34 为表示变形例 8 的数据设定的时序例图；

图 35 为表示变形例 9 的像素电路的构成图。

#### 主要组件符号说明

|                |              |                |          |

|----------------|--------------|----------------|----------|

| C <sub>p</sub> | 寄生电容         | C <sub>s</sub> | 电容器      |

| CS             | 控制线、电容设定线    |                |          |

| CV             | 阴极电源（负电源）    |                |          |

| DL             | 数据线          | EL             | 有机 EL 组件 |

| ENB            | 使能（enable）信号 |                |          |

|      |                    |     |         |

|------|--------------------|-----|---------|

| ES   | 发光设定线              | GL  | 栅极线     |

| Gl   | 栅极长度               | Gw  | 栅极宽度    |

| HSR  | 水平开关电路             |     |         |

| PVdd | 电源线（正电源）、电源电压、电源电位 |     |         |

| RST  | 复位线                | T1  | 选择晶体管   |

| T2   | 电位控制晶体管            | T3  | 短路晶体管   |

| T4   | 驱动晶体管              | T5  | 驱动控制晶体管 |

| TFT  | 薄膜晶体管              | Ve  | 阈值电压    |

| Vg   | 栅极电压、栅极电位          |     |         |

| Vgs  | 栅极源极间电压            |     |         |

| Vn   | 选择晶体管              | T1  | 侧的电压    |

| VSR  | 垂直开关电路             | Vs  | 源极电位    |

| Vsig | 数据电压               | Vtn | 阈值电压    |

| Vtp  | 阈值电压               | μ   | 载流子迁移率， |

| ε    | 介电常数               |     |         |

## 具体实施方式

以下根据图式说明本发明的实施例。

图1为表示实施例的像素电路的构成。数据线DL向垂直方向延伸，且将有关像素的显示辉度的数据信号（数据电压 Vsig）供给至像素电路。数据线D1相对于1列的像素设置1条，且依序将该像素的数据电压 Vsig 供给至垂直方向的像素。

在此，数据线DL连接有n沟道的选择晶体管T1的漏极，而该选择晶体管T1的源极则连接在电容器Cs的一端。选择晶体管T1的栅极连接在向水平方向延伸的栅极线GL。而在此栅极线GL则连接有水平方向的各像素电路的选择晶体管T1的栅极。

在此，栅极线GL连接有p沟道的电位控制晶体管T2的栅极。因此，在选择晶体管T1为导通（ON）时，电位控制晶体管T2即截止（OFF），而选择晶体管T1为截止时，电位控制晶体管T2即导通。电位控制晶体管T2的源极连接在电源线（正电源）PVdd，而漏极则连接在电容器Cs与选择晶体管T1的源极。另外，电源线PVdd也向垂

直方向延伸，将电源电压 PVdd 供给至垂直方向的各像素。

电容器 Cs 的另一端连接在 p 沟道的驱动晶体管 T4 的栅极。而驱动晶体管 T4 的源极则连接在电源线 PVdd，漏极则连接在 n 沟道的驱动控制晶体管 T5 的漏极。驱动控制晶体管 T5 的源极连接在有机 EL 组件 EL 的阳极，而栅极则连接在向水平方向延伸的发光设定线 ES。而且，有机 EL 组件 EL 的阴极连接在低电压的阴极电源(负电源)CV。

此外，在驱动晶体管 T4 的栅极连接有 n 沟道的短路晶体管 T3 的漏极，而该短路晶体管 T3 的源极连接在驱动晶体管 T4，而栅极则连接在栅极线 GL。

如此，在本实施例中，向垂直方向配置有数据线 DL、电源线 PVdd，且向水平方向配置有栅极线 GL、发光设定线 ES。

其次，说明此像素电路的动作。

如图 2 所示，此像素电路与栅极线 GL、发光设定线 ES 的状态(高(H)电位、低(L)电位)对应，具有(i)放电(discharge)(GL=H 电位，ES=H 电位)、(ii)复位(reset)(GL=H 电位，ES=L 电位)、(iii)电位固定(GL=L 电位，ES=L 电位)、(iv)发光(GL=L 电位，ES=H 电位)等 4 个状态，且重复此 4 个状态。换言之，在使数据线 DL 的数据有效状态下，(i)进行放电，之后，(ii)通过复位(reset)，决定电容器 Cs 的充电电压，在(iii)将栅极电压 Vg 固定，(iv)并以与被固定的栅极电压对应的驱动电流使有机 EL 组件 EL 发光。

并且，数据线 DL 的数据如图所示，在(i)放电步骤之前为有效，在(iii)固定步骤之后为无效。因此，从(i)放电步骤起至(iii)固定步骤为止在数据线设定有效数据。

以下说明个别的状态。另外，在图 3 至图 6 中以虚线表示截止(OFF)的晶体管。

(i) 放电(GL=H 电位，ES=H 电位)

首先，在对于数据线 DL 供给数据电压 Vsig 的状态下，将栅极线 GL、发光设定线 ES 两方设为 H 电位(高电位)。藉此，选择晶体管 T1、驱动控制晶体管 T5、短路晶体管 T3 即导通，而电位控制晶体管 T2 即截止。因此，如图 3 所示，在电容器 Cs 的选择晶体管 T1 侧的电压 Vn=Vsig 的状态下，来自电源线 PVdd 的电流即经由驱动晶体管 T4、

驱动控制晶体管 T5、有机 EL 组件 EL 流通于阴极电源 CV，且由此使保持在驱动晶体管 T4 的栅极的电荷被汲出。藉此，驱动晶体管 T4 的栅极电压  $V_g$  即成为预定的低电压。

(ii) 复位 (GL=H 电位, ES=L 电位)

从上述放电的状态，将发光设定线 ES 变更为 L 电位 (低电位)。藉此，如图 4 所示，驱动控制晶体管 T5 即截止，被复位为驱动晶体管 T4 的栅极电压  $V_g=V_{g0}=PV_{dd}-|V_{tp}|$ 。在此，该  $V_{tp}$  为驱动晶体管 T4 的阈值电压。即，驱动晶体管 T4 在源极连接于电源 PVdd 的状态下，通过短路晶体管 T3，使栅极漏极间短路，因此该驱动晶体管 T4 的栅极电压被复位为比电源 PVdd 仅低驱动晶体管 T4 的阈值电压  $|V_{tp}|$  的电压后被截止。此时电容器 Cs 的选择晶体管 T1 侧的电位  $V_n=V_{sig}$ ，至于电容器 Cs 则对其充电至  $|V_{sig}-(PV_{dd}-|V_{tp}|)|$  的电压。

(iii) 电位固定 (栅极线 GL=L 电位, ES=L 电位)

然后，将栅极线 GL 设为 L 电位，使选择晶体管 T1、短路晶体管 T3 截止 (off)，且使电位控制晶体管 T2 导通 (on)。藉此，如图 5 所示，驱动晶体管 T4 的栅极即从漏极被切离。然后，由于电位控制晶体管 T2 导通，而成为  $V_n=PV_{dd}$ 。因此，驱动晶体管 T4 的栅极电位  $V_g$ ，与  $V_n$  的变化对应而位移。另外，在驱动晶体管 T4 的栅极与源极之间，由于存在有寄生电容  $C_p$ ，因此栅极电位  $V_g$  会受到该寄生电容  $C_p$  的影响。

(iv) 发光 (GL=L 电位, ES=H 电位)

接着，如图 6 所示，通过将发光设定线 ES 设为 H 电位，使驱动控制晶体管 T5 导通，且由此使来自驱动晶体管 T4 的驱动电流流通于有机 EL 组件 EL。此时的驱动电流虽会成为由驱动晶体管 T4 的栅极电压所决定的驱动晶体管 T4 的漏极电流，然而此漏极电流与驱动晶体管 T4 的阈值电压  $V_{tp}$  将变成无关，因而可抑制随阈值电压的变动所产生发光量的变动。

现根据图 7 说明此情况。

如上所述，(ii) 复位后，如图中○所示， $V_n (=V_{sig})$  为  $V_{sig} (\max)$  至  $V_{sig} (\min)$  之间的值， $V_g$  是从  $PV_{dd}$  仅减去驱动晶体管 T4 的阈值电压  $V_{tp}$  的电压  $V_{g0}$ 。即， $V_g=V_{g0}=PV_{dd}+V_{tp}$  ( $V_{tp}<0$ )、 $V_n=V_{sig}$ 。

再者，进入(iii)的电位固定时， $V_n$ 从 $V_{sig}$ 变化至 $PV_{dd}$ ，因此该变化量 $\Delta V_g$ 考虑 $C_s$ 、 $C_p$ 的电容，而表示成 $\Delta V_g = PV_{dd} + C_s (PV_{dd} - V_{sig}) / (C_s + C_p)$ 。

因此， $V_n$ 、 $V_g$ 如图中●所示，为 $V_n = PV_{dd}$ ， $V_g = V_{tp} + \Delta V_g = PV_{dd} + V_{tp} + C_s (PV_{dd} - V_{sig}) / (C_s + C_p)$ 。

在此，由于 $V_{gs} = V_g - PV_{dd}$ ，因此 $V_{gs} = V_{tp} + C_s (PV_{dd} - V_{sig}) / (C_s + C_p)$ 。

另一方面，漏极电流 $I$ 表示成 $I = (1/2) \beta (V_{gs} - V_{tp})^2$ ，将上式代入，漏极电流 $I$ 即以下式表示。

$$\begin{aligned} I &= (1/2) \beta \{V_{tp} + C_s (PV_{dd} - V_{sig}) / (C_s + C_p) - V_{tp}\}^2 \\ &= (1/2) \beta \{C_s (PV_{dd} - V_{sig}) / (C_s + C_p)\}^2 \\ &= (1/2) \beta \alpha (V_{sig} - PV_{dd})^2 \end{aligned}$$

在此， $\alpha = \{C_s / (C_s + C_p)\}^2$ ， $\beta$ 为驱动晶体管T4放大率，且 $\beta = \mu \epsilon G_w / G_1$ ，

$\mu$ 为载流子的迁移率， $\epsilon$ 为介电常数， $G_w$ 为栅极宽度， $G_1$ 为栅极长度。

如此，在漏极电流 $I$ 的式中，不包括 $V_{tp}$ ，而与 $V_{sig} - PV_{dd}$ 的2次乘方成比例。因此，可排除驱动晶体管T4的阈值电压的不均的影响，而达成与数据电压 $V_{sig}$ 对应的发光。

在上述说明中，仅说明关于1个像素的动作。实际上，显示面板将像素配置成矩阵状，且供给数据电压 $V_{sig}$ 以使各有机EL组件发光，其中该数据电压 $V_{sig}$ 与关于这些各像素对应的辉度信号对应。即，如图8所示，显示面板设有水平开关电路HSR与垂直开关电路VSR，通过这些电路的输出以控制数据线DL、栅极线GL、其它发光设定线ES等状态。尤其对于水平方向的各像素，使1条栅极线GL与其对应，而该栅极线GL通过垂直开关电路VSR而一个一个地依序被激活。接着，在1条栅极线GL被激活的1水平期间，通过水平开关电路HSR而将数据电压依照点顺序供给至所有的数据线DL，且此为将数据写入1水平线内的像素电路。然后，在各像素电路中即会有与写入到1垂直期间后的数据电压对应的发光。

其次，根据图9说明对于1水平线内的各像素写入数据的顺序。

首先，在用于表示 1 水平期间的开始的使能（enable）信号 ENB 的 L 电位之后，依照点顺序将数据电压 Vsig 写入所有的数据线 DL。即，数据线 DL 连接有电容等，通过设定电压信号，使该数据电压 Vsig 保持在数据线 DL。于是，通过将关于各行像素的数据电压 Vsig 设定在依序对应的数据线 DL，而将数据电压 Vsig 设定在所有的数据线 DL。

然后，在该数据的设定结束的阶段，将 Hout 设为 H 电位，并将栅极线 GL 设为 H 电位而使之被激活，且针对上述 1 水平方向的各像素进行动作，以进行各像素的数据写入、发光。

如此，即可依序将通常的视频信号（数据电压 Vsig）写入数据线 DL，且将该信号设定在像素电路而使其发光。

接着，根据图 10 说明另一方式。在此例中，在使能线 ENB 为 L 电位的期间，将发光设定线 ES 设为 L 电位，且在使能线 ENB 升起至 H 电位时将栅极线 GL 设为 H 电位（被激活）。在此状态下，依序将数据电压 Vsig 设定在数据线 DL。然后，在将数据电压 Vsig 设定在所有的数据线 DL 时，将发光设定线 ES 设为高电位，以进行上述的放电，且在之后将发光设定线 ES 恢复成 L 电位。栅极线 GL 与使能线 ENB 的下降同步恢复成 L 电位，而在使能线 ENB 为 L 电位时则将使能线 ENB 恢复为 H 电位。藉此，进行与上述示例同样的动作。

接着说明各种变形例。

#### (A) 变形例 1

图 11 为表示变形例 1 的构成。在此变形例 1 中将选择晶体管 T1、短路晶体管 T3 设为 p 沟道，且将电位控制晶体管 T2 设为 n 沟道。在此种构成中，通过将栅极线 GL 的 H 电位、L 电位设成与上述实施例相反，而能够使其与实施例同样的动作。

在此变形例 1 中的栅极线 GL、与发光设定线 ES 的控制对应的选 择晶体管 T1、驱动控制晶体管 T5 的导通与截止（on, off），如图 12 所示，与上述的图 2 所示的相同。

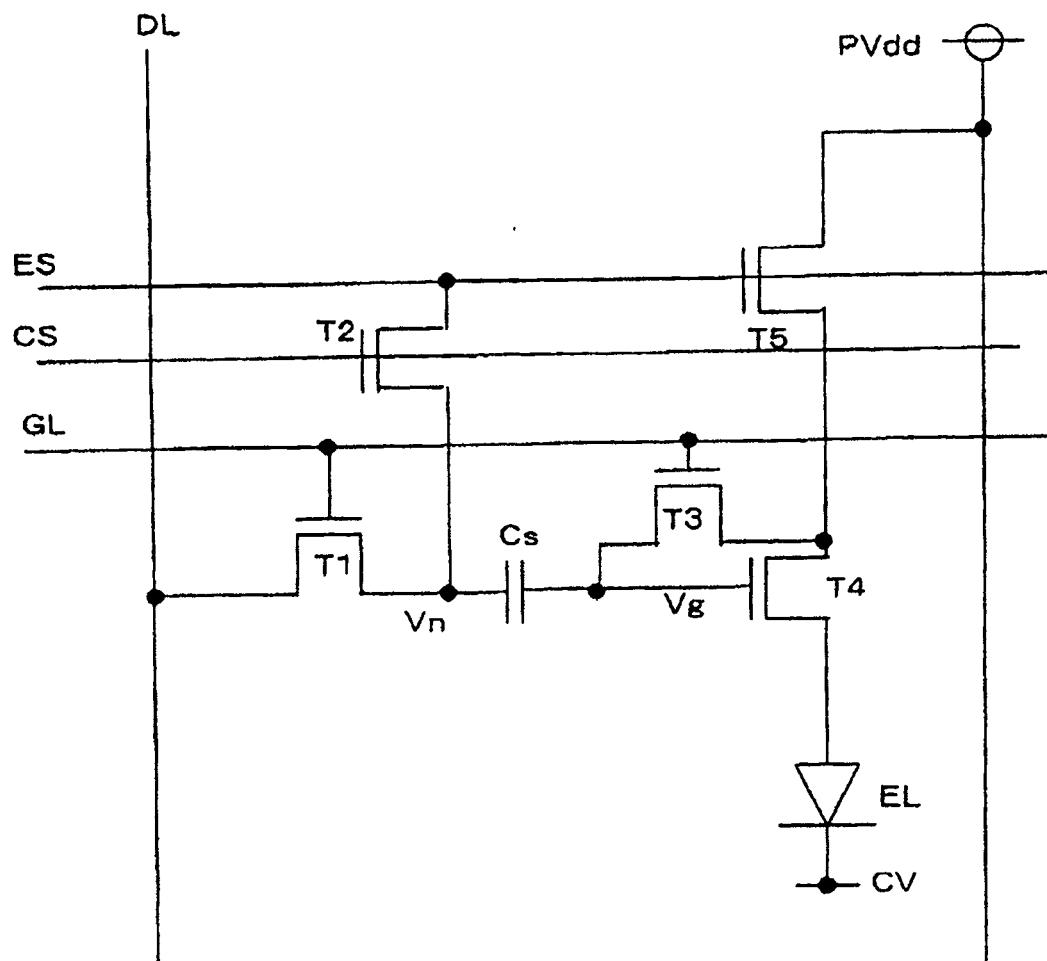

#### (B) 变形例 2

图 13 为表示变形例 2 的构成。在此变形例 2 中，相较于实施例的像素电路，设有专用的控制线 CS 作为控制电位控制晶体管 T2 之用。因此，可通过控制线 CS 而独立控制电位控制晶体管 T2。于是，如图

14 所示，可通过控制线 CS，在选择晶体管 T1 导通之前，使电位控制晶体管 T2 截止，且在选择晶体管 T1 截止之后，与驱动控制晶体管 T5 一同使电位控制晶体管 T2 导通。

依据此种构成，水平方向的线虽将增加，然而可在最适当的时序使电位控制晶体管 T2 导通截止。即，可确实消除短路晶体管 T3 与电位控制晶体管 T2 的同时导通的期间，且可予以正确的固定栅极电位，而使修正精确度提升。

另外，图 15 是相对于图 13 将电位控制晶体管 T2 设为 n 沟道的例子，图 16 是将选择晶体管 T1、短路晶体管 T3 设为 p 沟道，将电位控制晶体管 T2 设为 n 沟道的例子，图 17 是将选择晶体管 T1、短路晶体管 T3、电位控制晶体管 T2 均设为 p 沟道的例子。

#### (C) 变形例 3

图 18 为另一变形示例，将选择晶体管 T1、电位控制晶体管 T2 连接于栅极线 GL，且设置专用的设定线 RST，并将此设定线 RST 连接于短路晶体管 T3。在此构成中，如图 19 所示，可通过设定线 RST，在选择晶体管 T1 的截止及驱动控制晶体管 T5 的导通之前，先使短路晶体管 T3 截止。

因此，可与变形例 2 同样，消除电位控制晶体管 T2、短路晶体管 T3 的同时导通期间。通过此种构成，配置在栅极线 GL 附近的晶体管，只要选择晶体管 T1、电位控制晶体管 T2 两个即可，而晶体管在像素电路中的布局 (layout) 即变得容易。然而，此时选择晶体管 T1、短路晶体管 T3 的截止时序将偏移，而有可能于此时在 Vg 产生噪声。

#### (D) 变形例 4

图 20 为又一变形示例。在此例中，将选择晶体管 T1、电位控制晶体管 T2 连接在栅极线 GL，且将短路晶体管 T3、驱动控制晶体管 T5 连接在发光设定线 ES。在此例中，如图 21 所示，从发光状态起，栅极线 GL 成为 H 电位，电位控制晶体管 T2 成为截止，选择晶体管 T1 成为导通，而将数据电压 Vsig 供给至电容器 Cs 的一端。此时短路晶体管 T3 即截止，而驱动控制晶体管 T5 成呈导通。接下来，发光设定线 ES 成为 L 电位，短路晶体管 T3 成为导通，驱动控制晶体管 T5 成为截止。直到之前瞬间电流均流动于有机 EL 组件 EL，而驱动晶体管

T4 的漏极成为较低的电压，通过短路晶体管 T3 导通，而进行在 Vg 设定成 PVdd+Vtp 的值的复位。之后，发光设定线 ES 即成为 H 电位，而在短路晶体管 T3 截止，驱动控制晶体管 T5 导通的阶段，栅极线 GL 即成为 H 电位，进行电位的固定及发光。

依据此变形例 4，通过在栅极线 GL 的附近配置选择晶体管 T1、电位控制晶体管 T2，且于发光设定线 ES 的附近配置短路晶体管 T3、驱动控制晶体管 T5，配线的布线即变得非常容易。因此，像素电路的布局即变得容易。然而，由于选择晶体管 T1 与短路晶体管 T3 的时序偏移，因此也有噪声容易随之产生的缺点。再者，由于无法设置如其它构成例的放电步骤，因此也会有无法充分进行关于驱动晶体管 T4 的栅极的电荷的释放。

#### (E) 变形例 5

图 22 为又一变形例。在此例中，将电位控制晶体管 T2 连接在发光设定线 ES 而非电源 PVdd。即，在上述实施例中，虽通过电位控制晶体管 T2 将电容 Cs 的选择晶体管 T1 侧与电源 PVdd 作连接，然而在此例中则是将电容 Cs 的选择晶体管 T1 侧连接在发光设定线 ES。此发光设定线 ES 在 L 电位时设定为 VVBB，且在 H 电位时设定为 PVdd。于是，在此电路中，也可获得与上述电路同样的动作。另外，为了达成上述的动作，由电位控制晶体管 T2 所连接的电容 Cs 的选择晶体管 T1 侧的对象，并不以电源 PVdd 为限。即，针对驱动晶体管 T4，只要可获得适当的位移量，也可为其它电压的电源。

以下说明此变形例 5 的各状态。

##### (i) 放电 (GL=H, ES=H)

首先，在对于数据线 DL 供给数据电压 Vsig 的状态下，将栅极线 GL、发光设定线 ES 两方设为 H 电位（高电位）。藉此，选择晶体管 T1、驱动控制晶体管 T5、短路晶体管 T3 即导通，而电位控制晶体管 T2 即截止。因此，如图 23 所示，在电容器 Cs 的选择晶体管 T1 侧的电压 Vn=Vsig 的状态下，来自电源线 PVdd 的电流即经由驱动晶体管 T4、驱动控制晶体管 T5、有机 EL 组件 EL 流通至阴极电源 CV，且由此使保持在驱动晶体管 T4 的栅极的电荷被汲出。藉此，驱动晶体管 T4 的栅极电压 Vg 即成为预定的低电压。

(ii) 复位 (reset) (GL=H, ES=L)

从上述放电的状态, 将发光设定线 ES 变更为 L 电位 (低电位)。

藉此, 如图 24 所示, 驱动控制晶体管 T5 即截止, 被复位为驱动晶体管 T4 的栅极电压  $Vg=Vg0=PVdd - |Vtp|$ 。在此, 该  $Vtp$  为驱动晶体管 T4 的阈值电压。即, 驱动晶体管 T4 在源极连接在电源 PVdd 的状态下, 通过短路晶体管 T3, 使栅极漏极间短路, 因此该驱动晶体管 T4 的栅极电压被复位为比电源 PVdd 仅低驱动晶体管 T4 的阈值电压  $|Vtp|$  的电压后被截止。此时电容器  $Cs$  的选择晶体管 T1 侧的电位  $Vn=Vs$ , 至于电容器  $Cs$  则对其充电至  $|Vs-V(Vd-PVdd - |Vtp|)|$  的电压。

(iii) 电位固定 (GL=L, ES=L)

其次, 将栅极线 GL 设为 L 电位, 使选择晶体管 T1、短路晶体管 T3 截止 (不导通), 且使电位控制晶体管 T2 导通。此时, 发光设定线 ES 的电压为 L 电位, 被设定成与栅极线 GL 的 L 电位的电压 VVBB 相同的电压。因此,  $Vs > Vn > VVBB$ , 如果选择晶体管 T1 未成为截止 (不导通), 则电位控制晶体管 T2 不会导通。如此, 在选择晶体管 T1 截止至后, 由于电位控制晶体管 T2 导通, 因此充电至电容器  $Cs$  的电压即被维持, 而数据电压不会被破坏。

然后, 通过选择晶体管 T1 截止, 电位控制晶体管 T2 导通, 如图 25 所示, 驱动晶体管 T4 的栅极即从漏极被切离, 且通过一方电位控制晶体管 T2 导通,  $Vn$  即成为发光设定线  $ES=VVBB + |VtpT2|$ 。

(iv) 发光 (GL=L, ES=H)

其次, 如图 26 所示, 通过将发光设定线 ES 设为 H 电位, 使驱动控制晶体管 T5 导通。而且, 通过将发光设定线 ES 的电位设定为 PVdd, 驱动晶体管 T4 的栅极电位即仅位移  $PVdd - VVBB + |VtpT2|$ 。另外, 此时的电压位移量会受到驱动晶体管 T4 的栅极电容  $Cp$  的影响。

如此, 电压即位移, 且由于驱动控制晶体管 T5 导通而使来自驱动晶体管 T4 的驱动电流流动于有机 EL 组件 EL。此时的驱动电流虽会成为由驱动晶体管 T4 的栅极电压所决定的驱动晶体管 T4 的漏极电流, 然而此漏极电流与驱动晶体管 T4 的阈值电压  $Vtp$  将变成无关, 而可抑制随阈值电压的变动所产生发光量的变动。

并且，电位控制晶体管 T2 的漏极连接在发光设定线 ES。此发光设定线 ES 虽在 H 电位时设定为电源电压 PVdd，然而此发光设定线 ES 与用于将电流供给至有机 EL 组件 EL 的电源供给线 PVdd 各自独立地接收电源电压 PVdd 的供给。因此，由于各像素的有机 EL 组件 EL 的驱动电流，而使发光设定线 ES 的电压几乎不会变动。因此，可防止经由电位控制晶体管 T2 供给至电容器 Cs 一端的位移用的电压变动而使显示被扰乱的情况。

例如，电压位移量  $\Delta Vg$  如后述所示，表示成  $\Delta Vg = CS (Vsig - PVdd) / (Cs + Cp)$ ，包括有 PVdd。因此，当 PVdd 变动时， $\Delta Vg$  虽变化，然而在本实施例中会使该变化受到抑制。尤其在像素数增加时，该 PVdd 的变化，虽会成为串扰 (crosstalk) 或辉度斜率产生的原因，然而依据本实施例，可抑制对于这些显示所造成的影响。

#### (F) 变形例 6

图 27 为表示变形例 6 的构成。此例基本上虽与变形例 5 相同，然而是将选择晶体管 T1、短路晶体管 T3 设为 p 沟道，且将电位控制晶体管 T2 设为 n 沟道。在此种构成中，通过将栅极线 GL 的 H、L 设成与上述变形例 5 相反，而能够使其与实施例同样的动作。

#### (G) 变形例 7

图 28 为表示变形例 7 的构成。在此变形例 7 中，将电容设定线 CS 连接在电位控制晶体管 T2 的栅极。此外，在此例中，将电位控制晶体管 T2 设为 n 沟道晶体管。如此，具有作为导通截止电位控制晶体管 T2 之用的专用线的电容设定线 CS。然后，如图 29 所示，将该电容设定线 CS 设为 H 电位=VVDD、L 电位=VVBB。可防止电压 Vn 电位的一度下降。即在图 22 等的实施例中，由于栅极线 GL 与电容设定线 CS 为共享，发光线 ES 非以 L 电位的时序闭合 (close) 栅极线 GL 不可，而电压 Vn 则依  $Vsig \rightarrow VVBB + | VtpT2 | \rightarrow PVDD$  的方式变化。

在变形例 7 中，由于可将栅极线 GL 与电容设定线 CS 与发光线 ES 的时序个别设定，如图 29 所示，若在发光线 ES 成为 H 电位后使电容设定线 CS 导通，电压 Vn 不会一度下降而直接变化成 PVDD，可进行更稳定地动作。

另外，在上述实施例中，各种的电压最好设定成如下所示。即可

将电源线 PVdd 设定为 PVdd, 发光设定线 ES 设定为 H 电位=PVdd, L 电位=VVBB, 栅极线 GL 设定为 H 电位=VVDD, L 电位=VVBB, 电容设定线 Cs 设定为 H 电位=VVDD, L 电位=VVBB, 阴极电源 CV=CV, PVdd=8V, VVDD=10V, VVBB=-2V、CV=-2V 程度。

#### (H) 变形例 8

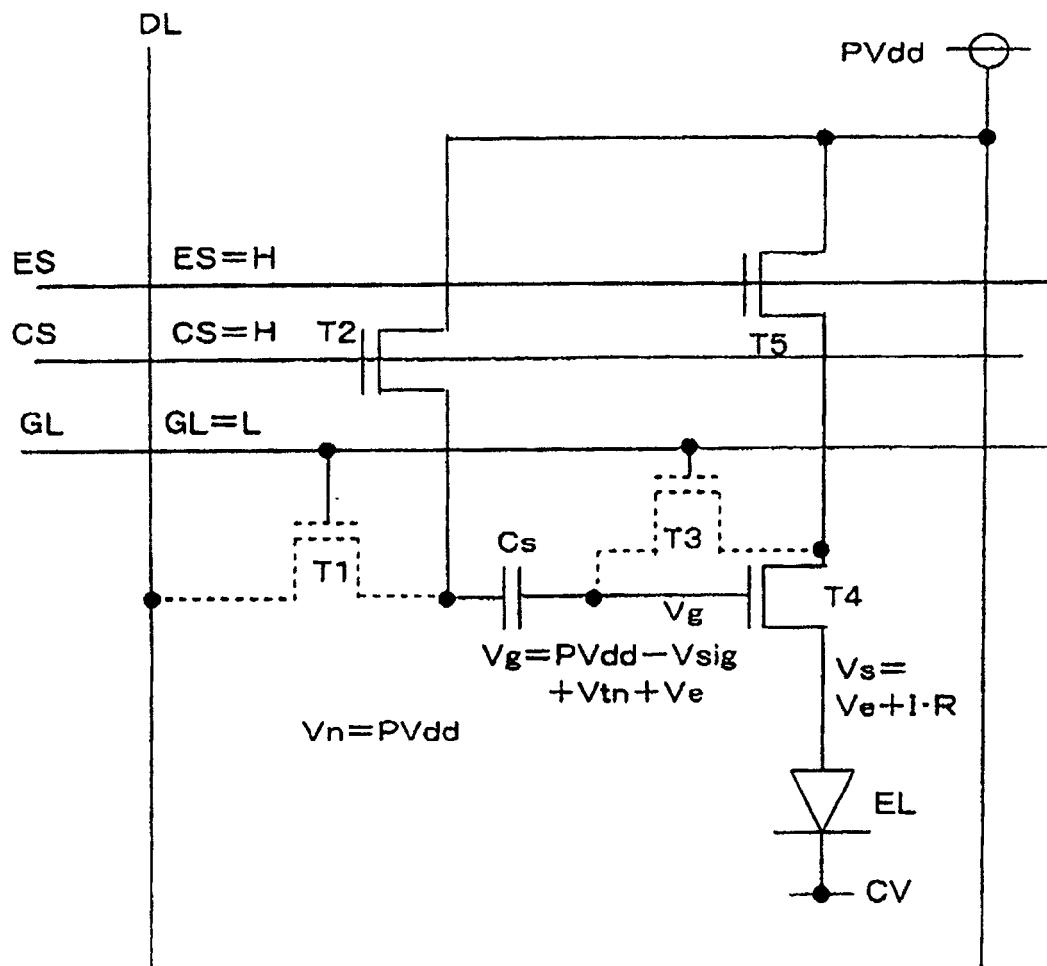

在此变形例 8 中, 如图 30 所示, 采用 n 沟道晶体管作为驱动晶体管 T4。再者, 此驱动晶体管 T4 的源极连接在有机 EL 组件 EL 的阳极, 而漏极则连接在 n 沟道的驱动控制晶体管 T5 的源极, 该驱动控制晶体管 T5 的漏极连接在电源 PVdd。

并且, 与栅极线 GL 同样设有向水平方向延伸的电容设定线 CS, 而在该电容设定线 CS 连接有 n 沟道的电位控制晶体管 T2。

另外, 其它构成基本上与图 1 的电路相同。

其次说明该像素电路的动作。

如图 31 所示, 此像素电路(包括数据线 DL), 在 1 水平期间, 与栅极线 GL、发光设定线 ES、电容设定线 CS 的状态(H、L)对应, 具有 (i) 数据设定(GL=H, ES=L, CS=L)、(ii) 预充电(GL=H, ES=H, CS=L)、(iii) 复位(GL=H, ES=L, CS=L)、(iv) 电位固定(GL=L, ES=L, CS=L)、(v) 发光(GL=L, ES=H, CS=H) 等 5 个状态, 且重复此 5 个状态。

并且, 在数据线 DL 的数据如图所示, 在选择写入对象的线的阶段中依序将数据设定在该水平线的各行的数据线 DL。即, 依照每一像素的点顺序而将数据对数据线 DL 作输出。再者, 在将数据设定在所有的数据线 DL 之后, 即将该数据(数据电压)取入各像素电路。

以下说明写入的动作。

##### (i) 数据设定 (GL=H, ES=L, CS=L)

首先, 设定发光设定线 ES=L 电位, 将来自电源线 PVdd 的电流遮断, 同时设定电容设定线 CS=L 电位, 以降低选择晶体管 T1 与电容 CS 的连接点的电压。然后, 在此状态下将栅极线 GL 设为 H 电位, 依序将与数据线 DL 对应的各像素的数据电压予以设定。因此, 将数据线 DL 设定数据的电压施加在电容 CS。另外, 对于数据线 DL 虽依照点顺序将数据电压对于数据线 DL 作设定, 然而各数据线 DL 连接有电容,

而使暂时被施加的数据电压被保持。

(ii) 预充电 (GL=H, ES=H, CS=L)

在结束对于各数据线 DL 的数据设定之后, 将发光设定线 ES 设为 H 电位。藉此, 由于驱动晶体管 T4 的漏极连接在电源线 PVdd, 且短路晶体管 T3 成为导通, 因此驱动晶体管 T4 的栅极即被充电到电源电位 PVdd。

(iii) 复位 (GL=H, ES=L, CS=L)

之后, 将发光设定线 ES 恢复为 L 电位, 且将驱动晶体管 T4 从电源 PVdd 予以切离。藉此, 驱动晶体管 T4 的栅极电位即从该源极电位下降到仅施加有阈值电压 Vtn 的补偿 (offset) 的电位。另一方面, 由于成为有机 EL 组件 EL 的阈值电压 Ve, 因此成为驱动晶体管 T4 的栅极电压  $Vg=Ve+Vtn$ 。而且, 此时的电容器 Cs 的数据线 DL 侧即成为数据线 DL 的数据电压 Vsig。

(iv) 电位固定 (GL=L, ES=L, CS=L)

接着, 将栅极线 GL 设定为 L 电位, 且使选择晶体管 T1、短路晶体管 T3 截止。藉此, 如图 32 所示, 即固定为驱动晶体管 T4 的栅极电压  $Vg=Ve+Vtn$ 。此时, 电容器 Cs 的相反侧的电压为 Vsig, 至于电容器 CS, 则对其充电至  $Vsig-Vg=Vsig-(Ve+Vtn)$  的电压。

(v) 发光 (GL=L, ES=H, CS=H)

在电位被固定之后, 将发光设定线 ES 及电容设定线 CS 设为 H 电位。藉此, 如图 30 所示, 电容器 Cs 的选择晶体管 T1 侧的电压即成为 PVdd, 因此驱动晶体管 T4 的栅极电压  $Vg=PVdd-Vsig+Ve+Vtn$ 。然后, 由于驱动控制晶体管 T5 也成为导通, 因此驱动晶体管 T4 即使与该栅极源极间电压 Vgs 对应的电流流通, 也将该电流供给至有机 EL 组件 EL。在此, 驱动晶体管 T4 的源极电位  $Vs=Ve+IR$ 。在此, I 是流动于有机 EL 组件 EL 的电流值, R 是有机 EL 组件 EL 的导通电阻。因此, 驱动晶体管 T4 的栅极源极间电压  $Vgs=Vg-Vs=PVdd-Vsig+Vtn-IR$ 。

有机 EL 组件 EL 的导通电阻 R 可通过将有机 EL 组件的面积增大, 且将有机 EL 组件的有机层变薄, 而使其变得极小。再者, 由于驱动晶体管 T4 的漏极电流 I 由  $I=(1/2)\beta(Vgs-Vtn)^2$  所决定, 因此不须

驱动晶体管 T4 的阈值电压, 即可将与数据电压  $V_{sig}$  对应的电流流通至驱动晶体管 T4。另外,  $\beta$  为驱动晶体管 T4 放大率, 表示成  $\beta = \mu \cdot \epsilon \cdot G_w/G$ ,  $\mu$  是载流子的迁移率, 而  $\epsilon$  是介电常数,  $G_w$  是栅极宽度,  $G_l$  是栅极长度。

尤其驱动晶体管 T4 的栅极源极间电压  $V_{gs}$  由根据将数据电压  $V_{sig}$  从  $PV_{dd}$  减算的电压而决定。因此, 数据电压  $V_{sig}$  可利用与直接供给至 p 沟道的驱动晶体管的栅极的数据电压  $V_{sig}$  相同的电压。因此, 可将用于驱动数据线 DL 的电路作成与传统相同的构成。

接着, 根据图 34 说明对于 1 水平线内的各像素写入数据的顺序。

首先, 在用于表示 1 水平期间的开始的使能信号 ENB 的 L 之后, 依照点顺序将数据电压  $V_{sig}$  写入所有的数据线 DL。即, 数据线 DL 连接有电容等, 通过设定电压信号, 以使该数据电压  $V_{sig}$  保持在数据线 DL。于是, 通过将关于各行像素的数据电压  $V_{sig}$  设定在依序对应的数据线 DL, 而将数据电压  $V_{sig}$  设定在所有的数据线 DL。

然后, 在结束该数据的设定的阶段, 将发光设定线 ES 设为 H 电位进行预充电, 且在之后将发光设定线 ES 恢复为 L 电位以进行复位。然后, 通过将栅极线 GL 恢复为 L 电位, 固定像素电路内的电容器  $C_s$  的充电电压, 并在之后通过将电容设定线 CS 设为 H 电位而使驱动晶体管 T4 的栅极位移, 以在该水平线的所有像素中进行发光。

如此, 即可依序将通常的视频信号 (数据电压  $V_{sig}$ ) 写入数据线 DL, 且将该信号设定在像素电路而使其发光。

尤其如图 30 所示, 最好将使用在像素电路的晶体管 (薄膜晶体管: TFT) 全部设为 n 沟道晶体管。n 沟道晶体管的特性比 p 沟道晶体管优异。因此, 即使将晶体管的有源层设为非晶硅, 也可充分动作。于是, 关于有源层方面, 即可不须予以多晶硅化的处理而改善良率。

并且, 即使在选择晶体管 T1 与驱动晶体管 T4 的栅极之间插入电容器  $C_s$ , 也可利用与将传统的选择晶体管直接连接在 p 沟道的驱动晶体管的控制端时相同极性的数据信号。

### (I) 变形例 9

图 35 为表示变形例 9 的像素电路的构成, 在此例中, 电位控制晶体管 T2 的一端 (漏极) 连接在发光设定线 ES 而非电源线  $PV_{dd}$ 。依据

此构成，也可获得与图 1 的例子相同的作用。而且，以电源而言虽连接在相同的 PVdd，然而发光设定线 ES 与电源线 PVdd 为个别的线，其相较于对于有机 EL 组件 EL 驱动供给的电源线 PVdd，不会有电压变动，而可获得稳定动作。即，在设定通过电位控制晶体管 T2 的电压  $V_n$  时，不会有受到电源线 PVdd 的电压降的影响的情况。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 10

图 11

|        |     |    |     |

|--------|-----|----|-----|

| GL(T1) | OFF | ON | OFF |

|--------|-----|----|-----|

|        |    |     |    |

|--------|----|-----|----|

| ES(T5) | ON | OFF | ON |

|--------|----|-----|----|

图 12

图 13

图 14

图 15

图 16

图 17

图 18

图 19

图 20

图 21

图 22

图 23

图 24

图 25

图 26

图 27

图 28

图 29

图 30

图 31

图 32

图 33

图 34

图 35

|                |                                                                                                              |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机EL像素电路                                                                                                     |         |            |

| 公开(公告)号        | <a href="#">CN100593185C</a>                                                                                 | 公开(公告)日 | 2010-03-03 |

| 申请号            | CN200510064215.0                                                                                             | 申请日     | 2005-04-12 |

| [标]申请(专利权)人(译) | 三洋电机株式会社                                                                                                     |         |            |

| 申请(专利权)人(译)    | 三洋电机株式会社                                                                                                     |         |            |

| 当前申请(专利权)人(译)  | 三洋电机株式会社                                                                                                     |         |            |

| [标]发明人         | 池田恭二                                                                                                         |         |            |

| 发明人            | 池田恭二                                                                                                         |         |            |

| IPC分类号         | G09G3/32 H05B33/08 G09F9/30 G09G3/30 H05B33/02                                                               |         |            |

| CPC分类号         | G09G2300/0842 G09G2300/0861 G09G2320/043 G09G3/3233 G09G2300/0819                                            |         |            |

| 代理人(译)         | 程伟                                                                                                           |         |            |

| 优先权            | 2004117332 2004-04-12 JP<br>2005092566 2005-03-28 JP<br>2005092588 2005-03-28 JP<br>2005096835 2005-03-30 JP |         |            |

| 其他公开文献         | CN1684558A                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                               |         |            |

#### 摘要(译)

本发明是通过控制驱动晶体管的控制端的电位以使与该晶体管的控制端的电位对应的驱动电流供给至有机EL组件。又在驱动晶体管与前述有机EL组件之间插入配置驱动控制晶体管，以使前述驱动电流导通或截止(on-off)。并且，设置短路晶体管，且通过该短路晶体管以控制是否将驱动晶体管予以二极管连接。再者，通过选择晶体管，控制是否将来自数据线的数据信号供给至前述驱动晶体管的控制端。再者，在该选择晶体管与前述驱动晶体管的控制端之间配置电容，同时通过电位控制晶体管使该电容的前述选择晶体管与预定的电源之间的连接予以导通或截止。