## (12) 发明专利

(10) 授权公告号 CN 1808722 B

(45) 授权公告日 2010.06.16

(21) 申请号 200510023023.5

16-18 行.

(22) 申请日 2005.11.04

JP 昭 62-240734 A, 1987.10.21, 说明书第 1-4 页.

## (30) 优先权数据

2004-320381 2004.11.04 JP

CN 1279518 A, 2001.01.10, 说明书第 3 页第 14 行 - 第 21 页第 29 行、图 1.

(73) 专利权人 株式会社半导体能源研究所

CN 1280394 A, 2001.01.17, 说明书第 1 页第 23-24 行.

地址 日本神奈川县

(72) 发明人 秋元健吾 丸山穗高 曾根宽人

池田寿雄 坂田淳一郎 濑尾哲史

审查员 邵烨

(74) 专利代理机构 中国专利代理(香港)有限公司 72001

代理人 范赤 邹雪梅

## (51) Int. Cl.

H01L 27/32(2006.01)

H01L 27/15(2006.01)

H01L 21/82(2006.01)

H05B 33/26(2006.01)

H05B 33/10(2006.01)

## (56) 对比文件

US 2004/0178724 A1, 2004.09.16, 说明书第 1 实施例、图 1.

CN 1334588 A, 2002.02.06, 说明书第 5 页第

权利要求书 1 页 说明书 31 页 附图 28 页

## (54) 发明名称

显示器件及其制备方法

## (57) 摘要

本发明的目的是低成本、高产量制备高可靠性的显示器件。本发明的显示器件包括：其间插有电致发光层的第一反射电极层和第二透明电极层，其中电致发光层具有含有有机化合物和无机化合物的层，且第一电极层包含含有选自钼、钛和碳中至少一种的铝合金。

1. 一种显示器件,包括:

形成在基底上的薄膜晶体管,该薄膜晶体管包括半导体层、栅绝缘层、栅极以及源极和漏极中的至少一种;

在该薄膜晶体管上的绝缘层,所述绝缘层用具有烷基的氧化硅形成;

设置在该绝缘层上的夹层膜,所述夹层膜由硅氮氧化物形成;

与所述源极和漏极中的至少一种电连接的发光元件,

其中所述发光元件包括其间插有电致发光层的第一电极和第二电极,

其中第一电极为含有钼和碳的铝合金;且

其中夹层膜仅设置在第一电极的下方。

2. 一种显示器件,包括:

形成在基底上的薄膜晶体管,该薄膜晶体管包括半导体层、栅绝缘层、栅极,以及源极和漏极中的至少一种;

在该薄膜晶体管上的绝缘层,所述绝缘层用具有烷基的氧化硅形成;

设置在该绝缘层上的夹层膜,所述夹层膜由硅氮氧化物形成;

与所述源极和漏极中的至少一种电连接的发光元件,

其中所述发光元件包括第一电极、在第一电极上的透光导电薄膜、在该透光导电薄膜上的电致发光层以及在该电致发光层上的第二电极,

其中第一电极为含有钼和碳的铝合金;且

其中夹层膜仅设置在第一电极的下方。

3. 根据权利要求 1 和 2 任一项的显示器件,其中第一电极中钼的含量超过 7.0 原子%。

4. 根据权利要求 3 的显示器件,其中在第一电极中钼的含量为 20 原子%或更低。

5. 根据权利要求 1 和 2 中任一项的显示器件,其中第一电极中碳的含量为 0.1-10 原子%。

6. 根据权利要求 1 和 2 中任一项的显示器件,其中第一电极为反射的,且第二电极为透明的。

7. 根据权利要求 1 和 2 中任一项的显示器件,其中所述电致发光层具有与第一电极接触的层,所述层包含有机化合物和无机化合物。

8. 根据权利要求 1 和 2 中任一项的显示器件,其中该显示器件被结合到选自计算机、图像重现设备、蜂窝电话、数码相机和电视中的至少一种。

## 显示器件及其制备方法

### 技术领域

[0001] 本发明涉及一种显示器件及其制备方法。

### 背景技术

[0002] 随着具有电致发光（下文也称 EL）元件或液晶元件的显示器件的屏幕越来越大、清晰度越来越高，纯铝作为配线材料越来越引起注意，这是由于纯铝具有低电阻且易于加工成配线。

[0003] 但是，纯铝在耐热性上存在问题。在显示器件制备过程中的热处理会在纯铝薄膜表面上产生称为小丘的凸状突起。所述的小丘导致了配线间的短路，产生了缺陷。

[0004] 因而，希望使用具有低电阻、高耐热性且减少小丘的配线材料。添加有另一种元素的铝合金薄膜应运而生（例如，参考 1：日本专利申请未审公开 No. 2003-89864）。

### 发明内容

[0005] 本发明的目的是提供一种工艺：通过使用该工艺，在不使用复杂的工序和设备下，通过使用低电阻和高耐热性的配线材料可以高产量地形成具有高可靠性和良好的电特性的显示器件，所述技术能抑制小丘的产生。

[0006] 在本发明中，作为反射电极的第一电极层含有铝合金，所述铝合金含有选自钼、钛和碳中的至少一种或多种。包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜在热处理时几乎不结晶，并且在膜表面上具有良好的平面性。而且，所述膜即使对接近可见光区域内的光也具有高的反射率，因而可以产生高效率的光反射。所述包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜为无毒的并且对人和环境无害，这些都是优点。

[0007] 可以应用本发明的显示器件包括发光显示器件，其具有连接至发光元件的 TFT，其中含有用于发光即称作电致发光（以下也称为 EL）的有机材料或有机材料与无机材料混合物的层设置在电极之间。

[0008] 本发明的显示器件包括：设置在第一反射电极层上的电致发光层；和设置在电致发光层上的第二透明电极层，其中电致发光层具有含有有机化合物和无机化合物的层，其与第一电极层接触，并且第一电极层含有铝合金，所述铝合金含有选自钼、钛和碳中的至少一种或多种。

[0009] 本发明的显示器件包括：在第一反射电极层上的透光导电膜；在导电膜上的电致发光层；和在电致发光层上的第二透明电极层，其中电致发光层具有与导电膜接触的、含有有机化合物和无机化合物的层，并且第一电极层含有铝合金，所述铝合金含有选自钼、钛和碳中的至少一种或多种。

[0010] 本发明的显示器件包括：含有半导体层、栅绝缘层、栅极层、源极层和漏极层的薄膜晶体管；设置在薄膜晶体管上的绝缘层；设置在绝缘层上的夹层膜；设置在夹层膜上的第一反射电极层；以及设置在电致发光层上的第二透明电极层，其中电致发光层具有含有有机化合物和无机化合物的层，其与第一电极层接触，所述夹层膜仅设置在第一电极层的

下面，并且第一电极层含有铝合金，所述铝合金含有选自钼、钛和碳中的至少一种或多种。

[0011] 本发明的显示器件包括：含有半导体层、栅绝缘层、栅极层、源极层和漏极层的薄膜晶体管；设置在薄膜晶体管上的绝缘层；设置在绝缘层上的夹层膜；设置在夹层膜上的第一反射电极层；设置在第一电极层上的透光导电膜；设置在导电膜上的电致发光层；以及设置在电致发光层上的第二透明电极层，其中电致发光层具有与导电膜接触的、含有有机化合物和无机化合物的层，所述夹层膜仅设置在第一电极层的下面，并且第一电极层含有铝合金，所述铝合金含有选自钼、钛和碳中的至少一种或多种。

[0012] 一种制备本发明的显示器件的方法，包括下述步骤：形成含有铝合金的第一反射电极层，所述铝合金含有选自钼、钛和碳中的至少一种或多种；在第一电极层上形成电致发光层；和在电致发光层上形成第二透明电极层，其中电致发光层形成使得含有有机化合物和无机化合物的层与第一电极层接触。

[0013] 一种制备本发明的显示器件的方法，包括下述步骤：形成含有铝合金的第一反射电极层，所述铝合金含有选自钼、钛和碳中的至少一种或多种；在第一电极层上形成透光导电膜；在导电膜上形成电致发光层；和在电致发光层上形成第二透明电极层，其中电致发光层形成使得含有有机化合物和无机化合物的层与导电膜接触。

[0014] 一种制备本发明的显示器件的方法，包括下述步骤：形成含有半导体层、栅绝缘层、栅极层、源极层和漏极层的薄膜晶体管；在薄膜晶体管上形成绝缘层；在绝缘层上形成夹层膜；在绝缘层和夹层膜中形成开口，其延伸至源极层或漏极层；在开口和夹层膜上形成含有选自钼、钛和碳中至少一种或多种的导电膜，使其与源极层或漏极层接触；使导电膜和夹层膜图案化来形成第一反射电极层；在第一电极层上形成电致发光层；并且在电致发光层上形成第二透明电极层，其中电致发光层形成使得含有有机化合物和无机化合物的层与第一电极层接触。

[0015] 一种制备显示器件的方法，包括下述步骤：形成含有半导体层、栅绝缘层、栅极层、源极层和漏极层的薄膜晶体管；在薄膜晶体管上形成绝缘层；在绝缘层上形成夹层膜；在绝缘层和夹层膜中形成开口，其延伸至源极层或漏极层；在开口和夹层膜上形成含有选自钼、钛和碳中至少一种或多种的第一导电膜，使其与源极层或漏极层接触；在第一导电膜上形成第二导电膜；使第一导电膜、第二导电膜和夹层膜图案化来形成第一反射电极层；在第一电极层上形成电致发光层；和在电致发光层上形成第二透明电极层，其中电致发光层形成使得含有有机化合物和无机化合物的层与第一电极层接触。

[0016] 通过使用本发明可以制备出高可靠性的显示器件。因而，可以高产量的制备高清晰度和高图像质量的显示器件。

## 附图说明

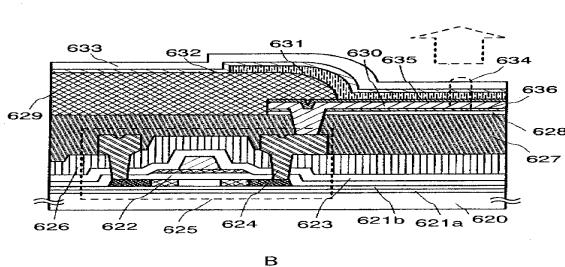

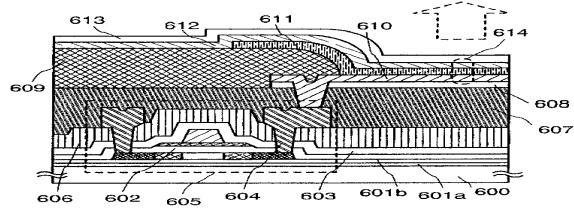

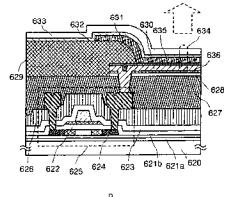

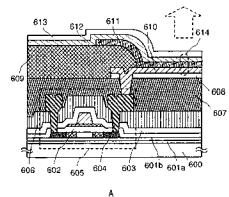

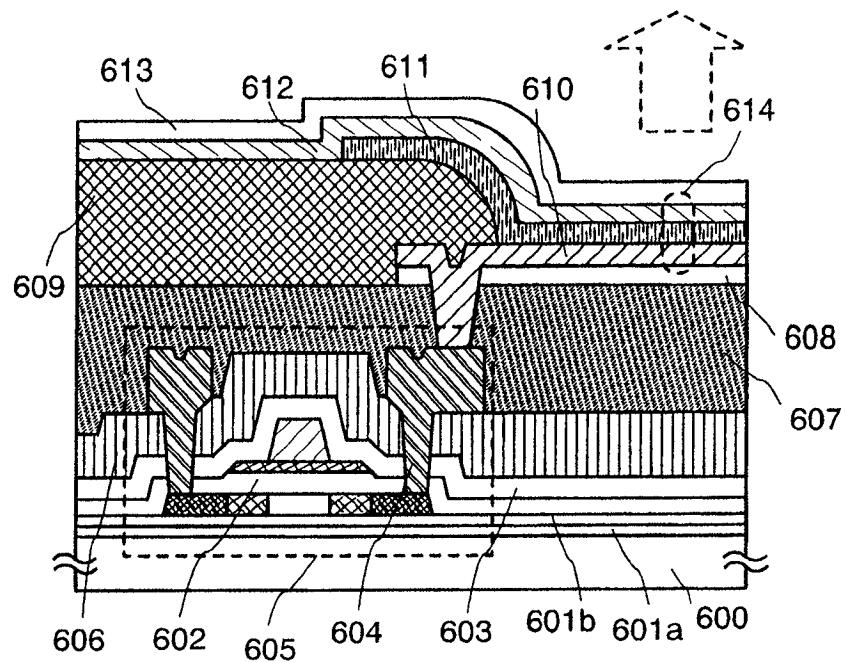

[0017] 图 1A 和 1B 分别显示了本发明的显示器件。

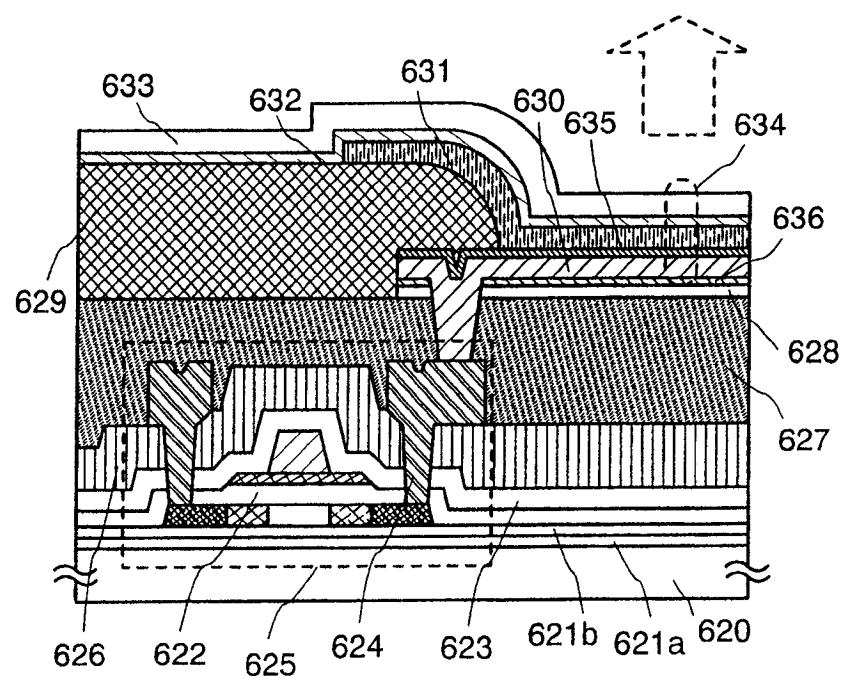

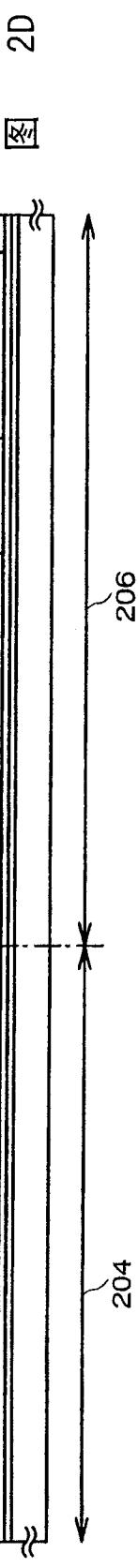

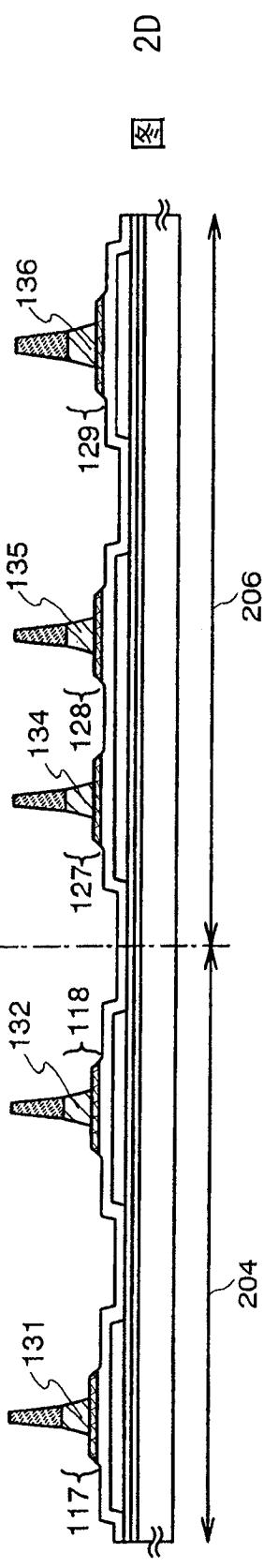

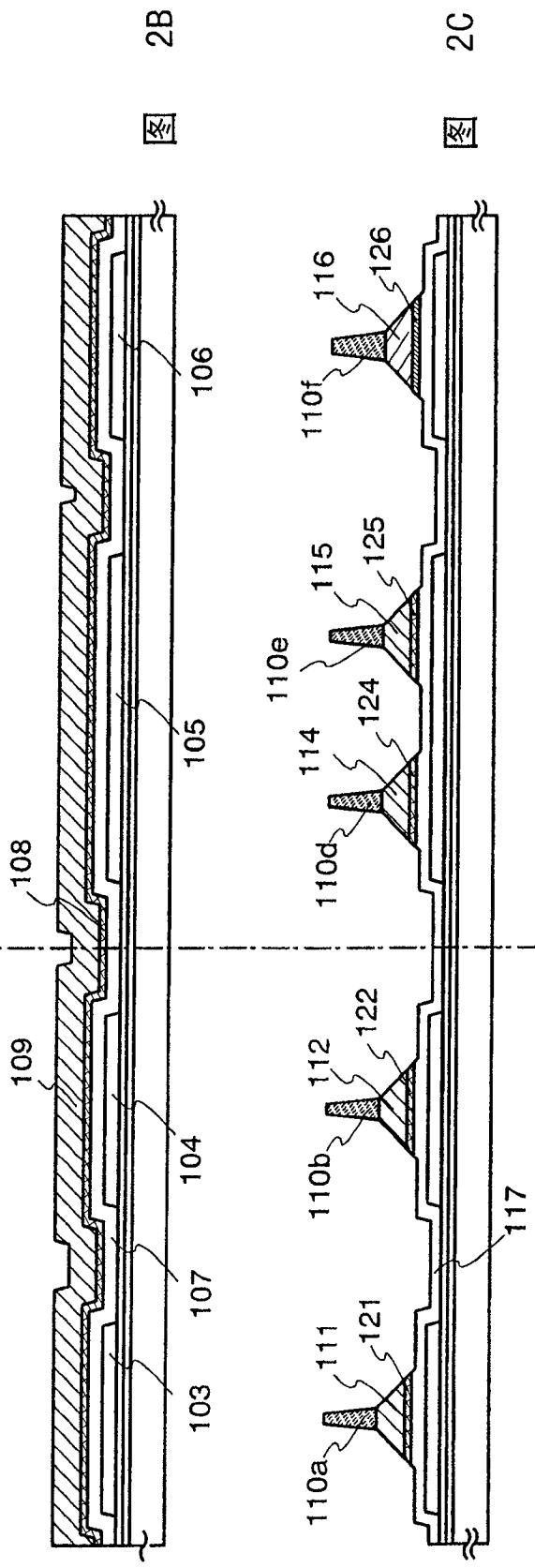

[0018] 图 2A-2D 显示了本发明显示器件的制备方法。

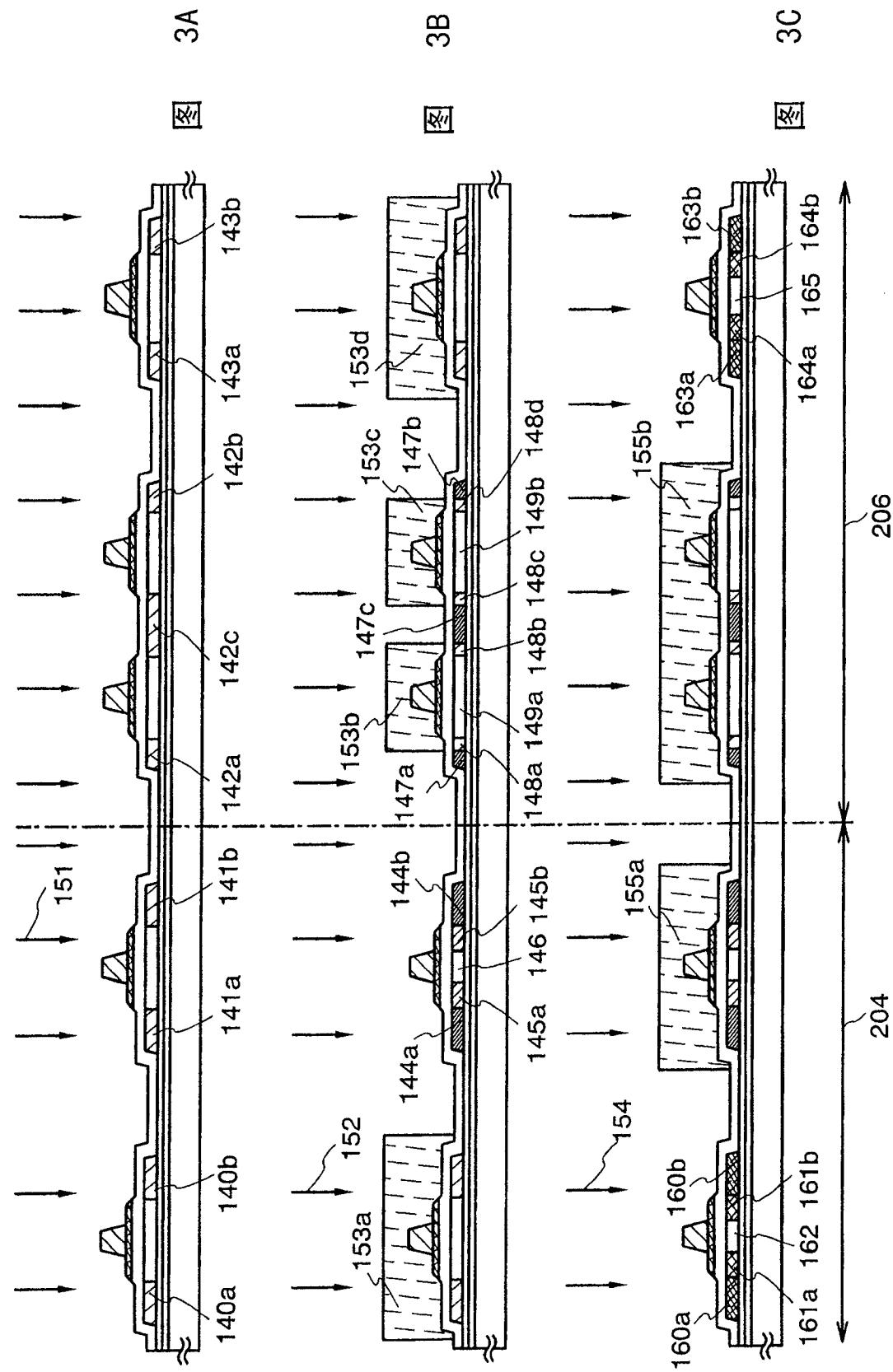

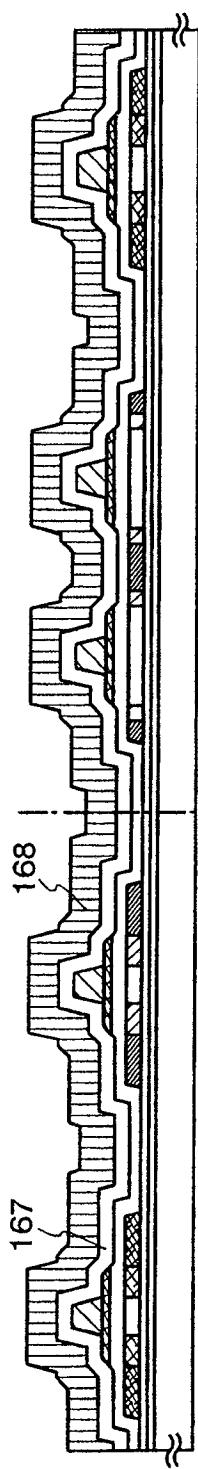

[0019] 图 3A-3C 显示了本发明显示器件的制备方法。

[0020] 图 4A 和 4B 显示了本发明显示器件的制备方法。

[0021] 图 5A-5C 显示了本发明显示器件的制备方法。

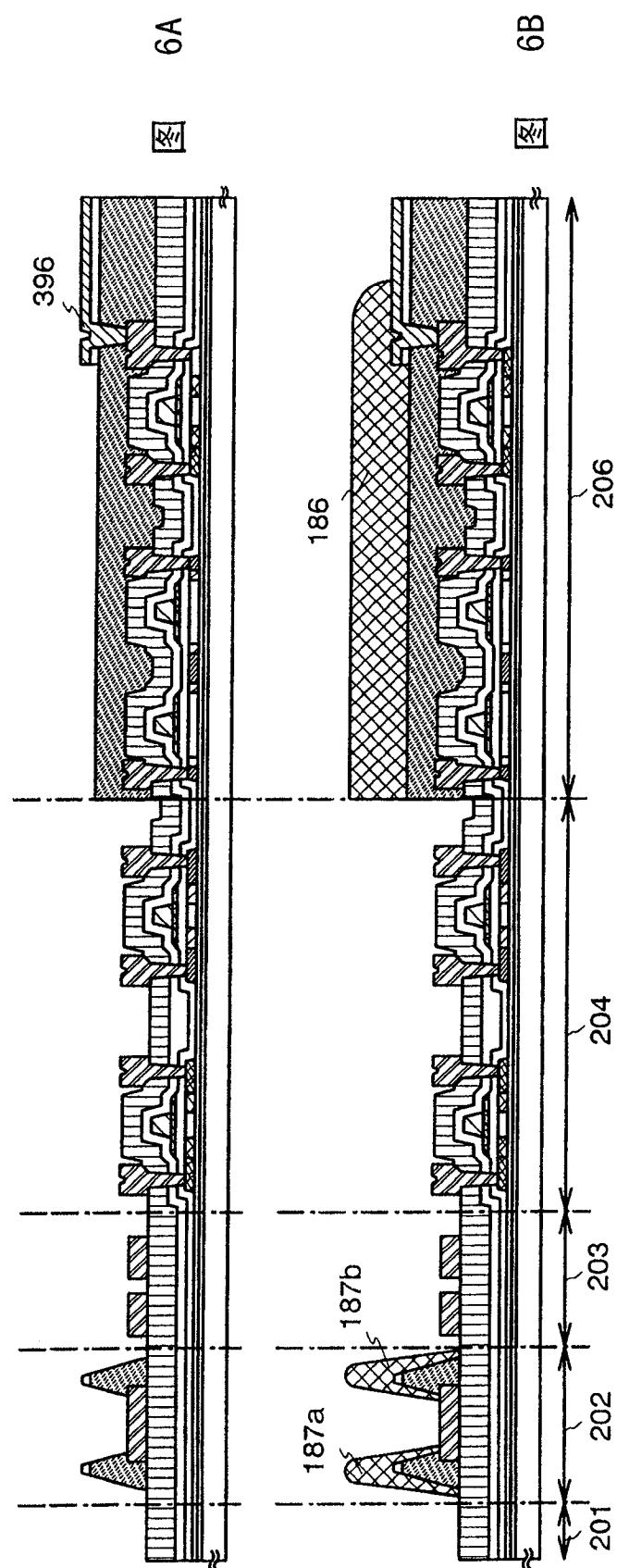

[0022] 图 6A 和 6B 显示了本发明显示器件的制备方法。

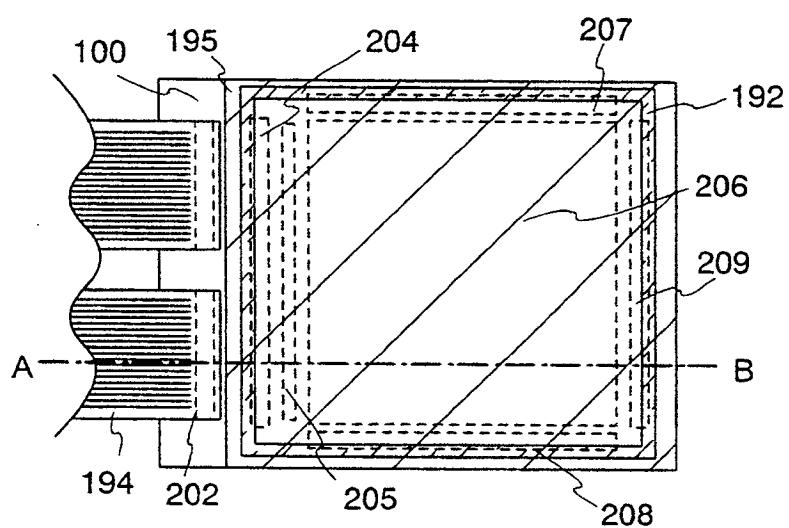

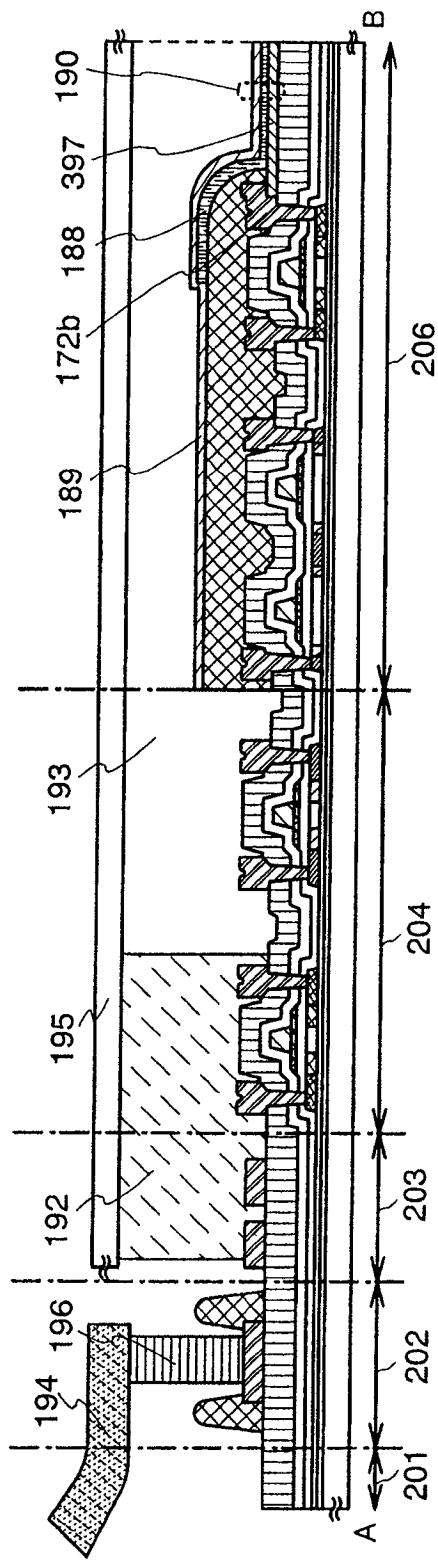

- [0023] 图 7A 和 7B 显示了本发明的显示器件。

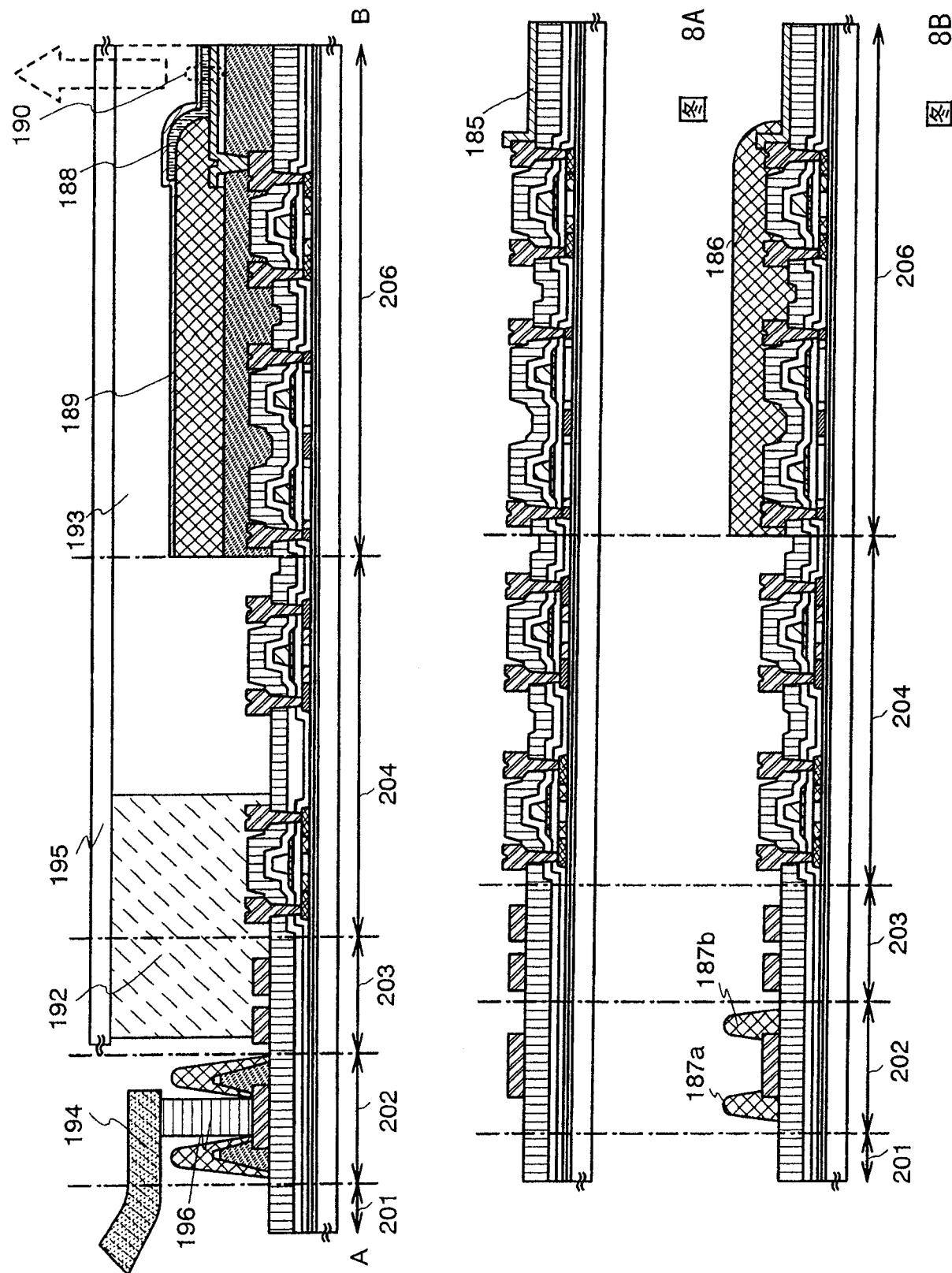

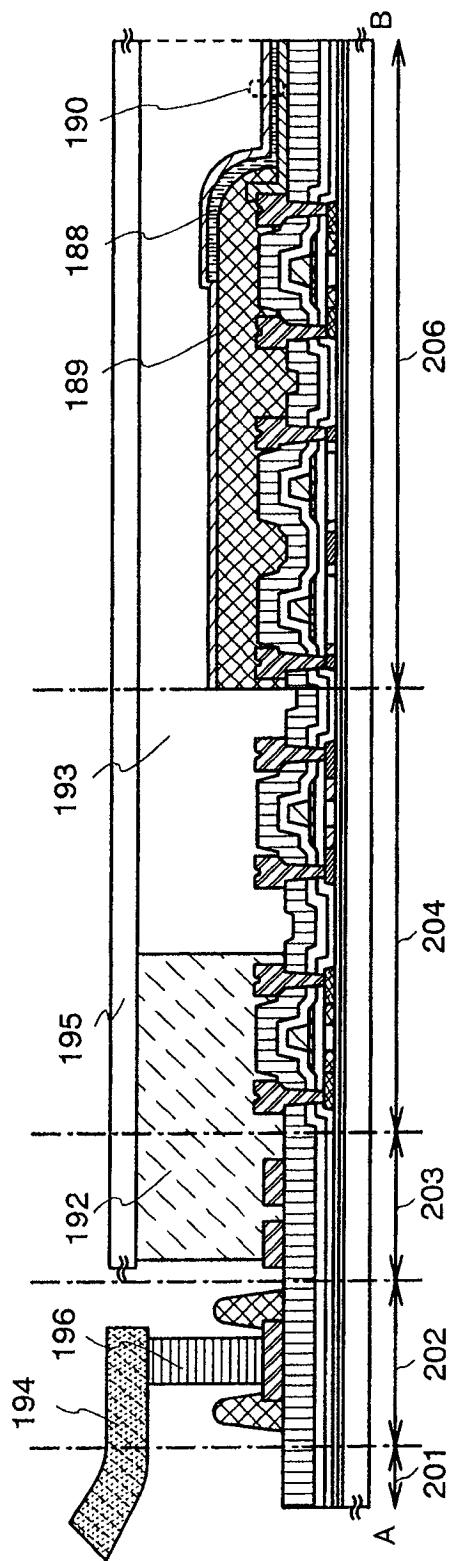

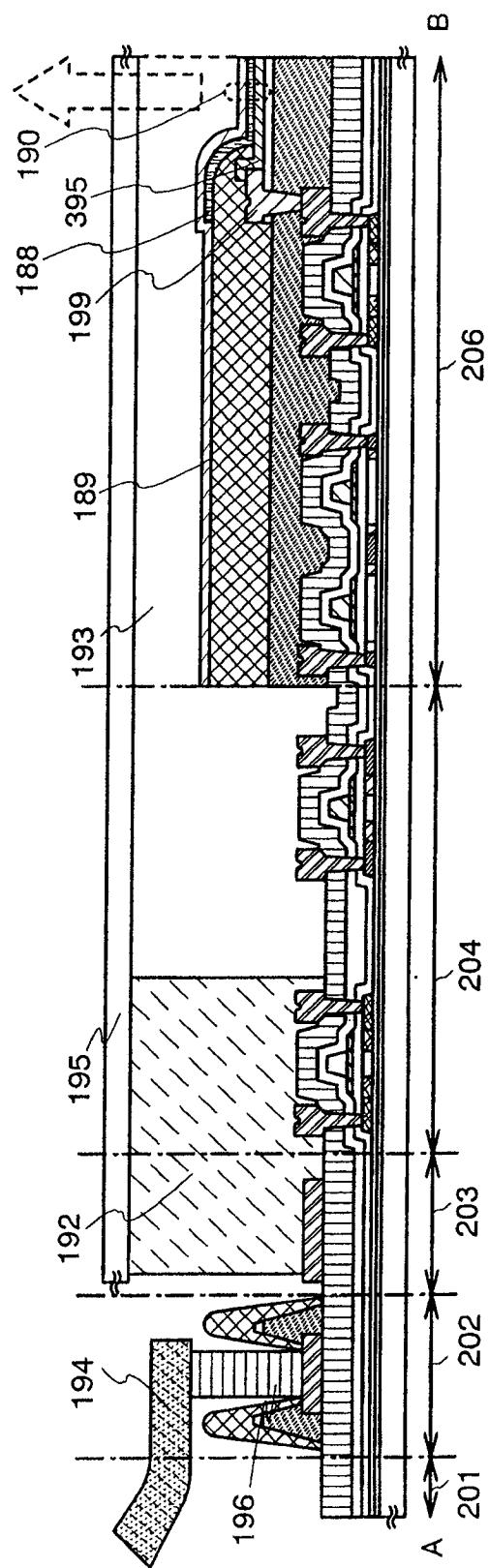

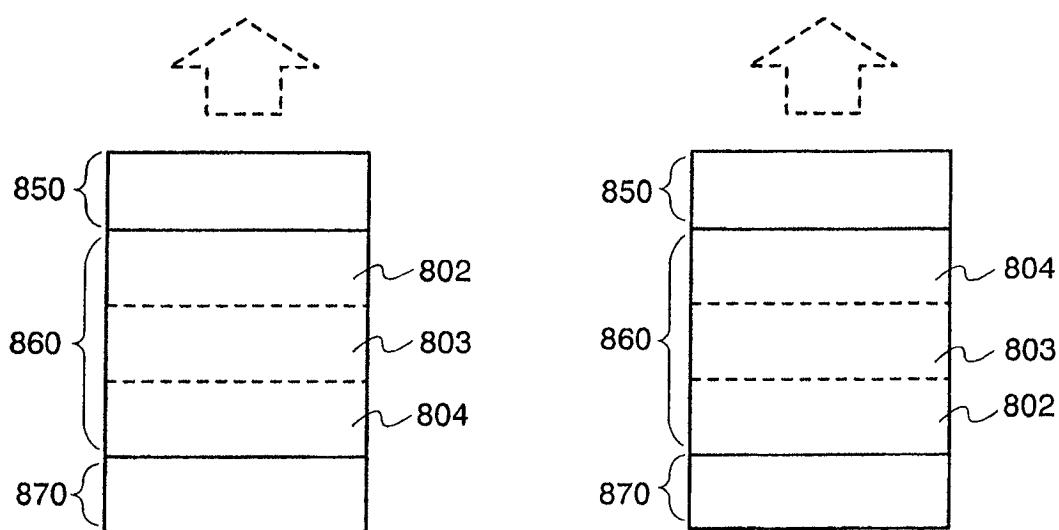

- [0024] 图 8A 和 8B 显示了本发明显示器件的制备方法。

- [0025] 图 9 显示了本发明的显示器件。

- [0026] 图 10 显示了本发明的显示器件。

- [0027] 图 11 显示了本发明的显示器件。

- [0028] 图 12 显示了本发明的显示器件。

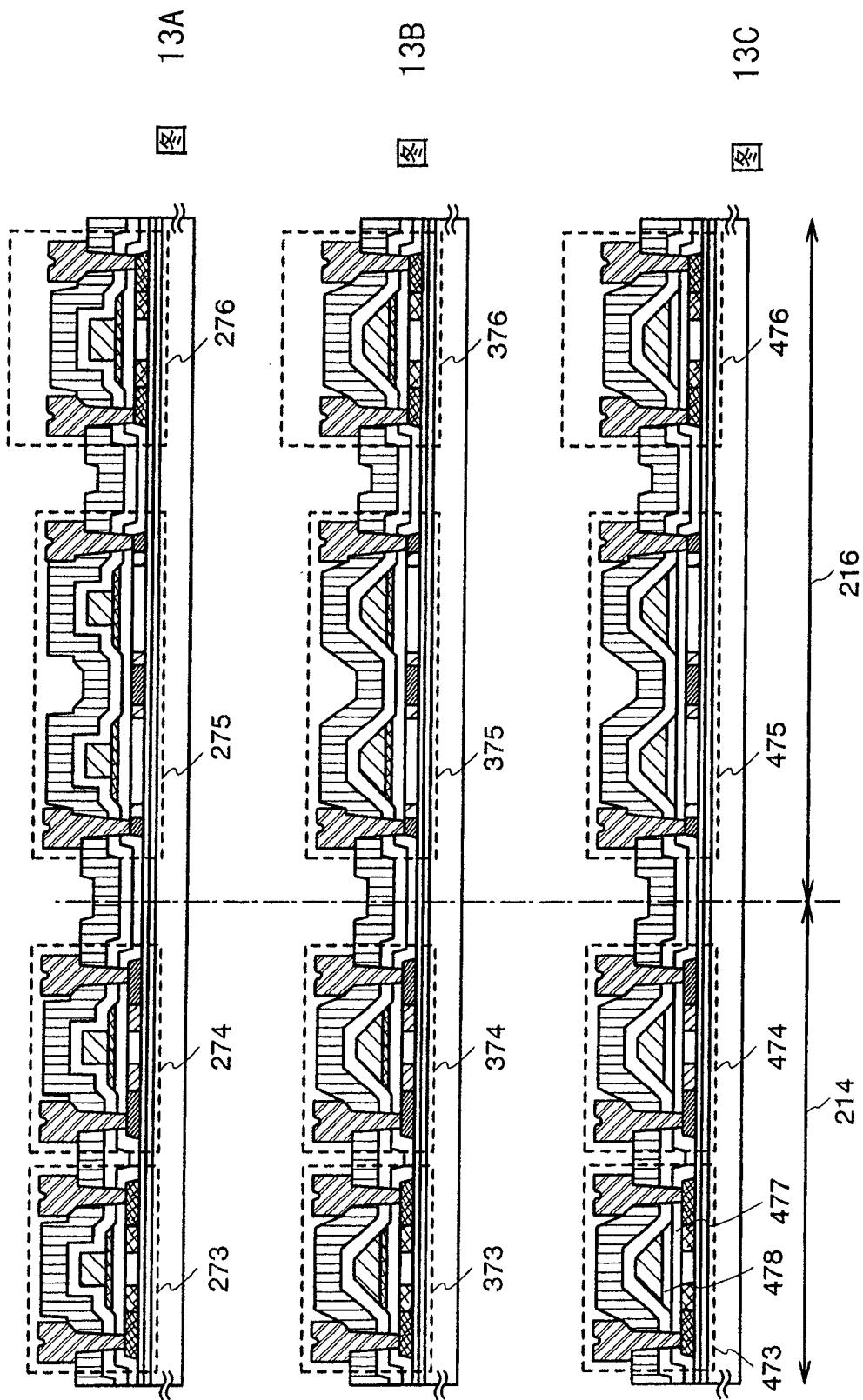

- [0029] 图 13A-13C 显示了本发明的显示器件。

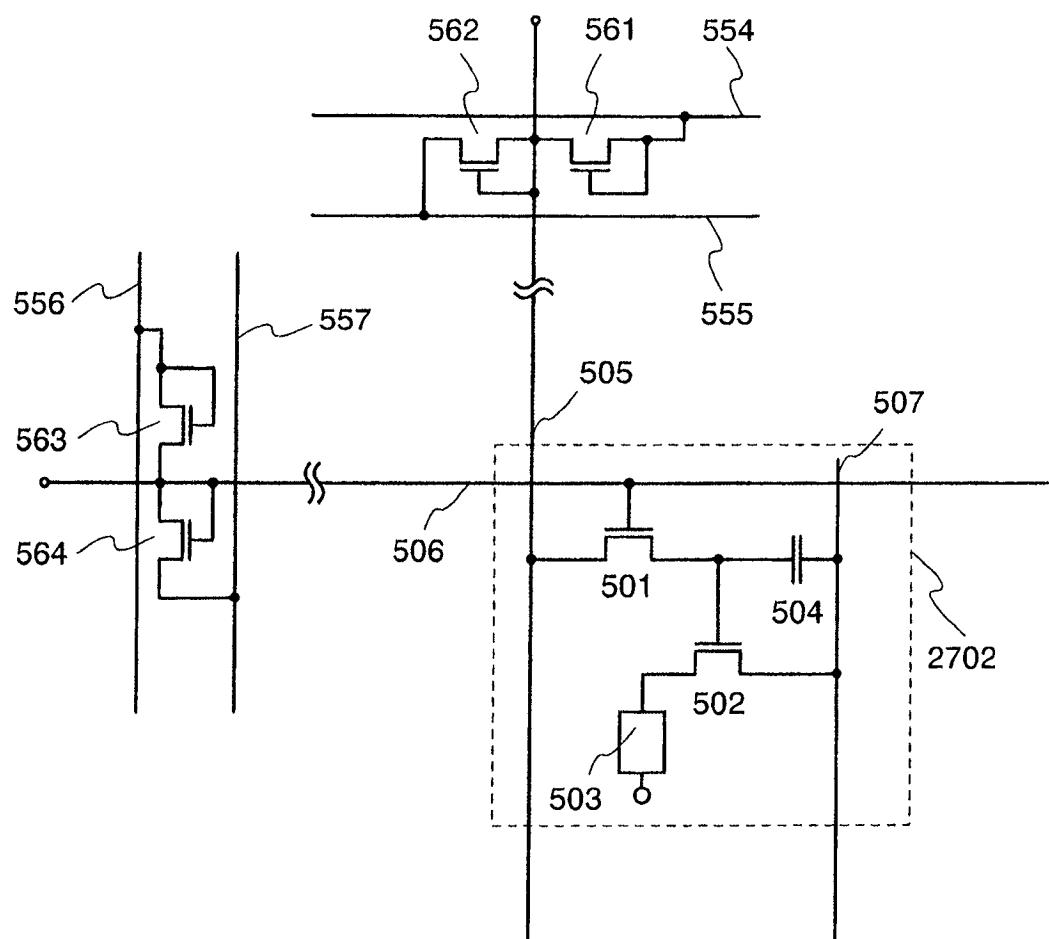

- [0030] 图 14 显示了图 15 中的显示器件的等效电路的示意图。

- [0031] 图 15 显示了本发明的显示器件。

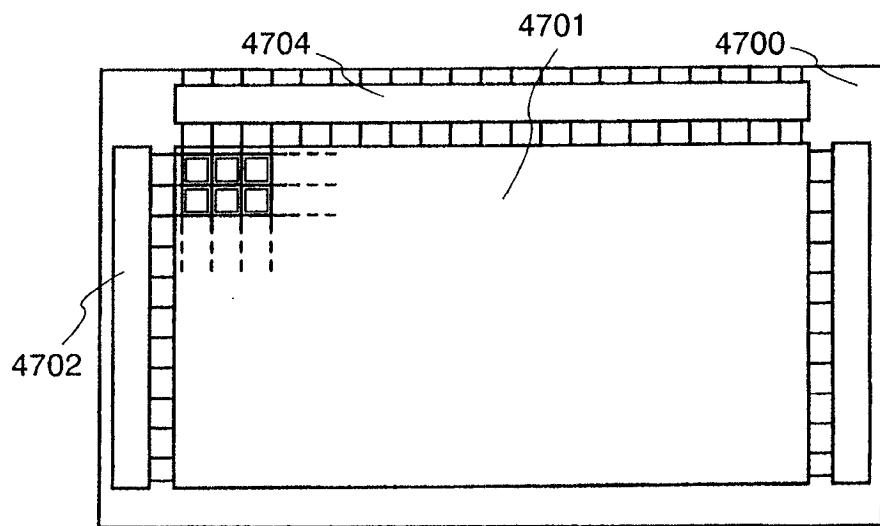

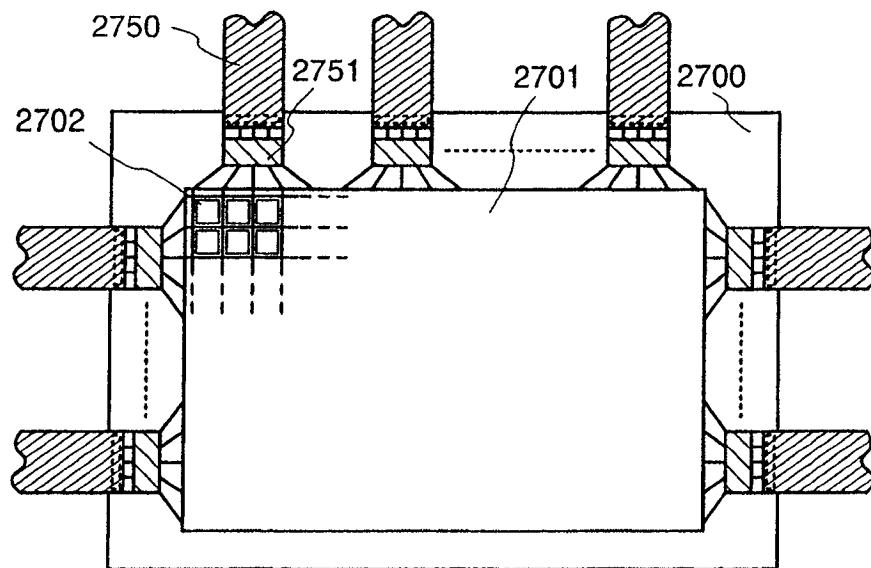

- [0032] 图 16A-16C 分别显示了本发明显示器件的顶视图。

- [0033] 图 17A 和 17B 分别显示了本发明显示器件的顶视图。

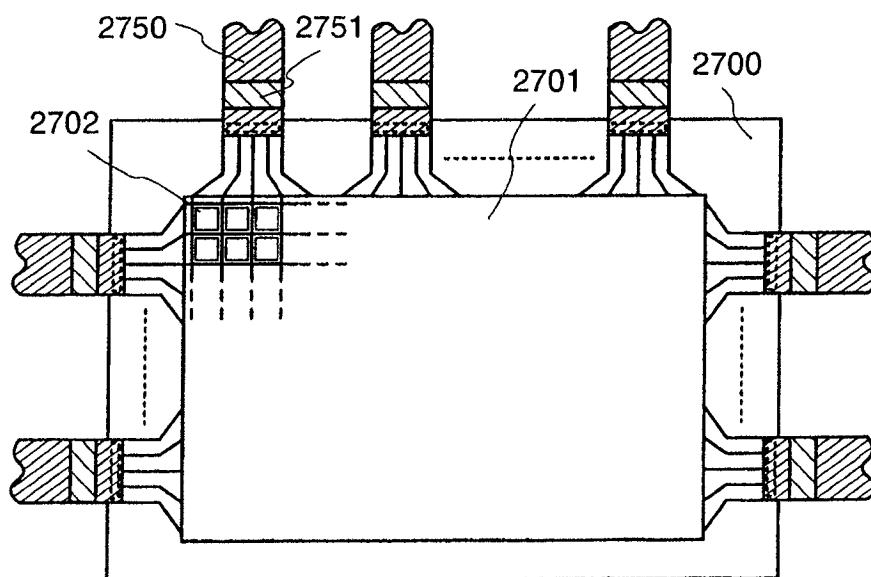

- [0034] 图 18A 和 18B 分别显示了可应用于本发明的发光元件的结构。

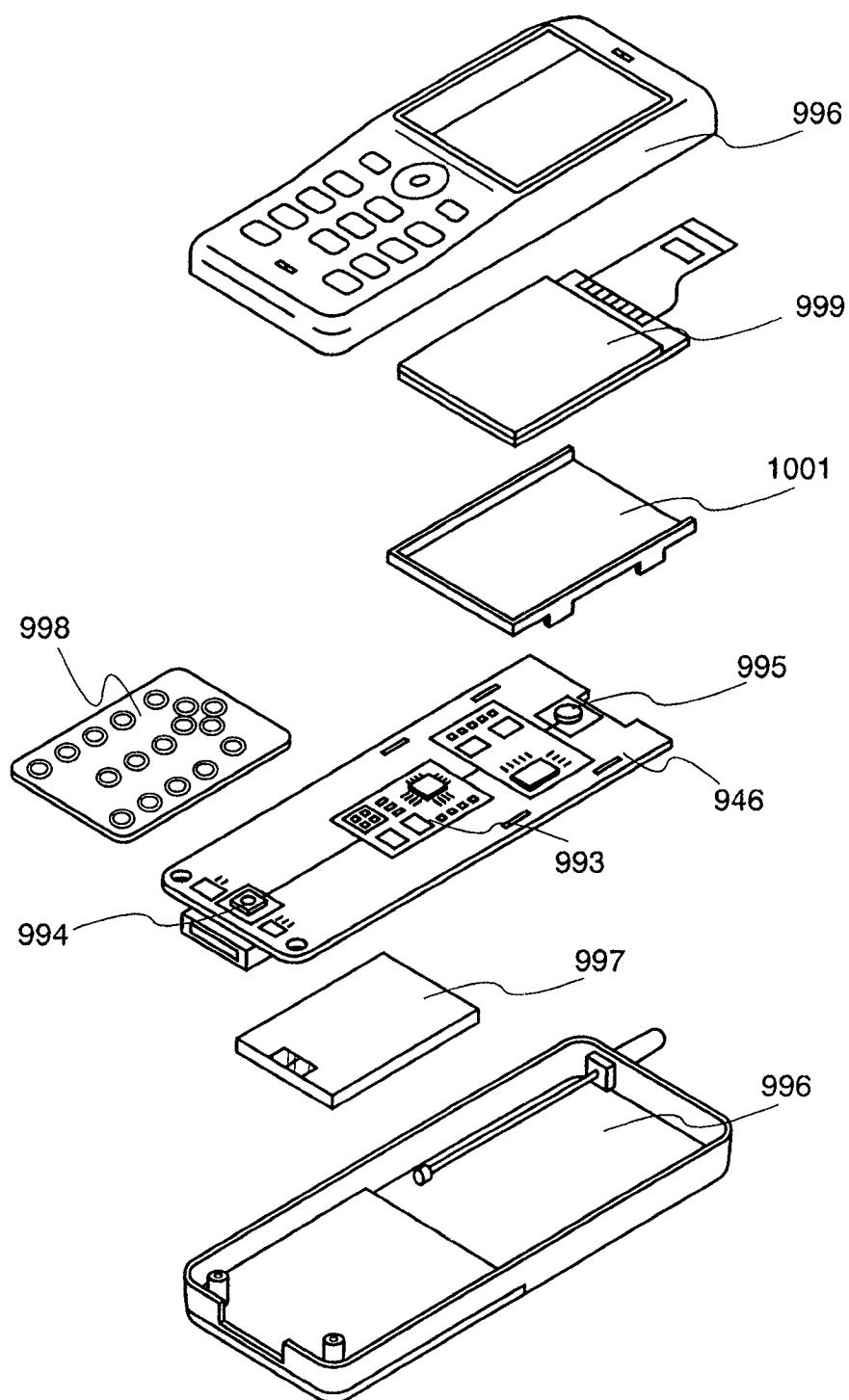

- [0035] 图 19A-19D 为应用本发明的电子设备。

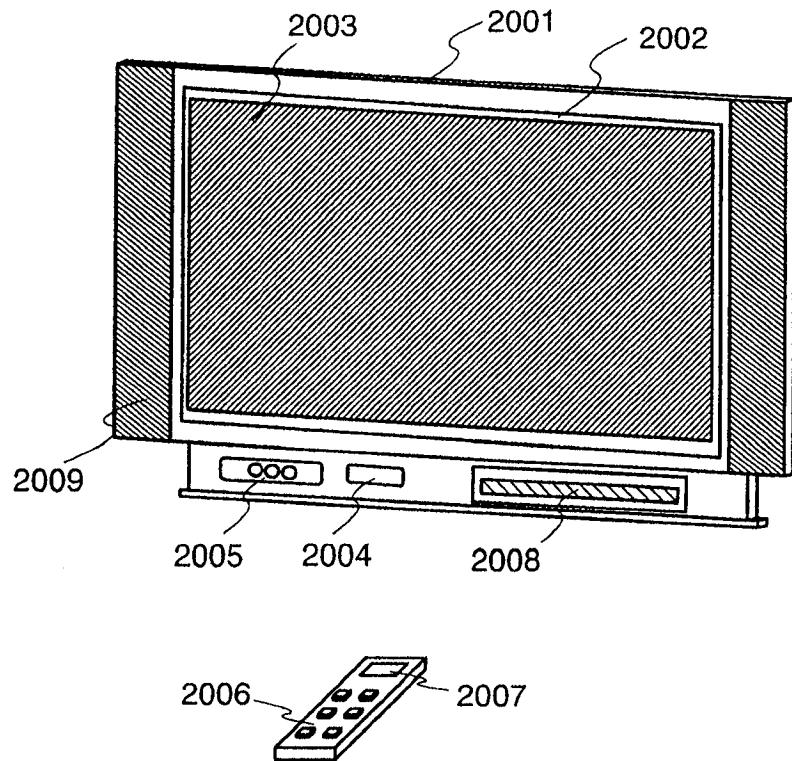

- [0036] 图 20A 和 20B 为应用本发明的电子设备。

- [0037] 图 21A 和 21B 为应用本发明的电子设备。

- [0038] 图 22 为应用本发明的电子设备。

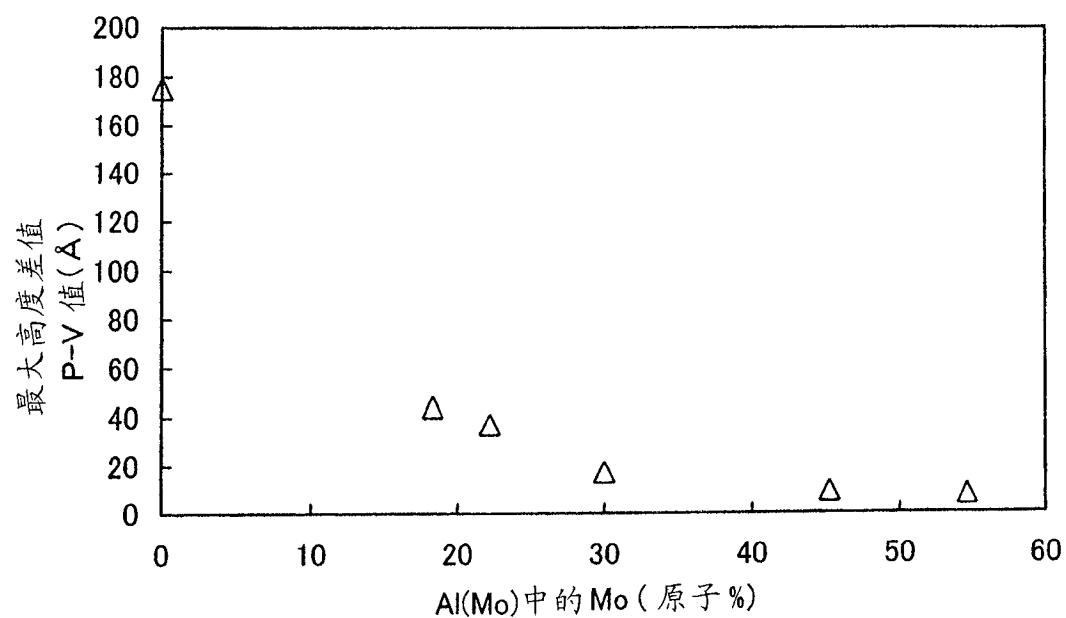

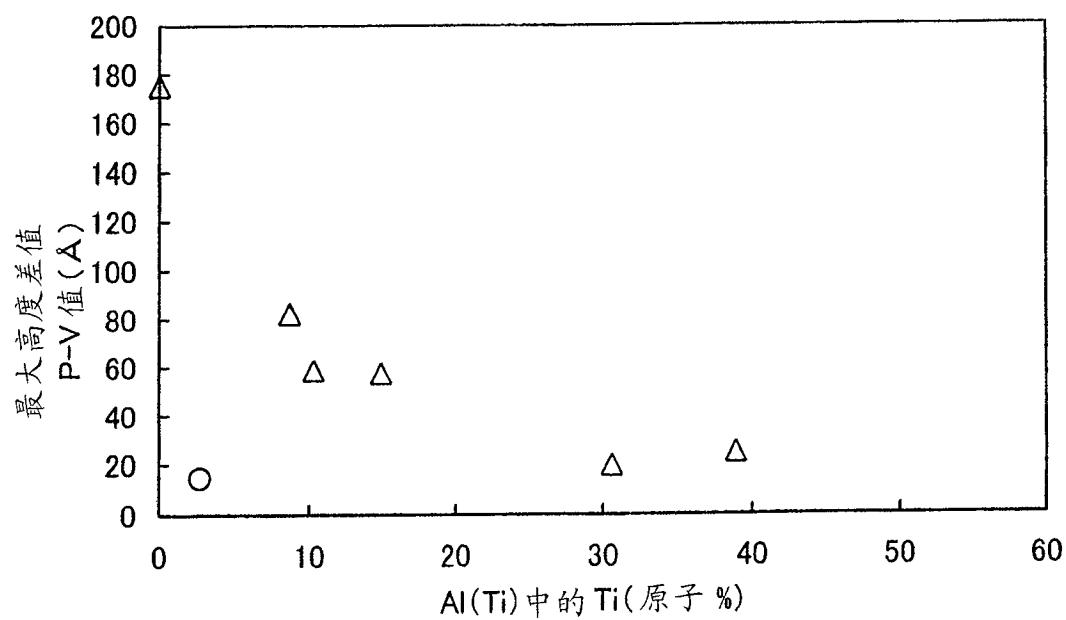

- [0039] 图 23A-23C 分别为实施方案 1 的样品的试验数据的曲线图。

- [0040] 图 24A 和 24B 分别为实施方案 1 的样品的试验数据的曲线图。

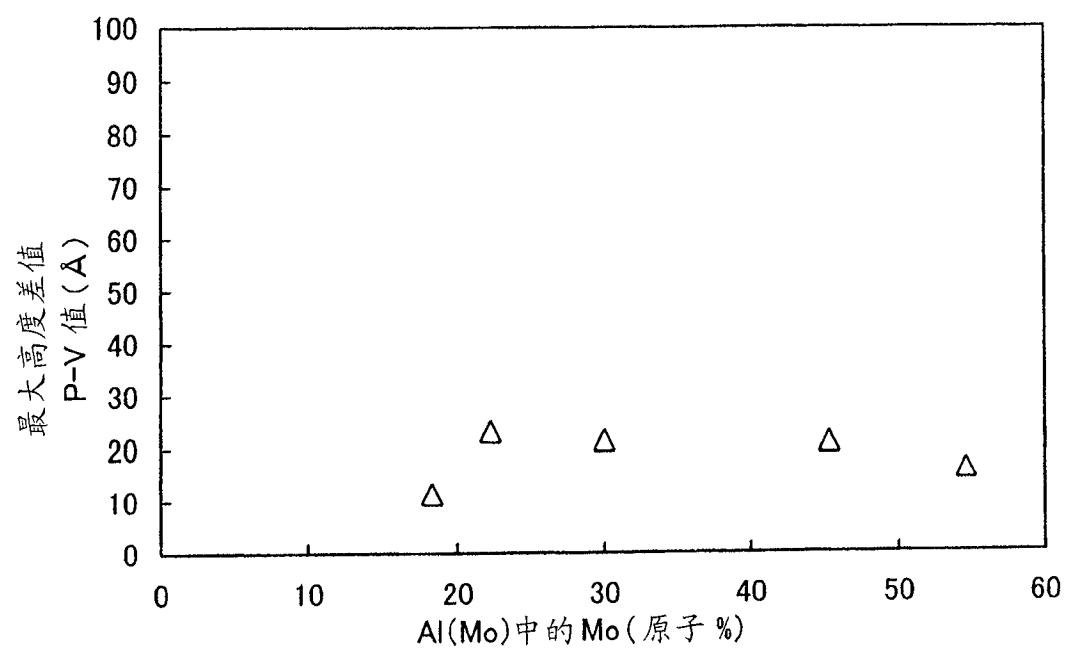

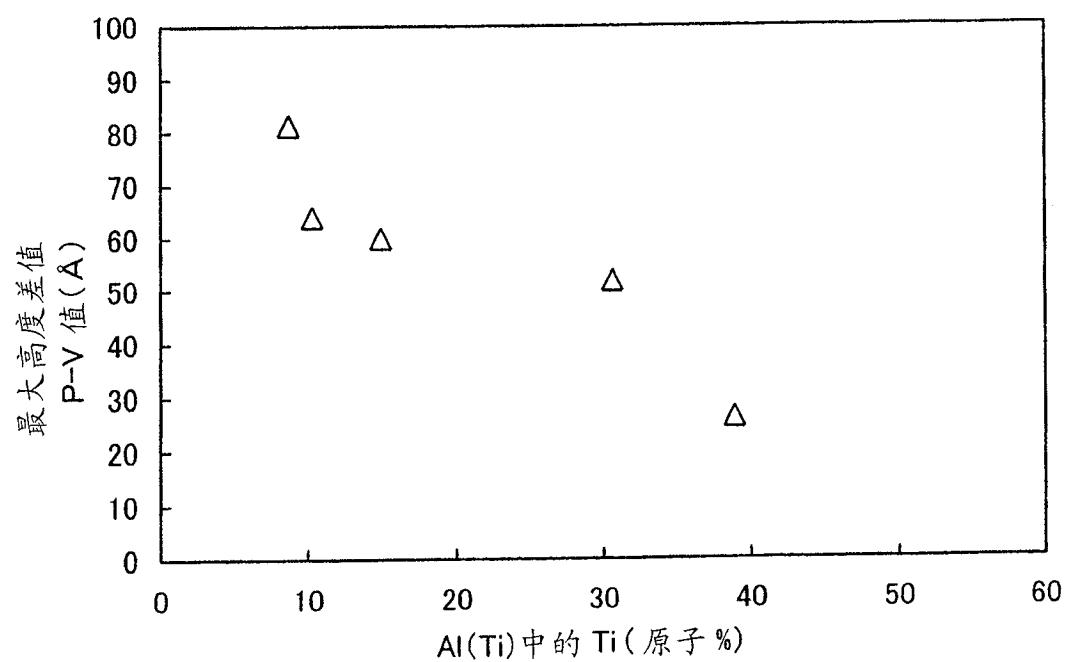

- [0041] 图 25A 和 25B 分别为实施方案 1 的样品的试验数据的曲线图。

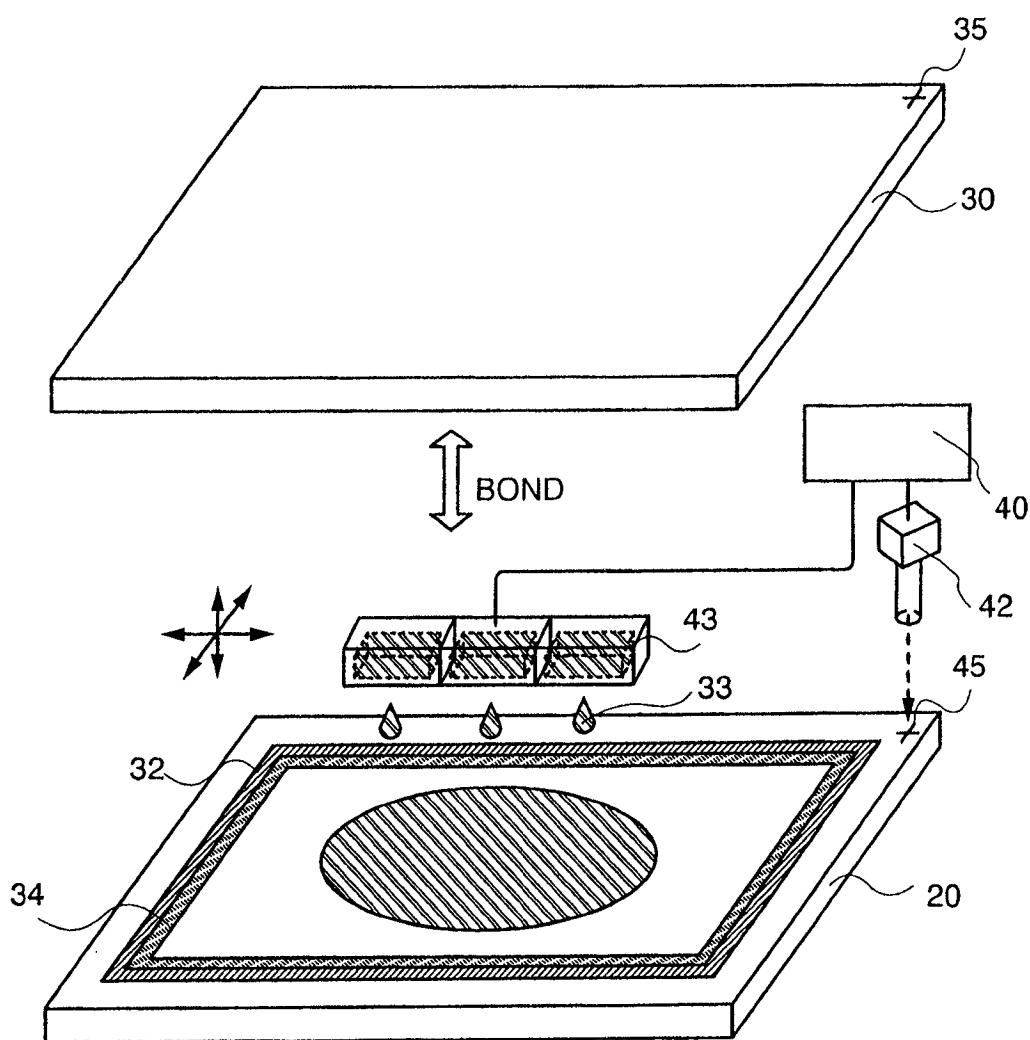

- [0042] 图 26 显示了可应用于本发明的滴注法。

- [0043] 图 27 为应用本发明的电子设备的主要结构的框图。

## 具体实施方式

[0044] 本发明的实施方式和实施例将参照附图进行具体的描述。但是，本发明不限于下面的描述，并且本领域技术人员容易理解在不脱离本发明内容和范围内，可以对本发明作出各种变化和修改。因而，本发明将通过下述非限定性的实施方式和实施例的描述得到解释。需要注意的是，在下述本发明的结构中，不同附图中相同的参照数字表示相同的部分或者具有相似功能的部分，且注释不会再重复。

### [实施方式 1]

[0046] 本实施方式的显示器件将参照图 1A 和 1B 进行描述。

[0047] 如图 1A 和 1B 所示，根据本实施方式的显示器件为顶端发光的显示器件，其中光从密封基底透出。图 1A 和 1B 的显示器件为具有不同结构的发光元件的实例。

[0048] 图 1A 中的显示器件包括：在基底 600 上的基膜 601a、基膜 601b、薄膜晶体管 605、栅绝缘层 602、绝缘层 603、绝缘层 606、绝缘层 607、夹层膜 608、用作存储单元的绝缘层 609、第一电极层 610、电致发光层 611、第二电极层 612 以及保护膜 613。薄膜晶体管 605 包括具有用作源区域和漏区域的杂质区域的半导体层、栅绝缘层 602、双层结构的栅极层、源极层以及漏极层。所述源极层或漏极层 604 电连接至半导体层的杂质区域，使其与第一电极层 610 接触。

[0049] 在本实施方式的显示器件中，第一电极层 610 为反射电极层，其反射从发光元件

614 发出的光。因而,光从第二电极层 612 沿箭头方向发出。因此,用作发光元件的像素电极的反射电极层需要具有高反射性和良好的表面平坦性。

[0050] 在本发明中,包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜用于第一电极层 610,其用作反射电极层。在本实施方式中,使用的是包含含有钼的铝合金的膜(下文也称 Al(Mo) 膜)。包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜在热处理下几乎不结晶并且在膜表面上具有良好的平坦性。而且,所述膜即使对接近可见光区域内的光也具有高的反射率,因而可以产生高效率的光反射。该包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜为无毒的并且对人和环境无害,这些都是优点。

[0051] 此外,含有镍的铝合金具有低的耐化学溶液性,例如用于形成绝缘层 609 的显影液,所述绝缘层用作存储单元,其覆盖一部分第一电极层 610。另一方面,本发明包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜具有高的耐化学性。特别是,包含含有钛的铝合金的膜(下文也称 Al(Ti) 膜)和包含含有 20 原子%或更多钼的铝合金的膜具有高的耐化学溶液性;因而,通过使用上述膜,在制备过程中诸如表面积减少或表面粗糙度减少的缺点几乎不发生。因此,可以保持良好的表面条件,使得其上形成的电致发光层 611 可以稳定的形成,从而可以增加显示器件的可靠性。自然地,具有高耐腐蚀性的显影液优选被用作显影液,这是有效的。而且,如果在包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜中,钼或钛的含量增加,预计可以抑制从发光元件发出的光的偏振。

[0052] 在包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜中,钼或钛的含量优选超过 7.0 原子%。而且,当所述包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜中,钼或钛的含量为 20 原子%或更低,可以得到对可见光区域内的光具有高反射率的优点。在包含含有碳的铝合金膜(下文也称 Al(C) 膜)中,碳的含量可以为 0.1 原子% -10 原子%,优选低于 1 原子%。在包含含有钼和碳的铝合金的膜以及包含含有钛和碳的铝合金的膜中,即使碳的含量是微小的,也可以达到效果;所述碳的含量可以为 0.3 原子%或更低或者甚至为 0.1 原子%或更低。

[0053] 包含含有钛的铝合金的膜也称为包含钛 - 铝合金的膜,包含含有碳的铝合金的膜也称为铝合金碳膜或者铝 - 碳合金膜。

[0054] 在本实施方式中,基底 600 用玻璃基底形成,基膜 601a 用氮氧化硅膜形成,基膜 601b 用氧氮化硅膜形成,栅绝缘层 602 用氧氮化硅膜形成,绝缘层 603 用氮氧化硅膜形成,绝缘层 606 用氧化硅膜形成,绝缘层 607 用含有烷基的氧化硅膜形成,夹层膜 608 用氮氧化硅膜形成,用作存储单元的绝缘层 609 包含聚酰亚胺,以及保护膜 613 用氮氧化硅膜形成。夹层 608 用来提高电极层 610 和绝缘层 607 的粘合力。

[0055] 可用于本实施方式的发光元件 614 的结构将参照附图 18A 和 18B 进行具体描述。在图 18A 和 18B 中,第一电极层 870 对应于图 1A 中的第一电极层 610,电致发光层 860 对应于电致发光层 611,以及第二电极层 850 对应于第二电极层 612。

[0056] 图 18A 和 18B 分别显示了本发明的发光元件的元件结构,其中是有机化合物和无机化合物的混合物的电致发光层 860 设置在第一电极层 870 和第二电极层 850 之间。如图所示,所述的电致发光层 860 包括第一层 804、第二层 803 以及第三层 802。第一层 804 和第三层 802 具有特殊的特征。

[0057] 首先,第一层 804 具有向第二层 803 传输空穴的功能,并且包括至少第一有机化合

物和能够对第一有机化合物表现出电子接受能力的第一无机化合物（充当电子受体）。重要的是第一无机化合物不仅与第一有机化合物混合，而且对第一有机化合物表现出电子接受能力（充当电子受体）。所述结构在本来几乎没有固有的载体的第一有机化合物中产生大量的空穴载体，从而提供了优异的空穴注入和 / 或空穴传输性能。

[0058] 因而，第一层 804 不仅提供了据认为是通过混合无机化合物带来的优点（例如，改善了耐热性），而且提供了优异的电导率（特别是，在第一层 804 中的空穴注入和 / 或传输能力）。该优异的电导率是不能从常规的空穴传输层得到的优点，常规的空穴传输层中，没有电子相互作用的有机化合物和无机化合物之间只是简单的混合。所述优点使得驱动电压比以前降低更多成为可能。另外，由于第一层 804 在不增加驱动电压的情况下，可以增厚，从而使得由于灰尘等造成的元件的短路也可以抑止。

[0059] 同时，由于如上所述在第一有机化合物中产生空穴载体，所以优选使用空穴 - 传输有机化合物作为第一有机化合物。空穴 - 传输有机化合物的实例包括，但是不限定于：酞菁染料（缩写 :H<sub>2</sub>Pc），酞菁铜（缩写 :CuPc），酞菁氧钒（缩写 :VOPc），4,4',4''- 三 (N,N- 二苯基氨基) - 三苯胺（缩写 :TDATA），4,4',4''- 三 [N-(3- 甲基苯基) - N- 苯基氨基] - 三苯胺（缩写 :MTDATA），1,3,5- 三 [N,N- 二 (间甲苯基) 氨基] 苯（缩写 :m-MTDAB），N,N' - 二苯基 - N,N' - 双 (3- 甲基苯基) - 1,1' - 二苯基 - 4,4' - 二胺（缩写 :TPD），4,4' - 双 [N-(1- 萍基) - N- 苯基氨基] 联苯（缩写 :NPB），4,4' - 双 {N-[4- 二 (间甲苯基) 氨基] 苯基 - N- 苯基氨基} 联苯（缩写 :DNTPD）以及 4,4',4''- 三 (N- 吡唑基) 三苯胺（缩写 :TCATA）。另外，在上述化合物中，TDATA、MTDATA、m-MTDAB、TPD、NPB、DNTPD 和 TCATA 这些芳族胺化合物容易产生空穴载体，适宜用作第一有机化合物的化合物。

[0060] 另一方面，第一无机化合物可以为任何材料，只要该材料容易从第一有机化合物接受电子，可以使用各种金属氧化物和金属氮化物。但是，由于容易提供电子接受能力，具有周期表中族 4-12 的任一种过渡金属的过渡金属氧化物为优选的。特别地，所述过渡金属氧化物包括氧化钛、氧化锆、氧化钒、氧化钼、氧化钨、氧化铼、氧化钌以及氧化锌。此外，在上述金属氧化物中，许多含有族 4-8 任一种过渡金属的过渡金属氧化物具有更高的电子接受能力，它们为优选的化合物。特别地，氧化钒、氧化钼、氧化钨和氧化铼为优选的，这是因为上述氧化物容易用于真空沉积。

[0061] 需要注意的是所述第一层 804 可以通过多层迭加来形成，每层包括上述有机化合物和无机化合物的组合，或者还可以包括另一种有机化合物或无机化合物。

[0062] 接着，将描述第三层 802。第三层 802 为具有向第二层 803 传输电子的功能的层，包括至少第三有机化合物和对第三有机化合物表现出电子给予能力的第三无机化合物（充当电子给体）。重要的是第三无机化合物不仅与第三有机化合物混合，而且对第三有机化合物表现出电子给予能力（充当电子给体）。所述结构在本来几乎没有固有载体的第三有机化合物中产生大量的空穴载体，从而提供了优异的电子注入和 / 或电子传输能力。

[0063] 因此，第三层 802 不仅提供了据认为是通过混合无机化合物带来的优点（例如，改善了耐热性），而且提供了优异的电导率（特别是，在第三层 802 中的电子注入和 / 或传输能力）。该优异的电导率是不能从常规的电子传输层得到的优点，常规的电子传输层中没有电子相互作用的有机化合物和无机化合物之间只是简单的混合。所述优点使得驱动电压比以前降低更多成为可能。另外，由于第三层 802 在不增加驱动电压的情况下，可以增厚，从

而使得由于灰尘等造成的元件的短路也可以抑止。

[0064] 同时,由于如上所述在第三有机化合物中产生电子载体,所以优选使用电子 - 传输有机化合物作为第三有机化合物。电子 - 传输有机化合物的实例包括,但是不限定于:三(8-喹啉)铝(缩写:Alq<sub>3</sub>),三(4-甲基-8-喹啉)铝(缩写:Almq<sub>3</sub>)、双(10-羟基苯[h]喹啉)铍(缩写:BeBq<sub>2</sub>),双(2-甲基-8-喹啉)(4-苯基苯酚)铝(缩写:BA1q),双[2-(2'-羟基苯基)-苯并噁唑]锌(缩写:ZnBOX)或者双[2-(2'-羟基苯基)-苯并噁唑]锌(缩写:Zn(BTZ)<sub>2</sub>),红菲咯啉(缩写:BPhen),浴铜灵(缩写:BCP),2-(4-双苯基)-5-(4-叔丁基苯基)-1,3,4-噁二唑(缩写:PBD),1,3-双[5-(4-叔丁基苯基)-1,3,4-噁二唑-2-基]苯(缩写:OXD-7),2,2',2''-(1,3,5-苯三基(benzenetriyl))-三(1-苯基-1H-苯并咪唑)(缩写:TPBI),3-(4-二苯基)-4-苯基5-(4-叔丁基苯基)-1,2,4-三唑(缩写:TAZ),以及3-(4-二苯基)-4-(4-乙基苯基)-5-(4-叔丁基苯基)-1,2,4-三唑(缩写:p-EtTAZ)。另外,在上述化合物中,容易产生电子载体的有:具有包括芳环的螯合配体的金属螯合配合物,典型为Alq<sub>3</sub>、Almq<sub>3</sub>、BeBq<sub>2</sub>、BA1q、Zn(BOX)<sub>2</sub>以及Zn(BTZ)<sub>2</sub>;具有菲咯啉骨架的有机化合物,典型为BPhen和BCP,以及具有噁二唑骨架的有机化合物,典型为PBD和OXD-7,它们适宜用作第三有机化合物。

[0065] 另一方面,第三无机化合物可以为任何材料,只要该材料容易从第三有机化合物给予电子即可,可以使用各种金属氧化物和金属氮化物。但是,由于容易提供电子给与能力,碱金属氧化物、碱土金属氧化物、稀土金属氧化物、碱金属氮化物、碱土金属氮化物以及稀土金属氮化物是优选的。特别地,上述氧化物的实例包括:氧化锂、氧化锶、氧化钡、氧化铕、氮化锂、氮化镁、氮化钙、氮化钇和氮化镧。特别地,氧化锂、氧化钡、氮化锂、氮化镁和氮化钙为优选的,这是因为这些氧化物和氮化物容易真空沉积。

[0066] 需要注意的是所述第三层802可以通过多层迭加来形成,每层包括上述有机化合物和无机化合物的组合,或者还可以包括另一种有机化合物或无机化合物。

[0067] 接着,将描述第二层803。所述第二层803为具有发光功能的层,并包括发光的第二有机化合物。此外还可以包括第二无机化合物。第二层803可以使用不同发光有机化合物和无机化合物中的一些来形成。但是,由于与第一层804或第三层802相比,人们认为难以在第二层803上施加电流,因此优选第二层803的厚度约为10-100nm。

[0068] 第二有机化合物没有特别的限定,只要使用的是发光有机化合物即可,且第二有机化合物的实例包括:9,10-二(2-萘基)蒽(缩写:DNA),9,10-二(2-萘基)-2-叔丁基蒽(缩写:t-BuDNA),4,4'-双(2,2-二苯基乙烯基)联苯(缩写:DPVBi),香豆素30,香豆素6,香豆素545,香豆素545T,茈,红荧烯,periflathene,2,5,8,11-四(叔丁基)茈(缩写:TBP),9,10-二苯基蒽(缩写:DPA),4-(二氰基亚甲基)-2-甲基[对(二甲基氨基)苯乙烯基]-4H-吡喃(缩写:DCM1),4-(二氰基亚甲基)-2-甲基-6-[2-(久洛里定-9-基)乙烯基]-4H-吡喃(缩写:DCM2),以及4-(二氰基亚甲基)-2,6-双[对(二甲基氨基)苯乙烯基]-4H-吡喃(缩写:BisDCM)。另外,也可以使用能产生荧光的化合物,例如双[2-(4',6'-二氟苯基)吡啶-N,C<sup>2'</sup>]铱(吡啶甲酸盐)(缩写:FIrpic),双{2-[3',5'-双(三氟甲基)苯基]吡啶-N,C<sup>2'</sup>}铱(吡啶甲酸盐)(缩写:Ir(CF<sub>3</sub>ppy)<sub>2</sub>(pic)),三(2-苯基吡啶-N,C<sup>2'</sup>)铱(缩写:Ir(ppy)<sub>3</sub>),双(2-苯基吡啶-N,C<sup>2'</sup>)铱(乙酰基丙酮盐)(缩写:Ir(ppy)<sub>2</sub>(acac)),双[2-(2'-噻吩基)吡啶-N,C<sup>2'</sup>]铱(乙酰基丙酮盐)(缩写:

Ir(thp)<sub>2</sub>(acac))，双(2-苯基喹啉-N,C<sup>2</sup>)铱(乙酰基丙酮盐)(缩写:Ir(pq)<sub>2</sub>(acac))以及双[2-(2'-苯基噻吩基)吡啶-N,C<sup>3</sup>]铱(乙酰基丙酮盐)(缩写:Ir(btp)<sub>2</sub>(acac))。

[0069] 此外，含有金属配合物或类似物的三重态发光材料以及单一态发光材料可以用于第二层803。例如，在发出红、绿和蓝光的像素中，在相当短的时间内亮度减半的发出红光的像素由三重态发光材料形成，且余下的由单一态发光材料形成。三重态发光材料具有良好的发光效率，并且得到相同的亮度时具有更低的能耗。当三重态发光材料用作红色像素时，仅需要给发光元件提供小量的电流。因而，可以提高可靠性。为了得到低的能耗，发出红光的像素和发绿光的像素可以由三重态发光材料形成，且发出蓝光的像素可以由单一态发光材料形成。低能耗还可以通过形成发出高可见度的绿光的发光元件来得到，该发光元件使用三重态发光材料得到。

[0070] 此外，第二层803不仅包括上述发光的第二有机化合物，而且还可以加入另一种有机化合物。可以加入的有机化合物的实例包括，但是不限定于：上述的TDATA、MTDATA、m-MTDAB、TPD、NPB、DNTPD、TCTA、Alq<sub>3</sub>、Almq<sub>3</sub>、BeBq<sub>2</sub>、BA1q、Zn(BOX)<sub>2</sub>、Zn(BTZ)<sub>2</sub>、BPhen、BCP、PBD、OXD-7、TPBI、TAZ、p-EtTAZ、DNA、t-BuDNA以及DPVBi，还有4,4'-双(N-咔唑基)-联苯(缩写:CBP)和1,3,5-三[4-(N-咔唑基)-苯基]苯(缩写:TCPB)。需要注意的是，除第二有机化合物之外、还附加的有机化合物优选为比该第二有机化合物具有更大激发能的有机化合物，并且加入量超过该第二有机化合物，以使得第二有机化合物有效地发光(其使得阻止该第二有机化合物的浓度猝灭成为可能)。此外，作为另一种功能，附加的有机化合物可以与第二有机化合物一起发光。

[0071] 通过使每个像素的发光层具有不同发射波长范围，第二层803可以具有形成彩色显示的结构。通常，形成对应于R(红色)、G(绿色)或B(蓝色)每种颜色的发光层。此时，通过在像素的发光侧提供能透过一定发射波长范围的光的滤光片，色纯度可以提高且可以阻止像素部分产生镜面(反射)。通过提供滤光片，常规所需的圆形起偏振片或类似物可以省略，而且从发光层发出的光的损失可以消除。并且当倾斜地看像素部分(显示屏)时，发生的色调变化可以减少。

[0072] 高分子量发光材料或低分子量发光材料可以用作第二层803的材料。高分子量有机发光材料比低分子量材料在物理意义更强，在元件的耐久性上占优势。此外，高分子量有机发光材料可以通过涂覆形成；因而元件的制造相对容易。

[0073] 发出的颜色取决于形成发光层的材料，因而显示所需发光的发光元件可以通过选择合适的发光层材料来形成。作为形成发光层的高分子量电致发光材料，可以使用基于聚对亚苯基-亚乙烯基的材料、基于聚对亚苯基的材料、基于聚噻吩的材料或者基于聚芴的材料。

[0074] 作为基于聚对亚苯基-亚乙烯基的材料，可以使用聚(对亚苯基亚乙烯基)[PPV]衍生物，例如，聚(2,5-二烷氧基1,4-亚苯基亚乙烯基)[RO-PPV]；聚(2-(2'-乙基-己氧基)-5-甲氧基-1,4-亚苯基亚乙烯基)[MEH-PPV]；聚(2-(二烷氧基苯基)-1,4-亚苯基亚乙烯基)[ROPh-PPV]等。作为基于聚对亚苯基的材料，可以使用聚对亚苯基[PPP]的衍生物，例如，聚(2,5-二烷氧基-1,4-亚苯基)[RO-PPP]；聚(2,5-二己氧基-1,4-亚苯基)等。作为基于聚噻吩的材料，可以使用聚噻吩[PT]衍生物，例如，聚(3-烷基噻吩)[PAT]；聚(3-己基噻吩)[PHT]；聚(3-环己基噻吩)[PCHT]；聚(3-环己基-4-甲基噻吩)[PCHMT]；

聚(3,4-二环己基噻吩)[PDCHT]；聚[3-(4-辛基苯基)噻吩][POPT]；聚[3-(4-辛基苯基)-2,2-双噻吩][PTOPT]等。作为基于聚芴的材料，可以使用聚芴[PF]衍生物，例如，聚(9,9-二烷基芴)[PDAF]；聚(9,9-二辛基芴)[PDOF]等。

[0075] 第二无机化合物可以使用任何无机材料，只要第二有机化合物的发光不易被该无机化合物猝灭即可，可以使用各种金属氧化物、金属氮化物。特别是，由于第二有机化合物的发光不易被猝灭，含有周期表13族或14族金属的金属氧化物为优选的，特别是氧化铝、氧化镓、氧化硅和氧化锗是优选的。但是，第二无机化合物不限定于此。

[0076] 需要注意的是所述第二层803可以通过多层迭加来形成，每层包括上述有机化合物和无机化合物的组合，或者还包括另一种有机化合物或无机化合物。

[0077] 上述材料形成的发光元件通过施加正向偏压来发光。发光元件形成的显示器件的像素可以通过简单的矩阵模式或有源矩阵模式来驱动。无论如何，每个像素通过其上施加的正向偏压在特定的计时发光；但是，像素在某时期是非发光态的。在非发光时间通过施加反向偏压可以提高发光元件的可靠性。在发光元件中，存在一种变劣模式，其中在特定的驱动条件下，发射强度降低，或者这样一种变劣模式，其中像素中的非发光区域扩大且亮度明显降低。但是，通过施加正向和反向偏压处的交替电流驱动，可以使得恶化的趋势减缓。从而可以提高发光器件的可靠性。另外，可以施加数字驱动和模拟驱动中的任一种。

[0078] 彩色滤光片(着色层)可以在密封基底上形成。该彩色滤光片(着色层)可以通过沉积法或滴状喷射法(droplet discharge method)形成。通过使用彩色滤光片(着色层)，也可以完成高清晰度的显示。这是因为在每个RGB的发光光谱上，宽峰可以变得陡峭。

[0079] 全色显示可以通过形成显示单一色彩的材料并结合彩色滤光片以及彩色转换层来完成。所述的彩色滤光片(着色层)或彩色转换层例如，可以形成在第二基底(密封基底)上，并可以与基底附着。

[0080] 自然地，显示也可以在单色下完成。例如，通过使用单色发射，可以制备区域彩色型(area color type)显示器件。所述区域彩色型适宜于无源矩阵型显示区域，且可以主要显示字符和符号。

[0081] 选择第一电极层870和第二电极层850的材料时，需要考虑功函。取决于像素结构，第一电极层870和第二电极层850可以为阳极或阴极。在本实施方式中，如图18A所示，当驱动晶体管具有p型电导率时，则第一电极层870可优选用作阳极，且第二电极层850可用作阴极。如图18B所示，由于驱动TFT具有n型电导率，则第一电极层870可优选为阴极且第二电极层850可用作阳极。将描述可以用于第一电极层870或第二电极层850的材料。优选使用具有较大功函的材料(特别是功函为4.5eV或更大的材料)来制备用作阳极的第一电极层870和第二电极层850中的一个，具有较小功函(特别是功函为3.5eV或更大)的材料来制备用作阴极的另一个。但是，由于第一层804和第三层802各自在空穴注入和/或传输能力以及电子注入和/或传输能力上占优势，第一电极层870或第二电极层850的功函很少有限定，各种材料均可以用于第一电极层870和第二电极层850。

[0082] 第二电极层850具有透光性能。在此情况下，可以特别地使用透明导电膜，可以使用氧化铟锡(ITO)、氧化铟锌(IZO)、掺杂有氧化硅的氧化铟锡(ITSO)等。而且，即使使用金属膜，通过使金属膜变薄(优选约5nm-30nm)至透光，光可以从第二电极层850透出。含有钛、钨、镍、金、铂、银、铝、镁、钙或锂的导电膜，含有上述金属的合金的导电膜等可以用于

第二电极层 850。而且,第一电极层 870 和第二电极层 850 可以由含有铝合金的膜和上述透明导电膜叠加形成,所述铝合金含有选自钼、钛和碳中的至少一种或多种。当 ITS0 或 ITS0 透明导电膜用于第二电极层 850 时,其可以形成在 BzOs-Li 膜上,其中 Li 被加入至苯并噁唑衍生物 (BzOs) 中,或可以使用类似物。

[0083] 需要注意的是,通过改变第一电极层 870 和第二电极层 850 的类型,根据本发明的发光元件具有不同的变化形式。

[0084] 图 1B 显示了在电致发光层 860 中,从第一电极层 870 侧依次设置的第三层 802、第二层以及第一层 804 的情形。

[0085] 如上所述,在根据本发明的发光元件中,插入在第一电极层 870 和第二电极之间的层由电致发光层 860 组成,其中结合有有机化合物和无机化合物。该发光元件为新型有机 - 无机组合物发光元件,具有通过混合有机化合物和无机化合物来提供一种称为高载体注入和 / 或载体传输性能的功能的多层(也就是第一层 804 和第三层 802),所述功能不能仅从有机化合物或仅从无机化合物得来。而且,当设置在用作反射电极的第一电极层 870 侧时,第一层 804 和第三层 802 特别需要是结合有机化合物和无机化合物的层,当设置在第二电极层 850 侧时,可以仅仅含有有机化合物或无机化合物。

[0086] 而且,各种已知的方法可以用作形成混有有机化合物和无机化合物的电致发光层 860 的方法。例如,已知的方法包括:通过电阻加热,使有机化合物和无机化合物都蒸发的共蒸发法。此外,在共蒸发法中,无机化合物可以通过电子束 (EB) 来蒸发,而有机化合物可以通过电阻加热来蒸发。此外,已知的方法也包括这样的方法:溅射无机化合物,而通过电阻加热蒸发有机化合物来同时沉积二者。另外,沉积可以通过湿法完成。

[0087] 此外,对于第一电极层 870 和第二电极层 850,通过电阻加热的蒸发、EB 蒸发、溅射、湿法等同样可以使用。

[0088] 图 1B 中的显示器件包括:在基底 620 上的基膜 621a、基膜 621b、薄膜晶体管 625、栅绝缘层 622、绝缘层 623、绝缘层 626、绝缘层 627、夹层膜 628、夹层膜 636、用作存储单元的绝缘层 629、第一电极层 630、透明导电膜 635、电致发光层 631、第二电极层 632 以及保护膜 633。薄膜晶体管 625 包括具有用作源区域和漏区域的杂质区域的半导体层;栅绝缘层 622、双层结构的栅极层;源极层以及漏极层。所述源极层或漏极层 624 电连接至半导体层的杂质区域,使其与第一电极层 630 接触。

[0089] 图 1B 的显示器件中的发光元件 634 包括:第一电极层 630、透明导电膜 635、电致发光层 631 以及第二电极层 632。第一电极层 630 和透明导电膜 635 形成层叠结构。包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜用于第一电极层 630。ITS0 膜用于透明导电膜 635。如图 1B 所示,当透明导电膜 635 具有层叠结构时,第一电极层 630 可以被保护,这样可以提高产量。而且,薄至透光的银制薄膜可以用于第二电极层 632。

[0090] 图 1B 中的其它部件可以使用与图 1A 相同的材料并且以相同的方式制备。在图 1B 的显示器件中,夹层膜 628 为氮氧化硅膜,且夹层膜 636 为氮化钛膜。夹层 628 和夹层 636 形成在绝缘层 627 和第一电极层 630 之间;因而可以提高绝缘层 627 和第一电极层 630 之间的粘结力。并且氮化钛膜有助于静电保护。也可以用于绝缘层 627 的含有烷基的氧化硅膜可以较薄的厚度设置在用于夹层膜的氮氧化硅膜和氮化钛膜之间。

[0091] 因而,通过实施本发明,具有高可靠性的显示器件可以通过简单的步骤制备。因此

可以低成本、高产量的制备具有高清晰度和图像品质的显示器件。

[0092] [ 实施方式 2]

[0093] 根据本实施方式的显示器件的制备方法将参照图 2A-7B、16A-16C 以及 17A 和 17B 进行具体描述。

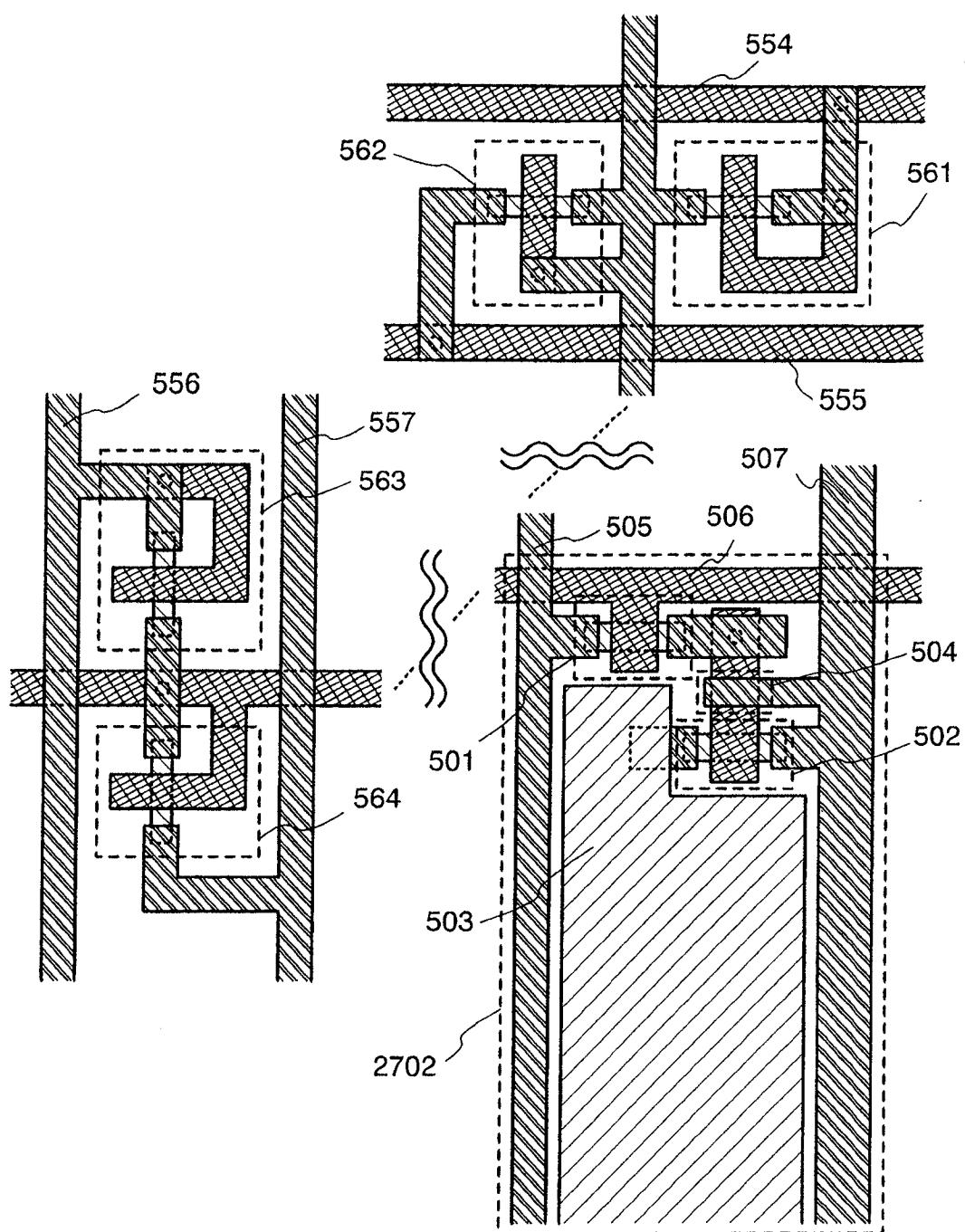

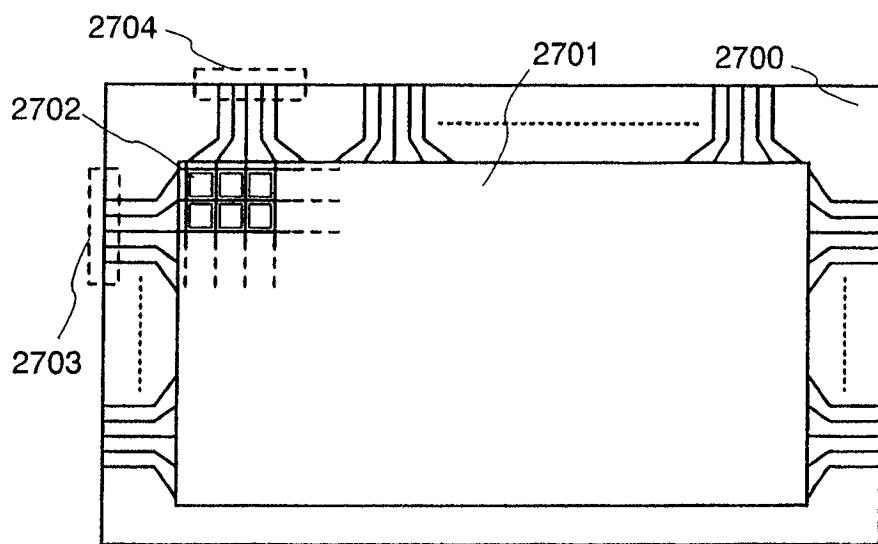

[0094] 图 16A 为根据本发明的显示板的结构的顶视图,该显示板包括像素部分 2701(其中像素 2702 排列在矩阵里)、形成在具有绝缘表面的基底 2700 上的扫描线侧输入终端 2703 和信号线侧输入终端 2704。像素的数目可以根据不同的标准设置,例如,在 XGA 中  $1024 \times 768 \times 3$  (RGB), 在 UXGA 中  $1600 \times 1200 \times 3$  (RGB) 以及在使用全规格高清晰显示器中的  $1920 \times 1080 \times 3$  (RGB)。

[0095] 像素 2702 排列在从扫描线侧输入终端 2703 延伸的扫描线和从信号线侧输入终端 2704 延伸的信号线交叉处的矩阵上。每个像素 2702 提供有开光元件并且其上连接有像素电极层。开光元件的典型实例为 TFT。TFT 的栅极层侧连接至扫描线,源侧或漏侧连接至信号线,因此每个像素可以通过从外部输入的信号分别控制。

[0096] TFT 的主要部件包括半导体层、栅绝缘层和栅极层。还设置有连接至形成在半导体层中的源区域和漏区域的配线层。通常已知的是顶端栅结构,其中半导体层、栅绝缘层和栅极层从基底侧设置,已知的还有底端栅结构,其中栅极层,栅绝缘层和半导体层从基底侧设置,以及其它的结构,本发明可以采用上述任一种结构。

[0097] 图 16A 显示了显示板的结构,其中信号输入至信号线且信号线通过外部驱动电路控制,但是,驱动器 IC 2751 可以通过 COG (玻璃上的芯片) 方法安装在基底 2700 上,如图 17A 所示。此外,如图 17B 所示的另一种模式 TAB (带式自动键合) 方法也可以采用。驱动器 IC 可以形成在单晶半导体基底或玻璃基底上,所述基底上通过 TFT 形成电流。在图 17A 和 17B 中,驱动器 IC 2751 连接至 FPC (挠性印刷电路) 2750 上。

[0098] 此外,当使用晶体半导体在像素里形成 TFT 时,扫描线侧驱动电路 3702 可以在基底 3700 集成,如图 16B 所示。在图 16B 中,像素部分 3701 通过与图 16A 相似的外部驱动电路来控制,其中像素部分 3701 连接至信号线侧输入终端 3704。当使用具有高迁移率的多晶(微晶)半导体、单晶半导体等在像素里形成 TFT 时,像素部分 4701、扫描线驱动电路 4702 以及信号线驱动电路 4704 可以在基底 4700 上集成。

[0099] 作为具有绝缘表面的基底 100 上的基膜,氮氧化硅膜 (SiNO) 通过溅射法、PVD 法 (物理气相沉积) 和诸如低压 CVD 法 (LPCVD 法) 或等离子 CVD 法的 CVD 法 (化学气相沉积),形成厚度为  $10\text{--}200\text{nm}$  (优选  $50\text{--}100\text{nm}$ ) 的基膜 101a,并且氧氮化硅膜 (SiON) 形成厚度为  $50\text{--}200\text{nm}$  (优选  $100\text{--}150\text{nm}$ ) 的基膜 101b。在本实施方式中,基膜 101a 和基膜 101b 通过等离子 CVD 法形成。基底 100 可以为表面覆盖有绝缘膜的玻璃基底、石英基底、硅基底、金属基底或不锈钢基底。而且,可以耐本实施方式的加工温度的塑料基底或诸如膜的柔性基底也可以使用。作为塑料基底,可以使用由 PET (聚对苯二甲酸乙二酯)、PEN (聚萘二甲酸乙二酯) 或 PES (聚醚砜) 形成的基底,而诸如丙烯酸的合成树脂可用作柔性基底。

[0100] 作为基膜,氧化硅、氮化硅、氧氮化硅、氮氧化硅等可以以单层或者两层或三层的叠层形式使用。需要注意的是,氧氮化硅含有的氧的含量高于氮的含量,也可以称为含有氮的氧化硅。类似地,氮氧化硅含有的氮的含量高于氧的含量,可以被称为含有氧的氮化硅。在本实施方式中,氮氧化硅膜使用  $\text{SiH}_4$ 、 $\text{NH}_3$ 、 $\text{N}_2\text{O}$ 、 $\text{N}_2$  和  $\text{H}_2$  作为反应气体形成  $50\text{nm}$  的厚度,

而氧氮化硅膜使用  $\text{SiH}_4$  和  $\text{N}_2\text{O}$  作为反应气体形成 100nm 的厚度。另外，氮氧化硅膜的厚度可以是 140nm，并且将被叠置的氧氮化硅膜的厚度可以是 100nm。

[0101] 接着，在基膜上形成半导体膜。所述半导体膜可以通过已知方法（溅射法、LPCVD 法、等离子 CVD 法等）形成 25–200nm（优选 30–150nm）的厚度。在本实施方式中，优选使用通过激光辐照无定形半导体膜而使之结晶制得的结晶性半导体膜。

[0102] 形成半导体膜的材料可以为：通过使用典型为硅烷和锗烷的半导体材料气体、用真空沉积法和溅射法形成的无定形半导体（下文也称为“无定形半导体：AS”）、通过使用光能和热能而使无定形半导体结晶形成的多晶半导体、或者为半无定形半导体（也称为微晶且下文称为“SAS”）等。

[0103] SAS 为具有介于无定形和结晶（包括单晶和多晶）结构之间的中间结构且具有在自由能下稳定的第三态的半导体。而且，SAS 为具有短距离有序和晶格畸变的结晶性半导体，并且通过将直径为 0.5–20nm 的晶粒分散在膜的至少一部分来形成。当含有硅作为主要组分时，SAS 的拉曼光谱向低于  $520\text{cm}^{-1}$  的波数位移。通过 X 射线衍射，在 SAS 膜上观察到认为是源自 Si 晶体晶格的衍射峰 (111) 和 (220)。所述半无定形半导体膜含有至少 1 原子% 或更多的氢和卤素来中止不饱和键。SAS 通过辉光放电沉积硅化物气源（等离子 CVD）来形成。所述硅化物气体通常为  $\text{SiH}_4$ ，也可以为  $\text{Si}_2\text{H}_6$ 、 $\text{SiH}_2\text{Cl}_2$ 、 $\text{SiHCl}_3$ 、 $\text{SiCl}_4$ 、 $\text{SiF}_4$  等。也可以混合  $\text{F}_2$  和  $\text{GeF}_4$ 。所述硅化物气源也可以用  $\text{H}_2$  或  $\text{H}_2$  与诸如 He、Ar、Kr 和 Ne 的一种或多种稀有气体元素的混合气体来稀释。在约 0.1–133Pa 的压力，1–120MHz 的电源频率、更优选 13–60MHz 的高频功率下，所述的硅化物气源优选稀释至 2–1000 倍。加热基底的温度优选为 300°C 或更低，更优选 100–250°C。优选诸如氧、氮和碳的大气组分的杂质作为膜中的杂质元素，浓度为  $1 \times 10^{20}/\text{cm}^3$  或更低。特别地，氧气浓度优选为  $5 \times 10^{19}/\text{cm}^3$  或更低，更优选  $1 \times 10^{19}/\text{cm}^3$  或更低。此外，当诸如 He、Ar、Kr 或 Ne 的稀有气体元素混入 SAS 时，晶格畸变增加因而稳定性增强，从而形成有利的 SAS。而且，作为半导体膜，基于氢的气体形成的 SAS 层可以堆积在基于氟的气体形成的 SAS 层上。

[0104] 作为典型的无定形半导体，可以使用氢化无定形硅，而多晶硅等可以用作结晶性半导体。多晶硅（多晶硅）包括使用在 800°C 或更高加工温度下形成的多晶硅作为主材料制成的所谓高温多晶硅、使用在 600°C 或更低的加工温度下形成的多晶硅作为主材料制成的所谓低温多晶硅、以及通过加入促进结晶的元素来结晶的多晶硅等。勿庸置疑，如上所述的在半无定形半导体中含有结晶相的半导体或者半导体膜也可以使用。

[0105] 当使用结晶性半导体膜作为半导体膜时，该结晶性半导体膜可以通过已知的方法（激光结晶法、热结晶法、使用诸如促进结晶的元素镍的热结晶法等）形成。而且，用作 SAS 的微晶半导体可以通过激光辐照结晶来提高结晶度。当不使用促进结晶的元素时，在将无定形半导体膜用激光辐照之前，所述无定形半导体膜于 500°C 在氮气气氛中加热 1 小时来释放氢气，使得氢气的浓度变为  $1 \times 10^{20}$  原子/ $\text{cm}^3$  或更低。如果所述无定形半导体膜含有大量氢，则在激光辐照下该膜会发生破裂。结晶热处理可以使用退火炉、激光辐照、灯光辐照（也称为灯退火）等来完成。作为热法，可以使用诸如用加热气体的 GRTA（气体快速热退火）法和用灯的 LRTA（利用灯的快速热退火）法的 RTA 法。

[0106] 在无定形半导体膜上引入金属元素的方法没有限定，只要是在无定形半导体膜的表面或内部形成金属元素的方法即可。例如，可以使用溅射法、CVD 法、等离子处理（包括

等离子 CVD 法)、吸收法或者涂覆金属盐溶液的方法。上述方法中, 使用溶液的方法是简单的并且具有容易控制金属元素浓度的优势。理想的是, 在氧气气氛中通过 UV 光辐照、热氧化法、或者通过使用含有羟基的臭氧水或过氧化氢处理等方法形成氧化物膜, 以提高无定形半导体膜表面的可湿性, 从而使水溶液扩散在无定形半导体膜的整个表面上。

[0107] 为了在结晶中得到大晶粒晶体, 优选使用能持续振荡的固态激光器的基波的第二 - 第四谐波。通常使用 Nd:YVO<sub>4</sub> 激光器(基波为 1064nm) 的第二 (532nm) 和第三 (355nm) 谐波。特别是, 通过使用非线性光元件, 从持续振荡型 YVO<sub>4</sub> 激光器发出的激光被转化为谐波, 从而得到输出为数 W 或更高的激光。通过辐照物体的光学系统, 优选使激光在辐照表面形成矩形或椭圆形。此时的能量密度需要约 0.001-100MW/cm<sup>2</sup>(优选 0.1-10MW/cm<sup>2</sup>)。半导体膜以约 0.5-2000cm/sec(优选 10-200cm/sec) 的扫描速率用激光辐照。

[0108] 优选激光束的形状为线性。结果生产量可以提高。而且, 优选入射角  $\theta$  ( $0 < \theta < 90^\circ$ ) 的激光辐照的半导体膜, 从而可以阻止激光干扰。

[0109] 通过相对地扫描所述激光和半导体膜, 可以实现激光辐照。为了以高精度重叠光束并控制起始和结束激光辐照的位置, 可以形成标记。所述标记可以同时形成在基底上作为无定形半导体膜。

[0110] 需要注意的是, 激光器可以为能够持续振荡或脉冲振荡的气相激光器、固态激光器、铜蒸汽激光器、金蒸汽激光器等。所述的气相激光器包括受激准分子激光器、Ar 激光器、Kr 激光器、He-Cd 激光器, 而固态激光器包括 YAG 激光器、YVO<sub>4</sub> 激光器、YLF 激光器、YAlO<sub>3</sub> 激光器、Y<sub>2</sub>O<sub>3</sub> 激光器、玻璃激光器、红宝石激光器、变石激光器、Ti : 蓝宝石激光器等。

[0111] 通过以 0.5MHz 或更高重复率的脉冲激光器可以完成激光结晶, 所述的重复率范围大大高于数十至数百 Hz 的常规重复率范围。据说在脉冲激光器中激光辐照和半导体膜固化之间的时间为数十至数百纳秒。因此, 在使用前置脉冲使半导体膜熔融和通过使用前述范围的重复率固化半导体膜的期间内, 半导体膜可以通过下述激光脉冲辐照。由于固 - 液界面可以在半导体膜上连续迁移, 形成了具有在激光束扫描方向上连续生长的晶粒的半导体膜。特别地, 可以形成在扫描方向上宽度为 10-30 μm 且在垂直于扫描方向上宽度为 1-5 μm 的晶粒聚集体。通过沿着扫描方向伸展的单晶的晶粒形成, 可以形成至少在 TFT 的通道方向几乎没有晶体边界的半导体膜。

[0112] 所述半导体膜可以在诸如稀有气体或氮气的惰性气氛中被辐照。因而, 由于激光辐照引起的半导体膜的表面粗糙可以被抑制, 并且由于界面态密度的变化引起的阈值电压的变化也可以被抑制。

[0113] 无定形半导体膜可以通过热处理和激光辐照的组合来结晶, 或者热处理和激光辐照中一种可以多次实施。

[0114] 在本实施方式中, 通过在基膜 101b 上形成无定形半导体膜并结晶该无定形半导体膜来形成结晶性半导体膜。作为无定形半导体膜, 可以使用用 SiH<sub>4</sub> 和 H<sub>2</sub> 作为反应气体形成的无定形硅。在本实施方式中, 在同样的温度 330℃ 下, 不需中断相同反应腔内的真空, 通过改变反应气体即可连续地形成基膜 101a、基膜 101b 和无定形半导体膜。

[0115] 在除去形成在无定形半导体膜上的氧化物膜以后, 通过在氧气气氛中的 UV 光辐照、热氧化法、或通过含有羟基的臭氧水或过氧化氢溶液等处理, 来形成厚度为 1-5nm 的氧化物膜,。在本实施方式中, Ni 用作促进结晶的元素。含有 10ppm 的 Ni 的醋酸盐的水溶液

通过旋涂法被施加。

[0116] 在本实施方式中,通过 RTA 法于 750℃热处理 3 分钟后,形成在半导体膜上的氧化物膜被除去并施加激光辐照。无定形半导体膜通过前述结晶处理结晶来形成结晶性半导体膜。

[0117] 当使用金属元素来进行结晶时,进行吸杂步骤来减少或除去所述的金属元素。在本实施方式中,使用无定形半导体膜作为吸杂汇点 (gettering sink) 来截获金属元素。首先,通过在氧气气氛中的 UV 光辐照、热氧化法、或者通过含有羟基的臭氧水或过氧化氢处理等方法在结晶性半导体膜上形成氧化物膜。进一步地,无定形半导体膜通过等离子 CVD 法 (本实施方式的条件是 350W 和 35Pa) 形成 50nm 的厚度。

[0118] 随后,在 744℃下通过 RTA 法进行热处理 3 分钟来减少或除去金属元素。热处理可以在氮气气氛中进行。然后,作为吸杂汇点的无定形半导体膜和形成在无定形半导体膜上的氧化物膜通过氢氟酸等除去,从而可以得到其上减少或除去了金属元素的结晶性半导体膜 102(见图 2A)。在本实施方式中,作为吸杂汇点的无定形半导体膜通过 TMAH(四甲基氢氧化铵)除去。

[0119] 以本方式形成的半导体膜可以掺杂少量杂质元素 (硼或磷) 来控制薄膜晶体管的阈值电压。杂质元素的掺杂可以在结晶前掺杂无定形半导体膜。当无定形半导体膜掺杂杂质元素时,杂质可以通过随后的结晶热处理激活。而且,掺杂时产生的缺陷等也可以被改善。

[0120] 接着,使用掩模来图案化结晶性半导体膜 102。在本实施方式中,除去形成在结晶性半导体膜 102 上的氧化物膜以后,重新形成了氧化物膜。然后,形成光掩模并通过光刻法使其图案化,从而形成了半导体层 103、半导体层 104、半导体层 105 以及半导体层 106。

[0121] 图案化时的蚀刻工艺可以为等离子蚀刻 (干蚀刻) 或湿蚀刻。在加工大面积基底时,更优选等离子蚀刻。作为蚀刻气体,可以使用诸如  $\text{CF}_4$ 、 $\text{NF}_3$ 、 $\text{Cl}_2$  或  $\text{BCl}_3$  的氟基气体和氯基气体,诸如 He 和 Ar 的惰性气体也可以适当加入。在通过大气压放电来提供蚀刻工艺时,可以实现局部放电,其不需要掩模层就可以形成在基底的整个表面上。

[0122] 在本实施方式中,形成配线层或电极层的导电层、形成预定图案的掩模层等,可以通过可选择地形成图案的方法来形成,例如滴状喷射法。在滴状喷射法中 (根据其中的系统也称为喷墨法),预定的图案 (导电层、绝缘层等) 可以通过选择性地排出 (喷射) 特定用途的组合物液体来形成。在此情形中,控制润湿性和吸附力的方法可以在其上待形成的区域内进行。此外,可以使用转移或刻画图案的方法,例如,印刷法 (一种形成图案的方法,例如丝网印刷和胶版印刷) 或类似的方法。

[0123] 在本实施方式中,诸如环氧树脂、丙烯酸树脂、酚醛树脂、酚醛清漆树脂、三聚氰胺树脂或聚氨酯树脂的树脂材料可以用作掩模。或者,掩模也可以通过下述材料制得:具有透光性的有机材料,例如苯环丁烯、聚对亚苯基二甲基、flare 和聚酰亚胺;通过硅氧烷聚合物或类似物聚合得到的化合物材料;含有水溶性均聚物和水溶性共聚物的组合物材料;等等。另外,市售可得的含有光敏剂的光刻胶材料也可以使用。例如,可以使用典型的含有酚醛清漆树脂和作为光敏剂的萘醌二叠氮化合物的正性光刻胶;碱性树脂即负性光刻胶,二苯基硅烷二醇,酸生成材料等。当使用滴状喷射法时,通过控制溶剂的浓度、加入表面活性剂等来适当调整任意材料的表面张力和粘度。

[0124] 形成覆盖半导体层 103、半导体层 104、半导体层 105 和半导体层 106 的栅绝缘层 107。所述的栅绝缘层 107 通过等离子 CVD 法或溅射法,由厚度为 10–150nm 的含有硅的绝缘膜形成。所述的栅绝缘层 107 可以通过诸如硅的氧化物材料或硅的氮化物材料的已知材料形成并且可以为叠层或单层,所述的材料典型为氮化硅、氧化硅、氧氮化硅和氮氧化硅。而且,绝缘层可以为包含氮化硅膜、氧化硅膜和氮化硅膜的叠层,或者单层,或者为氧氮化硅膜双层的叠层。更优选地,使用具有致密膜品质的氮化硅膜。氧化硅薄膜可以形成在半导体层和栅绝缘层中间,厚度为 1–100nm、优选 1–10nm、更优选 2–5nm。半导体区域的半导体表面通过 GRTA(气体快速热退火)法、LRTA(利用灯的快速热退火法)等氧化并形成热氧化物膜,从而形成薄薄的一层氧化硅膜。需要注意的是,在低成膜温度下,为了形成具有小的栅漏流的致密绝缘膜,诸如 Ar 的稀有气体元素可以加入至反应气体中,并混入待形成的绝缘层中。在本实施方式中,氧氮化硅膜形成 115nm 的厚度,作为栅绝缘层 107。

[0125] 接着,分别用作栅极层的厚度为 20–100nm 的第一导电膜 108 和厚度为 100–400nm 的第二导电膜 109,被层叠在栅绝缘层 107(图 2B)上。所述的第一导电膜 108 和第二导电膜 109 可以通过诸如溅射法、真空沉积法或 CVD 法的已知方法形成。所述的第一导电膜 108 和第二导电膜 109 可以由选自钽(Ta)、钨(W)、钛(Ti)、钼(Mo)、铝(Al)、铜(Cu)、铬(Cr)和钕(Nd)的元素、或者含有上述元素作为主要组分的合金材料或化合物材料来形成。典型的掺杂有诸如磷杂质元素的多晶硅膜或 AgPdCu 合金的半导体膜,可以用作第一导电膜 108 和第二导电膜 109。所述导电膜没有限定于双层结构,例如,可以具有三层结构,其中厚度为 50nm 的钨膜、厚度为 500nm 的铝–硅(Al–Si)合金膜以及厚度为 30nm 的氮化钛膜被依次层叠。在三层结构中,氮化钨可以替代第一导电膜的钨;铝–钛合金膜(Al–Ti)可以替代第二导电膜的铝–硅(Al–Si)合金膜;或者钛膜可以替代第三导电膜的氮化钛膜。而且,也可以使用单层结构。在本实施方式中,厚度为 30nm 的氮化钽(TaN)用作第一导电膜 108 且厚度为 370nm 的钨(W)用作第二导电膜 109。

[0126] 随后,使用光刻胶,通过光刻法形成掩模 110a、110b、110c、110d 和 110f,并且图案化第一导电膜 109 和第二导电膜 108 来形成第一栅极层 121、122、124、125 和 126,然后形成导电层 111、112、113、115 和 116(见图 2C)。使用 ICP(电感耦合等离子体)蚀刻法,通过适当调整蚀刻条件(施加在呈线圈型的电极层的电功率、施加在基底侧的电极层的电功率、基底侧的电极温度等等),可以使第一栅极层 121、122、124、125 和 126 以及导电层 111、112、113、115 和 116 蚀刻为需要的锥形。而且,所述锥形的角度等可以通过掩模 110a、110b、110d 和 110f 的形状来控制。作为蚀刻气体,可以适当使用以 Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub> 或 CC<sub>1</sub><sub>4</sub> 等为典型的氯基气体,或者以 CF<sub>4</sub>、CF<sub>5</sub>、SF<sub>6</sub> 或 NF<sub>3</sub> 等为典型的氟基气体,或者 O<sub>2</sub>。在本实施方式中,第二导电膜 109 通过使用含有 CF<sub>5</sub>、Cl<sub>2</sub> 和 O<sub>2</sub> 的蚀刻气体来蚀刻,然后第一导电膜 108 使用含有 CF<sub>5</sub> 和 Cl<sub>2</sub> 的蚀刻气体连续蚀刻。

[0127] 接着,使用掩模 110a、110b、100c、110d、110e 和 110f 使导电层 111、112、114、115 和 116 图案化。此时,以对形成导电层的第二导电膜 109 和形成第一栅极层的第一导电膜 108 高选择比的蚀刻条件来蚀刻导电层。通过上述蚀刻,导电层 111、112、113、114、115 和 116 被蚀刻形成第二栅极层 131、132、134、135 和 136。在本实施方式中,导电层 163 为锥角大于第一栅极层 121、122、124、125 和 126 的锥形。需要注意的是,所述的锥角为侧表面相对于第一栅极层、第二栅极层和导电层的表面的角度。因而,当锥角升至 90° 时,导电层具

有垂直侧边且不为锥形。在本实施方式中，使用蚀刻气体 Cl<sub>2</sub>、SF<sub>6</sub> 和 O<sub>2</sub> 来形成第二栅极。

[0128] 在本实施方式中，第一栅极层、导电层和第二栅极层中的每一个都形成锥形，这样两个栅极层都具有锥形。但是，本发明不限定于此，栅极层中的一个可以为锥形，而另一个具有可以通过各向异性的蚀刻形成垂直的侧边。如本实施方式所述，在层叠的栅极层之间，锥角可以相同也可以不同。通过锥形，其上层叠的膜的覆盖范围可以增加且缺陷减少，这使得可靠性提高。

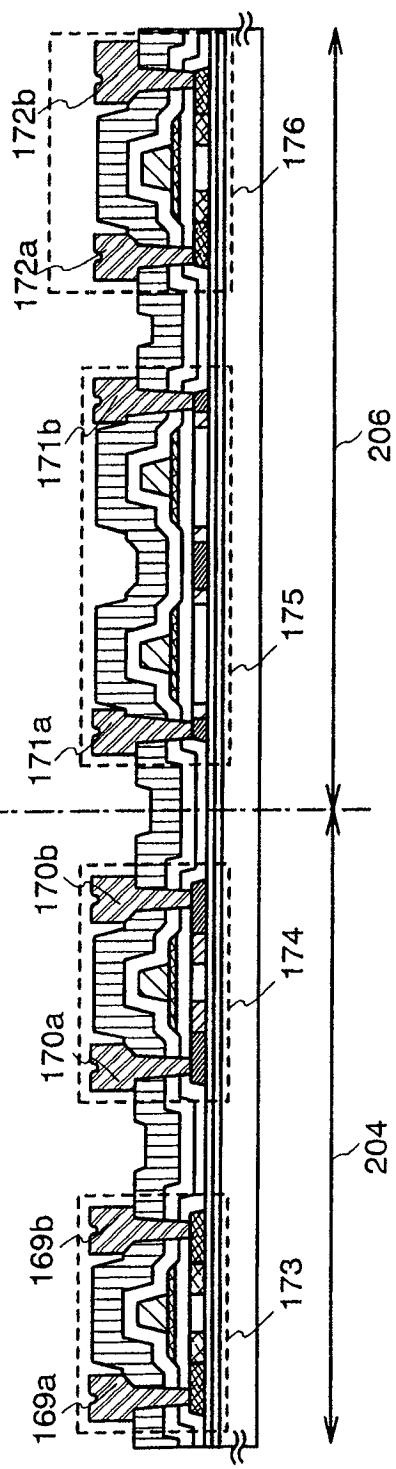

[0129] 通过前述步骤，由第一栅极层 121 和第二栅极层 131 形成的栅极层 117、由第一栅极层 122 和第二栅极层 132 形成的栅极层 118 可以在外围驱动电路区域 204 内形成，由第一栅极层 124 和第二栅极层 134 形成的栅极层 127、由第一栅极层 125 和第二栅极层 135 形成的栅极层 128、以及由第一栅极层 126 和第二栅极层 136 形成的栅极层 129 可以在像素部分 206 内形成（见图 2D）。在本实施方式中，栅极层通过干蚀刻法形成，但是也可以用湿蚀刻法替代。

[0130] 所述的栅绝缘层 107 可以蚀刻至某种程度并通过蚀刻步骤减少厚度来形成栅极层。

[0131] 通过形成的栅极层的宽度很小，可以形成能高速运作的薄膜晶体管。形成在通道方向上栅极层宽度很小的两种方法见下文。

[0132] 第一种方法是：形成用于栅极层的掩模，通过蚀刻、灰化等在宽度方向上使掩模变细长，然后形成具有更小宽度的掩模。通过使用具有更小宽度的掩模，可以形成具有更小宽度形状的栅极层。

[0133] 第二种方法是：形成常规的掩模，然后使用该掩模形成栅极层。然后在需要减薄的宽度方向侧蚀刻栅极层。因而可以形成具有更小宽度的栅极层。通过上述步骤，可以形成具有短通道长度的薄膜晶体管，其可以实现能高速运作的薄膜晶体管。

[0134] 接着，通过使用栅极层 117、118、127、128 和 129 作为掩模，加入赋予 n 型电导率的杂质元素 151 来形成第一 n 型杂质区域 140a、140b、141a、141b、142a、142b、142c、143a 和 143b（见图 3A）。在本实施方式中，在气流速率为 80sccm、束流为 54 μA/cm、加速电压为 50kV 且剂量为  $7.0 \times 10^{13}$  离子 / cm<sup>2</sup> 下，通过使用磷 (PH<sub>3</sub>) 作为含有杂质元素的掺杂气体（用氢气 (H<sub>2</sub>) 稀释 PH<sub>3</sub> 作为掺杂气体，在气体中，PH<sub>3</sub> 的组分比率为 5%）来进行掺杂。在此，掺杂进行至赋予 n 型电导率的杂质元素在第一 n 型杂质区域 140a、140b、141a、141b、142a、142b、142c、143a 和 143b 中的含有浓度为约  $1 \times 10^{17}$ – $5 \times 10^{18}$  / cm<sup>3</sup>。在本实施方式中，磷 (P) 被用作赋予 n 型电导率的杂质元素。

[0135] 在本实施方式中，覆盖有栅极层的区域的杂质区域（栅绝缘层插入在栅极层和该区域之间）表示为 Lov 区，而没有覆盖有栅极层的区域的杂质区域（栅绝缘层插入在栅极层和该区域之间）的表示为 Loff 区。在图 3A 中，杂质区域通过阴影区和空白区来表示。这不是意味着空白区没有加入杂质元素，而是表示在该区域内杂质元素的浓度分布反映出掩模和掺杂条件。注意的是在本说明书的其它附图中也是相同的。

[0136] 随后，形成覆盖半导体层 103、半导体层 105 的一部分以及半导体层 106 的掩模 153a、153b、153c 和 153d。通过使用掩模 153a、153b、153c、153d 以及作为掩模的第二栅极层 132，赋予 n 型电导率的杂质元素 152 被加入，形成了第二 n 型杂质区域 144a、144b、第三 n 型杂质区域 145a、145b、第二 n 型杂质区域 147a、147b 和 147c、第三 n 型杂质区域

148a、148b、148c 以及 148d。在本实施方式中，在气流速率为 80sccm、束流为  $540 \mu A/cm$ 、加速电压为 70kV 且剂量为  $5.0 \times 10^{15}$  离子 / $cm^2$  下，通过使用膦 (PH<sub>3</sub>) 作为含有杂质元素的掺杂气体（用氢气 (H<sub>2</sub>) 稀释 PH<sub>3</sub> 作为掺杂气体，在气体中，PH<sub>3</sub> 的组分比率为 5%）来进行掺杂。此时，掺杂的进行使得每个第二 n 型杂质区域 144a 和 144b 所含的杂质元素浓度是约  $5 \times 10^{19} - 5 \times 10^{20}/cm^3$ 。形成的第三 n 型杂质区域 145a 和 145b 与第三 n 型杂质区域 148a、148b、148c 和 148d 含有大约相同浓度的赋予 n 型电导率的杂质元素，或者前者浓度稍高于后者。而且，通道形成区域 146 形成在半导体层 104 里，通道形成区域 149a 和 149b 形成在半导体层 105 里（见图 3B）。

[0137] 第二 n 型杂质区域 144a、144b、147a、147b 和 147c 为起到源和漏区域作用的高浓度 n 型杂质区域。另一方面，第三 n 型杂质区域 145a、145b、148a、148b、148c 和 148d 为起到 LDD（少许掺杂的漏区域）区域作用的低浓度杂质区域。第一栅极 122 层覆盖的 n 型杂质区域 145a 和 145b（栅绝缘层 107 插入在该电极层和杂质区域之间）为 Lov 区域，其可以减轻漏区域周围的电场并抑制由于热载流子引起的通电电流的降低。结果，能高速运作的薄膜晶体管可以形成。另一方面，第三 n 型杂质区域 148a、148b、148c 和 148d 形成在没有被栅极层 127 和 128 覆盖的 Loff 区域，因此漏区域周围的电场可以被减轻并且由于热载流子注入引起的降级也可以抑制，也减少了断电电流。结果，可以形成具有高可靠性和低功率消耗的半导体器件。

[0138] 接着，除去掩模 153a、153b、153c 和 153d 并形成覆盖半导体层 103 和 105 的掩模 155a 和 155b。通过使用掩模 155a 和 155b 以及作为掩模的栅极层 117 和 129，加入赋予 p 型电导率的杂质元素 154，形成了第一 p 型杂质区域 160a、160b、163a、163b，第二 p 型杂质区域 161a、161b、164a 和 164b（见图 7C）。在本实施方式中，硼 (B) 用作杂质元素，因而在气流速率为 70sccm、束流为  $180 \mu A/cm$ 、加速电压为 80kV 且剂量为  $2.0 \times 10^{15}$  离子 / $cm^2$  下，使用乙硼烷 (B<sub>2</sub>H<sub>6</sub>)（用氢气 (H<sub>2</sub>) 稀释 B<sub>2</sub>H<sub>6</sub> 作为掺杂气体，气体中 B<sub>2</sub>H<sub>6</sub> 的组分比例为 15%）作为含有杂质元素的掺杂气体来进行掺杂。在此，掺杂进行至使得第一 p 型杂质区域 160a、160b、163a、163b、第二 p 型杂质区域 161a、161b、164a 和 164b 含有浓度为约  $1 \times 10^{20} - 5 \times 10^{21}/cm^3$  的赋予 p 型电导率的杂质元素。在本实施方式中，第二 p 型杂质区域 161a、161b、164a 和 164b 通过对照栅极层 117 和 129 的形状以自排列方式来形成，从而比第一 p 型杂质区域 160a、160b、163a 和 163b 含有更低浓度的杂质元素。而且，通道形成区域 162 形成在半导体层 103 里且通道形成区域 165 形成在半导体层 106 里（见图 3C）。

[0139] 第二 n 型杂质区域 144a、144b、147a、147b 和 147c 为起到源和漏区域作用的高浓度 n 型杂质区域。另一方面，第二 p 型杂质区域 161a、161b、164a 和 164b 为起到 LDD（少许掺杂的漏区域）区域作用的低浓度杂质区域。第一栅极层 121 和 126 覆盖的第二 p 型杂质区域 161a、161b、164a 和 164b（栅绝缘层 107 插入该电极层和杂质区域之间）为 Lov 区域，其能减轻漏区域周围的电场并抑制由于热载流子引起的通电电流的降低。

[0140] 掩模 155a 和 155b 通过氧气灰化或者使用光刻胶剥离溶液除去，因而也可以除去氧化物膜。然后，可以形成绝缘膜、即侧壁来覆盖栅绝缘层的侧边。所述的侧壁可以通过等离子 CD 法和低压 CVD (LPCVD) 法、由含有硅的绝缘层形成。

[0141] 为了激活杂质元素，可以使用热处理、强光辐照或激光辐照。激活的同时，对栅绝缘层和栅绝缘层与半导体层之间界面的等离子损害可以被恢复。

[0142] 接着,形成覆盖棚绝缘层和棚极层的夹层绝缘层。在本实施方式中,采用绝缘膜 167 和 168 的叠层结构(参见图 4A)。作为绝缘膜 167 的具有 100nm 厚度的氮氧化硅膜、和作为绝缘膜 168 的具有 900nm 厚度的绝缘氧氮化物膜形成叠层结构。而且,通过形成厚度为 30nm 的氧氮化硅膜、厚度为 140nm 的氮氧化硅膜和厚度为 800nm 的氧氮化硅膜,可以采用三层的叠层结构。在本实施方式中,绝缘膜 167 和 168 通过与基膜相似的等离子 CVD 法连续形成。绝缘膜 167 和 168 不限于上述材料,可以为通过等离子 CVD 法形成的氮化硅膜、氮氧化硅膜、氧氮化硅膜和氧化硅膜。或者,也可以采用含有其它硅的绝缘膜的单层结构或者三或多层的叠层结构。

[0143] 而且,热处理在氮气气氛中于 300–550°C 进行 1–12 小时,从而使半导体层氢化。优选地,该步骤在 400–500°C 进行。根据该步骤,半导体层中的不饱和键可以通过用作夹层绝缘膜的绝缘膜 167 中含有的氢来封端。在本实施方式中,热处理在 410°C 进行 1 小时。

[0144] 绝缘膜 167 和 168 可以由选自氮化铝 (AlN)、氧氮化铝 (AlON)、含有的氮多于氧的氮氧化铝 (AlNO)、氧化铝、金刚石状碳 (DLC)、氮化碳膜 (CN) 以及其它含有无机绝缘材料的物质的材料形成。而且,也可以使用硅氧烷材料。需要注意的是,硅氧烷材料相当于含有 Si–O–Si 键的树脂。硅氧烷具有硅 (Si) 和氧 (O) 的键的骨架。作为取代基,至少含有氢(例如,烷基和芳基碳氢化物)的有机基团或氟基团可以使用。或者至少含有氢的有机基团和氟基团也可以用作取代基。而且,也可以使用有机绝缘材料,例如聚酰亚胺、丙烯酸、聚酰胺、聚酰亚胺酰胺、光刻胶、苯并环丁烯或聚硅氮烷。也可以使用由涂覆法形成的具有高平面化的涂覆膜。

[0145] 接着,通过使用光刻胶掩模,在绝缘膜 167 和 168 以及棚绝缘层 107 内形成延伸至半导体层的接触孔(洞)。根据所使用材料的选择比,可以进行一次或多次蚀刻。在本实施方式中,第一蚀刻在作为氮氧化硅膜的绝缘膜 167 和棚绝缘层 107 之间可以得到的选择比的条件下进行,从而除去了绝缘膜 168。然后,绝缘膜 167 和棚绝缘层 107 通过第二蚀刻除去,形成了作为源区域或漏区域的、通往第一 p 型杂质区域 160a、160b、163a 和 163b 以及第二 n 型杂质区域 144a、144b、147a 和 147b 的孔,第二 n 型杂质区域 144a 和 144b 以及第二 n 型杂质区域 147a 和 147b。在本实施方式中,第一蚀刻通过湿蚀刻进行而第二蚀刻通过干蚀刻进行。基于氟的溶液,例如氟化氢铵或含有氟化铵的混合物可以用作湿蚀刻的蚀刻剂。作为蚀刻气体,以 Cl<sub>2</sub>、BCl<sub>3</sub>、SiCl<sub>4</sub> 或 CC<sub>4</sub> 等为代表的基于氯的气体、以及 CF<sub>4</sub>、SF<sub>6</sub> 或 NF<sub>3</sub> 等为代表的基于氟的气体或者氧气可以适当使用。而且,惰性气体可以加入至蚀刻气体中。作为加入的惰性元素,可以使用选自 He、Ne、Ar、Kr 和 Xe 中的一种或多种。

[0146] 形成导电膜来覆盖上述孔,并且将导电膜蚀刻,以形成源极层或漏极层 169a、源极层或漏极层 169b、源极层或漏极层 170a、源极层或漏极层 170b、源极层或漏极层 171a、源极层或漏极层 171b、源极层或漏极层 172a 以及源极层或漏极层 172b,它们电连接至形成的每个源区域或漏区域的一部分。通过 PVD 法、CVD 法、汽相沉积法等形成导电膜,然后将导电膜蚀刻成需要的形状,可以形成源极层或漏极层。而且,通过滴状喷射法、印刷法、电解电镀法等,导电层可以选择性地形成在预定的位置。此外也可以使用回流法和金属镶嵌法。所述源极层或漏极层由选自 Ag、Au、Cu、Ni、Pt、Pd、Ir、Rh、W、Al、Ta、Mo、Cd、Zn、Fe、Ti、Si、Ge、Zr、Ba 等的金属、或它们的合金或金属氮化物形成。而且,可以使用它们的叠层结构。在本实施方式中, Ti 形成至 60nm 的厚度、氮化钛形成至 40nm 的厚度、铝形成至 700nm 的厚度,

以及钛 (Ti) 形成至 200nm 的厚度来形成叠层结构, 然后图案化至需要的形状。

[0147] 通过上述步骤, 有源矩阵基底可以形成, 其中在 Lov 区域内具有 p 型杂质区域的 p 通道薄膜晶体管 173 和在 Lov 区域内具有 n 通道杂质区域的 n 通道薄膜晶体管 174 可以形成在外围驱动电路区 204 内, 并且在 Loff 区域内具有 n 型杂质区域的多通道型 n 通道薄膜晶体管 175 和在 Lov 区域内具有 p 型杂质区域的 p 通道薄膜晶体管 176 可以形成在像素部分 206 内 (见图 4B)。

[0148] 随后, 有源矩阵基底可以用于具有自发光元件的发光器件、具有液晶元件的液晶显示器以及其它显示器件。而且, 所述的有源矩阵基底可以用于诸如以 CPU(中央处理器) 为代表的各种处理器以及结合有 ID 芯片的卡等的半导体器件中。

[0149] 本发明不限于本实施方式, 且薄膜晶体管可以具有单栅结构, 其中形成一个通道形成区域, 可以具有双栅结构, 其中形成两个通道形成区域, 或具有三重栅结构, 其中形成三个通道形成区域。而且, 在外围驱动电路区内的薄膜晶体管可以具有单栅结构、双栅结构或三重栅结构。

[0150] 需要注意的是, 本发明不是限定于本实施方式描述的薄膜晶体管的制备方法, 而是也可以施用于顶端栅型 (平面型)、底端栅型 (反交错型) 或双栅型, 或者其它的结构, 其中在双栅型结构中, 两个栅极层排列在通道区域的顶端和底端, 栅绝缘膜插入在它们之间。

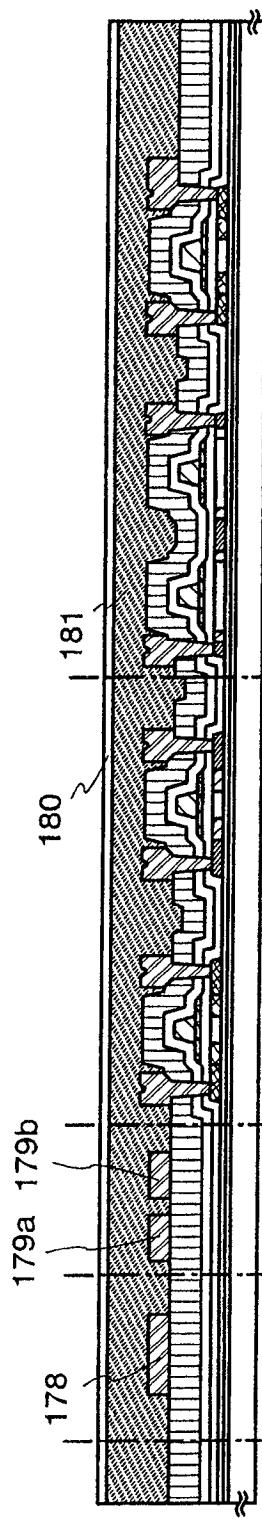

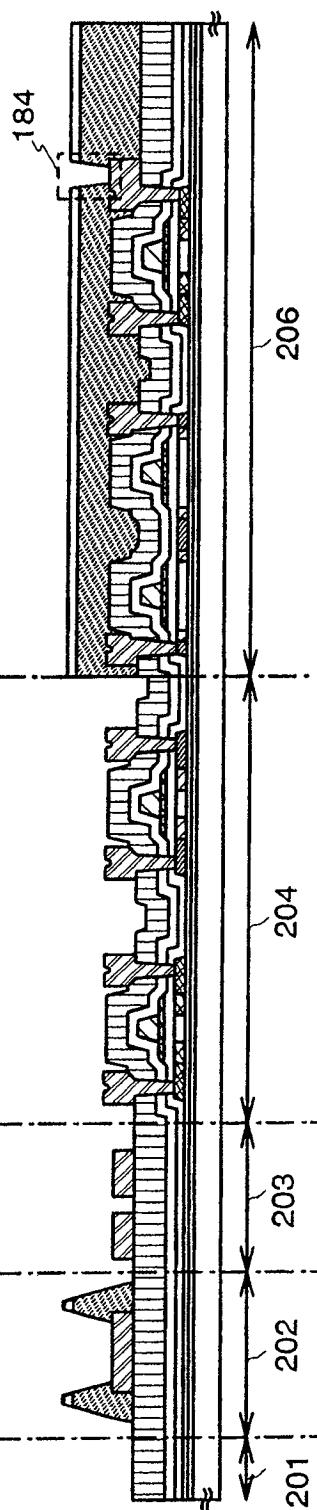

[0151] 接着, 形成作为第二夹层绝缘层的绝缘膜 180, 并且夹层膜 181 形成在绝缘层 180 和第一电极层 396 之间 (图 5A)。图 5A-5C 显示了显示器件的制备步骤, 其中提供了通过划线被切开的区域 201、与 FPC 连接的外部终端连接区域 202、配线区域 203 (即在外围部分引导配线的区域)、外围驱动电路区域 204 以及像素部分 260。配线 179a 和 179b 形成在配线区域 203 内, 与外部终端连接的终端电极层 178 形成在外部终端连接区域 202 内。

[0152] 夹层膜 180 和绝缘层 181 可以使用选自下述的材料形成: 氧化硅、氮化硅、氧氮化硅、氮氧化硅、氮化铝 (AlN)、氧氮化铝 (AlON)、氮含量多于氧含量的氮氧化铝 (AlNO)、氧化铝、金刚石状碳 (DLC)、含氮的碳 (CN) 膜、PSG (磷玻璃)、BPSG (硼磷玻璃)、铝膜以及其他含有无机绝缘材料的物质。而且, 可以采用硅氧烷材料 (无机硅氧烷或有机硅氧烷)。可以使用光敏性或非光敏性有机绝缘材料, 例如, 聚酰亚胺、丙烯酸、聚酰胺、聚酰亚胺酰胺、光刻胶或苯并环丁烯、聚硅氮烷, 或者可以使用低 k 的材料即低介电常数的材料。

[0153] 在本实施方式中, 绝缘层 181 优选通过诸如旋涂的涂覆法形成, 因为需要在耐热性、绝缘性能和平面性上具有优势的层来作为平面化的夹层绝缘膜。在本实施方式中, 夹层膜 180 具有改善绝缘层 181 和第一电极层 396 之间粘合力的功能。所述夹层膜 180 通过在绝缘层 181 上层叠氮氧化硅膜和氮化钛膜形成。通过 CVD 法, 氧氮化硅膜形成至 50nm 的厚度且其上的氮化钛形成至 10nm 的厚度。所述夹层膜 180 改善了绝缘层 181 和第一电极层 396 之间的粘合力; 因而也提高了制得的显示器件的可靠性和产量。

[0154] 在本实施方式中, 硅氧烷材料的涂层膜用作绝缘层 181 的材料。烘烤后的该膜可以称为含有烷基的氧化硅膜 ( $\text{SiO}_x$ ) ( $x = 1, 2, \dots$ )。所述的含有烷基的氧化硅膜 ( $\text{SiO}_x$ ) 可以经受 300°C 或更高温度的热处理。

[0155] 浸渍涂布、喷涂、刮刀涂布、辊式涂布机、帘幕涂布机、刮刀式涂布机、CVD 法、气相沉积法等可以用来形成夹层膜 180 和绝缘层 181。另外, 夹层膜 180 和绝缘层 181 可以通过滴状喷射法形成。当使用滴状喷射法时, 可以节省材料溶液。能够向滴状喷射法一样转移

或绘制图案的方法也可以使用,例如印刷法等(通过该方法形成图案,如丝网印刷或胶版印刷)。

[0156] 如图5B所示,在夹层膜180和用作第二夹层绝缘膜的绝缘层181内形成开口。夹层膜180和绝缘层181需要在连接区域(未显示)、配线区域203、外部终端连接区域202、待切除区域201等处大范围地被蚀刻。但是,在像素部分206内,开口的面积依然小于在连接区域等处的开口,且变得微小。因而,通过使用光刻法在像素部分和连接区域内形成开口,可以拓宽蚀刻条件的限制。因而,可以提高产量。通过拓宽蚀刻条件的限制,像素部分的接触孔可以高精度地形成。

[0157] 特别地,具有大面积的开口形成在夹层膜180和绝缘膜181内,部分形成在连接区域、配线区域203、外部终端连接区域202、待切除区域201以及外围驱动电路区域204的一部分内。从而形成了覆盖形成在像素部分206内的中间层膜180和绝缘膜181、以及连接区域和外围驱动电路区域204的一部分的掩模。平行板RIE(反应性离子蚀刻)系统或ICP蚀刻系统可以用来蚀刻。注意的是,可以设置蚀刻时间,以使得配线层或第一夹层绝缘膜被过蚀刻。通过设置时间,在基底内膜厚度的变化以及蚀刻速率的变化可以减少,致使配线层或第一夹层绝缘层被过蚀刻。这样,开口183可以形成在外部终端连接区域202内。

[0158] 微小的开口(也就是接触孔)形成在像素部分206的夹层膜180和绝缘层181内(见图5C)。这时,形成覆盖像素部分206、部分外围驱动电路区域204和像素部分206的掩模。所述掩模为用来在像素部分206内形成开口的掩模,并在其中需要的位置提供细小的开口。例如,光刻胶掩模可以用作掩模。

[0159] 夹层膜180和绝缘层181通过平行板RIE(反应性离子蚀刻)体系来蚀刻。注意的是,可以设置蚀刻时间使得配线层或第一夹层绝缘层被过蚀刻。通过设置时间,在基底内膜厚度的变化以及蚀刻速率的变化可以减少,致使配线层或第一夹层绝缘层被过蚀刻。

[0160] ICP系统可以用作蚀刻系统。通过上述步骤,在像素部分206内,形成了延伸至源或漏极层172a的开口184。而且,源或漏极层可以形成在总厚度大的区域内,所述区域内层叠多层薄膜。作为本实施方式的薄膜晶体管,源或漏极层优选形成在栅极层上。在此情形中,由于开口184不需要形成很深,所以形成开口的工序可以缩短,从而可以增加可控性。此外,形成在开口内的电极层可以以适当的覆盖度形成,从而增加了可靠性,这是因为所述电极层不需要大范围覆盖具有大角度的开口。

[0161] 本实施方式描述了这样的方案:其中夹层膜180和绝缘层181使用掩模蚀刻,所述掩模覆盖配线区域203、外部终端连接区域202的一部分、待切除区域201和外围驱动电路区域204的一部分,并在像素部分206上具有需要的开口。但是,本发明不限定于此。例如,在连接区域内开口的面积大,则蚀刻量也大。具有大面积的开口可以多次蚀刻。如果形成的开口深于其它开口,则相似地可以进行多次蚀刻。

[0162] 在本实施方式中,如图5B和5C所示,在夹层膜180和绝缘层181内,开口的形成可以多次进行;但是,也可以仅仅进行一次蚀刻。在此情形中,ICP系统用来进行蚀刻,ICP功率为7000W,偏压功率为1000W,压力为0.8Pa,使用240sccm的CF<sub>4</sub>和160sccm的氧气作为蚀刻气体。所述的偏压功率优选为1000-4000W。这时,优点在于可以得到简化的工艺,这是因为对于形成开口,一次蚀刻已经足够。

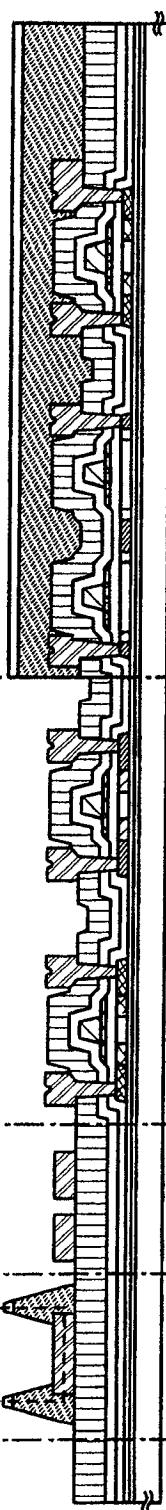

[0163] 然后,形成与源或漏极层172a接触的第一电极396(也称为像素电极)。

[0164] 在本实施方式中,发光元件用作显示元件,并且从发光元件发出的光从第二电极层 189 侧透出。因而,第一电极层 185 为反射性。形成包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜,并将其蚀刻为需要的形状来形成第一电极层 396。在本实施方式中,氮化钛膜的叠层用于夹层膜 180。由于氮化钛膜为导电性的,所以当第一电极层 396 被图案化时,夹层膜 180 同时也被图案化。

[0165] 在本发明中,包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜用于第一电极层 396,即反射电极层。在本实施方式中,A1(Mo) 膜用于第一电极层 396。第一电极层 396 的厚度可以为 20nm~200nm,优选 35~100nm。在本实施方式中,A1(Mo) 膜通过溅射形成 35nm 的厚度。包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜即使经受热处理,也难以结晶,并且该膜的表面平坦性良好。而且,在近可见光区域内,光的反射率高,可以进行有效的光反射。包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜还具有杰出的优点:对人体安全并对环境无害(见图 6A)。

[0166] 在包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜中,钼或钛的含量优选超过 7.0 原子%。而且,当钼或钛的含量为 20 原子%或更低时,由于在近可见光区域内的光反射,这是有利的。在 A1(C) 膜中,膜中碳的含量为 0.1 原子%~10 原子%,优选低于 1 原子%。在包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜中,即使含有微量的碳也是有效的,所以膜中碳的含量可以为 0.3 原子%或更低,而且,可以为 0.1 原子%或更低。

[0167] 诸如 ITO 膜或 ITS0 膜的透明导电膜可以形成在第一电极层 396 上。ITS0 膜可以通过使用靶材溅射形成至 185nm 的厚度,其中,在以下的条件下,将 1~10% 的氧化硅 ( $\text{SiO}_2$ ) 加入至氧化铟锡中:Ar 气体流速为 120sccm、氧气流速为 5sccm、压力为 0.25Pa 且电功率为 3.2kW。第一电极层 369 可以通过 CMP 或通过使用诸如聚乙烯醇的多孔材料来清洗或抛光,使得其表面平坦。另外,使用 CMP 法抛光后,紫外线辐照、氧气等离子处理等可以在第一电极层 369 的表面进行。

[0168] 在形成第一电极层 396 后,可以进行热处理。通过热处理,包含在第一电极层 396 中的水汽可以被释放。因而,不会从第一电极层 396 产生脱气等。即使当易于受潮变劣的发光材料形成在第一电极层上时,该发光材料也不会变劣;因而可以制得高可靠性的显示器件。在本实施方式中,包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜用于第一电极层,所以即使当进行烘烤时,它也难以结晶,并可以保持无定形态。因此,第一电极层 396 具有高平坦性并难以与第二电极层短路,即使是当含有有机化合物的层变薄时亦如此。

[0169] 在本实施方式中,光敏性聚酰亚胺用于绝缘层 186、187a 和 187b。而且,通过使用与绝缘层 181 相同的材料和相同的步骤来形成绝缘层 186、187a 和 187b,可以降低制造成本。而且,通过使用共用的沉积设备、蚀刻设备等可以降低成本(见图 6B)。

[0170] 对于例如用于形成绝缘层 186 的显影液的化学溶液而言,含有镍的铝合金具有低抵抗力,所述绝缘层用作存储单元,其覆盖一部分第一电极层 396。包含含有选自钼、钛和碳中至少一种或多种的铝合金的膜具有高的抵抗力。因此,在制备过程中,诸如表面积减少或表面粗糙度的缺点几乎不发生。因此,可以保持良好的表面条件,使得其上形成的电致发光层 188 可以稳定的形成,从而可以增加显示器件的可靠性。

[0171] 绝缘层 186 可以通过下述绝缘材料形成:例如无机绝缘材料比如氧化硅、氮化硅、

氧氮化硅、氧化铝、氮化铝或氧氮化铝,丙烯酸,甲基丙烯酸,它们的衍生物,耐热性高分子材料比如聚酰亚胺、芳族聚酰胺或聚苯并咪唑,或者硅氧烷树脂材料。或者绝缘层 186 也可以通过使用诸如丙烯酸或聚酰亚胺的光敏性或非光敏性材料形成。绝缘层 186 优选具有曲径连续变化的形状的侧面。因而,其上形成的电致发光层 188 和第二电极层 189 的覆盖度可以提高。

[0172] 已经通过图案化加工成具有阶梯的夹层膜 180 和绝缘膜 181 的末端部分急剧倾斜。因而,其上层叠的第二电极层 189 的覆盖度不是有利的。相应地,在开口外围的阶梯用绝缘层 189 覆盖至平缓,因而提高了其上层叠的第二电极层 189 的覆盖度。在连接区域内,通过相同的步骤和与第二电极层相同的材料形成的配线层电连接至通过相同的步骤和与栅极层相同的材料形成的配线层。

[0173] 而且,为了提高可靠性,优选在形成电致发光层 188 之前,通过真空加热进行基底的脱气。例如,优选在低气压或惰性气氛中,于 200–400°C 或优选 250–350°C 进行热处理,去除包含在基底内的气体。而且,优选通过真空气相沉积法或滴状喷射法,在减压下,不需将基底暴露在空气中,形成电致发光层 188。通过上述热处理,可以释放出包含于或附着于将成为第一电极层的导电膜或绝缘层(存储单元)的水汽。所述热处理可以与在前的热步骤结合使用,只要在不中断真空的条件下,基底可以在真空腔中迁移即可。因此,在形成绝缘层(存储单元)以后,在前的热处理仅仅需要进行一次。在此,通过使用高耐热性物质形成夹层绝缘膜和绝缘层(存储单元)时,为了提高可靠性,热处理步骤可以充分进行。

[0174] 电致发光层 188 形成在第一电极层 396 上。尽管图 1A 和 1B 中仅仅显示了一个像素,但是在本实施方式中,对应于 R(红)、G(绿) 和 B(蓝) 的每种颜色的电致发光层可以分别形成。电致发光层 188 可以如实施方式 1 的方式来制得;有机化合物和无机化合物混合在第一电极层 396 上,所以具有高载流子注入性能和高载流子传输性能的层可以得到,所述的性能不能通过仅仅使用一种化合物来得到。

[0175] 所述的显示红(R)、绿(G) 和蓝(B) 每种颜色发光的材料(低或高分子量材料等),也可以通过滴状喷射法形成。

[0176] 接着,由导电膜形成的第二电极层 189 设置在电致发光层 188 上。作为第二电极层 189,可以使用具有低功函的材料(Al、Ag、Li、Ca 或它们的合金,如 MgAg、MgIn、AlLi,以及化合物 CaF<sub>2</sub> 或氮化钙)。在本方法中,形成了由第一电极层 185、电致发光层 188 和第二电极层 189 形成的发光元件 190。

[0177] 如图 7B 所示的本实施方式的显示器件中,从发光元件 190 发出的光从第二电极层 189 侧发出,沿图 7B 所示的箭头方向传送。

[0178] 设置钝化膜来覆盖第二电极层 189 是有效的。所述的钝化膜可以由单层或叠层的绝缘膜形成,所述的绝缘膜含有氮化硅、氧化硅、氧氮化硅(SiON)、氮氧化硅(SiNO)、氮化铝(AlN)、氧氮化铝(AlON)、氮含量多于氧含量的氮氧化铝(AlNO)、氧化铝、金刚石状碳(DLC) 或氮化碳膜(CN)。而且,也可以使用硅氧烷材料。

[0179] 这时,优选形成具有适宜覆盖度的钝化膜,对此碳膜、特别是 DLC 膜可以有效的使用。在室温至 100°C 的温度范围内,可以沉积的 DLC 膜容易形成在具有低耐热性的电致发光层 188 上。DLC 膜可以通过下述方法形成:等离子 CVD 法(典型为 RF 等离子 CVD 法、微波 CVD 法、电子回旋共振(ECR)CVD 法、热细丝 CVD 法等)、燃烧法、溅射法、离子束气相沉积法、

激光气相沉积法等。作为反应气体,氢气和基于氢化碳的气体(例如,CH<sub>4</sub>、C<sub>2</sub>H<sub>2</sub>、C<sub>6</sub>H<sub>6</sub>等)通过辉光放电被离子化,且离子加速碰撞施加了负自偏电压的阴极。而且,CN膜可以通过使用C<sub>2</sub>H<sub>2</sub>和N<sub>2</sub>作为反应气体来形成。DLC膜对氧气具有高阻挡效果,因而可以抑制电致发光层188的氧化。因而,在后续密封步骤前,电致发光层188被氧化的问题可以被阻止。

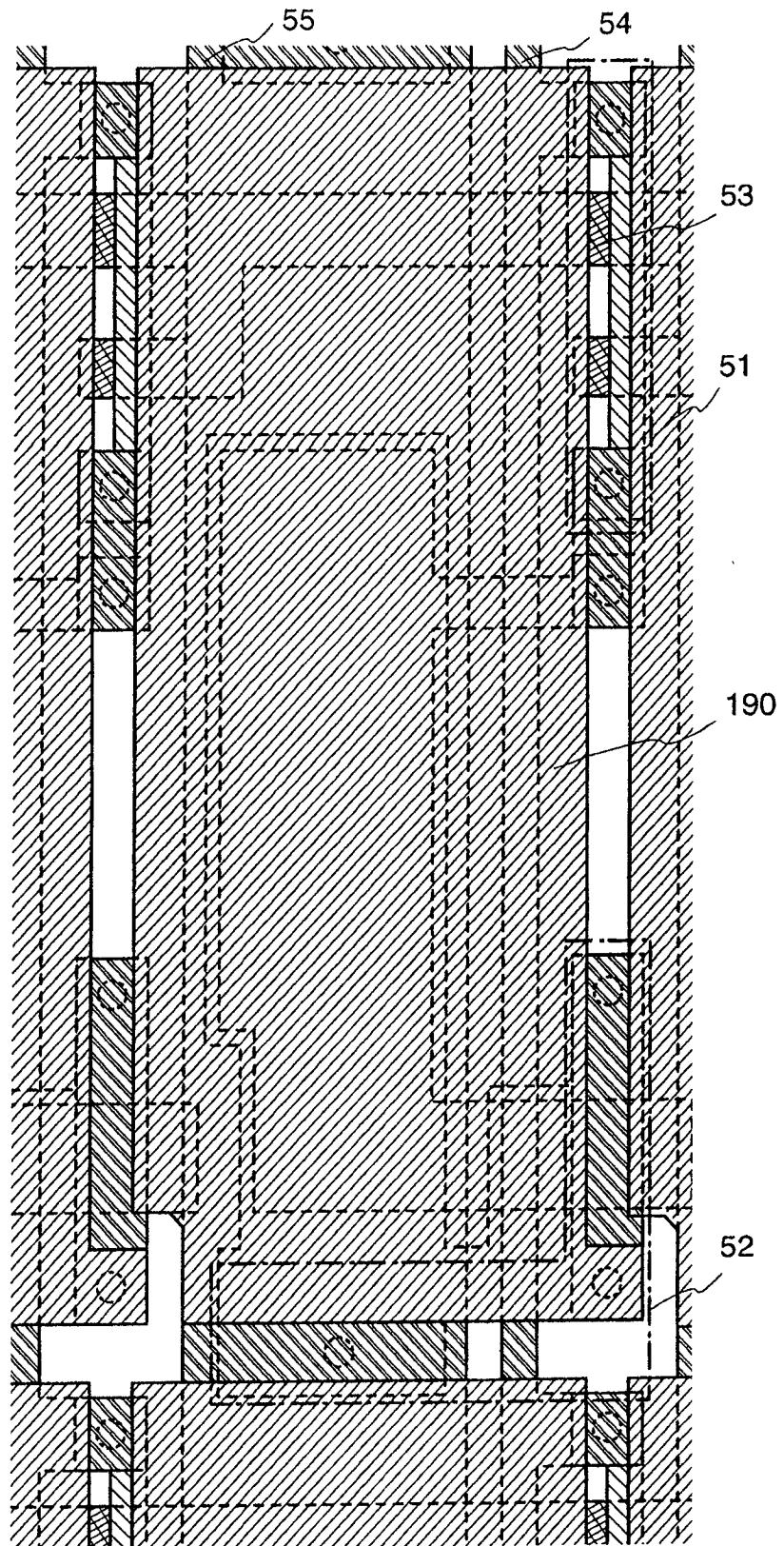

[0180] 在本实施方式中制得的显示器件的像素部分的顶视图见图11所示。在图11中,像素包括薄膜晶体管51、薄膜晶体管52、发光元件190、栅配线层53、源和漏配线层54以及电源线55。

[0181] 此时,通过使用密封材料192,牢固地固定密封基底195和其上形成有发光元件190的基底100,所述发光元件被密封(见图7A和7B)。在本发明的显示器件中,密封材料192和绝缘层186分开形成,这样不会相互接触。通过彼此分开形成密封材料192和绝缘层186,即使当使用具有高吸水性能的有机材料作为绝缘材料用于绝缘层186时,水汽也不容易进入,其可以抑制发光元件的变劣并提高显示器件的可靠性。作为密封材料192,典型优选使用可见光固化树脂、紫外线固化树脂或热固化树脂。例如,双酚A液体树脂、双酚A固体树脂、含溴环氧树脂、双酚F树脂、双酚AD树脂、酚树脂、甲酚树脂、酚醛清漆树脂、环脂族环氧树脂、Epi-Bis型(表氯醇-双酚)环氧树脂、缩水甘油酯树脂、缩水甘油胺树脂、杂环环氧树脂和改性环氧树脂。需要注意的是,密封材料包围的区域可以填充有填充材料193,通过在氮气气氛中密封,可以使之含有氮。由于本实施方式利用了底部发射型,填充材料193不需要透光。但是,当光穿过填充材料193透出时,则填充材料需要透光。典型地,可以使用可见光固化、紫外线固化或热固化环氧树脂。通过上述步骤,使用本实施方式的发光元件,完成了具有显示功能的显示器件。而且,填充材料可以通过滴入液态的填充材料,填充入显示器件内。

[0182] 使用配料器法的滴注法将参照图26进行描述。图26显示的滴注法包括控制装置40、成像设备42、顶盖(head)43、填充材料33、标记35、标记45、阻挡层34、密封材料32、TFT基底30和对立(counter)基底20。填充材料33从顶盖43一次或多次滴入密封材料32形成的封闭回路中。当填充材料具有高粘度时,所述填充材料被连续释放并且没有中断地附着到形成区域。当填充材料具有低粘度时,所述填充材料被间断地释放出并滴入,如图26所示。此时,提供的阻挡层34可以阻止密封材料32与填充材料33反应。接着,在真空中基底相互粘合,然后通过紫外线固化来用所述填充材料填充。作为填充材料,具有吸水性能的物质可以用来得到更多的吸水效果,从而阻止元件的恶化。

[0183] 在EL显示板中提供干燥剂来阻止水分带来的恶化。在本实施方式中,干燥剂设置在形成的凹陷部分,以使得其在密封材料中围绕像素部分,而不妨碍薄的设计。而且,干燥剂也形成在与栅配线层对应的区域内,使得吸水面积变大,通过这种方式可以有效地吸水。此外,由于干燥剂形成在不发光的栅配线层上,因此不会降低光透出效率。

[0184] 需要注意的是,发光元件通过玻璃基底而被密封,但是,下述方法中的任一种均可以使用:通过覆盖材料来机械密封发光元件的方法,通过热固化树脂或紫外线固化树脂来密封发光元件的方法,或者通过具有高阻挡性能的诸如金属氧化物、金属氮化物等的薄膜来密封发光元件的方法等。作为覆盖材料,可以使用玻璃、陶瓷、塑料或金属,但是当光发射至覆盖材料侧时,需要使用能透光的材料。通过使用诸如热固化树脂或紫外线固化树脂的密封材料,用热处理或紫外线辐照处理来固化树脂,使得覆盖材料与其上形成有发光元件

的基底附着，从而形成了密封空间。在该密封空间内设置以氧化钡为典型的吸湿材料也是有效的。所述的吸湿材料可以设置为与密封材料接触，在存储单元上或在其外围，这样不会阻挡从发光元件发出的光。而且，在覆盖材料和其上形成有发光元件的基底之间形成的空间可以用热固化树脂或紫外线固化树脂填充。在此情形中，在热固化树脂或紫外线固化树脂中加入以氧化钡为典型的吸湿材料也是有效的。

[0185] 图 12 显示了本实施方式制得的显示器件的一个实施，见图 1A 和 1B，其中源极层或漏极层不是相互直接接触来连接，而是通过配线层连接。在图 12 的显示器件中，驱动发光元件的薄膜晶体管的源极层或漏极层电连接至第一电极层 395。而且，在图 12 中，第一电极层 395 部分层叠在配线 199 上来接触。可供选择地，第一电极层 395 先形成，然后在第一电极层上形成配线层 199 来接触。

[0186] 在本实施方式中，FPC 194 通过位于外部终端连接区域 202 内的各向异性导电层 196 连接至终端电极层 178，以用于外部电连接。如显示器件的顶视图（图 7A）所示，本实施方式制得的显示器件除了含有信号线驱动电路的外围驱动电路区域 204 和 209 以外，还包括都含有扫描线驱动电路的外围驱动电路区域 207 和 208。

[0187] 前述的电路在本实施方式中形成，但是，本发明不限定于此。通过前述的 COG 法或 TAB 法，可以安装 IC 芯片作为外围驱动电路。而且，栅线驱动电路和源线驱动电路分别可以设置为单数或复数。

[0188] 在本发明的显示器件中，图像显示的驱动方法没有特别的限定，可以使用点顺序驱动法、线顺序驱动法、区域顺序驱动法等。通常可以使用线顺序驱动法，时分灰度驱动法和区域灰度驱动法也可以适当使用。而且，输入至显示器件源线的视频信号可以为模拟信号或数字信号。驱动电路等可以按照视频信号适当设计。

[0189] 而且，使用数字视频信号的显示器件采用了输入至像素的恒压 (CV) 或恒流 (CC) 视频信号。恒压 (CV) 视频信号包括施加在发光元件的恒压 (CVCV) 和施加在发光元件的恒流 (CVCC)。而且，恒流 (CC) 视频信号包括施加在发光元件的恒压 (CCCV) 和施加在发光元件的恒流 (CCCC)。

[0190] 通过使用本发明，具有高可靠性的显示器件可以通过简单的步骤制得。因而，具有高分辨率和图像品质的显示器件可以低成本、高产量的制得。

### [实施方式 3]

[0192] 按照本发明的实施方式参照图 8A-10 进行描述。本实施方式将描述这样的实例：其中在实施方式 1 制得的显示器件中，不形成第二夹层绝缘膜。因此，省略了相同的部分和具有相同功能的部分的描述。

[0193] 如实施方式 1 中所示，p 通道薄膜晶体管 173-176 和绝缘膜 168 形成在基底 100 上。连接至半导体层的源或漏区域的源或漏极层形成在每个薄膜晶体管中。形成第一电极层 395 来与 p 通道薄膜晶体管 176 中的源或漏极层 172b 接触，所述薄膜晶体管设置在像素部分 206 中（图 8A）。

[0194] 第一电极层 395 用作像素电极，并且可以用与实施方式 2 中第一电极层 395 相同的方法、用相同的材料形成。在本实施方式中，光从如实施方式 1 中的第一电极层透出，因而用作反射电极的 Al (Mo) 膜用于第一电极层 395 并被图案化。

[0195] 形成绝缘层 186 来覆盖第一电极层 395 和薄膜晶体管的边缘部分（图 8B）。在本

实施方式中丙烯酸用于绝缘层 186。电致发光层 188 形成在第一电极层上，并且第二电极层 189 叠层在其上形成了发光元件 190。基底 100 通过密封材料 192 附着于密封基底 195，并且填料 193 填充显示器件（图 9）。在本发明的显示器件中，密封材料和绝缘层 186 分别形成，这样不会相互接触。当密封材料和绝缘层 186 分别形成时，即使当高度吸湿的有机材料的绝缘垫用作绝缘层 186 时，湿气也几乎不能进入发光元件；因而，发光元件的变劣可以阻止并且显示器件的可靠性可以提高。

[0196] 在图 10 所示的显示器件中，在形成连接至 p 通道薄膜晶体管 176 的源或漏极电极层 172b 之前，第一电极层 395 选择性地形成在绝缘膜 168 上。在此情形中，通过在第一电极层上叠置源或漏极层 172b，使源或漏极层 172b 连接至第一电极层 395。当第一电极层 395 在源或漏极层 172b 形成之前形成时，所述第一电极 395 可以形成在平坦区域；由于可以充分实施诸如 CMP 的抛光处理，所以可以具有良好的覆盖度。

[0197] 通过实施本发明，可以制得高可靠性的显示器件。因而，具有高分辨率和高图像品质的显示器件可以制得。

[0198] [ 实施方式 4 ]

[0199] 参照图 13A-13C 描述本发明的实施方式。在本实施方式中，描述了这样的实例：其中在按照实施方式 1 制得的显示器件中，薄膜晶体管的栅极层具有不同的结构。因此，相同的部分或具有相似功能的部分将不会重复。

[0200] 图 13A-13C 分别显示了显示器件的制备步骤，其对应于图 4B 所示的实施方式 1 的显示器件。

[0201] 在图 13A 中，薄膜晶体管 273 和 274 设置在外围驱动电路区域 214 中，且薄膜晶体管 275 和 276 设置在像素部分 216 内。图 13A 中，薄膜晶体管的栅极层由两层导电膜的叠层形成，其中顶部栅极层图案化至比底部栅极层具有更薄的宽度。底部栅极层具有锥形，而顶部栅极层不具有锥形。如此，栅极层可以具有锥形或者为侧角几乎垂直的、没有锥形化的形状。

[0202] 在图 13B 中，薄膜晶体管 373 和 374 设置在外围驱动电路区域 214 内，且薄膜晶体管 375 和 376 设置在像素部分 216 内。在图 13B 中，薄膜晶体管的栅极层也由两层导电膜的叠层形成，其中顶部和底部栅极层具有连续的锥形。

[0203] 图 13C 中，薄膜晶体管 473 和 474 设置在外围驱动电路区域 214 内，且薄膜晶体管 475 和 476 设置在像素部分 216 内。在图 13C 中，薄膜晶体管的栅极层结构具有单层结构并为锥形。此时，栅极层可以具有单层结构。

[0204] 图 13C 的显示器件中，栅绝缘层包括栅绝缘层 477 和选择性地设置在栅绝缘层 477 上的另一栅绝缘层 478。因而，栅绝缘层 478 可以选择性地设置在栅极层的下方，并且其末端或末端部分可以具有锥形。在图 13C 中，栅绝缘层 478 或形成在其上的栅极层中的任一个的端部均具有锥形；但是，它们也可以其它的方式形成阶梯状。

[0205] 如上所述，按照其结构和形状，栅极层可以具有不同的结构。因而，其制得的显示器件也具有不同的结构。当杂质区域使用栅极层作为掩模、以自动对准方式形成时，半导体层中的杂质区域的结构和浓度分布可以根据栅极层的结构来变化。考虑到上述各个方面，具有需要的功能的薄膜晶体管可以通过设计来制得。

[0206] 本实施方式可以与实施方式 1-3 中任一种结合来实施。

[0207] [实施方式 5]

[0208] 下面参照图 15 描述的是这样的方式：其中扫描线侧输入终端部分和信号线侧输入终端部分设置有保护二极管。在图 15 中，像素 2702 设置有 TFT 501 和 502、电容器 504 和发光元件 503。所述的 TFT 具有与实施方式 1 相似的结构。

[0209] 保护二极管 561 和 562 设置在信号线侧输入终端部分内。所述的保护二极管通过与 TFT 501 和 502 相似的步骤来制得，从而，栅与漏和源中的一个连接来用作二极管。图 14 显示了图 15 的顶视图的等效电路图。

[0210] 保护二极管 561 包括栅极层、半导体层和配线层。保护二极管 562 具有相似的结构。连接至上述保护二极管的共用等势线 554 和 555 由与栅极层相同的层形成。因而，需要在绝缘层里形成接触孔来电连接至配线层。

[0211] 在绝缘层里的接触孔可以通过形成掩模层并在其上施加蚀刻来形成。在此情形中，通过施加常压放电蚀刻，可以进行局部放电，其中掩模层不需要形成在基底的整个表面上。

[0212] 信号配线层由与源和漏配线层 505 相同的层形成。所述信号配线层和源或漏侧相互连接。

[0213] 在扫描信号线侧上的输入终端部分具有相似的结构。保护二极管 563 包括栅极层、半导体层和配线层。保护二极管 564 具有相似的结构。连接至上述保护二极管的共用等势线 556 和 557 由与源极层和漏极层相同的层形成。设置在输入级内的保护二极管同时形成。需要注意的是，保护二极管不限定于设置在本实施方式中显示的位置，而可以设置在驱动电路和像素之间。

[0214] [实施方式 6]

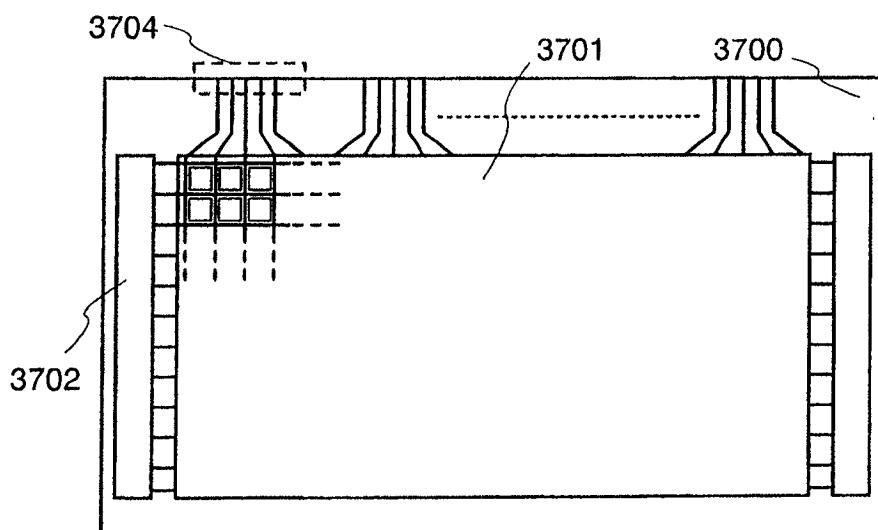

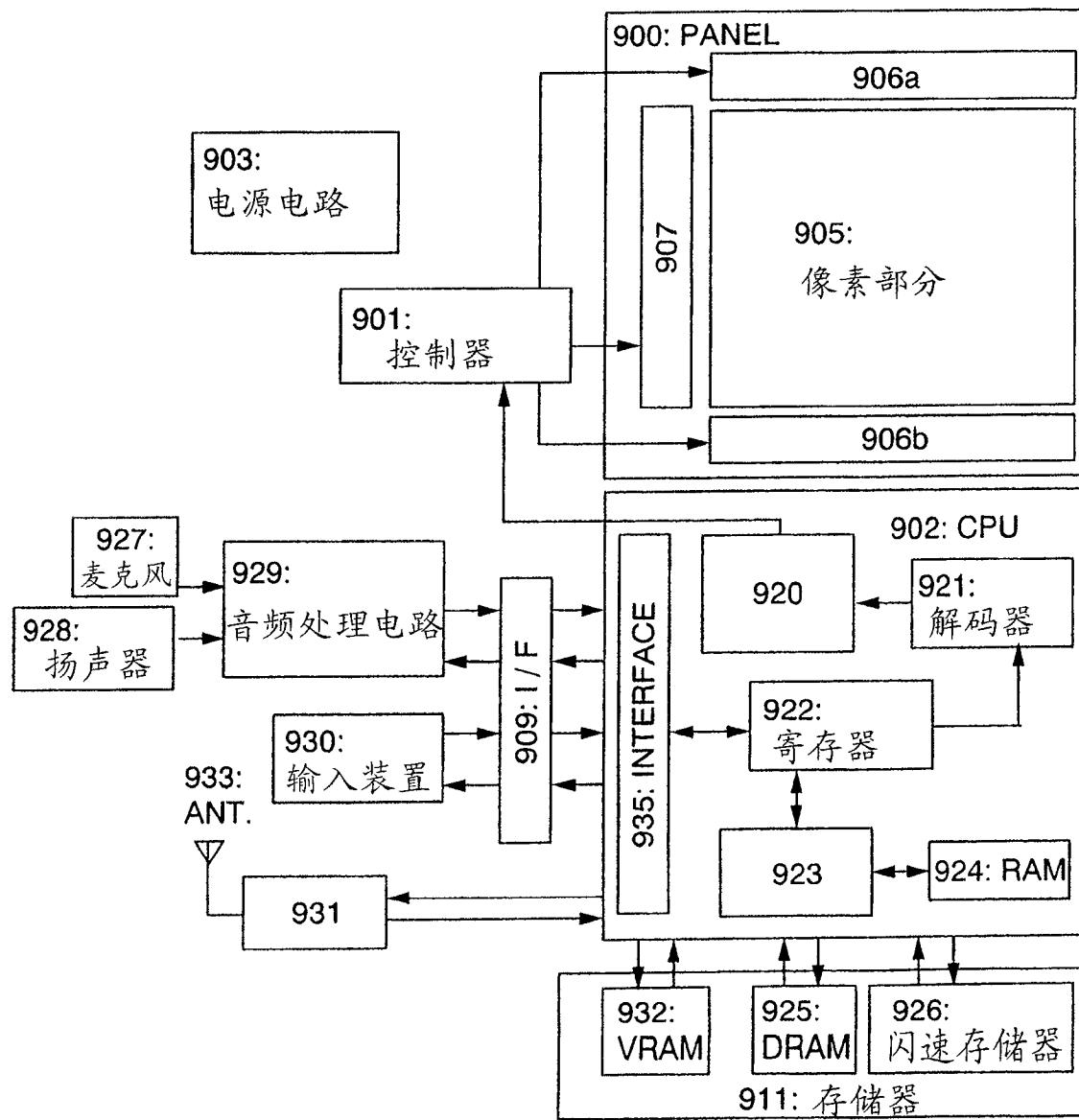

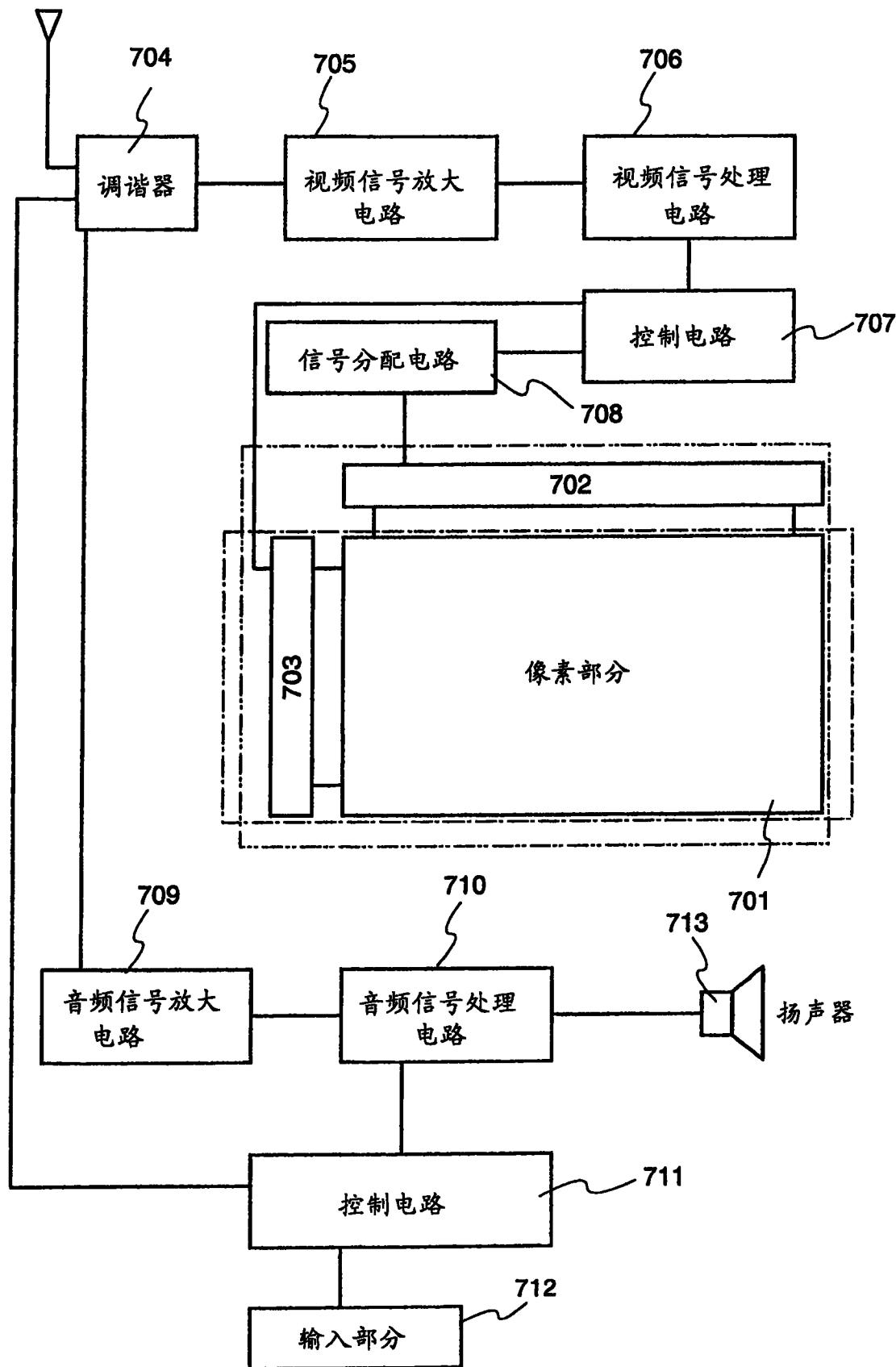

[0215] 电视设备可以由按照本发明形成的显示器件来完成。图 27 为显示电视设备（本实施方式中的 EL 电视设备）的主要结构的框图。显示板可以通过下述任一种方式形成：图 16A 所示的结构只形成像素部分 701，且扫描线驱动电路 703 和信号线驱动电路 702 通过如图 17B 所示 TAB 法设置；或者图 16A 所示的结构只形成像素部分 701，且扫描线驱动电路 703 和信号线驱动电路 702 通过如图 17A 所示 COG 法设置；如图 16B 所示，由 SAS 形成 TFT，像素部分 701 和扫描线驱动电路 703 形成并集成在基底上，且信号线驱动电路 702 分别用作驱动 IC；如图 16C 所示，像素部分 701、信号线驱动电路 702 和扫描线驱动电路 703 形成并集成在基底上等等。

[0216] 在视频信号的输入侧，外部电路的另一种结构包括：视频信号放大电路 705，其放大通过调谐器收到的信号中的视频信号；视频信号处理电路 706，其将输出的信号转换为对应于红、绿和蓝每种颜色的彩色信号；控制电路，其将视频信号转换为驱动器 IC 的输入规格；等等。控制电路 707 将信号分别输出至扫描线侧和信号线侧。在数字驱动中，信号分配电路 708 可以设置在信号线侧上，这样输入的数字信号通过分为 m 片来提供。

[0217] 在从调谐器 704 收到的信号中，音频信号传送至音频放大电路 709，且其的输出通过音频信号处理电路 710 提供给扬声器 713。控制电路 711 在接收站（接收频率）处收到控制信息或者收到从输入部分 712 得来的音量，并将信号传送至调谐器 704 或音频信号处理电路 710。

[0218] 如图 20A 和 20B 所示，电视设备可以通过将显示模块结合在机壳中来完成。如图 1

所示的、附着有FPC的显示板通常称为EL显示模块。当使用如图1所示的EL显示模块时，EL电视设备可以完成。通过使用显示模块形成主屏幕2003，且扬声器单元2009、操作开关等作为其它附属装备来设置。在此情形中，按照本发明可以完成电视设备。

[0219] 另外，通过使用波片和偏光片，从外部进入的光的反射光可以被屏蔽。在顶部发射型显示器件中，将成为存储单元的绝缘层可以着色来用作黑色矩阵。所述的存储单元可以通过滴状喷射法等形成，且黑色树脂颜料、混有碳黑的、诸如聚酰亚胺的树脂材料等可以使用，或者也可以使用它们的叠层结构。按照滴状喷射法，不同的材料可以多次喷射在相同的区域来形成存储单元。四分之一或半波片可以用作波片并可以设计为能控制光。作为这样的结构，TFT元件基底、发光元件、密封基底（密封材料）、波片（四分之一或半波片）、偏光片依次层叠，其中从发光元件发出的光穿过上述部件，从偏光片侧的外面发出。波片或偏光片可以设置在光发出侧，或者当使用光从双面发出的双发射型显示器件时，可以设置在两侧。另外，抗反射膜可以设置在偏光片的外侧。相应地，可以显示较高分辨率和较高精确度的图像。

[0220] 如图20A所示，使用显示元件的显示板2002被结合在机壳2001内。通过使用接收器2005，除了接收常规的TV广播，还可以通过固定线路或借助无线调制解调器2004来连接至通讯网络，使信息通信在一个方向（从发送器到接收器）或在双方向（发送器和接收器之间或者在接收器之间）实现。电视设备的操作可以通过结合在机壳内的开关或者通过与主体分开的遥控器2006来实现。显示待输出信息的显示部分2007也可以设置在遥控器上。

[0221] 此外，在电视设备中，除了主屏2003以外，通过形成作为第二显示板的子屏幕，用来显示频道、音量等的结构还可以另外设置。在该结构中，主屏2003由在视角上占优势的EL显示板形成，而子屏幕由液晶显示板形成，所述液晶显示板能低功耗地显示子屏幕。为了优先考虑低功耗，下述结构也可以适用：其中主屏2003由液晶显示板形成，而子屏幕由EL显示板形成，且子屏幕能够闪出(flash on)和消失(flash off)。根据本发明，即便当使用大量TFT和电子部件时，使用如此大的基底，具有高可靠性的显示器件也可以制得。

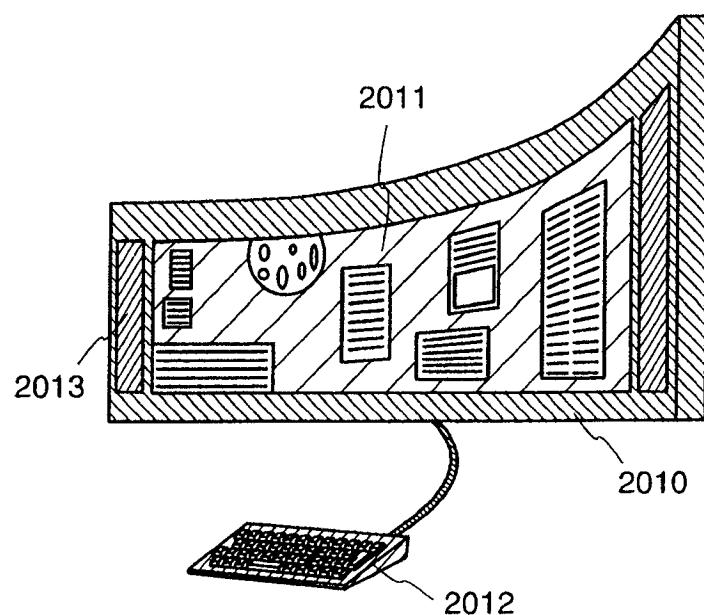

[0222] 图20B显示了具有大的显示部分例如20-80英寸的电视设备，其包括机壳2010、作为操作部分的键盘2012、显示部分2011、扬声器单元2013等。本发明适用于制备显示部分2011。图20B显示了具有曲面显示部分的电视设备，因为将柔性材料用于了显示部分。由于显示部分的形状可以自由地设计，所以具有需要的形状的电视设备可以制得。

[0223] 根据本发明，通过简单的工艺可以制得显示器件，从而生产成本可以降低。因此，通过使用本发明，即使是具有大屏幕显示部分的电视设备也可以以低成本形成。相应地，具有高性能和高可靠性的电视设备可以以高产量制得。

[0224] 注意的是，本发明不限于电视设备，并且可以用于各种用途，特别是用于具有大面积的显示介质，如在车站、机场等的信息显示板，或者街道上的广告显示板，也可以用于个人电脑的显示器。

[0225] [实施方式7]

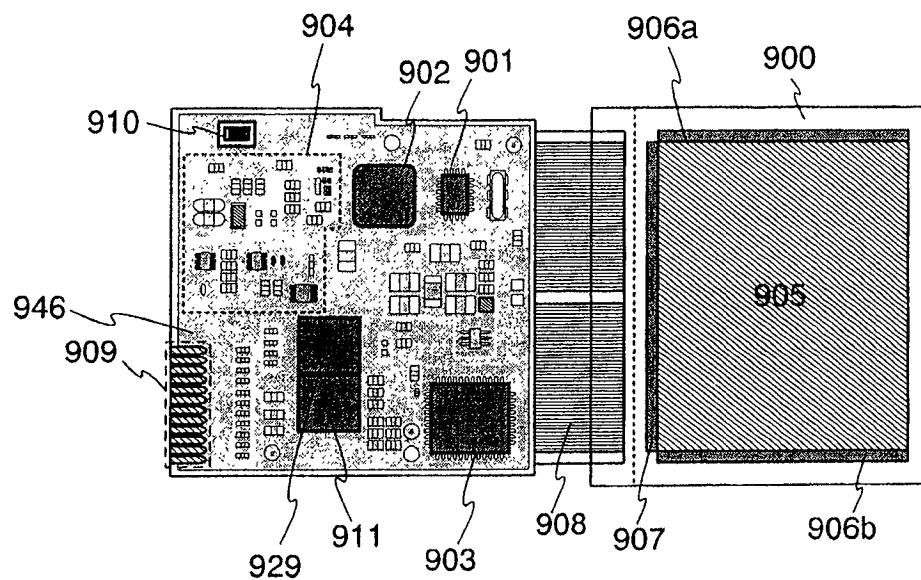

[0226] 本实施方式参照图21A和21B描述。在本实施方式中，描述基于使用带有按照实施方式1-6制得的显示器件的面板的模块的实例。

[0227] 如图21A所示的信息终端模块具有印刷电路板946，其上安装有控制器901、中央

处理器 (CPU) 902、存储器 911、电源电路 903、音频处理电路 929、传输 / 接收电路 904、以及诸如电阻器、缓冲器、电容器的其它部件。而且，面板 900 通过柔性印刷电路 (FPC) 908 连接至印刷电路板 946。

[0228] 面板 900 包括像素部分 905、在像素部分 905 上选择像素的第一扫描线侧驱动电路 906a 和第二扫描线侧驱动电路 906b、以及给被选像素提供视频信号的信号线驱动电路 907，所述的像素部分 905 中每个像素具有发光元件。

[0229] 各种信号通过设置在印刷电路板 946 上的接口 (I/F) 909 输入和输出。利用天线发射和接收信号的天线端口 910 设置在印刷电路板 946 上。

[0230] 需要注意的是，在本实施方式中，印刷电路板 946 通过 FPC908 连接至面板 900，但是本发明不限于这种结构。控制器 901、音频处理电路 929、存储器 911、CPU 902 或电源电路 903 可以通过 COG (玻板上的芯片) 法，直接安装在面板 900 上。而且，诸如电容器和缓冲器的各种元件设置在印刷电路板 946 上，从而可以阻止下述情况发生：电源电压和信号中产生噪音以及信号上升时间变慢。

[0231] 图 21B 为图 21A 所示的模块的框图。该模块 999 包括作为存储器 911 的 VRAM 932、DRAM 925、闪速存储器 926 等。所述的 VRAM 932 具有显示在面板上的图像数据，DRAM 925 具有图像数据或音频数据，且闪速存储器具有各种程序。

[0232] 电源电路 903 产生施加在面板 900、控制器 901、CPU 902、音频处理电路 929、存储器 911 和传输 / 接收电路 931 上的电源电压。电流源提供在电源电路 903 的何处取决于所述面板的规格。

[0233] CPU 902 包括控制信号产生电路 920、解码器 921、寄存器 922、运算电路 923、RAM 924、用于 CPU 的界面 935 等。通过接口 935 输入至 CPU 902 的各种信号保存在寄存器 922 中，然后输入至运算电路 923、解码器 921 等。在运算电路 923 中，基于输入信号完成算术运算并确定各种指令的地址。同时，输入至解码器 921 的信号被解码并输入至控制信号产生电路 920。控制信号产生电路 920 产生含有基于输入信号的各种指令的信号，然后将所述信号传输至运算电路 923 确定的地址，具体有存储器 911、传输 / 接收电路 931、音频处理电路 929 和控制器 901 等。

[0234] 存储器 911、传输 / 接收电路 929 和控制器 901 中每一个均按照收到的指令运行。由此简短地描述了运行过程。

[0235] 从输入装置 930 输入的信号传输至 CPU902，所述的 CPU902 通过接口 909 安装至印刷电路板 946。基于从诸如指点器 (pointing device) 和键盘的输入装置 930 传输的信号，控制信号产生电路 920 将储存在 VRAM932 中的图像数据转换为预定的格式，并传输所述数据至控制器 901。

[0236] 控制器 901 处理含有从按照面板规格的 CPU 902 传输的图像数据的信号，然后将所述信号传输至面板 900。而且，基于从电源电路 903 输入的电源电压以及从 CPU 902 输入的各种信号，控制器 901 产生 Hsync 信号、Vsync 信号、时钟信号 CLK、交流电压 (AC Cont) 和开关信号 L/R，并将这些信号供给面板 900。

[0237] 传输 / 接收电路 904 处理信号，所述信号通过天线 933，作为电磁波来传输和接收。具体地，传输 / 接收电路 904 包括高频电路，例如隔离器、带通滤波器、VOC (电压控制的振荡器)、LPF (低通滤波器)、耦合器以及平衡 - 不平衡变压器。在通过传输 / 接收电路 904 传

输和接收的信号中,根据 CPU 902 的指令,含有音频数据的信号传输至音频处理电路 929。

[0238] 含有根据 CPU 902 的指令传输的音频数据的信号通过音频处理电路 929 解调为音频信号,并传输至扬声器 928。根据 CPU902 的指令,从麦克风 927 传输的音频信号通过音频处理电路 929 调制,并传输至传输 / 接收电路 904。

[0239] 控制器 901、CPU902、电源电路 903、音频处理电路 929 以及存储器 911 可以作为本实施方式的封装安装。本实施方式可适用于任何电路,除了高频电路,例如隔离器、带通滤波器、VCO(电压控制的振荡器)、LPF(低通滤波器)、耦合器和平衡 - 不平衡变压器。

[0240] [ 实施方式 8 ]

[0241] 本实施方式参照图 21A- 图 22 进行描述。图 22 显示了含有按照实施方式 8 制得的模块的无线紧凑型电话(蜂窝电话)的一个模式。可拆卸的面板 900 可以装入外壳 1001 中并易于与模块 999 集成。外壳 1001 的形状和尺寸可以根据电子设备适当变化。

[0242] 装配面板 900 的外壳 1001 安装在印刷电路板 946 上,并且完成来作为模块。印刷电路板 946 结合有控制器、CPU、存储器、电源电路以及诸如电阻器、缓冲器和电容器的其它元件。而且,设置含有麦克风 994 和扬声器 995 的音频处理电路,以及诸如传输 / 接收电路的信号处理电路 993。面板 900 通过 FPC908 连接至印刷电路板 946。

[0243] 所述的模块 999、输入装置 998 以及电池 997 存储在外壳 996 内。面板 900 的像素部分设置为可以从外壳 996 上形成的开放式窗口看到。

[0244] 如图 22 所示的外壳 996 显示了电话的外观的一个实例。按照本实施方式的电子设备可以根据功能和应用变化为各种模式。这些模式中的一个实例见下述实施方式的描述。

[0245] [ 实施方式 9 ]

[0246] 通过实施本发明可以制得各种显示器件。换句话说,本发明可以适用于各种电子设备,其中所述的显示器件结合在显示区域内。

[0247] 所述的电子设备包括诸如摄像机或数码相机的照相机、投影仪、前置型显示器(head mounted display)(突出型显示器(goggle type display))、汽车导航系统、汽车立体声、个人电脑、游戏机、便携式信息终端(移动电脑、蜂窝电话、电子书等)、设置有记录介质的图像再现设备(特别是能够播放记录介质的设备,例如数字光盘放映机(DVD)以及具有能显示图像的显示器件的设备)等。图 19A-19D 显示了它们的实例。

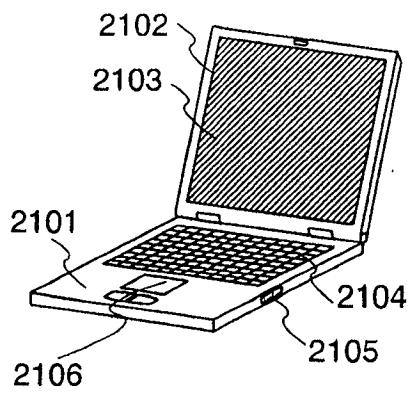

[0248] 图 19A 显示了计算机,其包括机身 2101、机壳 2102、显示区域 2103、键盘 2104、外接部分 2105、指示鼠标 2106 等。根据本发明,可以显示具有高可靠性和高分辨率的图像的计算机可以完成,即便该计算机小型化且像素是微小的。

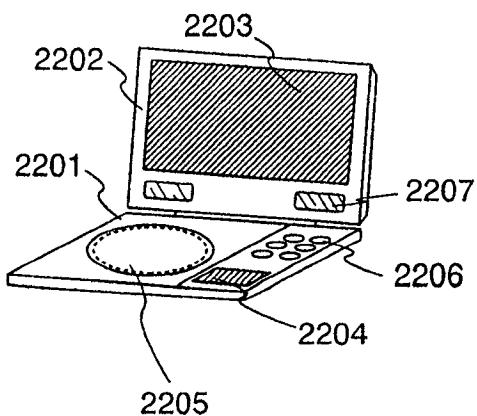

[0249] 图 19B 显示了设置有记录介质的图像再现设备(特别是 DVD 再现设备),其包括机身 2201、机壳 2202、显示区域 A 2203、显示区域 B 2204、记录介质(如 DVD)读取部分 2205、操作键 2206、扬声器部分 2207 等。显示区域 A 2203 主要显示图像信息,而显示区域 B 2204 主要显示字符信息。根据本发明,可以显示具有高可靠性和高分辨率的图像的图像再现设备可以完成,即便该设备小型化且像素是微小的。

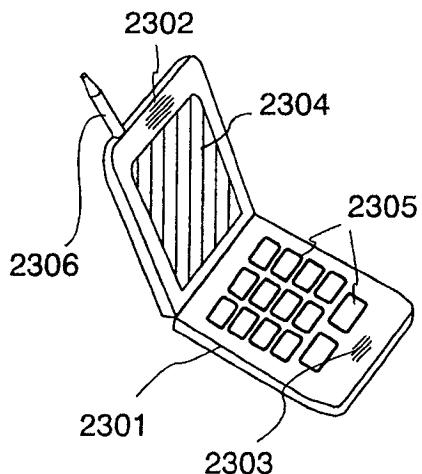

[0250] 图 19C 显示了蜂窝电话,其包括机身 2301、音频输出部分 2302、音频输入部分 2303、显示区域 2304、操作开光 2305 和天线 2306 等。根据本发明,可以显示具有高可靠性和高分辨率的图像的蜂窝电话可以完成,即便该蜂窝电话小型化且像素是微小的。

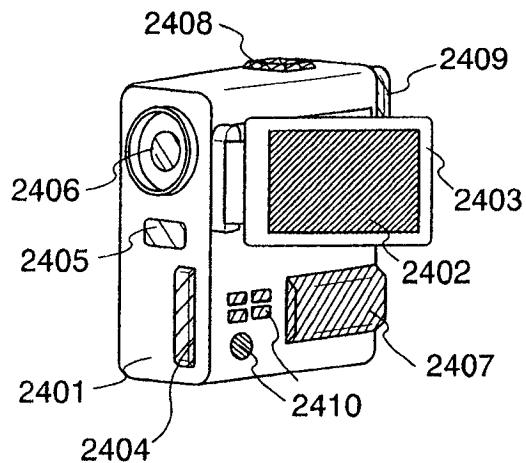

[0251] 图 19D 显示了摄像机,其包括机身 2401、显示区域 2402、机壳 2403、外部连接口

2404、遥控接收部分 2405、图象接收部分 2406、电池 2407、音频输入部分 2408、目镜 2409、操作键 2410 等。根据本发明，可以显示具有高可靠性和高分辨率的图像的摄像机可以完成，即便该摄像机小型化且像素是微小的。本实施方式可以自由地与上述实施方式结合。

[0252] [ 实施例 1 ]

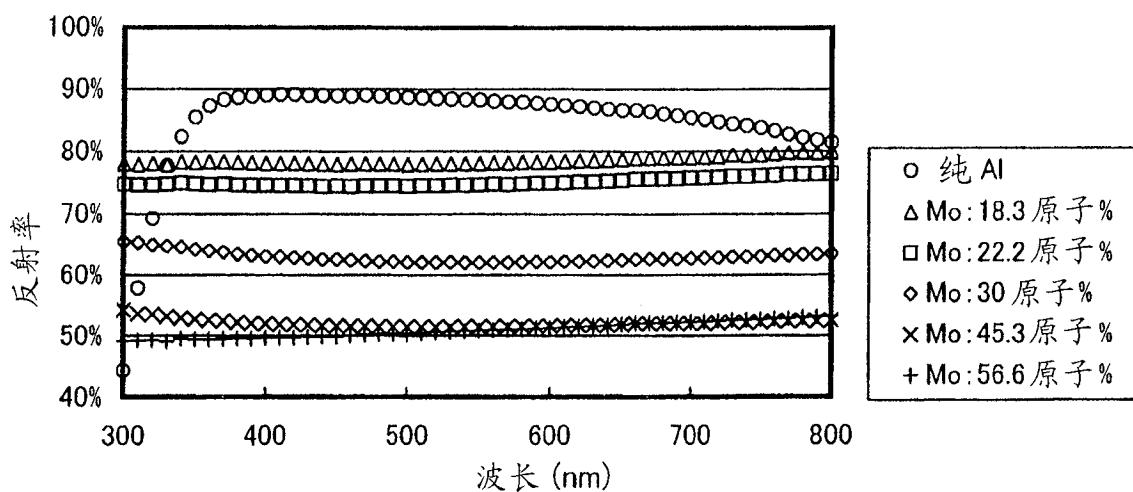

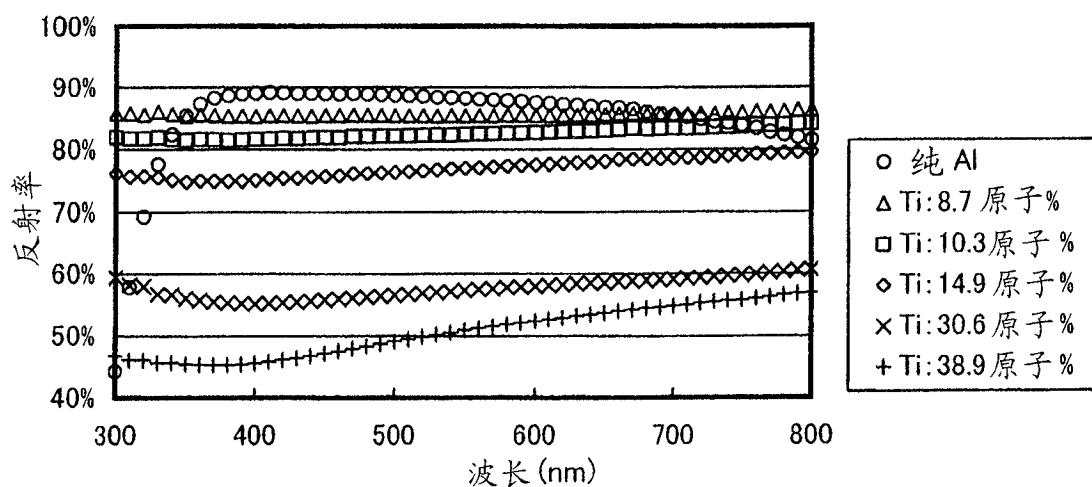

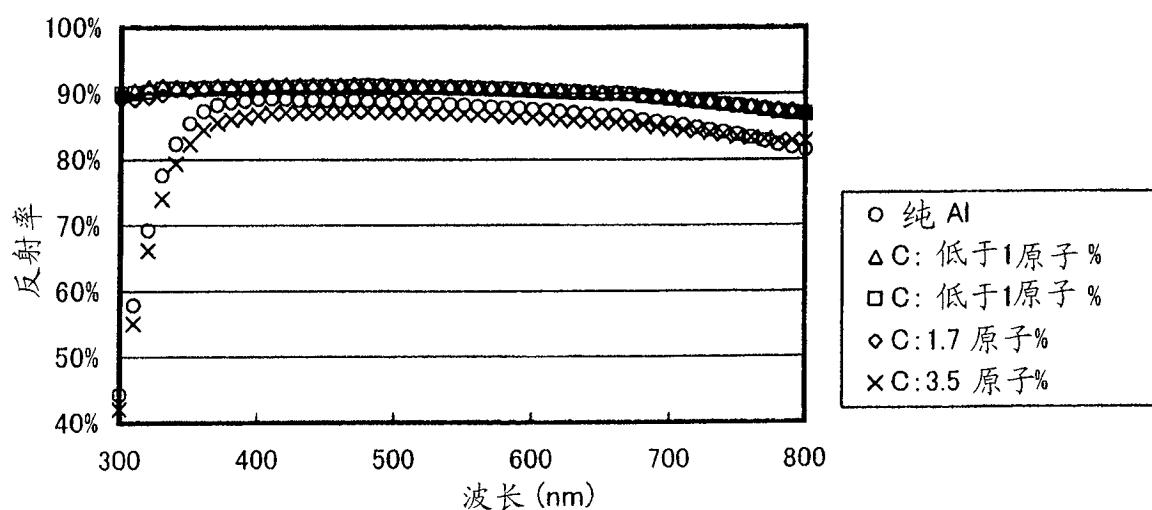

[0253] 在本实施方式中，将显示用作本发明电极层的含有铝合金的膜的性能测试结果，所述铝合金含有选自钼、钛和碳中的至少一种或多种。

[0254] 薄片状的钼、钛或碳分别在铝靶上制备，并溅射形成含有包含钼的铝合金的膜 (Al(Mo))、含有包含钛的铝合金的膜 (Al(Ti)) 以及含有包含碳的铝合金的膜 (Al(C))。沉积条件如下：功率为 1.5–2kW，压力为 0.4Pa，且 Ar 气体的流动速率为 50sccm。在样品中，Al(Mo) 膜中钼的含量、Al(Ti) 膜中 Ti 的含量以及 Al(C) 膜中碳的含量是变化的，并且每个样品的性能均进行评价。

[0255] 首先，测试包含铝合金的膜的反射率，所述铝合金含有选自钼、钛和碳中的至少一种或多种。下述膜用作样品：钼含量分别为 18.3 原子%、22.2 原子%、30.0 原子%、45.3 原子% 和 56.6 原子% 的五种 Al(Mo) 膜；钛含量分别为 8.7 原子%、10.3 原子%、14.9 原子%、30.6 原子% 和 38.9 原子% 的五种 Al(Ti) 膜；四种 Al(C) 膜，其中两种的碳含量低于 1 原子% 且其它两种分别具有 1.7 原子% 和 3.5 原子% 的碳含量；以及纯铝膜（参照在图 23A–23C 的符号为纯 Al）。注意的是，在测试前，沉积后的所述样品在 300°C 加热 1 小时，这在实际处理中要记住。在实际处理中加热步骤通常在形成反射电极以后进行。Al(Mo) 的每个样品对应于每个波长的反射率见图 23A 所示，Al(Ti) 的每个样品对应于每个波长的反射率见图 23B 所示，且 Al(C) 的每个样品对应于每个波长的反射率见图 23C 所示。

[0256] 在图 23A 中，圆圈表示纯铝膜，三角形表示含有 18.3 原子% 的钼的 Al(Mo) 膜的测量值，方形表示含有 22.2 原子% 的钼的 Al(Mo) 膜的测量值，菱形表示含有 30.0 原子% 的钼的 Al(Mo) 膜的测量值，× 形表示含有 45.3 原子% 的钼的 Al(Mo) 膜的测量值，且十字形表示含有 56.6 原子% 的钼的 Al(Mo) 膜的测量值。类似地，在图 23B 中，圆圈表示纯铝膜，三角形表示含有 8.7 原子% 的钛的 Al(Ti) 膜的测量值，方形表示含有 10.3 原子% 的钛的 Al(Ti) 膜的测量值，菱形表示含有 14.9 原子% 的钛的 Al(Ti) 膜的测量值，× 形表示含有 30.6 原子% 的钛的 Al(Ti) 膜的测量值，且十字形表示含有 38.9 原子% 的钛的 Al(Ti) 膜的测量值。在图 23C 中，圆圈表示纯铝膜，三角形和方形表示含有低于 1 原子% 的碳的 Al(C) 膜的测量值，菱形表示含有 1.7 原子% 的碳的 Al(C) 膜的测量值，× 形表示含有 3.5 原子% 的碳的 Al(C) 膜的测量值。虽然均表示碳含量低于 1 原子%，用三角形表示的膜比用方形表示的膜含有更低含量的碳。测量反射率的样品每个具有 200nm 的厚度。

[0257] 如图 23A、23B 和 23C 所示，在波长低于约 450nm 处，纯铝膜的反射率降低；但是含有铝合金的膜中大多数在波长接近可见光区域处，反射率几乎为恒定的并且没有减少，所述的铝合金中含有选自钼、钛和碳中的至少一种或多种。因而，由于反射率的波长无关性，每个含有铝合金的膜可以在可见光区域内保持一定的反射率，从而用作反射电极来有效地反射从发光元件发出的光，所述的铝合金中含有选自钼、钛和碳中的至少一种或多种。而且，所述的膜几乎不吸收光，因而几乎不在其中集热。因此，由于热导致的发光元件变劣也可以阻止，从而可以提高显示器件的可靠性。因此，所述的显示器件可以充分利用而功能不会下降，即使是使用在强光下，例如户外亦如此。当膜中钼、钛或碳的含量增加时，反射率会

降低。考虑到膜用作反射电极时的光反射率,优选在 Al(Mo) 膜中钼的含量为 22.2 原子% 或更低,在 Al(Ti) 膜中钛的含量为 14.9 原子% 或更低,且在 Al(C) 膜中碳的含量为 1.7 原子% 或更低。

[0258] 接着,测量每个样品的膜表面上的不均匀处的最大高度差值(峰 - 谷值(P-V 值))。测量使用原子力显微镜(AFM)来进行;测量范围为  $2 \mu\text{m} \times 2 \mu\text{m}$ 。在 Al(Mo) 膜中钼含量的 P-V 值变化见图 24A 所示,在 Al(Ti) 膜中根据钛含量,P-V 值变化见图 24B 所示。在图 24B 中,圆圈表示包含含有钛和碳的铝合金的膜,且钛在膜中的含量为 2.7 原子%、碳在膜中含量为 1 原子% 或更低。而且,图 24A 和 24B 显示了 Al(Mo) 膜和 Al(Ti) 膜的表面评价结果。含有氧化硅的氧化铟锡膜(ITS0 膜)形成在每一个 Al(Mo) 膜和 Al(Ti) 膜上。测量每个 ITS0 膜的表面的顶层的 P-V 值,结果见图 25A 和 25B 所示。测量 P-V 值的每个样品的厚度为 35nm。

[0259] 在图 24A 中,每个样品的 P-V 测量值如下:纯铝膜:17.51nm,含有 18.3 原子% 的钼的 Al(Mo) 膜:4.421nm,含有 22.2 原子% 的钼的 Al(Mo) 膜:3.711nm,含有 30.0 原子% 的钼的 Al(Mo) 膜:1.738nm,含有 45.3 原子% 的钼的 Al(Mo) 膜:0.9358nm,且含有 56.6 原子% 的钼的 Al(Mo) 膜:0.8159nm。在图 24B 中,每个样品的 P-V 测量值如下:纯铝膜:17.51nm,含有 8.7 原子% 的钛的 Al(Ti) 膜:8.239nm,含有 10.3 原子% 的钛的 Al(Ti) 膜:5.887nm,含有 14.9 原子% 的钛的 Al(Ti) 膜:5.75nm,含有 30.6 原子% 的钛的 Al(Ti) 膜:1.981nm,含有 38.9 原子% 的钛的 Al(Ti) 膜:2.493nm,且包含含有钛和碳的铝合金的膜:1.46nm。

[0260] 在图 25A 中,每个 ITS0 膜表面的最上层的 P-V 测量值如下:含有 18.3 原子% 的钼的 Al(Mo) 膜:1143nm,含有 22.2 原子% 的钼的 Al(Mo) 膜:2.32nm,含有 30.0 原子% 的钼的 Al(Mo) 膜:2.144nm,含有 45.3 原子% 的钼的 Al(Mo) 膜:2.109nm,且含有 56.6 原子% 的钼的 Al(Mo) 膜:1.603nm。在图 25B 中,每个 ITS0 膜表面的最上层的 P-V 测量值如下:含有 8.7 原子% 的钛的 Al(Ti) 膜:8.137nm,含有 10.3 原子% 的钛的 Al(Ti) 膜:6.407nm,含有 14.9 原子% 的钛的 Al(Ti) 膜:6.005nm,含有 30.6 原子% 的钛的 Al(Ti) 膜:5.178nm,且含有 38.9 原子% 的钛的 Al(Ti) 膜:2.635nm。

[0261] 纯铝膜表面的 P-V 值为 Al(Mo) 膜、Al(Ti) 膜以及包含含有钛和碳的铝合金的膜表面的 P-V 值的两倍或多于两倍,这表示纯铝膜的平面化程度较差。另一方面,勿庸置疑,由于它们的 P-V 值低,所以 Al(Mo) 膜、Al(Ti) 膜以及包含含有钛和碳的铝合金的膜在表面上具有良好的平面性。而且,已经表明在含有铝合金的膜中,钼或钛的含量越高,则 P-V 值往往越低,其中所述的铝合金中含有选自钼、钛和碳中的至少一种或多种。而且,即便当钛的含量为 2.7 原子% 时,包含含有钛和碳的铝合金的膜的 P-V 值低至 1.46nm。因而,加入碳来提高表面平坦性的效果是可以证实的。

[0262] 此外,形成纯铝膜和 Al(C) 膜(膜中碳的含量低于 1 原子%)。用 X 射线衍射(XRD)测量它们的结晶度,来评价在 300°C 烘烤的薄膜的表面条件。在 Al(C) 膜的 (111) 衍射峰内的峰值强度为 684CPS,其为纯铝膜的 4341CPS 的七分之一。由于结晶被促进,所以纯铝的结晶度相应地较高。另一方面,由于结晶被抑制,所以 Al(C) 膜的结晶度较低。所以可以认为由于具有较低的结晶度,Al(C) 膜的平面化较高。

[0263] 从上述测试结果可以证实,通过在铝中加入选自钼、钛和碳的一种或多种,膜的表面平面化可以提高并且可以得到高的反射率。当所述的膜用作显示器件的反射电极时,从

所述发光元件发射光的效率是优选的，而且可以制得高可靠性的显示器件，其中由于电极表面粗糙引起的缺陷可以减少。

图 1A

图 1B

4A

图

4B

图

5A

图

5B

图

5C

图

图 7A

图 7B

图 9

图 10

图 11

图 12

图 14

图 15

图 16A

图 16B

图 16C

图 17A

图 17B

图 18A

图 18B

图 19A

图 19B

图 19C

图 19D

图 20A

图 20B

图 21A

图 21B

图 22

图 23A

图 23B

图 23C

图 24A

图 24B

图 25A

图 25B

图 26

图 27

|                |                                                                                                     |         |            |

|----------------|-----------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示器件及其制备方法                                                                                          |         |            |

| 公开(公告)号        | <a href="#">CN1808722B</a>                                                                          | 公开(公告)日 | 2010-06-16 |

| 申请号            | CN200510023023.5                                                                                    | 申请日     | 2005-11-04 |

| [标]申请(专利权)人(译) | 株式会社半导体能源研究所                                                                                        |         |            |

| 申请(专利权)人(译)    | 株式会社半导体能源研究所                                                                                        |         |            |

| 当前申请(专利权)人(译)  | 株式会社半导体能源研究所                                                                                        |         |            |

| [标]发明人         | 秋元健吾<br>丸山穂高<br>曾根寛人<br>池田寿雄<br>坂田淳一郎<br>瀬尾哲史                                                       |         |            |

| 发明人            | 秋元健吾<br>丸山穂高<br>曾根寛人<br>池田寿雄<br>坂田淳一郎<br>瀬尾哲史                                                       |         |            |

| IPC分类号         | H05B33/26 H05B33/10 H01L21/82 H01L27/15 H01L27/32                                                   |         |            |

| CPC分类号         | H01L27/3244 H01L27/3258 H01L2251/5315 H01L51/5206 H01L27/1214 H01L51/5052 H01L27/124<br>H01L51/5218 |         |            |

| 审查员(译)         | 邵烨                                                                                                  |         |            |

| 优先权            | 2004320381 2004-11-04 JP                                                                            |         |            |

| 其他公开文献         | CN1808722A                                                                                          |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                      |         |            |

**摘要(译)**

本发明的目的是低成本、高产量制备高可靠的显示器件。本发明的显示器件包括：其间插有电致发光层的第一反射电极层和第二透明电极层，其中电致发光层具有含有有机化合物和无机化合物的层，且第一电极层包含含有选自铝、钛和碳中至少一种的铝合金。