## [12] 发明专利申请公开说明书

[21] 申请号 200510053150. X

[43] 公开日 2005 年 9 月 7 日

[11] 公开号 CN 1664901A

[22] 申请日 2005. 3. 4

[74] 专利代理机构 中科专利商标代理有限责任公司

[21] 申请号 200510053150. X

代理人 王 玮

[30] 优先权

[32] 2004. 3. 4 [33] GB [31] 0404919. 3

[71] 申请人 精工爱普生株式会社

地址 日本东京

[72] 发明人 西蒙·塔姆

权利要求书 6 页 说明书 18 页 附图 17 页

[54] 发明名称 像素电路

[57] 摘要

已知的是，对用于驱动发光器件的像素电路中的驱动晶体管的阈值电压变化进行补偿，例如电流驱动有机发光器件。然而，对这样的像素电路进行编程和初始化可能较慢且需要多个控制或信号线。本发明提出了一种像素电路，包括用于对驱动晶体管进行二极管连接的 n 沟道晶体管和用于减少信号和控制线数量的装置。

## 1. 一种像素电路，包括：

5 在电源线和参考线之间串联的第一晶体管和电容器，第一晶体管的栅极端子设置用于接收第一控制信号；

在电源线和另一线之间串联的驱动晶体管和发光器件，所述驱动晶体管具有与位于第一晶体管和电容器之间的第一节点相连的栅极端子、以及用于接收数据信号的第一端子；以及

10 第二晶体管，设置用于响应在第二晶体管的栅极端子处接收到的第二控制信号，对驱动晶体管进行二极管连接，由此，使数据信号能够通过被二极管连接的驱动晶体管并保持在第一节点处，所述第二晶体管是n沟道型晶体管。

2. 根据权利要求1所述的像素电路，其特征在于还包括：在电源线和驱动晶体管之间串联的第三晶体管和在发光器件和驱动晶体管之间串联的第四晶体管，其中第二晶体管的一个端子与在驱动晶体管和第三晶体管之间的第二节点处的驱动晶体管的第二端子相连。

3. 根据权利要求2所述的像素电路，其特征在于所述第三和第四晶体管是p沟道型晶体管且它们的栅极端子设置用于接收第二控制信号。

4. 根据权利要求2或3所述的像素电路，其特征在于还包括在数据信号线和位于驱动晶体管和第四晶体管之间的第三节点之间连接的第五晶体管。

5. 根据权利要求4所述的像素电路，其特征在于第五晶体管是n沟道型晶体管且包括用于接收第二控制信号的栅极端子。

6. 根据权利要求2到5任一个所述的像素电路，其特征在于还包括在第四晶体管和发光器件之间串联的第六晶体管，所述第六晶体管具有与第一晶体管相反的沟道类型且具有用于接收第一控制信号的栅极端子。

30 7. 根据权利要求1到6任一个所述的像素电路，其特征在于还包

括在驱动晶体管的栅极端子和第一节点之间串联的第七晶体管、以及连接在电源线和位于第七晶体管的一个端子和驱动晶体管的栅极端子之间的第四节点之间的第八晶体管，其中第八晶体管具有与第一晶体管相同的沟道类型且第七晶体管具有与第一晶体管相反的沟道类型，

5 第七和第八晶体管的栅极端子设置用于接收第一控制信号。

8. 根据权利要求1到6任一个所述的像素电路，其特征在于还包括连接在第一节点和与驱动晶体管的栅极端子相连的第二晶体管的端子之间的第九晶体管、以及连接在第一节点和与驱动晶体管的第二端子相连的第二晶体管的另一端子之间的第十晶体管，其中第九晶体管是p沟道型晶体管而第十晶体管是n沟道型晶体管，且第九和第十晶体管的栅极端子设置用于分别接收第一和第二控制信号。

9. 一种用于驱动电流驱动元件的像素电路，包括：

第一晶体管，其导通状态对应于提供给电流驱动元件的驱动电流的电流电平，第一晶体管具有第一栅极端子、第一端子和第二端子；

15 第二晶体管，具有第二栅极端子；以及

第三晶体管，设置用于控制第一栅极端子和第一端子和第二端子之一之间的电连接，所述第三晶体管具有第三栅极端子；

第一端子设置用于通过第二晶体管接收数据信号，所述数据信号确定第一晶体管的导通状态；以及

20 第一晶体管的导通类型不同于第二晶体管的导通类型。

10. 一种用于驱动电流驱动元件的像素电路，包括：

第一晶体管，其导通状态对应于提供给电流驱动元件的驱动电流的电流电平，第一晶体管具有第一栅极端子、第一端子和第二端子；

第二晶体管，具有第二栅极端子；以及

25 第三晶体管，设置用于控制第一栅极端子和第一端子和第二端子之一之间的电连接，所述第三晶体管具有第三栅极端子；

第一端子设置用于通过第二晶体管接收数据信号，所述数据信号确定第一晶体管的导通状态；以及

第一晶体管的导通类型不同于第三晶体管的导通类型。

30 11. 根据权利要求9或10所述的像素电路，其特征在于

还包括在电流驱动元件和第一晶体管之间串联且具有第四栅极端子的第四晶体管。

12. 根据权利要求11所述的像素电路，其特征在于第四晶体管的导通类型不同于第二晶体管的导通类型。

5 13. 根据权利要求11或12所述的像素电路，其特征在于

还包括第五晶体管，串联在第一晶体管和电源线之间，该电源线通过第一晶体管向电流驱动元件提供驱动电流，且具有第五栅极端子。

14. 根据权利要求13所述的像素电路，其特征在于第四晶体管的导通类型与第五晶体管的导通类型相同。

10 15. 根据权利要求9或10所述的像素电路，其特征在于第一晶体管的导通类型是p沟道型。

16. 根据权利要求11所述的像素电路，其特征在于第四栅极端子、第二栅极端子和第三栅极端子与一条信号线相连。

15 17. 根据权利要求13所述的像素电路，其特征在于第五栅极端子、第二栅极端子和第三栅极端子与一条信号线相连。

18. 根据权利要求13所述的像素电路，其特征在于还包括在第四晶体管和电流驱动元件之间串联的第六晶体管。

20 19. 根据权利要求9到18任一个所述的像素电路，其特征在于第一栅极通过电容器与电源线相连。

20. 根据权利要求19所述的像素电路，其特征在于还包括连接在第一栅极和第一电容器之间的第七晶体管。

25 21. 根据权利要求20所述的像素电路，其特征在于还包括直接连接在电源线和第一栅极之间的第八晶体管。

22. 根据权利要求20所述的像素电路，其特征在于还包括连接在电容器和第二端子之间的第九晶体管。

23. 一种包括根据前述权利要求任一个所述的多个像素电路的显示设备。

30 24. 根据权利要求23所述的显示设备，其特征在于所述显示设备

至少由矩阵中的第一信号线、第二信号线、第三信号线和数据信号线、用于向第一像素电路提供第一控制信号的第一控制信号线、以及用于向第一像素电路提供第二控制信号的第二控制信号线形成，其中针对第二像素电路的第一控制信号是由第二控制信号线提供的、针对第一像素电路的第二控制信号，并且第三控制线提供针对第二像素电路的第二控制信号。

25. 一种用于驱动像素电路的方法，包括：

施加第一控制信号以使连接在电源线和参考线之间且与第一电容器串联的第一晶体管导通；

10 施加第二控制信号以使第二晶体管导通，以便对驱动晶体管进行二极管连接，所述第二晶体管是n沟道晶体管且驱动晶体管与位于电源线和另一线之间的发光器件串联，驱动晶体管的栅极端子与位于第一晶体管和第一电容器之间的第一节点相连，并且所述驱动晶体管的第一端子设置用于接收数据信号；

15 施加第一控制信号以使第一晶体管截止；

将数据信号施加到驱动晶体管的第一端子；

施加第二控制信号以使第二晶体管截止。

26. 根据权利要求25所述的方法，其特征在于包括：

将第二控制信号施加到在电源线和驱动晶体管之间串联的第三晶体管和在发光器件和驱动晶体管之间串联的第四晶体管，以使第三和第四晶体管截止而使第二晶体管导通，以及使第三和第四晶体管导通而使第二晶体管截止，其中第二晶体管的一个端子与在驱动晶体管和第三晶体管之间的第二节点处的驱动晶体管的一个端子相连。

27. 根据权利要求26所述的方法，其特征在于所述第三和第四晶体管是p沟道型晶体管。

28. 根据权利要求26或27所述的方法，其特征在于包括：

将所述第二控制信号施加到在数据信号线和位于驱动晶体管和第四晶体管之间的第三节点之间连接的第五晶体管，以使第五晶体管导通同时使第二晶体管导通，以及使第五晶体管截止同时使第二晶体管截止。

29. 根据权利要求26到28任一个所述的方法，其特征在于包括：

将第一控制信号施加到在第四晶体管和发光器件之间串联的第六晶体管，以使第六晶体管截止而使第一晶体管导通，所述第六晶体管具有与第一晶体管相反的沟道类型。

5 30. 根据权利要求25到29任一个所述的方法，其特征在于包括：

将第一控制信号施加到在驱动晶体管的栅极端子和第一节点之间串联的第七晶体管、以及连接在电源线和位于第七晶体管的一个端子和驱动晶体管的栅极端子之间的第四节点之间的第八晶体管，其中第八晶体管具有与第一晶体管相同的沟道类型且第七晶体管具有与第一晶体管相反的沟道类型，以使第七晶体管截止并使第八晶体管导通同时使第一晶体管导通。

31. 根据权利要求25到30任一个所述的方法，其特征在于包括：

将第一控制信号施加到连接在第一节点和与驱动晶体管的栅极端子相连的第二晶体管的端子之间的第九晶体管，并且将第二控制信号施加到连接在第一节点和与驱动晶体管的第二端子相连的第二晶体管的另一端子之间的第十晶体管，其中第九晶体管是p沟道型晶体管而第十晶体管是n沟道型晶体管，以便当使第二晶体管导通时使第九晶体管截止，以及当使第二晶体管导通时使第十晶体管导通。

32. 根据权利要求25到27任一个所述的方法，其特征在于所述参考线是数据信号线，或者根据权利要求28或29所述的方法，其特征在于所述第一晶体管串联在第五晶体管和电容器之间，由此，所述数据信号线是参考线，所述方法包括：

在施加第一控制信号以使第一晶体管导通之后，以及在施加第一控制信号以使第一晶体管截止之前，将预充电信号施加到数据信号线上，所述预充电信号具有低于所述数据信号的值。

33. 一种用于驱动像素电路的方法，所述像素电路具有第一栅极端子、第一端子和第二端子的第一晶体管、具有第二栅极端子的第二晶体管、具有第三栅极端子并控制第一栅极端子和第二端子之间的电连接的第三晶体管、用于控制电流驱动元件和第一晶体管之间的电连接的第四端子、以及用于控制第二端子和预定电压之间的电连接的第

五端子，所述方法包括：

产生像素电路的第一状态，其中通过使第五晶体管导通将第二端子设置为预定电压；

5 产生像素电路的第二状态，其中至少在第一端子通过第二晶体管接收数据信号的第一周期的一部分时间内，所述第一端子通过第三晶体管与第二端子电连接；以及

产生像素电路的第三状态，其中将其电流电平对应于通过第二状态所设置的导通状态的驱动电流通过第一晶体管和第四晶体管提供给电流驱动元件；

10 第二端子在第二状态中与预定电压断开电连接；

第一端子在第二状态中与电流驱动元件断开电连接；以及

将一个控制信号公共地提供给第二栅极端子、第三端子、第四端子和第五端子。

## 像素电路

5

### 技术领域

本发明大体上涉及一种在使用电流驱动有机或其他发光器件作为光源的显示系统中采用的一种类型的像素电路。

### 10 背景技术

显示系统通常包括具有作为光源的有机发光器件（OLED）的像素电路阵列和用于根据接收到的数据信号来驱动OLED的驱动电路。所述OLED由夹在阳极层和阴极层之间的发光聚合体（LEP）层构成。从电学上说，OLED作为二极管操作，而从光学上，当正向偏置时，OLED发光，15 发射光的亮度随着正向偏置电流的增加而增加。通过利用低温多晶硅薄膜晶体管（TFT）技术将各个像素电路的驱动电路集成在阵列中，能够控制每一个相应OLED的亮度，以便在显示器上提供静态或运动图像。

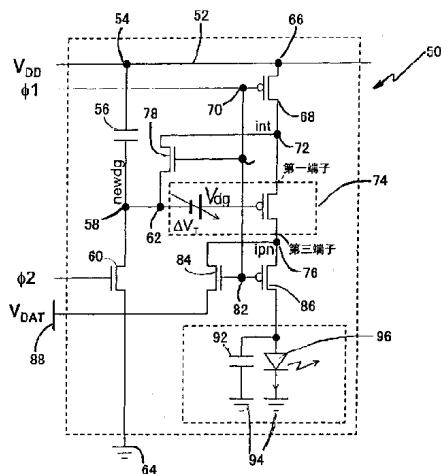

由于OLED是电流驱动器件，如果像素电路接收到电压信号，则驱动晶体管等需要响应于接收到的电压信号向OLED提供适当的电流电平。图1示出了用于驱动有源矩阵OLED显示的公知电压驱动像素电路的示例。参考图1，像素电路10由每一个像素包括第一p沟道TFT T<sub>1</sub>和第二p沟道TFT T<sub>2</sub>组成。第一TFT T<sub>1</sub>是用于寻址像素电路10的开关且包括与第一电源线12相连的端子，用于接收电压数据信号VData。第一TFT T<sub>1</sub>还包括与第二电源线14相连的栅极端子，用于接收电源电压VSEL；20 以及与第二TFT T<sub>2</sub>的栅极端子相连的端子。第二TFT T<sub>2</sub>包括与第三电源线16相连的端子，用于接收电源电压VDD；以及与OLED 18的阳极端子相连的端子；OLED 18的阴极端子与地相连。第二TFT T<sub>2</sub>是模拟驱动TFT，用于将电压数据信号VData转换为电流信号，所述电流信号依次将OLED 18驱动于指定的亮度上。

30 如图1所示的采用电压驱动像素电路的阵列的显示系统在其显示

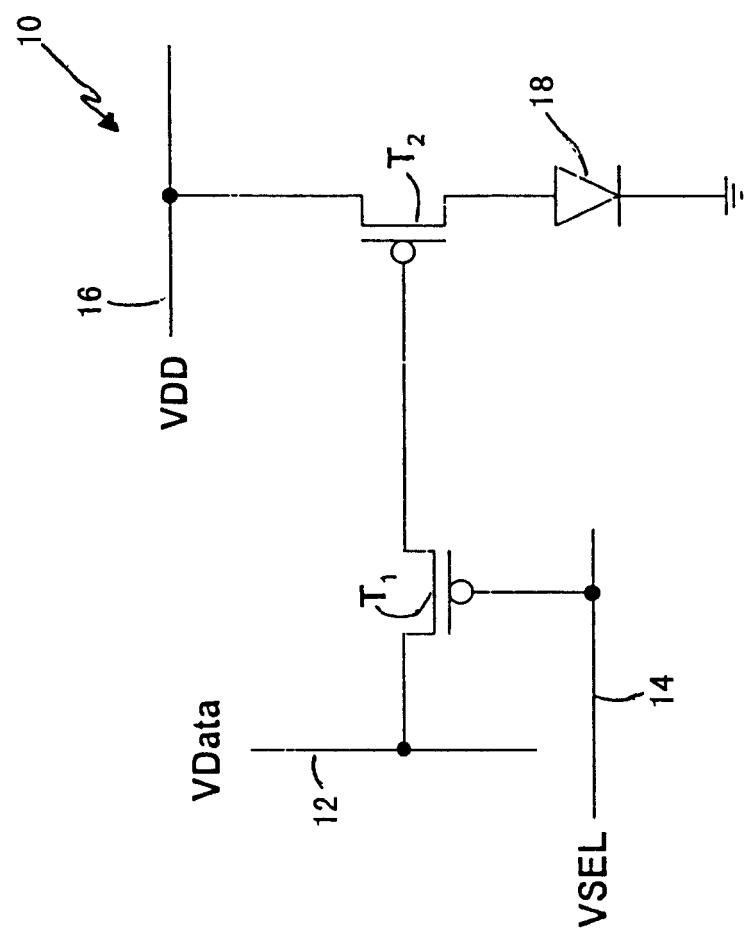

图像中可能会经受不均匀的问题,即使向阵列中的各个驱动TFT提供相同的电压数据信号和电源电压。该不均匀是由于形成显示器的像素电路阵列内的各个驱动TFT的阈值电压的空间变化所引起的。因此,对于驱动TFT之间的阈值电压的不同,每一个OLED被驱动在不同的亮度上。由S. M. Choi等人在“*A self-compensated voltage programming pixel structure for active-matrix organic light emitting diodes*”,国际显示工作站2003,第535到538页中已经公开了解决该不均匀问题的一个方案。图2中示出了由Choi等人所公开的一种像素电路实施例。

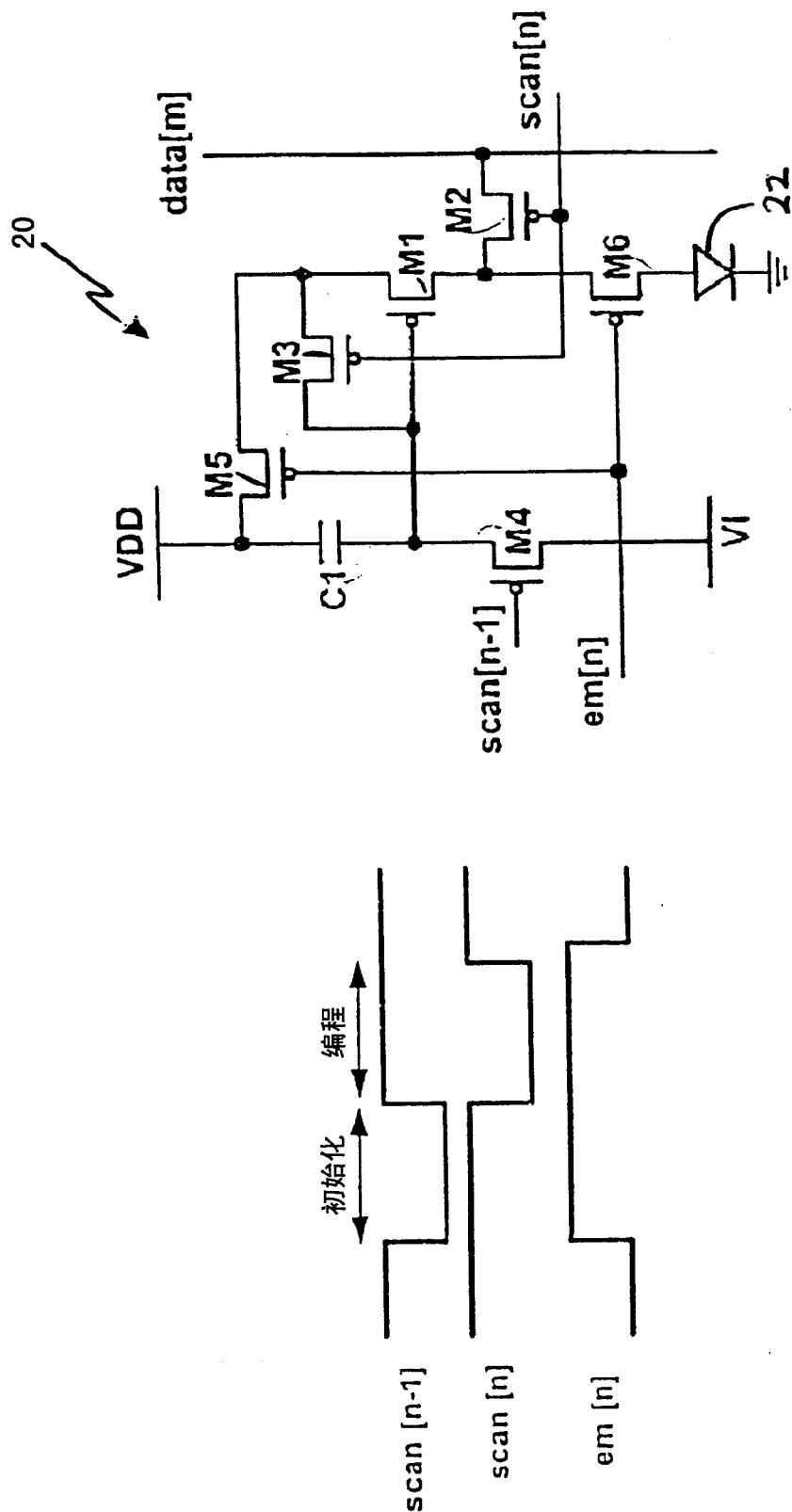

参考图2,用于补偿各个驱动TFT的电压阈值变化的像素电路20包括六个TFT M1、M2、M3、M4、M5和M6;一个电容器C1和两个水平控制线scan[n-1]和scan[n]。M2、M3、M4、M5和M6是开关TFT,而M1是模拟驱动TFT,以便在一帧的时间周期内,提供电流依次将OLED 22驱动在指定的亮度上。

在操作时,第四TFT M4提供电流路径以便按预定值来建立驱动TFT M1的栅极端子电压。电容器C1是存储电容器并存储驱动器TFT M1的栅极端子电压。由于像素电路20需要两条行线时间来完成数据编程操作,因此将scan[n] (当前行扫描) 和scan[n-1] (前一行扫描) 信号应用于对像素电路20的编程。

在前一行扫描期间,当scan[n-1]信号为逻辑低电平时,在被称为初始化的步骤中,将驱动器TFT M1的栅极端子电压充电为电压VI。紧接当前行扫描和在当前行扫描期间,当scan[n]信号为逻辑低电平时,使TFT M2和TFT M3导通,从而通过二极管连接的驱动TFT M1,将电压数据信号data[m]编程到驱动器TFT M1的栅极节点。此时,将驱动TFT M1的栅极节点处的编程电压自动减小为小于驱动TFT M1的阈值电压 $V_{TH}$ 的数值数据信号电压data[m]。在初始化和编程期间,使TFT M5和M6截止。

在前一和当前行扫描之后,由em[n]信号使TFT M5和TFT M6导通以建立从VDD到地的电流路径,从而使电流能够流经驱动TFT M1并驱动OLED 22。因此,驱动TFT M1独立于电压阈值 $V_{TH}$ 来调节电流。

尽管上述像素电路20提供了一种补偿各个驱动TFT的电压阈值变化的手段，但是需要增加像素电路进行编程的速度，当要提供高带宽数据或当要应用于大型显示器中时，为了使显示系统能够胜任地执行，编程速度的增加是必须的。此外，需要以更低能量消耗为特征的更小5型的显示系统，以便延长电源的寿命并扩展系统的功能性。

## 发明内容

根据本发明的第一方面，提出了一种像素电路，包括：

在电源线和参考线之间串联的第一晶体管和电容器，第一晶体管10的栅极端子设置用于接收第一控制信号；

在电源线和另一线之间串联的驱动晶体管和发光器件，所述驱动晶体管具有与位于第一晶体管和电容器之间的第一节点相连的栅极端子、以及用于接收数据信号的第一端子；以及

第二晶体管，被设置以二极管连接驱动晶体管以响应在第二晶体15管的栅极端子处接收到的第二控制信号，由此，使数据信号能够通过被二极管连接的驱动晶体管并保持在第一节点处，所述第二晶体管是n沟道型晶体管。

优选地，在电源线和驱动晶体管之间串联第三晶体管和在发光器件和驱动晶体管之间串联第四晶体管，其中第二晶体管的一个端子与20在驱动晶体管和第三晶体管之间的第二节点处的驱动晶体管的第二端子相连。

优选地，所述第三和第四晶体管是p沟道型晶体管且它们的栅极端子设置用于接收第二控制信号。更优选地，在数据信号线和位于驱动晶体管与第四晶体管之间的第三节点之间连接第五晶体管。第五晶体管是n沟道型晶体管且包括用于接收第二控制信号的栅极端子。25

优选地，在第四晶体管和发光器件之间串联第六晶体管，所述第六晶体管具有与第一晶体管相反的沟道类型且具有用于接收第一控制信号的栅极端子。

优选地，在驱动晶体管的栅极端子和第一节点之间串联第七晶体30管、以及在电源线和位于第七晶体管的一个端子和驱动晶体管的栅极

端子之间的第四节点之间连接第八晶体管，其中第八晶体管具有与第一晶体管相同的沟道类型且第七晶体管具有与第一晶体管相反的沟道类型，第七和第八晶体管的栅极端子设置用于接收第一控制信号。

所述像素电路还包括连接在第一节点和与驱动晶体管的栅极端子相连的第二晶体管的端子之间的第九晶体管、以及连接在第一节点和与驱动晶体管的第二端子相连的第二晶体管的另一端子之间的第十晶体管，其中第九晶体管是p沟道型晶体管而第十晶体管是n沟道型晶体管，且第九和第十晶体管的栅极端子设置用于分别接收第一和第二控制信号。

根据本发明的另一方面，提出了一种用于驱动电流驱动元件的像素电路，包括：

第一晶体管，其导通状态对应于提供给电流驱动元件的驱动电流的电流电平，第一晶体管具有第一栅极端子、第一端子和第二端子；

第二晶体管，具有第二栅极端子；以及

第三晶体管，设置用于控制第一栅极端子与第一端子和第二端子之一之间的电连接，所述第三晶体管具有第三栅极端子；

第一端子设置用于通过第二晶体管接收数据信号，所述数据信号确定第一晶体管的导通状态；以及

第一晶体管的导通类型不同于第二晶体管的导通类型。

根据本发明的另一方面，提出了一种用于驱动电流驱动元件的像素电路，包括：

第一晶体管，其导通状态对应于提供给电流驱动元件的驱动电流的电流电平，第一晶体管具有第一栅极端子、第一端子和第二端子；

第二晶体管，具有第二栅极端子；以及

第三晶体管，设置用于控制第一栅极端子与第一端子和第二端子之一之间的电连接，所述第三晶体管具有第三栅极端子；

第一端子设置用于通过第二晶体管接收数据信号，所述数据信号确定第一晶体管的导通状态；以及

第一晶体管的导通类型不同于第三晶体管的导通类型。

优选地，在电流驱动元件和第一晶体管之间串联具有第四栅极端

子的第四晶体管。更优选地，第四晶体管的导通类型不同于第二晶体管的导通类型。

优选地，具有第五栅极端子的第五晶体管串联在第一晶体管和从中通过第一晶体管向电流驱动元件提供驱动电流的电源线之间。

5 第四晶体管的导通类型与第五晶体管的导通类型相同。第一晶体管的导通类型可以是p沟道型。

优选地，第四栅极端子、第二栅极端子和第三栅极端子与一条信号线相连。优选地，第五栅极端子、第二栅极端子和第三栅极端子与一条信号线相连。优选地，在第四晶体管和电流驱动元件之间串联第10 六晶体管。

优选地，第一栅极通过电容器与电源线相连。更优选地，在第一栅极和第一电容器之间连接第七晶体管。

优选地，第八晶体管直接连接在电源线和第一栅极之间。

优选地，第九晶体管连接在电容器和第二端子之间。

15 根据本发明的另一方面，提出了一种包括如上所述的多个像素电路的显示设备。优选地，所述显示设备至少由矩阵中的第一信号线、第二信号线、第三信号线和数据信号线、用于向第一像素电路提供第一控制信号的第一控制信号线、以及用于向第一像素电路提供第二控制信号的第二控制信号线组成，其中针对第二像素电路的第一控制信号是由第二控制信号线提供的、针对第一像素电路的第二控制信号，并且第三控制线提供针对第二像素电路的第二控制信号。

根据本发明的另一方面，提出了一种用于驱动像素电路的方法，包括：

25 施加第一控制信号以使连接在电源线和参考线之间且与第一电容器串联的第一晶体管导通；

施加第二控制信号以使第二晶体管导通，以便对驱动晶体管进行二极管连接，所述第二晶体管是n沟道晶体管且驱动晶体管与位于电源线和另一线之间的发光器件串联，驱动晶体管的栅极端子与位于第一晶体管和第一电容器之间的第一节点相连，并且所述驱动晶体管的第一端子设置用于接收数据信号；

施加第一控制信号以使第一晶体管截止；

将数据信号施加到驱动晶体管的第一端子；

施加第二控制信号以使第二晶体管截止。

优选地，所述方法还包括：将第二控制信号施加到在电源线和驱动晶体管之间串联的第三晶体管和在发光器件和驱动晶体管之间串联的第四晶体管，以使第三和第四晶体管截止而使第二晶体管导通，以及使第三和第四晶体管导通而使第二晶体管截止，其中第二晶体管的一个端子与在驱动晶体管和第三晶体管之间的第二节点处的驱动晶体管的一个端子相连。

10 优选地，所述第三和第四晶体管是p沟道型晶体管。优选地，所述方法还包括：将所述第二控制信号施加到在数据信号线和位于驱动晶体管和第四晶体管之间的第三节点之间连接的第五晶体管，以使第五晶体管导通同时使第二晶体管导通，以及使第五晶体管截止同时使第二晶体管截止。

15 优选地，所述方法还包括：将第一控制信号施加到在第四晶体管和发光器件之间串联的第六晶体管，以使第六晶体管截止而使第一晶体管导通，所述第六晶体管具有与第一晶体管相反的沟道类型。

优选地，所述方法还包括：将第一控制信号施加到在驱动晶体管的栅极端子和第一节点之间串联的第七晶体管、以及连接在电源线和位于第七晶体管的一个端子和驱动晶体管的栅极端子之间的第四节点之间的第八晶体管，其中第八晶体管具有与第一晶体管相同的沟道类型且第七晶体管具有与第一晶体管相反的沟道类型，以使第七晶体管截止并使第八晶体管导通同时使第一晶体管导通。

25 优选地，所述方法还包括：将第一控制信号施加到连接在第一节点和与驱动晶体管的栅极端子相连的第二晶体管的端子之间的第九晶体管，并且将第二控制信号施加到连接在第一节点和与驱动晶体管的第二端子相连的第二晶体管的另一端子之间的第十晶体管，其中第九晶体管是p沟道型晶体管而第十晶体管是n沟道型晶体管，以便当使第一晶体管导通时使第九晶体管截止，以及当使第二晶体管导通时使第十晶体管导通。

所述参考线可以是数据信号线，或者在所述第一晶体管串联在第五晶体管和电容器之间时，所述数据信号线是参考线，所述方法还包括：

在施加第一控制信号以使第一晶体管导通之后，以及在施加第一

5 控制信号以使第一晶体管截止之前，将预充电信号施加到数据信号线上，所述预充电信号具有低于所述数据信号的值。

根据本发明的另一方面，提出了一种用于驱动像素电路的方法，所述像素电路包括具有第一栅极端子、第一端子和第二端子的第一晶体管；具有第二栅极端子的第二晶体管；具有第三栅极端子并控制第一

10 棚极端子和第二端子之间的电连接的第三晶体管；用于控制电流驱动元件和第一晶体管之间的电连接的第四端子、以及用于控制第二端子和预定电压之间的电连接的第五端子，所述方法包括：

产生像素电路的第一状态，其中通过使第五晶体管导通将第二端子设置在预定电压；

15 产生像素电路的第二状态，至少在第一端子通过第二晶体管接收数据信号的第一周期的一部分时间内，所述第一端子通过第三晶体管与第二端子电连接；以及

产生像素电路的第三状态，其中将其电流电平对应于通过第二状态所设置的导通状态的驱动电流通过第一晶体管和第四晶体管提供给

20 电流驱动元件；

第二端子在第二状态中与预定电压断开电连接；

第一端子在第二状态中与电流驱动元件断开电连接；以及

将一个控制信号公共地提供给第二栅极端子、第三端子、第四端子和第五端子。

25 当使用时，减少了对根据本发明的像素电路的初始化和编程所需的时间，由此提供了一种比现有技术更为有效、快速和更为通用的显示系统。由于像素电路的配置允许信号em[n]和scan[n]由单一控制信号替代，因此不再需要在现有技术中使用的第三信号em[n]。在优选实施例中，不再需要参考信号提供线，从而提供了更为紧凑的显示系统。

30 还可以减少控制线的数量，由此还提供了一种比已知的现有技术更为

紧凑和有效的显示系统。

### 附图说明

现在，仅通过示例并参考附图，将描述本发明的实施例，其中，

5 图1是用于有源矩阵OLED显示器的现有技术电压驱动像素电路的示意图；

图2是用于有源矩阵OLED显示器的现有技术自补偿电压编程像素结构的示意图；

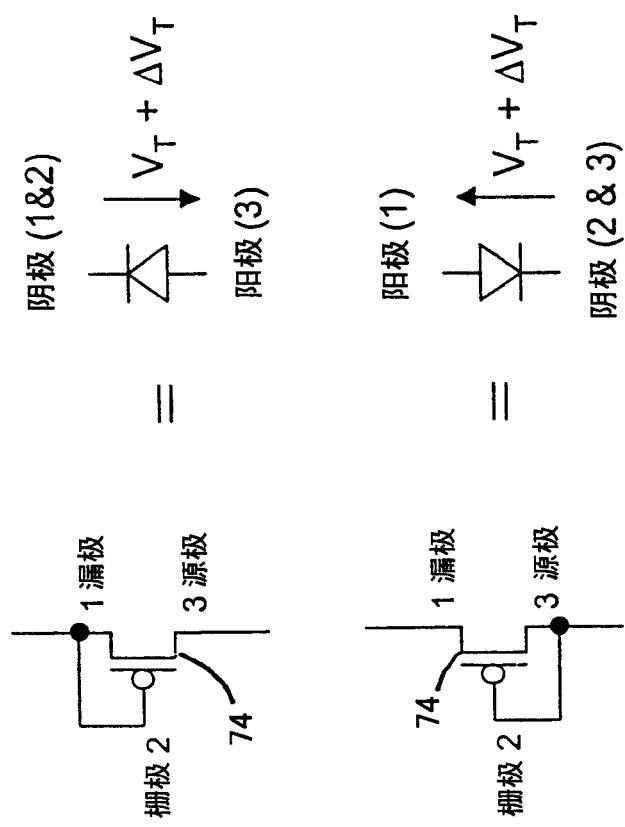

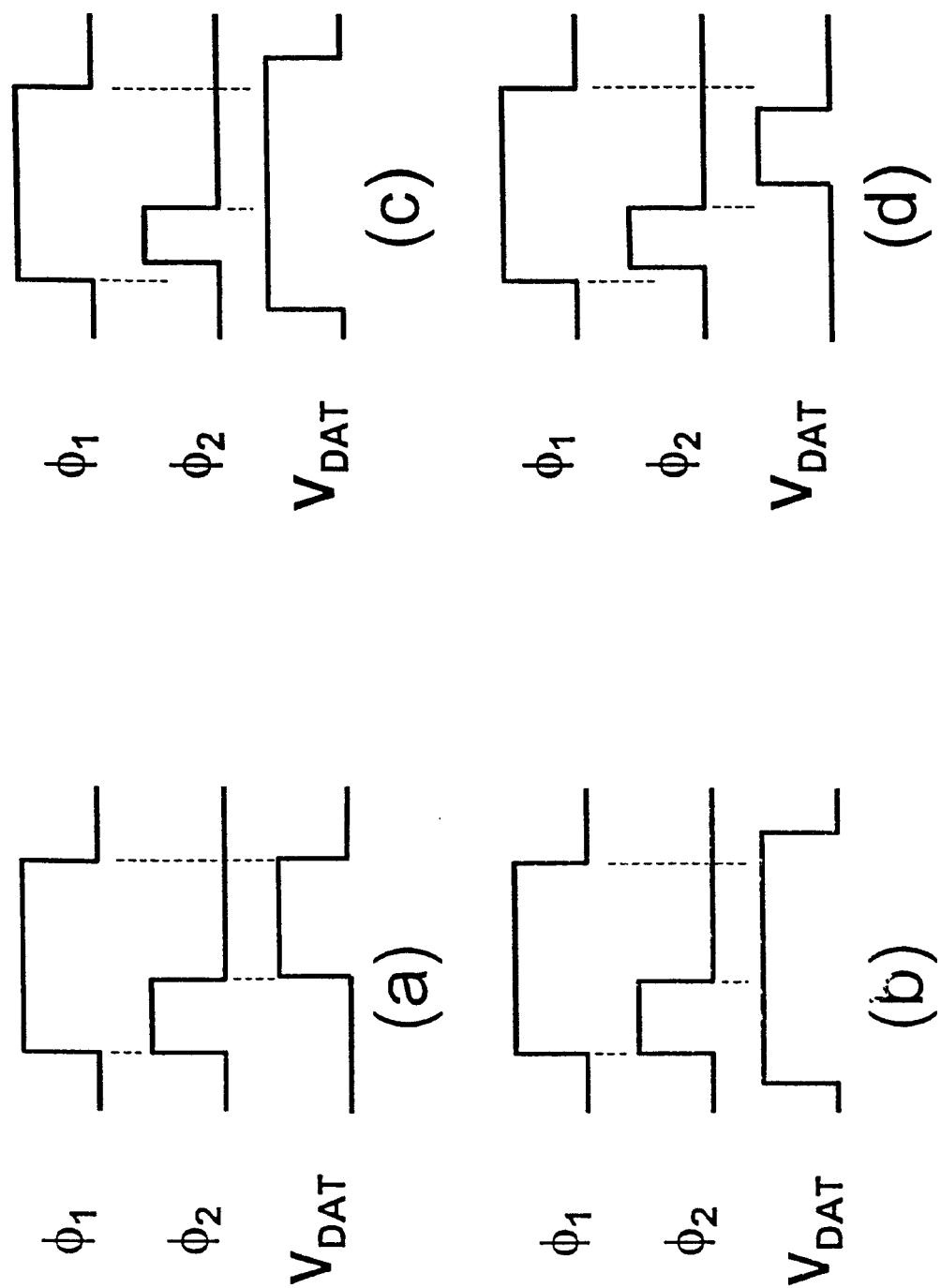

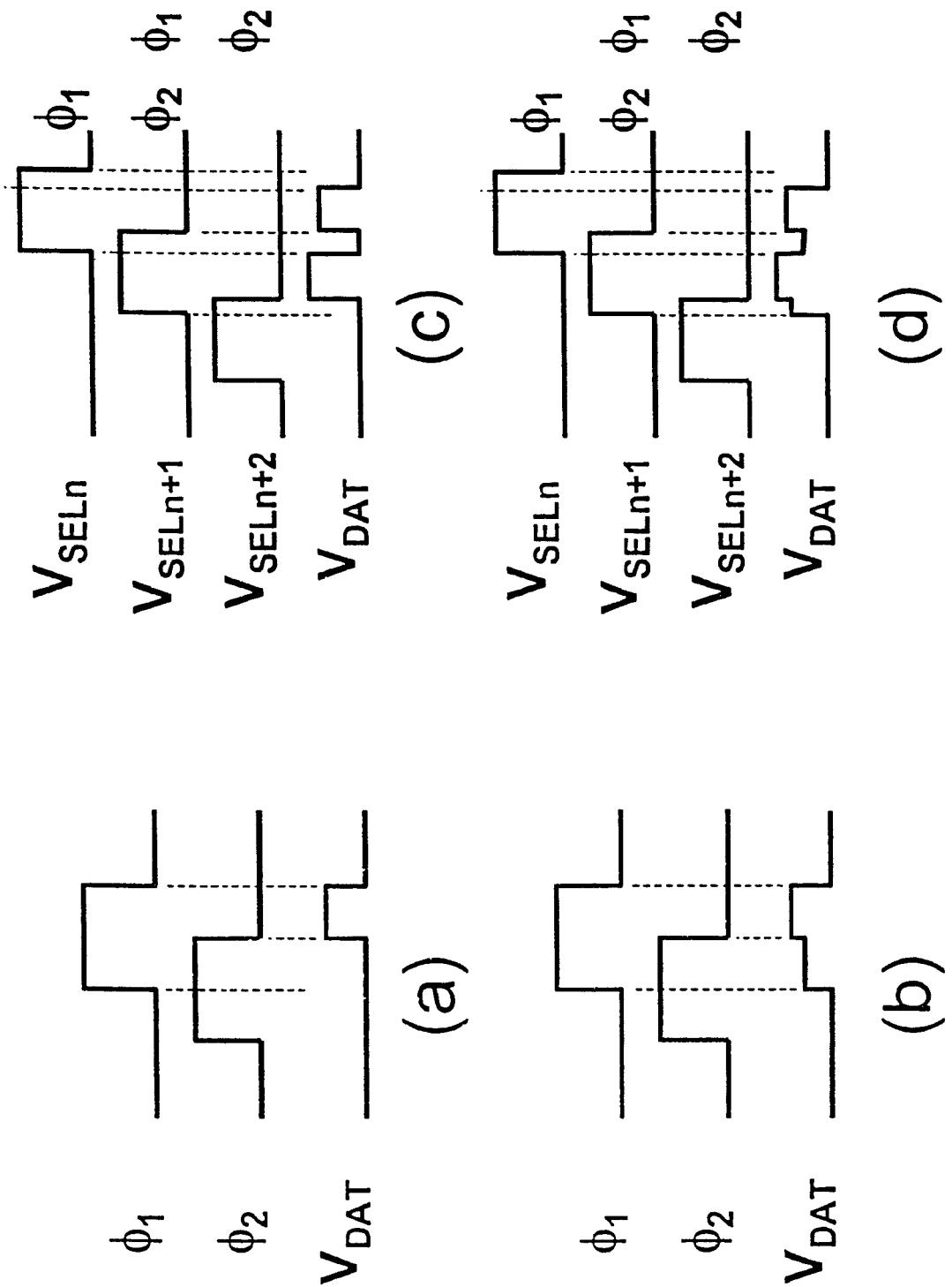

图3是示出了对晶体管进行二极管连接的两种方式的示意图；

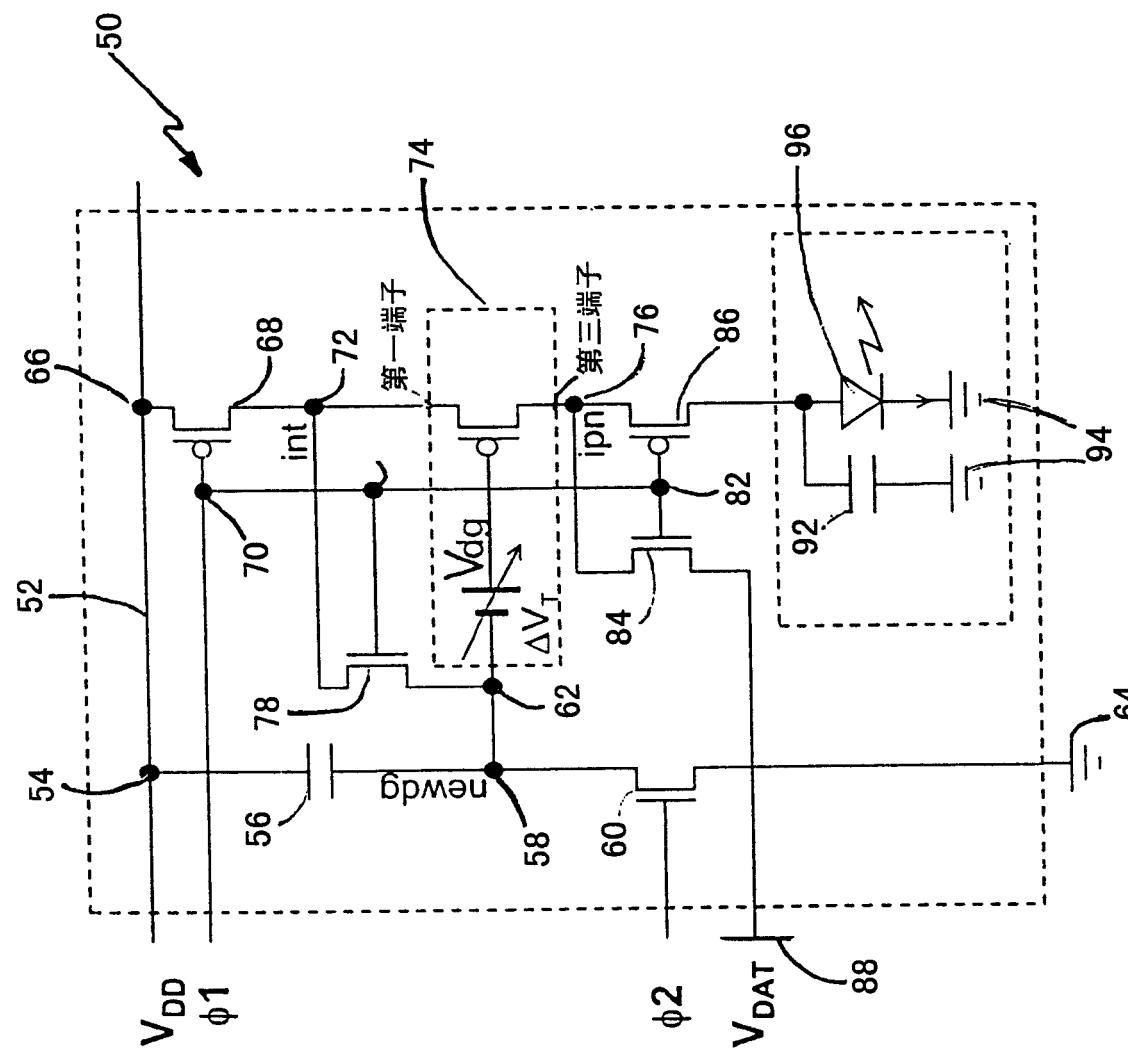

10 图4是根据本发明第一实施例的像素电路的示意图；

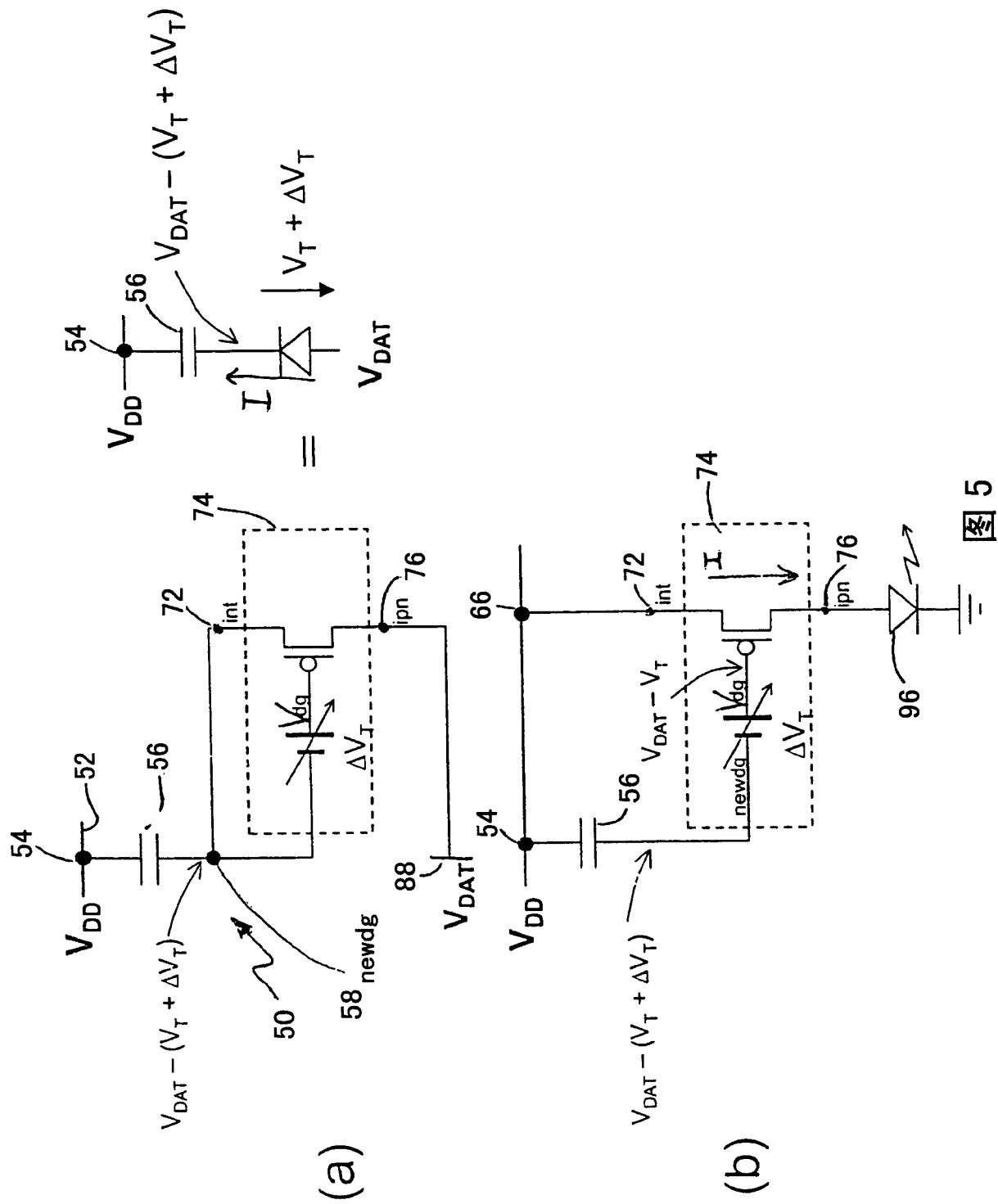

图5是在稳定状态电压处的图4所示的像素电路的部分的示意图；

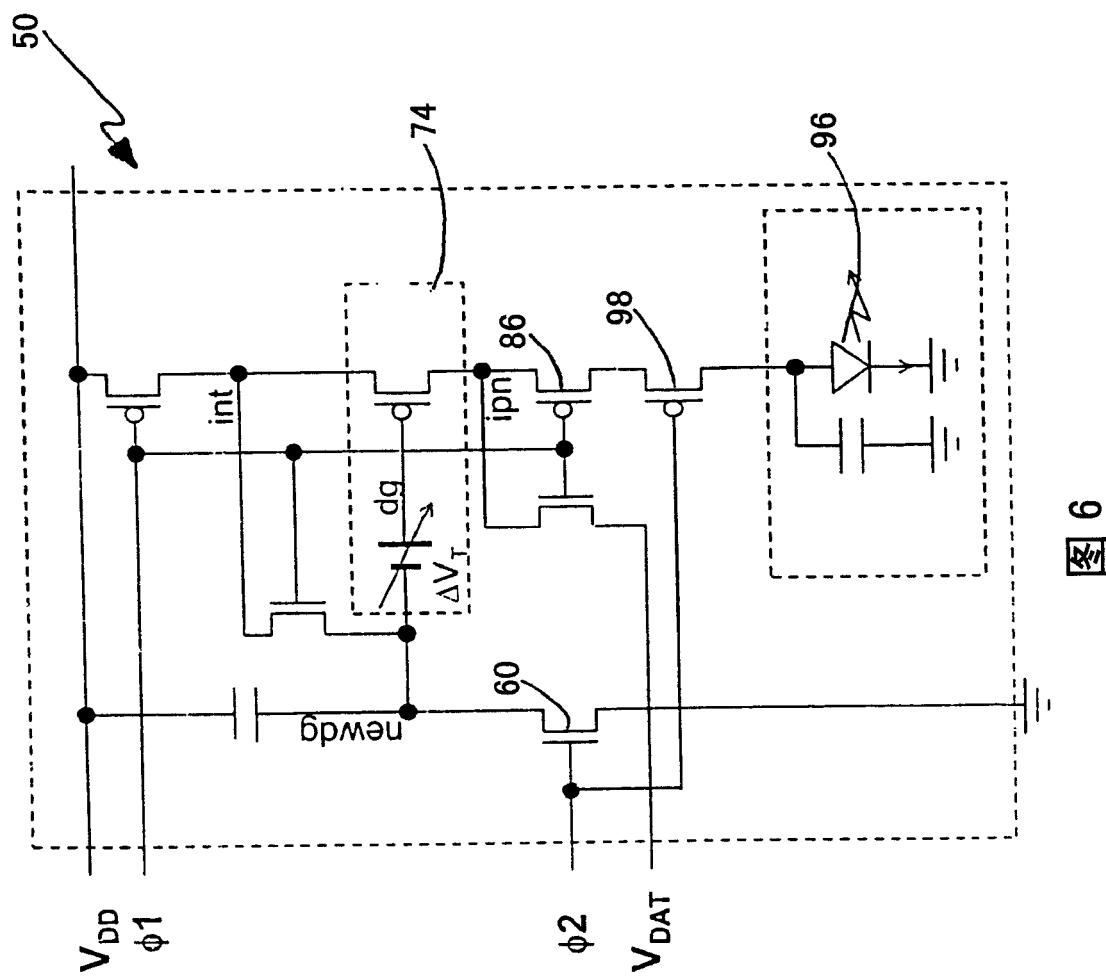

图6是根据本发明第二实施例的像素电路的示意图；

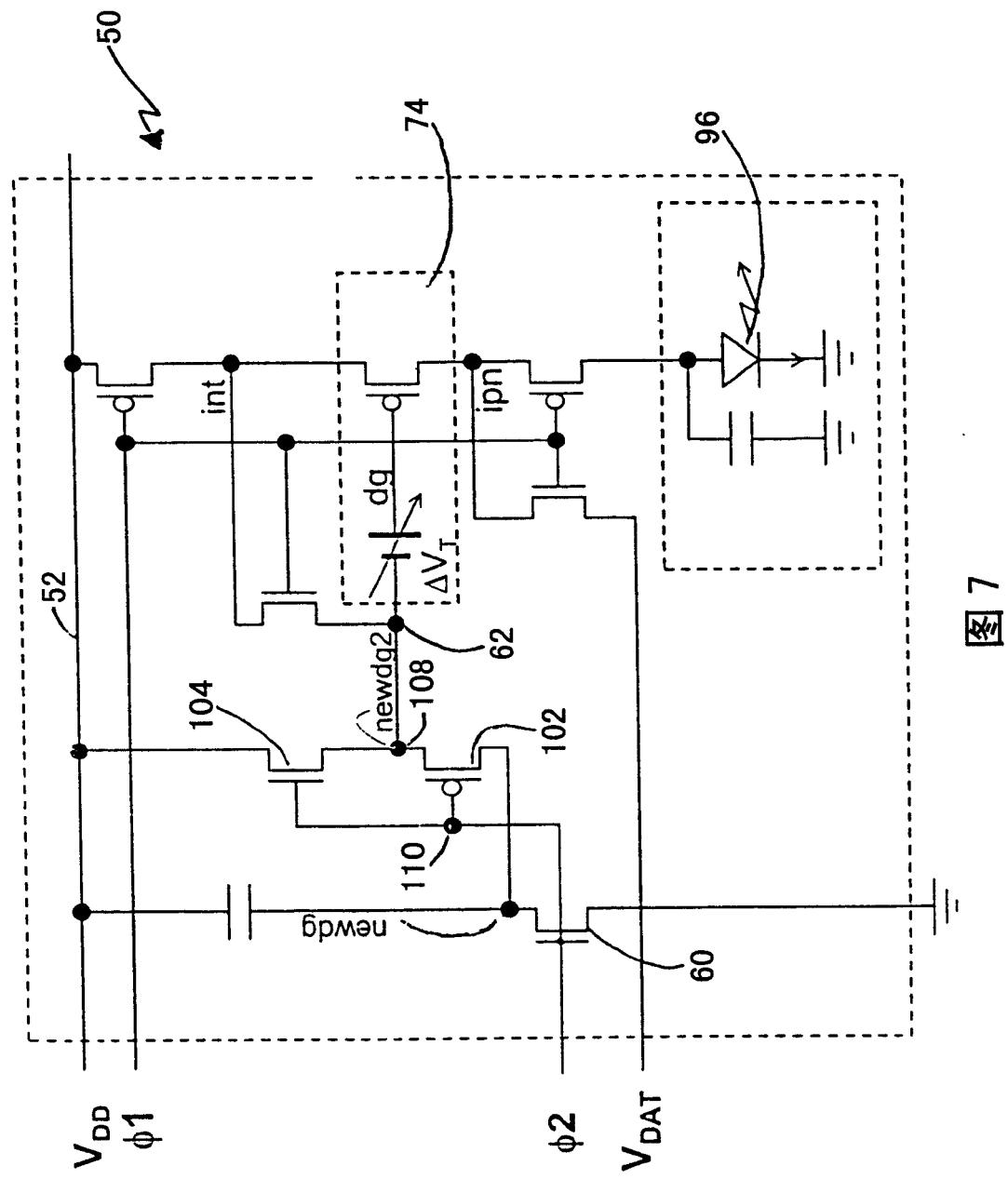

图7是根据本发明第三实施例的像素电路的示意图；

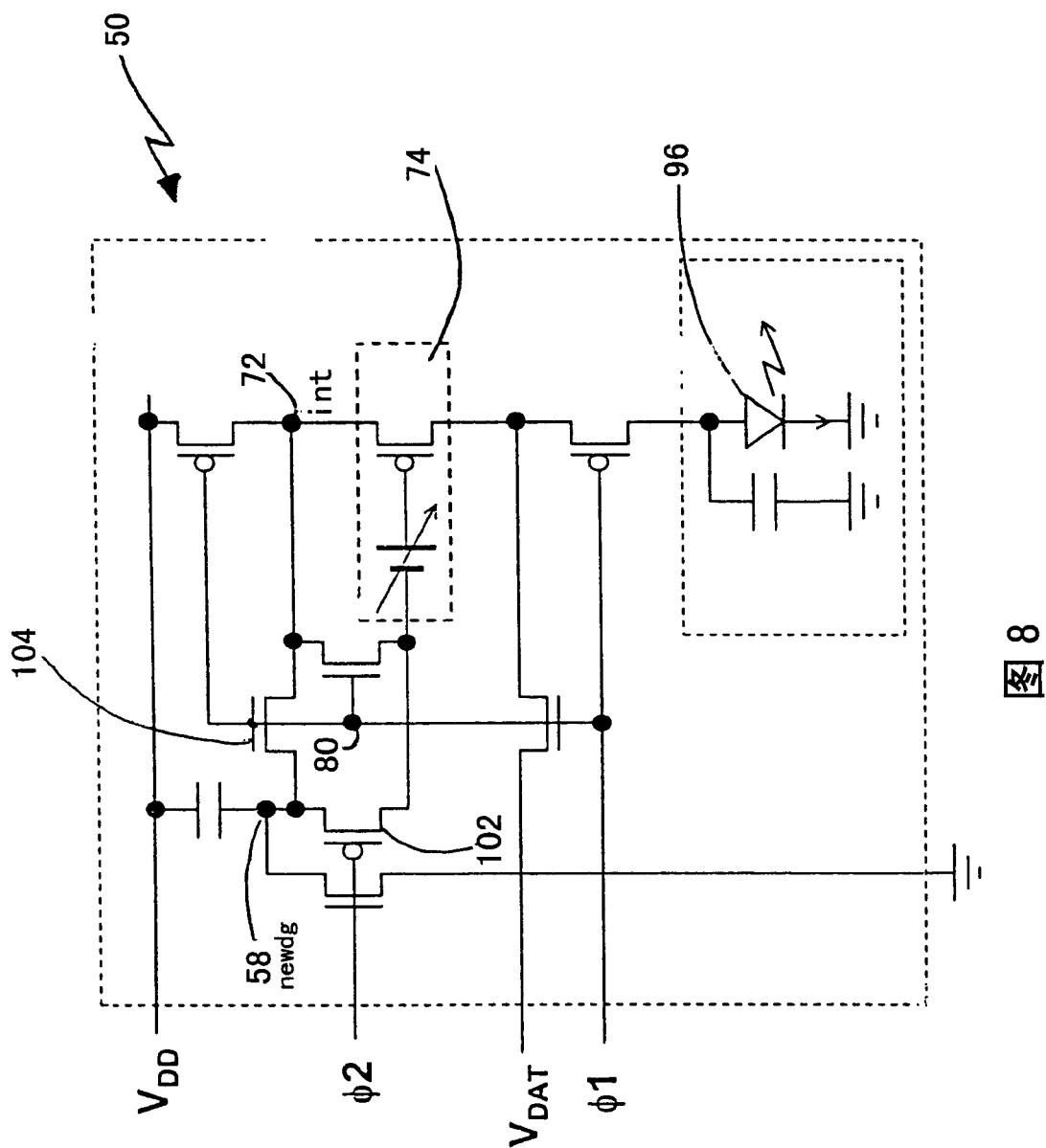

图8是根据本发明第四实施例的像素电路的示意图；

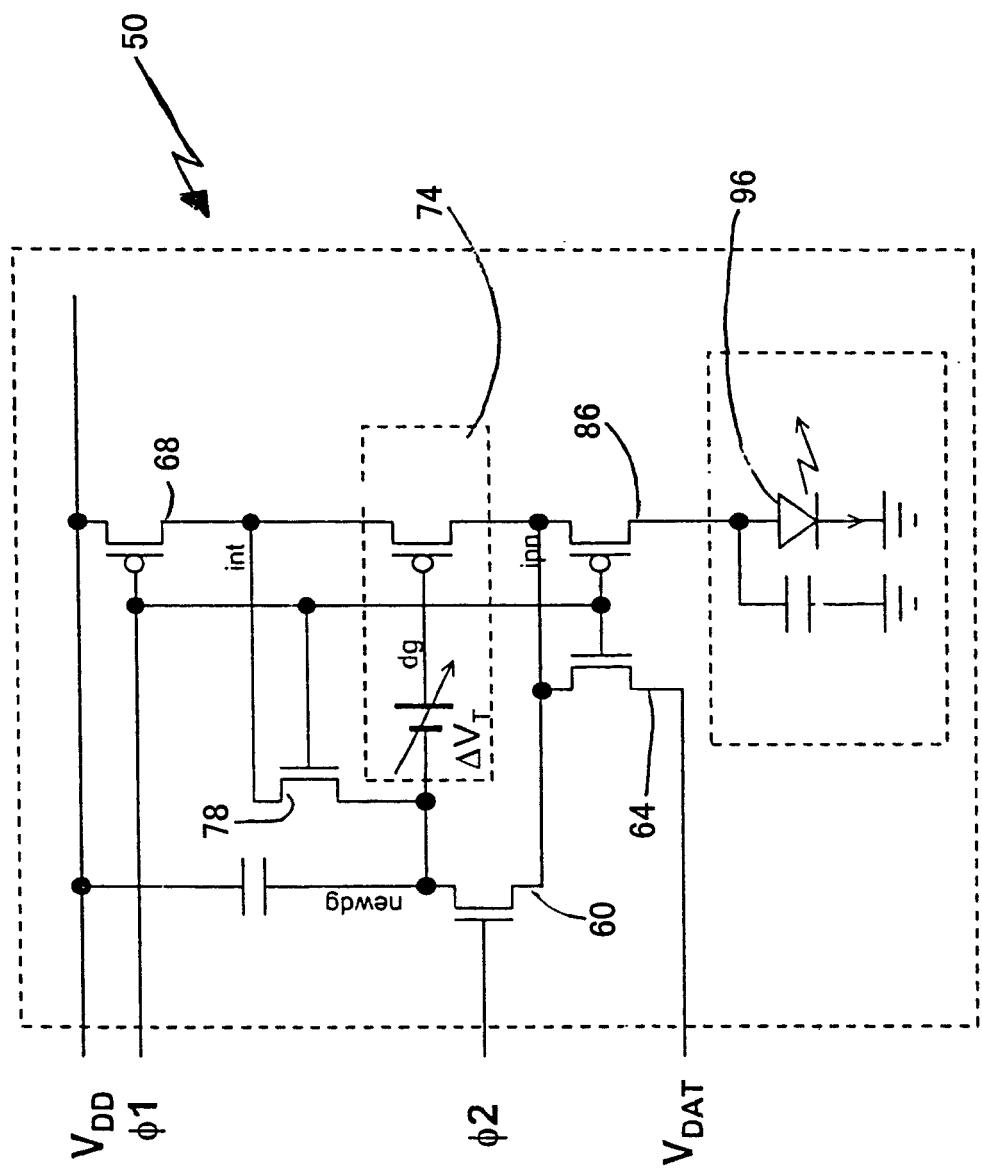

15 图9是根据本发明第五实施例的像素电路的示意图；

图10是如图4、6、7、8和9所示的像素电路的一般驱动波形的示意图；

图11是如图6、7、8和9所示的像素电路的一般驱动波形的示意图；

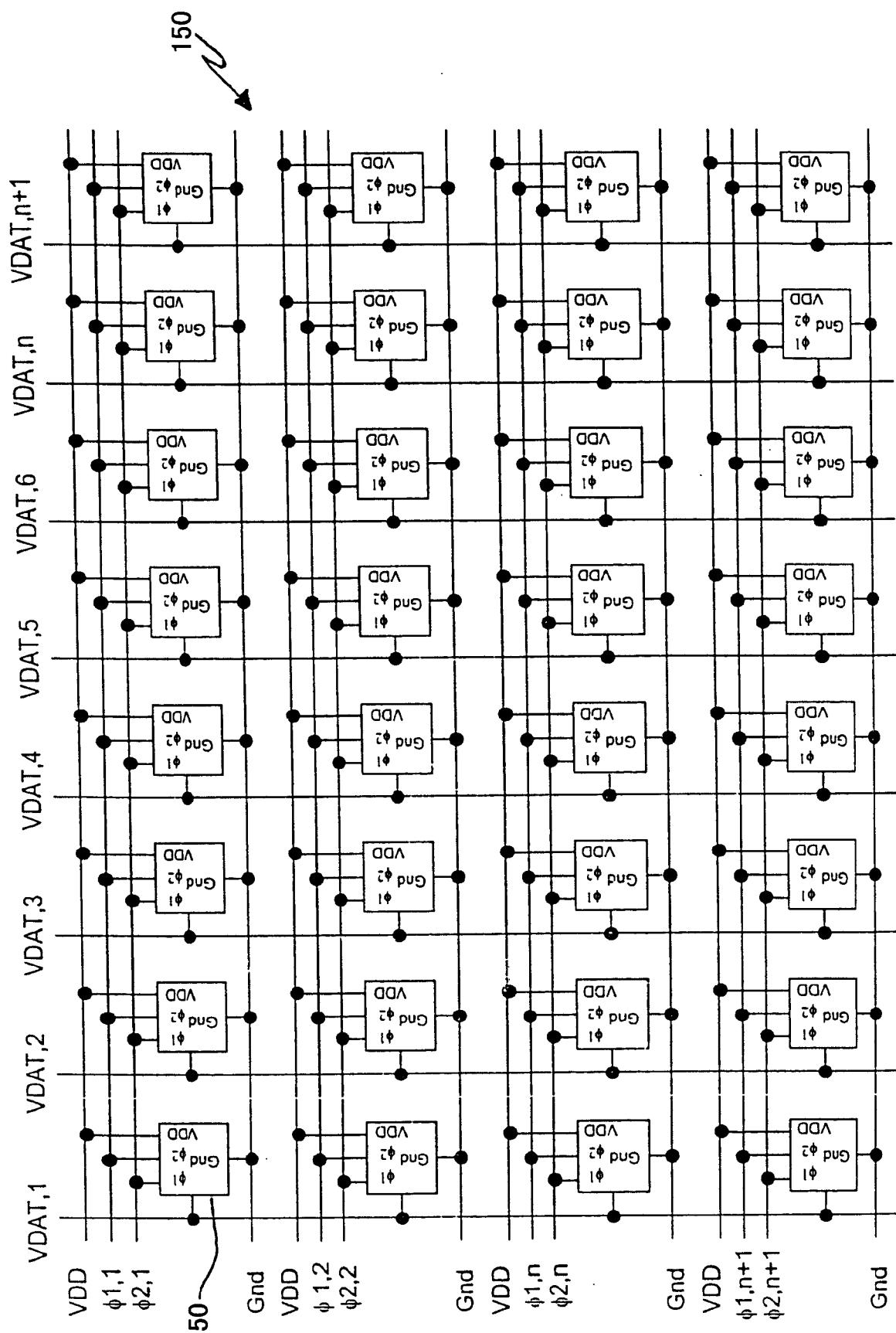

图12是如图4、6、7和8所示的像素电路的结构的示意图；

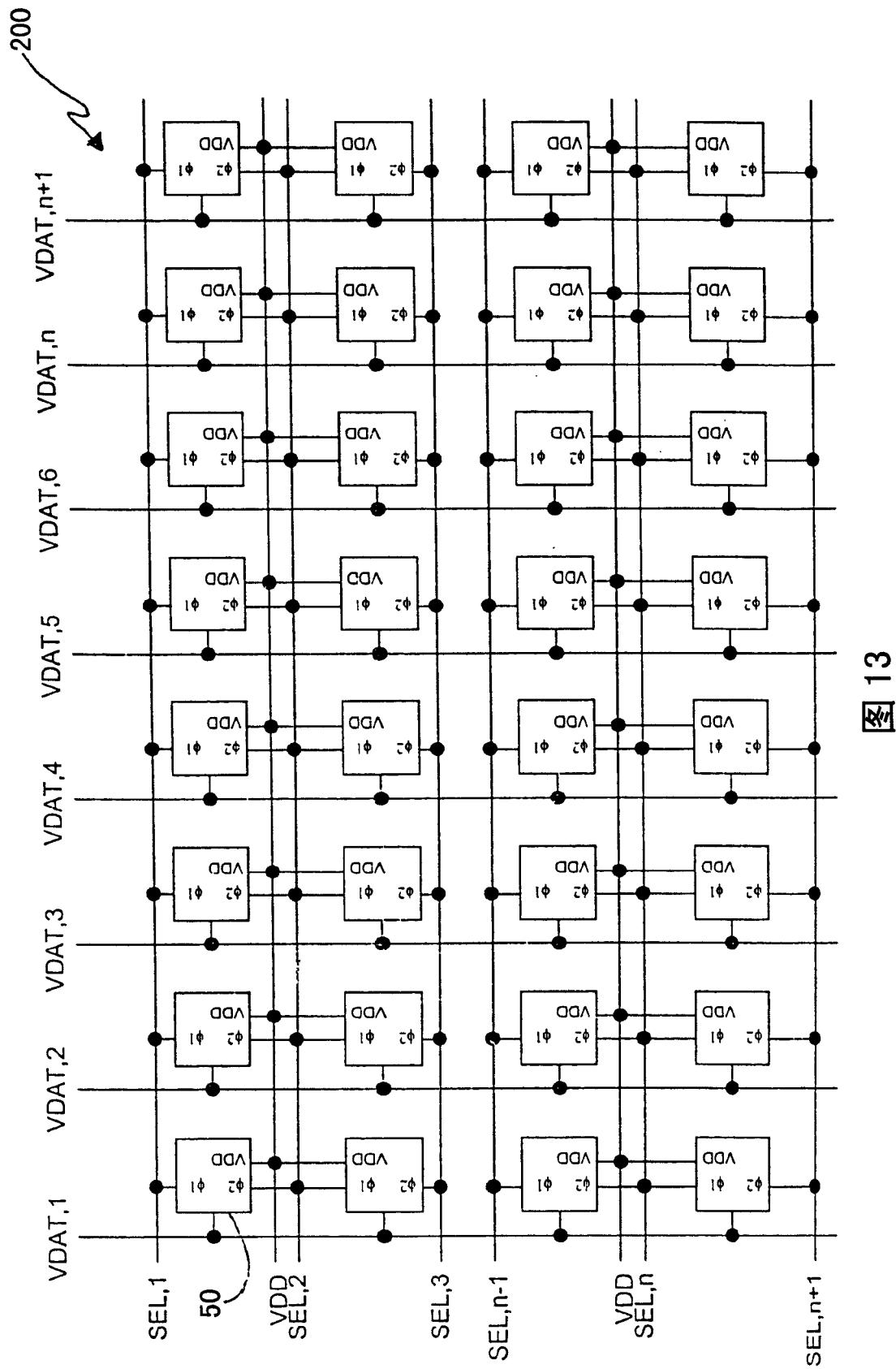

20 图13是图9所示的像素电路的结构的示意图；

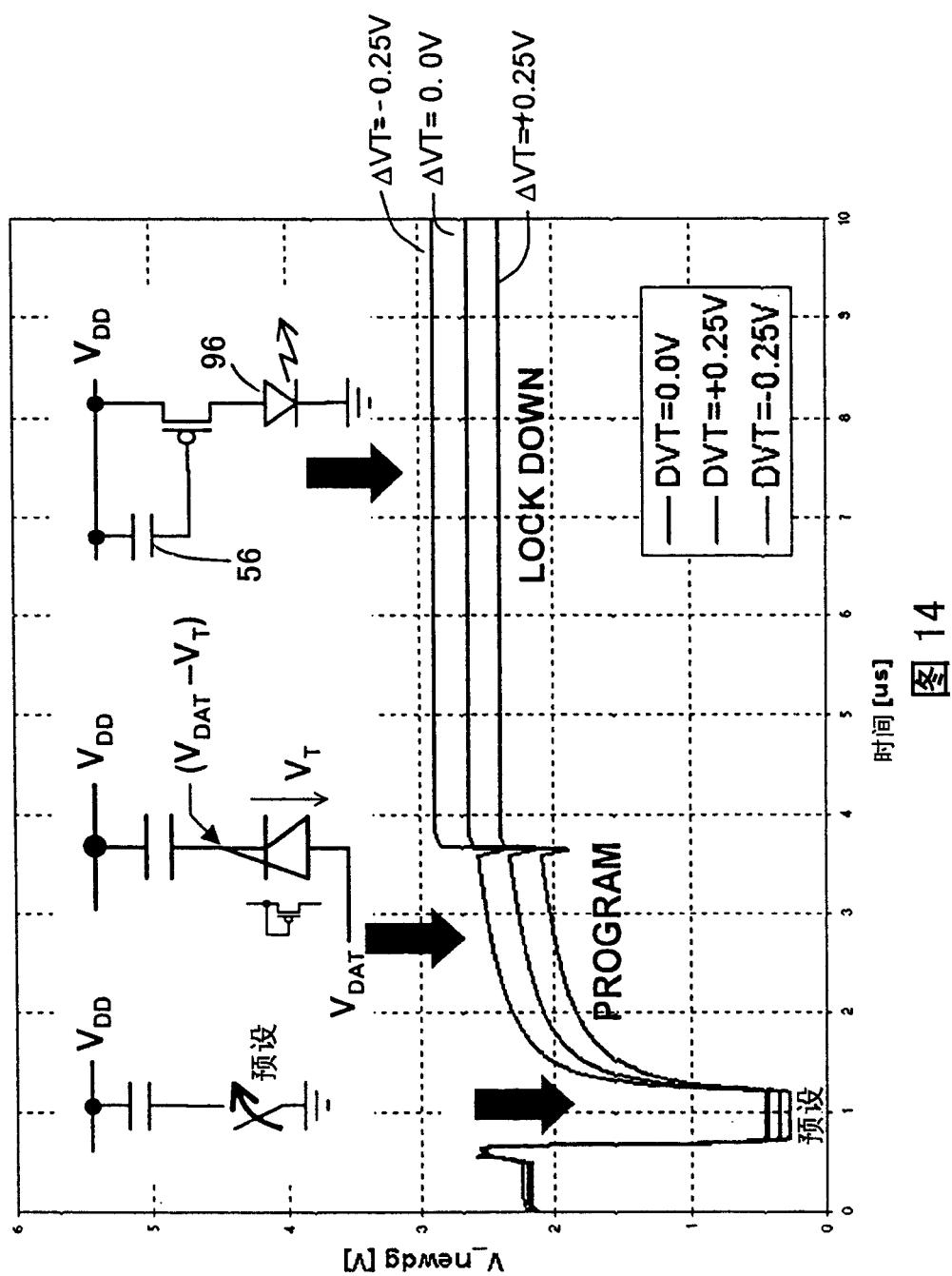

图14是在图4所示的像素电路的节点newdg处的电压模拟的示意图；

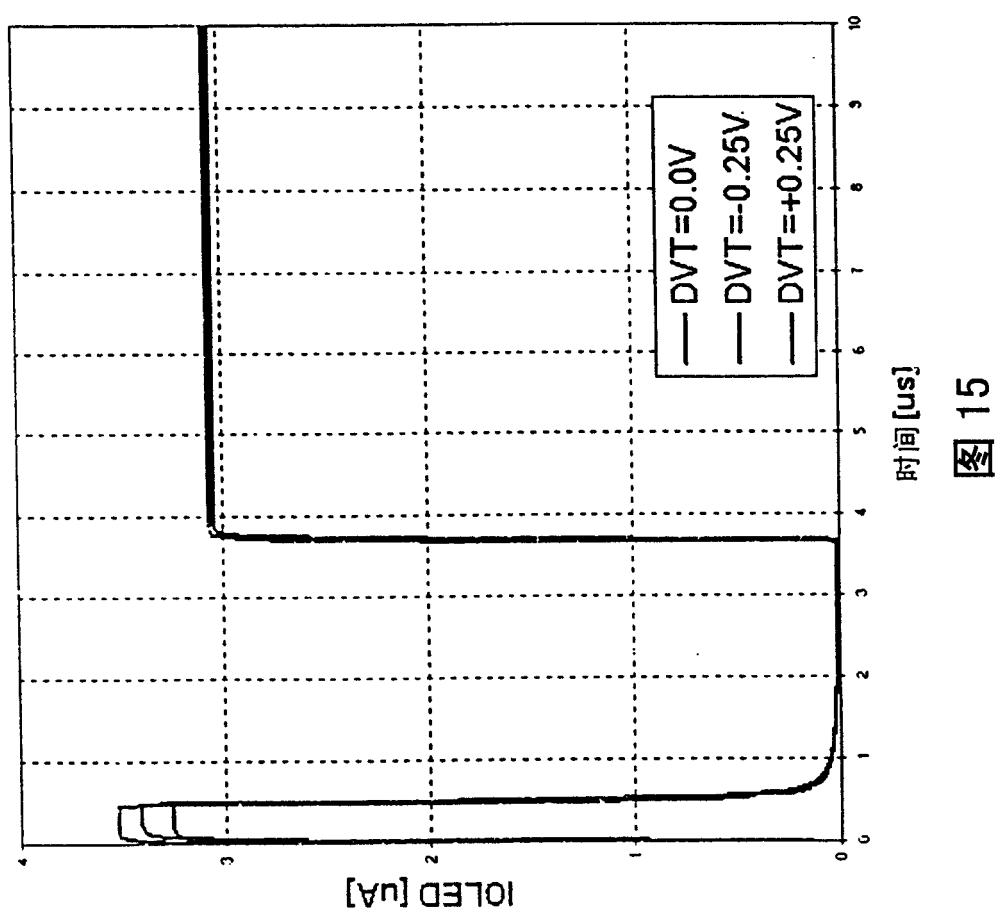

图15是 $\Delta V_T$ 的值变化时的输出电流的模拟的示意图；

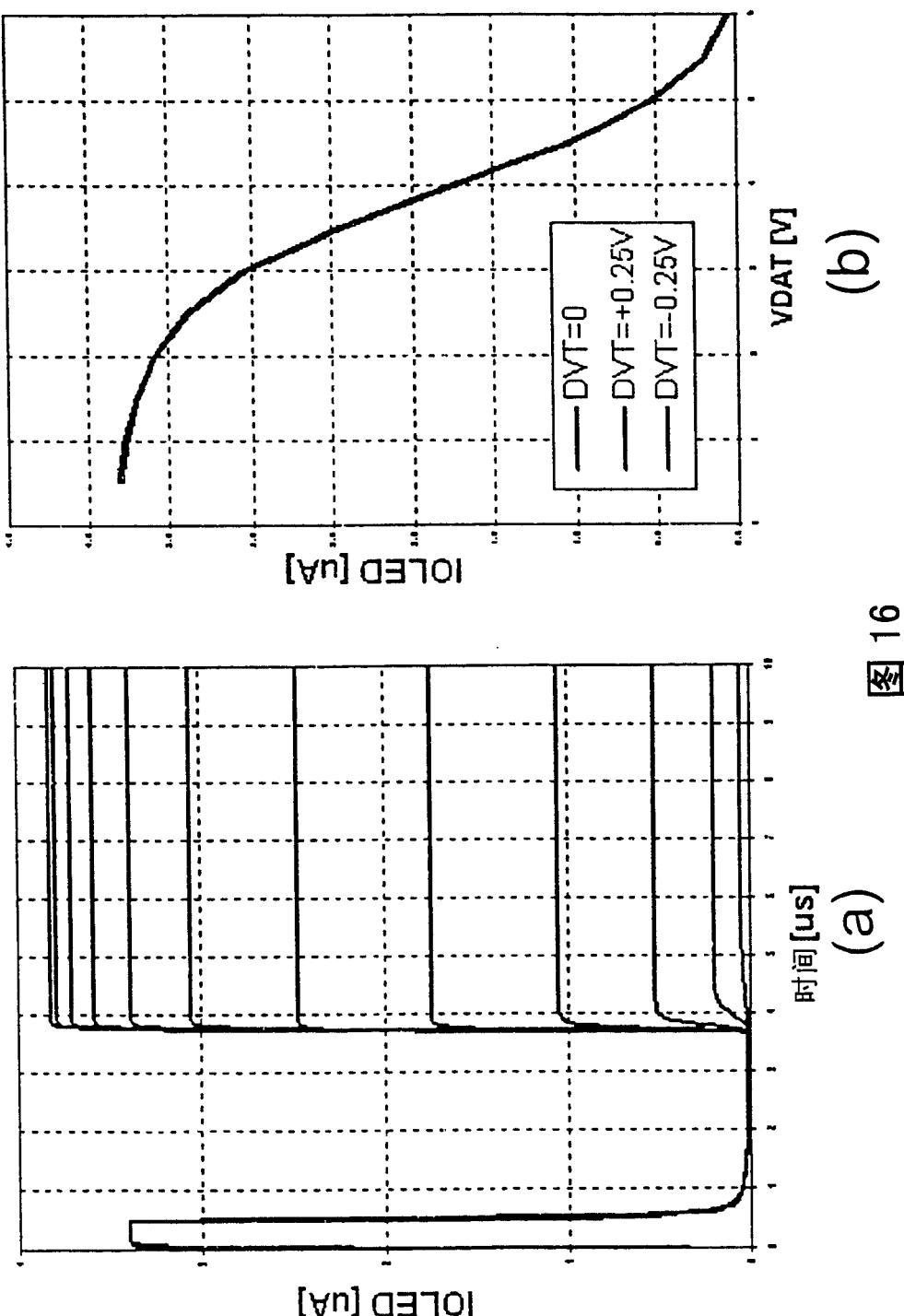

图16是针对不同输入电压和 $\Delta V_T$ 的值变化时的输出电流的模拟的示意图；

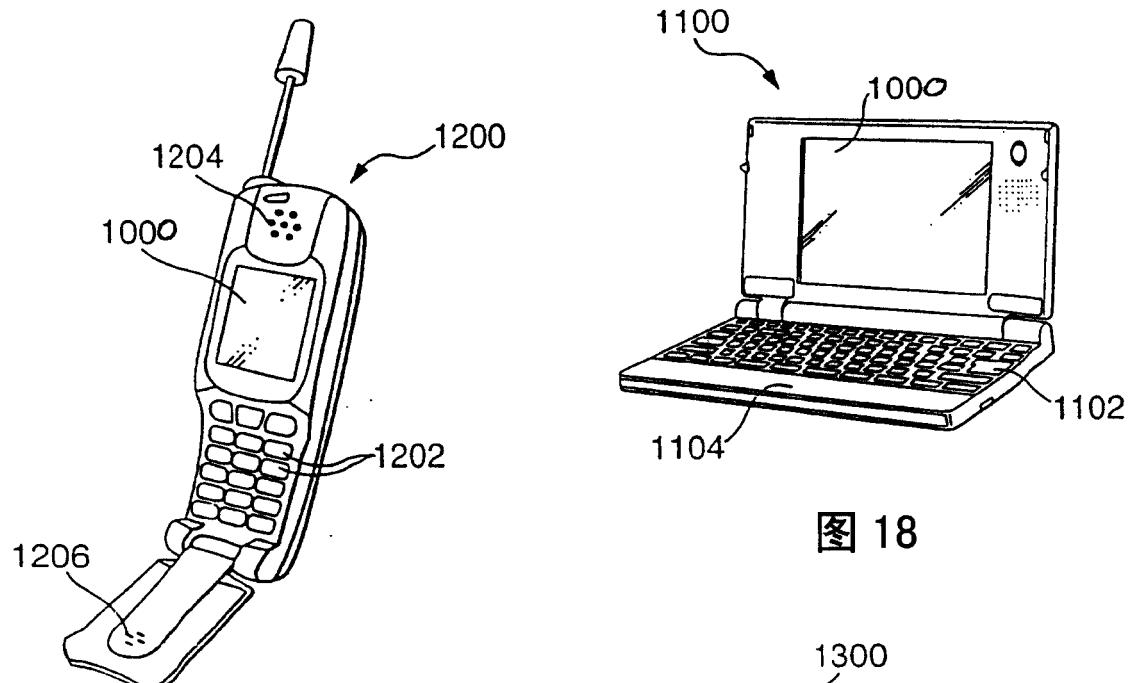

25 图17是包括根据本发明的显示系统的移动电话的示意图；

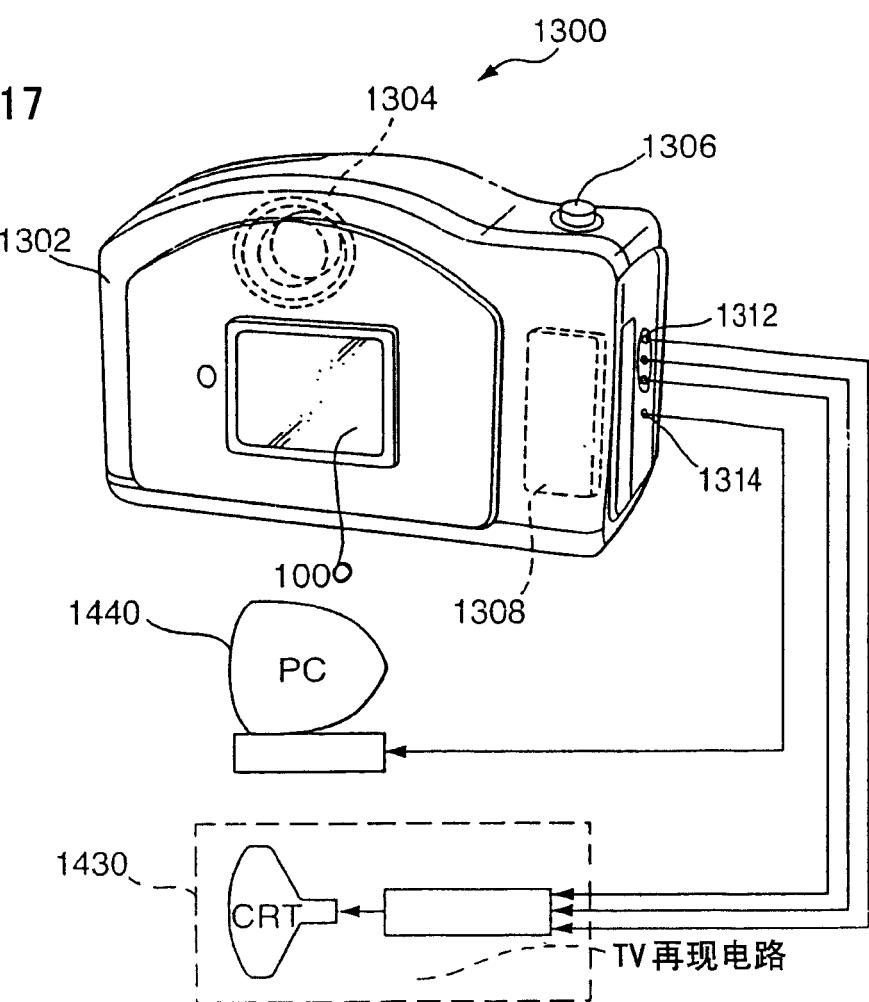

图18是包括根据本发明的显示系统的移动个人计算机的示意图；

图19是包括根据本发明的显示系统的数字摄像机的示意图。

### 30 具体实施方式

在整个以下描述中，将使用相同的参考数字来表示相同的部分。

参考图3，可以按照两种方式对具有引脚1、2、3的驱动晶体管74进行二极管连接，尽管在二极管连接的晶体管的任一配置中，栅极端子总是与漏极端子相连。可以将引脚1和2相连从而形成阴极端子，而5 引脚3形成阳极端子。可选地，可以将引脚2和3相连从而形成阴极端子，而引脚1形成阳极端子。

如上所述，类似TFT具有变化的阈值电压，即使同时和以相同的工艺对其进行制造。在阵列中的所有TFT可以被认为具有共同的标称阈值电压 $V_T$ 。此外，各个TFT可以被认为具有不同阈值电压变化 $\Delta V_T$ 。因此，每一个TFT的实际阈值电压是 $V_T + \Delta V_T$ ， $\Delta V_T$ 在TFT之间变化。

10

在本发明中，驱动晶体管具有以下属性：阈值电压 $V_T + \Delta V_T$ 是相同的，而与电流流过的方向无关-换句话说，哪一个端子被设为源极而哪一个端子被设置为漏极都是可以的。

在源极和漏极端子之间对称且还未加压的驱动晶体管具有该属性。在对称的晶体管中，源极和漏极端子被同等涂覆且相对于栅极端子对称。这样的晶体管是通常是自动对准的。对于具有标称阈值电压 $V_T$ 和阈值电压变化 $\Delta V_T$ 的对称驱动晶体管74而言，当二极管连接时所观察到的驱动晶体管74的阈值电压保持为 $V_T + \Delta V_T$ 并与对驱动晶体管74进行二极管连接的方式无关。

15

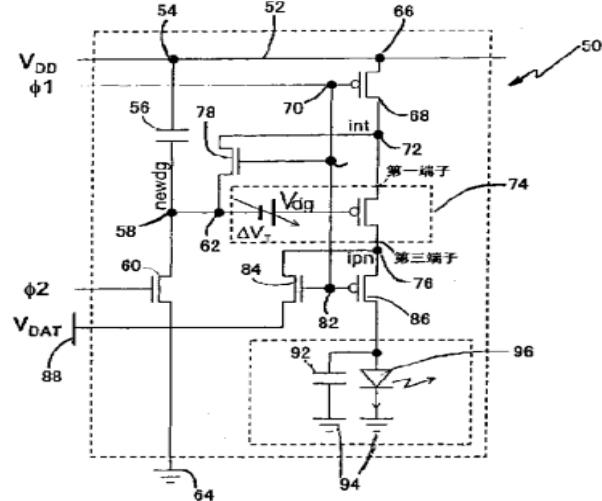

参考图4，根据本发明第一实施例的像素电路50包括具有第一电容器56的第一端子相连的第一节点54的第一干线干线（rail）52。第一电容器56的第二端子与连接到第一n沟道晶体管60的源极端子和第三节点62的第二节点58（被称为newdg）相连。第一n沟道晶体管60包括栅极端子以及与第二干线64相连的漏极端子。

20

第一干线52包括与第一p沟道晶体管68的源极端子相连的第一节点66，所述第一p沟道晶体管68包括与第五节点70相连的栅极端子和与第六节点72（被称为int）相连的漏极端子。所述第六节点72 int与具有栅极端子和第三端子的驱动晶体管74的第一端子相连。所述驱动晶体管74是第二p沟道晶体管。如参考图3较好地看到的以及还参考图5

25 30 稍后详细描述的，根据所述驱动晶体管74是否为二极管连接的，驱动

晶体管74的第一端子和第三端子可以互换为源极和漏极端子。驱动晶体管74的第三端子与第七节点76(被称为ipn)相连并且其栅极端子与第三节点62相连。

第六节点72 int还与第二n沟道晶体管78的源极端子相连，所述n沟道晶体管78包括与第八节点80相连的栅极端子和与第三节点62相连的漏极端子。第八节点80与第九节点82相连，所述第九节点82与第三n沟道晶体管84的栅极端子和第三p沟道晶体管86的栅极端子相连。第三n沟道晶体管84的漏极端子与第七节点76 ipn相连，源极端子与第三干线88相连。第三p沟道晶体管86的源极端子与第七节点76 ipn相连，漏极端子与包括与第四干线94相连的阴极端子的OLED 96的阳极端子相连。还将第二电容器92包括在像素电路50中以表示OLED 96的相关寄生电容。

参考上述描述和以下整个描述，对像素电路50的节点的参考仅是说明性的。作为示例，可选地，可以将图4所示的节点70、80和82表示为一个连接。

在操作时，将诸如5V的电压 $V_{DD}$ 施加到像素电路50的两端以驱动OLED 96，尽管能够使用其他电压。如参考图3所讨论的，驱动晶体管74具有标称阈值电压 $V_T$ 和阈值电压变化 $\Delta V_T$ 。因此，当进行二极管连接时观察到驱动晶体管74的阈值电压为 $V_T + \Delta V_T$ 。图4示出了阈值电压变化 $\Delta V_T$ ，并且其跟随与驱动晶体管74的栅极端子串联的可变电压源。第一n沟道晶体管60、第二n沟道晶体管78和第三n沟道晶体管84与第一p沟道晶体管68和第三p沟道晶体管86一起在第一信号 $\phi_1$ 和第二信号 $\phi_2$ 的控制下作为开关操作，而第二p沟道晶体管是用于向OLED 96提供受控电平的电流的驱动晶体管74。

像素电路50具有三级操作：预充电级、自调节级和输出级。

在预充电级中，第一信号 $\phi_1$ 是逻辑1并将其施加到第二n沟道晶体管78、第三n沟道晶体管84、第一p沟道晶体管68和第三p沟道晶体管86的栅极端子。因此，使第二n沟道晶体管78和第三n沟道晶体管导通而使第一p沟道晶体管68和第三p沟道晶体管86截止。另外，在预充电级中，第二信号 $\phi_2$ 是逻辑1并将其施加到第一n沟道晶体管60从而使第

一n沟道晶体管60导通。因此，使用第二n沟道晶体管78对驱动晶体管74进行二极管连接，通过使第一p沟道晶体管68截止，使 $V_{DD}$ 对地路径隔离，并且通过使第一n沟道晶体管60导通，使第二节点58 newdg接地。

第三干线88处于电压 $V_{DAT}$ ，在本实施例的预充电级中，为诸如0V，5 尽管可以使用其他电压。结果，将第二节点58 newdg预充电到等于第二干线64的电压的电压 $V_{newdg}$ ，例如地(0V)，并且所述像素电路50可以由图5(a)所示的像素电路50来表示。因此，跨接在第一电容器56两端的电压为 $V_{DD} - V_{newdg} = 5V$ 。

10 第二节点58 newdg和第六节点72 int通过第二n沟道晶体管78连接，并且跨接在第二节点58两端的电压 $V_{newdg}$ 等于跨接在第六节点72两端的电压 $V_{int}$ 。提供电压 $V_{DAT}$ 的供电干线88通过第三n沟道晶体管84与第七节点76 ipn相连，并且跨接在第七节点76两端的电压 $V_{ipn}$ 等于 $V_{DAT}$ 。因此，第二节点58 newdg是二极管连接的驱动晶体管74的阴极端子而第七节点76 ipn是其阳极端子。

15 在自调节级中，并且更具体地在自调节级的数据传输期间，第一信号 $\phi_1$ 保持为逻辑1，施加到第二n沟道晶体管78、第三n沟道晶体管84、第一p沟道晶体管68和第三p沟道晶体管86的栅极端子。使第二n沟道晶体管78和第三n沟道晶体管保持导通而使第一p沟道晶体管68和第三p沟道晶体管86保持截止。

20 第二信号 $\phi_2$ 变为逻辑0，施加到第一n沟道晶体管60的栅极端子，从而通过使第一n沟道晶体管60截止来使第二节点newdg不再接地。

现在，使电压 $V_{DAT}$ 跳到(pulse)用于驱动OLED 96的 $V_{DAT}$ 的所需值，例如3V。优选地，开始跳到 $V_{DAT}$ 的所需值与第一n沟道晶体管60的截止同时或在其之后发生。

25 由于将第二节点58 newdg预充电到地(0V)并小于 $V_{DAT}$ (3V)，对二极管连接的驱动晶体管74进行正向偏置，并使电流I流到第一电容器56以使第一电容器56放电，直到达到稳定的状态为止。

在稳定状态处， $V_{newdg} = V_{DAT} - (V_T + \Delta V_T)$ 。跨接在第一电容器56两端的电压因而为 $V_{DD} - V_{newdg} = V_{DD} - (V_{DAT} - (V_T + \Delta V_T))$ 。如果将值1.1V30 提供给标称阈值电压 $V_T$ ，则在稳定状态下跨接在第一电容器56两端的

电压等于 $3.1V + \Delta V_T$ 。达到稳定状态所需的时间主要取决于在第一电容器56和使驱动晶体管74能够被二极管连接的第二n沟道晶体管78的阻抗之间所产生的RC时间常数。尽管不太重要，但是驱动晶体管74和第三n沟道晶体管84的电阻还提供达到稳定状态所需的时间。

5 棚极端子的有效电压 $V_{dg} = V_{newdg} + \Delta V_T$ 。因此，当达到稳定状态时，可以将棚极端子 $V_{dg}$ 的有效电压写作 $V_{dg} = V_{DAT} - V_T = 1.9V$ ，与任何阈值变化 $\Delta V_T$ 无关。

10 在输出级中，第一信号 $\Phi 1$ 是逻辑0并施加到第二n沟道晶体管78、第三n沟道晶体管84、第一p沟道晶体管68和第三p沟道晶体管86的栅极端子。由此，使第二n沟道晶体管78和第三n沟道晶体管截止而使第一p沟道晶体管68和第三p沟道晶体管86导通。在输出级中，第二信号 $\Phi 2$ 保持为逻辑0。

15 如图5 (b) 较好示出的，在输出级中，在第一端子和棚极端子之间对驱动晶体管74不再进行二极管连接，因此，所述驱动晶体管74充当OLED 96的恒流源。由驱动晶体管74传递到OLED 96的电流幅度取决于 $V_{DAT}$ 的值（更具体地，在自调节级中 $V_{DAT}$ 所跳到的值）并且不是阈值变化 $\Delta V_T$ 。因此，针对相同的 $V_{DAT}$ 值，将形成显示器的阵列中的所有像素电路50驱动到相同的亮度。

20 图10示出了如图4所示的像素电路的典型驱动波形。参考图10 (a)，第一信号 $\Phi 1$ 和第二信号 $\Phi 2$ 均为逻辑1，表示预充电级的开始，以便将第二节点58 newdg设置到等于地的电压，如上所述。随着第二信号 $\Phi 2$ 下降到逻辑0，自调节级开始且 $V_{DAT}$ 跳到诸如3V的值。由于将第二节点58 newdg预充电到等于地电压并小于 $V_{DAT}$  (3V) 的电压，因此，对二极管连接的驱动晶体管74进行正向偏置，并且电流I流到第一电容器56以便对第一电容器56进行放电，直到达到稳定状态为止。在达到状态状态时，第一信号 $\Phi 1$ 变为逻辑0而输出级开始，从而独立于阈值变化 $\Delta V_T$ 来驱动OLED 96。如本领域的技术人员应该理解的，图10 (b) 到 (d) 所示的驱动波形还同样适用于如上所述的像素电路50。

30 与以下所讨论的配置相同，如图4所示的配置具有以下优点：与现有技术配置相比，显著地减小了对像素电路进行初始化和编程所需

的时间，从而提供了一种更为有效、快速和更为通用的显示系统。而且，在本发明中减小了各个像素电路的尺寸，从而提供了一种更为紧凑和有效的显示器，具有改善的孔径比。

在图4所示的像素电路50的可选实施例中，第一n沟道晶体管60与5 供电线 $V_{ss}$ 而非第二干线64相连。OLED 96的阴极端子还可以或替代地与供电线 $V_{ss}$ 而非第四干线94相连。

参考图6，根据本发明第二实施例的图4所示的像素电路50包括附加第四p沟道晶体管98，包括与第三p沟道晶体管86的漏极端子相连的源极端子和与OLED 96的阳极端子相连的漏极端子。

10 在操作中，在预充电级中，将第二信号 $\phi_2$ 施加到第四p沟道晶体管98的栅极端子。使第一n沟道晶体管60导通并使第四p沟道晶体管98截止，从而在预充电级期间隔离OLED 96，即使在当第二信号 $\phi_2$ 为逻辑1时第一信号 $\phi_1$ 是逻辑0的情况下。因此，第二实施例允许使用不同的驱动波形，如以下参考图11 (a) 和11 (b) 所述的。

15 参考图11 (a) 和 (b)，在第一信号 $\phi_1$ 变为逻辑1之前，第二信号 $\phi_2$ 是逻辑1。如果要在图4所示的电路中使用这些驱动波形，则当第二信号 $\phi_2$ 是逻辑1时，节点newdg 58接地并且p型驱动晶体管的栅极端子也接地。因此，在第一信号 $\phi_1$ 为逻辑1之前，可以暂时使驱动晶体管74导通并使晶体管68和86截止。此时，OLED 96将被暂时驱动到最大20 亮度。然而，在图6所示的像素电路中，这并不重要，由于当使开关60导通时开关98截止并且OLED 96被隔离，如以上所讨论的。

参考图7，根据本发明第三实施例的图4所示的像素电路50包括附加第五p沟道晶体管102和附加第四n沟道晶体管104。第四n沟道晶体管104包括与第一干线52相连的源极端子和与被称为newdg2的节点108相连的漏极端子。节点newdg2与第三节点62相连-即，节点newdg2和第三节点62在技术上是相同的-并且与第五p沟道晶体管102的第一端子相连。第五p沟道晶体管102包括与第二节点58 (newdg) 相连的第二端子。

30 在操作时，在预充电级中，将第二信号 $\phi_2$ 施加到第四n沟道晶体管104的栅极端子和第五p沟道晶体管102的栅极端子。当第二信号 $\phi_2$ 是逻辑1且使第一n沟道晶体管60导通时，第五p沟道晶体管102截止且

第四n沟道晶体管104导通，从而确保了驱动晶体管74也处于截止以隔离OLED 96。

还可以将上述和以下参考图11 (a) 和11 (b) 所述的驱动波形与如图7所示的像素电路50一起使用。更具体地，在图7，在节点newdg 58接地的所有时间，将节点newdg2 108保持在 $V_{DD}$ 处，从而使驱动晶体管的栅极电压等于 $V_{DD}$ 并且不会使驱动晶体管导通。因此，不需要图6中所设置的晶体管98。

在图7所示的配置的一个可选方案中，可以将晶体管104从n沟道晶体管改变为p沟道晶体管，并且可以将晶体管102从p沟道晶体管改变为n沟道晶体管。这有利于从电源 $V_{DD}$ 中提取电流。然而，利用与第二信号 $\phi_2$ 相连的两个这样改变的晶体管的栅极，所述两个晶体管充当反相器。如果仅进行该变化，则这样得到的反相器将会在节点newdg2处输出反相后的第二信号 $\phi_2bar$  (bar)。因此，在 $\phi_2$ 是高电平从而使晶体管60导通而使节点newdg接地的同时，由晶体管104、102形成的反相器将在newdg2处输出反相后的信号 $\phi_2bar$  (换句话说，低电平)。在该情况下，将使p型驱动晶体管导通，并且在 $\phi_1$ 变为高电平之前和对驱动晶体管进行二极管连接之前，OLED将发光。

为了对付这种情况，在第二信号线和通过改变后的晶体管104、102形成的反相器之间添加另外的反相器。因此，输入到由改变后的晶体管104、102形成的反相器的信号是 $\phi_2bar$ 。因此，在 $\phi_2$ 是高电平从而使晶体管60导通而使节点newdg接地的同时，由晶体管104、102形成的反相器具有作为输入的 $\phi_2bar$ 且在newdg2处输出 $\phi_2$  (换句话说，高电平)。结果，使p型驱动晶体管截止，并且在 $\phi_1$ 变为高电平之前和对驱动晶体管进行二极管连接之前，OLED 96不会发光。

参考图8，本发明的第四实施例包括图7所示的像素电路，在可选配置中，具有第四n沟道晶体管104。第四n沟道晶体管104包括与第六节点72 int相连的端子和与第二节点newdg相连的端子。第四n沟道晶体管104包括与用于接收第一信号 $\phi_1$ 的第八节点80相连的栅极端子。

在操作时并且当在预充电级和自调节级期间第一信号 $\phi_1$ 为逻辑1时，使第四n沟道晶体管104导通以便改善第七节点ipn和第二节点

newdg之间的导电路径。

参考图9，根据本发明第五实施例的图4所示的像素电路50包括与第七节点ipn相连的第一n沟道晶体管60的端子，作为与第二干线64相连的替代。因此，驱动晶体管74与第三p沟道晶体管86的端子和第三n沟道晶体管84的端子相连。

在操作时，电压 $V_{DAT}$ 通过第一n沟道晶体管60和第三n沟道晶体管84向第二节点newdg提供预充电级电压。因此，第二干线64不再需要作为地(0V)，也不再由供电线 $V_{ss}$ 替代。在预充电级期间，电压 $V_{DAT}$ 必须小于 $V_{DAT}$ 在自调节级中跳到的电压，从而使驱动晶体管74能够充当正向偏置的二极管连接的晶体管。

图11(b)示出了如图9所示的像素电路50的典型驱动波形。在预充电级中，当第一信号 $\phi 1$ 是逻辑0且第二信号 $\phi 2$ 变为逻辑1时，最初节点newdg通过第一n沟道晶体管60、第三p沟道晶体管86和OLED 96对地放电。第一信号 $\phi 1$ 变为逻辑1且 $V_{DAT}$ 增加到值 $V_{DAT}$ 低电平。由此，驱动晶体管74变为二极管连接的，并且通过第三n沟道晶体管84和第一n沟道晶体管60、驱动晶体管74和第二n沟道晶体管78，将节点newdg初始化为电压 $V_{DAT}$ 低电平。

随着第二信号 $\phi 2$ 下降到逻辑0且在自调节级中， $V_{DAT}$ 低电平增加到值 $V_{DAT}$ 高电平。由此，节点newdg通过第三n沟道晶体管84、驱动晶体管74和第二n沟道晶体管78增加到值 $V_{DAT}$ 高电平- $(V_T + \Delta V_T)$ 。

在输出级处，第一信号 $\phi 1$ 是逻辑0且在第一端子和栅极端子之间不再对驱动晶体管74进行二极管连接。因此，驱动晶体管74通过第一p沟道晶体管68、驱动晶体管74和第三p沟道晶体管86，充当OLED 96的恒流源。由驱动晶体管74传递到OLED 96的电流的幅度取决于值 $V_{DAT}$ (更具体地，在自调节级中，值 $V_{DAT}$ 高电平)而非阈值变化 $\Delta V_T$ 。因此，将形成显示器的阵列中的所有像素电路50驱动到相同的亮度。

在另一可选方案中，也可以将如图6所示的晶体管98包括在如图7到9所示的每一个配置中。因此，在像素电路包括串联在晶体管86和OLED 96之间的p沟道晶体管98的每一种情况下，将控制信号 $\phi 2$ 施加到p沟道晶体管98的栅极，从而使p沟道晶体管98截止而使n沟道晶体管60

导通。

参考图12，在形成显示系统的阵列150中示出了如图4、6、7和8所示的像素电路50的结构。通过图10或图11 (a) 的任一典型波形来驱动阵列150。阵列150的每一个像素电路50包括地线Gnd，可以由供电线5  $V_{ss}$ 来替代，如上所讨论的。所述结构还包括两个单独的水平控制线，以向第一和第二供电信号 $\phi 1$ 和 $\phi 2$ 供电。

参考图13，在形成显示系统的阵列200中示出了如图9所示的像素电路50的结构。通过在如图9所示的像素电路50的情况下采用如图11 (d) 所示的波形，与图12所示的结构相比，示出了水平控制线的数量10 的减少。

由于所述控制线SEL, 2 (在图11 (c) 和 (d) 中被称为控制信号  $V_{SEL_{n+1}}$ ) 为相邻像素电路50提供第一控制信号 $\phi 1$ 和第二控制信号 $\phi 2$ ，因此实现了水平控制线数量的减少。

当然，可以对其中为每一行像素提供了两条信号线的图12所示的15 结构进行调节，从而每一个像素电路中的电容器对数据线VDAT而非对地Gnd进行放电，类似于图13。通过在图6、7和8所示的像素电路50的情况下采用如图11 (c) 所示的波形，与图12所示的结构相比，示出了水平线数量的减少。

类似地，可以对其中在相邻的像素行之间共享信号线的图13所示20 的结构进行调节，从而每一个像素电路中的电容器对地Gnd而非数据线VDAT进行放电，类似于图12。通过在图9所示的像素电路50的情况下采用如图11 (b) 所示的波形，与图12所示的结构相比，示出了水平线数量的减少。

当然，图12和13所示的阵列还可适用于本发明的像素电路的所有25 适当可选方案，无论以上是否描述过。

应该注意，在图11 (a) 到 (d) 的每一个中，第一和第二控制信号 $\phi 1$ 和 $\phi 2$ 重叠。即，针对 $\phi 2$ 为高电平的部分时间， $\phi 1$ 为高电平而针对 $\phi 1$ 为高电平的部分时间， $\phi 2$ 为高电平。然而，针对 $\phi 2$ 为低电平30 的部分时间， $\phi 1$ 也为高电平，而针对 $\phi 1$ 为低电平的部分时间， $\phi 2$ 也为高电平。到目前为止未知的使用重叠控制信号的可能性能够增加

扫描速度，结果，提高了显示的运动图像的质量。

参考图14，相对于以微秒为单位的时间，图示了如图4所示的像素电路50的第二节点58处的电压V<sub>newdg</sub>的模拟。在预充电级（在图12中标记为PRESET）中，电压V<sub>newdg</sub>实质上下降到地（0V）。在图12所示的自调节级（标记为PROGRAM）中，随着V<sub>DAT</sub>跳到用于驱动OLED 96的电压，电压V<sub>newdg</sub>爬到值V<sub>DAT</sub>-（V<sub>T</sub>+ΔV<sub>T</sub>）。在图12所示的输出级（被称为LOCK DOWN）中，由第一电容器56保持电压V<sub>newdg</sub>，直到重复该处理为止。如从图12中可以容易地意识到，电压V<sub>newdg</sub>相对于变化值ΔV<sub>T</sub>发生变化。

从图14中可以看到，可以仅在几微秒内完成预充电和自调节级。这大约比现有技术中所实现的快两个数量级的幅度（或100倍）。因此，可以使用更低的电压。因此，本发明提供了改进的显示质量和减小的能量消耗。然而，根据本发明的像素电路和显示设备比现有技术中的像素电路和显示设备更小和更为紧凑。

参考图15，相对于变化值ΔV<sub>T</sub>绘制了用于驱动OLED 96的输出电流（I<sub>OLED</sub>）的模拟。由此，图15示出了输出电流I<sub>OLED</sub>是相同的，而与ΔV<sub>T</sub>无关，从而可以将形成阵列的像素电路驱动到相同的亮度，而与变化值ΔV<sub>T</sub>无关。

图16示出了类似的效果。在图16（a）中，针对导致了输出电流I<sub>OLED</sub>的变化幅度的输入电压V<sub>DD</sub>的变化值、以及不会影响输出I<sub>OLED</sub>的和变化值ΔV<sub>T</sub>，相对于以微秒为单位的时间图示了输出电流I<sub>OLED</sub>。图16（b）示出了针对不同的ΔV<sub>T</sub>，随着V<sub>DAT</sub>的变化的I<sub>OLED</sub>的变化。输出电流I<sub>OLED</sub>实质上是相同的，而与ΔV<sub>T</sub>无关，因此，针对ΔV<sub>T</sub>的各个值的输出电流I<sub>OLED</sub>会重叠。因此，可以将形成阵列的像素电路驱动到相同的亮度，而与变化值ΔV<sub>T</sub>无关。

如上所述的使用像素电路50的显示系统100适用于小型移动电子产品，例如移动电话、个人数字助理（PDA）、计算机、CD播放器、DVD播放器等-尽管并不局限于此。

现在将描述其中可以嵌入显示系统1000的多个终端设备。

将描述其中将显示系统1000应用于便携式或移动电话的示例。图

17是示出了便携式电话的配置的立体图。在图中，所述便携式电话1200具有多个操作键1202、耳机1204、话筒1206和具有显示板形式的显示系统1000。话筒1206或耳机1204可以用于输出语音。

现在将描述其中将根据上述实施例之一的显示系统1000应用于

5 移动个人计算机的示例。

图18是示出了该个人计算机的配置的立体图。在该图中，个人计算机1100具有包括键盘1102的主体1104和具有显示板形式的显示系统1000。

接下来，将描述使用显示系统1000的数字静态摄像机。图19是简

10 要示出了数字静态摄像机的配置和与外部设备的连接的立体图。

典型摄像机根据来自对象的光学图像使胶片感光，而数字静态摄像机1300利用诸如电荷耦合器件（CCD），通过光电转换从对象的光学图像中产生成像信号。所述数字静态摄像机1300具有在壳体1302的背面处的显示板形式的显示系统1000以根据来自CCD的成像信号来进行

15 显示。因此，显示系统1000充当用于显示对象的取景器。将包括光学镜头和CCD的光接受单元1304设置在外壳1302的前侧（该图背面）。可以将显示系统1000嵌入在数字静态摄像机中。

除了图17所示的便携式电话、图18所示的个人计算机和图19所示的数字静态摄像机之外的终端设备的另外的示例包括：个人数字助理

20 （PDA）、电视机、取景器型和监视器型视频磁带记录器、车载导航系统、寻呼机、电子笔记本、便携式计算器、字处理器、工作站、TV电话、销售点系统（POS）终端和具有触摸板的设备。当然，本发明的显示系统可以应用于这些终端设备中的任一个。

仅作为示例给出了前面的描述，本领域的技术人员将会意识到，

25 在不脱离本发明的范围的情况下，可以进行修改。

图 1

由 S. M. Choi 等人所写的 "A self-compensated voltage programming pixel structure for active-matrix organic light emitting diodes", 国际显示工作站 2003, 第 535 到 538 页 (2003)

图 2

图3

图7

图 9

图 10

图 11

图 17

图 18

图 19

|                |                                                                                                             |                      |            |

|----------------|-------------------------------------------------------------------------------------------------------------|----------------------|------------|

| 专利名称(译)        | 像素电路                                                                                                        |                      |            |

| 公开(公告)号        | <a href="#">CN1664901A</a>                                                                                  | 公开(公告)日              | 2005-09-07 |

| 申请号            | CN200510053150.X                                                                                            | 申请日                  | 2005-03-04 |

| [标]申请(专利权)人(译) | 精工爱普生株式会社                                                                                                   |                      |            |

| 申请(专利权)人(译)    | 精工爱普生株式会社                                                                                                   |                      |            |

| 当前申请(专利权)人(译)  | 精工爱普生株式会社                                                                                                   |                      |            |

| [标]发明人         | 西蒙塔姆                                                                                                        |                      |            |

| 发明人            | 西蒙·塔姆                                                                                                       |                      |            |

| IPC分类号         | H01L51/50 G09G3/20 G09G3/30 G09G3/32 H05B33/14 G09F9/30 H01L29/786                                          |                      |            |

| CPC分类号         | G09G2300/0842 G09G2320/043 G09G2310/0262 G09G2320/0252 G09G2320/0233 G09G3/3233 G09G2300/0819 G09G2300/0426 |                      |            |

| 代理人(译)         | 王玮                                                                                                          |                      |            |

| 优先权            | 2004004919 2004-03-04 GB                                                                                    |                      |            |

| 其他公开文献         | CN100498902C                                                                                                |                      |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                   | <a href="#">SIPO</a> |            |

## 摘要(译)

已知的是，对用于驱动发光器件的像素电路中的驱动晶体管的阈值电压变化进行补偿，例如电流驱动有机发光器件。然而，对这样的像素电路进行编程和初始化可能较慢且需要多个控制或信号线。本发明提出了一种像素电路，包括用于对驱动晶体管进行二极管连接的n沟道晶体管和用于减少信号和控制线数量的装置。