[19] 中华人民共和国国家知识产权局

[12] 发明专利申请公布说明书

[21] 申请号 200610139245.8

[51] Int. Cl.

G09G 3/30 (2006.01)

G09G 3/20 (2006.01)

H05B 33/08 (2006.01)

H05B 33/14 (2006.01)

[43] 公开日 2007 年 3 月 28 日

[11] 公开号 CN 1937020A

[22] 申请日 2006.9.20

[21] 申请号 200610139245.8

[30] 优先权

[32] 2005.9.20 [33] KR [31] 10 - 2005 - 0087425

[71] 申请人 三星 SDI 株式会社

地址 韩国京畿道水原市灵通区信洞 575

[72] 发明人 申东蓉

[74] 专利代理机构 北京铭硕知识产权代理有限公司

代理人 郭鸿禧 韩素云

权利要求书 5 页 说明书 11 页 附图 7 页

[54] 发明名称

扫描驱动电路和使用该扫描驱动电路的有机发光显示器

[57] 摘要

公开了一种扫描驱动电路和使用该扫描驱动电路的有机发光显示器。具有多个第一级联结构的第一扫描驱动器依次输出选择信号，具有多个第二级联结构的第二扫描驱动器依次输出发射信号。所述第一级联结构和所述第二级联结构的每个被构造为具有基本为零的静态电流，并且操作速度可被最优化，而不会显著地增加功耗。

1、一种扫描驱动电路，包括；

第一扫描驱动器，包括多个第一级联结构并被构造为依次输出选择信号；

和

第二扫描驱动器，包括多个第二级联结构并被构造为依次输出发射信号，

其中，第一级联结构和第二级联结构的每个包括：

第一晶体管，被构造为接收前一级联结构的输出电压或第一输入信

号，其包括与第一时钟端连接的栅极端和输出端；

第二晶体管，与第二时钟端和输出线连接，其包括与第一晶体管的

输出端连接的栅极端；

第三晶体管，连接在第二电源和第一节点之间，其包括与第一时钟

端连接的栅极端；

第四晶体管，与第一时钟端和第一节点连接，其包括与第一晶体管

的输出端连接的栅极端； 和

第五晶体管，连接在第一电源和输出线之间，其包括与第一节点连

接的栅极端。

2、如权利要求 1 所述的扫描驱动电路，还包括：第一电容器，连接在第

一晶体管的输出端和输出线之间。

3、如权利要求 1 所述的扫描驱动电路，其中，第一级联结构和第二级联

结构的每个被构造为接收具有彼此基本相反的相位的第一时钟端的信号和第

二时钟端的信号。

4、如权利要求 1 所述的扫描驱动电路，还包括被构造为分别接收第一时

钟信号和第二时钟信号的第一时钟输入线和第二时钟输入线，其中，第一时

钟输入线与第一扫描驱动器的多个奇数级联结构的第一时钟端连接，第二时

钟输入线与第一扫描驱动器的所述多个奇数级联结构的第二时钟端连接。

5、如权利要求 4 所述的扫描驱动电路，其中，第一扫描驱动器的所述多

个奇数级联结构的每个被构造为：当第一时钟信号具有低电平时执行预充电

操作，当第一时钟信号具有高电平时执行赋值操作。

6、如权利要求 5 所述的扫描驱动电路，其中，执行预充电操作的步骤包

括：输出高电平输出和接收输入信号，执行赋值操作的步骤包括输出与所述

---

输入信号相应的电平，其中，所述多个第一级联结构总体被构造为依次产生选择信号序列，其中，基本上在第一时钟信号和第二时钟信号中的至少一个的每半个周期产生选择信号一次。

7、如权利要求 1 所述的扫描驱动电路，还包括被构造为分别接收第一时钟信号和第二时钟信号的第一时钟输入线和第二时钟输入线，其中，第二时钟输入线与第二扫描驱动器的多个奇数级联结构的第一时钟端连接，第一时钟输入线与第二扫描驱动器的所述多个奇数级联结构的第二时钟端连接。

8、如权利要求 7 所述的扫描驱动电路，其中，第二扫描驱动器的所述多个奇数级联结构的每个被构造为：当第二时钟信号具有低电平时执行预充电操作，当第二时钟信号具有高电平时执行赋值操作。

9、如权利要求 8 所述的扫描驱动电路，其中，执行预充电操作的步骤包括输出高电平输出和接收输入信号，执行赋值操作的步骤包括输出与所述输入信号相应的电平，其中，所述多个第二级联结构总体被构造为依次产生发射信号序列，其中，基本上在第一时钟信号和第二时钟信号中的至少一个的每半个周期产生发射信号一次。

10、如权利要求 1 所述的扫描驱动电路，其中，输入到第一扫描驱动器的奇数级联结构的第一时钟端和第二时钟端的每个的时钟信号的每个与输入到第二扫描驱动器的偶数级联结构的第一时钟端和第二时钟端的每个的时钟信号的每个基本相同。

11、如权利要求 1 所述的扫描驱动电路，其中，输入到第一扫描驱动器的偶数级联结构的第一时钟端和第二时钟端的每个的时钟信号的每个与输入到第二扫描驱动器的奇数级联结构的第一时钟端和第二时钟端的每个的时钟信号的每个基本相同。

12、如权利要求 1 所述的扫描驱动电路，还包括被构造为分别接收第一时钟信号和第二时钟信号的第一时钟输入线和第二时钟输入线，其中，第二扫描驱动器的所述多个级联结构被构造为接收与第一时钟信号和第二时钟信号中的至少一个的整数个周期基本相等的持续时间的输入信号。

13、如权利要求 12 所述的扫描驱动电路，其中，所述持续时间在不同的数据帧时间段基本恒定。

14、如权利要求 12 所述的扫描驱动电路，其中，第二扫描驱动器的每个级联结构被构造为响应所述输入信号输出高电平和低电平交替的序列。

15、一种扫描驱动电路，包括：

第一时钟信号输入线和第二时钟信号输入线，被构造为分别接收第一时钟信号和第二时钟信号；

第一扫描驱动器，被构造为输出选择信号，其包括多个第一级联结构；

第二扫描驱动器，被构造为输出发射信号，其包括多个第二级联结构；

其中，第一级联结构和第二级联结构的每个包括输入端以及第一时钟端和第二时钟端，并且与输入端的输入线或前一级联结构的输出线连接以接收输入端的输入信号，与第一时钟信号输入线和第二时钟信号输入线连接以接收第一时钟端的第一时钟信号和第二时钟端的第二时钟信号，

其中，每个级联结构被构造为执行输出高电平信号和接收输入信号的预充电操作，其中，在第一时钟信号和第二时钟信号中的至少一个的第一部分时间段期间执行预充电操作，并且每个级联结构被构造为输出与所述输入信号的电平相应的电平，其中，所述多个第一级联结构总体被构造为依次产生低电平脉冲序列，其中，基本上在第一时钟信号和第二时钟信号中的至少一个的每半个周期产生所述低电平脉冲一次。

16、如权利要求 15 所述的扫描驱动电路，其中，所述级联结构的每个包括：

第一晶体管，被构造为接收前一级联结构的输出电压或第一输入信号，其包括与第一时钟端连接的栅极端和输出端；

第二晶体管，与第二时钟端和输出线连接，其包括与第一晶体管的输出端连接的栅极端；

第三晶体管，连接在第二电源和第一节点之间，其包括与第一时钟端连接的栅极端；

第四晶体管，与第一时钟端和第一节点连接，其包括与第一晶体管的输出端连接的栅极端；和

第五晶体管，连接在第一电源和输出线之间，其包括与第一节点连接的栅极端。

17、如权利要求 16 所述的扫描驱动电路，还包括连接在第一晶体管的输出端和输出线之间的第一电容器。

18、如权利要求 15 所述的扫描驱动电路，其中，第一级联结构和第二级联结构的每个被构造为接收具有彼此基本相反的相位的第一时钟信号和第二

---

时钟信号。

19、如权利要求 15 所述的扫描驱动电路，其中，第一时钟信号输入线与第一扫描驱动器的多个奇数级联结构的第一时钟端连接，第二时钟信号输入线与第一扫描驱动器的所述多个奇数级联结构的第二时钟端连接。

20、如权利要求 19 所述的扫描驱动电路，其中，第一扫描驱动器的所述多个奇数级联结构的每个被构造为：当第一时钟信号具有低电平时执行预充电操作，当第一时钟信号具有高电平时执行赋值操作。

21、如权利要求 20 所述的扫描驱动电路，其中，执行预充电操作的步骤包括输出高电平输出，执行赋值操作的步骤包括输出与在执行预充电操作时接收的输入信号相应的电平，其中，所述多个第一级联结构总体被构造为依次产生选择信号序列，其中，基本上在第一时钟信号和第二时钟信号中的至少一个的每半个周期产生选择信号一次。

22、如权利要求 15 所述的扫描驱动电路，其中，第二时钟信号输入线与第二扫描驱动器的多个奇数级联结构的第一时钟端连接，第一时钟信号输入线与第二扫描驱动器的所述多个奇数级联结构的第二时钟端连接。

23、如权利要求 22 所述的扫描驱动电路，其中，第二扫描驱动器的所述多个奇数级联结构的每个被构造为：当第二时钟信号具有低电平时执行预充电操作，当第二时钟信号具有高电平时执行赋值操作。

24、如权利要求 23 所述的扫描驱动电路，其中，执行预充电操作的步骤包括输出高电平输出，执行赋值操作的步骤包括输出与在执行预充电操作时接收的输入相应的电平，其中，所述多个第二级联结构总体被构造为依次产生发射信号序列，其中，基本上在第一时钟信号和第二时钟信号中的至少一个的每半个周期产生发射信号一次。

25、如权利要求 15 所述的扫描驱动电路，其中，输入到第一扫描驱动器的奇数级联结构的第一时钟端和第二时钟端的每个的时钟信号的每个与输入到第二扫描驱动器的偶数级联结构的第一时钟端和第二时钟端的每个的时钟信号的每个基本相同。

26、如权利要求 15 所述的扫描驱动电路，其中，输入到第一扫描驱动器的偶数级联结构的第一时钟端和第二时钟端的每个的时钟信号的每个与输入到第二扫描驱动器的奇数级联结构的第一时钟端和第二时钟端的每个的时钟信号的每个基本相同。

27、如权利要求 15 所述的扫描驱动电路，其中，第二扫描驱动器的所述多个级联结构被构造为接收与第一时钟信号和第二时钟信号中的至少一个的整数个周期基本相等的持续时间的输入信号。

28、如权利要求 27 所述的扫描驱动电路，其中，所述持续时间在不同的数据帧时间段期间基本恒定。

29、如权利要求 27 所述的扫描驱动电路，其中，第二扫描驱动器的每个级联结构被构造为响应所述输入信号输出高电平和低电平交替的序列。

30、一种有机发光显示器，包括：

像素阵列，与选择信号线、数据线和发射信号线连接；

数据驱动电路，被构造为将数据信号提供给数据线；和

扫描驱动电路，包括：

第一时钟信号输入线和第二时钟信号输入线，被构造为接收第一时钟信号和第二时钟信号；

第一扫描驱动器，被构造为输出选择信号，第一扫描驱动器包括多个第一级联结构；

第二扫描驱动器，被构造为输出发射信号，第二扫描驱动器包括多个第二级联结构；

其中，第一级联结构和第二级联结构的每个包括输入端以及第一时钟端和第二时钟端，并且与输入端的输入线或前一级联结构的输出线连接以接收输入端的输入信号，与第一时钟信号输入线和第二时钟信号输入线连接以接收第一时钟端的第一时钟信号和第二时钟端的第二时钟信号，

其中，每个级联结构被构造为执行输出高电平信号和接收输入信号的预充电操作，其中，在第一时钟信号和第二时钟信号中的至少一个的第一部分时间段期间执行预充电操作，并且每个级联结构被构造为输出具有与所述输入信号相应的电平的电平，其中，所述多个第一级联结构总体被构造为依次产生低电平脉冲序列，其中，基本上在第一时钟信号和第二时钟信号中的至少一个的每半个周期产生所述低电平脉冲一次。

## 扫描驱动电路和使用该扫描驱动电路的有机发光显示器

本申请要求于 2005 年 9 月 20 日在韩国知识产权局提交的第 2005-87425 号韩国专利申请的权益，该申请的内容公开于此以资参考。

### 技术领域

本发明涉及一种有机发光显示器，更具体地讲，涉及一种可减少数据驱动器中的输出线的数量的发光显示器及其驱动方法和电路。

### 背景技术

通常，有机发光显示器电激发有机化合物，从而该有机发光显示器发光。电路使用电压或电流来驱动有机发光胞阵列以显示图像。这样的有机发光胞通常包括由铟锡氧化物 (ITO) 形成的阳极、有机薄膜和由金属形成的阴极层。

有机薄膜具有包括发光层 (EML)、电子传输层 (ETL) 和空穴传输层 (HTL) 的多层结构，从而保持电子和空穴之间的平衡并提高发光效率。有机薄膜还可包括电子注入层 (EIL) 和空穴注入层 (HIL)。

用于驱动有机发光胞的方法包括无源矩阵法和使用薄膜晶体管 (TFT) 或金属氧化物半导体场效应晶体管 (MOSFET) 的有源矩阵法。无源矩阵具有彼此交叉的阴极线和阳极线，并选择性地驱动阴极线和阳极线。有源矩阵连接 TFT 和具有每个 ITO 像素电极的电容器以根据该电容器存储电压。根据为在电容器存储电压而提供的信号，有源矩阵法分为电压编制法或电流编制法。

有源矩阵类型的有机发光显示器包括显示面板、数据驱动电路、扫描驱动电路和时序控制器。扫描驱动电路从时序控制器接收扫描驱动控制信号，产生扫描信号，并依次将该扫描信号提供给显示面板的扫描线。

也就是说，扫描驱动电路的作用是依次产生将被提供给显示面板的扫描信号以驱动包括在显示面板中的像素。

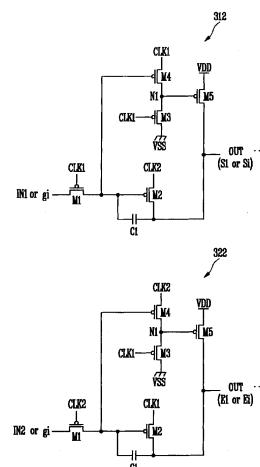

图 1 是显示传统的扫描驱动电路的框图。参考图 1，传统的扫描驱动电路包括与起始脉冲 SP 输入线连接的多个级联结构 ST1 至 STn。所述多个级联

结构 ST1 至 STn 响应起始时钟 SP 依次将时钟脉冲移位以产生输出信号 SO1 至 SOn。在这种情况下，第二级联结构 ST2 至第 n 级联结构 STn 接收前一级联结构的输出信号作为起始脉冲并将该输出信号移位。

因此，所述级联结构以起始脉冲被依次移位的方式产生输出信号 SO1 至 SOn，并将这些输出信号提供给矩阵像素阵列。

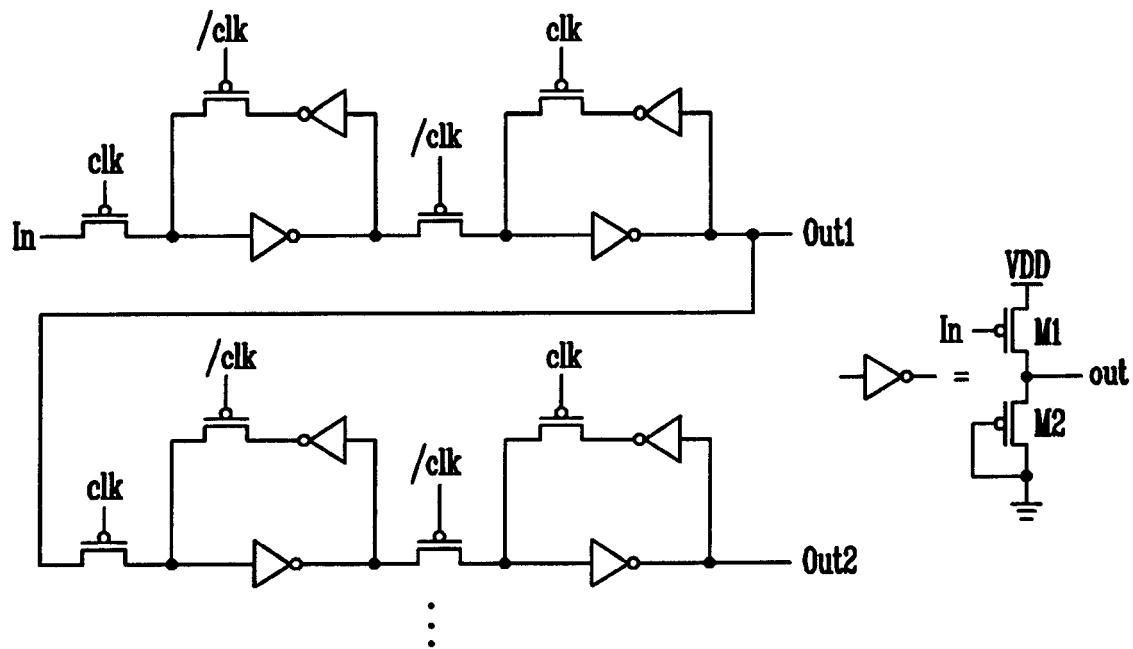

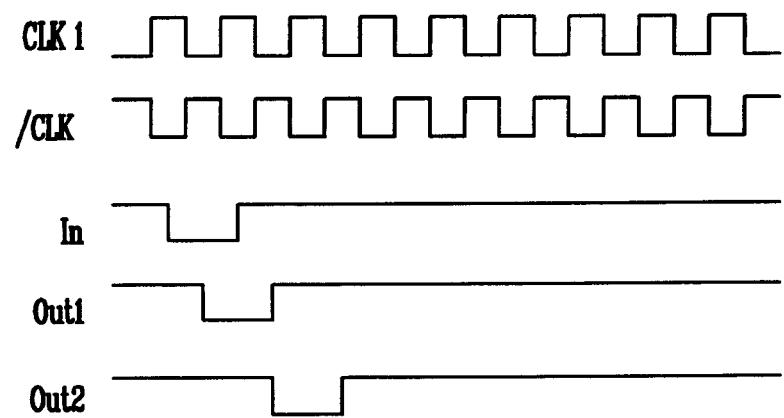

图 2 是图 1 所示的扫描驱动电路中的级联结构的电路图。图 3 是图 2 所示的级联结构的输入和输出波形图。参考图 2 和图 3，每个级联结构使用主从触发器。当时钟 clk 为低电平时，这种触发器连续地接收输入并保持前一输出。

相反，当时钟 clk 为高逻辑电平时，即使输入 IN 变化时，该触发器也保持当时钟 clk 为低电平时接收的输入 IN 并输出接收的信号。

在前述电路中，包括在图 2 所示的触发器中的反相器的问题在于当其输入为低电平时静态电流流过。此外，在该触发器中，已接收高电平输入的反相器的数量与已接收低电平输入的反相器的数量相同。因此，静态电流恒定流过该触发器中的一半反相器，从而引起过高的功耗。

另外，图 2 显示了反相器电路的实施例。根据该实施例，根据第一 PMOS 晶体管 M1 和第二 PMOS 晶体管 M2 的阻抗值之比确定反相器的高电平输出。根据第一 PMOS 晶体管 M1 的阈值电压确定反相器的低电平输出。

由于制造差异，导致晶体管之间的阻抗和阈值参数明显不同。由于有机发光显示器的晶体管通常使用具有高制造可变性的晶体管，所以这是一个重要的问题。结果，图 2 的电路的性能不确定。例如，阈值变化会引起每个反相器的低电平输出变化。结果，当从具有不确定值的第一反相器输出的低电平被作为输入提供给第二反相器时，由于不确定的低值导致第二反相器的第一 PMOS 晶体管中的上拉阻抗不确定，所以第二反相器可具有降低的高输出电平。

此外，在所述反相器中，当输出高电平时，恒定电流流过第一 PMOS 晶体管 M1 和第二 PMOS 晶体管 M2。这导致了恒定功耗。此外，在第二 PMOS 晶体管 M2 中流动的恒定电流使得反相器输出信号的上升时间变慢。

### 发明内容

因此，本发明的一方面在于提供一种可通过从有源矩阵类型电流编制有

机发光显示器中的扫描驱动电路去除静态电流的电流流动路径来减少功耗的扫描驱动电路和使用该扫描驱动电路的有机发光显示器，其中，扫描驱动电路包括用于提供选择信号的第一扫描驱动器和用于提供发射信号的第二扫描驱动器。

### 附图说明

从下面结合附图对实施例的描述中，这些和/或其它方面和优点将变得清楚和更容易理解，其中：

- 图 1 是显示传统的扫描驱动电路的框图；

- 图 2 是图 1 所示的扫描驱动电路中的级联结构的电路图；

- 图 3 是图 2 所示的级联结构的输入/输出波形图；

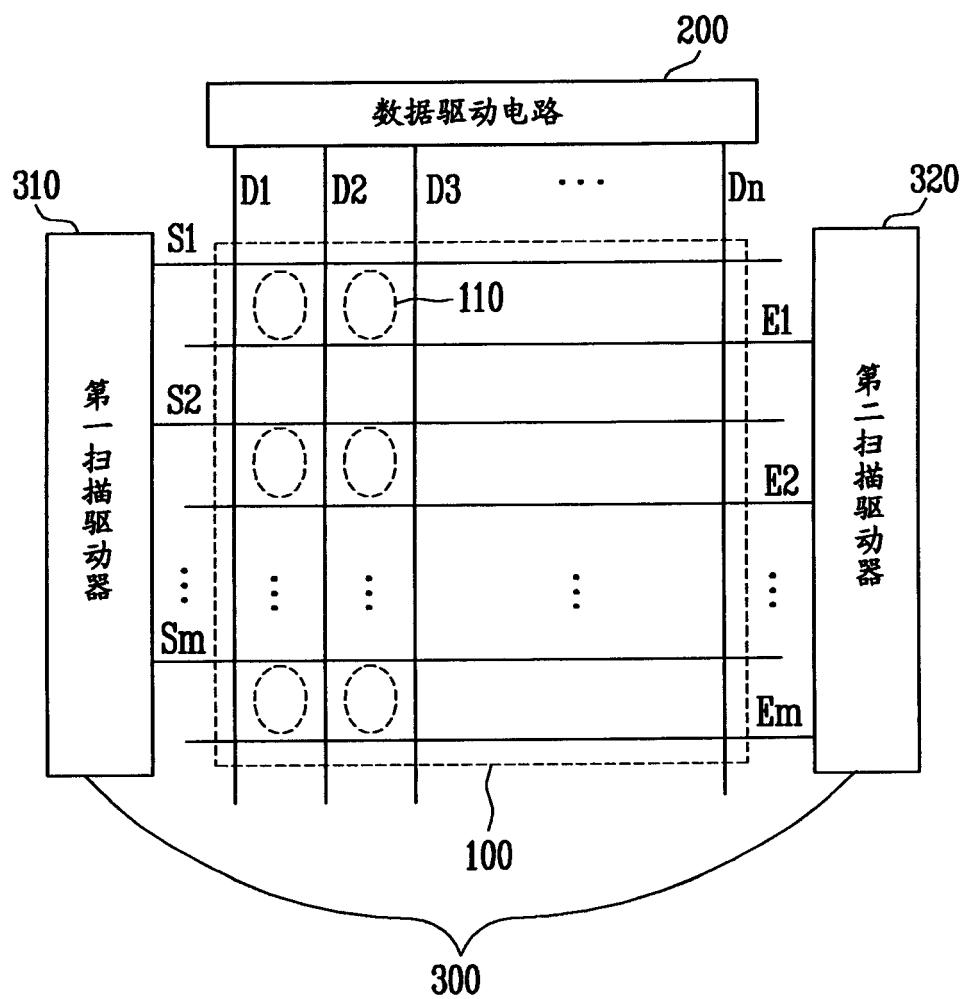

- 图 4 是显示根据一个实施例的有机发光显示器的框图；

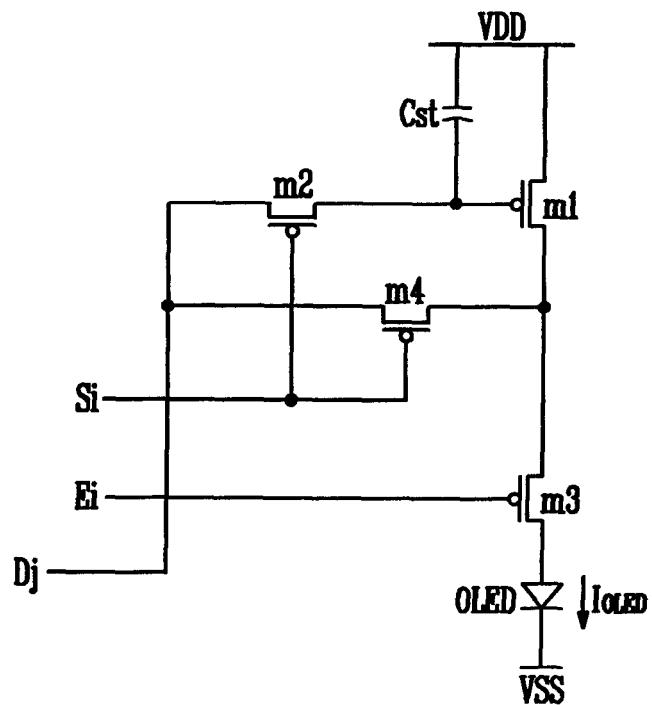

- 图 5 是显示图 4 所示的有机发光显示器的每个像素区域处布置的像素电路的示例的电路图；

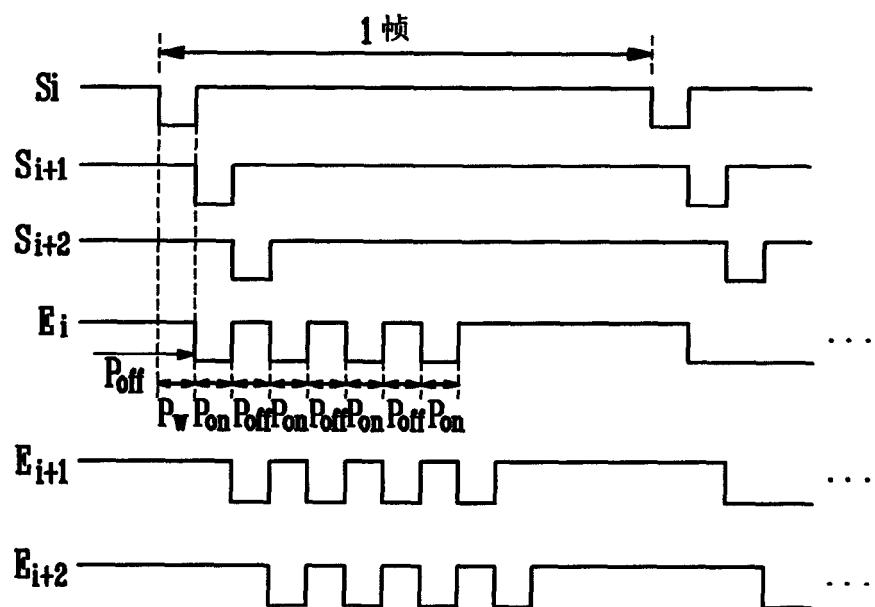

- 图 6 是提供给图 5 所示的像素电路的选择信号和发射信号的波形图；

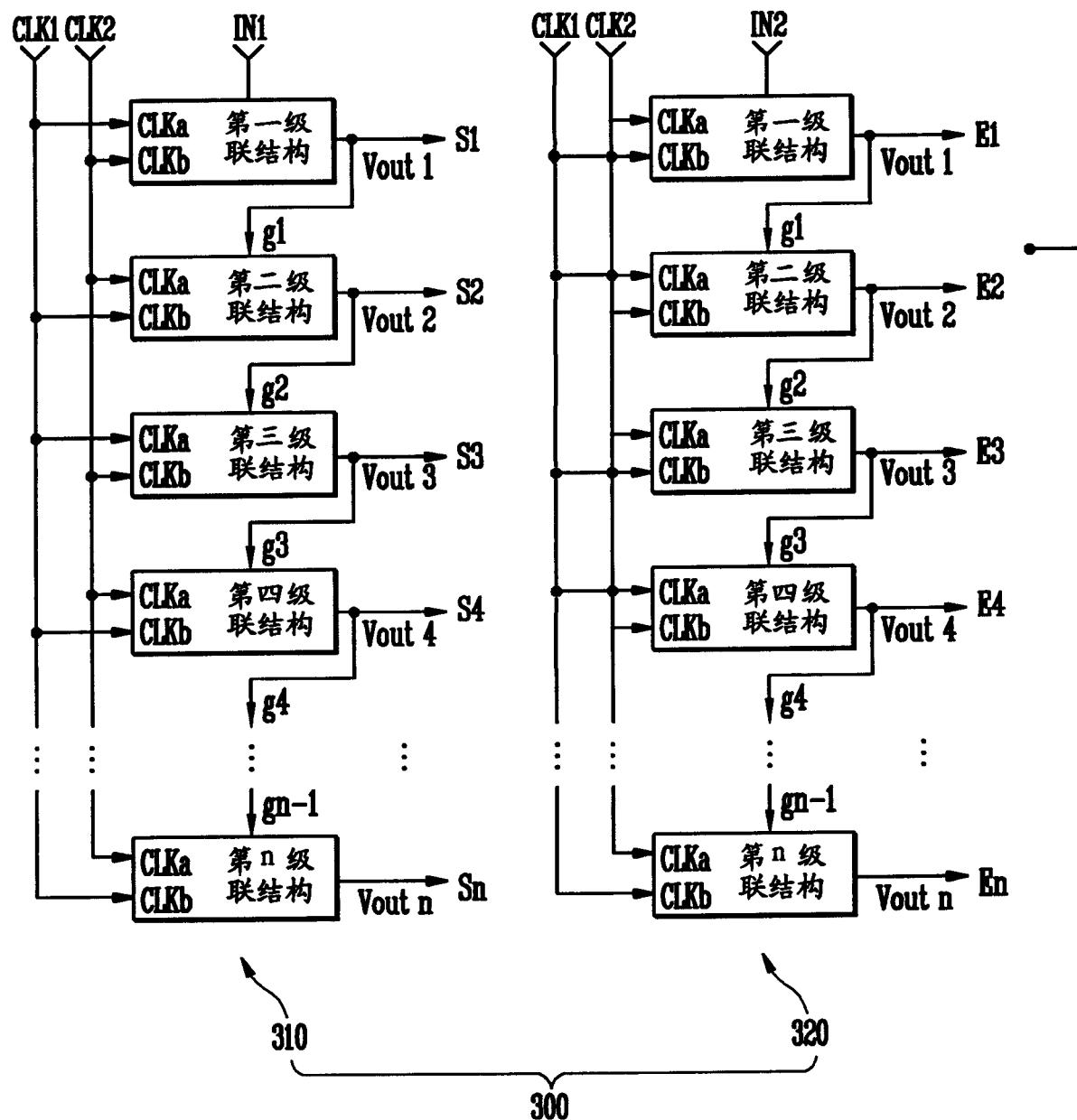

- 图 7 是显示根据一个实施例的扫描驱动电路的构造的框图；

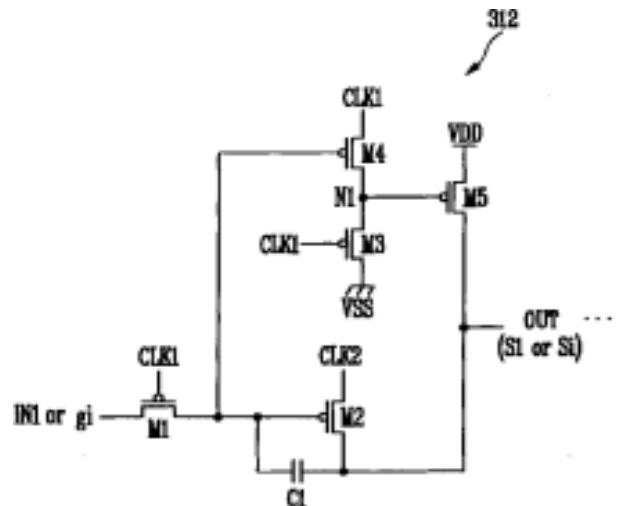

- 图 8 是图 7 所示的扫描驱动电路中的级联结构的电路图； 和

- 图 9 是图 8 所示的级联结构的输入/输出波形图。

### 具体实施方式

以下，将参考附图描述本发明的特定实施例。这里，当第一元件连接至第二元件时，第一元件可直接连接至第二元件或者可经过第三元件间接地连接至第二元件。此外，为了清晰，省略了不相关的元件。此外，相同的标号始终表示相同的元件。

图 4 是显示根据一个实施例的有机发光显示器的框图。

如图 4 所示，根据本发明的一个实施例的有机发光显示器包括有机发光显示面板（以下称作“显示面板”）100、数据驱动电路 200 和扫描驱动电路 300。扫描驱动电路 300 包括第一扫描驱动器 310 和第二扫描驱动器 320。第一扫描驱动器 310 提供选择信号。第二扫描驱动器 320 提供发射信号。

显示面板 100 包括多条数据线 D1 至 Dn、多条信号线 S1 至 Sm 和 E1 至 Em 以及多个像素电路 110。所述多条数据线 D1 至 Dn 按行方向布置。所述

多条信号线 S1 至 Sm 和 E1 至 Em 按列方向布置。所述多个像素电路 110 按矩阵模式布置。

这里，信号线 S1 至 Sm 和 E1 至 Em 包括用于传送选择信号以选择像素的多条选择信号线 S1 至 Sm 和用于传送发射信号以控制有机发光二极管的发射时间段的多条发射信号线 E1 至 Em。

此外，像素电路 110 形成在由数据线 D1 至 Dn、选择信号线 S1 至 Sm 和发射信号线 E1 至 Em 限定的像素区域中。

数据驱动电路 200 将数据电流  $I_{DATA}$  施加到数据线 D1 至 Dn。扫描驱动电路 300 的第一扫描驱动器 310 依次将用于选择像素电路 110 的选择信号施加到选择信号线 S1 至 Sm。此外，第二扫描驱动器 320 将用于控制像素电路 110 的发光的发射信号施加到发射信号线 E1 至 Em。

图 5 是显示图 4 所示的像素电路的示例的电路图。然而，为了帮助理解像素电路，图 5 只显示了连接至第 j 数据线 Dj 及第 i 信号线 Si 和 Ei 的像素电路。

如图 5 所示，根据一个实施例的像素电路包括有机发光二极管 OLED、晶体管 m1 至 m4 和电容器 Cst。这里，虽然 PMOS 晶体管用于晶体管 m1 至 m4 的每个，但是也可用 NMOS 和 CMOS 来实现。

第一晶体管 m1 连接在电源 VDD 和有机发光二极管 OLED 之间，并控制通过有机发光二极管 OLED 的电流。详细地讲，第一晶体管 m1 的源极与电源 VDD 连接，其漏极通过第三晶体管 m3 与有机发光二极管 OLED 的阴极连接。

此外，响应来自选择信号线 Si 的选择信号，第二晶体管 m2 将来自数据线 Dj 的电压传递到第一晶体管 m1 的栅极。第四晶体管 m4 响应该选择信号将第一晶体管 m1 连接成二极管。

而且，电容器 Cst 连接在第一晶体管 m1 的栅极和源极之间，并被以与向数据线 Dj 提供数据电流  $I_{DATA}$  的第一晶体管 m1 的栅极电压相应的电压充电。第三晶体管 m3 响应来自发射信号线 Ei 的发射信号将流过第一晶体管 m1 的电流传递到有机发光二极管 OLED。

图 6 是提供给图 5 所示的像素电路的选择信号和发射信号的波形图。

如图 6 所示，用于导通第二晶体管 m2 和第四晶体管 m4 的选择信号被依次施加到选择信号线 Si、Si+1 和 Si+2。当第二晶体管 m2 和第四晶体管 m4

导通时，电容器 Cst 在第一晶体管 m1 被第二晶体管 m2 和 m4 连接成作为二极管的同时响应第一晶体管 m1 向数据线 D1 至 Dn 提供数据电流  $I_{DATA}$  而被以与第一晶体管 m1 的栅极电压相应的电压充电。因此，在提供数据电流  $I_{DATA}$  的同时，电容器 Cst 存储与第一晶体管 m1 的栅极电压相应的电压。

在存储电荷之后，去除选择信号 Si 并施加发射信号 Ei。相应地，第二晶体管 m2 和第四晶体管 m4 截止，第三晶体管 m3 导通。由于电容器 Cst 保持第一晶体管 m1 的栅极电压，所以数据电流  $I_{DATA}$  通过第一晶体管 m1 和第三晶体管 m3 流至 OLED。

在一些实施例中，可以以改变电平的方式在一帧时间的其余时间期间将发射信号施加到发射信号线 Ei、Ei+1 和 Ei+2。例如，如图 6 所示，低电平和高电平可被依次施加到信号线 Ei、Ei+1 和 Ei+2。

在该实施例中，当施加到发射信号线 Ei、Ei+1 和 Ei+2 的发射信号具有低电平时，第三晶体管 m3 导通，因而来自第一晶体管 m1 的电流被提供给有机发光二极管 OLED，其结果是有机发光二极管 OLED 响应该电流发光。与之相反，当发射信号为高电平时，第三晶体管 m3 截止，因而从第一晶体管 m1 施加的电流不被提供给有机发光二极管 OLED，其结果是有机发光二极管 OLED 不发光。

因此，在记录时间段 Pw 期间，发射信号线 Ei 为高从而第三晶体管 m3 截止，选择信号 Si 为低从而第一晶体管 m1 连接成二极管，并且电容器 Cst 被以与来自数据线 D1 至 Dn 的数据电流  $I_{DATA}$  相应的电压充电。

接下来，在开启时间段 Pon 期间，发射信号线 Ei 为低从而来自第一晶体管 m1 的电流被施加到 OLED，OLED 响应施加的电流发光。接下来，在关闭时间段 Poff 期间，发射信号线 Ei 为高从而 OLED 基本上不接收电流，于是变暗。如图 6 所示，开启时间段 Pon 和关闭时间段 Poff 可依次交替。在一些实施例中，开启时间段 Pon 和关闭时间段 Poff 的持续时间可不相等。在一些实施例中，在整个帧时间段中可持续交替开启时间段 Pon 和关闭时间段 Poff。在这样的实施例中，可通过控制发射信号 Ei 的占空比来调节 OLED 的发光时间的部分。例如，发射信号 Ei 的占空比大约为 50%，对应于 OLED 在大约 50% 的帧时间段发光。

从图 4 可看出，分别通过第一扫描驱动器 310 和第二扫描驱动器 320 将选择信号和发射信号提供给面板。将解释根据一些实施例的扫描驱动电路的

构造和操作。在这些实施例中，选择信号和发射信号具有图 6 所示的波形，然而也可使用其它波形和对应的实施例。

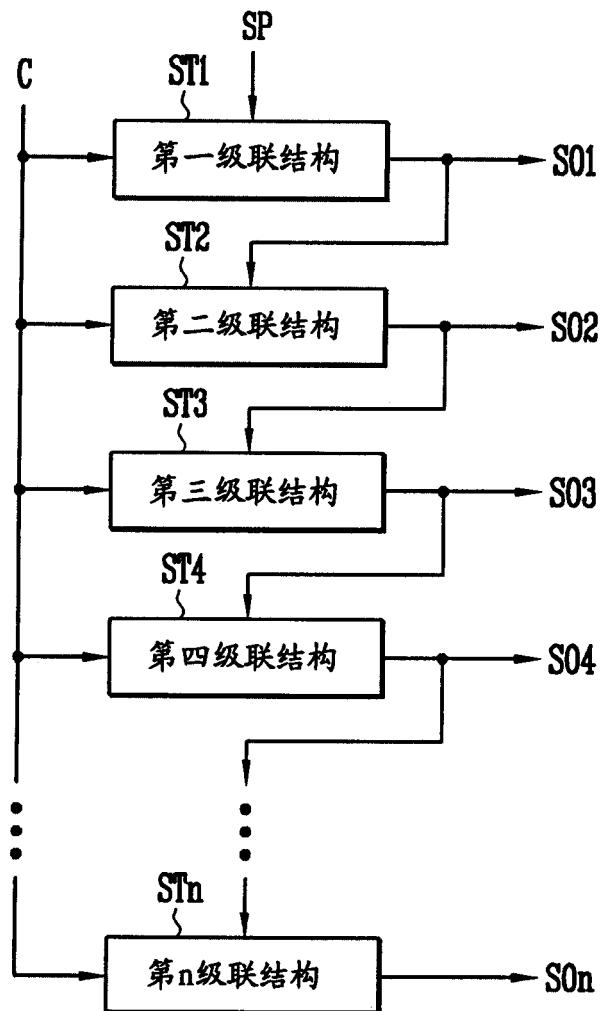

图 7 是显示扫描驱动电路的实施例的框图。如前所注意到的，扫描驱动电路 300 包括第一扫描驱动器 310 和第二扫描驱动器 320。第一扫描驱动器 310 输出用于驱动  $m \times n$  像素阵列的选择信号。第二扫描驱动器 320 输出发射信号。第一扫描驱动器 310 包括与第一输入信号 IN1 线连接的第一  $n$  个级联结构。第二扫描驱动器 320 包括与第二输入信号 IN2 线连接的第二  $n$  个级联结构。

第一  $n$  个级联结构的第一输出线与像素阵列中的第一  $n$  行线 S1 至 Sn 连接，并将选择信号提供给像素行。第二  $n$  个级联结构的第二输出线与像素阵列中的第二  $n$  行线 E1 至 En 连接，并将发射信号提供给像素行。

这里，第一输入信号 IN1 被提供给第一扫描驱动器 310 中的第一级联结构，第二输入信号 IN2 被提供给第二扫描驱动器 320 中的第一级联结构。第一级联结构至第( $n-1$ )级联结构的输出信号被提供给各下一级联结构作为输入信号。

此外，第一扫描驱动器 310 的每个级联结构包括第一时钟端 CLKa 和第二时钟端 CLKb。相位相反的第一时钟信号 CLK1 和第二时钟信号 CLK2 被提供给第一时钟端 CLKa 和第二时钟端 CLKb。第一时钟信号 CLK1 被提供给第一扫描驱动器 310 中的奇数级联结构的第一时钟端 CLKa，第二时钟信号 CLK2 被提供给奇数级联结构的第二时钟端 CLKb。与之相反，第二时钟信号 CLK2 被提供给偶数级联结构的第一时钟端 CLKa，第一时钟信号 CLK1 被提供给偶数级联结构的第二时钟端 CLKb。

每个级联结构接收第一输入信号 IN1 或前一级联结构的输出电压 gi 以及第一时钟信号 CLK1 和第二时钟信号 CLK2。相应地，每个级联结构通过输出线依次输出低电平信号。

类似地，第二扫描驱动器 320 的每个级联结构包括第一时钟端 CLKa 和第二时钟端 CLKb。相位相反的第一时钟信号 CLK1 和第二时钟信号 CLK2 被提供给第一时钟端 CLKa 和第二时钟端 CLKb。第二时钟信号 CLK2 被提供给第二扫描驱动器 320 中的奇数级联结构的第一时钟端 CLKa，第一时钟信号 CLK1 被提供给奇数级联结构的第二时钟端 CLKb。与之相反，第一时钟信号 CLK1 被提供给偶数级联结构的第一时钟端 CLKa，第二时钟信号 CLK2 被提

供给偶数级联结构的第二时钟端 CLKb。

每个级联结构接收第一输入信号 IN2 或前一级联结构的输出电压  $g_i$  以及第一时钟信号 CLK1 和第二时钟信号 CLK2。相应地，每个级联结构以发射信号在低电平和高电平之间交替的方式通过输出线依次输出发射信号。

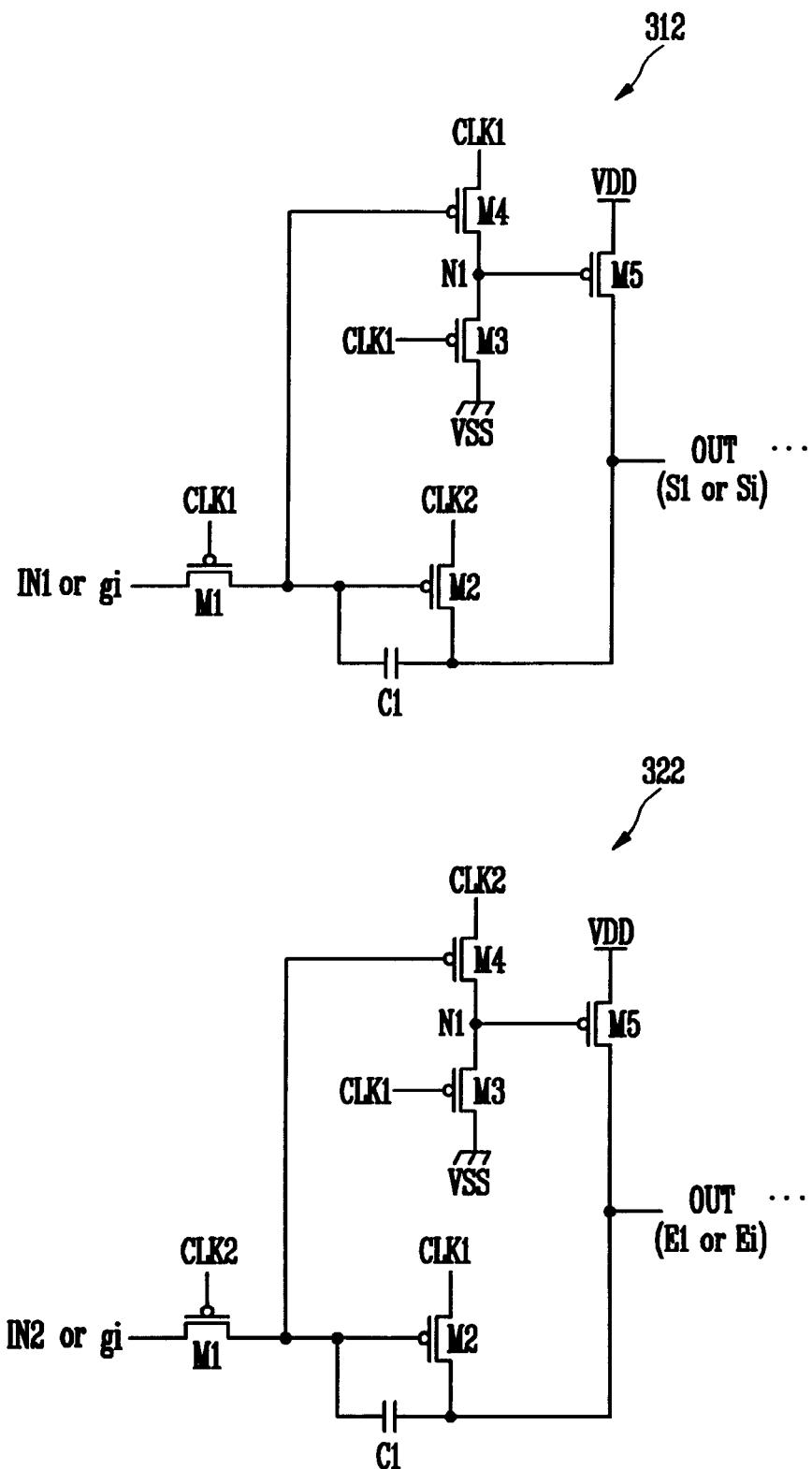

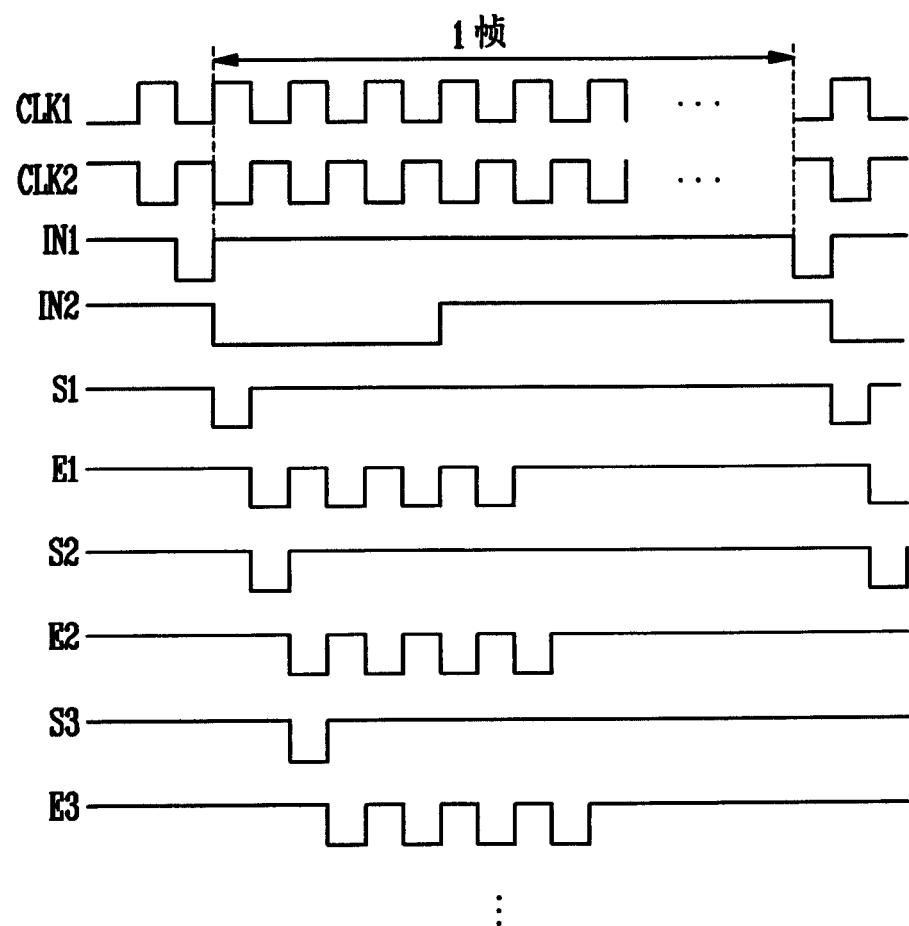

图 8 是图 7 所示的扫描驱动电路中的级联结构的电路图。图 8 显示了第一扫描驱动器的奇数级联结构 312 的详细电路布置和第二扫描驱动器的奇数级联结构 322 的详细电路布置。图 9 是图 8 所示的级联结构的输入/输出波形图。

参考图 8 和图 9，输入时钟信号 CLK1 和 CLK2 的一个周期分为第一时间段和第二时间段。第一扫描驱动器的奇数级联结构 312 和第二扫描驱动器的奇数级联结构 322 的每个在第一时间段期间执行预充电操作。奇数级联结构 312 和 322 在第二时间段期间执行赋值 (evaluation) 操作，赋值操作使低电平脉冲被移位半个时钟信号周期并被输出。奇数级联结构 312 和 322 的每个在预充电时间段输出高电平信号，并输出与在赋值时间段期间接收的输入相应的信号。

此外，通过将奇数级联结构的赋值时间段布置成与偶数级联结构的预充电时间段一致，低电平信号在所有的级联结构中依次传送，其中，传送发生在与该时钟的半个周期相应的时间。

以下，将通过参考图 8 所示的奇数级联结构的电路布置来详细解释奇数级联结构 312 的操作。包括第一扫描驱动器的偶数级联结构的其它级联结构以及第二扫描驱动器的级联结构具有类似的结构。

现在将描述作为包括在所述级联结构中的晶体管的示例的 PMOS 薄膜晶体管。然而，本发明的实施例不限于此。例如，可另外使用或替换使用 NMOS 晶体管。

参考图 8，奇数级联结构 312 包括第一 PMOS 晶体管 M1、第二 PMOS 晶体管 M2、第三 PMOS 晶体管 M3、第四 PMOS 晶体管 M4 和第五 PMOS 晶体管 M5。第一 PMOS 晶体管 M1 接收前一级联结构的输出电压  $g_i$  或第一输入信号 IN1。第一 PMOS 晶体管 M1 的栅极端与第一时钟端 CLK1 连接。第二 PMOS 晶体管 M2 与第二时钟端 CLK2 和输出线 OUT 连接，第二 PMOS 晶体管 M2 的栅极端与第一 PMOS 晶体管 M1 的输出端连接。第三 PMOS 晶体管 M3 连接在第二电源 VSS 和第一节点 N1 之间，具有与第一时钟端 CLK1

连接的栅极端。第四 PMOS 晶体管 M4 连接在第一时钟端和第一节点 N1 之间，具有与第一 PMOS 晶体管 M1 的输出端连接的栅极端。第五 PMOS 晶体管 M5 连接在第一电源 VDD 和输出线 OUT 之间，具有与第一节点 N1 连接的栅极端。奇数级联结构 312 还包括第一电容器 C1，第一电容器 C1 连接在第一 PMOS 晶体管 M1 的输出端和输出线 OUT 之间。

如所示，第一扫描驱动器的奇数级联结构 312 具有提供给第一时钟端的第一时钟信号 CLK1 和提供给第二时钟端的第二时钟信号 CLK2。第二扫描驱动器的奇数级联结构 322 具有提供给第一时钟端的第二时钟信号 CLK2 和提供给第二时钟端的第一时钟信号 CLK1。

与之相反，当所述级联结构为第一扫描驱动器的偶数级联结构时，第一时钟信号 CLK1 被提供给第二时钟端，第二时钟信号 CLK2 被提供给第一时钟端。此外，当所述级联结构为第二扫描驱动器的偶数级联结构时，第一时钟信号 CLK1 被提供给第一时钟端，第二时钟信号 CLK2 被提供给第二时钟端。

此外，负的电源电压可被提供给第二电源 VSS。如图 8 所示，可将第二电源 VSS 接地。

每个级联结构包括传送单元、反相单元和缓冲单元。在图 8 的实施例中，传送单元包括第一 PMOS 晶体管 M1、第二 PMOS 晶体管 M2 和第一电容器 C1。反相单元包括第一 PMOS 晶体管 M1、第三 PMOS 晶体管 M3 和第四 PMOS 晶体管 M4。

假设所述级联结构为第一扫描驱动器的奇数级联结构 312，则当第一时钟信号 CLK1 具有低电平且第二时钟信号 CLK2 具有高电平时的时间段为预充电时间段。当第一时钟信号 CLK1 具有高电平且第二时钟信号 CLK2 具有低电平时的时间段为赋值时间段。第一扫描驱动器的奇数级联结构 312 在预充电时间段期间输出高电平信号，在赋值时间段期间输出与在预充电时间段期间接收的输入相应的信号。

与之相反，假设所述级联结构为第二扫描驱动器的奇数级联结构 322，则当第一时钟信号 CLK1 具有高电平且第二时钟信号 CLK2 具有低电平时的时间段变成预充电时间段。当第一时钟信号 CLK1 具有低电平且第二时钟信号 CLK2 具有高电平时的时间段变成赋值时间段。第二扫描驱动器的奇数级联结构 322 在预充电时间段期间输出高电平信号，在赋值时间段期间输出与

在预充电时间段期间接收的输入相应的信号。

将参考图 8 和图 9 解释第一扫描驱动器的奇数级联结构 312 的操作。首先，在预充电时间段期间，低电平的第一时钟信号 CLK1 和高电平的第二时钟信号 CLK2 被输入。因此，第一晶体管 M1 和第三晶体管 M3 导通，由此输入信号 IN1 被传递到第二晶体管 M2 和第四晶体管 M4 的栅极端。

因此，由于前一级联结构的输出电压或输入信号 IN1 作为输入信号被存储在第一电容器 C1 中，并且第一节点 N1 被充有第一时钟信号 CLK1 或来自第二电源 VSS 的低电平信号，所以第五晶体管 M5 导通，其结果是高电平的第一电源 VDD 被输出到输出端 OUT。即，在预充电时间段期间，所述级联结构的缓冲单元的输出为高电平。

此外，在赋值时间段期间，高电平的第一时钟信号 CLK1 和低电平的第二时钟信号 CLK2 被输入。因此，第一晶体管 M1 截止，因而阻止了输入信号 IN1，相应地，第三晶体管 M3 截止。

在赋值时间段期间，电容器 C1 保持在预充电时间段期间充电的输入信号的电平。当在预充电时间段期间接收的输入电压为高电平时，第四晶体管 M4 在赋值时间段期间保持截止，缓冲单元继续输出高电平信号。

与之相反，当在预充电时间段期间接收的输入电压为低电平时，第四晶体管 M4 在赋值时间段期间为导通，节点 N1 连接至第一时钟信号 CLK1。此外，第二晶体管 M2 导通，缓冲单元的输出 OUT 连接到第二时钟信号 CLK2。

总之，在赋值时间段期间，当在预充电时间段期间接收的信号，即，前一级联结构的输出电压或输入信号 IN1 为低电平时，所述级联结构输出低电平信号。类似地，当在预充电时间段期间接收的信号为高电平时，所述级联结构在赋值时间段期间输出高电平信号。

因此，第一扫描驱动器的每个级联结构接收第一输入信号 IN1 或前一级联结构的输出电压  $g_i$  以及第一时钟信号 CLK1 和第二时钟信号 CLK2。根据这些输入信号，每个级联结构在第一时间段期间执行预充电操作，在第二时间段期间执行赋值操作。由于所述级联结构串联，所以低电平脉冲被各后一级联结构移位输入时钟 CLK1 和 CLK2 的半个周期并被输出。因此，通过每个级联结构的输出线依次输出低电平信号。因此将所述级联结构的输出线构造为用作所述阵列的像素行的选择信号。

根据图 9 中的时序信号进行描述的图 8 所示的第二扫描驱动器的奇数级

联结构 322 的电路布置与上述第一扫描驱动器的奇数级联结构 312 的电路布置相同，因而省略其详细描述。

在第二扫描驱动器的奇数级联结构 322 中，第二时钟信号 CLK2 被提供给第一时钟端，第一时钟信号 CLK1 被提供给第二时钟端。即，信号/输入对应关系与第一扫描驱动器的奇数级联结构的信号/输入对应关系相反。

因此，第一扫描驱动器和第二扫描驱动器的预充电时间段和赋值时间段重叠。即，输入到第一扫描驱动器的偶数级联结构的第一时钟端和第二时钟端的时钟信号与输入到第二扫描驱动器的奇数级联结构的第一时钟端和第二时钟端的时钟信号相同。类似地，输入到第一扫描驱动器的奇数级联结构的第一时钟端和第二时钟端的时钟信号与输入到第二扫描驱动器的偶数级联结构的第一时钟端和第二时钟端的时钟信号相同。因此，当第一扫描驱动器的奇数级联结构输出低电平信号时，第二扫描驱动器的奇数级联结构输出高电平信号。

此外，如图 9 所示，第二输入信号 IN2 在与时钟信号的不同于将第一输入信号 IN1 提供给第一扫描驱动器的几个时间段相应的时间段期间被提供给第二扫描驱动器。

因此，响应第二输入信号 IN2 并根据上述操作，第二扫描驱动器的每个级联结构依次输出低电平和高电平序列。将所述级联结构的输出信号构造为用作将被提供给显示阵列的像素行的发射信号。

在一些实施例中，可在整个帧时间段内施加第二输入信号 IN2。在这样的实施例中，可通过控制第一时钟信号 CLK1 和第二时钟信号 CLK2 的占空比，相应地，发射信号 Ei 的占空比来调节 OLED 的发光时间。例如，大约为 50% 的发射信号的占空比对应于 OLED 在大约 50% 的帧时间段发光。

从以上描述中显而易见的是，根据这些实施例的扫描驱动电路，提供选择信号的第一扫描驱动器和提供发射信号的第二扫描驱动器使得在数据帧时间段期间至少施加发射信号一次以防止当恒定电流被传统的像素吸收时可发生的像素的劣化。

此外，由于所述级联结构电路基本上没有静态电流，所以所述级联结构电路具有最小的功耗。类似地，当驱动诸如像素行的纯容性负载时，基本上没有静态输出电流，相应地，功耗被最小化。因此，对于大的容性负载，操作速度可被最优化，而不会显著地增加功耗。

---

虽然已显示和描述了本发明的几个实施例，但是本领域的技术人员应该理解，在不脱离本发明的原理和精神的情况下，可对该实施例进行改变。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

|                |                                                                                   |         |            |

|----------------|-----------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 扫描驱动电路和使用该扫描驱动电路的有机发光显示器                                                          |         |            |

| 公开(公告)号        | <a href="#">CN1937020A</a>                                                        | 公开(公告)日 | 2007-03-28 |

| 申请号            | CN200610139245.8                                                                  | 申请日     | 2006-09-20 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                       |         |            |

| 申请(专利权)人(译)    | 三星SDI株式会社                                                                         |         |            |

| 当前申请(专利权)人(译)  | 三星SDI株式会社                                                                         |         |            |

| [标]发明人         | 申东蓉                                                                               |         |            |

| 发明人            | 申东蓉                                                                               |         |            |

| IPC分类号         | G09G3/30 G09G3/20 H05B33/08 H05B33/14                                             |         |            |

| CPC分类号         | G09G2300/0842 G09G3/325 G09G3/20 G09G2310/0286 G09G2330/021 G11C19/184 G09G3/3266 |         |            |

| 优先权            | 1020050087425 2005-09-20 KR                                                       |         |            |

| 其他公开文献         | CN100541577C                                                                      |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>                                    |         |            |

#### 摘要(译)

公开了一种扫描驱动电路和使用该扫描驱动电路的有机发光显示器。具有多个第一级联结构的第一扫描驱动器依次输出选择信号，具有多个第二级联结构的第二扫描驱动器依次输出发射信号。所述第一级联结构和所述第二级联结构的每个被构造为具有基本为零的静态电流，并且操作速度可被最优化，而不会显著地增加功耗。