[19] 中华人民共和国国家知识产权局

[12] 发明专利申请公布说明书

[21] 申请号 200610125721.0

[51] Int. Cl.

*H01L 27/32 (2006.01)*

*H01L 21/82 (2006.01)*

*H01L 21/768 (2006.01)*

[43] 公开日 2007 年 1 月 17 日

[11] 公开号 CN 1897299A

[22] 申请日 2006.6.22

[21] 申请号 200610125721.0

[30] 优先权

[32] 2005.6.22 [33] KR [31] 54165/05

[71] 申请人 三星 SDI 株式会社

地址 韩国京畿道

[72] 发明人 黄义勋 李相杰

[74] 专利代理机构 北京市柳沈律师事务所

代理人 张 波

权利要求书 5 页 说明书 15 页 附图 28 页

[54] 发明名称

有机发光显示装置及其制造方法

[57] 摘要

本发明提供一种有机发光显示装置(OLED)及其制造方法。在同时形成金属互连和栅极电极时或在形成第一电极时，形成用于电连接元件的互连。从而，能减少使用掩模的次数，从而缩短总体制造工艺且降低成本。

1. 一种有机发光显示装置(OLED)，包括：

具有第一薄膜晶体管(TFT)、第二 TFT、以及金属互连的基板；

设置于具有所述第一 TFT、所述第二 TFT、以及所述金属互连的所述基板上的平坦化层；

设置于所述平坦化层的预定区域中从而暴露所述第一 TFT 的第一源极和漏极区域、所述第二 TFT 的第二源极和漏极区域、以及所述金属互连的预定区域的接触孔；以及

用于通过所述接触孔电连接所述金属互连、所述第一源极和漏极区域、以及所述第二源极和漏极区域的互连。

2. 根据权利要求 1 所述的 OLED，还包括：

连接到所述第一源极和漏极区域以及所述第二源极和漏极区域之一的第一电极；

设置于所述第一电极上的有机层；以及

设置于所述有机层上的第二电极。

3. 根据权利要求 2 所述的 OLED，其中所述第一电极包括反射层和透明层。

4. 根据权利要求 3 所述的 OLED，其中所述反射层由选自含有铝(Al)、银(Ag)、以及它们的合金的组的一种形成。

5. 根据权利要求 3 所述的 OLED，其中所述透明层由氧化铟锡(ITO)和氧化铟锌(IZO)之一形成。

6. 根据权利要求 1 所述的 OLED，其中所述互连设置在与所述第一电极相同的层上且由与所述第一电极相同的材料形成。

7. 根据权利要求 1 所述的 OLED，其中所述第一 TFT 的第一栅极电极、所述第二 TFT 的第二栅极电极、以及所述金属互连设置在相同层上。

8. 根据权利要求 7 所述的 OLED，其中所述第一栅极电极、所述第二栅极电极、以及所述金属互连由选自含有钼(Mo)、钨(W)、铝(Al)、以及它们的合金的组的一种形成。

9. 根据权利要求 1 所述的 OLED，其中所述第一 TFT 包括：

设置于所述基板上的第一栅极电极；

设置于所述第一栅极电极上的栅绝缘层；以及

设置于所述栅绝缘层上的第一半导体层，对应于所述第一栅极电极，且包括所述第一源极和漏极区域以及第一沟道区域，且

其中所述第二 TFT 包括：

设置于所述基板上的第二栅极电极；

设置于所述第二栅极电极上的所述栅绝缘层；以及

设置于所述栅绝缘层上的第二半导体层，对应于所述第二栅极电极，且包括所述第二源极和漏极区域以及第二沟道区域。

10. 根据权利要求 1 所述的 OLED，其中所述第一 TFT 包括：

设置于所述基板上且包括所述第一源极和漏极区域以及第一沟道区域的第一半导体层；

设置于所述第一半导体层上的栅绝缘层；以及

设置于所述栅绝缘层上且对应于所述第一沟道区域的第一栅极电极，且其中所述第二 TFT 包括：

设置于所述基板上且包括所述第二源极和漏极区域以及第二沟道区域的第二半导体层；

设置于所述第二半导体层上的栅绝缘层；以及

设置于所述栅绝缘层上且对应于所述第二沟道区域的第二栅极电极。

11. 根据权利要求 9 或 10 所述的 OLED，还包括设置于所述第一和第二漏极区域与所述第一沟道区域之间的轻掺杂漏极(LDD)区域。

12. 一种有机发光显示装置(OLED)，包括：

设置于基板上的金属互连、第一栅极电极、以及第二栅极电极；

设置于所述金属互连、所述第一栅极电极、以及所述第二栅极电极上的栅绝缘层；

设置于所述栅绝缘层上的第一半导体层和第二半导体层，所述第一半导体层对应于所述第一栅极电极且包括第一源极和漏极区域以及第一沟道区域，所述第二半导体层对应于所述第二栅极电极且包括第二源极和漏极区域以及第二沟道区域；

设置于所述第一半导体层和所述第二半导体层上的平坦化层；

通过蚀刻所述平坦化层的预定区域形成且暴露所述金属互连、所述第一源极和漏极区域、以及所述第二源极和漏极区域的预定区域的接触孔；

用于通过所述接触孔将所述金属互连与所述第一源极和漏极区域之一连接的第一互连，用于通过所述接触孔将所述第一源极和漏极区域的另一个与所述第二源极和漏极区域之一连接的第二互连，以及通过所述接触孔连接到所述第二源极和漏极区域的另一个的第一电极；

设置于所述第一互连、所述第二互连、以及所述第一电极上并暴露所述第一电极的预定区域的像素定义层；以及

设置于所述第一电极的所述暴露区域上的有机层和第二电极，所述有机层至少包括有机发光层。

13. 根据权利要求 12 所述的 OLED，其中所述金属互连、所述第一栅极电极、以及所述第二栅极电极由相同材料形成。

14. 根据权利要求 12 所述的 OLED，还包括设置于所述第一源极和漏极区域与所述第一沟道区域之间或所述第二源极和漏极区域与所述第二沟道区域之间的 LDD 区域。

15. 根据权利要求 12 所述的 OLED，其中所述第一互连、所述第二互连、以及所述第一电极包括反射层和透明层。

16. 一种有机发光显示装置(OLED)，包括：

设置于基板上的金属互连；

设置于所述金属互连上的缓冲层；

设置于所述缓冲层上的第一半导体层和第二半导体层，所述第一半导体层包括第一源极和漏极区域以及第一沟道区域，所述第二半导体层包括第二源极和漏极区域以及第二沟道区域；

设置于所述第一半导体层和所述第二半导体层上的栅绝缘层；

设置于所述栅绝缘层上且分别对应于所述第一沟道区域和所述第二沟道区域的第一栅极电极和第二栅极电极；

设置于所述第一栅极电极和所述第二栅极电极上的平坦化层；

通过蚀刻所述平坦化层和所述栅绝缘层的预定区域形成来暴露所述第一源极和漏极区域以及所述第二源极和漏极区域的预定区域，以及通过蚀刻所述平坦化层、所述栅绝缘层、以及所述缓冲层的预定区域形成来暴露所述金属互连的预定区域的接触孔；

用于通过所述接触孔将所述金属互连与所述第一源极和漏极区域之一连接的第一互连，用于通过所述接触孔将所述第一源极和漏极区域的另一个

与所述第二源极和漏极区域之一连接的第二互连，以及通过所述接触孔连接到所述第二源极和漏极区域的另一个的第一电极；

设置于所述第一互连、所述第二互连、以及所述第一电极上并暴露所述第一电极的预定区域的像素定义层；以及

设置于所述第一电极的所述暴露区域上的有机层和第二电极，所述有机层至少包括有机发光层。

17. 根据权利要求 16 所述的 OLED，还包括设置于所述第一源极和漏极区域与所述第一沟道区域之间或所述第二源极和漏极区域与所述第二沟道区域之间的 LDD 区域。

18. 根据权利要求 16 所述的 OLED，其中所述第一互连、所述第二互连、以及所述第一电极包括反射层和透明层。

19. 一种制造 OLED 的方法，包括：

在基板上形成金属互连；

在所述金属互连上形成缓冲层；

在所述缓冲层上形成第一半导体层和第二半导体层；

在所述第一半导体层和所述第二半导体层上形成栅绝缘层；

在所述栅绝缘层上形成第一栅极电极和第二栅极电极使得所述第一栅极电极和所述第二栅极电极分别对应于所述第一半导体层的第一沟道区域和所述第二半导体层的第二沟道区域；

在所述第一栅极电极和所述第二栅极电极上形成平坦化层；

通过蚀刻所述平坦化层和所述栅绝缘层的预定区域形成接触孔以暴露所述第一半导体层的第一源极和漏极区域的预定区域以及所述第二半导体层的第二源极和漏极区域的预定区域，且通过蚀刻所述平坦化层、所述栅绝缘层、以及所述缓冲层的预定区域形成接触孔以暴露所述金属互连的预定区域；

在具有所述接触孔的所述基板上形成反射层和透明层；

通过构图所述反射层和所述透明层形成第一互连、第二互连、以及第一电极，所述第一互连用于将所述金属互连与所述第一源极和漏极区域之一连接，所述第二互连用于将所述第一源极和漏极区域的另一个与所述第二源极和漏极区域之一连接，所述第一电极连接到所述第二源极和漏极区域的另一个；

在具有所述第一互连、所述第二互连、以及所述第一电极的所述基板上形成像素定义层以暴露所述第一电极的预定区域；以及

在所述第一电极的所述暴露区域形成至少包括有机发光层的有机层和第二电极。

20. 根据权利要求 19 所述的方法，其中形成所述第一半导体层和所述第二半导体层包括：

在所述缓冲层上形成硅层；

构图所述硅层且形成第一硅图案和第二硅图案；

在所述第一硅图案和所述第二硅图案的预定区域上形成第一光致抗蚀剂图案并以低浓度注入第一杂质离子；

去除所述第一光致抗蚀剂图案，形成第二光致抗蚀剂图案以覆盖比所述第一光致抗蚀剂图案覆盖的所述第一硅图案的区域具有更大宽度的所述第一硅图案且完全覆盖所述第二硅图案，且通过以高浓度将第一杂质离子注入到所述第一硅图案中形成具有第一源极和漏极区域、LDD 区域、以及第一沟道区域的第一半导体层；以及

去除所述第二光致抗蚀剂图案，形成第三光致抗蚀剂图案从而完全覆盖所述第一半导体层且覆盖与所述第二硅图案的被所述第一光致抗蚀剂图案覆盖的区域相同的区域，且通过以高浓度注入第二杂质离子形成具有第二源极和漏极区域以及第二沟道区域的第二半导体层。

21. 根据权利要求 19 所述的方法，其中所述第一杂质离子是 n 型杂质离子。

22. 根据权利要求 19 所述的方法，其中所述第二杂质离子是 p 型杂质离子。

## 有机发光显示装置及其制造方法

### 技术领域

本发明涉及一种有机发光显示装置(OLED)及其制造方法，更特别地，涉及一种OLED，其中当同时形成金属互连和栅极电极时或者当形成第一电极时，形成用于电连接元件的互连，使得通过减少所使用掩模的数量，缩短总体制造工艺并降低制造成本。

### 背景技术

在平板显示装置(FPD)中，有机发光显示装置(OLED)是一种具有宽视角和1ms或更短的快响应速度的发光装置。另外，OLED能以低成本制造为薄的厚度并具有良好的对比度。

在具有置于阳极和阴极之间的有机发光层(EML)的OLED中，从阳极传输的空穴与从阴极传输的电子结合从而形成空穴-电子对，即激子(exciton)。这样，OLED通过激子从激发态转变到基态时产生的能量发光。

通常，由于OLED的每个像素包括薄膜晶体管(TFT)，因此不管OLED的像素数目，提供特定的电流，以致于OLED能以稳定的亮度发光并消耗较小的功率。由于这个原因，OLED特别适于高分辨率大尺寸显示装置。

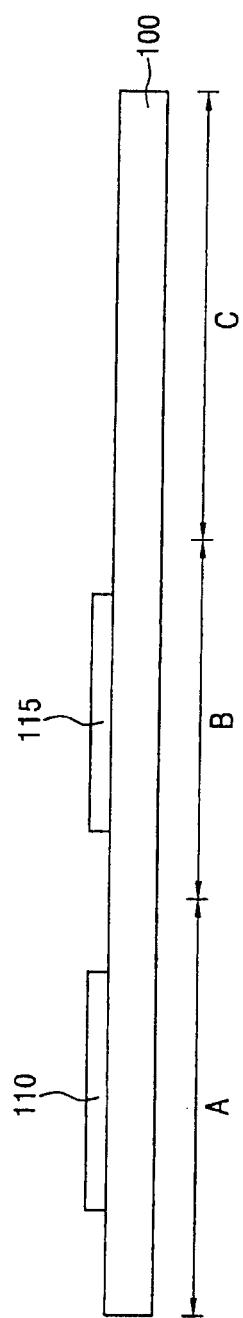

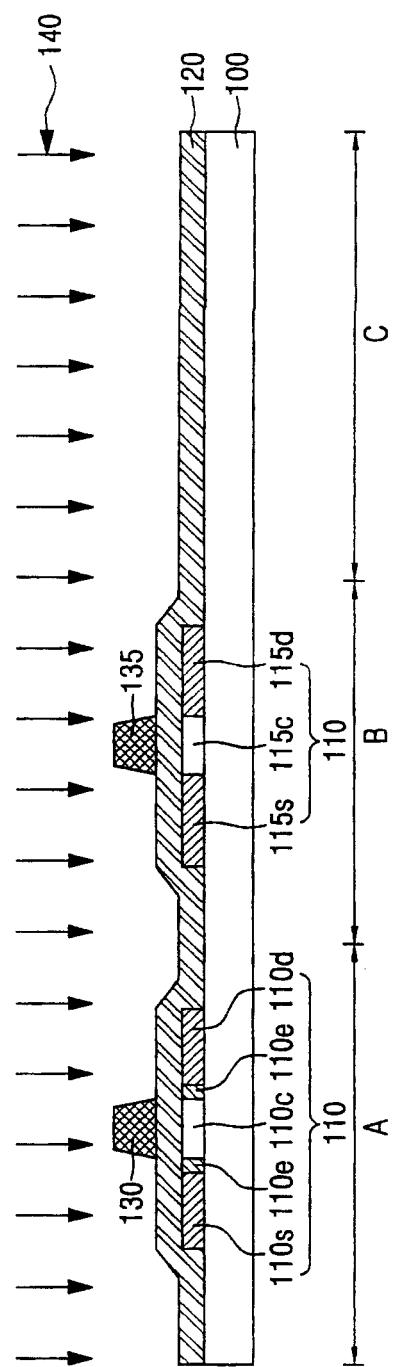

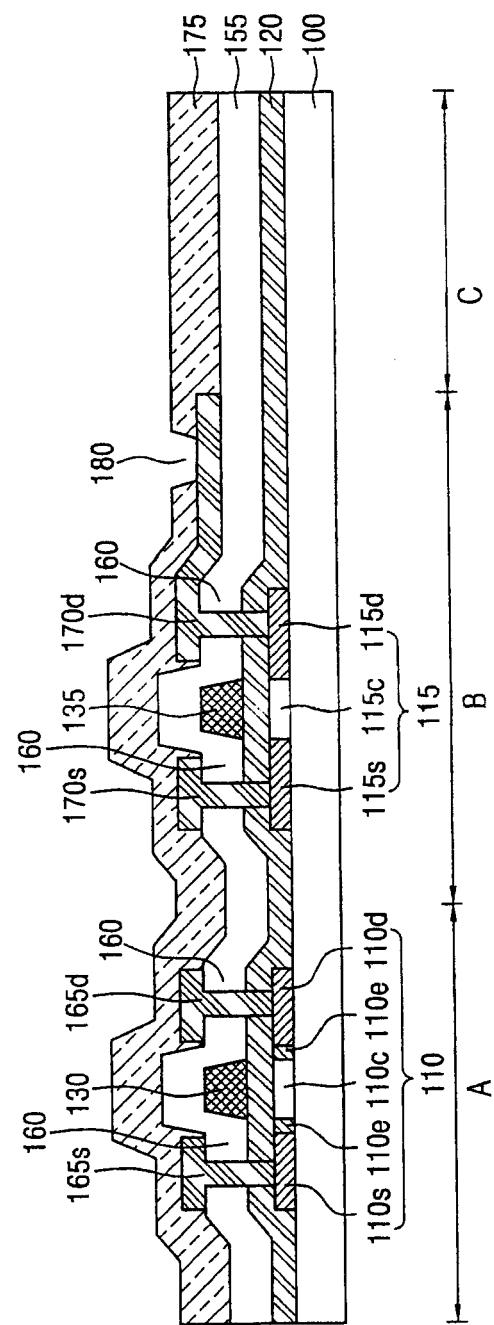

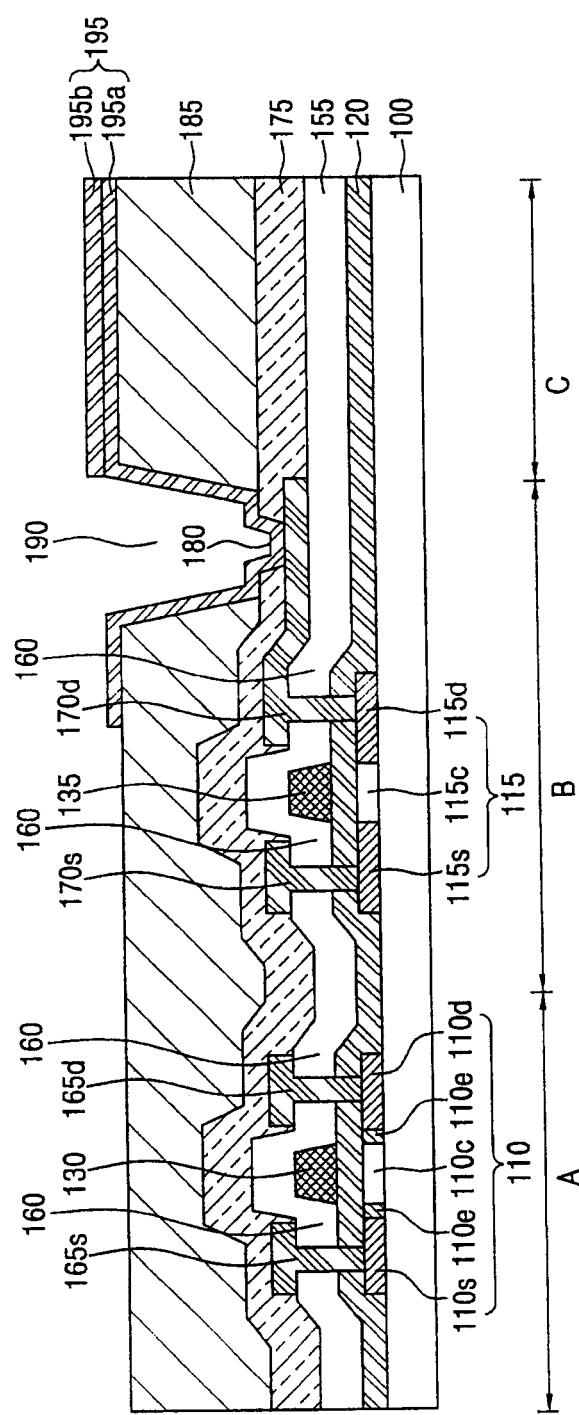

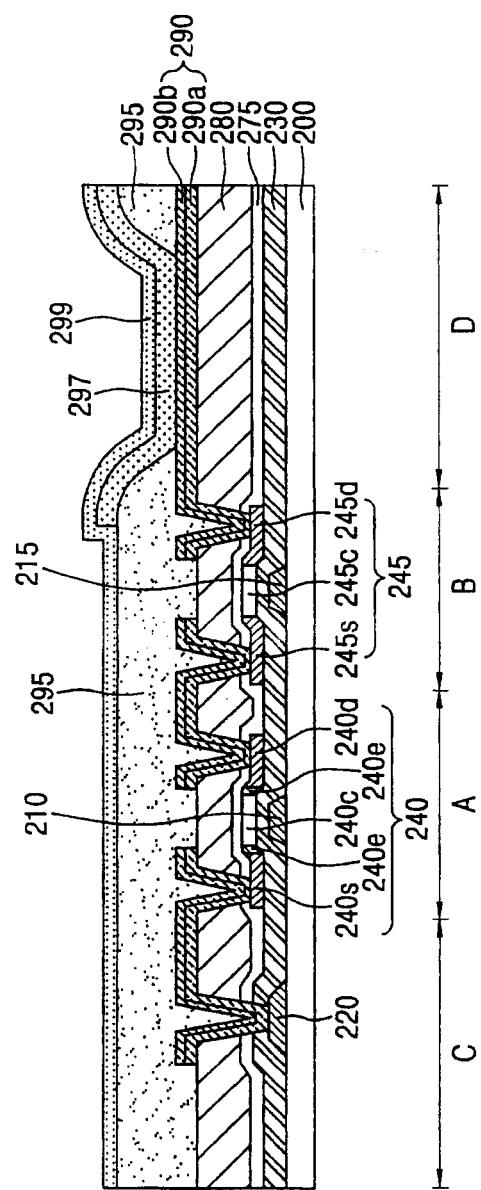

图1A至1K是剖视图，示出具有顶栅型(top gate type)CMOS TFT的传统OLED及其制造方法。

参照图1A，具有顶栅型互补金属氧化物半导体(CMOS)TFT的传统OLED包括基板100，基板100具有第一TFT区域A、第二TFT区域B、以及开口区域C。非晶硅(a-Si)层沉积在基板100上，通过结晶方法结晶，然后利用第一掩模(未示出)图案化，由此形成第一半导体层110和第二半导体层115。

通常，掩模在光刻工艺中用于形成光致抗蚀剂(PR)图案。蚀刻工艺利用所形成的PR图案进行。之后，利用干蚀刻工艺通过灰化工艺(ashing process)去除PR图案。在灰化工艺之后，残余的PR通过PR剥离(stripping)工艺被全部去除。

参照图 1B, 棚绝缘层 120 形成在具有第一和第二半导体层 110 和 115 的基板 100 的整个表面上。在第一和第二 TFT 区域 A 和 B 中在第一和第二半导体层 110 和 115 上利用第二掩模(未示出)形成第一 PR 图案 125。可进行第一杂质注入工艺 127 从而将 n 型杂质离子例如 P 离子、As 离子、Sb 离子或 Bi 离子注入到第一 TFT 区域 A 的第一半导体层 110 中。从而, 第一 TFT 区域 A 的第一半导体层 110 形成包括第一源极和漏极区域 110s 和 110d 以及置于第一源极和漏极区域 110s 和 110d 之间的第一沟道区域 110c 的 NMOS 晶体管。

参照图 1C, 棚极电极材料沉积在第一和第二 TFT 区域 A 和 B 中棚绝缘层 120 上且然后利用第三掩模(未示出)被构图, 由此形成与第一和第二半导体层 110 和 115 的第一沟道区域 110c 和第二沟道区域 115c 对应的第一栅极电极 130 和第二栅极电极 135。在此情形下, 第一栅极电极 130 被构图成比第一 TFT 区域 A 中第一半导体层 110 的第一沟道区域 110c 小的尺寸。第二杂质注入工艺 140 利用第一栅极电极 130 作为掩模进行, 由此在第一半导体层 110 的第一沟道区域 110c 的预定区域中形成轻掺杂漏极(LDD)区域 110e。这样, 第一 TFT 区域 A 的第一半导体层 110 定义掺杂有 n 型杂质离子的第一源极和漏极区域 110s 和 110d、LDD 区域 110e、以及置于 LDD 区域 110e 之间的第一沟道区域 110c。另外, 由于第二杂质注入工艺 140, 第二 TFT 区域 B 的半导体层 115 定义第二源极和漏极区域 115s 和 115d 以及第二沟道区域 115c。

参照图 1D, 利用第四掩模(未示出)形成第二光致抗蚀剂图案 145 以完全覆盖第一 TFT 区域 A 且覆盖第二 TFT 区域 B 中的仅第二栅极电极 135。然后进行第三杂质注入工艺 150 使得 P 型杂质离子例如 B 离子、Al 离子、Ga 离子或 In 离子被注入到第二 TFT 区域 B 的第二源极和漏极区域 115s 和 115d 中。在此情形下, 以比 LDD 区域 110e 更高的浓度将 P 型杂质离子注入到第二 TFT 区域 B 的第二源极和漏极区域 115s 和 115d 中。因此, 第二 TFT 区域 B 的第二半导体层 115 形成包括第二源极和漏极区域 115s 和 115d 以及第二沟道区域 115c 的 PMOS 晶体管。

在此工艺中, 形成具有 NMOS 晶体管和 PMOS 晶体管两者的 CMOS 晶体管。

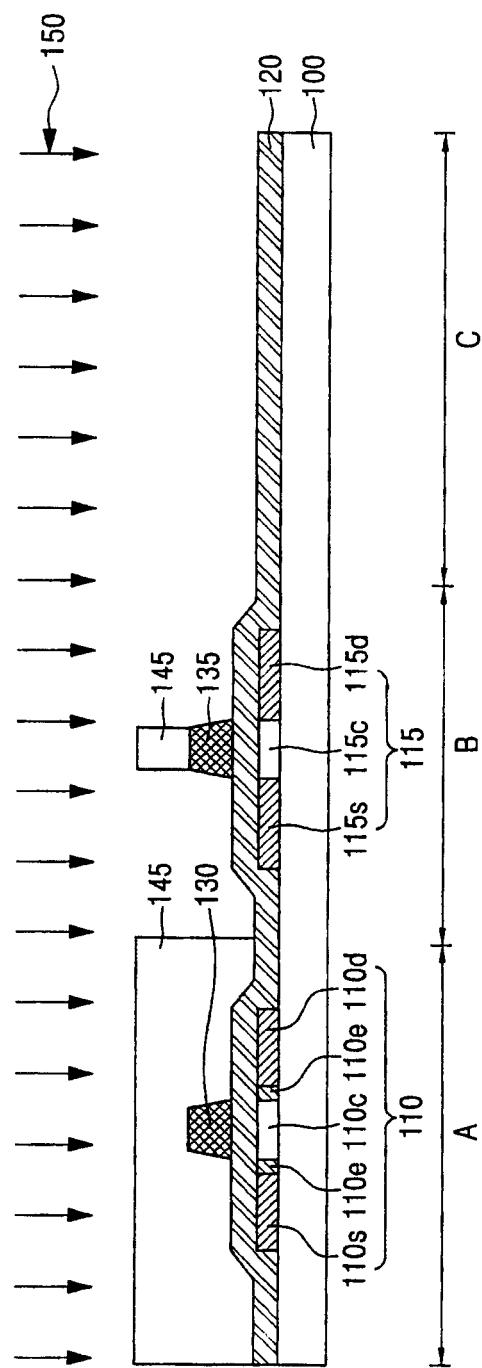

参照图 1E, 层间绝缘层 155 形成在具有第一和第二栅极电极 130 和 135

的基板 100 的整个表面上。利用第五掩模(未示出)在形成于第一和第二 TFT 区域 A 和 B 中的层间绝缘层 155 中形成接触孔 160 以暴露第一和第二源极和漏极区域 110s、110d、115s 和 115d 的部分。

参照图 1F, 源极和漏极电极材料通过层间绝缘层 155 的接触孔 160 沉积然后利用第六掩模(未示出)构图, 由此形成分别与第一和第二半导体层 110 和 115 的第一和第二源极和漏极区域 110s、110d、115s 和 115d 接触的第一和第二源极和漏极电极 165s、165d、170s 和 170d。

参照图 1G, 钝化层 175 形成在具有第一和第二源极和漏极电极 165s、165d、170s 和 170d 的基板 100 的整个表面上。利用第七掩模(未示出)通过进行蚀刻工艺, 在形成于开口区域 C 中的钝化层 175 中形成第一通孔 180。

参照图 1H, 平坦化层 185 形成在具有带第一通孔 180 的钝化层 175 的基板 100 的整个表面上以减少步骤。利用第八掩模(未示出)和相关于平坦化层 185 具有高度蚀刻选择性的蚀刻剂进行湿蚀刻处理, 在开口区域 C 的平坦化层 185 中形成第二通孔 190。

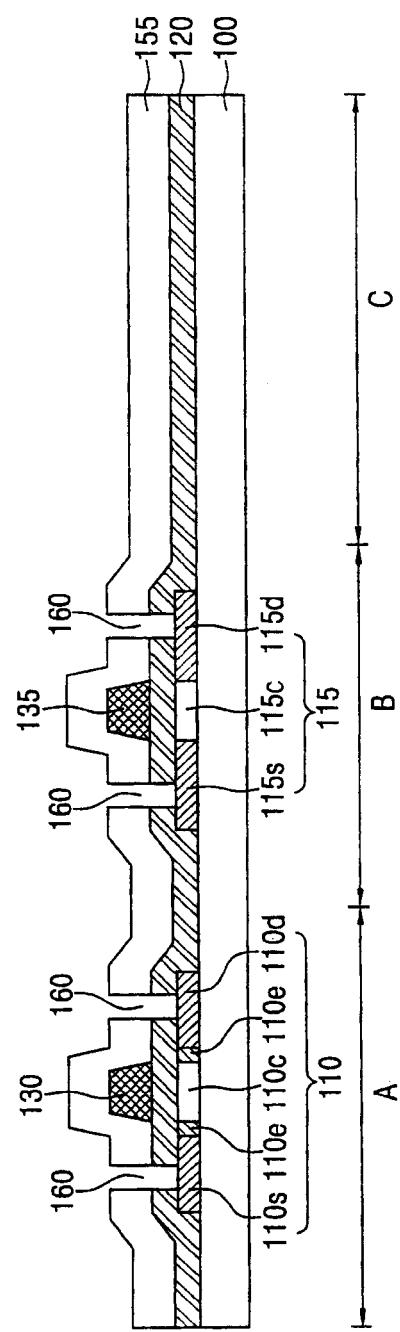

参照图 1I 和 1J, 第一电极 195 形成在第二通孔 190 周围以及在开口区域 C 的第一和第二通孔 180 和 190 的内壁和底表面上。第一电极 195 为包括透明电极 195b 和具有高反射率的反射层 195a 的反射阳极。

参照图 1I, 通过沉积铝 (Al) 且然后利用第九掩模(未示出)构图铝(Al)来形成第一电极 195 的反射层 195a。

参照图 1J, 通过在反射层 195a 上沉积氧化铟锡(ITO)或氧化铟锌(IZO)且然后利用第十掩模(未示出)通过湿或干蚀刻工艺构图所沉积的材料来形成透明电极 195b。

参照图 1K, 像素定义层 197 沉积在具有第一电极 195 的基板 100 的整个表面上且然后利用第十一掩模(未示出)构图, 由此形成开口 P 以暴露第一电极 195 的一部分表面。

具有至少发光层的有机层(未示出)形成在第一电极 195 的暴露表面上, 第二电极(未示出)沉积在具有有机层的基板 100 的整个表面上。第二电极是薄透射电极, 其由选自包括 Mg、Ca、Al、Ag 及其合金的组的一种材料形成。

通过普通方法将具有第二电极的基板 100 与上基板封装在一起, 由此完成具有顶栅型 CMOS TFT 的顶发射 (top-emitting) OLED。所述 CMOS TFT

在 NMOS 晶体管中包括 LDD 区域。

另外，制造具有带 LDD 区域的底栅型 CMOS TFT 的 OLED 的方法与上述制造具有带 LDD 区域的顶栅型 CMOS TFT 的 OLED 的方法类似。

首先，栅极电极材料沉积在基板的第一 TFT 区域和第二 TFT 区域中且然后利用第一掩模构图，由此形成栅极电极。在与栅极电极对应的栅绝缘层上形成半导体层且然后利用第二掩模构图。利用第三掩模将 n 型杂质离子注入到第一 TFT 区域中半导体层中，从而形成 NMOS 区域。另外，利用第四掩模注入 LDD 杂质离子以形成 LDD 区域。之后，利用第五掩模将 p 型杂质离子注入到第二 TFT 区域的半导体层中，从而形成 PMOS 区域。结果，获得了具有带 LDD 区域的 NMOS 晶体管和 PMOS 晶体管的 CMOS 晶体管。

之后，与上述制造具有顶栅型 CMOS TFT 的 OLED 的方法相同，利用第六掩模在层间绝缘层中形成接触孔，利用第七掩模构图源极和漏极电极，利用第八掩模形成第一通孔，利用第九掩模形成第二通孔，利用第十掩模构图第一电极的反射层，利用第十一掩模构图第一电极的透明电极，以及利用第十二掩模形成具有开口的像素定义层。也就是说，通过进行掩模工艺十二次来形成具有带 LDD 区域的底栅型 CMOS TFT 的 OLED。

如上所述，因为 PMOS TFT 和 NMOS TFT 应形成在单个基板上，通孔应被构图两次，第一电极应被构图两次，所以具有带 LDD 区域的顶栅型或底栅型 CMOS TFT 的 OLED 的制造需要相当多的工艺步骤。另外，尽管形成 LDD 区域来减小 NMOS TFT 的泄漏电流并解决小型化引起的热载流子效应，但是 LDD 区域的形成会导致用于制造 CMOS TFT 的掩模数量的进一步增加。

通过进行掩模工艺十一至十二次来获得具有带 LDD 区域的顶栅型或底栅型 CMOS TFT 的传统 OLED。因此，总体工艺作业时间延长，工艺变得复杂，产率降低，产品成本增大。

## 发明内容

本发明涉及一种有机发光显示装置(OLED)及其制造方法，其中当同时形成金属互连和栅极电极时或者当形成第一电极时，形成用于电连接元件的互连，使得通过减少所使用掩模的数量来缩短总体制造工艺并降低成本。

在本发明的一个示例性实施例中，OLED 包括：具有第一薄膜晶体管 (TFT)、第二 TFT 和金属互连的基板；设置在具有所述第一 TFT、所述第二 TFT 和所述金属互连的所述基板上的平坦化层；设置在所述平坦化层的预定区域中以暴露所述第一 TFT 的第一源极和漏极区域、所述第二 TFT 的第二源极和漏极区域、以及所述金属互连的预定区域的接触孔；以及用于通过所述接触孔电连接所述金属互连、所述第一源极和漏极区域、以及所述第二源极和漏极区域的互连。

在根据本发明的另一示例性实施例中，OLED 包括：设置于基板上的金属互连、第一栅极电极、以及第二栅极电极；设置于所述金属互连、所述第一栅极所述、以及所述第二栅极电极上的栅绝缘层；设置于所述栅绝缘层上的第一半导体层和第二半导体层，所述第一半导体层对应于所述第一栅极电极且包括第一源极和漏极区域以及第一沟道区域，所述第二半导体层对应于所述第二栅极电极且包括第二源极和漏极区域以及第二沟道区域；设置于所述第一半导体层和所述第二半导体层上的平坦化层；通过蚀刻所述平坦化层的预定区域形成的且暴露所述金属互连、所述第一源极和漏极区域、以及所述第二源极和漏极区域的预定区域的接触孔；用于通过所述接触孔将所述金属互连与所述第一源极和漏极区域之一连接的第一互连，用于通过所述接触孔将所述第一源极和漏极区域中的另一个与所述第二源极和漏极区域之一连接的第二互连，以及通过所述接触孔连接到所述第二源极和漏极区域的另一个的第一电极；设置在所述第一互连、所述第二互连、以及所述第一电极上且暴露所述第一电极的预定区域的像素定义层；以及设置于所述第一电极的暴露区域上的有机层和第二电极，所述有机层包括至少一个有机发光层 (EML)。

在本发明的又一个示例性实施例中，OLED 包括：设置于基板上的金属互连；设置于所述金属互连上的缓冲层；设置于所述缓冲层上的第一半导体层和第二半导体层，所述第一半导体层包括第一源极和漏极区域以及第一沟道区域，所述第二半导体层包括第二源极和漏极区域以及第二沟道区域；设置于所述第一半导体层和所述第二半导体层上的栅绝缘层；设置于所述栅绝缘层上并分别对应于所述第一沟道区域和所述第二沟道区域的第一栅极电极和第二栅极电极；设置于所述第一栅极电极和所述第二栅极电极上的平坦化层；通过蚀刻所述平坦化层和所述栅绝缘层的预定区域以暴露所述第一源

极和漏极区域以及所述第二源极和漏极区域的预定区域形成的接触孔，以及通过蚀刻所述平坦化层、所述栅绝缘层、以及所述缓冲层的预定区域从而暴露所述金属互连的预定区域形成的接触孔；用于通过所述接触孔将所述金属互连与所述第一源极和漏极区域之一连接的第一互连，用于通过所述接触孔将所述所述第一源极和漏极区域中的另一个与所述第二源极和漏极区域之一连接的第二互连，以及通过所述接触孔连接到所述第二源极和漏极区域的另一个的第一电极；设置于所述第一互连、所述第二互连、以及所述第一电极上并暴露所述第一电极的预定区域的像素定义层；以及设置于所述第一电极的所述暴露区域上的有机层和第二电极，所述有机层包括至少一个有机发光层（EML）。

在本发明的再一示例性实施例中，一种制造 OLED 的方法包括：在基板上形成金属互连；在所述金属互连上形成缓冲层；在所述缓冲层上形成第一半导体层和第二半导体层；在所述第一半导体层和所述第二半导体层上形成栅绝缘层；在所述栅绝缘层上形成第一栅极和第二栅极使得所述第一栅极电极和所述第二栅极电极分别对应于所述第一半导体层的第一沟道区域和所述第二半导体层的第二沟道区域；在所述第一栅极电极和所述第二栅极电极上形成平坦化层；通过蚀刻所述平坦化层和所述栅绝缘层的预定区域形成暴露所述第一半导体层的第一源极和漏极区域的预定区域以及所述第二半导体层的第二源极和漏极区域的预定区域的接触孔，且通过蚀刻所述平坦化层、所述栅绝缘层、以及所述缓冲层的预定区域形成暴露所述金属互连的预定区域的接触孔；在具有所述接触孔的所述基板上形成反射层和透明层；通过构图所述反射层和所述透明层形成第一互连、第二互连、以及第一电极，所述第一互连用于将所述金属互连与所述第一源极和漏极区域之一连接，所述第二互连用于将所述第一源极和漏极区域中的另一个与所述第二源极和漏极区域之一连接，所述第一电极连接到所述第二源极和漏极区域的另一个；在具有所述第一互连、所述第二互连、以及所述第一电极的基板上形成像素定义层以暴露所述第一电极的预定区域；以及在所述第一电极的暴露区域上形成至少具有有机发光层的有机层和第二电极。

## 附图说明

现在将参照附图相关于本发明的特定示例性实施例描述本发明的上述

和其它特征，附图中：

图 1A 至 1K 是剖视图，示出具有顶栅型 CMOS 薄膜晶体管(TFT)的传统有机发光显示装置(OLED)及其制造方法；

图 2A 至 2H 是剖视图，示出根据本发明一示例性实施例的具有底栅型 CMOS TFT 的 OLED 及其制造方法；以及

图 3A 至 3I 是剖视图，示出根据本发明另一示例性实施例的具有顶栅型 CMOS TFT 的 OLED 及其制造方法。

### 具体实施方式

现在将参照附图更充分地描述本发明，附图中示出本发明的示例性实施例。在附图中，为清楚起见而放大了层的厚度和区域。在整个说明文件中相同的附图标记表示相同的元件。

#### 实施例 1

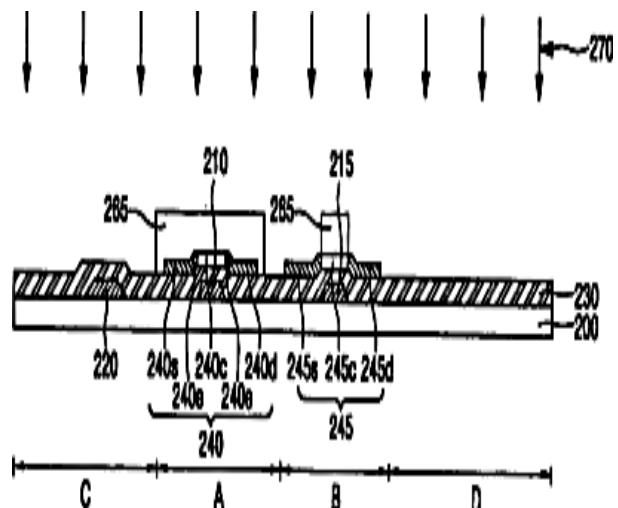

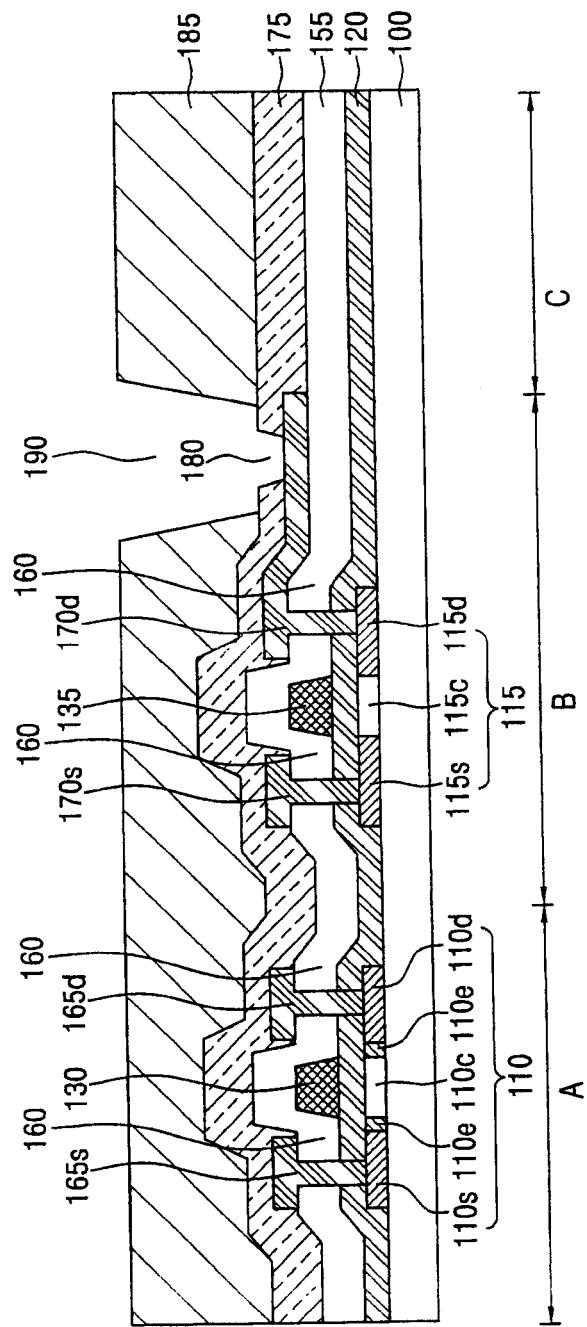

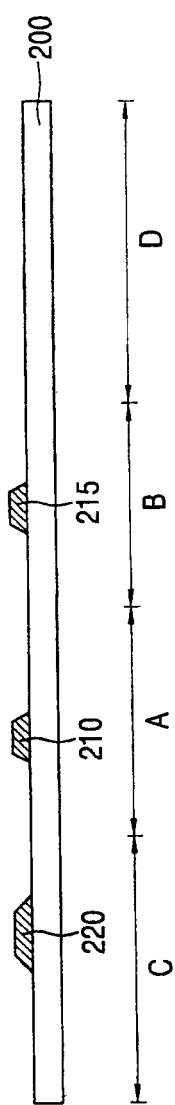

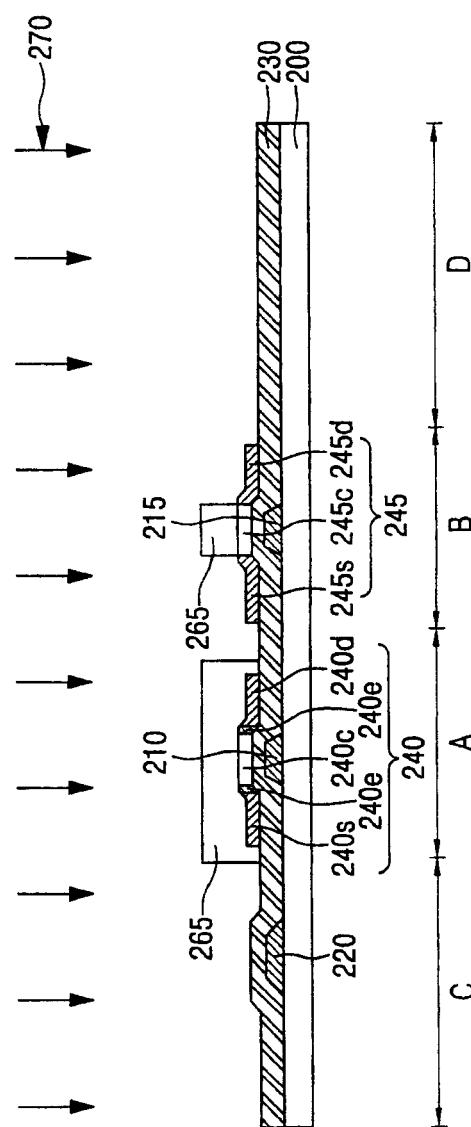

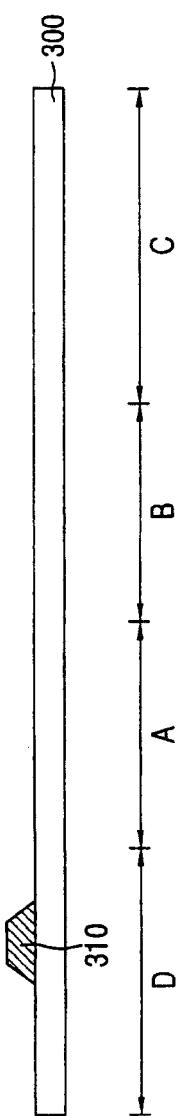

图 2A 至 2H 是剖视图，示出根据本发明一示例性实施例的具有底栅型互补金属氧化物半导体薄膜晶体管(CMOS TFT)的有机发光显示装置(OLED)及其制造方法。

参照图 2A 至 2H，根据本发明一示例性实施例的具有底栅型 CMOS TFT 的 OLED 包括具有第一 TFT 区域 A、第二 TFT 区域 B、开口区域 C、以及互连区域 D 的基板 200。基板 200 可以是由玻璃、塑料或石英形成的透明基板。

参照图 2A，第一栅极电极 210、第二栅极电极 215、以及金属互连 220 形成在基板 200 的第一和第二 TFT 区域 A 和 B 中并利用第一掩模(未示出)构图。第一和第二栅极电极 210 和 215 可以由选自包括钼(Mo)、钨(W)、铝(Al)、以及它们的合金的组的一种材料形成，例如，钨钼(MoW)、钼(Mo)、钨(W)、硅化钨(WSi<sub>2</sub>)、硅化钼(MoSi<sub>2</sub>)、以及铝(Al)。第一和第二栅极电极 210 和 215 可以通过溅镀法或真空沉积法形成。通常，第一和第二栅极电极 210 和 215 可同通过利用溅镀法沉积材料且然后构图所沉积的材料来形成。

第一掩模通过光刻工艺根据形成在中间掩模 (reticle) 上的图案形成光致抗蚀剂图案，然后光致抗蚀剂图案通过灰化和光致抗蚀剂剥离工艺被去除。

在形成第一和第二栅极电极 210 和 215 期间，金属互连 220 形成在基板

200 的互连区域 D 中。金属互连 220 与第一和第二栅极电极 210 和 215 形成在相同层上并与第一和第二栅极电极 210 和 215 间隔开预定距离。金属互连 220 可以通过沉积与第一和第二栅极电极 210 和 215 相同的材料且然后使用第一掩模构图所述材料而形成。

参照图 2B, 栅绝缘层 230 形成在具有第一和第二栅极电极 210 和 215 以及金属互连 220 的基板 200 的整个表面上。栅绝缘层 230 可以是氧化硅层、氮化硅层、或者它们的堆叠层。栅绝缘层 230 可以通过等离子增强化学气相沉积(PECVD)工艺或低压 CVD(LPCVD)工艺形成。

利用第二掩模(未示出)分别在第一和第二 TFT 区域 A 和 B 中在栅绝缘层 230 上形成第一半导体层 240 和第二半导体层 245。在此情形下, 第一和第二半导体层 240 和 245 可以由非晶硅(a-Si)或多晶硅(poly-Si)形成, 优选为多晶硅。第一和第二半导体层 240 和 245 可以通过利用 PECVD 工艺沉积 a-Si, 利用结晶方法将 a-Si 结晶为多晶硅层, 且利用第二掩模构图所述多晶硅层而形成。在此情形下, 在利用 PECVD 工艺沉积 a-Si 之后接着利用退火工艺使 a-Si 脱氢从而降低氢的浓度。

之后, 用于构图第一和第二半导体层 240 和 245 的第二掩模被定位于基板 200 之下, 利用第二掩模且利用第一和第二栅极电极 210 和 215 作为掩模进行背曝光工艺从而形成与第一和第二 TFT 区域 A 和 B 中第一和第二半导体层 240 和 245 的预定区域上的第一和第二栅极电极 210 和 215 对应的第一光致抗蚀剂图案 247。

更具体地, 背曝光工艺包括将用于构图第一和第二半导体层 240 和 245 的第二掩模定位于基板 200 之下且朝向基板 200 的底部辐照光。这样, 第一光致抗蚀剂图案 247 形成在第一和第二半导体层 240 和 245 的与所述第一和第二 TFT 区域 A 和 B 中的第一和第二栅极电极 210 和 215 对应的预定区域上。第一光致抗蚀剂图案 247 可以由正光敏材料形成。这样, 当部分第一光致抗蚀剂图案 247 暴露于光时, 该部分变为在显影液中可溶的材料且因此被蚀刻。通常, 光敏材料由控制粘度的溶剂、与紫外(UV)线反应的光活性化合物、以及是化学结合物 (chemical combination) 的聚合物树脂构成。光敏材料可包括丙烯酸树脂或聚酰亚胺(PI)。

因此, 位于透射从基板 200 的底部入射的光的栅绝缘层 230 上和半导体层的不与栅极电极对应的区域上的光致抗蚀剂在背曝光工艺中暴露于光, 变

为在显影液中可溶的材料，且被蚀刻。另一方面，由于形成在基板 200 的第一和第二 TFT 区域 A 和 B 中的第一和第二栅极电极 210 和 215 由金属形成且不能传输光，因此它们不曝光于从基板 200 的底部入射的光，从而使第一光致抗蚀剂图案 247 形成与第一和第二电极 210 和 215 相同的尺寸。

通过利用由背曝光工艺得到的第一光致抗蚀剂图案 247 进行第一杂质注入工艺 250，将轻掺杂漏极(LDD)杂质离子注入到第一和第二半导体层 240 和 245 中。这样，LDD 区域 240e 和第一沟道区域 240c 形成于第一 TFT 区域 A 中，第二源极和漏极区域 245s 和 245d 以及第二沟道区域 245c 形成于第二 TFT 区域 B 中。第一杂质注入工艺 250 可以使用普通 n 型杂质离子进行，例如  $\text{PH}_3$  离子。特别地，形成 LDD 区域 240e 以改善 TFT 的性能。另外，因为在第一和第二半导体层 240 和 245 的形成之后通过背曝光工艺形成第一光致抗蚀剂图案 247，所以能将 LDD 杂质离子注入到第一 TFT 区域 A 中的第一半导体层 240 中而不需另外的掩模，使得数量上能节省一道掩模工艺。

在背曝光工艺不必要或不能使用的情况下，可以利用用于光致抗蚀剂图案的掩模形成第一光致抗蚀剂图案 247。然而，此时需要多一道掩模。

参照图 2C，第一光致抗蚀剂图案 247 被去除，利用第三掩模(未示出)形成第二光致抗蚀剂图案 255。具体地，第二光致抗蚀剂图案 255 形成为具有比第一 TFT 区域 A 中第一半导体 240 上的第一沟道区域 240c 稍大的宽度从而完全覆盖第一沟道区域 240c 和部分覆盖 LDD 区域 240e。另外，第二光致抗蚀剂图案 255 形成为完全覆盖第二 TFT 区域 B 中的第二半导体层 245。

之后，利用第二光致抗蚀剂图案 255 将 n 型杂质离子注入第一 TFT 区域 A 中 LDD 区域 240e 的暴露部分中。n 型杂质离子包括选自含有磷(P)、砷(As)、锑(Sb)和铋(Bi)的组的一种材料。n 型杂质离子的浓度高于 LDD 杂质离子的浓度。结果，包括掺杂以 n 型杂质离子的第一源极和漏极区域 240s 和 240d、掺杂以 LDD 杂质离子的 LDD 区域 240e、以及置于 LDD 区域 240e 之间的第一沟道区域 240c 的 NMOS 晶体管形成在第一半导体层 240 中。另一方面，形成在被第二光致抗蚀剂图案 255 覆盖的第二 TFT 区域 B 中的第二半导体层 245 没有被掺杂以 n 型杂质离子。

参照图 2D，第二光致抗蚀剂图案 255 被去除，利用第四掩模(未示出)形成第三光致抗蚀剂图案 265。第三光致抗蚀剂图案 265 覆盖通过第一杂质

注入工艺 250 定义于第二 TFT 区域 B 的第二半导体层 245 中的第二沟道区域 245c，暴露第二源极和漏极区域 245s 和 245d，并完全覆盖第一 TFT 区域 A 中的第一半导体层 240。

随后，利用第三光致抗蚀剂图案 265 进行第三杂质注入工艺 270，使得 p 型杂质离子被注入到第二 TFT 区域 B 的第二源极和漏极区域 245s 和 245d 中。p 型杂质离子包括选自含有硼(B)、铝(Al)、镓(Ga)和铟(In)的组的一种。p 型杂质离子的浓度高于 LDD 杂质离子的浓度。这样，包括被掺杂以 p 型杂质离子的第二源极和漏极区域 245s 和 245d、置于第二源极和漏极区域 245s 和 245d 之间的第二沟道区域 245c 的 PMOS 晶体管形成在第二半导体层 245 中。另一方面，形成在被第三光致抗蚀剂图案 265 覆盖的第一 TFT 区域中的第一半导体层 240 未被掺杂以 p 型杂质离子。

结果，形成了具有形成在第一 TFT 区域 A 中的 NMOS 晶体管和形成在第二 TFT 区域 B 中的 PMOS 晶体管两者的 CMOS TFT。

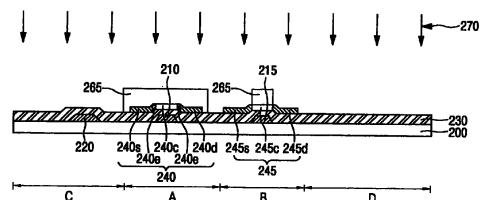

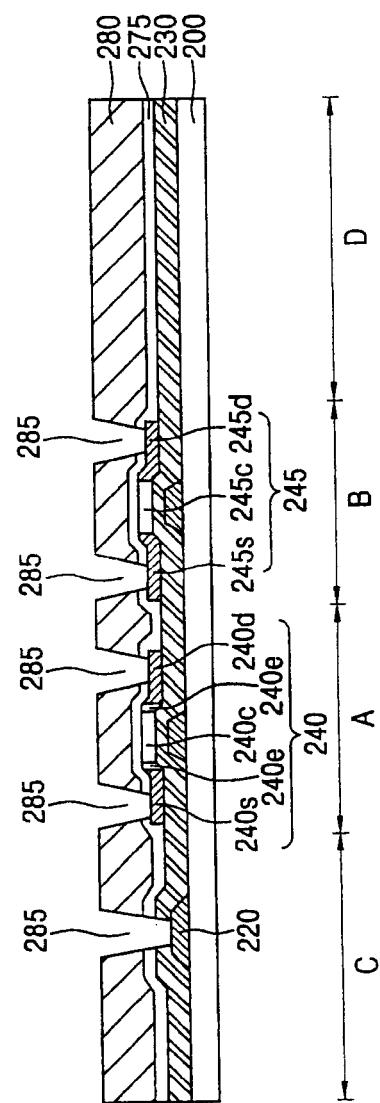

参照图 2E，钝化层 275 形成于第一和第二半导体层 240 和 245 上。通常，形成钝化层 275 从而防止 TFT 受外界污染。钝化层 275 可以由无机绝缘层形成，其是氮化硅层、氧化硅层、或它们的堆叠层。钝化层 275 可以通过 PECVD 工艺或 LPCVD 工艺形成。优选地，通过沉积无机绝缘材料，退火该材料，以及氢化退火后的材料而获得钝化层 275。

平坦化层 280 形成在钝化层 275 上以减少台阶。平坦化层 280 通常可以由选自含有苯环丁烷(BCB)、PI、聚酰胺(PA)、丙烯酸树脂和酚醛树脂的组的一种有机材料形成。平坦化层 280 可以通过旋涂工艺形成。

之后，形成在第一和第二 TFT 区域 A 和 B 以及互连区域 D 中的钝化层 275 和平坦化层 280 利用第五掩模(未示出)被蚀刻，由此在钝化层 275 和平坦化层 280 中形成接触孔 285 从而暴露部分第一和第二源极和漏极区域 240s、240d、245s 和 245d 以及金属互连 220。

参照图 2F，包括反射层 290a 和透明层 290b 的第一电极材料层 290 设置于接触孔 285 中且然后通过毯式蚀刻(blanket etching)被构图，从而形成第一电极 291、第一互连 292、以及第二互连 293。

反射层 290a 由具有高反射率的金属形成，其是选自含有铝(Al)、银(Ag)、及其合金的组中的一种。另外，透明层 290b 由 ITO 和 IZO 之一形成。这样，第一电极 291 形成为反射阳极。反射层 290a 和透明层 290b 可以通过溅镀方

法、真空沉积方法、或离子电镀方法顺序沉积。通常，反射层 290a 和透明层 290b 通过溅镀方法形成。

第一电极材料层 290 的反射层 290a 可以由 Ag 形成，使得反射层 290a 可以通过毯式蚀刻与透明层 290b 一起被构图，透明层 290b 可以由 ITO 形成。第一电极材料层 290 可以通过利用溅镀方法顺序沉积 Ag 和 ITO 且然后利用第六掩模(未示出)通过毯式蚀刻湿或干蚀刻 Ag 层和 ITO 层来形成。毯式蚀刻可以利用普通蚀刻工艺。通过毯式蚀刻包括反射层 290a 和透明层 290b 的第一电极材料层 290，在形成第一电极 291 期间数量上可节省一道掩模工艺。

结果，第一电极材料层 290 被构图从而形成第一互连 292 和第二互连 293。第一互连 292 将形成于互连区域 C 中的金属互连 220 与形成于第一 TFT 区域 A 中的第一半导体层 240 的第一源极和漏极区域 240s 和 240d 中的一个(例如第一源极区域 240s)连接。另外，第二互连 293 将形成于第一 TFT 区域 A 中的第一半导体层 240 的第一源极和漏极区域 240s 和 240d 中的另一个(例如第一漏极区域 240d)与形成于第二 TFT 区域 B 中的第二半导体层 245 的第二源极和漏极区域 245s 和 245d 中的一个(例如第二源极区域 245s)连接。

当形成第一电极 291 时，所述第一电极 291 是与第二源极和漏极区域 245s 和 245d 接触的反射阳极，形成用于将第二源极和漏极区域 245s 和 245d 与源极和漏极电极连接的接触孔的工艺，以及形成源极和漏极电极的工艺可以被省略，使得数量上能进一步节省一道掩模工艺。

参照图 2G，像素定义层 295 形成于基板 200 的整个表面上以暴露第一电极 291 的预定区域。像素定义层 295 通常由选自包括 BCB、PI、PA、丙烯酸树脂和酚醛树脂的组的一种有机材料形成。通过利用旋涂工艺沉积有机材料且然后利用第七掩模蚀刻来形成像素定义层 295，使得开口 P 形成于开口区域 C 中从而暴露第一电极 291 的部分表面。开口 P 可以通过干或湿蚀刻工艺形成，通常是湿蚀刻工艺。

参照图 2H，至少包括有机发光层(EML)的有机层 297 和第二电极 299 形成于开口 P 中第一电极 291 的暴露部分上。除了 EML 之外，有机层 297 还可包括电子注入层(EIL)、电子传输层(ETL)、空穴传输层(HTL)和空穴注入层(HIL)中的至少一种。

EML 可以由低分子物质或高分子物质形成。低分子物质可以是选自含有三(8-羟基喹啉)铝(Alq3)、并三苯、环戊二烯、ZnPBO、Balq 和 DPVBi

的组的一种。高分子物质可以是选自含有聚噻吩(PT)、对聚对苯乙炔(poly(p-phenylenevinylene), PPV)、聚亚苯基(PPP)和它们的衍生物的组的一种。有机层 297 可以通过真空沉积方法、旋涂法、喷墨印刷法、或激光诱导热成像(LITI)法形成。通常，有机层 297 可以通过旋涂法形成。另外，有机层 297 可以利用遮光掩模通过 LITI 法或真空沉积法构图。

第二电极 299 是薄透射电极，其可以由选自含有 Mg、Ca、Al、Ag、及其合金的组的一种形成。另外，第二电极 299 可以通过真空沉积法形成。

具有第二电极 299 的基板 200 利用普通方法与上基板封装起来。这样，根据本发明该实施例的具有带 LDD 区域的底栅型 CMOS TFT 的顶部发射 OLED 使用七个掩模完成(或如果不使用背曝光工艺则使用八个掩模)。

## 实施例 2

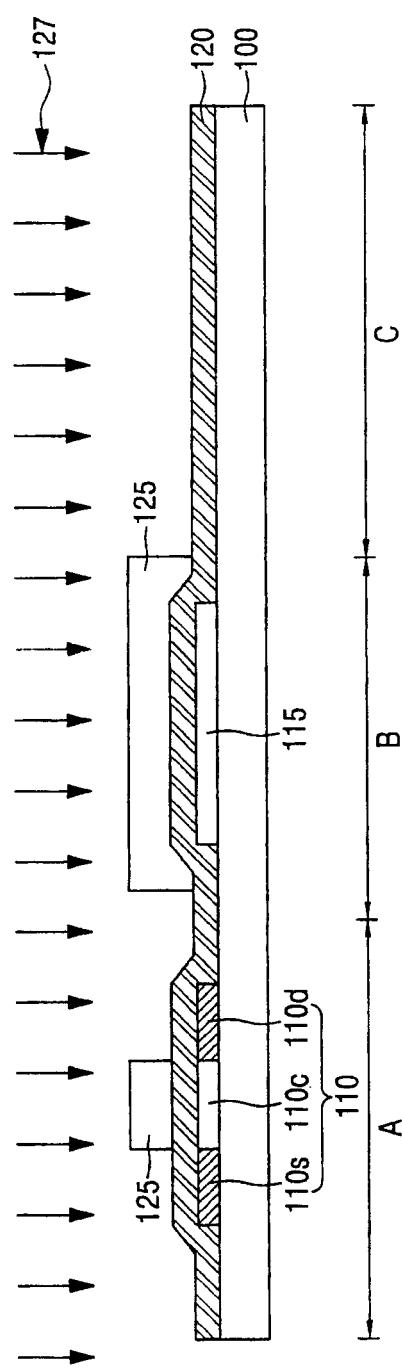

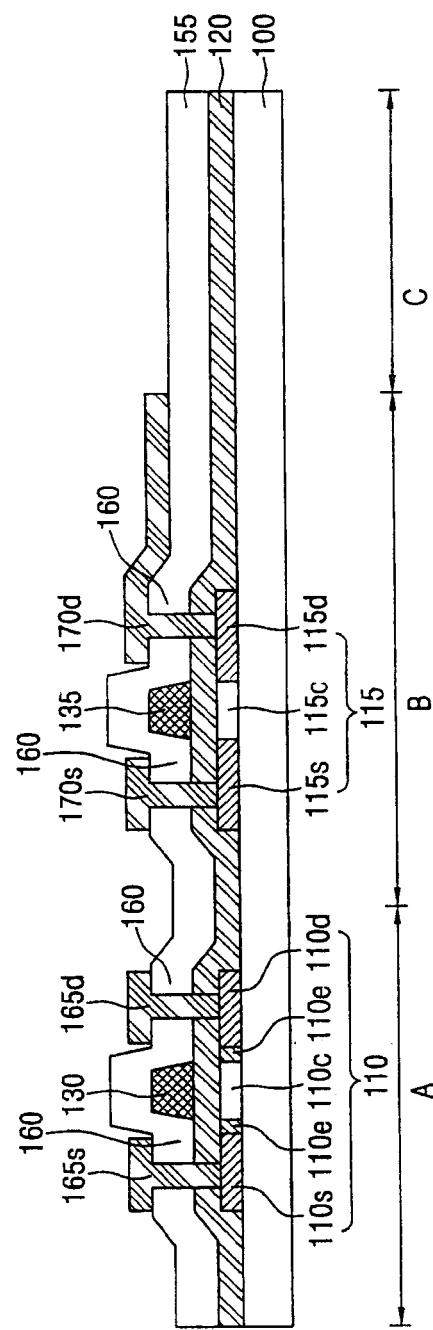

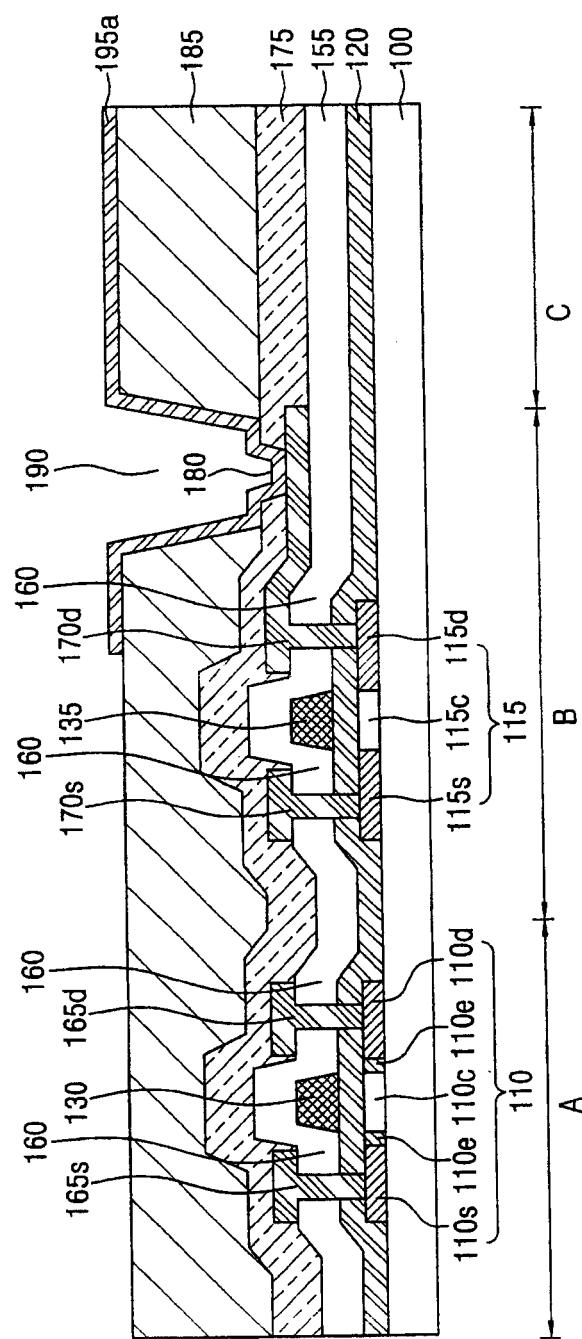

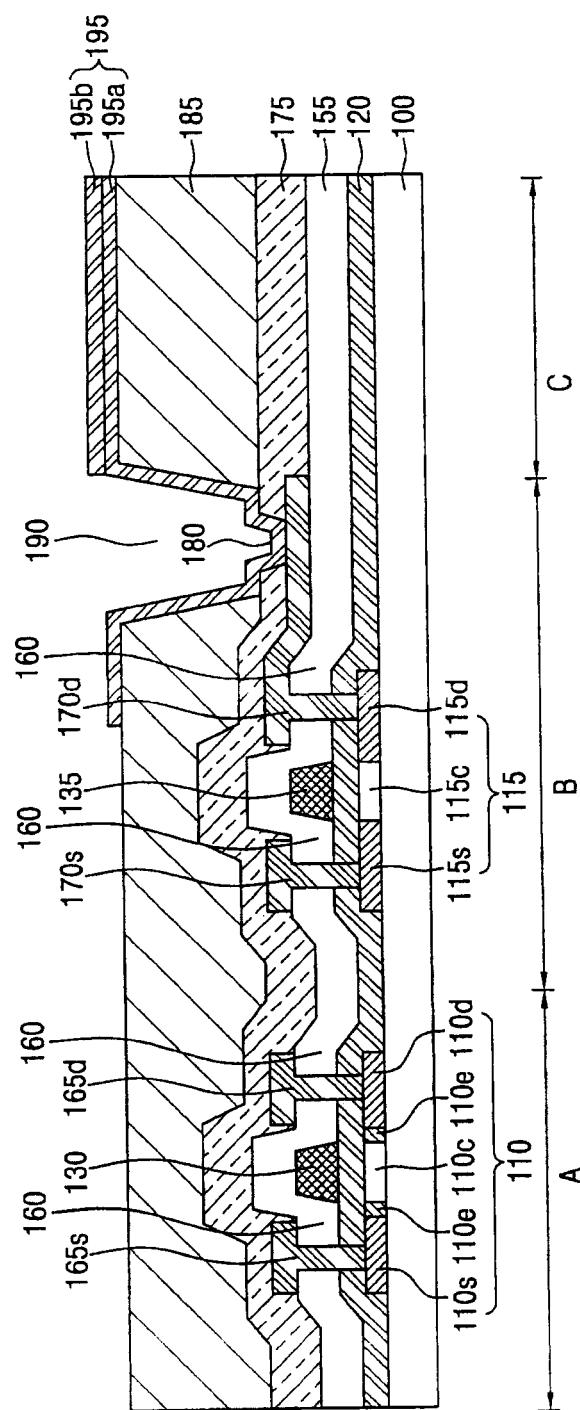

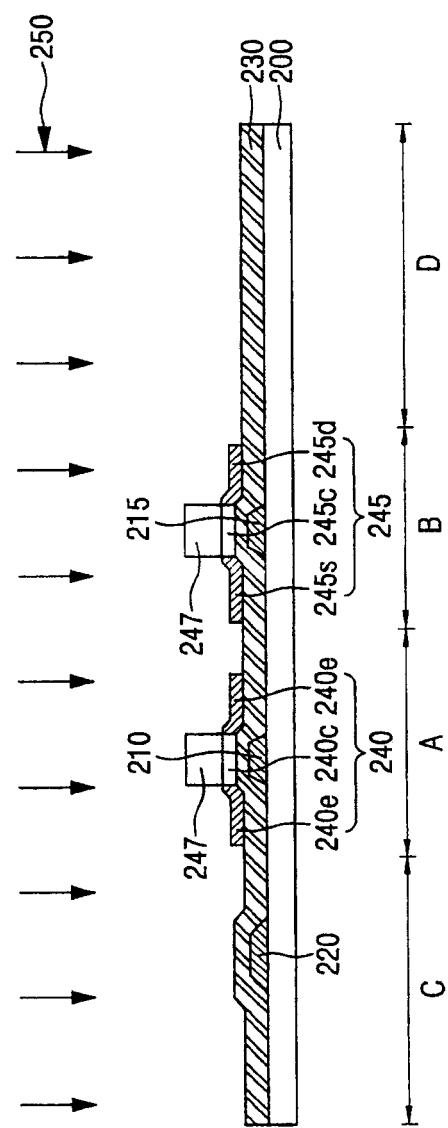

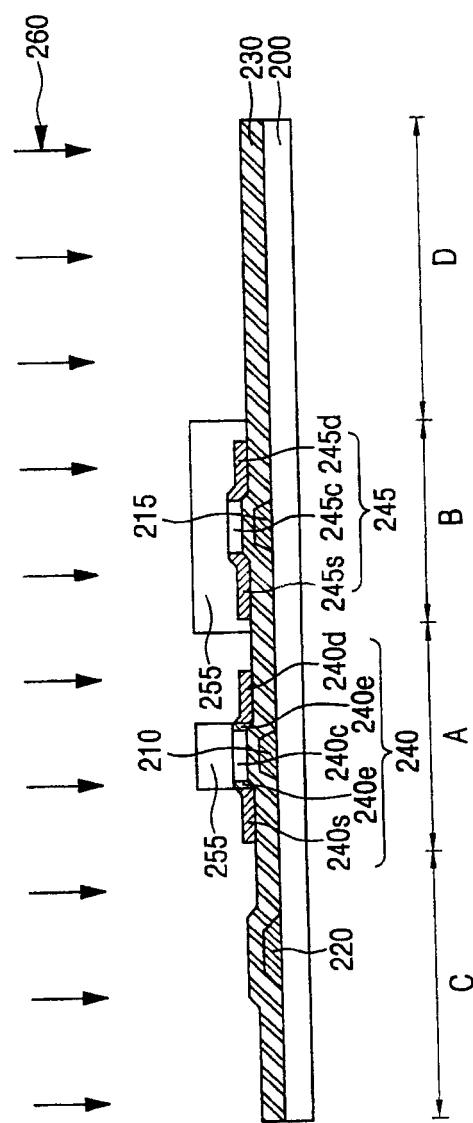

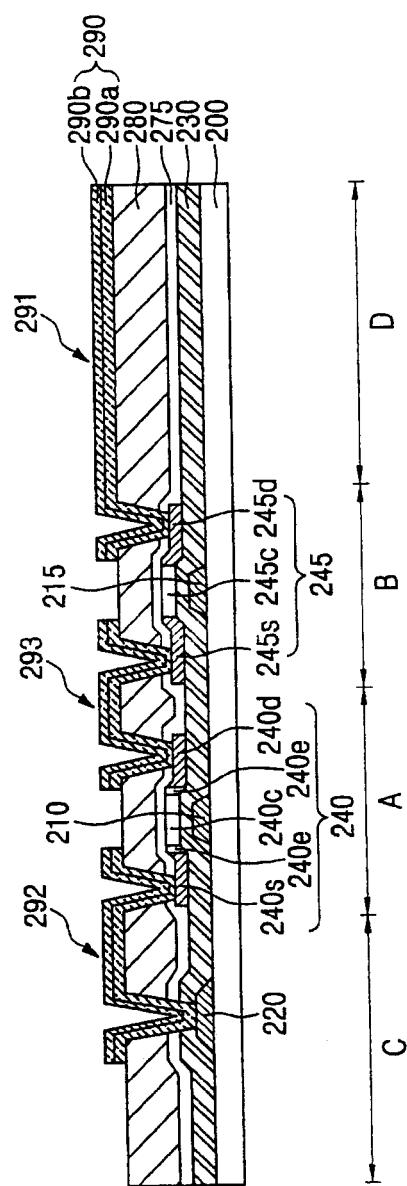

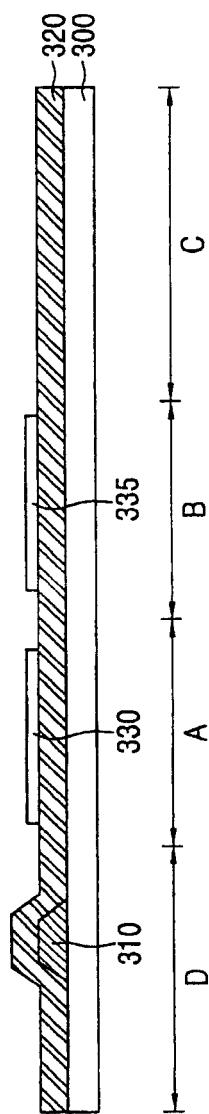

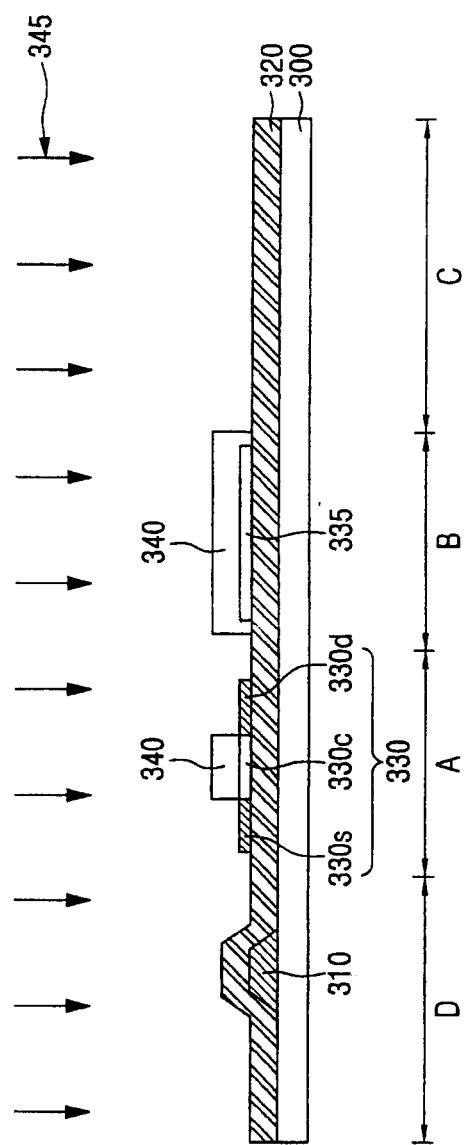

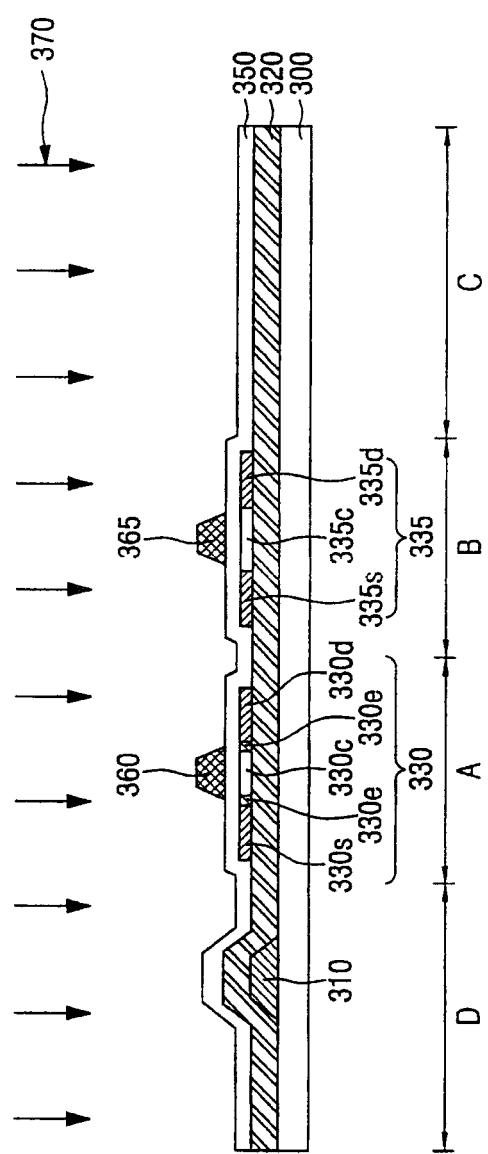

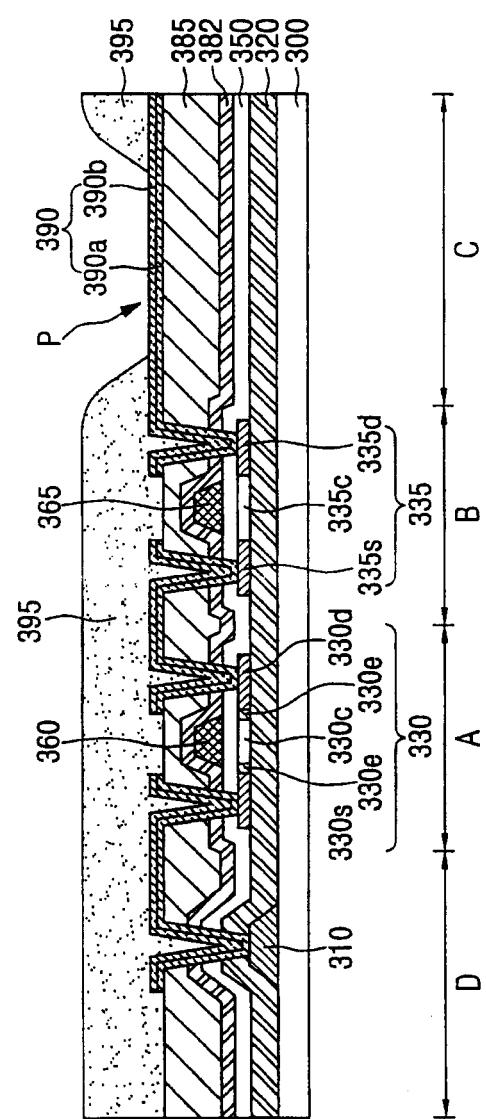

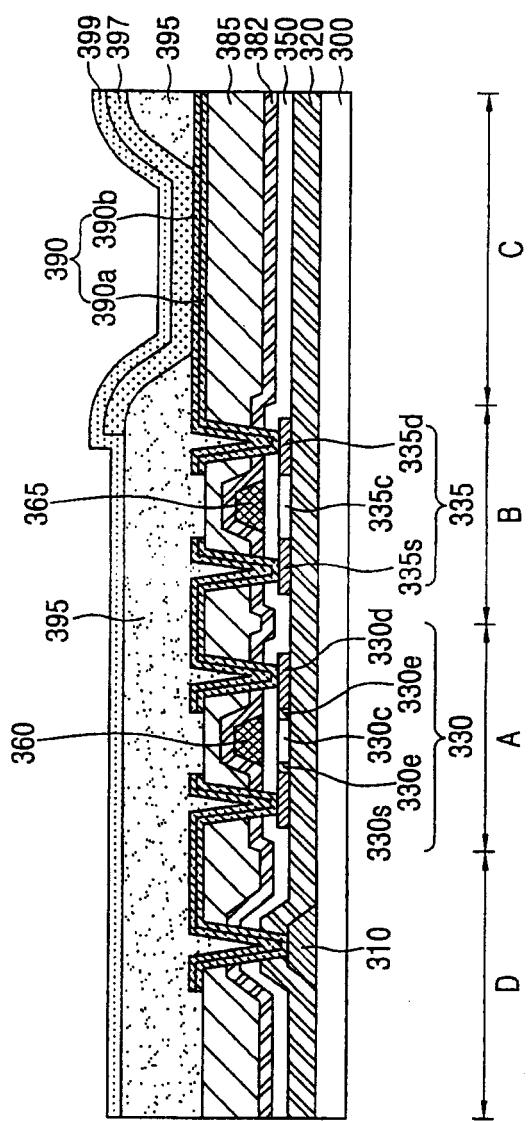

图 3A 至 3I 是剖视图，示出根据本发明另一实施例的具有顶栅型 CMOS TFT 的 OLED 及其制造方法。

参照图 3A，根据本发明另一实施例的具有顶栅型 CMOS TFT 的 OLED 包括具有第一 TFT 区域 A、第二 TFT 区域 B、开口区域 C 和互连区域 D 的基板 300。基板 300 可以是由玻璃、塑料或石英形成的透明基板。

金属互连 310 利用第一掩模(未示出)形成在基板 300 的互连区域 D 中。金属互连 310 可以由选自含有 Mo、W、Al、及其合金的组的一种材料形成。金属互连 310 可以通过溅镀方法或真空沉积法形成。通常，金属互连 310 可以通过利用溅镀方法沉积材料且然后构图所沉积的材料来形成。

参照图 3B，缓冲层 320 形成在具有金属互连 310 的基板 300 的整个表面上，第一半导体层 330 和第二半导体层 335 被形成且然后利用第二掩模(未示出)被构图在第一和第二 TFT 区域 A 和 B 中缓冲层 320 上。

形成缓冲层 320 从而保护稍后将形成的 TFT 免受从基板 300 扩散的杂质离子的影响。缓冲层 320 可以是氧化硅层、氮化硅层、或它们的堆叠层。缓冲层 320 通过 PECVD 工艺或 LPCVD 工艺形成。形成第一和第二半导体层 330 和 335 的方法与实施例 1 中描述的方法相同。

参照图 3C，利用第三掩模(未示出)形成第一光致抗蚀剂图案 340 从而暴露第一 TFT 区域 A 中第一半导体层 330 的预定区域，利用第一光致抗蚀剂图案 340 进行第一杂质注入工艺 345 使得 n 型杂质离子被注入到第一半导体

层 330 中。n 型杂质离子包括选自含有 P、As、Sb 和 Bi 的组的一种。从而，第一半导体层 330 定义掺杂以 n 型杂质离子的第一源极和漏极区域 330s 和 330d，以及置于第一源极和漏极区域 330s 和 330d 之间的第一沟道区域 330c。另一方面，形成在被第一光致抗蚀剂图案 340 覆盖的第二 TFT 区域 B 中的第二半导体层 335 未被掺杂以 n 型杂质离子。

参照图 3D，在第一杂质注入工艺 345 之后，通过灰化 (ashing) 和 PR 剥离工艺去除第一光致抗蚀剂图案 340，栅绝缘层 350 形成于具有第一和第二半导体层 330 和 335 的基板 300 的整个表面上。栅绝缘层 350 可以是氧化硅层、氮化硅层、或它们的堆叠层。另外，栅绝缘层 350 可以通过 PECVD 工艺或 LPCVD 工艺获得。

第一栅极电极 360 和第二栅极电极 365 利用第四掩模(未示出)形成于第一和第二 TFT 区域 A 和 B 中栅绝缘层 350 上。第一和第二栅极电极 360 和 365 由选自含有 Mo、W、Al、以及它们的合金的组的一种材料形成。在此情况下，形成在第一 TFT 区域 A 中的第一栅极电极 360 形成为具有比图 3C 所示的第一沟道区域 330c 小的宽度从而为将在后面形成的 LDD 区域留出空间。第一和第二栅极电极 360 和 365 可以通过溅镀方法或真空沉积方法形成。通常，第一和第二栅极电极 360 和 365 通过利用溅镀方法沉积材料且然后构图所沉积的材料而形成。

利用第一和第二栅极电极 360 和 365 作为掩模在第一和第二 TFT 区域 A 和 B 中进行第二杂质注入工艺 370，使得 LDD 区域 330e 形成于第一半导体层 330 中。掺入 LDD 区域 330e 中的杂质离子是 n 型杂质离子，通常为 PH<sub>3</sub>。LDD 杂质离子的浓度低于 n 型杂质离子的浓度。因此，形成于第一 TFT 区域 A 中的第一半导体层 330 形成包括被掺杂以 n 型杂质离子的第一源极和漏极区域 330s 和 330d、被掺杂以低浓度杂质离子的 LDD 区域 330e、以及置于 LDD 区域 330e 之间的第一沟道区域 330c 的 NMOS 晶体管。在此情况下，由于第二杂质注入工艺 370，形成于第二 TFT 区域 B 中的第二半导体层 335 定义第二源极和漏极区域 335s 和 335d 以及置于第二源极和漏极区域 335s 和 335d 之间的第二沟道区域 335c。

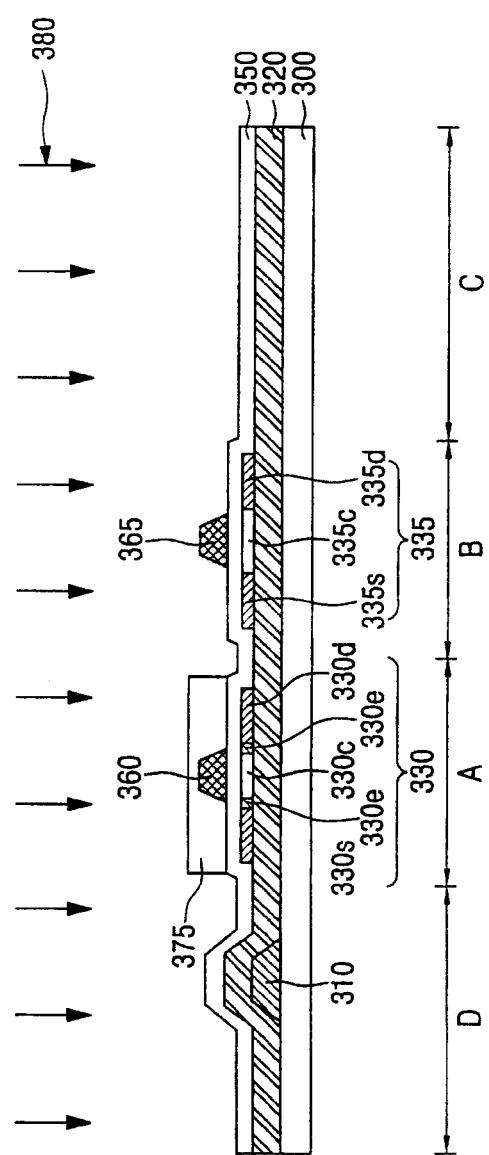

参照图 3E，利用第五掩模(未示出)形成第二光致抗蚀剂图案 375 以完全覆盖第一 TFT 区域 A 中的第一半导体层 330 且暴露第二 TFT 区域 B 中的第二半导体层 335。利用第二光致抗蚀剂图案 375 在第二 TFT 区域 B 中的第二

半导体层 335 上进行第三杂质注入工艺 380 从而注入 p 型杂质离子以形成第二源极和漏极区域 335s 和 335d。p 型杂质离子包括选自含有 B、Al、Ga 和 In 的组的一种。p 型杂质离子的浓度高于 LDD 杂质离子的浓度。这样，第二半导体层 335 形成包括被掺杂以 p 型杂质离子的第二源极和漏极区域 335s 和 335d、以及置于第二源极和漏极区域 335s 和 335d 之间的第二沟道区域 335c 的 PMOS 晶体管。

从而，形成了具有形成在第一 TFT 区域 A 中的 NMOS 晶体管和形成在第二 TFT 区域 B 中的 PMOS 晶体管两者的 CMOS TFT。

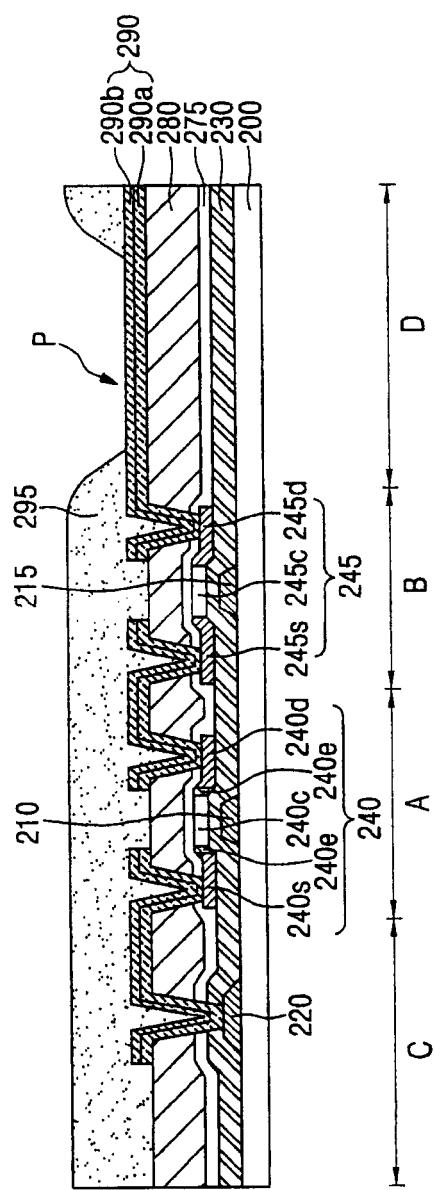

参照图 3F，钝化层 382 形成于第一和第二栅极电极 360 和 365 上，然后平坦化层 385 形成于钝化层 382 上。

利用第六掩模(未示出)蚀刻钝化层 382 和平坦化层 385，由此形成接触孔 387 从而暴露部分第一和第二源极和漏极区域 330s、330d、335s 和 335d 以及金属互连 310。

形成钝化层 382、平坦化层 385、以及接触孔 387 的方法与实施例 1 中描述的方法的相同。

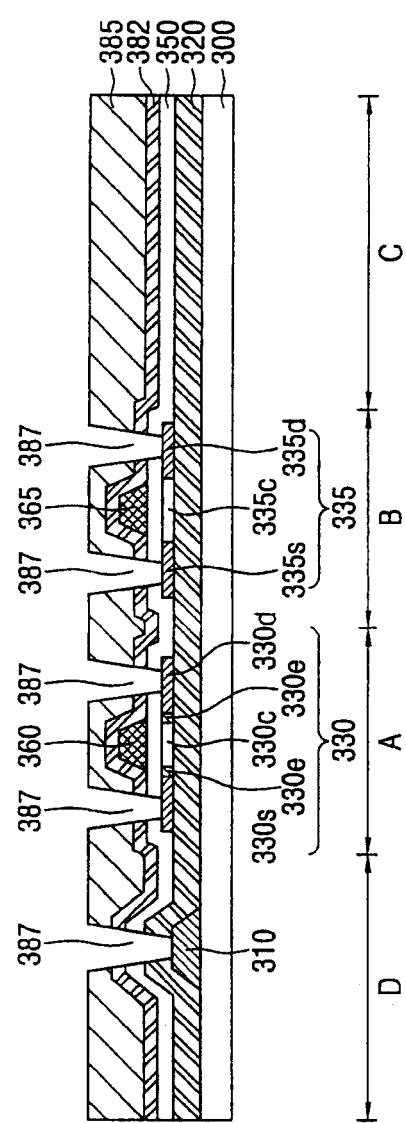

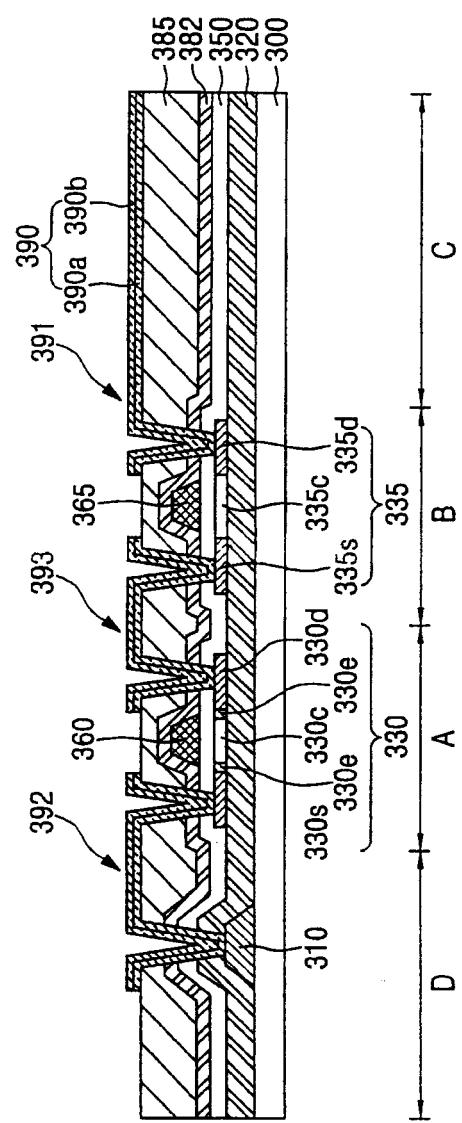

参照图 3G，包括反射层 390a 和透明层 390b 的第一电极材料层 390 堆叠于接触孔 387 中，然后利用第七掩模(未示出)通过毯式蚀刻工艺被构图，由此形成第一电极 391、第一互连 392、以及第二互连 393。

第一电极材料层 390 的形成和构图与实施例 1 中描述的相同。包括反射层 390a 和透明层 390b 的第一电极材料层 390 被毯式蚀刻，使得在形成第一电极 391 期间可以在数量上节省一道掩模工艺。

结果，第一电极 391 与第二 TFT 区域 B 中第二半导体层 335 的第二源极和漏极区域 335s 和 335d 之一连接，第一互连 392 与互连区域 C 中金属互连 310 以及第一 TFT 区域 A 中第一源极和漏极区域 330s 和 330d 中的一个接触。另外，第二互连 393 与第一 TFT 区域 A 中第一源极和漏极区域 330s 和 330d 的另一个以及第二 TFT 区域 B 中第二源极和漏极区域 335s 和 335d 的另一个接触。

由于第一电极 391、第一互连 392、以及第二互连 393 同时形成，所以形成用于将源极和漏极区域与源极和漏极电极连接的接触孔的工艺、以及形成源极和漏极电极的工艺能被省略。因此，数量上能进一步节省两道掩模工艺。

参照图 3H, 像素定义层 395 形成在具有第一电极 391 的基板 300 的整个表面上。形成像素定义层 395 的方法与实施例 1 中描述的方法相同。利用第八掩模(未示出)蚀刻像素定义层 395 使得开口 P 形成于开口区域 C 中从而暴露第一电极 391 的部分表面。开口 P 通过干或湿蚀刻工艺形成。

参照图 3I, 至少具有 EML 的有机层 397 和第二电极 399 形成于开口 P 中第一电极 391 的暴露部分上。形成有机层 397 和第二电极 399 的方法与实施例 1 中描述的方法相同。

利用普通方法将具有第二电极 399 的基板 300 与上基板封装起来。这样, 根据本发明另一实施例的具有带 LDD 区域的顶栅型 CMOS TFT 的顶部发射 OLED 利用八道掩模工艺完成了。

根据如上所述的本发明, 当形成作为反射阳极的第一电极时, 同时使互连与内部器件接触。这样, 与使用 11 至 12 道掩模工艺的传统 OLED 相比, 具有带 LDD 区域的 CMOS TFT 的 OLED 仅使用了 7 至 8 道掩模工艺形成。因此, 能缩短总体制造工艺, 减少制造成本, 增加产量。

尽管参照其特定示例性实施例描述了本发明, 但是本领域技术人员应理解, 在不脱离本发明所附权利要求及其等价物定义的本发明的思想和范围的情况下能进行许多修改和变化。

本申请要求享有于 2005 年 6 月 22 提交的韩国专利申请 No. 2005-54165 的优先权, 在此引入其全部内容作为参考。

图 1A

图 1B

图 1C

图 1D

图 1E

图 1F

图 1G

图 1H

图 11

图 1J

图 1K

图 2A

图 2B

图 2C

图 2D

图 2E

2F

图 2G

图 2H

图 3A

图 3B

图 3C

图 3D

3E

四

图 3F

图 3G

图 3H

图 31

专利名称(译) 有机发光显示装置及其制造方法

公开(公告)号 [CN1897299A](#) 公开(公告)日 2007-01-17

申请号 CN200610125721.0 申请日 2006-06-22

[标]申请(专利权)人(译) 三星斯笛爱股份有限公司

申请(专利权)人(译) 三星SDI株式会社

当前申请(专利权)人(译) 三星SDI株式会社

[标]发明人 黄义勋

李相杰

发明人 黄义勋

李相杰

IPC分类号 H01L27/32 H01L21/82 H01L21/768

CPC分类号 H01L27/3244 H01L51/56 H01L27/3276 H01L2251/5315 H01L51/5218

代理人(译) 张波

优先权 1020050054165 2005-06-22 KR

其他公开文献 CN100481489C

外部链接 [Espacenet](#) [Sipo](#)

#### 摘要(译)

本发明提供一种有机发光显示装置(OLED)及其制造方法。在同时形成金属互连和栅极电极时或在形成第一电极时，形成用于电连接元件的互连。从而，能减少使用掩模的次数，从而缩短总体制造工艺且降低成本。