(12) 发明专利申请

(10) 申请公布号 CN 101996578 A

(43) 申请公布日 2011.03.30

(21) 申请号 201010518610.2

(51) Int. Cl.

(22) 申请日 2006.11.14

G09G 3/32 (2006.01)

(30) 优先权数据

2005-328334 2005.11.14 JP

(62) 分案原申请数据

200680042467.6 2006.11.14

(71) 申请人 索尼公司

地址 日本东京都

(72) 发明人 内野胜秀 山下淳一

(74) 专利代理机构 北京东方亿思知识产权代理

有限责任公司 11258

代理人 李晓冬 南霆

权利要求书 2 页 说明书 17 页 附图 15 页

(54) 发明名称

像素电路和显示装置

(57) 摘要

可以提高具有阈值电压校正功能的像素电路的效率并简化像素电路。采样晶体管(Tr1)在水平扫描周期期间响应于从扫描线(WS)提供的控制信号被电连接，并且将从信号线(SL)提供的视频信号采样到像素电容器(Cs)中。像素电容器(Cs)响应于被采样的视频信号将输入电压(Vgs)施加到驱动晶体管(Trd)的栅极(G)。驱动晶体管(Trd)将根据输入电压(Vgs)的输出电流提供给发光器件(EL)。输出电流具有对驱动晶体管(Trd)的阈值电压(Vth)的依赖性。为了消除输出电流对阈值电压(Vth)的依赖性，设置了校正装置(Tr3, Tr4)，该校正装置在水平扫描周期的一部分中操作，检测驱动晶体管(Trd)的阈值电压(Vth)，并将其写入像素电容器(Cs)中。

1. 一种像素电路，至少包括采样晶体管、像素电容器、驱动晶体管和发光器件，其中，所述采样晶体管将视频信号从信号线采样到所述像素电容器的一端，其中，所述驱动晶体管根据所述像素电容器中存储的信号向所述发光器件提供输出电流，其中，所述像素电容器连接在所述驱动晶体管的栅极和源极之间，其中，所述像素电路包括校正装置，该校正装置在所述视频信号被施加到所述像素电容器之前操作，使得在所述像素电容器两端的电势差被设置到超过所述驱动晶体管的阈值电压之后、所述驱动晶体管的栅极被保持在一特定电势期间，所述像素电容器通过所述驱动晶体管被充电。

2. 如权利要求 1 所述的像素电路，其中，所述特定电势是从所述信号线通过所述采样晶体管提供的。

3. 如权利要求 1 所述的像素电路，其中，在所述驱动晶体管的栅极被保持在一特定电势直到所述像素电容器两端的电势差变为所述阈值电压期间，所述像素电容器通过所述驱动晶体管被充电。

4. 如权利要求 1 所述的像素电路，其中，所述采样晶体管被连接到所述采样晶体管的栅极的扫描线所切换。

5. 如权利要求 1 所述的像素电路，其中，所述采样晶体管连接在所述驱动晶体管的源极与信号线之间，其中，所述发光器件连接到所述驱动晶体管的源极。

6. 一种像素电路，被设置在提供控制信号的行形式的扫描线和提供视频信号的列形式的信号线彼此交叉的部分处，并且至少包括采样晶体管、连接到所述采样晶体管的像素电容器、连接到所述像素电容器的驱动晶体管和连接到所述驱动晶体管的发光器件，其中，在分配给所述扫描线的水平扫描周期期间，所述采样晶体管响应于从所述扫描线提供的所述控制信号导通，并且将从所述信号线提供的所述视频信号采样到所述像素电容器中，其中，所述像素电容器响应于被采样的视频信号将输入电压施加到所述驱动晶体管的栅极，其中，所述驱动晶体管在预定发光周期期间将根据所述输入电压的输出电流提供给所述发光器件，并且所述输出电流具有对所述驱动晶体管的沟道区域中的阈值电压的依赖性，并且，其中，通过从所述驱动晶体管提供的所述输出电流，所述发光器件按照根据所述视频信号的亮度发光，所述像素电路的特征在于包括校正装置，该校正装置在所述水平扫描周期的一部分中操作，并且检测所述驱动晶体管的所述阈值电压，将所述阈值电压写入所述像素电容器中，以便消除所述输出电流对所述阈值电压的依赖性，其中，所述校正装置在对所述像素电容器进行充电直到所述像素电容器两端的所述电势差变为所述阈值电压为止之前，将所述像素电容器两端的电势差设置为超过所述阈值电压。

7. 如权利要求 6 所述的像素电路，特征在于，所述校正装置在所述采样晶体管导通并

且所述像素电容器的一端被所述信号线保持在一特定电势的状态中在所述水平扫描周期期间工作，并且对所述像素电容器充电直到所述像素电容器的另一端与所述特定电势的电势差变为所述阈值电压为止。

8. 如权利要求 6 所述的像素电路，特征在于，所述校正装置在所述水平扫描周期的前半部分中检测所述驱动晶体管的所述阈值电压并将所述阈值电压写入所述像素电容器中，

而所述采样晶体管在所述水平扫描周期的后半部分中将从所述信号线提供的所述视频信号采样到所述像素电容器中，

并且所述像素电容器在所述驱动晶体管的栅极和源极之间施加输入电压，所述输入电压是被采样的视频信号和被写入的阈值电压的总和，从而消除所述输出电流对所述阈值电压的依赖性。

9. 如权利要求 6 所述的像素电路，特征在于，所述采样晶体管在所述水平扫描周期中所述信号线处于所述视频信号的电势的信号提供周期期间，将从所述信号线提供的所述视频信号采样到所述像素电容器中，

而所述校正装置在所述水平扫描周期中所述扫描线处于一特定电势的信号固定周期期间，检测所述驱动晶体管的所述阈值电压并将所述阈值电压写入所述像素电容器中。

10. 如权利要求 9 所述的像素电路，特征在于，所述校正装置还在分配给其他扫描线的水平扫描周期中的信号固定周期中工作，并且在每个信号固定周期中以分时方式将所述像素电容器充电到所述阈值电压。

11. 如权利要求 10 所述的像素电路，特征在于，所述信号固定周期是限定顺序分配给各条扫描线的各个水平扫描周期的水平消隐周期，

并且所述校正装置在每个水平消隐周期中以分时方式将所述像素电容器充电到所述阈值电压。

12. 如权利要求 10 所述的像素电路，特征在于，在所述校正装置已在每个信号固定周期中对所述像素电容器充电后，在所述信号线被从所述特定电势切换到所述视频信号的电势之前，所述采样晶体管被关闭并且所述像素电容器在电气上与所述信号线断开。

13. 如权利要求 6 所述的像素电路，特征在于，除了所述沟道区域中的所述阈值电压之外，所述驱动晶体管的输出电流还具有对载流子迁移率的依赖性，

并且所述校正装置在所述水平扫描周期的一部分中工作，在所述视频信号被采样的状态中从所述驱动晶体管获得所述输出电流，并且将所述输出电流负反馈到所述像素电容器来校正所述输入电压，以便消除所述输出电流对所述载流子迁移率的依赖性。

## 像素电路和显示装置

[0001] 本申请是 2006 年 11 月 14 日递交的发明名称为“像素电路和显示装置”、申请号为 200680042467.6 (PCT/JP2006/322653) 的专利申请的分案申请。

### 技术领域

[0002] 本发明涉及针对各个像素布置并且利用电流驱动发光器件 (light emitting device) 的像素电路。更具体而言，本发明涉及利用在每个像素电路中设置的绝缘栅场效应晶体管 (insulated gate field effect transistor) 对被提供给发光器件 (例如，有机 EL (电致发光)) 的电流的量进行控制并且被应用于所谓的有源矩阵显示装置的像素电路。另外，本发明还涉及包括该像素电路的显示装置。

### 背景技术

[0003] 在例如液晶显示器之类的图像显示装置中，以矩阵形式布置了许多液晶像素，并且根据要显示的图像信息控制每个像素中的入射光的透射和反射强度，从而显示图像。这在像素中包括有机 EL 器件的有机 EL 显示器等等之中相同的，但是有机 EL 器件是不同于液晶像素的自发光器件。因此，有机 EL 显示器的优点包括可视性比液晶显示器的可视性高，不需要背光，并且响应速度较高。另外，每个发光器件的亮度级别 (灰度级别) 可由流入到该器件的电流的值控制，因此作为所谓的电流控制型的有机 EL 显示器与作为电压控制型的液晶显示器极大不同。

[0004] 与液晶显示器一样，有机 EL 显示器的驱动系统被划分成简单矩阵系统 (simple matrix system) 和有源矩阵系统 (active matrix system)。前者具有简单的结构，但是存在难以实现较大的高分辨率显示器的问题。因此，现在对有源矩阵系统的开发比较活跃。在该系统中，流到每个像素电路中的发光器件的电流受控于像素电路中设置的有源器件 (一般是薄膜晶体管 (TFT))，在日本未实审专利申请公开 No. 2003-255856、No. 2003-271095、No. 2004-133240、No. 2004-029791 和 No. 2004-093682 中描述了该系统。

[0005] 传统的像素电路被布置在提供控制信号的行形式的扫描线和提供视频信号的列形式的信号线彼此交叉的位置处，并且每个像素电路包括至少一个采样晶体管 (sampling transistor)、电容器单元、驱动晶体管 (drive transistor) 和发光器件。采样晶体管响应于提供扫描线的控制信号导通，从而对提供自信号线的视频信号进行采样。电容器单元根据被采样的视频信号保持输入电压。驱动晶体管在预定发光周期期间根据电容器单元中保持的输入电压提供输出电流。一般来说，输出电流具有对驱动晶体管的沟道区域中的载流子迁移率 (carrier mobility) 和阈值电压的依赖性。利用从驱动晶体管提供的输出电流，发光器件按照根据视频信号的亮度发光。

[0006] 驱动晶体管在其栅极中接收在电容器单元中保持的输入电压，并且在源极和漏极之间提供输出电流，以使发光器件导通。一般而言，发光器件的发光亮度与流到该发光器件的电流的量成正比。此外，从驱动晶体管提供的输出电流的量受控于栅极电压，即，电容器单元中写入的输入电压。在传统的像素电路中，通过根据输入视频信号来改变施加到驱动

晶体管的栅极的输入电压,来对提供到发光器件的电流的量进行控制。

[0007] 在这里,驱动晶体管的操作特性由如下表达式 1 表示。

$$[0008] I_{ds} = (1/2) \mu (W/L) C_{ox} (V_{gs} - V_{th})^2 \quad \dots \text{表达式 1}$$

[0009] 在该晶体管特性表达式 1 中,  $I_{ds}$  表示在源极和漏极之间流动的漏极电流,并且是被提供给像素电路中的发光器件的输出电流。 $V_{gs}$  表示被施加到栅极的相对于源极的栅极电压,并且是像素电路中的上述输入电压。 $V_{th}$  是晶体管的阈值电压。另外,  $\mu$  表示构成晶体管的沟道的半导体薄膜的迁移率。另外,  $W$  表示沟道的宽度、 $L$  表示沟道的长度、并且  $C_{ox}$  表示栅极电容。从晶体管特性表达式 1 可清楚,当 TFT 在饱和区中工作时,如果栅极电压  $V_{gs}$  上升到超过阈值电压  $V_{th}$ ,则 TFT 进入导通 (ON) 状态,并且漏极电流  $I_{ds}$  流动。原理上,如上述晶体管特性表达式 1 所示,恒定的栅极电压  $V_{gs}$  允许相同量的漏极电流  $I_{ds}$  被恒定地提供给发光器件。因此,通过将相同电平的视频信号提供给构成屏幕的所有像素,所有像素按照相同亮度发光,从而可以确保获得屏幕的均一性。

[0010] 但实际上,由多晶硅半导体薄膜等构成的薄膜晶体管 (TFT) 的器件特性会变化。具体而言,阈值电压  $V_{th}$  不是恒定的,而是在每个像素中会不同。从上述晶体管特性表达式 1 可以清楚,如果阈值电压  $V_{th}$  在每个驱动晶体管中不同,那么即使栅极电压  $V_{gs}$  恒定,每个像素中的漏极电流  $I_{ds}$  也会不同,并且亮度也不同,从而有损屏幕的均一性。传统上,开发了具有消除驱动晶体管的阈值电压的变化的功能的像素电路,例如在上述日本未实审专利申请公开 No. 2004-133240 中有所公开。

[0011] 但是,具有消除阈值电压的变化的功能(阈值电压校正功能)的传统像素电路具有复杂的结构,这妨碍了像素的小型化和高分辨率。另外,具有阈值电压校正功能的传统像素电路效率较低,并且使得电路设计复杂。另外,具有阈值电压校正功能的传统像素电路导致产量下降,因为其中设置的元件的数目相对较多。

## 发明内容

[0012] 考虑到现有技术的上述问题,本发明的一个目的是提高具有阈值电压校正功能的像素电路的效率和简单性,以实现显示装置的高分辨率并且提高其产量。为了实现该目标,采用了下面的措施。即,本发明特征在于,一种像素电路,被设置在提供控制信号的行形式的扫描线和提供视频信号的列形式的信号线彼此交叉的部分处,并且至少包括采样晶体管、连接到所述采样晶体管的像素电容器、连接到所述像素电容器的驱动晶体管和连接到所述驱动晶体管的发光器件,其中,在分配给所述扫描线的水平扫描周期期间,所述采样晶体管响应于从所述扫描线提供的所述控制信号导通,并且将从所述信号线提供的所述视频信号采样到所述像素电容器中,其中,所述像素电容器响应于被采样的视频信号将输入电压施加到所述驱动晶体管的栅极,其中,所述驱动晶体管在预定发光周期期间将根据所述输入电压的输出电流提供给所述发光器件,并且所述输出电流具有对所述驱动晶体管的沟道区域中的阈值电压的依赖性,并且其中,通过从所述驱动晶体管提供的所述输出电流,所述发光器件按照根据所述视频信号的亮度发光,所述像素电路包括校正装置,该校正装置在所述水平扫描周期的一部分中操作,并且检测所述驱动晶体管的所述阈值电压,将所述阈值电压写入所述像素电容器中,以便消除所述输出电流对所述阈值电压的依赖性。

[0013] 优选地,所述校正装置在所述采样晶体管导通并且所述像素电容器的一端被所述

信号线保持在一特定电势的状态中在所述水平扫描周期期间工作，并且对所述像素电容器充电直到所述像素电容器的另一端与所述特定电势的电势差变为所述阈值电压为止。另外，所述校正装置在所述水平扫描周期的前半部分中检测所述驱动晶体管的所述阈值电压并将所述阈值电压写入所述像素电容器中，而所述采样晶体管在所述水平扫描周期的后半部分中将从所述信号线提供的所述视频信号采样到所述像素电容器中，并且所述像素电容器在所述驱动晶体管的栅极和源极之间施加输入电压，所述输入电压是被采样的视频信号和被写入的阈值电压的总和，从而消除所述输出电流对所述阈值电压的依赖性。另外，所述校正装置包括第一开关晶体管，其在所述水平扫描周期前导通，并且进行设置使得所述像素电容器两端的电势差超过所述阈值电压；以及第二开关晶体管，其在所述水平扫描周期期间导通，并且对所述像素电容器进行充电直到所述像素电容器两端的所述电势差变为所述阈值电压为止。另外，所述第一开关晶体管响应于在分配给位于所述扫描线前的另一扫描线的在前水平扫描周期期间从所述另一扫描线提供的控制信号导通，从而进行设置使得所述像素电容器两端的所述电势差超过所述阈值电压。另外，所述第一开关晶体管响应于在分配给刚好位于所述扫描线前的另一扫描线的前一个水平扫描周期期间从所述另一扫描线提供的控制信号导通，从而进行设置使得所述像素电容器两端的所述电势差超过所述阈值电压。另外，所述采样晶体管在所述水平扫描周期中所述信号线处于所述视频信号的电势的信号提供周期期间，将从所述信号线提供的所述视频信号采样到所述像素电容器中，而所述校正装置在所述水平扫描周期中所述扫描线处于一特定电势的信号固定周期期间，检测所述驱动晶体管的所述阈值电压并将所述阈值电压写入所述像素电容器中。另外，所述校正装置还在分配给其他扫描线的水平扫描周期中的信号固定周期中工作，并且在每个信号固定周期中以分时方式将所述像素电容器充电到所述阈值电压。另外所述信号固定周期是限定顺序分配给各条扫描线的各个水平扫描周期的水平消隐周期，所述校正装置在每个水平消隐周期中以分时方式将所述像素电容器充电到所述阈值电压。另外，在所述校正装置已在每个信号固定周期中对所述像素电容器充电后，在所述信号线被从所述特定电势切换到所述视频信号的电势之前，所述采样晶体管被关闭并且所述像素电容器在电气上与所述信号线断开。另外，除了所述沟道区域中的所述阈值电压之外，所述驱动晶体管的输出电流还具有对载流子迁移率的依赖性，所述校正装置在所述水平扫描周期的一部分中工作，在所述视频信号被采样的状态中从所述驱动晶体管获得所述输出电流，并且将所述输出电流负反馈到所述像素电容器来校正所述输入电压，以便消除所述输出电流对所述载流子迁移率的依赖性。

[0014] 另外，本发明特征在于，一种像素电路，被设置在提供控制信号的行形式的扫描线和提供视频信号的列形式的信号线彼此交叉的部分处，并且至少包括采样晶体管、连接到所述采样晶体管的像素电容器、连接到所述像素电容器的驱动晶体管和连接到所述驱动晶体管的发光器件，其中，在分配给所述扫描线的水平扫描周期期间，所述采样晶体管响应于从所述扫描线提供的所述控制信号导通，并且将从所述信号线提供的所述视频信号采样到所述像素电容器中，其中，所述像素电容器响应于被采样的视频信号将输入电压施加到所述驱动晶体管的栅极，其中，所述驱动晶体管在预定发光周期期间将根据所述输入电压的输出电流提供给所述发光器件，并且所述输出电流具有对所述驱动晶体管的沟道区域中的阈值电压的依赖性，并且其中，通过从所述驱动晶体管提供的所述输出电流，所述发光器件

按照根据所述视频信号的亮度发光，所述像素电路包括校正装置，该校正装置检测所述驱动晶体管的所述阈值电压，将所述阈值电压写入所述像素电容器中，以便消除所述输出电流对所述阈值电压的依赖性，并且所述校正装置包括第一开关晶体管和第二开关晶体管，所述第一开关晶体管响应于在分配给位于所述扫描线前的另一扫描线的在前水平扫描周期期间从所述另一扫描线提供的控制信号导通，从而进行设置使得所述像素电容器两端的电势差超过所述阈值电压，所述第二开关晶体管在所述水平扫描周期期间导通，并且对所述像素电容器进行充电直到所述像素电容器两端的所述电势差变为所述阈值电压为止。

[0015] 优选地，所述第一开关晶体管响应于在分配给刚好位于所述扫描线前的另一扫描线的前一个水平扫描周期期间从所述另一扫描线提供的控制信号导通，从而进行设置使得所述像素电容器两端的所述电势差超过所述阈值电压。

[0016] 此外，本发明特征在于，一种像素电路，被设置在提供控制信号的行形式的扫描线和提供视频信号的列形式的信号线彼此交叉的部分处，并且至少包括采样晶体管、连接到所述采样晶体管的像素电容器、连接到所述像素电容器的驱动晶体管和连接到所述驱动晶体管的发光器件，其中，在分配给所述扫描线的水平扫描周期期间，所述采样晶体管响应于从所述扫描线提供的所述控制信号导通，并且将从所述信号线提供的所述视频信号采样到所述像素电容器中，其中，所述像素电容器响应于被采样的视频信号将输入电压施加到所述驱动晶体管的栅极，其中，所述驱动晶体管在预定发光周期期间将根据所述输入电压的输出电流提供给所述发光器件，并且所述输出电流具有对所述驱动晶体管的沟道区域中的阈值电压的依赖性，并且其中，通过从所述驱动晶体管提供的所述输出电流，所述发光器件按照根据所述视频信号的亮度发光，所述像素电路包括校正装置，该校正装置在对所述视频信号的采样之前检测所述驱动晶体管的所述阈值电压并将所述阈值电压写入所述像素电容器中，以便消除所述输出电流对所述阈值电压的依赖性，并且所述校正装置在分配给多条扫描线的多个水平扫描周期中工作，并且以分时方式将所述像素电容器充电到所述阈值电压。

[0017] 优选地，所述采样晶体管在分配给所述扫描线的所述水平扫描周期中所述信号线处于所述视频信号的电势的信号提供周期期间，将从所述信号线提供的所述视频信号采样到所述像素电容器中，而所述校正装置在分配给所述多条扫描线的各个水平扫描周期中所述信号线处于一特定电势的各个信号固定周期期间，以分时方式检测所述驱动晶体管的所述阈值电压并将所述像素电容器充电到所述阈值电压。另外，所述信号固定周期是限定顺序分配给各条扫描线的各个水平扫描周期的水平消隐周期，并且所述校正装置在每个水平消隐周期中以分时方式将所述像素电容器充电到所述阈值电压。另外，在所述校正装置已在每个信号固定周期中对所述像素电容器充电后，在所述信号线被从所述特定电势切换到所述视频信号的电势之前，所述采样晶体管被关闭并且所述像素电容器在电气上被从所述信号线断开。

[0018] 根据本发明的像素电路包括校正装置，以便消除向所述发光器件提供的输出电流对阈值电压的依赖性。作为一个特征，所述校正装置在水平扫描周期的一部分中工作，检测所述驱动晶体管的阈值电压，并且预先将所述阈值电压写入像素电容器中。校正阈值电压的操作是通过使用水平扫描周期中执行对去往所述像素电容器的视频信号进行采样的那部分执行的，从而可以简化所述校正装置的配置。具体而言，根据本发明的校正装置可由第

一开关晶体管和第二开关晶体管构成，所述第一开关晶体管在水平扫描周期之前导通并且预先复位所述像素电容器，所述第二开关晶体管在水平扫描周期期间导通并且以阈值电压对所述像素电容器充电。因此，根据本发明的像素电容器可由以下元件构成：构成校正装置的第一和第二开关晶体管、对视频信号进行采样的采样晶体管、以及驱动所述发光元件的驱动晶体管。这样，根据本发明的像素电路可由四个晶体管构成，从而减少了器件的数目。因此，可以减少电源线和栅极线的数目，并且可以减少线路交叉的数目，从而可以提高产量。同时，可以实现面板的高分辨率。

[0019] 另外，根据本发明，上述第一开关晶体管使用位于分配给像素的扫描线前的另一条扫描线作为用于控制的栅极线。具体而言，构成本发明的校正装置的第一开关晶体管响应于在分配给位于所述扫描线前的另一扫描线的在前水平扫描周期期间从所述另一扫描线提供的控制信号导通，从而使像素电容器复位。这样，通过使用属于在前的行的扫描线作为构成校正装置的第一开关晶体管的栅极线，减少了栅极线的总数目，从而减少了线路交叉，结果提高了产量。同时，可以实现面板的高分辨率。

[0020] 此外，根据本发明，结合到像素电路中的校正装置在分配给多条扫描线的多个水平扫描周期中工作，并且以分时方式将所述像素电容器充电到所述阈值电压。这样，通过将阈值电压校正操作分布到多个水平扫描周期中，从而将该操作划分成多次操作，每个水平扫描周期中的阈值电压校正时间可以被设置得较短。因此，可以确保一个水平扫描周期中的视频信号的充足的采样时间。因此，即使在高分辨率并且高频驱动的面板中，也可以充分地将视频信号电势写入像素电容器中。因此，可以实现显示面板的更高分辨率和更高频驱动。

## 附图说明

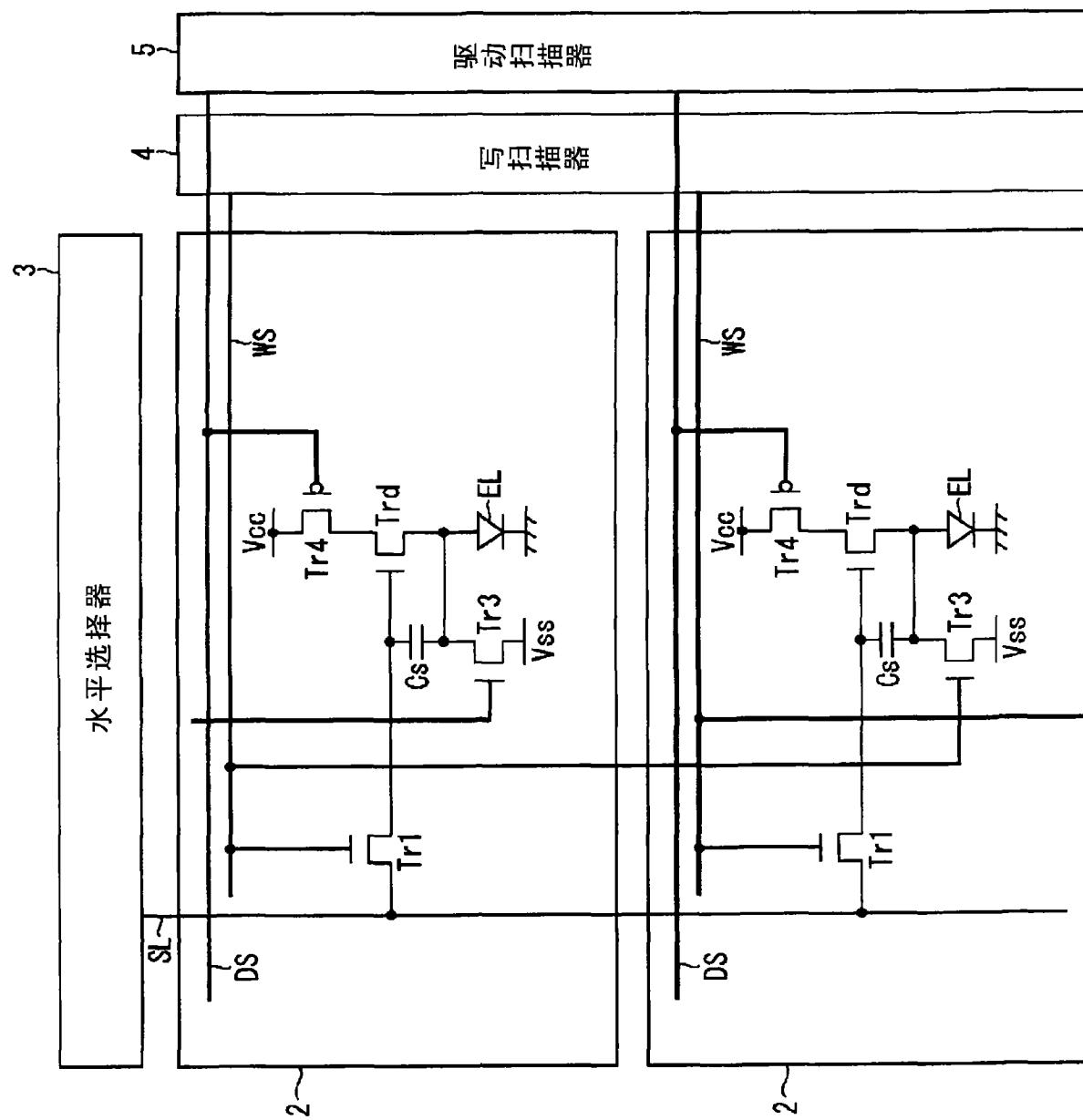

- [0021] 图 1 是示出了根据本发明的显示装置的框图。

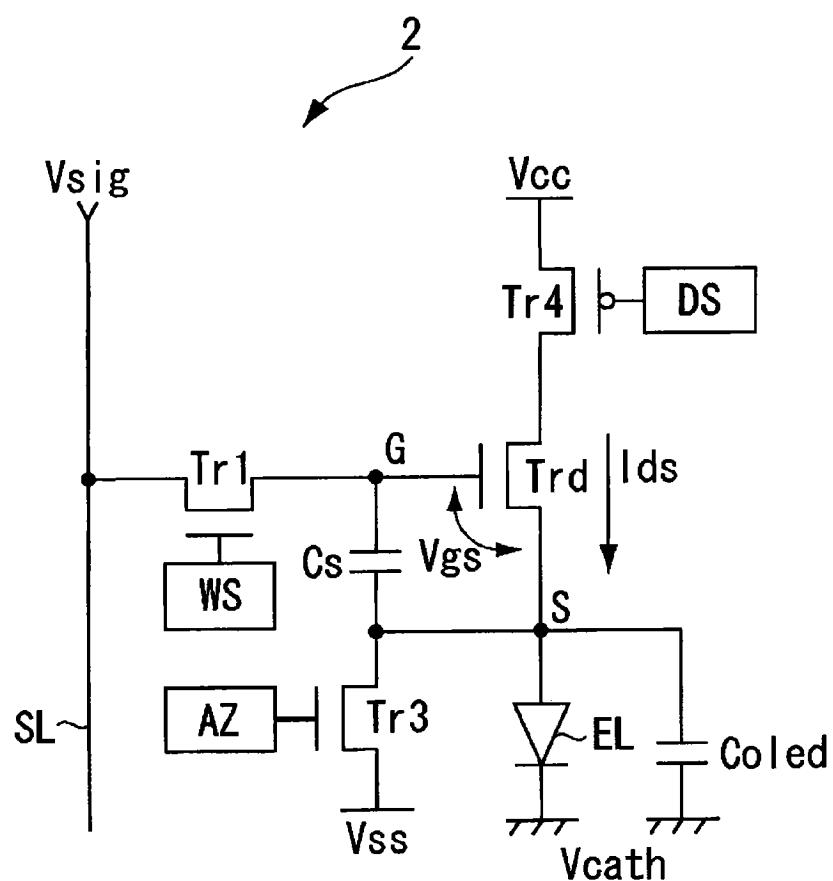

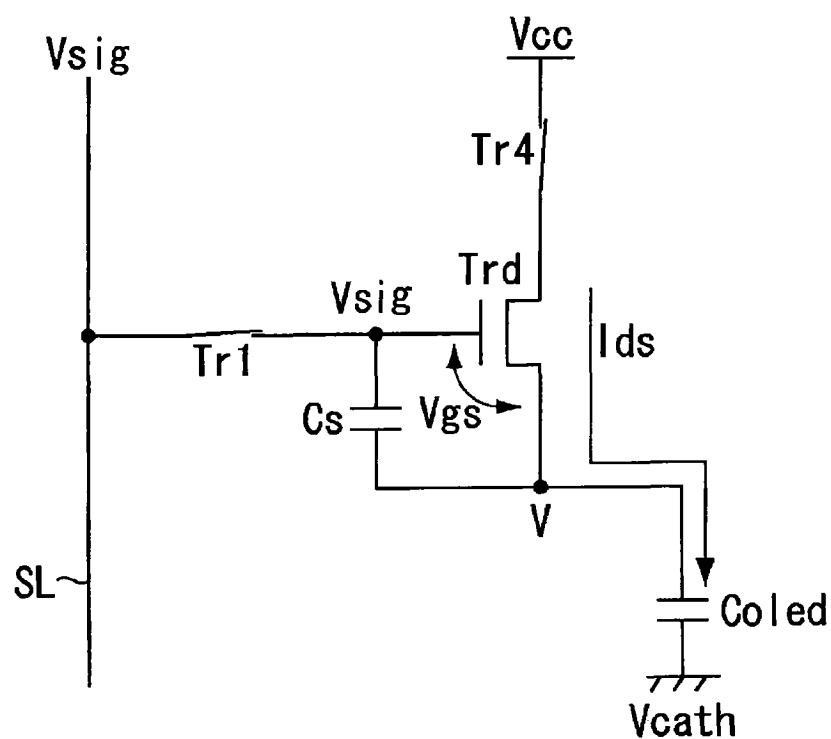

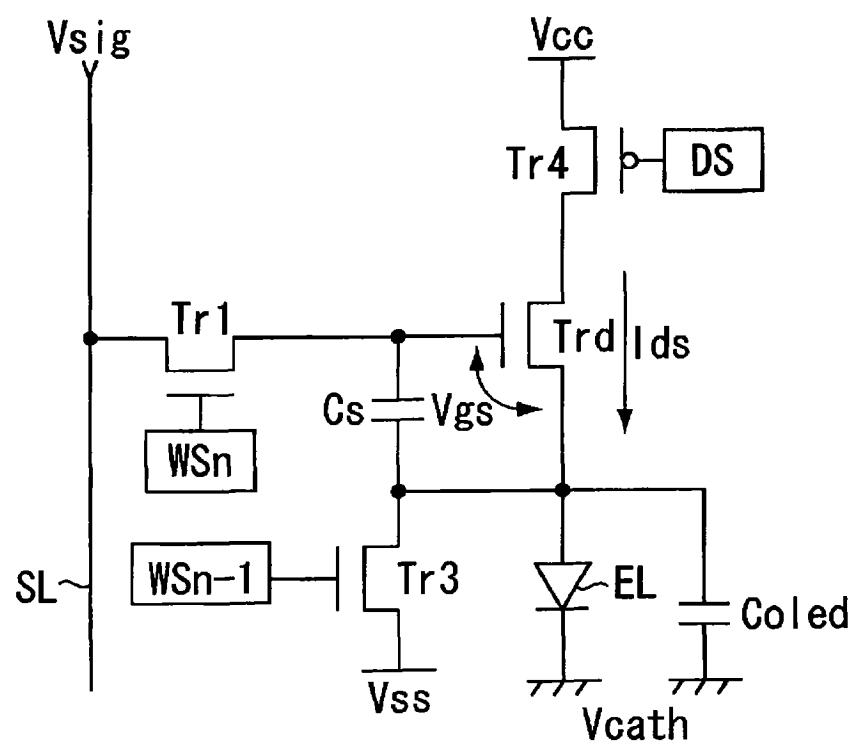

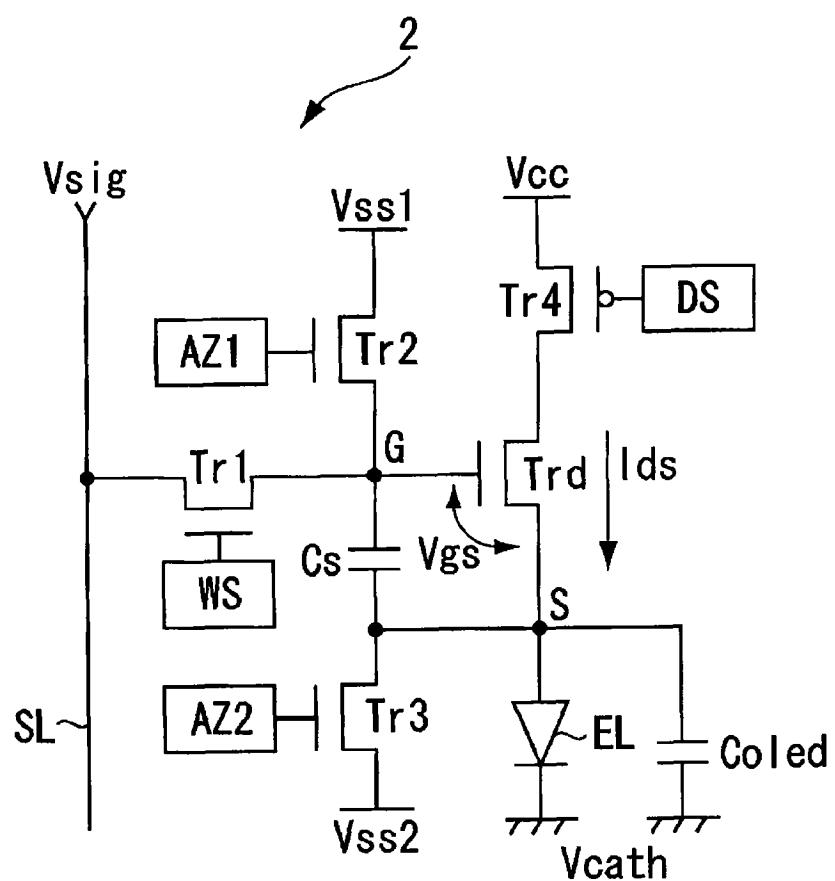

- [0022] 图 2 是示出了图 1 所示显示装置中包括的像素电路的第一实施例的电路图。

- [0023] 图 3 是示出了图 2 所示显示装置中包括的像素电路的示意图。

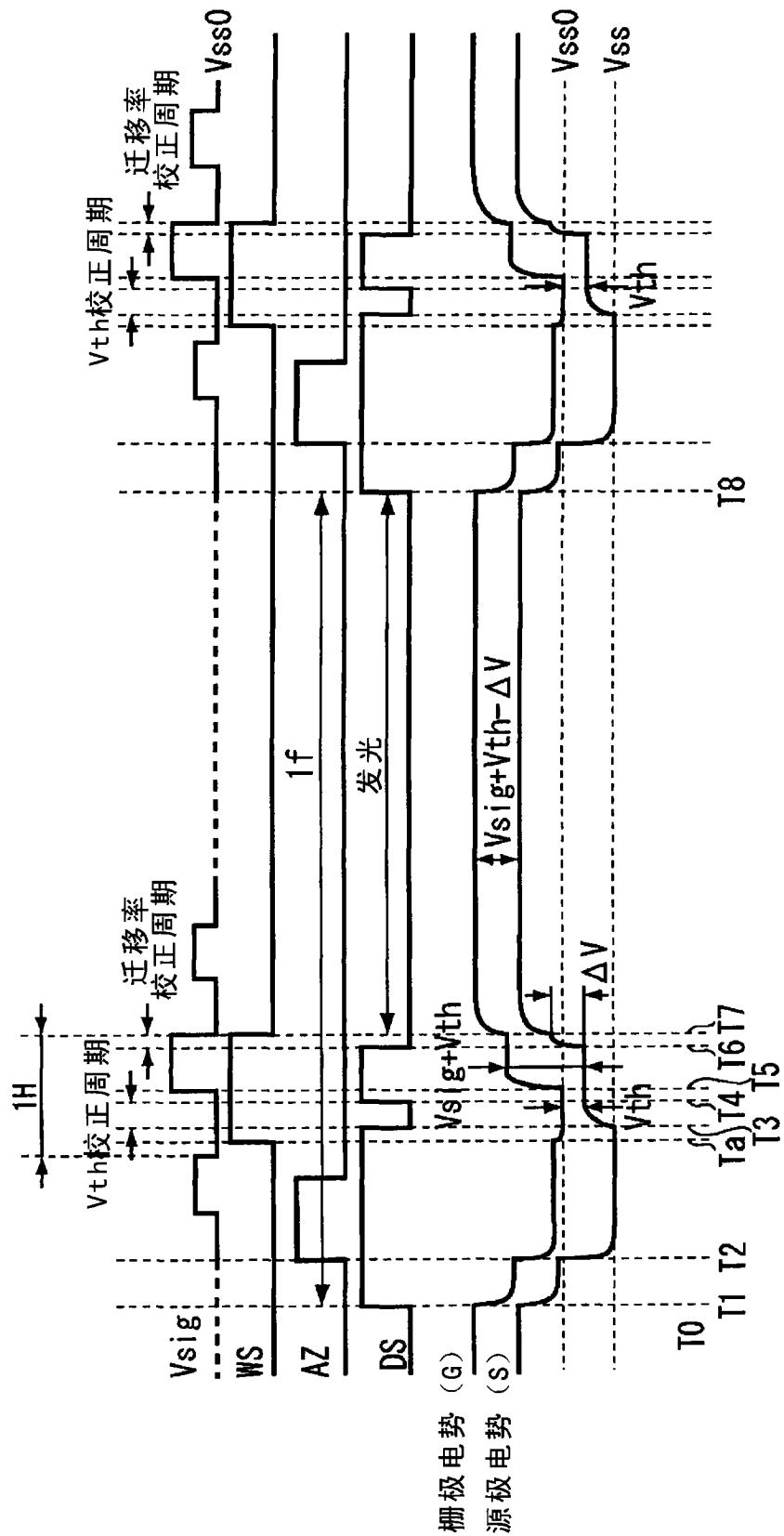

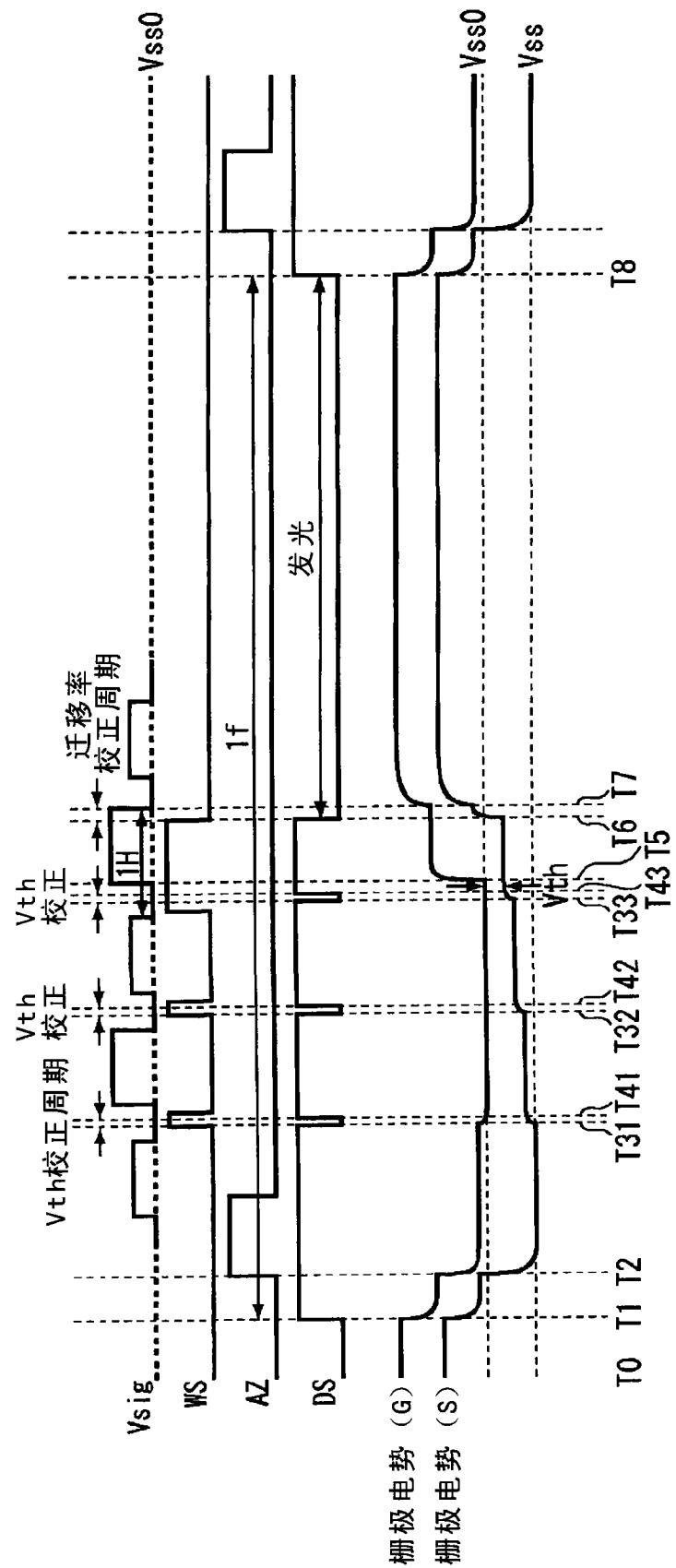

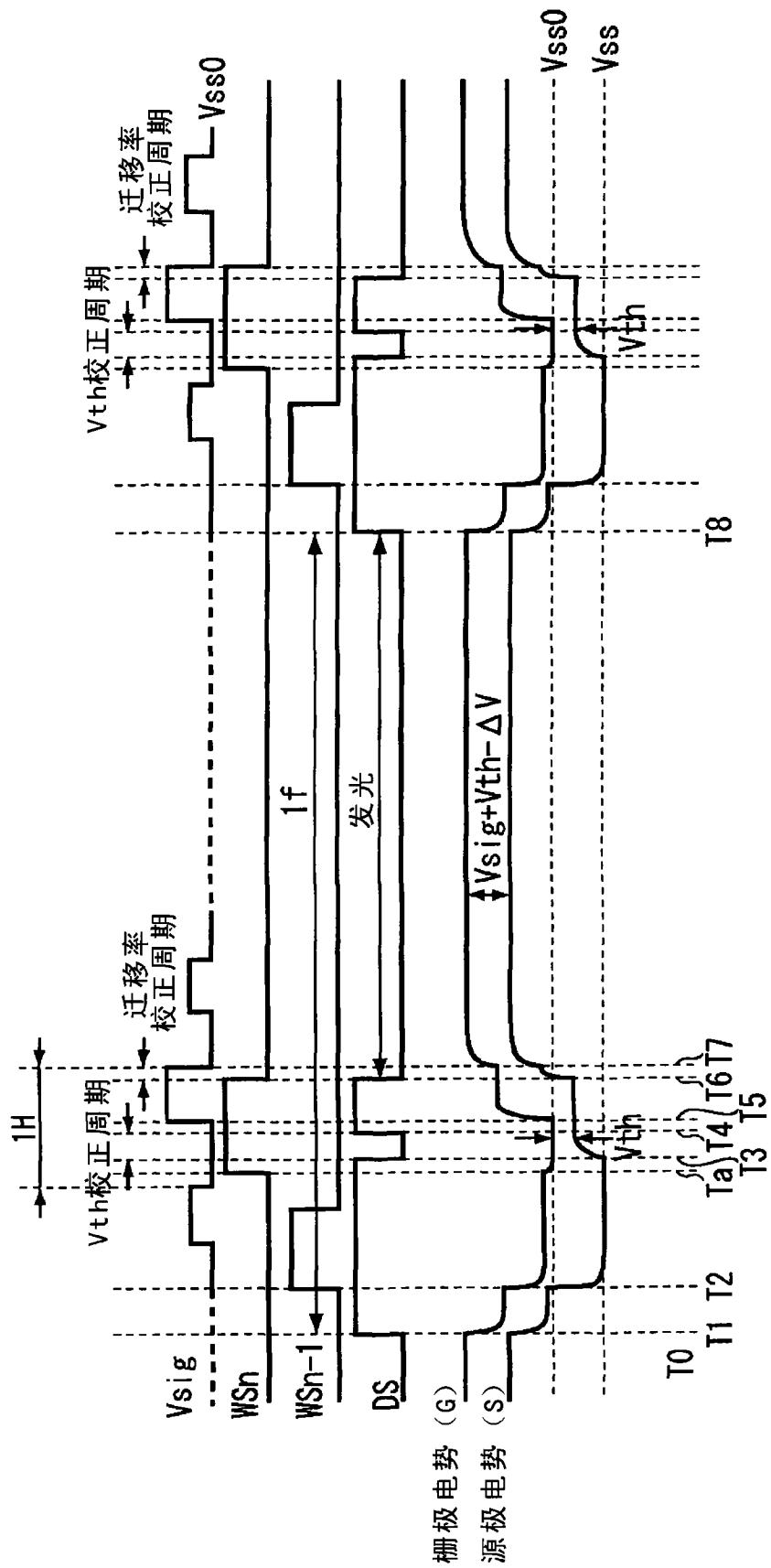

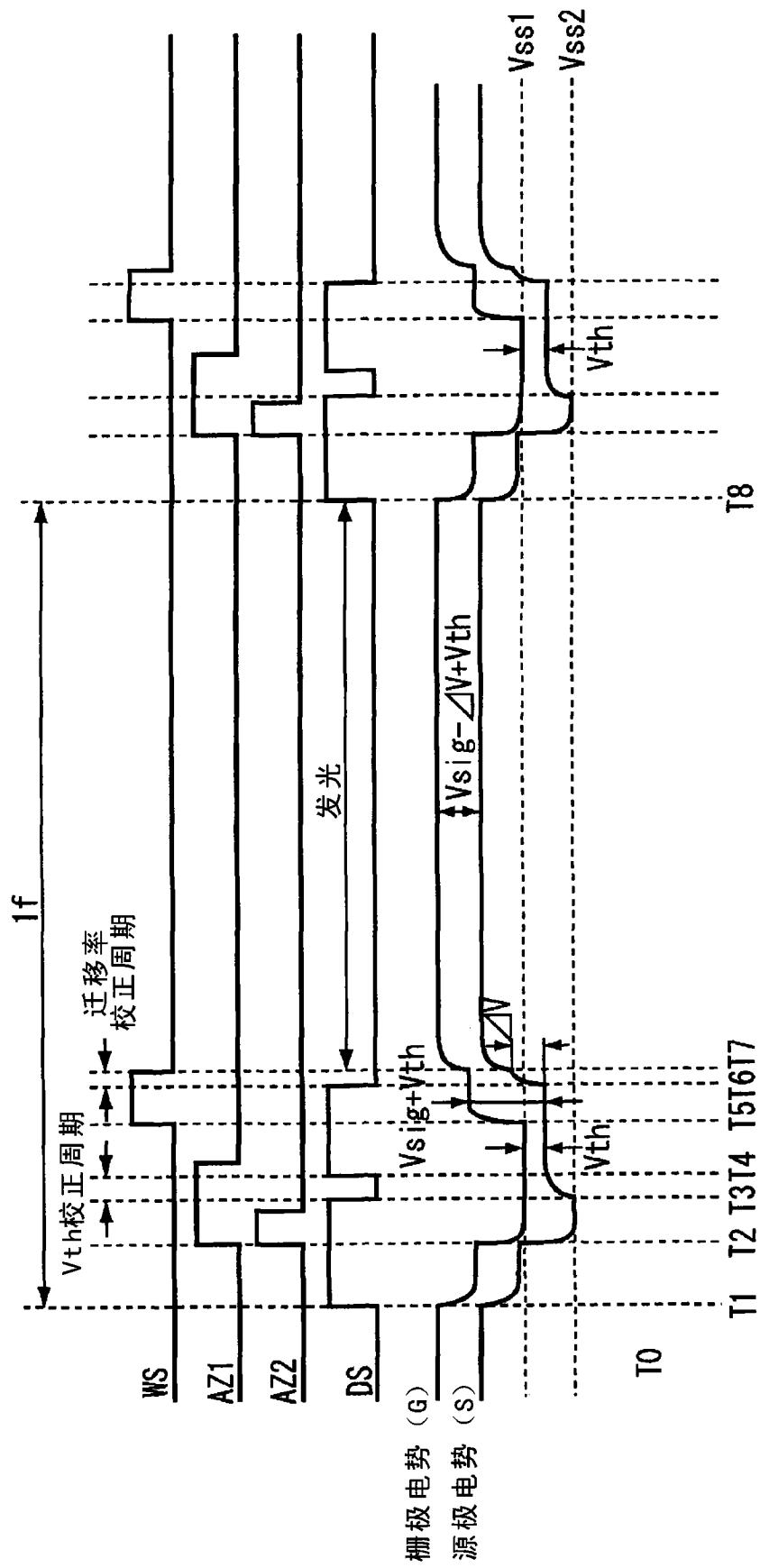

- [0024] 图 4 是用于描述图 3 所示像素电路的操作的时序图。

- [0025] 图 5 是用于描述图 3 所示像素电路的操作的示意图。

- [0026] 图 6 是用于描述操作的图。

- [0027] 图 7 是用于描述操作的示意图。

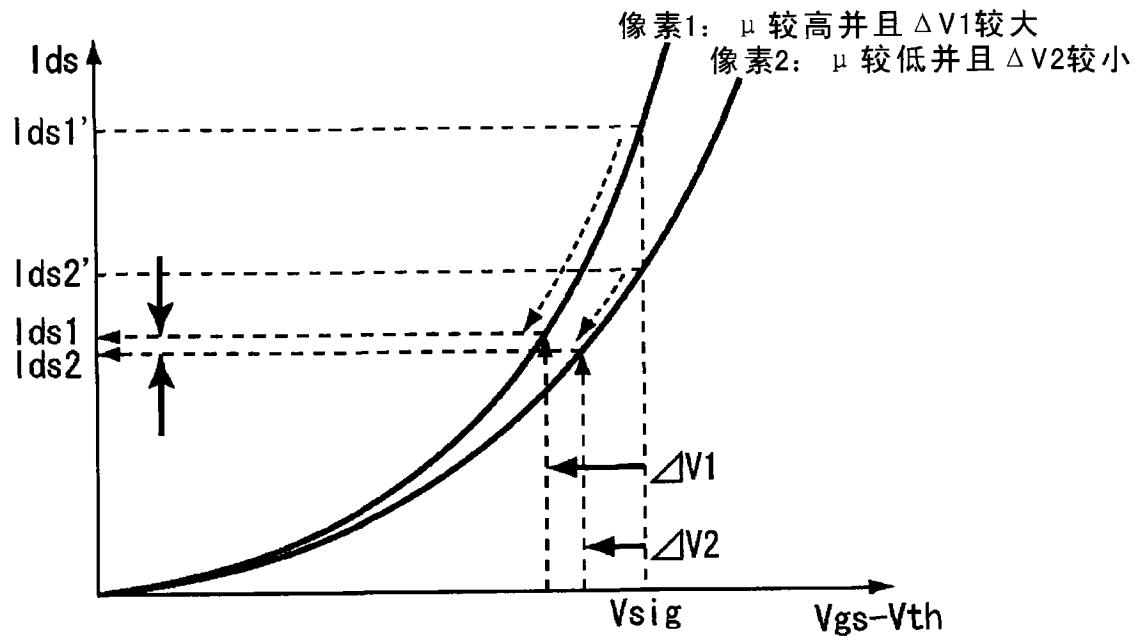

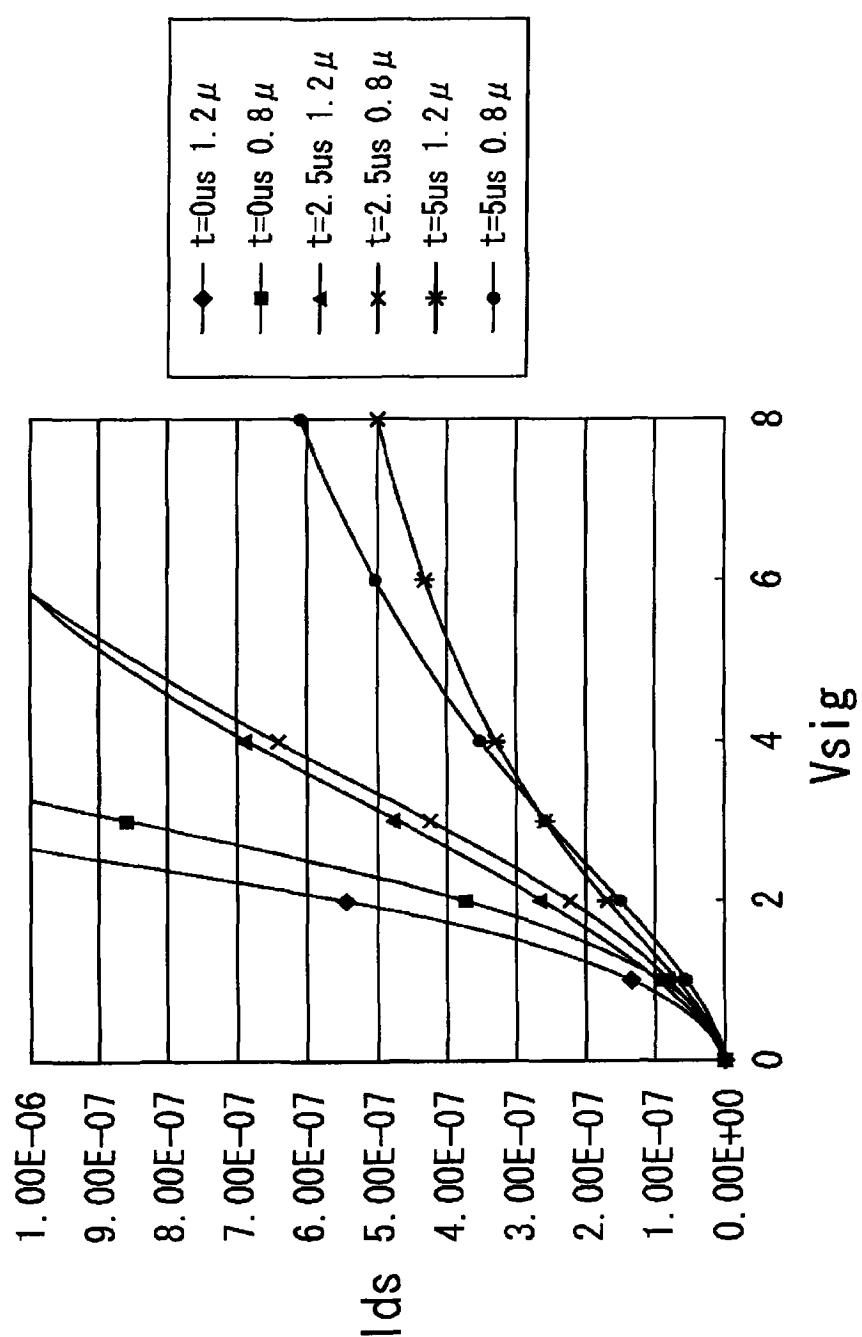

- [0028] 图 8 是示出了图 7 所示像素电路中包括的驱动晶体管的操作特性的图。

- [0029] 图 9 是示出了根据本发明的像素电路的第二实施例的时序图。

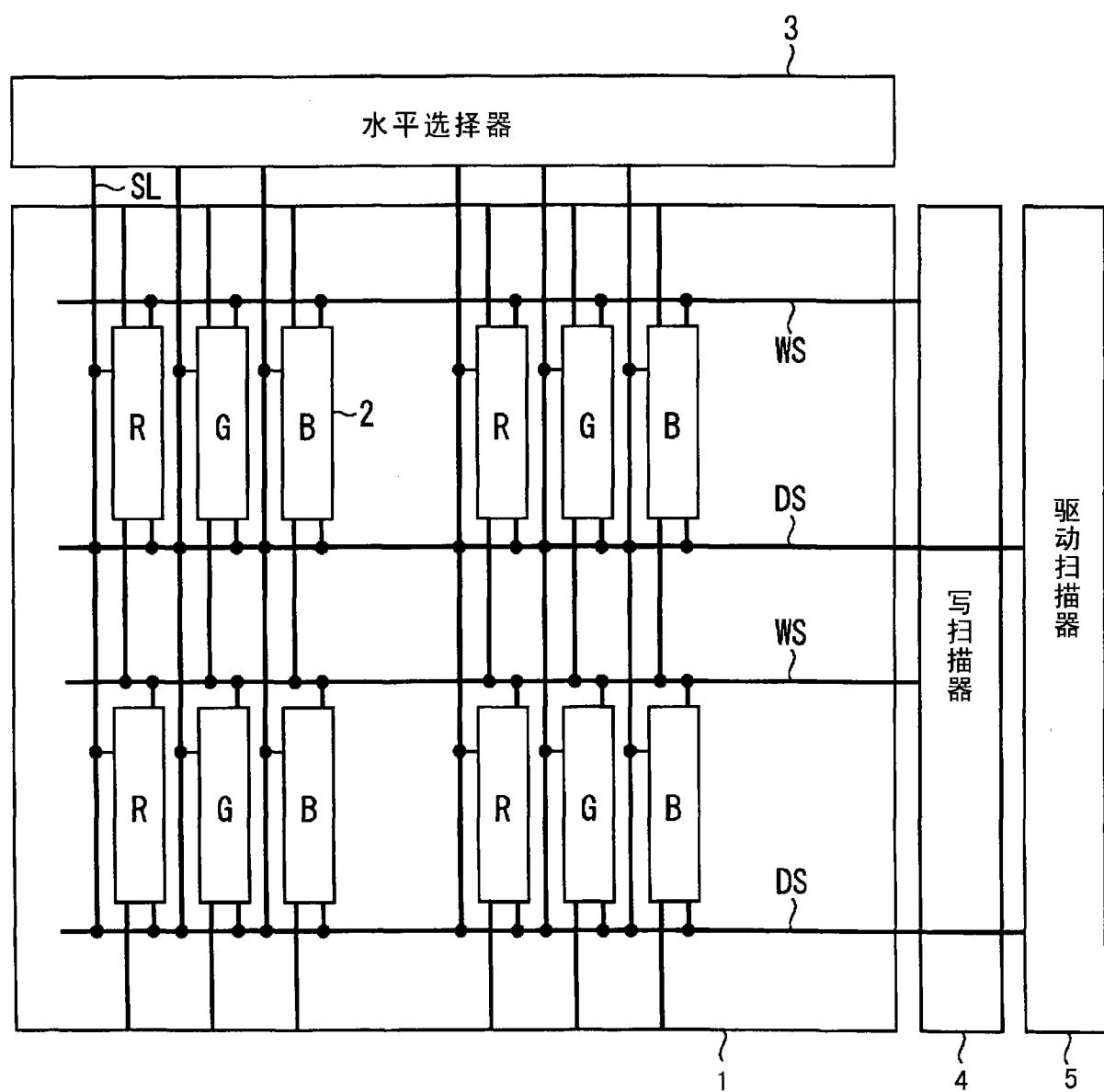

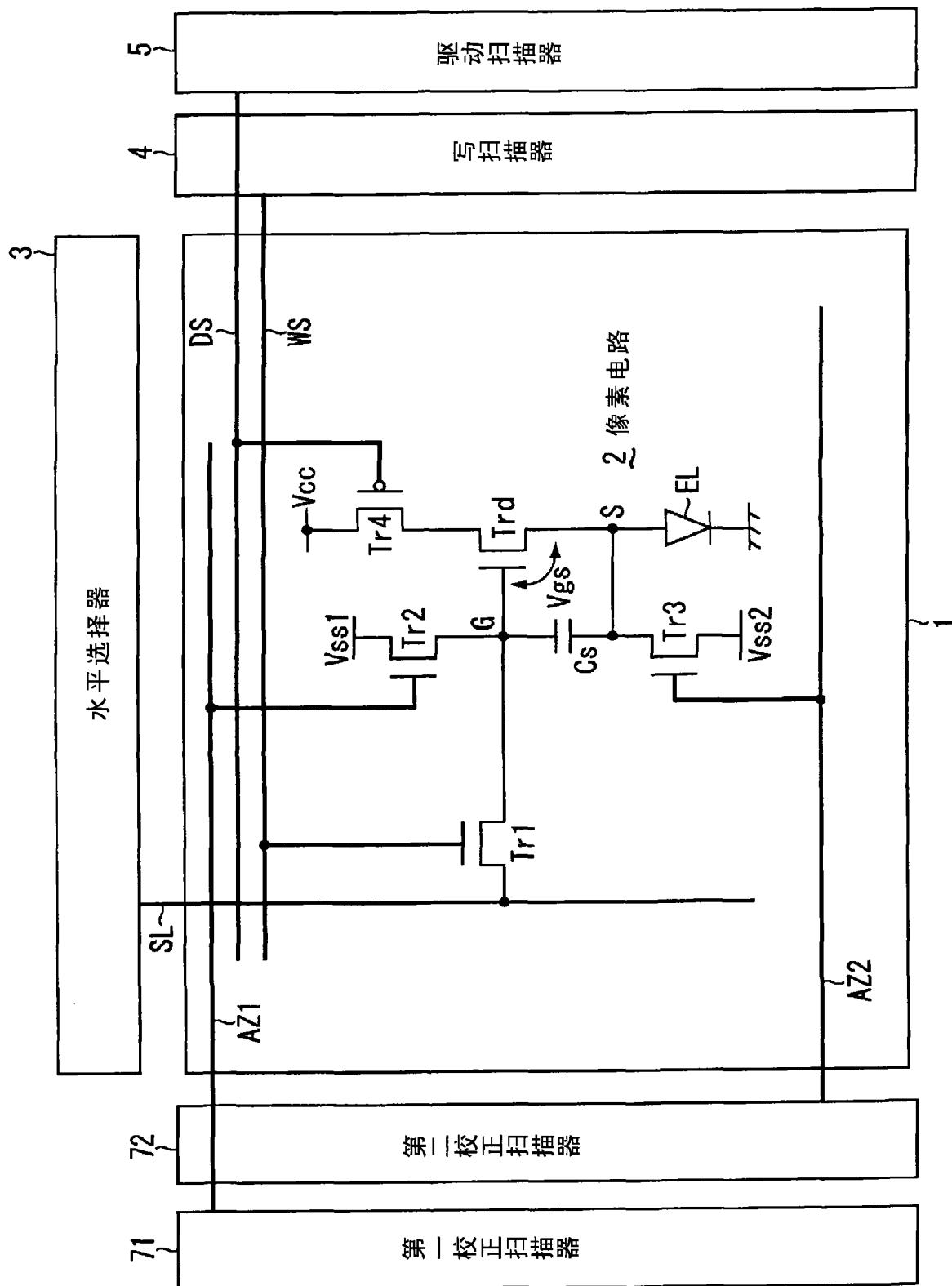

- [0030] 图 10 是示出了根据本发明的显示装置的框图。

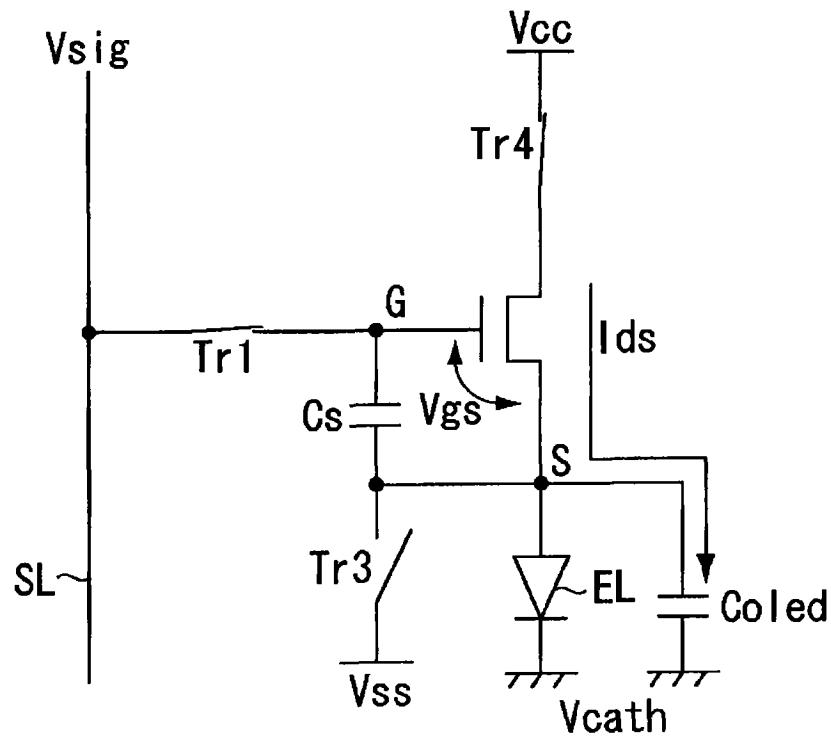

- [0031] 图 11 是示出了图 10 所示显示装置中包括的像素电路的第三实施例的电路图。

- [0032] 图 12 是示出了图 11 所示显示装置中包括的像素电路的示意图。

- [0033] 图 13 是用于描述图 12 所示像素电路的操作的时序图。

- [0034] 图 14 是示出了根据参考示例的显示装置的框图。

- [0035] 图 15 是图 14 所示显示装置中包括的像素电路的示意图。

- [0036] 图 16 是用于描述图 15 所示像素电路的操作的时序图。

## 具体实施方式

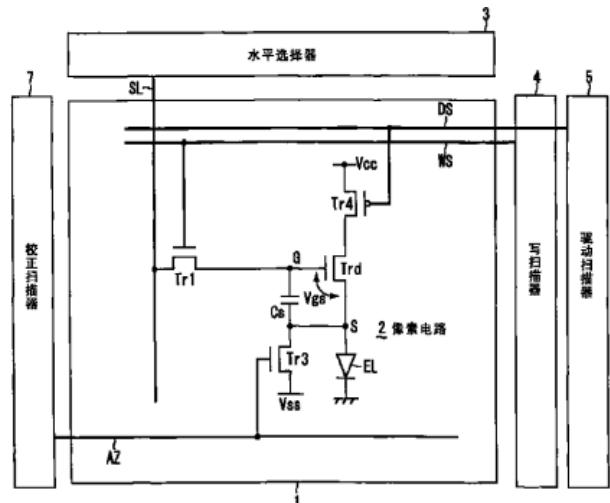

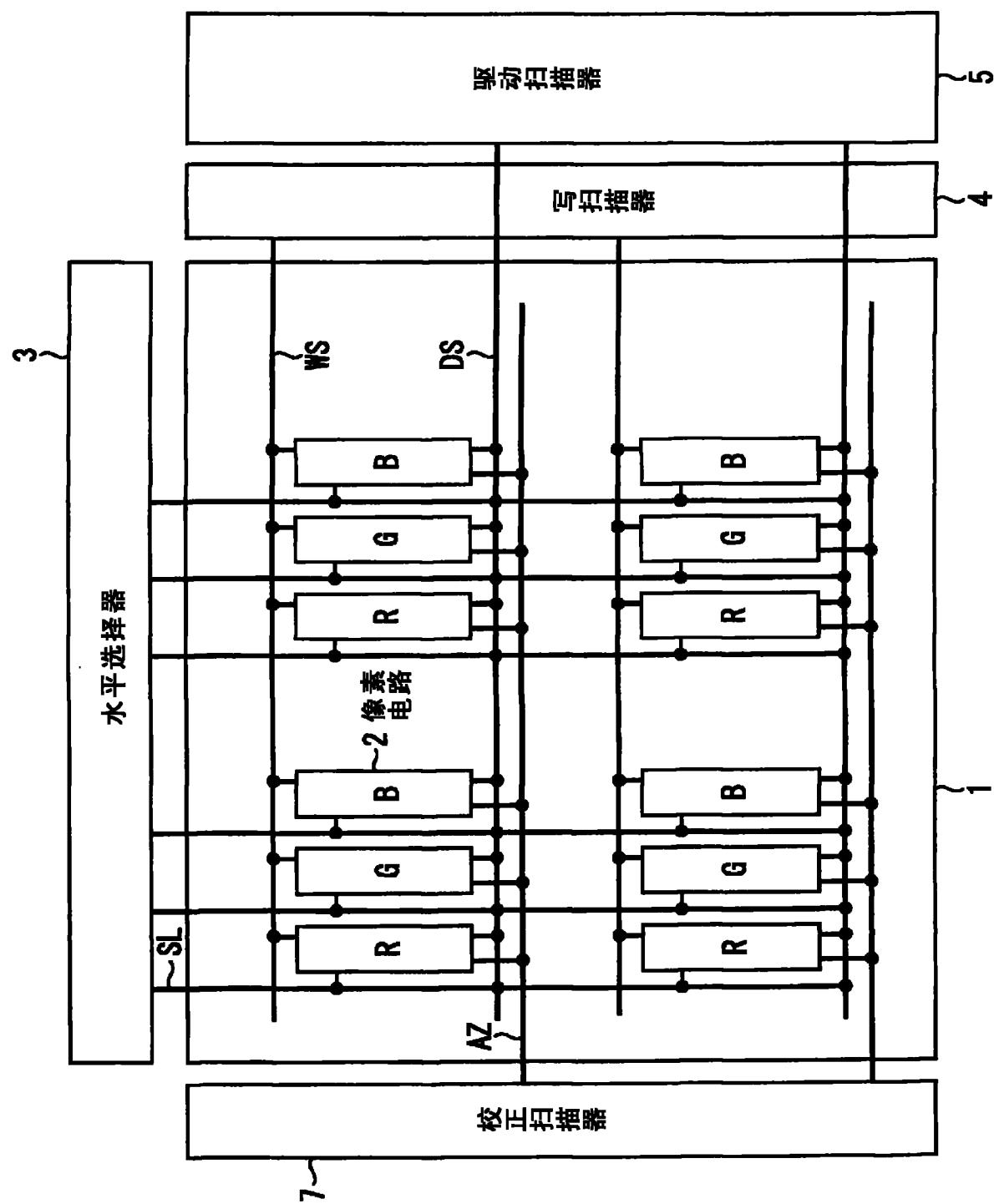

[0037] 在下文中，参考附图详细描述了本发明的实施例。首先，参考图1描述具有阈值电压( $V_{th}$ )校正功能的有源矩阵显示装置的总体配置。如图所示，该有源矩阵显示装置包括作为主单元的像素阵列1和外围电路单元。外围电路单元包括水平选择器3、写扫描器4、驱动扫描器5、校正扫描器7等。像素阵列1包括行形式的扫描线WS、列形式的信号线SL，以及以矩阵形式在前述两种线彼此交叉的位置处布置的像素R、G和B。三原色RGB的像素被提供来使能颜色显示，但是本发明不限于此。像素R、G和B中的每一个包括一个像素电路2。信号线SL由水平选择器3驱动。水平选择器3构成信号单元，并且将视频信号提供给信号线SL。写扫描器4对扫描线WS进行扫描。另外，与扫描线WS并行地提供了其他扫描线DS和AZ。驱动扫描器5对扫描线DS进行扫描。校正扫描器7对扫描线AZ进行扫描。写扫描器4、驱动扫描器5和校正扫描器7构成扫描器单元，并且在每个水平周期中顺序扫描像素行。每个像素电路2在被扫描线WS选中时对来自信号线SL的视频信号进行采样。此外，像素电路2在被扫描线DS选中时响应于被采样的视频信号驱动像素电路2中包括的发光器件。另外，像素电路2在被扫描线AZ扫描时执行预定的校正操作。

[0038] 上述像素阵列1一般形成在绝缘衬底上，例如，玻璃，并且是扁平平板。每个像素电路2包括无定形硅薄膜晶体管(TFT)或者低温多晶硅TFT。在无定形硅TFT的情形中，扫描器单元由与该平板分离的TAB等构成，并且经由柔性线缆被连接到该扁平平板。在低温多晶硅TFT的情形中，信号单元和扫描器单元也可以由低温多晶硅TFT形成，从而像素阵列单元、信号单元和扫描器单元可以整体形成在该扁平平板上。

[0039] 图2是示出了被结合到图1所示显示装置中的像素电路2的第一实施例的电路图。像素电路2包括四个TFT(Tr1、Tr3、Tr4和Trd)，一个电容器元件(像素电容器)Cs和一个发光器件EL。晶体管Tr1、Tr3和Trd是N沟道多晶硅TFT。仅晶体管Tr4是P沟道多晶硅TFT。电容器元件Cs构成像素电路2的像素电容器。发光器件EL是二极管型有机EL器件，包括例如阳极和阴极。但是，本发明不限于此，而是发光器件包括一般通过电流驱动发光的所有器件。

[0040] 在作为像素电路2的主组件的驱动晶体管Trd中，栅极G连接到像素电容器Cs的一端，并且源极S连接到像素电容器Cs的另一端。驱动晶体管Trd的漏极经由第一开关晶体管Tr4连接到电源Vcc。开关晶体管Tr4的栅极连接到扫描线DS。发光器件EL的阳极连接到驱动晶体管Trd的源极，并且阴极接地。地电势可由Vcath表示。另外，第二开关晶体管Tr3存在于驱动晶体管Trd的源极S和预定参考电势Vss之间。晶体管Tr3的栅极连接到扫描线AZ。另一方面，采样晶体管Tr1连接在信号线SL和驱动晶体管Trd的栅极G之间。采样晶体管Tr1的栅极连接到扫描线WS。

[0041] 在该配置中，在分配给扫描线WS的水平扫描周期(1H)期间，采样晶体管Tr1响应于从扫描线WS提供的控制信号WS导通，将从信号线SL提供的视频信号Vsigt采样到像素电容器Cs。像素电容器Cs响应于被采样的视频信号Vsigt，将输入电压Vgs施加到驱动晶体管Trd的栅极。驱动晶体管Trd在预定发光周期期间根据输入电压Vgs向发光器件EL提供输出电流Ids。输出电流Ids具有对驱动晶体管Trd的沟道区域中的阈值电压Vth的依赖性。通过从驱动晶体管Trd提供的输出电流Ids，发光器件EL按照根据视频信号Vsigt的亮度发光。

[0042] 作为本发明的一个特征,像素电路 2 包括校正装置,该校正装置包括第一开关晶体管 Tr3 和第二开关晶体管 Tr4。该校正装置在水平扫描周期 (1H) 的一部分中操作,检测驱动晶体管 Trd 的阈值电压 Vth,并且将其写到像素电容器 Cs 中,从而消除输出电流 Ids 对阈值电压 Vth 的依赖性。该校正装置在其中在水平扫描周期 (1H) 期间采样晶体管 Tr1 导通并且像素电容器 Cs 的一端被信号线 SL 保持在一特定电势 Vss0 的状态中操作,并且对像素电容器 Cs 充电,直到像素电容器 Cs 的另一端与该特定电势 Vss0 之间的电势差变为阈值电压 Vth 为止。该校正装置在水平扫描周期 (1H) 的前半部分中检测驱动晶体管 Trd 的阈值电压 Vth,并将其写入像素电容器 Cs 中,而在水平扫描周期 (1H) 的后半部分中,采样晶体管 Tr1 将从信号线 SL 提供的视频信号 Vsig 采样到像素电容器 Cs。像素电容器 Cs 在驱动晶体管 Trd 的栅极 G 和源极 S 之间施加作为被采样的视频信号 Vsig 和写入的阈值电压 Vth 的总和的输入电压 Vgs,从而消除输出电流 Ids 对阈值电压 Vth 的依赖性。该校正装置包括第一开关晶体管 Tr3 和第二开关晶体管 Tr4,其中第一开关晶体管 Tr3 在水平扫描周期 (1H) 之前导通,并且执行复位以使得像素电容器 Cs 两端的电势差超过阈值电压 Vth,而第二开关晶体管 Tr4 在水平扫描周期 (1H) 期间导通,并且对像素电容器 Cs 进行充电直到像素电容器 Cs 上的电势差变为阈值电压 Vth 为止。当在水平扫描周期 (1H) 中信号线 SL 的电势等于视频信号 Vsig 的电势时的信号提供周期期间采样晶体管 Tr1 将从信号线 SL 提供的视频信号 Vsig 采样到像素电容器 Cs 中,而当在水平扫描周期 (1H) 中信号线 SL 的电势等于一特定电势 Vss0 时的信号固定周期期间该校正装置检测驱动晶体管 Trd 的阈值电压 Vth 并将其写入像素电容器 Cs 中。

[0043] 在该实施例中,来自驱动晶体管 Trd 的输出电流 Ids 除了沟道区域中的阈值电压 Vth 之外还依赖于载流子迁移率  $\mu$ 。为了应对此,本发明的校正装置在水平扫描周期 (1H) 的一部分中操作以便消除输出电流 Ids 对载流子迁移率  $\mu$  的依赖性,在视频信号 Vsig 被采样的状态下从驱动晶体管 Trd 得到输出电流 Ids,负反馈该输出电流 Ids,从而校正输入电压 Vgs。

[0044] 图 3 是图 2 所示显示装置中的像素电路 2 的一部分的视图。为了易于理解,还示出了采样晶体管 Tr1 所采样的视频信号 Vsig、驱动晶体管 Trd 的输入电压 Vgs 和输出电流 Ids,以及发光器件 EL 所保持的电容分量 Coled。另外,还示出了连接到各个晶体管的栅极的扫描线 WS、DS 和 AZ。该像素电路 2 在水平扫描周期期间执行 Vth 校正操作和视频信号写操作。因此,像素电路 2 可由四个晶体管 Tr1、Tr3、Tr4 和 Trd、一个像素电容器 Cs 和一个发光器件 EL 构成。与具有 Vth 校正功能的传统像素电路相比,可以减少至少一个晶体管。因此,可以减少至少一条电源线和一条栅极线(扫描线),从而提高了面板的产量。另外,像素电路的简化的布局还能提高分辨率。

[0045] 图 4 是图 2 和图 3 所示的像素电路的时序图。下面参考图 4 详细描述图 2 和图 3 中所示的像素电路的操作。图 4 沿时间轴 T 示出了施加到各条扫描线 WS、AZ 和 DS 的控制信号的波形。为了简化图示,用与相应的扫描线的代码相同的代码指示每个控制信号。另外,沿时间轴 T 示出了被施加到信号线的视频信号 Vsig 的波形。如图所示,视频信号 Vsig 在每个水平扫描周期 H 的前半部分中处于一特定电势 Vss0,并且在后半部分中处于信号电势。晶体管 Tr1 和 Tr3 是 N 沟道晶体管,因而在扫描线 WS 和 AZ 为高电平时导通,在扫描线 WS 和 AZ 为低电平时截止 (OFF)。另一方面,晶体管 Tr4 是 P 沟道晶体管,因而在扫描线 DS

为高电平时截止,在扫描线 DS 为低电平时导通。另外,该时序图示出了驱动晶体管 Trd 的栅极 G 和源极 S 的电势变化,以及各个控制信号 WS、AZ 和 DS 的波形和视频信号 Vsig 的波形。

[0046] 在图 4 中的时序图中,定时 T1-T8 对应于一场 (1f)。像素阵列的各行在一场比赛期间被顺序扫描一次。该时序图示出了被施加到一行的像素的各个控制信号 WS、AZ 和 DS 的波形。

[0047] 在场开始之前的定时 T0 处,所有控制信号 WS、AZ 和 DS 都为低电平。因此,N 沟道晶体管 Tr1 和 Tr3 处于截止状态中,而仅 P 沟道晶体管 Tr4 处于导通状态中。因此,驱动晶体管 Trd 经由导通状态的晶体管 Tr4 连接到电源 Vcc,从而根据预定输入电压 Vgs 将输出电流 Ids 提供给发光器件 EL。因此,发光器件 EL 在时刻 T0 发光。在该时刻被施加到驱动晶体管 Trd 的输入电压 Vgs 由栅极电势 (G) 和源极电势 (S) 之间的差表示。

[0048] 在场开始的定时 T1 处,控制信号 DS 被从低电平切换到高电平。因此,晶体管 Tr4 被截止并且驱动晶体管 Trd 被从电源 Vcc 断开,使得光发射停止,进入不发光周期。在时刻 T1,晶体管 Tr1、Tr3 和 Tr4 都进入截止状态。

[0049] 然后,在定时 T2 处,控制信号 AZ 从低电平上升到高电平,并且开关晶体管 Tr3 导通。因此,参考电势 Vss 被写入到像素电容器 Cs 的另一端和驱动晶体管 Trd 的源极 S。此刻,驱动晶体管 Trd 的栅极电势处于高阻抗,因此栅极电势 (G) 根据源极电势 (S) 的下降而下降。

[0050] 此后,控制信号 AZ 返回到低电平,并且开关晶体管 Tr3 截止。然后,在定时 Ta 处,控制信号 WS 变为高电平并且采样晶体管 Tr1 导通。此刻,信号线中出现的电势被设置到预定的一特定电势 Vss0。在这里,Vss0 和 Vss 被设置为使得  $Vss0 - Vss > Vth$  得到满足。 $Vss0 - Vss$  是驱动晶体管 Trd 的输入电压 Vgs。在这里,  $Vgs > Vth$  是作为对之后执行的 Vth 校正操作的准备而实现的。换言之,在定时 Ta 处,像素电容器 Cs 的两端都被设置为超过 Vgs 的电压,并且像素电容器 Cs 在 Vth 校正之前被复位。此外,通过设置  $VthEL > Vss$ ,其中 VthEL 是发光器件 EL 的阈值电压,反向偏置被施加到发光器件 EL。这对于之后正常执行 Vth 校正操作是必需的。

[0051] 然后,在定时 T3 处,控制信号 DS 被切换到低电平,开关晶体管 Tr4 导通,Vth 校正被执行。此刻,信号线的电势仍被保持在一特定电势 Vss0,以便准确地执行 Vth 校正。导通开关晶体管 Tr4 使驱动晶体管 Trd 被连接到电源 Vcc,引起输出电流 Ids 流动。因此,像素电容器 Cs 被充电,并且连接到像素电容器 Cs 的另一端的源极电势 (S) 上升。另一方面,像素电容器 Cs 的一端的电势 (栅极电势 G) 被固定到 Vss0。因此,源极电势 (S) 根据像素电容器 Cs 的充电而上升,并且当输入电压 Vgs 刚好达到 Vth 时驱动晶体管 Trd 截止。在驱动晶体管 Trd 截止时,其源极电势 (S) 变为  $Vss0 - Vth$ ,如时序图所示。

[0052] 然后,在定时 T4 处,控制信号 DS 返回到高电平并且开关晶体管 Tr4 截止,使得 Vth 校正操作结束。利用该校正操作,与阈值电压 Vth 相对应的电压被写入像素电容器 Cs 中。

[0053] 这样,当经过了一个水平扫描周期 (1H) 的一半时,从定时 T3 到定时 T4 执行了 Vth 校正,然后信号线的电势从 Vss0 改变到 Vsig。因此,视频信号 Vsig 被写入像素电容器 Cs 中。像素电容器 Cs 与发光器件 EL 的等效电容器 Coled 相比足够小。结果,视频信号 Vsig 的大部分被写入像素电容器 Cs 中。因此,驱动晶体管 Trd 的栅极 G 和源极 S 之间的电压

$V_{gs}$  变为先前被检测出并且被保持的  $V_{th}$  和此刻被采样的  $V_{sig}$  的总和的电平 ( $V_{sig}+V_{th}$ )。栅源电压  $V_{gs}$  变为  $V_{sig}+V_{th}$ , 如图 4 中的时序图所示。对视频信号  $V_{sig}$  的采样继续直到定时  $T_7$ , 此时控制信号  $WS$  返回到低电平时。也就是说, 定时  $T_5$  至定时  $T_7$  对应于采样周期。

[0054] 如上所述, 在本发明中,  $V_{th}$  校正周期  $T_3-T_4$  和采样周期  $T_5-T_7$  包括在一个水平扫描周期 (1H) 中。在 1H 期间, 用于采样的控制信号  $WS$  为高电平。在本发明中,  $V_{th}$  校正和  $V_{sig}$  写入在采样晶体管  $Tr1$  处于导通状态的状态中被执行。因此, 简化了像素电路 2 的配置。

[0055] 在该实施例中, 除了上述  $V_{th}$  校正之外, 同时还执行了对迁移率  $\mu$  的校正。但是, 本发明不限于此, 而是当然可以被应用到不执行迁移率  $\mu$  校正而仅执行简单的  $V_{th}$  校正的像素电路。另外, 在根据本实施例的像素电路 2 中, N 沟道和 P 沟道晶体管被用作除驱动晶体管  $Trd$  之外的晶体管。但是, 本发明不限于此, 而是这些晶体管可以仅由 N 沟道晶体管或者仅由 P 沟道晶体管构成。

[0056] 对迁移率  $\mu$  的校正在从定时  $T_6$  到定时  $T_7$  执行。后面将对此详细描述。在采样周期结束的定时  $T_7$  之前, 在定时  $T_6$  处控制信号  $DS$  变为低电平并且开关晶体管  $Tr4$  导通。因此, 驱动晶体管  $Trd$  被连接到电源  $V_{cc}$ , 从而像素电路从不发光周期进入发光周期。这样, 在采样晶体管  $Tr1$  仍处于导通状态中并且开关晶体管  $Tr4$  已进入导通状态时的  $T_6-T_7$  期间, 执行了对驱动晶体管  $Trd$  的迁移率校正。即, 在本实施例中, 迁移率校正是在采样周期的结束部分和发光周期的开始部分彼此重叠时的周期  $T_6-T_7$  期间执行的。注意, 在执行迁移率校正的发光周期的开始处, 发光器件  $EL$  处于反向偏置状态中, 因此不发光。在该迁移率校正周期  $T_6-T_7$  中, 漏极电流  $I_{ds}$  在驱动晶体管  $Trd$  的栅极  $G$  被固定到视频信号  $V_{sig}$  的电平的状态中在驱动晶体管  $Trd$  中流动。在这里, 设置  $V_{ss0}-V_{th} < V_{thEl}$  允许发光器件  $EL$  处于反向偏置状态中, 从而具有简单的电容特性而不是二极管特性。因此, 在驱动晶体管  $Trd$  中流动的电流  $I_{ds}$  被写入电容器  $C = C_s + C_{oled}$  中, 其是像素电容器  $C_s$  和发光器件  $EL$  的等效电容器  $C_{oled}$  的组合。因此, 驱动晶体管  $Trd$  的源极电势上升。该上升由图 4 中的时序图中的  $\Delta V$  表示。该上升  $\Delta V$  最终被从像素电容器  $C_s$  中保持的栅 - 源电压  $V_{gs}$  中减去, 这等效于负反馈。这样, 通过将驱动晶体管  $Trd$  的输出电流  $I_{ds}$  负反馈到驱动晶体管  $Trd$  的输入电压  $V_{gs}$ , 可以校正迁移率  $\mu$ 。注意, 通过调节迁移率校正周期  $T_6-T_7$  的时间宽度  $t$ , 可以优化负反馈量  $\Delta V$ 。

[0057] 在定时  $T_7$  处, 控制信号  $WS$  变为低电平并且采样晶体管  $Tr1$  截止。结果, 驱动晶体管  $Trd$  的栅极  $G$  与信号线  $SL$  断开。因为停止施加视频信号  $V_{sig}$ , 所以驱动晶体管  $Trd$  的栅极电势 ( $G$ ) 可以上升, 并且随源极电势 ( $S$ ) 上升。在该时间期间, 像素电容器  $C_s$  中保持的栅 - 源电压  $V_{gs}$  维持值 ( $V_{sig}-\Delta V+V_{th}$ )。随着源极电势 ( $S$ ) 上升, 发光器件  $EL$  的反向偏置状态被消除, 从而输出电流  $I_{ds}$  的流入导致发光器件  $EL$  实际开始发光。此刻, 通过在上述晶体管特性表达式中将  $V_{sig}-\Delta V+V_{th}$  代入  $V_{gs}$ , 漏极电流  $I_{ds}$  和栅极电压  $V_{gs}$  之间的关系可以由如下表达式 2 给出。

$$I_{ds} = k \mu (V_{gs}-V_{th})^2 = k \mu (V_{sig}-\Delta V)^2 \quad \cdots \text{表达式 2}$$

[0059] 在上述表达式 2 中,  $k = (1/2)(W/L)C_{ox}$ 。 $V_{th}$  项被从该特性表达式 2 中消去, 并且可理解提供到发光器件  $EL$  的输出电流  $I_{ds}$  不依赖于驱动晶体管  $Trd$  的阈值电压  $V_{th}$ 。基本上, 漏极电流  $I_{ds}$  由视频信号的信号电压  $V_{sig}$  确定。换言之, 发光器件  $EL$  按照根据视频

信号  $V_{sig}$  的亮度发光。此时,利用反馈量  $\Delta V$  校正了  $V_{sig}$ 。该校正量  $\Delta V$  用来消除位于特性表达式 2 的系数部分中的迁移率  $\mu$  的影响。因此,漏极电流  $I_{ds}$  基本上仅依赖于视频信号  $V_{sig}$ 。

[0060] 最后,在定时 T8 处,控制信号 DS 变为高电平,开关晶体管 Tr4 截止,并且发光结束从而该场结束。然后,下一场开始,并且再次重复  $V_{th}$  校正操作、迁移率校正操作和发光操作。

[0061] 图 5 是示出了在迁移率校正周期 T6-T7 中像素电路 2 的状态的电路图。如图所示,在迁移率校正周期 T6-T7 中,采样晶体管 Tr1 和开关晶体管 Tr4 处于导通状态中,而另一个开关晶体管 Tr3 处于截止状态中。在该状态中,驱动晶体管 Tr4 的源极电势 (S) 为  $V_{ss0}-V_{th}$ 。该源极电势 S 是发光器件 EL 的阳极电势。如上所述,设置  $V_{ss0}-V_{th} < V_{thEL}$  允许发光器件 EL 处于反向偏置状态中,并且具有简单的电容特性而不是二极管特性。因此,在驱动晶体管 Trd 中流动的电流  $I_{ds}$  流入像素电容器  $C_s$  和发光器件 EL 的等效电容器  $C_{oled}$  的复合电容器  $C = C_s+C_{oled}$ 。换言之,漏极电流  $I_{ds}$  的一部分被负反馈到像素电容器  $C_s$ ,从而执行了对迁移率的校正。

[0062] 图 6 是示出了上述晶体管特性表达式 2 的图,其中垂直轴指示  $I_{ds}$  并且水平轴指示  $V_{sig}$ 。在该图下面还示出了特性表达式 2。图 6 中的图示出了对像素 1 和 2 进行比较的特性曲线。像素 1 的驱动晶体管的迁移率  $\mu$  相对较高。另一方面,像素 2 中包括的驱动晶体管的迁移率  $\mu$  相对较低。这样,当驱动晶体管由多晶硅薄膜晶体管等构成时,在像素之间迁移率  $\mu$  不可避免地会变化。例如,当相同电平的视频信号  $V_{sig}$  被写入像素 1 和 2 中时,并且未执行任何迁移率校正时,在具有较高迁移率  $\mu$  的像素 1 中流动的输出电流  $I_{ds1}'$  和在具有较低迁移率  $\mu$  的像素 2 中流动的输出电流  $I_{ds2}'$  之间存在较大的差。这样,由于迁移率  $\mu$  变动,在输出电流  $I_{ds}$  中存在极大的差,导致损害了屏幕的均一性。

[0063] 在本发明中,通过将输出电流负反馈到输入电压一侧,消除了迁移率变化。从晶体管特性曲线将清楚,较高的迁移率导致较大的漏极电流  $I_{ds}$ 。因此,迁移率越高负反馈量  $\Delta V$  越大。如图 6 中的图线所示,具有高迁移率  $\mu$  的像素 1 的负反馈量  $\Delta V_1$  大于具有低迁移率的像素 2 的负反馈量  $\Delta V_2$ 。因此当迁移率  $\mu$  较高时施加较大量的负反馈,从而变化可以得到抑制。如图所示,当在具有较高迁移率  $\mu$  的像素 1 中应用了对  $\Delta V$  的校正时,输出电流从  $I_{ds1}'$  显著降低到  $I_{ds1}$ 。另一方面,具有较低迁移率  $\mu$  的像素 2 中的校正量  $\Delta V_2$  较小,因此输出电流  $I_{ds2}'$  未如此显著地下降到  $I_{ds2}$ 。结果,  $I_{ds1}$  和  $I_{ds2}$  变为彼此几乎相等,从而消除了迁移率变化。对迁移率变化的消除是在从背电平到白电平的整个  $V_{sig}$  范围中执行的,从而可以获得非常高的屏幕均一性。总之,当存在具有不同迁移率的像素 1 和 2 时,具有较高迁移率的像素 1 的校正量  $\Delta V_1$  比具有较低迁移率的像素 2 的校正量  $\Delta V_2$  小。即,因为迁移率较大,所以  $\Delta V$  较大并且  $I_{ds}$  的下降值较大。因此,具有不同迁移率的像素的电流值被一致化,从而可以校正迁移率变化。

[0064] 在下文中,将参考图 7 作为参考执行上述迁移率校正的数值分析。如图 7 所示,在晶体管 Tr1 和 Tr4 处于导通状态的状态中,通过将驱动晶体管 Trd 的源极电势作为变量 V 执行分析。将驱动晶体管 Trd 的源极电势 (S) 当作 V,在驱动晶体管 Trd 中流动的漏极电流  $I_{ds}$  由下面的表达式 3 表示。

[0065] [ 式 1 ]

[0066]  $I_{ds} = k \mu (V_{gs} - V_{th})^2 = k \mu (V_{sig} - V - V_{th})^2$  表达式 3

[0067] 另外, 基于漏极电流  $I_{ds}$  和电容器  $C (= C_s + C_{oled})$  之间的关系, 如下面的表达式 4 所示, 满足  $I_{ds} = dQ/dt = CdV/dt$ 。

[0068] [ 式 2 ]

[0069]  $I_{ds} = \frac{dQ}{dt} = C \frac{dV}{dt}$  从而  $\int \frac{1}{C} dt = \int \frac{1}{I_{ds}} dV$  表达式 4

[0070]  $\Leftrightarrow \int_0^t \frac{1}{C} dt = \int_{-V_{th}}^V \frac{1}{k \mu (V_{sig} - V_{th} - V)^2} dV$

[0071]  $\Leftrightarrow \frac{k \mu}{C} t = \left[ \frac{1}{V_{sig} - V_{th} - V} \right]_{-V_{th}}^V = \frac{1}{V_{sig} - V_{th} - V} - \frac{1}{V_{sig}}$

[0072]  $\Leftrightarrow V_{sig} - V_{th} - V = \frac{1}{\frac{1}{V_{sig}} + \frac{k \mu}{C} t} = \frac{V_{sig}}{1 + V_{sig} \frac{k \mu}{C} t}$

[0073] 表达式 3 被代入表达式 4, 对两侧积分。在这里, 假设源极电压  $V$  的初始状态是  $-V_{th}$  并且迁移率变化校正时间 ( $T_6-T_7$ ) 为  $t$ 。通过求解该差分方程, 迁移率校正时间  $t$  的像素电流可以由如下表达式 5 给出。

[0074] [ 式 3 ]

[0075]  $I_{ds} = k \mu \left( \frac{V_{sig}}{1 + V_{sig} \frac{k \mu}{C} t} \right)^2$  表达式 5

[0076] 图 8 是示出了表达式 5 的图, 其中垂直轴表示输出电流  $I_{ds}$ , 并且水平轴表示视频信号  $V_{sig}$ 。作为参数, 设置了迁移率校正周期  $t = 0$  微秒 (us)、2.5 微秒和 5 微秒。此外, 迁移率  $\mu$  也被用作参数, 包括相对较高的  $1.2 \mu$  或相对较低的  $0.8 \mu$ 。可以理解, 与  $t = 0$  微秒中基本未校正迁移率的情形相比, 当  $t = 2.5$  微秒时可以充分地校正迁移率变化。在未校正迁移率的情况下  $I_{ds}$  具有 40% 的变化, 而通过执行迁移率校正可以将变化抑制到 10% 或者更小。但是, 如果校正周期为  $t = 5$  微秒的较长的校正周期, 则由于迁移率  $\mu$  的差异, 输出电流  $I_{ds}$  的变化变得显著。这样,  $t$  需要被设置为最优值, 以便执行适当的迁移率校正。在图 8 所示图中, 最优值为约  $t = 2.5$  微秒。

[0077] 接下来将描述根据本发明的像素电路的第二实施例。在上述第一实施例中,  $V_{th}$  校正和  $V_{sig}$  写入在一个水平扫描周期 (1H) 内被执行, 如图 4 中的时序图所示。因此, 减少了电路元件的数目。但是, 在根据第一实施例的像素电路中, 当在面板中有大量的像素、分辨率较高时, 或者为了较高的图像质量因而场频较高时, 水平扫描周期 (1H) 较短, 从而有可能不能充分执行  $V_{th}$  校正。另一方面, 如果确保了一定的  $V_{th}$  校正周期, 则  $V_{sig}$  写周期被压缩, 因此有可能视频信号不能被充分地写入像素电容器中。通过对第一实施例进行改进, 给出了第二实施例, 第二实施例可以应对面板的高分辨率和高质量。根据第二实施例的像素电路的配置与图 2 所示根据第一实施例的像素电路的配置基本相同。但是, 其操作序列不同, 将参考图 9 中的时序图详细描述。为了易于理解, 与示出第一实施例的操作的图 4 中的时序图中的那些部分相对应的部分由相应的标号标注。

[0078] 参考图 9 可以清楚, 在该实施例中  $V_{th}$  校正周期被划分成多个周期。因此, 尽管每

个 V<sub>th</sub> 校正周期较短,但是通过执行多次校正,可以确保足够长的 V<sub>th</sub> 校正周期。这能够减少电路元件的数目,并且应对面板的较高的分辨率和较高的频率。每个 V<sub>th</sub> 校正周期为非常短的若干微秒,但是多次的总校正量使得能够充分校正 V<sub>th</sub> 的变化。

[0079] 在下文中,将参考图 9 中的时序图详细描述第二实施例的操作。首先,在定时 T1 处,允许控制信号 DS 处于高电平并且开关晶体管 Tr4 截止。然后,在定时 T2 处,允许控制信号 AZ 处于高电平并且开关晶体管 Tr3 导通。因此,参考电势 V<sub>ss</sub> 被写入驱动晶体管 Trd 的源极电势。此刻,栅极电势 (G) 处于高阻抗,从而栅极电势 (G) 根据源极电势 (S) 的下降而下降。

[0080] 此后,在水平消隐 (blanking) 周期中以分时 (timesharing) 方式执行 V<sub>th</sub> 校正,来限定各个水平扫描线。在每个水平消隐周期中,信号线的电势被设置为一特定电势 V<sub>ss0</sub>。在第一 V<sub>th</sub> 校正周期中,控制信号 WS 变为高电平,并且采样晶体管导通。此刻,信号线的电势被设为 V<sub>ss0</sub>,如上所述。在这里,满足 V<sub>ss0</sub>-V<sub>ss</sub> = V<sub>gs</sub> > V<sub>th</sub>,并且 V<sub>gs</sub> > V<sub>th</sub> 允许为后续的 V<sub>th</sub> 校正作准备。另外,当发光器件 EL 的阈值电压为 V<sub>thEL</sub> 时,设置 V<sub>thEL</sub> > V<sub>ss</sub> 允许反向偏置被施加到发光器件 EL。为了正常执行后续 V<sub>th</sub> 校正操作和迁移率校正操作,这是必需的。

[0081] 然后,在将采样晶体管保持在导通状态中时,在定时 T31 处,控制信号 DS 被切换到低电平并且开关晶体管 Tr4 被导通。因此,执行了第一 V<sub>th</sub> 校正。此刻,信号线的电势被保持在该特定电势 V<sub>ss0</sub>,以便准确地执行 V<sub>th</sub> 校正。导通开关晶体管 Tr4 使得驱动晶体管 Trd 输出输出电流 I<sub>ds</sub> 从而趋向截止。然后,在定时 T41 处,控制信号 DS 返回到高电平,开关晶体管 Tr4 截止,第一 V<sub>th</sub> 校正结束。然后,希望在信号线的电势改变并且采样晶体管截止之前控制信号 WS 返回低电平。但是,即使该操作未执行,在该操作中也不会发生问题。

[0082] 在本实施例中,每个 V<sub>th</sub> 校正周期被设置为在水平消隐周期内。因此,在一个 V<sub>th</sub> 校正操作中,驱动晶体管 Trd 不截止,并且其源极电势 (S) 被保持在中间操作点处。

[0083] 当信号线的电势在下一个水平消隐周期中再次变为 V<sub>ss0</sub> 时,执行第二 V<sub>th</sub> 校正操作。即,WS 被切换到高电平,从而使采样晶体管 Tr1 导通。另外,控制线 DS 被切换到低电平,从而使开关晶体管 Tr4 导通。因此,执行了第二 V<sub>th</sub> 校正操作。第二 V<sub>th</sub> 校正周期由 T32-T42 表示。通过执行一系列的 V<sub>th</sub> 校正操作多次,直到驱动晶体管截止为止, V<sub>th</sub> 校正完成。

[0084] 在图 9 中的时序图中示出的示例中,在位于分配给扫描线 WS 的水平扫描周期 (1H) 的开始处的水平消隐周期中执行了第三 V<sub>th</sub> 校正,然后视频信号 V<sub>sig</sub> 被写入像素电容器中,然后迁移率  $\mu$  被校正。第三 V<sub>th</sub> 校正周期由 T33-T43 表示。在第三 V<sub>th</sub> 校正完成后,栅极电势 (G) 和源极电势 (S) 之间的差被设为刚好 V<sub>th</sub>。

[0085] 如上所述,在本实施例中,被结合到像素电路 2 中的校正装置在分配给多条扫描线的多个水平扫描周期中工作,并且以分时方式将像素电容器 Cs 充电到阈值电压 V<sub>th</sub>。在分配给扫描线 WS 的水平扫描周期 (1H) 中,在信号线 SL 处于视频信号的电势 V<sub>sig</sub> 的信号提供周期期间,采样晶体管将从信号线 SL 提供的视频信号采样到像素电容器 Cs。另一方面,在分配给多条扫描线 WS 的水平扫描周期中的每一个中,在信号线 SL 处于一特定电势 V<sub>ss0</sub> 的信号固定周期期间,校正装置检测驱动晶体管 Trd 的阈值电压 V<sub>th</sub>,以分时方式将像素电容器 Cs 充电到阈值电压 V<sub>th</sub>。该信号固定周期是限定被顺序分配给各条扫描线 WS 的各个

水平扫描周期的水平消隐周期。校正装置在每个水平消隐周期中以分时方式将像素电容器 Cs 充电到阈值电压 Vth。优选地，在校正装置已在每个信号固定周期中对像素电容器 Cs 充电后，在信号线 SL 被从该特定电势 Vss0 切换到视频信号的电势 Vsig 前，采样晶体管 Tr1 应当被关闭并且像素电容器 Cs 应当在电气上与信号线 SL 断开。

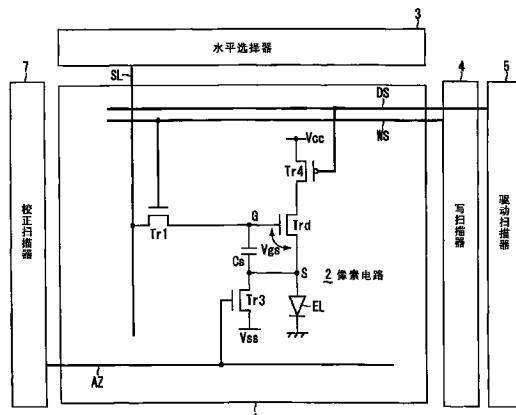

[0086] 图 10 是示出了根据本发明第三实施例的显示装置的示意框图。为了易于理解，与图 1 中示出的根据第一实施例的显示装置的部分相对应的部分用相应的标号表示。不同点在于根据第三实施例的像素阵列 1 包括两类扫描线 WS 和 DS 以进一步减少栅极线，而在第一实施例中设置了三类扫描线（栅极线）WS、DS 和 AZ。具体而言，未设置扫描线 AZ。使用前一级中的扫描线 WS，来替代该级中的扫描线 AZ。因此，可以减少一类栅极线，并且不需要校正扫描器。

[0087] 图 11 示意性地示出了图 10 中示出的显示装置的像素阵列中包括的像素电路中的两个像素电路，前一级中的一个和本级中的另一个。各个像素电路 2 的配置与图 2 中示出的第一实施例的配置基本类似，并且相应的部分由相应的标号表示。每个像素电路 2 包括采样晶体管 Tr1、驱动晶体管 Trd、第一开关晶体管 Tr3、第二开关晶体管 Tr4、像素电容器 Cs 和发光器件 EL。不同点在于前一级的扫描线 WS 连接到第一开关晶体管 Tr3 的栅极。但是，第一级的像素电路 2 不具有前一级的扫描线 WS，因此需要提供另一个。

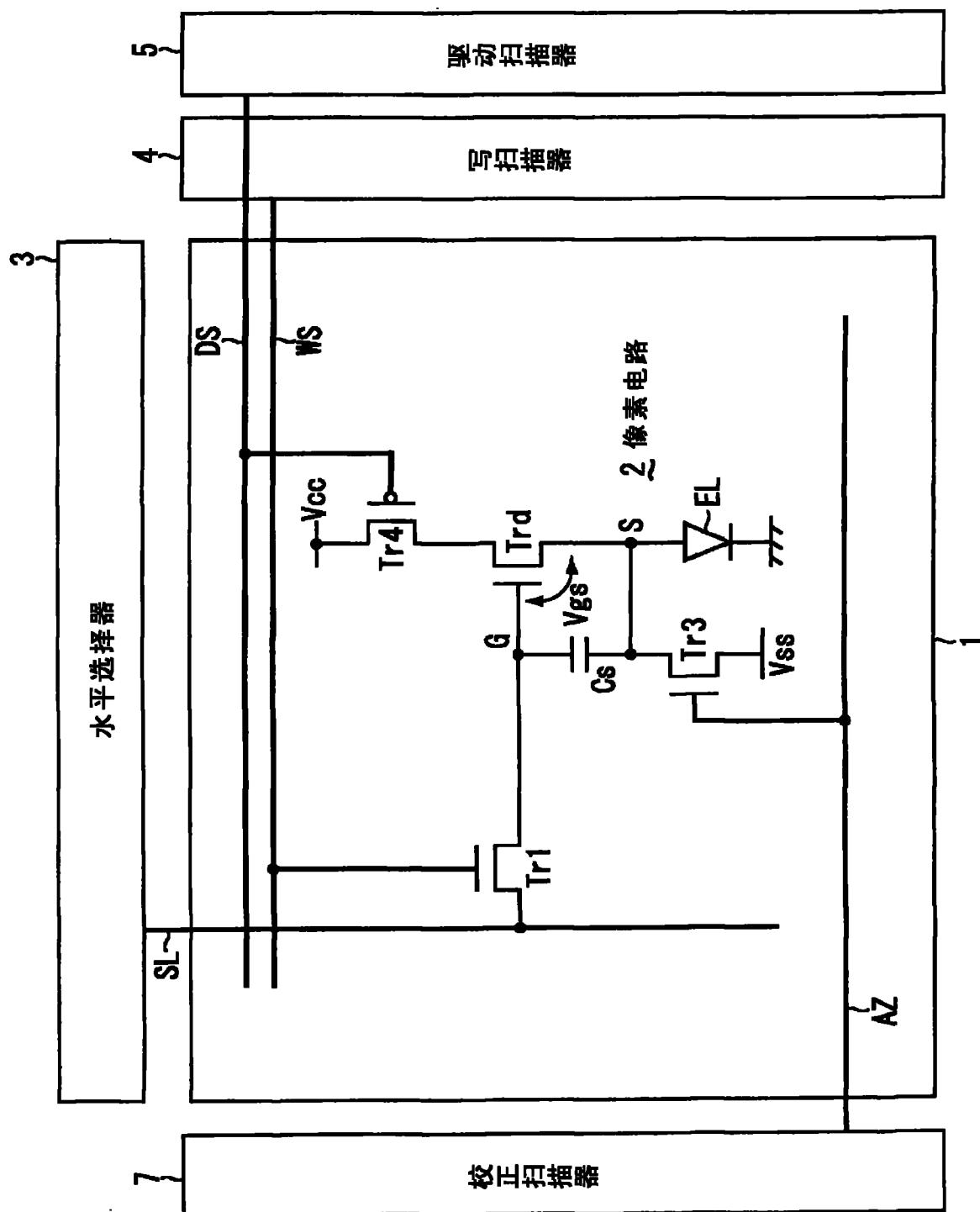

[0088] 图 12 是示出了图 11 中示出的像素阵列中的一个像素电路的示意图。为了易于理解，示出了由采样晶体管 Tr1 采样的视频信号 Vsig、驱动晶体管 Trd 的输入电压 Vgs 和输出电流 Ids、以及由发光器件 EL 保持的电容器分量 Coled。另外，本级中的连接到采样晶体管 Tr1 栅极的扫描线由 WSn 表示，前一级中的连接到第一开关晶体管 Tr3 的栅极的扫描线由 WSn-1 表示，并且连接到第二开关晶体管 Tr4 的栅极的扫描线由 DS 表示。

[0089] 图 13 是示出了图 12 中示出的像素电路的操作的时序图。为了易于理解，与图 4 中示出的第一实施例的时序图中的部分相对应的部分用相应的标号表示。该时序图沿时间轴 T 示出了被施加到各个扫描线 WSn、WSn-1 和 DS 的控制信号的波形。为了简化图示，控制信号由与对应的扫描线的代码相同的代码表示。另外，该时序图还示出了驱动晶体管 Trd 的栅极 G 和源极 S 的电势变化，以及被施加到信号线的视频信号 Vsig 的波形、各个控制信号 WSn、WSn-1 和 DS 的波形。如图所示，在每个水平扫描周期的前半部分中，视频信号 Vsig 被固定到一特定电势 Vss0，并且在后半部分中视频信号 Vsig 处于视频信号电势。在定时 T1 处，控制信号 DS 变为高电平，开关晶体管 Tr4 截止，并且像素电路进入不发光状态中。在定时 T2 处，前一级的控制信号 WSn-1 变为高电平并且开关晶体管 Tr3 导通。因此，像素电容器 Cs 被复位并且  $Vgs > Vth$  被设置。即，执行了 Vth 校正的准备工作。在定时 Ta 处，本级的控制信号 Wsn 上升到高电平，并且采样晶体管 Tr1 导通。然后，在定时 T3 处，控制信号 DS 变为低电平，并且第二开关晶体管 Tr4 导通。因此，在像素电容器 Cs 的一端被固定到一特定电势 Vss0 的状态中像素电容器 Cs 被充电以写 Vth。即，执行了 Vth 校正操作。然后，在定时 T5 处，视频信号 Vsig 被写入像素电容器 Cs 中。此外，在定时 T6 处，校正迁移率  $\mu$  的操作被执行，并且发光状态开始。

[0090] 如上所述，第三实施例具有校正装置，用于检测驱动晶体管 Trd 的阈值电压 Vth 并且将其写入像素电容器 Cs 中，以便消除输出电流 Ids 对阈值电压 Vth 的依赖性。该校正装置包括第一开关晶体管 Tr3 和第二开关晶体管 Tr4。在分配给其他扫描线 WSn-1 的前一水

平扫描周期期间,第一开关晶体管 Tr3 响应于从位于本级的扫描线 WSN 之前的另一扫描线 WSN-1 提供的控制信号 WSN-1 导通,从而进行设置使得像素电容器 Cs 两端的电势差超过阈值电压 Vth。第二开关晶体管 Tr4 在分配给本级的水平扫描周期 (1H) 中导通,并且对像素电容器 Cs 充电直到像素电容器 Cs 上的电势差 (Vgs) 变为阈值电压 Vth 为止。在图 13 所示实施例中,位于本级的扫描线 WSN 紧挨着的前面的扫描线 WSN-1 被用作前一级的扫描线。在某些情形中,扫描线 WSN-1 前的扫描线 WSN-2 或扫描线 WSN-2 前的扫描线而不是扫描线 WSN-1 可以被用作第一开关晶体管 Tr3 的栅极线。这样,在本实施例中,扫描线 WS 被两个像素共享,从而可以减少一类栅极线。这导致提高了面板的产量。另外,简化的布局使得能够实现较高的面板分辨率。

[0091] 图 14 是示出了像素电路的参考示例的框图。为了易于理解,与图 2 中示出的第一实施例的部分相对应的部分由相应的标号表示。不同点在于,在本参考示例中,在水平扫描周期前执行 Vth 校正操作。因此,为了准备 Vth 校正,除了开关晶体管 Tr3,开关晶体管 Tr2 也是必需的。一个晶体管 Tr3 使像素电容器 Cs 的源极侧端子复位,而额外的晶体管 Tr2 使像素电容器 Cs 的栅极侧端子复位。为了驱动额外的开关晶体管 Tr2,额外的扫描线 AZ1 和额外的校正扫描器 71 是必需的。在本发明中,对像素电容器 Cs 的栅极侧端子的设置是在水平扫描周期中被执行的,从而晶体管 Tr2 是不必要的。晶体管 Tr2 将电源电压 Vss1 写入栅极 G。另一方面,在本发明中,从信号线 SL 提供的固定电势 Vss0 在水平扫描周期期间被写入。

[0092] 在下文中,描述了根据图 14 中示出的参考示例的操作。该有源矩阵显示装置包括充当主单元的像素阵列 1 和外围电路单元。外围电路单元包括水平选择器 3、写扫描器 4、驱动扫描器 5、第一校正扫描器 71 和第二校正扫描器 72 等。像素阵列 1 包括行形式的扫描线 WS、列形式的信号线 SL,以及以矩阵形式在前述两种线彼此交叉的位置处布置的像素电路 2。在该图中,为了易于理解,通过放大一个像素电路 2 仅示出了该一个像素电路 2。信号线 SL 由水平选择器 3 驱动。水平选择器 3 构成信号单元,并且将视频信号提供给信号线 SL。写扫描器 4 对扫描线 WS 进行扫描。另外,与扫描线 WS 并行还提供了其他扫描线 DS、AZ1 和 AZ2。驱动扫描器 5 对扫描线 DS 进行扫描。第一校正扫描器 71 对扫描线 AZ1 进行扫描。第二校正扫描器 72 对扫描线 AZ2 进行扫描。写扫描器 4、驱动扫描器 5、第一校正扫描器 71 和第二校正扫描器 72 构成扫描器单元,并且在每个水平周期中顺序扫描像素行。每个像素电路 2 在被扫描线 WS 选中时对来自信号线 SL 的视频信号进行采样。此外,像素电路 2 在被扫描线 DS 选中时响应于被采样的视频信号驱动像素电路 2 中包括的发光器件 EL。另外,像素电路 2 在被扫描线 AZ1 和 AZ2 扫描时执行预定的校正操作。

[0093] 像素电路 2 包括五个薄膜晶体管 (Tr1-Tr4 和 Trd),一个电容器元件 (像素电容器) Cs 和一个发光器件 EL。晶体管 Tr1-Tr3 和 Trd 是 N 沟道多晶硅 TFT。仅晶体管 Tr4 是 P 沟道多晶硅 TFT。电容器元件 Cs 构成像素电路 2 的像素电容器。发光器件 EL 是二极管型有机 EL 器件,包括例如阳极和阴极。

[0094] 在充当像素电路 2 的主元件的驱动晶体管 Trd 中,其栅极 G 连接到像素电容器 Cs 的一端,并且其源极 S 连接到像素电容器 Cs 的另一端。另外,驱动晶体管 Trd 的栅极 G 经由开关晶体管 Tr2 连接到另一参考电势 Vss1。驱动晶体管 Trd 的漏极经由开关晶体管 Tr4 连接到电源 Vcc。开关晶体管 Tr2 的栅极连接到扫描线 AZ1。开关晶体管 Tr4 的栅极连接

到扫描线 DS。发光器件 EL 的阳极连接到驱动晶体管 Trd 的源极 S，并且阴极接地。该地电势可由  $V_{cath}$  表示。另外，开关晶体管 Tr3 存在于驱动晶体管 Trd 的源极 S 和预定参考电势  $V_{ss2}$  之间。晶体管 Tr3 的栅极连接到扫描线 AZ2。另一方面，采样晶体管 Tr1 连接在信号线 SL 和驱动晶体管 Trd 的栅极 G 之间。采样晶体管 Tr1 的栅极连接到扫描线 WS。

[0095] 在该配置中，在预定采样周期期间，采样晶体管 Tr1 响应于从扫描线 WS 提供的控制信号 WS 导通，并且将从信号线 SL 提供的视频信号 Vsig 采样到像素电容器 Cs。电容器单元 Cs 响应于被采样的视频信号 Vsig，将输入电压  $V_{gs}$  施加到驱动晶体管的栅极 G 和源极 S 之间。驱动晶体管 Trd 在预定发光周期期间根据输入电压  $V_{gs}$  向发光器件 EL 提供输出电流  $I_{ds}$ 。注意，输出电流（漏极电流） $I_{ds}$  依赖于驱动晶体管 Trd 的沟道区域中的载流子迁移率  $\mu$  和阈值电压  $V_{th}$ 。通过从驱动晶体管 Trd 提供的输出电流  $I_{ds}$ ，发光器件 EL 按照根据视频信号 Vsig 的亮度发光。

[0096] 像素电路 2 包括包含开关晶体管 Tr2 至 Tr4 的校正装置，并且对在发光周期的开始时预先保持在电容器单元 Cs 中的输入电压  $V_{gs}$  进行校正，以便消除输出电流  $I_{ds}$  对载流子迁移率  $\mu$  的依赖性。具体而言，该校正装置 (Tr2 至 Tr4) 响应于从扫描线 WS 和 DS 提供的控制信号 WS 和 DS 在采样周期的一部分中工作，在视频信号 Vsig 被采样的状态中从驱动晶体管 Trd 获得输出电流  $I_{ds}$ ，将该输出电流  $I_{ds}$  负反馈到电容器单元 Cs，从而校正了输入电压  $V_{gs}$ 。此外，该校正装置 (Tr2 至 Tr4) 在采样周期之前检测驱动晶体管 Trd 的阈值电压  $V_{th}$ ，并且将检测出的阈值电压  $V_{th}$  加到输入电压  $V_{gs}$ ，以便消除输出电流  $I_{ds}$  对阈值电压  $V_{th}$  的依赖性。

[0097] 驱动晶体管 Trd 是 N 沟道晶体管。其漏极连接到电源  $V_{cc}$  侧，而源极连接到发光器件 EL 侧。在该情形中，在发光周期的与采样周期的后部分重叠的开始部分处，上述校正装置从驱动晶体管 Trd 获得输出电流  $I_{ds}$  并将该输出电流  $I_{ds}$  负反馈到电容器单元 Cs 侧。此刻，该校正装置允许在发光周期的开始部分处从驱动晶体管 Trd 的源极 S 侧获得的输出电流  $I_{ds}$  流入到由发光器件 EL 保持的电容器中。具体而言，发光器件 EL 是包括阳极和阴极的二极管型发光器件。阳极侧连接到驱动晶体管 Trd 的源极 S，而阴极侧接地。在本配置中，校正装置 (Tr2-Tr4) 预先将发光器件 EL 的阳极和阴极之间设置到反向偏置状态，并且在从驱动晶体管 Trd 的源极 S 侧获得的输出电流  $I_{ds}$  流入发光器件 EL 时允许二极管型发光器件 EL 作为电容器元件工作。另外，该校正装置可以调节采样周期中从驱动晶体管 Trd 获得输出电流  $I_{ds}$  的时间宽度  $t$ ，从而优化到电容器单元 Cs 的输出电流  $I_{ds}$  的负反馈量。

[0098] 图 15 是示出了图 14 中示出的显示装置中的像素电路的一部分的示意图。为了易于理解，示出了由采样晶体管 Tr1 所采样的视频信号 Vsig、驱动晶体管 Trd 的输入电压  $V_{gs}$  和输出电流  $I_{ds}$ 、以及由发光器件 EL 保持的电容器分量  $C_{oled}$ 。下文中，将基于图 15 描述像素电路 2 的基本操作。

[0099] 图 16 是示出了图 15 中示出的像素电路的时序图。下面参考图 16 详细描述图 15 中示出的像素电路的操作。图 16 沿时间轴 T 示出了被施加到各个扫描线 WS、AZ1、AZ2 和 DS 的控制信号的波形。为了简化图示，控制信号由与对应的扫描线的代码相同的代码表示。晶体管 Tr1、Tr2 和 Tr3 都是 N 沟道晶体管，并且当扫描线 WS、AZ1 和 AZ2 处于高电平时导通，处于低电平时截止。另一方面，晶体管 Tr4 是 P 沟道晶体管，并且当扫描线 DS 处于高电平时截止，处于低电平时导通。例如，该时序图还示出了驱动晶体管 Trd 的栅极 G 和源极 S

的电势变化,以及各个控制信号 WS、AZ1、AZ2 和 DS 的波形。

[0100] 在图 16 中的时序图中,定时 T1-T8 对应于一场 (1f)。像素阵列的各行在一场比赛期间被顺序扫描一次。该时序图示出了被施加到一行中的像素的各个控制信号 WS、AZ1、AZ2 和 DS 的波形。

[0101] 在场开始之前的定时 T0 处,所有控制信号 WS、AZ1、AZ2 和 DS 都为低电平。因此,N 沟道晶体管 Tr1、Tr2 和 Tr3 处于截止状态中,而仅 P 沟道晶体管 Tr4 处于导通状态中。因此,驱动晶体管 Trd 经由导通状态的晶体管 Tr4 连接到电源 Vcc,从而根据预定输入电压 Vgs 将输出电流 Ids 提供给发光器件 EL。因此,发光器件 EL 在时刻 T0 处发光。在该时刻被施加到驱动晶体管 Trd 的输入电压 Vgs 由栅极电势 (G) 和源极电势 (S) 之间的差表示。

[0102] 在场开始的定时 T1 处,控制信号 DS 被从低电平切换到高电平。因此,晶体管 Tr4 被截止并且驱动晶体管 Trd 与电源 Vcc 断开,使得光发射停止,进入不发光周期。因此,在时刻 T1 处,晶体管 Tr1-Tr4 都进入截止状态。

[0103] 然后,在定时 T2 处,控制信号 AZ1 和 AZ2 变为高电平,使得开关晶体管 Tr2 和 Tr3 导通。结果,驱动晶体管 Trd 的栅极 G 被连接到参考电势 Vss1,并且源极 S 被连接到参考电势 Vss2。在这里,满足  $Vss1 - Vss2 > Vth$ 。通过设置  $Vss1 - Vss2 = Vgs > Vth$ ,执行了对在定时 T3 处执行的 Vth 校正的准备。换言之,周期 T2-T3 对应于驱动晶体管 Trd 的复位周期。另外,在用  $Vth_{EL}$  表示发光器件 EL 的阈值电压时, $Vth_{EL} > Vss2$  被设置。因此,负偏置被施加到发光器件 EL,从而发生了所谓的反向偏置。该反向偏置状态对于稍后正常执行 Vth 修造操作和迁移率校正操作是必需的。

[0104] 就在定时 T3 之前,允许控制信号 AZ2 处于低电平。另外,在定时 T3 处,允许控制信号 DS 处于低电平。因此,晶体管 Tr3 截止,而晶体管 Tr4 导通。结果,漏极电流 Ids 流入像素电容器 Cs,并且 Vth 校正操作开始。此刻,驱动晶体管 Trd 的栅极 G 被保持在 Vss1,电流 Ids 流动直到驱动晶体管 Trd 截止为止。在截止后,驱动晶体管 Trd 的源极电势变为  $Vss1 - Vth$ 。在漏电流截止之后的定时 T4 处,控制信号 DS 返回到高电平,并且驱动晶体管 Tr4 截止。此外,控制信号 AZ1 返回到低电平,并且开关晶体管 Tr2 截止。结果,Vth 在像素电容器 Cs 中被保持并且被固定。如上所述,定时 T3-T4 是检测驱动晶体管 Trd 的阈值电压 Vth 的周期。在这里,该检测周期 T3-T4 被称作 Vth 校正周期。

[0105] 在已按照上述方式执行了 Vth 校正后的定时 T5 处,控制信号 WS 被切换到高电平,采样晶体管 Tr1 导通,并且视频信号 Vsig 被写入像素电容器 Cs 中。与发光器件 EL 的等效电容器 Coled 相比,像素电容器 Cs 足够小。结果,视频信号 Vsig 的大部分被写入到像素电容器 Cs 中,准确地说是写到 Vss1。Vsиг 与 Vss1 的差  $Vsig - Vss1$  被写入到像素电容器 Cs 中。因此,驱动晶体管 Trd 的栅极 G 和源极 S 之间的电压 Vgs 变为先前被检测出并且被保持的 Vth 和此刻被采样的  $Vsig - Vss1$  的总和的电平 ( $Vsig - Vss1 + Vth$ )。在下文中,为了易于描述,假设  $Vss1 = 0$ ,从而栅 - 源电压 Vgs 变为  $Vsig + Vth$ ,如图 7 中的时序图所示。对视频信号 Vsig 的采样被执行直到控制信号 WS 返回到低电平的定时 T7 为止。即,定时 T5-T7 对应于采样周期。

[0106] 在采样周期结束的定时 T7 前的定时 T6 处,控制信号 DS 变为低电平并且开关晶体管 Tr4 导通。因此,驱动晶体管 Trd 被连接到电源 Vcc,使得像素电路从不发光周期进入发光周期。这样,在采样晶体管 Tr1 仍处于导通状态中并且开关晶体管 Tr4 进入导通状态的周

期 T6-T7 中执行了对驱动晶体管 Trd 的迁移率校正。即，在本实施例中，迁移率校正是在采样周期的后部分与发光周期的开始部分彼此重叠的周期 T6-T7 中执行的。注意，在执行迁移率校正的发光周期的开始处，发光器件 EL 实际上处于反向偏置中，因此不发光。在该迁移率校正周期 T6-T7 中，漏极电流  $I_{ds}$  在驱动晶体管 Trd 的栅极 G 被固定到视频信号  $V_{sig}$  的电平的状态中在驱动晶体管 Trd 中流动。在这里，通过设置  $V_{ss1}-V_{th} < V_{thEL}$ ，发光器件 EL 被保持在反向偏置状态中，从而具有简单的电容特性，而不是二极管特性。因此，在驱动晶体管 Trd 中流动的电流  $I_{ds}$  被写入电容器  $C = C_s + C_{oled}$  中，电容器 C 是像素电容器  $C_s$  和发光器件 EL 的等效电容器  $C_{oled}$  的总和。因此，驱动晶体管 Trd 的源极电势 (S) 上升。在图 16 中的时序图中，这种上升由  $\Delta V$  表示。该上升  $\Delta V$  最终被从像素电容器  $C_s$  中保持的栅 - 源电压  $V_{gs}$  中减去，这对应于负反馈。这样，通过将驱动晶体管 Trd 的输出电流  $I_{ds}$  负反馈到驱动晶体管 Trd 的输入电压  $V_{gs}$ ，可以校正迁移率  $\mu$ 。通过调节迁移率校正周期 T6-T7 的时间宽度 t，可以优化负反馈量  $\Delta V$ 。

[0107] 在定时 T7 处，控制信号 WS 变为低电平并且采样晶体管 Tr1 截止。结果，驱动晶体管 Trd 的栅极 G 与信号线 SL 断开。因为停止施加视频信号  $V_{sig}$ ，所以驱动晶体管 Trd 的栅极电势 (G) 可以上升，并且随源极电势 (S) 上升。在该时间期间，像素电容器  $C_s$  中保持的栅 - 源电压  $V_{gs}$  维持值 ( $V_{sig}-\Delta V+V_{th}$ )。根据源极电势 (S) 的上升，发光器件 EL 的反向偏置状态被消除，从而输出电流  $I_{ds}$  的流入导致发光器件 EL 实际开始发光。此刻，通过将  $V_{sig}-\Delta V+V_{th}$  代入到上述晶体管特性表达式的  $V_{gs}$ ，漏极电流  $I_{ds}$  和栅极电压  $V_{gs}$  之间的关系可以由如下表达式 2 给出。

$$[0108] I_{ds} = k \mu (V_{gs}-V_{th})^2 = k \mu (V_{sig}-\Delta V)^2 \quad \cdots \text{表达式 2}$$

[0109] 在上述表达式 2 中， $k = (1/2)(W/L)C_{ox}$ 。 $V_{th}$  项被从该特性表达式 2 中消去，并且可理解提供到发光器件 EL 的输出电流  $I_{ds}$  不依赖于驱动晶体管 Trd 的阈值电压  $V_{th}$ 。基本上，漏极电流  $I_{ds}$  由视频信号的信号电压  $V_{sig}$  确定。换言之，发光器件 EL 按照根据视频信号  $V_{sig}$  的亮度发光。在该时刻，利用反馈量  $\Delta V$  校正了  $V_{sig}$ 。该校正量  $\Delta V$  用来消除位于特性表达式 2 的系数部分中的迁移率  $\mu$  的影响。因此，漏极电流  $I_{ds}$  基本上仅依赖于视频信号  $V_{sig}$ 。

[0110] 最后，在定时 T8 处，控制信号 DS 变为高电平，开关晶体管 Tr4 截止，并且发光结束，而且该场结束。然后，下一场开始，并且再次重复  $V_{th}$  校正操作、迁移率校正操作和发光操作。

图 1

图 2

图 3

图 4

图 5

$$I_{ds} = k \mu (V_{gs} - V_{th})^2 = k \mu (V_{sig} - \Delta V)^2$$

图 6

图 7

图 8

图 9

图 10

图 11

图 12

图 13

图 14

图 15

图 16

|                |                                                                                                                    |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 像素电路和显示装置                                                                                                          |         |            |

| 公开(公告)号        | <a href="#">CN101996578A</a>                                                                                       | 公开(公告)日 | 2011-03-30 |

| 申请号            | CN201010518610.2                                                                                                   | 申请日     | 2006-11-14 |

| [标]申请(专利权)人(译) | 索尼公司                                                                                                               |         |            |

| 申请(专利权)人(译)    | 索尼公司                                                                                                               |         |            |

| 当前申请(专利权)人(译)  | 索尼公司                                                                                                               |         |            |

| [标]发明人         | 内野胜秀<br>山下淳一                                                                                                       |         |            |

| 发明人            | 内野胜秀<br>山下淳一                                                                                                       |         |            |

| IPC分类号         | G09G3/32                                                                                                           |         |            |

| CPC分类号         | G09G2320/045 G09G3/3291 G09G2300/0842 G09G2300/0861 G09G2320/043 G09G3/3266 G09G3/3233 G09G2300/0819 G09G2310/0256 |         |            |

| 代理人(译)         | 李晓冬                                                                                                                |         |            |

| 优先权            | 2005328334 2005-11-14 JP                                                                                           |         |            |

| 其他公开文献         | <a href="#">CN101996578B</a>                                                                                       |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                     |         |            |

#### 摘要(译)

可以提高具有阈值电压校正功能的像素电路的效率并简化像素电路。采样晶体管(Tr1)在水平扫描周期期间响应于从扫描线(WS)提供的控制信号被电连接，并且将从信号线(SL)提供的视频信号采样到像素电容器(Cs)中。像素电容器(Cs)响应于被采样的视频信号将输入电压(Vgs)施加到驱动晶体管(Trd)的栅极(G)。驱动晶体管(Trd)将根据输入电压(Vgs)的输出电流提供给发光器件(EL)。输出电流具有对驱动晶体管(Trd)的阈值电压(Vth)的依赖性。为了消除输出电流对阈值电压(Vth)的依赖性，设置了校正装置(Tr3，Tr4)，该校正装置在水平扫描周期的一部分中操作，检测驱动晶体管(Trd)的阈值电压(Vth)，并将其写入像素电容器(Cs)中。