[19] 中华人民共和国国家知识产权局

## [12] 发明专利申请公布说明书

[21] 申请号 200610108997.8

[51] Int. Cl.

G09G 3/30 (2006.01)

G09G 3/32 (2006.01)

G09G 3/20 (2006.01)

H05B 33/08 (2006.01)

H05B 33/14 (2006.01)

[43] 公开日 2007 年 2 月 7 日

[11] 公开号 CN 1909043A

[22] 申请日 2006.7.31

[21] 申请号 200610108997.8

[30] 优先权

[32] 2005.8.1 [33] KR [31] 10 - 2005 - 0070438

[71] 申请人 三星 SDI 株式会社

地址 韩国京畿道水原市

共同申请人 汉阳大学校产业协力团

[72] 发明人 郑宝容 柳道亨 金烘权 权五敬

[74] 专利代理机构 北京铭硕知识产权代理有限公司

代理人 韩明星 常桂珍

权利要求书 5 页 说明书 30 页 附图 10 页

[54] 发明名称

有机发光显示器的数据驱动电路和驱动方法

[57] 摘要

本发明提供了一种用于驱动发光显示器的像素从而以均匀的亮度显示图像的数据驱动电路，所述数据驱动电路包括：伽马电压单元，产生多个灰阶电压；数模转换器，利用第一数据选择多个灰阶电压之一作为数据信号；解码器，利用第一数据产生第二数据；电流吸收器；电压控制器，利用第二数据和基于预定电流产生的补偿电压来控制数据信号的电压值；开关单元，在所述完整周期的第一部分时间段之后流逝的任何部分时间段期间，将数据信号供给至像素。在驱动像素的完整周期的第一部分时间段期间，基于选择的灰阶电压，电流吸收器从像素接收预定电流。

1、一种用于根据从外部提供给像素的第一数据来驱动发光显示器的所述像素的数据驱动电路，其中，所述像素经数据线与所述驱动电路电连接，所述数据驱动电路包括：

伽马电压单元，产生多个灰阶电压；

数模转换器，利用  $k$  位的所述第一数据来选择所述多个灰阶电压中的一个作为数据信号， $k$  为自然数；

解码器，利用所述  $k$  位的第一数据产生  $p$  位的第二数据， $p$  为自然数；

电流吸收器，在驱动所述像素的完整周期的第一部分时间段期间，基于选择的灰阶电压从所述像素接收预定电流；

电压控制器，利用所述的第二数据和基于所述预定电流产生的补偿电压来控制所述数据信号的电压值；

开关单元，将具有所述控制的电压值的数据信号供给到所述像素，在所述完整周期的所述第一部分时间段之后流逝的所述完整周期的任何部分的时间段期间，所述开关单元供给所述数据信号。

2、根据权利要求 1 所述的数据驱动电路，其中，所述解码器将所述第一数据转换成二进制加权值以产生所述第二数据。

3、根据权利要求 1 所述的数据驱动电路，还包括：

第一晶体管，设置在所述数模转换器和所述开关单元之间，在所述第一部分时间段的预定时间期间，所述数模转换器导通以将具有所述控制的电压值的数据信号传输到所述开关单元；

第一缓冲器，连接在所述第一晶体管和所述开关单元之间。

4、根据权利要求 3 所述的数据驱动电路，其中，所述伽马电压单元包括：

多个分配电阻器，用于产生所述灰阶电压并分配基准电源电压和第一电源电压；

第二缓冲器，用于将所述第一电源电压供给到所述电压控制器。

5、根据权利要求 4 所述的数据驱动电路，其中，所述电压控制器包括：

$P$  个电容器，所述  $p$  个电容器中的每个具有连接到所述第一晶体管和所述第一缓冲器之间的电通路的第一接线端；

第二晶体管，分别连接在所述  $p$  个电容器的每个的第二接线端和所述第

二缓冲器之间；

第三晶体管，分别连接在所述 p 个电容器的每个的所述第二接线端和所述电流吸收器之间，所述第三晶体管的传导类型与所述第二晶体管的传导类型不同。

6、根据权利要求 5 所述的数据驱动电路，其中，在所述第一部分时间段期间，所述解码器导通所述第二晶体管，并将所述第一电源电压供给到所述 p 个电容器各自的第二接线端。

7、根据权利要求 5 所述的数据驱动电路，其中，所述 p 个电容器的电容被设置为二进制的加权值。

8、根据权利要求 7 所述的数据驱动电路，其中，所述解码器基于所述第二数据的位数导通和截止所述第三晶体管，并且在所述第二部分时间段期间，所述解码器选择性地控制供给到所述 p 个电容器各自的第二接线端的所述补偿电压。

9、根据权利要求 1 所述的数据驱动电路，其中，所述电流吸收器包括：电流源，接收所述预定电流；

第一晶体管，设置在连接到所述像素的所述数据线和所述电压控制器之间，所述第一晶体管在所述第一部分时间段期间导通；

第二晶体管，设置在所述数据线和所述电流源之间，所述第二晶体管在所述第一部分时间段期间导通；

电容器，存储所述补偿电压；

缓冲器，设置在所述第一晶体管和所述电压控制器之间，所述缓冲器选择性地将所述补偿电压传输到所述电压控制器。

10、根据权利要求 9 所述的数据驱动电路，其中，所述预定电流的电流值等于所述像素发射最大亮度的光时流过所述像素的最小电流的电流值，并且最大的亮度与所述多个重置的灰阶电压中最高的一个被施加到所述像素时所述像素的亮度对应。

11、根据权利要求 1 所述的数据驱动电路，其中，所述开关单元包括至少一个在所述第二部分时间段期间导通的晶体管。

12、根据权利要求 11 所述的数据驱动电路，其中，所述开关单元包括两个晶体管，所述的两个晶体管连接以形成传输门。

13、根据权利要求 1 所述的数据驱动电路，包括：

移位寄存器单元，包括至少一个用于依次产生取样脉冲的移位寄存器；

取样锁存器单元，包括至少一个用于响应所述取样脉冲来接收所述第一数据的取样锁存器；

保持锁存器单元，包括至少一个用于接收存储在所述取样锁存器中的所述第一数据的保持锁存器并将存储在所述保持锁存器中的所述第一数据供给到所述数模转换器和所述解码器。

14、根据权利要求 13 所述的数据驱动电路，还包括：

电平转换器，用于选择性地改变存储在所述保持锁存器中的所述第一数据的电压电平并将电平改变了的所述第一数据供应到所述数模转换器和所述解码器。

15、一种接收外部供给的第一数据的发光显示器，包括：

像素单元，包括与  $n$  条扫描线、多条数据线和多条发射控制线连接的多个像素，其中， $n$  是自然数；

扫描驱动器，在每个扫描周期，将  $n$  个扫描信号分别依次地供给到所述的  $n$  条扫描线，并将发射控制信号依次地供给到所述多条发射控制线；

数据驱动器，在完整的周期的第一部分时间段期间，从通过第一扫描信号选择的所述像素中的各个像素接收预定电流，利用基于所述各个预定电流产生的各个补偿电压和通过利用二进制加权值将所述各个第一数据转换成第二数据产生的各个第二数据来分别控制数据信号的电压值，并在与所述各个像素中的每个相关的各个完整的周期的所述第一部分时间段之后流逝的所述完整周期的部分时间段期间，分别将具有控制的电压值的所述数据信号供给到所述数据线。

16、根据权利要求 15 所述的发光显示器，其中，所述像素中的每个与所述  $n$  条扫描线中的两条扫描线连接，在每个所述扫描周期期间，在所述两条扫描线中的第二条接收所述  $n$  个扫描信号中的各自的一个之前，所述两条扫描线中的第一条接收所述  $n$  个扫描信号中的各自的一个，所述像素中的每个包括：

第一电源；

发光器，从所述第一电源接收电流；

第一晶体管和第二晶体管，每个具有连接到与所述像素相关的数据线中的各自的一条的第一电极，当供给所述扫描信号中的第二扫描信号时，所述

第一晶体管和所述第二晶体管导通；

第三晶体管，具有连接到基准电源的第一电极和连接到所述第一晶体管的第二电极的第二电极，当供给所述两个扫描信号中的所述第一扫描信号时，所述第三晶体管导通；

第四晶体管，控制供给到所述发光器的电流的量，所述第四晶体管的第一接线端与所述第一电源连接；

第五晶体管，具有连接到所述第四晶体管的栅电极的第一电极和连接到所述第四晶体管的第二电极的第二电极，当供给所述两个扫描信号中的所述第一扫描信号时，所述第五晶体管导通，从而所述第四晶体管作为二极管操作。

17、根据权利要求 16 所述的发光显示器，其中，所述像素中的每个包括：

第一电容器，具有连接到所述第一晶体管的第二电极或所述第四晶体管的所述栅电极之一的第一电极和连接到所述第一电源的第二电极；

第二电容器，具有连接到所述第一晶体管的所述第二电极的第一电极和连接到所述第四晶体管的所述栅电极的第二电极。

18、根据权利要求 16 所述的发光显示器，其中，所述像素中的每个还包括：第六晶体管，具有连接到所述第四晶体管的所述第二电极的第一接线端和连接到所述发光器的第二接线端，当供给所述各发射控制信号时，所述第六晶体管截止，

其中，在驱动所述像素的一个完整周期的第一部分时间段期间，所述电流吸收器从所述像素接收所述预定电流，所述第一部分时间段发生在驱动所述像素的所述完整周期的第二部分时间段之前，在驱动所述像素的所述完整周期的第二部分时间段期间，所述第六晶体管截止。

19、一种用于驱动发光显示器的方法，包括：

基于 k 位的从外部供给的第一数据，选择多个灰阶电压中的一个作为数据信号，k 为自然数；

将所述第一数据转换成二进制加权值并产生 p 位的第二数据，p 为自然数；

基于选择的灰阶电压，在驱动所述像素的完整周期的第一部分时间段期间，从扫描信号选择的像素接收预定电流；

利用产生的第二数据和当供给所述预定电流时产生的补偿电压来控制所

述数据信号的电压值；

在控制所述数据信号的电压值之后，将所述数据信号供给到所述像素，在驱动所述像素的所述完整周期的第二部分时间段期间，将所述数据信号供给到所述像素。

20、根据权利要求 19 所述的方法，还包括：通过在多个分压电阻器中，分配基准电压和第一电源电压之间的电压来产生所述多个灰阶电压。

21、根据权利要求 19 所述的方法，其中，控制所述数据信号的电压值的步骤包括：

在所述第一部分时间段期间，将所述第一电源的电压值供给到多个电容器中的每个的第二接线端；

在所述完整周期的第二部分时间段期间，基于所述第二数据的位数，选择性地控制所述补偿电压对所述多个电容器的各自的第二接线端的供给。

22、一种用于驱动发光显示器的数据驱动电路，包括：

选择装置，基于 k 位的从外部供给的第一数据来选择多个灰阶电压之一作为数据信号，k 为自然数；

转换装置，用于将所述第一数据转换成二进制加权值并产生 p 位的第二数据，p 为自然数；

接收装置，在驱动像素的完整周期的第一部分时间段期间，基于选择的灰阶电压，从通过扫描信号选择的像素中接收预定电流；

控制装置，用于利用产生的第二数据和供应所述预定电流时产生的补偿电压来控制所述数据信号的电压值；

在控制所述数据信号的所述电压值之后，将所述数据信号供给到所述像素，所述数据信号在驱动所述像素的所述完整周期的第二部分时间段期间被供给到所述像素。

## 有机发光显示器的数据驱动电路和驱动方法

### 技术领域

本发明涉及一种数据驱动电路、采用这种数据驱动电路的发光显示器以及驱动这种发光显示器的方法。更具体地讲，本发明涉及一种能够以均匀的亮度显示图像的数据驱动电路、利用这种数据电路的发光显示器以及驱动这种发光显示器以显示具有均匀亮度的图像的方法。

### 背景技术

正在研发平板显示器 (FPD)，通常 FPD 比阴极射线管 (CRT) 亮和小型化。FPD 包括液晶显示器 (LCD)、场发射显示器 (FED)、等离子体显示面板 (PDP) 和发光显示器。

发光显示器可利用当电子和空穴复合时发光的有机发光二极管 (OLED) 来显示图像。发光显示器通常具有快速的响应速度并且消耗的能量的量相对低。

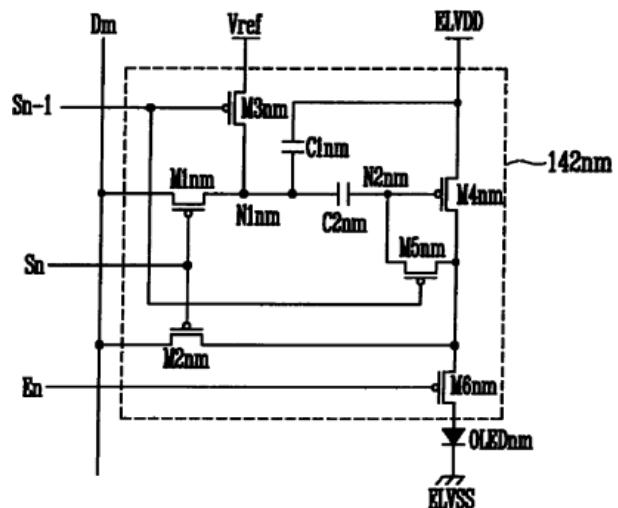

图 1 示出了公知的发光显示器的结构的示意图。

如图 1 所示，发光显示器可包括像素单元 30、扫描驱动器 10、数据驱动器 20 和时序控制器 50。像素单元 30 可包括与扫描线 S1 至 Sn 和数据线 D1 至 Dm 连接的多个像素 40。扫描驱动器 10 可驱动扫描线 S1 至 Sn。数据驱动器 20 可驱动数据线 D1 至 Dm。时序控制器 50 可控制扫描驱动器 10 和数据驱动器 20。

时序控制器 50 可基于外部供给的同步信号 (未示出) 来产生数据驱动控制信号 DCS 和扫描驱动控制信号 SCS。可将数据驱动控制信号 DCS 提供到数据驱动器 20，可将扫描驱动控制信号 SCS 提供到扫描驱动器 10。时序控制器 50 可根据外部供给的数据 (未示出) 对数据驱动器 20 提供数据 DATA。

扫描驱动器 10 从时序控制器 50 接收扫描驱动控制信号 SCS。扫描驱动器 10 可基于接收的扫描驱动控制信号 SCS 来产生扫描信号 (未示出)。可经扫描线 S1 至 Sn 将产生的扫描信号顺序地供给到像素单元 30。

数据驱动器 20 从时序控制器 50 接收数据驱动控制信号 DCS 和数据

DATA。数据驱动器 20 可基于接收的数据 DATA 和数据驱动控制信号 DCS 来产生数据信号(未示出)。可将产生的数据信号中的相应信号与被提供到扫描线 S1 至 Sn 的扫描信号中的各个信号同步地提供到数据线 D1 至 Dm。

像素单元 30 可与第一电源 ELVDD 和第二电源 ELVSS 连接, 第一电源 ELVDD 将第一电压 VDD 提供到像素 40, 第二电源 ELVSS 将第二电压 VSS 提供到像素 40。像素 40 与第一电压 VDD 信号和第二电压 VSS 信号一起可根据相应的数据信号来控制流过各 OLED 的电流。从而, 基于第一电压 VDD 信号、第二电压 VSS 信号和数据信号, 像素 40 可产生光。

在公知的发光显示器中, 每个像素 40 可包括像素电路, 像素电路包括至少一个用于选择性地提供各数据信号和各扫描信号的晶体管, 所述的各扫描信号用于选择性地将发光显示器的各像素 40 选通和断开。

发光显示器的各像素 40 将响应各数据信号的不同值来产生预定亮度的光。例如, 当对该显示器的所有像素 40 施加相同的数据信号时, 通常期望该显示器的所有像素 40 产生相同的亮度。然而, 每个像素 40 产生的亮度不仅取决于数据信号, 还取决于每个像素 40 的特性, 例如, 取决于像素电路的各晶体管的阈值电压。

通常, 从晶体管到晶体管, 阈值电压和/或电子迁移率是存在差异的, 从而不同的晶体管具有不同的阈值电压和电子迁移率。晶体管的特性还可以随着时间和/或使用来改变。例如, 晶体管的阈值电压和电子迁移率可取决于该晶体管的导通/截止的经历。

因此, 在发光显示器中, 每个像素响应各数据信号产生的亮度取决于可包括在各像素电路中的晶体管的特性。这种阈值电压和电子迁移率的差异会防止和/或妨碍被显示图像的均匀性。因此, 这种阈值电压和电子迁移率的差异还会妨碍以期望的亮度来显示图像。

尽管通过控制像素 40 的像素电路的结构对包括在多个像素中的多个晶体管的阈值电压之间的差会进行至少部分补偿, 但是仍然需要能够补偿电子迁移率的变化的电路和方法。还期望不管电子迁移率如何变化都能够以均匀的亮度来显示图像的 OLED。

## 发明内容

因此, 本发明提出了一种数据驱动电路和利用该数据驱动电路的发光显

示器，该数据驱动电路基本上克服了由于现有技术的局限和缺点而导致的一个或多个问题。

因此，本发明的实施例的一特征在于提供一种能够驱动发光显示器的像素以显示具有均匀亮度的图像的数据驱动电路，以及提供一种利用该数据驱动电路的发光显示器和驱动该发光显示器的方法。

本发明的以上和其它特征和优点中的至少一个可通过提供一种数据驱动电路来实现，所述数据驱动电路基于从外部对发光显示器的像素提供的第一数据来驱动所述像素，其中，所述像素经数据线与驱动电路可电连接，所述数据驱动电路包括：伽马电压单元，产生多个灰阶电压；数模转换器，利用  $k$  位的第一数据来选择多个灰阶电压中的一个作为数据信号， $k$  为自然数；解码器，利用  $k$  位的第一数据产生  $p$  位的第二数据， $p$  为自然数；电流吸收器，在驱动所述像素的完整周期的第一部分时间段期间，基于选择的灰阶电压从所述像素接收预定电流；电压控制器，利用第二数据和基于预定电流产生的补偿电压来控制数据信号的电压值；开关单元，将具有控制的电压值的数据信号供给到所述像素，在所述完整周期的第一部分时间段后流逝的所述完整周期的任何部分的时间段期间，开关单元供给数据信号。

所述数据驱动电路可包括：第一晶体管，设置在数模转换器和开关单元之间，在第一部分时间段的预定时间期间，数模转换器导通以将具有控制的电压值的数据信号传输到开关单元；第一缓冲器，连接在第一晶体管和开关单元之间。

解码器可将第一数据转换成二进制加权值以产生第二数据。伽马电压单元可包括：多个分配电阻器，用于产生灰阶电压并分配基准电源电压和第一电源电压；第二缓冲器，用于将第一电源电压供给到电压控制器。

电压控制器可包括： $P$  个电容器，所述  $p$  个电容器中的每个具有连接到第一晶体管和第一缓冲器之间的电通路的第一接线端；第二晶体管，分别连接在  $p$  个电容器的每个的第二接线端和第二缓冲器之间；第三晶体管，分别连接在所述  $p$  个电容器的每个的第二接线端和电流吸收器之间，第三晶体管的传导类型与第二晶体管的传导类型不同。在第一部分时间段期间，解码器导通第二晶体管，并将第一电源电压供给到所述  $p$  个电容器各自的第二接线端。

所述  $p$  个电容器的电容可被设置为二进制的加权值。解码器可基于第二

数据的位数导通和截止第三晶体管，并且在第二部分时间段期间，解码器选择性地控制供给到 p 个电容器各自的第二接线端的补偿电压。

电流吸收器可包括：电流源，接收预定电流；第一晶体管，设置在连接到所述像素的数据线和电压控制器之间，第一晶体管在第一部分时间段期间导通；第二晶体管，设置在数据线和电流源之间，第二晶体管在第一部分时间段期间导通；电容器，存储补偿电压；缓冲器，设置在第一晶体管和电压控制器之间，缓冲器选择性地将补偿电压传输到电压控制器。

所述预定电流的电流值可等于所述像素发射最大亮度的光时流过所述像素的最小电流的电流值，并且最大的亮度与所述多个重置的灰阶电压中最高的一个被施加到所述像素时所述像素的亮度对应。所述开关单元可包括至少一个在所述第二部分时间段期间导通的晶体管。所述开关单元可包括两个晶体管，所述的两个晶体管连接以形成传输门。

所述数据驱动电路可包括：移位寄存器单元，包括至少一个用于依次产生取样脉冲的移位寄存器；取样锁存器单元，包括至少一个用于响应所述取样脉冲来接收所述第一数据的取样锁存器；保持锁存器单元，包括至少一个用于接收存储在所述取样锁存器中的所述第一数据的保持锁存器并将存储在所述保持锁存器中的所述第一数据供给到所述数模转换器和所述解码器。所述数据驱动电路可包括电平转换器，用于选择性地改变存储在所述保持锁存器中的所述第一数据的电压电平并将所述电平改变了的第一数据供应到所述数模转换器和所述解码器。

本发明的以上和其它特征和优点中的至少一个可通过提供一种发光显示器来单独地实现，所述发光显示器接收外部供给的第一数据并包括：像素单元，包括与 n 条扫描线、多条数据线和多条发射控制线连接的多个像素，其中，n 是自然数；扫描驱动器，在每个扫描周期，将 n 个扫描信号分别依次地供给到所述的 n 条扫描线，并将发射控制信号依次地供给到所述多条发射控制线；数据驱动器，在完整的周期的第一部分时间段期间，从通过第一扫描信号选择的所述像素中的各个像素接收预定电流，基于所述各个预定电流产生的各个补偿电压和通过利用二进制加权值将所述各个第一数据转换成第二数据产生的各个第二数据来分别控制数据信号的电压值，并在与所述各个像素中的每个相关的各个完整的周期的所述第一部分时间段之后流逝的所述完整周期的部分时间段期间，分别将具有控制的电压值的所述数据信号供给

到所述数据线。

所述像素中的每个可与所述 n 条扫描线中的两条扫描线连接，在每个所述扫描周期期间，在所述两条扫描线中的第二条接收所述 n 个扫描信号中的各自的一个之前，所述两条扫描线中的第一条接收所述 n 个扫描信号中的各自的一个，所述像素中的每个可包括：第一电源；发光器，从所述第一电源接收电流；第一晶体管和第二晶体管，每个具有连接到与所述像素相关的数据线中的各自的一条的第一电极，当供给所述扫描信号中的第二扫描信号时，所述第一晶体管和所述第二晶体管导通；第三晶体管，具有连接到基准电源的第一电极和连接到所述第一晶体管的第二电极的第二电极，当供给所述两个扫描信号中的所述第一扫描信号时，所述第三晶体管导通；第四晶体管，控制供给到所述发光器的电流的量，所述第四晶体管的第一接线端与所述第一电源连接；第五晶体管，具有连接到所述第四晶体管的栅电极的第一电极和连接到所述第四晶体管的第二电极的第二电极，当供给所述两个扫描信号中的所述第一扫描信号时，所述第五晶体管导通，从而所述第四晶体管作为二极管操作。

所述像素中的每个可包括：第一电容器，具有连接到所述第一晶体管的第二电极或所述第四晶体管的所述栅电极之一的第一电极和连接到所述第一电源的第二电极；第二电容器，具有连接到所述第一晶体管的所述第二电极的第一电极和连接到所述第四晶体管的所述栅电极的第二电极。

所述像素中的每个还可包括：第六晶体管，具有连接到所述第四晶体管的所述第二电极的第一接线端和连接到所述发光器的第二接线端，当供给所述各发射控制信号时，所述第六晶体管截止，其中，在驱动所述像素的一个完整周期的第一部分时间段期间，所述电流吸收器从所述像素接收所述预定电流，所述第一部分时间段发生在驱动所述像素的所述完整周期的第二部分时间段之前，在驱动所述像素的所述完整周期的第二部分时间段期间，所述第六晶体管截止。

本发明的以上和其它特征和优点中的至少一个可通过提供一种驱动发光显示器的方法来实现，所述方法包括：基于 k 位的从外部供给的第一数据，选择多个灰阶电压中的一个作为数据信号，k 为自然数；将所述第一数据转换成二进制加权值并产生 p 位的第二数据，p 为自然数；基于选择的灰阶电压，在驱动所述像素的完整周期的第一部分时间段期间，从扫描信号选择的

像素接收预定电流；利用产生的第二数据和当供给所述预定电流时产生的补偿电压来控制所述数据信号的电压值；在控制所述数据信号的电压值之后，将所述数据信号供给到所述像素，所述数据信号在驱动所述像素的所述完整周期的第二部分时间段期间被供给到所述像素。

所述方法还可包括：通过在多个分压电阻器中，分配基准电压和第一电源电压之间的电压来产生所述多个灰阶电压。

控制所述数据信号的电压值的步骤可包括：在所述第一部分时间段期间，将所述第一电源的电压值供给到多个电容器中的每个的第二接线端；在所述完整周期的第二部分时间段期间，基于所述第二数据的位数，选择性地控制所述补偿电压对所述多个电容器的各自的第二接线端的供给。

本发明的以上和其它特征和优点中的至少一个可通过提供一种驱动发光显示器的数据驱动电路来单独地实现，所述驱动电路包括：选择装置，基于  $k$  位的从外部供给的第一数据来选择多个灰阶电压之一作为数据信号， $k$  为自然数；转换装置，用于将所述第一数据转换成二进制加权值并产生  $p$  位的第二数据， $p$  为自然数；接收装置，在驱动所述像素的完整周期的第一部分时间段期间，基于选择的灰阶电压，从通过扫描信号选择的像素中接收预定电流；控制装置，用于利用产生的第二数据和供应预定电流时产生的补偿电压来控制所述数据信号的电压值；在控制所述数据信号的所述电压值之后，将所述数据信号供给到所述像素，所述数据信号在驱动所述像素的所述完整周期的第二部分时间段期间被供给到所述像素。

#### 附图说明

通过参考附图来详细描述本发明的示例性实施例，本发明的这些和其它特征和优点对于本领域的技术人员来说会变得清楚，其中：

- 图 1 示出了公知的发光显示器的示意图；

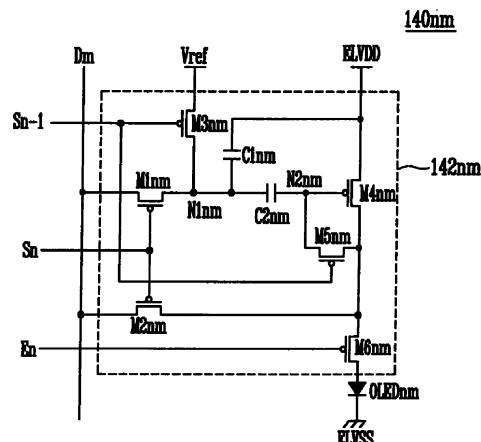

- 图 2 示出了根据本发明实施例的发光显示器的示意图；

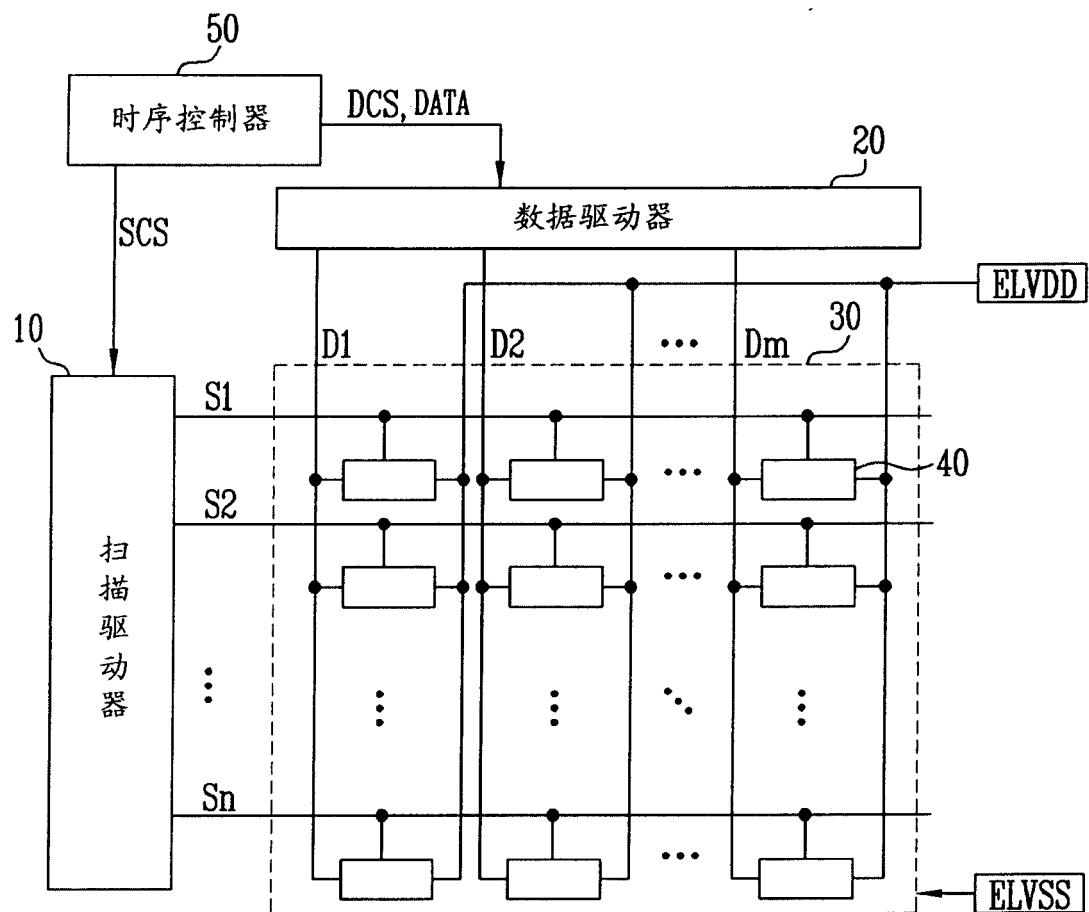

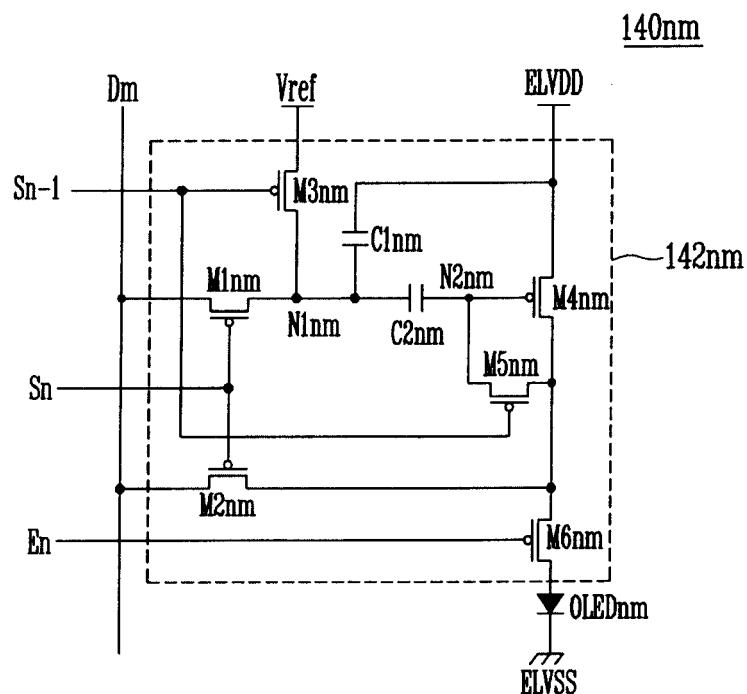

- 图 3 示出了在图 2 中示出的发光显示器可采用的示例性像素的电路图；

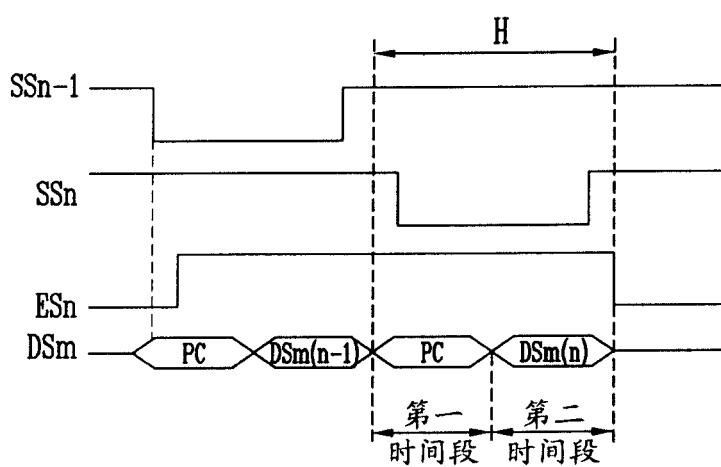

- 图 4 示出了驱动图 3 中示出的像素可采用的示例性波形；

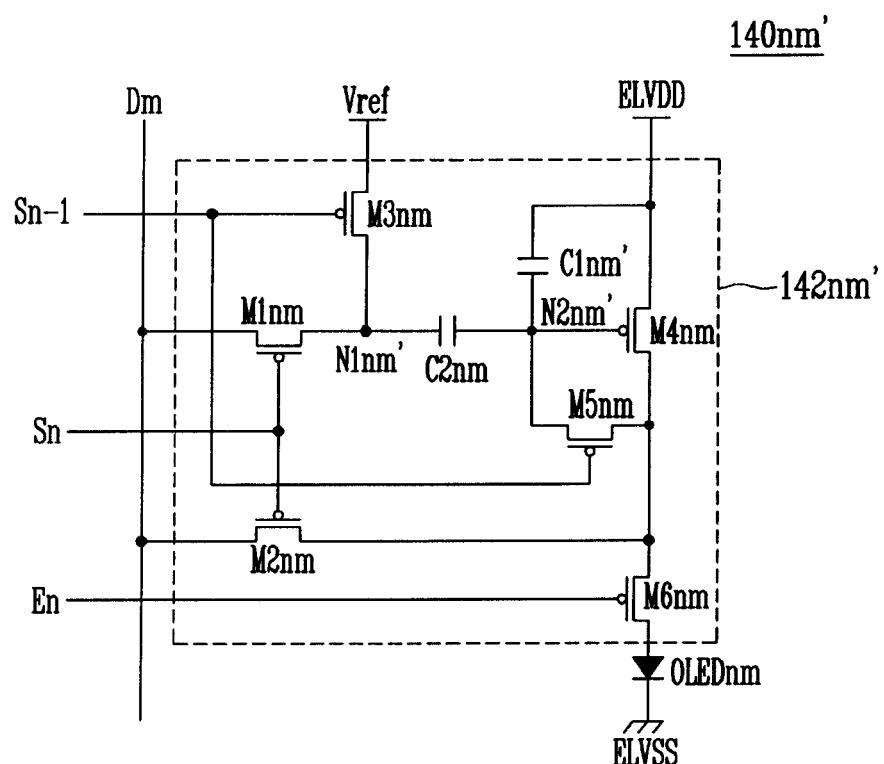

- 图 5 示出了在图 2 中示出的发光显示器可采用的另一示例性像素的电路图；

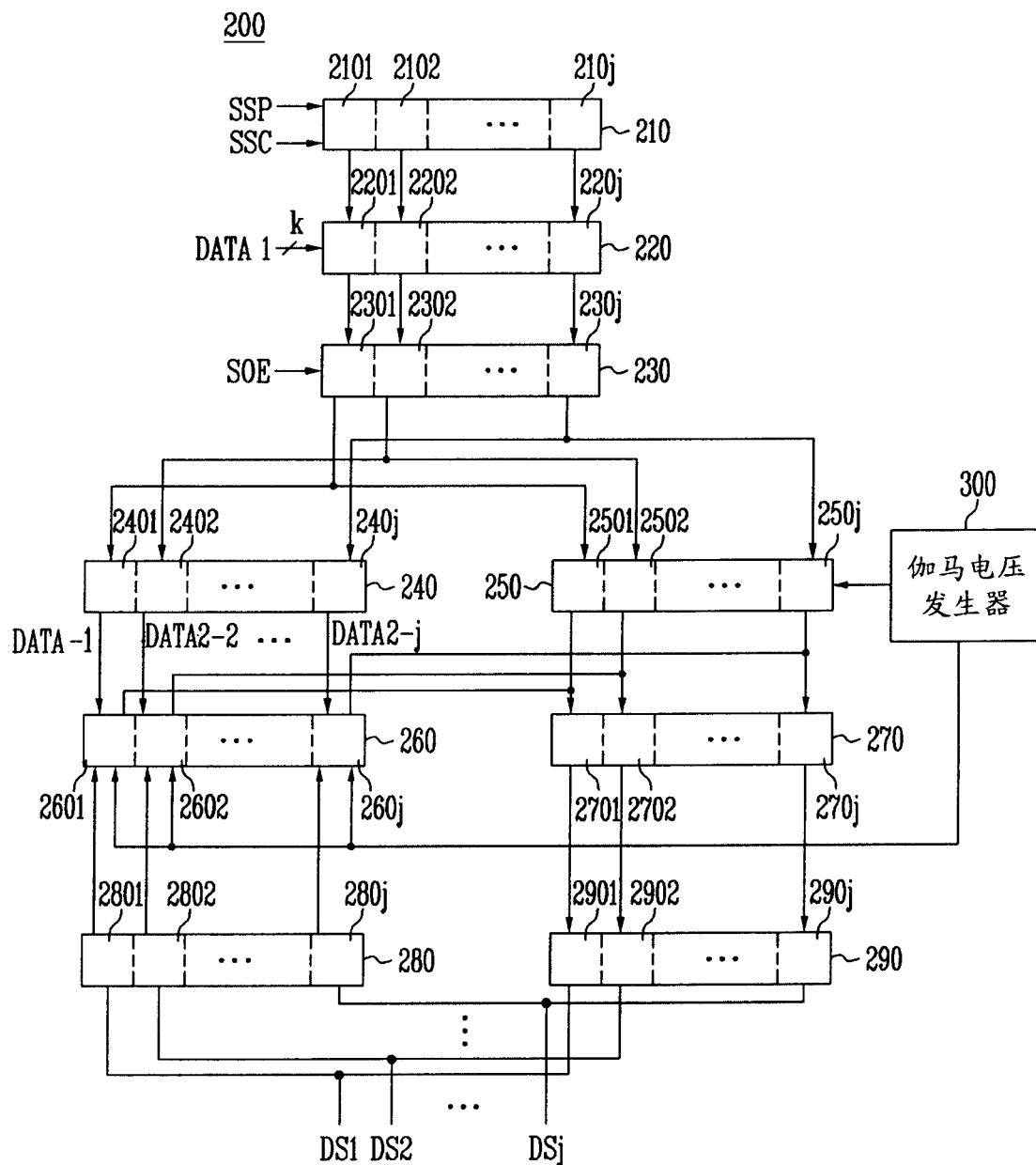

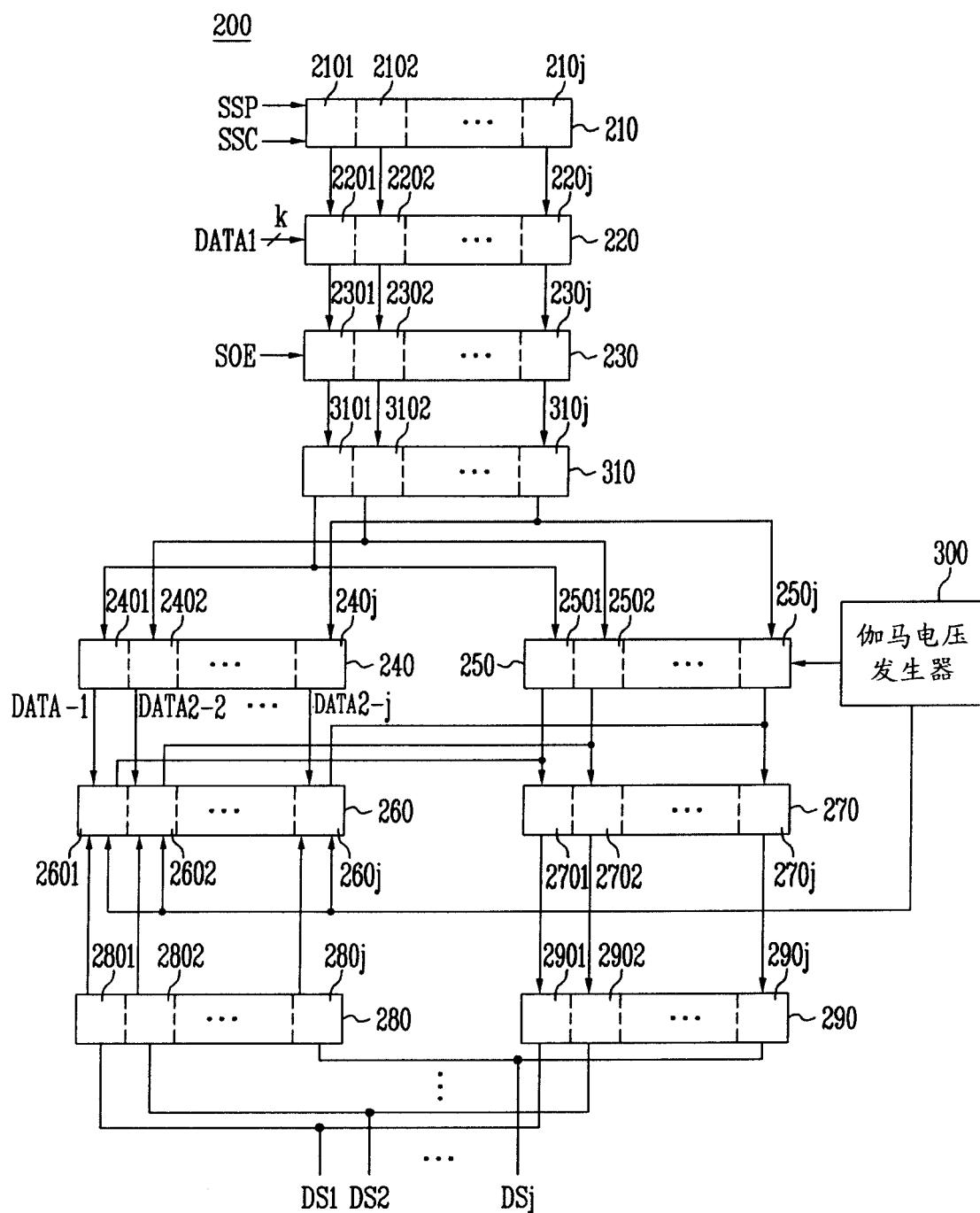

- 图 6 示出了图 2 中示出的数据驱动电路的第一实施例的方框图；

图 7 示出了图 2 中示出的数据驱动电路的第二实施例的方框图；

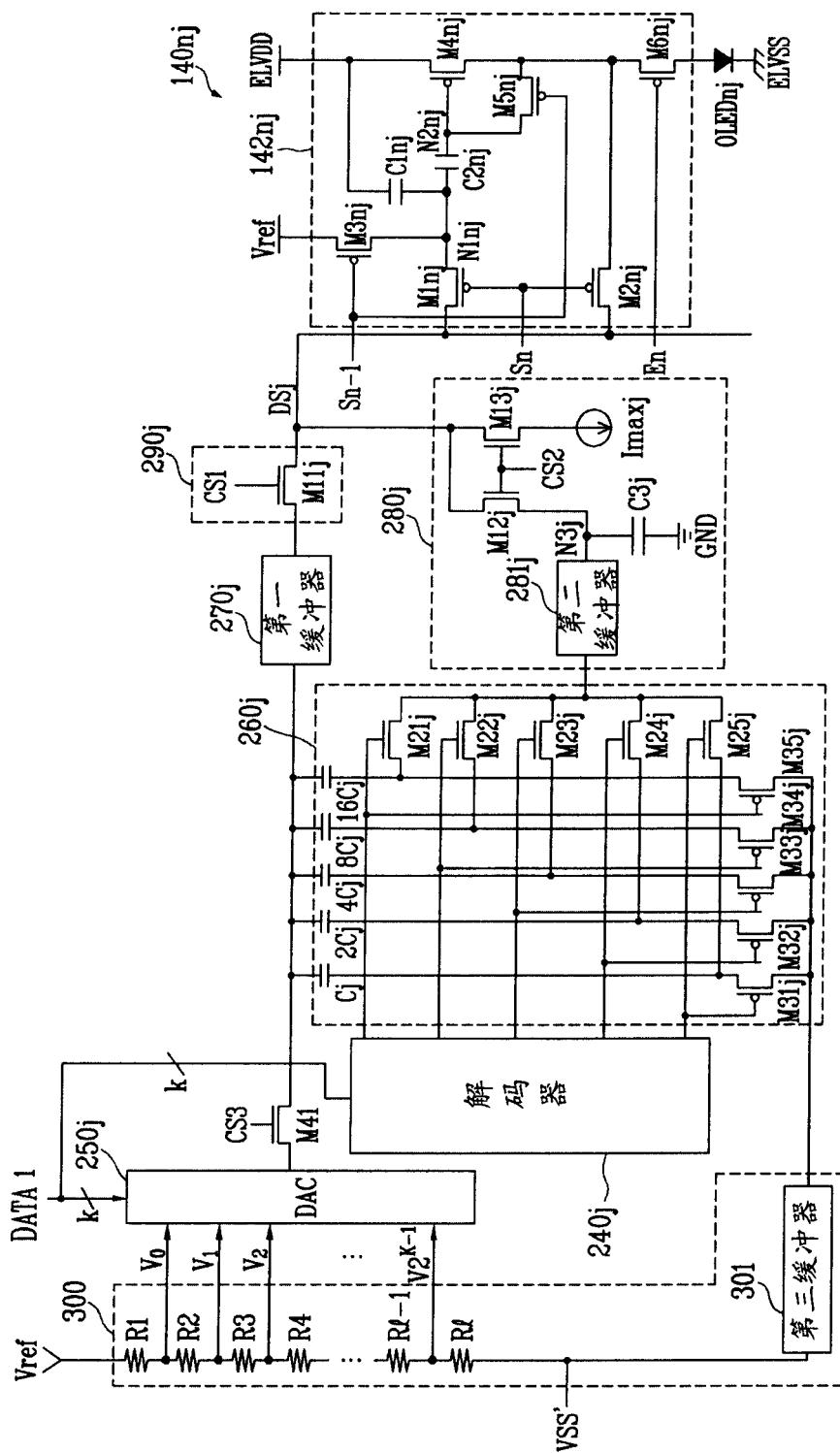

图 8 示出了连接图 6 中示出的伽马电压单元、数模转换器、解码器、电压控制器、开关单元和电流吸收单元以及图 3 中示出的像素的连接方案的第一实施例的示意图；

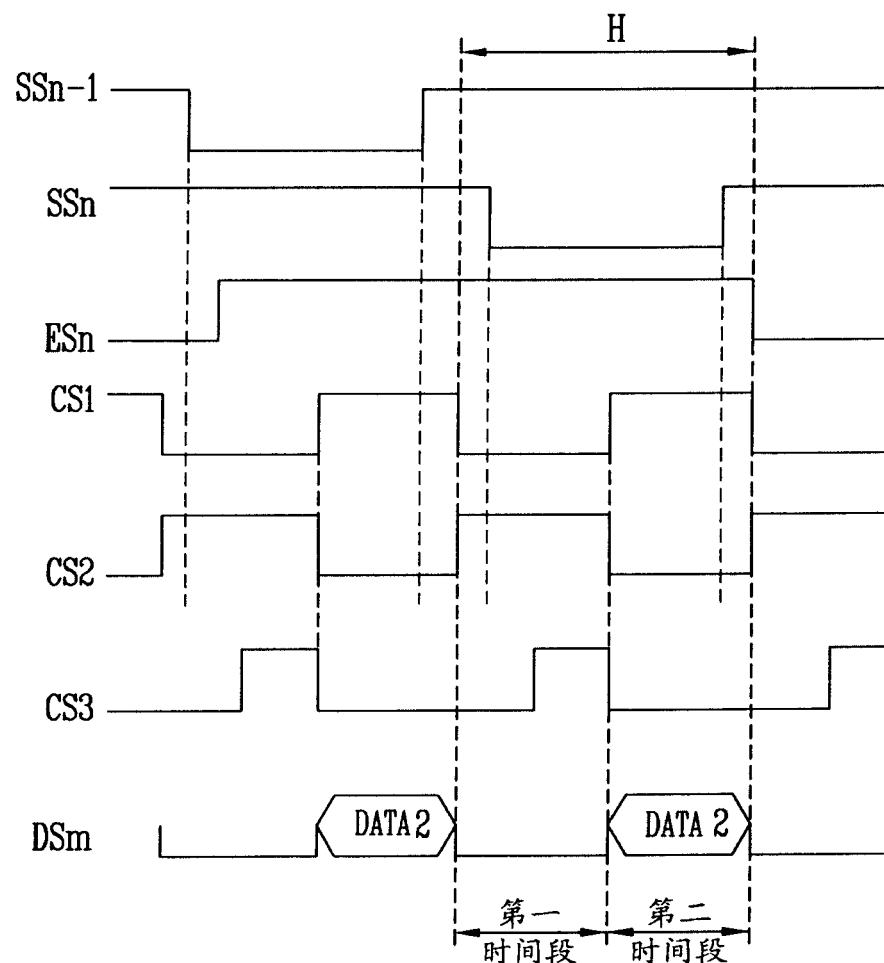

图 9 示出了用于驱动图 8 中示出的像素、开关单元和电流吸收单元可采用的示例性波形；

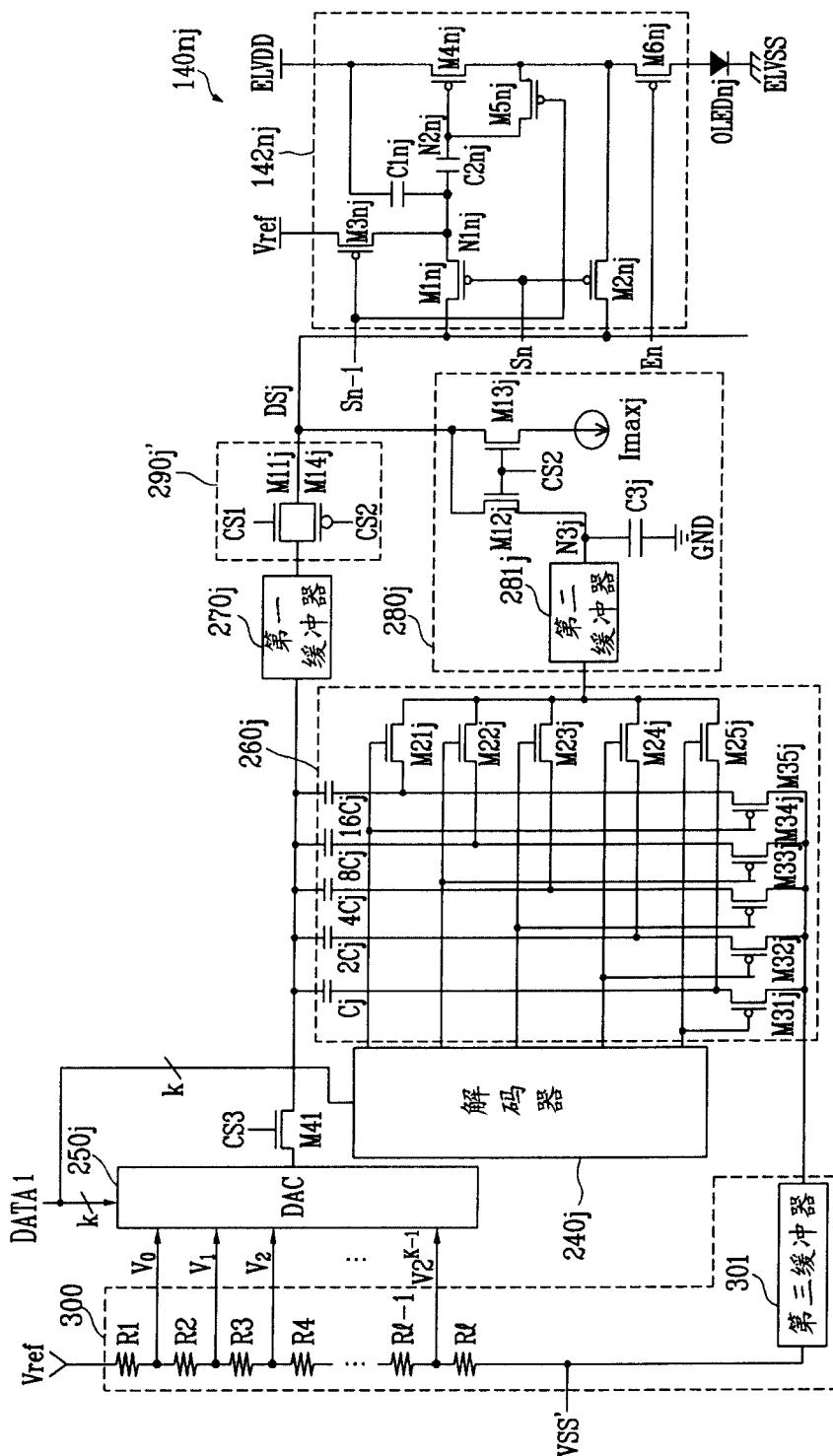

图 10 示出了采用开关单元的另一实施例的图 8 中示出的连接方案；

图 11 示出了连接图 6 中示出的伽马电压单元、数模转换器、解码器、电压控制器、开关单元和电流吸收单元以及图 5 中示出的像素的连接方案的第二实施例的示意图。

### 具体实施方式

2005 年 8 月 1 日在韩国知识产权局提交的题为“数据驱动电路和利用该数据驱动电路的有机发光显示器的驱动方法”的第 2005-0070438 号韩国专利申请通过引用全部包含于此。

以下，将参照附图更充分地描述本发明，在附图中示出了本发明的示例性实施例。然而，本发明可以以不同的形式实施，不应该被理解为限于在此提出的实施例。提供了这些实施例将使得本公开彻底和完整，并将本发明的范围充分地传达给本领域的技术人员。相同的标号始终表示相同的元件。

以下，将参照图 2 至图 11 来描述本发明的示例性实施例。在采用本发明的一个或多个方面的数据驱动电路、数据驱动方法和发光显示器中，由于利用当从各像素吸收电流时产生的补偿电压来重置数据信号的电压，所以不管晶体管的电子迁移率、阈值电压等如何变化，都能够显示均匀的图像。

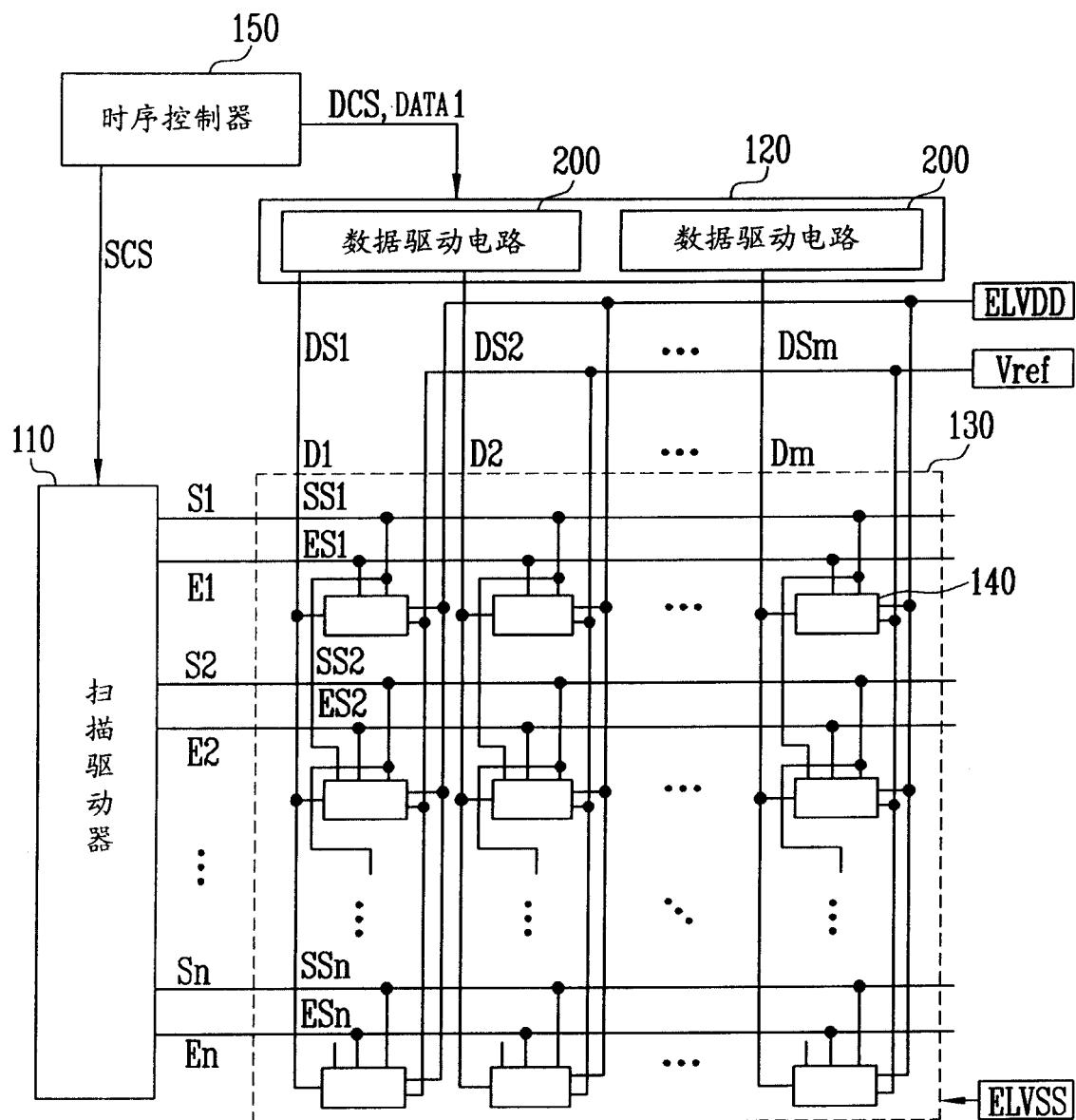

图 2 示出了根据本发明实施例的发光显示器的示意图。

如图 2 所示，发光显示器可包括扫描驱动器 110、数据驱动器 120、像素单元 130 和时序控制器 150。像素单元 130 可包括多个像素 140。例如，像素单元 130 可包括布置成 n 行和 m 列的  $n \times m$  个像素 140，其中，n 和 m 可均为整数。像素 140 可与扫描线 S1 至 Sn、发射控制线 E1 至 En 和数据线 D1 至 Dm 连接。在由发射控制线 E1 至 En 和数据线 D1 至 Dm 划分的区域中分别形成像素 140。扫描驱动器 110 可驱动扫描线 S1 至 Sn 和发射控制线 E1 至 En。数据驱动器 120 可驱动数据线 D1 至 Dm。时序控制器 150 可控制扫描驱

动器 110 和数据驱动器 120。数据驱动器 120 可包括一个或多个数据驱动电路 200。

时序控制器 150 响应外部供应的同步信号（未示出）产生数据驱动控制信号 DCS 和扫描驱动控制信号 SCS。可将由时序控制器 150 产生的数据驱动控制信号 DCS 供应到数据驱动器 120。可将时序控制器 150 产生的扫描驱动控制信号 SCS 供应到扫描驱动器 110。时序控制器 150 可根据外部供给的数据（未示出）将第一数据 DATA1 供给至数据驱动器 120。

扫描驱动器 110 可从时序控制器 150 接收扫描驱动控制信号 SCS。扫描驱动器 110 基于接收的扫描驱动控制信号 SCS 产生扫描信号 SS1 至 SS<sub>n</sub>，并可将扫描信号 SS1 至 SS<sub>n</sub> 顺序地并分别地供给至扫描线 S1 至 S<sub>n</sub>。扫描驱动器 110 可将发射控制信号 ES1 至 ES<sub>n</sub> 顺序地供给至发射控制线 E1 至 E<sub>n</sub>。可从低电压信号变成高电压信号地供给各发射控制信号 ES1 至 ES<sub>n</sub>，例如，使得“导通”发射控制信号，例如高电压信号，至少部分地与扫描信号 SS1 至 SS<sub>n</sub> 中的至少两个重叠。因此，在本发明的实施例中，发射控制信号 ES1 至 ES<sub>n</sub> 的脉宽可等于或大于扫描信号 SS1 至 SS<sub>n</sub> 的脉宽。

数据驱动器 120 可从时序控制器 150 接收数据驱动控制信号 DCS。数据驱动器 120 可基于接收的数据驱动控制信号 DCS 和第一数据 DATA1 来产生数据信号 DS1 至 DS<sub>m</sub>。可将产生的数据信号 DS1 至 DS<sub>m</sub> 与供应到扫描线 S1 至 S<sub>n</sub> 的扫描信号 SS1 至 SS<sub>n</sub> 同步地供给至数据线 D1 至 D<sub>m</sub>。例如，当供给第一扫描信号 SS1 时，可将对应于像素 140 (1) (1 ~ m) 产生的数据信号 DS1 至 DS<sub>m</sub> 经数据线 D1 至 D<sub>m</sub> 同步地供给至第 1 行中的第 1 至第 m 像素；当供给第 n 扫描信号 SS<sub>n</sub> 时，可将对应于像素 140 (n) (1 ~ m) 产生的数据信号 DS1 至 DS<sub>m</sub> 经数据线 D1 至 D<sub>m</sub> 同步地供给至第 n 行中的第 1 至第 m 像素。

在用于驱动一个或多个像素 140 的一个水平周期 1H 的第一时间段期间，数据驱动器 120 可将预定电流供给至数据线 D1 至 D<sub>m</sub>。例如，一个水平周期 1H 可与完整的周期相对应，所述完整的周期与为了驱动各个像素 140 被供给至各个像素 140 的扫描信号 SS1 至 SS<sub>n</sub> 之一和数据信号 DS1 至 DS<sub>m</sub> 中相对应的一个相关。在一个水平周期的第二时间段期间，数据驱动器 120 可将预定电压供给至数据线 D1 至 D<sub>m</sub>。例如，一个水平周期 1H 可与完整的周期相对应，所述完整的周期与为了驱动各个像素 140 被供给至各个像素 140 的扫

描信号 SS1 至 SS<sub>n</sub> 之一和数据信号 DS1 至 DS<sub>m</sub> 中相对应的一个相关。在本发明的实施例中，数据驱动器 120 可包括至少一个数据驱动电路 200，所述数据驱动电路 200 用于在一个水平周期 1H 的第一时间段和第二时间段期间供给这种预定电流和预定电压。在下面的描述中，将在第二时间段期间可被供给至数据线 D1 至 D<sub>m</sub> 的预定电压称作数据信号 DS1 至 DS<sub>m</sub>。

像素单元 130 可连接到用于将第一电压 VDD 供给至像素 140 的第一电源 ELVDD、用于将第二电压 VSS 供给至像素 140 的第二电源 ELVSS 和用于将基准电压 Vref 供给至像素 140 的基准电源 ELVref。可从外部提供第一电源 ELVDD、第二电压 ELVSS 和基准电源 ELVref。像素 140 可接收第一电压 VDD 信号和第二电压 VSS 信号，并可根据可由数据驱动器 120 提供给像素 140 的数据信号 DS1 至 DS<sub>m</sub>，来控制流过各个发光器件/材料（例如 OLED）的电流。从而，像素 140 可产生与接收到的第一数据 DATA1 对应的光分量。

一些像素 140 或全部像素 140 可分别从第一电源 ELVDD、第二电源 ELVSS 和基准电源 ELVref 接收第一电压 VDD 信号、第二电压 VSS 信号和基准电压 Vref 信号。像素 140 可利用基准电压 Vref 信号来补偿第一电压 VDD 信号的压降和/或阈值电压。补偿的量可基于分别由基准电源 ELVref 和第一电源 ELVDD 提供的基准电压 Vref 信号和第一电压 VDD 信号的电压值之间的差。响应各个数据信号 DS1 至 DS<sub>m</sub>，像素 140 可将各个电流从第一电源 ELVDD 经例如 OLED 供给到第二电源 ELVSS。在本发明的实施例中，例如，每个像素 140 可具有如图 3 或图 5 所示的结构。

图 3 示出了在图 2 中示出的发光显示器中可采用的第 n<sub>m</sub> 示例性像素 140nm 的电路图。为了简单，图 3 示出了可在第 n 行扫描线 S<sub>n</sub> 和第 m 行数据线 D<sub>m</sub> 的交叉处设置的像素第 n<sub>m</sub> 像素。第 n<sub>m</sub> 像素 140nm 可连接到第 m 数据线 D<sub>m</sub>、第 n-1 和第 n 扫描线 S<sub>n-1</sub> 和 S<sub>n</sub> 及第 n 发射控制线 E<sub>n</sub>。为了简单，图 3 仅示出了一个示例性像素 140nm。在本发明的实施例中，发光显示器的所有像素 140 或者部分像素 140 可采用示例性像素 140nm 的结构。

参照图 3，第 n<sub>m</sub> 像素 140nm 可包括发光材料/器件（例如，OLED<sub>n</sub><sub>m</sub>）和用于将电流供应到相关发光材料/器件的第 n<sub>m</sub> 像素电路 142nm。

第 n<sub>m</sub> OLED<sub>n</sub><sub>m</sub> 响应从第 n<sub>m</sub> 像素电路 142nm 供应的电流，可产生预定颜色的光。第 n<sub>m</sub> OLED<sub>n</sub><sub>m</sub> 可由例如有机材料、荧光体材料和/或无机材料形成。

在本发明的实施例中，第 nm 像素电路 142nm 可产生用于补偿像素 140 内的变化和/或像素 140 之中的变化的补偿电压，从而像素 140 可显示亮度均匀的图像。在每个扫描周期内，第 nm 像素电路 142nm 可利用扫描信号 SS1 至 SS<sub>n</sub> 中的前一个供给的扫描信号来产生补偿电压。在本发明的实施例中，一个扫描周期可对应于被顺序地供给的扫描信号 SS1 至 SS<sub>n</sub>。因此，在本发明的实施例中，在每个周期内，可在供应第 n 扫描信号 SS<sub>n</sub> 之前供应第 n-1 扫描信号 SS<sub>n-1</sub>，并且当将第 n-1 扫描信号 SS<sub>n-1</sub> 供给到发光显示器的第 n-1 扫描线时，第 nm 像素电路 142nm 可采用第 n-1 扫描信号 SS<sub>n-1</sub> 来产生补偿电压。例如，在第二列中的第二像素，即，像素 140<sub>22</sub>，可利用第一扫描信号 SS1 来产生补偿电压。

补偿电压可补偿源电压信号中的压降和/或由第 nm 像素电路 142nm 的晶体管的阈值电压而导致的压降。例如，第 nm 像素电路 142nm 可基于利用在相同的扫描周期内前一个供给的扫描信号而产生的补偿电压，来补偿第一电压 VDD 信号的压降和/或晶体管的阈值电压，例如，补偿像素电路 142nm 的第四晶体管 M4nm 的阈值电压。

在本发明的实施例中，当将第 n-1 扫描信号 SS<sub>n-1</sub> 供给到第 n-1 扫描线 S<sub>n-1</sub> 时，像素电路 142nm 可补偿第一电源 ELVDD 的压降和第四晶体管 M4nm 的阈值电压，当将第 n 扫描信号 SS<sub>n</sub> 供给至第 n 扫描线 S<sub>n</sub> 时，像素电路 142nm 可充入与数据信号 DSm 对应的电压。在本发明的实施例中，像素电路 142nm 可包括第一至第六晶体管 M1nm 至 M6nm、第一电容器 C1nm 和第二电容器 C2nm，以产生补偿电压并驱动发光材料/器件。

第一晶体管 M1nm 的第一电极可连接到数据线 Dm，第一晶体管 M1nm 的第二电极可连接到第一节点 N1nm。第一晶体管 M1nm 的栅电极可连接到第 n 扫描线 S<sub>n</sub>。当将第 n 扫描信号 SS<sub>n</sub> 供给至第 n 扫描线 S<sub>n</sub> 时，可使第一晶体管 M1nm 导通。当第一晶体管 M1nm 导通时，数据线 Dm 可与第一节点 N1nm 电连接。

第一电容器 C1nm 的第一电极可连接到第一节点 N1nm，第一电容器 C1nm 的第二电极可连接到第一电源 ELVDD。

第二晶体管 M2nm 的第一电极可连接到数据线 Dm，第二晶体管 M2nm 的第二电极可连接到第四晶体管 M4nm 的第二电极。第二晶体管 M2nm 的栅电极可连接到第 n 扫描线 S<sub>n</sub>。当将第 n 扫描信号 SS<sub>n</sub> 供给至第 n 扫描线 S<sub>n</sub>

时，可使第二晶体管 M2nm 导通。当第二晶体管 M2nm 导通时，数据线 Dm 可与第四晶体管 M4nm 的第二电极电连接。

第三晶体管 M3nm 的第一电极可连接到基准电源 ELVref，第三晶体管 M3nm 的第二电极可连接到第一节点 N1nm。第三晶体管 M3nm 的栅电极可连接到第 n-1 扫描线 Sn-1。当将第 n-1 扫描信号 SSn-1 供给至第 n-1 扫描线 Sn-1 时，可使第三晶体管 M3nm 导通。当第三晶体管 M3nm 导通时，基准电压 Vref 可与第一节点 N1nm 电连接。

第四晶体管 M4nm 的第一电极可连接到第一电源 ELVDD，第四晶体管 M4nm 的第二电极可连接到第六晶体管 M6nm 的第一电极。第四晶体管 M4nm 的栅电极可连接到第二节点 N2nm。

第二电容器 C2nm 的第一电极可连接到第一节点 N1nm，第二电容器 C2nm 的第二电极可连接到第二节点 N2nm。

在本发明的实施例中，当供给第 n-1 扫描信号 SSn-1 时，可对第一电容器 C1nm 和第二电容器 C2nm 充电。具体地讲，可对第一电容器 C1nm 和第二电容器 C2nm 充电，并且第四晶体管 M4nm 可将与第二节点 N2nm 处的电压对应的电流供应到第六晶体管 M6nm 的第一电极。

第五晶体管 M5nm 的第二电极可连接到第二节点 N2nm，第五晶体管 M1nm 的第一电极可连接到第四晶体管 M4nm 的第二电极。第五晶体管 M5nm 的栅电极可连接到第 n-1 扫描线 Sn-1。当将第 n-1 扫描信号 SSn-1 供给至第 n-1 扫描线 Sn-1 时，可使第五晶体管 M5nm 导通，从而电流流过第四晶体管 M4nm。因此，第四晶体管 M4nm 可作为二极管来操作。

第六晶体管 M6nm 的第一电极可连接到第四晶体管 M4nm 的第二电极，第六晶体管 M6nm 的第二电极连接到第 nm OLEDnm 的阳极。第六晶体管 M6nm 的栅电极可连接到第 n 发射控制线 En。当将发射控制信号 ESn (例如，高电压信号) 供给至第 n 发射控制线 En 时，可使第六晶体管 M6nm 截止，当没有发射控制信号被供给至第 n 发射控制线 En 时，例如，将低电压信号供给至第 n 发射控制线 En 时，可使第六晶体管 M6nm 导通。

在本发明的实施例中，可供给发射控制信号 ESn 以与第 n-1 扫描信号 SSn-1 和第 n 扫描信号 SSn 至少部分叠置，其中，发射控制信号 ESn 被供给至第 n 发射控制线 En，第 n-1 扫描信号 SSn-1 可被供给至第 n-1 扫描线 Sn-1，第 n 扫描信号 SSn 可被供给至第 n 扫描线 Sn。因此，当将第 n-1 扫描信号 SSn-1

供给至第 n-1 扫描线 Sn-1，例如，将低电压信号供给至第 n-1 扫描线 Sn-1 时，和当将第 n 扫描信号 SSn 供给至第 n 扫描线 Sn，例如，将低电压信号供给至第 n 扫描线 Sn 时，可使第六晶体管 M6nm 截止，从而预定的电压可充入第一电容器 C1nm 和第二电容器 C2nm。在其它时间，可使第六晶体管 M6nm 导通以将第四晶体管 M4nm 和第 nm OLEDnm 相互电连接。在图 3 所示的示例性实施例中，晶体管 M1nm 至 M6nm 是 PMOS 晶体管，PMOS 晶体管是当低电压信号被供给至各自的栅电极时导通，而当高电压信号被供给至各自的栅电极时截止的晶体管。然而，本发明并不限于 PMOS 器件。

在图 3 示出的像素中，由于基准电源 ELVref 不能将电流供给至像素 140，所以不会发生基准电压 Vref 的压降。因此，不管像素 140 位于什么位置，都能够将基准电压 Vref 信号的电压值保持一致。在本发明的实施例中，基准电压 Vref 的电压值可等于第一电压 VDD 或不同于第一电压 VDD。

图 4 示出了用于驱动图 3 中示出的示例性的第 nm 像素 140nm 可采用的示例性波形。如图 4 所示，用于驱动第 nm 像素 140nm 的一个水平周期 1H 可分为第一时间段和第二时间段。在第一时间段期间，预定的电流 (PC) 可分别流过数据线 D1 至 Dm。在第二时间段期间，可经数据线 D1 至 Dm 将数据信号 DS1 至 DSM 供给各个像素 140。在第一时间段期间，可将各 PC 从每个像素 140 供给至数据驱动电路 200，数据驱动电路 200 可至少部分起电流吸收器的作用。在第二时间段期间，可将数据信号 DS1 至 DSM 从数据驱动电路 200 供给至像素 140。为了简单，在下面的描述中，将假定至少最初，即，在像素 140 的操作过程中可产生任何压降之前，基准电压 Vref 信号的电压值等于第一电压 VDD 信号的电压值。

将参照图 3 和图 4 详细描述操作像素 140 中的第 nm 像素 140nm 的第 nm 像素电路 142nm 的示例性方法。首先，可将第 n-1 扫描信号 SSn-1 供给至第 n-1 扫描线 Sn-1，以控制可与第 n-1 扫描线 Sn-1 连接的 m 个像素的选通/关断操作。当扫描信号 SSn-1 被供给至第 n-1 扫描线 Sn-1 时，可使第 nm 像素 140nm 的第 nm 像素电路 142nm 的第三晶体管 M3nm 和第五晶体管 M5nm 导通。当第五晶体管 M5nm 导通时，电流可流过第四晶体管 M4nm，使得第四晶体管 M4nm 可作为二极管操作。当第四晶体管 M4nm 作为二极管进行操作时，第二节点 N2nm 的电压值可与第四晶体管 M4nm 的阈值电压和由第一电源 ELVDD 供给的第一电压 VDD 信号的电压之间的差对应。

更具体地讲，当第三晶体管 M3nm 导通时，可将来自基准电源 ELVref 的基准电压 Vref 信号施加到第一节点 N1nm。第二电容器 C2nm 可被充入与第一节点 N1nm 和第二节点 N2nm 之间的差相对应的电压。在本发明的来自基准电源 ELVref 的基准电压 Vref 信号和来自第一电源 ELVDD 的第一电压 VDD 信号在最初（即，在像素 140 的操作过程中可产生压降之前）可相同的实施例中，与第四晶体管 M4nm 的阈值电压对应的电压可充入第二电容器 C2nm 中。在本发明的第一电压 VDD 信号出现预定的压降的实施例中，在第二电容器 C2nm 中可充入第四晶体管 M4nm 的阈值电压和与第一电源 ELVDD 的压降的幅度对应的电压。

在本发明的实施例中，在可将第 n-1 扫描信号 SS<sub>n-1</sub> 供给至第 n-1 扫描线 S<sub>n-1</sub> 的时间段期间，可对第二电容器 C2nm 充入预定电压，所述预定电压与对应于第一电压 VDD 信号的压降的电压和第四晶体管 M4nm 的阈值电压之和对应。通过在第 m 列的各个 n-1 像素的操作过程中存储与来自第一电源 ELVDD 的第一电压 VDD 信号的压降和第四晶体管 M4nm 的阈值电压之和对应的电压，能够在各个第 nm 像素 140nm 的操作过程中稍后利用存储的电压来补偿第一电压 VDD 信号的压降和所述的阈值电压。

在本发明的实施例中，在将第 n 扫描信号 SS<sub>n</sub> 供给至第 n 扫描线 S<sub>n</sub> 之前，可将对应于第四晶体管 M4nm 的阈值电压与基准电压 Vref 信号和第一电压 VDD 信号之间的差的和的电压充入第二电容器 C2nm。当将第 n 扫描信号 SS<sub>n</sub> 供给至第 n 扫描线 S<sub>n</sub> 时，可使第一晶体管 M1nm 和第二晶体管 M2nm 导通。在一个水平周期的第一时间段期间，当第 nm 像素 140nm 的像素电路 142nm 的第二晶体管 M2nm 导通时，可将 PC 经数据线 D<sub>m</sub> 从第 nm 像素 140nm 供给至数据驱动电路 200。在本发明的实施例中，可将 PC 经第一电源 ELVDD、第四晶体管 M4nm、第二晶体管 M2nm 和数据线 D<sub>m</sub> 供给至数据驱动电路 200。然后响应供给的 PC，可对第一电容器 C1nm 和第二电容器 C2nm 充入预定的电压。

数据驱动电路 200 可基于预定的电压，即，基于如上所述吸收 PC 时会产生的补偿电压，重置伽马电压单元（未示出）的电压。来自伽马电压单元（未示出）的重置电压可用于产生将被分别供给至数据线 D1 至 D<sub>m</sub> 的数据信号 DS1 至 DS<sub>m</sub>。

在本发明的实施例中，在一个水平周期的第二时间段期间，可将产生的

数据信号 DS<sub>1</sub> 至 DS<sub>m</sub> 分别供给到各数据线 D<sub>1</sub> 至 D<sub>m</sub>。更具体地讲，例如，在一个水平周期的第二时间段期间，可将各自产生的数据信号 DS<sub>m</sub> 经第一晶体管 M<sub>1nm</sub> 供给到各自的第一节点 N<sub>1nm</sub>。然后，可对第一电容器 C<sub>1nm</sub> 充入与数据信号 DS<sub>m</sub> 和第一电源 ELVDD 之间的差对应的电压。随后，第二节点 N<sub>2nm</sub> 可浮置，并且第二电容器 C<sub>2nm</sub> 可保持先前充入的电压。

在本发明的实施例中，在控制第 m 列中的第 n 像素并将扫描信号 SS<sub>n-1</sub> 供给到前一个的扫描线 S<sub>n-1</sub> 的时间段期间，可对第 nm 像素 140nm 中的第二电容器 C<sub>2nm</sub> 充入与第四晶体管 M<sub>4nm</sub> 的阈值电压和来自第一电源 ELVDD 的第一电压 VDD 信号的压降对应的电压，以补偿来自第一电源 ELVDD 的第一电压 VDD 信号的压降和第四晶体管 M<sub>4nm</sub> 的阈值电压。

在本发明的实施例中，在将第 n 扫描信号 SS<sub>n</sub> 供给到第 n 扫描线 S<sub>n</sub> 的时间段期间，可重置伽马电压单元（未示出）的电压，从而利用各个重置的伽马电压可补偿包括在与各条数据线 D<sub>1</sub> 至 D<sub>m</sub> 相关的各个第 n 像素 140n 中的晶体管的电子迁移率，并可将各自产生的数据信号 DS<sub>1</sub> 至 DS<sub>m</sub> 供给到第 n 像素 140n。因此，在本发明的实施例中，可补偿晶体管的阈值电压的非均匀性和电子迁移率的非均匀性，并可显示亮度均匀的图像。下面将描述重置伽马电压单元的电压的过程。

图 5 示出了图 2 中示出的发光显示器可采用的第 nm 像素 140nm' 的另一示例性实施例。图 5 中示出的第 nm 像素 140nm' 的结构与图 3 中示出的第 nm 像素 140nm 的结构基本相同，除了像素电路 142 nm' 中的第一电容器 C<sub>1 nm'</sub> 的布置以及与第一节点 N<sub>1 nm'</sub> 和第二节点 N<sub>2 nm'</sub> 的各个连接。在图 5 示出的示例性实施例中，第一电容器 C<sub>1 nm'</sub> 的第一电极可连接到第二节点 N<sub>2 nm'</sub>，第一电容器 C<sub>1 nm'</sub> 的第二电极可连接到第一电源 ELVDD。第二电容器 C<sub>2nm</sub> 的第一电极可连接到第一节点 N<sub>1 nm'</sub>，第二电容器 C<sub>2nm</sub> 的第二电极可连接到第二节点 N<sub>2 nm'</sub>。第一节点 N<sub>1 nm'</sub> 可连接到第一晶体管 M<sub>1nm</sub> 的第二电极、第三晶体管 M<sub>3nm</sub> 的第二电极和第二电容器 C<sub>2nm</sub> 的第一电极。第二节点 N<sub>2 nm'</sub> 可连接到第四晶体管 M<sub>4nm</sub> 的栅电极、第五晶体管 M<sub>5nm</sub> 的第二电极、第一电容器 C<sub>1 nm'</sub> 的第一电极和第二电容器 C<sub>2nm</sub> 的第二电极。

在下面的描述中，将采用与以上图 3 中示出的第 nm 像素 140nm 的描述中使用的标号相同的标号来描述图 5 中示出的第 nm 像素 140 nm' 的示例性实施例中的相同特征。

将参照图 4 和图 5 来详细描述操作像素 140 的第 nm 像素 140 nm' 的第 nm 像素电路 142 nm' 的示例性方法。首先，在驱动第 n-1 像素 140 (n-1) (1 ~ m)，即，驱动在第 n-1 行排列的像素的水平周期期间，当将第 n-1 扫描信号 SS<sub>n-1</sub> 供给到第 n-1 扫描线 S<sub>n-1</sub> 时，可使第 n 像素 140 (n) (1 ~ m) 中的第三晶体管 M<sub>3nm</sub> 和第五晶体管 M<sub>5nm</sub> 导通，即，使在第 n 行排列的像素中的第三晶体管 M<sub>3nm</sub> 和第五晶体管 M<sub>5nm</sub> 导通。

当第五晶体管 M<sub>5nm</sub> 导通时，电流可流过第四晶体管 M<sub>4nm</sub>，使得第四晶体管 M<sub>4nm</sub> 可作为二极管操作。当第四晶体管 M<sub>4nm</sub> 用作二极管时，可将与通过从第一电源 ELVDD 减去第四晶体管 M<sub>4nm</sub> 的阈值电压而获得的值对应的电压施加到第二节点 N<sub>2 nm'</sub>。可对第一电容器 C<sub>1 nm'</sub> 充入与第四晶体管 M<sub>4nm</sub> 的阈值电压对应的电压。如图 5 所示，第一电容器 C<sub>1 nm'</sub> 可设置在第二节点 N<sub>2 nm'</sub> 和第一电源 ELVDD 之间。

当第三晶体管 M<sub>3nm</sub> 导通时，可将基准电源 ELVref 的电压施加到第一节点 N<sub>1 nm'</sub>。然后，可对第二电容器 C<sub>2nm</sub> 充入与第一节点 N<sub>1 nm'</sub> 和第二节点 N<sub>2 nm'</sub> 之间的差对应的电压。在将第 n-1 扫描信号 SS<sub>n-1</sub> 供给到第 n-1 扫描线 S<sub>n-1</sub> 并且第一晶体管 M<sub>1nm</sub> 和第二晶体管 M<sub>2nm</sub> 可截止的时间段期间，不能将数据信号 DS<sub>m</sub> 供应到第 nm 像素 140 nm'。

然后，在驱动第 nm 像素 140 nm' 的一个水平周期的第一时间段期间，可将扫描信号 SS<sub>n</sub> 供应到第 n 扫描线 S<sub>n</sub>，第一晶体管 M<sub>1nm</sub> 和第二晶体管 M<sub>2nm</sub> 可导通。当第二晶体管 M<sub>2nm</sub> 导通时，在一个水平周期的第一时间段期间，可经数据线 D<sub>m</sub> 将各 PC 从第 nm 像素 140 nm' 供给到数据驱动电路 200。可经第一电源 ELVDD、第四晶体管 M<sub>4nm</sub>、第二晶体管 M<sub>2nm</sub> 和数据线 D<sub>m</sub> 将 PC 供给到数据驱动电路 200。响应 PC，可对第一电容器 C<sub>1nm'</sub> 和第二电容器 C<sub>2nm</sub> 充入预定的电压。

数据驱动电路 200 可利用响应 PC 施加的补偿电压重置伽马电压单元的电压，以利用伽马电压单元的各自重置的电压来产生数据信号 DS。

然后，在驱动第 nm 像素 140 nm' 的一个水平周期的第二时间段期间，可将数据信号 DS<sub>m</sub> 供给到第一节点 N<sub>1nm'</sub>。与数据信号 DS<sub>m</sub> 对应的预定电压可充入第一电容器 C<sub>1nm'</sub> 和第二电容器 C<sub>2nm'</sub>。

当供给数据信号 DS<sub>m</sub> 时，第一节点 N<sub>1 nm'</sub> 的电压可从基准电源 ELVref 的电压 V<sub>ref</sub> 下降到数据信号 DS<sub>m</sub> 的电压。这时，由于第二节点 N<sub>2 nm'</sub> 可被

浮置时，响应第一节点 N<sub>1 nm'</sub>的压降的量，可减小第二节点 N<sub>2nm'</sub>的电压值。在第二节点 N<sub>2nm'</sub>处可发生的电压减小的量可由第一电容器 C<sub>1nm'</sub>和第二电容器 C<sub>2nm'</sub>的电容确定。

当第二节点 N<sub>2nm'</sub>的电压下降时，与第二节点 N<sub>2nm'</sub>的电压值对应的预定电压可充入第一电容器 C<sub>1nm'</sub>。当基准电源 ELVref 的电压值固定时，充入第一电容器 C<sub>1nm'</sub>的电压的量可由数据信号 DSm 确定。即，在图 5 中示出的第 nm 像素 140nm' 中，因为充入第一电容器 C<sub>1nm'</sub>和第二电容器 C<sub>2nm'</sub>中的电压值可由基准电源 ELVref 和数据信号 DSm 确定，所以无论第一电源 ELVDD 的压降是多少，都能够充入期望的电压。

在本发明的实施例中，可重置伽马电压单元的电压，利用重置的伽马电压，使得可补偿包括在各像素 140 中的晶体管的电子迁移率，并供给各自产生的数据信号。在本发明的实施例中，可补偿晶体管的阈值电压之间的非均匀性和晶体管的电子迁移率的偏差，从而能够使得将被显示的图像具有均匀的亮度。

图 6 示出了图 2 中示出的数据驱动电路的第一示例性实施例的方框图。为了简单，在图 6 中，假定数据驱动电路 200 具有 j 个通道，其中，j 是等于或大于 2 的自然数。

如图 6 所示，数据驱动电路 200 可包括移位寄存器单元 210、取样锁存器单元 220、保持锁存器单元 230、解码器单元 240、数模转换器单元（以下，称作 DAC）250、电压控制器单元 260、第一缓冲器单元 270、电流供给单元 280、选择器 290 和伽马电压单元 300。

移位寄存器单元 210 可从时序控制器 150 接收源移位时钟 SSC 和源起始脉冲 SSP。移位寄存器单元 210 可利用源移位时钟 SSC 和源起始脉冲 SSP 以在源移位时钟 SSC 的每一个周期将源起始脉冲 SSP 移位的同时依次产生 j 个取样信号。移位寄存器单元 210 可包括 j 个移位寄存器 2101 至 210j。

取样锁存器单元 220 响应从移位寄存器单元 210 依次供给的取样信号，依次存储各第一数据 DATA1。为了分别存储 j 个第一数据 DATA1-1 至 DATA1-j，取样锁存器单元 220 可包括 j 个取样锁存器 2201 至 220j。取样锁存器 2201 至 220j 中的每个可具有与第一数据 DATA1 的位数对应的大小。例如，当第一数据 DATA1 是 k 位时，取样锁存器 2201 至 220j 中的每个可具有 k 位的大小，从而取样锁存器 2201 至 220j 可分别存储 k 位的 j 个第一数据

DATA1-1 至 DATA1-j 中的每个。

当将源输出使能 SOE 信号输入到保持锁存器单元 230 时，保持锁存器单元 230 可从取样锁存器单元 220 接收第一数据 DATA1 并存储第一数据 DATA1。当输入 SOE 信号时，保持锁存器单元 230 可将存储在其中的第一数据 DATA1 供给到解码器单元 240 和/或 DAC 单元 250。为了存储 j 个第一数据 DATA1-1 至 DATA1-j，保持锁存器单元 230 可包括 j 个保持锁存器 2301 至 230j。保持锁存器 2301 至 230j 中的每个可具有与第一数据 DATA1 的位数相对应的大小。例如，保持锁存器 2301 至 230j 中的每个可具有 k 位的大小，从而可分别存储 k 位的第一数据 DATA1-1 至 DATA1-j 中的每个。

解码器单元 240 可包括 j 个解码器 2401 至 240j。解码器 2401 至 240j 中的每个可接收 k 位的各个第一数据 DATA1，并可将 k 位的第一数据 DATA1 转换成 p (p 是自然数) 位的第二数据 DATA2。在本发明的实施例中，解码器 2401 至 240j 中的每个可利用二进制加权值来产生 p 位的第二数据 DATA2。

在本发明的实施例中，可确定外部接收的第一数据 DATA1 的加权值以对伽马电压单元 300 设置预定的电压。例如，可确定允许从多个灰阶电压中选择期望的灰阶电压的第一数据 DATA1 的位数。伽马电压单元 300 可产生多个灰阶电压。对应于灰阶电压，解码器 2401 至 240j 可利用二进制的加权值将 k 位的第一数据 DATA1 转换成各个 p 位的第二数据 DATA2-1 至 DATA2-j。例如，解码器 2401 至 240j 可利用 8 位的第一数据 DATA1 产生 5 位的第二数据 DATA2。

电流供给单元 280 可从由扫描信号 SS1 至 SS<sub>n</sub> 之一选择的各像素 140 吸收预定的电流 PC。在每个水平周期的第一时间段期间，电流供给单元 280 可经数据线 D1 至 D<sub>j</sub> 中的各条来接收吸收电流。

在本发明的实施例中，电流供给单元 280 可吸收与各个发光器（例如，OLED）可采用以发射最大亮度的光的最小电流量对应的电流量。随后，电流供给单元 280 可将预定的补偿电压供给到电压控制器单元 260。吸收各个预定电流 PC 的同时可产生补偿电压。在图 6 中示出的示例性实施例中，电流供给单元 280 包括 j 个电流吸收单元 2801 至 280j。

伽马电压单元 300 可产生与 k 位的第一数据 DATA1 对应的预定灰阶电压。如图 8 所示，伽马电压单元 300 可包括多个配电器或多个分压电阻器 R<sub>1</sub> 至 R<sub>l</sub>，并可产生 2<sup>k</sup> 个灰阶电压。伽马电压单元 300 产生的灰阶电压可被供给

到 DAC 单元 250。

DAC 单元 250 可包括 j 个 DAC 2501 至 250j。可将伽马电压单元 300 产生的灰阶电压供给到 j 个 DAC 2501 至 250j 中的每个。DAC 2501 至 250j 中的每个可基于从各个保持锁存器 2301 至 230j 供给的第一数据 DATA1-1 至 DATA1-j, 来选择伽马电压单元 300 可供给的灰阶电压之一作为数据信号 DS。例如, DAC 2501 至 250j 可基于各第一数据 DATA1-1 至 DATA1-j 的位数来分别选择伽马电压单元 300 可供给的灰阶电压之一作为数据信号 DS。

电压控制器单元 260 可包括 j 个电压控制器 2601 至 260j。

电压控制器 2601 至 260j 均可接收补偿电压和第三供给电压 VSS' 信号, 其中, 所述补偿电压例如经各电流吸收单元 2801 至 280j 供给的电压或第二数据 DATA2。在本发明的实施例中, 可采用相同的电源或不同的电源来供给第二电压 VSS 信号和第三电压 VSS' 信号。可将第三电压 VSS' 信号可供给到伽马电压单元 300 的接线端。电压控制器 2601 至 260j 可接收补偿电压和/或第二数据 DATA1, 以及第三电压 VSS' 信号, 并且电压控制器 2601 至 260j 可控制选择的数据信号 DS 的电压值, 从而可补偿像素 140 中包括的晶体管的变化, 如补偿由包括在各像素 140 中的晶体管的电子迁移率、阈值电压等引起的变化。

第一缓冲器单元 270 可将各个数据信号 DS 供给到选择器 290。如上所述, 电压控制器单元 260 可控制各个数据信号 DS 的电压。在本发明的实施例中, 第一缓冲器单元 270 可包括 j 个第一缓冲器 2701 至 270j。

选择器 290 可控制数据线 D1 至 Dj 和第一缓冲器 2701 至 270j 之间的电连接。在一个水平周期的第二时间段期间, 选择器 290 可将数据线 D1 至 Dj 和第一缓冲器 2701 至 270j 相互电连接。在本发明的实施例中, 仅在第二时间段期间, 选择器 290 可将数据线 D1 至 Dj 和第一缓冲器 2701 至 270j 相互电连接。在除了第二时间段之外的时间段期间, 选择器 290 可保持数据线 D1 至 Dj 和第一缓冲器 2701 至 270j 相互断开。

选择器 290 可包括 j 个开关单元 2901 至 290j。可将产生的各个数据信号 DS1 至 DSj 从第一缓冲器 2701 至 270j 经开关单元 2901 至 290j 分别供给至数据线 D1 至 Dj。在本发明的实施例中, 选择器 290 可采用其它类型的开关单元。图 10 示出了选择器 290 可采用的开关单元 290j' 的另一个实施例。

如图 7 所示, 在第二示例性实施例中, 数据驱动电路 200 可包括连接到

保持锁存器单元 230 的电平转换器 310。电平转换器 310 可包括电平寄存器 3101 至 310j， 并可将可从保持锁存器单元 230 供给的第一数据 DATA1 的电压升高，可将电平转换的结果提供到 DAC 单元 250 和解码器单元 240。当从外部系统提供到数据驱动电路 200 的数据（未示出）具有高电压电平时，通常应该提供具有耐高压性能的电路组件，因此增加了制造成本。在本发明的实施例中，从外部系统供给到数据驱动电路 200 的数据可具有低电压电平，并且可通过电平转换器 310 将该低电压电平转变成高电压电平。

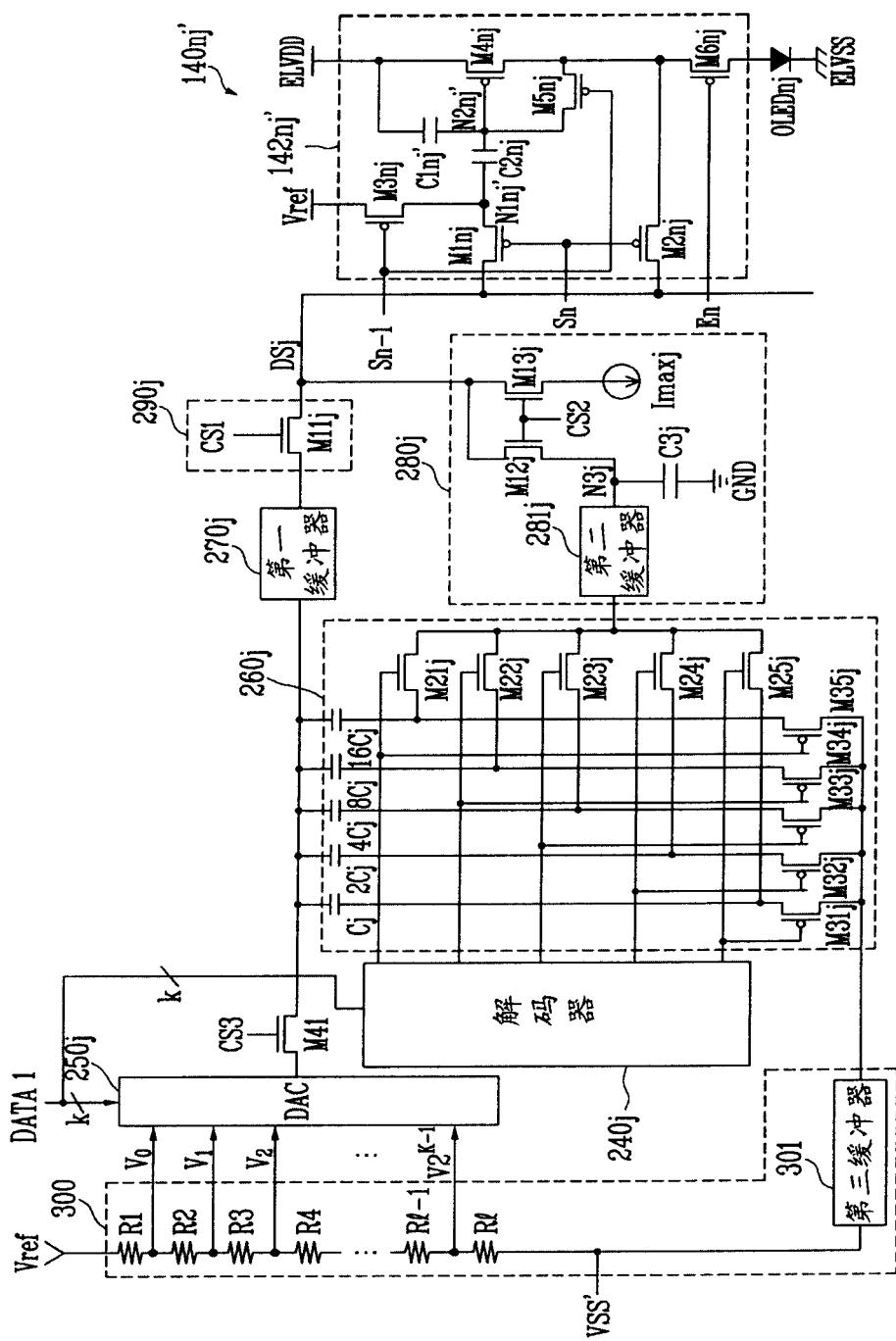

图 8 示出了用于连接伽马电压单元 300、DAC 250j、解码器 240j、电压控制器 260j、开关单元 290j、电流吸收单元 280j 和像素 140nj 的连接方案的第一实施例。为了简单，图 8 仅示出了一个通道；即，第 j 通道，并且假定数据线 Dj 连接到根据图 3 中示出的像素 140nm 的示例性实施例的第 nj 像素 140nj。

如图 8 所示，伽马电压单元 300 可包括多个配电电阻器 R1 至 Rl。可将配电电阻器 R1 至 Rl 设置在基准电源电压 Vref 和第三电源电压 VSS'之间。配电电阻器 R1 至 Rl 可分配供应到其的电压或将供应到其的电压分压。例如，配电电阻器 R1 至 Rl 可分配基准电源电压 Vref 和第三电源电压 VSS'之间的电压或者将该电压分压，并可产生多个灰阶电压 V0 至 V<sub>2^K-1</sub>。配电电阻器 R1 至 Rl 可将产生的灰阶电压 V0 至 V<sub>2^K-1</sub> 供给到 DAC250j。伽马电压单元 300 可将第三电源电压 VSS' 经第三缓冲器 301 供给到电压控制器 260j。

DAC 250j 可基于第一数据 DATA1 的位数，选择灰阶电压 V0 至 V<sub>2^K-1</sub> 之一作为数据信号 DS，并可将选择的电压供给到第一缓冲器 270j。

如图 8 所示，可在 DAC 250j 和第一缓冲器 270j 之间设置晶体管，例如，第四十一晶体管 M41，所述第四十一晶体管 M41 由第三控制信号 CS3 控制。在这样的实施例中，在驱动像素 140nj 的水平周期的第一时间段的预定时间期间，第四十一晶体管 M41 可导通，第四十一晶体管 M41 将从 DAC 250j 供给的数据信号 DSj 供给到第一缓冲器 270j。更具体地讲，例如，在第二控制信号 CS2 之后可提高第三控制信号 CS3（将在后面描述），且第三控制信号 CS3 可与第二控制信号 CS2 同时下降。

电流吸收单元 280j 可包括第十二晶体管 M12j、第十三晶体管 M13j、电流源 Imaxj、第三电容器 C3j、第三节点 N3j、地电压源 GND 和第二缓冲器 281j。第二控制信号 CS2 可控制第十二晶体管 M12j 和第十三晶体管 M13j。

电流源  $I_{maxj}$  可连接到第十三晶体管  $M13j$  的第一电极。第三电容器  $C3j$  可连接在第三节点  $N3j$  和地电压源  $GND$  之间。第二缓冲器  $281j$  可连接在第三节点  $N3j$  和电压控制器  $260j$  之间。

第十二晶体管  $M12j$  的栅电极可连接到第十三晶体管  $M13j$  的栅电极。第十二晶体管  $M12j$  的第二电极可连接到第十三晶体管  $M13j$  的第二电极和数据线  $Dj$ 。第十二晶体管  $M12j$  的第一电极可连接到第二缓冲器  $281$ 。在各水平周期  $1H$  的第一时间段期间，可使第十二晶体管  $M12j$  和第十三晶体管  $M13j$  导通。在水平周期  $1H$  的第二时间段期间，可使第十二晶体管  $M12j$  和第十三晶体管  $M13j$  截止。第二控制信号  $CS2$  可控制第十二晶体管  $M12j$  和第十三晶体管  $M13j$  的导通/截止状态。

在一个水平周期  $1H$  的第一时间段期间，电流源  $I_{maxj}$  可从像素  $140nj$  接收可被供给到像素  $140nj$  的发光器（例如， $OLEDnj$ ）的用于以最大亮度发光的至少最小电流量。如上所述，第二控制信号  $CS2$  可控制第十二晶体管  $M12j$  和第十三晶体管  $M13j$  在第一时间段期间导通，从而使得预定的电流  $PC$  从像素  $140nj$  流入电流吸收单元  $280j$ 。

当来自像素  $140nj$  的电流吸收到电流源  $I_{maxj}$  时，第三电容器  $C3j$  可存储可施加到第三节点  $N3j$  的补偿电压。在一个水平周期  $1H$  的第一时间段期间，第三电容器  $C3j$  可存储施加到第三节点  $N3j$  的补偿电压，即使在第十二晶体管  $M12j$  和第十三晶体管  $M13j$  截止时，也可以保持第三节点  $N3j$  处的补偿电压稳定。

第二缓冲器  $281$  可将施加到第三节点  $N3j$  的补偿电压传输到电压控制器  $260j$ 。

解码器  $240j$  可接收  $k$  位的第一数据  $DATA1$  并利用二进制加权值将  $k$  位的第一数据  $DATA1$  转换成  $p$  位的第二数据  $DATA2$ 。在水平周期  $1H$  的第一时间段期间，解码器  $240j$  可将初始信号（未示出）供给到电压控制器  $260j$ ，然后在同一水平周期  $1H$  的第二时间段期间，解码器  $240j$  将  $p$  位的第二数据  $DATA2$  供给到电压控制器  $260j$ 。在下面的示例性实施例的描述中，为了简单，将假定  $p$  位是 5 位。在本发明的实施例中， $p$  可以是大于或等于 0 的任何整数。

电压控制器  $260j$  可接收补偿电压和/或第二数据  $DATA2$ ，以及第三电源电压  $VSS'$ ，并可以控制数据信号  $DSj$  的电压值。在示例性实施例的描述中，

参考术语“p”将等于 5，然而，“p”可是任何整数。为了控制数据信号 DSj 的电压值，电压控制器 260j 可包括 p 个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj，p 个 PMOS 晶体管 M31j、M32j、M33j、M34j 和 M35j，以及 p 个 NMOS 晶体管 M21j、M22j、M23j、M24j 和 M25j。电容器 Cj、2Cj、4Cj、8Cj 和 16Cj 可连接到连接第四十一晶体管 M41 和第一缓冲器 270j 的电通路。p 个 PMOS 晶体管 M31j、M32j、M33j、M34j 和 M35j 可分别连接到第三缓冲器 301 和 p 个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj。p 个 NMOS 晶体管 M21j、M22j、M23j、M24j 和 M25j 可分别连接在第二缓冲器 281j 和 p 个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj 之间。

P 个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj 的电容值可彼此相关，从而 p 个电容器的电容可以按  $2^0$ 、 $2^1$ 、 $2^2$ 、 $2^3$  和  $2^4$  的顺序分别增大。例如，p 个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj 的电容可根据第二数据 DATA2 具有各自的二进制加权值。

p 个 PMOS 晶体管 M31j、M32j、M33j、M34j 和 M35j 可分别设置在 p 个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj 和第三缓冲器 301 之间。当从解码器 240j 供给初始信号（未示出）时，可导通 p 个 PMOS 晶体管 M31j、M32j、M33j、M34j 和 M35j，并且 p 个 PMOS 晶体管 M31j、M32j、M33j、M34j 和 M35j 可将 p 个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj 的接线端的电压分别设置为第三电源电压 VSS'。

p 个 NMOS 晶体管 M21j、M22j、M23j、M24j 和 M25j 可分别设置在 p 个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj 的每个和第二缓冲器 281j 之间。基于从解码器 240j 产生的第二数据 DATA2，在驱动像素 140nj 的一个水平周期 1H 的第二时间段期间，p 个 NMOS 晶体管 M21j、M22j、M23j、M24j 和 M25j 可导通或截止。可基于第二数据 DATA2 的位加权值来控制 p 个 NMOS 晶体管 M21j、M22j、M23j、M24j 和 M25j，以选择 p 个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj 的各一个/多个。例如，如果将由解码器 240j 产生的第二数据 DATA2 的位设置成“00011”，则第二十四晶体管 M24j 和第二十五晶体管 M25j 导通，以将补偿电压（例如，存储在第三电容器 C3j 中的电压）施加到 p 个电容器中的各自的第一电容器和第二电容器（例如，Cj 和 2Cj）的接线端。在这些实施例中，如果与  $2^0$  和  $2^1$  对应的位的值为“1”，则可控制 p 个 NMOS 晶体管 M21j、M22j、M23j、M24j 和 M25j 的导通/截止状态，从而可将补偿

电压施加到 p 个电容器 C<sub>j</sub>、2C<sub>j</sub>、4C<sub>j</sub>、8C<sub>j</sub> 和 16C<sub>j</sub> 中的第一电容器 C<sub>j</sub> 和第二电容器 2C<sub>j</sub> 的各自的接线端。如上所述，在本发明的实施例中，p 个电容器 C<sub>j</sub>、2C<sub>j</sub>、4C<sub>j</sub>、8C<sub>j</sub> 和 16C<sub>j</sub> 中的第一电容器 C<sub>j</sub> 和第二电容器 2C<sub>j</sub> 可具有与 2<sup>0</sup> 和 2<sup>1</sup> 对应的电容。

在本发明的实施例中，施加到第四十一晶体管 M41 和第一缓冲器 270j 之间的电通路上的数据信号 DS<sub>j</sub> 的电压值可根据可施加到 p 个电容器 C<sub>j</sub>、2C<sub>j</sub>、4C<sub>j</sub>、8C<sub>j</sub> 和 16C<sub>j</sub> 的各个接线端的补偿电压增大或降低。更具体地讲，施加到第四十一晶体管 M41 和第一缓冲器 270j 之间（随后到数据线 D<sub>j</sub>）的电通路上的数据信号 DS<sub>j</sub> 的电压值的任何增大或降低可取决于补偿电压的电压值。因为可以用施加的补偿电压来控制数据信号 DS<sub>j</sub> 的电压值，所以可控制数据信号 DS<sub>j</sub> 的电压值，使得可补偿像素 140 的变化，并且像素单元 130 可显示均匀的图像。

例如，因为可以用施加的补偿电压来控制数据信号 DS<sub>j</sub> 的电压值，所以可以补偿包括在像素 140nj 中的晶体管的电子迁移率和/或阈值电压的不同。在本发明的实施例中，因为数据驱动电路 200 可利用基于各个像素 140 的特性，例如电子迁移率、阈值电压等产生的补偿电压来控制数据信号 DS<sub>j</sub> 的电压值，所以数据驱动电路可控制被供给到各个像素 140 的各数据信号 DS 的电压值，并且可补偿晶体管的电子迁移率的不同。

如图 8 所示，第一缓冲器 270j 可将施加到第四十一晶体管 M41 和第一缓冲器 270j 之间的电连接上的数据信号 DS<sub>j</sub> 传输到开关单元 290j。

开关单元 290j 可包括第十一晶体管 M11j。通过第一控制信号 CS1 可控制第十一晶体管 M11j，如图 8 和图 9 所示。在本发明的实施例中，在驱动第 j 通道中的 n 个像素中的每个的各个水平周期 1H 的第二时间段期间，第十一晶体管 M11j 可导通。在这些实施例中，在驱动第 j 通道中的 n 个像素中的每个的各个水平周期 1H 的第一时间段期间，第十一晶体管 M11j 可截止。因此，在水平周期 1H 的第二时间段期间，可将数据信号 DS<sub>j</sub> 供给到数据线 D<sub>j</sub>，而在单个水平周期 1H 的其他时间段期间，例如在第一时间段期间，不会供给数据信号 DS<sub>j</sub>。在本发明的实施例中，可仅在单个水平周期 1H 的第二时间段期间供给数据信号 DS<sub>j</sub>。在本发明的实施例中，在单一水平周期 1H 的第一时间段期间可从不将数据信号 DS<sub>j</sub> 供给到数据线 D<sub>j</sub>。

图 9 示出了驱动图 8 中示出的像素、开关单元和电流吸收单元可采用的

示例性波形。将参照图 8 和图 9 来详细描述控制分别供给到像素 140 的数据信号 DS 的电压的示例性方法。在图 8 中示出的示例性实施例中，提供了根据图 3 中示出的示例性实施例的像素 140nj 和像素电路 142nj。在下面的描述中，将采用与以上在图 3 中示出的第 nm 像素 140nm 的描述中采用的标号相同的标号来描述在图 8 中示出的第 nj 像素 140nj 的示例性实施例中的相同部件。

首先，可将扫描信号 SS<sub>n-1</sub> 供给到第 n-1 扫描线 Sn-1。当将扫描信号 SS<sub>n-1</sub> 供给到第 n-1 扫描线 Sn-1 时，可导通第三晶体管 M<sub>3nj</sub> 和第五晶体管 M<sub>5nj</sub>。然后可将通过从第一电源 ELVDD 减去第四晶体管 M<sub>4nj</sub> 的阈值电压而获得的电压值施加到第二节点 N<sub>2nj</sub>，并可将基准电源 ELVref 的电压施加到第一节点 N<sub>1nj</sub>。然后与第一电源 ELVDD 的压降对应的电压和第四晶体管 M<sub>4nj</sub> 的阈值电压可被充入第二电容器 C<sub>2nj</sub>。

施加到第一节点 N<sub>1nj</sub> 和第二节点 N<sub>2nj</sub> 的电压可由等式 1 和等式 2 表示。

[等式 1]

$$V_{N1} = V_{ref}$$

[等式 2]

$$V_{N2} = ELVDD - |V_{thM4}|$$

在等式 1 和等式 2 中，V<sub>N1</sub>、V<sub>N2</sub> 和 V<sub>thM4</sub> 分别表示施加到第一节点 N<sub>1nj</sub> 的电压、施加到第二节点 N<sub>2nj</sub> 的电压、第四晶体管 M<sub>4nj</sub> 的阈值电压。

从将扫描信号 SS<sub>n-1</sub> 供给到第 n-1 扫描线 Sn-1 停止，例如，从低电压信号改变为高电压信号的时刻，到将扫描信号 SS<sub>n</sub> 供给到第 n 扫描线 Sn，例如，从高电压信号改变为低电压信号的时刻，第一节点 N<sub>1nj</sub> 和第二节点 N<sub>2nj</sub> 可以浮置。因此，在那段时间内充入第二电容器 C<sub>2nj</sub> 的电压值不会改变。

然后将第 n 扫描信号 SS<sub>n</sub> 供给到第 n 扫描线 Sn，从而第一晶体管 M<sub>1nj</sub> 和第二晶体管 M<sub>2nj</sub> 可通道。当将扫描信号 SS<sub>n</sub> 供给到第 n 扫描线 Sn 时，在驱动第 n 扫描线 Sn 的一个水平周期的第一时间段期间，第十二晶体管 M<sub>12j</sub> 和第十三晶体管 M<sub>13j</sub> 可导通。当第十二晶体管 M<sub>12j</sub> 和第十三晶体管 M<sub>13j</sub> 导通时，可吸收经第一电源 ELVDD、第四晶体管 M<sub>4nj</sub>、第二晶体管 M<sub>2nj</sub>、数据线 D<sub>j</sub> 和第十三晶体管 M<sub>13j</sub> 流过电流源 I<sub>maxj</sub> 的电流。

当电流经第一电源 ELVDD、第四晶体管 M<sub>4nj</sub> 和第二晶体管 M<sub>2nj</sub> 流入

电流源  $I_{maxj}$  时，可应用等式 3。

[等式 3]

$$I_{max} = \frac{1}{2} \mu_p C_{ox} \frac{W}{L} (ELVDD - V_{N2} - |V_{thM4}|)^2$$

在等式 3 中， $\mu_p$ 、 $C_{ox}$ 、 $W$  和  $L$  分别表示电子迁移率、氧化层的电容、沟道的宽度和沟道的长度。

当通过等式 3 获得的电流流过第四晶体管  $M4nj$  时施加到第二节点  $N2nj$  的电压可由等式 4 表示。

[等式 4]

$$V_{N2} = ELVDD - \sqrt{\frac{2I_{max}}{\mu_p C_{ox}}} \frac{L}{W} - |V_{thM4}|$$

通过耦合第二电容器  $C2nj$ ，施加到第一节点  $N1nj$  的电压可由等式 5 表示。

[等式 5]

$$V_{N1} = V_{ref} - \sqrt{\frac{2I_{max}}{\mu_p C_{ox}}} \frac{L}{W} = V_{N3}$$

在等式 5 中，电压  $V_{N1}$  可与施加到第一节点  $N1nj$  的电压对应，电压  $V_{N3}$  可与施加到第三节点  $N3j$  的电压对应。在本发明的实施例中，当通过电流源  $I_{maxj}$  吸收电流时，满足等式 5 的电压可被施加到第三节点  $N3j$ 。

从等式 5 可知，施加到第三节点  $N3j$  的电压会受到包括在正在将电流供应到电流源  $I_{maxj}$  的像素 140nj 中的晶体管的电子迁移率的影响。因此，例如，当电子迁移率在每个像素 140 中变化时，电流正被供给到电流源  $I_{maxj}$  时施加到第三节点  $N3j$  的电压值在各个像素 140 中可能是不同的。

在驱动像素 140 中的每个的水平周期 1H 的第一时间段期间，DAC 250 可基于各个像素的第一数据 DATA1 来选择  $f$  个灰阶电压中的第  $h$  灰阶电压，其中， $f$  和  $h$  是自然数。例如，DAC 250j 可选择与第  $nj$  像素 140nj 的第一数据 DATA1 对应的  $f$  个灰阶电压中的第  $h$  灰阶电压。然后，当第四十一晶体管  $M41$  导通时，DAC 250j 和电压控制器 260j 一起可将  $f$  个灰阶电压中选择的第

$h$  灰阶电压作为数据信号 DSj 选择性地施加到第四十一晶体管 M41 和第一缓冲器 270j 之间的电连接。施加到第四十一晶体管 M41 和第一缓冲器 270j 之间的电连接的电压可由等式 6 表示。

[等式 6]

$$V_L = V_{ref} - \frac{h}{f} (V_{ref} - VSS)$$

同时，如上所述，在每个水平周期 1H 的第一时间段期间，解码器 240j 可供给初始信号。初始信号可导通第三十一晶体管 M31j、第三十二晶体管 M32j、第三十三晶体管 M33j、第三十四晶体管 M34j 和第三十五晶体管 M35j。因此，在每个水平周期 1H 的第一时间段期间， $p$  个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj 中的每个的接线端的电压可被设置为第三电源电压 VSS' 的电压。在本发明的实施例中，可将第三电源电压 VSS' 的电压值设置得低于基准电源电压 ELVref 的电压值。例如，可将第三电源电压 VSS' 设置成补偿电压的平均电压，所述补偿电压可由包括在像素单元 130 中的像素 140 产生。

在将  $p$  个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj 中的每个的接线端的电压设置成第三电源电压 VSS' 后，在水平周期的第二时间段期间，根据可从解码器 240j 供给的第二数据 DATA2，可导通或截止第二十一晶体管 M21j、第二十二晶体管 M22j、第二十三晶体管 M23j、第二十四晶体管 M24j 和第二十五晶体管 M25j。解码器 240j 可控制第二十一晶体管 M21j、第二十二晶体管 M22j、第二十三晶体管 M23j、第二十四晶体管 M24j 和第二十五晶体管 M25j 的导通/截止状态。具体地讲，解码器 240j 可控制第二十一晶体管 M21j、第二十二晶体管 M22j、第二十三晶体管 M23j、第二十四晶体管 M24j 和第二十五晶体管 M25j 的导通/截止状态，以获得与等式 6 中  $h/f$  的值相近的值。

例如，如果将由解码器 240j 产生的第二数据信号 DATA2 的位设置成“00011”，则第二十四晶体管 M24j 和第二十五晶体管 M25j 可被导通，以将补偿电压施加到  $p$  个电容器中的第一电容器 Cj 和第二电容器 2Cj 的每个的接线端。在这个示例中，因为补偿电压可被施加到  $p$  个电容器中的第一电容器 Cj 和第二电容器 2Cj 的每个的接线端，所以可推导出等式 7。

[等式 7]

$$\frac{C+2C}{C+2C+4C+8C+16C} = \frac{h}{f}$$

更具体地讲，因为可从第一数据 DATA1 得到第二数据 DATA2，所以满足等式 7 的值与 h/f 的值近似。

同时，如果补偿电压被施加到 p 个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj 中的至少一个，则第四十一晶体管 M41 和第一缓冲器 270j 之间的电连接的电压可由等式 8 表示。

[等式 8]

$$\begin{aligned} V_L &= V_{ref} - \frac{h}{f} (V_{ref} - V_{SS}) + V_{boost} \quad V_{boost} = \frac{h}{f} (V_{N3} - V_{SS}) \\ &= V_{ref} - \frac{h}{f} (V_{ref} - V_{N3}) \\ &= V_{ref} - \frac{h}{f} \sqrt{\frac{2I_{max}}{\mu_p C_{OX}} \frac{L}{W}} \end{aligned}$$

可将满足等式 8 的电压经第一缓冲器 270j 供给到第十一晶体管 M11j。在一个水平周期 1H 的第二时间段期间，因为可导通第十一晶体管 M11j，所以可将供给到第一缓冲器 270j 的电压经第十一晶体管 M11j、数据线 Dj 和第一晶体管 M1nj 供给到第一节点 N1nj。满足等式 8 的电压可被供给到第一节点 N1nj。通过耦合第二电容器 C2nj 施加到第二节点 N2nj 的电压可由等式 9 表示。

[等式 9]

$$V_{N2} = ELVDD - \frac{h}{f} \sqrt{\frac{2I_{max}}{\mu_p C_{OX}} \frac{L}{W}} - |V_{thM4}|$$

这里，流过第四晶体管 M4nj 的电流可由等式 10 表示。

[等式 10]

$$\begin{aligned} I_{N4} &= \frac{1}{2} \mu_p C_{OX} \frac{W}{L} (ELVDD - V_{N2} - |V_{thM4}|)^2 \\ &= \frac{1}{2} \mu_p C_{OX} \frac{W}{L} \left( ELVDD - \left( ELVDD - \frac{h}{f} \sqrt{\frac{2I_{max}}{\mu_p C_{OX}} \frac{L}{W}} - |V_{thM4}| \right) - |V_{thM4}| \right)^2 \\ &= \left( \frac{h}{f} \right)^2 I_{max} \end{aligned}$$

参照等式 10，在本发明的实施例中，流过第四晶体管 M4nj 的电流可取决于供给到各像素 140 的各个数据信号 DS，更具体地讲，取决于由电压控制器 260j 产生的灰阶电压。因此，在本发明的实施例中，通过供给基于补偿电压的电流，无论各个像素的晶体管（例如，M4nj）的阈值电压、电子迁移率等多大，都可以选择期望的电流并供给选择的期望电流作为各个数据信号 DS，其中，该补偿电压通过从各个像素 140nj 吸收电流而产生。因此，不管在像素单元 130 的像素 140 内/中的电子迁移率和阈值电压如何变化，本发明的实施例都能够使将显示的图像均匀。

在本发明的实施例中，如上所述，可采用不同的开关单元。图 10 示出了采用开关单元 290j' 的另一实施例的图 8 中示出的连接方案。图 10 中示出的示例性连接方案于图 8 中示出的示例性连接方案基本相同，除了开关单元 290j' 的另一示例性实施例。在下面的描述中，将采用与以上采用的标号相同的标号来描述在图 10 中示出的示例性实施例中的相同的部件。

如图 10 所示，另一示例性开关单元 290j' 可包括第十一晶体管 M11j 和第十四晶体管 M14j，第十一晶体管 M11j 和第十四晶体管 M14j 以传输门的形式相互连接。第十四晶体管 M14j 可为 PMOS 型晶体管，并可接收第二控制信号 CS2。第十一晶体管 M11j 可为 NMOS 型晶体管，并可接收第一控制信号 CS1。在这种实施例中，当第一控制信号 CS1 的极性与第二控制信号 CS2 的极性相反时，第十一晶体管 M11j 和第十四晶体管 M14j 可同时导通同时截止。

在第十一晶体管 M11j 和第十四晶体管 M14j 可以以传输门的形式相互连接的本发明的实施例中，电压-电流特性曲线可以是直线形式，并可将开关误差最小化。

图 11 示出了用于连接伽马电压单元 300、DAC 250j、解码器 240j、电压控制器 260j、开关单元 290j'、电流吸收单元 280j 和像素 140nj' 的连接方案的第二实施例。为了简单，图 11 仅示出了一个通道，即，第 j 通道，并假定数据线 Dj 连接到根据图 5 中示出的像素 140nm' 的示例性实施例的第 nj 像素 140nj'。

将参照图 9 和图 11 来详细描述驱动发光显示器的像素 140 的方法。首先，当将扫描信号 SSn-1 供给到第 n-1 扫描线 Sn-1 时，满足等式 1 和等式 2 的电压可被分别施加到第一节点 N1nj' 和第二节点 N2nj'。

可将第 n 扫描信号施加到第 n 扫描线 Sn。在用于驱动第 nj 像素 140nj' 的水平周期 1H 的第一时间段期间，当第十二晶体管 M12j 和第十三晶体管 M13j 可导通时，流过第四晶体管 M4nj 的电流可满足等式 3，施加到第二节点 N2nj' 的电压可满足等式 4。在下面的描述中，将采用与在以上图 8 中示出的示例性实施例的描述中采用的标号相同的标号来描述在图 11 中示出的连接方案的示例性实施例中的相同部件。

通过耦合第二电容器 C2nj 施加到第一节点 N1nj' 的电压可由等式 11 表示。

[等式 11]

$$V_{N1} = V_{ref} \cdot \left( \frac{C1+C2}{C2} \right) \sqrt{\frac{2Imax}{\mu_p C_{ox}} \cdot \frac{L}{W}} = V_{N3}$$

同时，在驱动第 nj 像素 140nj' 的水平周期的第一时间段期间，DAC 250j 可根据第一数据 DATA1 来选择 f 个灰阶电压中的第 h 灰阶电压，其中，h 和 f 是自然数。DAC 250j 还可供应满足等式 6 的灰阶电压。当第四十一晶体管 M41 导通时，可将 f 个灰阶电压中选择的第 h 灰阶电压供给到第一缓冲器 270j。可选择 f 个灰阶电压中选择的第 h 灰阶电压作为各数据信号 DSj 以经数据线 Dj 将该第 h 灰阶电压供给至像素 140nj'。

在驱动像素 140nj' 的水平周期 1H 的第一时间段期间，解码器 240j 可将初始信号供给至第三十一晶体管 M31j、第三十二晶体管 M32j、第三十三晶体管 M33j、第三十四晶体管 M34j 和第三十五晶体管 M35j，从而可导通 p 个晶体管 M31j、M32j、M33j、M34j 和 M35j 中的每个。因此，在一个水平周期 1H 的第一时间段期间，p 个电容器 Cj、2Cj、4Cj、8Cj 和 16Cj 中的每个的接线端的电压可为第三电源电压 VSS'。

然后，在驱动像素 140nj' 的水平周期 1H 的第二时间段期间，根据可从解码器 240j 供给的第二数据 DATA2，可导通或截止第二十一晶体管 M21j、第二十二晶体管 M22j、第二十三晶体管 M23j、第二十四晶体管 M24j 和第二十五晶体管 M25j。解码器 240j 可控制第二十一晶体管 M21j、第二十二晶体管 M22j、第二十三晶体管 M23j、第二十四晶体管 M24j 和第二十五晶体管 M25j 的导通/截止。具体地讲，如上所述，解码器 240j 可控制第二十一晶体管 M21j、第二十二晶体管 M22j、第二十三晶体管 M23j、第二十四晶体管

M24j 和第二十五晶体管 M25j 的导通/截止，以获得与等式 6 中的 h/f 的值相似的值。

这时，第四十一晶体管 M41 和第一缓冲器 270j 之间的电连接的电压  $V_L$  可由等式 12 表示。

[等式 12]

$$\begin{aligned} V_L &= V_{ref} - \frac{h}{f} (V_{ref} - V_{SS}) + V_{boost} \quad V_{boost} = \frac{h}{f} (V_{N3} - V_{SS}) \\ &= V_{ref} - \frac{h}{f} (V_{ref} - V_{N3}) \\ &= V_{ref} - \frac{h}{f} \left( \frac{C1+C2}{C2} \right) \sqrt{\frac{2I_{max}}{\mu_p C_{OX}}} \frac{L}{W} \end{aligned}$$

可将满足等式 12 的电压经第一缓冲器 270j 供给到第十一晶体管 M11j。在驱动像素 140nj' 的水平周期 1H 的第二时间段期间，因为可导通第十一晶体管 M11j，所以可将供给到第一缓冲器 270j 的电压经第十一晶体管 M11j、数据线 Dj 和第一晶体管 M1nj 供给到第一节点 N1nj'。在本发明的实施例中，可将满足等式 12 的电压供给到第一节点 N1nj'。

通过耦合第二电容器 C2nj 施加到第二节点 N2nj' 的电压可由等式 9 表示。因此，流过第四晶体管 M4nj 的电流可由等式 10 表示。在本发明的实施例中，无论第四晶体管 M4nj 的电子迁移率和重置电压多大，与由 DAC 250j 选择的灰阶电压对应的电流可流入第四晶体管 M4nj。如上所述，本发明的实施例使得显示的图像具有均匀的亮度。

在本发明的一些实施例中，例如，在采用图 11 中示出的像素 140nj' 的实施例中，尽管第一节点 N1nj' 的电压可快速改变，即， $(C1+C2)/C2$ ，但是第二节点 N2nj' 的电压也可以逐渐改变。当采用图 11 中示出的像素 140nj' 时，可对伽马电压单元 300 设置的电压范围比采用图 8 中示出的像素 140nj 时可对伽马电压单元 300 设置的电压范围大。如上所述，当将伽马电压单元 300 的电压范围设置得更大时，能够降低第十一晶体管 M11j 和第一晶体管 M1nj 的开关误差的影响。

因此，与图 3 中示出的像素结构 140nj 相比，图 5 中示出的像素结构 140nj' 可扩大伽马电压单元 300 的可利用的电压范围。如此，通过扩大伽马电压单

元 300 的可利用的电压范围，能够降低通过第十一晶体管 M11j、第一晶体管 M1nj 等的开关误差而产生的影响。

如上所述，在采用本发明的一个或多个方面的数据驱动电路、数据驱动方法和发光显示器中，由于利用从各像素吸收电流时产生的补偿电压重置了数据信号的电压，所以无论晶体管的电子迁移率、阈值电压等多大，都可以显示均匀的图像。

在此已经公开了本发明的示例性实施例，尽管采用了特定的术语，但是仅是使用它们并且以一般的描述性意思对它们进行解释，而不是出于限制的目的。因此，本领域的普通技术人员应该理解，在不脱离如权利要求提出的本发明的精神和范围的情况下，可以在形式和细节上做出各种改变。

图 1

图 2

图 3

图 4

图 5

图 6

图 7

图 8

图 9

图 10

图 11

|                |                                                                                                                                                           |         |            |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机发光显示器的数据驱动电路和驱动方法                                                                                                                                       |         |            |

| 公开(公告)号        | <a href="#">CN1909043A</a>                                                                                                                                | 公开(公告)日 | 2007-02-07 |

| 申请号            | CN200610108997.8                                                                                                                                          | 申请日     | 2006-07-31 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                                               |         |            |

| 申请(专利权)人(译)    | 三星SDI株式会社<br>汉阳大学校产业协力团                                                                                                                                   |         |            |

| 当前申请(专利权)人(译)  | 三星SDI株式会社<br>汉阳大学校产业协力团                                                                                                                                   |         |            |

| [标]发明人         | 郑宝容<br>柳道亨<br>金烘权<br>权五敬                                                                                                                                  |         |            |

| 发明人            | 郑宝容<br>柳道亨<br>金烘权<br>权五敬                                                                                                                                  |         |            |

| IPC分类号         | G09G3/30 G09G3/32 G09G3/20 H05B33/08 H05B33/14                                                                                                            |         |            |

| CPC分类号         | G09G3/3233 G09G3/2011 G09G3/3283 G09G3/3291 G09G2300/0819 G09G2300/0852 G09G2300/0861 G09G2310/0251 G09G2310/027 G09G2310/0289 G09G2320/0276 G09G2320/043 |         |            |

| 代理人(译)         | 韩明星                                                                                                                                                       |         |            |

| 优先权            | 1020050070438 2005-08-01 KR                                                                                                                               |         |            |

| 其他公开文献         | CN100492474C                                                                                                                                              |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                                                            |         |            |

#### 摘要(译)

本发明提供了一种用于驱动发光显示器的像素从而以均匀的亮度显示图像的数据驱动电路，所述数据驱动电路包括：伽马电压单元，产生多个灰阶电压；数模转换器，利用第一数据选择多个灰阶电压之一作为数据信号；解码器，利用第一数据产生第二数据；电流吸收器；电压控制器，利用第二数据和基于预定电流产生的补偿电压来控制数据信号的电压值；开关单元，在所述完整周期的第一部分时间段之后流逝的任何部分时间段期间，将数据信号供给至像素。在驱动像素的完整周期的第一部分时间段期间，基于选择的灰阶电压，电流吸收器从像素接收预定电流。