## (12) 发明专利申请

(10) 申请公布号 CN 102246220 A

(43) 申请公布日 2011.11.16

(21) 申请号 200980148912.0

地址 加拿大安大略

(22) 申请日 2009.12.08

(72) 发明人 G·R·查基 A·内森

(30) 优先权数据

2,647,112 2008.12.09 CA

(74) 专利代理机构 中国国际贸易促进委员会专利商标事务所 11038

代理人 欧阳帆

(85) PCT申请进入国家阶段日

2011.06.08

(51) Int. Cl.

G09G 3/20 (2006.01)

(86) PCT申请的申请数据

PCT/CA2009/001769 2009.12.08

G09G 3/32 (2006.01)

(87) PCT申请的公布数据

W02010/066030 EN 2010.06.17

(71) 申请人 伊格尼斯创新公司

权利要求书 3 页 说明书 18 页 附图 28 页

## (54) 发明名称

用于发射型显示器的低功率电路和驱动方法

## (57) 摘要

提供了一种显示器系统、用于驱动该显示阵列的驱动器、操作该显示器系统的方法和该显示器系统中的像素电路。该驱动器包括：双向电流源，具有与时变电压耦接的转换器，该转换器用于将该时变电压转换为电流。该像素电路包括：晶体管，用于向发光器件提供像素电流；和与该晶体管电耦接的存储电容器，该电容器在用于基于时变电压提供电流的预定定时中与该时变电压耦接。该方法包括：在编程操作的第一周期中，将提供给像素电路中的存储电容器的时变电压从参考电压改变为编程电压，该存储电容器与用于驱动发光器件的驱动晶体管电耦接；以及在该编程操作的第二周期中，将该时变电压维持在该编程电压。该方法包括：在编程操作中，从数据线向像素电路提供编程数据，该像素电路包括与该数据线耦接的晶体管以及存储电容器；以及在驱动操作中，经由电源线向该像素电路中的存储电容器提供用于接通发光器件的时变电压。该像素电路包括：有机发光二极管(OLED)器件，具有电极和OLED层；和交指型电容器，具有多个层。

1. 一种用于驱动显示器系统的驱动器,包括:

双向电流源,用于向显示器系统提供电流,所述双向电流源包括:

与时变电压耦接的转换器,用于将所述时变电压转换为电流,以及

控制器,用于控制所述时变电压的产生。

2. 根据权利要求 1 所述的驱动器,其中所述转换器包括:

电容器。

3. 根据权利要求 2 所述的驱动器,其中所述显示器系统包括以列和行方式排列的多个像素电路,并且其中所述电容器被分配给每个列以便操作所述列中的像素电路。

4. 根据权利要求 3 所述的驱动器,其中所述时变电压在多于一个列中共用。

5. 根据权利要求 2 所述的驱动器,其中所述电容器是所述显示器系统中的像素电路的存储电容器,并且与所述时变电压结合来充当电流源。

6. 根据权利要求 5 所述的驱动器,其中在所述像素电路的编程周期或驱动周期期间所述时变电压被提供给所述存储电容器。

7. 根据权利要求 1 所述的驱动器,其中所述电流源与所述显示器系统中的电流编程的像素电路耦接。

8. 根据权利要求 1 所述的驱动器,其中来自所述电流源的电流作为偏置电流而被提供给所述显示器系统中的像素电路。

9. 根据权利要求 1 所述的驱动器,其中所述转换器包括:

与用于提供所述电流的输出节点耦接的多个电容器,每个电容器具有不同的尺寸并且基于控制信号来接收时变电压。

10. 根据权利要求 9 所述的驱动器,包括:

复制器块,用于复制由所述转换器产生的电流,并且向所述显示器系统提供复制的电流。

11. 根据权利要求 1 所述的驱动器,其中所述转换器与多个时变电压耦接,并且其中所述转换器包括:

与用于提供恒定电流的输出节点耦接的多个电容器,每个电容器基于控制信号来接收相应的时变电压。

12. 根据权利要求 11 所述的驱动器,包括:

复制器块,用于复制由所述转换器产生的电流,并且向所述显示器系统提供复制的电流。

13. 根据权利要求 1 所述的驱动器,其中所述转换器包括具有多个层的交指型电容器。

14. 根据权利要求 13 所述的驱动器,其中像素包括具有电极和 OLED 层的有机发光二极管 (OLED) 器件,并且其中所述交指型电容器的多个层中的一个层与所述电极互连。

15. 根据权利要求 14 所述的驱动器,其中所述电极是透明电极,并且其中所述电容器的多个层位于所述透明电极之下,而不遮盖来自于所述透明电极上的 OLED 层的光。

16. 根据权利要求 14 所述的驱动器,其中所述显示器系统包括顶部发射显示器,所述顶部发射显示器具有 OLED 层和在所述电容器的多个层上布置的电极。

17. 一种像素电路,包括:

晶体管,用于向发光器件提供像素电流;以及

与所述晶体管电耦接的存储电容器,所述电容器在用于基于时变电压提供电流的预定定时中与所述时变电压耦接。

18. 根据权利要求 17 所述的像素电路,其中所述存储电容器与用于提供编程数据的数据线耦接,并且在编程周期的一部分中经由所述数据线接收所述时变电压。

19. 根据权利要求 18 所述的像素电路,其中所述晶体管是具有栅极、第一端子和第二端子的驱动晶体管,所述电容器耦接在所述数据线和所述驱动晶体管的栅极之间。

20. 根据权利要求 19 所述的像素,包括与所述驱动晶体管的栅极以及所述驱动晶体管的第一端子和第二端子之一耦接的开关晶体管,在编程周期期间所述开关晶体管导通直到所述时变电压达到所述编程电压。

21. 根据权利要求 17 所述的像素电路,其中所述存储电容器耦接在电源线和所述发光器件之间,并且在驱动周期期间经由所述电源线接收所述时变电压。

22. 根据权利要求 21 所述的像素电路,其中所述晶体管是耦接在用于提供编程数据的数据线和存储电容器之间的开关晶体管。

23. 根据权利要求 17 所述的像素,其中所述电容器是具有多个层的交指型电容器。

24. 根据权利要求 23 所述的像素电路,其中所述发光器件是具有电极和 OLED 层的有机发光二极管 (OLED) 器件,并且其中所述交指型电容器的多个层中的一个层与所述电极互连。

25. 根据权利要求 24 所述的像素电路,其中所述电极是透明电极,并且其中所述电容器的多个层位于所述透明电极之下,而不遮盖来自于所述透明电极上的 OLED 层的光。

26. 根据权利要求 24 所述的像素电路,其中所述像素电路是顶部发射像素电路,所述顶部发射像素电路具有 OLED 层和在所述电容器的多个层上布置的电极。

27. 一种操作像素电路的方法,包括:

在编程操作中的第一周期中,将向像素电路中的存储电容器提供的时变电压从参考电压改变为编程电压,所述存储电容器与用于驱动发光器件的驱动晶体管电耦接;以及

在所述编程操作中的第二周期中,将所述时变电压维持在所述编程电压。

28. 根据权利要求 27 所述的方法,其中所述像素电路包括与所述存储电容器和所述驱动晶体管的栅极端子耦接的开关晶体管,并且包括:

在第一周期中使所述开关晶体管导通;以及

在第二周期中使所述开关晶体管截止。

29. 一种操作像素电路的方法,包括:

在编程操作中,将编程数据从数据线提供到像素电路,所述像素电路包括与所述数据线耦接的晶体管和存储电容器;以及

在驱动操作中,经由电源线向所述像素电路中的存储电容器提供用于使发光器件导通的时变电压。

30. 根据权利要求 29 所述的方法,其中所述像素电路被布置在每个列和行中以便在所述编程操作中对像素顺序地编程。

31. 一种像素电路,包括:

有机发光二极管 (OLED) 器件,具有电极和 OLED 层;和

用于操作 OLED 的具有多个层的交指型电容器,所述 OLED 器件被布置在所述多个层上,

所述交指型电容器的多个层中的一个层与所述 OLED 的电极互连。

32. 根据权利要求 31 所述的像素电路, 其中所述电极是透明电极, 并且其中所述电容器的多个层位于所述透明电极之下, 而不遮盖来自于所述透明电极上的 OLED 层的光。

33. 根据权利要求 31 所述的像素电路, 其中所述像素电路是顶部发射像素电路, 所述顶部发射像素电路具有 OLED 层和在所述电容器的多个层上布置的电极。

34. 根据权利要求 31 所述的像素电路, 其中所述电容器与斜坡电压结合来充当电流源。

## 用于发射型显示器的低功率电路和驱动方法

### 技术领域

[0001] 本发明涉及发光显示器,更特别地涉及用于驱动发光显示器的方法和系统。

### 背景技术

[0002] 电致发光显示器已被发展用于诸如蜂窝电话、个人数字助理 (PDA) 之类的广泛的各种设备。这样的显示器包括液晶显示器 (LCD)、场致发射显示器 (FED)、等离子体显示面板 (PDP)、发光显示器 (LED) 等等。特别地,具有非晶硅 (a-Si)、多晶硅、有机物或其它驱动背板的有源矩阵有机发光二极管 (AMOLED) 显示器由于诸如可行的柔性显示器、其低成本制造、高分辨率和宽的视角之类的优点而已经变得更加引人注意。

[0003] 用来驱动发射型显示器的一种方法是利用电流直接对像素进行编程 (例如,电流驱动的 OLED 器件)。但是,伴随着大的寄生电容的 OLED 所需的小的电流增大了 AMOLED 显示器的编程的建立时间。此外,难以设计用于提供精确且恒定的驱动电流的外部驱动器。存在对确保高的显示质量的具有高的开口率 (aperture ratio) 或填充因子 (fill factor) (被定义为发光显示器面积与总的像素面积之比) 的高分辨率显示器的需求。还存在对降低具有显示器的设备的大小和功耗的需求。

[0004] 存在提供一种能够改善显示器的寿命、图像均匀性、稳定性和 / 或产量并且能够提供高分辨率的、稳定的低功率显示器的显示器系统及其操作方法的需要。

### 发明内容

[0005] 本发明的目的是提供一种消除或减轻现有系统的至少一个缺点的方法和系统。

[0006] 根据本发明的实施例的一方面,提供一种用于驱动显示器系统的驱动器,其包括:用于向显示器系统提供电流的双向电流源,该双向电流源包括与时变电压耦接的转换器,该转换器用于将该时变电压转换为该电流;以及控制器,用于控制该时变电压的产生。

[0007] 根据本发明的实施例的另一方面,提供一种像素电路,其包括:晶体管,用于向发光器件提供像素电流;以及与该晶体管电耦接的存储电容器,该电容器在用于基于时变电压提供电流的预定定时中与该时变电压耦接。

[0008] 根据本发明的实施例的另一方面,提供一种操作像素电路的方法,其包括:在编程操作中的第一周期中,将提供给像素电路中的存储电容器的时变电压从参考电压改变为编程电压,该存储电容器与用于驱动发光器件的驱动晶体管电耦接;以及在该编程操作中的第二周期中,将该时变电压维持在该编程电压。

[0009] 根据本发明的实施例的另一方面,提供一种操作像素电路的方法,其包括:在编程操作中,从数据线向像素电路提供编程数据,该像素电路包括与该数据线耦接的晶体管以及存储电容器;以及在驱动操作中,经由电源线向该像素电路中的存储电容器提供用于使发光器件导通的时变电压。

[0010] 根据本发明的实施例的另一方面,提供一种像素电路,其包括:有机发光二极管 (OLED) 器件,具有电极和 OLED 层;以及用于操作该 OLED 的具有多个层的交指型

(inter-digited) 电容器, 该 OLED 器件被布置在该多个层上, 该交指型电容器的多个层中的一个层与该 OLED 的电极互连。

## 附图说明

- [0011] 通过下面参考附图的描述, 本发明的这些及其它特征将变得更清楚, 在附图中:

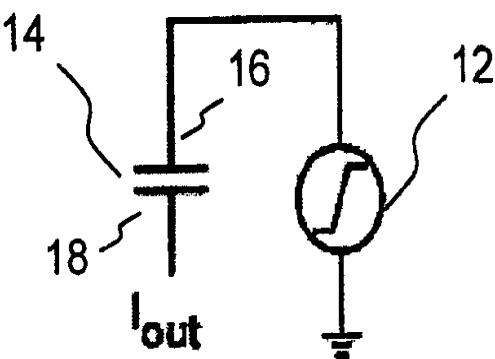

- [0012] 图 1 例示了根据本公开的实施例的双向电流源;

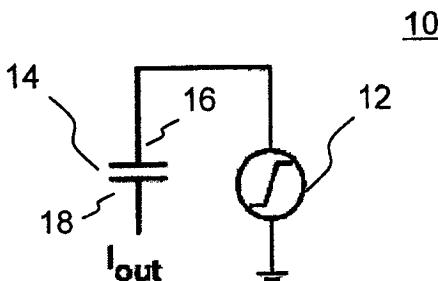

- [0013] 图 2 例示了具有图 1 的双向电流源的显示器系统的示例;

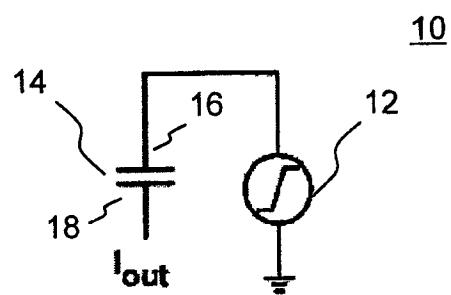

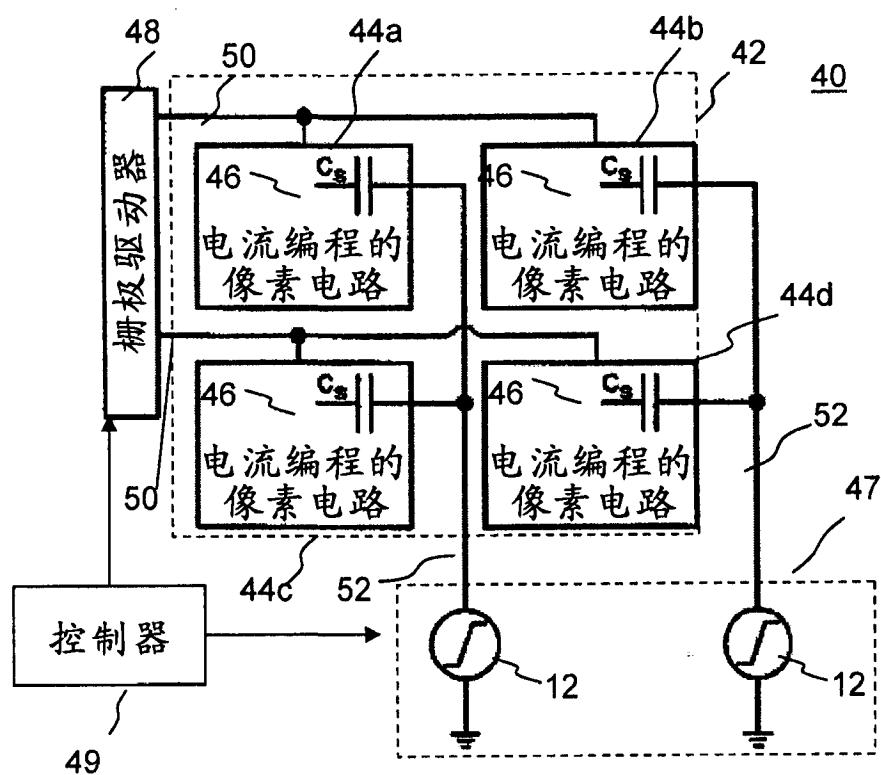

- [0014] 图 3 例示了具有图 1 的双向电流源的显示器系统的又一个示例;

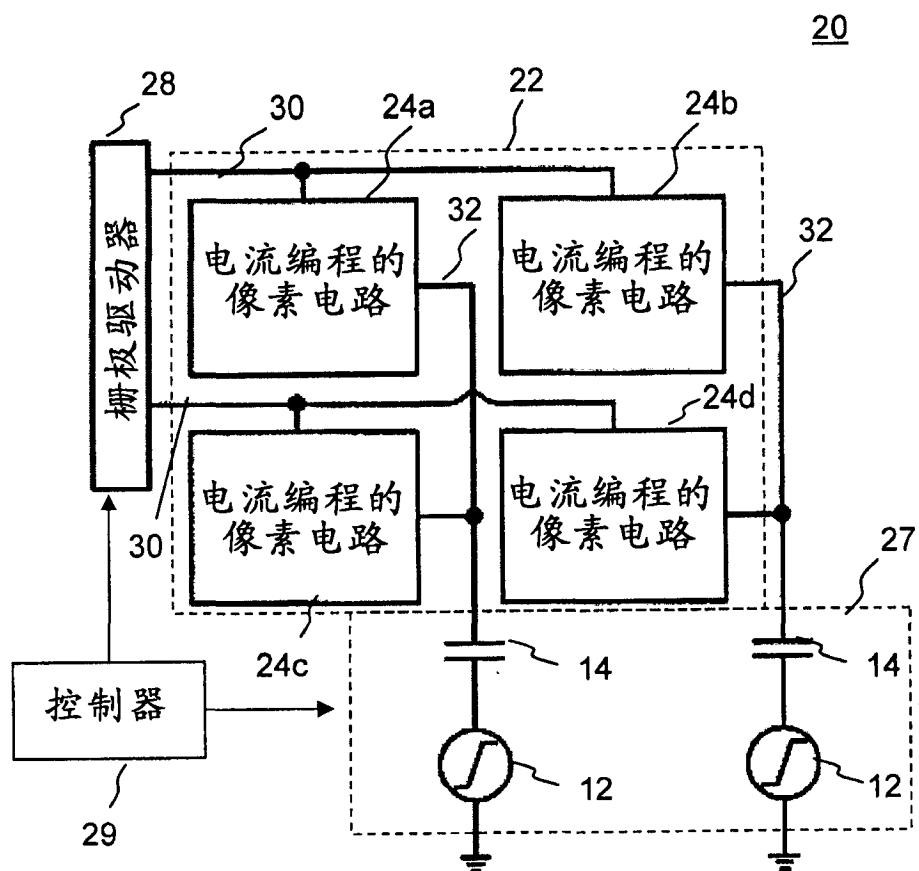

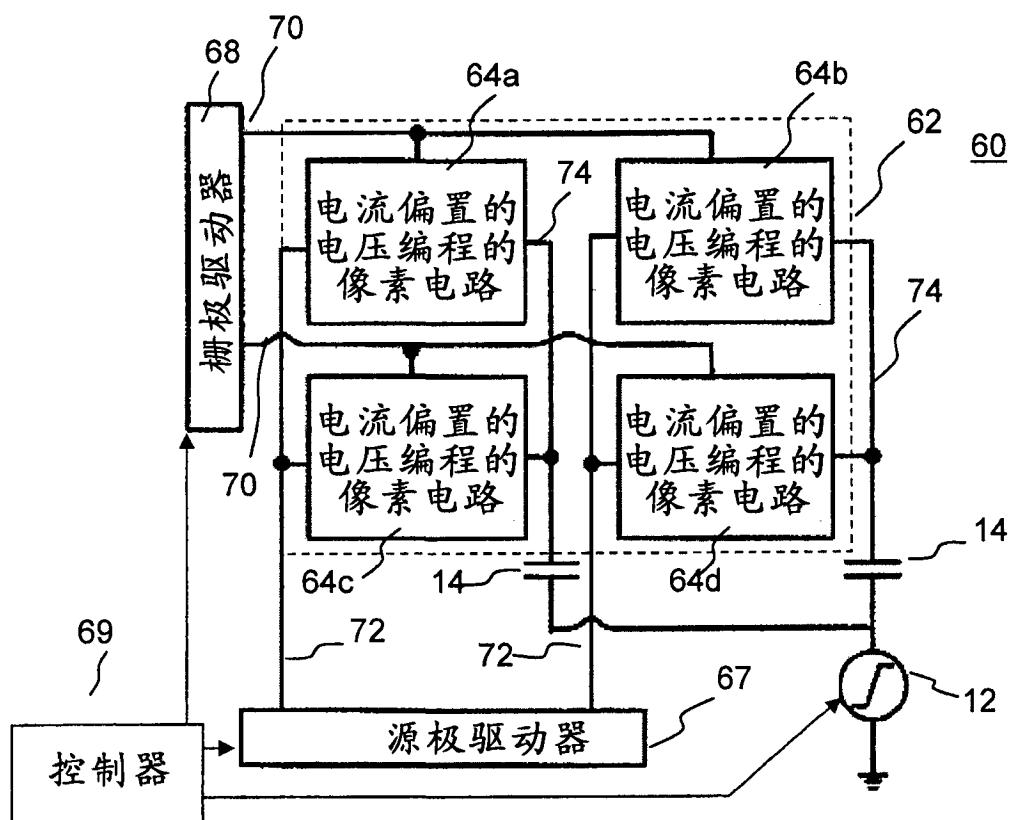

- [0015] 图 4 例示了具有图 1 的双向电流源的显示器系统的又一个示例;

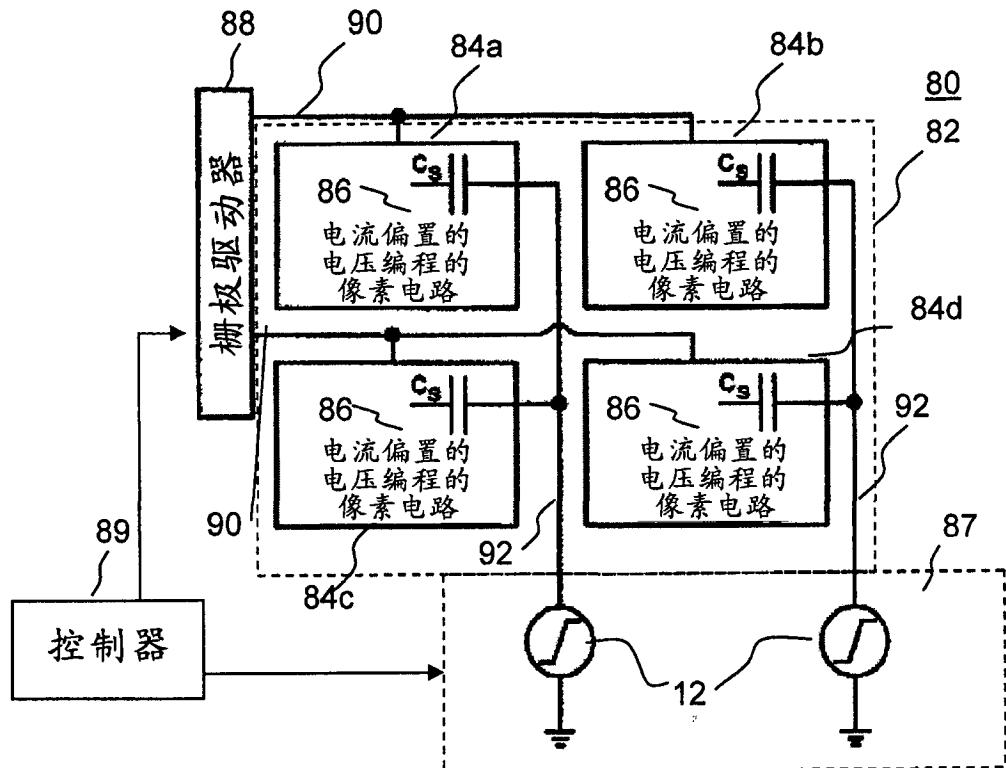

- [0016] 图 5 例示了具有图 1 的双向电流源的显示器系统的又一个示例;

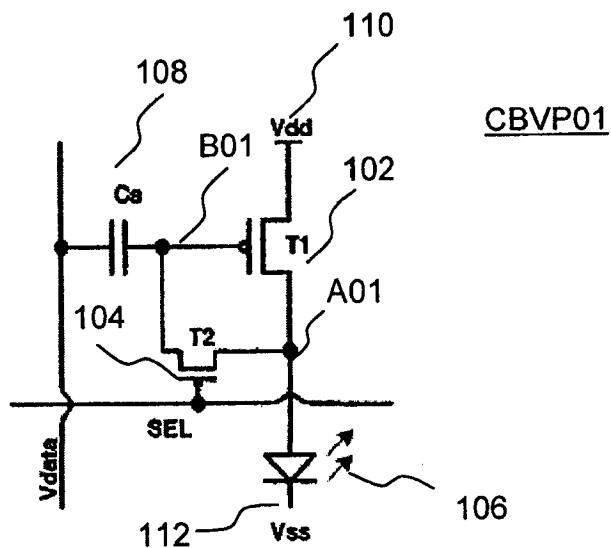

- [0017] 图 6A 例示了适用于图 5 的显示器系统的电流偏置的电压编程的像素电路的示例;

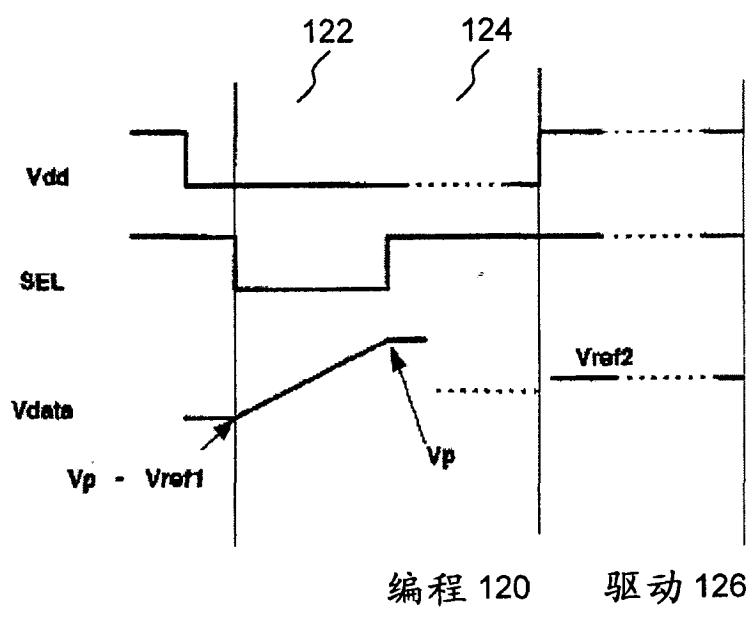

- [0018] 图 6B 例示了图 6A 的像素电路的时序图的示例;

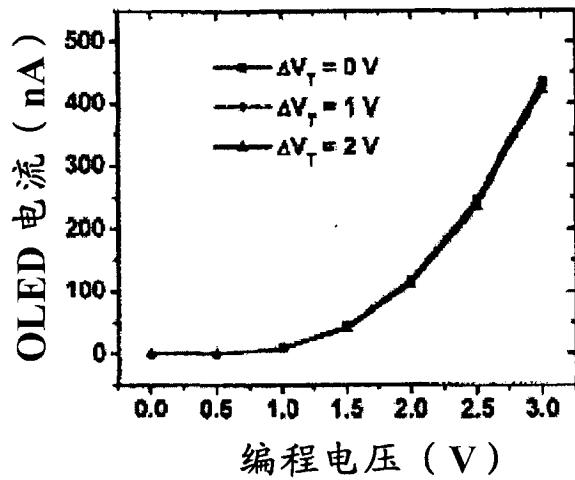

- [0019] 图 7A 例示了图 6A 的像素电路的模拟结果;

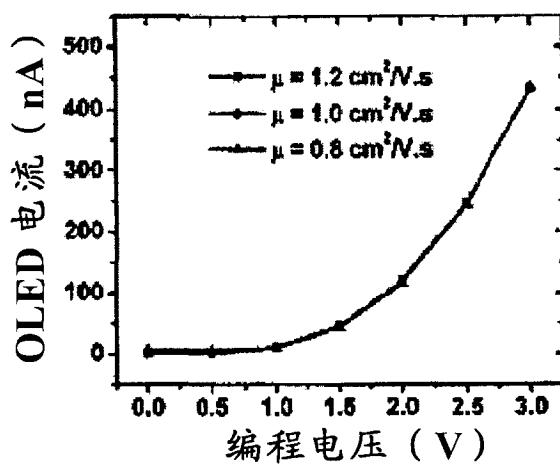

- [0020] 图 7B 例示了图 6A 的像素电路的另外的模拟结果;

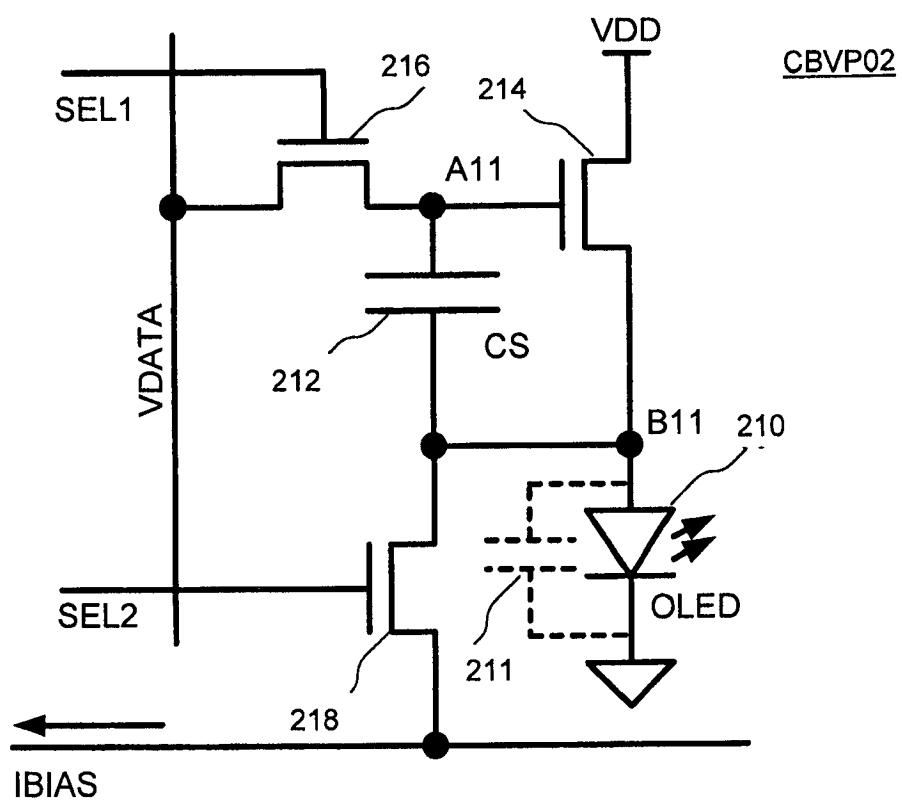

- [0021] 图 8A 例示了电流偏置的电压编程的像素电路的又一个示例;

- [0022] 图 8B 例示了图 8A 的像素电路的时序图的示例;

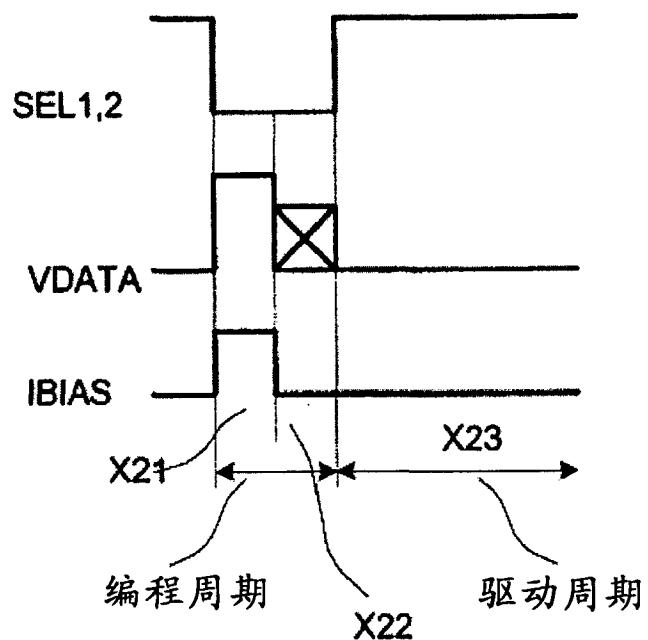

- [0023] 图 8C 例示了图 8A 的像素电路的时序图的另一个示例;

- [0024] 图 9A 例示了电流偏置的电压编程的像素电路的又一个示例;

- [0025] 图 9B 例示了图 9A 的像素电路的时序图的示例;

- [0026] 图 9C 例示了图 9A 的像素电路的时序图的另一个示例;

- [0027] 图 10A 例示了电流偏置的电压编程的像素电路的又一个示例;

- [0028] 图 10B 例示了图 10A 的像素电路的时序图的示例;

- [0029] 图 11A 例示了电流偏置的电压编程的像素电路的又一个示例;

- [0030] 图 11B 例示了图 11A 的像素电路的时序图的示例;

- [0031] 图 12A 例示了具有电流偏置的电压编程的像素电路的显示器的示例;

- [0032] 图 12B 例示了图 12A 的显示器的时序图的示例;

- [0033] 图 13A 例示了具有电流偏置的电压编程的像素电路的显示器的示例;

- [0034] 图 13B 例示了图 13A 的显示器的时序图的示例;

- [0035] 图 14A 例示了电流偏置的电压编程的像素电路的又一个示例;

- [0036] 图 14B 例示了图 14A 的像素电路的时序图的示例;

- [0037] 图 15A 例示了电流偏置的电压编程的像素电路的又一个示例;

- [0038] 图 15B 例示了图 15A 的像素电路的时序图的示例;

- [0039] 图 16 例示了具有电流偏置的电压编程的像素电路的显示器系统的又一个示例;

- [0040] 图 17A 例示了电压偏置的电流编程的像素电路的示例;

- [0041] 图 17B 例示了图 17A 的像素电路的时序图的示例;

- [0042] 图 18A 例示了电压偏置的电流编程的像素电路的又一个示例;

- [0043] 图 18B 例示了图 18A 的像素电路的时序图的示例;

- [0044] 图 19 例示了具有电压偏置的电流编程的像素电路的显示器系统的示例;

- [0045] 图 20A 例示了应用双向电流源的像素电路的示例；

- [0046] 图 20B 例示了应用双向电流源的像素电路的另一个示例；

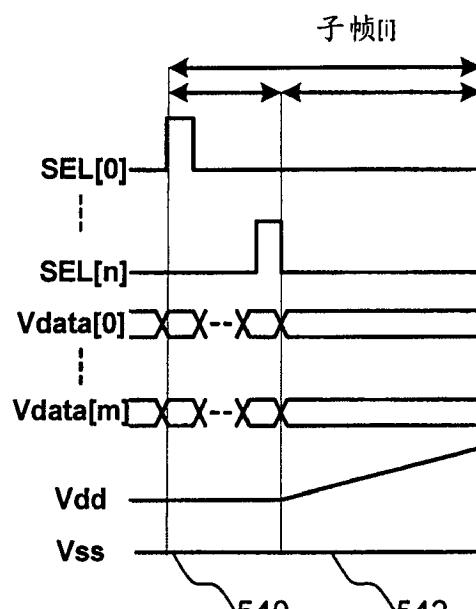

- [0047] 图 21A 例示了图 20A-20B 的像素电路的时序图的示例；

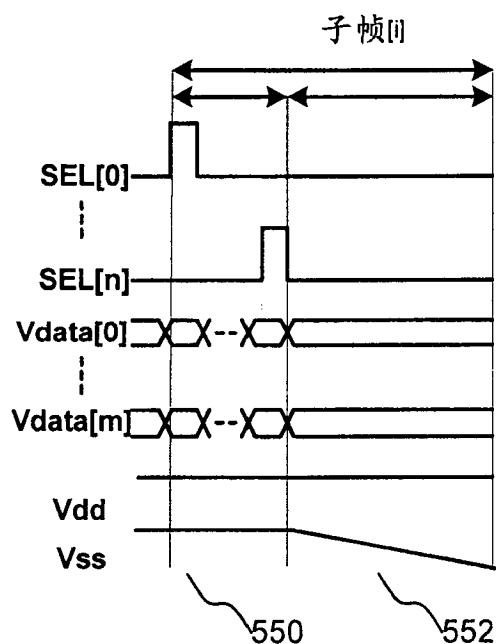

- [0048] 图 21B 例示了图 20A-20B 的像素电路的时序图的另一个示例；

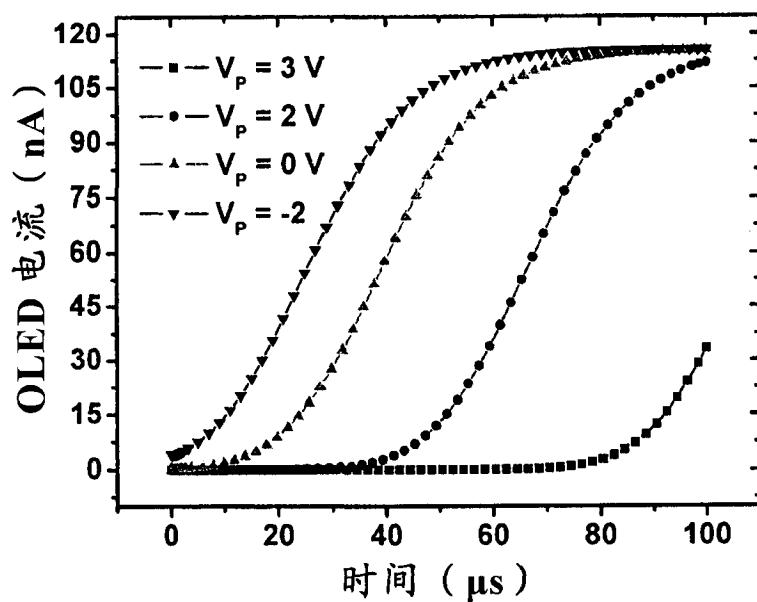

- [0049] 图 22 例示了示出图 20A-20B 的像素电路在一个子帧中对于不同的编程电压的模拟结果 (OLED 电流) 的图；

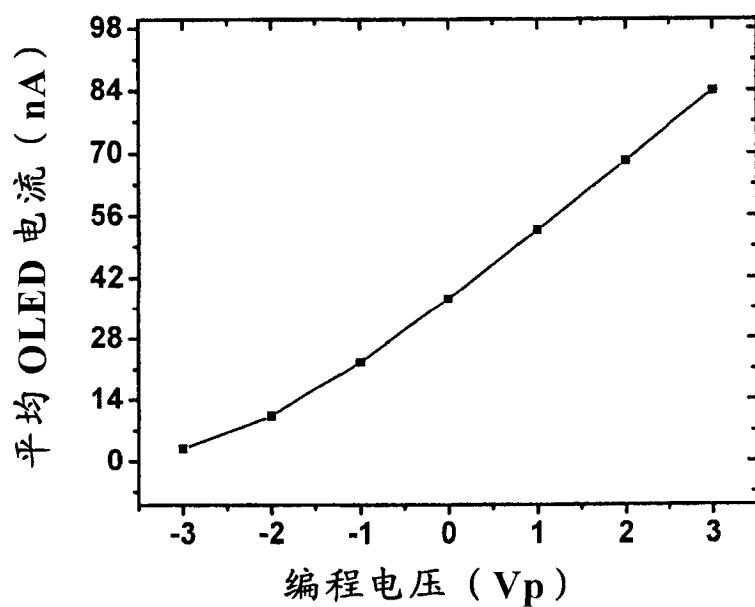

- [0050] 图 23 例示了示出图 20A-20B 的像素电路的模拟结果 (平均电流) 的图；

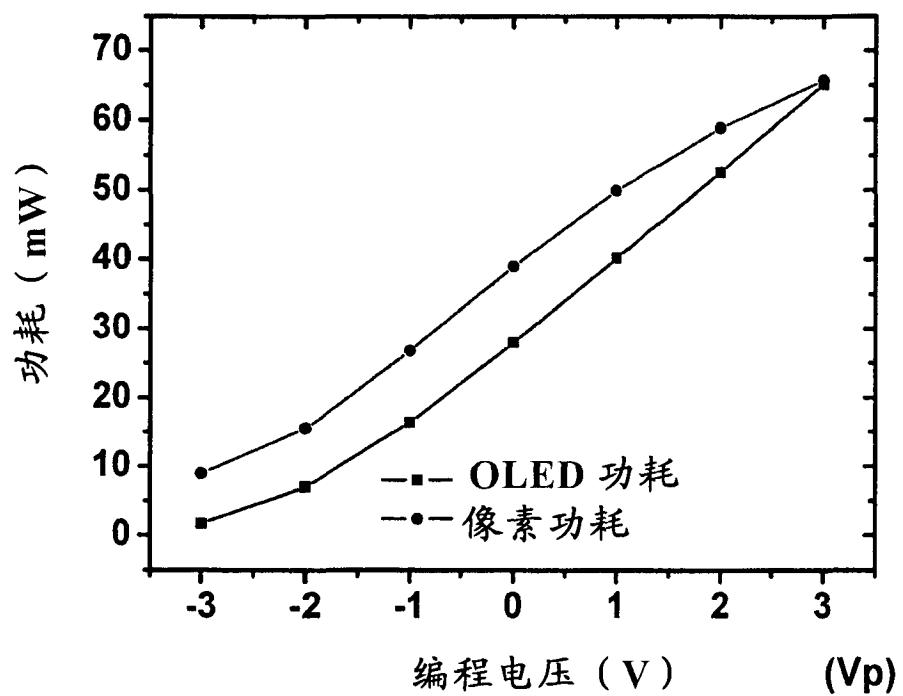

- [0051] 图 24 例示了示出 2.2 英寸 QVGA 面板的功耗和用于 OLED 的功耗的图；

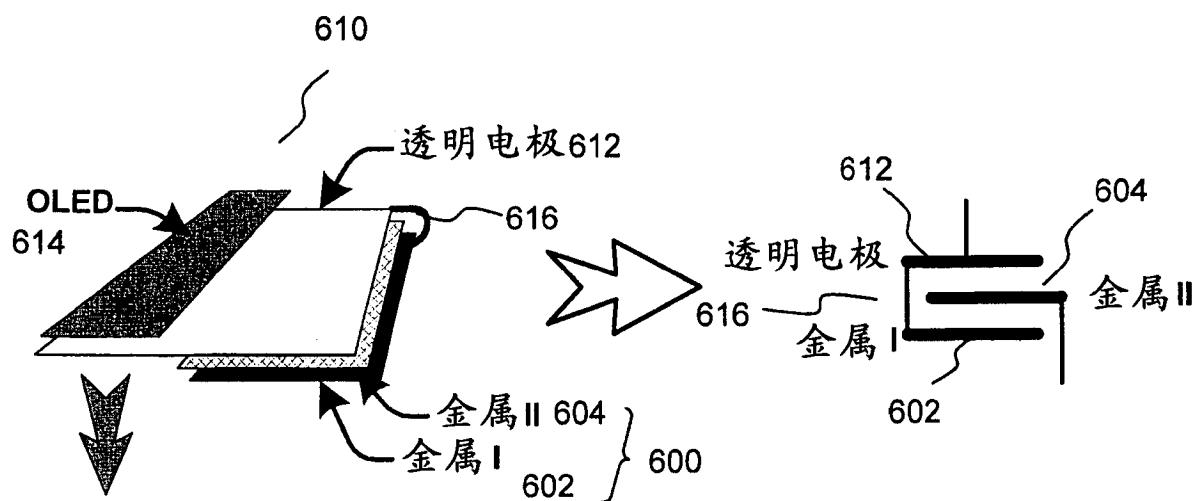

- [0052] 图 25 例示了用于驱动底部发射显示器的电容器的实现方式的示例；

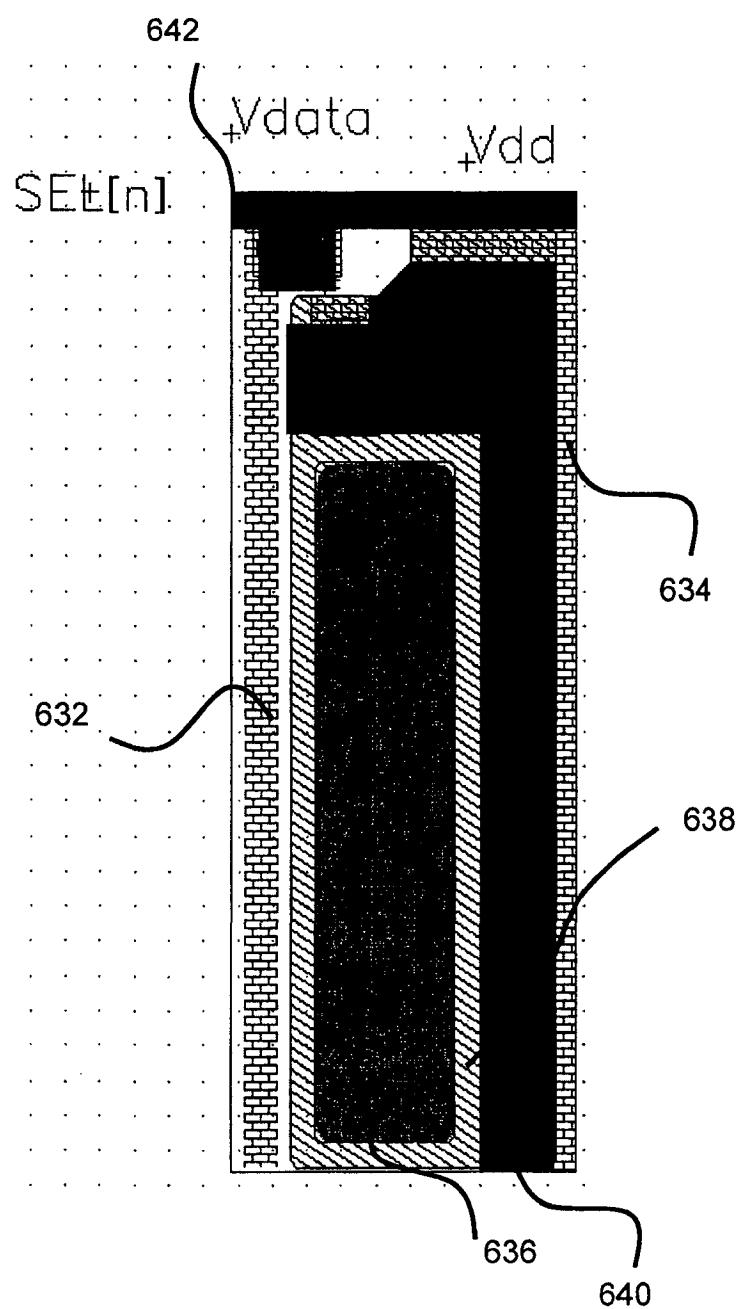

- [0053] 图 26 例示了底部发射像素的布局的示例；

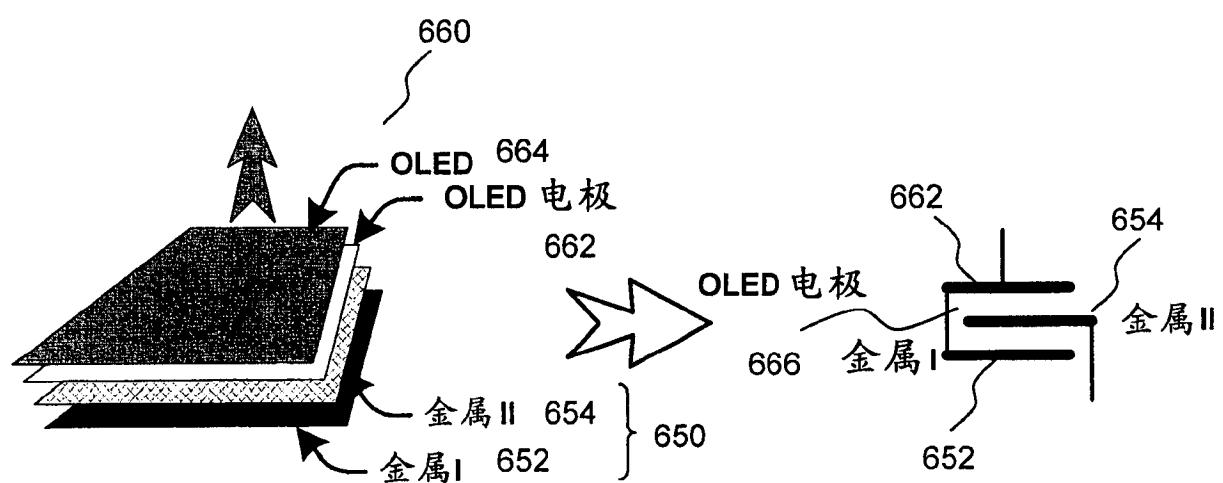

- [0054] 图 27 例示了用于驱动顶部发射显示器的电容器的实现方式的示例；

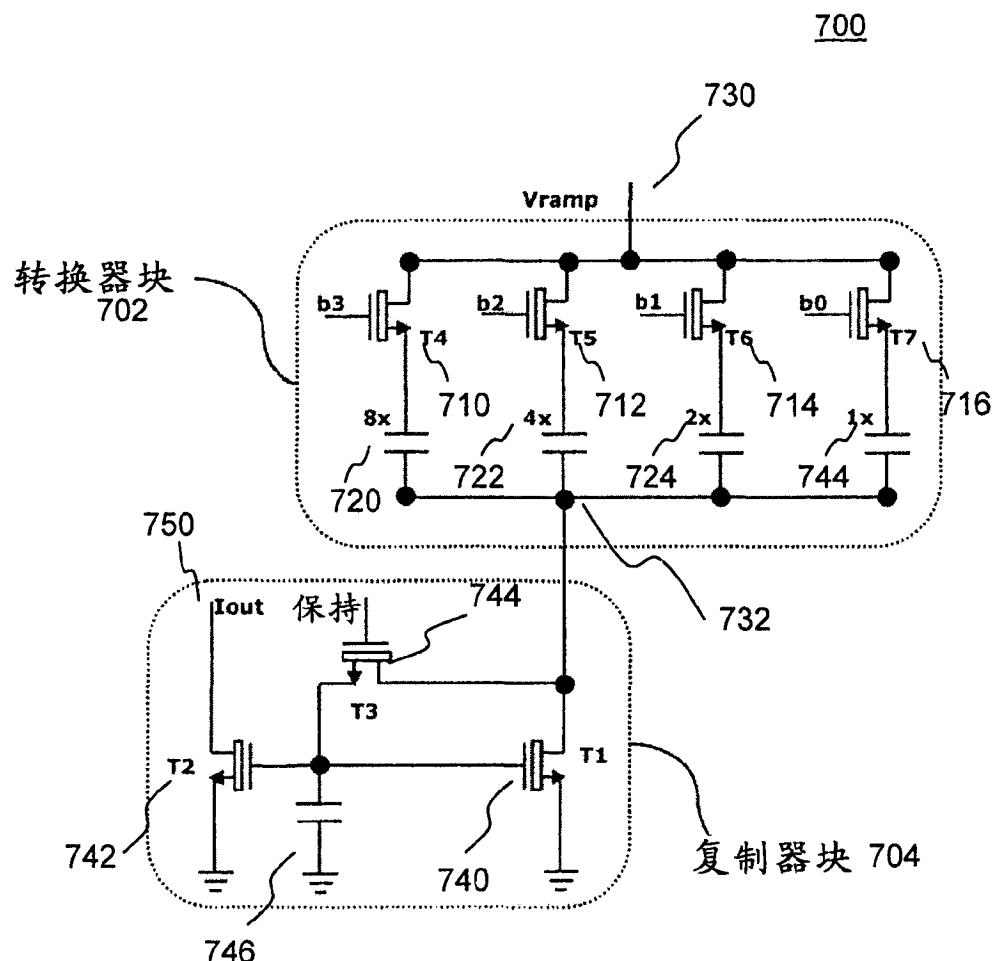

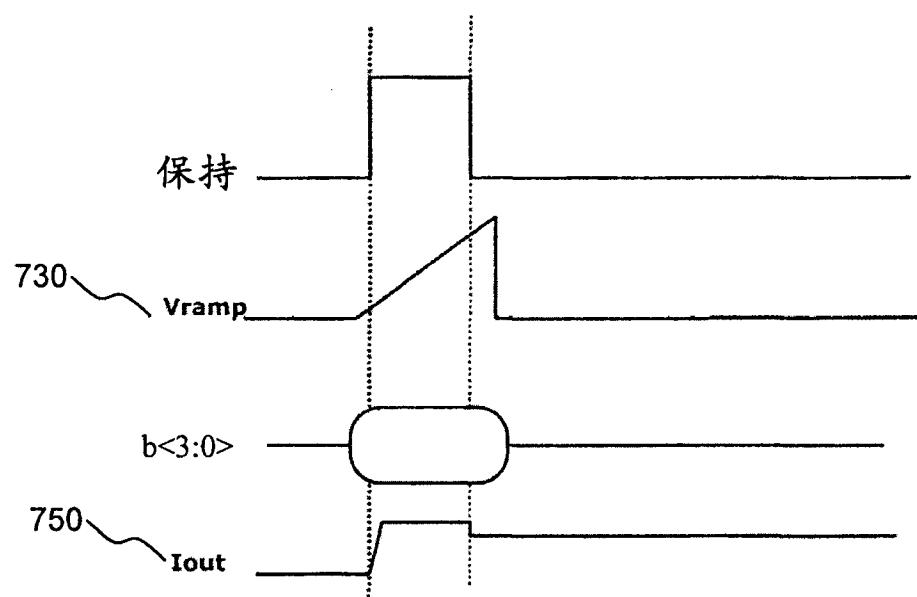

- [0055] 图 28 例示了基于电容驱动的数模转换器 (DAC) 的示例；

- [0056] 图 29 例示了图 28 的 DAC 的时序图的示例；

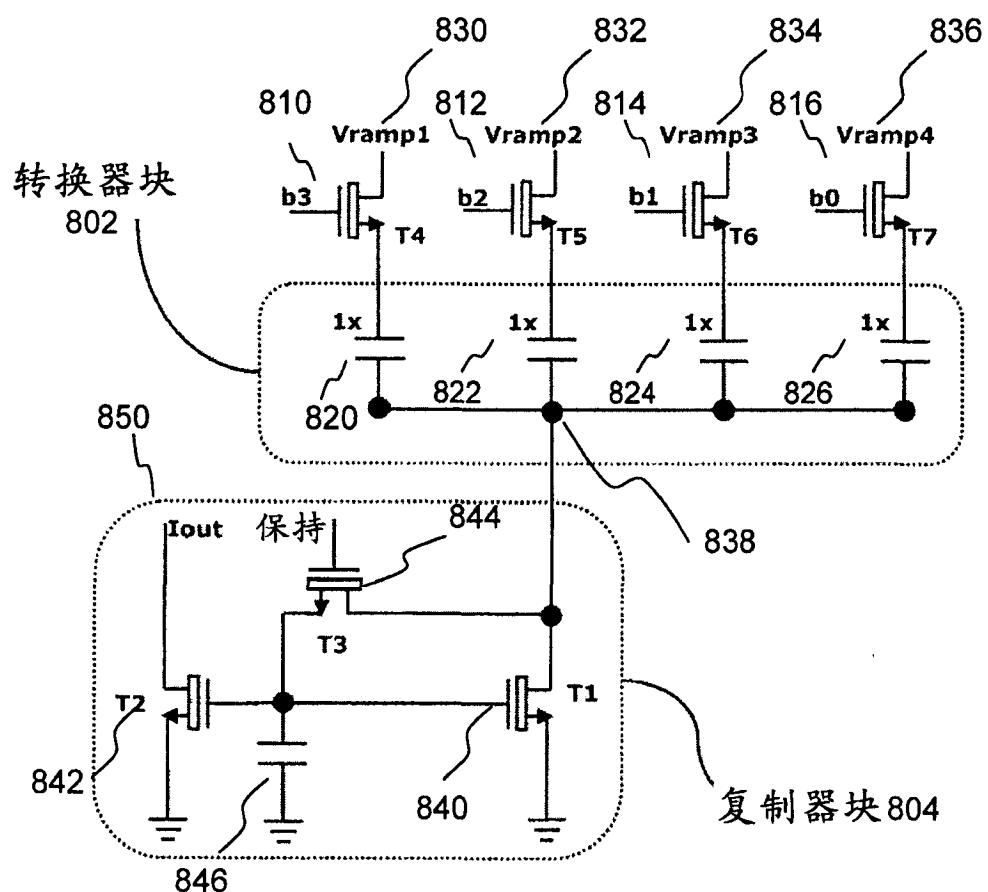

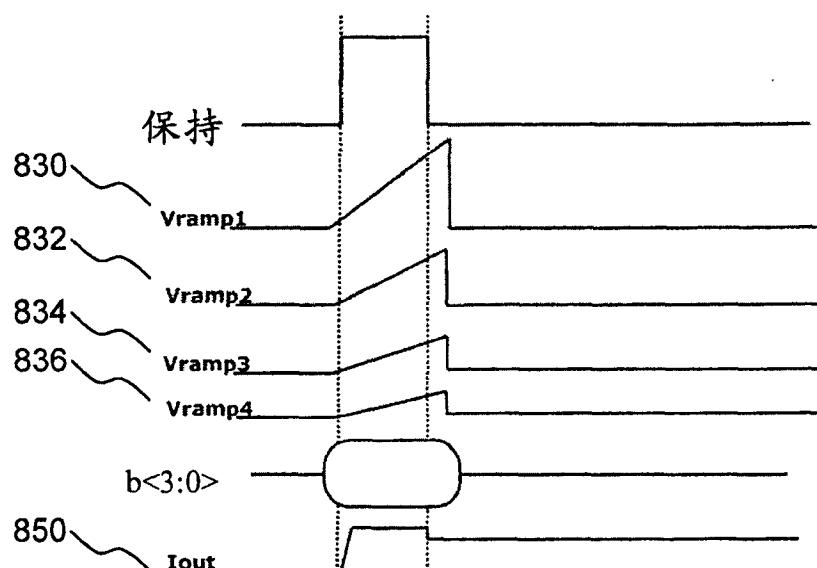

- [0057] 图 30 例示了基于电容驱动的数模转换器 (DAC) 的另一个示例；和

- [0058] 图 31 例示了图 30 的 DAC 的时序图的示例。

## 具体实施方式

[0059] 已通过举例方式描述了一个或多个当前优选的实施例。本领域技术人员将理解，在不脱离在权利要求中限定的本发明的范围的情况下，可以进行许多变化和修改。

[0060] 使用可以使用不同的制造技术制造的显示器系统来描述本发明的实施例，所述制造技术包括但不限于，例如，非晶硅、多晶硅、金属氧化物、传统的 CMOS、有机物、纳米 / 微米晶体半导体或它们的组合。显示器系统包括可以具有晶体管、电容器和发光器件的像素。晶体管可以用各种材料系统技术实现，所述材料系统技术包括非晶硅、微米 / 纳米晶体硅、多晶硅、有机物 / 聚合物材料和有关的纳米复合物、半导电氧化物或它们的组合。电容器可以具有不同的结构，包括金属 - 绝缘体 - 金属和金属 - 绝缘体 - 半导体。发光器件可以是例如 OLED，但是不限于此。显示器系统可以是 AMOLED 显示器系统，但是不限于此。

[0061] 在说明书中，“像素电路”和“像素”可以可互换地使用。每个晶体管可以具有栅极端子和两个其它端子（第一端子和第二端子）。在说明书中，晶体管的端子之一或“第一端子”（另一端子或“第二端子”）可以与漏极端子（源极端子）或源极端子（漏极端子）对应，但是不限于此。

[0062] 为了降低制造成本，用在显示器背板中的大部分制造技术仅仅提供一种类型的晶体管。由于每一种晶体管固有地对于单向电流源有益，因此像素电路和 / 或外围驱动器电路变得复杂，导致降低了产量、分辨率和开口率。另一方面，电容在所有技术中是可用的。

[0063] 描述使用用于将时变电压转换为电流的微分器 / 转换器的电流驱动技术。在说明书中，使用电容器来将斜坡电压 (ramp voltage) 转换为电流（例如，DC 电流）。参考图 1，示出了基于电容发展的电流源。图 1 的电流源 10 是可以提供正电流和负电流的双向电流源。电流源 10 包括用于产生时变电压的电压发生器 12 和驱动电容器 14。电压发生器 12 与驱动电容器 14 的一个端子 16 耦接。节点 “Iout” 与驱动电容器 14 的另一个端子 18 耦接。在此示例中，由电压发生器 12 产生斜坡电压。在实施例中，术语“电容性电流源”、“电

容性电流源驱动器”、“电容性驱动器”和“电流源”可以可互换地使用。在实施例中,术语“电压发生器”和“斜坡电压发生器”可以可互换地使用。在图 1 中,电流源 10 包括斜坡电压发生器 12,但是电流源 10 可以由接收斜坡电压的驱动电容器 14 形成。

[0064] 假定节点“ $I_{out}$ ”是虚拟地。将斜坡电压施加于驱动电容器 14 的端子 16,导致固定的电流经过驱动电容器 14 并且流到  $I_{out}$ 。 $i(t) = CdVR(t)/dt$  ( $C$ :电容,  $VR(t)$ :斜坡电压)。斜坡的斜率的幅度和符号是可控制的(可改变的),其可以改变输出电流的值和方向。此外,驱动电容器 14 的量可以改变电流值。结果,可以使用基于电容性电流源 10 的数字化的电容来发展简单且有效的电流模式的模数转换器(ADC),产生小且低功率的驱动器。此外,它提供了可以与制造技术无关地、容易地集成在面板上的简单的源极驱动器,结果改善了显示器的产量和简单性并且显著降低了系统成本。

[0065] 在一个示例中,电容性电流源 10 可以用于向电流编程的像素(例如,OLED 像素)提供编程电流。在另一个示例中,电容性电流源 10 可以用于提供用于加速像素(例如,图 8-16 中的电流偏置的电压编程的像素和图 17-19 中的电压偏置的电流编程的像素)的编程的偏置电流。在又一个示例中,电容性电流源 10 可以用于驱动像素。利用电容性电流源 10 的电容性的驱动技术改善了编程/驱动的建立时间,其适合于较大且较高分辨率的显示器,因而可以利用电容性电流源 10 实现低功率高分辨率的发射型显示器,如下所述。利用电容性电流源 10 的电容性的驱动技术补偿 TFT 老化(例如,阈值电压变化),因而可以改善显示器的均匀性和寿命,如下所述。

[0066] 在又一个示例中,可以与例如电流模式的模数转换器(ADC)一起地使用电容性电流源 10 来向将输入电流转换为数字信号的电流模式 ADC 提供参考电流。在又一个示例中,电容性的驱动可以用于基于斜坡电压和电容器产生电流的数模转换器(DAC)。

[0067] 参考图 2,示出了具有电容性驱动器 10 的集成显示器系统的示例。图 2 的集成显示器系统 20 包括具有以列和行方式排列的多个像素 24a-24d 的像素阵列 22、用于选择像素的栅极驱动器 28、和用于向选择的像素提供编程电流的源极驱动器 27。

[0068] 像素 24a-24d 是电流编程的像素电路。每个像素包括例如存储电容器、驱动晶体管、开关晶体管(或者驱动且切换的晶体管)和发光器件。在图 2 中,示出了四个像素;但是,本领域技术人员将理解,像素阵列 22 中的像素的数目不限于四个并且可以变化。像素阵列 22 可以包括基于电流和电压来操作像素的电流偏置的电压编程(CBVP)的像素(例如,图 8-16)或电压偏置的电压编程(VBCP)的像素(例如,图 17-19)。CBVP 驱动技术和 VBCP 驱动技术适合于用在 AMOLED 显示器中,在其中它们改善了像素的建立时间。

[0069] 每个像素与地址线 30 和数据线 32 耦接。每个地址线 30 在一行中的像素之间共用。每个数据线 32 在一列中的像素之间共用。栅极驱动器 28 经由地址线 30 驱动像素中的开关晶体管的栅极端子。源极驱动器 27 对于每一列包括电容性的驱动器 10。电容性的驱动器 10 与相应的列中的数据线 32 耦接。电容性的驱动器 10 驱动数据线 32。设置控制器 29 以控制和调度显示阵列 22 的编程、校准、驱动及其它操作。控制器 29 控制源极驱动器 27 和栅极驱动器 28 的操作。可以校准每个斜坡电压发生器 12。在显示器系统 20 中,驱动电容器 14 例如被实现在显示器的边缘上。

[0070] 在提供斜坡电压之初,电容(驱动电容器 14)充当电压源并且调整数据线 32 的电压。在数据线 32 的电压达到某一适当的电压之后,数据线 32 充当虚拟地(图 1 的“ $I_{out}$ ”)。

因而,在此点后,电容将充当用于提供恒定电流的电流源。此二重性 (duality) 导致快速的建立编程。

[0071] 在图 2 中,分开地分配像素的存储电容器和驱动电容器 14。但是,驱动电容器 14 可以与像素的存储电容器共用,如图 3 所示。

[0072] 参考图 3,示出了具有图 1 的电容性的驱动器 10 的集成显示器系统的另一个示例。图 3 的集成显示器系统 40 包括具有以列和行方式排列的多个像素 44a-44d 的像素阵列 42。像素 44a-44d 是电流编程的像素电路,并且可以与图 2 的像素 24a-24d 相同。在图 3 中,示出了四个像素;但是,本领域技术人员将理解,像素阵列 42 中的像素的数目不限于四个并且可以变化。每个像素包括例如存储电容器、驱动晶体管、开关晶体管(或者驱动且切换的晶体管)和发光器件。例如,像素阵列 42 可以包括基于编程电压和电流偏置来操作像素的图 6A 的像素。

[0073] 每个像素与地址线 50 和数据线 52 耦接。每个地址线 50 在一行中的像素之间共用。栅极驱动器 48 经由地址线 50 驱动像素中的开关晶体管的栅极端子。每个数据线 52 在一列中的像素之间共用,并且与该列中的每个像素中的电容器 46 耦接。列中的每个像素中的电容器 46 经由数据线 52 与斜坡电压发生器 12 耦接。源极驱动器 47 包括斜坡电压发生器 12。将斜坡电压发生器 12 分配给每列。设置控制器 49 以控制和调度显示阵列 42 的编程、校准、驱动及其它操作。控制器 49 控制栅极驱动器 48 和具有斜坡电压发生器 12 的源极驱动器 47。在显示器系统 40 中,像素中的电容器 46 充当该像素的存储电容器并且还充当驱动电容(图 1 的电容器 14)。

[0074] 参考图 4,示出了具有图 1 的电容性的驱动器 10 的集成显示器系统的另一个示例。图 4 的集成显示器系统 60 包括具有以列和行方式排列的多个像素 64a-64d 的像素阵列 62。在图 4 中,示出了四个像素;但是,本领域技术人员将理解,像素阵列 62 中的像素的数目不限于四个并且可以变化。像素 64a-64d 是 CBVP 像素电路,像素 64a-64d 中的每个像素与地址线 70、数据线 72 和电流偏置线 74 耦接。像素阵列 62 可以包括图 8-16 的 CBVP 像素。

[0075] 每个地址线 70 在一行中的像素之间共用。栅极驱动器 68 经由地址线 70 驱动像素中的开关晶体管的栅极端子。每个数据线 72 在一列中的像素之间共用,并且与用于提供编程数据的源极驱动器 67 耦接。源极驱动器 67 还可以提供偏置电压(例如,图 6 的 Vdd)。每个偏置线 74 在一列中的像素之间共用。驱动电容器 14 被分配给每一列并且与偏置线 74 和斜坡电压发生器 12 耦接。斜坡电压发生器 12 由多于一列共用。设置控制器 69 以控制和调度显示阵列 62 的编程、校准、驱动及其它操作。控制器 69 控制源极驱动器 67、栅极驱动器 68 和斜坡电压发生器 12。在显示器系统 60 中,容易将电容性电流源放在面板的外围上,结果降低了实现成本。在图 4 中,斜坡电压发生器 12 与源极驱动器 67 分开示出。但是,源极驱动器 67 可以提供斜坡电压。

[0076] 具有 CBVP 像素电路的显示器系统使用电压来提供不同的灰度级(电压编程),并且使用偏置来加速编程和补偿像素的时间相关的参数,诸如阈值电压漂移和 OLED 电压漂移。用于驱动具有 CBVP 像素电路的显示阵列的驱动器将像素亮度数据转换成电压。根据 CBVP 驱动方案,过驱动电压被产生并提供给驱动晶体管,其与它的阈值电压和 OLED 电压无关。通过存储在存储电容器中的电压并且将它施加于驱动晶体管的栅极来补偿像素元件的特性的漂移(例如,在长时间的显示操作下发光器件的退化和驱动晶体管的阈值电压漂

移)。因而,像素电路可以提供通过发光器件的稳定的电流而没有任何漂移效应,这改善了显示器工作寿命。此外,由于电路简单,因此它确保了比传统的像素电路更高的产品产量、更低的制造成本和更高的分辨率。由于像素电路的建立时间比传统的像素电路小得多,因此它适合于诸如高清晰度电视之类的大面积显示器,但是它也不排除较小的显示器面积。电容性的驱动技术可应用于 CBVP 显示器以进一步改善适于较大和较高分辨率的显示器的建立时间。

[0077] 电容性的驱动技术提供在 CBVP 显示器中共用电流偏置线和电压数据线的独特的机会。参考图 5,示出了具有图 1 的电容性的驱动器 10 的集成显示器系统的又一个示例。图 5 的集成显示器系统 80 包括具有以列和行方式排列的多个像素 84a-84d 的像素阵列 82。像素 84a-84d 是 CBVP 像素电路,并且可以与图 4 的像素 64a-64d 相同。在图 5 中,示出了四个像素;但是,本领域技术人员将理解,像素阵列 82 中的像素的数目不限于四个并且可以变化。每个像素与地址线 90 和电压数据 / 电流偏置线 92 耦接。

[0078] 每个地址线 90 在一行中的像素之间共用。栅极驱动器 88 经由地址线 90 驱动像素中的开关晶体管的栅极端子。每个电压数据 / 电流偏置线 92 在一列中的像素之间共用,并且与该列中的每个像素中的电容器 86 耦接。列中的每个像素中的电容器 86 经由电压数据 / 电流偏置线 92 与斜坡电压发生器 12 耦接。源极驱动器 87 具有斜坡电压发生器 12。将斜坡电压发生器 12 分配给每列。设置控制器 89 以控制和调度显示阵列 82 的编程、校准、驱动及其它操作。控制器 89 控制栅极驱动器 88 和具有斜坡电压发生器 12 的源极驱动器 87。通过电压数据 / 电流偏置线 92 携带数据电压和偏置电流。在显示器系统 80 中,像素中的电容器 86 充当该像素的存储电容器并且还充当驱动电容(图 1 的电容器 14)。

[0079] 参考图 6A,示出了可应用于图 5 的像素的 CBVP 像素电路的示例。图 6 的像素电路 CBVP01 包括驱动晶体管 102、开关晶体管 104、发光器件 106 和电容器 108。在图 6A 中,晶体管 102 和 104 是 p 型晶体管;但是,本领域技术人员将理解,具有 n 型晶体管的 CBVP 像素也可用作图 5 的像素。

[0080] 驱动晶体管 102 的栅极端子在 B01 处与电容器 108 耦接。驱动晶体管 102 的第一端子和第二端子中的一个端子与电源 (Vdd) 110 耦接,而另一个端子在节点 A01 处与发光器件 106 耦接。发光器件 106 与电源 (Vss) 112 耦接。开关晶体管 104 的栅极端子与地址线 SEL 耦接。开关晶体管 104 的第一端子和第二端子中的一个端子与驱动晶体管 102 的栅极耦接,而另一个端子在节点 A01 处与发光器件 106 和驱动晶体管 102 耦接。电容器 108 耦接在数据线 Vdata 和驱动晶体管 102 的栅极端子之间。电容器 108 充当存储电容器以及作为驱动器元件的电容性电流源(图 1 的 14)。

[0081] 电容器 108 与图 5 的电容器 86 对应。地址线 SEL 与图 5 的地址线 90 对应。数据线 Vdata 与图 5 的电压数据 / 电流偏置线 92 对应,并且与斜坡电压发生器(图 1 的 12)耦接。图 5 的源极驱动器 87 对数据线 Vdata 操作以向像素提供偏置信号和编程数据 (Vp)。

[0082] 在图 6A 中,斜坡电压用来传送偏置电流,而斜坡的初始电压 (Vref1-Vp) 用来向像素电路 CBVP01 发送编程电压,如图 6B 所示。

[0083] 参考图 6A 和图 6B,像素电路 CBVP01 的操作周期包括编程周期 120 和驱动周期 126。与驱动晶体管 102 耦接的电源 Vdd 在编程周期 120 期间为低。在编程周期 120 的初始阶段 122 中,向数据线 Vdata 提供斜坡电压。Vdata 的电压从 (Vref1-Vp) 变为 Vp,其中 Vp

是用于对像素进行编程的编程电压,  $V_{ref1}$  是参考电压。在初始阶段 122 期间, 地址线 SEL 被设置为低电压以使得开关晶体管 104 导通。在初始阶段 122 期间, 电容器 108 充当电流源。节点 A01 的电压变为  $VB_{T1}$ , 其中  $VB$  是  $T1$  的特性的函数 ( $T1$  : 驱动晶体管 102), 并且节点 B01 的电压变为  $VB_{T1}+V_{r_{T2}}$ , 其中  $V_{r_{T2}}$  是  $T2$  两端的电压降 ( $T2$  : 开关晶体管 104)。

[0084] 在初始阶段 122 之后的下一个阶段 124 处,  $V_{data}$  的电压保持  $V_p$ , 并且地址线 SEL 变为高以使得开关晶体管 104 截止。在阶段 124 期间, 电容器 108 充当存储元件。在驱动周期 126 期间, 数据线  $V_{data}$  变为  $V_{ref2}$ , 并且对于帧的其余部分, 保持在  $V_{ref2}$ 。

[0085]  $V_{ref1}$  限定偏置电流  $I_{bias}$  的电平, 并且例如基于 TFT、OLED 以及显示器特性和规格 (specification) 来确定它。 $V_{ref2}$  是  $V_{ref1}$  和像素特性的函数。

[0086] 参考图 7A-7B, 例示了示出使用图 6B 的操作的图 6A 的像素电路的模拟结果的图。在图 7A 中, “ $AV_T$ ” 表示驱动晶体管阈值  $V_T$  的变化, 并且 “ $\mu$ ” 表示迁移率 ( $cm^2N.s$ )。如图 7A-7B 所示, 不管驱动晶体管阈值  $V_T$  的变化和迁移率如何, 像素电流对于所有灰度级都是稳定的。

[0087] 参考图 8-16, 示出了 CBVP 像素电路的示例, 其可以形成图 2-5 的像素阵列。在图 8-16 中, 电流偏置线 (“ $I_{bias}$ ” 或 “ $IBIAS$ ”) 向相应的像素提供偏置电流。图 1 的电容性的驱动器 10 可以向电流偏置线提供恒定的偏置电流。CBVP 像素、显示器系统和操作的示例在美国专利申请公开 US2006/0125408 和 PCT 国际申请公开 WO2009/127065 中公开, 通过参考将这两个申请公开并入于此。

[0088] 图 8A 的像素电路 CBVP02 包括 OLED 210、存储电容器 212、驱动晶体管 214 以及开关晶体管 216 和 218。晶体管 214、216 和 218 是 n 型 TFT 晶体管。本领域技术人员将理解与像素电路 CBVP02 互补并且具有 p 型晶体管的电路。两条选择线 SEL1 和 SEL2、信号线 VDATA、偏置线 IBIAS、电压供应线 VDD 以及公共地与像素电路 CBVP02 耦接。在图 8A 中, 公共地用于 OLED 顶部电极。公共地不是像素电路的一部分, 并且在形成 OLED 210 时的最后阶段形成。晶体管 214 和 216 以及存储电容器 212 与节点 A11 连接。OLED 210、存储电容器 212 以及晶体管 214 和 218 与节点 B11 连接。

[0089] 驱动晶体管 214 的栅极端子通过开关晶体管 216 与信号线 VDATA 连接并且与电容器 212 连接。驱动晶体管 214 的第一端子和第二端子中的一个端子与电压供应线 VDD 连接, 而另一个端子在 B11 处与 OLED 210 的阳极电极连接。存储电容器 212 连接在 A11 处的驱动晶体管 214 的栅极端子和 B11 处的 OLED 210 之间。开关晶体管 216 的栅极端子与第一选择线 SEL1 连接。开关晶体管 216 的第一端子和第二端子中的一个端子与信号线 VDATA 连接, 而另一个端子在 A11 处与驱动晶体管 214 的栅极端子连接。开关晶体管 218 的栅极端子与第二选择线 SEL2 连接。开关晶体管 218 的第一端子和第二端子中的一个端子在 B11 处与 OLED 210 的阳极电极和存储电容器 212 连接, 而另一个端子与偏置线 IBIAS 连接。OLED 210 的阴极电极与公共地连接。

[0090] 像素电路 CBVP02 的操作包括具有多个编程周期的编程阶段和具有一个驱动周期的驱动阶段。在编程阶段期间, 节点 B11 被充电到驱动晶体管 214 的阈值电压的负值, 并且节点 A11 被充电到编程电压  $V_p$ 。

[0091] 结果, 驱动晶体管 214 的栅 - 源电压为 :

$$V_{GS} = V_p - (-V_T) = V_p + V_T \quad (1)$$

[0093] 其中 VGS 表示驱动晶体管 214 的栅 - 源电压, 并且 VT 表示驱动晶体管 214 的阈值电压。在驱动阶段中此电压保持在电容器 212 上, 导致在驱动阶段中期望的电流流过 OLED 210。

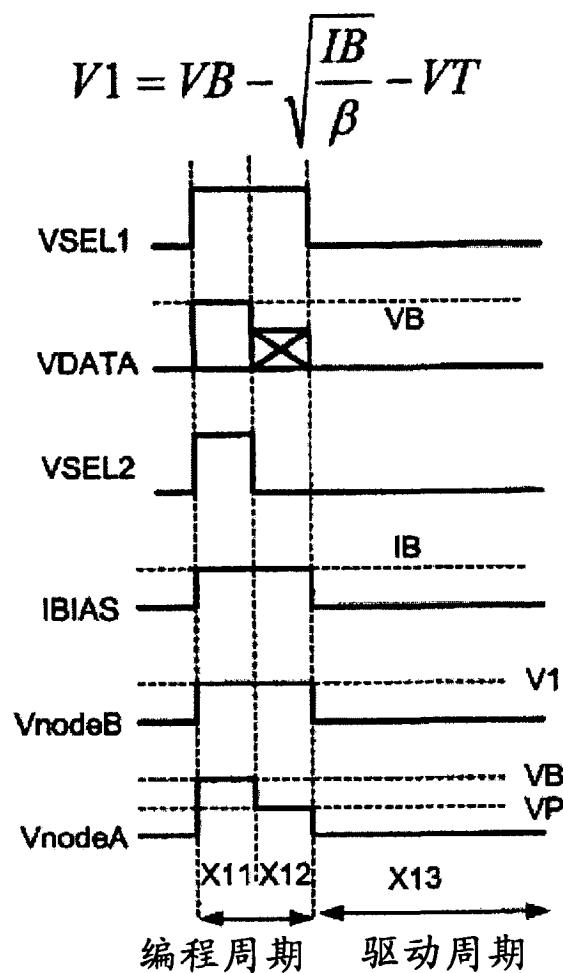

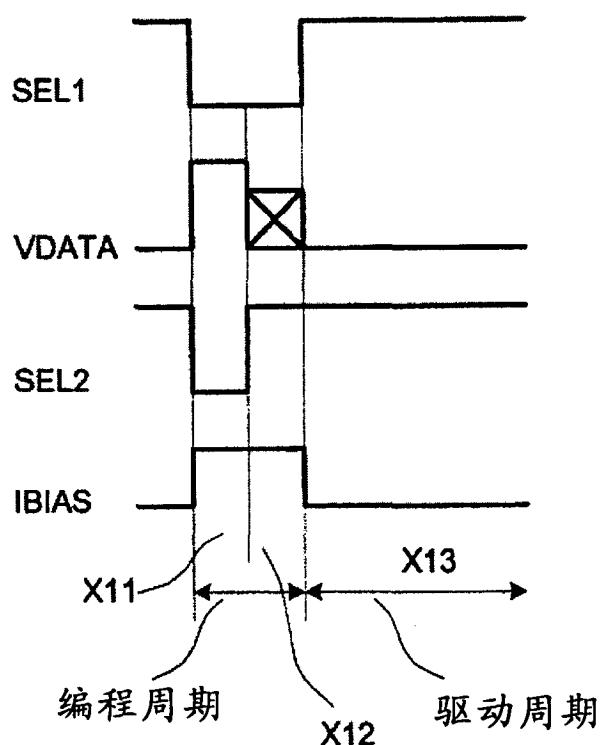

[0094] 参考图 8B, 示出了应用于图 8A 的像素电路 CBVP02 的一个示例性的操作过程。在图 8B 中, “VnodeB”表示在图 8A 的节点 B11 处的电压, “VnodeA”表示在图 8A 的节点 A11 处的电压, “VSEL1”与图 8A 的 SEL1 对应, 并且“VSEL2”与图 8A 的 SEL2 对应。编程阶段具有两个操作周期 X11、X12, 并且驱动阶段具有一个操作周期 X13。

[0095] 第一操作周期 X11: 两个选择线 SEL1 和 SEL2 都为高。偏置电流 IB 流过偏置线 IBIAS, 并且 VDATA 变为偏置电压 VB。

[0096] 结果, 节点 B11 的电压为:

$$[0097] V_{nodeB} = VB - \sqrt{\frac{IB}{\beta}} - VT \quad (2)$$

[0098] 其中 VnodeB 表示节点 B11 的电压, VT 表示驱动晶体管 214 的阈值电压, 并且  $\beta$  表示由  $IDS = \beta (VGS - VT)^2$  给出的 TFT 的电流 - 电压 (I-V) 特性中的系数。IDS 表示驱动晶体管 214 的漏 - 源电流。

[0099] 第二操作周期 X12: 在 SEL2 为低且 SEL1 为高时, VDATA 变为编程电压 VP。由于 OLED 210 的电容 211 大, 因此在先前周期中产生的节点 B11 的电压保持原样。

[0100] 因此, 驱动晶体管 214 的栅 - 源电压可以被得出为:

$$[0101] VGS = VP + \Delta VB + VT \quad (3)$$

$$[0102] \Delta VB = \sqrt{\frac{IB}{\beta}} - VB \quad (4)$$

[0103] 当基于 (4) 适当地选择 VB 时,  $\Delta VB$  为零。将驱动晶体管 214 的栅 - 源电压 (即  $VP + VT$ ) 存储在存储电容器 212 中。

[0104] 第三操作周期 X13: IBIAS 变为低。SEL1 变为零。将存储在存储电容器 212 中的电压施加于驱动晶体管 214 的栅极端子。驱动晶体管 214 导通。驱动晶体管 214 的栅 - 源电压随着存储在存储电容器 212 中的电压发展 (develop over)。因而, 通过 OLED 210 的电流变得与驱动晶体管的阈值电压的漂移和 OLED 特性的漂移无关。

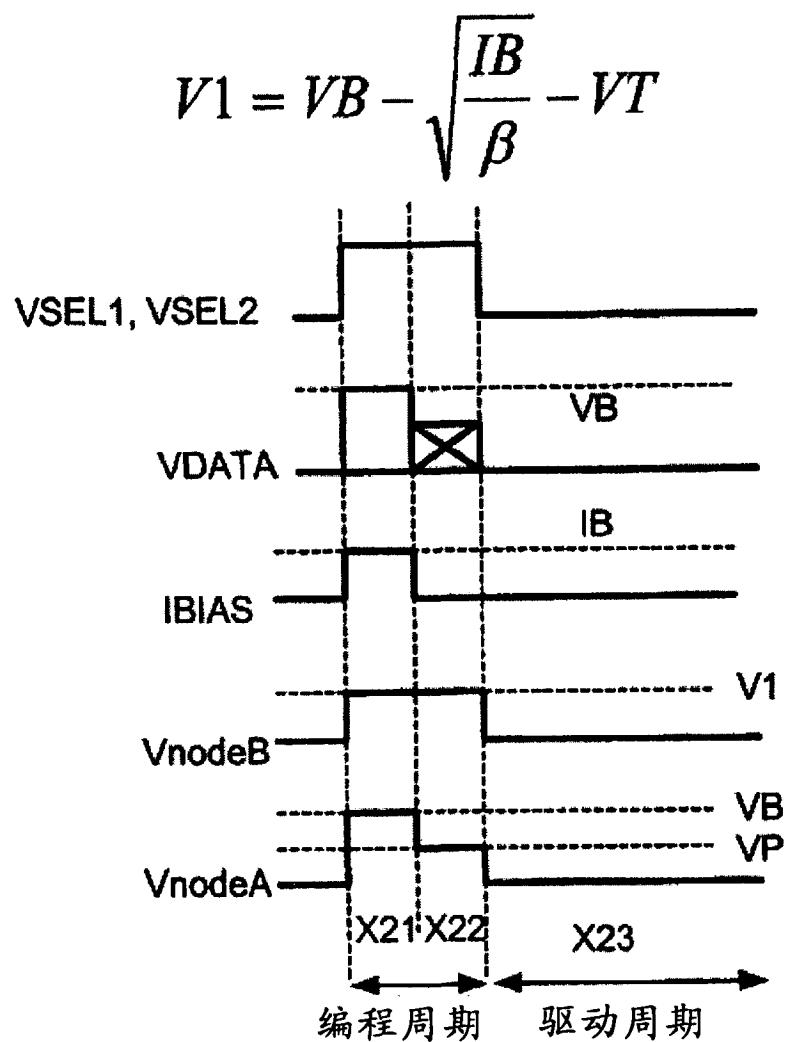

[0105] 参考图 8C, 示出了应用于图 8A 的像素电路 CBVP02 的又一个示例性的操作过程。在图 8C 中, “VnodeB”表示在图 8A 的节点 B11 处的电压, “VnodeA”表示在图 8A 的节点 A11 处的电压, “VSEL1”与图 8A 的 SEL1 对应, 以及“VSEL2”与图 8A 的 SEL2 对应。编程阶段具有两个操作周期 X21、X22, 以及驱动阶段具有一个操作周期 X23。第一操作周期 X21 与图 8B 的第一操作周期 X11 相同。第三操作周期 X23 与图 8B 的第三操作周期 X13 相同。在图 8C 中, 选择线 SEL1 和 SEL2 具有相同的时序。因而, SEL1 和 SEL2 可以与同一选择线连接。

[0106] 第二操作周期 X22: SEL1 和 SEL2 为高。开关晶体管 218 导通。流过 IBIAS 的偏置电流 IB 为零。

[0107] 驱动晶体管 214 的栅 - 源电压可以为  $VGS = VP + VT$ , 如上所述。将驱动晶体管 214 的栅 - 源电压 (即  $VP + VT$ ) 存储在存储电容器 212 中。

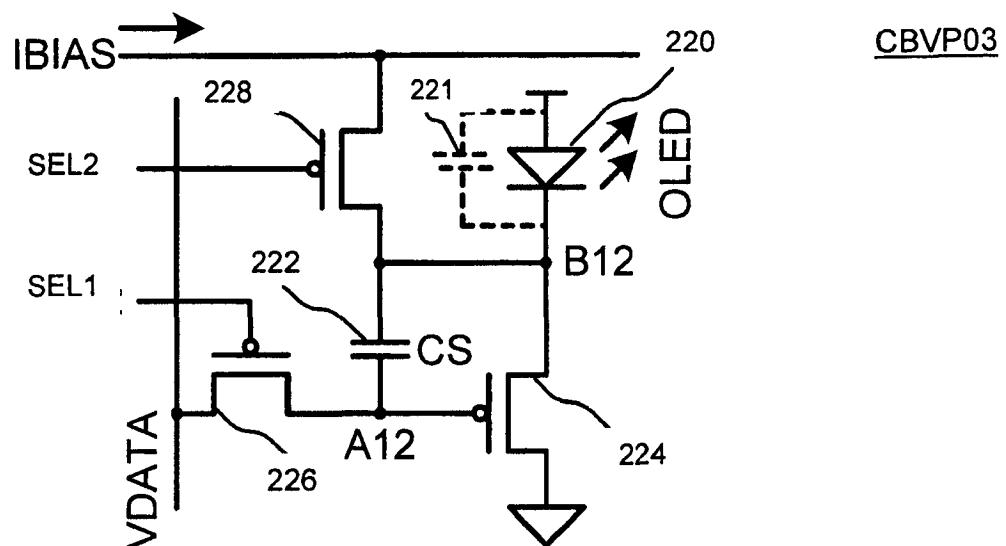

[0108] 图 9A 的像素电路 CBVP03 与图 8A 的像素电路 CBVP02 互补并且具有 p 型晶体管。像素电路 CBVP03 包括 OLED 220、存储电容器 222、驱动晶体管 224 以及开关晶体管 226 和 228。晶体管 224、226 和 228 是 p 型晶体管。将两条选择线 SEL1 和 SEL2、信号线 VDATA、偏置线 IBIAS、电压供应线 VDD 以及公共地与像素电路 CBVP03 耦接。

[0109] 晶体管 224 和 226 以及存储电容器 222 在 A12 处连接。OLED 220 的阴极电极、存储电容器 222 以及晶体管 224 和 228 在 B12 处连接。由于 OLED 阴极与像素电路 CBVP03 的其它元件连接,因此这确保了与任何 OLED 制造的集成。

[0110] 参考图 9B-9C,示出了应用于图 9A 的像素电路 CBVP03 的示例性的操作过程。图 9B 与图 8B 对应。图 9C 与图 8C 对应。图 9B-9C 的 CBVP 驱动方案使用与图 8B-8C 类似的 IBIAS 和 VDATA。

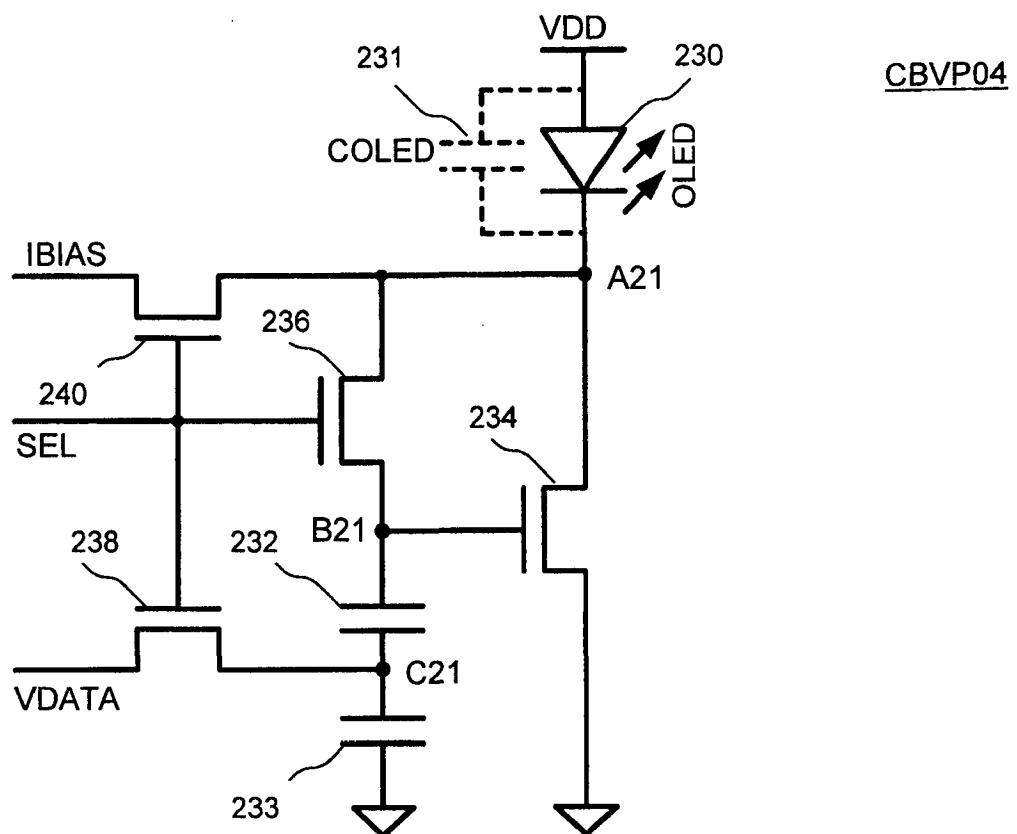

[0111] 图 10A 的像素电路 CBVP04 包括 OLED 230、存储电容器 232 和 233、驱动晶体管 234、以及开关晶体管 236、238 和 240。晶体管 234、236、238 和 240 是 n 型 TFT 晶体管。本领域技术人员将理解与像素电路 CBVP04 互补并且具有 p 型晶体管的电路。将选择线 SEL、信号线 VDATA、偏置线 IBIAS、电压线 VDD 以及公共地与像素电路 CBVP04 耦接。OLED 230、晶体管 234、236 和 240 在节点 A21 处连接。存储电容器 232 以及晶体管 234 和 236 在节点 B21 处连接。

[0112] 驱动晶体管 234 的第一端子和第二端子中的一个端子在 A21 处与 OLED 230 的阴极电极连接,而另一个端子与地电势连接。存储电容器 232 和 233 串联并且连接在 B21 处的驱动晶体管 234 的栅极和地之间。开关晶体管 236、238 和 240 的栅极端子与选择线 SEL 连接。开关晶体管 236 的第一端子和第二端子中的一个端子在 A21 处与 OLED 230 和驱动晶体管 234 连接,而另一个端子在 B21 处与驱动晶体管 234 的栅极端子连接。开关晶体管 238 的第一端子和第二端子中的一个端子与信号线 VDATA 连接,而另一个端子与连接存储电容器 232 和 233 的 C21 连接。开关晶体管 240 的第一端子和第二端子中的一个端子与偏置线 IBIAS 连接,而另一个端子与作为 A21 的 OLED230 的阴极端子连接。OLED 230 的阳极电极与 VDD 连接。

[0113] 像素电路 CBVP04 的操作包括具有多个编程周期的编程阶段和具有一个驱动周期的驱动阶段。在编程阶段期间,第一存储电容器 232 被充电到编程电压 VP 加上驱动晶体管 234 的阈值电压,并且第二存储电容器 233 被充电到零。

[0114] 结果,驱动晶体管 234 的栅 - 源电压为 :

[0115]  $VGS = VP + VT$  (5)

[0116] 其中 VGS 表示驱动晶体管 234 的栅 - 源电压,以及 VT 表示驱动晶体管 234 的阈值电压。

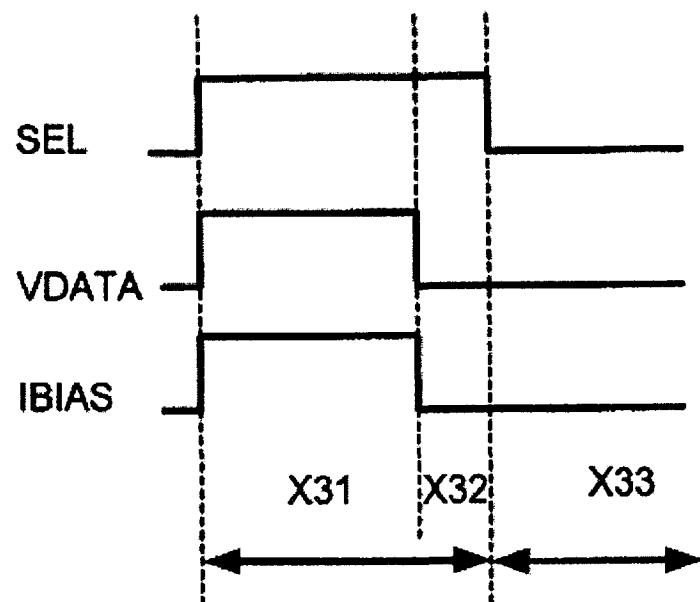

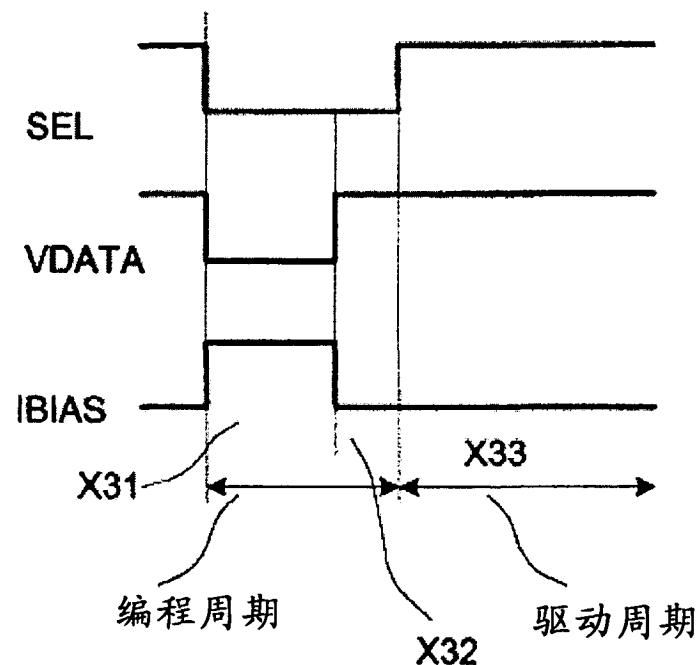

[0117] 参考图 10B,示出了应用于图 10A 的像素电路 CBVP04 的一个示例性的操作过程。编程阶段具有两个操作周期 X31、X32,并且驱动阶段具有一个操作周期 X33。

[0118] 第一操作周期 X31 :选择线 SEL 为高。偏置电流 IB 流过偏置线 IBIAS,并且 VDATA 变为  $VB - VP$ ,其中 VP 是编程电压并且 VB 由下式给出 :

$$[0119] VB = \sqrt{\frac{IB}{\beta}} \quad (6)$$

[0120] 结果,存储在第一电容器 232 中的电压为 :

[0121]  $VC1 = VP+VT$  (7)

[0122] 其中  $VC1$  表示存储在第一存储电容器 232 中的电压,  $VT$  表示驱动晶体管 234 的阈值电压,  $\beta$  表示由  $IDS = \beta (VGS-VT)^2$  给出的 TFT 的电流 - 电压 (I-V) 特性中的系数。  $IDS$  表示驱动晶体管 234 的漏 - 源电流。

[0123] 第二操作周期 X32 : 在  $SEL$  为高时,  $VDATA$  为零, 并且  $IBIAS$  变为零。由于 OLED 230 的电容 231 以及偏置线  $IBIAS$  的寄生电容大, 因此在先前周期中产生的节点 B21 处的电压和节点 A21 处的电压保持不变。

[0124] 因此, 驱动晶体管 234 的栅 - 源电压可以被得到为 :

[0125]  $VGS = VP+VT$  (8)

[0126] 其中  $VGS$  表示驱动晶体管 234 的栅 - 源电压。将驱动晶体管 234 的栅 - 源电压存储在存储电容器 232 中。

[0127] 第三操作周期 X33 :  $IBIAS$  变为零。  $SEL$  变为零。节点 C21 的电压变为零。将存储在存储电容器 232 中的电压施加于驱动晶体管 234 的栅极端子。驱动晶体管 234 的栅 - 源电压随着存储在存储电容器 232 中的电压发展。考虑到驱动晶体管 234 的电流主要由它的栅 - 源电压限定, 通过 OLED 230 的电流变得与驱动晶体管 234 的阈值电压的漂移和 OLED 特性的漂移无关。

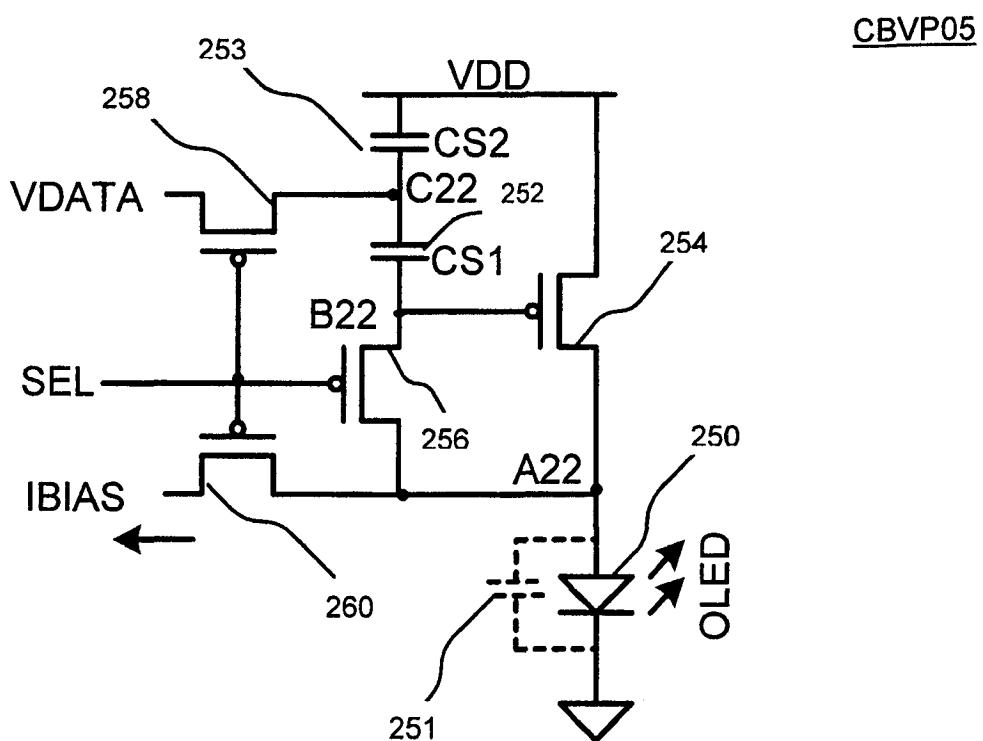

[0128] 图 11A 的像素电路 CBVP05 与图 10A 的像素电路 CBVP04 互补并且具有 p 型晶体管。像素电路 CBVP05 包括 OLED 250、存储电容器 252 和 253、驱动晶体管 254 以及开关晶体管 256、258 和 260。晶体管 254、256、258 和 260 是 p 型晶体管。将两条选择线  $SEL1$  和  $SEL2$ 、信号线  $VDATA$ 、偏置线  $IBIAS$ 、电压供应线  $VDD$  以及公共地与像素电路 CBVP05 耦接。公共地可以与图 8A 的公共地相同。

[0129] OLED 250 的阳极电极、晶体管 254、256 和 260 在节点 A22 处连接。存储电容器 252 以及晶体管 254 和 256 在节点 B22 处连接。开关晶体管 258 以及存储电容器 252 和 253 在节点 C22 处连接。

[0130] 参考图 11B, 示出了应用于图 11A 的像素电路 CBVP05 的一个示例性的操作过程。图 11B 与图 10B 对应。如图 11B 所示, 图 11B 的 CBVP 驱动方案使用与图 10B 类似的  $IBIAS$  和  $VDATA$ 。

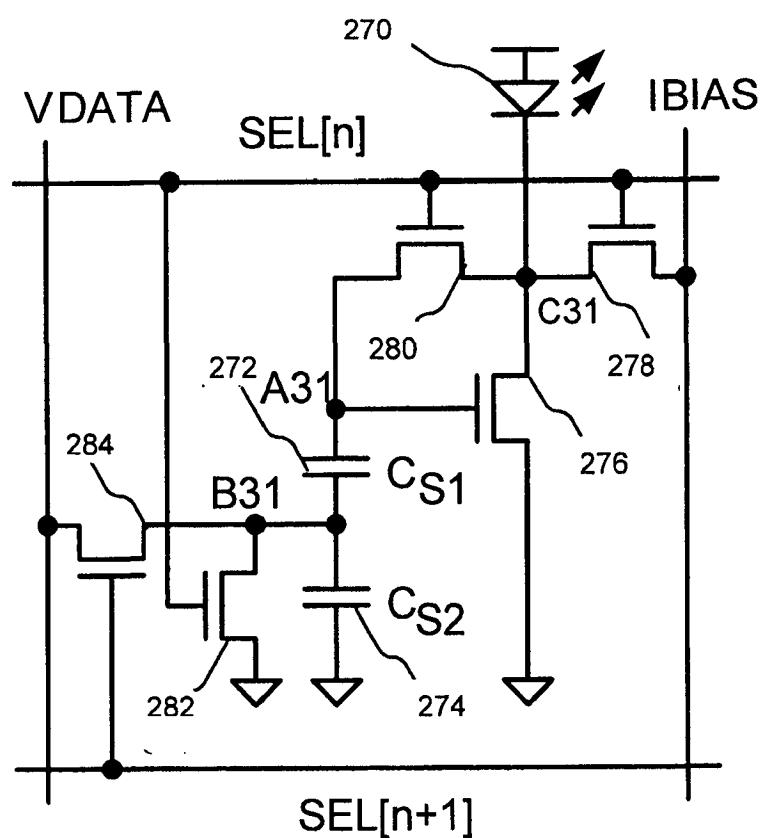

[0131] 具有图 12A 中的 CBVP 像素电路的显示器基于图 10A 的像素电路 CBVP04, 并且包括 OLED 270、存储电容器 272 和 274、以及晶体管 276、278、280、282 和 284。晶体管 276 是驱动晶体管。晶体管 278、280 和 284 是开关晶体管。晶体管 276 和 280 以及存储电容器 272 在节点 A31 处连接。晶体管 282 和 284 及存储电容器 272 和 274 在 B31 处连接。晶体管 278、280 和 282 的栅极端子与用于第  $n$  行的地址线  $SEL[n]$  耦接, 并且开关晶体管 284 的栅极端子与用于第  $(n+1)$  行的地址线  $SEL[n+1]$  耦接。晶体管 276、278、280、282 和 284 是 n 型 TFT 晶体管。本领域技术人员将理解与图 12A 的像素电路互补并且具有 p 型晶体管的电路。本领域技术人员将理解, 应用于图 12A 的驱动技术可应用于该互补的像素电路。在图 12A 中, 示出了与两行和一列有关的元件。图 12A 的显示器可以包括多于两行和多于一列。

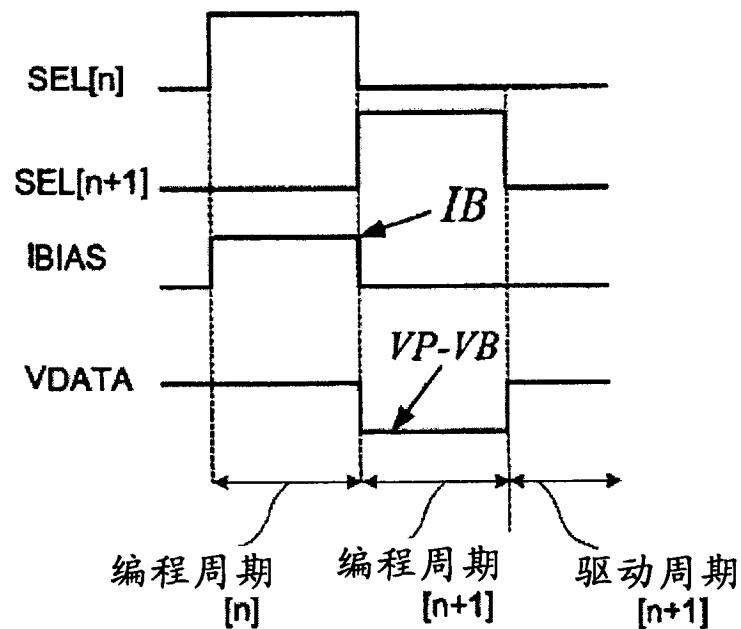

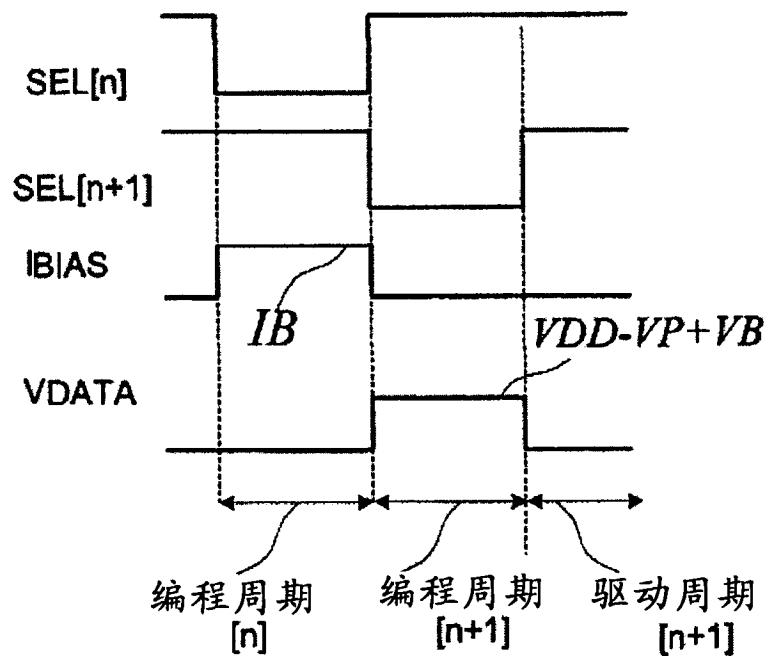

[0132] 参考图 12B, 示出了应用于图 12A 的显示器的一个示例性的操作过程。在图 12B 中,

“编程周期 [n]”表示对于显示器的行 [n] 的编程周期。在两个连续的行 (n 和 n+1) 之间共享编程时间。在第 n 行的编程周期期间, SEL[n] 为高, 并且偏置电流 IB 流过晶体管 278 和 280。节点 A31 处的电压被自调节到  $(IB/\beta)1/2+VT$ , 而节点 B31 处的电压为零, 其中 VT 表示驱动晶体管 276 的阈值电压, 并且  $\beta$  表示由  $IDS = \beta(VGS-VT)^2$  给出的 TFT 的电流 - 电压 (I-V) 特性中的系数, 并且 IDS 表示驱动晶体管 276 的漏 - 源电流。

[0133] 在第 (n+1) 行的编程周期期间, VDATA 变为 VP-VB。结果, 如果  $VB = (IB/\beta)1/2$ , 则节点 A31 处的电压变为 VP+VT。由于对于所有的像素采用恒定的电流, 因此 IBIAS 线始终具有合适的电压, 以使得没有必要对该线预充电, 结果缩短了编程时间并且降低了功耗。更重要的是, 在第 n 行的编程周期开始时, 节点 B31 的电压从 VP-VB 变为零。因此, 节点 A31 处的电压变为  $(IB/\beta)1/2+VT$ , 并且它已经被调节到它的最终值, 得到快速的建立时间。

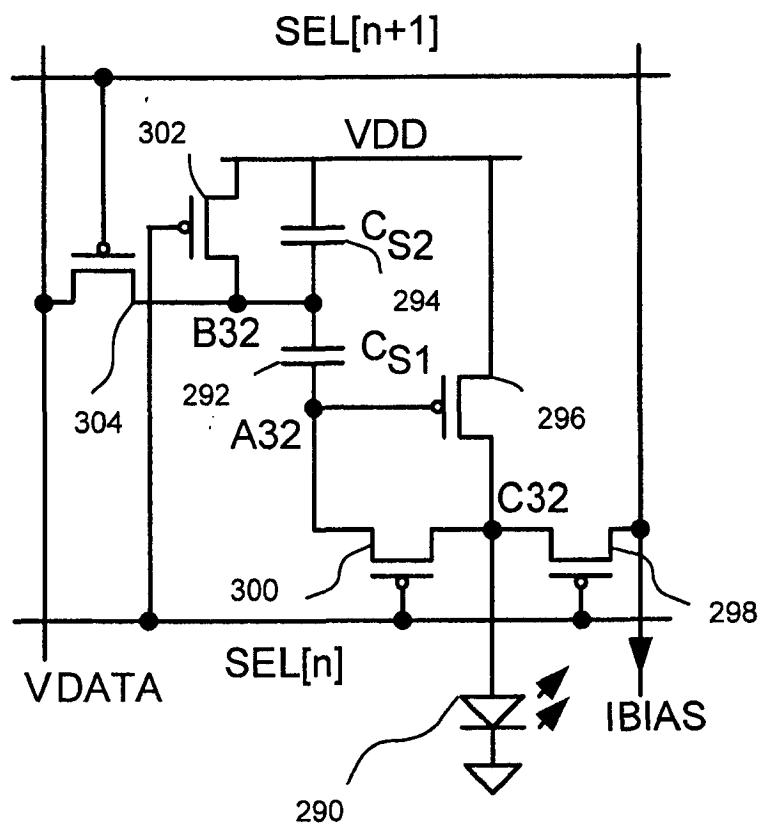

[0134] 具有图 13A 中的 CBVP 像素电路的显示器基于图 11 的像素电路 CBVP05, 并且具有 OLED 290、存储电容器 292 和 294、以及 p 型 TFT 晶体管 296、298、300、302 和 304。晶体管 296 是驱动晶体管。晶体管 298、300 和 304 是开关晶体管。晶体管 296 和 300 以及存储电容器 292 在节点 A32 处连接。晶体管 302 和 304 以及存储电容器 292 和 294 在 B32 处连接。晶体管 296、298 和 200 以及 OLED 290 在 C32 处连接。晶体管 298、300 和 302 的栅极端子与用于第 n 行的地址线 SEL[n] 耦接, 并且开关晶体管 304 的栅极端子与用于第 (n+1) 行的地址线 SEL[n+1] 耦接。本领域技术人员将理解与图 13A 的像素电路互补并且具有 n 型晶体管的电路。本领域技术人员将理解, 应用于图 13A 的驱动技术可以应用于该互补的像素电路。在图 13A 中, 示出了与两行和一列有关的元件。图 13A 的显示器可以包括多于两行和多于一列。驱动晶体管 296 连接在 OLED 290 的阳极电极和电压供应线 VDD 之间。

[0135] 参考图 13B, 示出了应用于图 13A 的显示器的一个示例性的操作过程。图 13B 与图 12B 对应。图 13B 的 CBVP 驱动方案使用与图 12B 类似的 IBIAS 和 VDATA。

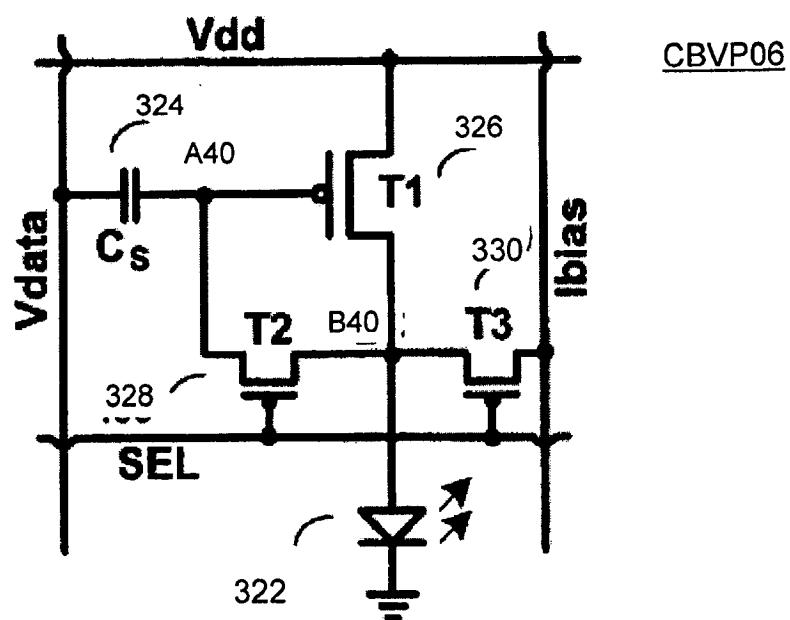

[0136] 图 14A 的像素电路 CBVP06 包括 OLED 322、存储电容器 324、驱动晶体管 326、以及开关晶体管 328 和 330。晶体管 326、328 和 330 是 p 型 TFT 晶体管。本领域技术人员将理解与图 14A 的像素电路互补并且具有 n 型晶体管的电路。本领域技术人员将理解, 应用于图 14A 的驱动技术可以应用于该互补的像素电路。选择线 SEL、信号线 Vdata、偏置线 Ibias 和电压供应线 Vdd 与像素电路 CBVP06 连接。偏置线 Ibias 提供基于显示器规格 (诸如寿命、功率、以及器件性能和均匀性) 限定的偏置电流 (Ibias)。

[0137] 驱动晶体管 326 的第一端子和第二端子中的一个端子与电压供应线 Vdd 连接, 而另一个端子在 B40 处与 OLED 322 连接。电容器 324 的一个端子与信号线 Vdata 连接, 而另一个端子在节点 A40 处与驱动晶体管 326 的栅极端子连接。开关晶体管 328 和 330 的栅极端子与选择线 SEL 连接。开关晶体管 328 连接在 A40 和 B40 之间。开关晶体管 330 连接在 B40 和偏置线 Ibias 之间。在像素电路 CBVP06 中, 通过晶体管 330 提供预定的固定电流 (Ibias) 以补偿所有的空间和时间非均匀性, 并且电压编程用来将电流划分成不同的灰度级所需的不同的电流电平。

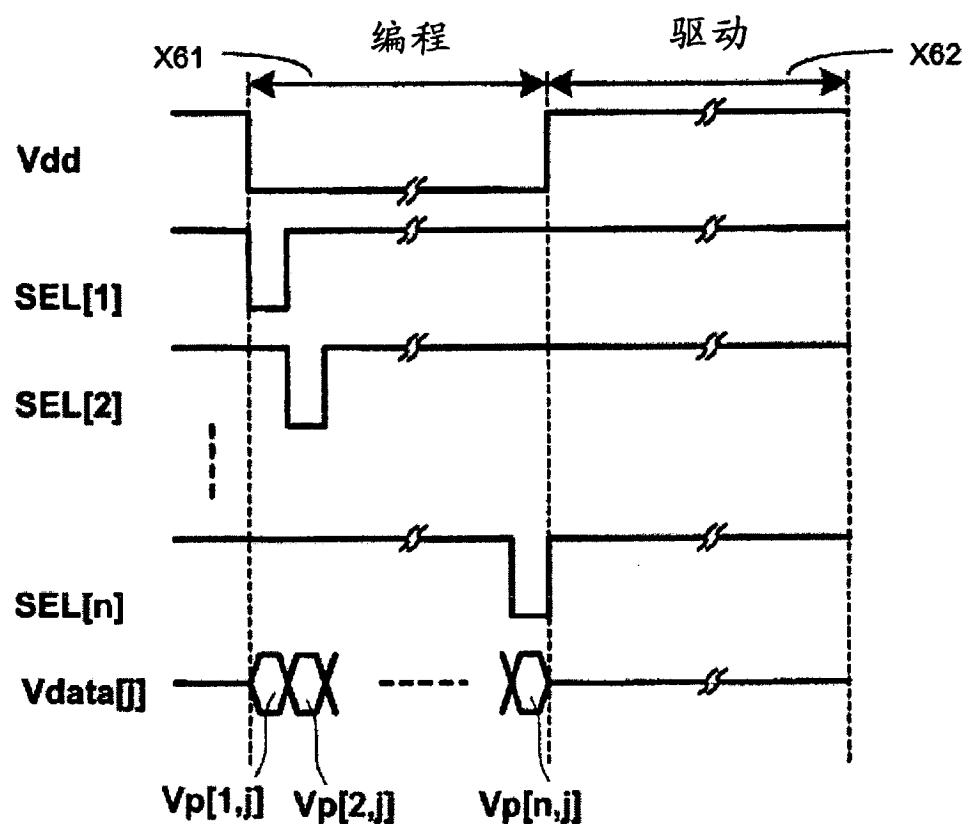

[0138] 参考图 14B, 示出了应用于图 14A 的像素电路 CBVP06 的一个示例性的操作过程。操作过程包括编程阶段 X61 和驱动阶段 X62。图 14B 中的 Vdata[j] 与图 14A 的 Vdata 对应。图 14B 中的  $Vp[k, j]$  ( $k = 1, 2, \dots, n$ ) 表示 Vdata[j] 上的第 k 个编程电压, 其中 “j” 是列号。图 14B 中的 SEL[j] ( $j = 1, 2, \dots$ ) 表示用于第 j 列的选择线 (图 14A 中的 “SEL”)。

[0139] 在编程周期 X61 期间, SEL 为低以使得开关晶体管 328 和 330 导通。经由偏置线 Ibias 向像素电路 CBVP06 施加偏置电流 Ibias, 并且驱动晶体管 326 的栅极端子被自调节以使得所有电流能够经过驱动晶体管 326 的源极 - 漏极。在这个周期中, Vdata 具有与像素的灰度级有关的编程电压。在驱动周期 X62 期间, 开关晶体管 328 和 330 截止, 并且电流经过驱动晶体管 326 和 OLED 322。

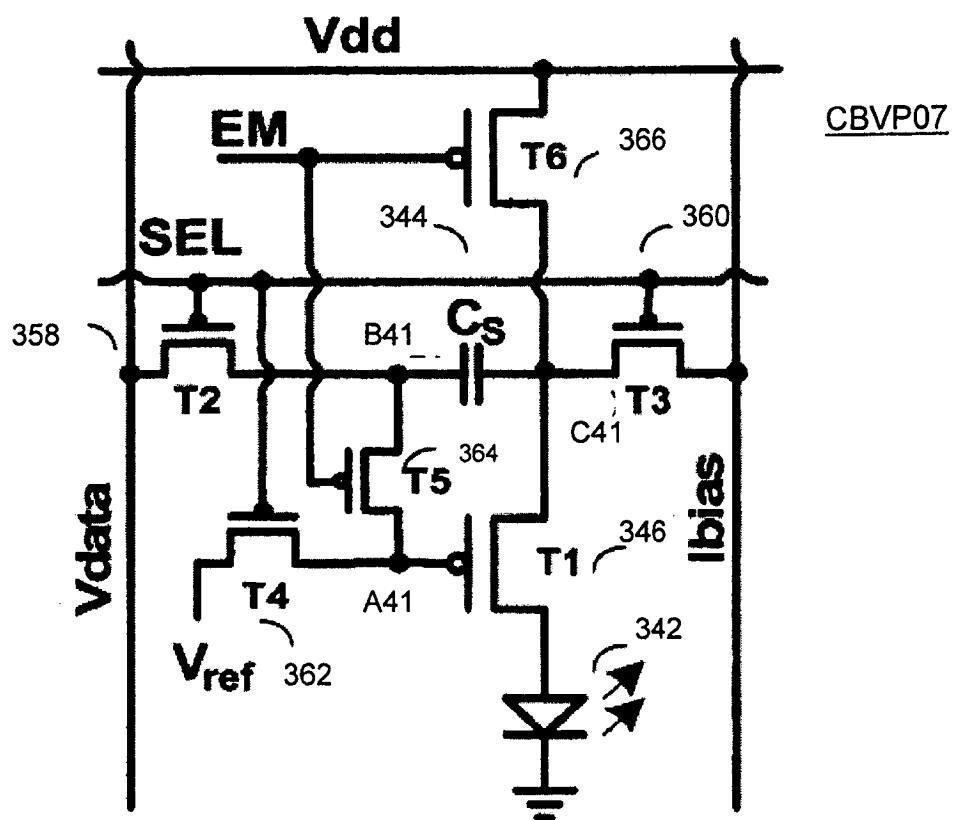

[0140] 图 15A 的像素电路 CBVP07 包括 OLED 342、存储电容器 344 以及晶体管 346、358、360、362、364 和 366。晶体管 346、358、360、362、364 和 366 是 p 型 TFT 晶体管。本领域技术人员将理解与图 15A 的像素电路互补并且具有 n 型晶体管的电路。本领域技术人员将理解, 应用于图 15A 的驱动技术可以应用于该互补的像素电路。一条选择线 SEL、信号线 Vdata、偏置线 Ibias、电压供应线 Vdd、参考电压线 Vref 和发射信号线 EM 与像素电路 CBVP07 连接。偏置线 Ibias 提供基于显示器规格 (诸如寿命、功率以及器件性能和均匀性) 限定的偏置电流 (Ibias)。参考电压线 Vref 提供参考电压 (Vref)。可以基于偏置电流 Ibias 和可以包括灰度级和 / 或对比度的显示器规格来确定参考电压 Vref。信号线 EM 提供使像素电路 CBVP07 导通的发射信号 EM。像素电路 CBVP07 基于发射信号 EM 而变为发射模式。选择线 SEL 与晶体管 358、360 和 362 的栅极端子连接。选择线 EM 与晶体管 364 和 366 的栅极端子连接。晶体管 346 是驱动晶体管。晶体管 358、360、362、364 和 366 是开关晶体管。

[0141] 晶体管 362 的第一端子和第二端子中的一个端子与参考电压线 Vref 连接, 而另一个端子在节点 A41 处与晶体管 346 的栅极端子连接。晶体管 364 的第一端子和第二端子中的一个端子与 A41 连接, 而另一个端子在 B41 处与电容器 344 连接。晶体管 358 的第一端子和第二端子中的一个端子与 Vdata 连接, 而另一个端子与 B41 连接。晶体管 366 的第一端子和第二端子中的一个端子与 Vdd 连接, 而另一个端子在 C41 处与电容器 344 和晶体管 346 连接。晶体管 360 的第一端子和第二端子中的一个端子与 Ibias 连接, 而另一个端子在 C41 处与电容器 344 和晶体管 346 连接。晶体管 346 的第一端子和第二端子中的一个端子与 OLED 342 连接, 而另一个端子在 C41 处与电容器 344 以及晶体管 366 和 360 连接。

[0142] 在像素电路 CBVP07 中, 通过晶体管 360 提供预定的固定电流 (Ibias), 而将参考电压 Vref 通过晶体管 362 而施加于晶体管 346 的栅极端子, 并且将编程电压 VP 通过晶体管 358 而施加于存储电容器 344 的另一个端子 (即, 节点 B41)。这里, 晶体管 346 的源极电压 (即, 节点 C41 的电压) 将被自调节以使得偏置电流能够通过晶体管 346, 因而它补偿所有的空间和时间不均匀性。此外, 电压编程用来将电流划分成不同的灰度级所需的不同的电流电平。

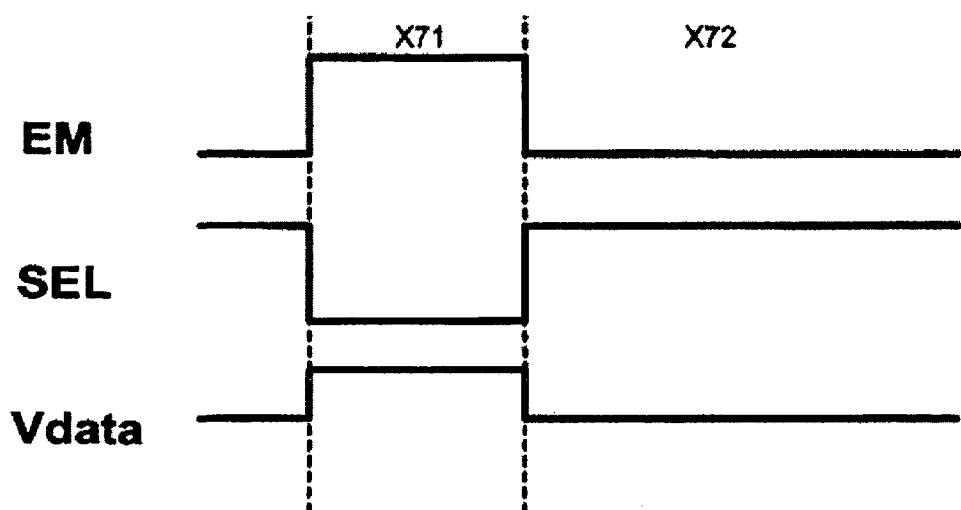

[0143] 参考图 15B, 示出了应用于图 15A 的像素电路 CBVP07 的一个示例性的操作过程。操作过程包括编程阶段 X71 和驱动阶段 X72。在编程周期 X71 期间, SEL 为低以使得晶体管 358、360 和 362 导通, 将固定偏置电流施加于 Ibias 线, 并且晶体管 346 的源极被自调节以使得所有电流能够经过晶体管 346 的源极 - 漏极。在此周期处, Vdata 具有与像素的灰度级有关的编程电压, 并且电容器 344 存储编程电压和由用于失配补偿的电流产生的电压。在驱动周期 X72 期间, 晶体管 358、360 和 362 截止, 而晶体管 364 和 366 由发射信号 EM 导通。在此驱动周期 X72 期间, 晶体管 346 为 OLED 342 提供电流。

[0144] 在图 14B 中, 整个显示器被编程, 然后它被点亮 (变为发射模式)。相反, 在图 15B 中, 通过使用发射线 EM, 每一行可以在编程之后点亮。

[0145] 在图 8-15 的上述示例中,每个像素的电容器可以充当图 1 的驱动电容器 14 和存储电容器。在上述示例中,图 1 的电容性电流源 10 用来向偏置电流线提供恒定电流。在另一个示例中,电容性电流源 10 可以在显示器的操作期间调节偏置电流。

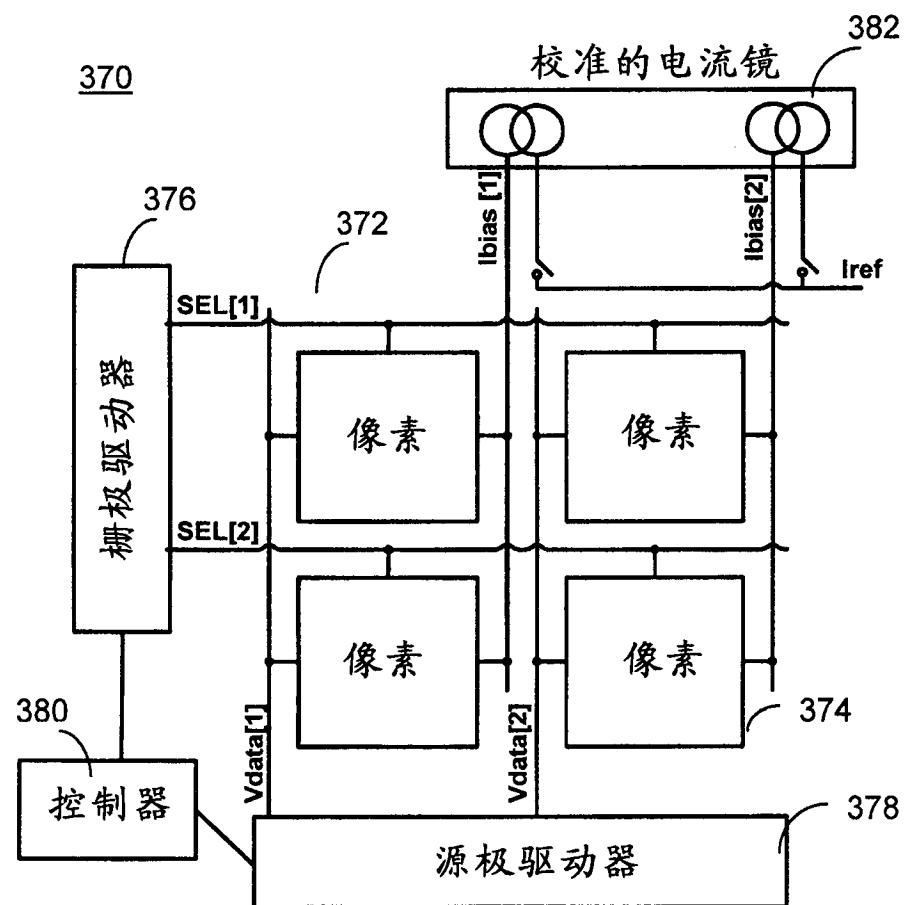

[0146] 参考图 16,示出了具有用于实现 CBVP 驱动方案的阵列结构的显示器系统的另一个示例。图 16 的显示器系统 370 包括具有多个像素 374 的像素阵列 372、栅极驱动器 376、源极驱动器 378 和控制器 380。设置控制器 380 以控制和调度显示阵列 372 的编程、校准、驱动及其它操作,其包括如上所述的 CBVP 驱动方案和电容性的驱动。控制器 380 控制驱动器 376 和 378。像素电路 374 是电流偏置的电压编程的像素(例如,图 8-15 的像素),其中  $SEL[i]$  ( $i = 1, 2, \dots$ ) 是选择(地址)线(例如,  $SEL$ ),  $Vdata[j]$  ( $j = 1, 2, \dots$ ) 是信号(数据)线(例如,  $Vdata$ 、 $VDATA$ ),以及  $Ibias[j]$  ( $j = 1, 2, \dots$ ) 是偏置线(例如,  $Ibias$ 、 $IBIAS$ )。栅极驱动器 376 对地址(选择)线(例如,  $SEL[1], SEL[2], \dots$ ) 进行操作。源极驱动器 378 对数据线(例如,  $Vdata[1], Vdata[2], \dots$ ) 进行操作。当使用图 15A 的像素电路 CBVP07 作为像素电路 374 时,显示器的外围处的驱动器(诸如栅极驱动器 376) 控制每一发射线  $EM$ 。

[0147] 显示器系统 370 包括用于使用参考电流  $Iref$  对偏置线(例如,  $Ibias[1], Ibias[2]$ ) 进行操作的校准的电流镜块 382。块 382 包括多个校准的电流镜,每个校准的电流镜用于相应的  $Ibias$ 。可以通过开关向校准的电流镜块 382 提供参考电流  $Iref$ 。

[0148] 在图 16 中,利用参考电流源校准电流镜。在面板的编程周期(例如,图 14B 的  $X61$ 、图 15B 的  $X71$ ) 期间,校准的电流镜(块 382) 向偏置线  $Ibias$  提供电流。可以将这些电流镜制造在面板的边缘。图 1 的电容性的驱动器 10 可以产生图 16 中的参考电流  $Iref$ 。

[0149] 通过存储在存储电容器中的电压并且将它施加于驱动晶体管的栅极来补偿像素元件的特性的漂移(例如,在长时间的显示操作下发光器件的退化和驱动晶体管的阈值电压漂移)。因而,像素电路可以提供通过发光器件的稳定的电流而没有任何漂移效应,这改善了显示器工作寿命。此外,由于电路简单,因此它确保了比传统的像素电路更高的产品产量、更低的制造成本和更高的分辨率。由于如上所述的像素电路的建立时间比传统的像素电路小得多,因此它适合于诸如高清晰度电视之类的大面积的显示器,但是它也不排除较小的显示器面积。

[0150] 参考图 17-19,示出了 VBCP 像素电路的示例,其可以形成图 2-5 的像素阵列。VBCP 像素、它们的显示器系统和操作的示例在美国专利申请公开 US2006/0125408 和 PCT 国际申请公开 WO2009/127065 中公开,通过参考将这两个申请公开并入于此。

[0151] 在 VBCP 驱动方案中,将像素电流按比例缩小而不用调整镜晶体管的尺寸。VBCP 驱动方案使用电流来提供不同的灰度级(电流编程),并且使用偏置来加速编程并补偿像素的时间相关的参数(诸如阈值电压漂移)。驱动晶体管的端子之一与虚拟地  $VGND$  连接。通过改变虚拟地的电压,像素电流改变。在驱动器侧将偏置电流  $IB$  增加到编程电流  $IP$ ,然后通过改变虚拟地的电压来从像素电路内的编程电流中去掉偏置电流。用于驱动具有 VBCP 像素电路的显示阵列的驱动器将像素亮度数据转换成电流。

[0152] 电容性的驱动技术可应用于 VBCP 显示器以进一步改善适于较大和较高分辨率的显示器的建立时间。在图 17-19 中,数据线  $IDATA$  向相应的像素提供编程电流  $IP$  和偏置电流  $IB$ ,其中使用例如图 1 的电容性的驱动器 10 来提供偏置电流  $IB$ 。

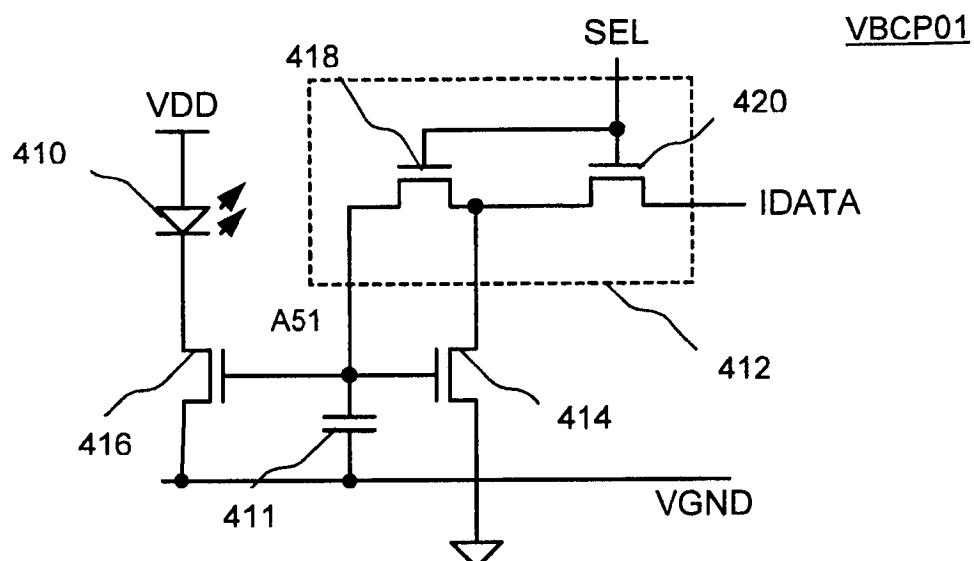

[0153] 图 17A 的像素电路 VBCP01 包括 OLED 410、存储电容器 411、开关网络 412 以及镜晶体管 414 和 416。镜晶体管 414 和 416 形成电流镜，其中晶体管 414 是编程晶体管，晶体管 416 是驱动晶体管。开关网络 412 包括开关晶体管 418 和 420。晶体管 414、416、418 和 420 是 n 型 TFT 晶体管。本领域技术人员将理解与像素电路 VBCP01 互补并且具有 p 型晶体管的电路。选择线 SEL、信号线 IDATA、虚拟地线 VGND、电压供应线 VDD 以及公共地与像素电路 VBCP01 连接。

[0154] 晶体管 416 的第一端子和第二端子中的一个端子与 OLED 410 的阴极电极连接，而另一个端子与 VGND 连接。晶体管 414 的栅极端子、晶体管 416 的栅极端子和存储电容器 411 在节点 A51 处连接。开关晶体管 418 和 420 的栅极端子与 SEL 连接。开关晶体管 418 的第一端子和第二端子中的一个端子在 A51 处与晶体管 416 的栅极端子连接，而另一个端子与晶体管 414 连接。开关晶体管 420 的第一端子和第二端子中的一个端子与 IDATA 连接，而另一个端子与晶体管 414 连接。

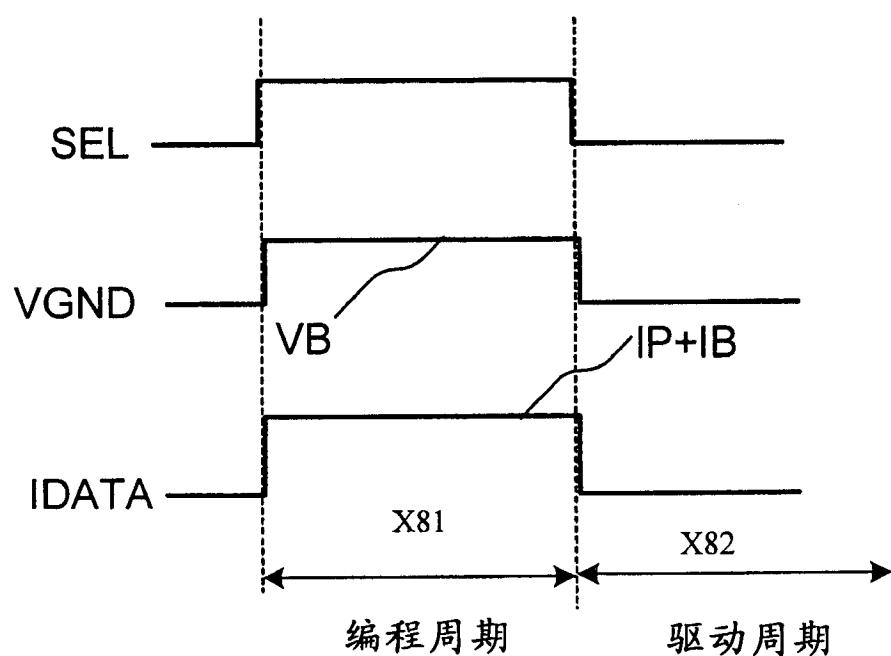

[0155] 参考图 17B，示出了图 17A 的像素电路 VBCP01 的示例性的操作。参考图 17A 和图 17B，详细描述应用于像素电路 VBCP01 的电流缩放技术。像素电路 VBCP01 的操作具有编程周期 X81 和驱动周期 X82。

[0156] 编程周期 X81 :SEL 为高。因而，开关晶体管 418 和 420 导通。VGND 变为偏置电压 VB。通过 IDATA 提供电流 (IB+IP)，其中 IP 表示编程电流，IB 表示偏置电流。等于 (IB+IP) 的电流经过开关晶体管 418 和 420。

[0157] 驱动晶体管 416 的栅 - 源电压被自调节为：

$$[0158] VGS = \sqrt{\frac{IP + IB}{\beta}} + VT \quad (9)$$

[0159] 其中 VT 表示驱动晶体管 416 的阈值电压，并且  $\beta$  表示由  $IDS = \beta(VGS - VT)^2$  给出的 TFT 的电流 - 电压 (I-V) 特性中的系数。IDS 表示驱动晶体管 416 的漏 - 源电流。

[0160] 存储在存储电容器 411 中的电压为：

$$[0161] VCS = \sqrt{\frac{IP + IB}{\beta}} - VB + VT \quad (10)$$

[0162] 其中 VCS 表示存储在存储电容器 411 中的电压。

[0163] 由于驱动晶体管 416 的一个端子与 VGND 连接，因此在编程时间期间流过 OLED 410 的电流为：

$$[0164] Ipixel = IP + IB + \beta \cdot (VB)^2 - 2\sqrt{\beta} \cdot VB \cdot \sqrt{IP + IB} \quad (11)$$

[0165] 其中 Ipixel 表示流过 OLED 410 的像素电流。

[0166] 如果  $IB \gg IP$ ，则像素电流 Ipixel 可以被写为：

$$[0167] Ipixel = IP + (IB + \beta \cdot (VB)^2 - 2\sqrt{\beta} \cdot VB \cdot \sqrt{IB}) \quad (12)$$

[0168] 如下适当地选择 VB：

$$[0169] \quad VB = \sqrt{\frac{IB}{\beta}} \quad (13)$$

[0170] 像素电流  $I_{pixel}$  变成等于编程电流  $IP$ 。因此,它避免在编程周期期间的不必要的发射。由于不需要调整尺寸,因此可以实现电流镜像素电路中的两个镜晶体管之间的更好的匹配。

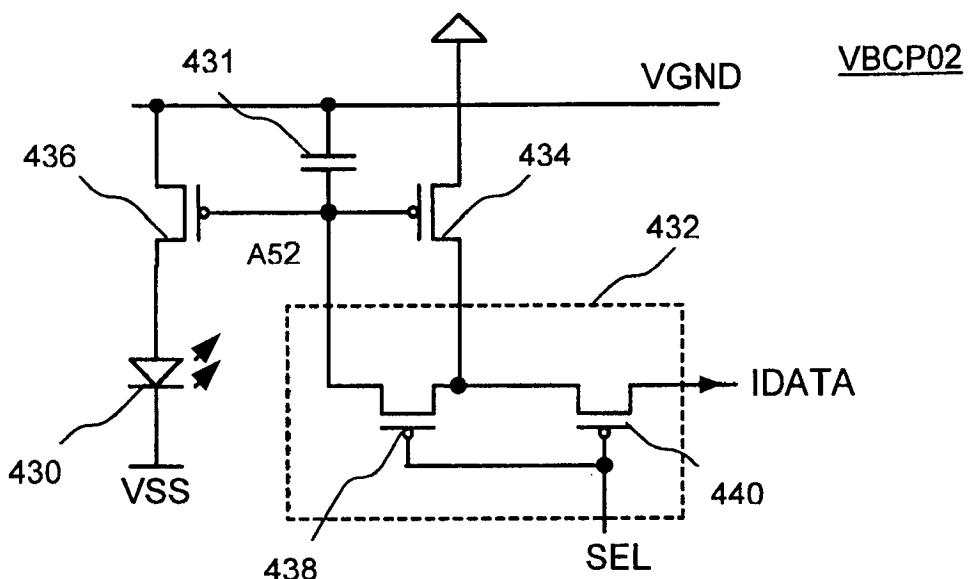

[0171] 图 18A 的像素电路 VBCP02 与图 17A 的像素电路 VBCP01 互补并且具有 p 型晶体管。像素电路 VBCP02 使用如图 18B 所示的 VBCP 驱动方案。像素电路 VBCP02 包括 OLED 430、存储电容器 431、开关网络 432 以及镜晶体管 434 和 436。镜晶体管 434 和 436 形成电流镜,其中晶体管 434 是编程晶体管,晶体管 436 是驱动晶体管。开关网络 432 包括开关晶体管 438 和 440。晶体管 434、436、438 和 440 是 p 型 TFT 晶体管。向像素电路 VBCP02 提供选择线 SEL、信号线 IDATA、虚拟地线 VGND 和电压供应线 VSS。

[0172] 晶体管 436 的第一端子和第二端子中的一个端子与 VGND 连接,而另一个端子与 OLED 430 的阴极电极连接。晶体管 434 的栅极端子、晶体管 436 的栅极端子、存储电容器 431 和开关网络 432 在节点 A52 处连接。

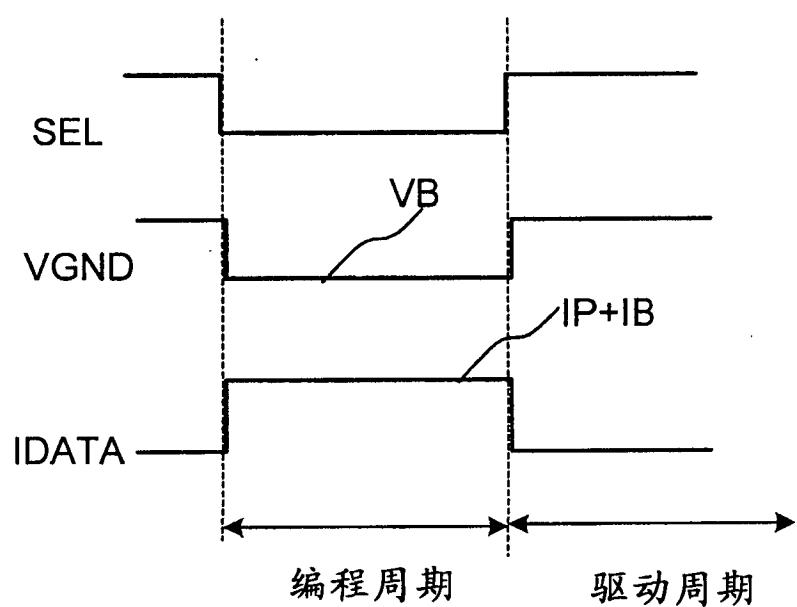

[0173] 参考图 18B,示出了图 18A 的像素电路 VBCP02 的示例性的操作。图 18B 与图 17B 对应。图 18B 的 VBCP 驱动方案使用与图 17B 类似的 IDATA 和 VGND。

[0174] 应用于图 17A 和图 18A 的像素电路 VBCP01 和 VBCP02 的 VBCP 技术可应用于除了电流镜型像素电路之外的其它电流编程的像素电路。

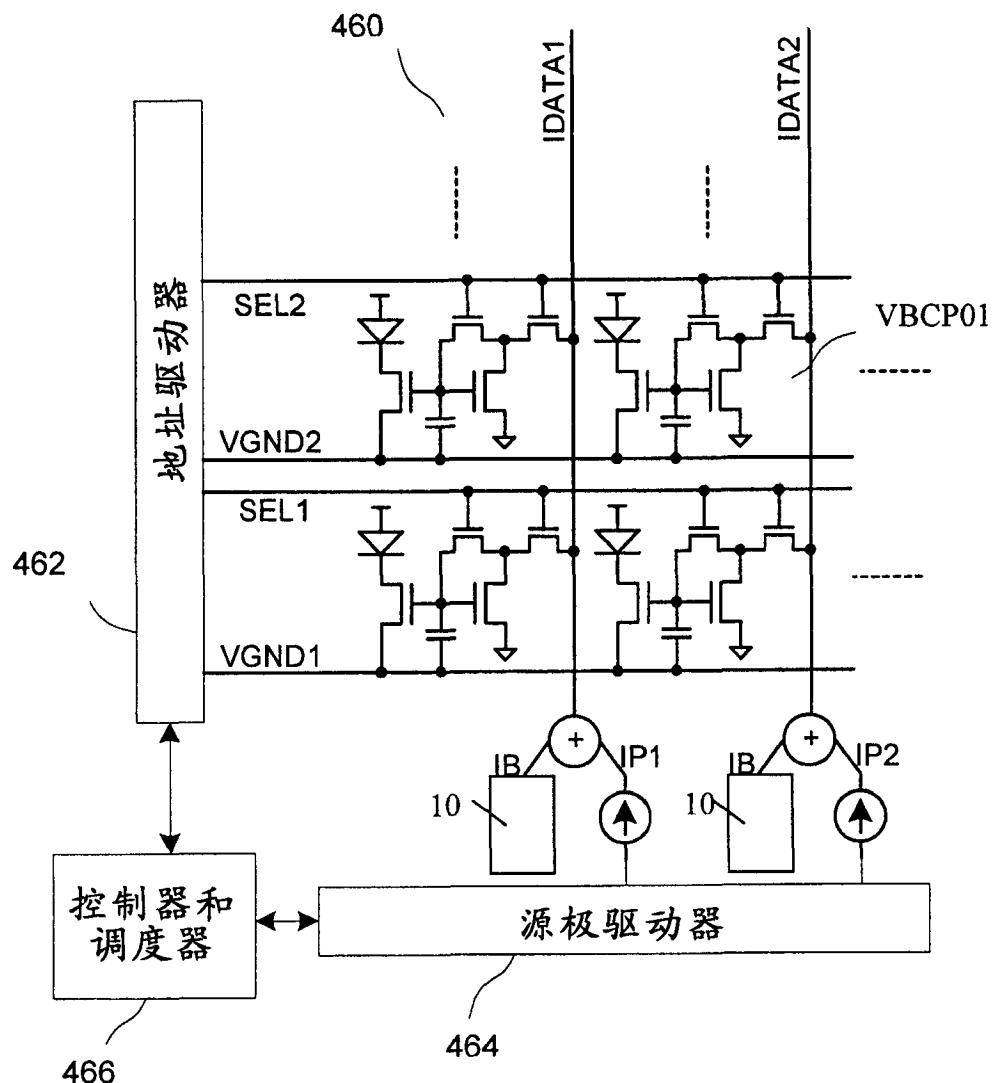

[0175] 参考图 19,示出了具有多个 VBCP 像素电路的显示器系统。图 19 的显示阵列 460 包括图 17A 的像素电路 VBCP01。显示阵列 460 可以包括可应用所述 VBCP 驱动方案的任何其它像素电路。在图 19 中,示出了四个 VBCP 像素电路;但是,显示阵列 460 可以具有多于四个或小于四个 VBCP 像素电路。图 19 所示的“SEL1”和“SEL2”与图 17A 的 SEL 对应。图 19 所示的“VGND1”和“VGND2”与图 17A 的 VGND 对应。图 19 所示的“IDATA1”和“IDATA2”与图 17A 的 IDATA 对应。

[0176] 在阵列结构中, IDATA1 (或 IDATA2) 在同一列的像素之间共用,而 SEL1 (或 SEL2) 和 VGND1 (或 VGND2) 在同一行的像素之间共用。通过地址驱动器 462 驱动 SEL1、SEL2、VGND1 和 VGND2。通过源极驱动器 464 驱动 IDATA1 和 IDATA2。设置控制器和调度器 (scheduler) 466 以用于控制和调度编程、校准、驱动及用于操作显示阵列的其它操作,其包括对如上所述的 VBCP 驱动方案和电容性驱动的控制和调度。

[0177] 详细描述开发高分辨率、稳定、低功率的发射型显示器的进一步的技术。在下面图 20A-20B 和图 21A-21B 的示例中,图 1 的电容性电流源 10 用在像素的驱动周期中。

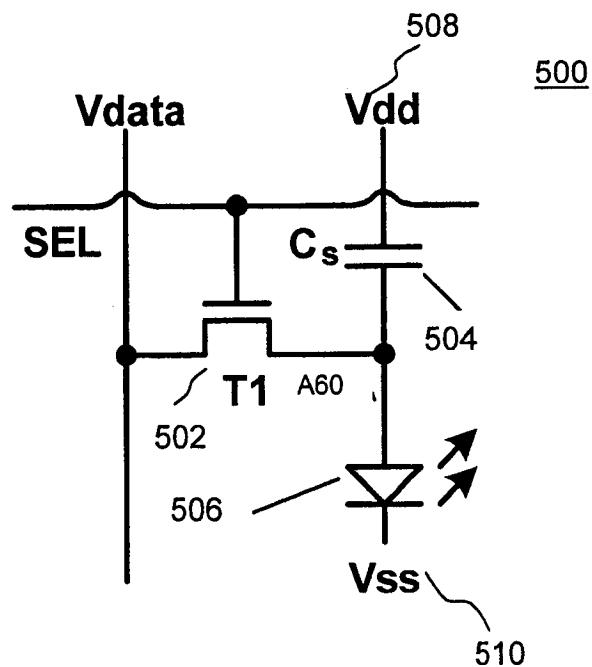

[0178] 参考图 20A,示出了可以在帧时间期间提供恒定电流的像素电路的一个示例。图 20A 的像素电路 500 包括单个开关晶体管 (T1) 502、存储电容器 504 和 OLED 506。电容器 504 与电源 Vdd 508 耦接。OLED 506 与另一个电源 Vss 510 耦接。开关晶体管 502 的栅极端子与地址线 SEL 耦接。开关晶体管 502 的第一端子和第二端子中的一个端子与数据线 Vdata 耦接,而另一个端子在节点 A60 处与电容器 504 和 OLED 506 耦接。

[0179] 参考图 20B,示出了可以在帧时间期间提供恒定电流的像素电路的另一个示例。图 20B 的像素电路 520 包括开关晶体管 (T1) 522、存储电容器 524 和 OLED 526。电容器 524 与

电源  $V_{dd}$  528 耦接。OLED526 与另一个电源  $V_{ss}$  530 耦接。开关晶体管 522 的栅极端子与地址线 SEL 耦接。开关晶体管 522 的第一端子和第二端子中的一个端子与数据线  $V_{data}$  耦接, 而另一个端子在节点 A61 处与电容器 524 和 OLED 526 耦接。

[0180] 参考图 21A, 示出了应用于图 20A-20B 的像素电路的波形的一个示例。图 21A 中的  $SEL[i]$  ( $i = 0, \dots, n$ ) 表示用于第  $i$  行的地址线并且与图 20A-20B 的 SEL 对应; 图 21A 中的  $V_{data}[j]$  ( $j = 0, \dots, m$ ) 表示用于第  $j$  列的数据线并且与图 20A-20B 的  $V_{data}$  对应; 图 21A 中的  $V_{dd}$  与图 20A-20B 的  $V_{dd}$  对应; 图 21A 中的  $V_{ss}$  与图 20A-20B 的  $V_{ss}$  对应。图 21A 的帧时间被分成编程周期 540 和驱动周期 542。在编程周期 540 期间, 由地址线  $SEL[i]$  连续地选择行, 并且利用编程数据  $V_{data}[0]-V_{data}[m]$  对选择的行中的像素进行编程。在编程周期 540 期间, 电容器和 OLED 之间的连接节点 (例如, A60、A61) 通过  $V_{data}$  (其充当图 1 的  $I_{out}$ ) 被充电到编程电压 ( $V_p$ )。

[0181] 在驱动周期 542 期间, 通过将例如来自于图 1 的斜坡电压发生器 12 的斜坡电压施加到  $V_{dd}$  而增大电源  $V_{dd}$ 。恒定电流经由电容器 (504、524) 流动。结果, 连接节点 (例如, A60、A61) 开始充电, 直到 OLED 导通。然后, 等于  $C_s V_R / \tau$  的电压经过 OLED, 其中“ $V_R$ ”是斜坡电压, “ $\tau$ ”是斜坡时间, 以及“ $C_s$ ”表示电容器 (504、524) 的电容。

[0182] 参考图 21B, 示出了应用于图 20A-20B 的像素电路的波形的另一个示例。图 21B 中的  $SEL[i]$  ( $i = 0, \dots, n$ ) 表示用于第  $i$  行的地址线并且与图 20A-20B 的 SEL 对应; 图 21B 中的  $V_{data}[j]$  ( $j = 0, \dots, m$ ) 表示用于第  $j$  列的数据线并且与图 20A-20B 的  $V_{data}$  对应; 图 21B 中的  $V_{dd}$  与图 20A-20B 的  $V_{dd}$  对应; 图 21B 中的  $V_{ss}$  与图 20A-20B 的  $V_{ss}$  对应。图 21B 的帧时间被分成编程周期 550 和驱动周期 552。在编程周期 550 期间, 由地址线  $SEL[i]$  连续地选择行, 并且利用编程数据  $V_{data}[0]-V_{data}[m]$  对选择的行中的像素进行编程。在编程周期 550 期间, 电容器和 OLED 之间的连接节点 (例如, A60、A61) 通过  $V_{data}$  (其充当图 1 的  $I_{out}$ ) 被充电到编程电压 ( $V_p$ )。

[0183] 在驱动周期 552 期间, 通过将例如来自于图 1 的斜坡电压发生器 12 的斜坡电压施加到  $V_{ss}$  而减小电源  $V_{ss}$ 。恒定电流经由电容器 (524、502) 流动。结果, 连接节点 (例如, A60、A61) 开始放电, 直到 OLED 导通。然后, 等于  $C_s V_R / \tau$  的电压经过 OLED。

[0184] 如图 20A、图 20B、图 21A 和图 21B 所示, 此技术不需要任何比 AMLCD 显示器中使用的更多的驱动周期或驱动电路, 结果得到显示器的更短的驱动时间、更低的功耗、高的开口率和稳定性, 因而得到对于包括移动装置和 PDA 的便携式设备的更低成本应用。

[0185] 参考图 22, 存在示出图 20A-20B 的像素电路在一个子帧中对于不同的编程电压的模拟结果 (OLED 电流) 的图。在图 22 中, “ $V_p$ ”表示编程电压。如图 22 所示, 随着编程电压 ( $V_p$ ) 改变, 按时间调制像素电流。

[0186] 参考图 23, 存在示出图 20A-20B 的像素电路的模拟结果 (平均 OLED 电流) 的图。图 23 中的图示出像素的 I-V 特性。如图 23 所示, 像素电流明显由编程电压 ( $V_p$ ) 控制。

[0187] 参考图 24, 存在示出 2.2 英寸四分之一视频图形阵列 (QVGA) 面板的功耗和用于 OLED 的功耗的图。如图 24 所示, 整个面板的功耗非常接近于 OLED 的功耗。特别地, 由于整个电容电压去往 OLED (图 20A-20B 的 506、536), 因此在高电流电平处, 功耗接近于 OLED 的功耗。这里, 绝热的电荷共享也可以被用于例如通过共享两个相邻的行之间的电荷来改善驱动器侧的功耗。

[0188] 参考图 25,示出了用于驱动底部发射显示器的大的电容器的实施方式的示例。图 25 所示的电容器 600 是交指型电容器并且可用作图 1 的驱动电容器 10 和 / 或像素电路的存储电容器。图 20A-20B 的电容器 504 和 524 可以是交指型电容器 600。交指型电容器 600 包括金属 I 层 602 和金属 II 层 604。OLED 器件 610 被形成在交指型电容器 600 上,该 OLED 器件 610 至少具有透明的底部电极 612 和 OLED 层 614。OLED 层 614 位于底部电极 612 上。金属 I 层 602 经由互连线 616 与 OLED 底部电极 612 耦接。金属 I 层 602 和金属 II 层 604 位于底部电极 612 之下,而不遮盖来自于 OLED 614 的光。在图 25 中, OLED 层 614 被放置在底部电极 612 的一侧,而金属层 602 和 604 被放置在底部电极 612 的另一侧之下。这可以得到大的电容器而不牺牲开口率。

[0189] 参考图 26,示出了对于 180-ppi 的显示器分辨率的具有 25% 以上的开口率的底部发射像素的布局的示例。在图 26 中,已经使用多个层来产生用于图 20A 所示的像素电路的大的电容。这里,电容器从三个层当中产生:金属 II 634 夹在 ITO 638 和金属 I 640 之间。金属层 634 和 640 形成图 20A 的电容器 504。金属 I 层 640 可以与图 25 的 602 对应;金属 II 层 634 与图 25 的 604 对应。数据线 632 用来利用电压对像素进行编程。OLED 堤(bank)636 是使得 OLED 能够接触图案化的 OLED 电极的开口。选择线 642 用来使用于提供对用于编程的像素的访问的选择晶体管导通。

[0190] 参考图 27,示出了用于驱动顶部发射显示器的大的电容器的实施方式的示例。图 27 所示的电容器 650 是交指型电容器并且可用作图 1 的驱动电容器 10 和 / 或像素电路的存储电容器。图 20A-20B 的电容器 504 和 524 可以是交指型电容器 650。交指型电容器 650 包括金属 I 层 652 和金属 II 层 654。OLED 器件 660 被形成在交指型电容器 650 上,其至少具有底部电极 662 和 OLED 层 664。OLED 层 664 位于底部电极 662 上。金属 I 电极层 652 经由互连线 566 与 OLED 底部电极 662 耦接。这可以得到大的电容器而不牺牲显示器分辨率。

[0191] 详细描述基于电容性驱动的数模转换器 (DAC)。参考图 28-29,示出了基于电容性驱动的 DAC 和它的操作的一个示例。图 28 的 DAC700 包括转换器块 702 和复制器块 704。转换器块 702 包括多个晶体管和多个电容器。在图 28 中,开关晶体管 710、712、714 和 716 以及电容器 720、722、724 和 726 被示出为转换器块 702 的组件的一个示例。晶体管和电容器串联耦接在 Vramp 节点 730 与节点 732 之间。电容器 720、722、724 和 726 的大小不同。Vramp 节点 730 可以与例如图 1 的斜坡电压发生器 12 耦接。转换器块 702 产生电流。

[0192] 复制器块 704 在节点 732 处与转换器块 702 耦接,并且包括晶体管 740、742 和 744 以及电容器 746。晶体管 740 复制由转换器块 702 产生的电流。晶体管 742 经由 Iout 750 向包括像素电路的任何外部电路施加电流。

[0193] 在转换器块 702 中产生电流期间,晶体管 710、712、714 和 716 基于相应的比特值 b3 到 b0( $b<3:0>$ ) 而导通或截止。结果,斜坡电压 Vramp 施加于与导通开关(晶体管)连接的电容器。由于电容器大小不同,因此每个电容器将产生以数字度量的、表示它的相应比特的值的电流。例如,如果  $b<3:0>$  为“1010”,则两个电容器(例如,图 28 的 720 和 724)将与斜坡电压(730)连接。结果,将产生等于  $8C * S + 2C * S$  的电流,其中 C 是单位电容器(unit capacitor),S 是斜坡的斜率。电容器将斜坡转换为电流。电流的总和将去往晶体管 740,晶体管 740 在晶体管 744 导通时复制它们。

[0194] 在图 28 的示例中,经由复制器块 704 提供由转换器块 702 产生的电流。但是,在另一个示例中,转换器块 702 可以直接与包括像素电路的外部电路连接。

[0195] 参考图 30-31,示出了基于电容性驱动的 DAC 和它的操作的另一个示例。图 30 的 DAC 800 包括转换器块 802 和复制器块 804。转换器块 802 包括多个电容器,每个电容器与开关晶体管耦接。在图 30 中,电容器 820、822、824 和 826 被示出为转换器块 802 的组件的一个示例,并且开关晶体管 810、812、814 和 816 分别与电容器 820、822、824 和 826 耦接。晶体管 810、812、814 和 816 与 Vramp 节点 830、832、834 和 836 耦接,以分别接收 Vramp1、Vramp2、Vramp3 和 Vramp4。电容器 820、822、824 和 826 可以具有相同的大小。Vramp 节点 830、832、834 和 836 中的每一个可以与例如图 1 的斜坡电压发生器 12 耦接。Vramp 节点 830、832、834 和 836 上的斜坡电压 Vramp1、Vramp2、Vramp3、Vramp4 彼此不同。转换器块 802 产生电流。

[0196] 复制器块 804 在节点 838 处与转换器块 802 耦接,并且包括晶体管 840、842 和 844 以及电容器 846。晶体管 840 复制由转换器块 802 产生的电流。晶体管 842 经由 Iout 850 向包括像素电路的任何外部电路施加电流。复制器块 804 与图 28 的复制器块 704 对应。

[0197] 在图 30 的示例中,改变施加于每个电容器的斜坡斜率来代替改变电容器的尺寸。虽然电路的基本操作与图 28 的相同,但是电流电平由不同的斜坡斜率限定。例如,如果 b<3:0> 为“1010”,则两个电容器(例如,图 30 的 820 和 824)将与斜坡(例如,图 30 的 830 和 834)连接。结果,将产生等于  $C * 8S + C * 2S$  的电流,其中 C 是电容器,S 是斜坡的单位斜率。

[0198] 本发明的以上实施例可以降低与不同的材料系统的背板技术有关的功耗,所述不同的材料系统包括薄膜硅(例如,a-Si、nc-Si、μc-Si、多晶 Si)和相关的 Si 集成电路 CMOS 技术、真空沉积和溶液处理的有机物和聚合体、以及相关的无机/有机纳米复合物、和半导体氧化物(例如,铟氧化物、锌氧化物)。此外,本发明的以上实施例使得能够对于更长寿命要求的应用来使用低成本的驱动方案。此外,它对温度变化和机械应力不敏感。

图 1

图 2

图 3

图 4

图 5

图 6A

图 6B

图 7A

图 7B

图 8A

图 8B

图 8C

图 9A

图 9B

图 9C

图 10A

图 10B

图 11A

图 11B

图 12A

图 12B

图 13A

图 13B

图 14A

图 14B

图 15A

图 15B

图 16

图 17A

图 17B

图 18A

图 18B

图 19

图 20A

图 21A

图 20B

图 21B

图 22

图 23

图 24

图 25

图 27

图 26

图 28

图 29

800

图 30

冬 31

|                |                                                                                                                                                                                                            |         |            |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于发射型显示器的低功率电路和驱动方法                                                                                                                                                                                        |         |            |

| 公开(公告)号        | <a href="#">CN102246220A</a>                                                                                                                                                                               | 公开(公告)日 | 2011-11-16 |

| 申请号            | CN200980148912.0                                                                                                                                                                                           | 申请日     | 2009-12-08 |

| [标]申请(专利权)人(译) | 伊格尼斯创新公司                                                                                                                                                                                                   |         |            |

| 申请(专利权)人(译)    | 伊格尼斯创新公司                                                                                                                                                                                                   |         |            |

| 当前申请(专利权)人(译)  | 伊格尼斯创新公司                                                                                                                                                                                                   |         |            |

| [标]发明人         | GR查基<br>A内森                                                                                                                                                                                                |         |            |

| 发明人            | G· R· 查基<br>A· 内森                                                                                                                                                                                          |         |            |

| IPC分类号         | G09G3/20 G09G3/32 G09G3/3208                                                                                                                                                                               |         |            |

| CPC分类号         | G09G2310/027 G09G2310/066 G09G2310/0259 G09G2330/021 G09G2320/043 G09G2300/0842<br>G09G3/3283 G09G3/3233 G09G2310/0262 G09G3/3291 G09G2300/0852 G09G2320/0233 G09G2330<br>/023 G09G2300/0819 G09G2300/0465 |         |            |

| 代理人(译)         | 欧阳帆                                                                                                                                                                                                        |         |            |

| 优先权            | 2654409 2008-12-19 CA<br>2647112 2008-12-09 CA                                                                                                                                                             |         |            |

| 其他公开文献         | CN102246220B                                                                                                                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                                                                                                                             |         |            |

### 摘要(译)

提供了一种显示器系统、用于驱动该显示阵列的驱动器、操作该显示器系统的方法和该显示器系统中的像素电路。该驱动器包括：双向电流源，具有与时变电压耦接的转换器，该转换器用于将该时变电压转换为电流。该像素电路包括：晶体管，用于向发光器件提供像素电流；和与该晶体管电耦接的存储电容器，该电容器在用于基于时变电压提供电流的预定定时中与该时变电压耦接。该方法包括：在编程操作的第一周期中，将提供给像素电路中的存储电容器的时变电压从参考电压改变为编程电压，该存储电容器与用于驱动发光器件的驱动晶体管电耦接；以及在该编程操作的第二周期中，将该时变电压维持在该编程电压。该方法包括：在编程操作中，从数据线向像素电路提供编程数据，该像素电路包括与该数据线耦接的晶体管以及存储电容器；以及在驱动操作中，经由电源线向该像素电路中的存储电容器提供用于接通发光器件的时变电压。该像素电路包括：有机发光二极管(OLED)器件，具有电极和OLED层；和交指型电容器，具有多个层。

10