[19] 中华人民共和国国家知识产权局

[12] 发明专利申请公开说明书

[21] 申请号 200610006074.1

[51] Int. Cl.

H01L 27/32 (2006.01)

H01L 29/786 (2006.01)

H01L 21/8234 (2006.01)

H01L 21/336 (2006.01)

[43] 公开日 2006 年 9 月 6 日

[11] 公开号 CN 1828927A

[22] 申请日 2006.1.24

[21] 申请号 200610006074.1

[71] 申请人 友达光电股份有限公司

地址 台湾省新竹市

[72] 发明人 林俊仪 陈明炎

[74] 专利代理机构 北京市柳沈律师事务所

代理人 陶凤波 侯宇

权利要求书 4 页 说明书 13 页 附图 11 页

[54] 发明名称

有机发光二极管显示面板及其多晶硅通道层的形成方法

[57] 摘要

本发明涉及一种多晶硅通道层及其形成方法。首先，提供一基板，基板之上具有一多晶硅层。接着，掺杂一非 IIIA 族及非 VA 族的掺杂原子于多晶硅层中，以形成一多晶硅通道层。

1. 一种有机发光二极管显示面板，包括：

基板；

5 像素，设置于该基板之上；以及

第一薄膜晶体管，设置于该像素内，并包含第一多晶硅通道层，该第一多晶硅通道层中掺杂有非IIIA族及非VA族的第一掺杂原子。

2. 如权利要求1所述的面板，其中该第一掺杂原子为电中性原子。

3. 如权利要求2所述的面板，其中该第一掺杂原子包含惰性气体及/或

10 IVA族。

4. 如权利要求3所述的面板，其中该第一掺杂原子选自于氦、氖、氩、氪、氙及氡所组成的族群中至少一及其任意组合。

5. 如权利要求1所述的面板，其中该第一掺杂原子在该第一多晶硅通道层中的掺杂浓度为 $10^{11} \sim 10^{15}$ 原子个数/平方厘米。

15 6. 如权利要求1所述的面板，其中该第一薄膜晶体管还包括第一栅极、第一源极及第一漏极，该第一源极及该第一漏极对应地与该第一多晶硅通道层的二端电连接，该第一源极与第一固定电压电连接，该有机发光二极管显示面板还包括：

第一扫描线及第二扫描线，相互平行地设置于该基板之上；

20 第一数据线及第二数据线，相互平行地设置于该基板之上，并与该第一扫描线及该第二扫描线相互垂直地交错，而定义该像素；以及

第二薄膜晶体管，设置于该像素内，并包含第二栅极、第二源极、第二漏极及第二多晶硅通道层，该第二源极及该第二漏极对应地与该第二多晶硅通道层的二端电连接，该第二栅极与该第一扫描线电连接，该第二源极与该25 第一数据线电连接，该第二漏极与该第一栅极电连接。

7. 如权利要求6所述的面板，其中该第二多晶硅通道层中掺杂有非IIIA族及非VA族的第二掺杂原子，该第二掺杂原子在该第二多晶硅通道层中的掺杂浓度与该第一掺杂原子在该第一多晶硅通道层中的掺杂浓度相同或不同。

30 8. 如权利要求7所述的面板，其中该第一掺杂原子及该第二掺杂原子为电中性原子。

9. 如权利要求 8 所述的面板，其中该第一掺杂原子及该第二掺杂原子包含惰性气体及/或ⅣA 族。

10. 如权利要求 9 所述的面板，其中该第一掺杂原子及该第二掺杂原子各选自于氦、氖、氩、氪、氙及氡所组成的族群中至少一及其任意组合。

5 11. 如权利要求 7 所述的面板，其中该第一掺杂原子在该第一多晶硅通道层中的掺杂浓度大于该第二掺杂原子在该第二多晶硅通道层中的掺杂浓度。

12. 如权利要求 11 所述的面板，其中该第一掺杂原子在该第一多晶硅通道层中的掺杂浓度为  $10^{11} \sim 10^{15}$  原子个数/平方厘米。

10 13. 如权利要求 6 所述的面板，还包括：

储存电容，设置于该像素内，该储存电容的一端电连接于该第二漏极及该第一栅极之间，该储存电容的另一端电连接于该第一源极及该第一固定电压之间。

14. 如权利要求 6 所述的面板，还包括：

15 有机电激发光元件，设置于该像素内，用以与该第一漏极及第二固定电压电连接。

15. 一种多晶硅通道层的形成方法，包括：

提供基板，该基板之上具有非晶硅层；

热处理该非晶硅层，以形成多晶硅层；以及

20 掺杂非ⅢA 族及非ⅤA 族的掺杂原子于该多晶硅层中，以形成多晶硅通道层。

16. 如权利要求 15 所述的方法，其中该掺杂原子为电中性原子。

17. 如权利要求 16 所述的方法，其中该掺杂原子包含惰性气体及/或ⅣA 族。

25 18. 如权利要求 17 所述的方法，其中该掺杂原子选自于氦、氖、氩、氪、氙及氡所组成的族群中至少一及其任意组合。

19. 如权利要求 15 所述的方法，其中该掺杂原子在该多晶硅通道层中的掺杂浓度为  $10^{11} \sim 10^{15}$  原子个数/平方厘米。

20. 一种多晶硅通道层的形成方法，包括：

30 提供基板，该基板之上具有第一多晶硅层及第二多晶硅层；

以第一光掩模遮住该基板，该第一光掩模具有第一开口暴露该第一多晶

硅层；以及

掺杂非IIIA族及非VA族的第一掺杂原子于该第一多晶硅层中，以形成第一多晶硅通道层。

21. 如权利要求20所述的方法，其中该第一掺杂原子为电中性原子。

5 22. 如权利要求21所述的方法，其中该第一掺杂原子包含惰性气体及/或IV A族。

23. 如权利要求22所述的方法，其中该第一掺杂原子选自于氦、氖、氩、氪、氙及氡所组成的族群中至少一及其任意组合。

10 24. 如权利要求20所述的方法，其中该第一掺杂原子在该第一多晶硅通道层中的掺杂浓度为 $10^{11} \sim 10^{15}$ 原子个数/平方厘米。

25. 如权利要求20所述的方法，还包括：

移除该第一光掩模且以第二光掩模遮住该基板，该第二光掩模具有第二开口暴露该第二多晶硅层；以及

15 掺杂非IIIA族及非VA族的第二掺杂原子于该第二多晶硅层中，以形成第二多晶硅通道层，该第二掺杂原子在该第二多晶硅通道层中的掺杂浓度与该第一掺杂原子在该第一多晶硅通道层中的掺杂浓度相同或不同。

26. 如权利要求25所述的方法，其中该第一掺杂原子该第二掺杂原子为电中性原子。

27. 如权利要求26所述的方法，其中该第一掺杂原子及该第二掺杂原子包含惰性气体及/或IV A族。

28. 如权利要求27所述的方法，其中该第一掺杂原子及该第二掺杂原子各选自于氦、氖、氩、氪、氙及氡所组成的族群中至少一及其任意组合。

29. 如权利要求25所述的方法，其中该第一掺杂原子在该第一多晶硅通道层中的掺杂浓度大于该第二掺杂原子在该第二多晶硅通道层中的掺杂浓度。

30. 如权利要求29所述的方法，其中该第一掺杂原子在该第一多晶硅通道层中的掺杂浓度为 $10^{11} \sim 10^{15}$ 原子个数/平方厘米。

31. 如权利要求20所述的方法，其中该提供该基板的步骤包括：

提供该基板，该基板之上具有非晶硅层；

30 热处理该非晶硅层，以形成多晶硅层；以及

去除部分的该多晶硅层，以形成该第一多晶硅层及该第二多晶硅层。

32. 一种多晶硅通道层的形成方法，包括：

提供基板，该基板之上具有第一多晶硅层及第二多晶硅层；

以第一光掩模遮住该基板，该第一光掩模具有第一开口及第二开口分别暴露该第一多晶硅层及该第二多晶硅层；

5 掺杂非IIIA族及非VA族的第一掺杂原子于该第一多晶硅层及该第二多晶硅层中，以分别形成第一多晶硅通道层及第二多晶硅通道层，该第一掺杂原子在该第一多晶硅通道层中的掺杂浓度与该第一掺杂原子在该第二多晶硅通道层中的掺杂浓度相同；

10 移除该第一光掩模且以第二光掩模遮住该基板，该第二光掩模具有第三开口暴露该第一多晶硅通道层；以及

掺杂第二掺杂原子于该第一多晶硅通道层中，以形成第三多晶硅通道层，该第一掺杂原子及该第二掺杂原子在该第三多晶硅通道层中的总掺杂浓度大于该第一掺杂原子在该第二多晶硅通道层中的掺杂浓度。

15 33. 如权利要求32所述的方法，其中该第一掺杂原子及该第二掺杂原子为电中性原子。

34. 如权利要求33所述的方法，其中该第一掺杂原子及该第二掺杂原子包含惰性气体及/或IVA族。

35. 如权利要求34所述的方法，其中该第一掺杂原子及该第二掺杂原子各选自于氦、氖、氩、氪、氙及氡所组成的族群中至少一及其任意组合。

20 36. 如权利要求32所述的方法，其中该第一掺杂原子及该第二掺杂原子在该第三多晶硅通道层中的总掺杂浓度为 $10^{11} \sim 10^{15}$ 原子个数/平方厘米。

37. 如权利要求32所述的方法，其中该提供该基板的步骤包括：

提供该基板，该基板之上具有非晶硅层；

热处理该非晶硅层，以形成多晶硅层；以及

25 去除部分的该多晶硅层，以形成该第一多晶硅层及该第二多晶硅层。

## 有机发光二极管显示面板及其多晶硅通道层的形成方法

### 5 技术领域

本发明涉及一种有机发光二极管显示面板（organic light emitting diode, OLED）及其多晶硅通道层的形成方法，特别是涉及一种于多晶硅通道层中掺杂有非IIIA族及非VA族的掺杂原子的有机发光二极管显示面板及其多晶硅通道层的形成方法。

10

### 背景技术

在传统低温多晶硅（low temperature polysilicon, LTPS）液晶显示面板（liquid crystal display panel LCD panel）和有机发光二极管（organic light emitting diode, OLED）显示面板的工艺中，业界会使用准分子激光回火（excimer laser annealing, ELA）技术扫描且熔融非晶硅（amorphous silicon, a-Si）层，以结晶成多晶硅层。而这多晶硅层将可以作为薄膜晶体管（thin film transistor, TFT）的通道层，以改善薄膜晶体管的电性表现。

根据相关文献研究指出，影响多晶硅 TFT 电性表现的缺陷类型主要有两种，即晶界陷阱（grain boundary trap）缺陷和界面陷阱（interface trap）缺陷。其中，晶界陷阱缺陷主要来自熔融非晶硅层结晶为多晶硅层的过程中的变异。尤其是使用 ELA 将非晶硅层熔融而结晶为多晶硅层的结晶技术（以下简称为 ELA 结晶技术）时，晶界陷阱缺陷和界面陷阱缺陷的数量约是  $10^{12}$  及  $10^{11}$  的数量级。由其缺陷的数量可知，多晶硅层的沟道质量（channel quality）受晶界陷阱缺陷影响最大。

对 LTPS LCD 而言，虽然透过 ELA 结晶技术所制作的高效能的 TFT 中通道层有上述缺陷的产生，但由于 TFT 只作为像素的开关元件的要求，仍然可达到 LTPS LCD 对于 TFT 性能的标准。

但对 OLED 显示面板而言，其缺陷影响就不容忽略。在 OLED 显示面板的有源像素矩阵中，每一像素的 TFT 以电流驱动的方式驱动一包含阳极、阴极及有机材料层的有机电激光元件（organic electroluminescent device, OELD）。由于透过 ELA 结晶技术所制作的多晶硅层常常会有结晶及缺陷的

不均匀性，导致所有 TFT 的通道层的特性不尽相同。因此，进而造成 OLED 显示面板制作完成点亮后，将会产生明暗不均的条纹现象（以下简称为 line mura）。如此一来，大大地影响 OLED 显示面板的显示质量。

## 5 发明内容

有鉴于此，本发明的目的就是在提供一种有机发光二极管显示面板及其多晶硅通道层的形成方法。其于热处理非晶硅层后所结晶成的多晶硅层（例如以 ELA 结晶技术所形成的多晶硅层）中掺杂非 IIIA 族及非 VA 族的掺杂原子的设计，可以均匀化多晶硅层的缺陷。因此，可以改善多晶硅层结晶及缺陷的不均匀性，使得所有像素 TFT 的多晶硅通道层的特性相同。因此，进而使得所有像素的 TFT 的特性相同，避免有机发光二极管显示面板于运作时产生明暗不均的条纹现象（line mura）。如此一来，大大地提升有机发光二极管显示面板的显示质量。

根据本发明的目的，提出一种有机发光二极管显示面板，包括一基板、一像素及一薄膜晶体管。像素设置于基板之上。薄膜晶体管设置于像素内，并包含一多晶硅通道层。多晶硅通道层中掺杂有一非 IIIA 族及非 VA 族的掺杂原子。

根据本发明的另一目的，提出一种多晶硅通道层的形成方法。首先，提供一基板，基板之上具有一非晶硅层。接着，热处理非晶硅层，以形成一多晶硅层。然后，掺杂一非 IIIA 族及非 VA 族的掺杂原子于多晶硅层中，以形成一多晶硅通道层。

根据本发明的再一目的，提出一种多晶硅通道层的形成方法。首先，提供一基板，基板之上具有一第一多晶硅层及一第二多晶硅层。接着，以一光掩模遮住基板，光掩模具有一开口暴露第一多晶硅层。然后，掺杂一非 IIIA 族及非 VA 族的掺杂原子于第一多晶硅层中，以形成一多晶硅通道层。

根据本发明的又一目的，提出一种多晶硅通道层的形成方法。首先，提供一基板，基板之上具有一第一多晶硅层及一第二多晶硅层。接着，以一第一光掩模遮住基板，第一光掩模具有一第一开口及一第二开口分别暴露第一多晶硅层及第二多晶硅层。然后，掺杂一非 IIIA 族及非 VA 族的第一掺杂原子于第一多晶硅层及第二多晶硅层中，以分别形成一第一多晶硅通道层及一第二多晶硅通道层。第一掺杂原子在第一多晶硅通道层中的掺杂浓度与第一

掺杂原子在第二多晶硅通道层中的掺杂浓度相同。接着，移除第一光掩模且以一第二光掩模遮住基板，第二光掩模具有一第三开口暴露第一多晶硅通道层。然后，掺杂一非IIIA族及非VA族的第二掺杂原子于第一多晶硅通道层中，以形成一第三多晶硅通道层。其中，第一掺杂原子及第二掺杂原子在第5三多晶硅通道层中的总掺杂浓度大于第一掺杂原子在第二多晶硅通道层中的掺杂浓度。

为让本发明的上述目的、特征、和优点能更明显易懂，以下配合附图以及优选实施例，以更详细地说明本发明。

## 10 附图说明

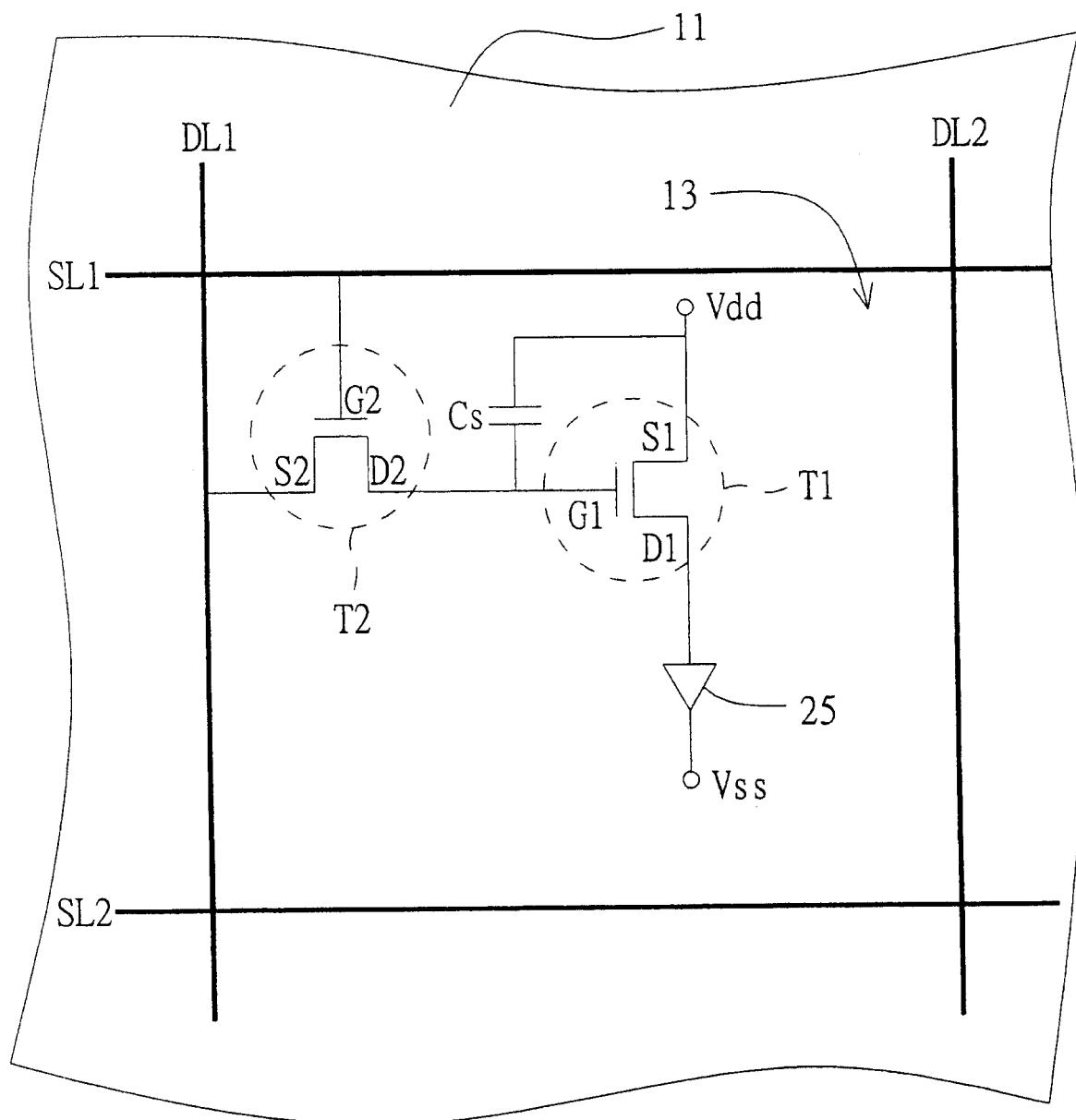

图 1 绘示乃依照本发明的实施例一的有机发光二极管（organic light emitting diode，OLED）显示面板的单一像素中电路架构的示意图；

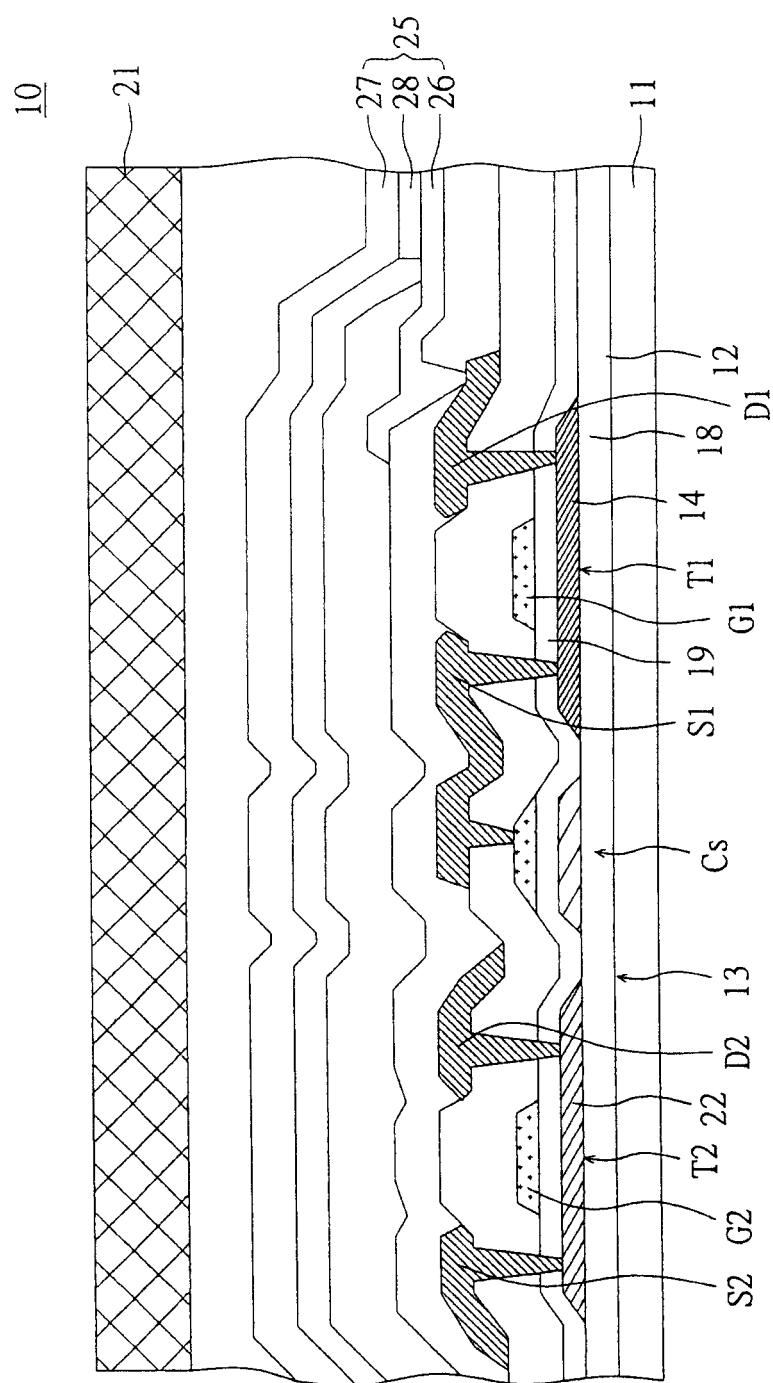

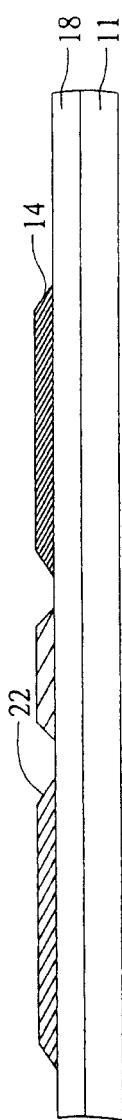

图 2 绘示乃依照本发明的实施例一的有机发光二极管显示面板的单一像素中细部结构的剖面图；

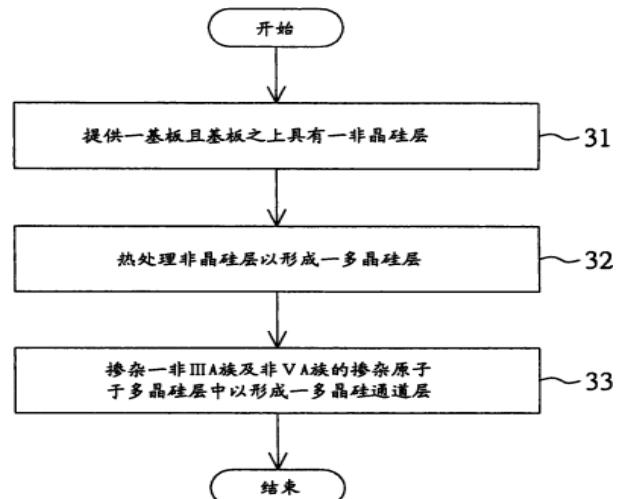

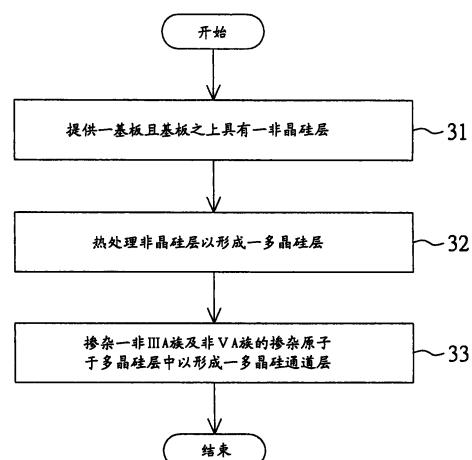

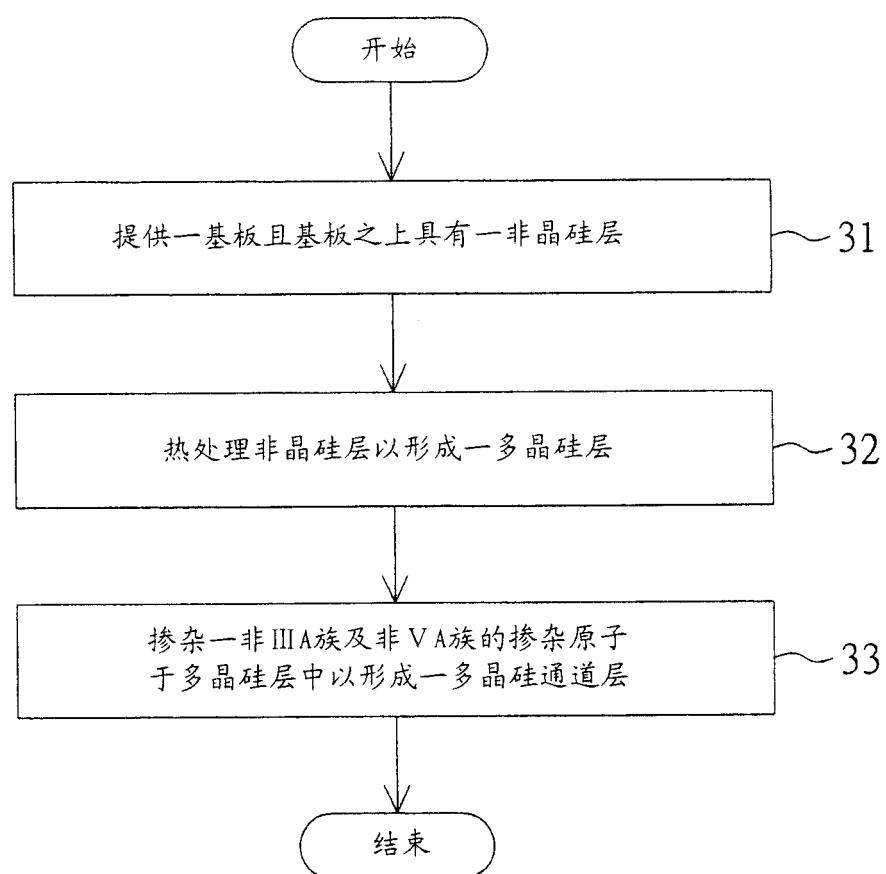

15 图 3 绘示乃依照本发明的实施例二的多晶硅通道层的形成方法的流程图；

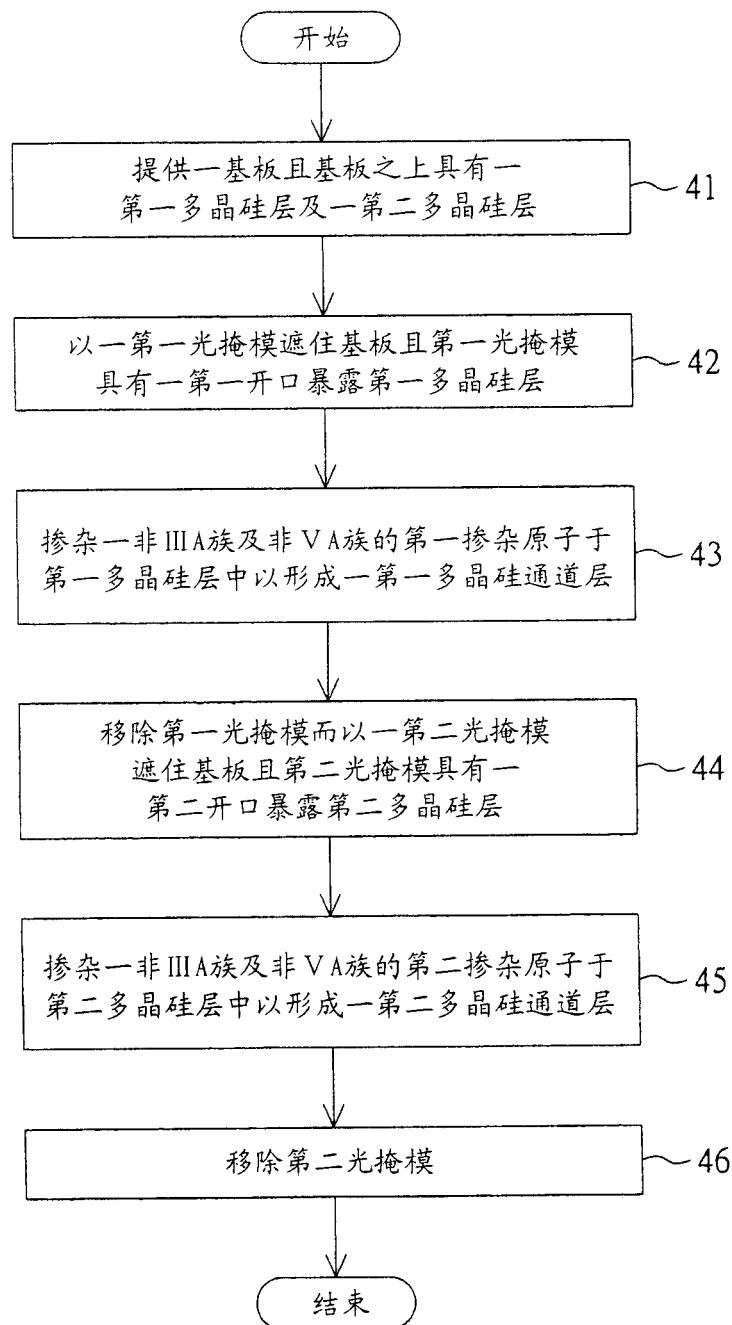

图 4 绘示乃依照本发明的实施例三的多晶硅通道层的形成方法的流程图；

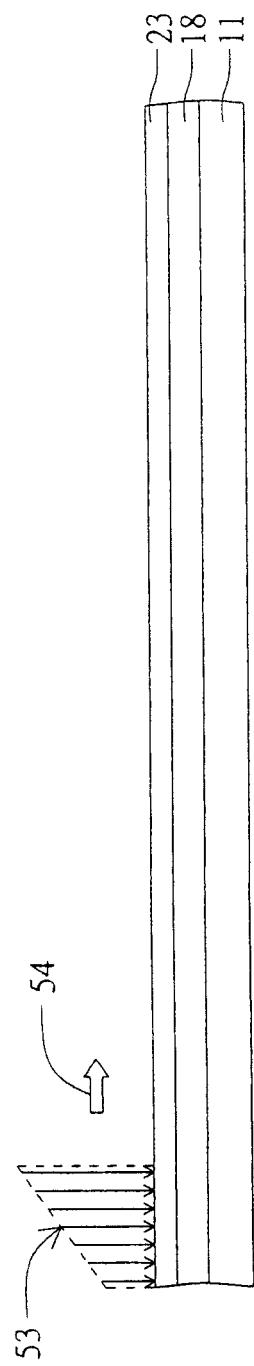

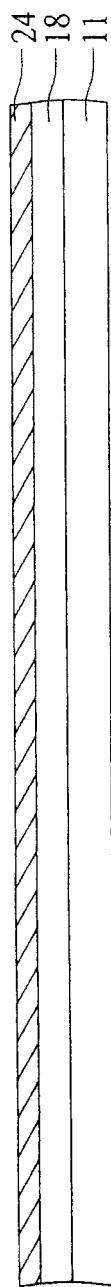

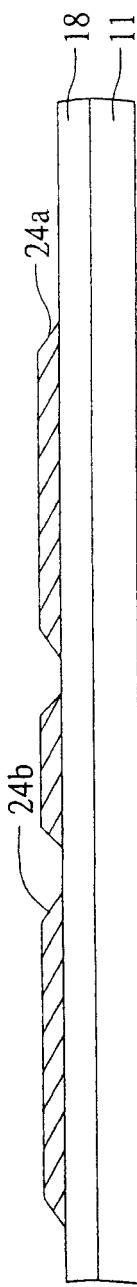

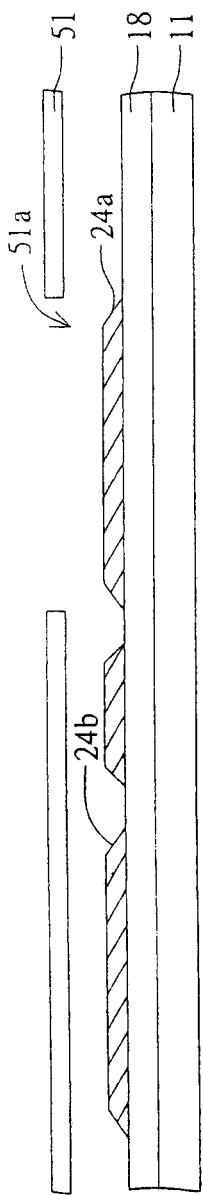

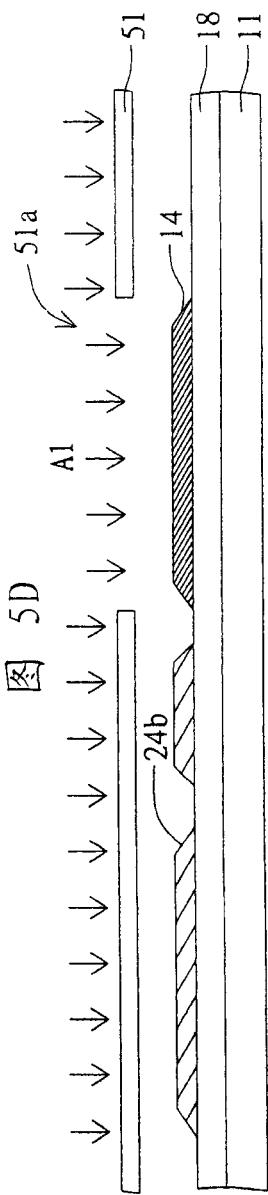

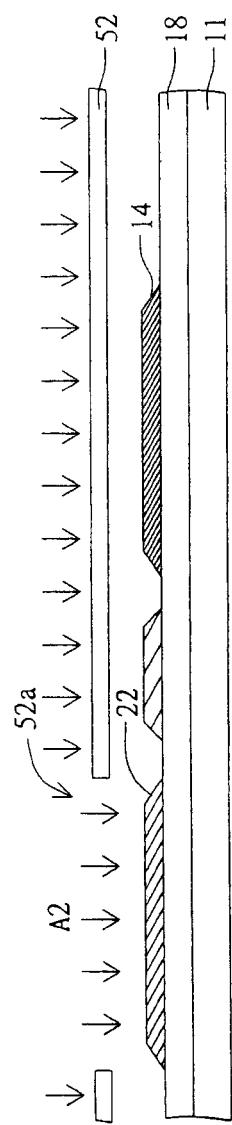

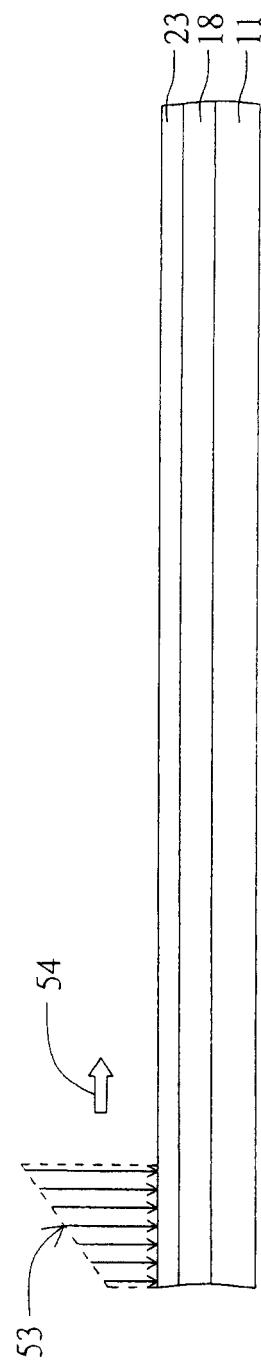

图 5A~5H 绘示乃本发明的实施例三的多晶硅通道层的工艺剖面图；

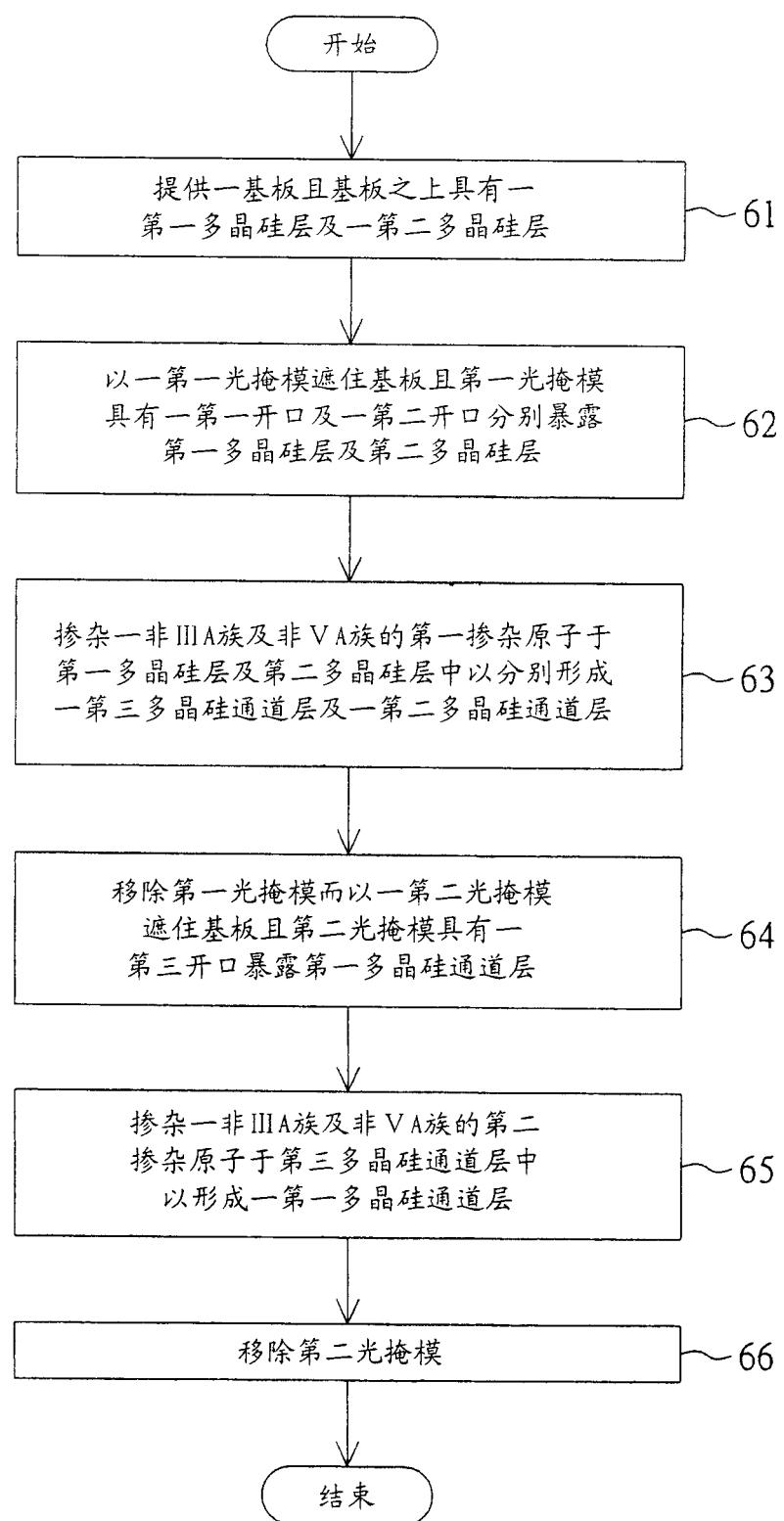

20 图 6 绘示乃依照本发明的实施例四的多晶硅通道层的形成方法的流程图；以及

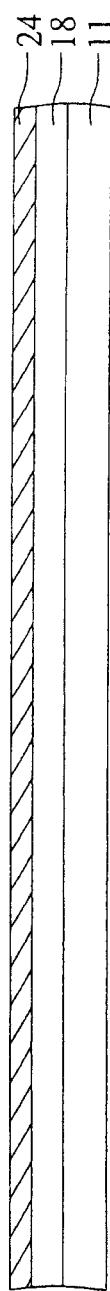

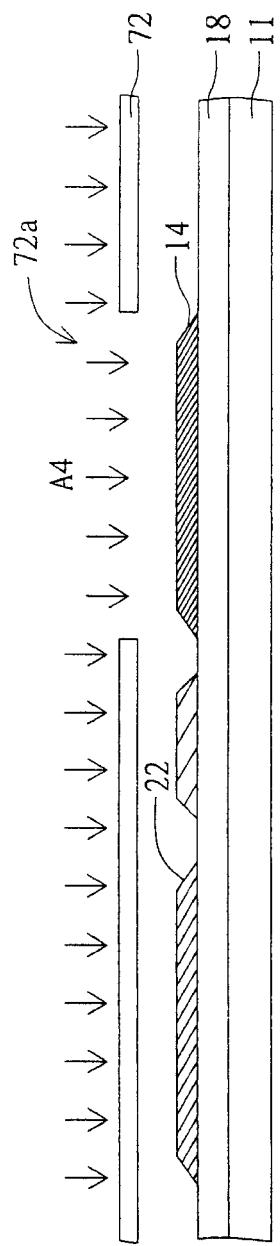

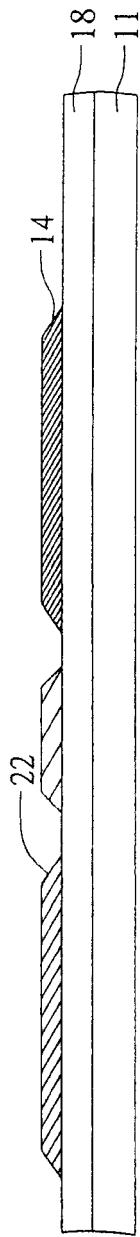

图 7A~7H 绘示乃本发明的实施例四的多晶硅通道层的工艺剖面图。

## 简单符号说明

10: 有机发光二极管显示面板

25 11、21: 基板

13: 像素

14: 第一多晶硅通道层

18、19: 绝缘层

22: 第二多晶硅通道层

30 23: 非晶硅层

24: 多晶硅层

- 24a: 第一多晶硅层

24b: 第二多晶硅层

24c: 第三多晶硅通道层

25: 有机电激发光元件

5 26: 阳极

27: 阴极

28: 有机材料层

51、71: 第一光掩模

51a、71a: 第一开口

10 52、72: 第二光掩模

52b、71b: 第二开口

72b: 第三开口

53: 准分子激光

54: 箭头

15 Cs: 储存电容

D1: 第一漏极

D2: 第二漏极

DL1: 第一数据线

DL2: 第二数据线

20 G1: 第一栅极

G2: 第二栅极

S1: 第一源极

S2: 第二源极

SL1: 第一扫描线

25 SL2: 第二扫描线

T1: 第一薄膜晶体管

T2: 第二薄膜晶体管

### 具体实施方式

#### 30 实施例一

请同时参照图1~2, 图1绘示乃依照本发明的实施例一的有机发光二极

管 ( organic light emitting diode, OLED ) 显示面板的单一像素中电路架构的示意图，图 2 绘示乃依照本发明的实施例一的有机发光二极管显示面板的单一像素中细部结构的剖面图。如图 1~2 所示，有机发光二极管显示面板 10 至少包括一基板 11、一像素 13 及一第一薄膜晶体管 ( thin film transistor, TFT )

5 T1。像素 13 设置于基板 11 之上，例如以有源矩阵像素阵列 ( active matrix pixel array ) 的数个像素中的一像素为例作说明。第一薄膜晶体管 T1 设置于像素 13 中，并包含一第一多晶硅通道层 14。第一多晶硅通道层 14 除了包含多晶硅之外，还掺杂有不同于多晶硅的一非 IIIA 族及非 VA 族的第一掺杂原子，

10 以均匀化掺杂前多晶硅层的缺陷 ( defect )。因此，可以改善多晶硅层结晶及缺陷的不均匀性，使得所有像素 TFT 中多晶硅通道层的特性相同。因此，进而使得所有像素的 TFT 的特性相同，避免有机发光二极管显示面板于运作时产生明亮不均的条纹现象 ( line mura )。如此一来，可以大大地提升有机发光二极管显示面板的显示质量，增加消费者对于 OLED 显示面板的好印象。

其中，掺杂于第一多晶硅通道层 14 中的第一掺杂原子可以是电中性原子，还可包含惰性气体及/或 IVA 族。例如，第一掺杂原子选自于氦(He)、氖(Ne)、氩(Ar)、氪(Kr)、氙(Xe)及氡(Rn)所组成的族群中至少一掺杂原子及其任意组合的掺杂原子。第一掺杂原子选自于碳(IC)、硅(Si)、锗(Ge)、锡(Sn)及铅(Pb)所组成的族群中至少一掺杂原子及其任意组合的掺杂原子。第一掺杂原子亦可选自于惰性气体及 IVA 族的组合。但本实施例的技术并不局限在此，例如，第一掺杂原子可选自于周期表 IIIA 族及 VA 族以外的电中性掺杂原子，即第一掺杂原子不是选自于周期表 IIIA 族及 VA 族。另外，第一掺杂原子在第一多晶硅通道层 14 中的掺杂浓度为  $10^{11} \sim 10^{15}$  原子个数/平方厘米 ( atoms/cm<sup>2</sup> )，亦可大于  $10^{12}$  原子个数/平方厘米。上述的第一多晶硅通道层 14 可由一多晶硅层被掺杂第一掺杂原子后完成，而多晶硅层可由一非晶硅层

20 透过热处理后而结晶完成。例如，非晶硅层可以透过激光回火 ( laser annealing ) 法熔融而结晶成多晶硅层，激光回火法可透过一准分子激光 ( excimer laser ) 扫描且熔融非晶硅层。

25

在本实施例中，于制造第一薄膜晶体管 T1 的过程中，首先以准分子激光回火 ( excimer laser annealing, ELA ) 结晶技术将非晶硅层熔融而结晶为多晶硅层。接着，掺杂一定量的第一掺杂原子于多晶硅层，以完成上述的第一多晶硅通道层 14。

在本实施例中，第一薄膜晶体管 T1 还包括一第一栅极 G1、一第一源极 S1 及一第一漏极 D1。第一源极 S1 及第一漏极 D1 设置于第一多晶硅通道层 14 之上，并对应地与第一多晶硅通道层 14 的二端电连接。第一栅极 G1 设置于第一多晶硅通道层 14 之上，并位于第一源极 S1 及第一漏极 D1 之间。

5 其中，第一源极 S1 及第一漏极 D1 分别透过重掺杂 N 型层 (N+) 与多晶硅通道层 14 欧姆性接触且电连接。

再者，有机发光二极管显示面板 10 还包括一第一扫描线 SL1、一第二扫描线 SL2、一第一数据线 DL1、一第二数据线 DL2、一第二薄膜晶体管 T2。第一扫描线 SL1 及第二扫描线 SL2 平行地设置于基板 11 之上，第一数据线 DL1 及第二数据线 DL2 平行地设置于基板 11 之上，并与第一扫描线 SL1 及第二扫描线 SL2 相互垂直，而交错地定义出像素 13。第二薄膜晶体管 T2 设置于像素 13 内，并包含一第二栅极 G2、一第二源极 S2、一第二漏极 D2 及一第二多晶硅通道层 22。第二源极 S2 及第二漏极 D2 对应地设置于第二多晶硅通道层 22 的二端，并透过 N+ 与第二多晶硅通道层 22 的二端欧姆性接触且电连接。第二栅极 G2 与第一扫描线 SL1 电连接，第二源极 S2 与第一数据线 DL1 电连接，第二漏极 D2 与第一栅极 G1 电连接。

10

15

其中，第二多晶硅通道层 22 中还可掺杂有一非 IIIA 族及非 VA 族的第二掺杂原子。第二掺杂原子在第二多晶硅通道层 22 中的掺杂浓度与第一掺杂原子在第一多晶硅通道层 14 中的掺杂浓度相同或不同。第一掺杂原子在第一多晶硅通道层 14 中的掺杂浓度可大于第二掺杂原子在第二多晶硅通道层 22 中的掺杂浓度。第二掺杂原子可以是电中性原子，还可包含惰性气体及/或 IVA 族。例如，第二掺杂原子各选自于氦(He)、氖(Ne)、氩(Ar)、氪(Kr)、氙(Xe)及氡(Rn)所组成的族群中至少一及其任意组合。第二掺杂原子选自于碳(IC)、硅(Si)、锗(Ge)、锡(Sn)及铅(Pb)所组成的族群中至少一掺杂原子及其任意组合的掺杂原子。第二掺杂原子亦可选自于惰性气体及 IVA 族的组合。第一掺杂原子与第二掺杂原子相同或不同。第二掺杂原子可选自于周期表 IIIA 族及 VA 族以外的电中性掺杂原子。再者，上述的第二多晶硅通道层 22 可由一多晶硅层被掺杂第二掺杂原子后完成，而多晶硅层可由一非晶硅层透过热处理后而结晶完成。例如，非晶硅层可以透过激光回火 (laser annealing) 法熔融而结晶成多晶硅层，激光回火法可透过一准分子激光 (excimer laser) 扫描且熔融非晶硅层。

20

25

30

又，有机发光二极管显示面板 10 还包括一储存电容 Cs 及一有机电激发光元件 (organic electroluminescent device, OELD) 25。储存电容 Cs 设置于像素 13 内，储存电容 Cs 的一端电连接于第一栅极 G1 及第二漏极 D2 之间，储存电容 Cs 的另一端电连接于第一源极 S1 及一第一固定电压 Vdd 之间。

5 有机电激发光元件 25 设置于像素 13 内，用以与第一漏极 D1 及一第二固定电压 Vss 电连接。

本实施例所属技术领域中的技术人员亦可以明了本实施例的技术并不局限在此。例如，有机发光二极管显示面板 10 还包括一绝缘层 18，绝缘层 18 设置于第一多晶硅通道层 14、第二多晶硅通道层 22 及基板 11 之间。此 10 外，有机发光二极管显示面板 10 还包括一绝缘层 19，绝缘层 19 设置于第一栅极 G1、第二栅极 G2 及第一多晶硅通道层 14 之间。绝缘层 18 及 19 包含氧化物、氮化物、氮氧化物，氮化硅或氧化氮。

至于有机电激发光元件 25 的细部结构在此作个简单说明，但本实施例的技术并不局限在此。有机电激发光元件 25 至少包含一阳极 26、一阴极 27 及一有机材料层 28，有机材料层 28 设置于阳极 26 及阴极 27 之间。阳极 26 15 与第一漏极 D1 电连接，阴极 27 可以可接地或被施加一固定电压。有机材料层 28 可包含一空穴源、一电子源及一发光层，发光层设置于空穴源及电子源之间。空穴源邻接阳极 26，且电子源邻接阴极 27。

在本实施例中，有机发光二极管显示面板 10 还包括一基板 21，基板 21 20 与 11 同时透过框胶 (sealant) 而平行组装，以将像素 13、第一薄膜晶体管 T1、第二薄膜晶体管 T2、储存电容 Cs 及有机电发光元件 25 密封且与外界隔绝。其中，基板 11 及 21 包含玻璃基板、塑料基板、陶瓷基板或可挠性基板。

虽然本实施例以栅极在上 (top gate) 的 TFT 结构作说明，但本实施例 25 的多晶硅通道层中掺杂有非 IIIA 族及非 VA 族的掺杂原子的技术亦可应用于栅极在下 (bottom gate) 或双栅极 (dual gates) 的 TFT 结构上。

本实施例即是在非晶硅层透过准分子激光回火 (excimer laser annealing, ELA) 熔融多晶硅层而结晶成多晶硅层 (即 ELA 结晶技术) 后，利用非 IIIA 族及非 VA 族的掺杂原子掺杂多晶硅层而形成多晶硅通道层的技术来调整原 30 先多晶硅层的缺陷浓度。因非 IIIA 族及非 VA 族的掺杂原子的掺杂能量及浓度可以很精准的控制，故 TFT 的特性可以有效的被控制。而掺杂技术所提供

的均匀性可以改善 ELA 结晶所产生的不均匀性，进而改善明暗不均的条纹效应。下表为 OLED 显示面板的沟道层中缺陷浓度改善的示意范例，以整个 OLED 显示面板来比较有无掺杂非 IIIA 族及非 VA 族的掺杂原子的结果，但本实施例的技术并不局限在此。

5

|                                     | 无条纹区域                | 有条纹区域              | 缺陷比率 |

|-------------------------------------|----------------------|--------------------|------|

| 掺杂前缺陷浓度 (缺陷个数/单位面积)                 | $10^{12}$            | $10^{13}$          | 10   |

| 非 IIIA 族及非 VA 族的掺杂原子杂质浓度(原子个数/单位面积) | $10^{13}$            | $10^{13}$          |      |

| 掺杂后缺陷浓度 (缺陷个数/单位面积)                 | $1.1 \times 10^{13}$ | $2 \times 10^{13}$ | 1.67 |

上表可以看出，在无掺杂非 IIIA 族及非 VA 族的掺杂原子的传统 OLED 显示面板中，其有无条纹区域的缺陷比率为 10 倍。在本实施例的 OLED 显示面板中，其掺杂非 IIIA 族及非 VA 族的掺杂原子于无条纹区域后虽然增加了非 IIIA 族及非 VA 族的掺杂原子杂质浓度 10 倍，但其有无条纹区域的缺陷比率经由一经过计算的非 IIIA 族及非 VA 族的掺杂原子掺杂后，可以由 10 倍改善到 1.67 倍。故用适量的非 IIIA 族及非 VA 族的掺杂原子掺杂可以均匀化沟道质量 (channel quality)，使所有像素的 TFT 的多晶硅通道层的特性相同，并有效的改善 ELA 结晶及缺陷的不均匀性。因此，进而使得所有像素的 TFT 的特性相同。

本实施例于不同非 IIIA 族及非 VA 族的掺杂原子的掺杂浓度时的 OLED 显示面板表现上，在非 IIIA 族及非 VA 族的掺杂原子的掺杂浓度为  $1.5 \times 10^{12}/\text{cm}^2$  的条件仍有 line mura 的效应，但比标准条件轻微一些。

而非 IIIA 族及非 VA 族的掺杂原子的掺杂浓度为  $1.5 \times 10^{13}/\text{cm}^2$  时，可看到已无 line mura 的现象。此适当调整非 IIIA 族及非 VA 族的掺杂原子的掺杂浓

度应可以改善 line mura 现象，因为非IIIA 族及非 VA 族的掺杂原子的掺杂效应主导了沟道质量（channel quality）的表现，而非原先由 ELA 结晶技术来决定沟道质量。

当掺杂前的多晶硅层的晶粒大小（grain size）介于 0.1 ~ 10 微米（ $\mu\text{m}$ ），

5 而掺杂前的多晶硅层的晶界缺陷浓度（grain boundary defect density）大于  $10^{11}$

缺陷个数/平方厘米，且多晶硅层于  $5\mu\text{m}$  范围内最厚及最薄的厚度相差 100

埃（ $\text{\AA}$ ）以上（即多晶硅层突起的高度）时，非IIIA 族及非 VA 族的第一掺

杂原子掺杂于第一多晶硅通道层 14 中的浓度可以大于  $10^{12}$  原子个数/平方厘

10 米。因此，本实施例可视多晶硅层的晶粒大小、晶界缺陷浓度及多晶硅层突

起的高度适当地调整非IIIA 族及非 VA 族的掺杂原子掺杂于多晶硅层中的浓

度，以形成所需要的多晶硅通道层。

## 实施例二

请参照图 3，其绘示乃依照本发明的实施例二的多晶硅通道层的形成方

法的流程图。如图 3 所示，首先，在步骤 31 中，提供一基板，基板之上具

15 有一非晶硅层。接着，进入步骤 32 中，热处理非晶硅层，以形成一多晶硅

层。然后，进入步骤 33 中，掺杂一非IIIA 族及非 VA 族的掺杂原子于多晶硅

层中，以形成一多晶硅通道层。其中，掺杂原子可以是电中性原子，还包括

惰性气体及/或IV A 族。例如，掺杂原子选自于氦(He)、氖(Ne)、氩(Ar)、氪

20 (Kr)、氙(Xe)及氡(Rn)所组成的族群中至少一及其任意组合，非选自于周期

表IIIA 族及 VA 族。掺杂原子选自于碳(IC)、硅(Si)、锗(Ge)、锡(Sn)及铅(Pb)

所组成的族群中至少一掺杂原子及其任意组合的掺杂原子。掺杂原子亦可选

自于惰性气体及IV A 族的组合。此外，掺杂原子在多晶硅通道层中的掺杂浓

度为  $10^{11} \sim 10^{15}$  原子个数/平方厘米，更可大于  $10^{12}$  原子个数/平方厘米。此外，

亦可透过激光回火法热处理非晶硅层，例如，以一准分子激光步进扫描且熔

25 融非晶硅层，以形成多晶硅层（即所谓的 ELA 结晶技术）。

本实施例于热处理非晶硅层后所结晶成的多晶硅层（例如以 ELA 结晶

技术所形成的多晶硅层）中掺杂非IIIA 族及非 VA 族的掺杂原子（例如是惰

性气体）的设计，可以将多晶硅层中的缺陷均匀化，且改善多晶硅结晶及缺

陷的不均匀性。如此一来，可以避免后续工艺所完成的有机发光二极管显示

30 面板于运作时产生明亮不均的条纹现象（line mura），大大地提升有机发光

二极管显示面板的显示质量。

### 实施例三

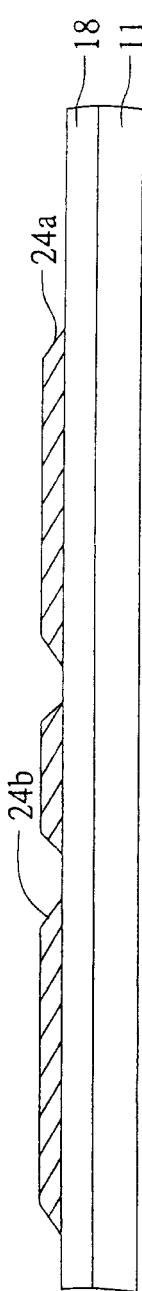

请同时参照图 4~5H，图 4 绘示乃依照本发明的实施例三的多晶硅通道层的形成方法的流程图，图 5A~5H 绘示乃本发明的实施例三的多晶硅通道层的工艺剖面图。如图 4 所示，首先，在步骤 41 中，提供一基板 11，基板 11 之上具有一第一多晶硅层 24a 及一第二多晶硅层 24b。至于第一多晶硅层 24a 及第二多晶硅层 24b 形成于基板 11 上的方式在此简单说明如下，但本实施例的技术并不局限在此。如图 5A 所示，提供基板 11，基板 11 之上具有一非晶硅层 23。接着，热处理非晶硅层 23，以形成一多晶硅层 24，如图 5B 所示。在此，亦可透过激光回火法热处理非晶硅层 23，例如，以一准分子激光 53 沿着图 5A 的箭头 54 的方向步进扫描且熔融非晶硅层 23，以逐步结晶成多晶硅层 24。然后，如图 5C 所示，去除部分的多晶硅层 24，以形成第一多晶硅层 24a 及第二多晶硅层 24b。但，本实施例形成上述第一多晶硅层 24a 及第二多晶硅层 24b 的技术并不局限在此。

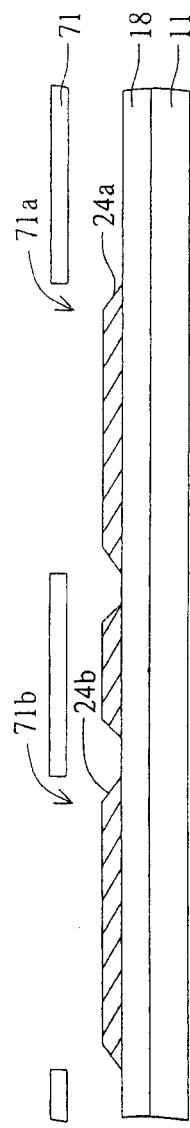

待第一多晶硅层 24a 及第二多晶硅层 24b 形成于基板 11 上后，进入步骤 42 中，如图 5D 所示，以一第一光掩模 51 遮住基板 11。第一光掩模 51 具有一第一开口 51a，第一开口 51a 暴露第一多晶硅层 24a。

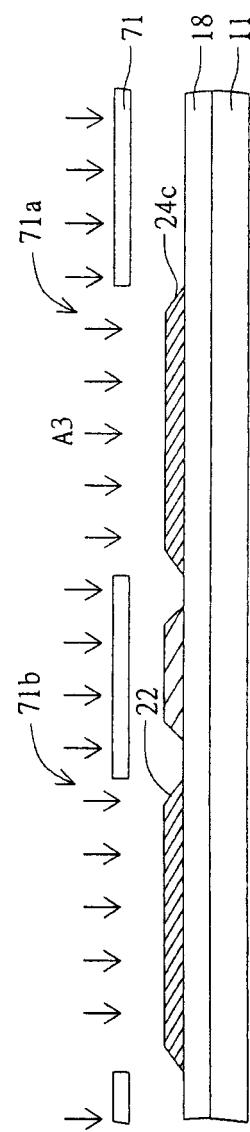

然后，进入步骤 43 中，如图 5E 所示，掺杂一非 IIIA 族及非 VA 族的第一掺杂原子 A1 于第一多晶硅层 24a 中，以形成一第一多晶硅通道层 14。第一掺杂原子 A1 可以是电中性原子，还包括惰性气体及/或 IVA 族。其中，第一掺杂原子 A1 选自于氦(He)、氖(Ne)、氩(Ar)、氪(Kr)、氙(Xe)及氡(Rn)所组成的族群中至少一及其任意组合。第一掺杂原子 A1 选自于碳(IC)、硅(Si)、锗(Ge)、锡(Sn)及铅(Pb)所组成的族群中至少一掺杂原子及其任意组合的掺杂原子。第一掺杂原子 A1 亦可选自于惰性气体及 IVA 族的组合。第一掺杂原子 A1 在第一多晶硅通道层 14 中的掺杂浓度为  $10^{11} \sim 10^{15}$  原子个数/平方厘米。在步骤 43 中，亦可使用第一掺杂原子 A1 为掺杂物来源，透过离子注入法将第一掺杂原子 A1 掺杂于第一多晶硅层 24a 中。

接着，进入步骤 44 中，如图 5F 所示，移除第一光掩模 51 且以一第二光掩模 52 遮住基板 11。第二光掩模 52 具有一第二开口 52a，第二开口 52a 暴露第二多晶硅层 24b。

然后，进入步骤 45 中，如图 5G 所示，掺杂一非 IIIA 族及非 VA 族的第二掺杂原子 A2 于第二多晶硅层 24b 中，以形成一第二多晶硅通道层 22。第

二掺杂原子 A2 可以是电中性原子，还包括惰性气体及/或ⅣA 族。其中，第二掺杂原子 A2 在第二多晶硅通道层 22 中的掺杂浓度与第一掺杂原子 A1 在第一多晶硅通道层 14 中的掺杂浓度相同或不同。第一掺杂原子 A1 在第一多晶硅通道层 14 中的掺杂浓度大于第二掺杂原子 A2 在第二多晶硅通道层 22 中的掺杂浓度。第二掺杂原子选自于氦(He)、氖(Ne)、氩(Ar)、氪(Kr)、氙(Xe)及氡(Rn)所组成的族群中至少一及其任意组合。第二掺杂原子 A2 选自于碳(IC)、硅(Si)、锗(Ge)、锡(Sn)及铅(Pb)所组成的族群中至少一掺杂原子及其任意组合的掺杂原子。第二掺杂原子 A2 亦可选自于惰性气体及ⅣA 族的组合。第一掺杂原子 A1 及第二掺杂原子 A2 可以相同或不同。在步骤 45 中，亦可使用第二掺杂原子 A2 为掺杂物来源，透过离子注入法将第二掺杂原子 A2 掺杂于第二多晶硅层 24b 中。接着，进入步骤 46 中，如图 5H 所示，移除第二光掩模 52。

本实施例所属技术领域中的技术人员亦可以明了本实施例的技术并不局限在此。例如，于第一多晶硅层 24a 及第二多晶硅层 24b 形成于基板 11 上后，更可覆盖一层薄牺牲层（如二氧化硅， $\text{SiO}_2$ ）于第一多晶硅层 24a 及第二多晶硅层 24b 上。此外。于第二掺杂原子 A2 掺杂于第二多晶硅层 24b 后，使用稀氢氟酸（dilute HF）去除上述的牺牲层。在此，牺牲层可以做第一掺杂原子 A1 及第二掺杂原子 A2 分别掺杂于第一多晶硅层 24a 及第二多晶硅层 24b 时的缓冲层，以降低第一掺杂原子 A1 及第二掺杂原子 A2 掺杂时分别对第一多晶硅层 24a 及第二多晶硅层 24b 的表面的破坏。

#### 实施例四

请同时参照图 6~7H，图 6 绘示乃依照本发明的实施例四的多晶硅通道层的形成方法的流程图，图 7A~7H 绘示乃本发明的实施例四的多晶硅通道层的工艺剖面图。如图 6 所示，首先，在步骤 61 中，提供一基板 11，基板 11 之上具有一第一多晶硅层 24a 及一第二多晶硅层 24b。至于第一多晶硅层 24a 及第二多晶硅层 24b 形成于基板 11 上的方式图 7A~7C 所示，已于实施例二中说明过，在此不再赘述。

接着，进入步骤 62 中，如图 7D 所示，以一第一光掩模 71 遮住基板 11。第一光掩模 71 具有一第一开口 71a 及一第二开口 71b，第一开口 71a 及第二开口 71b 分别暴露第一多晶硅层 24a 及第二多晶硅层 24b。

然后，进入步骤 63 中，如图 7E 所示，掺杂一非ⅢA 族及非 VA 族的

第一掺杂原子 A3 于第一多晶硅层 24a 及第二多晶硅层 24b 中，以分别形成一第三多晶硅通道层 24c 及一第二多晶硅通道层 22。第一掺杂原子 A3 可以是电中性原子，还包括惰性气体及/或ⅣA 族。其中，第一掺杂原子 A3 于第二多晶硅通道层 22 中的掺杂浓度与第一掺杂原子 A3 于第三多晶硅通道层 24c 中的掺杂浓度相同。第一掺杂原子 A3 选自于氦(He)、氖(Ne)、氩(Ar)、氪(Kr)、氙(Xe)及氡(Rn)所组成的族群中至少一及其任意组合。第一掺杂原子 A3 选自于碳(IC)、硅(Si)、锗(Ge)、锡(Sn)及铅(Pb)所组成的族群中至少一掺杂原子及其任意组合的掺杂原子。第一掺杂原子 A3 亦可选自于惰性气体及ⅣA 族的组合。在步骤 63 中，使用第一掺杂原子 A3 为掺杂物来源，透过离子注入法将第一掺杂原子 A3 掺杂于第一多晶硅层 24a 及第二多晶硅层 24b 中。

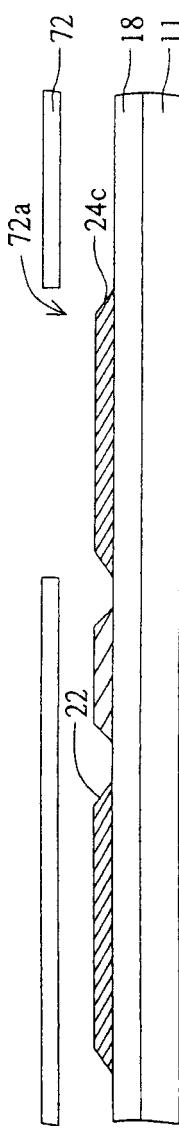

接着，进入步骤 64 中，如图 7F 所示，移除第一光掩模 71 且以一第二光掩模 72 遮住基板 11。第二光掩模 72 具有一第三开口 72a，第三开口 72a 暴露第三多晶硅通道层 24c。

然后，进入步骤 65 中，如图 7G 所示，掺杂一非ⅢIA 族及非ⅤA 族的第二掺杂原子 A4 于第三多晶硅通道层 24c 中，以形成一第一多晶硅通道层 14。第二掺杂原子 A4 可以是电中性原子，还包括惰性气体及/或ⅣA 族。其中，第一掺杂原子 A3 及第二掺杂原子 A4 在第一多晶硅通道层 14 中的总掺杂浓度与第一掺杂原子 A3 在第二多晶硅通道层 22 中的掺杂浓度相同或不同。例如，第一掺杂原子 A3 及第二掺杂原子 A4 在第一多晶硅通道层 14 中的总掺杂浓度大于第一掺杂原子 A3 在第二多晶硅通道层 22 中的掺杂浓度。第一掺杂原子 A3 及第二掺杂原子 A4 在第一多晶硅通道层 14 中的总掺杂浓度为  $10^{11} \sim 10^{15}$  原子个数/平方厘米，或者是大于  $10^{12}$  原子个数/平方厘米。第二掺杂原子 A4 选自于氦(He)、氖(Ne)、氩(Ar)、氪(Kr)、氙(Xe)及氡(Rn)所组成的族群中至少一及其任意组合。第二掺杂原子 A4 选自于碳(IC)、硅(Si)、锗(Ge)、锡(Sn)及铅(Pb)所组成的族群中至少一掺杂原子及其任意组合的掺杂原子。第二掺杂原子 A4 亦可选自于惰性气体及ⅣA 族的组合。第一掺杂原子 A3 及第二掺杂原子 A4 可以相同或不同。在步骤 65 中，亦可使用第二掺杂原子 A4 为掺杂物来源，透过离子注入法将第二掺杂原子 A4 掺杂于第三多晶硅通道层 24c 中。接着，进入步骤 66 中，如图 7H 所示，移除第二光掩模 72。

本发明上述实施例所揭露的有机发光二极管显示面板及其多晶硅通道层的形成方法，其于热处理非晶硅层后所结晶成的多晶硅层（例如以 ELA 结晶技术所形成的多晶硅层）中掺杂原子的设计，可以均匀化多晶硅层的缺陷。因此，可以改善多晶硅层结晶及缺陷的不均匀性，使得所有像素的 TFT 5 的多晶硅通道层的特性相同。因此，进而使得所有像素的 TFT 的特性相同，避免有机发光二极管显示面板于运作时产生明亮不均的条纹现象。如此一来，大大地提升有机发光二极管显示面板的显示质量。

综上所述，虽然本发明以优选实施例揭露如上，然而其并非用以限定本发明，本领域的技术人员在不脱离本发明的精神和范围内，可作些许的更动 10 与润饰，因此本发明的保护范围应当以后附的权利要求所界定者为准。

10

图 1

图 2

图 3

图 4

图 5A

图 5B

图 5C

图 5D

图 5G

图 5H

图 6

图 7A

图 7B

图 7C

图 7D

图 7E

图 7F

图 7G

图 7H

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机发光二极管显示面板及其多晶硅通道层的形成方法                       |         |            |

| 公开(公告)号        | <a href="#">CN1828927A</a>                     | 公开(公告)日 | 2006-09-06 |

| 申请号            | CN200610006074.1                               | 申请日     | 2006-01-24 |

| [标]申请(专利权)人(译) | 友达光电股份有限公司                                     |         |            |

| 申请(专利权)人(译)    | 友达光电股份有限公司                                     |         |            |

| 当前申请(专利权)人(译)  | 友达光电股份有限公司                                     |         |            |

| [标]发明人         | 林俊仪<br>陈明炎                                     |         |            |

| 发明人            | 林俊仪<br>陈明炎                                     |         |            |

| IPC分类号         | H01L27/32 H01L29/786 H01L21/8234 H01L21/336    |         |            |

| 代理人(译)         | 侯宇                                             |         |            |

| 其他公开文献         | CN100399574C                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a> |         |            |

## 摘要(译)

本发明涉及一种多晶硅通道层及其形成方法。首先，提供一基板，基板之上具有一非晶硅层。接着，掺杂一非IIIA族及非VA族的掺杂原子于多晶硅层中，以形成一多晶硅通道层。