## [12] 发明专利申请公开说明书

[21] 申请号 200410068283. X

[43] 公开日 2005 年 3 月 9 日

[11] 公开号 CN 1592520A

[22] 申请日 2004. 8. 27

[74] 专利代理机构 北京市柳沈律师事务所

[21] 申请号 200410068283. X

代理人 陶凤波 侯 宇

[30] 优先权

[ 32 ] 2003. 8. 28 [33] KR [31] 0060016/2003

[71] 申请人 三星 SDI 株式会社

地址 韩国京畿道

[72] 发明人 朴商一 姜泰旭

权利要求书 3 页 说明书 7 页 附图 2 页

[54] 发明名称 有机电致发光显示器

[57] 摘要

一种有机电致发光显示器包括一个衬底，该衬底具有一个具有像素的阵列部分和一个耦连至外部电源的焊盘部分。在衬底上形成具有源电极、漏电极和焊盘的半导体结构。在该半导体结构上形成一层具有通孔的钝化层，该通孔露出在阵列部分上的源和漏电极的区域以及在焊盘部分上的焊盘的区域。接触通孔的钝化层部分在阵列部分和焊盘部分之间具有相同的厚度。一层导电层填充该通孔。一层像素限定层形成于一层平整层和导电层的整个表面上，其在所述阵列部分上具有露出导电层的区域的像素区。一个有机电致发光薄膜形成于每个像素区上。本发明通过减小阵列部分和焊盘部分之间的钝化层的厚度差异，防止了源电极和漏电极被蚀刻过度。

- 1、一种有机电致发光显示器，包括：

- 一衬底，具有一带像素的阵列部分和一具有焊盘的焊盘部分；

- 5 一形成于所述衬底上具有一源电极和一漏电极的半导体结构；

- 一形成于所述半导体结构上的具有通孔的钝化层，所述通孔露出在所述阵列部分上的所述源电极和所述漏电极以及在所述焊盘部分上的所述焊盘的区域，其中含有所述通孔的所述钝化层的部分在所述阵列部分和所述焊盘部分之间具有相同的厚度；

- 10 一充填所述通孔的导电层；

- 一形成于所述钝化层和所述导电层上的像素限定层，其具有在所述阵列部分露出所述导电层的区域的像素区；以及

- 一有机电致发光薄膜，形成于各个像素区上。

- 2、如权利要求1所述的有机电致发光显示器，其中在所述焊盘部分的所述衬底上的所述半导体结构包括顺序沉积在所述衬底之上的一栅极绝缘层、栅电极、一层间绝缘层以及所述焊盘，而在所述阵列部分的所述衬底上的所述半导体结构包括所述衬底之上的所述栅极绝缘层、在所述衬底之上顺序沉积的一虚设栅极图形、所述层间绝缘层、以及所述源电极和所述漏电极。

- 20 3、如权利要求2所述的有机电致发光显示器，其中所述虚设栅极图形形成于所述阵列部分上所述通孔的下面。

- 4、如权利要求2所述的有机电致发光显示器，其中所述虚设栅极图形和所述栅电极由相同材料同时形成，同时具有相同的厚度。

- 5、如权利要求1所述的有机电致发光显示器，其中在所述阵列部分的所述衬底上的所述半导体结构包括顺序沉积在所述衬底上的一栅极绝缘层、栅电极、一层间绝缘层、以及所述源和漏电极。

- 25 6、如权利要求1所述的有机电致发光显示器，其中所述钝化层具有一反映下层结构拓扑的、具有均匀厚度的第一绝缘层和一形成于所述第一绝缘层上的、具有平的顶面的第二绝缘层。

- 30 7、如权利要求1所述的有机电致发光显示器，其中一源极区和一漏极区分别连接至在所述阵列部分的所述源电极和所述漏电极。

8、如权利要求 7 所述的有机电致发光显示器，其中所述源极区和所述漏极区通过在一多晶硅层的周边掺入杂质而形成，并且所述多晶硅层置于所述源极区和所述漏极区之间的部分起沟道区的作用。

5 9、如权利要求 1 所述的有机电致发光显示器，其中所述栅电极、所述源电极和所述漏电极用金属材料形成。

10、如权利要求 8 所述的有机电致发光显示器，其中所述衬底为一种绝缘材料，并且在所述衬底和所述多晶硅层之间以及在所述衬底与所述栅极绝缘层之间形成一阻挡层。

11、一种有机电致发光显示器，包括：

10 一具有一阵列部分和一焊盘部分的衬底，所述阵列部分具有像素，所述焊盘部分具有一将被连接到外部电源上的焊盘；

一形成于所述衬底上的半导体结构；

形成于所述半导体结构上的一源电极和一漏电极，其中在所述阵列部分处的所述漏电极的顶面和在所述焊盘部分处的所述焊盘位于相同近似平面之内；

一形成于所述半导体结构上的具有通孔的钝化层，所述通孔露出在所述阵列部分上的所述漏电极的以及在所述焊盘部分上的所述焊盘的区域；

一充填所述通孔的导电层；

20 一形成于所述钝化层和所述导电层上的像素限定层，其具有在所述阵列部分露出所述导电层的区域的像素区；以及

一有机电致发光薄膜，形成于各个像素区上。

12、如权利要求 11 所述的有机电致发光显示器，其中在所述焊盘部分的所述衬底上的所述半导体结构包括顺序沉积在所述衬底之上的一栅极绝缘层、栅电极、一层间绝缘层以及所述焊盘，并且其中在所述阵列部分的所述衬底上的所述半导体结构包括所述衬底上的所述栅极绝缘层、在所述衬底之上顺序沉积的一虚设栅极图形、所述层间绝缘层、以及所述源电极和所述漏电极。

13、如权利要求 12 所述的有机电致发光显示器，其中所述虚设栅极图形形成于所述阵列部分上所述通孔的下面。

30 14、如权利要求 12 所述的有机电致发光显示器，其中所述虚设栅极图形和所述栅电极由相同材料同时形成，同时具有相同的厚度。

15、如权利要求 11 所述的有机电致发光显示器，其中在所述焊盘部分的所述衬底上的所述半导体结构包括顺序沉积在所述衬底上的一栅极绝缘层、栅电极、一层间绝缘层以及所述焊盘。

5 16、如权利要求 11 所述的有机电致发光显示器，其中所述钝化层具有

一反映下层结构拓扑的、具有均匀厚度的第一绝缘层，以及一形成于所述

第一绝缘层上的、具有平的顶面的第二绝缘层。

17、如权利要求 11 所述的有机电致发光显示器，其中一源极区和一漏

极区分别连接至在所述阵列部分的所述源电极和所述漏电极。

10 18、如权利要求 17 所述的有机电致发光显示器，其中所述源极区和所

述漏极区通过在多晶硅层的侧周边掺入杂质而形成，并且所述多晶硅层置

于所述源极区和所述漏极区之间的部分起沟道区的作用。

19、如权利要求 11 所述的有机电致发光显示器，其中所述栅电极、所

述源电极、和所述漏电极由金属材料形成。

15 20、如权利要求 18 所述的有机电致发光显示器，其中所述衬底为一种

绝缘材料，并且在所述衬底和所述多晶硅层之间以及在所述衬底与所述栅

极绝缘层之间形成一阻挡层。

## 有机电致发光显示器

5 本申请要求 2003 年 8 月 28 日申请的韩国专利申请 No. 2003-0060016 的权益，该申请在此参照引用，目的在于就好像已在此对其进行了全面陈述一样。

## 技术领域

10 本申请涉及一种有机电致发光显示器，具体地说，涉及一种通过消除阵列部分与焊盘部分之间的与通孔相接触的钝化层的厚度差异而防止了源和漏电极的蚀刻过度的有机电致发光显示器。

## 背景技术

15 通常，电致发光 (EL) 显示器是一种利用了这样的原理的显示器：将来自阴极的电子和来自阳极的空穴注入到发光层，同时使其结合以便形成激子，并且当激子从激发态减弱为基态时，发光层发光。

与传统的薄膜晶体管液晶显示器相反，有机 EL 显示器不需要单独的光源，并使用了体积缩小了的轻量结构。在有机 EL 显示器中，施加电流时发光的有机材料膜设置在呈矩阵形式的各个像素处，并且改变施加到该有机材料膜上的电流的量以便显示所需图像。有机 EL 显示器具有许多优点，如低驱动电压、轻重量、平直度、宽视角、和快速的响应时间。此外，有机 EL 显示器预计是下一代显示装置。

20 有机 EL 显示器包括以矩阵形式设置的多个像素、以及形成于每个像素区上的许多薄膜图形，如用来开关 (switching) 和驱动元件的薄膜晶体管、像素电极、以及有机 EL 薄膜。

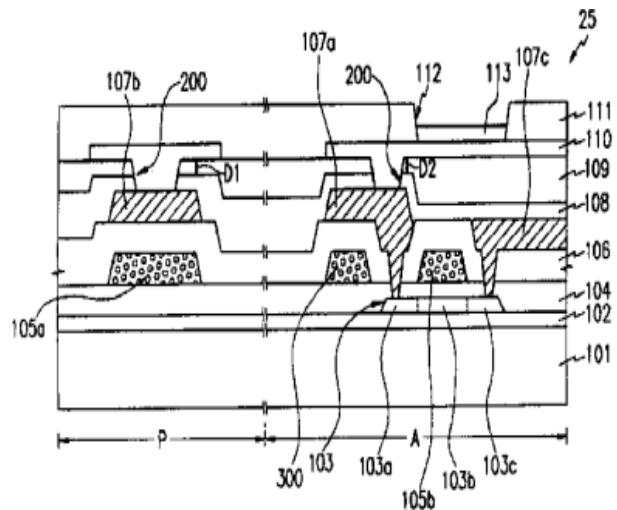

参见附图，图 1 是根据现有技术构造的有机 EL 显示器 15 的横截面视图。如图 1 所示，有机 EL 显示器 15 具有一个板，该板具有一个用来形成像素的阵列部分 A、以及一个置于其周边以便连接至外部电源 (未示出) 的电路焊盘部分 (circuit pad portion) P。一层由  $\text{SiO}_2$  制成的阻挡层 (blocking layer) 2 形成于绝缘衬底层 1 上，以及多晶硅层 3 形成于阻挡层 2 上具有预

定宽度。

分别掺杂高浓度杂质的源极和漏极区 3a 和 3c 形成于多晶硅层 3 处，并且在源极区 3c 与漏极区 3a 之间形成一个沟道区 (channel region) 3b。

5 一层  $\text{SiO}_2$  或  $\text{Si}_3\text{N}_4$  的栅极绝缘层 (gate insulating layer) 4 形成于阻挡层 2 和多晶硅层 3 的整个表面之上。由铝 (Al) 制成的栅电极 5a 和 5b 形成于栅极绝缘层 4 上具有预定宽度，并且层间绝缘层 6 形成于栅极绝缘层 4 和栅电极 5a 和 5b 之上。

10 由铝 (Al) 制成的源电极 7a 和漏电极 7b 分别形成于层间绝缘层 6 上，从而源电极 7a 和漏电极 7b 分别连接至源极区 3c 和漏极区 3a。第一和第二绝缘钝化层 8 和 9 形成于源电极 7a 和漏电极 7b 上，形成了其平的顶面。

第一和第二绝缘钝化层 8 和 9 分别被有选择地蚀刻，从而它们露出源电极 7a 和漏电极 7b。一层导电层 10 填满了第一绝缘钝化层 8 和第二绝缘钝化层 9 的已蚀刻部分，并且一层像素限定层 11 形成于导电层 10 上。像素限定层 11 被有选择地蚀刻以便形成像素区 12。

15 在形成第一绝缘和第二绝缘钝化层 8、9 的工艺期间，具有薄厚度的第一绝缘钝化层 8 首先形成，然后具有厚的厚度的第二绝缘钝化层 9 形成于其上，并具有平的顶面以便制成一致拓扑。当第一绝缘钝化层 8 以均匀厚度在下层结构上形成时，其呈现出该下层结构的拓扑，与绝缘衬底层 1 类似。第二绝缘钝化层 9 消除了下层结构中的表面阶梯状差异，并且在晶片 20 的整个区域上形成平的顶面。

第一和第二绝缘钝化层 8、9 必须在绝缘衬底 1 的整个区域上具有平的顶面，以便随后进行用来形成通孔 20 的光刻工艺。在形成第一和第二绝缘钝化层 8、9 之后，形成使源和漏电极 7a 和 7b 分别露出的通孔 20。借助于通孔 20，阵列部分 A 处的像素电极 13 被连接至下层金属元件或导电层 10，同时在焊盘部分 P 处的焊盘电极 (pad electrode) 19 被连接至下层金属元件或导电层 10。

30 然而，第一和第二绝缘钝化层 8、9 由于下层结构的表面阶梯状差异而具有不同厚度。更准确地说，在第一和第二绝缘钝化层 8、9 下面可以是单独的源和漏电极 7a、7b，或者源和漏电极 7a、7b 加上栅电极 5b，或者源和漏电极 7a、7b 加上栅电极 5a、5b 加上多晶硅层 3。

在阵列部分 A 和焊盘部分 P 之间形成了第一和第二绝缘钝化层 8、9

厚度的差异。由于第一和第二绝缘钝化层 8、9 的厚度差异，在阵列部分 A 和焊盘部分 P 之间，用来形成通孔 20 的蚀刻深度也不一样。

如图 1 所示，在焊盘部分 P 处将被蚀刻的第二绝缘钝化层 9 的厚度用 T1 表示，在阵列部分 A 处将被蚀刻的第二绝缘钝化层 9 的厚度用 T2 表示。

5 T1 清楚地显示为小于 T2。除具有均匀厚度的第一绝缘钝化层 8 以外，在阵列部分 A 和焊盘部分 P 之间，用来形成通孔 20 的蚀刻深度相差 T2 减去 T1 的值。

当用来形成通孔 20 的蚀刻深度差异变得更大时，在阵列部分 A 处，第一和第二绝缘钝化层 8、9 的较厚部分被蚀刻，直到下层源和漏电极 7a、7b 10 露出为止，而在焊盘部分 P 处，第一和第二绝缘钝化层 8、9 的较薄部分以及下层源和漏电极 7a、7b 被连续地蚀刻。这就导致了焊盘 7c 的蚀刻过度。

当用来形成通孔的第一和第二绝缘钝化层 8、9 的蚀刻深度的差异为 3000 埃或以上时，在焊盘部分 P 处，焊盘 7c 的蚀刻过度变得更加严重。于是电极蚀刻过度导致了接触的破坏。

15 因此，需要防止源和漏电极在通孔形成工艺期间由于钝化层厚度的差异而被过度蚀刻。

### 发明内容

本发明的一个方面是要防止源电极和漏电极被蚀刻过度。

20 本发明能够减小阵列部分和焊盘部分之间的钝化层的厚度差异。

一种有机 EL 显示器在阵列部分处具有一个形成于源电极和漏电极下面的虚设栅极图形 (dummy gate pattern)，以便将阵列部分处平整层 (flattening layer) 的厚度减小至与焊盘部分处相同的水平。可供选择地，在焊盘部分处可以省去栅电极，以便将焊盘部分处的平整层的厚度增加至 25 与阵列部分处相同的水平。

根据本发明的一个方面，有机 EL 显示器包括一个衬底，该衬底具有一个具有像素的阵列部分和一个连接至外部电源的焊盘部分。在衬底上形成一个具有源和漏电极的半导体结构。在半导体结构上形成一层具有通孔的绝缘钝化层，该通孔露出阵列部分上的源和漏电极以及焊盘部分的预定区域。钝化层与通孔接触的部分在阵列部分和焊盘部分之间具有相同的厚度。30 一层导电层充填该通孔。在平整层和导电层上的整个表面上形成一层像素

限定层，其在阵列部分上具有露出导电层预定区域的像素区。一个有机电致发光薄膜形成于每个像素区上。

根据本发明的另一个方面，该有机 EL 显示器包括一个衬底，该衬底具有一个具有像素的阵列部分和一个连接至外部电源的焊盘部分。在衬底上 5 形成一个半导体结构，并且在半导体结构上形成源和漏电极。在阵列部分中的源和漏电极的顶面和焊盘部分中的焊盘的顶面位于相同的平面上。在半导体结构上形成绝缘钝化层。在阵列部分和焊盘部分上形成露出源和漏电极以及焊盘的预定区域的通孔。一层导电层充填该通孔。在平整层的整个表面上形成一层像素限定层。在阵列部分上形成导电层，其具有露出导 10 电层预定区域的像素区。一个有机 EL 薄膜形成于每个像素区上。

位于阵列部分中通孔下面的是按下列顺序沉积的衬底、一层栅极绝缘层、栅电极、一层层间绝缘层、以及源和漏电极；而在焊盘部分处，在通孔下面的是按下列顺序沉积的衬底、栅极绝缘层、一个虚设栅极图形、层间绝缘层、以及焊盘。虚设栅极图形和栅电极用相同材料同时形成，同时 15 具有相同的厚度。

在阵列部分在通孔下面，衬底、一层栅极绝缘层、一层层间绝缘层、以及源和漏电极按该顺序沉积；而在焊盘部分在通孔下面，衬底、栅极绝缘层、层间绝缘层、以及焊盘按该顺序沉积。

绝缘钝化层具有一层反映下层结构拓扑的、具有均匀厚度的第一绝缘 20 层，以及一层形成于第一绝缘层上的、具有平的顶面的第二绝缘层。

在阵列部分，一个下源极和一个下漏极分别连接至源和漏电极。

下源极和下漏极通过在多晶硅层的周边掺入杂质而形成，并且多晶硅层位于下源极和下漏极之间的部分起沟道区的作用。栅电极以及源和漏电极由金属材料形成。

25 衬底用一种绝缘材料形成，并且在衬底和多晶硅层之间的界面上以及在衬底与栅极绝缘层之间的界面上形成一层阻挡层。

#### 附图说明

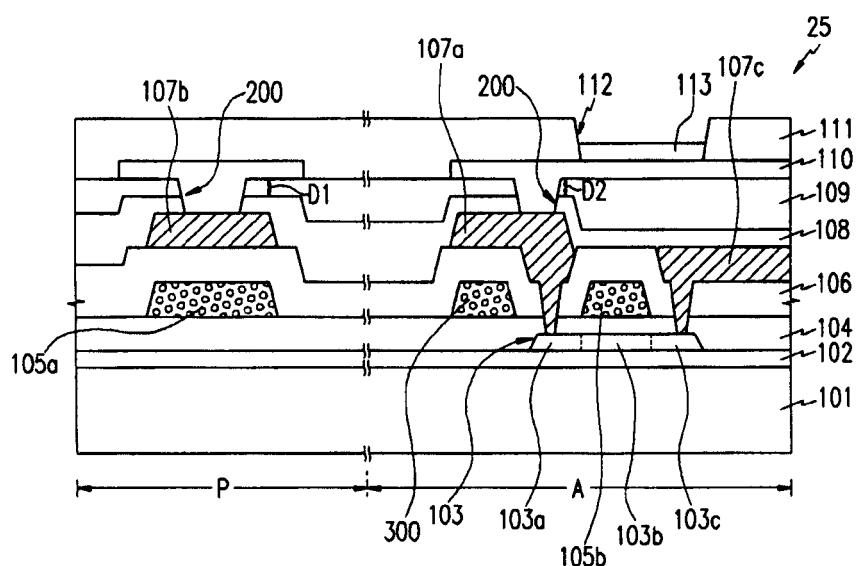

图 1 是传统有机 EL 显示器的横截面视图；

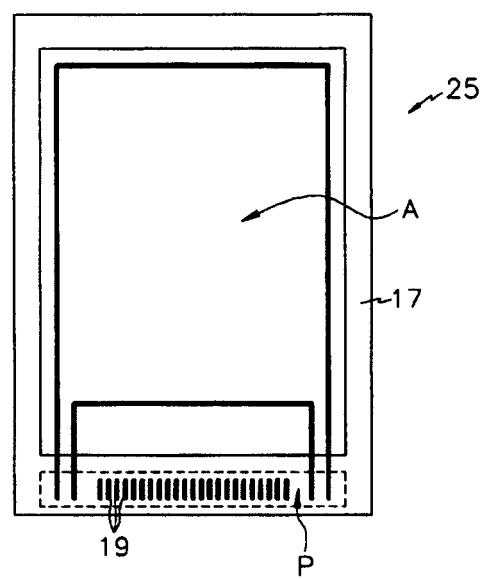

30 图 2 是根据本发明的一个示范性实施例而构造的有机 EL 显示器的阵列部分和焊盘部分的平面图；

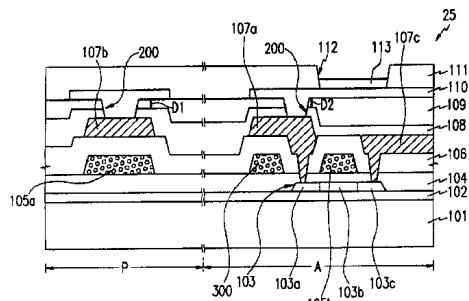

图3是根据本发明该示范性实施例而构造的有机EL显示器的横截面视图；

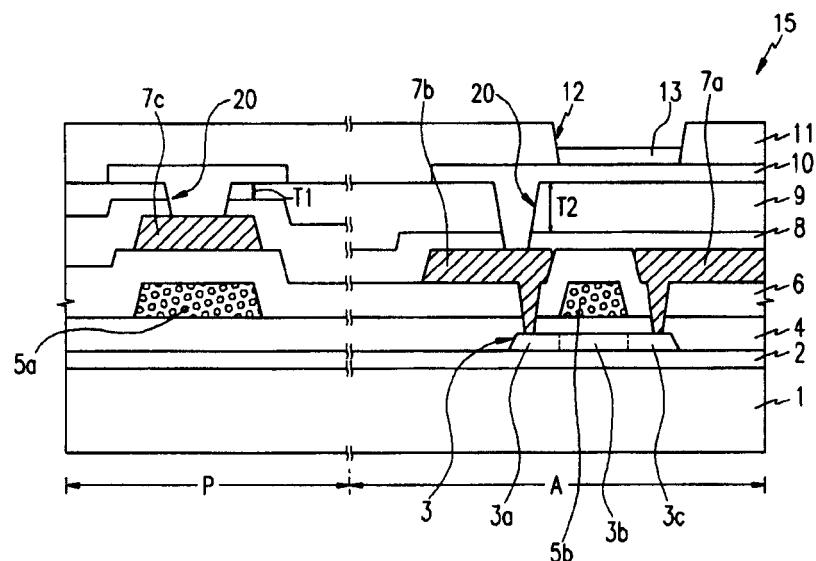

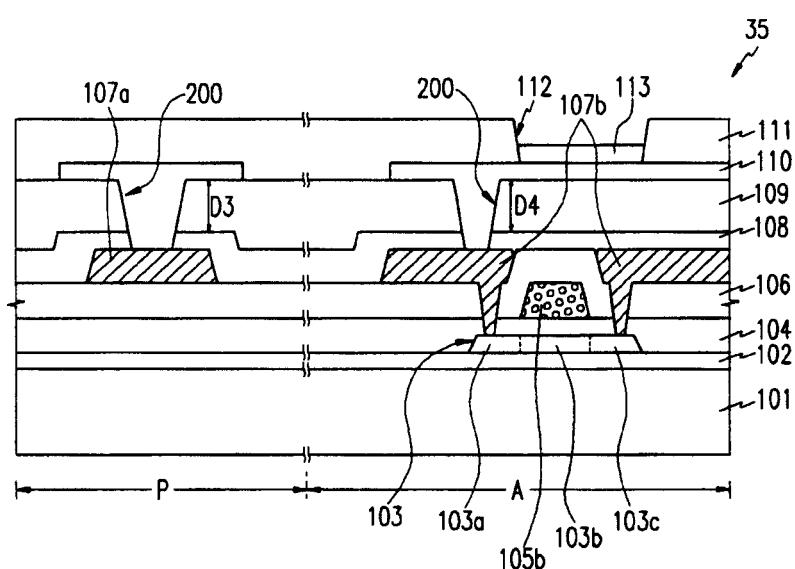

图4是根据本发明另一个示范性实施例而构造的有机EL显示器的横截面视图。

5

### 具体实施方式

图2和3展示出根据本发明一个示范性实施例而构造的有机EL显示器25。EL显示器25具有一个板17，该板具有一个用来形成像素的阵列部分A、以及一个位于其周边的焊盘部分P。焊盘19形成于焊盘部分P处，以便将驱动电信号施加到电力传输线、扫描线和数据线上。

如图3所示，有机EL显示器25具有一层在绝缘衬底101上的由SiO<sub>2</sub>制成的阻挡层2以及一层形成于阻挡层102上的具有预定宽度的多晶硅层103。

在多晶硅层103的周边掺杂高浓度的N型或P型杂质离子，以便形成一个下漏极区103a和一个下源极区103c。下漏极区103a和下源极区103c之间的区域成为一个电子和空穴在此迁移的沟道区103b。

一层SiO<sub>2</sub>或Si<sub>3</sub>N<sub>4</sub>的栅极绝缘层104形成于阻挡层102和多晶硅层103的整个表面之上。栅极绝缘层104位于多晶硅层103上的部分高于它的其他部分。由于多晶硅层103相对较薄，因此阻挡层102和多晶硅层103之间的阶梯状差异如此之小，以致于其影响无关紧要。因此，为了便于说明，在图3中，这种阶梯状差异被省略了，并且没有示出。

由铝(Al)制成的虚设栅极图形300和栅电极105a和105b形成于栅极绝缘层104上具有预定宽度。一层层间绝缘层106形成于栅极绝缘层104、栅电极105a和105b、以及虚设栅极图形300上。

优选的是，虚设栅极图形300和栅电极105a和105b通过同一淀积和光刻工艺而同时形成。因此，虚设栅极图形300和栅电极105a和105b将由相同的材料形成，同时具有相同的厚度。

虚设栅极图形300位于稍后将与一个通孔200一起形成的漏电极107a的下面，并且这是有意形成的，以便减小平整层109接触在阵列部分A处形成通孔200的厚度。用来形成通孔200的蚀刻深度与在焊盘部分P处的蚀刻深度处于相同水平。虚设栅极图形300的形状不限于一个特定的形状，

而是可以用任何可容许的变化来更改。

形成于焊盘部分 P 处的栅电极 105a 使得焊盘 107b 的接触电阻降低，该焊盘还与图 2 的焊盘电极 18 相对应，并能够通过通孔 200 与外部电源电耦连。

5 层间绝缘层 106 直接反映 (reflect) 下层结构的拓扑。也就是说，层间绝缘层 106 在虚设栅极图形 300 和栅电极 105a 和 105b 之上的部分位于一个高于它的其他部分的平面上。

源电极 107c 和漏电极 107a 以及焊盘 107b 由铝 (Al) 制成，并形成于层间绝缘层 106 上具有预定宽度。在阵列部分 A 处的源电极 107c 和漏电极 10 107a 分别与多晶硅层 103 的下源极区 103c 和下漏极区 103a 相连。

第一和第二绝缘钝化层 108 和 109 形成于层间绝缘层 106 的整个表面以及源和漏电极 107a 和 107c 及焊盘 107b 之上，以便使其顶面 109 变平。

15 为了制得第一和第二绝缘钝化层 108 和 109，第一绝缘钝化层 108 形成为具有均匀的厚度，从而其直接反映下层结构的拓扑，并且在该钝化层上形成具有平的顶面的第二绝缘钝化层 109。第一和第二绝缘钝化层 108 和 109 分别具有一个在晶片整个区域之上的平的顶面，以便进行随后的用来形成通孔 200 的构图工艺。

20 第一和第二绝缘钝化层 108 和 109 分别具有经有选择地蚀刻、并分别使漏电极 107a 和焊盘 107b 以预定程度露出的通孔 200，并且一层导电层 110 充满通孔 200，同时置于其上。

在阵列部分 A 处的通孔 200 将像素电极 110 连接至下层金属元件漏电极 107a 上，而在焊盘部分 P 处的通孔 200 将焊盘电极 19 连接至下层金属元件或焊盘 107b 上。

25 置于阵列部分 A 处的含有通孔 200 的第一和第二绝缘钝化层 108、109 与位于焊盘部分 P 处的含有通孔 200 的第一和第二绝缘钝化层厚度相同。因此，在阵列部分 A 处的和在焊盘部分 P 处的用来形成通孔 200 的第一和第二绝缘钝化层 108、109 的蚀刻深度相同。

30 与图 1 所示的其中 T1 和 T2 不同的传统设计相比，在焊盘部分 P 处的蚀刻深度 D1 和在阵列部分 A 处的蚀刻深度 D2 相同，上述蚀刻深度不包括第一绝缘钝化层 108 的均匀厚度，而是仅仅包括第二绝缘钝化层 109 的厚度。在焊盘部分 P 处接触通孔 200 的绝缘钝化层的厚度与在阵列部分 A 处

接触通孔 200 的绝缘钝化层的厚度相同。

因此,当第一和第二绝缘钝化层 108、109 被蚀刻以便形成通孔 200 时,在阵列部分 A 处的漏电极 107a 和在焊盘部分 P 处的焊盘 107b 同时暴露。因此,保护了在焊盘部分 P 处的焊盘 107b 不被过度蚀刻。

5 像素限定层 111 形成于导电层 110 和平整层 109 上,并被有选择地蚀刻以便形成像素区 112。一层有机 EL 薄膜 113 形成于每个像素区 112 上。

图 4 图示出根据本发明另一个实施例而构造的有机 EL 显示器 35。与图 3 所示的其中虚设栅极图形 300 形成于阵列部分 A 上的 EL 显示器 25 相比,根据本发明该另一个实施例构造的 EL 显示器 35 在焊盘部分 P 上没有 10 先前在图 3 中示出的栅电极 105a。

在 EL 显示器 35 中,省掉了图 3 在焊盘部分 P 处的栅电极 105a,同时减小了表面阶梯,从而消除了在焊盘部分 P 和阵列部分 A 之间接触通孔 200 的第一和第二绝缘钝化层 108、109 的厚度差异。

因此,焊盘部分 P 的蚀刻深度 D3 与阵列部分 A 处的蚀刻深度 D4 相同, 15 该蚀刻深度 D3、D4 不包括第一绝缘层 108 的厚度而仅仅包括第二绝缘层 109 的厚度。与第一实施例的情况相比, D3 大于 D1。

如上所述,在阵列部分上形成虚设栅极图形,或者省去焊盘部分上的栅电极,以便消除阵列部分和焊盘部分之间的钝化层的厚度差异,由此,保护了源和漏电极或者焊盘不被过度蚀刻。

20 尽管在上文中已经对本发明的优选实施例进行了详细地描述,但是应当清楚理解的是,对在此所教导的基本发明构思的许多改变和/或改进对于本领域普通技术人员来说是显而易见的,仍然落在由所附权利要求所限定的本发明的精神和范围之内。

图 1

图 2

图 3

图 4

|                |                                                                                          |         |            |

|----------------|------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机电致发光显示器                                                                                |         |            |

| 公开(公告)号        | <a href="#">CN1592520A</a>                                                               | 公开(公告)日 | 2005-03-09 |

| 申请号            | CN200410068283.X                                                                         | 申请日     | 2004-08-27 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                              |         |            |

| 申请(专利权)人(译)    | 三星SDI株式会社                                                                                |         |            |

| 当前申请(专利权)人(译)  | 三星SDI株式会社                                                                                |         |            |

| [标]发明人         | 朴商一<br>姜泰旭                                                                               |         |            |

| 发明人            | 朴商一<br>姜泰旭                                                                               |         |            |

| IPC分类号         | H01L51/50 G09F9/30 H01L21/77 H01L21/84 H01L27/32 H05B33/22 H05B33/12 H05B33/08 H05B33/02 |         |            |

| CPC分类号         | H01L27/1248 H01L27/3244 H01L27/1214 H01L27/3248 H01L27/3276 H01L27/3223 H01L27/124       |         |            |

| 代理人(译)         | 侯宇                                                                                       |         |            |

| 优先权            | 1020030060016 2003-08-28 KR                                                              |         |            |

| 其他公开文献         | <a href="#">CN100449773C</a>                                                             |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>                                           |         |            |

## 摘要(译)

一种有机电致发光显示器包括一个衬底，该衬底具有一个具有像素的阵列部分和一个耦连至外部电源的焊盘部分。在衬底上形成具有源电极、漏电极和焊盘的半导体结构。在该半导体结构上形成一层具有通孔的钝化层，该通孔露出在阵列部分上的源和漏电极的区域以及在焊盘部分上的焊盘的区域。接触通孔的钝化层部分在阵列部分和焊盘部分之间具有相同的厚度。一层导电层填充该通孔。一层像素限定层形成于一层平整层和导电层的整个表面上，其在所述阵列部分上具有露出导电层的区域的像素区。一个有机电致发光薄膜形成于每个像素区上。本发明通过减小阵列部分和焊盘部分之间的钝化层的厚度差异，防止了源电极和漏电极被蚀刻过度。