(12) 发明专利

(10) 授权公告号 CN 101978412 B

(45) 授权公告日 2014. 08. 20

(21) 申请号 200980109383. 3

(51) Int. Cl.

(22) 申请日 2009. 11. 27

G09G 3/32(2006. 01)

(30) 优先权数据

2008-305714 2008. 11. 28 JP

(56) 对比文件

(85) PCT国际申请进入国家阶段日

2010. 09. 16

US 2008111812 A1, 2008. 05. 15, 全文 .

CN 1989539 A, 2007. 06. 27, 全文 .

审查员 朱琼

(86) PCT国际申请的申请数据

PCT/JP2009/070370 2009. 11. 27

(87) PCT国际申请的公布数据

W02010/061975 EN 2010. 06. 03

(73) 专利权人 卡西欧计算机株式会社

地址 日本东京都

(72) 发明人 小仓润 武居学 横山俊二

(74) 专利代理机构 永新专利商标代理有限公司

72002

代理人 陈松涛 蹇炜

权利要求书5页 说明书24页 附图19页

(54) 发明名称

一种像素驱动设备、发光设备和像素驱动设备中的特性参数获取方法

(57) 摘要

一种像素驱动设备，具有：电压施加电路(14)、电压测量电路(114)、以及特性参数获取电路(16)，电压施加电路输出超过驱动晶体管(T3)的阈值电压的参考电压(Vref)，特性参数获取电路获取与像素的电特性相关的特性参数。像素驱动设备在具有电致发光元件(101)和驱动晶体管的像素上施加参考电压。在从参考电压被切断起，多个沉降时间中的每一个消逝后，电压测量电路获取信号线(Ld)的电压作为测得的电压。特性参数获取电路基于电压测量电路获取的多个测得的电压的值，获取驱动晶体管的阈值电压和电流放大因子作为特性参数。

B

CN

101978412

1. 一种用于驱动像素(21(i, j))的像素驱动设备,所述像素(21(i, j))连接至信号线(Ld),并包括发光元件(101)、和像素驱动电路(DC),所述像素驱动电路(DC)具有驱动晶体管(T3)和保持电容(Cs),所述驱动晶体管用于控制供应至所述发光元件的电流,且所述驱动晶体管的电流路径的一端连接至所述发光元件的一个端子,所述保持电容用于通过施加于所述驱动晶体管的控制端子上的电压来储存电荷,所述像素驱动设备包括:

电压施加电路(14),用于输出参考电压(Vref);

电压测量电路(114);

开关电路(Sw3),用于在所述电压施加电路和所述电压测量电路之间切换所述信号线的一端的连接;以及

特性参数获取电路(16),用于获取与所述像素的电特性相关的特性参数;

其中,

所述参考电压具有的电位使得,所述驱动晶体管的所述电流路径的所述一端相对于另一端的电位差是超过所述驱动晶体管的阈值电压(Vth)的值;以及

所述开关电路将所述信号线的所述一端连接至所述电压施加电路,并在通过所述电压施加电路在所述信号线的所述一端上施加所述参考电压达预定的时间后将所述信号线的所述一端和所述电压施加电路之间的连接设定为中断,且在预定的沉降时间消逝后将所述信号线的所述一端连接至所述电压测量电路;以及

当通过所述开关电路将所述电压测量电路连接至所述信号线的所述一端时,所述电压测量电路获取所述信号线的所述一端的电压值作为所测得的电压;以及

基于所述电压测量电路获取的针对多个所述沉降时间的多个所测得的电压的值,所述特性参数获取电路获取所述驱动晶体管的所述阈值电压和所述像素驱动电路的电流放大因子作为特性参数。

2. 如权利要求1所述的像素驱动设备,其中

将多个沉降时间设定为比  $C/\beta_0$  大的值,其中, C 是总电容,所述总电容为所述保持电容、寄生于信号线上的寄生电容、以及寄生于所述发光元件上的发光元件电容的和,且  $\beta_0$  是所述电流放大因子的参考值。

3. 如权利要求2所述的像素驱动设备,其中

所述电流放大因子的所述参考值是所述电流放大因子的典型值或设计值。

4. 如权利要求2所述的像素驱动设备,其中

当所述沉降时间为 t 时,通过将多个所述沉降时间的每一个和多个所测得的电压的值的每一个代入方程(1),所述特性参数获取电路获取所述阈值电压和所述电流放大因子,其中,所测得的电压为 Vmeas(t)、所述阈值电压为 Vth、以及所述电流放大因子为  $\beta$ ,

$$(1) \dots V_{meas}(t) = V_{th} + \frac{(C/\beta)}{t}.$$

5. 如权利要求1所述的像素驱动设备,还包括:

信号校正电路(16),其基于所述特性参数获取电路获取的所述特性参数校正所供应的图像数据并生成校正的灰度信号;以及

驱动信号施加电路(118),用于基于所校正的灰度信号生成驱动信号并将所述驱动信号施加于所述信号线的所述一端上。

6. 一种发光设备,包括:

至少一个像素(21(i, j)),所述至少一个像素连接至至少一个信号线(Ld),并包括发光元件(101)、和像素驱动电路(DC),所述像素驱动电路(DC)具有驱动晶体管(T3)和保持电容(Cs),所述驱动晶体管用于控制供应至所述发光元件的电流,且所述驱动晶体管的电流路径的一端连接至所述发光元件的一个端子,所述保持电容用于通过施加于所述驱动晶体管的电流控制端子上的电压来储存电荷;

电压施加电路(14),用于输出参考电压(Vref);

电压测量电路(114);

开关电路(Sw3),用于切换所述信号线的一端和所述电压测量电路的连接;以及

特性参数获取电路(16),用于获取与所述像素的电特性相关的特性参数;

其中,

所述参考电压具有的电位使得,所述驱动晶体管的所述电流路径的所述一端和另一端之间的电位差是超过所述驱动晶体管的阈值电压的值;以及

所述开关电路将所述信号线的所述一端连接至所述电压施加电路,并在通过所述电压施加电路在所述信号线的所述一端上施加所述参考电压达预定的时间后将所述信号线的所述一端和所述电压施加电路之间的连接设定为中断,且在预定的沉降时间消逝后将所述信号线的所述一端连接至所述电压测量电路;以及

当通过所述开关电路将所述电压测量电路连接至所述信号线的所述一端时,所述电压测量电路获取所述信号线的所述一端的电压值作为所测得的电压;以及

基于所述电压测量电路获取的针对多个所述沉降时间的多个所测得的电压的值,所述特性参数获取电路获取所述驱动晶体管的所述阈值电压和所述像素驱动电路的电流放大因子作为特性参数。

7. 如权利要求6所述的发光设备,其中

多个所述信号线沿第一方向布置;

并具有沿与所述第一方向正交的第二方向布置的至少一个扫描线;

多个所述像素中的每一个布置在所述扫描线和所述多个信号线的每个交点附近;

所述发光设备具有选择驱动电路,用于通过在所述扫描线上施加选择的信号来设定连接至所述扫描线的多个所述像素的选择的状态;以及

特性参数获取电路获取处于所述选择驱动电路所选择的状态中的多个所述像素的所述特性参数。

8. 如权利要求7所述的发光设备,其中

所述像素驱动电路包括:至少,

第一薄膜晶体管(T3),预定的电源电压施加于所述第一薄膜晶体管的电流路径的一端上,并且所述第一薄膜晶体管具有将所述电流路径的另一端连接至所述发光元件的所述一个端子的连接点;

第二薄膜晶体管(T1),其控制端子连接至所述扫描线,所述第二薄膜晶体管的电流路径的一端连接至所述第一薄膜晶体管的所述电流路径的所述一端,并且所述第二薄膜晶体管的所述电流路径的另一端连接至所述第一薄膜晶体管的控制端子;以及

第三薄膜晶体管(T2),其控制端子连接至所述扫描线,所述第三薄膜晶体管的电流路

径的一端连接至所述信号线,且所述第三薄膜晶体管的所述电流路径的另一端连接至所述连接点;

其中,

所述第一薄膜晶体管对应于所述驱动晶体管,

并且在所述像素处于所述选择驱动电路选择的状态时,所述第二薄膜晶体管和所述第三薄膜晶体管进入导通状态,所述第一薄膜晶体管的所述电流路径的所述一端与所述第一薄膜晶体管的所述控制端子连接,并且所述信号线通过所述第三薄膜晶体管的所述电流路径连接至所述连接点,由此,从所述电压施加电路供应的所述参考电压通过所述第三薄膜晶体管施加于所述连接点上;以及

在每个沉降时间消逝后,所述电压测量电路经由所述第三薄膜晶体管和每个信号线获取布置在所述第二方向上的处于选择的状态中的每个所述像素的所述连接点的电压作为所测得的电压。

9. 如权利要求 6 所述的发光设备,其中

将所述沉降时间设定为多个比  $C/\beta_0$  大的不同规定值,其中, C 是总电容,所述总电容为所述保持电容、寄生于信号线上的寄生电容、以及寄生于所述发光元件上的发光元件电容的和,且  $\beta_0$  是所述电流放大因子的参考值。

10. 如权利要求 9 所述的发光设备,其中

所述电流放大因子的所述参考值是所述电流放大因子的典型值或设计值。

11. 如权利要求 9 所述的发光设备,其中

当所述沉降时间为 t 时,通过计算多个所述沉降时间 t 和方程(2) 中描述的多个所测得的电压  $V_{meas}(t)$  的值,所述特性参数获取电路获取所述阈值电压和所述电流放大因子,其中,所测得的电压为  $V_{meas}(t)$ 、所述阈值电压为  $V_{th}$ 、以及所述电流放大因子为  $\beta$ ,

$$(2) \dots V_{meas}(t) = V_{th} + \frac{(C/\beta)}{t}.$$

12. 如权利要求 6 所述的发光设备,还包括:

信号校正电路(16),其基于所述特性参数获取电路获取的所述特性参数校正所供应的图像数据并生成校正的灰度信号;以及

驱动信号施加电路(118),用于基于所校正的灰度信号生成驱动信号并将所述驱动信号施加于所述信号线的所述一端上。

13. 一种用于驱动像素(21(i, j))的像素驱动设备中的特性参数获取方法,所述像素连接至信号线(Ld),并包括发光元件(101)、和像素驱动电路(DC),所述像素驱动电路(DC)具有驱动晶体管(T3)和保持电容(Cs),所述驱动晶体管的电流路径的一端连接至所述发光元件的一个端子,用于控制供应至所述发光元件的电流,所述保持电容用于通过施加于所述驱动晶体管的控制端子上的电压来储存电荷,所述方法包括:

参考电压施加步骤,通过将电压施加电路(14)连接至所述信号线的一端,在所述信号线的所述一端上施加参考电压(Vref),使得所述驱动晶体管的所述电流路径的一端相对于另一端的电位差是超过所述驱动晶体管的阈值电压的值;

测量电压获取步骤,其中断所述信号线的一端和所述电压施加电路之间的连接,然后在所述中断后在预定的多个不同沉降时间的每一个消逝后,获取所述信号线的一端的电压

作为多个测得的电压；以及

特性参数获取步骤，其基于获取的针对所述多个不同沉降时间的所述多个测得的电压的值获取所述驱动晶体管的所述阈值电压和所述像素驱动电路的电流放大因子作为特性参数。

14. 如权利要求 13 所述的像素驱动设备中的特性参数获取方法，其中

测量电压获取步骤包括用于将多个沉降时间设定为多个比  $C/\beta_0$  大的规定值的步骤，其中，C 是总电容，所述总电容为所述保持电容、寄生于信号线上的寄生电容、以及寄生于所述发光元件上的发光元件电容的和，且  $\beta_0$  是所述电流放大因子的参考值。

15. 如权利要求 14 所述的特性参数获取方法，其中

所述特性参数获取步骤包括：

当所述沉降时间为 t 时，将所述多个沉降时间 t 的每一个和所述多个测得的电压的值代入方程(3)中描述的  $V_{meas}(t)$  的步骤，其中，所测得的电压为  $V_{meas}(t)$ 、所述阈值电压为  $V_{th}$ 、以及所述电流放大因子为  $\beta$ ；以及

通过基于所述沉降时间和方程(3)中描述的所述多个测得的电压的值执行计算，获取所述阈值电压和所述电流放大因子的值，

$$(3) \dots V_{meas}(t) = V_{th} + \frac{(C/\beta)}{t}.$$

16. 一种发光设备，包括：

像素(21(i, j))，所述像素连接至信号线(Ld)，并具有发光元件(101)、驱动晶体管(T3)和保持电容(Cs)，所述驱动晶体管具有电流路径和控制端子，且将所述电流路径的一端连接至所述发光元件的一个端子，并基于在所述控制端子和所述电流路径的所述一端之间写入的电压数据控制通过所述电流路径供应至所述发光元件的电流，所述保持电容储存通过施加于所述驱动晶体管上的电压确定的电荷；

电压测量电路(114)，用于获取电压值作为所述信号线的一端的测得的电压；以及

特性参数获取电路(16)，用于获取与所述像素的电特性相关的特性参数；

其中，

在经由所述信号线的所述一端将电压施加于所述驱动晶体管的所述电流路径的两端以使得所施加的电压超过所述驱动晶体管的所述阈值电压后，在从所述信号线处于高阻抗状态而停止所施加的电压的时刻起消逝的时间等于沉降时间 t 时，所述电压测量电路获取方程(4)中所表示的所述信号线的所述一端的电压的电压值作为所测得的电压，并且其中，C 是总电容，且为所述信号线连接的所述像素的所述保持电容、寄生于所述信号线上的寄生电容、以及寄生于所述发光元件上的发光元件电容的和；以及

所述特性参数获取电路基于当所述沉降时间 t 是满足条件  $(C/\beta)/t < 1$  的多个不同值时所述测量电路获取的多个所测得的电压，获取所述驱动晶体管的所述阈值电压和  $C/\beta$  值作为特性参数，

$$(4) \dots V_{meas}(t) = V_{th} + \frac{1}{\frac{t}{(C/\beta)} + \frac{1}{V_{ref} - V_{th}}}$$

其中，t：沉降时间，

V<sub>meas</sub>(t) :所述电压测量电路在消逝的沉降时间 t 获取的测得的电压，

V<sub>th</sub> :所述驱动晶体管的所述阈值电压，

V<sub>ref</sub> :参考电压，

C :总电容( $C = C_s + C_p + C_{el}$ )，

C<sub>s</sub> :保持电容，

C<sub>p</sub> :配线寄生电容

C<sub>el</sub> :发光元件电容

β :常数。

17. 如权利要求 16 所述的发光设备，其中

所述特性参数获取电路通过使用根据方程(4)修改的方程(5)获取所述特性参数，

$$(5) \dots V_{meas}(t) = V_{th} + \frac{(C/\beta)}{t}.$$

## 一种像素驱动设备、发光设备和像素驱动设备中的特性参数获取方法

### 技术领域

[0001] 本发明涉及像素驱动设备、发光设备和像素驱动设备中的特性参数获取方法。

[0002] 背景技术

[0003] 近些年,对发光元件类型的显示设备(发光元件类型的显示器、发光设备)的研究和开发得到了普及,该类型的显示设备提供以矩阵形式布置发光元件的显示面板(像素阵列)作为替代液晶显示设备的下一代显示设备。

[0004] 电流驱动类型的发光元件,诸如有机电致发光元件(有机EL元件)和无机电致发光元件(无机EL元件),或发光二极管(LED)是已知的此类型的发光元件。

[0005] 与已知的液晶显示设备相比,应用有源矩阵驱动方法的发光元件类型的显示设备特别具有的特点包括较快的显示响应速度、无视角依赖性、高亮度和出众的对比度、以及高分辨率显示图像质量的能力。

[0006] 另外,发光元件类型的显示设备具有极其有利的特点:因为不像LCD设备那样,发光元件类型的显示设备不需要背光或光导板,进一步减薄薄膜变得可能。因此,可以预期将此类型的显示设备应用于将来的电子设备上。

[0007] 日本专利申请特开2002-156923号中公开了利用有源矩阵驱动方法的有机EL显示设备作为此类型的发光元件类型的显示设备,该有源矩阵驱动方法通过电压信号控制电流。

[0008] 利用有源矩阵驱动方法的有机EL显示设备给每个像素配备了为发光元件的有机EL元件,并配备了具有开关薄膜晶体管和驱动有机EL元件的电流控制薄膜晶体管的像素驱动电路。

[0009] 电流控制薄膜晶体管通过施加电压信号后施加的栅极电压来控制在电流控制薄膜晶体管的漏极和源极之间流动的电流的电流值,该电压信号具有基于电流控制薄膜晶体管的电流控制端上的每个像素的图像数据确定的电压值(以下写作“基于图像数据的电压值”)。供应至有机EL元件的此电流使得有机EL元件发光。开关薄膜晶体管执行开关以向电流控制薄膜晶体管的栅极供应基于图像数据的电压信号。

[0010] 以此方式构成的显示设备中的电流控制薄膜晶体管的特性会随着使用经历年代改变。具体地,已知在电流控制薄膜晶体管由非晶硅TFT(薄膜晶体管)构成时,作为该TFT的一个性质的阈值电压V<sub>th</sub>呈现相对大的年代变化。

[0011] 甚至在给电流控制薄膜晶体管栅极施加用于图像数据的相同灰度值的具有相同电压值的电压信号时,其中该电压信号具有通过基于图像数据的电压信号的电压值来控制显示的图像的灰度的构成,在阈值电压V<sub>th</sub>改变时,在电流控制薄膜晶体管的漏极和源极之间流动的电流的电流值也改变,由此对于图像数据的相同灰度值,改变从显示像素的有机EL元件发射的光的亮度。

[0012] 电流控制薄膜晶体管的其它特性,例如像素之间的电流放大因子β的无规性也影响显示的图像。电流控制薄膜晶体管的漏极和源极之间流动的电流的电流值与电流放大

因子  $\beta$  成比例。因此,即使每个像素的电流控制薄膜晶体管的阈值电压相同,当电流放大因子  $\beta$  值中发生源自例如制造工艺的无规性时,电流控制薄膜晶体管的漏极和源极之间流动的电流的电流值中也将产生无规性,由此在从有机 EL 元件发射的光的亮度中产生无规性。

[0013] 电流放大因子的无规性归因于迁移率的无规性。迁移率的无规性在低温多晶硅 TFT 中尤其突出,而非晶硅 TFT 中此类型的无规性相对较低。然而,即使这样,源于制造工艺的迁移率,即电流放大因子  $\beta$ ,的无规性的影响是不可避免的。

[0014] 以此方式,阈值电压  $V_{th}$  的改变和源于制造工艺的电流放大因子  $\beta$  的无规性影响显示的图像的图像数据再现性,即图像等同性。

## 发明内容

[0015] 为了控制归因于这些类型的阈值电压  $V_{th}$  的改变和源于制造工艺的电流放大因子  $\beta$  的无规性的图像质量的退化,本发明中,获取例如用于每个像素的阈值电压和电流放大因子  $\beta$  作为特性参数,并且能够基于此特性参数来校正基于供应的图像数据供应至每个像素的电压信号。

[0016] 根据本公开的像素驱动设备是用于驱动像素的像素驱动设备,所述像素连接至信号线,并包括发光元件、和像素驱动电路,像素驱动电路具有驱动晶体管和保持电容,所述驱动晶体管用于控制供应至所述发光元件的电流,且所述驱动晶体管的电流路径的一端连接至所述发光元件的一个端子,所述保持电容用于通过施加于所述驱动晶体管的控制端子上的电压储存电荷,所述像素驱动设备包括:

[0017] 电压施加电路,用于输出参考电压;

[0018] 电压测量电路;

[0019] 开关电路,用于在所述电压施加电路和所述电压测量电路之间切换所述信号线的一端的连接;以及

[0020] 特性参数获取电路,用于获取与所述像素的电特性相关的特性参数;

[0021] 其中,

[0022] 所述参考电压具有的电位使得,所述驱动晶体管的所述电流路径的所述一端相对于另一端的电位差是超过所述驱动晶体管的阈值电压的值;以及

[0023] 所述开关电路将所述信号线的所述一端连接至所述电压施加电路,并在通过所述电压施加电路在所述信号线的所述一端上施加所述参考电压达预定的时间后将所述信号线的所述一端和所述电压施加电路之间的连接设定为中断,且在预定的沉降时间消逝后将所述信号线的所述一端连接至所述电压测量电路;以及

[0024] 当通过所述开关电路将所述电压测量电路连接至所述信号线的所述一端时,所述电压测量电路获取所述信号线的所述一端的电压值作为所测得的电压;以及

[0025] 基于所述电压测量电路获取的针对所述多个沉降时间的所述多个测得的电压的值,所述特性参数获取电路获取所述驱动晶体管的所述阈值电压 和所述像素驱动电路的电流放大因子作为特性参数。

[0026] 根据本公开的第一发光设备是发光设备,包括:至少一个像素,所述至少一个像素连接至至少一个信号线,并包括发光元件、和像素驱动电路,所述像素驱动电路具有驱动晶

体管和保持电容，所述驱动晶体管用于控制供应至所述发光元件的电流，且所述驱动晶体管的电流路径的一端连接至所述发光元件的一个端子，所述保持电容用于通过施加于所述驱动晶体管的电流控制端子上的电压储存电荷：

- [0027] 电压施加电路，用于输出参考电压；

- [0028] 电压测量电路；

- [0029] 开关电路，用于切换所述信号线的一端和所述电压测量电路的连接；以及

- [0030] 特性参数获取电路，用于获取与所述像素的电特性相关的特性参数；

- [0031] 其中，

- [0032] 所述参考电压具有的电位使得，所述驱动晶体管的所述电流路径的所述一端和另一端之间的电位差是超过所述驱动晶体管的阈值电压的值；以及

- [0033] 所述开关电路将所述信号线的所述一端连接至所述电压施加电路，并在通过所述电压施加电路在所述信号线的所述一端上施加所述参考电压达预定的时间后将所述信号线的所述一端和所述电压施加电路之间的连接设定为中断，且在预定的沉降时间消逝后将所述信号线的所述一端连接至所述电压测量电路；以及

- [0034] 当通过所述开关电路将所述电压测量电路连接至所述信号线的所述一端时，所述电压测量电路获取所述信号线的所述一端的电压值作为所测得的电压；以及

- [0035] 基于所述电压测量电路获取的针对所述多个沉降时间的所述多个测得的电压的值，所述特性参数获取电路获取所述驱动晶体管的所述阈值电压和所述像素驱动电路的电流放大因子作为特性参数。

- [0036] 根据本公开的一种像素驱动设备中的特性参数获取方法是用于驱动像素的像素驱动设备中的特性参数获取方法，所述像素连接至信号线，并包括发光元件、和像素驱动电路，所述像素驱动电路具有驱动晶体管和保持电容，所述驱动晶体管的电流路径的一端连接至所述发光元件的一个端子，用于控制供应至所述发光元件的电流，所述保持电容用于通过施加于所述驱动晶体管的控制端子上的电压储存电荷，所述方法包括：

- [0037] 参考电压施加步骤，通过将电压施加电路连接至所述信号线的一端，在所述信号线的所述一端上施加参考电压，使得所述驱动晶体管的所述电流路径的一端相对于另一端的电位差是超过所述驱动晶体管的阈值电压的值；

- [0038] 测量电压获取步骤，其中断所述信号线的一端和所述电压施加电路之间的连接，然后在所述中断后在预定的多个不同沉降时间的每一个消逝后，获取所述信号线的一端的电压作为多个测得的电压；以及

- [0039] 特性参数获取步骤，其基于获取的针对所述多个沉降时间的所述多个测得的电压的值获取所述驱动晶体管的所述阈值电压和所述像素驱动电路的所述电流放大因子作为特性参数。

- [0040] 根据本公开的第二发光设备是如下发光设备，其包括：

- [0041] 像素，所述像素连接至信号线，并具有发光元件、驱动晶体管和保持电容，所述驱动晶体管具电流路径和控制端子，且将所述电流路径的一端连接至所述发光元件的一个端子，并基于在所述控制端子和所述电流路径的所述一端之间写入的电压数据控制通过所述电流路径供应至所述发光元件的电流，所述保持电容储存通过施加于所述驱动晶体管上的电压确定的电荷；

- [0042] 电压测量电路,用于获取电压值作为所述信号线的一端的测得的电压;以及

[0043] 特性参数获取电路,用于获取与所述像素的电特性相关的特性参数;

[0044] 其中,

[0045] 在经由所述信号线的所述一端将电压施加于所述驱动晶体管的所述电流路径的两端使得所述电压超过所述驱动晶体管的所述阈值电压后,从存在高阻抗状态而停止所施加的电压的时刻起消逝的时间变为沉降时间 t 时,所述电压测量电路获取方程(4)中所表示的所述信号线的所述一端的电压的电压值作为所测得的电压,并且其中,C 是总电容,且为由所述信号线连接的所述像素的所述保持电容、寄生于所述信号线上的寄生电容、以及寄生于所述发光元件上的发光元件电容的和;以及

[0046] 所述特性参数获取电路基于当所述沉降时间 t 是满足条件  $(C/\beta)/t < 1$  的多个不同值时所述测量电路获取的所述多个测得的电压,获取所述驱动晶体管的所述阈值电压和  $(C/\beta)$  值作为特性参数,

$$(4) \dots V_{meas}(t) = V_{th} + \frac{1}{\frac{t}{(C/\beta)} + \frac{1}{V_{ref} - V_{th}}}$$

- [0048] 其中,t :沉降时间,

[0049]  $V_{meas}(t)$  :所述电压测量电路在消逝的沉降时间 t 获取的测得的电压,

[0050]  $V_{th}$  :所述驱动晶体管的所述阈值电压,

[0051]  $V_{ref}$  :参考电压,

[0052] C :总电容 ( $C = C_s + C_p + C_{el}$ ),

[0053]  $C_s$  :保持电容,

[0054]  $C_p$  :配线寄生电容

[0055]  $C_{el}$  :发光元件电容

[0056]  $\beta$  :常数。

[0057] 本发明能够提供像素驱动设备、发光设备、以及像素驱动设备中的特性获取方法,像素驱动设备能够获取像素的特性以基于图像数据校正电压信号的电压值。

[0058] 本发明能够提供像素驱动设备、发光设备、以及像素驱动设备中的特性参数获取方法,像素驱动设备能够控制像素退化。

## 附图说明

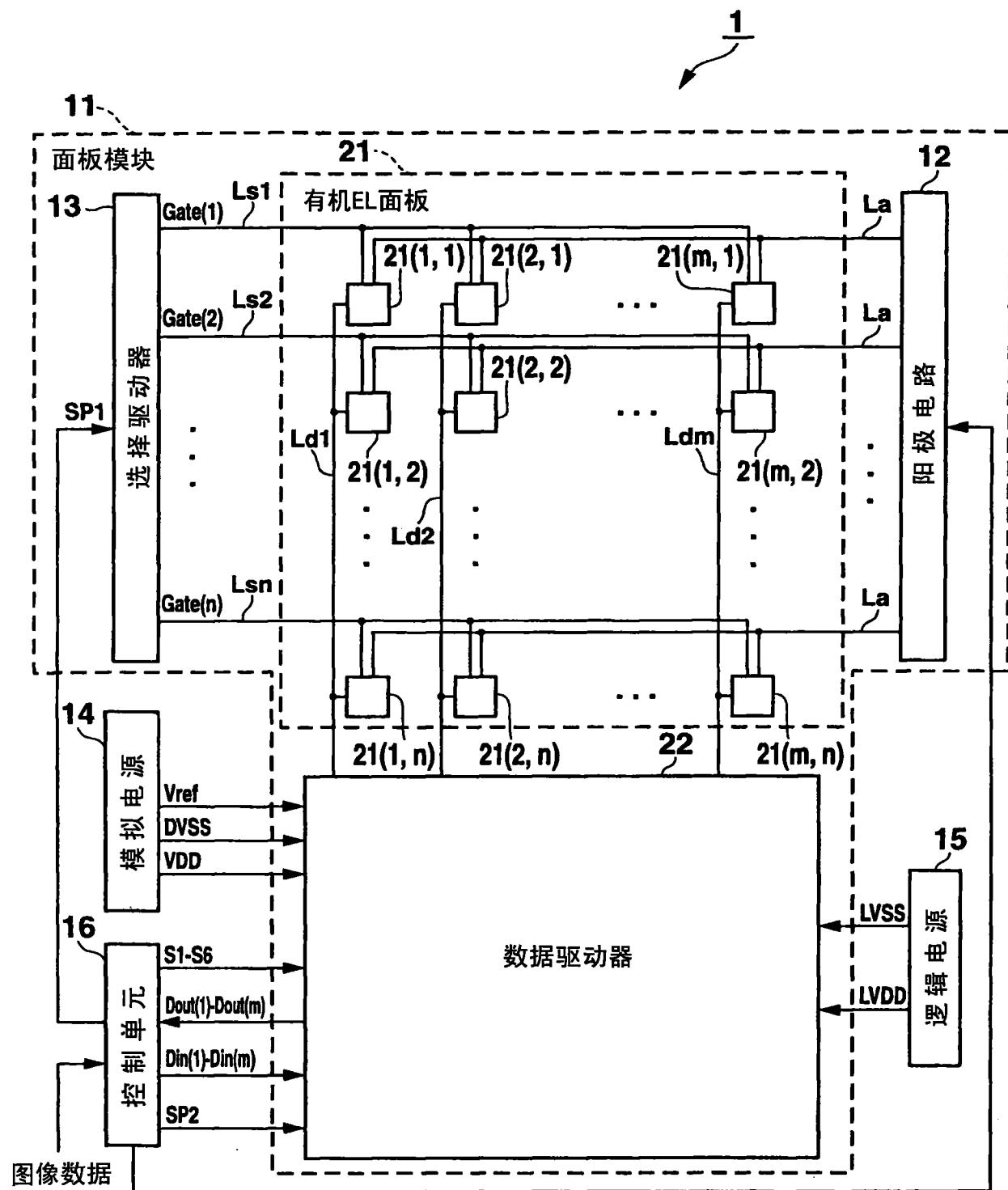

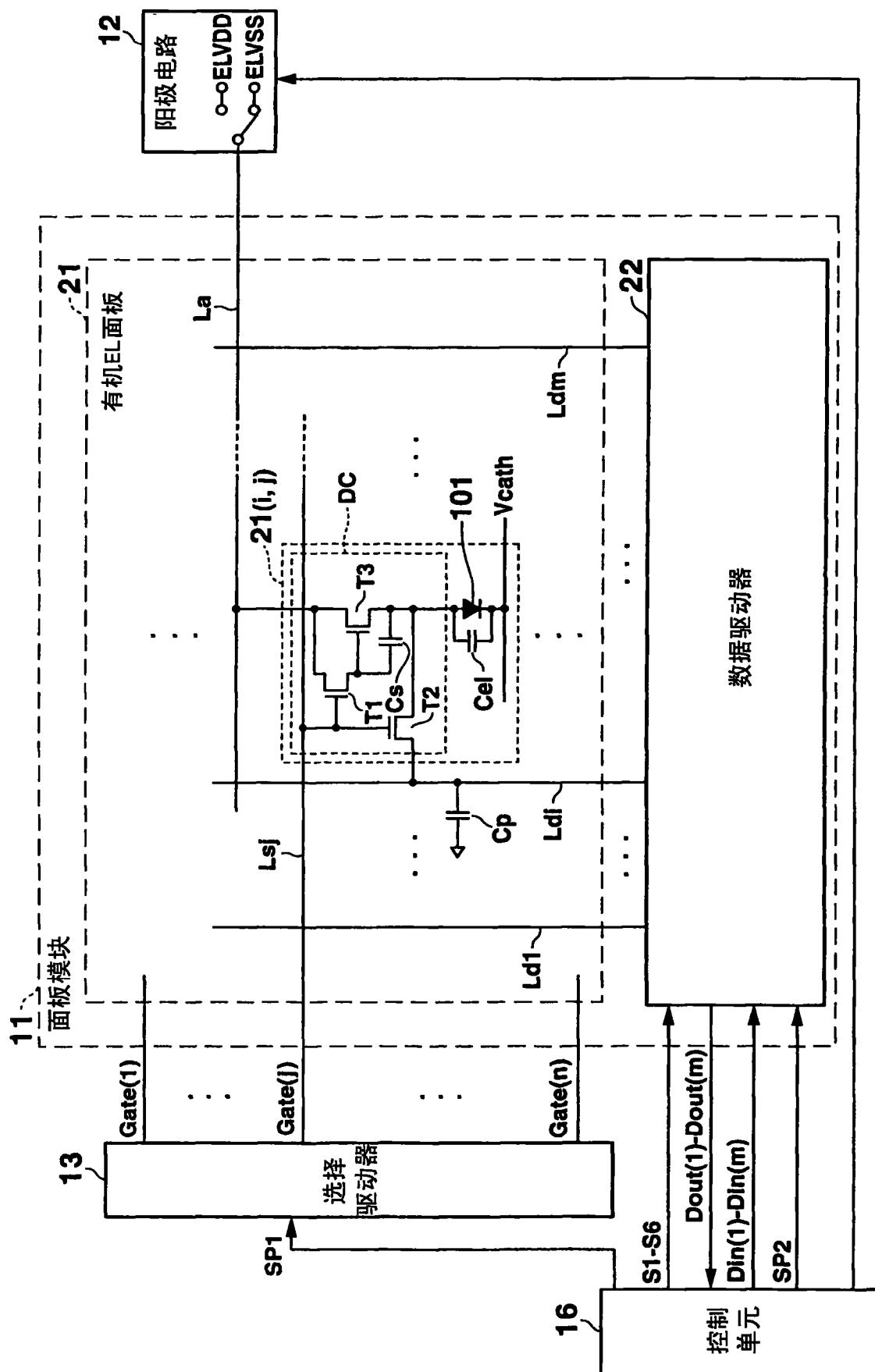

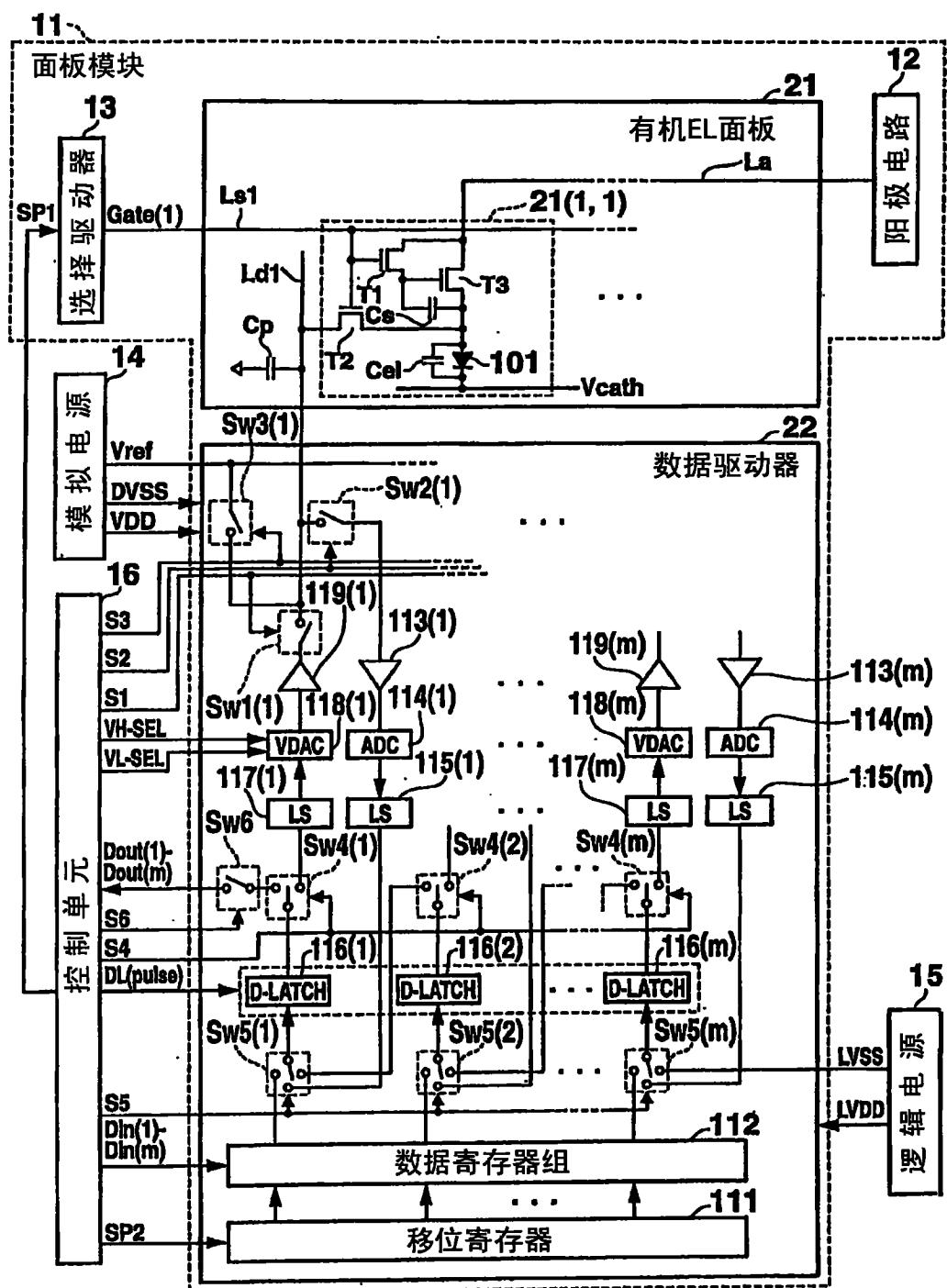

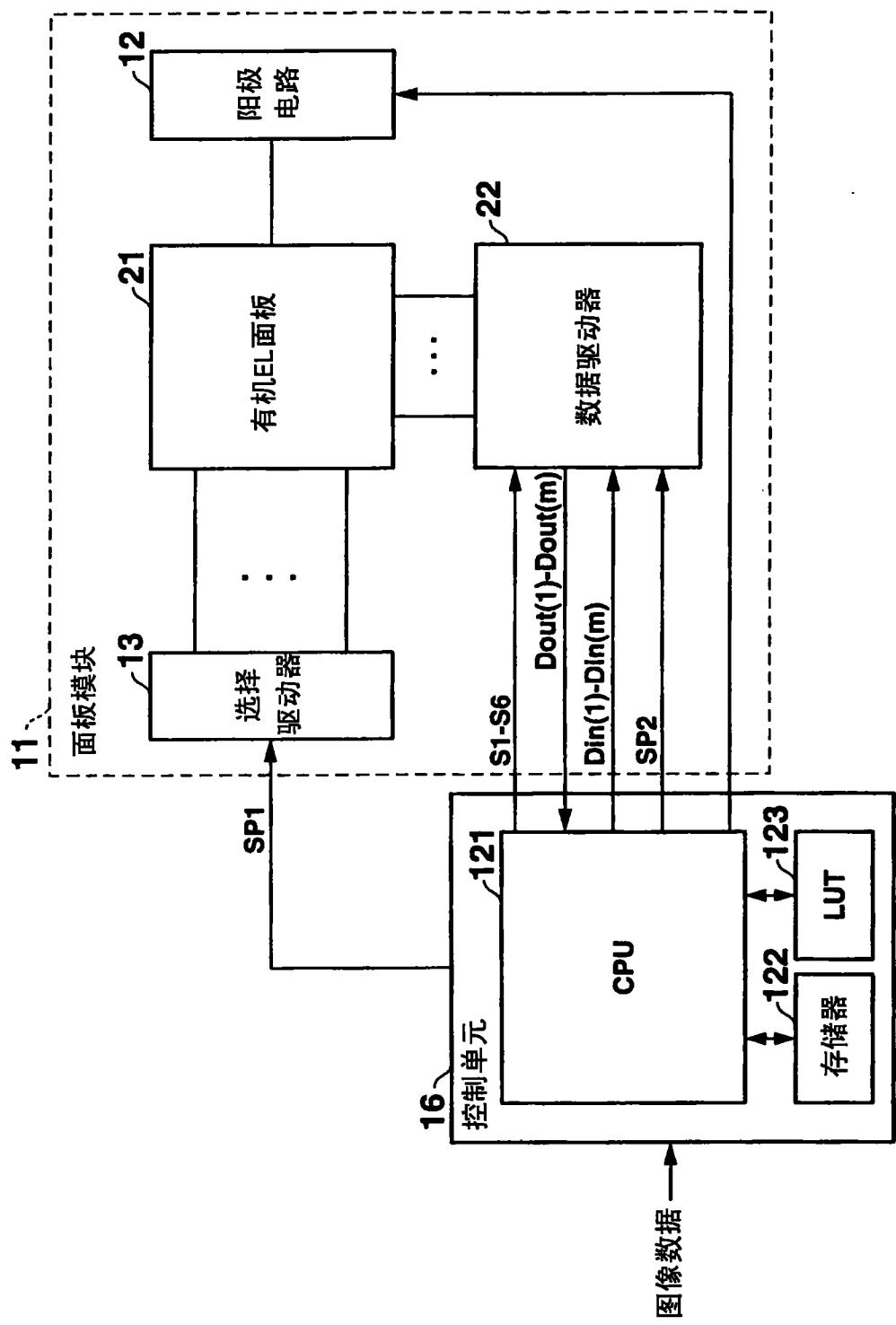

- [0059] 图 1 是示出根据本发明的实施例的显示设备的构成的框图;

[0060] 图 2 是示出图 1 中所示的有机 EL 面板和数据驱动器的构成的图样;

[0061] 图 3A 和 B 是解释像素驱动电路写入时的电压 / 电流特性的图示和曲线图;

[0062] 图 4A 和 B 是解释根据本实施例使用自动调零方法时,数据线的电压测量方法的曲线图;

[0063] 图 5 是示出图 1 中所示的数据驱动器的详细构成的框图;

[0064] 图 6A 和 B 是解释图 5 中所示的 DVAC 和 ADC 的构成和功能的图示;

[0065] 图 7 是示出图 1 中所示的控制单元的构成的框图;

[0066] 图 8 是示出图 7 中所示的存储器的每个储存区的图示;

- [0067] 图 9A 和 B 是示出图 7 中所示的 LUT 中的图像数据转换特性的范例的曲线图；

- [0068] 图 10A 和 B 是解释图 7 中所示的 LUT 中的图像数据转换特性的图示；

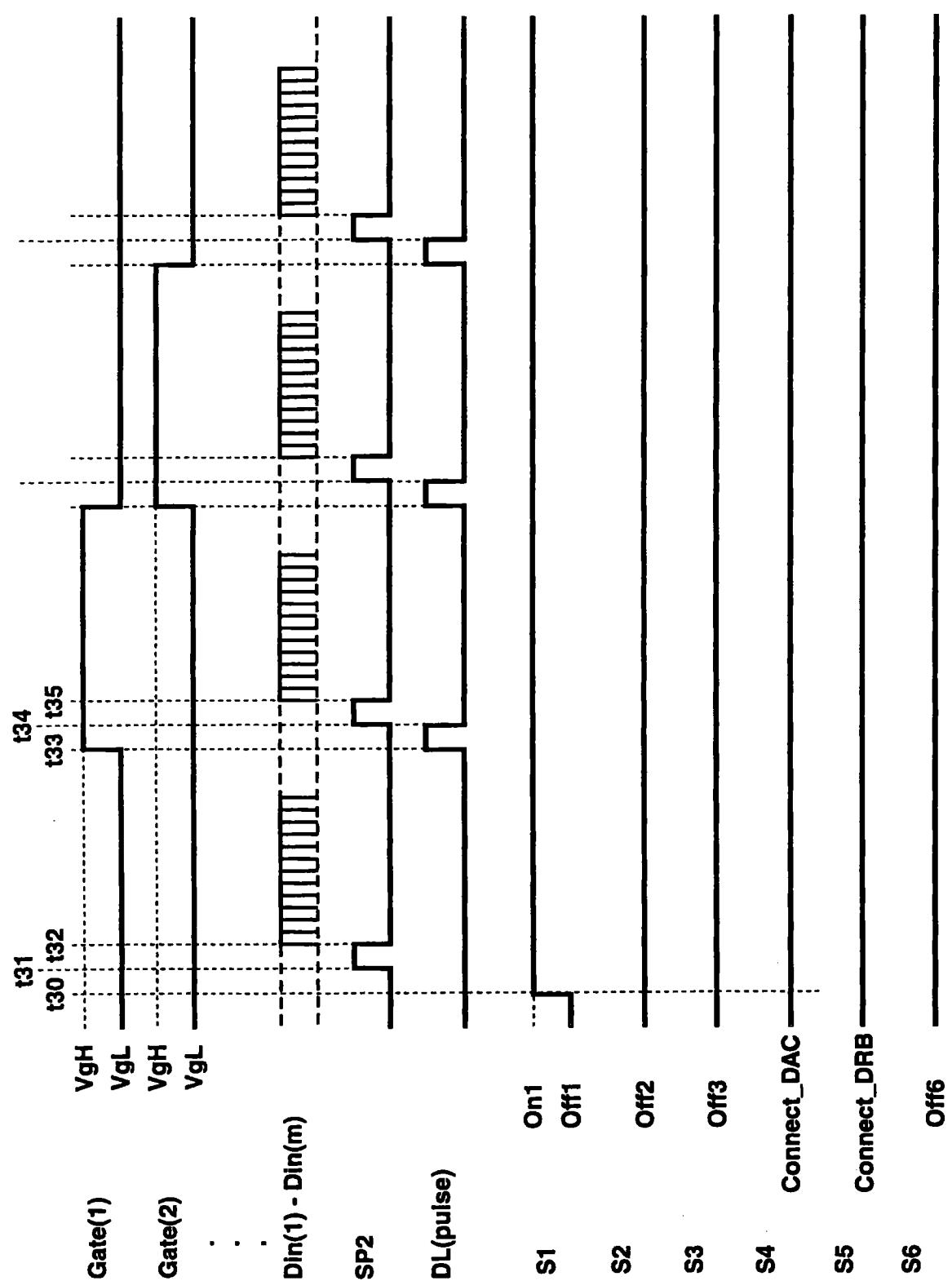

- [0069] 图 11 是示出利用自动调零方法进行电压测量时，每个部件的操作的定时图；

- [0070] 图 12A 和 B 是示出从数据驱动器向控制单元输出数据时，每个开关的连接性关系的图示；

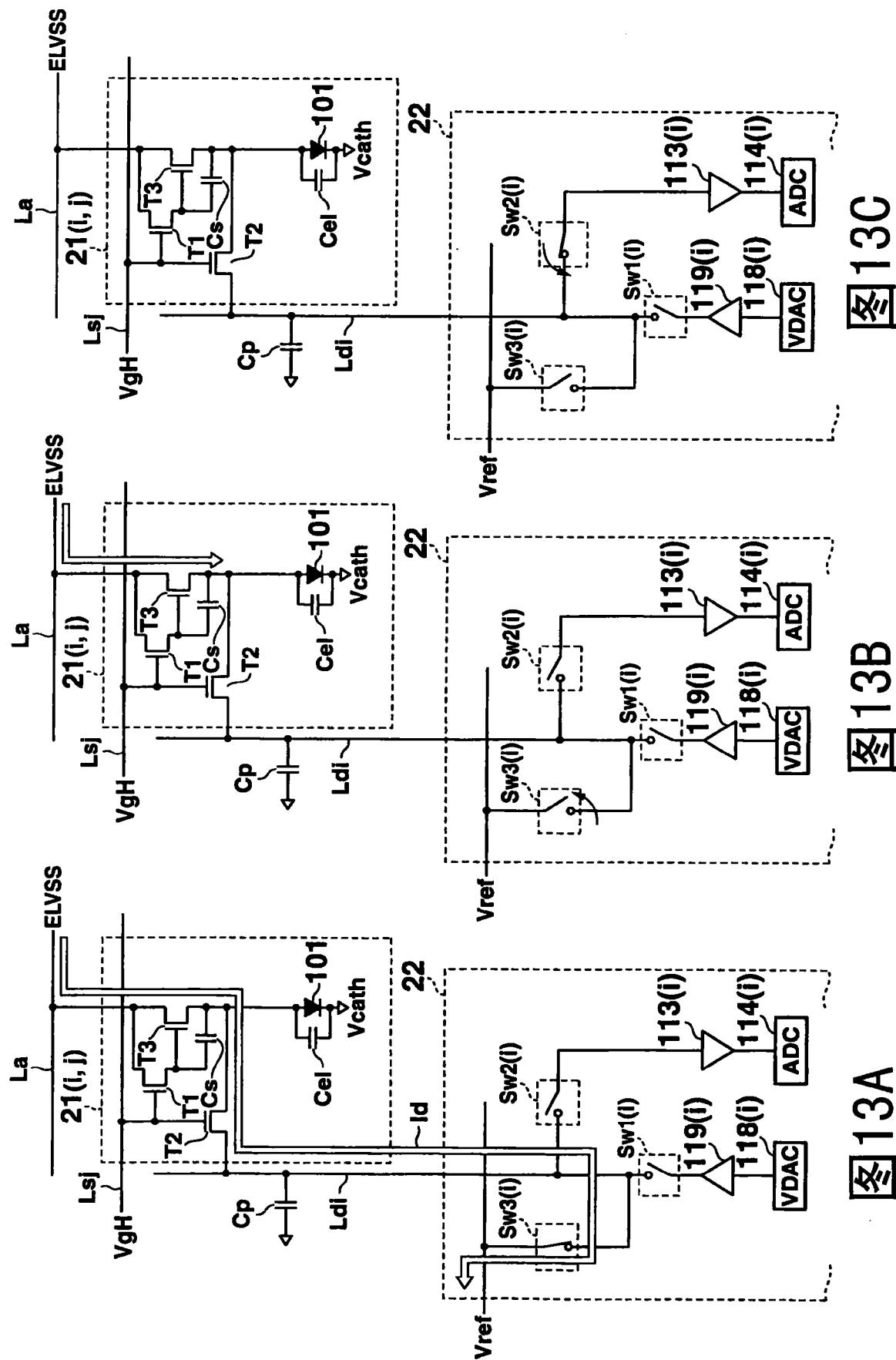

- [0071] 图 13A、B 和 C 是示出利用自动调零方法进行电压测量时，每个开关的连接性关系的图示；

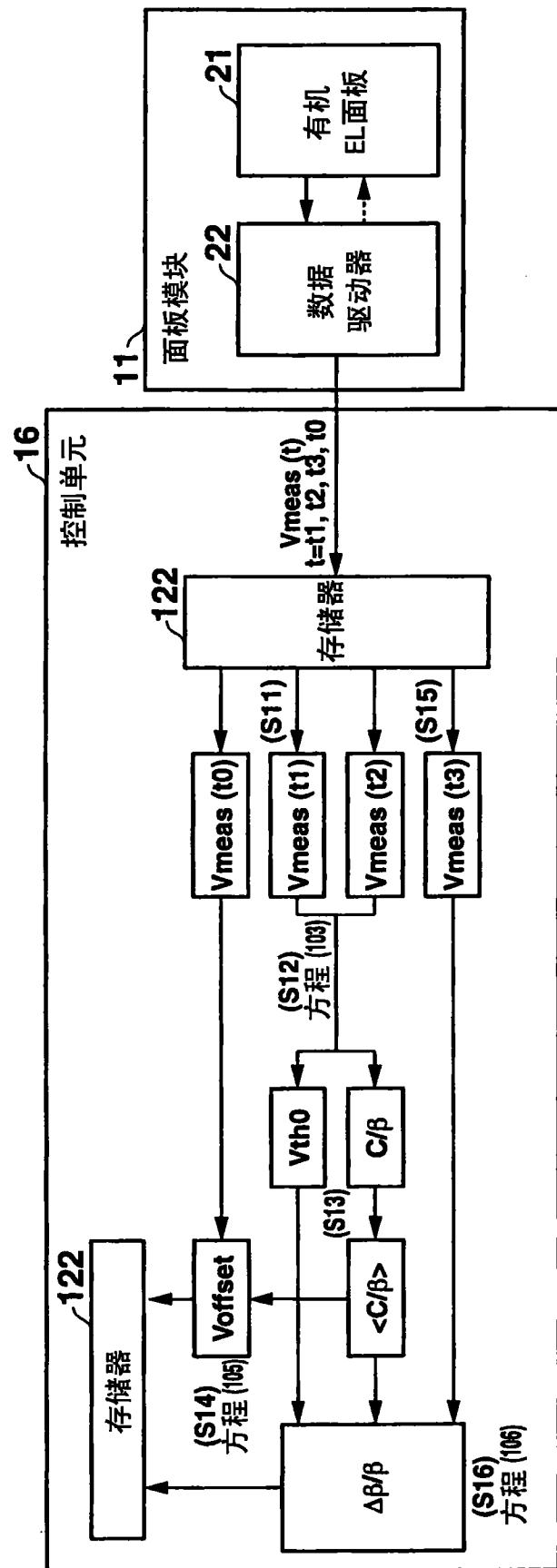

- [0072] 图 14 是解释获取特性参数用于校正时，控制单元执行的驱动顺序的图示；

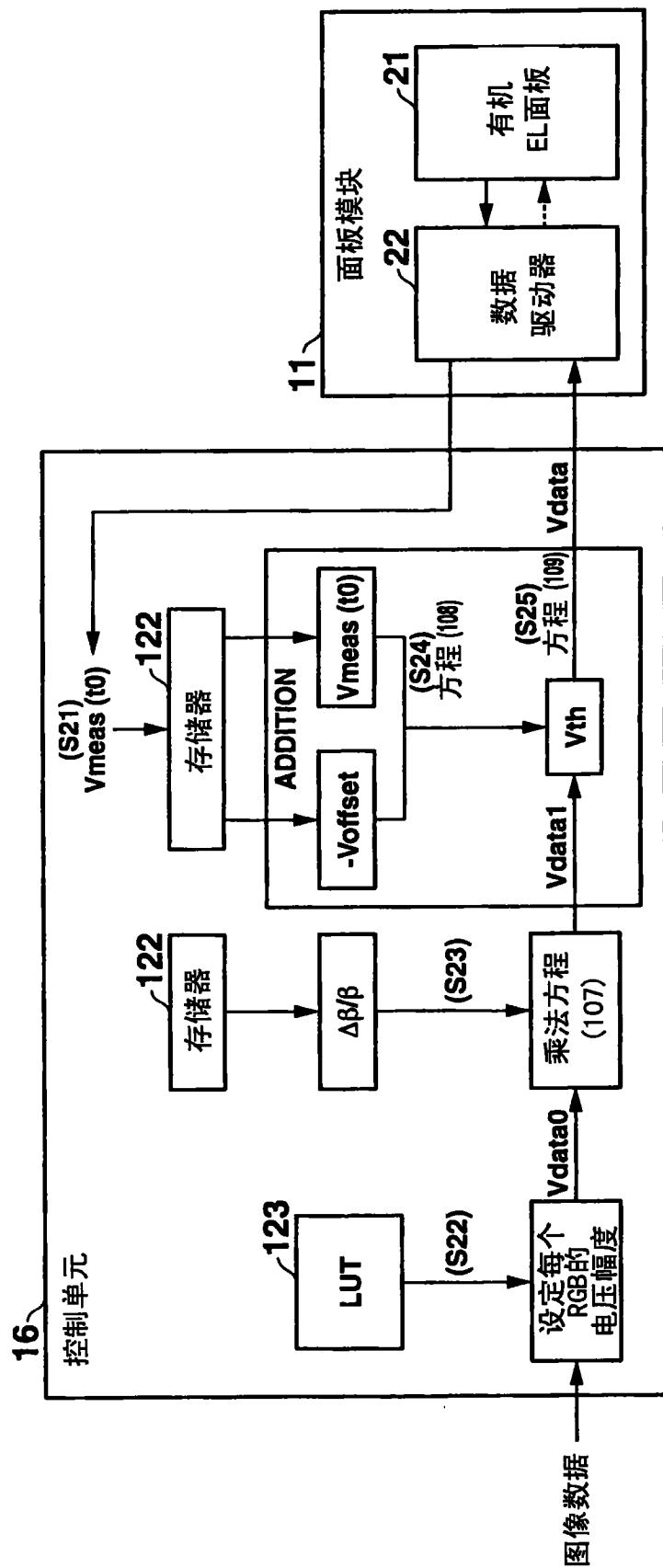

- [0073] 图 15 是解释在校正后向数据驱动器输出基于供应的图像数据的电压信号时，控制单元执行的驱动顺序的图示；

- [0074] 图 16 是示出操作时每个部件的操作的定时图；

- [0075] 图 17 是示出写入电压信号时，每个开关的连接性关系的图示；

- [0076] 图 18 是示出从控制单元向数据驱动器输入数据时，每个开关的连接性关系的图示；

### 具体实施方式

[0077] 以下将参照图样中所示出的实施例详细描述根据本发明的像素驱动设备、发光设备、以及像素驱动设备中的特性参数获取方法。另外，本实施例中发光设备描述为显示设备。

- [0078] 图 1 示出了根据本实施例的显示设备的构成。

- [0079] 根据本实施例的显示设备（发光设备）1 由面板模块 11、模拟电源（电压施加电路）14、逻辑电源 15、和控制单元（包括参数获取电路和信号校正电路）16 组成。

- [0080] 面板模块 11 提供有机 EL 面板（像素阵列）21、数据驱动器（信号线驱动电路）22、阳极电路（功率驱动电路）12、和选择驱动器（选择驱动电路）13。

- [0081] 有机 EL 面板 21 提供按行方向布置的多个数据线（信号线）Ldi ( $i = 1 \sim m$ )、按列方向布置的多个选择线（扫描线）Lsj ( $j = 1 \sim n$ )、按列方向布置的多个阳极线 La、和多个像素 21(i, j) ( $i = 1 \sim m, j = 1 \sim n, m, n : \text{自然数}$ )。像素 21(i, j) 排列在数据线 Ldi 和选择线 Lsj 的交叉点附近并分别与这些线连接。

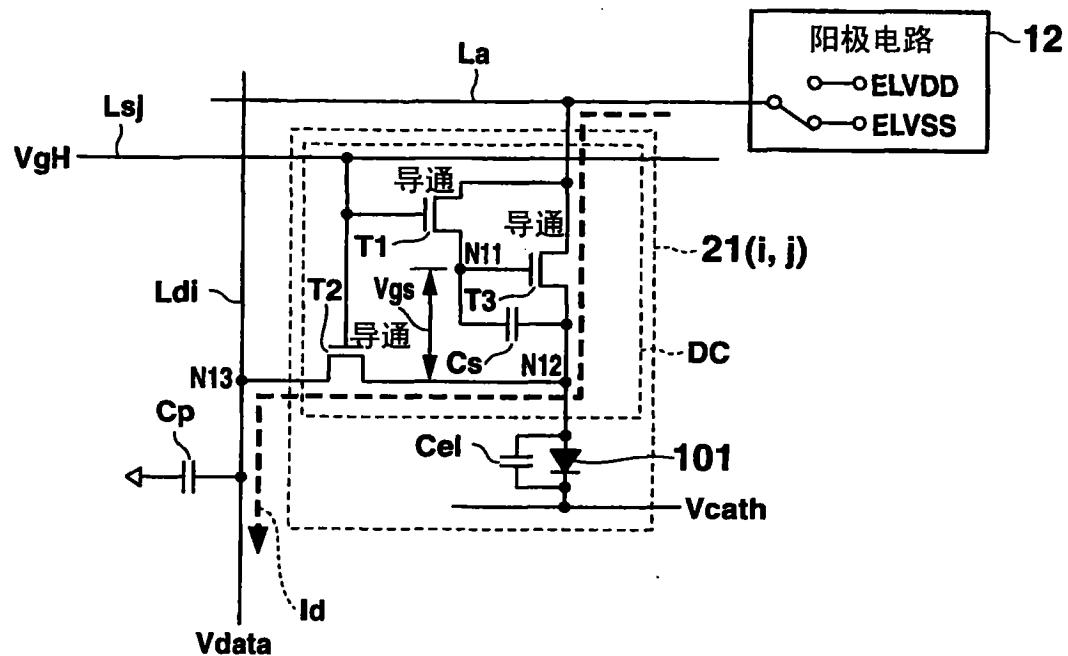

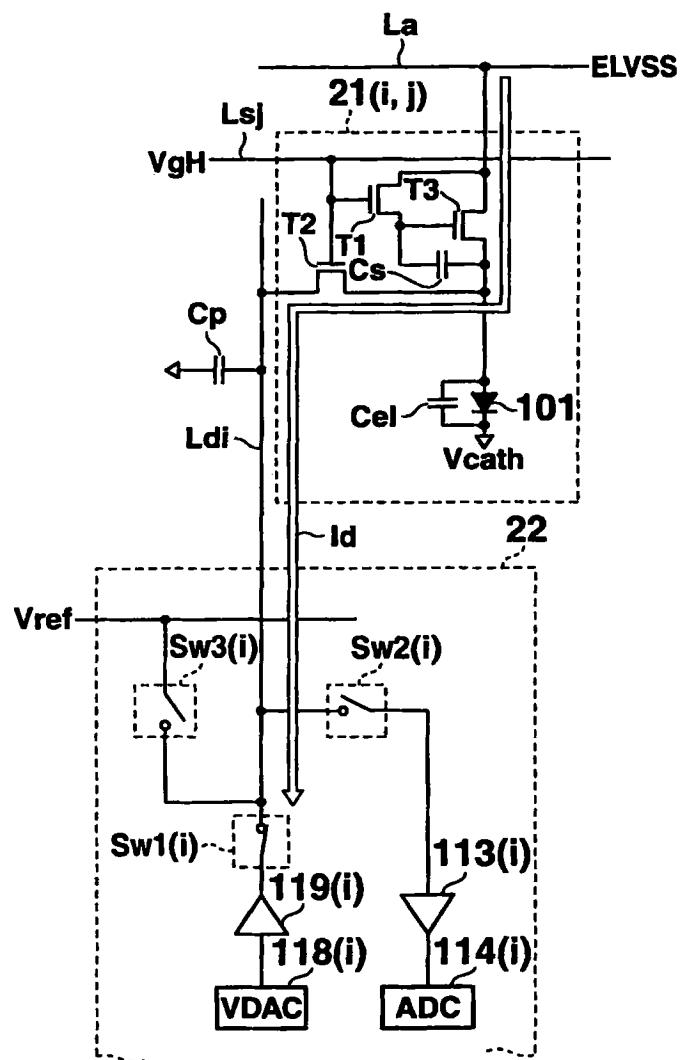

- [0082] 图 2 示出了图 1 中所示的面板模块 11 的构成的细节。每个像素 21(i, j) 示出图像的一个像素的图像数据，如图 2 中所示，其提供有机 EL 元件（发光元件 101）、和由晶体管 T1 至 T3 和保持电容 Cs 构成的像素驱动电路 DC。

- [0083] 有机 EL 元件 101 是自发光型显示元件，其使用经由激子的发光现象，该激子由空穴和注入有机化合物的电子的复合产生。以由供应至有机 EL 元件 101 的电流的电流值确定的亮度发射光。

- [0084] 像素电极形成在有机 EL 元件 101 上，且空穴注入层、发光层、和对电极按顺序形成在像素电极上。空穴注入层具有向发光层供应空穴的功能。

- [0085] 像素电极由透明或半透明导电材料组成，例如 ITO（氧化铟锡）、ZnO（氧化锌）等。每个像素电极由夹层绝缘体与其它相邻像素的像素电极绝缘。

- [0086] 空穴注入层由可运输有机聚合物材料（空穴注入 / 运输材料）组成。此外，例如，

水成 PEDOT/PSS 分散液用作含有有机聚合物的电子空穴注入 / 运输材料的有机化合物溶液, 在该分散液中, 在水介质中分散有导电聚合物、聚 3,4- 乙撑二氧噻吩 (PEDOT) 和掺杂质、聚磺苯乙烯 (PSS)。

[0087] 发光层形成在例如夹层上。像素电极和对电极分别是阳极电极和阴极电极。通过在阳极电极和阴极电极之间施加预定电压, 发光层具有发光的功能。

[0088] 发光层由发射例如红 (R)、绿 (G) 和蓝 (B) 光的发光材料形成, 包括诸如聚对苯乙炔 (polyparaphenylenevinylene) 基、氟基的共轭双键聚合物, 它们是公知的能够发射荧光或磷光的发光聚合物材料。

[0089] 此外, 通过利用喷嘴涂布方法、喷墨方法等在夹层上施加溶液 (或分散液) 并然后使溶剂挥发来形成功能层, 其中, 溶液 (或分散液) 是在合适的水成溶剂或有机溶剂中溶解 (或分散) 有上述发光材料, 有机溶剂诸如是萘满、四甲基苯、1,3,5- 三甲基苯、二甲苯。

[0090] 当发光层由红 (R)、绿 (G) 和蓝 (B) 三原色发光材料组成时, 通常将每种发光材料施加于每一列。

[0091] 对电极是由导电材料组成的两层结构, 例如诸如 Ca、Ba 等低功函数材料构成的层和诸如 Al 的反光导电层。

[0092] 电流从像素电极流向对电极, 即从阳极电极流向阴极电极, 并且不以相反方向流动。阴极电压  $V_{cath}$  施加于阴极电极上。在本实施例中, 阴极电压  $V_{cath}$  设定为 GND (地电位)。

[0093] 有机 EL 元件 101 具有有机 EL 像素电容 (光发射器电容)  $C_{el}$ 。有机 EL 像素电容  $C_{el}$  连接于等效电路上的有机 EL 元件 101 的阴极和阳极之间。

[0094] 选择驱动器 13 用于给每个选择线  $L_{sj}$  输出  $Gate(j)$  信号并选择每一列中的像素  $21(i, j)$  ( $j = 1 \sim n$ )。选择驱动器 13 提供例如移位寄存器, 并且利用此移位寄存器, 根据供应的时钟信号如图 2 中所示地顺序移位从控制单元 16 供应的开始脉冲  $SP_1$ 。选择驱动器 13 输出关于被顺序移位的开始脉冲  $SP_1$  的  $Hi$  (高) 电平信号 ( $V_{gh}$ ) 或  $Lo$  (低) 电平信号 ( $V_{gl}$ ) 作为  $Gate(1) \sim Gate(n)$  信号。

[0095] 数据驱动器 22 具有用于测量每个数据线  $L_{di}$  ( $i = 1 \sim m$ ) 的电压并获取所测得的时间  $t$  的电压  $V_{meas}(t)$  的组成, 并且具有用于施加电压信号的组成, 该电压信号具有基于每个数据线  $L_{di}$  上的所测得的电压  $V_{meas}(t)$  被校正的电压值  $V_{data}$ 。

[0096] 阳极电路 12 经由每个阳极线  $L_a$  在有机 EL 面板 21 上施加电压。阳极电路 12 如图 2 中所示地由控制单元 16 控制, 并且从而, 用于施加在阳极线  $L_a$  上的电压被切换至电压  $ELVDD$  或  $ELVSS$ 。

[0097] 电压  $ELVDD$  是在每个像素  $21(i, j)$  的有机 EL 元件 101 发光时, 施加于阳极线  $L_a$  上的显示电压。在本实施例中, 电压  $ELVDD$  是具有大于地电位的正电位的电压。

[0098] 电压  $ELVSS$  是在像素驱动电路 DC 设定为下述写入状态且执行下述自动调零方法时, 施加于阳极线  $L_a$  上的电压。在本实施例中, 电压  $ELVSS$  设定为与有机 EL 元件 101 的阴极电压  $V_{cath}$  相同的电压。

[0099] 每个像素  $21(i, j)$  中, 像素驱动电路 DC 的晶体管 T1 至 T3 是由 n 沟道型 FET (场效应晶体管) 组成的 TFT, 并且例如由非晶硅或多晶硅 TFT 组成。

[0100] 晶体管 T3 是驱动晶体管 (第一薄膜晶体管) 和电流控制薄膜晶体管, 通过基于栅

极 - 源极电压  $V_{gs}$  (以下称作栅极电压  $V_{gs}$ ) 控制安培数, 其用于向有机 EL 元件 101 供应电流。

[0101] 漏极 (端子) 连接至阳极线 La, 源极 (端子) 连接至有机 EL 元件 101 的阳极 (电极), 且漏极 - 源极是电流路径, 栅极是用于晶体管 T3 的控制端子。

[0102] 晶体管 T1 是开关晶体管 (第二薄膜晶体管), 以在执行下述写入时将晶体管 T3 连接至二极管。

[0103] 晶体管 T1 的漏极连接至晶体管 T3 的漏极, 晶体管 T1 的源极连接至晶体管 T3 的栅极。

[0104] 每个像素  $21(i, j) \sim 21(m, j)$  的晶体管 T1 的栅极 (端子) 连接至选择线  $Lsd(j = 1 \sim n)$ 。

[0105] 对于像素  $21(1, 1)$ , 当高电平  $Gate(1)$  信号  $VgH$  输出至选择线  $Ls1$  作为来自选择驱动器 13 的  $Gate(1)$  信号时, 晶体管 T1 成为导通状态。

[0106] 当低电平  $Gate(1)$  信号  $VgLH$  输出至选择线  $Ls1$  作为来自选择驱动器 13 的  $Gate(1)$  信号时, 晶体管 T1 成为截止状态。

[0107] 晶体管 2 是开关晶体管 (第三薄膜晶体管), 以在阳极电路 12 和数据驱动器 22 之间导通或中断。晶体管 T2 根据选择驱动器 13 的选择处于导通或截止状态。导通或截止状态确定阳极电路 12 和数据驱动器 22 之间的导通或中断模式。有关情形对于其它像素  $21(i, j)$  也是相同的。

[0108] 每个像素  $21(i, j)$  的晶体管 T2 的漏极连接至有机 EL 元件 101 的阳极 (电极) 和晶体管 T3 的源极。

[0109] 每个像素  $21(i, j) \sim 21(m, j)$  的晶体管 T2 的栅极连接至选择线  $Lsj(j = 1 \sim n)$ 。

[0110] 此外, 每个像素  $21(i, 1) \sim 21(i, n)$  的晶体管 T2 的源极连接至数据线  $Ldi(i = 1 \sim m)$ 。

[0111] 对于像素  $21(1, 1)$ , 在高电平  $Gate(1)$  信号 ( $VgH$ ) 作为  $Gate(1)$  信号输出 至选择线  $Ls1$  时, 晶体管 T2 成为导通状态, 由此连接数据线  $Ld1$  和有机 EL 元件 101 的阳极以及晶体管 T3 的源极。

[0112] 在 Lo 电平信号 ( $VgL$ ) 作为  $Gate(1)$  信号输出至选择线  $Ls1$  时, 晶体管 T2 成为截止状态, 并中断数据线  $Ld1$  和有机 EL 元件 101 的阳极线以及晶体管 T3 的源极之间的连接。有关情形对于其它像素  $21(i, j)$  也是相同的。

[0113] 保持电容  $Cs$  是用于保持晶体管 T3 的栅极电压  $V_{gs}$  的电容, 并经由其一个端子连接至晶体管 T1 的源极和晶体管 T3 的栅极, 经由其另一端子连接至晶体管 T3 的源极和有机 EL 元件 101 的阳极。

[0114] 晶体管 T3 中, 晶体管 T1 的源极和漏极分别连接至其栅极和漏极。当电压  $ELVSS$  由阳极电路 12 施加于阳极线 La 上、 $Hi$  电平信号 ( $VgH$ ) 由选择驱动器 13 施加于选择线  $Ls1$  上作为  $Gate(1)$  信号、且电压信号施加于数据线  $Ld1$  上时, 晶体管 T1 和晶体管 T2 处于导通状态。

[0115] 那时, 通过经由晶体管 T1 在栅极和漏极之间连接, 晶体管 T3 处于二极管连接状态。

[0116] 此外, 当那时由数据驱动器 22 将电压信号施加于数据线  $Ld1$  上时, 电压信号经由

晶体管 T2 施加于晶体管 T3 的源极上,从而,晶体管 T3 处于导通状态。随后,电压信号确定的电流从阳极电路 12 经由阳极线 La、晶体管 T3、和晶体管 T2 流向数据线 Ld1。保持电容 Cs 由此时晶体管 T3 的栅极电压 Vgs 充电,且电荷储存在保持电容 Cs 中。

[0117] 当 Lo 电平信号 (VgL) 由选择驱动器 13 施加于选择线 Ls1 上作为 Gate(1) 信号时,晶体管 T1 和 T2 成为截止状态。那时,保持电容 Cs 保持晶体管 T3 的栅极电压 Vs。有关情形对于其它像素 21(i, j) 也是相同的。

[0118] 另外,在有机 EL 面板 21 内还存在导线寄生电容 Cp。导线寄生电容 Cp 主要产生于数据线 Ld1 ~ Ldm 和选择线 Ls1 ~ Lsn 的交叉点处。

[0119] 根据本实施例的显示设备 1 利用自动调零方法测量数据线电压多次作为每个像素 21(i, j) 的像素驱动电路 DC 的特性值。利用此测量,能够获取每个像素 21(i, j) 的晶体管 T3 的阈值电压 Vth 和像素驱动电路 DC 中的电流放大因子 β 的无规性作为公共电路中的图像数据的校正参数。

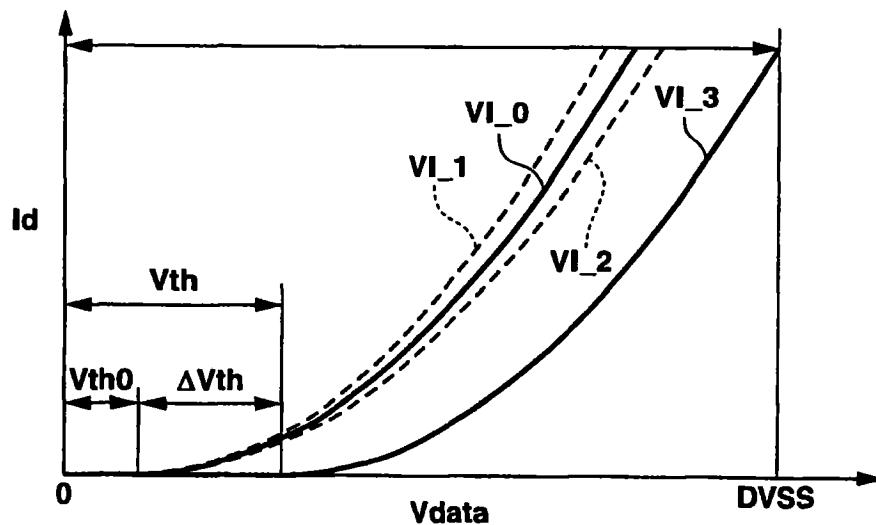

[0120] 图 3A 和图 3B 是解释像素驱动电路的图像数据写入时的电压 / 电流性质的图示和曲线图。图 3A 是示出写入时像素 21(i, j) 的每个部件的电压和电流 的图示。

[0121] 如图 3A 中所示,写入时,Hi 电平信号 (VgH) 由选择驱动器 13 施加于选择线 Lsj 上。然后,晶体管 T1 和 T2 成为导通状态,为电流控制薄膜晶体管的晶体管 T3 为二极管连接。

[0122] 随后,电压值由图像数据确定的电压信号 Vdata 由数据驱动器 22 施加于数据线 Ldi 上。那时,电压 ELVSS 由阳极电路 12 施加于阳极线 La 上。

[0123] 电压信号确定的电流 Id 于是通过像素驱动电路 DC 从阳极电路 12 经由晶体管 T2 和 T3 流向数据线 Ldi。

[0124] 此电流 Id 的电流值由下方程 (101) 表示。方程 (101) 中的 β 是电流放大因子,以及 Vth 是晶体管 T3 的阈值电压。

[0125] 施加于晶体管 3 的源极和漏极之间的电压 Vds 是阳极线 La 的电压 ELVSS 视为 0V 时,从电压 Vdata 的绝对值减去晶体管 T2 的漏极 - 源极电压 (连接部 N13 和连接部 N12 之间的电压) 的电压。

[0126] 换句话说,方程 (101) 不仅表示晶体管 T3 的电压 / 电流特性,而且表示像素驱动电路 DC 基本用作一个元件,且 β 为像素驱动电路 DC 的有效电流放大因子时的特性。

[0127] (101)... Id = β (|Vdata| - Vth)<sup>2</sup>

[0128] 图 3B 是示出电流 Id 随电压 Vdata 的绝对值的改变的曲线图。

[0129] 晶体管 T3 具有初始状态的特性,并且当阈值电压 Vth 具有初始值 Vth0、像素驱动电路 DC 的电流放大因子 β 具有初始值 β0(参考值) 时,该特性由图 3B 中所示的电压 / 电流特性 VI\_0 表示。

[0130] 这里,作为 β 的参考值,β0 设定为例如像素驱动电路 DC 的设计值或典型值。

[0131] 当晶体管 T3 随时间退化,且阈值电压 Vth 移位 (增加) 刚好 ΔVth 时,电压 / 电流特性成为图 3B 中所示的电压 / 电流特性 VI\_3。

[0132] 当由于 β0(参考值) 的无规性,电流放大因子 β 的值为小于 β0 的 β1 (= β0 - Δβ) 时,电压 / 电流特性成为电压 / 电流特性 VI\_1,并且当电流放大因子 β 的值为大于 β0 的 β2 (= β0 + Δβ) 时,电压 / 电流特性成为电压 / 电流特性 VI\_2。

[0133] 接下来,将给出关于自动调零方法的描述。

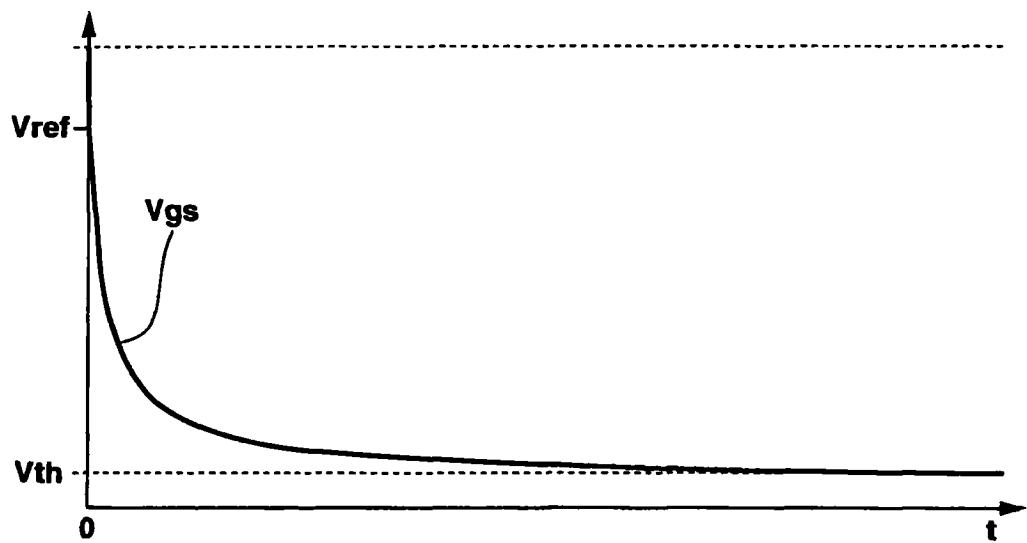

[0134] 在自动调零方法中,首先,在上述写入期间,经由数据线 Ldi 将参考电压 Vref 施加于像素 21(i, j) 的像素驱动电路 DC 的晶体管 T3 的栅极 - 源极上。参考电压设定为与阳极线 La 的电压 ELVSS 的电位差的绝对值超过阈值电压 Vth 的电压。以下,数据线 Ldi 处于高阻抗状态。这样,栅极数据线 Ldi 的电压自然降低(减小)。在完成自然降低后,测量数据线 Ldi 的电压,并且将所测得的电压视为阈值电压 Vth。

[0135] 与上述通常的自动调零方法相比,根据本实施例的自动调零方法测量刚好处于完全完成上述自然降低之前的时刻的数据线 Ldi 的电压。以下将给出详细解释。

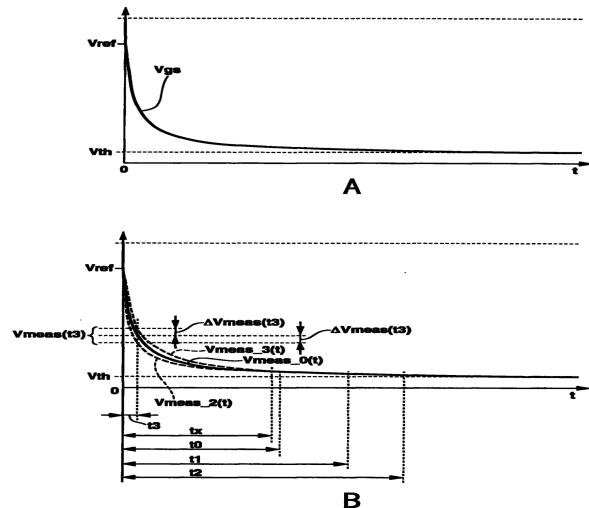

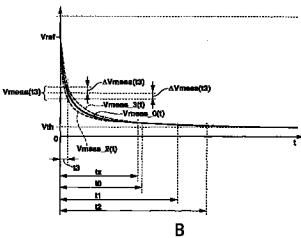

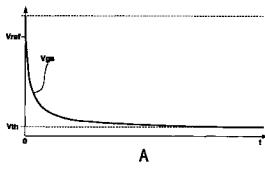

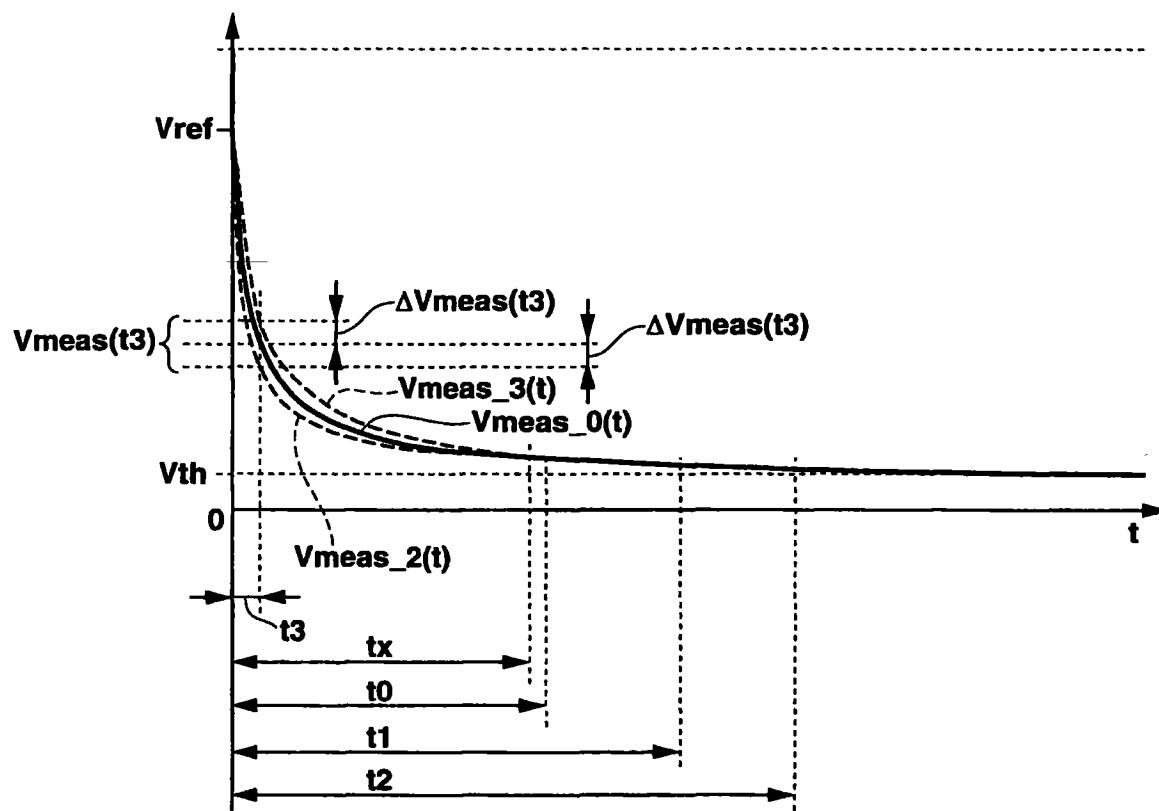

[0136] 图 4A 和 B 是解释根据本实施例使用自动调零方法时,数据线的电压测量方法的曲线图。图 4A 是示出在数据线 Ldi 上施加上述参考电压 Vref 后,数据线 Ldi 处于高阻抗状态时,数据线 Ldi 的时间变化(沉降特性)的曲线图。

[0137] 由数据驱动器 22 获取数据线 Ldi 的电压作为所测得的电压 Vmeas(t)。所测得的电压 Vmeas(t) 通常是等于晶体管 T3 的栅极电压 Vgs 的电压。

[0138] 图 4B 是解释存在图 3B 中所示的  $\beta$  无规性时,对数据线电压(测得的电压 Vmeas(t))的影响。另外,图 4A 和 4B 中的竖直轴示出了数据线 Ldi 电压(测得的电压 Vmeas(t))的绝对值。水平轴表示从在数据线 Ldi 上施加参考电压 Vref 使得数据线 Ldi 成为高阻抗状态且然后停止施加参考电压 Vref 起,所消逝的时间 t(沉降时间)。

[0139] 将给出利用自动调零方法进行的有关数据线电压的测量的更详细的描述。

[0140] 在写入状态中,首先,相对于阳极线 LA 的电压 ELVSS 的电位差的绝对值超过晶体管 T3 的阈值电压 Vth,具有比电压 ELVSS 低的电位的负极性参考电压 Vref 经由数据线 Ldi 施加于像素 21(i, j) 的像素驱动电路 DC 的晶体管 T3 的栅极 - 源极上。这样,参考电压 Vref 确定的电流从阳极电路 12 经由阳极线 La、晶体管 T3、和晶体管 T2 流向数据线 Ldi。

[0141] 此时,连接至晶体管 T3 的栅极 - 源极(图 3A 中的连接点 N11 和 N12)的保持电容 Cs 被充电至基于参考电压 Vref 的电压。

[0142] 接下来,数据线 Ldi 的数据输入侧(数据驱动器 22 侧)设定在高阻抗(HZ)状态。紧接建立高阻抗状态后,保持电容 Cs 中被充电的电压保持在基于参考电压 Vref 的电压,并且晶体管 T3 的栅极 - 源极电压保持在保持电容 Cs 中被充电的电压。

[0143] 这样,紧接建立高阻抗状态后,晶体管 T3 维持导通状态,且电流继续流至晶体管 T3 的漏极 - 源极。

[0144] 由此,晶体管 T3 的源极端子侧(连接点 N12)的电位随时间变化逐渐增大,接近漏极端子侧的电位。因此,在晶体管 T3 的漏极 - 源极之间流动的电流的值减小。

[0145] 与此结合,储存在保持电容 Cs 中的电荷的部分被放电。当储存在 Cs 中的电荷逐渐被放电时,保持电容 Cs 的两端之间的电压逐渐减小。

[0146] 以此方式,晶体管 T3 的栅极电压 Vgs 逐渐减小。因此,数据线 Ldi 的电压的绝对值也逐渐减小,如图 4A 中所示。

[0147] 最后,当晶体管 T3 的漏极 - 源极之间没有电流流动时,保持电容 Cs 的放电停止。那时,晶体管 T3 的栅极电压 Vgs 成为晶体管 T3 的阈值电压。

[0148] 因为那时晶体管 T2 的漏极 - 源极之间不存在电流流动,晶体管 T2 的漏极 - 源极之间的电压几乎为零。结果,数据线 Ldi 的电压变为几乎等于晶体管 T3 的阈值电压 Vth。

[0149] 如图 4A 中所示,数据线 Ldi 的电压随时间(沉降时间)渐进接近阈值电压 Vth。然而,即使理论上此电压无时间限制时接近阈值电压 Vth,其也不会变为完全等于阈值电压,无论设定多长的沉降时间。

[0150] 由此,本实施例中,显示设备 1 中的控制单元 16 设定为高阻抗状态,且预先设定用于测量数据线 Ldi 的电压的沉降时间 t。然后,在设定的沉降时间 t 测量数据线 Ldi 的电压(测得的电压 Vmeas(t)),从而,基于所测得的电压 Vmeas(t) 获取像素驱动电路 DC 的电流放大因子  $\beta$  和晶体管 T3 的阈值电压 Vth。

[0151] 能够以以下方程(102)表示所测得的电压 Vmeas(t)与沉降时间 t 的关系。

$$[0152] \quad (102) \dots V_{meas}(t) = V_{th} + \frac{1}{\frac{t}{(C/\beta)} + \frac{1}{V_{ref} - V_{th}}}$$

[0153] 其中,  $C = C_p + C_s + C_{el}$ 。

[0154] 当沉降时间 t 设定为满足条件  $(C/\beta)/t < 1$ (换句话说,  $(C/\beta) < t$ ) 的值时,在设定的沉降时间 t 所测得的电压 Vmeas(t) 能够以以下方程(103)表示。

[0155]

$$(103) \dots V_{meas}(t) = V_{th} + \frac{(C/\beta)}{t}$$

[0156] 当图 4B 中所示的沉降时间 tx 为满足  $(C/\beta)/t = 1$  的时间时,超过此沉降时间 tx 的时间变为满足条件  $(C/\beta)/t < 1$  的沉降时间。此沉降时间 tx 是所测得的电压 Vmeas(t) 通常为参考电压 Vref 的约 30% 的时间,并且更具体地,通常在 1ms 和 4ms 之间。

[0157] 接下来,图 4B 中的实线表示的 Vmeas\_0(t) 示出了电流放大因子  $\beta$  为初始值  $\beta_0$ (参考值)(与图 3B 中所示的电压 / 电流特性 VI\_0 的  $\beta$  的条件相同)时,数据线 Ldi 的电压的沉降特性。

[0158] 图 4B 中所示的 Vmeas\_2(t) 示出了电流放大因子  $\beta$  的值为小于  $\beta_0$  的  $\beta_1 (= \beta_0 - \Delta \beta)$ (与图 3B 中所示的电压 / 电流特性 VI\_1 的  $\beta$  的条件相同)时,数据线 Ldi 的电压的沉降特性。Vmeas\_3(t) 示出了电流放大因子  $\beta$  的值为大于  $\beta_0$  的  $\beta_2 (= \beta_0 + \Delta \beta)$ (与图 3B 中所示的电压 / 电流特性 VI\_2 的  $\beta$  的条件相同)时,数据线 Ldi 的电压的沉降特性。

[0159] 在显示设备 1 的早期阶段,诸如出货时,超过沉降时间 tx 的两个不同时间 t1 和 t2 设定为满足以上条件  $(C/\beta)/t < 1$  的沉降时间。随后,在根据上述自动调零方法在数据线 Ldi 上施加参考电压 Vref 后,以沉降时间 t1、t2 的定时两次测量数据线 Ldi 的电压。能够基于以上方程(103)从针对沉降时间 t1、t2 的测量获得的数据线 Ldi 的电压值推导初始阈值电压 Vth,即 Vth0 和  $(C/\beta)$ 。

[0160] 其后,通过上述方法推导有机 EL 面板 21 中的所有像素中的每一个的阈值电压 Vth0 和  $(C/\beta)$ 。然后,计算每个像素 21 的  $(C/\beta)$  的平均值(mean value)  $\langle C/\beta \rangle$  和其无规性。

[0161] 此外,确定满足  $(C/\beta)/(\beta t) < 1$  且无规性在阈值电压 Vth 测量的容许精度内的最短沉降时间 t0。

[0162] 当操作中供应图像数据时,能够使用获取的所测得的电压 Vmeas(t0) 根据从方程(103)更改的以下方程(104)推导操作中的阈值电压 Vth。

[0163] 每个像素 21 的算术平均值 ( $C/\beta$ ) 能够用作每个像素 21 的 ( $C/\beta$ ) 的平均值 ( $\langle C/\beta \rangle$ ), 然而也可以使用每个像素 21 的 ( $C/\beta$ ) 的中值。

$$[0164] (104) \dots V_{th} = V_{meas}(t_0) - \frac{\langle C/\beta \rangle}{t_0}$$

[0165] 这里, 以上方程 (104) 中的方程的右侧的第二部分定义为偏移电压  $V_{offset}$ 。

$$[0166] (105) \dots V_{offset} = \frac{\langle C/\beta \rangle}{t_0}$$

[0167] 其后, 将描述关于像素 21(i, j) 的像素驱动电路 DC 的电流放大因子  $\beta$  在  $\beta_0$  附近  $\Delta \beta$  的范围内无规则的情况,  $\beta_0$  附近  $\Delta \beta$  的范围示为  $\beta_0 \pm \Delta \beta = \beta_0(1 \pm \Delta \beta / \beta_0)$ 。

[0168] 那时数据线 Ldi 的电压 (测得的电压  $V_{meas}(t)$ ) 的归因于  $\Delta \beta$  的改变量  $\Delta V_{meas}(t)$  能够以下方程 (106) 表示。

$$[0169] (106) \dots \Delta V_{meas}(t) = -\left[\frac{\Delta \beta}{\beta}\right] \times \frac{\langle C/\beta \rangle}{t} \left\{ 1 - \frac{2}{V_{ref} - V_{th}} \frac{\langle C/\beta \rangle}{t} \right\}$$

[0170] ( $\Delta \beta / \beta$ ) 是示出每个像素 21(i, j) 的像素驱动电路 DC 的电流特性的无规性的无规性参数,  $\Delta V_{meas}(t)$  表示数据线 Ldi 的电压对无规性  $\Delta \beta$  (或无规性参数 ( $\Delta \beta / \beta$ )) 的依赖关系。换句话说, 如方程 (106) 中所示, 归因于  $\beta$  的无规性, 数据线 Ldi 的电压仅波动  $\Delta V_{meas}(t)$ 。

[0171] 那时的沉降时间  $t$  能够设定为与沉降时间  $t_x$  相比较小的值  $t_3$ , 如图 4B 中所示,  $((C/\beta)/t \geq 1, t = t_3)$ 。

[0172] 在此沉降时间  $t_3$ , 数据线 Ldi 的电压迅速沉降 (降低), 如图 4B 中所示。因此, 数据线 Ldi 的电压 (测得的电压  $V_{meas}(t)$ ) 对  $\beta$  的无规性的依赖相对较大。

[0173] 为此原因, 当在沉降时间  $t_3$  测量  $\Delta_{meas}(t)$  时, 与在沉降时间  $t_1$  或  $t_2$  测得的  $\Delta_{meas}(t)$  相比, 能够获取较大的值, 并且容易区别测得的电压  $V_{meas}(t)$  相对于无规性  $\Delta \beta$  的改变。这些是为什么由沉降时间  $t_3$  获取  $V_{meas}(t)$  的原因。根据此  $V_{meas}(t)$  推导  $\Delta_{meas}(t)$ , 并且能够根据方程 (106) 获取 ( $\Delta \beta / \beta$ )。

[0174] 以下将描述关于基于供应的图像数据施加在数据线 Ldi 上的电压信号的电压值  $V_{data}$  的校正。此校正的目的是减小归因于阈值的改变和电流放大因子  $\beta$  的无规性对显示图像的影响。

[0175] 电压值  $V_{data1}$  由将方程 (106) 对电压求微分导出的以下方程 (107) 表示, 其中, 电压值  $V_{data0}$  是基于每个像素 21(i, j) 的像素驱动电路 DC 的电流特性的无规性参数 ( $\Delta \beta / \beta$ ) 校正的, 校正前的电压视为基于图像数据的  $V_{data0}$ 。

$$[0176] (107) \dots V_{data1} = V_{data0} \times \left\{ 1 - \frac{1}{2} \left( \frac{\Delta \beta}{\beta} \right) \right\}$$

[0177] 根据自动调零方法, 针对沉降时间  $t_0$ , 通过使用方程 (105) 中定义的偏移电压  $V_{offset}$ , 阈值电压  $V_{th}$  由以下方程 (108) 表示。

$$[0178] (108) \dots V_{th} = V_{meas}(t_0) - V_{offset}$$

[0179] 电压值 (校正的电压)  $V_{data}$  由以下方程 (109) 表示, 其中基于图像数据的电压值  $V_{data0}$  是基于像素驱动电路 DC 的电流特性的无规性参数 ( $\Delta \beta / \beta$ ) 和阈值电压  $V_{th}$  校正的。

[0180] 此电压 Vdata 是由数据驱动器 22 施加于数据线 Ld1 上的电压信号（驱动信号）的电压值。

[0181] (109)...  $V_{data} = V_{data1} + V_{th}$

[0182] 以下将详细描述关于数据驱动器 22 的组成。

[0183] 图 5 示出了示出图 1 中所示的数据驱动器 22 的详细构成的框图。

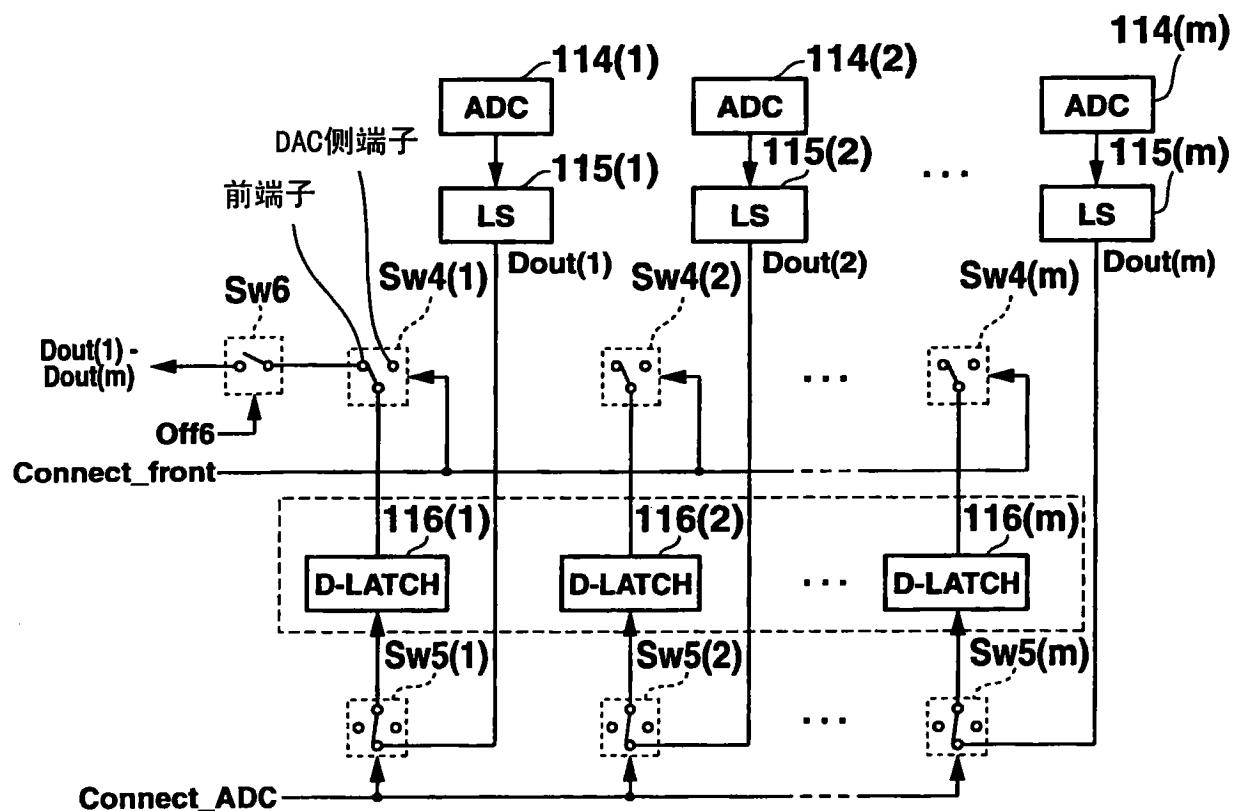

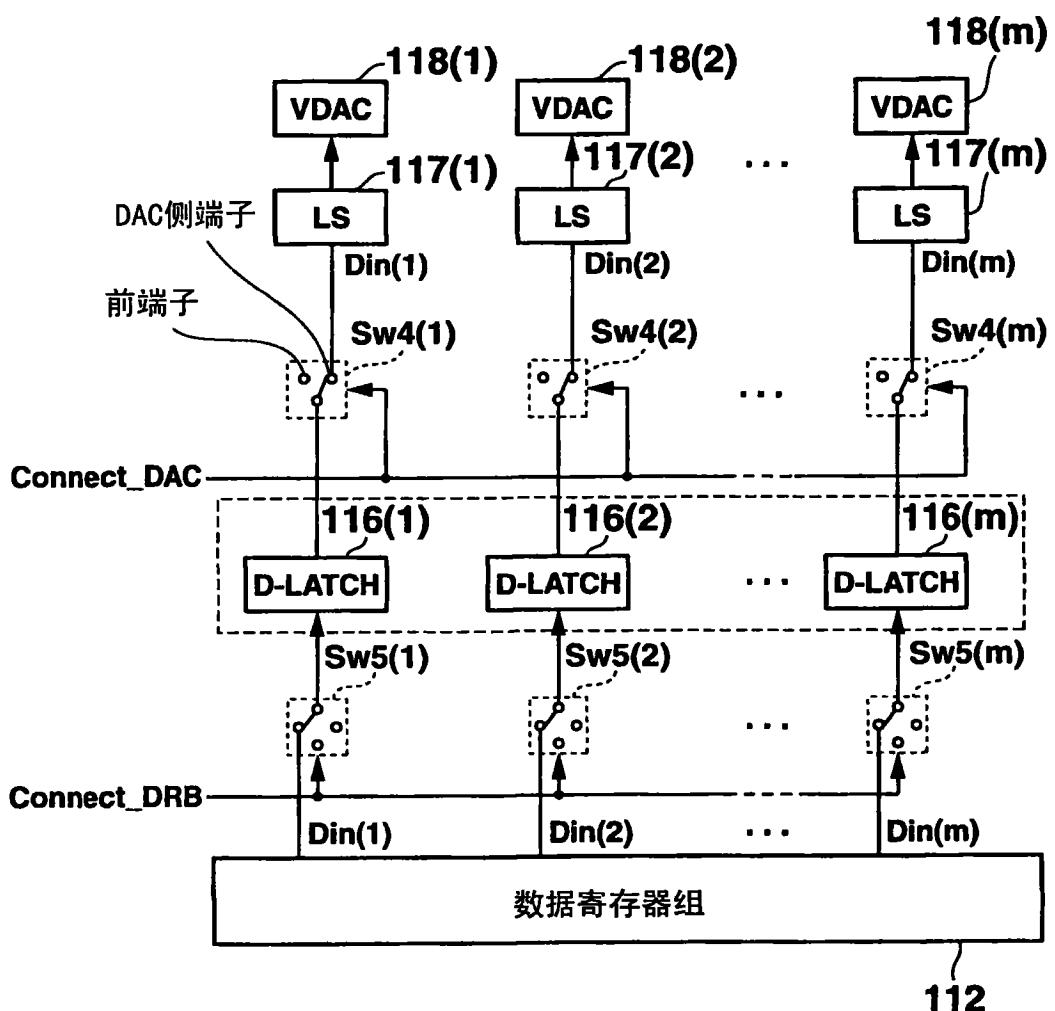

[0184] 如图 5 中所示, 数据驱动器 22 提供: 移位寄存器 111; 数据寄存器组 112; 缓冲器 113(1) 至 (m)、119(1) 至 119(m); ADC 114(1) 至 114(m); 电平移动电路 (图样中描述为“LS”) 115(1) 至 115(m)、117(1) 至 117(m); 数据锁存器电路 (图样中描述为“D-Latch”) 116(1) 至 116(m); VDAC 118(1) 至 118(m); 以及开关 Sw1(1) 至 Sw1(m)、SW2(1) 至 SW2(m)、Sw3(1) 至 SW3(m)、Sw4(1) 至 Sw4(m)、Sw5(1) 至 Sw5(m)、以及 Sw6。

[0185] Sw3(1) 至 Sw3(m) 对应于开关电路。

[0186] 移位寄存器 111 通过顺序移动从控制单元 16 供应的开始脉冲 SP2 一个时钟信号而生成移位信号, 并顺序将这些移位信号供应到数据寄存器组 112 中。

[0187] 数据寄存器组 112 由 m 片寄存器组成。基于图像数据生成的数字数据  $Din(i)$  ( $i = 1 \sim m$ ) 从控制单元 16 供应至数据寄存器组 112 中。数据寄存器组 112 根据从移位寄存器 111 供应的移位信号顺序将这些数字数据  $Din(i)$  ( $i = 1 \sim m$ ) 保持在以上 m 个寄存器的每一个中。

[0188] 缓冲器 113(i) ( $i = 1 \sim m$ ) 为缓冲电路, 以将数据线  $Ldi$  ( $i = 1 \sim m$ ) 的电压相应地施加于 ADC 114(i) ( $i = 1 \sim m$ ) 上作为模拟数据。

[0189] ADC 114(i) ( $i = 1 \sim m$ ) 为将模拟电压转换为数字信号的模拟 - 数字转换器。ADC 114(i) 将缓冲器 113(i) 施加的模拟数据转换成数字数据输出信号  $Dout(i)$ 。ADC 114(i) 用作测量数据线  $Ldi$  ( $i = 1 \sim m$ ) 的电压的测量仪器 (电压测量电路)。

[0190] 电平移动电路 115(i) 对 ADC 114(i) 通过转换生成的数字数据进行电平移动, 以便适应电路的电源电压 ( $i = 1 \sim m$ )。

[0191] 数字数据  $Din(i)$  保持在数据寄存器组 112 的每个寄存器中。数据锁存器电路 116(i) 保持从数据寄存器组 112 的每个寄存器供应的数字数据  $Din(i)$ 。数据锁存器电路 116(i) 在从控制单元 16 供应的数据锁存器脉冲 DL (脉冲) 上升时刻锁存并保持数字数据  $Din(i)$ 。

[0192] 电平移动电路 117(i) 对数据锁存器电路 106(i) 保持的数字数据  $Din(i)$  进行电平移动, 以便适应电路的电源电压 ( $i = 1 \sim m$ )。

[0193] VDAC 118(i) ( $i = 1 \sim m$ ) 将数字信号转换为模拟电压的数字 - 模拟转换器。VDAC 118(i) 将由电平移动电路 117(i) 进行了电平移动的数字数据  $Din(i)$  转换为模拟电压, 并经由缓冲器 119(i) ( $i = 1 \sim m$ ) 输出至数据线  $Ldi$ 。VDAC 118(i) 等效于生成驱动信号并将它们施加于后续电路上的驱动信号施加电路。

[0194] 缓冲器 119(i) 是缓冲器电路, 以将从 VDAC 118(i) 输出的模拟电压输出至数据线  $Ldi$  ( $i = 1 \sim m$ )。

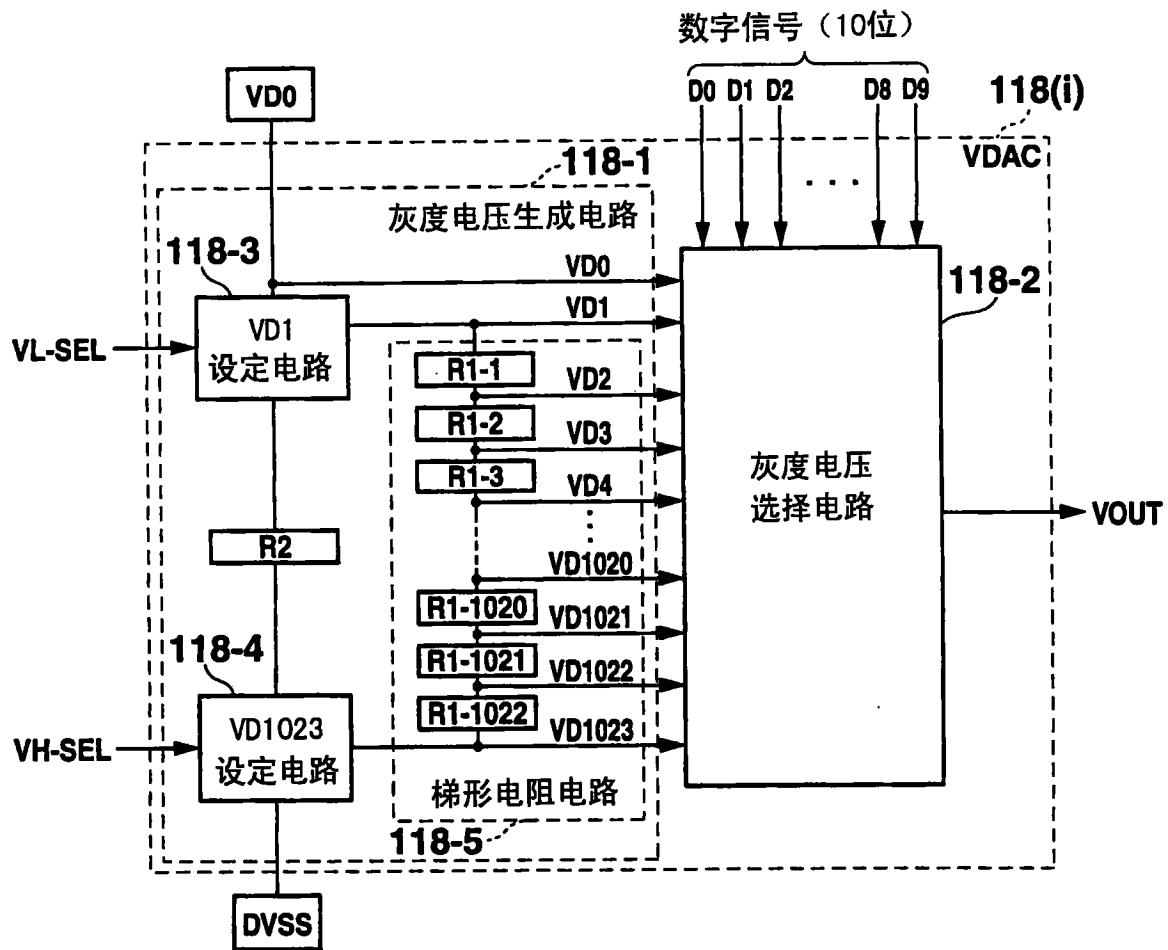

[0195] 图 6A 和 B 是解释图 5 中所示的 VDAC 118 的构成和功能的图示。

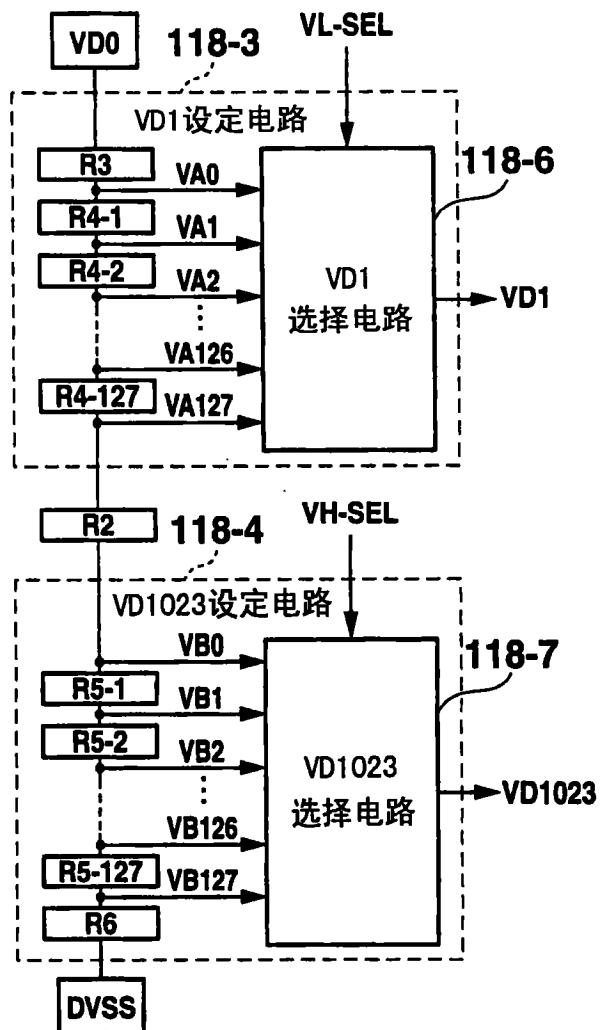

[0196] 图 6A 示出了 VDAC 的总体构成, 图 6B 示出了包括在 VDAC 118 中的 VD1 设定电路 118-3 和 VD1023 设定电路 118-4 的构成。

[0197] 如图 6A 中所示,VDAC 118(i) 具有灰度电压生成电路 118-1 和灰度电压选择电路 118-2。

[0198] 灰度电压生成电路 118-1 生成由输入至 VDAC 118 中的数字信号位的数量确定的预定数量的灰度电压(模拟电压)。如图 6A 中所示,例如,当待输入的数字信号为 10 位(D0-D9)时,灰度电压生成电路 118-1 生成 1024 个灰度电压 VD0 至 VD1023。

[0199] 灰度电压生成电路 118-1 具有 VD1 设定电路 118-3、VD1023 设定电路 118-4、电阻 R2、以及梯形电阻电路 118-5。

[0200] VD1 设定电路 118-3 是基于从控制单元 16 供应的控制信号 VL-SE1 和待施加的电压 VD0 来设定灰度电压 VD1 的电压值的电路。电压 VD0 是最小灰度电压,并设定为例如与电源电压 ELVSS 相同的电压。

[0201] VD1 设定电路 118-3 具有电阻 R3、R4-1 至 R4-127 和 VD1 选择电路 118-6,如图 6B 中所示。

[0202] 电阻 R3、R4-1 至 R4-127 是按此顺序串联连接的分压电阻。电压 VD0 施加于串联连接的电阻的电阻 R3 侧的那端。串联连接的电阻的电阻 R4-127 侧的那端连接至电阻 R2 的一端。电阻 R3 和电阻 R4-1 的连接点的电压是电压 VA0, 电阻 4-i 和电阻 4-i+1 的连接点的电压是电压 VAi (i = 1 ~ 126), 电阻 R4-127 和电阻 R2 的连接点的电压是电压 VA127。

[0203] VD1 选择电路 118-6 基于从控制单元 16 供应的控制信号 VL-SE1 选择电压 VA0 至 VA127 内的任一电压,并输出所选择的电压作为灰度电压 VD1。VD1 设定电路 118-3 将灰度电压 VD1 设定为对应于阈值电压 Vth0 的值。

[0204] VD1023 设定电路 118-4 是基于从控制单元 16 供应的控制信号 VH-SEL 和模拟电源 14 施加的电压 DVSS 设定最大灰度电压 VD1023 的电压值的电路。

[0205] VD1023 设定电路 118-4 具有电阻 R5-1 至 R5-127、R6、和 VD1023 选择电路 118-7,如图 6B 中所示。

[0206] 电阻 R5-1 至 R5-127 和 R6 是按此顺序串联连接的分压电阻。串联连接的电阻的电阻 R5-1 侧的那端连接至电阻 R2 的另一端,电压 VDSS 施加于串联连接的电阻的电阻 R6 侧的那端上。这些电阻 R2 和 R5-1 的连接点的电压是电压 VB0, 电阻 R5-i 和 R5-i+1 的连接点的电压是电压 VBi (i = 1 ~ 126), 电阻 R5-127 和电阻 R6 的连接点的电压是电压 VB127。

[0207] VD1023 选择电路 118-7 基于从控制单元 16 供应的控制信号 VH-SEL 选择电压 VB0 至 VB127 内的任一电压,并输出所选择的电压作为灰度电压 VD1023。

[0208] 梯形电阻电路 118-5 提供多个梯形电阻,例如串联连接的 R1-1 至 R1-1022。梯形电阻 R1-1 至 R1-1022 的每一个具有相同阻值。

[0209] 梯形电阻电路 118-5 的电阻 R1-1 侧的那端连接至 VD1 设定电路 118-3 的输出端子,且电压 VD1 施加于此端子上。梯形电阻电路 118-5 的电阻 R1-1022 侧的那端连接至 VD1023 设定电路 118-4 的输出端子,且电压 VD1023 施加于此端子上。

[0210] 梯形电阻 R1-1 至 R1-1022 在 VD1 至 VD1023 之间均匀地分配电压。梯形电阻电路 118-5 将均匀分配的电压输出至灰度电压选择电路 118-2 中作为灰度电压 VD2 ~ VD1022。

[0211] 由电平移动电路 117(i) 进行了电平移动的数字信号输入至灰度电压选择电路 118-2 作为数字信号 D0 ~ D9。其后,灰度电压选择电路 118-2 选择对应于数字信号 D0 ~ D9 的值的电压,并输出灰度电压作为 VDAC 118 的输出电压 VOUT,D0 ~ D9 是从灰度电压生

成电路 118-1 供应的灰度电压 VD0 ~ VD1023 的每一个输入的。

[0212] 如上述, VDAC 118(i) 将输入数字信号转换为对应于数字信号的灰度值的模拟电压。

[0213] 在本实施例中, 输入至 VDAC 118 的数字信号的值设定在比由图像数据位的数量确定的总灰度范围窄的范围内, 并且 VDAC 118(i) 输出的输出电压 VOUT 的电压范围设定在灰度电压生成电路 118-1 生成的总灰度电压范围 VD0 ~ VD1023 的一部分内。

[0214] 在本实施例中, 如上述, 为了减小归因于阈值电压 Vth 的波动的图像数据波动, 基于那时获取的阈值电压 Vth 的值, 对供应的图像数据执行校正。通过执行此校正, 图像数据的所有灰度值的输出电压 VOUT 的电压范围的宽度不改变, 然而, 为图像数据的第一灰度的电压范围内的下限电压值仅被移动对应于阈值电压 Vth 的改变量 ( $\Delta Vth$ ) 的值。因此, 图像数据的所有灰度值的输出电压 VOUT 的电压范围在所有灰度电压 VD0 ~ VD1023 的范围内移动。

[0215] 这里, 灰度电压生成电路 118-1 设定的每个灰度电压 VD1 ~ VD1023 设定为均匀间隔的值。因此, 即使输出电压 VOUT 的电压范围移动, 也能够一致地维持对应于图像数据的灰度值的 VDAC118(i) 的输出电压的改变特性。

[0216] 当图像数据的灰度值为零时, VDAC 118(i) 输出对应于零灰度的最小灰度电压 VD0。因为此时有机 EL 元件 101 处于给出黑色显示的不发光状态, 所以不必基于阈值电压 Vth 的值进行校正。因此, 灰度电压 VD0 设定为固定电压值。

[0217] ADC114(i) 和 VDAC 118(i) 均具有例如相同的位宽度, 并且对应于 1 灰度的电压宽度设定为相同值。

[0218] 开关 Sw1(i) ( $i = 1 \sim m$ ) 为分别连接或断开数据线 Ldi 和缓冲器 119(i) 的输出端子的开关。

[0219] 当具有电压值 Vdata 的电压信号施加于数据线 Ldi 上时, 在从控制单元 16 供应 On1 信号作为开关控制信号 S1 后, 每个开关 Sw1(i) 成为导通状态(闭合), 连接缓冲器 119(i) 的输出端子和数据线 Ldi。

[0220] 在数据线 Ldi 上施加电压值 Vdata 的电压信号完成后, 当从控制单元 16 供应 Off1 信号作为开关控制信号 S1 时, 每个开关 Sw1(i) 成为截止状态, 中断缓冲器 119(i) 的输出端子和数据线 Ldi 之间的连接。

[0221] 每个开关 Sw2(i) ( $i = 1 \sim m$ ) 是连接或断开数据线 Ldi 和缓冲器 119(i) 的输入端子的开关。

[0222] 当利用自动调零方法执行对数据线 Ldi 的电压测量时, 当从控制单元 16 供应 On2 信号作为开关控制信号 S2 时, 每个开关 Sw2(i) 成为导通状态(闭合), 连接缓冲器 113(i) 的输入端子和数据线 Ldi。

[0223] 在完成对数据线 Ldi 的电压测量后, 当从控制单元 16 供应 Off2 信号作为开关控制信号 S2 时, 每个开关 Sw2(i) 成为截止状态, 中断缓冲器 113(i) 的输出端子和数据线 Ldi 之间的连接。

[0224] 每个开关 Sw3(i) 是连接或断开数据线 Ldi 和模拟电源 14 的参考电压 Vref 的输出端子的开关。

[0225] 当参考电压 Vref 施加于数据线 Ldi 上时, 当从控制单元 16 供应 On3 信号作为开

关控制信号 S3 时,每个开关 Sw3(i) 成为导通状态,连接模拟电源 14 的参考电压 Vref 的输出端子和数据线 Ldi。

[0226] 仅短时间供应 On3 信号至开关 Sw3(i),该时间是施加参考电压 Vref 以利用上述自动调零方法测量电压所需的。随后,当从控制单元 16 供应 Off3 信号作为开关控制信号 S3 时,每个开关 Sw3(i) 成为截止状态,中断模拟电源 14 的参考电压 Vref 的输出端子和数据线 Ldi 之间的连接。

[0227] 开关 Sw4(1) 是用于开关数据锁存器电路 116(1) 的输出端子和开关 Sw6 的一个端子或电平移动电路 117(1) 之间的连接的开关。此开关具有连接至开关 Sw6 的一端和 DAC 侧端子的前端子,DAC 侧端子连接至电平移动电路 117(1)。

[0228] 每个开关 Sw4(i) ( $i = 2 \sim m$ ) 是用于开关数据锁存器电路 116(i) 的输出端子和开关 Sw5(i-1) 的一个端子或电平移动电路 117(i) 之间的连接的开关。此开关具有连接至平移动电路 117(i) 的 DAC 侧端子和连接至 Sw5(i-1) 的一个端子的前端子。

[0229] 当从数据驱动器 22 输出测量电压 Vmeas(t) 作为输出信号 Dout(1) ~ Dout(m) 时,从控制单元 16 向每个开关 Sw4(i) ( $i = 1 \sim m$ ) 供应 Connect\_front 信号作为开关控制信号 S4。

[0230] 通过从控制单元 16 供应的 Connect\_front 信号,开关 Sw4(i) ( $i = 1 \sim m$ ) 连接数据锁存器电路 116(i) 的输出端子和前端子。

[0231] 当电压值 Vdata 的电压信号施加于每个数据线 Ldi 上时,从控制单元 16 向每个开关 Sw4(i) ( $i = 1 \sim m$ ) 供应 Connect\_DAC 作为开关控制信号 S4。通过 Connect\_DAC 信号,开关 Sw4(i) 连接数据锁存器电路 116(i) 的输出端子和 DAC 侧的端子。

[0232] 每个开关 Sw5(i) ( $i = 1 \sim m$ ) 是用于开关数据锁存器电路 116(i) 的输入端子和数据寄存器组 112、电平移动电路 115(i) 和开关 Sw4(i) 的任一个之间的连接的开关。

[0233] 当从控制单元 16 向每个开关 Sw5(i) 供应 Connect\_ADC 信号作为开关控制信号 S5 时,开关 Sw5(i) 连接数据锁存器电路 116(i) 的输入端子和电平移动电路 115(i) 的输出端子。

[0234] 当从控制单元 16 向每个开关 Sw5(i) 供应 Connect\_rear 信号作为开关控制信号 S5 时,开关 Sw5(i) 连接数据锁存器电路 116(i) 的输入端子和开关 Sw4(i+1) 的前端子。

[0235] 当从控制单元 16 向每个开关 Sw5(i) 供应 Connect\_DRB 信号作为开关控制信号 S5 时,开关 Sw5(i) 连接数据锁存器电路 116(i) 的输入端子和数据寄存器组 112 的输出端子。

[0236] 开关 Sw6 是连接或断开开关 Sw4(1) 的前端子和控制单元 116 的开关。

[0237] 当测量电压 Vmeas(t) 输出至控制单元 16 作为输出信号 Dout(1) ~ Dout(m) 时,当从控制单元 16 向开关 Sw6 供应 On6 信号作为开关控制信号 S6 时,开关 Sw6 成为导通状态,连接开关 Sw4(1) 的前端子和控制单元 16。

[0238] 当测量电压 Vmeas(t) 完全输出时,当从控制单元 16 向 Sw6 供应 Off6 信号作为开关控制信号 S6 时,开关 Sw6 成为截止状态,中断开关 Sw4(1) 的前端子和控制单元 16 之间的连接。

[0239] 返回图 1,阳极电路 12 通过经由阳极线 La 在有机 EL 面板 21 上施加电压而供应电流。

[0240] 模拟电源 14 是在数据驱动器 22 上施加参考电压 Vref、电压 DVSS 和 DV0 的电源。

[0241] 参考电压  $V_{ref}$  施加于数据驱动器 22 上,以便在利用自动调零方法对数据线  $L_{di}$  进行电压测量时,从每个像素  $21(i, j)$  引出电流。相对于阳极电路 12 施加于每个像素驱动电路 DC 上的电源电压  $ELVSS$ ,参考电压  $V_{ref}$  为负电压,并且相对于电源电压  $ELVSS$  的电位差的绝对值设定为大于每个像素  $21(i, j)$  的晶体管 T3 的阈值电压  $V_{th}$  的绝对值的值。

[0242] 模拟电压  $DVSS$  和  $VD0$  是用于驱动缓冲器 113(i)、缓冲器 119(i)、ADC114(i) 和  $VDAC\ 118(i)$  ( $i = 1 \sim m$ ) 的模拟电压。相对于阳极电路 12 施加于阳极线  $La$  上的电源电压  $ELVSS$ ,模拟电压  $DVSS$  为负电压,并设定为例如约  $-12V$ 。

[0243] 逻辑电源 15 是用于在数据驱动器 22 上施加电压  $LVSS$  和  $LVDD$  的电源。电压  $LVSS$  和  $LVDD$  是用于驱动数据驱动器 22 的数据锁存器电路 116(i) ( $i = 1 \sim m$ )、数据寄存器组、和移位寄存器的逻辑电压。这里,电压  $DVSS$ 、 $VD0$ 、 $LVSS$ 、和  $LVDD$  设定为满足条件,例如  $(DVSS-VD0) < (LVSS-LVDD)$ 。

[0244] 控制单元 16 储存每个数据并基于所储存的数据控制每个部件。如上述,本实施例中的控制单元 16 具有向数据驱动器 22 供应数字数据  $Din(i)$  ( $i = 1 \sim m$ ) 的构成,并对数字值执行控制单元 16 内的处理计算等,数字数据  $Din(i)$  是通过对供应的数字信号的图像数据进行各种校正而生成的。另外,为方便,通过将数字信号与模拟电压适当地进行比较,给出以下描述。

[0245] 控制单元 16 利用自动调零方法经由驱动器 22 测量数据线  $L_{di}$  的电压,例如,在诸如显示设备 1 的发货的早期阶段控制每个部件时,并获取所有像素  $21(i, j)$  的测得的电压  $V_{meas}(t1)$ 、 $V_{meas}(t2)$ 、和  $V_{meas}(t3)$ 。

[0246] 然后,控制单元 16 通过根据方程 (103) 并使用测得的电压  $V_{meas}(t1)$  和  $V_{meas}(t2)$  进行计算,获取像素驱动电路 DC 的  $C/\beta$  值和每个像素  $21(i, j)$  的晶体管 T3 的(初始)阈值电压  $V_{th0}$  作为特性参数。此外,控制单元 16 获取所有像素  $21(i, j)$  的  $C/\beta$  的平均值  $\langle C/\beta \rangle$ 。此外,确定用于真实操作的沉降时间  $t_0$ ,并通过根据方程 (105) 进行计算来获取偏移电压  $V_{offset}$ 。

[0247] 此外,控制单元 16 通过使用测得的电压  $V_{meas}(t3)$  来计算  $AV_{meas}(t3)$ ,并通过根据方程 (106) 进行计算来获取无规性参数  $(\Delta \beta / \beta)$  作为特性参数。

[0248] 随后,控制单元 16 控制每个部件,并在利用自动调零方法测量数据线  $L_{di}$  的电压时,获取供应图像数据时所有像素  $21(i, j)$  的测得的电压  $V_{meas}(t0)$ ,同时,经由操作中的数据驱动器 22 的沉降时间为  $t_0$ 。

[0249] 通过如下述转换数据值(电压幅度),控制单元 16 基于对应于供应的图像数据的灰度电压数据获取对应于每个 RGB 中的图像数据的灰度值的电压值  $V_{data0}$ 。

[0250] 彩色显示中,每个 RGB 所需的白显示为最大灰度。然而,由于供应的电流的电流值,用于像素  $21(i, j)$  的每个 RGB 色的有机 EL 元件 101 通常具有不同的发光亮度特性。

[0251] 结果,在控制单元 16 中对用于每个 RGB 的图像数据灰度值的电压幅度执行转换,以便供应至有机 EL 元件 101 的用于图像数据灰度值的每个 RGB 的电流的电流值能够具有与白显示中相互不同的值,白显示时每个 RGB 处于最大灰度。

[0252] 通过对所有像素  $21(i, j)$  执行此类型的电压幅度转换,控制单元 16 获取电压值  $V_{data0}$ 。

[0253] 在获取电压值  $V_{data0}$  后,控制单元 16 根据方程 (107) 获取基于  $(\Delta \beta / \beta)$  的校

正的电压值 Vdata1。

[0254] 控制单元 16 根据方程 (108) 和 (109) 获取基于阈值电压 Vth 的校正的电压值 Vdata 作为最终输出电压。更具体地,通过对应阈值电压 Vth 的位增加,控制单元 16 校正电压值 Vdata1,以获取电压值 Vdata。

[0255] 控制单元 16 将用于所有像素 21(i, j) 的校正的图像数据 Vdata 一次一行输出至数据驱动器 22 作为数字数据 Din(i) (i = 1 ~ m)。

[0256] 图 7 是示出图 1 中所示的控制单元的构成的框图。

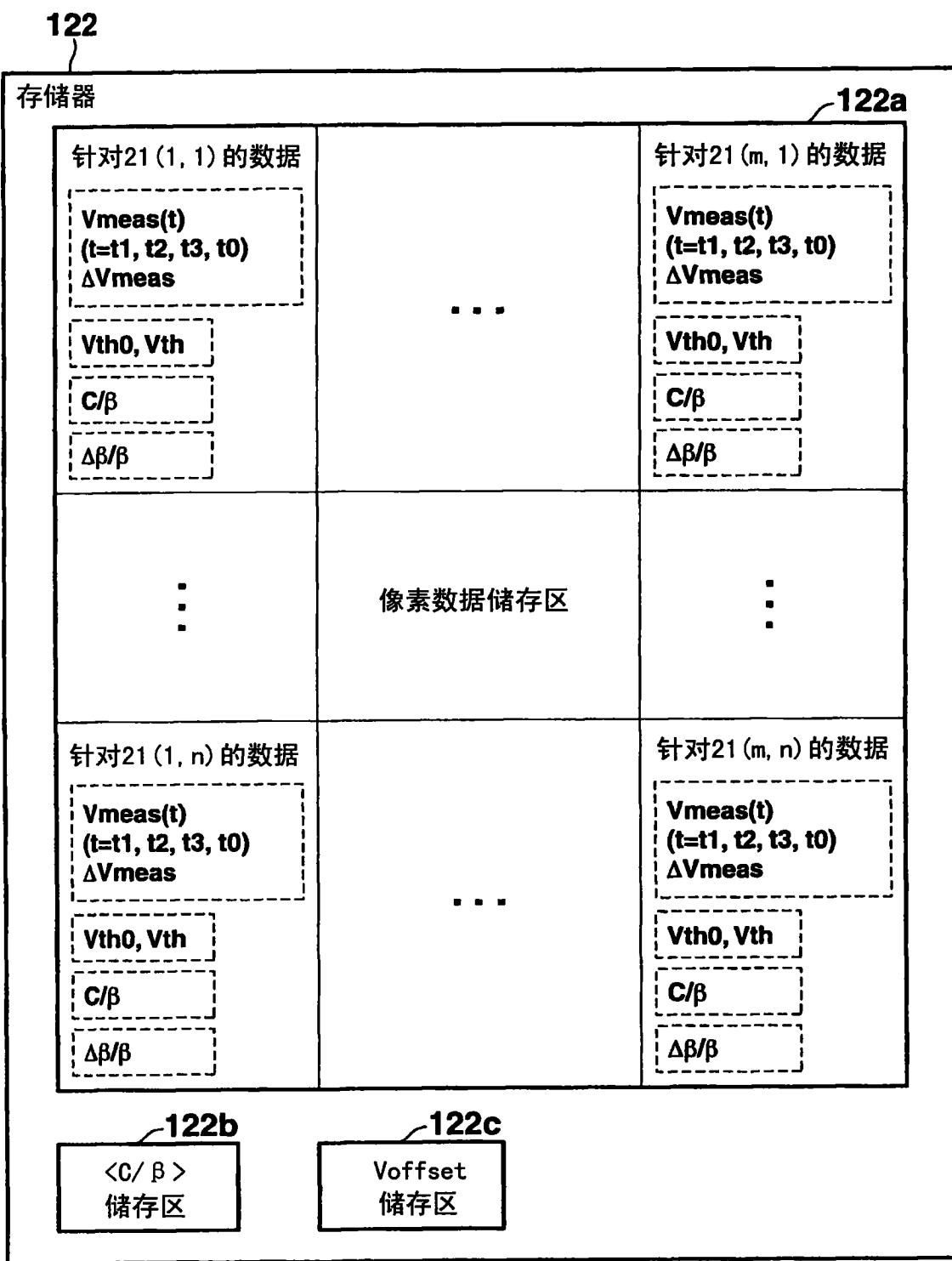

[0257] 图 8 是示出图 7 中所示的存储器的每个储存区的图示。

[0258] 控制单元 16 提供 CPU(中央处理器单元)121、存储器 122、和 LUT(查找表)123,如图 7 中所示,以执行上述处理。

[0259] CPU 121 用于控制阳极电路 12、选择驱动器 13、和数据驱动器 22,并用于执行各种计算的每一种。

[0260] 存储器 122 由 ROM(只读存储器)、RAM(随机存取存储器)等组成,并储存 CPU 121 执行的每个处理程序并储存处理所需的各种数据。

[0261] 存储器 122 提供像素数据储存区 122a、 $\langle C/\beta \rangle$  储存区 122b 和 Voffset 储存区 122c 作为储存各种数据的区域,如图 8 中所示。

[0262] 像素数据储存区 122a 是用于储存每个像素 21(i, j) 的测得的电压 Vmeas(t1)、Vmeas(t2)、Vmeas(t3)、Vmeas(t0)、 $\Delta V_{meas}$ 、阈值电压 Vth0、Vth、C/ $\beta$  和  $\Delta \beta/\beta$  中的每一个数据的区域。

[0263]  $\langle C/\beta \rangle$  储存区 122b 是用于存储每个像素 21(i, j) 的 C/ $\beta$  的平均值  $\langle C/\beta \rangle$  的区域。

[0264] Voffset 储存区 122c 是用于储存根据方程 (105) 定义的偏移电压 Voffset 的区域。

[0265] LUT 123 是预设的表,以转换用于供应的图像的每个 RGB 色的数据值。

[0266] 通过参照 LUT 123,控制单元 16 转换用于供应的图像数据值的每个 RGB 的数据值。

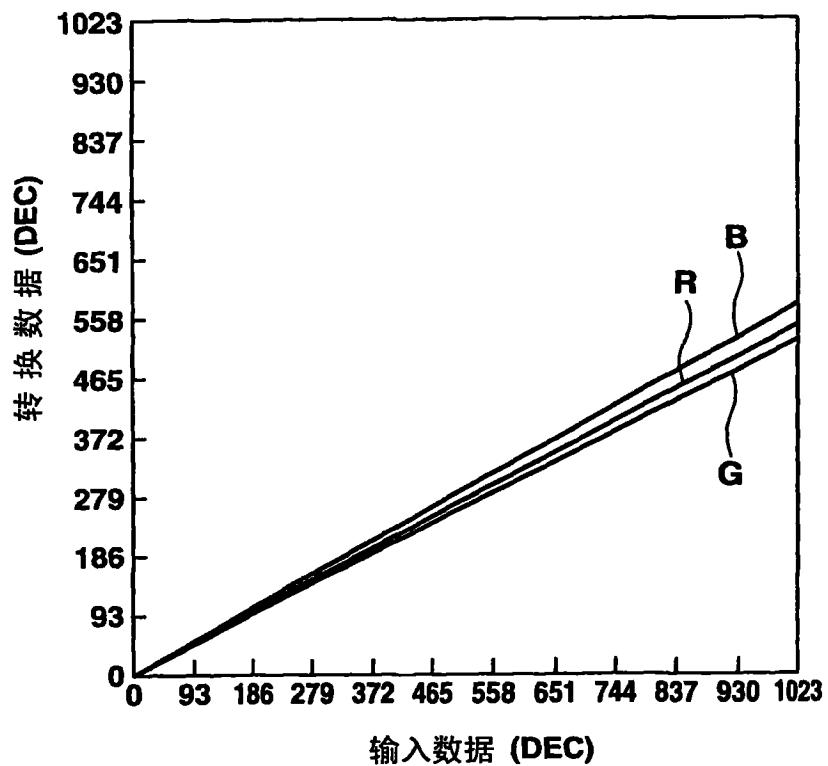

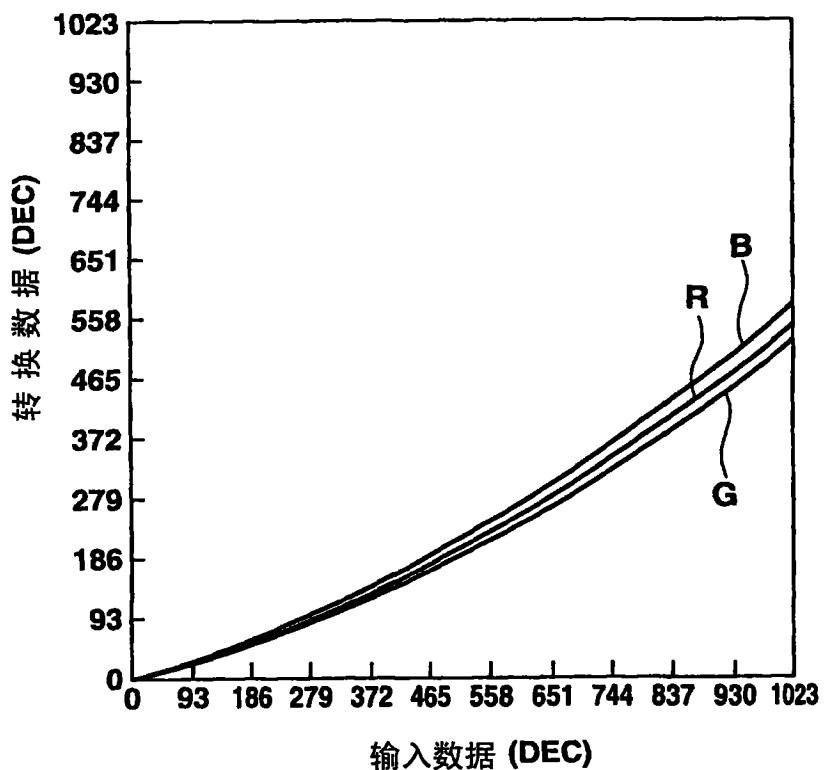

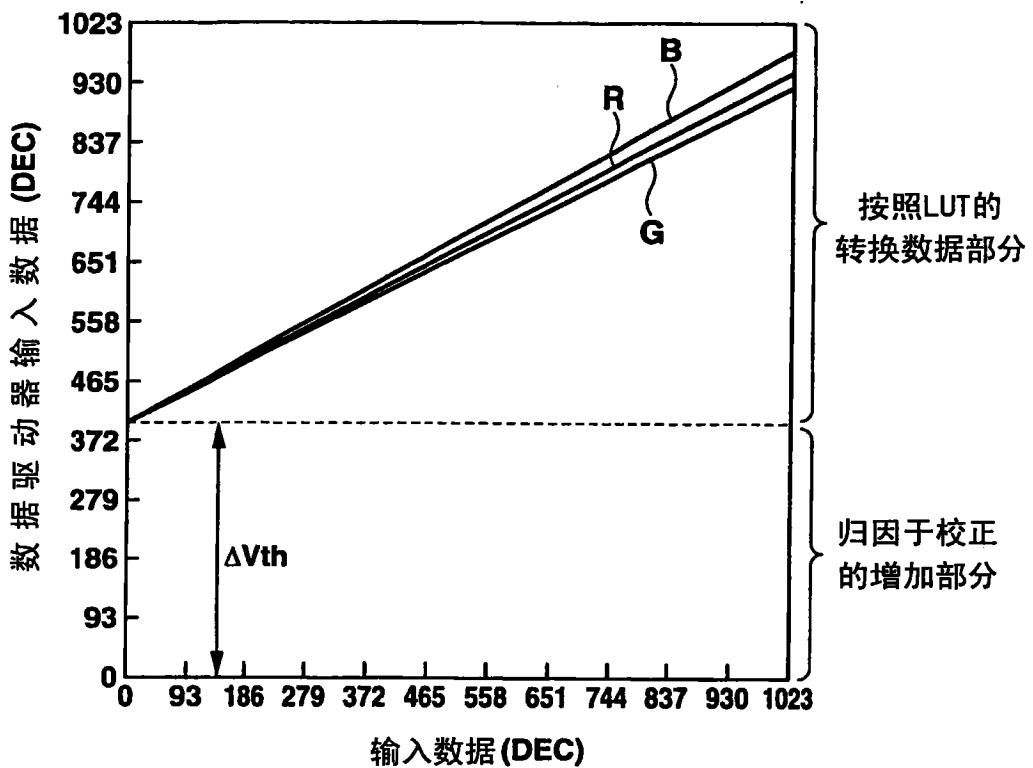

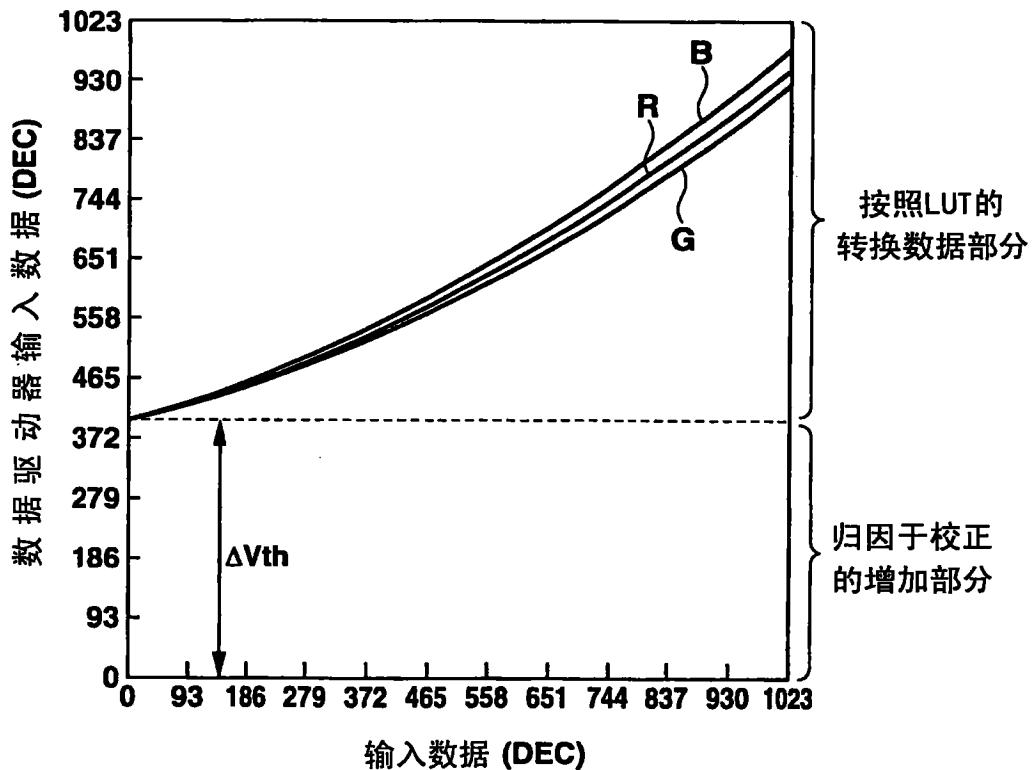

[0267] 接下来,图 9A 和 B 是示出在 VDAC118(i) 为 10 位的情况下执行数据转换时,图 7 中所示的 LUT 中的图像数据转换特性的范例的曲线图。

[0268] 图 10A 和 B 是解释 LUT 中的图像数据转换特性的曲线图。利用此范例,转换后数据值按以下顺序不同,蓝 (B) > 红 (R) > 绿 (G)。

[0269] 首先,图 9A 和 B 的水平轴示出输入数据,即图像数据为 10 位时的图像数据灰度值。图 9A 和 B 的竖直轴示出由 LUT 123 将图像数据转换得到的转换的数据的灰度值。基于数据驱动器 22 中的此转换的数据设定 RGB 电压幅度。另外,在 LUT 123 中预先设定图像数据灰度值的转换的数据灰度值的转换特性。图 9A 示为将转换的数据灰度值设定为与图像数据灰度值成线性关系。图 9B 示为将转换的数据灰度值设定为与图像数据灰度值成曲线伽玛特性关系。能够如所需地自由设定的转换的数据灰度值与 LUT 123 中的图像数据灰度值的关系。

[0270] 这里,当具有 10 位组成时,数据驱动器 22 的 VDAC118(i) 能够接收输入数据 0 ~ 1023。然而,LUT 123 转换后的转换的数据设定为约 0 ~ 600。这是基于以下原因。

[0271] 图 10A 和 B 的水平轴示出了输入数据,与图 9A 和 B 中相同。图 10A 和 B 的竖直轴

示出从控制单元 16 输入至数据驱动器 22 的对应于图像数据灰度值的数字数据  $Din(i)$ 。

[0272] 这里,图 10A 基于图 9A,图 10B 基于图 9B。如上述,在本实施例中,基于控制单元 16 中的阈值电压  $Vth$  的估计值对供应的图像数据执行校正。

[0273] 如方程 (109) 中所示,此校正包括基于图像数据的电流放大因子  $\beta$  的无规性的校正,和增加对应于作为其校正的结果获得的数据的阈值电压  $Vth$  的量的校正。

[0274] 这里,因为数据驱动器 22 的 VDAC 118 中的灰度电压  $VD1$  设定为阈值电压  $Vth$  为上述初始值  $Vth0$  时的值,所以根据校正增加至灰度电压  $VD1$  的量是对应于  $\Delta Vth$  的量,  $\Delta Vth$  是阈值电压  $Vth$  相对于其初始值  $Vth0$  的改变量。

[0275] 这里,从控制单元 16 输出的数字数据  $Din(i)$  的灰度值必需在数据驱动器 22 的 VDAC118(i) 的输入致能范围 ( $0 \sim 1023$ ) 内。

[0276] 因此,在由 LUT 123 转换后的转换的数据灰度值的最大值设定为通过校正增加的量被从数据驱动器 22 的 VDAC 118(i) 的输入致能范围预先减去的值。

[0277] 这里,通过校正增加的量不是固定的量,因为其根据阈值电压  $Vth$  的改变量  $\Delta Vth$  确定,并且其随使用时间逐渐增大。

[0278] 因此,例如通过基于显示设备 1 的估计的使用时间估计通过校正增加的量的最大值,来确定由 LUT 123 转换的数据灰度值的最大值。

[0279] 另外,当图像数据的灰度值为黑色显示中的零时,有机 EL 元件 101 处于不发光状态。因此,此时不必进行以上校正。结果,当黑色显示中的图像数据具有零灰度时,控制单元 16 将零灰度原样供应至数据驱动器 22,不进行对阈值的波动校正,并且不参照 LUT 123。

[0280] 以下提供根据实施例的显示设备 1 的操作的描述。

[0281] 在初始步骤中,当利用自动调零方法进行每个数据线  $Ldi$  的电压测量时,控制单元 16 控制阳极电路 12 在阳极线  $La$  上施加电压  $ELVSS$ 。

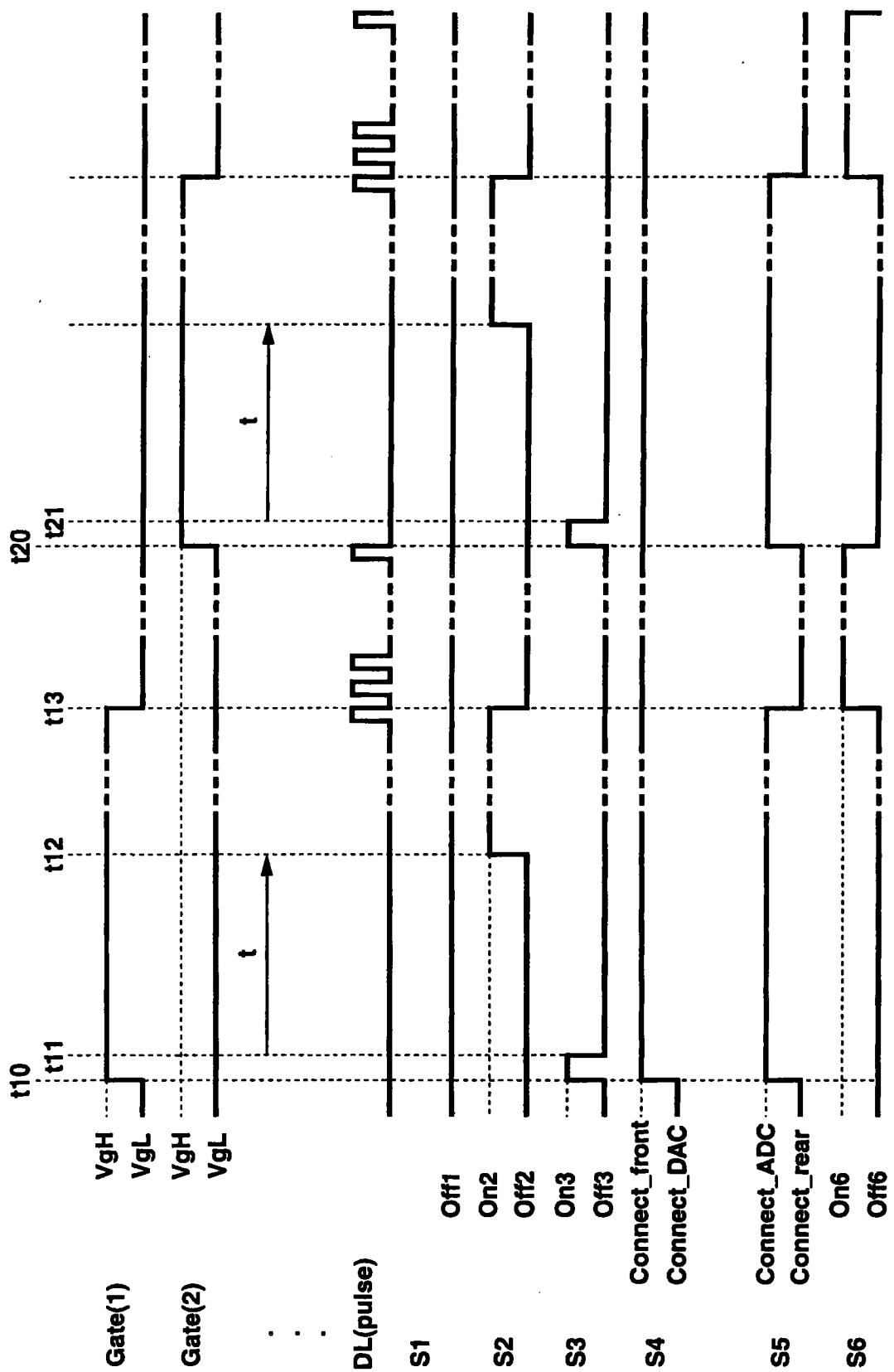

[0282] 图 11 是示出利用自动调零方法进行电压测量时,每个部件的操作的时序图。

[0283] 如图 11 中所示,控制单元 16 在时间  $t10$  向选择驱动器 13 供应开始脉冲。此时,选择驱动器 13 向选择线  $Ls1$  输出  $VgH$  电平  $Gate(1)$  信号。

[0284] 当通过选择驱动器 13 将  $VgH$  电平  $Gate(1)$  信号输出至选择线  $Ls1$  时,像素  $21(i, j)$  ( $i = 1 \sim m$ ) 的第一列的晶体管  $T1$  和  $T2$  成为导通状态。当晶体管  $T1$  处于导通状态时,晶体管  $T3$  的栅极 - 漏极连接,并且晶体管 3 成为二极管连接状态。

[0285] 在时间  $t10$ ,控制单元 16 向数据驱动器 22 供应信号  $Off1$ 、 $Off2$ 、 $On3$ 、 $Connect_{front}$ 、 $Connect_{ADC}$ 、和  $Off6$  中的每一个作为开关控制信号  $S1 \sim S6$ 。

[0286] 图 12A 和 B 是示出从数据驱动器向控制单元 16 输出数据时,每个开关的连接性关系的图示。

[0287] 此时,从控制单元 16 供应  $Connect_{front}$  信号,并且如图 12A 中所示,开关  $Sw4(i)$  连接数据锁存器电路 116(i) 的输出端子和前端子 ( $i = 1 \sim m$ )。

[0288] 此时,从控制单元 16 供应  $Connect_{ADC}$  信号,并且如图 12A 中所示,开关  $Sw5(i)$  连接数据锁存器电路 116(i) 的输入端子和电平移动电路 115(i) 的输出端子 ( $i = 1 \sim m$ )。

[0289] 图 13A、B 和 C 是示出利用自动调零方法进行电压测量时,每个开关的连接性关系的图示。

[0290] 当从控制单元 16 向开关  $Sw1(i)$  和  $Sw2(i)$  分别供应  $Off1$  和  $Off2$  信号时,开关

Sw1(i) 和 Sw2(i) 成为截止状态。此外,当从控制单元 16 向开关 Sw3(i) 供应 On3 信号时,其成为导通状态 ( $i = 1 \sim m$ )。

[0291] 因为在晶体管 T1 至 T3 处于导通状态时,模拟电源 14 的参考电压 Vref 具有负极性的电压,所以模拟电源 14 通过数据线 Ldi 从像素 21(i, j) ( $i = 1 \sim m$ ) 的第 i 行引出电流 Id。

[0292] 此时,像素 21(i, j) ( $i = 1 \sim m$ ) 的第一列的有机 EL 元件 101 不发光,因为阴极电位为 Vcath 并且阳极侧成为比 Vcath 更负的电位,导致反偏,并且电流将不流动。

[0293] 因为开关 Sw1(i) 和 Sw2(i) ( $i = 1 \sim m$ ) 处于截止状态,所以模拟电源 14 引出的电流 Id 不能流至缓冲器 113(i)、119(i) ( $i = 1 \sim m$ )。

[0294] 因此,如图 13A 中所示,电流 Id 经由每个数据线 Ldi 从像素 21(i, j) ( $i = 1 \sim m$ ) 的第一列的晶体管 T3 和 T2 流向模拟电源 14。

[0295] 当电流 Id 流动时,以参考电压 Vref 确定的电压对每个像素 21(i, j) ( $i = 1 \sim m$ ) 的保持电容进行充电。

[0296] 随后,在时间 t11,当完成这些电容的充电时,控制单元 16 向数据驱动器 22 供应 Off3 信号作为开关控制信号 S3。

[0297] 如图 13B 中所示,当从控制单元 16 供应 Off3 信号时,开关 Sw3(i) 成为截止状态。此时,开关 Sw1(i) 和 Sw2(i) 中的每一个保持在截止状态。因此,通过将开关 Sw3(i) 切换到截止状态,中断有机 EL 面板 21 和数据驱动器 22 之间的连接。以此方式,给数据线 Ldi 产生高阻抗状态 (HZ)。

[0298] 紧接在数据线 Ldi 中建立高阻抗状态后,储存在保持电容 Cs 中的电荷保持在最后的先前值,由此维持晶体管 T3 中的导通状态。

[0299] 以此方式,电流继续在晶体管 T3 的漏极 - 源极之间流动,且晶体管 T3 的源极端子侧的电位逐渐增大,接近漏极端子侧的电位。因此,在晶体管 T3 的漏极 - 源极之间流动的电流的电流值继续减小。

[0300] 与此结合,保持电容 Cs 中储存的一部分电荷被放电,并且保持电容 Cs 的两个端子之间的电压降低。通过这样,晶体管 T3 的栅极电压 Vgs 逐渐降低,由此将数据线 Ldi 的电压的绝对值从参考电压 Vref 逐渐降低。

[0301] 在时间 t12,控制单元 16 向数据驱动器 22 供应 On2 信号作为开关控制信号 S2,时间 t12 是从时间 t11 经过预定沉降时间 t 时的时间。此沉降时间 t 设定为满足条件  $C / (\beta t) < 1$ 。

[0302] 如图 13C 中所示,此时,从控制单元 16 供应 On2 信号,开关 Sw2(i) 成为导通状态,且 ADC 114(i) 获取数据线 Ldi 的电压值作为测得的电压 Vmeas(t1) ( $i = 1 \sim m$ )。

[0303] 电平移动电路 115(i) 对 ADC114(i) ( $i = 1 \sim m$ ) 获取的测得的电压 Vmeas(t1) 进行电平移动。

[0304] 如图 12A 中所示,因为数据锁存器电路 116(i) 的输入端子和电平移动电路 115(i) 的输出端子通过开关 Sw5(i) 相互连接,由每个电平移动电路 115(i) 进行了电平移动的测得的电压 Vmeas(t1) 供应至数据锁存器电路 116(i) ( $i = 1 \sim m$ )。

[0305] 控制单元 116 向数据驱动器 22 输出数据锁存器脉冲 DL(脉冲),并在接收到此脉冲时,数据锁存器电路 116(i) ( $i = 1 \sim m$ ) 的每一个保持供应的测得的电压 Vmeas(t1)。

[0306] 在时间  $t_{13}$ , Gate(1) 信号下降, 控制单元 16 向数据驱动器 22 供应  $On_6$  信号作为开关控制信号  $S_6$ , 并且在接收到此信号时, 开关  $Sw_6$  成为导通状态, 如图 12B 中所示。

[0307] 如图 12B 中所示, 数据锁存器电路 116(i) 的输出端子和开关  $Sw_6$  的一个端子由从控制单元 16 供应给开关  $Sw_4(i)$  的 Connect\_rear 信号通过开关  $Sw_4(1)$  的前端子连接, 并且数据锁存器电路 116(i) 的输出端子和开关  $Sw_5(i-1)$  的输入端子通过开关  $Sw_4(i)$  ( $i = 2 \sim m$ ) 的前端子连接。

[0308] 因此, 在每次从控制单元 16 供应 DL(脉冲) 时, 数据锁存器电路 116(i) 顺序将测得的像素  $21(i, 1)$  的第一列的数据线  $L_{di}$  的电压  $V_{meas}(t_1)$  向前传送, 并作为数据  $D_{out}(i)$  输出至控制单元 16 ( $i = 1 \sim m$ ), 电压  $V_{meas}(t_1)$  由数据锁存器电路 116 保持。

[0309] 控制单元 16 获取数据  $D_{out}(i)$  ( $i = 1 \sim m$ ), 并在图 8 中所示的存储器 122 的像素数据储存区 122a 中储存此数据。以此方式完成对第一列像素  $21(i, 1)$  ( $i = 1 \sim m$ ) 的电压测量。

[0310] 当 Gate(2) 信号在时间  $t_{20}$  上升时, 控制单元 16 以与上述相同的方式向数据驱动器 22 供应开关控制信号  $S_1-S_6$ , 由此对第二列像素  $21(i, 2)$  执行数据线  $L_{di}$  ( $i = 1 \sim m$ ) 的电压测量。

[0311] 对每一列重复该测量, 在对第  $n$  列像素  $21(i, n)$  执行了数据线  $L_{di}$  ( $i = 1 \sim m$ ) 的电压测量后, 完成时间  $t_1$  中的每个电压测量。

[0312] 其后, 控制单元 16 以相同方式设定沉降时间  $t$  为  $t_2$  并对每个像素  $21(i, j)$  ( $i = 1 \sim m, j = 1 \sim n$ ) 执行数据线  $L_{di}$  的电压测量。控制单元 16 获取针对沉降时间  $t_2$  的每个像素  $21(i, j)$  的数据线  $L_{di}$  的测得的电压  $V_{meas}(t_2)$ , 并将其储存在存储器 122 ( $i = 1 \sim m, j = 1 \sim n$ ) 的像素数据储存区 122a 中。

[0313] 接下来, 控制单元 16 以相同方式设定沉降时间  $t$  为  $t_3$  并对每个像素  $21(i, j)$  ( $i = 1 \sim m, j = 1 \sim n$ ) 执行数据线  $L_{di}$  的电压测量。控制单元 16 获取针对沉降时间  $t_3$  的每个像素  $21(i, j)$  的数据线  $L_{di}$  的测得的电压  $V_{meas}(t_3)$ , 并将其储存在存储器 122 ( $i = 1 \sim m, j = 1 \sim n$ ) 的像素数据储存区 122a 中。

[0314] 图 14 是解释获取校正参数时, 控制单元执行的驱动顺序的图示。

[0315] 控制单元 16 获取测得的电压  $V_{meas}(t_1)$ 、 $V_{meas}(t_2)$ 、和  $V_{meas}(t_3)$ , 并且在将它们储存在存储器 122 的每个像素数据储存区 122a 中后, 根据图 14 中所示的驱动顺序进行计算, 由此获取校正参数。

[0316] 控制单元 16 从存储器 122 的每个像素数据储存区 122a 读取像素  $21(1, 1)$  的数据线  $L_{di}$  的测得的电压  $V_{meas}(t_1)$  和  $V_{meas}(t_2)$  (步骤 S11)。

[0317] 此外, 控制单元 16 根据方程 (103) 进行计算, 由此获取像素  $21(1, 1)$  的阈值电压  $V_{th0}$  和  $C/\beta$  (步骤 S12)。

[0318] 控制单元 16 对每个像素  $21(i, j)$  ( $i = 1 \sim m, j = 1 \sim n$ ) 执行此处理。一旦获取了每个像素  $21(i, j)$  的阈值电压  $V_{th0}$  和  $C/\beta$ , 则获取每个像素  $21(i, j)$  的  $C/\beta$  的平均值  $\langle C/\beta \rangle$  (步骤 S13), 并在操作中设定沉降时间  $t = t_0$ 。

[0319] 控制单元 16 使用确定的沉降时间  $t_0$  获取由方程 (105) 定义的偏移电压  $V_{offset}$  (步骤 S14)。

[0320] 控制单元 16 将获取的平均值  $\langle C/\beta \rangle$  和偏移电压  $V_{offset}$  分别储存在存储器 122

的  $\langle C / \beta \rangle$  储存区 122b 和偏移电压储存区 122c 中。控制单元 16 还从存储器 122 的每个像素数据储存区 122a 读取像素  $21(i, j)$  ( $i = 1 \sim m, j = 1 \sim n$ ) 的测得的电压  $V_{meas}(t3)$  (步骤 S15)。

[0321] 控制单元 16 使用作为  $V_{th}$  的先前获取的  $V_{th0}$  和每个像素  $21(i, j)$  的测得的电压  $V_{meas}(t3)$  通过修改方程 (106) 进行计算, 以获取每个像素  $21(i, j)$  ( $i = 1 \sim m, j = 1 \sim n$ ) 的  $\Delta \beta / \beta$  (步骤 S16)。

[0322] 控制单元 16 将获取的  $\Delta \beta / \beta$  储存在存储器 122 的每个像素数据储存区 122a 中。

[0323] 图 15 是解释在校正后将基于供应的图像数据的电压信号输出至数据驱动器时, 控制单元 16 执行的驱动顺序的图示。

[0324] 图像数据供应至操作中的控制单元 16。控制单元 16 根据图 15 中所示的驱动顺序 (2) 校正图像数据。

[0325] 控制单元 16 根据图 11 中所示的定时图控制每个部件, 并从数据驱动器 22 获取针对对真实操作 (应用) 确定的沉降时间  $t = t0$  的测得的电压  $V_{meas}(t0)$  (步骤 S21)。然后, 控制单元将获取的测得的电压  $V_{meas}(t0)$  储存在存储器 122 的每个像素数据储存区 122a 中。

[0326] 在输入图像数据的数字信号时, 控制单元 16 对每个像素  $21(i, j)$  ( $i = 1 \sim m, j = 1 \sim n$ ) 参照 LUT 123 对每个 RGB 图像数据进行灰度值转换。转换的灰度值指定为电压值  $V_{data0}$  并作为每个像素  $21(i, j)$  的原始灰度信号 (步骤 S22)。

[0327] 如上述, 原始灰度信号的最大值设定为基于诸如上述阈值电压  $V_{th}$  的特性参数从 VDAC 118(i) 的输入范围中的最大值减去校正量而得到的值以下的值。

[0328] 通过使用  $\Delta \beta / \beta$  作为  $\beta$  的无规性的校正参数根据方程 (107) 进行计算, 控制单元 16 获取对应于电压值  $V_{data1}$  的信号。

[0329] 控制单元 16 从存储器 122 的偏移电压储存区 122c 读取偏移电压  $V_{offset}$ , 并通过使用测得的电压  $V_{meas}(t0)$  和偏移电压  $V_{offset}$  根据方程 (108) 进行计算来获取阈值电压  $V_{th}$  作为校正量 (步骤 S24)。

[0330] 通过根据方程 (109) 将电压值  $V_{data1}$  和阈值电压  $V_{th}$  相加, 控制单元 16 获取对应于电压值  $V_{data}$  的信号作为校正的灰度信号 (步骤 S25)。

[0331] 控制单元 16 对每个像素执行此类型的驱动顺序 (2)。此外, 控制单元 16 将对应于电压值  $V_{data}$  的信号输出至数据驱动器 22 作为每个像素的数据  $Din(1) \sim Din(m)$ 。

[0332] 图 16 是示出操作中每个部件的操作的定时图。

[0333] 控制单元根据图 16 中所示的数据输出定时图控制每个部件, 并将数据  $Din(1) \sim Din(m)$  输出至数据驱动器 22。

[0334] 在时间  $t30$ , 控制单元 16 向数据驱动器 22 供应信号 Off1、Off2、Off3、Connect\_DAC、Connect\_DRB、和 Off6 的每一个作为开关控制信号  $S1 \sim S6$ 。

[0335] 图 17 是示出写入电压信号时, 每个开关的连接性关系的图示。

[0336] 如图 17 中所示, 当从控制单元 16 供应 Off2 和 Off3 信号时,  $Sw2(i)$  和  $Sw3(i)$  均进入截止状态, 中断缓冲器 113(i) 和数据线  $Ldi$  之间的连接, 以及模拟电源 14 和数据线  $Ldi$  之间的连接。

[0337] 当从控制单元 16 供应 On1 信号时, 每个开关  $Sw1(i)$  成为导通状态, 由此通过缓冲

器 119(i) 连接 VDAC 118(i) 和数据线 Ldi。

[0338] 图 18 是示出将数据从控制单元 16 输入至数据驱动器 22 时, 每个开关的连接性关系的图示。

[0339] 如图 18 中所示, 当从控制单元 16 供应 Connect\_DRB 信号至开关 Sw5(i) 的每一个时, 每个开关 Sw5(i) 连接数据锁存器电路 116(i) 的输入端子和数据寄存器组 112 的输出端子。

[0340] 当从控制单元 16 供应 Connect\_DAC 信号至开关 Sw4(i) 的每一个时, 每个开关 Sw4(i) 连接数据锁存器电路 116(i) 的输出端子和 DAC 侧端子。

[0341] 当从控制单元 16 向开关 Sw6 供应 Off6 信号时, 开关 Sw6 成为截止状态, 中断数据锁存器电路 116(1) 和控制单元 16 之间的连接。

[0342] 如图 16 中所示, 控制单元 16 在时间 t31 抬高开始脉冲 SP2 并在时间 t32 使开始脉冲下降至 Lo 电平。

[0343] 当开始脉冲 SP2 下降至 Lo 电平时, 通过根据时钟信号顺序地对开始脉冲 SP2 进行移位, 图 5 中所示的数据驱动器 22 的移位寄存器生成移位信号, 并将生成的移位信号供应至数据寄存器组 112。

[0344] 通过与供应的移位信号同步, 数据寄存器组 112 顺序地取出数据 Din(1) ~ Din(m)。

[0345] 当在时间 t33 将 Gate(1) 信号抬高至 VgH 电平时, 像素 21(i,1) (i = 1 ~ m) 的每个晶体管 T1 和 T2 成为导通状态。

[0346] 控制单元 16 抬高数据锁存器脉冲 DL(脉冲), 且数据驱动器 22 的数据锁存器电路 116(i) (i = 1 ~ m) 在抬高数据锁存器脉冲 DL(脉冲) 的定时锁存数据。

[0347] 电平移动电路 117(i) 对数据锁存器电路 116(i) 锁存的数据执行电平移动, 并供应经电平移动的数据至 VDAC118(i) (i = 1 ~ m)。

[0348] VDAC 118(i) 将数字数据转换为负模拟电压, 并通过缓冲器 118(i) (i = 1 ~ m) 将转换的负模拟电压施加于数据线 Ldi 上。

[0349] 当负模拟电压施加于数据线 Ldi 上时, 每个像素 21(i,j) (i = 1 ~ m) 的有机 EL 元件 101 成为反偏, 阻止电流流动。通过数据线 Ldi、以及像素 21(i,1) (i = 1 ~ m) 的晶体管 T3 和 T2, 电流从阳极电路 12 流至数据驱动器 22 的 VDAC 118(i)。

[0350] 因为每个像素 21(i,1) (i = 1 ~ m) 的晶体管 T1 处于导通状态, 晶体管 t3 为栅极 - 漏极连接且为二极管连接。因此, 晶体管 T3 工作于饱和区, 且漏极电流 Id 按晶体管 T3 中的二极管特性流动。

[0351] 因为晶体管 T1 为导通状态且漏极电流 Id 流至晶体管 t3, 所以晶体管 T3 的栅极电压 Vgs 设定为确定漏极电流 Id 的电压, 且保持电容 Cs 由栅极电压 Vgs 充电。

[0352] 以此方式, 如图 17 中所示, 数据驱动器 22 从每个像素 21(i,1) (i = 1 ~ m) 的晶体管 T3 引出基于校正参数校正的电流, 基于电压值 Vdata 的晶体管 T3 的栅极电压 Vgs 由保持电容 Cs 保持。

[0353] 以此方式完成将数据写入到第一列中的每个像素 21(i,1) (i = 1 ~ m) 的保持电容 Cs 中。

[0354] 在时间 t34, 控制单元 16 随 DL(脉冲) 的降低抬高开始脉冲 SP2, 且在时间 t35 降

低开始脉冲 SP2 并将数据写入到第二列中的每个像素  $21(i, 2)$  ( $i = 1 \sim m$ ) 的保持电容  $C_s$  中。

[0355] 其后,以此方式,控制单元 16 基于电压值  $V_{data}$  将电压顺序地写入到像素  $21(i, 3)$  ( $i = 1 \sim m, \dots, 21(i, n)$  ( $i = 1 \sim m$ )) 的保持电容  $C_s$  中。

[0356] 在将电压值  $V_{data}$  写入到所有像素  $21(i, j)$  的保持电容  $C_s$  中后,且在  $Gate(n)$  信号为  $V_{gL}$  时,所有像素  $21(i, j)$  的晶体管 T1 和 T2 成为截止状态。

[0357] 当所有像素  $21(i, j)$  的晶体管 T1 和 T2 成为截止状态时,晶体管 T3 成为不可选状态。当晶体管 T3 成为不可选状态时,晶体管 T3 的栅极电压  $V_{gs}$  保持在保持电容  $C_s$  中的写入的电压。

[0358] 控制单元 16 控制阳极电路 12,使得电压  $ELVDD$  施加于阳极线  $La$  上。此电压  $ELVDD$  设定为例如 15V。

[0359] 此时,因为晶体管 T3 的栅极电压  $V_{gs}$  由保持电容  $C_s$  保持,漏极电流  $I_d$  与将电流值  $V_{data}$  写入到保持电容  $C_s$  中时在晶体管 T3 的漏极 - 源极之间流动的电流的值相同。

[0360] 因为晶体管 T1 处于截止状态,且有机 EL 元件 101 的阳极侧的电位比 其阴极侧的电位高,所以将漏极电流供应至有机 EL 元件 101。

[0361] 此时,基于阈值电压  $V_{th}$  和  $\beta$  的无规性的波动校正流至每个像素  $21(i, j)$  的有机 EL 元件 101 的电流  $I_d$ ,且有机 EL 元件 101 以校正的电流发光。

[0362] 如上述,根据本实施例的显示设备 1 选择满足  $(C/\beta)/t < 1$  的例如  $t_1$  和  $t_2$  的沉降时间作为沉降时间  $t$ ,并根据自动调零方法,以对应于所选的沉降时间的数量的次数执行每个数据线  $L_{di}$  的电压测量。

[0363] 显示设备 1 选择满足  $(C/\beta)/t \geq 1$  的时间  $t_3$  作为沉降时间  $t$ ,并根据自动调零方法,执行每个数据线的电压测量,由此获取表示每个像素的像素驱动电路的电流放大因子  $\beta$  的无规性的  $(\Delta \beta / \beta)$ 。

[0364] 因此,显示设备 1 基于获取的  $(\Delta \beta / \beta)$  校正基于操作中供应的图像数据的电压值  $V_{data0}$ ,并从而能够获取校正的电压值  $V_{data1}$ 。此外,其基于获取的阈值电压  $V_{th}$  校正校正的电压值  $V_{data1}$ ,并从而能够获取电压值  $V_{data}$ 。

[0365] 以根据本实施例的此方式,能够实现像素驱动设备,其基于操作中供应的图像数据校正供应至有机 EL 元件 101 的电流,以减小每个显示的像素  $21(i, j)$  中阈值电压的波动的影响和像素间电流放大因子的无规性。因此,利用此像素驱动设备,通过显示设备 1 控制显示图像中源自此类型的波动和无规性的图像质量的退化变得可能。

[0366] 此外,根据本实施例的显示设备能够获取阈值电压  $V_{th}$ 、 $(C/\beta)$  值、和表示  $\beta$  的无规性的  $(\Delta \beta / \beta)$  作为像素驱动设备中具有公共 (common) 电路的每个像素的特性参数。

[0367] 因此,在提供上述校正方面,显示设备 1 能够简化像素驱动设备或显示设备 1 的构成,无需配备测量  $\beta$  的无规性的单独的电路或测量阈值电压  $V_{th}$  的电路。

[0368] 此外,可以考虑本发明的各种实施例,而不限于上述实施例。

[0369] 例如,本实施例中描述了演示有机 EL 元件作为发光元件。然而,发光元件不限于有机 EL 元件,而可以是例如无机 EL 元件或 LED。

[0370] 虽然本实施例描述了将本发明应用于具有有机 EL 面板 21 的显示设备 1,但是本发明不限于此范例。例如,可以将其应用于提供发光元件阵列的曝光设备,其中,具有发光元

件（有机 EL 元件 101 等）的多个像素布置在单个方向上，并基于图像数据从发光元件阵列辐射输出束到感光体鼓上以 曝光鼓上的感光体。采用本实施例的曝光设备能够控制归因于像素间特性的无规性和像素特性随时间的退化的曝光条件的退化。

[0371] 本实施例使得能够设定两个时间  $t_1$  和  $t_2$  作为满足  $(C/\beta)/t < 1$  的沉降时间。然而，也可以设定满足此条件的三个或更多个沉降时间。

[0372] 本实施例使得控制单元 16 使用 LUT 123 基于供应的图像数据对每个 RGB 执行转换。然而，通过引入并计算方程来代替使用 LUT 123，控制单元 16 也可以对图像数据执行此类型的转换。

[0373] 可以不脱离本发明的宽广精神和范围作出各种实施例和改变。上述实施例意在示例本发明，而不是限制本发明的范围。本发明的范围由所附的权利要求限定，而不是由实施例限定。在本发明的权利要求的等同意义的范围内和权利要求的范围内所作的各种修改视为在本发明的范围内。

[0374] 此申请以 2008 年 11 月 28 日提交的并包括说明书、权利要求、附图和发明内容的日本专利申请 2008-305714 号为基础。于此通过引用并入了上述日本专利申请公开的全部内容。

图 1

图 2

图 3A

|                                                                  |

|------------------------------------------------------------------|

| $VI\_0: Id_0 = \beta_0 (V_{data} - V_{th0})^2$                   |

| $VI\_1: Id_1 = (\beta_0 - \Delta\beta) (V_{data} - V_{th0})^2$   |

| $VI\_2: Id_2 = (\beta_0 + \Delta\beta) (V_{data} - V_{th0})^2$   |

| $VI\_3: Id_3 = \beta_0 (V_{data} - (V_{th0} + \Delta V_{th}))^2$ |

图 3B

图 4A

图 4B

图 6A

图 6B

图 7

图 8

图 9A

图 9B

图 10A

图 10B

图 11

图 12A

图 12B

图 14

图 15

图 16

图 17

图 18

|                |                                                    |         |            |

|----------------|----------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种像素驱动设备、发光设备和像素驱动设备中的特性参数获取方法                     |         |            |

| 公开(公告)号        | <a href="#">CN101978412B</a>                       | 公开(公告)日 | 2014-08-20 |

| 申请号            | CN200980109383.3                                   | 申请日     | 2009-11-27 |

| [标]申请(专利权)人(译) | 卡西欧计算机株式会社                                         |         |            |

| 申请(专利权)人(译)    | 卡西欧计算机株式会社                                         |         |            |

| 当前申请(专利权)人(译)  | 卡西欧计算机株式会社                                         |         |            |

| [标]发明人         | 小仓润<br>武居学<br>樋山俊二                                 |         |            |

| 发明人            | 小仓润<br>武居学<br>樋山俊二                                 |         |            |

| IPC分类号         | G09G3/32                                           |         |            |

| CPC分类号         | G09G3/3291 G09G2320/04 G09G2300/0819 G09G2300/0842 |         |            |

| 代理人(译)         | 陈松涛                                                |         |            |

| 审查员(译)         | 朱琼                                                 |         |            |

| 优先权            | 2008305714 2008-11-28 JP                           |         |            |

| 其他公开文献         | <a href="#">CN101978412A</a>                       |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>     |         |            |

## 摘要(译)

一种像素驱动设备，具有：电压施加电路(14)、电压测量电路(114)、以及特性参数获取电路(16)，电压施加电路输出超过驱动晶体管(T3)的阈值电压的参考电压(Vref)，特性参数获取电路获取与像素的电特性相关的特性参数。像素驱动设备在具有电致发光元件(101)和驱动晶体管的像素上施加参考电压。在从参考电压被切断起，多个沉降时间中的每一个消逝后，电压测量电路获取信号线(Ld)的电压作为测得的电压。特性参数获取电路基于电压测量电路获取的多个测得的电压的值，获取驱动晶体管的阈值电压和电流放大因子作为特性参数。