1. 一种有机发光显示器，其包括：

包括电路区域和像素区域的基板；

分别排列在所述电路区域和所述像素区域上的至少一个电路薄膜晶体管和至少一个像素薄膜晶体管，每个薄膜晶体管包括半导体层、栅电极、源电极和漏电极；

电连接到所述至少一个像素薄膜晶体管的所述源和漏电极中之一的像素电极；以及

至少一个氮化硅层布置在所述电路薄膜晶体管的源和漏电极与所述基板之间，且在整个像素区域中开口。

2. 根据权利要求 1 的有机发光显示器，其进一步包括布置在所述电路薄膜晶体管和像素薄膜晶体管的源和漏电极与所述基板之间的至少一层氧化硅层。

3. 根据权利要求 1 的有机发光显示器，其中所述氮化硅层包括布置在所述基板与所述至少一个电路薄膜晶体管的半导体层之间的缓冲氮化硅层。

4. 根据权利要求 3 的有机发光显示器，其进一步包括缓冲氧化硅层，所述缓冲氧化硅层布置在所述基板与所述缓冲氮化硅层之间或布置在所述缓冲氮化硅层与所述至少一个电路薄膜晶体管的半导体层之间，以及布置在所述基板与所述至少一个像素薄膜晶体管的半导体层之间。

5. 根据权利要求 1 的有机发光显示器，其中所述氮化硅层包括布置在所述至少一个电路薄膜晶体管的半导体层与所述至少一个电路薄膜晶体管的栅电极之间的栅绝缘氮化硅层。

6. 根据权利要求 5 的有机发光显示器，其进一步包括栅绝缘氧化硅层，所述栅绝缘氧化硅层布置在所述至少一个电路薄膜晶体管的半导体层与所述栅绝缘氮化硅层之间或布置在所述栅绝缘氮化硅层与所述至少一个电路薄膜晶体管的栅电极之间，以及布置在所述至少一个像素薄膜晶体管的半导体层与所述至少一个像素薄膜晶体管的栅电极之间。

7. 根据权利要求 1 的有机发光显示器，其中所述氮化硅层包括布置在所述至少一个电路薄膜晶体管的栅电极与所述至少一个电路薄膜晶体管的源和漏电极之间的层间绝缘氮化硅层。

8. 根据权利要求 7 的有机发光显示器，其进一步包括层间绝缘氧化硅层，所述层间绝缘氧化硅层布置在所述至少一个电路薄膜晶体管的栅电极与所述层间绝缘氮化硅层之间或布置在所述层间绝缘氮化硅层与所述至少一个电路薄膜晶体管的源和漏电极之间，以及布置在所述至少一个像素薄膜晶体管的栅电极与所述至少一个像素薄膜晶体管的源/漏电极之间。

9. 根据权利要求 1 的有机发光显示器，其中所述半导体层包括多晶硅层。

10. 根据权利要求 1 的有机发光显示器，其中所述像素电极包括透明电极。

11. 根据权利要求 1 的有机发光显示器，其进一步包括布置在所述像素电极上的发光层和布置在所述发光层上的相对电极。

12. 一种制造有机发光显示器的方法，该方法包括：

提供具有电路区域和像素区域的基板；

在所述基板的所述电路区域和像素区域上分别形成至少一个电路薄膜晶体管和至少一个像素薄膜晶体管，每个薄膜晶体管包括半导体层、栅电极、源电极和漏电极；

形成电连接到所述至少一个像素薄膜晶体管的源和漏电极中之一的像素电极；以及

在形成所述源和漏电极之前，在所述基板上形成在整个像素区域中开口的至少一层氮化硅层。

13. 根据权利要求 12 的方法，其进一步包括在形成所述电路薄膜晶体管和像素薄膜晶体管的源和漏电极之前，在所述基板上形成至少一层氧化硅层。

14. 根据权利要求 12 的方法，

其中所述氮化硅层包括在形成所述半导体层之前在所述基板上形成的缓冲氮化硅层，以及

进一步包括在形成所述缓冲氮化硅层之前或形成所述缓冲氮化硅层之后在所述基板的整个表面上形成缓冲氧化硅层。

15. 根据权利要求 12 的方法，

其中所述氮化硅层包括在形成所述栅电极之前在所述半导体层上形成的栅绝缘氮化硅层，以及

---

进一步包括在形成所述栅绝缘氮化硅层之前或者形成所述栅绝缘氮化硅层之后在所述基板的整个表面上形成栅绝缘氧化硅层。

16. 根据权利要求 12 的方法，

其中所述氮化硅层包括在形成所述源和漏电极之前在所述栅电极上形成的层间绝缘氮化硅层；

还包括在所述栅电极和层间绝缘氮化硅层之间形成层间绝缘氧化硅层，以及

其中所述层间绝缘氮化硅层与利用半色调网点掩模在所述氮化硅层和所述层间绝缘氧化硅层中形成源极和漏极接触孔同时形成。

## 有机发光显示器及其制造方法

### 优先权要求

本申请参照 2004 年 2 月 9 日向韩国知识产权局提交的标题为“ORGANIC LIGHT EMITTING DISPLAY AND METHOD OF FABRICATING THE SAME(有机发光显示器及其制造方法)”、序列号为 No. 2004-8494 的申请，并要求其在中国获得的所有权益，该申请在此引入。

### 技术领域

本发明涉及一种显示装置及其制造方法，尤其涉及一种有机发光显示器(OLED)及其制造方法。

### 背景技术

OLED 配备有排列成矩阵结构的  $N \times M$  子像素，并根据驱动  $N \times M$  子像素的方式分为无源矩阵 LED 或有源矩阵 LED。

有源矩阵 OLED 的每个像素包括像素电极和至少一个用于将电信号提供给像素电极的薄膜晶体管(TFT)。此外，有源矩阵 OLED 可以包括单块基板上的像素部分和电路部分。在像素部分中，像素排列成矩阵结构。电路部分具有用于控制像素部分的电路。电路部分布置在像素部分的周边，并且用于控制像素部分的电路包括 TFT。因此，有源矩阵 OLED 可以在像素部分和电路部分中包括各自的 TFT，即像素 TFT 和电路 TFT。

在日本公开专利公告 No.H05-55582 中论述了一种 TFT。在该日本专利中论述的 TFT 包括由布置在绝缘基板上的氮化硅形成的第一阻挡层、由布置在第一阻挡层上的氧化硅形成的绝缘层、布置在绝缘层上的半导体层、布置在半导体层上的栅电极、由布置在栅电极上的氮化硅形成的第二阻挡层、和由布置在第二阻挡层上的 PSG 形成的层间绝缘层。然而，将这种 TFT 共用到电路 TFT 和像素 TFT 可能会有碍需要不同电学特性的电路 TFT 和像素 TFT 的电学特性的优化。

## 发明内容

因此，本发明通过提供一种 OLED 解决与传统器件有关的上述问题，在这种 OLED 中电路 TFT 和像素 TFT 各自的电学特性得到了最优化。

在本发明的示范性实施例中，OLED 包括具有电路区域和像素区域的基板。至少一个电路 TFT 和至少一个像素 TFT 分别排列在电路区域和像素区域上。每个 TFT 具有半导体层、栅电极、源电极和漏电极。将像素电极电连接到至少一个像素 TFT 的源和漏电极中的一个。至少一个氮化硅层布置在源和漏电极与基板之间，并在整个像素区域中开口（opened）。

该 OLED 还可以包括布置在源和漏电极与基板之间的至少一层氧化硅层。

氮化硅层可以包括  $\text{SiN}_x$  或  $\text{SiON}$ 。

氮化硅层可以为布置在基板与至少一个电路 TFT 的半导体层之间的缓冲氮化硅层。此外，OLED 还可以包括布置在基板与缓冲氮化硅层之间或在缓冲氮化硅层与至少一个电路 TFT 的半导体层之间，以及在基板与至少一个像素 TFT 的半导体层之间的缓冲氧化硅层。

氮化硅层可为布置在至少一个电路 TFT 的半导体层与至少一个电路 TFT 的栅电极之间的栅绝缘氮化硅层。此外，该 OLED 还可包括布置在至少一个电路 TFT 的半导体层与栅绝缘氮化硅层之间或在栅绝缘氮化硅层与至少一个电路 TFT 的栅电极之间，以及在至少一个像素 TFT 的半导体层与至少一个像素 TFT 的栅电极之间的栅绝缘氧化硅层。

氮化硅层可以为布置在至少一个电路 TFT 的栅电极与至少一个电路 TFT 的源/漏电极之间的层间绝缘氮化硅层。此外，该 OLED 还可以包括布置在至少一个电路 TFT 的栅电极与层间绝缘氮化硅层之间或在层间绝缘氮化硅层与至少一个电路 TFT 的源和漏电极之间，以及在至少一个像素 TFT 的栅电极与至少一个像素 TFT 的源和漏电极之间的层间绝缘氧化硅层。

优选地，半导体层是多晶硅层。另外，像素电极优选为透明电极。

该 OLED 还可以包括布置在像素电极上的发光层（emission layer）和布置在发光层上的相对电极（opposite electrode）。

在本发明的另一个示范性实施例中，制造有机发光显示器的方法包括提供具有电路区域和像素区域的基板。至少一个电路 TFT 和至少一个像素 TFT

分别形成在基板的电路区域和像素区域上。每个 TFT 具有半导体层、栅电极、源电极和漏电极。形成像素电极以电连接到至少一个像素 TFT 的源和漏电极中之一。在形成源和漏电极之前，在基板上形成在整个像素区域中开口的至少一层氮化硅层。

### 附图说明

将根据所属附图参照其特定示范性实施例说明本发明的上述和其它特征，附图中：

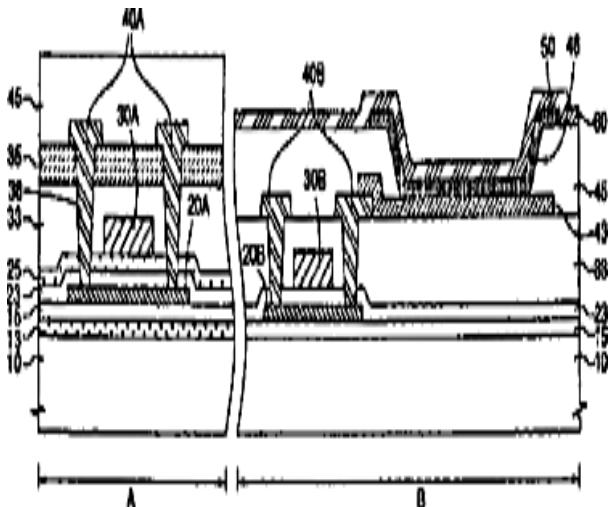

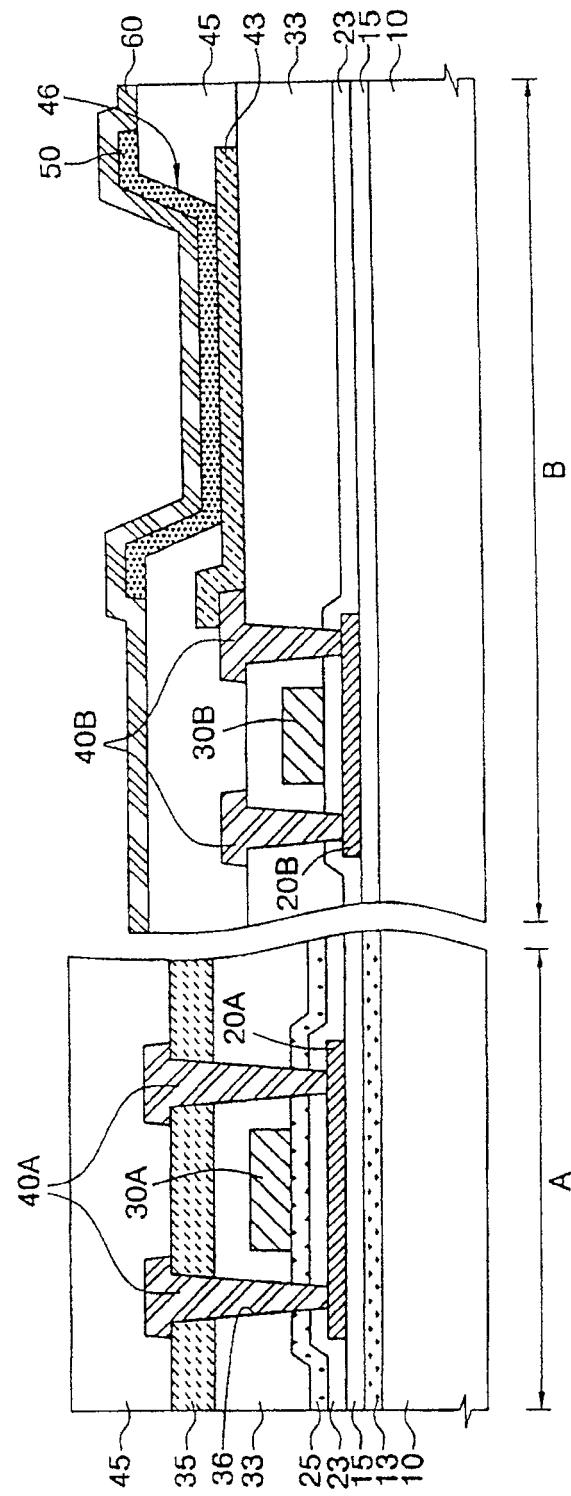

图 1A 至 1D 是根据本发明的实施例的 OLED 和其制造方法的截面图；

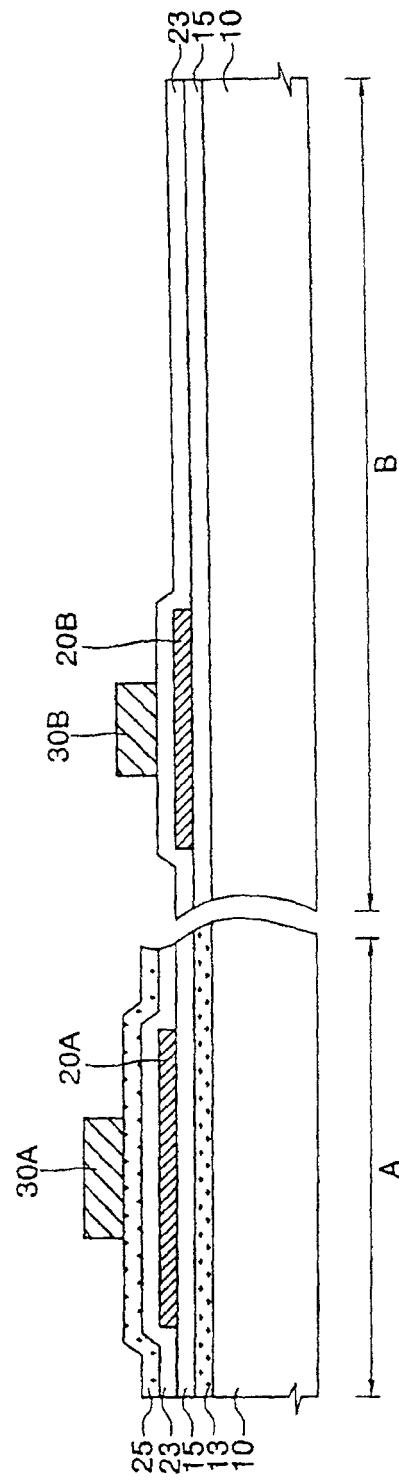

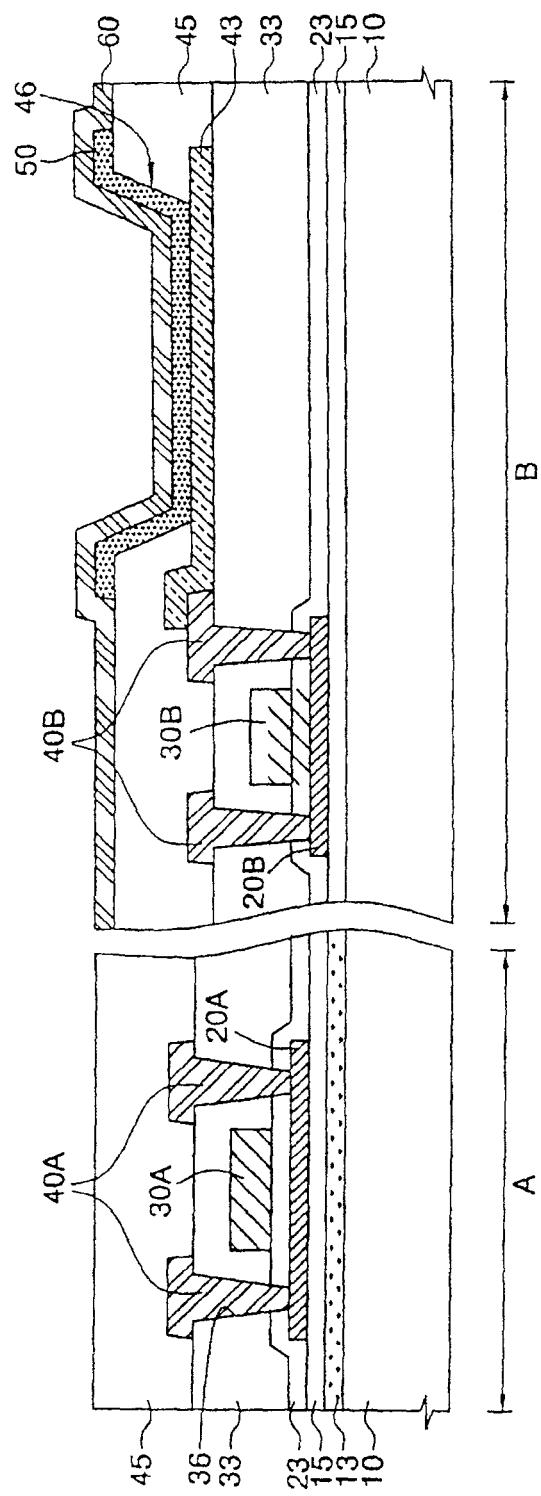

图 2 是根据本发明的另一实施例的 OLED 的截面图；

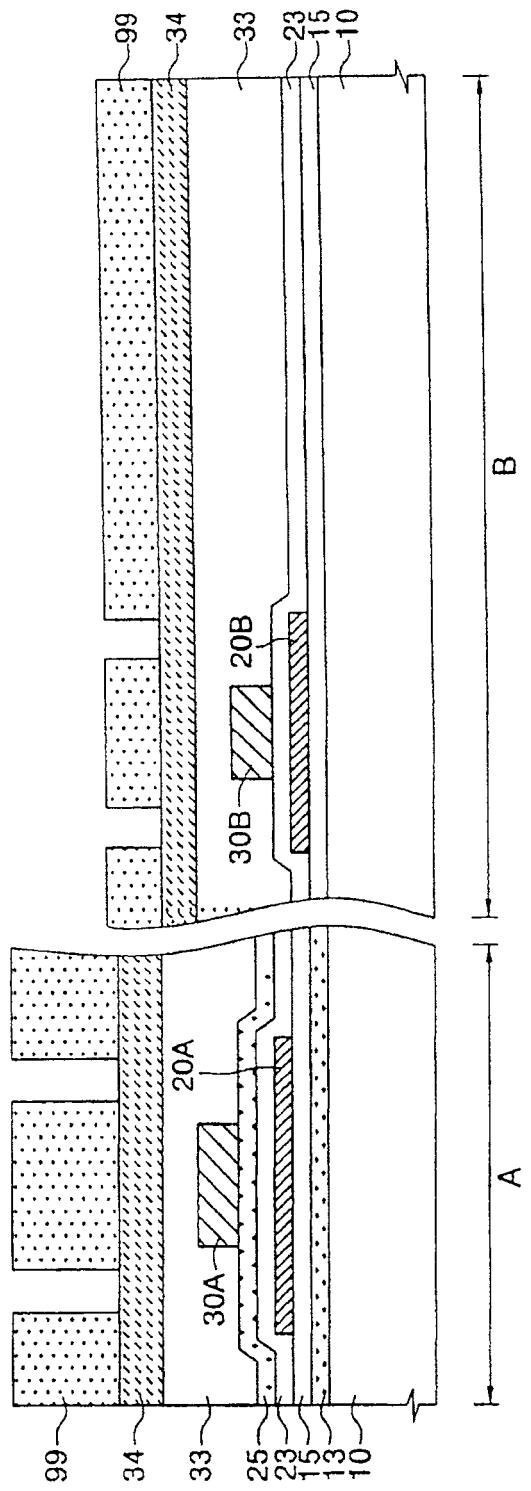

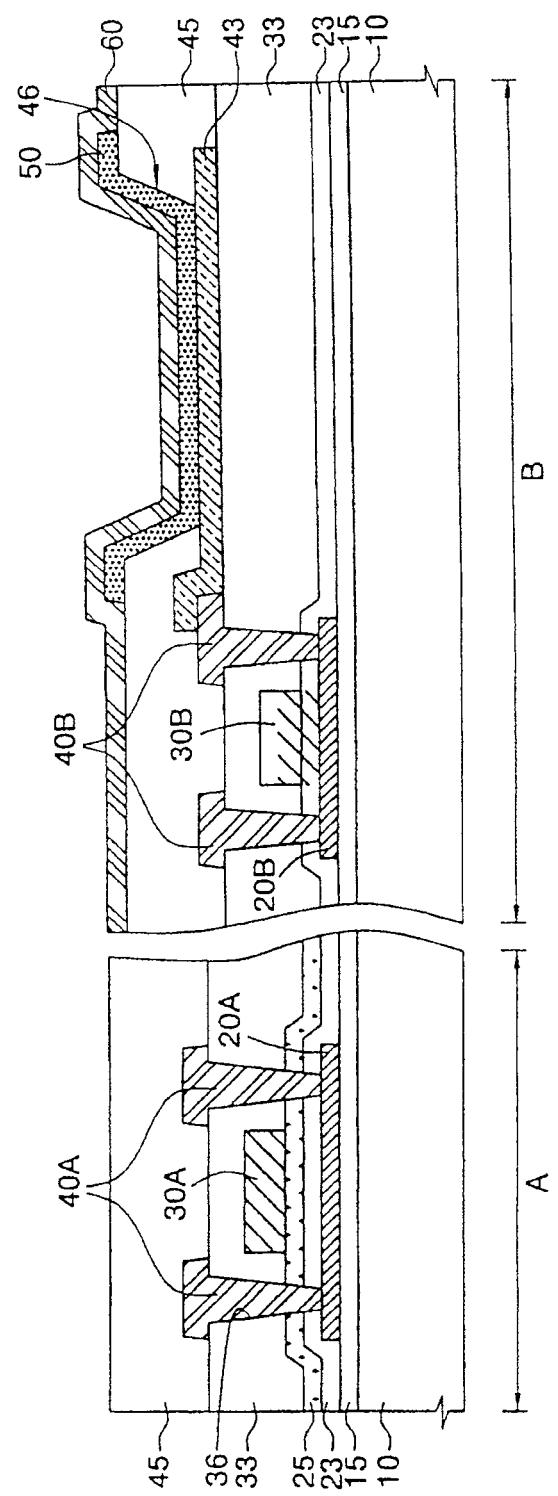

图 3 是根据本发明的另一实施例的 OLED 的截面图；

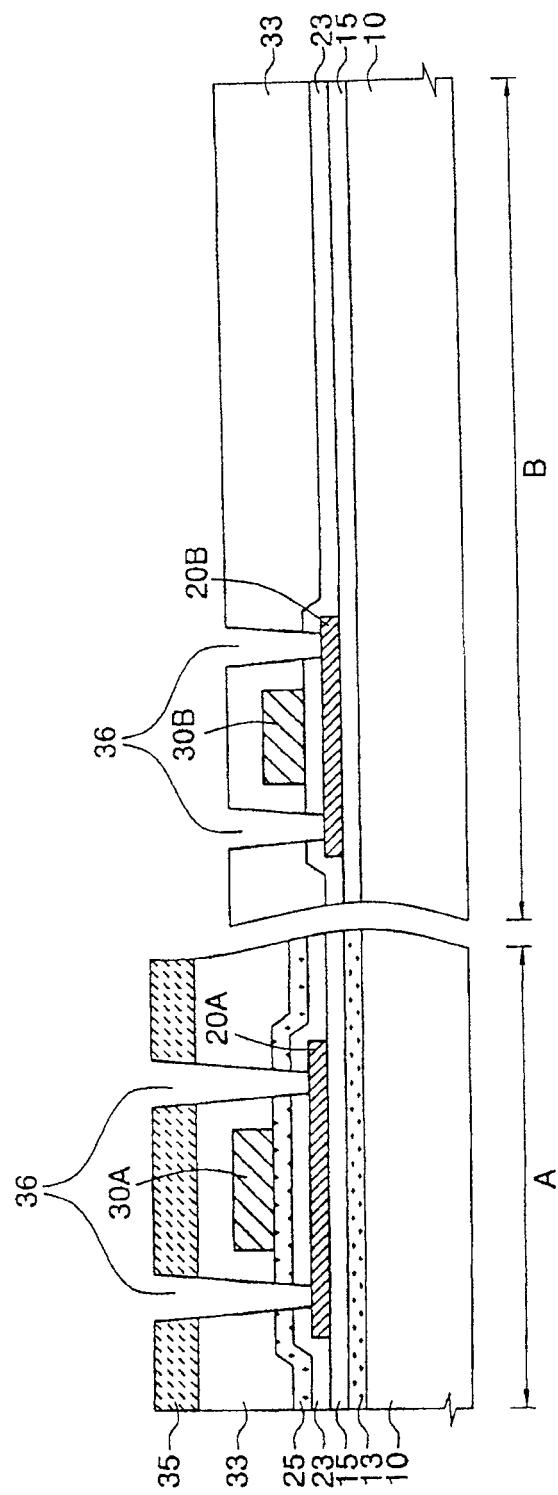

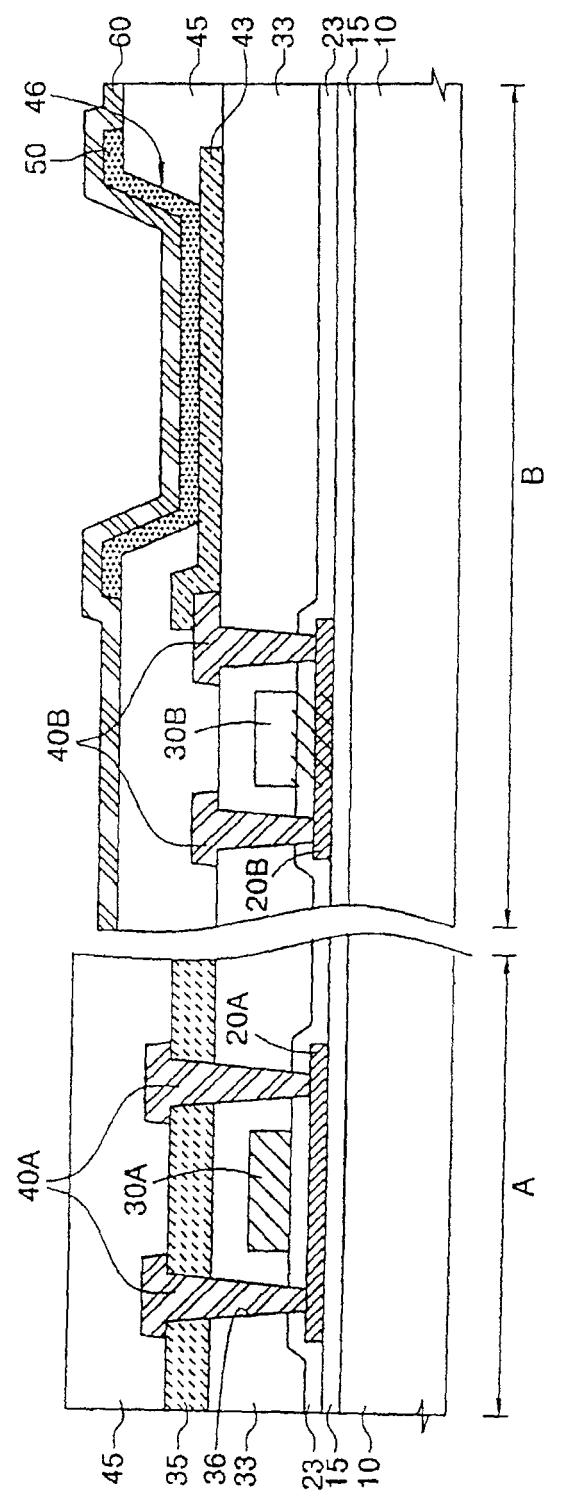

图 4 是根据本发明的另一实施例的 OLED 的截面图；

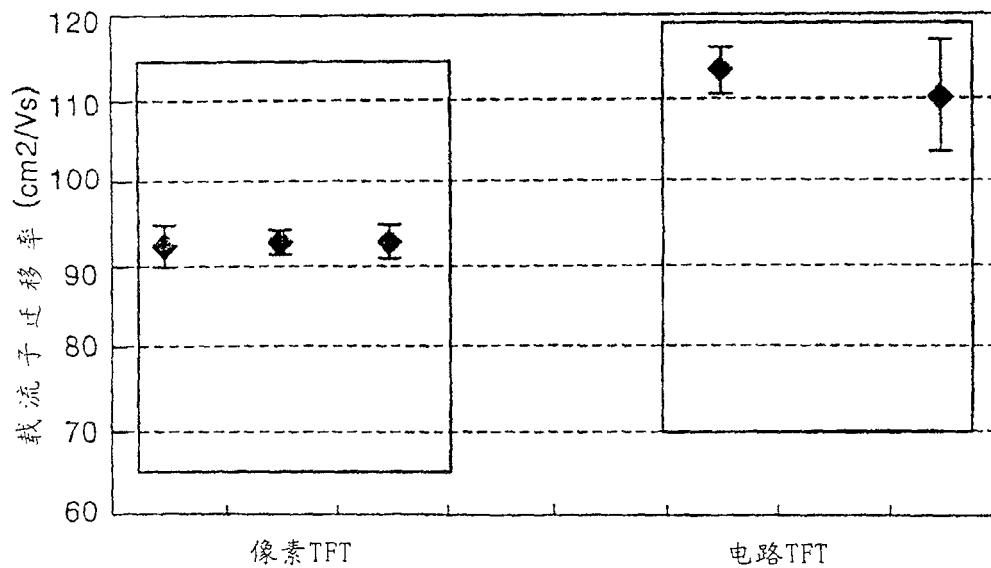

图 5A 是根据本发明的实施例制造的像素 TFT 和电路 TFT 的载流子迁移率的图表；

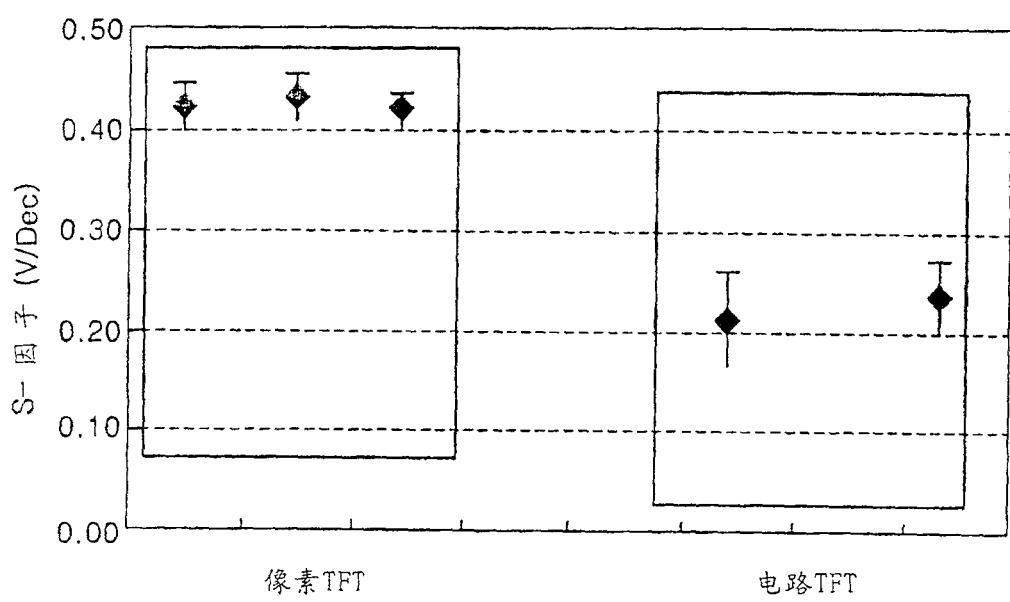

图 5B 是根据本发明实施例制造的像素 TFT 和电路 TFT 的 S 因子值的图表；

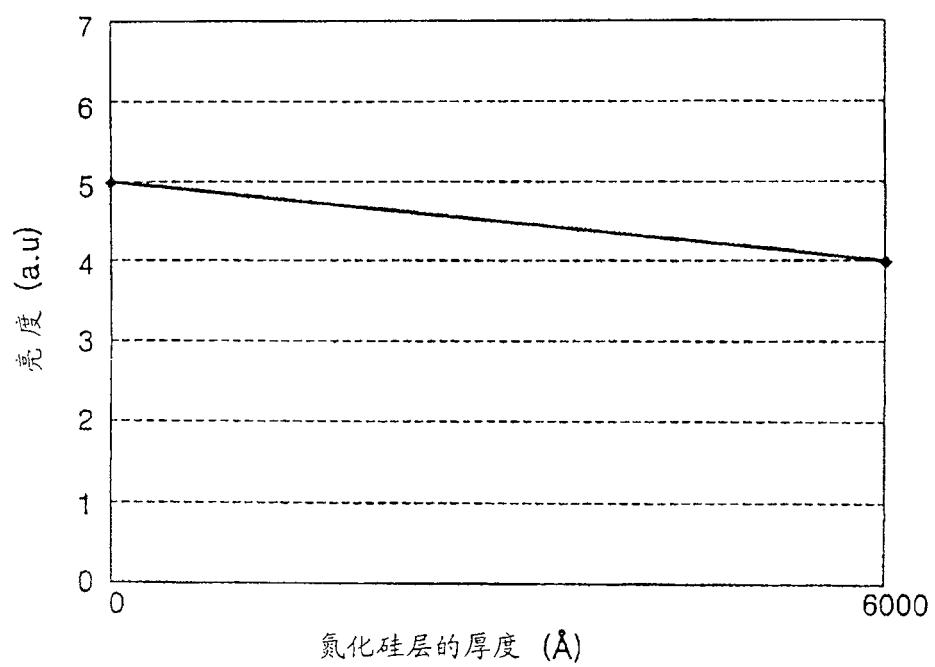

图 6 是亮度随氮化硅层的厚度而变化的图表。

### 具体实施方式

现在详细地参照本发明的实施例，附图中给出了本发明的实例，其中全文中相同的参考数字代表相同的元件。一层布置在另一层或基板上的表达意味着该层直接形成在另一层或基板上或者其间可以插入第三层。

图 1D 是根据本发明的实施例的 OLED 的截面图。

参照图 1D，根据本发明的实施例的 OLED 包括具有电路区域 A 和像素区域 B 的基板 10。像素区域 B 是像素在其中布置成矩阵结构的区域，电路区域 A 是布置用于电控制像素的电路的区域，图 1D 仅显示了各区域的一部分。

至少一个电路 TFT（下文称作电路 TFT）布置在基板的电路区域 A 上。给电路 TFT 提供半导体层 20A、部分地重叠在半导体层 20A 上的栅电极 30A、源电极 40A 和漏电极 40A。源和漏电极 40A 电连接到半导体层 20A 的两端。至少一个像素 TFT（下文中，称作像素 TFT）布置在基板的像素区域 B 上。

给像素 TFT 提供半导体层 20B、部分地重叠在半导体层 20B 上的栅电极 30B、源电极 40B 和漏电极 40B。源和漏电极 40B 电连接到半导体层 20B 的两端。优选地，半导体层 20A 和 20B 是具有比非晶硅层更大载流子迁移率的多晶硅层。

布置像素电极 43 以电接触像素 TFT 的源和漏电极 40B 中之一。优选地，像素电极 43 是能够将光透射到基板 10 的透明电极。透明像素电极 43 可以为阳极或为阴极。用作阳极的透明像素电极 43 优选由 ITO (氧化铟锡) 或 IZO (氧化铟锌) 形成，用作阴极的透明像素电极 43 优选由 Mg、Ca、Al、Ag、Ba 或其合金形成，其优选具有能够透光的薄厚度。

像素限定层 45 布置在像素电极 43 和源和漏电极 40A 和 40B 上。像素限定层 45 包括部分地暴露像素电极 43 的表面的开口 46，暴露在开口 46 中的像素电极 43 限定了像素的发光区域。发光层 50 布置在暴露的像素电极 43 上，相对电极 60 布置在发光层 50 上。可以通过像素对发光层 50 构图。另外，电荷注入层 (未显示) 和/或电荷输运层 (未显示) 可以布置在发光层 50 与像素电极 43 之间或在发光层 50 与相对电极 60 之间。相对电极 60 可以为透明电极或反射电极，当像素电极 43 是阳极时，相对电极是阴极，当像素电极 43 是阴极时，相对电极是阳极。

开口于整个像素区域 B 中的至少一层氮化硅层 13、25 和 35 布置在源/漏电极 40A 与基板 10 之间。换句话说，氮化硅层 13、25 和 35 没有布置在像素区域 B 中，而是布置在电路区域 A 中。氮化硅层可以包括氮化硅(SiNx)或氮氧化硅(SiON)。氮化硅层包含大量的氢，氢能够修复缺陷；例如存在于邻近氮化硅层的多晶半导体层的晶界中的悬挂键。因此，能够调整 TFT 的电学特性，例如载流子的迁移率和 S-因子。更具体地说，其中布置有氮化硅层 13、25 和 35 的电路区域 A 的电路 TFT 具有较高的载流子迁移率和较小的 S-因子值。因此，包括电路 TFT 的电路具有快的数据传输速度，并且该电路 TFT 能够实现优良的开关操作。在另一方面，其中没有布置氮化硅层 13、25 和 35 的像素区域 B 的像素 TFT 相对于电路 TFT 具有较低的载流子迁移率和较大的 S-因子值。具有较大 S-因子值的像素 TFT 能够容易地显示灰度级图像，由于像素 TFT 的特性低的载流子迁移率无关紧要。因此，通过形成至少一层开口于整个像素区域 B 的氮化硅层图案 13、25 和 35 可以实现最优化的像素 TFT 和电路 TFT 的电学特性。

氮化硅层具有较低的光透射率。因此，不将氮化硅层布置在像素电极 B 中以防止从发光层 50 射向基板 10 的光损失，由此能够提高 OLED 的亮度。

氮化硅层可以为布置在基板 10 与电路 TFT 的半导体层 20A 之间的缓冲氮化硅层。另外，缓冲氧化硅层 15 可以布置在基板 10 与缓冲氮化硅层 13 之间。优选地，如图所示，缓冲氧化硅层 15 布置在缓冲氮化硅层 13 与电路 TFT 的半导体层 20A 之间。这样做的原因是氧化硅层相比氮化硅层具有较好的与半导体层粘附的特性。另外，缓冲氧化硅层 15 也布置在基板 10 与像素 TFT 的半导体层 20B 之间。缓冲氮化硅层 13 和缓冲氧化硅层 15 起防止半导体层 20A 和 20B 被从基板向外扩散的杂质损害的作用。

氮化硅层可以是布置在电路 TFT 的半导体层 20A 与电路 TFT 的栅电极 30A 之间的栅绝缘氮化硅层 25。此外，栅绝缘氧化硅层 23 可以布置在电路 TFT 的半导体层 20A 与栅绝缘氮化硅层 25 之间或在栅绝缘氮化硅层 25 与电路 TFT 的栅电极 30A 之间。另外，栅绝缘氧化硅层 23 也布置在像素 TFT 的半导体层 20B 与像素 TFT 的栅电极 30B 之间。

此外，氮化硅层可以为布置在电路 TFT 的栅电极 30A 与电路 TFT 的源/漏电极 40A 一层之间的层间绝缘氮化硅层 35。此外，层间绝缘氧化硅层 33 可以布置在电路 TFT 的栅电极 30A 与层间绝缘氮化硅层 35 之间或在层间绝缘氮化硅层 35 与电路 TFT 的源/漏电极 40A 之间。层间绝缘氧化硅层 33 也布置在像素 TFT 的栅电极 30B 与像素 TFT 的源和漏电极 40B 之间。优选地，层间绝缘氧化硅层 33 布置在电路 TFT 的栅电极 30A 与层间绝缘氮化硅层 35 之间。

图 1A-1D 是根据本发明的实施例制造 OLED 的方法的截面图。

参照图 1A，提供具有电路区域 A 和像素区域 B 的基板 10。在基板 10 上形成氮化硅层并对其构图形成开口于整个像素区域 B 的缓冲氮化硅层 13。在形成氮化硅层之前，可以在基板的整个表面上形成缓冲氧化硅层 15。优选地，在形成缓冲氮化硅层 13 之后，在基板的整个表面上形成缓冲氧化硅层 15。在电路区域 A 和像素区域 B 上布置缓冲氧化硅层 15。

半导体层 20A 和 20B 分别形成在电路区域 A 和像素区域 B 的缓冲氧化硅层 15 上。优选地，半导体层 20A 和 20B 为多晶硅层。通过在缓冲氧化硅层 15 上形成非晶硅层，并结晶且构图所形成的非晶硅层来形成多晶硅半导体层 20A 和 20B。结晶方法包括固相结晶(SPC)法、激准分子激光退火(ELA)

法、顺序横向固化 (SLS) 法、金属诱导结晶 (MIC) 法、和金属诱导横向结晶 (MILC) 法等。

在半导体层 20A 和 20B 上形成另一氮化硅层并对其构图，由此形成开口于整个像素区域 B 的栅绝缘氮化硅层 25。在形成栅绝缘氮化硅层 25 之前或之后，可以在基板的整个表面上形成栅绝缘氧化硅层 23。在电路区域 A 和像素区域 B 上布置栅绝缘氧化硅层 23。

分别在电路区域 A 和像素区域 B 的栅绝缘氧化物层 23 上形成部分地重叠半导体层 20A 和 20B 的栅电极 30A 和 30B。

参照图 1B，在栅电极 30A 和 30B 上顺序地形成层间绝缘氧化硅层 33 和另一氮化硅层 34，并使用半色调网点掩模(halftone mask)在氮化硅层 34 上形成光致抗蚀剂图案 99。形成光致抗蚀剂图案 99 使得电路区域 A 的高度高于像素区域 B 的高度，并且开口于将要在其中形成源极和漏极接触孔的区域。

参照图 1C，通过使用光致抗蚀剂图案 99 作为掩模蚀刻图 1B 的氮化硅层 34、层间绝缘氧化硅层 33、栅绝缘氮化硅层 25 和栅绝缘氧化硅层 23 形成暴露半导体层 20A 和 20B 的两端的源极和漏极接触孔 36。同时，蚀刻具有比电路区域 A 低的图案高度的像素区域 B 的光致抗蚀剂，也蚀刻其下的图 1B 的氮化硅层 34，由此形成开口于整个像素区域 B 的层间绝缘氮化硅层 35。

在另一方面，可以在栅电极 30A 和 30B 上淀积图 1B 的氮化硅层 34，并对其构图以形成开口于整个像素区域 B 的层间绝缘氮化硅层 35，并接着在层间绝缘氮化硅层 35 上形成层间绝缘氧化硅层 33。可以形成缓冲氮化硅层 13、栅绝缘氮化硅层 25 和层间绝缘氮化硅层 35 中的至少一层氮化硅层，不形成其余层。例如，如图 2 所示仅形成缓冲氮化硅层 13，如图 3 所示仅形成栅绝缘氮化硅层 25，以及如图 4 所示仅形成层间绝缘氮化硅层 35。

参照图 1D，在具有源极和漏极接触孔 36 的基板的整个表面上淀积源和漏电极材料并对其构图，以在电路区域 A 和像素区域 B 上分别形成源和漏电极 40A 和 40B。形成在电路区域 A 中的半导体层 20A、栅电极 30A 和一对源和漏电极 40A 组成了电路 TFT，形成在像素区域 B 中的半导体层 20B、栅电极 30B 和一对源和漏电极 40B 组成了像素 TFT。

其后，形成接触像素 TFT 的源和漏电极 40B 中之一的像素电极 43。通

过使用荫罩真空淀积像素电极材料形成像素电极 43。像素电极 43 优选为透明电极。透明像素电极 43 可由 ITO 或 IZO 形成。在这种情况下，像素电极 43 为阳极。在另一方面，当形成透明像素电极 43 时，像素电极材料可以是 Mg、Ca、Al、Ag、Ba 或其合金，将其形成薄至能够透光。在这种情况下，像素电极为阴极。

在像素电极 43 和源和漏电极 40A 和 40B 上形成像素限定层 45。在像素限定层 45 中形成部分地暴露像素电极 43 的表面的开口 46。暴露在开口 46 中的像素电极 43 限定了像素的发光区域。在暴露的像素电极 43 上形成发光层 50，并在发光层 50 上形成相对电极 60。可以通过利用像素构图形成发光层 50。另外，可以在发光层 50 与像素电极 43 之间或在发光层 50 与相对电极 60 之间形成电荷注入层（未显示）和/或电荷输运层（未显示）。相对电极 60 可以由透明电极或反射电极形成。当像素电极 43 是阳极时，相对电极是阴极，当像素电极 43 是阴极时，相对电极是阳极。

图 5A 是根据本发明实施例制造的像素 TFT 和电路 TFT 的载流子迁移率的图表，而图 5B 是根据本发明实施例制造的像素 TFT 和电路 TFT 的 S-因子值的图表。

参照图 5A 和 5B，电路 TFT 相对于像素 TFT 具有更高的载流子迁移率和更小的 S-因子值。因此，电路 TFT 实现了优良的开关操作，并且包括电路 TFT 的电路具有快的数据传输速度。在另一方面，像素 TFT 容易显示灰度级图像。因此，能够最优化电路 TFT 和像素 TFT 的电学特性。

图 6 是亮度随氮化硅层的厚度变化的图表。

参照图 6，当增加氮化硅层的厚度时，亮度降低。因此，能够通过在整个像素区域上方对氮化硅层开口来防止 OLED 的亮度降低。

如上述所见，通过形成开口于整个像素区域的氮化硅层，获得了像素 TFT 和电路 TFT 的最优电学特性，并且没有降低 OLED 的亮度。

尽管已根据其示范性实施例描述了本发明，但本领域的技术人员应当理解在不脱离所附的权利要求限定的本发明的精神或范围情况下可以进行各种修改和变化。

图 1A

图 1B

图 1C

图 1D

图 2

图 3

图 4

图 5A

图 5B

图 6

|                |                                                                                                                            |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机发光显示器及其制造方法                                                                                                              |         |            |

| 公开(公告)号        | <a href="#">CN100492705C</a>                                                                                               | 公开(公告)日 | 2009-05-27 |

| 申请号            | CN200510054183.6                                                                                                           | 申请日     | 2005-02-08 |

| [标]申请(专利权)人(译) | 三星斯笛爱股份有限公司                                                                                                                |         |            |

| 申请(专利权)人(译)    | 三星SDI株式会社                                                                                                                  |         |            |

| 当前申请(专利权)人(译)  | 三星移动显示器株式会社                                                                                                                |         |            |

| [标]发明人         | 李宪贞<br>朴商一                                                                                                                 |         |            |

| 发明人            | 李宪贞<br>朴商一                                                                                                                 |         |            |

| IPC分类号         | H01L51/50 H01L51/56 H01L27/32 H01L51/52 H05B33/10 G09F9/30 H01L21/314 H01L21/318 H01L21/77 H01L29/786 H05B33/00            |         |            |

| CPC分类号         | H01L27/3244 H01L21/3185 H01L29/78603 H01L27/1214 H01L51/5253 H01L21/3144 G09G2320/0233 G09G2300/0426 H01L51/50 H01L27/1248 |         |            |

| 代理人(译)         | 侯宇                                                                                                                         |         |            |

| 审查员(译)         | 刘军                                                                                                                         |         |            |

| 优先权            | 1020040008494 2004-02-09 KR                                                                                                |         |            |

| 其他公开文献         | CN1655655A                                                                                                                 |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">SIPO</a>                                                                             |         |            |

## 摘要(译)

一种OLED包括具有电路区域和像素区域的基板。至少一个电路薄膜晶体管(TFT)和至少一个像素TFT分别排列在电路区域和像素区域上。每个TFT具有半导体层、栅电极、源电极和漏电极。像素电极电连接到像素TFT的源和漏电极中的一个。至少一个氮化硅层布置在源和漏电极与基板之间，且在整个像素区域中开口。