## 〔12〕发明 专利 说明 书

专利号 ZL 03165011.2

[45] 授权公告日 2007 年 12 月 12 日

[11] 授权公告号 CN 100354908C

[22] 申请日 2003.9.25 [21] 申请号 03165011.2

### [30] 优先权

[32] 2002. 9. 25 [33] KR [31] 58210/02

[73] 专利权人 三星电子株式会社

地址 韩国京畿道

[72] 发明人 崔峻厚 蔡钟哲 崔凡洛

## [56] 参考文献

CN1361510A 2002.7.31

EP1102234A2 2001.5.23

JP2002 - 14653A 2002. 1. 18

US6091203A 2000.7.18

CN1278635A 2001.1.3

审查员 王一娟

[74] 专利代理机构 北京市柳沈律师事务所

代理人 陶凤波 侯 宇

[54] 发明又称

## 有机发光显示装置及其制造方法

[57] 摘要

一种有机发光显示设备，包括：在提供驱动信号到有机发光二极管的顺序进程中分别传送前一级和当前栅极信号的栅极线；传送在图像显示装置上显示图像的数据信号的数据线；响应当前栅极信号传送来自数据线的数据信号的导电通路的第一开关晶体管；响应前一级栅极信号传送外部提供的基准信号的导电通路的第二开关晶体管；响应第二开关晶体管的状态传送从第一开关晶体管提供的数据信号的导电通路的第三开关晶体管；以及响应来自第二开关晶体管的基准信号和第三开关晶体管的数据信号之一接收偏压和产生到有机发光二极管的驱动信号的导电通路的第四开关晶体管。第三和第四开关晶体管具有彼此基本上相同的开关性能。

1. 一种用于提供驱动信号到图像显示装置中的有机发光二极管的设备，包括：

在用于提供驱动信号到有机发光二极管的顺序进程中分别传送前一级和当前控制信号的第一和第二控制线；

用于传送用于在图像显示装置上显示图像的数据信号的数据线；

第一开关器件，包括用于传送来自数据线的数据信号的导电通路，第一开关器件的导电通路由来自第二控制线的当前控制信号控制；

第二开关器件，包括用于传送外部提供的基准信号的导电通路，第二开关器件的导电通路由来自第一控制线的前一级控制信号控制；

第三开关器件，包括用于传送从第一开关器件提供的数据信号的导电通路，第三开关器件的导电通路由第二开关器件的状态控制；

第四开关器件，包括用于传送偏压的导电通路，第四开关器件的导电通路由来自第二开关器件的基准信号和来自第三开关器件的数据信号之一控制；以及

第五开关器件，包括用于接收来自第四开关器件的偏压并产生到有机发光二极管的驱动信号的导电通路，该导电通路由来自第一控制线的前一级控制信号控制。

2. 如权利要求1所述的设备，其中第三和第四开关器件具有彼此基本上相同的开关性能。

3. 如权利要求2所述的设备，还包括用于用偏压充电和用于提供电压信号以控制第三开关器件的导电通路的电容器。

4. 如权利要求3所述的设备，其中第一、第二、第三和第四开关器件分别是第一、第二、第三和第四薄膜晶体管，每一个具有处在源极和漏极之间的导电通路和用于接收控制信号以控制导电通路的栅极；第一和第二控制线分别是第一和第二栅极线；前一级和当前控制信号分别是前一级和当前的栅极信号。

5. 如权利要求4所述的设备，其中第一、第二、第三以及第四薄膜晶体管是多晶硅薄膜晶体管。

6. 如权利要求4所述的设备，其中第一薄膜晶体管具有栅极、源极和漏

极，当前栅极信号从第二栅极线施加到栅极，源极和漏极形成用于传送数据信号的导电通路；第二薄膜晶体管具有栅极、源极和漏极，前一级栅极信号从第一栅极线施加到栅极，源极和漏极形成用于传送基准信号的导电通路；第三薄膜晶体管具有栅极、源极和漏极，来自电容器电压信号施加到栅极，源极和漏极形成用于传送数据信号的导电通路；以及第四薄膜晶体管具有栅极、源极和漏极，来自第二薄膜晶体管的基准信号和来自第三薄膜晶体管的数据信号施加到栅极，源极和漏极在偏压和第五开关器件之间形成导电通路。

7. 如权利要求6所述的设备，其中第二薄膜晶体管的导电通路和第三薄膜晶体管的导电通路连接到第四薄膜晶体管的栅极且相对于第四薄膜晶体管的栅极彼此平行。

8. 如权利要求6所述的设备，其中第三薄膜晶体管的栅极与第四薄膜晶体管的栅极连接。

9. 如权利要求6所述的设备，其中第三和第四薄膜晶体管具有基本上相等的阈值电压。

10. 如权利要求9所述的设备，其中第三和第四薄膜晶体管阈值电压具有负值。

11. 如权利要求6所述的设备，其中第一和第二薄膜晶体管是N型薄膜晶体管，第三和第四薄膜晶体管是P型薄膜晶体管。

12. 如权利要求11所述的设备，其中基准信号的电压等于或大于第一薄膜晶体管的栅极截止电压以及等于或小于第三薄膜晶体管的阈值电压和数据信号的最小电压值之和。

13. 如权利要求6所述的设备，其中第四薄膜晶体管的有效栅-源电压取决于偏压和数据信号，与第四薄膜晶体管的阈值电压无关。

14. 如权利要求6所述的设备，其中从基本上平行于数据线布置的电源线提供偏压。

15. 如权利要求6所述的设备，其中第五开关器件是第五薄膜晶体管，该第五薄膜晶体管具有源极和漏极之间的导电通路及用于接收控制该导电通路的控制信号的栅极，且该导电通路在第四薄膜晶体管和有机发光二极管之间，导电通路由来自第一栅极线的前一级栅极信号控制。

16. 如权利要求15所述的设备，其中第五薄膜晶体管是P型薄膜晶体管，

具有形成导电通路的源极和漏极以及接收前一级栅极信号的栅极。

17. 如权利要求6所述的设备,其中第二薄膜晶体管的源极与第二栅极线连接,以便第二薄膜晶体管的导电通路传送当前栅极信号到第四薄膜晶体管作为基准信号。

18. 如权利要求6所述的设备,其中从基本上平行于第一和第二栅极线布置的电源线提供偏压。

19. 如权利要求18所述的设备,其中该第五开关器件是第四薄膜晶体管和有机发光二极管之间具有导电通路的第五薄膜晶体管,导电通路由来自第二栅极线的当前栅极信号控制。

20. 如权利要求19所述的设备,其中第五薄膜晶体管是P型薄膜晶体管,具有形成导电通路的源极和漏极以及接收当前的栅极信号的栅极。

21. 如权利要求18所述的设备,其中该第五开关器件包括:

第五薄膜晶体管,具有用于传送来自第四薄膜晶体管的驱动信号的导电通路,导电通路由来自第一栅极线的前一级栅极信号控制;以及

第六薄膜晶体管,具有用于传送来自第五薄膜晶体管的驱动信号到有机发光二极管的导电通路,第六薄膜晶体管的导电通路由来自第二栅极线的当前栅极信号控制。

22. 如权利要求21所述的设备,其中第五薄膜晶体管是P型薄膜晶体管,具有源极和漏极以及栅极,源极和漏极形成用于传送来自第四薄膜晶体管的驱动信号的导电通路,栅极接收前一级栅极信号,以及第六薄膜晶体管是N型薄膜晶体管,具有源极和漏极以及栅极,源极和漏极形成用于传送来自第五薄膜晶体管的驱动信号的导电通路,栅极接收当前的栅极信号。

23. 如权利要求6所述的设备,还包括在第四薄膜晶体管和有机发光二极管之间具有导电通路的第五薄膜晶体管,该导电通路由来自第一栅极线的前一级栅极信号控制,

其中第一和第二、第三以及第四薄膜晶体管是P型薄膜晶体管,第五薄膜晶体管是N型薄膜晶体管。

24. 如权利要求23所述的设备,其中基准电压大于第一薄膜晶体管的栅极截止电压。

25. 如权利要求24所述的设备,其中基准电压小于第三薄膜晶体管的阈值电压和数据信号的最小电压值之和。

26. 一种有机发光显示装置，包括：

多个栅极线，顺序地提供一源栅极线于其上；

多个数据线，施加数据信号于其上，以在有机发光显示装置上显示图像；

以及

多个像素驱动单元，每个像素驱动单元与多个数据线中的至少一个及一对栅极线相关地提供驱动信号到相应的OLED二极管；其中每个像素驱动单元包括：

具有导电通路的第一驱动晶体管，导电通路一端接收偏压另一端提供偏压到第二驱动晶体管，其中第二驱动晶体管具有一导电通路，该第二驱动晶体管的导电通路的一端接收偏压且另一端提供偏压到二极管；

具有用于传送基准信号的导电通路的第一开关晶体管，第一开关晶体管的导电通路由前一级栅极信号控制；以及

具有用于传送数据信号的导电通路的第二开关晶体管，第二开关晶体管的导电通路由第一开关晶体管的状态控制，

其中第一驱动晶体管的导电通路由来自第一开关晶体管的基准信号和来自第二开关晶体管的数据信号之一控制。

27. 如权利要求26所述的有机发光显示装置，其中多个栅极线包括用于提供栅极信号到第一个像素驱动单元的第一开关晶体管的虚设栅极线。

28. 如权利要求27所述的有机发光显示装置，其中虚设栅极线与最后一个栅极线同步。

29. 如权利要求27所述的有机发光显示装置，其中同样的栅极信号同时施加到虚设栅极线和最后一个栅极线上。

30. 如权利要求26所述的有机发光显示装置，其中每个像素驱动单元还包括第三开关晶体管，第三开关晶体管具有用于传送来自相应的数据线的数据信号到第二开关晶体管的导电通路，第三开关晶体管的导电通路由当前的栅极信号控制。

31. 如权利要求26所述的有机发光显示装置，其中第一驱动晶体管和第二开关晶体管具有基本上相等的阈值电压。

32. 如权利要求26所述的有机发光显示装置，还包括多个电源线，每个与相应的像素驱动单元的一个相关联，用于提供偏压到相应的像素驱动单元，其中电源线平行于数据线。

---

33. 如权利要求26所述的有机发光显示装置，还包括多个电源线，每个与相应的像素驱动单元的一个相关联，用于提供偏压到相应的像素驱动单元，其中电源线平行于栅极线。

34. 如权利要求26所述的有机发光显示装置，其中第一驱动晶体管、第一和第二开关晶体管是薄膜晶体管，每一个具有源极和漏极以及栅极，源极和漏极形成导电通路，栅极接收栅极信号以控制导电通路。

## 有机发光显示装置及其制造方法

### 技术领域

本发明涉及有机发光显示装置，更具体地说，涉及用于驱动有机发光显示装置的像素的装置及其制造方法。

### 背景技术

阴极射线管（CRT）装置已广泛用于各种图像显示装置。近来，液晶显示（LCD）装置作为一种可供选择的显示装置，尤其是用于便携式设备、电脑监视器等的显示装置，业已显露出来。但是，CRT装置一般比较笨重和尺寸大，LCD装置也有一些不能令人满意的因素，如低亮度、低效率等。此外，LCD装置具有这样一种缺点：在LCD装置的侧面图像的视野很差。

因此，已对图像显示装置进行各种研制，作为新一代显示装置，该图像显示装置具有更轻的重量、更小的尺寸、可承受的价格、更好的效率等。这种新一代显示装置之一就是有机发光显示（OLED）装置。OLED装置利用某些有机化合物或高分子聚合物的电致发光性能响应对其施加的电流而发光。在OLED装置中，不需要为显示板提供LCD装置所需要的背光器件。因此，OLED装置与LCD装置相比较，有利之处在于重量更轻、尺寸更小、成本更低，以及制造更容易。此外，OLED装置可以有较高的亮度和更大的视角。

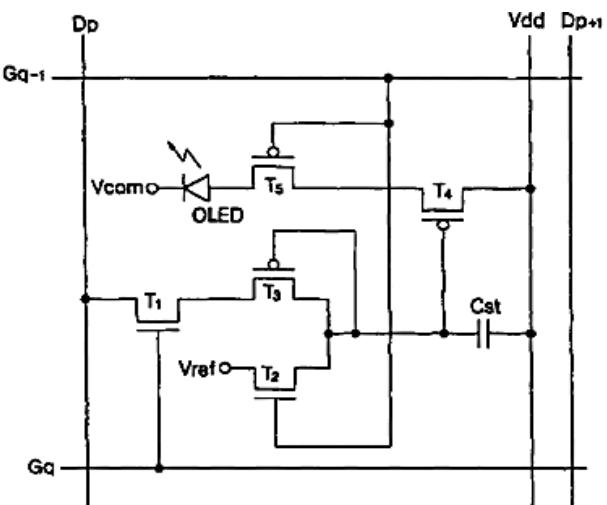

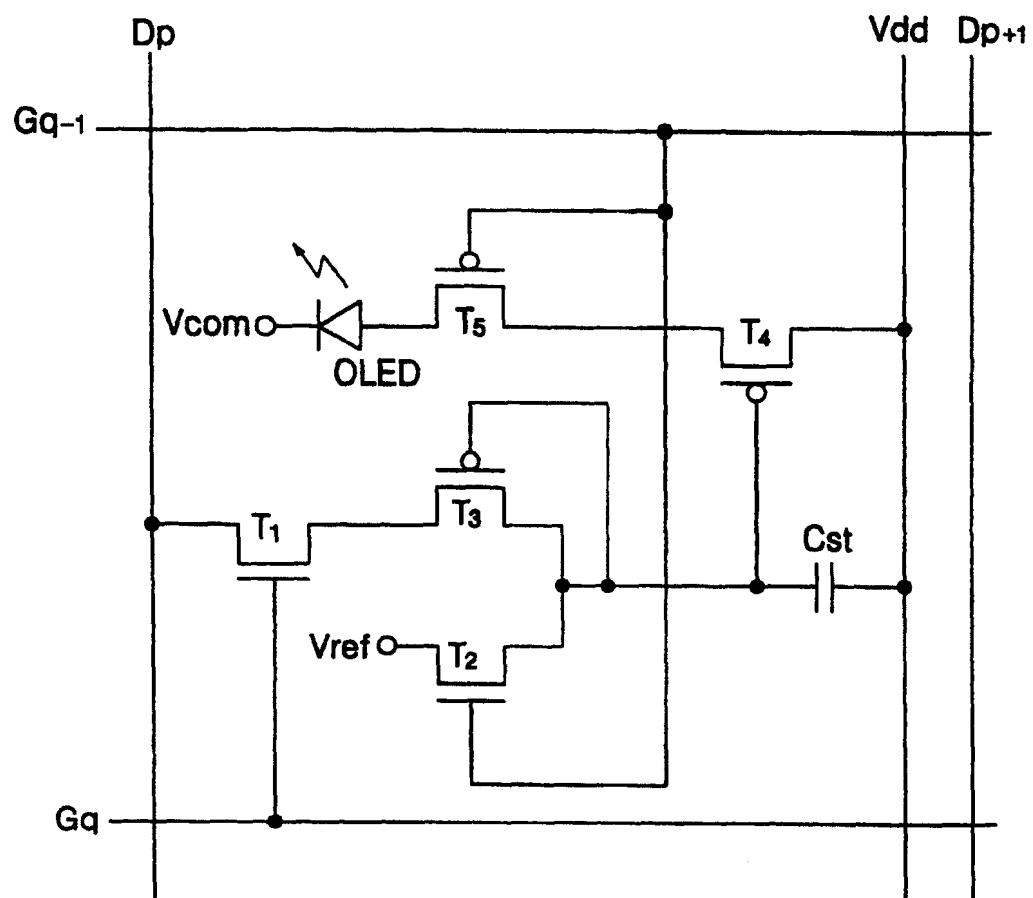

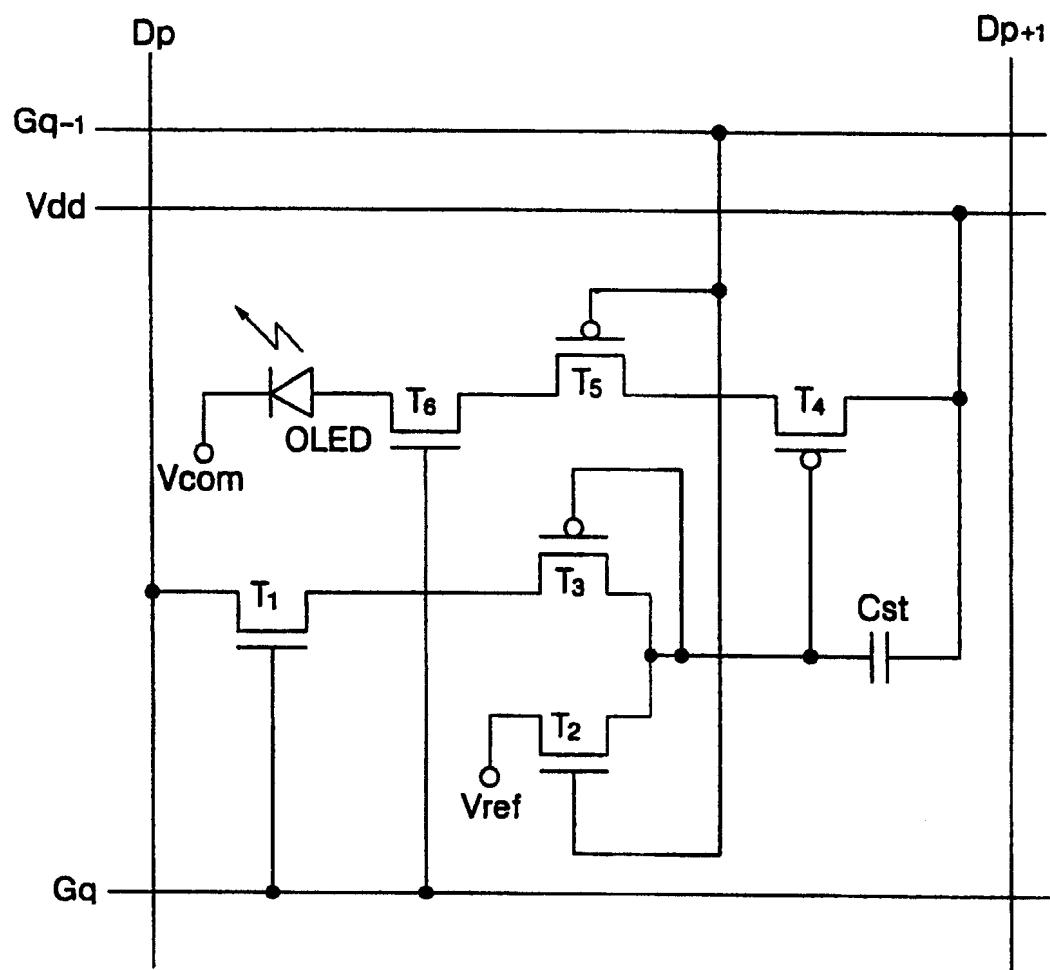

图1是说明用于OLED装置的常规驱动电路的电路图，图2是施加到图1的驱动电路的信号波形的图形视图。参考图1和2，用于OLED装置的常规驱动电路包括栅极和源极分别连接到栅极线G<sub>q</sub>和数据线D<sub>p</sub>的开关晶体管Q<sub>S</sub>、一端连接到开关晶体管Q<sub>S</sub>的漏极和另一端连接到偏压V<sub>dd</sub>的存储电容器C<sub>st</sub>、栅极连接到开关晶体管Q<sub>S</sub>的漏极和源极连接到偏压V<sub>dd</sub>的驱动晶体管Q<sub>D</sub>。

从驱动晶体管Q<sub>D</sub>的漏极提供驱动信号到有机发光二极管OLED。有机发光二极管OLED的一端连接到驱动晶体管Q<sub>D</sub>的漏极，另一端连接到公共电极电压V<sub>COM</sub>。通常，开关晶体管Q<sub>S</sub>是N型薄膜晶体管，通过施加高电平电压信

号到其栅极将其导通，驱动晶体管  $Q_D$  是 P 型薄膜晶体管，当高电平电压信号施加到其栅极时被截止。

在图 1 中的驱动电路工作中，当由通过栅极线  $Gq$  提供的栅极信号导通开关晶体管  $Q_S$  时，来自数据线  $Dp$  的数据信号通过开关晶体管  $Q_S$  的导电通路作为栅压传送到驱动晶体管  $Q_D$  的栅极。由于存储电容器  $Cst$  栅压保持一帧。此时，驱动晶体管  $Q_D$  的沟道电导由施加到栅极的栅压和施加到驱动晶体管  $Q_D$  的源极的偏压决定。同样，根据与偏压  $Vdd$  和公共电极电压  $V_{COM}$  之间的电压相关的有机发光二极管 OLED 的电压分布决定在有机发光二极管 OLED 的端子之间施加的电压强度，有机发光二极管 OLED 和驱动晶体管  $Q_D$  彼此串联连接。有机发光二极管 OLED 响应于流过其中的电流而发光，这对应于根据电压分布决定的电压强度。

因此，即使同样的数据信号施加到驱动晶体管  $Q_D$  的栅极，以便 OLED 装置的不同像素的不同驱动电路中的驱动晶体管  $Q_D$  的栅-源电压  $V_{GS}$  具有相等的值，根据不同像素中的驱动晶体管  $Q_D$  的性能，电压分布可以变化，以便有机发光二极管的端子之间的电压强度同样可以变化。结果，在 OLED 装置的不同像素中流过有机发光二极管 OLED 的电流可以不同。流过有机发光二极管 OLED 的电流的这种变化可能引起 OLED 装置的像素亮度和显示质量退化。

因此，希望改进 OLED 装置的驱动电路，以便在 OLED 装置的各个像素中的每个有机发光二极管响应同样的数据信号接收到同样的驱动电流，以便发射相同量的光。

## 发明内容

本发明提供一种用于 OLED 装置的像素驱动单元，该像素驱动单元均衡像素驱动单元中的驱动薄膜晶体管的性能，以提高 OLED 装置的显示质量。本发明还提供制造这种用于 OLED 装置的像素驱动单元的方法。

在本发明的一个方面，用于提供驱动信号到 OLED 装置中的有机发光二极管的像素驱动单元包括：第一和第二控制线，用于分别传送前一级和当前的控制信号，在顺序进程中用于提供驱动信号到有机发光二极管；数据线，用于传送用于在图像显示装置上显示图像的数据信号；第一开关器件，包括用于传送来自数据线的数据信号的导电通路，第一开关器件的导电通路由来

自第二控制线的当前控制信号控制；第二开关器件，包括用于传送外部提供的基准信号的导电通路，第二开关器件的导电通路由来自第一控制线的前一级控制信号控制；第三开关器件，包括用于传送从第一开关器件提供的数据信号的导电通路，第三开关器件的导电通路由第二开关器件的状态控制；以及第四开关器件，包括用于接收偏压和产生到有机发光二极管的驱动信号的导电通路，第四开关器件的导电通路由来自第二开关器件的基准信号和来自第三开关器件的数据信号之一控制。

在像素驱动单元中，第三和第四开关器件可以具有彼此基本上相同的开关性能。此外，可以包括用于用偏压充电和用于提供电压信号以控制第三开关器件的导电通路的电容器。第一、第二、第三和第四开关器件分别可以是第一、第二、第三以及第四薄膜晶体管，每个都具有一个在源极和漏极之间的导电通路，以及一个用于接收控制信号，以控制导电通路的栅极。第一和第二控制信号线分别可以是第一和第二栅极线，前一级和当前的控制信号分别可以是前一级和当前的栅极信号。

在本发明的另一方面，一种有机发光显示装置包括：被连续提供给激活的栅极信号的栅极线；被施加给数据信号以在有机发光显示装置上显示图像的数据线；像素驱动单元，每个像素驱动单元提供驱动信号给与一对栅极线和一对数据线相关的相应的OLE二极管，其中每个像素驱动单元具有一驱动晶体管，该驱动晶体管具有一导电通路，该导电通路一端接收偏压和另一端提供驱动信号到二极管；一第一开关晶体管，具有用于传送基准信号的一导电通路，该第一开关晶体管的导电通路由前一级栅极信号控制；以及一第二开关晶体管，具有用于传送数据信号的一导电通路，该第二开关晶体管的导电通路由第一开关晶体管的状态控制。驱动晶体管的导电通路可以由来自第一开关晶体管的基准信号和来自第二开关晶体管的数据信号之一控制。栅极线可以包括用于提供栅极信号到第一个像素驱动单元的第一开关晶体管的虚设栅极线。

在本发明的又一方面，提供一种用于制造在有机发光显示装置中提供像素驱动信号的半导体装置的方法。该方法包括：提供一绝缘基板；在该绝缘基板上形成用于提供像素驱动信号到有机发光二极管的第一非晶硅薄膜晶体管；在该绝缘基板上形成用于传送数据信号以控制该第一非晶硅薄膜晶体管的开关功能的一第二非晶硅薄膜晶体管；通过在第一和第二非晶硅薄膜晶

体管上执行激光扫描晶化第一和第二非晶硅薄膜晶体管；以及通过完成晶化步骤，使第一和第二非晶硅薄膜晶体管分别转化为第一和第二多晶硅薄膜晶体管。第一和第二多晶硅薄膜晶体管可以具有彼此基本上相同的性能。

从下面示例性实施例的详细说明将使本发明的这些及其他目的、特点以及优点更为明显，这必须结合附图进行阅读，其中在几个附图中同样的元件用相同的附图标记表示。

#### 附图说明

通过参考下面详细说明，同时结合附图考虑，本发明的上述及其他优点将变得更为明显，其中：

图1是说明用于OLED装置的常规驱动电路的电路图；

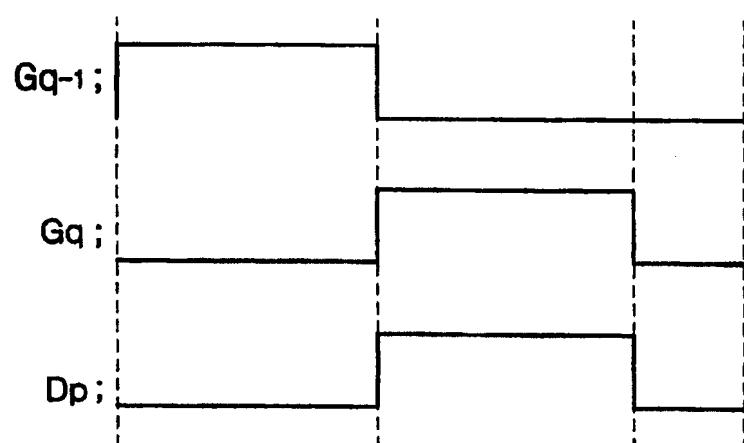

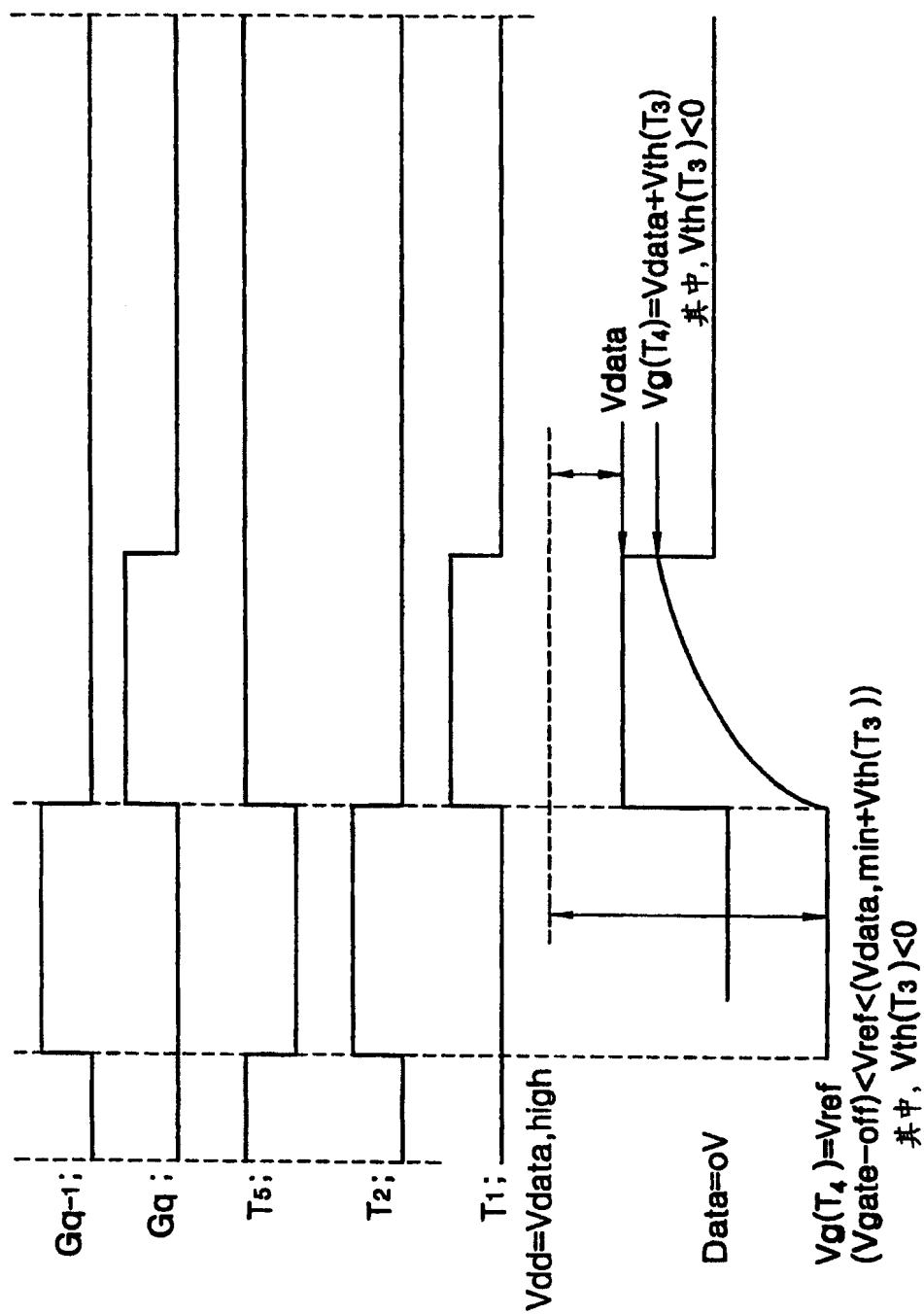

图2是施加到图1的驱动电路的信号波形的图形视图；

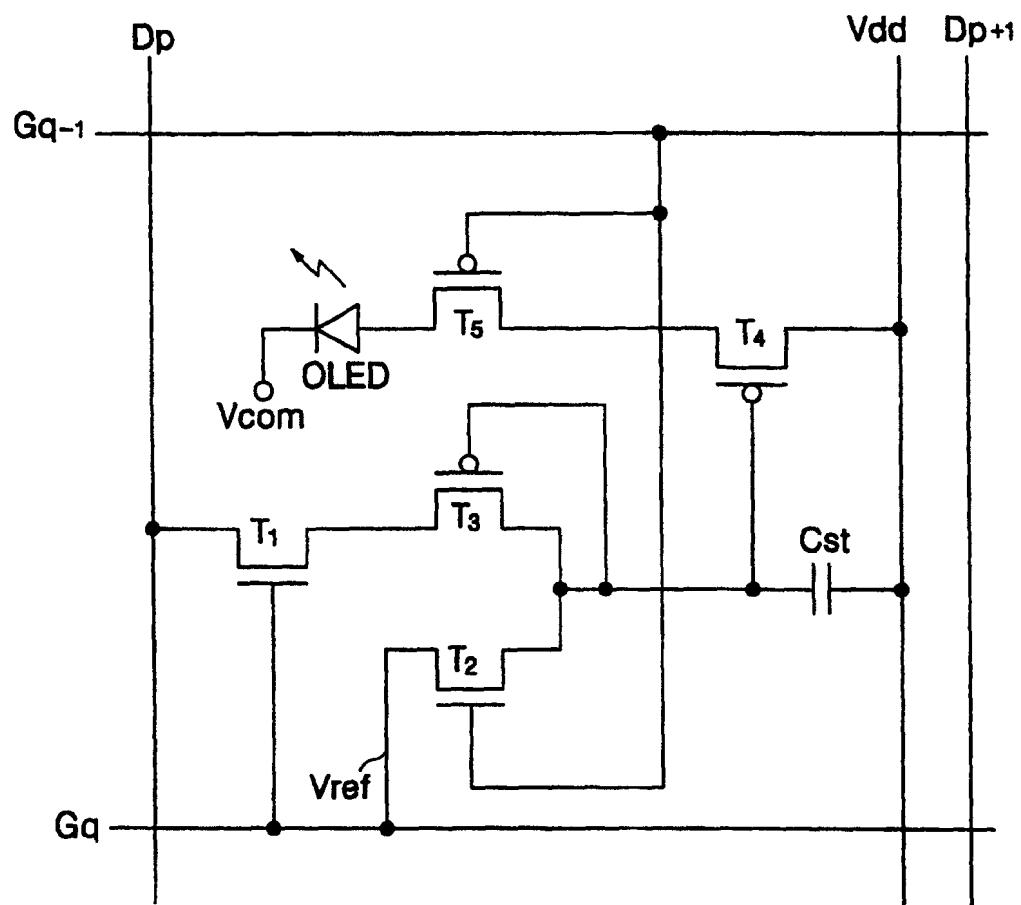

图3是说明根据本发明的第一实施例用于OLED装置的像素驱动单元的电路图；

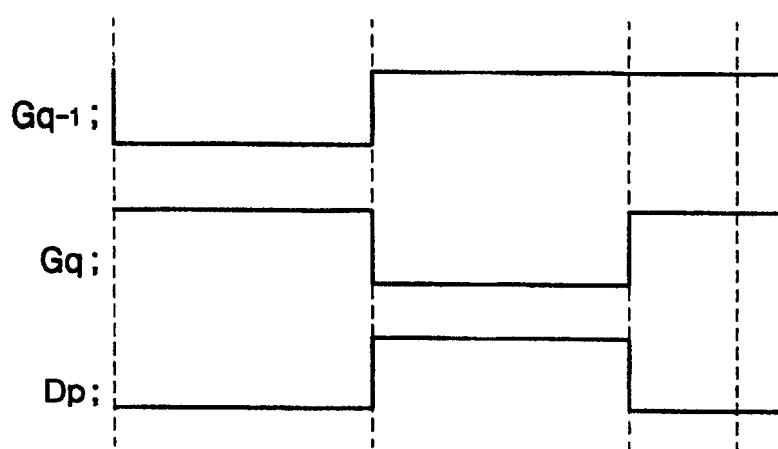

图4是施加到图3中的像素驱动单元的信号波形的图形视图；

图5A和5B是用于描述图3中的像素驱动单元工作的示意图；

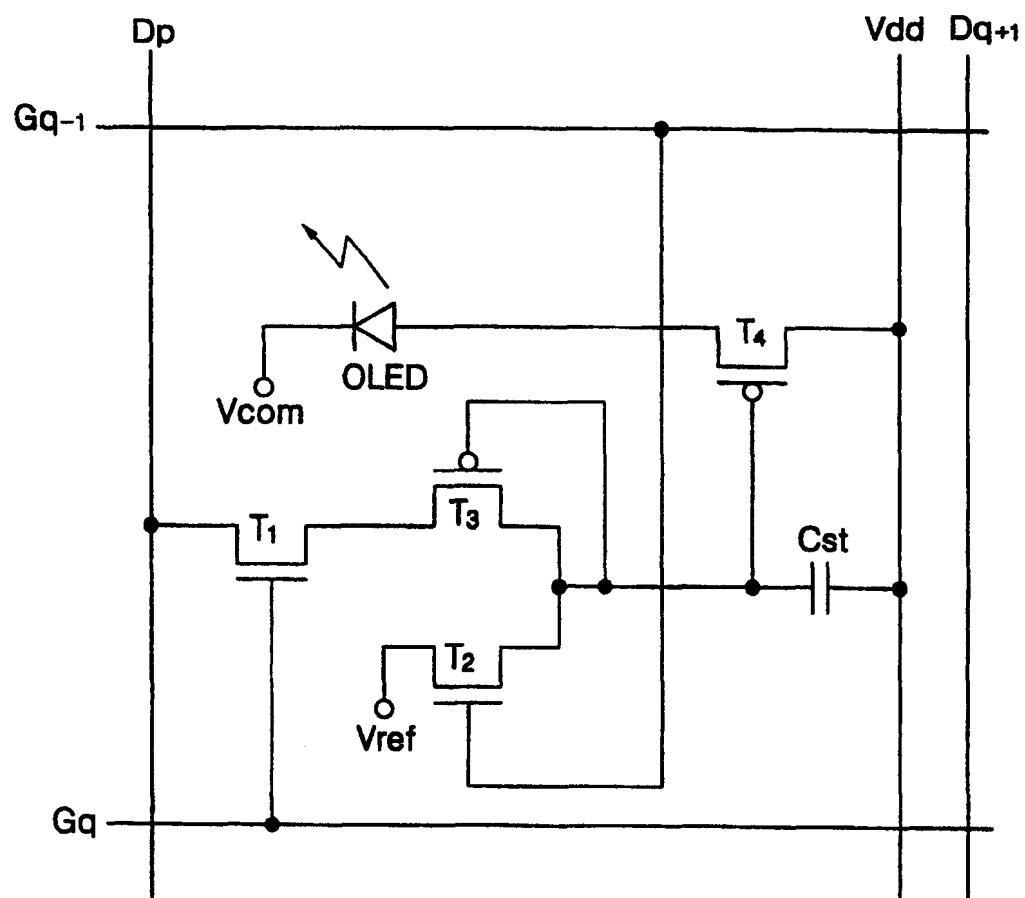

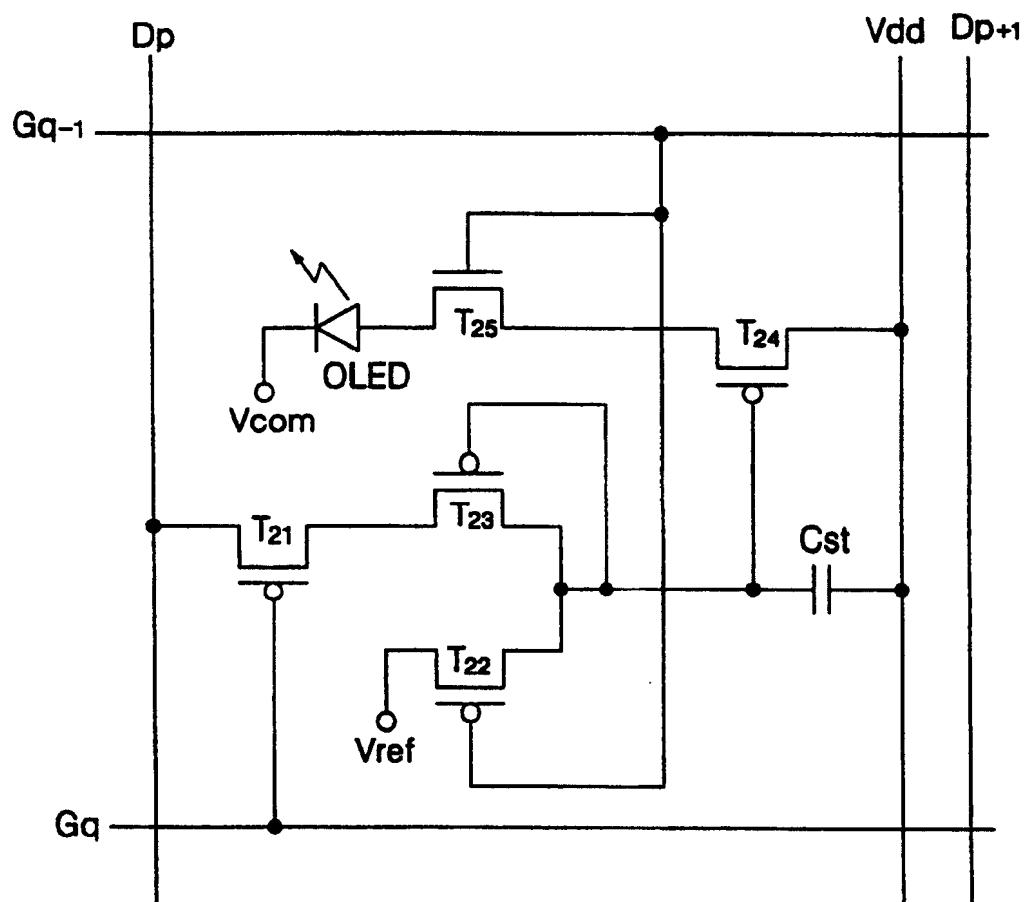

图6是说明根据本发明的第二实施例用于OLED装置的像素驱动单元的电路图；

图7是说明根据本发明的第三实施例用于OLED装置的像素驱动单元的电路图；

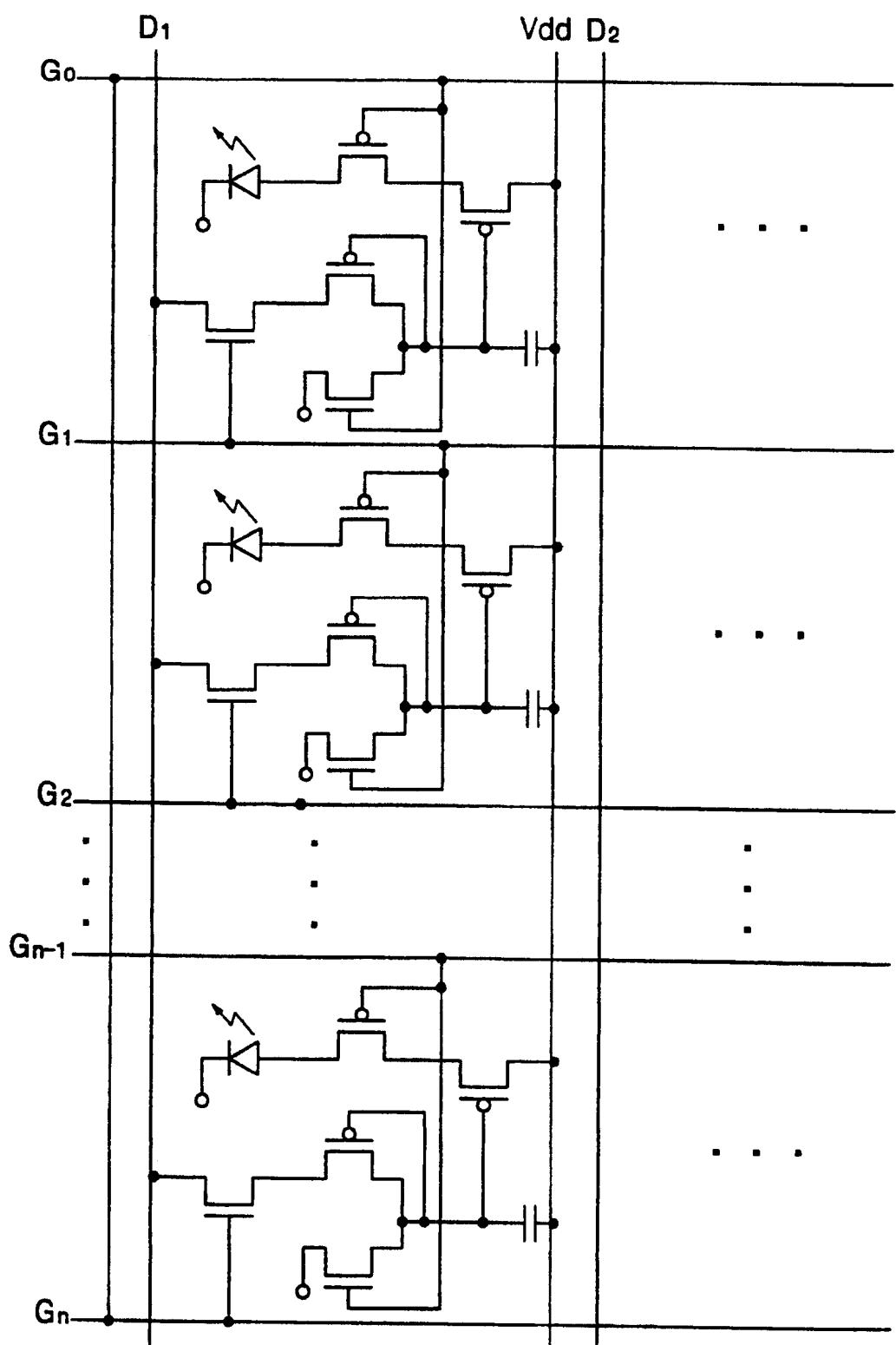

图8是说明根据本发明的一个实施例与栅极和数据线相关布置的OLED装置的多像素驱动单元的电路图；

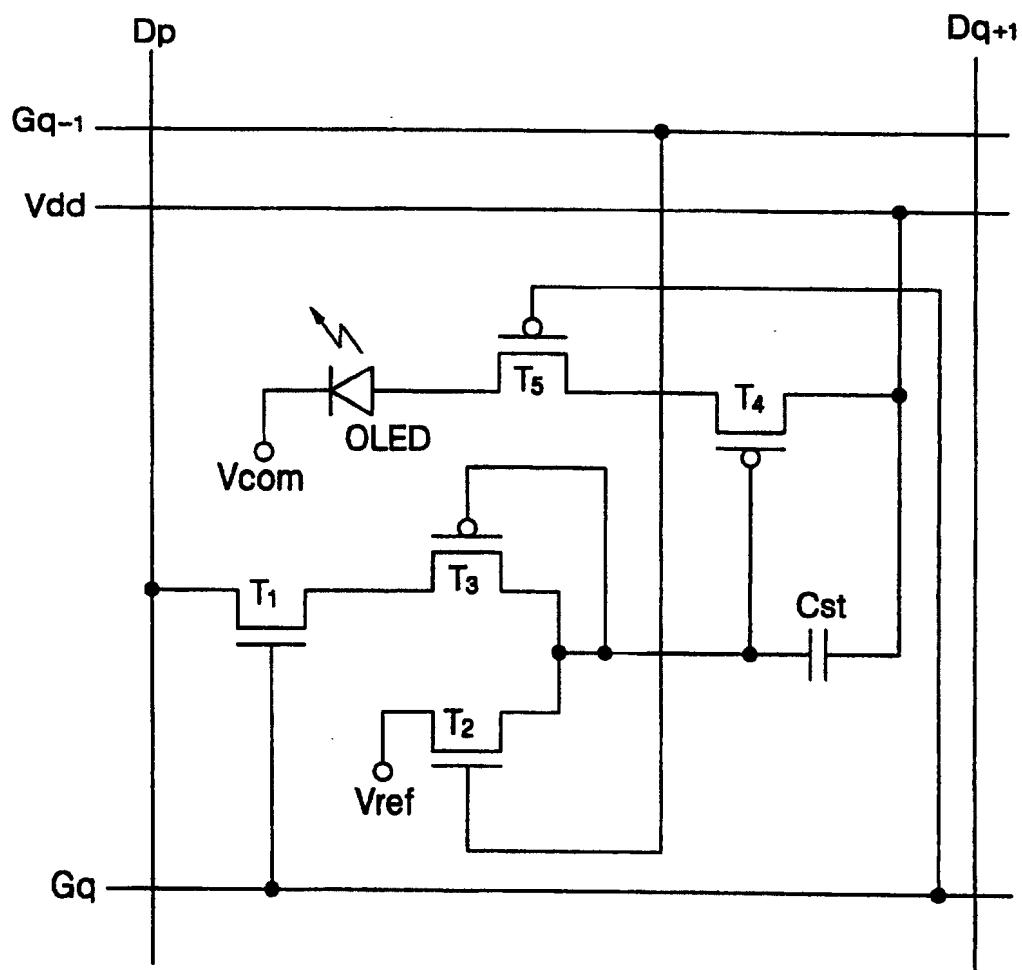

图9是说明根据本发明的第四实施例用于OLED装置的像素驱动单元的电路图；

图10是说明根据本发明的第五实施例用于OLED装置的像素驱动单元的电路图；

图11是说明根据本发明的第六实施例用于OLED装置的像素驱动单元的电路图；

图12是施加到图11的像素驱动单元的信号波形的图形视图；

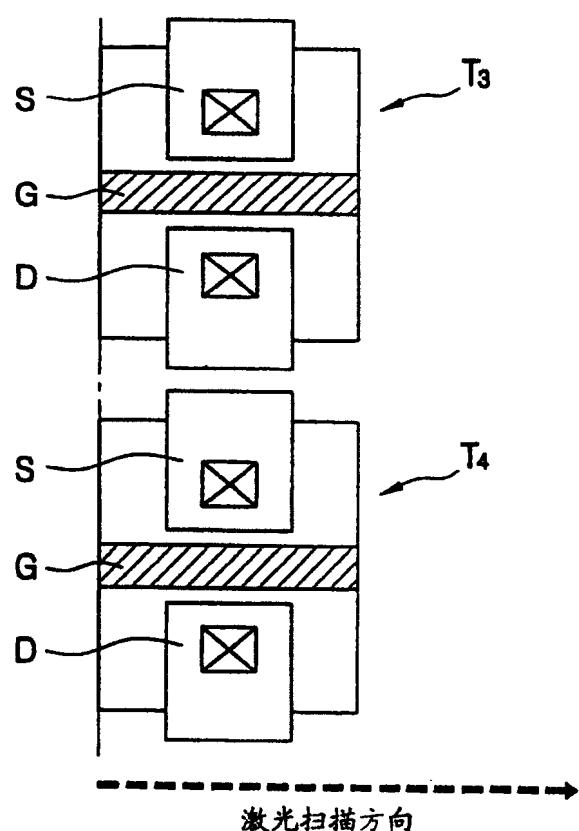

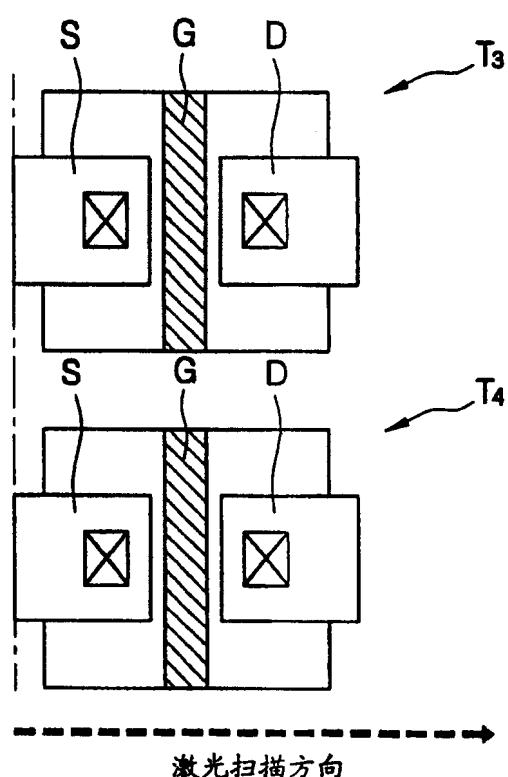

图13A和13B是说明根据本发明的示例性实施例制造的两个薄膜晶体管的示意图；

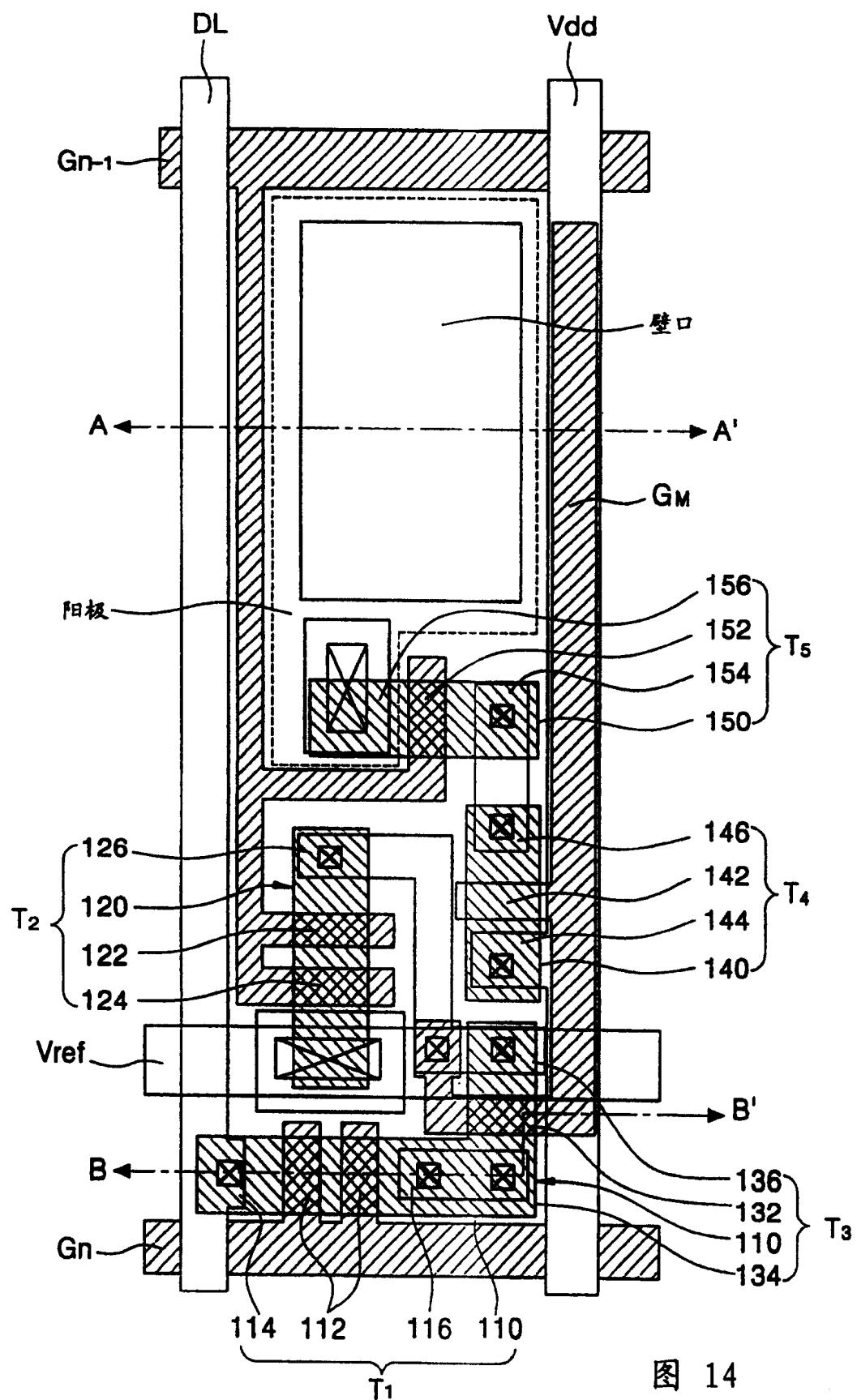

图14是图3的像素驱动单元的平面图；以及

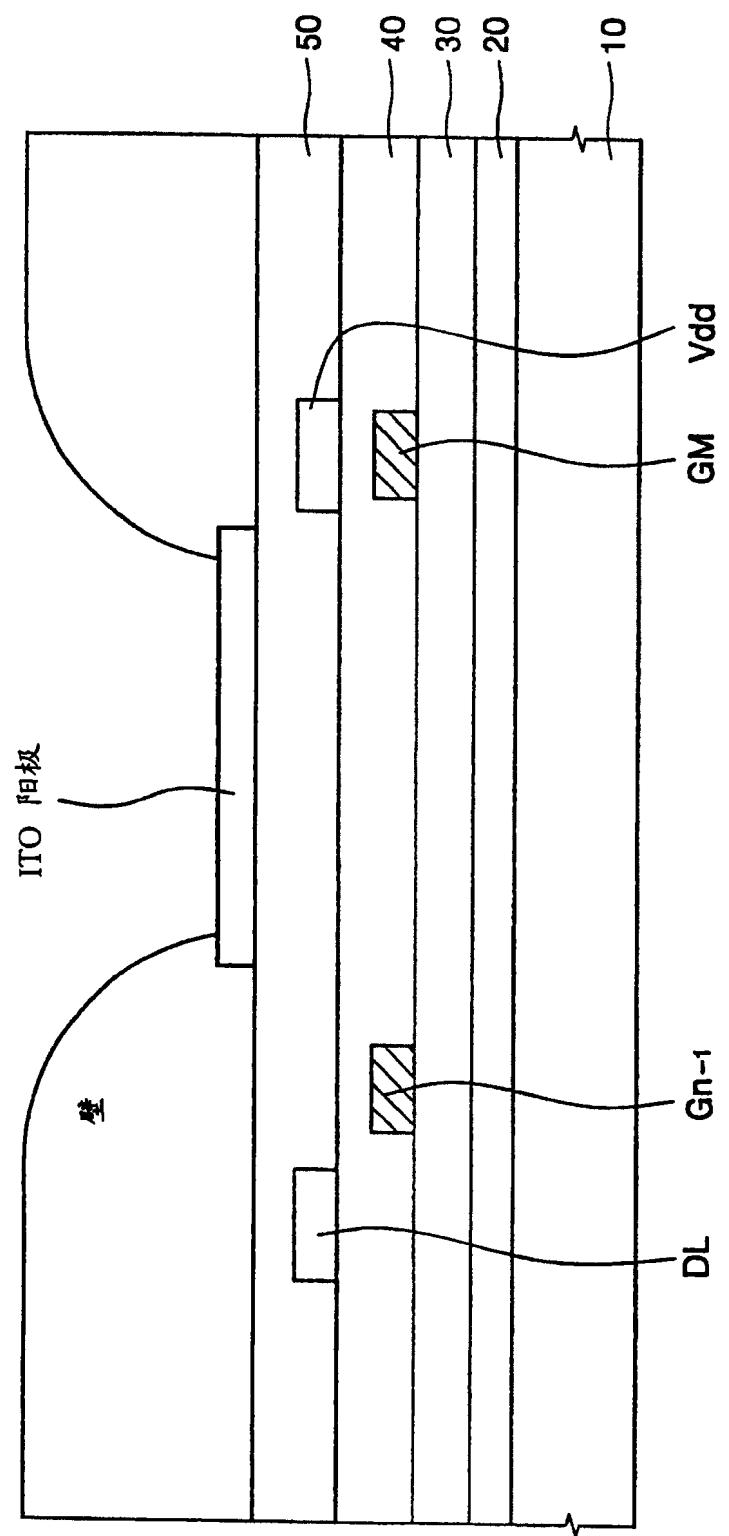

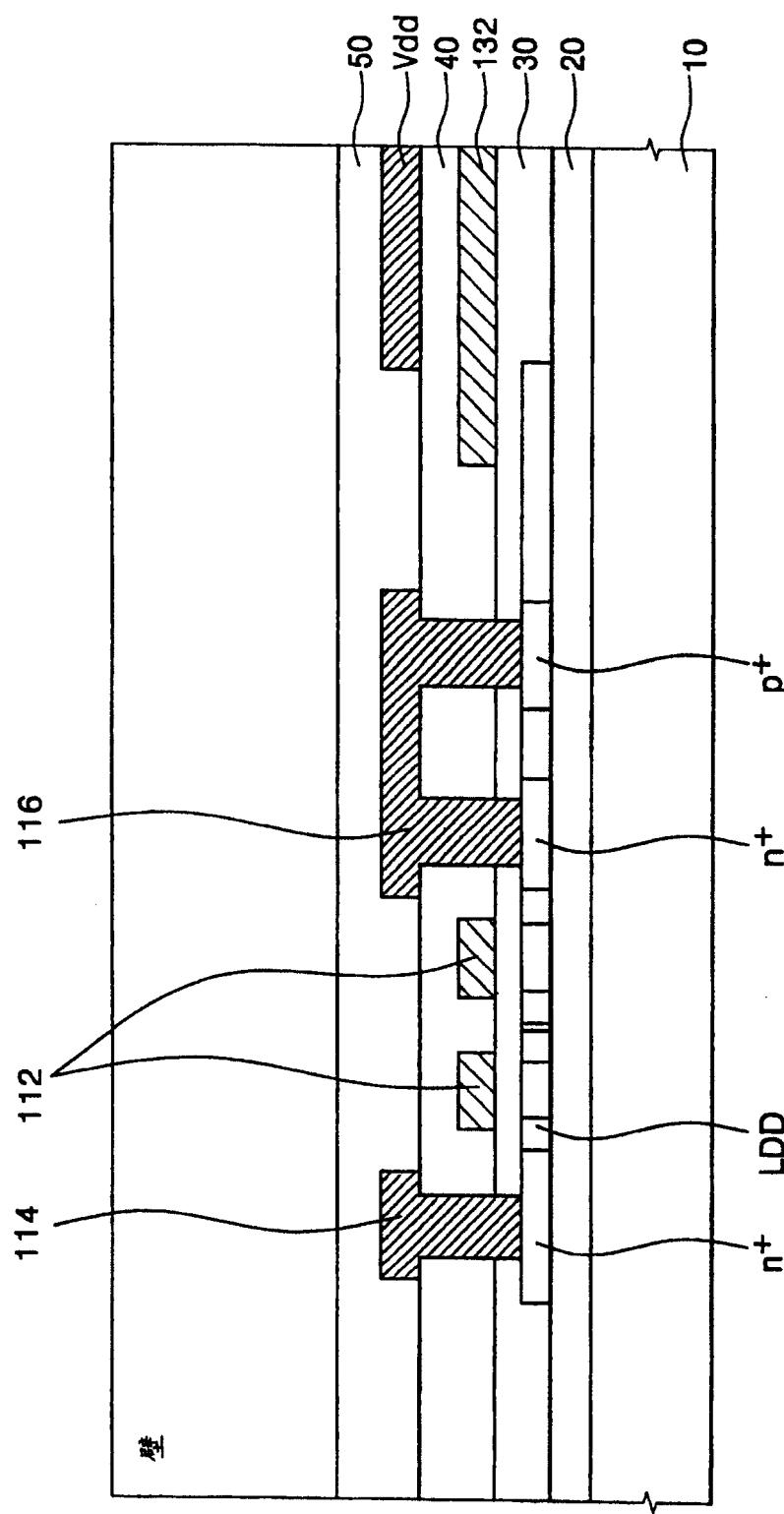

图15和16是分别沿图14的A-A'线和B-B'线的像素驱动单元的剖面图。

### 具体实施方式

在此公开了本发明的详细说明性实施例。但是，在此详细公开的具体结构和功能仅为了描述本发明示例性实施例。

图3是说明根据本发明的第一示例性实施例用于有机发光显示(OLED)装置的像素驱动单元的电路图，以及图4是施加到图3中的像素驱动单元的信号波形的图形视图。

在图3中，OLED装置的像素驱动单元包括五个晶体管，例如，第一至第三薄膜晶体管T<sub>1</sub>-T<sub>3</sub>，每一个具有开关功能，以及第四和第五薄膜晶体管T<sub>4</sub>、T<sub>5</sub>，每一个具有驱动功能。像素驱动单元还包括用于存储电荷的存储电容器C<sub>st</sub>和用于响应从第五薄膜晶体管T<sub>5</sub>施加的驱动信号而发光的OLED二极管。OLED二极管具有一接收来自第五晶体管T<sub>5</sub>的驱动信号的第一端，以及一连接到公共电极电压V<sub>COM</sub>的第二端。在该实施例中，五个薄膜晶体管T<sub>1</sub>-T<sub>5</sub>、存储电容器C<sub>st</sub>以及OLED二极管是主要构成用于OLED装置的一单元像素的像素驱动单元的元件。

像素驱动单元根据OLED装置的栅极线和数据线布置，以便每个像素驱动单元被布置在由相邻的栅极线和相邻的数据线围绕的区域中。为OLED装置提供偏压V<sub>dd</sub>的电源线也如此布置，以便每个电源线平行于相应数据线D<sub>p+1</sub>。选定数目的OLED装置的像素驱动单元连接到电源线V<sub>dd</sub>，像素驱动单元的数目等于栅极线的数目。电源线V<sub>dd</sub>可以形成为单个金属层(例如，MoW层)或双金属层(例如，MoW层和AlNd层)。

如图3所示，在具有m×n×3分辨率的OLED装置中由p<sub>th</sub>和(p+1)<sub>th</sub>数据线和(q-1)<sub>th</sub>和q<sub>th</sub>栅极线定义一个像素驱动单元(或一个单元像素)。在像素驱动单元中，例如，第一和第二薄膜晶体管T<sub>1</sub>、T<sub>2</sub>是N型晶体管，当施加到其栅极的栅极信号高于相应晶体管的阈值电压时，每个晶体管导通。第三至第五薄膜晶体管T<sub>3</sub>-T<sub>5</sub>是P型晶体管，当施加到其栅极的栅极信号低于相应晶体管的阈值电压时每个晶体管导通。具体地说，第一薄膜晶体管T<sub>1</sub>的栅极连接到当前的栅极线G<sub>q</sub>以及源极连接到数据线D<sub>p</sub>。第一薄膜晶体管T<sub>1</sub>响应通过当前的栅极线G<sub>q</sub>施加的栅极信号通过其漏极传送通过源极输入的数据信

号至第三薄膜晶体管T<sub>3</sub>。

第二薄膜晶体管T<sub>2</sub>具有一连接到前一级栅极线G<sub>q-1</sub>的栅极，以及一连接到向其提供基准电压V<sub>ref</sub>的基准电压线的源极。第二薄膜晶体管T<sub>2</sub>响应通过前一级栅极线G<sub>q-1</sub>施加的栅极信号通过其漏极传送通过源极输入的基准电压V<sub>ref</sub>至第四薄膜晶体管T<sub>4</sub>。换句话说，第二薄膜晶体管T<sub>2</sub>在基准电压V<sub>ref</sub>和第四薄膜晶体管T<sub>4</sub>的栅极之间具有一导电通路，该导电通路由从前一级栅极线施加的栅极信号控制。

第三薄膜晶体管T<sub>3</sub>的具有一连接到第一薄膜晶体管T<sub>1</sub>的漏极的源极，以及共同连接到第二薄膜晶体管的漏极、存储电容器Cst以及第四薄膜晶体管T<sub>4</sub>的栅极的一栅极和一漏极。第三薄膜晶体管T<sub>3</sub>将通过第一薄膜晶体管T<sub>1</sub>传送的数据信号传送至第四薄膜晶体管T<sub>4</sub>，作为第四薄膜晶体管T<sub>4</sub>的栅控信号。换句话说，第三薄膜晶体管T<sub>3</sub>具有一导电通路，将来自数据线Dp的数据信号传送至驱动晶体管的栅极，即，第四薄膜晶体管T<sub>4</sub>的栅极。第三薄膜晶体管T<sub>3</sub>的导电通路由第二薄膜晶体管T<sub>2</sub>的状态控制。换句话说，当第二薄膜晶体管T<sub>2</sub>截止时，第三薄膜晶体管T<sub>3</sub>导通。第二和第三薄膜晶体管相对于第四薄膜晶体管彼此平行，且分别提供基准电压和数据信号至第四薄膜晶体管的栅极。

第四薄膜晶体管T<sub>4</sub>具有一连接到用于提供偏压Vdd的电源线的源极。第四薄膜晶体管T<sub>4</sub>的栅极共同连接到存储电容器Cst的一端、第二薄膜晶体管的漏极以及第三薄膜晶体管T<sub>3</sub>的漏极。第四薄膜晶体管T<sub>4</sub>具有一传送偏压Vdd至第五薄膜晶体管T<sub>5</sub>的导电通路，该导电通路由栅极信号，即来自第二薄膜晶体管T<sub>2</sub>的基准信号或来自第三薄膜晶体管T<sub>3</sub>的数据信号之一，控制。第四薄膜晶体管T<sub>4</sub>具有类似或基本上相同于第三薄膜晶体管T<sub>3</sub>的性能。

第五薄膜晶体管T<sub>5</sub>具有一连接到第四薄膜晶体管T<sub>4</sub>的漏极的源极，一连接到OLED二极管的漏极以及一连接到前一级栅极线G<sub>q-1</sub>的栅极。第五薄膜晶体管T<sub>5</sub>响应通过前一级栅极线G<sub>q-1</sub>施加的栅极信号，输出从第四薄膜晶体管T<sub>4</sub>提供的驱动信号（例如，偏压Vdd）至OLED二极管。换句话说，第五薄膜晶体管T<sub>5</sub>具有由前一级栅极信号控制的导电通路，以提供驱动信号至OLED二极管。OLED二极管响应驱动信号而发光。OLED二极管具有两个端子，一端连接到第五薄膜晶体管的漏极，另一端连接到公共电极电压V<sub>COM</sub>。

存储电容器Cst具有两个端子，一端共同连接到第二和第三晶体管的漏

极以及第三和第四晶体管  $T_3$ 、 $T_4$  的栅极，另一端连接到偏压  $V_{dd}$ 。存储电容器  $C_{st}$  用偏压  $V_{dd}$  充电，并提供高电平信号（例如，偏压  $V_{dd}$ ）到第二至第四薄膜晶体管  $T_2-T_4$ ，时间一帧周期。当前一级栅极线  $G_{q-1}$  具有一逻辑高电平信号时，第二晶体管  $T_2$  导通，以便保存在存储电容器  $C_{st}$  中的电压通过第二晶体管放电，一逻辑低电平的基准信号  $V_{ref}$  被施加给第二晶体管中的源电极。结果，基准信号  $V_{ref}$  施加到第四晶体管  $T_4$  的栅极。

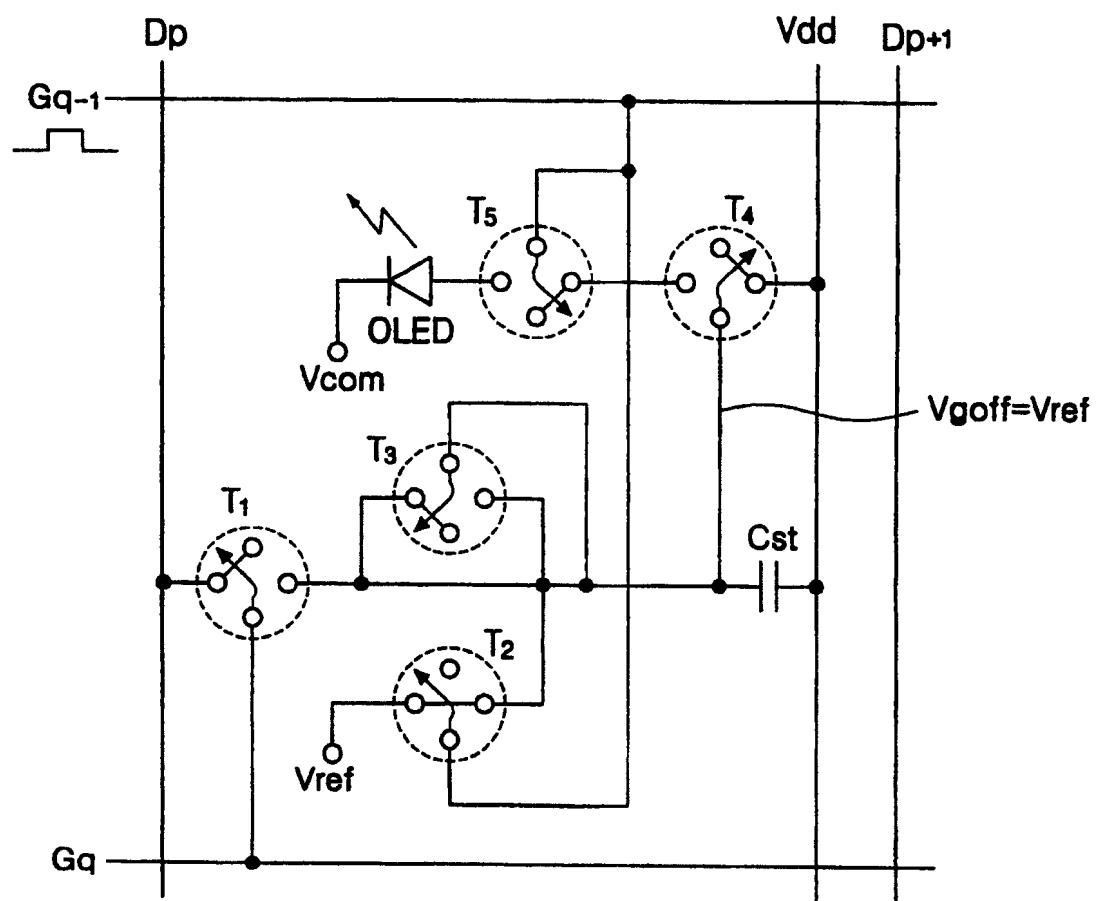

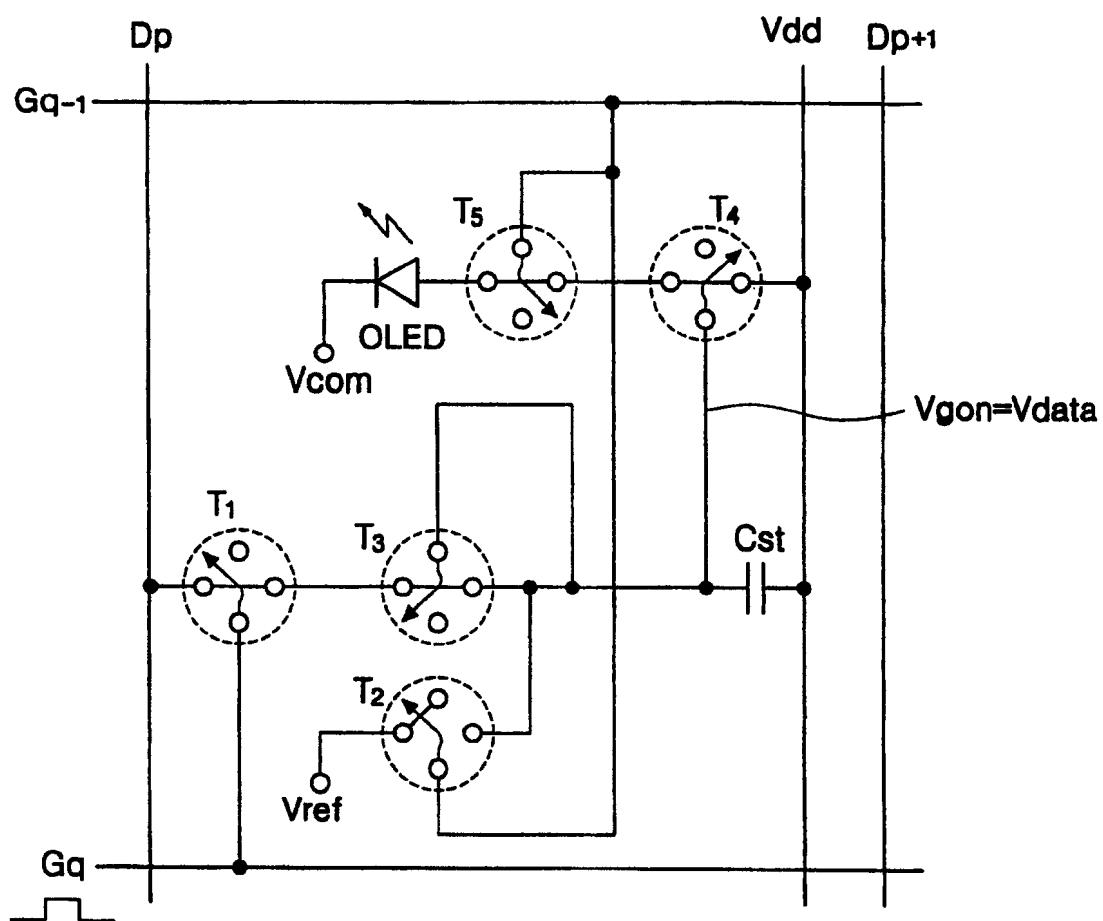

下面，进一步详细描述开关和驱动图3中的像素驱动单元的晶体管的工作。图5A和5B是用于描述图3的OLED装置的像素驱动单元工作的示意图。图5A示出了当激活的栅极信号施加到前一级栅极线时像素驱动单元的薄膜晶体管  $T_1-T_5$  的工作状态，图5B示出了当激活的栅极信号施加到当前的栅极线时像素驱动单元的薄膜晶体管  $T_1-T_5$  的工作状态。

参考图5A，当一个激活的信号（例如，高电平脉冲信号）施加到前一级栅极线时，第一、第三、第四以及第五薄膜晶体管  $T_1$ 、 $T_3$ 、 $T_4$ 、 $T_5$  截止，第二薄膜晶体管  $T_2$  导通。结果，从基准电压线提供的基准电压  $V_{ref}$  施加到第四薄膜晶体管  $T_4$  的栅极。基准电压  $V_{ref}$  可以定义为如下的公式1。

$$[V_{gate-off(T1)}] \leq V_{ref} \leq [V_{data,min} + V_{th(T3)}] \quad \text{公式 1}$$

这里， $V_{gate-off(T1)}$  是第一薄膜晶体管  $T_1$  的栅极截止电压， $V_{data,min}$  是施加到数据线  $D_p$  的数据信号的最小电压值， $V_{th(T3)}$  是第三薄膜晶体管  $T_3$  的阈值电压，是负电压。在此条件下，第四薄膜晶体管  $T_4$  的栅极截止电压变为基准电压  $V_{ref}$ ，第三薄膜晶体管  $T_3$  的栅极截止电压也变为基准电压  $V_{ref}$ 。

参考图5B，当一个激活的栅极信号（例如，高电平脉冲信号）施加到当前的栅极线时，第一薄膜晶体管  $T_1$  导通，第二薄膜晶体管  $T_2$  截止。结果，从数据线施加的数据信号通过第一薄膜晶体管的导电通路传送到第三薄膜晶体管  $T_3$ 。用数据信号电压  $V_{data}$  充电的存储电容器  $C_{st}$  提供高电平电压至第三薄膜晶体管  $T_3$  的栅极。然后，第三薄膜晶体管  $T_3$  导通，从第一薄膜晶体管  $T_1$  提供的数据信号传送到第四薄膜晶体管  $T_4$  的栅极。此时，决定流过第四薄膜晶体管  $T_4$  的导电通路的电流强度的有效栅-源电压  $V_{gs'(T4)}$  定义为如下的公式2。

$$V_{gs'(T4)} = V_{gs(T4)} + V_{th(T4)} \quad \text{公式 2}$$

这里，第四薄膜晶体管  $T_4$  的栅-源电压  $V_{gs(T4)}$  是第四薄膜晶体管  $T_4$  的栅压和偏压  $V_{dd}$  之间的差值，由下列公式3表示。

$$V_{gs(T4)} = V_{g(T4)} - V_{dd} \quad \text{公式 3}$$

这里，第四薄膜晶体管T<sub>4</sub>的栅压V<sub>g(T4)</sub>是数据电压（即，数据信号的电压值）和第三薄膜晶体管T<sub>3</sub>的阈值电压V<sub>th</sub>之间的差值，用下列公式4表示。

$$V_{g(T4)} = V_{data} + V_{th(T3)} \quad \text{公式4}$$

这里，第三薄膜晶体管T<sub>3</sub>的阈值电压V<sub>th(T3)</sub>是负电压。假定第三和第四薄膜晶体管T<sub>3</sub>、T<sub>4</sub>的性能彼此基本上相同，那么第三薄膜晶体管T<sub>3</sub>的阈值电压V<sub>th</sub>基本上等于第四薄膜晶体管T<sub>4</sub>的阈值电压V<sub>th</sub>。

$$V_{th(T3)} = V_{th(T4)} \quad \text{公式5}$$

从公式2至5，如下获得决定流过第四薄膜晶体管T<sub>4</sub>的电流强度的有效栅-源电压V<sub>gs'(T4)</sub>。

$$V_{gs'(T4)} = V_{data} - V_{dd} \quad \text{公式6}$$

如公式6所示，第四薄膜晶体管T<sub>4</sub>的有效栅-源电压V<sub>gs'(T4)</sub>是通过数据线D<sub>p</sub>提供的数据电压V<sub>data</sub>和通过外部电源线提供的偏压V<sub>dd</sub>之间的差值。因此，在OLED装置的每一个像素中的第四薄膜晶体管T<sub>4</sub>的有效栅-源电压V<sub>gs'(T4)</sub>仅取决于通过数据线D<sub>p</sub>施加的数据电压V<sub>data</sub>和通过外部电源线施加的偏压V<sub>dd</sub>的强度。换句话讲，决定流过驱动晶体管的电流强度的有效栅-源电压V<sub>gs'(T4)</sub>与驱动晶体管（即第四薄膜晶体管T<sub>4</sub>）的阈值电压V<sub>th</sub>无关。

因此，通过在OLED装置的每个像素驱动单元中应用具有基本相同的性能的第三和第四薄膜晶体管T<sub>3</sub>和T<sub>4</sub>，像素驱动单元均衡第四薄膜晶体管T<sub>4</sub>的性能（特别是阈值电压V<sub>th</sub>），该阈值电压V<sub>th</sub>在不同的像素中是不同的。结果，每个像素驱动单元的驱动晶体管响应相同的数据信号提供具有基本上相同强度的电流给OLED二极管，即使像素的驱动晶体管（即，第四薄膜晶体管T<sub>4</sub>）具有与其它像素的驱动晶体管不同的阈值电压。

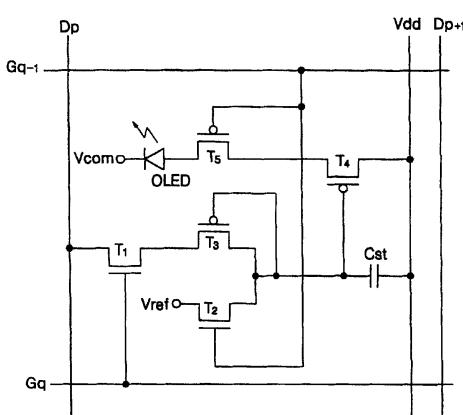

参考图6，根据本发明的第二示例性实施例提供一种用于OLED装置的像素驱动单元。在本实施例中，像素驱动单元不需要用于提供基准电压V<sub>ref</sub>的单独线。在图6的电路图中，用于OLED装置的像素驱动单元包括每个都具有开关功能的第一至第三薄膜晶体管T<sub>1</sub>-T<sub>3</sub>；每个都具有驱动功能的第四和第五薄膜晶体管T<sub>4</sub>、T<sub>5</sub>；一存储电容器C<sub>st</sub>以及一连接到公共电极电压V<sub>COM</sub>的OLED二极管。每个像素驱动单元定位在由用于传送栅极信号的栅极线和用于传送数据信号的数据线围绕的区域中。在图6中，与图3中相等的部分用同样的附图标记表示，并省去其描述以避免重复。

在本实施例中，通过当前栅极线G<sub>q</sub>施加的栅极信号用作第二薄膜晶体管

$T_2$ 的基准电压 $V_{ref}$ 。例如，第二薄膜晶体管 $T_2$ 的漏极与第一薄膜晶体管 $T_1$ 的栅极共同连接到当前栅极线 $Gq$ 。

在像素驱动单元的工作中，当激活的栅极信号（例如，高电平脉冲信号）施加到前一级栅极线 $G_{q-1}$ 时，第一、第三、第四以及第五薄膜晶体管 $T_1$ 、 $T_3$ 、 $T_4$ 、 $T_5$ 截止，第二薄膜晶体管 $T_2$ 导通。结果，基准电压 $V_{ref}$ 通过第二薄膜晶体管 $T_2$ 施加到第四薄膜晶体管 $T_4$ 的栅极。当选择前一级栅极线以接收激活的栅极信号时，由于基准电压 $V_{ref}$ 是施加到去激活的当前栅极线上的栅极信号，因此基准电压 $V_{ref}$ 是截止电平信号。

当激活的栅极信号施加到当前栅极线 $Gq$ 时，第一薄膜晶体管 $T_1$ 导通，以便从数据线 $Dp$ 施加到第一薄膜晶体管 $T_1$ 的源极的数据信号（例如，高电平电压信号）通过第一薄膜晶体管 $T_1$ 的导电通路传送到第三薄膜晶体管 $T_3$ 。此时，用数据信号电压 $V_{data}$ 充电的存储电容器 $Cst$ 提供高电平电压至第三薄膜晶体管 $T_3$ 的栅极，以导通第三薄膜晶体管 $T_3$ 。然后，通过第一和第三薄膜晶体管 $T_1$ 、 $T_3$ 传送的数据信号被提供给第四薄膜晶体管 $T_4$ 的栅极。因此，如上所述，在本实施例中不需要单独的基准线。

图7是说明根据本发明的第三示例性实施例用于OLED装置的像素驱动单元的电路图。参考图7，像素驱动单元包括第一至第三薄膜晶体管 $T_1$ - $T_3$ ，每个具有开关功能；第四薄膜晶体管 $T_4$ ，具有驱动功能；存储电容器 $Cst$ 以及连接到公共电极电压 $V_{COM}$ 的OLED二极管，这些构成OLED装置的一单元像素。像素驱动单元定位在由用于传送栅极信号的相邻栅极线和用于传送数据信号的相邻数据线围绕的区域中。在图7中，与图3中等效的部分用同样的附图标记表示，并省去其描述以避免重复。在本实施例的像素驱动单元中，将第五薄膜晶体管 $T_5$ 从图3中根据本发明的第一实施例的像素驱动单元中省略掉。

当一个激活的作栅极信号被施加到前一级栅极线 $G_{q-1}$ 时，第一、第三以及第四薄膜晶体管 $T_1$ 、 $T_3$ 、 $T_4$ 截止，第二薄膜晶体管 $T_2$ 导通。结果，从基准电压线提供到第二薄膜晶体管 $T_2$ 的源极的基准电压 $V_{ref}$ 被施加到第四薄膜晶体管 $T_4$ 的栅极。在该实施例中，基准电压 $V_{ref}$ 与等式1中描述的相同。

此外，当激活的栅极信号施加到当前栅极线 $Gq$ 时，第一薄膜晶体管 $T_1$ 导通，以便通过数据线 $Dp$ 施加到第一薄膜晶体管 $T_1$ 的源极的数据信号通过第一薄膜晶体管 $T_1$ 的导电通路被传送到第三薄膜晶体管 $T_3$ 。此时，由于用数据

信号电压  $V_{data}$  充电的存储电容器  $C_{st}$  提供高电平电压至第三薄膜晶体管  $T_3$  的栅极，因此第三薄膜晶体管  $T_3$  导通。因此，通过第一和第三薄膜晶体管  $T_1$ 、 $T_3$  的数据信号被提供给第四薄膜晶体管  $T_4$  的栅极。

同样地，本实施例的像素驱动单元对第四薄膜晶体管  $T_4$  的阈值电压  $V_{th}$  任意变化均衡它的像素驱动功能，阈值电压  $V_{th}$  的任意变化的第四薄膜晶体管  $T_4$  与相同的OLED装置的其它像素驱动单元中的第四薄膜晶体管的性能不同。利用这种均衡，像素驱动单元响应与不同的像素驱动单元中驱动晶体管变化的性能无关的同样的数据信号将相同的电流作为驱动信号提供给OLED二极管。

图8是说明根据本发明实施例与栅极和数据线相关布置的OLED装置的多像素驱动单位的电路图。在该实施例中，多像素驱动单元每个具有与图3的实施例相同的结构。参考图8，具有以矩阵形式布置的多像素驱动单元的OLED装置分别对应于OLED装置的像素。在该实施例中的OLED装置在一列中具有“n”个像素驱动单元（即，“n”个像素）和“n”个栅极线  $G_1-G_n$ ，每条栅极线与“n”个像素驱动单元相应的一个相对应。OLED装置连续地提供作为扫描信号的栅极信号至各个栅极线。

除用于“n”个像素驱动单元的“n”个栅极线  $G_1$ 、 $G_2$ ... $G_{n-1}$  之外，OLED装置还具有虚设栅极线  $G_0$ ，以提供栅极信号至与第一栅极线  $G_1$  对应的像素驱动单元的第二和第五薄膜晶体管  $T_2$  和  $T_5$  的栅极。虚设栅极线  $G_0$  与第  $n$  个栅极线  $G_n$  同步。通过使虚设栅极线  $G_0$  与第  $n$  个栅极线  $G_n$  同步，防止虚设栅极线  $G_0$  保持浮置状态。

另外，虚设栅极线  $G_0$  可以接收来自栅极驱动器的单独的栅极信号，而不是与第  $n$  个栅极线  $G_n$  同步。换句话说，栅极驱动器分别连续地提供“n”个栅极信号至“n”个栅极线，以驱动选择的栅极线。当栅极驱动器提供栅极信号至第  $n$  个栅极线  $G_n$  时，它同时还提供同样的栅极信号至虚设栅极线  $G_0$ 。因此，虚设栅极线  $G_0$  具有与第  $n$  个栅极线  $G_n$  同步的同样效果，防止保持浮置状态。

在图3至8的上述实施例中，OLED装置的像素驱动单元（或像素）以矩阵形式布置，以便每个像素驱动单元由在行方向延伸且在列方向彼此平行布置的相邻栅极线和在列方向延伸且在行方向彼此平行布置的相邻数据线限定。此外，电源线在列方向延伸且平行于数据线布置以提供偏压至各个像素驱动单元的驱动晶体管。

在该结构中，电源线平行于相应的数据线的这种布置可能在OLED装置中引起“串扰”(cross-talk)现象。换句话说，当如图8所示，电源线在平行于数据线的列方向延伸时，全电平偏压施加到第一像素驱动单元，但是偏压的电平可以逐渐降低到与它施加到较低的像素一样。结果，在第一像素驱动单元中的第四薄膜晶体管T<sub>4</sub>的栅-源电压V<sub>gs1(T4)</sub>和第n个像素驱动单元中的第四薄膜晶体管T<sub>4</sub>的栅-源电压V<sub>gsn(T4)</sub>之间可能存在电压差。由于像素驱动单元之间的栅-源电压的差值，即使具有同样电平的数据电压施加到像素驱动单元上，在各个像素驱动单元中的第四薄膜晶体管的源极之间也可能存在电压差。在较低的像素中这种“串扰”现象可能增加，由此引起OLED装置的显示质量退化。

图9是说明根据本发明的第四示例性实施例用于OLED装置的像素驱动单元的电路图。在本实施例中，电源线Vdd在行方向延伸且平行于栅极线布置，由此有效地减小“串扰”现象。参考图9，根据本发明的第四实施例的像素驱动单元包括第一至第三薄膜晶体管T<sub>1</sub>-T<sub>3</sub>，每个具有开关功能；第四和第五薄膜晶体管T<sub>4</sub>、T<sub>5</sub>，每个具有驱动功能；存储电容器Cst以及连接到公共电极电压V<sub>COM</sub>的OLED二极管，这些是主要构成OLED装置的单元像素的元件。像素驱动单元以矩阵形式布置在OLED装置中，以便每个像素驱动单元限定在由两个相邻栅极线和两个相邻数据线围绕的区域中，两个相邻的栅极线的每一个用于传送栅极信号，两个相邻的数据线的每一个用于传送数据信号。在图9中，与图3中等效的部分用同样的附图标记表示，并省去其描述以避免重复。在该实施例中，第五薄膜晶体管T<sub>5</sub>的栅极连接到当前栅极线G<sub>q</sub>，以便第五薄膜晶体管T<sub>5</sub>响应通过当前栅极信号线提供的栅极信号导通或截止。

在图9的像素驱动单元的工作中，当激活的栅极信号（例如，高电平脉冲信号）施加到前一级栅极线G<sub>q-1</sub>时，第一、第三以及第四薄膜晶体管T<sub>1</sub>、T<sub>3</sub>、T<sub>4</sub>截止，第二和第五薄膜晶体管T<sub>2</sub>、T<sub>5</sub>导通。结果，从基准电压线提供的基准电压V<sub>ref</sub>施加到第四薄膜晶体管T<sub>4</sub>的栅极。在该实施例使用的基准电压V<sub>ref</sub>与等式1中描述的相同。

当激活的栅极信号被施加到当前栅极线G<sub>q</sub>时，第一薄膜晶体管T<sub>1</sub>导通，以便从数据线D<sub>p</sub>施加到第一薄膜晶体管T<sub>1</sub>源极的数据信号传送到第三薄膜晶体管T<sub>3</sub>的漏极。此时，用数据信号电压V<sub>data</sub>充电的存储电容器Cst提供高

电平电压至第三薄膜晶体管T<sub>3</sub>的栅极，以便第三薄膜晶体管T<sub>3</sub>导通。因此，通过第一和第三薄膜晶体管T<sub>1</sub>、T<sub>3</sub>的数据信号被提供给第四薄膜晶体管T<sub>4</sub>的栅极。然后，第四薄膜晶体管T<sub>4</sub>响应施加到它栅极的数据信号通过它的导电通路提供偏压至第五薄膜晶体管。当前栅极线G<sub>q</sub>的信号变为逻辑高电平时，第五薄膜晶体管T<sub>5</sub>截止。接着，当前一级栅极线信号变为逻辑高电平以及当前栅极线信号变为逻辑低电平时，第五薄膜晶体管T<sub>5</sub>导通，并保持激活（即，导通）状态，直到下一帧。

在该实施例中，如上所述，通过布置在平行于栅极线的行方向上延伸的电源线有效地消除“串扰”现象，同时均衡不同像素驱动单元的驱动操作，用以改变不同像素驱动单元的第四薄膜晶体管T<sub>4</sub>的性能。

图10是说明根据本发明的第五示例性实施例用于OLED装置的像素驱动单元的电路图。在图10中，与图3相同部分用相同的附图标记表示。在该实施例中，电源线在平行于栅极线的行方向延伸以及在第五薄膜晶体管和OLED二极管之间提供附加的薄膜晶体管T<sub>6</sub>。

参考图10，像素驱动单元包括第一至第三薄膜晶体管T<sub>1</sub>-T<sub>3</sub>，每个具有开关功能，第四至第六薄膜晶体管T<sub>4</sub>-T<sub>6</sub>，每个具有驱动功能，存储电容器C<sub>st</sub>以及连接到公共电极电压V<sub>COM</sub>的OLED二极管，这些是构成OLED装置的单元像素的主要元件。OLED装置的每个像素驱动单元布置在由两个相邻栅极线和两个相邻数据线围绕的区域中，两个相邻的栅极线的每一个用于传送栅极信号，两个相邻的数据线的每一个用于传送数据信号。在该实施例中，第五薄膜晶体管T<sub>5</sub>是一P型薄膜晶体管，具有连接到前一级栅极线G<sub>q-1</sub>的栅极，以便响应通过前一级栅极信号线提供的栅极信号导通或截止。此外，第六薄膜晶体管T<sub>6</sub>是一N型薄膜晶体管，具有连接到第五薄膜晶体管T<sub>5</sub>的漏极的源极，连接到OLED二极管的漏极，以及连接到当前栅极线G<sub>q</sub>的栅极。因此第六薄膜晶体管T<sub>6</sub>响应通过当前栅极信号线G<sub>q</sub>施加的栅极信号导通或截止。

在运行中，当一个激活的栅极信号施加到前一级栅极线G<sub>q-1</sub>时，第一、第三、第四、第五以及第六薄膜晶体管T<sub>1</sub>、T<sub>3</sub>、T<sub>4</sub>、T<sub>5</sub>、T<sub>6</sub>截止，第二薄膜晶体管T<sub>2</sub>导通。因此，从基准电压线提供的基准电压V<sub>ref</sub>施加到第四薄膜晶体管T<sub>4</sub>的栅极。基准电压V<sub>ref</sub>与等式1中描述的相同。

当激活的栅极信号施加到当前栅极线G<sub>q</sub>时，第一薄膜晶体管T<sub>1</sub>导通，以便从数据线D<sub>p</sub>施加到第一薄膜晶体管T<sub>1</sub>的源极的数据信号通过第一薄膜晶

体管T<sub>1</sub>的导电通路传送到第三薄膜晶体管T<sub>3</sub>的漏极。此外，因为前一级栅极线去激活，所以第二薄膜晶体管截止。因此，通过第一和第三薄膜晶体管T<sub>1</sub>、T<sub>3</sub>的数据信号被提供给第四薄膜晶体管T<sub>4</sub>的栅极。因此，第四薄膜晶体管导电通路由从第三薄膜晶体管T<sub>3</sub>的源极提供的数据信号控制。

在本发明的第一至第五实施例的像素驱动单元中，第一和第二薄膜晶体管T<sub>1</sub>、T<sub>2</sub>是N型薄膜晶体管，第三至第五薄膜晶体管T<sub>3</sub>、T<sub>4</sub>、T<sub>5</sub>是P型薄膜晶体管。但是，本发明不局限于这种结构。例如，本发明的像素驱动单元可以包括是P型薄膜晶体管的第一至第四薄膜晶体管T<sub>1</sub>-T<sub>4</sub>，以及是N型薄膜晶体管的第五薄膜晶体管T<sub>5</sub>。

图11是说明根据本发明的第六示例性实施例用于OLED装置的像素驱动单元的电路图，图12是施加到图11中的像素驱动单元的信号波形的图形视图。参考图11，像素驱动单元包括每个具有开关功能的第一至第三薄膜晶体管T<sub>21</sub>-T<sub>23</sub>，每个具有驱动功能的第四和第五薄膜晶体管T<sub>24</sub>、T<sub>25</sub>，存储电容器Cst以及连接到公共电极电压V<sub>COM</sub>的OLED二极管，这些构成OLED装置的单元像素。像素驱动单元布置在由用于传送栅极信号的相邻栅极线和用于传送数据信号的相邻数据线围绕的区域中。由于第一至第四薄膜晶体管T<sub>21</sub>-T<sub>24</sub>是P型薄膜晶体管，因此当具有低于其阈值电压电平的栅极信号施加到第一至第四薄膜晶体管T<sub>21</sub>-T<sub>24</sub>的相应各个的栅极时，它们各自导通。第五薄膜晶体管T<sub>25</sub>是N型薄膜晶体管，因此当具有高于其阈值电压电平的栅极信号施加到第五薄膜晶体管T<sub>25</sub>的栅极时，第五薄膜晶体管T<sub>25</sub>导通。

如图12所示，分别施加到栅极线的栅极信号是反相的信号。换句话说，由于第一薄膜晶体管T<sub>21</sub>是P型薄膜晶体管，因此当施加到当前栅极线G<sub>q</sub>的栅极信号具有高电平时，第一薄膜晶体管T<sub>21</sub>保持去激活。相反，当施加到当前栅极线G<sub>q</sub>的栅极信号具有低电平（即，激活的低电平信号）时，第一薄膜晶体管T<sub>21</sub>保持激活。为了提供这种反相的栅极信号给用于OLED装置的像素驱动单元，在连续地输出栅极信号的栅极驱动器中提供一个反相器。

在像素驱动单元的工作中，当前一级栅极线被激活（即，低电平栅极信号施加到前一级栅极线G<sub>q-1</sub>以及高电平栅极信号施加到当前栅极线）时，第一、第三、第四以及第五薄膜晶体管T<sub>1</sub>、T<sub>3</sub>、T<sub>4</sub>、T<sub>5</sub>截止，第二薄膜晶体管T<sub>2</sub>导通。因此，基准电压V<sub>ref</sub>施加到第四薄膜晶体管T<sub>4</sub>的栅极。在此情况下，基准电压V<sub>ref</sub>可以按如下公式7和8定义。

$$V_{ref} < V_{gate-off(T21)} \quad \text{公式7}$$

这里,  $V_{gate-off(T21)}$  是第一薄膜晶体管  $T_{21}$  的栅极-截止电压。

$$V_{ref} < [V_{data,min} + V_{th(T23)}] \quad \text{公式8}$$

这里,  $V_{data,min}$  是施加到数据线  $D_p$  的最小电压值,  $V_{th(T23)}$  是第三薄膜晶体管  $T_{23}$  的阈值电压。

接下来, 当前栅极线  $G_q$  被激活时 (即, 低电平栅极信号施加到当前栅极线  $G_q$  以及高电平栅极信号施加到前一级栅极线  $G_{q-1}$ ) 时, 第一薄膜晶体管  $T_{21}$  导通, 以便施加到第一薄膜晶体管  $T_{21}$  的源极的数据信号传送到第三薄膜晶体管  $T_{23}$  的漏极。此时, 由于用数据信号电压  $V_{data}$  充电的存储电容器  $C_{st}$  提供高电平电压至第三薄膜晶体管  $T_{23}$  的栅极, 因此第三薄膜晶体管  $T_{23}$  导通。因此, 通过第一和第三薄膜晶体管  $T_{21}$ 、 $T_{23}$  的数据信号提供给第四薄膜晶体管  $T_{24}$  的栅极。此时, 由下面的公式9表示决定流过第四薄膜晶体管  $T_{24}$  的电流强度的有效栅-源电压  $V_{gs'(T24)}$ 。

$$V_{gs'(T24)} = V_{gs(T24)} - V_{th(T24)} \quad \text{公式9}$$

这里, 第四薄膜晶体管  $T_{24}$  的栅-源电压是第四薄膜晶体管  $T_{24}$  的栅压和偏置电压  $V_{dd}$  之间的差值。该栅-源电压由下列公式10表示。

$$V_{gs(T24)} = V_{g(T24)} - V_{dd} \quad \text{公式10}$$

这里, 第四薄膜晶体管  $T_{24}$  的栅压是数据电压和第三薄膜晶体管  $T_{23}$  的阈值电压之间的差值, 它由下列公式11表示。

$$V_{g(T24)} = V_{data} + V_{th(T23)} \quad \text{公式11}$$

这里, 由于第三和第四薄膜晶体管  $T_3$ 、 $T_4$  的性能彼此基本上相同, 因此如以下那样, 第三薄膜晶体管  $T_{23}$  的阈值电压  $V_{th}$  基本上等于第四薄膜晶体管  $T_{24}$  的阈值电压  $V_{th}$ 。

$$V_{th(T23)} = V_{th(T24)} \quad \text{公式12}$$

因此, 从公式9至12, 获得第四薄膜晶体管  $T_{24}$  的有效栅-源电压, 如下列公式13那样。

$$V_{gs'(T24)} = V_{data} - V_{dd} \quad \text{公式13}$$

如公式13所表示, 决定流过第四薄膜晶体管  $T_{24}$  的电流强度的有效栅-源电压  $V_{gs'(T24)}$  是通过数据线  $D_p$  施加的数据电压  $V_{data}$  和通过外部电源线施加的偏压  $V_{dd}$  之间的电压差。由此, 在所有像素驱动单元中各自布置的第四薄膜晶体管  $T_{24}$  的每一个的有效栅-源电压  $V_{gs'(T24)}$  仅取决于通过数据线  $D_p$  施加

的数据电压  $V_{data}$  和通过外部电源线施加的偏压  $V_{dd}$  的强度。但是，栅-源电压  $V_{gs'}(T_{24})$  与第四薄膜晶体管  $T_{24}$  的阈值电压  $V_{th}$  无关。

在该实施例中，像素驱动单元就其变化的性能均衡第四薄膜晶体管  $T_4$  的驱动操作，以便像素驱动单元中的第四薄膜晶体管  $T_4$  的阈值电压  $V_{th}$  可以不同于另一个像素驱动单元中的其它第四薄膜晶体管的阈值电压  $V_{th}$ 。利用这种均衡，响应与第四薄膜晶体管  $T_4$  的阈值电压无关的相同数据信号，提供相同的电流给OLED二极管，即使在驱动晶体管（即第四薄膜晶体管  $T_{24}$ ）在不同的像素驱动单元具有不同的阈值电压。假定本发明的像素驱动单元具有其性能彼此相似或基本相同的第三和第四薄膜晶体管。

在根据本发明用于OLED装置的像素驱动单元中使用的薄膜晶体管每一个具有多层结构，包括半导体层、绝缘层、保护层以及电极层。半导体层包括非晶硅或多晶硅。绝缘层包括氮化硅 ( $SiN_x$ )、氧化硅 ( $SiO_2$ )、氧化铝 ( $Al_2O_2$ ) 以及氧化钽 ( $TaO_x$ )。保护层包括透明有机绝缘材料或绝缘材料。电极层包括导电金属例如铝、铬以及钼。通过使用淀积设备如溅射装置和化学汽相淀积装置制备多层形成薄膜。然后，薄膜经受光刻工艺以形成用于OLED装置的像素驱动单元。

多层中，半导体层用作导电沟道，电子通过其移动，电极层包括源电极、漏电极以及栅电极。源电极施加电压信号到半导体层，传送到半导体层的电压信号通过漏电极输出。栅电极是用于控制从源电极流到漏电极的电流的装置（例如，开关）。

因此，具有这种结构的薄膜晶体管可以用作有源矩阵型OLED装置中的开关器件。有源矩阵型OLED装置的每个薄膜晶体管具有半导体层，半导体层由包括硒化镉 ( $CdSe$ )、含氢非晶硅 ( $a-Si:H$ ) 或多晶硅 ( $poly-Si$ ) 的材料制成。

非晶硅可以在低温下用简单的工艺处理，以便它用于大规模装置，例如太阳能电池。此外，可以在约  $350^{\circ}C$  的最高温度的低温处理系统中进行使用非晶硅的半导体制造工艺，以便在使用非晶硅的情况下可以容易地制造半导体器件。但是，非晶硅中的电子以很低的速度移动，由此使薄膜晶体管的开关性能退化。此外，用薄膜晶体管难以集成以高速控制薄膜晶体管的驱动电路。相反，具有包括多晶硅半导体层的薄膜晶体管适于有源矩阵型OLED装置。

尽管具有包括多晶硅半导体层的薄膜晶体管需要额外的工艺，但是用作在有源矩阵型OLED装置中提供的开关器件的多晶硅薄膜晶体管比非晶硅薄膜晶体管具有更快的响应速度。此外，多晶硅薄膜晶体管与非晶硅薄膜晶体管相比较具有优越的场效应迁移率。场效应迁移率决定薄膜晶体管的开关速度。多晶硅薄膜晶体管的开关速度显著地快于非晶硅薄膜晶体管的开关速度。

这是因为多晶硅由各种颗粒构成且与非晶硅比较具有低的缺陷。因此，多晶硅可以用于具有大屏幕的下一代OLED装置的开关器件，同时允许驱动电路与薄膜晶体管集成。可以通过固相晶化( SPC )工艺、金属诱导晶化( MIC )工艺或使用激光器的准分子激光退火工艺制造多晶硅薄膜晶体管，在固相晶化( SPC )工艺中非晶硅在高温下晶化，在金属诱导晶化( MIC )工艺中对非晶硅上淀积的金属加热。准分子激光退火工艺可以在低温下进行，使用便宜的玻璃基板，因此它可以节省制造成本。此外，通过准分子激光退火工艺制造的薄膜晶体管具有高迁移率的信号，以便提高半导体器件的工作性能。

下面，参考附图描述通过使用激光器使非晶硅薄膜晶体管晶化制造多晶硅薄膜晶体管的方法。

图13A和13B是说明根据本发明的示例性实施例制造的两个薄膜晶体管的示意图。两个薄膜晶体管是本发明(参考图3-11)的像素驱动单元中的第三和第四薄膜晶体管T<sub>3</sub> (或T<sub>23</sub>)、T<sub>4</sub> (或T<sub>24</sub>)。如上所述，在像素驱动单元中的第三和第四薄膜晶体管具有彼此类似或基本上相同的性能。根据制造两个薄膜晶体管的方法，通过使用激光器扫描使非晶硅薄膜晶体管晶化形成多晶硅薄膜晶体管，第三和第四薄膜晶体管T<sub>3</sub>和T<sub>4</sub>形成在同一平面中。

参考图13A，在玻璃基板的同一平面上形成第三和第四非晶硅薄膜晶体管T<sub>3</sub>和T<sub>4</sub>。彼此平行地形成第三和第四非晶硅薄膜晶体管T<sub>3</sub>和T<sub>4</sub>的栅电极G，以及形成在基本上垂直于激光器扫描方向上同一直线(即，定位在同一直线)布置的第三和第四非晶硅-薄膜晶体管T<sub>3</sub>和T<sub>4</sub>的源极和漏极S、D，激光器扫描方向基本上平行于栅电极G。然后，非晶硅薄膜晶体管T<sub>3</sub>、T<sub>4</sub>经受激光器扫描以被晶化和转变为多晶硅薄膜晶体管。

图13B是用于描述根据本发明的另一个实施例的制造第三和第四薄膜晶体管T<sub>3</sub>和T<sub>4</sub>的方法的示意图。在玻璃基板的同一平面上形成第三和第四非晶硅薄膜晶体管T<sub>3</sub>和T<sub>4</sub>。然后，在同一直线方向上形成第三和第四非晶硅薄膜

晶体管T<sub>3</sub>和T<sub>4</sub>栅电极G，在基本上平行于激光器扫描方向上形成第三和第四非晶硅-薄膜晶体管T<sub>3</sub>、T<sub>4</sub>的源极和漏电极S、D。在基本上垂直于激光器扫描方向的同一直线方向上形成栅电极G。一旦经受激光扫描，非晶硅薄膜晶体管被晶化并转变为多晶硅薄膜晶体管。

当通过激光退火工艺晶化非晶硅薄膜晶体管时，准备用于在玻璃基板上形成激光束图形的掩模和用于通过变焦拉远（zoom-out）掩模图形将掩模图形曝光到玻璃基板上的变焦透镜。更详细地讲，调整激光束以具有均匀分布，确定准备通过掩模待形成在玻璃基板上的激光束图形。例如，使用光源以从其尖端产生线光束。在此情况下，也使用线形掩模。在其他方法中，在玻璃基板和光源之间可以使用除线形掩模外的其它掩模形成具体图形。

然后，通过变焦拉远透镜（zoom-out lens）调整激光束以具有选择的束宽。在只使用线形掩模的情况下，束宽处于几毫米至几厘米的范围，长度从几厘米至几十厘米（或高达约2米）。在使用除线形掩模之外的其它掩模的情况下，束宽处于几微米至几毫米的范围。通过辐射激光束到玻璃基板上，同时在X-Y面移动玻璃基板或激光束晶化非晶硅薄膜晶体管，以便使非晶硅薄膜晶体管变为多晶硅薄膜晶体管。

图14是图3中OLED装置的像素驱动单元的平面图。图15和16分别是沿图14中的A-A'线和B-B'线的像素驱动单元的剖面图。如图15和16所示，以多层形式形成像素驱动单元，如包括玻璃、石英和/或蓝宝石的绝缘基板10、阻挡层20、栅绝缘层30、层间介质层40以及钝化层50。

参考图14至16，通过等离子体增强化学气相沉积工艺，以约2000Å的厚度在玻璃基板20上沉积氧化硅，在玻璃基板20上形成阻挡层20，在阻挡层20上形成五个薄膜晶体管T<sub>1</sub>-T<sub>5</sub>，一个存储电容器C以及五个布线G<sub>n-1</sub>、G<sub>n</sub>、DL、Vdd、V<sub>ref</sub>。提供阻挡层20以防止当晶化非晶硅层以形成多晶硅层时的热损失。

一个像素驱动单元由在第一方向延伸的第一和第二栅极线G<sub>n-1</sub>、G<sub>n</sub>，在基本上垂直于第一方向的第二方向延伸的数据线DL以及在第二方向延伸的电源线Vdd定义。基准电压线V<sub>ref</sub>在第一方向延伸且布置在第一和第二栅极线G<sub>n-1</sub>、G<sub>n</sub>之间。

更详细地讲，第一栅极线G<sub>n-1</sub>导通/截止前一列中的像素驱动单元的第一薄膜晶体管T<sub>1</sub>，以便通过数据线DL提供初始数据信号和灰阶数据信号。此外，第一栅极线G<sub>n-1</sub>使在当前列的像素驱动单元的第二和第五薄膜晶体管T<sub>2</sub>、T<sub>5</sub>

导通/截止。

第二栅极线  $G_n$  使当前列中的像素驱动单元的第一薄膜晶体管  $T_1$  导通/截止以执行开关功能，以便通过数据线  $DL$  提供初始数据信号和灰阶数据信号到像素驱动单元。此外，第二栅极线  $G_n$  使在下一列中的像素驱动单元的第二和第五薄膜晶体管  $T_2$ 、 $T_5$  导通/截止。通过电源线  $V_{dd}$ ，最大值的显示信号以直流形式恒定地施加到像素驱动单元。通过基准电压线，基准电压  $V_{ref}$  施加到第二薄膜晶体管  $T_2$ 。

参考图14，第一薄膜晶体管  $T_1$  包括布置在邻近第二栅极线  $G_n$  和数据线  $DL$  之间的交叉点区域的第一有源图形 110，从第二栅极线  $G_n$  延伸并通过上述第一有源图形 110 的栅电极 112，从数据线  $DL$  延伸并与定位在栅电极 112 的一侧的第一有源图形 110 接触的源电极 114，以及与定位在栅电极 112 的另一侧的与第一有源图形 110 接触的第一漏电极 116。第一薄膜晶体管  $T_1$  的栅电极 112 和源电极 114 分别连接到第二栅极线  $G_n$  和数据线  $DL$ 。

第二薄膜晶体管  $T_2$  包括第二有源图形 120，从第一栅极线  $G_{n-1}$  延伸并穿过上述第二有源图形 120 的栅电极 122，从基准电压线  $V_{ref}$  延伸并与定位在栅电极 122 的一侧的第二有源图形 120 接触的源电极 124，以及与定位在栅电极 122 的另一侧的第二有源图形 120 接触的漏电极 126。

第三薄膜晶体管  $T_3$  包括第一有源图形 110，从金属线  $G_M$  延伸并穿过上述第一有源图形 110 的栅电极 132，金属线  $G_M$  是形成第一栅极线  $G_{n-1}$  时形成的，从基准电压线  $V_{ref}$  延伸并与定位在栅电极 132 的一侧的第一有源图形 110 接触的源电极 134，以及与定位在栅电极 132 的另一侧的第一有源图形 110 接触的漏电极 136。

第四薄膜晶体管  $T_4$  包括第三有源图形 140、从金属极线  $G_M$  延伸并穿过上述第三有源图形 140 的栅电极 142、从基准电压线  $V_{ref}$  延伸并与定位在栅电极 142 的一侧的第三有源图形 140 接触的源电极 144，以及与定位在栅电极 142 的另一侧的第三有源图形 140 接触的漏电极 146。

第五薄膜晶体管  $T_5$  包括第四有源图形 150、从第一栅极线  $G_{n-1}$  延伸并穿过上述第四有源图形 150 的栅电极 152、从第四薄膜晶体管  $T_4$  的漏电极 147 延伸并与定位在栅电极 152 的一侧的第四有源图形 150 接触的源电极 154、以及与定位在栅电极 152 的另一侧的第四有源图形 150 接触并且与 OLED 装置的阳极接触的漏电极 156。

在该实施例中，第一和第二薄膜晶体管T<sub>1</sub>、T<sub>2</sub>是N型薄膜晶体管，第三至第五薄膜晶体管T<sub>3</sub>-T<sub>5</sub>是P型薄膜晶体管。存储电容器Cst是由形成第一栅极线时形成的金属线G<sub>M</sub>和在金属线GM上形成的电源线Vdd定义的。存储电容器Cst恒定地保持数据电压一帧周期。

在形成五个薄膜晶体管T<sub>1</sub>-T<sub>5</sub>、存储电容器Cst以及五个布线G<sub>n-1</sub>、G<sub>n</sub>、DL、Vdd、V<sub>ref</sub>之后，在像素驱动单元的顶部形成ITO阳电极并通过开口露出。此外，在像素驱动单元的有机绝缘壁上顺序地形成空穴转移层、发光层以及电子转移层，以及在其上形成阴极。在该实施例中，第三和第四薄膜晶体管布置在平行于数据线的方向上，以便当通过激光扫描工艺晶化非晶硅薄膜晶体管时，第三和第四薄膜晶体管的性能变得类似或彼此基本上相同。

如上所述，根据本发明的像素驱动单元均衡OLED装置的各个像素驱动单元中的驱动薄膜晶体管的阈值电压。驱动薄膜晶体管的有效栅-源电压仅取决于数据电压和外部施加的偏压，与驱动薄膜晶体管的阈值电压无关，以便每个OLED二极管响应同样的数据信号接收具有相同强度的驱动信号。

尽管已参考其示例性实施例对本发明进行了描述，但是本领域的技术人员应当明白在不脱离本发明的范围条件下，可以进行各种改变和用等效元件替代。此外，对于本发明的技术，在不脱离其实质范围的情况下，可以进行多种改进以适应具体情况或材料。因此，本发明不限于作为实施本发明的最佳方式公开的具体实施例，而是将包括落入所附权利要求书的范围内的所有实施例。

图 1

图 2

图 3

图 4

图 5A

图 5B

图 6

图 7

图 8

图 9

图 10

图 11

图 12

图 13A

图 13B

图 15

图 16

|                |                                                                                                              |         |            |

|----------------|--------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 有机发光显示装置及其制造方法                                                                                               |         |            |

| 公开(公告)号        | <a href="#">CN100354908C</a>                                                                                 | 公开(公告)日 | 2007-12-12 |

| 申请号            | CN03165011.2                                                                                                 | 申请日     | 2003-09-25 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                     |         |            |

| 申请(专利权)人(译)    | 三星电子株式会社                                                                                                     |         |            |

| 当前申请(专利权)人(译)  | 三星电子株式会社                                                                                                     |         |            |

| [标]发明人         | 崔俊厚<br>蔡钟哲<br>崔凡洛                                                                                            |         |            |

| 发明人            | 崔俊厚<br>蔡钟哲<br>崔凡洛                                                                                            |         |            |

| IPC分类号         | G09G3/22 G09G3/20 H01L33/00 H01L51/50 G09G3/30 G09G3/32 H01L21/77 H05B33/00                                  |         |            |

| CPC分类号         | G09G2300/0842 G09G2300/0861 G09G2320/043 G09G3/3233 G09G2300/0417 G09G2300/0819<br>H01L27/1296 G09G2320/0223 |         |            |

| 代理人(译)         | 侯宇                                                                                                           |         |            |

| 审查员(译)         | 王一娟                                                                                                          |         |            |

| 优先权            | 1020020058210 2002-09-25 KR                                                                                  |         |            |

| 其他公开文献         | CN1510652A                                                                                                   |         |            |

| 外部链接           | <a href="#">Espacenet</a> <a href="#">Sipo</a>                                                               |         |            |

#### 摘要(译)

一种有机发光显示设备，包括：在提供驱动信号到有机发光二极管的顺序进程中分别传送前一级和当前栅极信号的栅极线；传送在图像显示装置上显示图像的数据信号的数据线；响应当前栅极信号传送来自数据线的数据信号的导电通路的第一开关晶体管；响应前一级栅极信号传送外部提供的基准信号的导电通路的第二开关晶体管；响应第二开关晶体管的状态传送从第一开关晶体管提供的数据信号的导电通路的第三开关晶体管；以及响应来自第二开关晶体管的基准信号和第三开关晶体管的数据信号之一接收偏压和产生到有机发光二极管的驱动信号的导电通路的第四开关晶体管。第三和第四开关晶体管具有彼此基本上相同的开关性能。