(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2016-0090693

(43) 공개일자 2016년08월01일

- (51) 국제특허분류(Int. Cl.)

**G02F 1/1339** (2006.01) **G02F 1/1333** (2006.01)

**G02F 1/1335** (2006.01)

- (52) CPC특허분류

**G02F 1/1339** (2013.01)

**G02F 1/133514** (2013.01)

- (21) 출원번호 10-2015-0010796

(22) 출원일자 2015년01월22일

심사청구일자 없음

- (71) 출원인

**엘지디스플레이 주식회사**

서울특별시 영등포구 여의대로 128(여의도동)

- (72) 발명자

**장연희**

경기도 파주시 월롱면 엘지로 245, 105동 308호

(파주LCD지방산업단지 정다운마을)

- (74) 대리인

**박장원**

전체 청구항 수 : 총 7 항

(54) 발명의 명칭 **액정표시장치**

### (57) 요 약

본 발명의 액정표시장치는 고화질, 고성능 디스플레이를 위한 컬러필터-온-박막 트랜지스터(Color Filter on TFT; COT) 구조의 액정표시장치에 있어, 실 라인(seal line) 좌우에 여분의 실이 충진되는 홀(hole)을 형성하여 오버레이(overlay) 이동 및 퍼짐 폭 증가 등 공정 변동에 대처하는 것을 특징으로 한다.

이에 따라 실 라인의 선 폭 및 공정마진 축소를 통해 액정표시장치의 내로우 베젤(narrow bezel)을 구현할 수 있는 효과를 제공한다.

**대 표 도** - 도3

(52) CPC특허분류

G02F 2001/133357 (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

제 1 기판 위의 평탄화층;

상기 평탄화층 위의 실 라인;

상기 실 라인을 통해 상기 제 1 기판과 대향하여 합착되는 제 2 기판; 및

상기 실 라인 좌우의 상기 평탄화층에 형성된 홀(hole)을 포함하는 액정표시장치.

#### 청구항 2

제 1 항에 있어서, 상기 홀은 상기 실 라인을 따라 배치되는 액정표시장치.

#### 청구항 3

제 2 항에 있어서, 상기 홀은 상기 실 라인을 따라 액정패널의 일측이나 양측에 배치되는 액정표시장치.

#### 청구항 4

제 1 항에 있어서, 상기 평탄화층 하부에 위치하는 안료 층을 추가로 포함하는 액정표시장치.

#### 청구항 5

제 4 항에 있어서, 상기 제 1 기판의 화소부에 구성되는 서브-컬러필터들을 추가로 포함하며, 상기 안료 층은 상기 서브-컬러필터들을 구성하는 컬러안료로 이루어진 액정표시장치.

#### 청구항 6

제 1 항에 있어서, 상기 홀은 라인 형태나 일정하게 반복되는 패턴 형태를 가지는 액정표시장치.

#### 청구항 7

제 1 항에 있어서, 상기 홀 내에 상기 실 라인을 구성하는 여분의 실이 충진되는 액정표시장치.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 액정표시장치에 관한 것으로, 보다 상세하게는 어레이 기판에 박막 트랜지스터(Thin Film Transistor; TFT)와 함께 컬러필터를 형성하도록 한 컬러필터-온-박막 트랜지스터(Color Filter on TFT; COT) 구조의 액정표시장치에 관한 것이다.

### 배경 기술

[0002] 일반적으로 액정표시장치는 매트릭스(matrix) 형태로 배열된 화소들에 화상정보에 따른 데이터신호를 개별적으로 공급하여, 그 화소들의 광투과율을 조절함으로써 원하는 화상을 표시할 수 있도록 한 표시장치이다.

[0003] 따라서, 액정표시장치에는 화소들이 매트릭스 형태로 배열되는 액정패널과 화소들을 구동하기 위한 구동부가 구비된다.

[0004] 액정패널은 서로 대향하여 균일한 셀 갭(cell gap)이 유지되도록 합착된 어레이(array) 기판과 컬러필터(color filter) 기판 및 어레이 기판과 컬러필터 기판 사이의 셀 갭 내에 형성된 액정층(liquid crystal layer)으로 구성된다.

[0005] 이때, 어레이 기판과 컬러필터 기판이 합착된 액정패널에는 공통전극과 화소전극이 형성되어 액정층에 전계를

인가한다.

- [0006] 따라서, 공통전극에 전압이 인가된 상태에서 화소전극에 인가되는 데이터신호의 전압을 제어하게 되면, 액정층의 액정은 공통전극과 화소전극 사이의 전계에 따라 유전 이방성에 의해 회전함으로써 화소별로 빛을 투과시키거나 차단시켜 문자나 화상을 표시하게 된다.

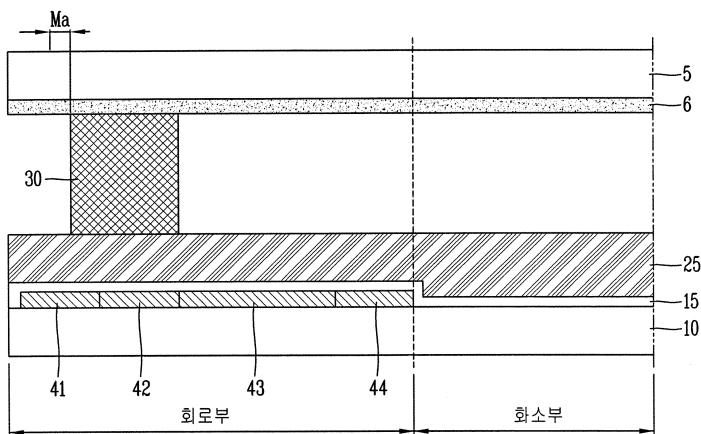

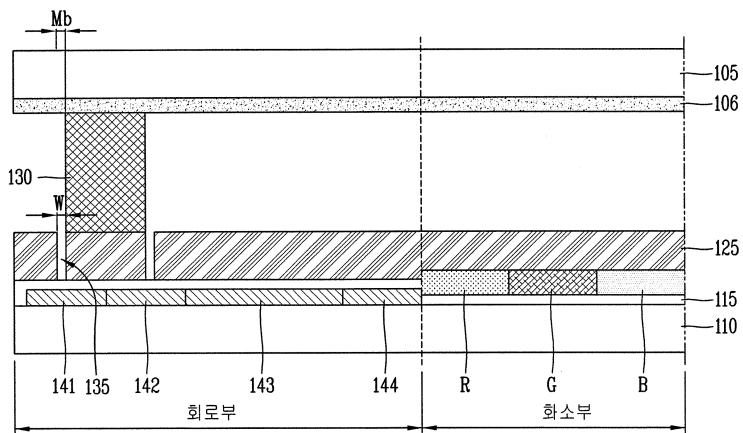

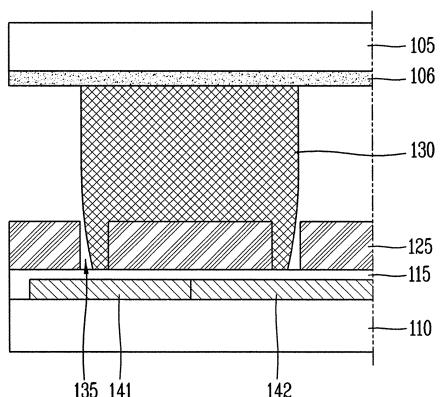

- [0007] 도 1은 일반적인 액정표시장치의 단면 구조를 개략적으로 보여주는 도면으로서, 회로부와 화소부 일부를 예로 들어 보여주고 있다.

- [0008] 도 1을 참조하면, 일반적인 액정표시장치는 컬러필터 기판(5)과 어레이 기판(10) 및 실 라인(30)에 의해 합착된 상태에서 컬러필터 기판(5)과 어레이 기판(10) 사이에 형성된 액정층(미도시)으로 구성된다.

- [0009] 도시하지 않았지만, 컬러필터 기판(5)에는 컬러필터 어레이가 형성되며, 컬러필터 어레이에는 블랙매트릭스(6)와 컬러필터 및 오버코트층을 포함한다.

- [0010] 또한, 화소부의 어레이 기판(10)에는 종횡으로 배열되어 화소영역을 정의하는 게이트라인과 데이터라인이 형성되어 있으며, 게이트라인과 데이터라인의 교차영역에는 스위칭소자인 박막 트랜지스터가 형성되어 있다.

- [0011] 이때, 인-플레인 스위칭(In Plane Switching; IPS) 모드의 경우 화소영역 내에는 수평전계를 형성하기 위한 다수의 화소전극과 공통전극이 교대로 형성된다.

- [0012] 그리고, 박막 트랜지스터는 게이트라인에 연결된 게이트전극, 데이터라인에 연결된 소오스전극 및 화소전극에 연결된 드레인전극으로 구성된다. 또한, 박막 트랜지스터는 이러한 구성요소들 사이의 절연을 위한 다수의 절연층(15) 및 게이트전극에 공급되는 게이트전압에 의해 소오스전극과 드레인전극 사이에 전도채널을 형성하는 액티브층을 포함한다.

- [0013] 이와 같이 구성되는 일반적인 액정표시장치는 액정패널의 화상구현에 필요한 각종 신호를 공급하는 구동회로부(미도시)를 구비한다.

- [0014] 구동회로부는 타이밍 컨트롤러(timing controller)와 게이트 드라이버(gate driver) 및 데이터 드라이버(data driver)를 포함한다.

- [0015] 최근 고해상도 모델의 베젤(bezel) 축소 및 비용 저감의 요구가 증대됨에 따라 게이트 드라이버를 액정패널에 내장한 게이트-인-패널(Gate In Panel; GIP) 방식의 액정표시장치가 개발되고 있다.

- [0016] 이 경우 회로부의 어레이 기판(10)에는 접지 배선(41)과 클럭신호 배선(42) 및 공통 배선(44) 이외에 GIP 회로(43)가 위치한다.

- [0017] 이때, 실 라인(30)은 접지 배선(41)과 클럭신호 배선(42) 위의 포토 아크릴 층(25)으로 평탄화된 어레이 기판(10) 위에 도포된다.

- [0018] 실 라인(30)의 선 폭을 1mm로 가정할 경우 오버레이(overlay) 및 퍼짐 폭을 고려한 공정마진(Ma)은  $\pm 3\text{a}$ 에 해당한다. 즉, 오버레이가 이동(shift)되거나 선 폭이 증가할 경우 등 공정 변동에도 안정적인 설계를 위해서 실 라인(30)의 선 폭 이외에 공정마진(Ma) 영역이 확보되어야 한다.

- [0019] 따라서, GIP 회로(43) 영역을 축소하더라도 내로우 베젤을 구현하는데 한계가 있으며, 합착 시 놀림으로 실이 좌우로 퍼지게 될 경우 캡 불량을 유발할 수 있는 단점이 있다.

## 발명의 내용

### 해결하려는 과제

- [0020] 본 발명은 상기한 문제를 해결하기 위한 것으로, 어레이 기판에 박막 트랜지스터와 함께 컬러필터를 형성하도록 한 컬러필터-온-박막 트랜지스터(Color Filter on TFT; COT) 구조의 액정표시장치를 제공하는데 목적이 있다.

- [0021] 본 발명의 다른 목적은 COT 구조의 액정표시장치에 있어, 내로우 베젤을 구현할 수 있는 액정표시장치를 제공하는데 목적이 있다.

- [0022] 기타, 본 발명의 다른 목적 및 특징들은 후술되는 발명의 구성 및 특허청구범위에서 설명될 것이다.

### 과제의 해결 수단

- [0023] 상기한 목적을 달성하기 위하여, 본 발명의 일 실시예에 따른 액정표시장치는 제 1 기판 위의 평탄화층, 평탄화층 위의 실 라인, 실 라인을 통해 제 1 기판과 대향하여 합착되는 제 2 기판 및 실 라인 좌우의 평탄화층에 형성된 홀(hole)을 포함하는 구성될 수 있다.

- [0024] 이때, 홀은 실 라인을 따라 배치될 수 있다.

- [0025] 이때, 홀은 실 라인을 따라 액정패널의 일측이나 양측에 배치될 수 있다.

- [0026] 또한, 본 발명의 일 실시예에 따른 액정표시장치는 평탄화층 하부에 위치하는 안료 층을 추가로 포함할 수 있다.

- [0027] 이때, 본 발명의 일 실시예에 따른 액정표시장치는 제 1 기판의 화소부에 구성되는 서브-컬러필터들을 추가로 포함할 수 있으며, 안료 층은 서브-컬러필터들을 구성하는 컬러안료로 이루어질 수 있다.

- [0028] 홀은 라인 형태나 일정하게 반복되는 패턴 형태를 가질 수 있다.

- [0029] 홀 내에 실 라인을 구성하는 여분의 실이 충진될 수 있다.

### 발명의 효과

- [0030] 상술한 바와 같이, 본 발명의 일 실시예에 따른 액정표시장치는 실 라인 좌우에 여분의 실이 충진되는 홀을 형성함으로써 실 라인의 선 폭 및 공정마진 축소를 통해 액정표시장치의 내로우 베젤을 구현할 수 있는 효과를 제공한다.

- [0031] 또한, 본 발명의 일 실시예에 따른 액정표시장치는 합착 시 놀림에도 실이 홀 내로 흘러내리기 때문에 캡 불량이 방지되는 효과를 제공한다.

### 도면의 간단한 설명

- [0032] 도 1은 일반적인 액정표시장치의 단면 구조를 개략적으로 보여주는 도면.

- 도 2는 본 발명의 제 1 실시예에 따른 액정표시장치의 구조를 개략적으로 보여주는 예시도.

- 도 3은 본 발명의 제 1 실시예에 따른 액정표시장치의 단면 구조를 개략적으로 보여주는 도면.

- 도 4a 및 도 4b는 오버레이 이동에 따른 실 라인의 상태를 예로 들어 보여주는 단면도.

- 도 5a 및 도 5b는 선 폭 증가에 따른 실 라인의 상태를 예로 들어 보여주는 단면도.

- 도 6은 본 발명의 제 2 실시예에 따른 액정표시장치의 단면 구조를 개략적으로 보여주는 도면.

- 도 7은 본 발명의 제 3 실시예에 따른 액정표시장치의 단면 구조를 개략적으로 보여주는 도면.

- 도 8은 본 발명의 제 4 실시예에 따른 액정표시장치의 구조를 개략적으로 보여주는 예시도.

- 도 9는 본 발명의 제 5 실시예에 따른 액정표시장치의 구조를 개략적으로 보여주는 예시도.

### 발명을 실시하기 위한 구체적인 내용

- [0033] 이하, 첨부한 도면을 참조하여 본 발명에 따른 액정표시장치의 바람직한 실시예를 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자가 용이하게 실시할 수 있도록 상세히 설명한다.

- [0034] 본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시예들을 참조하면 명확해질 것이다. 그러나, 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성요소를 지칭한다. 도면에서 층 및 영역들의 크기 및 상대적인 크기는 설명의 명료성을 위해 과장될 수 있다.

- [0035] 소자(element) 또는 층이 다른 소자 또는 "위(on)" 또는 "상(on)"으로 지칭되는 것은 다른 소자 또는 층의 바로 위뿐만 아니라 중간에 다른 층 또는 다른 소자를 개재한 경우를 모두 포함한다. 반면, 소자가 "직접 위(directly on)" 또는 "바로 위"로 지칭되는 것은 중간에 다른 소자 또는 층을 개재하지 않는 것을 나타낸다.

- [0036] 공간적으로 상대적인 용어인 "아래(below, beneath)", "하부(lower)", "위(above)", "상부(upper)" 등은 도면에 도시되어 있는 바와 같이 하나의 소자 또는 구성 요소들과 다른 소자 또는 구성 요소들과의 상관관계를 용이하게 기술하기 위해 사용될 수 있다. 공간적으로 상대적인 용어는 도면에 도시되어 있는 방향에 더하여 사용시 또는 동작시 소자의 서로 다른 방향을 포함하는 용어로 이해되어야 한다. 예를 들면, 도면에 도시되어 있는 소자를 뒤집을 경우, 다른 소자의 "아래(below)" 또는 "아래(beneath)"로 기술된 소자는 다른 소자의 "위(above)"에 놓여질 수 있다. 따라서, 예시적인 용어인 "아래"는 아래와 위의 방향을 모두 포함할 수 있다.

- [0037] 본 명세서에서 사용된 용어는 실시예들을 설명하기 위한 것이며, 따라서 본 발명을 제한하고자 하는 것은 아니다. 본 명세서에서, 단수형은 문구에서 특별히 언급하지 않는 한 복수형도 포함한다. 명세서에서 사용되는 "포함한다(comprise)" 및/또는 "포함하는(comprising)"은 언급된 구성요소, 단계, 동작 및/또는 소자는 하나 이상의 다른 구성요소, 단계, 동작 및/또는 소자의 존재 또는 추가를 배제하지 않는다.

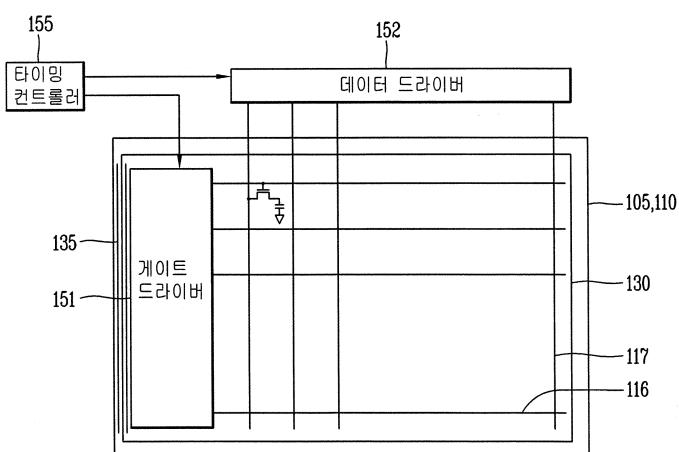

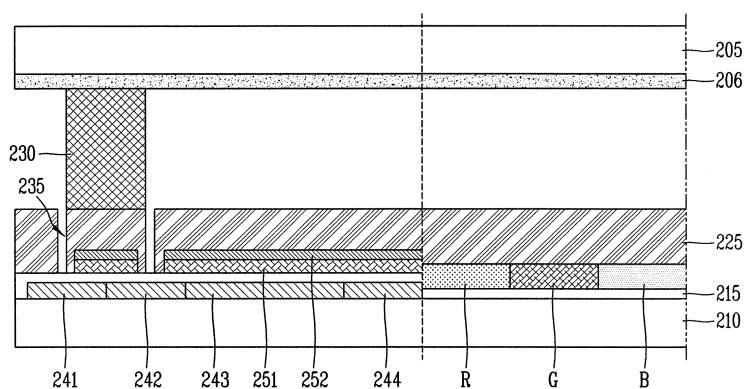

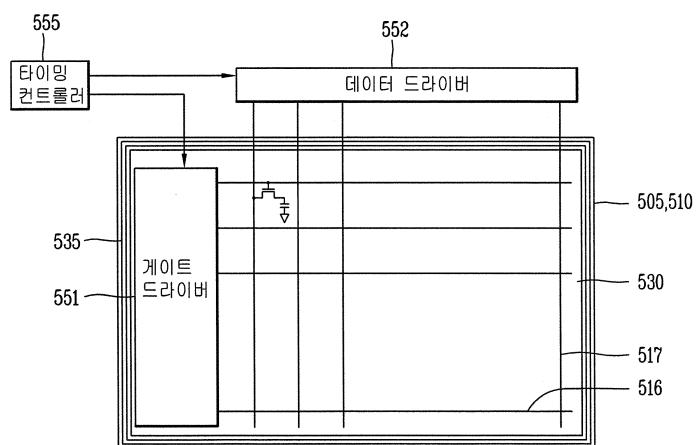

- [0038] 도 2는 본 발명의 제 1 실시예에 따른 액정표시장치의 구조를 개략적으로 보여주는 예시도이다.

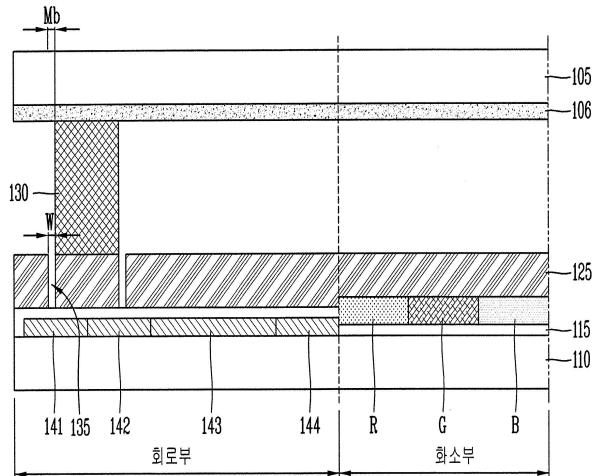

- [0039] 그리고, 도 3은 본 발명의 제 1 실시예에 따른 액정표시장치의 단면 구조를 개략적으로 보여주는 도면으로서, 회로부와 화소부 일부를 예로 들어 보여주고 있다.

- [0040] 이때, 도 2 및 도 3에 도시된 본 발명의 제 1 실시예에 따른 액정표시장치는 어레이 기판 내에 게이트 드라이버를 직접 실장시킨 GIP 방식의 액정표시장치를 예로 들고 있다. 다만, 본 발명이 GIP 방식의 액정표시장치에 한정되는 것은 아니다.

- [0041] 본 발명의 제 1 실시예에 따른 액정표시장치는 액정패널 및 액정패널의 화상구현에 필요한 각종 신호를 공급하는 구동회로부로 구성될 수 있다.

- [0042] 도 2 및 도 3을 참조하면, 액정패널은 제 1 기판(110)과 제 2 기판(105) 및 실 라인(130)에 의해 합착된 상태에서 제 1 기판(110)과 제 2 기판(105) 사이에 형성된 액정층(미도시)으로 구성될 수 있다.

- [0043] 이때, 제 1 기판(110)과 제 2 기판(105)의 내면에는 각각 어레이요소와 컬러필터요소가 갖추어진다.

- [0044] 어레이 기판이라 불리는 제 1 기판(110) 내면에는 어레이요소로서 수평방향의 게이트라인(116)과 수직방향의 데이터라인(117)이 종횡으로 교차해서 매트릭스 형태의 화소를 정의한다.

- [0045] 게이트라인(116)과 데이터라인(117)의 교차점에는 박막 트랜지스터가 구비되어 각 화소에 형성된 화소전극(미도시)과 일대일로 대응하여 연결된다.

- [0046] 도시하지 않았지만, 박막 트랜지스터는 게이트라인(116)에 연결된 게이트전극, 데이터라인(117)에 연결된 소오스전극 및 화소전극에 전기적으로 접속된 드레인전극으로 구성된다. 또한, 박막 트랜지스터는 이러한 구성요소들 사이의 절연을 위한 다수의 절연층(115) 및 게이트전극에 공급되는 게이트전압에 의해 소오스전극과 드레인전극 사이에 전도채널을 형성하는 액티브층을 포함한다.

- [0047] 이렇게 구성된 본 발명의 제 1 실시예에 따른 제 1 기판(110)은 박막 트랜지스터 위에 컬러필터가 형성된 컬러필터-온-박막 트랜지스터(Color Filter on TFT; COT) 구조로 이루어질 수 있다. 컬러필터는 컬러필터요소로서 특정 파장대의 빛만을 선택적으로 투과하는, 예를 들어 적, 녹 및 청색의 서브-컬러필터(R, G, B)들로 이루어질 수 있다.

- [0048] 그리고, 제 2 기판(105) 내면에는 블랙매트릭스(106)와 액정층을 사이에 두고 화소전극과 대향하는 공통전극(미도시) 등의 컬러필터요소가 구비된다.

- [0049] 블랙매트릭스(106)는 블랙 칼럼스페이서(Black Column Spacer; BCS)로 대체될 수 있다.

- [0050] 이때, 액정분자를 기판에 대해 수평한 방향으로 구동시켜 시야각을 향상시킨 인-플레인 스위칭(In Plane Switching; IPS) 모드의 경우 공통전극은 화소전극과 함께 제 1 기판(110) 내에 형성된다. 다만, 본 발명이 이에 한정되는 것은 아니며, 본 발명은 수직배향(Vertical Alignment; VA) 모드, 프린지-필드 스위칭(Fringe Field Switching; FFS) 모드, Super-IPS 모드, reverse TN IPS 모드의 액정표시장치에도 적용될 수 있다.

- [0051] 다음으로, 구동회로부는 타이밍 컨트롤러(155)와 게이트 드라이버(151) 및 데이터 드라이버(152)를 포함한다.

- [0052] 구동회로부는 그 외에도 외부구동시스템과 타이밍 컨트롤러(155)를 중계하는 인터페이스, 데이터 드라이버(152)에서 사용되는 기준전압을 생성하는 기준전압생성부, 구동회로부의 각 구성요소들에 대한 동작전원과 액정패널의 공통전극으로 전달되는 공통전압을 공급하는 전원전압생성부가 구비된다.

- [0053] 이에 따라 외부구동시스템으로부터 전달되는 영상 및 제어신호는 인터페이스에 의해 타이밍 컨트롤러(155)로 중계된다. 이때, 영상신호에는 액정패널의 화소를 통해 표시될 화상에 대한 회도정보가 담겨있고, 제어 신호에는 프레임 화면에 대한 시작 또는 끝을 표시하는 수직동기신호(Vertical Synchronous Signal; Vsync), 수평화소 열에 대한 시작 또는 끝을 표시하는 수평동기신호(Horizontal Synchronous Signal; Hsync), 수평화소 열 내의 유효 데이터 구간을 표시하는 DE(Data Enable), 유효 데이터의 주기를 표시하는 데이터 클럭(Data Clock; DCLK) 등이 담겨있다.

- [0054] 그리고, 이를 영상 및 제어신호는 타이밍 컨트롤러(155)에 의해 적절한 형태로 변형되어 게이트 드라이버(151) 및 데이터 드라이버(152)에 공급된다. 이로써 게이트 드라이버(151)는 매 프레임 별로 수평화소 열을 순차적으로 인에이블 시키는 게이트신호를 생성하여 게이트라인(116)에 스캔 전달한다. 또한, 데이터 드라이버(152)는 게이트신호에 의해 오픈(open)된 화소를 충전시키는 데이터신호를 생성해서 각 데이터라인(117)으로 전달한다.

- [0055] 따라서, 본 발명의 제 1 실시예에 따른 액정표시장치는 게이트라인(116)의 게이트신호에 의해 각 게이트라인(116)별로 선택된 화소가 오픈되면 데이터라인(117)의 데이터신호가 해당 화소에 전달되고, 이로 인한 화소전극 및 공통전극 사이의 전기장으로 액정이 구동되어 투과율 차이를 구현한다.

- [0056] 이를 위해 타이밍 컨트롤러(155)는 박막 트랜지스터가 온 되는 시간을 지정하는 GSC(Gate Shift Clock), 게이트 드라이버(151)의 출력을 제어하는 GOE(Gate Output Enable), 일 수직신호 중 화면의 시작 라인을 알려주는 GSP(Gate Start Pulse) 등이 내포된 프레임제어신호를 생성해서 게이트 드라이버(151)에 전달한다.

- [0057] 그리고, 데이터를 정렬함과 동시에 각 수평화소열의 데이터를 래치(latch)하는 SSC(Source Sampling Clock), SSC에 의해 래치된 데이터의 전달시점을 지시하는 데이터래치신호인 SOE, 일 수평신호 중 데이터의 시작점을 지시하는 SSP(Source start Pulse), SOE에 의해 동기되는 극성반전신호로서 데이터신호의 극성을 결정하는 정(+) 극성과 부(-)극성 피크를 교대로 나타내는 POL 등이 내포된 화상제어신호를 데이터 드라이버(152)로 전달한다.

- [0058] 본 발명의 제 1 실시예에 따른 액정표시장치는 박막 트랜지스터의 게이트 드라이버(151)의 일부 또는 전부가 액정패널의 제 1 기판(110) 내에 실장된 GIP 방식을 가지는 것을 특징으로 한다. 이에 따라 적어도 게이트 드라이버(151)의 시프트레지스터(shift register)부는 제 1 기판(110) 내에 실장되어 어레이요소 제조공정 중에 함께 제조될 수 있다.

- [0059] 즉, 게이트 드라이버(151)는 셋(set)과 리셋(reset)의 선택적 입력상황에 따라 일정신호를 출력하는 복수개의 플립플롭(Flip-Flop)으로 이루어진 시프트레지스터부, 그리고 이의 출력신호 레벨을 증폭시키는 레벨시프터(level shifter)부로 구분될 수 있다. 통상의 GIP 방식에서는 적어도 시프트레지스터부를 제 1 기판(110)에 실장 시키며, 이 경우 시프트레지스터부는 게이트라인(116)과 일대일 대응하여 연결된 복수개의 시프트레지스터 단위소자가 열을 지어 배치된 시프트레지스터 소자군(群)의 형태를 나타낸다.

- [0060] 그리고, 이와 같이 액정패널 내에 실장되는 게이트 드라이버(151)의 일부 또는 전부는 제 1 기판(110)의 어레이요소에 대한 제조공정 중에 제조될 수 있어 비용 및 공정이 절감된다.

- [0061] 따라서, GIP 방식의 제 1 기판(110)의 회로부에는 다수의 회로 배선들이 형성된다. 일 예로, 이러한 회로 배선들은 접지 배선(141)과 클럭신호 배선(142) 및 공통 배선(144) 이외에 GIP 회로(143)를 포함할 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

- [0062] 이 경우 본 발명의 제 1 실시예에 따른 실 라인(130)은 접지 배선(141)과 클럭신호 배선(142) 위에 평탄화층(125)으로 평탄화된 제 1 기판(110)의 회로부에 형성될 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

- [0063] 일 예로, 평탄화층(125)은 포토 아크릴 층으로 이루어질 수 있다.

- [0064] 본 발명의 제 1 실시예에 따른 실 라인(130)은 액정층을 적하 방식으로 형성하는 경우 액정패널의 가장자리를 둘러싸는 폐곡선의 형태를 가질 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

- [0065] 이때, 본 발명의 제 1 실시예에 따른 액정표시장치는 실 라인(130) 좌우에 홀(135)이 형성되어 있는 것을 특징으로 한다. 이때, 도 2에는 홀(135)이 액정패널의 일측에만 형성된 경우를 예로 들고 있으나, 본 발명이 이에 한정되는 것은 아니다. 액정패널의 다른 일측에 다수의 회로 배선들이 형성되는 경우 액정패널의 다른 일측에도 홀(135)이 형성될 수 있다. 또한, 회로 배선들의 형성 유무에 관련 없이 액정패널의 4면 모두에 홀(135)이 형성될 수도 있다.

- [0066] 이러한 홀(135)은 실 라인(130)이 도포되는 제 1 기판(110)의 최상층, 일 예로 평탄화층(125)에 형성될 수 있으

나, 본 발명이 이에 한정되는 것은 아니다.

[0067] 홀(135)은 여분의 실이 충진될 수 있도록 좁고 긴 형태를 가질 수 있다.

[0068] 또한, 깊은 홀(135)을 형성하기 위해 평탄화층(125) 하부에 안료 층(미도시)을 추가로 형성할 수도 있다.

[0069] 본 발명은 홀(135) 이외에 평탄화층(125)의 일부 깊이만이 제거된 흠 형태를 적용할 수도 있다.

[0070] 이렇게 형성된 홀(135)은 실 라인(130)을 구속함으로써 기준에 비해 실 라인(130)의 선 폭(W)을 감소시킬 수 있다.

[0071] 즉, 실 라인(130)의 좌우에 형성된 홀(135)로 인해 오버레이 이동(overlay shift) 또는 선 폭(W)이 증가하는 경우에도 실 라인(130)이 일정한 영역 내에 구속될 수 있다.

[0072] 또한, 합착 시 놀림으로 실 라인(130)이 좌우로 퍼지게 될 경우에도 여분의 실이 홀(135) 내로 흘러내림으로써 캡 불량을 방지할 수 있다.

[0073] 이와 같은 실 퍼짐 및 선 폭(W)의 제어로 공정마진(Mb)을 대략 기준의  $\pm 3\alpha$ 에서  $\pm \alpha$ 로 축소할 수 있다.

[0074] 이러한 실 라인(130)의 선 폭(W)은 액정패널의 모델과 크기 및 공정조건에 따라 달라질 수 있지만, 대략  $10\mu\text{m} \sim \text{수백}\mu\text{m}$ 로 설계할 수 있다. 또한, 일 예로 실 라인(130)의 선 폭(W)을 공정마진(Mb)과 동일한 크기로 설계할 수도 있다.

[0075] 공정마진(Mb)은 오버레이와 퍼짐 폭을 함께 고려하여 설정할 수 있다.

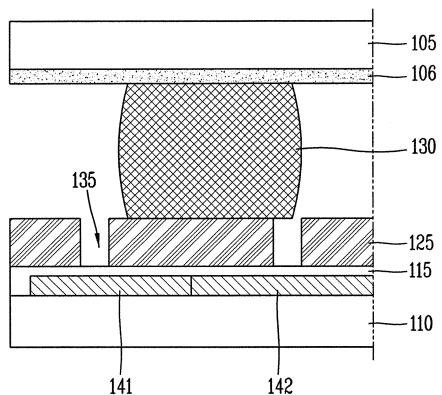

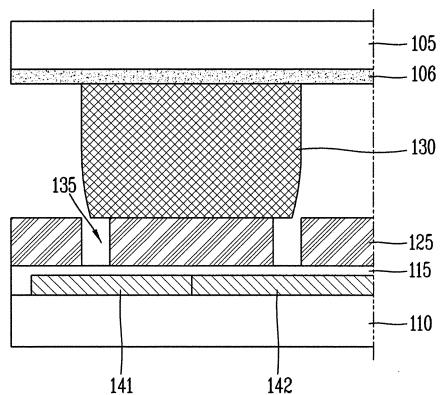

[0076] 도 4a 및 도 4b는 오버레이 이동에 따른 실 라인의 상태를 예로 들어 보여주는 단면도이다.

[0077] 그리고, 도 5a 및 도 5b는 선 폭 증가에 따른 실 라인의 상태를 예로 들어 보여주는 단면도이다.

[0078] 이때, 도 4b 및 도 5b는 도 4a 및 도 5a 각각의 경우에 있어, 합착 놀림 시의 실 라인의 상태를 개략적으로 보여주고 있다.

[0079] 도 4a 및 도 5a를 참조하면, 실 도포 시 오버레이가 이동하거나 실 라인(130)의 선 폭이 증가하여 실 라인(130)이 우측이나 양측으로 벗어나는 경우에도 여분의 실이 우측이나 양측의 홀(135) 내의 공간에 가두어지는 것을 알 수 있다.

[0080] 이 경우 도 4b 및 도 5b를 참조하면, 합착 시 놀림으로 실 라인(130)이 좌우로 퍼지게 될 경우에도 여분의 실이 우측이나 양측의 홀(135) 내로 흘러내림으로써 캡 불량을 방지할 수 있다.

[0081] 한편, 전술한 바와 같이 본 발명은 평탄화층 하부에 안료 층을 추가로 형성함으로써 홀의 깊이를 깊게 할 수도 있는데, 이를 다음의 본 발명의 제 2 실시예를 통해 상세히 설명한다.

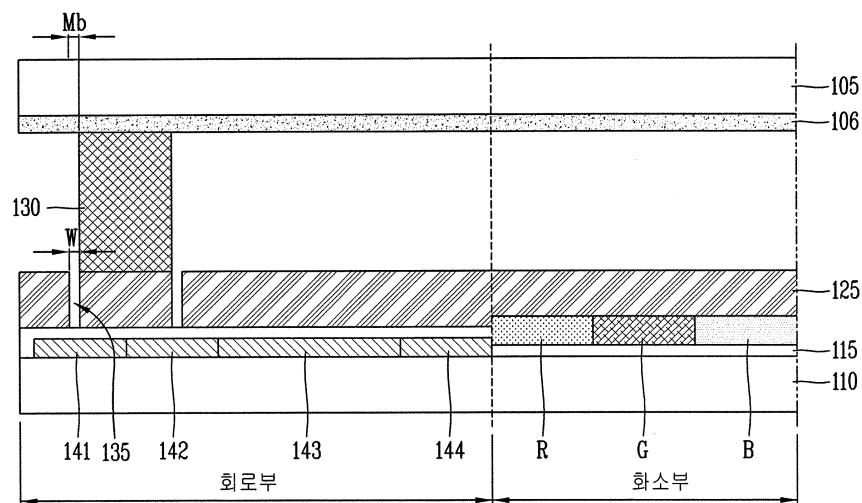

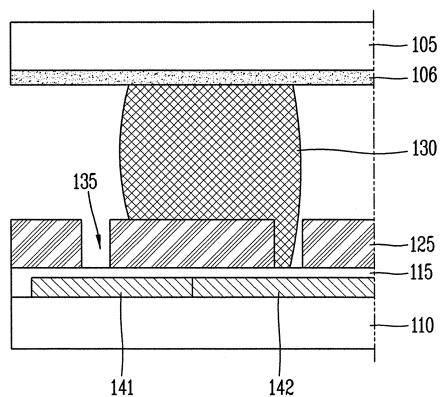

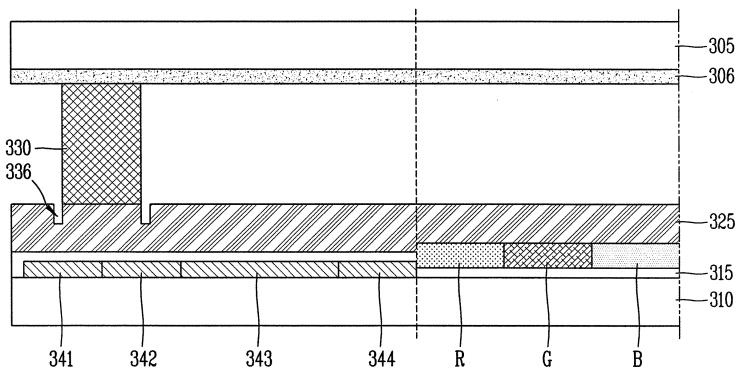

[0082] 도 6은 본 발명의 제 2 실시예에 따른 액정표시장치의 단면 구조를 개략적으로 보여주는 도면이다.

[0083] 도 6을 참조하면, 본 발명의 제 2 실시예에 따른 액정표시장치는 제 1 기판(210)과 제 2 기판(205) 및 실 라인(230)에 의해 합착된 상태에서 제 1 기판(210)과 제 2 기판(205) 사이에 형성된 액정층(미도시)으로 구성될 수 있다.

[0084] 이때, 제 1 기판(210)과 제 2 기판(205)의 내면에는 각각 어레이요소와 컬러필터요소가 갖추어진다.

[0085] 전술한 바와 같이 제 1 기판(210) 내면에는 어레이요소로서 수평방향의 게이트라인(미도시)과 수직방향의 데이터라인(미도시)이 종횡으로 교차해서 매트릭스 형태의 화소를 정의한다.

[0086] 게이트라인과 데이터라인의 교차점에는 박막 트랜지스터가 구비되어 각 화소에 형성된 화소전극(미도시)과 일대일로 대응하여 연결된다.

[0087] 도시하지 않았지만, 박막 트랜지스터는 게이트라인에 연결된 게이트전극, 데이터라인에 연결된 소오스전극 및 화소전극에 전기적으로 접속된 드레인전극으로 구성된다. 또한, 박막 트랜지스터는 이러한 구성요소들 사이의 절연을 위한 다수의 절연층(215) 및 게이트전극에 공급되는 게이트전압에 의해 소오스전극과 드레인전극 사이에 전도채널을 형성하는 액티브층을 포함한다.

[0088] 이렇게 구성된 본 발명의 제 2 실시예에 따른 제 1 기판(210)은 박막 트랜지스터 위에 컬러필터가 형성된 COT 구조로 이루어질 수 있다. 컬러필터는 컬러필터요소로서 특정 파장대의 빛만을 선택적으로 투과하는, 예를 들어

적, 녹 및 청색의 서브-컬러필터(R, G, B)들로 이루어질 수 있다.

[0089] 그리고, 제 2 기판(205) 내면에는 블랙매트릭스(206)와 액정층을 사이에 두고 화소전극과 대향하는 공통전극(미도시) 등의 컬러필터요소가 구비된다.

[0090] 블랙매트릭스(206)는 블랙 칼럼스페이서(Black Column Spacer; BCS)로 대체될 수 있다.

[0091] 이때, IPS 모드의 경우 공통전극은 화소전극과 함께 제 1 기판(210) 내에 형성된다. 다만, 본 발명이 이에 한정되는 것은 아니며, 전술한 바와 같이 본 발명은 VA 모드, FFS 모드, Super-IPS 모드, reverse TN IPS 모드의 액정표시장치에도 적용될 수 있다.

[0092] 전술한 본 발명의 제 1 실시예와 동일하게 본 발명의 제 2 실시예에 따른 액정표시장치는 GIP 방식을 가지는 것을 특징으로 한다.

[0093] 따라서, GIP 방식의 제 1 기판(210)의 회로부에는 다수의 회로 배선들이 형성된다. 일 예로, 이러한 회로 배선들은 접지 배선(241)과 클럭신호 배선(242) 및 공통 배선(244) 이외에 GIP 회로(243)를 포함할 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

[0094] 이 경우 본 발명의 제 2 실시예에 따른 실 라인(230)은 접지 배선(241)과 클럭신호 배선(242) 위에 평탄화층(225)으로 평탄화된 제 1 기판(210)의 회로부에 형성될 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

[0095] 일 예로, 평탄화층(225)은 포토 아크릴 층으로 이루어질 수 있다.

[0096] 본 발명의 제 2 실시예에 따른 실 라인(230)은 액정층을 적하 방식으로 형성하는 경우 액정패널의 가장자리를 둘러싸는 폐곡선의 형태를 가질 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

[0097] 이때, 본 발명의 제 2 실시예에 따른 액정표시장치는 실 라인(230) 좌우에 홀(235)이 형성되어 있는 것을 특징으로 한다.

[0098] 이러한 홀(235)은 실 라인(230)이 도포되는 제 1 기판(210)의 최상층, 일 예로 평탄화층(225)에 형성될 수 있으나, 본 발명이 이에 한정되는 것은 아니다.

[0099] 홀(235)은 여분의 실이 충진될 수 있도록 좁고 긴 형태를 가질 수 있다.

[0100] 특히, 본 발명의 제 2 실시예의 경우에는 회로부의 평탄화층(225) 하부에 서브-컬러필터(R, G, B)들을 구성하는 컬러안료로 이루어진 안료 층(251, 252)을 추가로 형성함에 따라 홀(235)의 깊이를 깊게 할 수 있다. 그 결과 전술한 본 발명의 제 1 실시예에 비해 실 퍼짐 및 선 폭을 보다 효과적으로 제어할 수 있는 효과를 가진다. 또한, 전술한 본 발명의 제 1 실시예에 비해 홀(235)의 깊이를 깊게 할 수 있어 상대적으로 홀(235)의 폭을 줄일 수 있고, 따라서 선 폭을 더욱 축소할 수 있는 효과를 가진다.

[0101] 도 7은 본 발명의 제 3 실시예에 따른 액정표시장치의 단면 구조를 개략적으로 보여주는 도면이다.

[0102] 이때, 도 7에 도시된 본 발명의 제 3 실시예는 전술한 본 발명의 제 2 실시예와는 달리 평탄화층의 일부 깊이만을 제거함으로써 홀 대신에 홈 형태를 형성한 경우를 예로 들고 있다.

[0103] 도 7을 참조하면, 본 발명의 제 3 실시예에 따른 액정표시장치는 제 1 기판(310)과 제 2 기판(305) 및 실 라인(330)에 의해 합착된 상태에서 제 1 기판(310)과 제 2 기판(305) 사이에 형성된 액정층(미도시)으로 구성될 수 있다.

[0104] 이때, 제 1 기판(310)과 제 2 기판(305)의 내면에는 각각 어레이요소와 컬러필터요소가 갖추어진다.

[0105] 전술한 바와 같이 제 1 기판(310) 내면에는 어레이요소로서 수평방향의 게이트라인(미도시)과 수직방향의 데이터라인(미도시)이 종횡으로 교차해서 매트릭스 형태의 화소를 정의한다.

[0106] 게이트라인과 데이터라인의 교차점에는 박막 트랜지스터가 구비되어 각 화소에 형성된 화소전극(미도시)과 일대일로 대응하여 연결된다.

[0107] 도시하지 않았지만, 박막 트랜지스터는 게이트라인에 연결된 게이트전극, 데이터라인에 연결된 소오스전극 및 화소전극에 전기적으로 접속된 드레인전극으로 구성된다. 또한, 박막 트랜지스터는 이러한 구성요소들 사이의 절연을 위한 다수의 절연층(315) 및 게이트전극에 공급되는 게이트전압에 의해 소오스전극과 드레인전극 사이에 전도채널을 형성하는 액티브층을 포함한다.

- [0108] 이렇게 구성된 본 발명의 제 3 실시예에 따른 제 1 기판(310)은 박막 트랜지스터 위에 컬러필터가 형성된 COT 구조로 이루어질 수 있다. 컬러필터는 컬러필터요소로서 특정 파장대의 빛만을 선택적으로 투과하는, 예를 들어 적, 녹 및 청색의 서브-컬러필터(R, G, B)들로 이루어질 수 있다.

- [0109] 그리고, 제 2 기판(305) 내면에는 블랙매트릭스(306)와 액정층을 사이에 두고 화소전극과 대향하는 공통전극(미도시) 등의 컬러필터요소가 구비된다.

- [0110] 블랙매트릭스(306)는 블랙 칼럼스페이서(Black Column Spacer; BCS)로 대체될 수 있다.

- [0111] 이때, IPS 모드의 경우 공통전극은 화소전극과 함께 제 1 기판(310) 내에 형성된다. 다만, 본 발명이 이에 한정되는 것은 아니며, 전술한 바와 같이 본 발명은 VA 모드, FFS 모드, Super-IPS 모드, reverse TN IPS 모드의 액정표시장치에도 적용될 수 있다.

- [0112] 전술한 본 발명의 제 1, 제 2 실시예와 동일하게 본 발명의 제 3 실시예에 따른 액정표시장치는 GIP 방식을 가지는 것을 특징으로 한다.

- [0113] 따라서, GIP 방식의 제 1 기판(310)의 회로부에는 다수의 회로 배선들이 형성된다. 일 예로, 이러한 회로 배선들은 접지 배선(341)과 클럭신호 배선(342) 및 공통 배선(344) 이외에 GIP 회로(343)를 포함할 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

- [0114] 이 경우 본 발명의 제 3 실시예에 따른 실 라인(330)은 접지 배선(341)과 클럭신호 배선(342) 위에 평탄화층(325)으로 평탄화된 제 1 기판(310)의 회로부에 형성될 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

- [0115] 일 예로, 평탄화층(325)은 포토 아크릴 층으로 이루어질 수 있다.

- [0116] 본 발명의 제 3 실시예에 따른 실 라인(330)은 액정층을 적하 방식으로 형성하는 경우 액정패널의 가장자리를 둘러싸는 폐곡선의 형태를 가질 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

- [0117] 이때, 본 발명의 제 3 실시예에 따른 액정표시장치는 실 라인(330) 좌우에 일정 깊이의 홈(336)이 형성되어 있는 것을 특징으로 한다.

- [0118] 이러한 홈(336)은 실 라인(330)이 도포되는 제 1 기판(310)의 최상층, 일 예로 평탄화층(325)에 형성될 수 있으나, 본 발명이 이에 한정되는 것은 아니다.

- [0119] 홈(336) 역시 여분의 실이 충진될 수 있도록 좁고 긴 형태를 가질 수 있다.

- [0120] 홈(336)은 평탄화층(325)에 하프-톤이나 슬릿 마스크를 적용하여 형성할 수 있다.

- [0121] 한편, 본 발명의 훌은 전술한 라인 형태 이외에 일정하게 반복되는 패턴 형태로도 변형이 가능하며, 이를 다음의 도 8을 참조하여 상세히 설명한다.

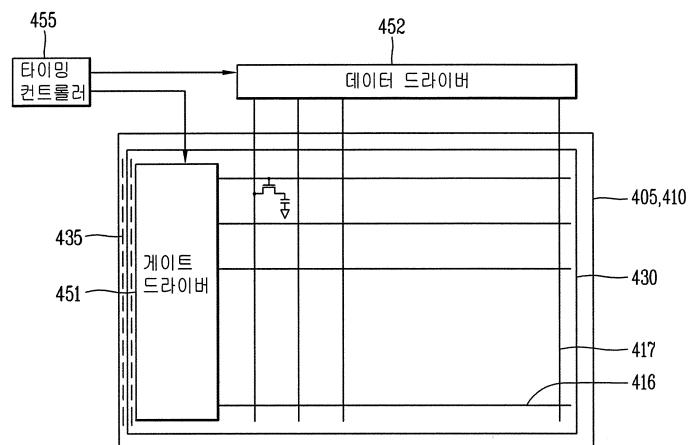

- [0122] 도 8은 본 발명의 제 4 실시예에 따른 액정표시장치의 구조를 개략적으로 보여주는 예시도이다.

- [0123] 도 8을 참조하면, 본 발명의 제 4 실시예에 따른 액정표시장치는 제 1 기판(410)과 제 2 기판(405) 및 실 라인(430)에 의해 합착된 상태에서 제 1 기판(410)과 제 2 기판(405) 사이에 형성된 액정층(미도시)으로 구성될 수 있다.

- [0124] 이때, 제 1 기판(410)과 제 2 기판(405)의 내면에는 각각 어레이요소와 컬러필터요소가 갖추어진다.

- [0125] 전술한 바와 같이 제 1 기판(410) 내면에는 어레이요소로서 수평방향의 게이트라인(416)과 수직방향의 데이터라인(417)이 종횡으로 교차해서 매트릭스 형태의 화소를 정의한다.

- [0126] 게이트라인(416)과 데이터라인(417)의 교차점에는 박막 트랜지스터가 구비되어 각 화소에 형성된 화소전극(미도시)과 일대일로 대응하여 연결된다.

- [0127] 이렇게 구성된 본 발명의 제 4 실시예에 따른 제 1 기판(410)은 박막 트랜지스터 위에 컬러필터가 형성된 COT 구조로 이루어질 수 있다. 다만, 전술한 바와 같이 본 발명이 이에 한정되는 것은 아니다.

- [0128] 그리고, 제 2 기판(405) 내면에는 블랙매트릭스(미도시)와 액정층을 사이에 두고 화소전극과 대향하는 공통전극(미도시) 등의 컬러필터요소가 구비된다.

- [0129] 블랙매트릭스는 블랙 칼럼스페이서(Black Column Spacer; BCS)로 대체될 수 있다.

- [0130] 이때, IPS 모드의 경우 공통전극은 화소전극과 함께 제 1 기판(410) 내에 형성된다. 다만, 본 발명이 이에 한정되는 것은 아니며, 전술한 바와 같이 본 발명은 VA 모드, FFS 모드, Super-IPS 모드, reverse TN IPS 모드의 액정표시장치에도 적용될 수 있다.

- [0131] 다음으로, 구동회로부는 타이밍 컨트롤러(455)와 게이트 드라이버(451) 및 데이터 드라이버(452)를 포함한다.

- [0132] 전술한 본 발명의 제 1 내지 제 3 실시예와 동일하게 본 발명의 제 4 실시예에 따른 액정표시장치는 GIP 방식을 가지는 것을 특징으로 한다. 다만, 본 발명이 이에 한정되는 것은 아니다.

- [0133] 따라서, 실 라인(430)은 접지 배선(미도시)과 클럭신호 배선(미도시) 위에 평탄화층(미도시)으로 평탄화된 제 1 기판(410)의 회로부에 형성될 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

- [0134] 본 발명의 제 4 실시예에 따른 실 라인(430)은 액정층을 적하 방식으로 형성하는 경우 액정패널의 가장자리를 둘러싸는 폐곡선의 형태를 가질 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

- [0135] 이때, 본 발명의 제 4 실시예에 따른 액정표시장치는 실 라인(430) 좌우에 홀(435)이 형성되어 있는 것을 특징으로 한다.

- [0136] 홀(435)은 여분의 실이 충진될 수 있도록 좁고 긴 형태를 가질 수 있다.

- [0137] 특히, 본 발명의 제 4 실시예는 홀(435)이 전술한 라인 형태 이외에 일정하게 반복되는 패턴 형태로 형성된 경우를 예로 들고 있다.

- [0138] 도 9는 본 발명의 제 5 실시예에 따른 액정표시장치의 구조를 개략적으로 보여주는 예시도이다.

- [0139] 이때, 도 9에 도시된 본 발명의 제 5 실시예는 액정패널의 4면 모두에 홀이 형성된 경우를 예로 들고 있다.

- [0140] 도 9를 참조하면, 본 발명의 제 5 실시예에 따른 액정표시장치는 제 1 기판(510)과 제 2 기판(505) 및 실 라인(530)에 의해 합착된 상태에서 제 1 기판(510)과 제 2 기판(505) 사이에 형성된 액정층(미도시)으로 구성될 수 있다.

- [0141] 이때, 제 1 기판(510)과 제 2 기판(505)의 내면에는 각각 어레이요소와 컬러필터요소가 갖추어진다.

- [0142] 전술한 바와 같이 제 1 기판(510) 내면에는 어레이요소로서 수평방향의 게이트라인(516)과 수직방향의 데이터라인(517)이 종횡으로 교차해서 매트릭스 형태의 화소를 정의한다.

- [0143] 게이트라인(516)과 데이터라인(517)의 교차점에는 박막 트랜지스터가 구비되어 각 화소에 형성된 화소전극(미도시)과 일대일로 대응하여 연결된다.

- [0144] 이렇게 구성된 본 발명의 제 5 실시예에 따른 제 1 기판(510)은 박막 트랜지스터 위에 컬러필터가 형성된 COT 구조로 이루어질 수 있다. 다만, 전술한 바와 같이 본 발명이 이에 한정되는 것은 아니다.

- [0145] 그리고, 제 2 기판(505) 내면에는 블랙매트릭스(미도시)와 액정층을 사이에 두고 화소전극과 대향하는 공통전극(미도시) 등의 컬러필터요소가 구비된다.

- [0146] 블랙매트릭스는 블랙 칼럼스페이서(Black Column Spacer; BCS)로 대체될 수 있다.

- [0147] 이때, IPS 모드의 경우 공통전극은 화소전극과 함께 제 1 기판(510) 내에 형성된다. 다만, 본 발명이 이에 한정되는 것은 아니며, 전술한 바와 같이 본 발명은 VA 모드, FFS 모드, Super-IPS 모드, reverse TN IPS 모드의 액정표시장치에도 적용될 수 있다.

- [0148] 다음으로, 구동회로부는 타이밍 컨트롤러(555)와 게이트 드라이버(551) 및 데이터 드라이버(552)를 포함한다.

- [0149] 전술한 본 발명의 제 1 내지 제 4 실시예와 동일하게 본 발명의 제 5 실시예에 따른 액정표시장치는 GIP 방식을 가지는 것을 특징으로 한다. 다만, 본 발명이 이에 한정되는 것은 아니다.

- [0150] 따라서, 실 라인(530)은 접지 배선(미도시)과 클럭신호 배선(미도시) 위에 평탄화층(미도시)으로 평탄화된 제 1 기판(510)의 회로부에 형성될 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

- [0151] 본 발명의 제 5 실시예에 따른 실 라인(530)은 액정층을 적하 방식으로 형성하는 경우 액정패널의 가장자리를 둘러싸는 폐곡선의 형태를 가질 수 있다. 다만, 본 발명이 이에 한정되는 것은 아니다.

- [0152] 이때, 본 발명의 제 5 실시예에 따른 액정표시장치는 실 라인(530) 좌우에 홀(535)이 형성되어 있는 것을 특징

으로 한다.

홀(535)은 여분의 실이 충진될 수 있도록 좁고 긴 형태를 가질 수 있다.

특히, 본 발명의 제 5 실시예는 회로 배선들의 형성 유무에 관련 없이 실 라인(530)을 따라 액정패널의 4면 모두에 흘(535)이 형성된 경우를 예로 들고 있다.

이때, 홀(535) 대신에 일정 깊이의 홈을 형성할 수도 있다.

상기한 설명에 많은 사항이 구체적으로 기재되어 있으나 이것은 발명의 범위를 한정하는 것이라기보다 바람직한 실시예의 예시로서 해석되어야 한다. 따라서 발명은 설명된 실시예에 의하여 정할 것이 아니고 특히청구범위와 특히청구범위에 균등한 것에 의하여 정하여져야 한다.

### 부호의 설명

105, 205, 305, 405, 505 : 제 2 기판 110, 210, 310, 410, 510 : 제 1 기판

130,230,330,430,530 : 실 라인 135,235,435,535 : 홀

336 : 흠

도면

## 도면1

도면2

도면3

도면4a

도면4b

도면5a

도면5b

도면6

도면7

도면8

도면9

|                |                                         |         |            |

|----------------|-----------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                   |         |            |

| 公开(公告)号        | <a href="#">KR1020160090693A</a>        | 公开(公告)日 | 2016-08-01 |

| 申请号            | KR1020150010796                         | 申请日     | 2015-01-22 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                               |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                               |         |            |

| [标]发明人         | JANG YEONHEE<br>장연희                     |         |            |

| 发明人            | 장연희                                     |         |            |

| IPC分类号         | G02F1/1339 G02F1/1333 G02F1/1335        |         |            |

| CPC分类号         | G02F1/1339 G02F1/133514 G02F2001/133357 |         |            |

| 代理人(译)         | 박장원                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>               |         |            |

#### 摘要(译)

本发明的液晶显示器高质量化并且在左右密封线上形成填充多余空间的孔，并且管理包括覆盖移动和扩散宽度增加等的变化的处理。液晶显示器的滤色器 - 一个 - 薄膜晶体管 ( TFT 上的彩色滤光片 : COT ) 结构，用于高效显示。因此，提供了通过密封线的线宽和工艺余量减小来实现液晶显示器的窄边框的效果。