(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2010-0077783

(43) 공개일자 2010년07월08일

(51) Int. Cl.

G09G 3/36 (2006.01) G02F 1/133 (2006.01)

(21) 출원번호 10-2008-0135823

(22) 출원일자 2008년12월29일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울 영등포구 여의도동 20번지

(72) 발명자

김민기

경상북도 철곡군 석적읍 남율리 우방신천지아파트

110동 508호

김진성

경상북도 구미시 송정동 푸르지오캐슬아파트 120

동 203호

차동훈

경상북도 구미시 진평동 988 인의주공아파트 202

동 1509호

(74) 대리인

김용인, 박영복

전체 청구항 수 : 총 5 항

(54) 액정표시장치용 라인 메모리 및 이의 구동방법

### (57) 요약

본 발명은 액정표시장치용 라인 메모리 및 이의 구동방법에 관한 것으로, 하나의 라인 메모리가 동일 기간에 라이트 동작과 리드 동작을 동시에 수행하도록 하고, 이때 라이트 동작과 리드 동작이 서로 중첩되지 않도록 함으로써 리드 및 라이트 동작을 빠르게 수행함으로써 라인 메모리 수를 줄일 수 있다.

### 대 표 도 - 도3

## 특허청구의 범위

### 청구항 1

제 n 기간에 제 1 라이트 신호에 응답하여 두 수평라인분의 화상 데이터들 중 제 1 화상 데이터들을 저장하고, 제 n+1 기간에 제 1 리드 신호에 응답하여 상기 저장된 제 1 화상 데이터들 중 일부를 출력하는 제 1 라인 메모리;

상기 제 n 기간에 제 2 라이트 신호에 응답하여 상기 두 수평라인분의 화상 데이터들 중 제 2 화상 데이터들을 저장함과 아울러 제 2 리드 신호에 응답하여 제 n-1 기간에 저장되었던 제 3 화상 데이터들 중 일부를 출력하고, 상기 제 n+1 기간에 제 2 라이트 신호에 응답하여 상기 두 수평라인분의 화상 데이터들 중 제 4 화상 데이터를 저장함과 아울러 제 2 리드 신호에 응답하여 상기 제 n 기간에 저장되었던 제 2 화상 데이터들 중 일부를 출력하는 제 2 라인 메모리;

상기 제 n 기간에 제 3 리드 신호에 응답하여 제 n-1 기간에 저장되었던 제 5 화상 데이터들 중 일부를 출력하는 제 3 라인 메모리를 포함하며;

상기 제 n 기간에서의 제 2 라이트 신호와 제 2 리드 신호가 중첩되지 않으며, 상기 제 n+1 기간에서의 제 2 라이트 신호와 제 2 리드 신호가 중첩되지 않는 것을 특징으로 하는 액정표시장치용 라인 메모리.

### 청구항 2

제 1 항에 있어서,

상기 제 1 라이트 신호는 상기 제 n 기간동안 하이상태를 유지하며;

상기 제 2 라이트 신호는 상기 제 n 기간의 일부 기간 및 제 n+1 기간의 일부 기간동안 하이상태를 유지하며;

상기 제 3 라이트 신호는 상기 제 n+1 기간동안 하이상태를 유지하며;

상기 제 1 리드 신호는 상기 제 n+1 기간의 일부 기간동안 하이상태를 유지하며;

상기 제 2 리드 신호는 상기 제 n 기간의 일부 기간 및 상기 제 n+1 기간의 일부 기간동안 하이상태를 유지하되, 상기 제 n 기간에서의 제 2 리드 신호의 펄스폭이 상기 제 n 기간에서의 제 2 라이트 신호의 펄스폭과 중첩하지 않으며, 상기 제 n+1 기간에서의 제 2 리드 신호의 펄스폭이 상기 제 n 기간에서의 제 2 라이트 신호의 펄스폭과 중첩하지 않으며; 그리고,

상기 제 3 리드 신호는 상기 제 n 기간의 일부 기간동안 하이상태를 유지하는 것을 특징으로 하는 액정표시장치용 라인 메모리.

### 청구항 3

제 1 항에 있어서,

상기 제 1 내지 제 3 라이트 신호와 상기 제 1 내지 제 3 리드 신호를 생성하고, 이들을 제 1 내지 제 3 라인 메모리에 공급하는 메모리 제어부를 더 포함함을 특징으로 하는 액정표시장치용 라인 메모리.

### 청구항 4

제 1 항에 있어서,

상기 제 1 내지 제 3 라인 메모리는 SRAM(Static Random Access Memory)인 것을 특징으로 하는 액정표시장치용 라인 메모리.

### 청구항 5

제 n 기간에 제 1 라이트 신호에 응답하여 두 수평라인분의 화상 데이터들 중 제 1 화상 데이터들을 저장하고, 제 n+1 기간에 제 1 리드 신호에 응답하여 상기 저장된 제 1 화상 데이터들 중 일부를 출력하는 단계;

상기 제 n 기간에 제 2 라이트 신호에 응답하여 상기 두 수평라인분의 화상 데이터들 중 제 2 화상 데이터들을 저장함과 아울러 제 2 리드 신호에 응답하여 제 n-1 기간에 저장되었던 제 3 화상 데이터들 중 일부를 출력하고, 상기 제 n+1 기간에 제 2 라이트 신호에 응답하여 상기 두 수평라인분의 화상 데이터들 중 제 4 화상

데이터를 저장함과 아울러 제 2 리드 신호에 응답하여 상기 제 n 기간에 저장되었던 제 2 화상 데이터들 중 일부를 출력하는 단계;

상기 제 n 기간에 제 3 리드 신호에 응답하여 제 n-1 기간에 저장되었던 제 5 화상 데이터들 중 일부를 출력하는 단계를 포함하며;

상기 제 n 기간에서의 제 2 라이트 신호와 제 2 리드 신호가 중첩되지 않으며, 상기 제 n+1 기간에서의 제 2 라이트 신호와 제 2 리드 신호가 중첩되지 않는 것을 특징으로 하는 액정표시장치용 라인 메모리의 구동방법.

## 명세서

### 발명의 상세한 설명

#### 기술 분야

[0001]

본 발명은 액정표시장치용 라인 메모리에 관한 것으로, 특히 라인 메모리의 수를 줄일 수 있는 액정표시장치용 라인 메모리에 대한 것이다.

#### 배경기술

[0002]

액정표시장치는 비디오신호에 따라 액정셀들의 광투과율을 조절하여 화상을 표시하게 된다. 액티브 매트릭스 (Active Matrix) 타입의 액정표시장치는 화소셀마다 스위칭소자가 형성되어 동영상을 표시하기에 유리하다. 스위칭소자로는 주로 박막트랜지스터(Thin Film Transistor; 이하 "TFT"라 함)가 이용되고 있다.

[0003]

종래의 액정표시장치는 외부로부터 공급되는 화상 데이터들을 재배열하기 위해, 4개의 라인 메모리를 포함하고 있다. 이와 같이 종래에는 많은 수의 라인 메모리가 필요함에 따라 이 라인 메모리들을 포함하는 타이밍 콘트롤러의 비용이 증가하고 소비전력이 증가하는 문제점이 있었다.

#### 발명의 내용

##### 해결 하고자하는 과제

[0004]

본 발명은 상기와 같은 문제점을 해결하기 위하여 안출한 것으로, 하나의 라인 메모리가 동일 기간에 라이트 동작과 리드 동작을 동시에 수행하도록 하고, 이때 라이트 동작과 리드 동작이 서로 중첩되지 않도록 함으로써 리드 및 라이트 동작을 빠르게 수행함으로써 라인 메모리 수를 줄일 수 있는 액정표시장치용 라인 메모리 및 이의 구동방법을 제공하는데 그 목적이 있다.

##### 과제 해결수단

[0005]

상기와 같은 목적을 달성하기 위한 본 발명에 따른 액정표시장치용 라인 메모리는, 제 n 기간에 제 1 라이트 신호에 응답하여 두 수평라인분의 화상 데이터들 중 제 1 화상 데이터들을 저장하고, 제 n+1 기간에 제 1 리드 신호에 응답하여 상기 저장된 제 1 화상 데이터들 중 일부를 출력하는 제 1 라인 메모리; 상기 제 n 기간에 제 2 라이트 신호에 응답하여 상기 두 수평라인분의 화상 데이터들 중 제 2 화상 데이터들을 저장함과 아울러 제 2 리드 신호에 응답하여 제 n-1 기간에 저장되었던 제 3 화상 데이터들 중 일부를 출력하고, 상기 제 n+1 기간에 제 2 라이트 신호에 응답하여 상기 두 수평라인분의 화상 데이터들 중 제 4 화상 데이터를 저장함과 아울러 제 2 리드 신호에 응답하여 상기 제 n 기간에 저장되었던 제 2 화상 데이터들 중 일부를 출력하는 제 2 라인 메모리; 상기 제 n 기간에 제 3 리드 신호에 응답하여 제 n-1 기간에 저장되었던 제 5 화상 데이터들 중 일부를 출력하는 제 3 라인 메모리를 포함하며; 상기 제 n 기간에서의 제 2 라이트 신호와 제 2 리드 신호가 중첩되지 않으며, 상기 제 n+1 기간에서의 제 2 라이트 신호와 제 2 리드 신호가 중첩되지 않는 것을 특징으로 한다.

[0006]

상기 제 1 라이트 신호는 상기 제 n 기간동안 하이상태를 유지하며; 상기 제 2 라이트 신호는 상기 제 n 기간의 일부 기간 및 제 n+1 기간의 일부 기간동안 하이상태를 유지하며; 상기 제 3 라이트 신호는 상기 제 n+1 기간동안 하이상태를 유지하며; 상기 제 1 리드 신호는 상기 제 n+1 기간의 일부 기간동안 하이상태를 유지하며; 상기 제 2 리드 신호는 상기 제 n 기간의 일부 기간 및 상기 제 n+1 기간의 일부 기간동안 하이상태를 유지하되, 상기 제 n 기간에서의 제 2 리드 신호의 펄스폭이 상기 제 n 기간에서의 제 2 라이트 신호의 펄스폭과 중첩하지 않으며, 상기 제 n+1 기간에서의 제 2 리드 신호의 펄스폭이 상기 제 n 기간에서의 제 2 라이트 신호의 펄스폭과 중첩하지 않으며; 그리고, 상기 제 3 리드 신호는 상기 제 n 기간의 일부 기간동안 하이상태를 유지하는 것

을 특징으로 한다.

[0007] 상기 제 1 내지 제 3 라이트 신호와 상기 제 1 내지 제 3 리드 신호를 생성하고, 이들을 제 1 내지 제 3 라인 메모리에 공급하는 메모리 제어부를 더 포함함을 특징으로 한다.

[0008] 상기 제 1 내지 제 3 라인 메모리는 SRAM(Static Random Access Memory)인 것을 특징으로 한다.

[0009] 또한 상기와 같은 목적을 달성하기 위한 본 발명에 따른 액정표시장치용 라인 메모리의 구동방법은, 제 n 기간에 제 1 라이트 신호에 응답하여 두 수평라인분의 화상 데이터들 중 제 1 화상 데이터들을 저장하고, 제 n+1 기간에 제 1 리드 신호에 응답하여 상기 저장된 제 1 화상 데이터들 중 일부를 출력하는 단계; 상기 제 n 기간에 제 2 라이트 신호에 응답하여 상기 두 수평라인분의 화상 데이터들 중 제 2 화상 데이터들을 저장함과 아울러 제 2 리드 신호에 응답하여 제 n-1 기간에 저장되었던 제 3 화상 데이터들 중 일부를 출력하고, 상기 제 n+1 기간에 제 2 라이트 신호에 응답하여 상기 두 수평라인분의 화상 데이터들 중 제 4 화상 데이터를 저장함과 아울러 제 2 리드 신호에 응답하여 상기 제 n 기간에 저장되었던 제 2 화상 데이터들 중 일부를 출력하는 단계; 상기 제 n 기간에 제 3 리드 신호에 응답하여 제 n-1 기간에 저장되었던 제 5 화상 데이터들 중 일부를 출력하는 단계를 포함하며; 상기 제 n 기간에서의 제 2 라이트 신호와 제 2 리드 신호가 중첩되지 않으며, 상기 제 n+1 기간에서의 제 2 라이트 신호와 제 2 리드 신호가 중첩되지 않는 것을 특징으로 한다.

### 효과

[0010] 본 발명에 따른 액정표시장치용 라인 메모리 및 이의 구동방법에는 다음과 같은 효과가 있다.

[0011] 본 발명에서는 하나의 라인 메모리가 동일 기간에 라이트 동작과 리드 동작을 동시에 수행하도록 하고, 이때 라이트 동작과 리드 동작이 서로 중첩되지 않도록 함으로써 리드 및 라이트 동작을 빠르게 수행함으로써 라인 메모리 수를 줄일 수 있다.

### 발명의 실시를 위한 구체적인 내용

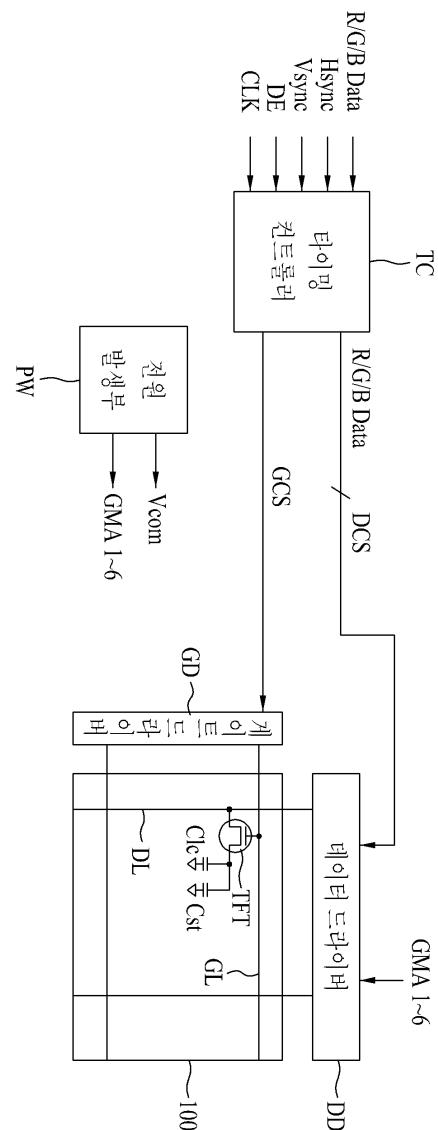

[0012] 도 1은 본 발명의 실시예에 따른 액정표시장치를 나타낸 도면이다.

[0013] 본 발명의 실시예에 따른 액정표시장치는, 도 1에 도시된 바와 같이, 서로 교차하는 게이트 라인(GL)들 및 데이터 라인(DL)들과, 그리고 상기 각 게이트 라인(GL)과 각 데이터 라인(DL)간의 교차부에 형성된 박막트랜지스터(TFT)를 포함하는 표시패널(100)과 상기 표시패널(100)의 데이터 라인(DL)들에 데이터를 입력하기 위한 데이터 드라이버(DD)와, 상기 표시패널(100)의 게이트 라인(GL)들에 스캔펄스를 입력하기 위한 게이트 드라이버(GD)와, 상기 표시패널(100)의 데이터 드라이버(DD) 및 게이트 드라이버(GD)를 제어하기 위한 타이밍 콘트롤러(TC)를 구비한다.

[0014] 각 화소는 게이트 라인으로부터의 스캔펄스에 응답하여 데이터 라인으로부터의 데이터를 스위칭하는 박막트랜지스터와, 상기 박막트랜지스터로부터 스위칭된 데이터에 따라 화상을 표시하는 액정셀을 포함한다. 이 박막트랜지스터(TFT)의 소스전극은 데이터 라인(DL)에 접속되며, 드레인전극은 액정셀의 화소전극에 접속된다. 그리고 박막트랜지스터(TFT)의 게이트전극은 게이트 라인(GL)에 접속된다. 상기 표시패널(100)은 액정층을 사이에 두고 서로 합착된 컬러필터 어레이 기판과 TFT 어레이 기판을 포함한다. 상기 컬러필터 어레이 기판상에는 컬러필터 및 공통전극이 형성된다. 컬러필터는 적색, 녹색 및 청색의 컬러필터들이 배치되어 특정 좌장대역의 광을 투과시킴으로써 컬러표시를 가능하게 한다. 인접한 색의 컬러필터사이에는 블랙 매트릭스(Black Matrix)가 형성된다.

[0015] 각 액정셀은 한 프레임 기간동안 데이터를 유지하기 위한 액정용량 커패시터(C1c)와, 상기 데이터를 상기 한 프레임 기간동안 안정적으로 유지시키기 위한 보조용량 커패시터를 포함한다.

[0016] 타이밍 콘트롤러(TC)는 자신에게 입력되는 수평동기신호(Hsync), 수직동기신호(Vsync), 및 클럭신호(CLK)를 이용하여 데이터 제어신호(DCS)와 게이트 제어신호(GCS)를 발생시켜 데이터 드라이버(DD)와 게이트 드라이버(GD)에 공급한다. 데이터 제어신호(DCS)는 도트클럭, 소스шу프트클럭, 소스인에이블신호, 극성반전신호 등을 포함한다. 상기 게이트 제어신호(GCS)는 게이트 스타트 펄스, 게이트шу프트클럭, 게이트출력인에이블 등을 포함하여 게이트 드라이버(GD)에 입력된다.

[0017] 데이터 드라이버(DD)는 타이밍 콘트롤러(TC)로부터의 데이터 제어신호(DCS)에 따라 데이터를 샘플링한 후에, 샘플링된 데이터를 수평기간(Horizontal Time : 1H, 2H, ...)마다 1 라인분식 래치하고 래치된 데이터를 데이터 라인(DL)들에 공급한다. 즉, 상기 데이터 드라이버(DD)는 타이밍 콘트롤러(TC)로부터의 데이터(R, G, B)를 전원

발생부(PW)로부터 입력되는 감마전압(GMA1~6)을 이용하여 아날로그 화소 신호로 변환하여 데이터 라인(DL)들에 공급한다.

[0018] 게이트 드라이버(GD)는 타이밍 콘트롤러(TC)로부터의 게이트 제어신호(GCS) 중 게이트 스타트 펄스에 응답하여 스캔펄스를 순차적으로 발생하는 쉬프트 레지스터와, 스캔펄스의 전압을 액정셀의 구동에 적합한 전압레벨로 쉬프트시키기 위한 레벨 쉬프터를 포함한다. 게이트 드라이버(GD)는 게이트 제어신호(GCS)에 응답하여 게이트 라인(GL)들에 순차적으로 게이트 하이전압을 공급한다.

[0019] 전원 발생부(PW)는 표시패널(100)에 공통전극전압(Vcom), 데이터 드라이버(DD)에 감마전압(GMA1~6)을 공급한다.

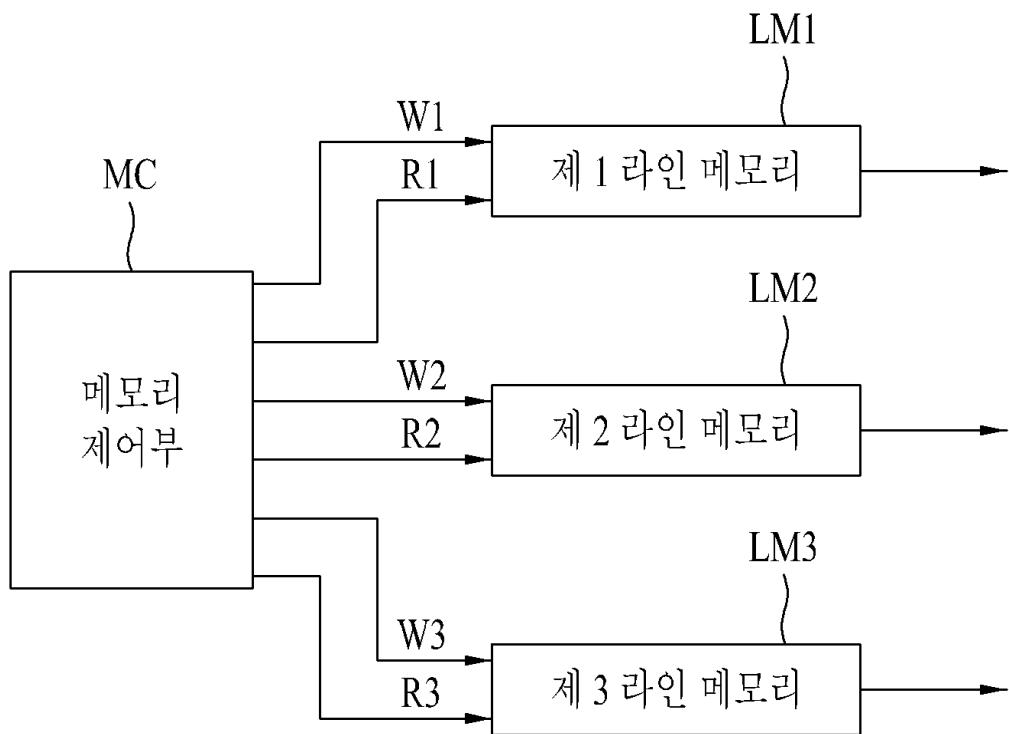

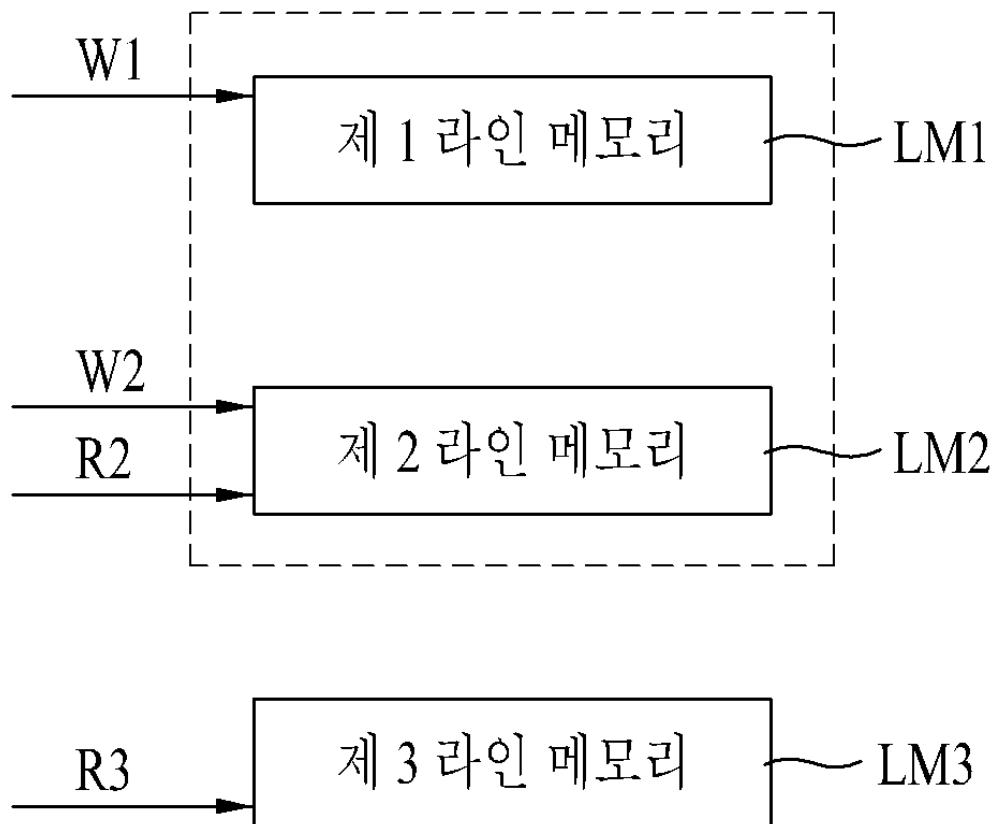

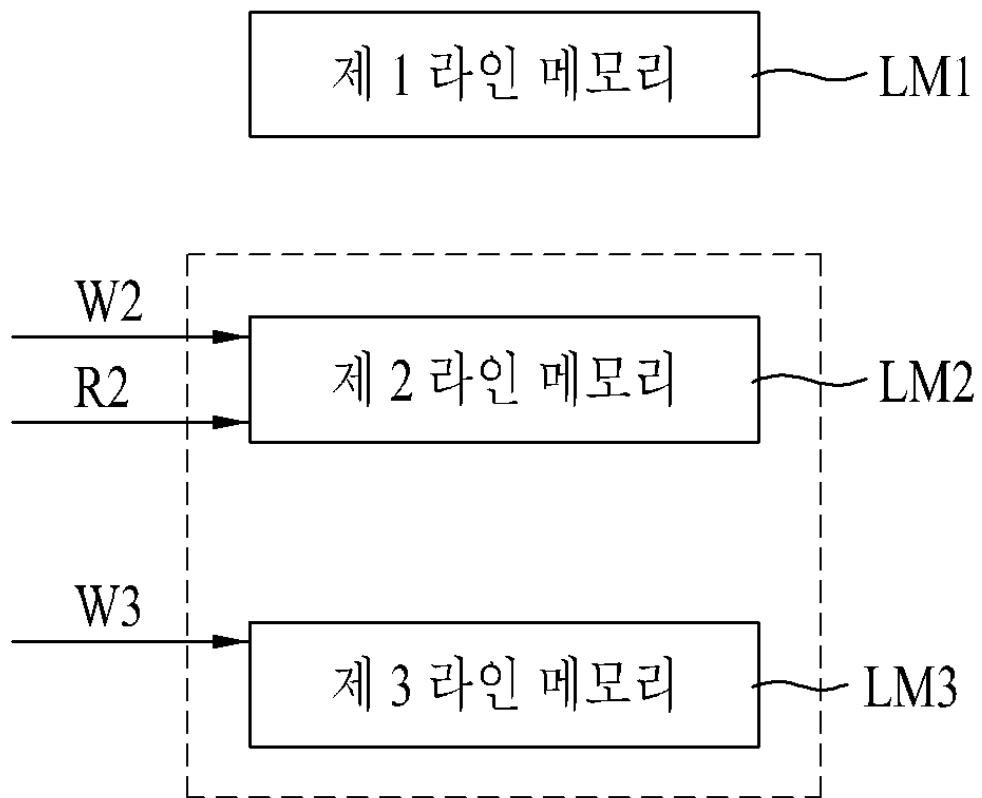

[0020] 도 2는 도 1의 타이밍 콘트롤러(TC)의 상세 구성도이다.

[0021] 타이밍 콘트롤러(TC)는, 도 2에 도시된 바와 같이, 외부로부터의 두 수평라인분의 화상 데이터들을 공급받아 재배열하기 위한 제 1 내지 제 3 라인 메모리(LM1 내지 LM3)와, 상기 제 1 내지 제 3 라인 메모리(LM1 내지 LM3)의 동작을 제어하기 위한 제 1 내지 제 3 라이트 신호(W1 내지 W3) 그리고 제 1 내지 제 3 리드 신호(R1 내지 R3)를 생성하고 이들을 제 1 내지 제 3 라인 메모리(LM1 내지 LM3)에 공급하는 메모리 제어부를 포함한다. 상기 제 1 내지 제 3 라인 메모리(LM1 내지 LM3)는 SRAM(Static Random Access Memory)이다.

[0022] 도 2에 도시된 바와 같이, 제 1 라인 메모리(LM1)는 메모리 제어부로부터의 제 1 라이트 신호(W1)에 따라 상기 두 수평라인분의 화상 데이터들 중 일부를 저장하고, 상기 메모리 제어부로부터의 제 1 리드 신호(R1)에 따라 저장된 화상 데이터들 중 일부를 출력한다. 마찬가지로, 제 2 라인 메모리(LM2)는 상기 메모리 제어부로부터의 제 2 라이트 신호(W2)에 따라 상기 두 수평라인분의 화상 데이터들 중 일부를 저장하고, 상기 메모리 제어부로부터의 제 2 리드 신호(R2)에 따라 저장된 화상 데이터들 중 일부를 출력한다. 또한, 제 3 라인 메모리(LM3)는 상기 메모리 제어부로부터의 제 3 라이트 신호(W3)에 따라 상기 두 수평라인분의 화상 데이터들 중 일부를 저장하고, 상기 메모리 제어부로부터의 제 3 리드 신호(R3)에 따라 저장된 화상 데이터들 중 일부를 출력한다.

[0023] 이들 제 1 내지 제 3 라인 메모리(LM1 내지 LM3)의 동작을 상세히 설명하면 다음과 같다.

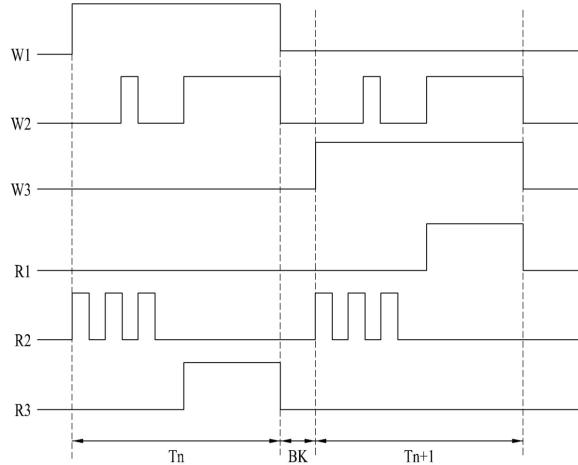

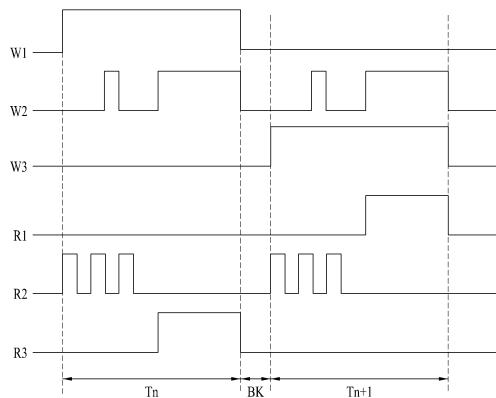

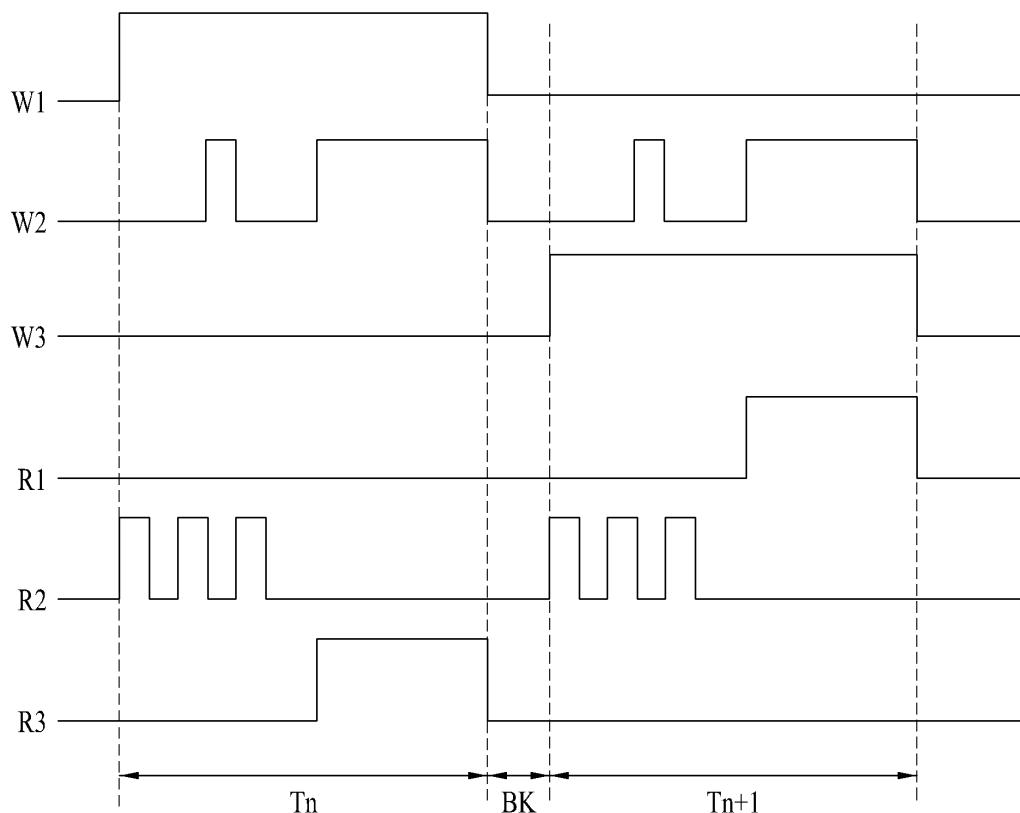

[0024] 도 3은 도 2의 제 1 내지 제 3 라인 메모리(LM1 내지 LM3)에 공급되는 제 1 내지 제 3 라이트 신호(W1 내지 W3)와 제 1 내지 제 3 리드 신호(R1 내지 R3)의 타이밍도를 나타낸 도면이고, 도 4a 및 도 4b는 제 2 라인 메모리(LM2)의 라이트 및 리드 동작을 설명하기 위한 도면이다.

[0025] 제 1 라인 메모리(LM1)는 제 n 기간(Tn)에 제 1 라이트 신호(W1)에 응답하여 두 수평라인분의 화상 데이터들 중 제 1 화상 데이터들을 저장하고, 그리고 제 n+1 기간(Tn+1)에 제 1 리드 신호에 응답하여 상기 저장된 제 1 화상 데이터들 중 일부를 출력한다. 여기서, n은 자연수이다.

[0026] 제 2 라인 메모리(LM2)는 제 n 기간(Tn)에 제 2 라이트 신호(W2)에 응답하여 상기 두 수평라인분의 화상 데이터들 중 제 2 화상 데이터들을 저장함과 아울러 제 2 리드 신호(R2)에 응답하여 제 n-1 기간에 저장되었던 제 3 화상 데이터들 중 일부를 출력한다. 또한, 상기 제 2 라인 메모리(LM2)는 상기 제 n+1 기간(Tn+1)에 제 2 라이트 신호(W2)에 응답하여 상기 두 수평라인분의 화상 데이터들 중 제 4 화상 데이터를 저장함과 아울러 제 2 리드 신호(R2)에 응답하여 상기 제 n 기간(Tn)에 저장되었던 제 2 화상 데이터들 중 일부를 출력한다.

[0027] 제 3 라인 메모리(LM3)는 상기 제 n 기간(Tn)에 제 3 리드 신호(R3)에 응답하여 제 n-1 기간에 저장되었던 제 5 화상 데이터들 중 일부를 출력한다.

[0028] 이때, 상기 제 n 기간(Tn)에서의 제 2 라이트 신호(W2)와 제 2 리드 신호(R2)가 중첩되지 않으며, 상기 제 n+1 기간(Tn+1)에서의 제 2 라이트 신호(W2)와 제 2 리드 신호(R2)가 중첩되지 않는다.

[0029] 즉, 제 n 기간(Tn)에는 제 1 라인 메모리(LM1)의 라이트 동작과, 제 2 라인 메모리(LM2)의 라이트 동작과, 그리고 제 2 라인 메모리(LM2)의 리드 동작과, 제 3 라인 메모리(LM3)의 리드 동작이 이루어지는데, 이 제 n 기간(Tn)에 상기 제 1 라인 메모리(LM1)의 라이트 동작과, 제 2 라인 메모리(LM2)의 라이트 동작과, 그리고 제 3 라인 메모리(LM3)의 리드 동작은 중첩되어 일어난다. 그러나, 이 제 n 기간(Tn)에서의 제 2 라인 메모리(LM2)의 라이트 동작과 리드 동작은 서로 중첩되지 않도록 발생한다. 또한, 제 n+1 기간(Tn+1)에는 제 2 라인 메모리(LM2)의 라이트 동작과, 제 3 라인 메모리(LM3)의 라이트 동작과, 그리고 제 1 라인 메모리(LM1)의 리드 동작과 그리고 제 2 라인 메모리(LM2)의 리드 동작이 이루어지는데, 이 제 n+1 기간(Tn+1)에 상기 2 라인 메모리의 라이트 동작과, 제 3 라인 메모리(LM3)의 라이트 동작과, 그리고 제 1 라인 메모리(LM1)의 리드 동작은 서로 중첩되어 일어난다. 그러나, 이 제 n+1 기간(Tn+1)에서의 제 2 라인 메모리(LM2)의 라이트 동작과 리드 동작은 중첩

되지 않도록 발생한다.

[0030] 이를 위해, 상기 제 1 내지 제 3 라이트 신호(W1 내지 W3), 그리고 제 1 내지 3 리드 신호는 다음과 같은 타이밍도를 갖는다.

[0031] 즉, 도 3에 도시된 바와 같이, 상기 제 1 라이트 신호(W1)는 상기 제 n 기간(Tn)동안 하이상태를 유지하며; 상기 제 2 라이트 신호(W2)는 상기 제 n 기간(Tn)의 일부 기간 및 제 n+1 기간(Tn+1)의 일부 기간동안 하이상태를 유지하며; 상기 제 3 라이트 신호(W3)는 상기 제 n+1 기간(Tn+1)동안 하이상태를 유지하며; 상기 제 1 리드 신호(R1)는 상기 제 n+1 기간(Tn+1)의 일부 기간동안 하이상태를 유지하며; 상기 제 2 리드 신호(R2)는 상기 제 n 기간(Tn)의 일부 기간 및 상기 제 n+1 기간(Tn+1)의 일부 기간동안 하이상태를 유지하되, 상기 제 n 기간(Tn)에서의 제 2 리드 신호(R2)의 펄스폭이 상기 제 n 기간(Tn)에서의 제 2 라이트 신호(W2)의 펄스폭과 중첩하지 않으며; 상기 제 n+1 기간(Tn+1)에서의 제 2 리드 신호(R2)의 펄스폭이 상기 제 n 기간(Tn)에서의 제 2 라이트 신호(W2)의 펄스폭과 중첩하지 않으며; 그리고, 상기 제 3 리드 신호(R3)는 상기 제 n 기간(Tn)의 일부 기간동안 하이상태를 유지한다.

[0032] 상기 각 기간 사이에는 제 1 내지 제 3 라이트 신호(W1 내지 W3), 그리고 제 1 내지 제 3 내지 리드 신호(R1 내지 R3)가 출력되지 않는 블랭크 기간(BK)이 존재한다.

[0033] 제 1 라이트 신호(W1)는 제 2k+1 기간마다 하이상태를 유지하고 나머지 기간동안 로우상태로 유지되며; 제 2 라이트 신호(W2)는 제 k 기간의 전반 1/2 기간 중 일부 기간 및 후반 1/2 기간동안 하이상태를 유지하고 나머지 기간동안 로우상태로 유지되며; 제 3 라이트 신호(W3)는 제 2k+2 기간마다 하이상태를 유지하고 나머지 기간동안 로우상태로 유지되며; 제 1 리드 신호(R1)는 제 2k+2 기간의 후반 1/2 기간동안 하이상태를 유지하고 나머지 기간동안 로우상태로 유지되며; 제 2 리드 신호(R2)는 제 k 기간의 전반 1/2 기간동안 하이 및 로우상태를 반복적으로 가지며; 제 3 리드 신호(R3)는 제 2k+1 기간의 후반 1/2 기간동안 하이상태를 유지하고 나머지 기간동안 로우상태로 유지된다. 여기서, k는 0을 포함한 자연수이다.

[0034] 한편, 제 1 내지 제 3 라인 메모리(LM1 내지 LM3)는 상술된 바와 같은 방식으로 한 수평라인분의 화상 데이터들을 나누어 저장하고 출력할 수도 있다.

[0035] 이와 같이 본 발명에서는 제 2 라인 메모리(LM2)가 라이트 동작과 리드 동작을 한 기간내에서 실행하되, 이 라이트 동작과 리드 동작이 중첩되지 않기 때문에 종래 대비 하나의 라인 메모리가 줄어든다.

[0036] 이상에서 설명한 본 발명은 상술한 실시예 및 첨부된 도면에 한정되는 것이 아니고, 본 발명의 기술적 사상을 벗어나지 않는 범위 내에서 여러 가지 치환, 변형 및 변경이 가능하다는 것이 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 있어 명백할 것이다.

### 도면의 간단한 설명

[0037] 도 1은 본 발명의 실시예에 따른 액정표시장치를 나타낸 도면

[0038] 도 2는 도 1의 타이밍 콘트롤러의 상세 구성도

[0039] 도 3은 도 2의 제 1 내지 제 3 라인 메모리에 공급되는 제 1 내지 제 3 라이트 신호와 제 1 내지 제 3 리드 신호의 타이밍도를 나타낸 도면

[0040] 도 4a 및 도 4b는 제 2 라인 메모리의 라이트 및 리드 동작을 설명하기 위한 도면

도면

도면1

## 도면2

## 도면3

도면4a

도면4b

|                |                                                                  |         |            |

|----------------|------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 用于液晶显示装置的行存储器及其驱动方法                                              |         |            |

| 公开(公告)号        | <a href="#">KR1020100077783A</a>                                 | 公开(公告)日 | 2010-07-08 |

| 申请号            | KR1020080135823                                                  | 申请日     | 2008-12-29 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                         |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                        |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                        |         |            |

| [标]发明人         | KIM MIN KI<br>김민기<br>KIM JIN SUNG<br>김진성<br>CHA DONG HOON<br>차동훈 |         |            |

| 发明人            | 김민기<br>김진성<br>차동훈                                                |         |            |

| IPC分类号         | G09G3/36 G02F1/133                                               |         |            |

| 代理人(译)         | 金勇<br>年轻的小公园                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                        |         |            |

### 摘要(译)

本发明涉及用于液晶显示器的行存储器及其驱动方法。同时，一行存储器在同一时段执行光移动和读取操作。通过此时快速执行引导和光移动，由于光移动和读取操作不重叠，所以可以减少行存储器数量。液晶显示器，行存储器，读取信号，光信号。