(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2014-0081555

(43) 공개일자 2014년07월01일

(51) 국제특허분류(Int. Cl.)

*G02F 1/133* (2006.01) *G09G 3/36* (2006.01)

(21) 출원번호 10-2012-0151441

(22) 출원일자 2012년12월21일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

김성원

경기 파주시 미래로 562, 908동 303호 (와동동,

가람마을9단지남양휴튼)

임종진

경기 파주시 책향기로 448, 1204동 1103호 (동파

동, 책향기마을진홍효자아파트)

(뒷면에 계속)

(74) 대리인

특허법인로얄

전체 청구항 수 : 총 13 항

(54) 발명의 명칭 액정표시장치와 그 구동 방법

### (57) 요 약

본 발명은 액정표시장치와 그 구동 방법에 관한 것으로, 이 액정표시장치는 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 클 때 데이터 전압의 주파수를 낮게 제어하는 타이밍 콘트롤러를 포함한다.

대 표 도 - 도6

(72) 발명자

이동우

충남 부여군 부여읍 성왕로328번길 15, 107동 409

호 (쌍북아파트)

홍희정

서울 양천구 목동동로 430, 612동 1203호 (목동,

목동6단지아파트)

---

## 특허청구의 범위

### 청구항 1

데이터 라인들과 게이트 라인들이 교차되고 픽셀들이 매트릭스 타입으로 배치된 표시패널;

상기 데이터 라인들에 데이터 전압을 공급하는 데이터 구동부;

상기 데이터 전압들과 동기되는 게이트펄스를 상기 게이트 라인들에 순차적으로 공급하는 게이트 구동부; 및

상기 표시패널의 제N(N은 양의 정수) 라인에 배치된 픽셀들에 기입될 제N 라인 데이터와, 상기 표시패널의 제N+1 라인의 픽셀들에 기입될 제N+1 라인 데이터 간의 계조 차이가 미리 설정된 기준값 보다 클 때 상기 데이터 구동부와 상기 게이트 구동부의 동작 주파수를 낮추어 상기 데이터 전압의 주파수를 낮게 제어하는 타이밍 콘트롤러를 포함하는 것을 특징으로 하는 액정표시장치.

### 청구항 2

제 1 항에 있어서,

상기 타이밍 콘트롤러는 상기 제N 라인 데이터와 상기 제N+1 라인 데이터 간의 계조 차이가 상기 기준값 이하로 작을 때 상기 데이터 구동부와 상기 게이트 구동부의 동작 주파수를 높여 상기 데이터 전압의 주파수를 높게 제어하는 타이밍 콘트롤러를 포함하는 것을 특징으로 하는 액정표시장치.

### 청구항 3

제 2 항에 있어서,

상기 타이밍 콘트롤러는,

상기 제N 라인 데이터와 상기 제N+1 라인 데이터 간의 계조 차이가 상기 기준값 보다 클 때 상기 데이터 구동부에 인가되어 상기 데이터 전압의 출력 타이밍을 제어하는 소스 출력 인에이블 신호(SOE)와, 상기 게이트 구동부에 인가되어 상기 게이트펄스의 출력 타이밍을 제어하는 게이트 출력 인에이블 신호(GOE)의 주파수를 낮추는 것을 특징으로 하는 액정표시장치.

### 청구항 4

제 2 항에 있어서,

상기 타이밍 콘트롤러는,

상기 제N 라인 데이터에서 선택된 제1 색 데이터와, 상기 제N+1 라인 데이터에서 선택된 제2 색 데이터 간의 계조 차이를 비교하는 것을 특징으로 하는 액정표시장치.

### 청구항 5

제 4 항에 있어서,

상기 타이밍 콘트롤러는,

상기 제N 라인 데이터에서 선택된 제1 색 데이터들을 바탕으로 계산된 제N 라인 대표값과, 상기 제N+1 라인 데이터에서 선택된 제2 색 데이터들을 바탕으로 계산된 제2 라인 대표값 간의 계조 차이를 비교하는 것을 특징으로 하는 액정표시장치.

### 청구항 6

제 5 항에 있어서,

상기 제N 라인 대표값은 상기 제N 라인 데이터에서 선택된 제1 색 데이터들의 평균값 또는 최빈값이고,

상기 제N+1 라인 대표값은 상기 제N+1 라인 데이터에서 선택된 제2 색 데이터들의 평균값 또는 최빈값인 것을 특징으로 하는 액정표시장치.

**청구항 7**

제 2 항에 있어서,

상기 타이밍 콘트롤러는,

상기 제N 라인 데이터와 상기 제N+1 라인 데이터의 계조 차이를 바탕으로 솔리드 데이터를 검색하고,

상기 솔리드 데이터를 포함한 솔리드 블록의 픽셀들에 공급될 데이터 전압의 주파수를 낮게 제어하는 것을 특징으로 하는 액정표시장치.

**청구항 8**

제 7 항에 있어서,

상기 타이밍 콘트롤러는,

상기 솔리드 블록 이외의 나머지 픽셀들에 공급될 데이터 전압의 주파수를 높게 제어하는 것을 특징으로 하는 액정표시장치.

**청구항 9**

제 1 항 내지 제 8 항 중 어느 한 항에 있어서,

상기 표시패널에서 상기 데이터 전압이 가변되는 영역은 다른 표시 영역의 액정셀들 비하여 액정셀의 데이터 전압 충전율인 낮은 국부 영역인 것을 특징으로 하는 액정표시장치.

**청구항 10**

제 1 항 내지 제 8 항 중 어느 한 항에 있어서,

상기 표시패널에서 상기 데이터 전압이 가변되는 영역은 다른 표시 영역의 액정셀들 비하여 액정셀의 데이터 전압 충전율인 낮은 국부 영역이고,

상기 데이터 구동부는 상기 데이터 라인들의 일측 끝단에 연결된 싱글 뱅크 타입의 데이터 구동부이고,

상기 게이트 구동부는 상기 게이트 라인들의 일측 끝단에 연결된 싱글 뱅크 타입의 게이트 구동부인 것을 특징으로 하는 액정표시장치.

**청구항 11**

제 1 항 내지 제 8 항 중 어느 한 항에 있어서,

상기 표시패널에서 상기 데이터 전압이 가변되는 영역은 다른 표시 영역의 액정셀들 비하여 액정셀의 데이터 전압 충전율인 낮은 국부 영역이고,

상기 데이터 구동부는 상기 데이터 라인들의 일측 끝단에 연결된 싱글 뱅크 타입의 데이터 구동부이고,

상기 게이트 구동부는 상기 게이트 라인들의 일측 끝단에 연결된 제1 게이트 구동부와, 상기 게이트 라인들의 타측 끝단에 연결된 제2 게이트 구동부를 포함하는 더블 뱅크 타입의 게이트 구동부인 것을 특징으로 하는 액정표시장치.

**청구항 12**

데이터 라인들과 게이트 라인들이 교차되고 픽셀들이 매트릭스 타입으로 배치된 표시패널, 상기 데이터 라인들에 데이터 전압을 공급하는 데이터 구동부, 상기 데이터 전압들과 동기되는 게이트필스를 상기 게이트 라인들에 순차적으로 공급하는 게이트 구동부 및 상기 데이터 구동부와 상기 게이트 구동부의 동작 타이밍을 제어하는 타이밍 콘트롤러를 포함하는 액정표시장치의 구동 방법에 있어서,

상기 표시패널의 제N(N은 양의 정수) 라인에 배치된 픽셀들에 기입될 제N 라인 데이터와, 상기 표시패널의 제N+1 라인의 픽셀들에 기입될 제N+1 라인 데이터 간의 계조 차이를 계산하는 단계; 및

상기 계조 차이가 미리 설정된 기준값 보다 클 때 상기 데이터 구동부와 상기 게이트 구동부의 동작 주파수를

낮추어 상기 데이터 전압의 주파수를 낮게 제어하는 단계를 포함하는 것을 특징으로 하는 액정표시장치의 구동 방법.

### 청구항 13

제 12 항에 있어서,

상기 계조 차이가 상기 기준값 이하로 작을 때 상기 데이터 구동부와 상기 게이트 구동부의 동작 주파수를 높여 상기 데이터 전압의 주파수를 높게 제어하는 단계를 더 포함한 것을 특징으로 하는 액정표시장치의 구동 방법.

### 명세서

#### 기술 분야

[0001]

본 발명은 데이터의 구동 주파수를 가변하는 액정표시장치와 그 구동 방법에 관한 것이다.

### 배경기술

[0002]

액티브 매트릭스(Active Matrix) 구동방식의 액정표시장치는 스위칭 소자로서 박막트랜지스터(Thin Film Transistor : 이하 "TFT"라 함)를 이용하여 동영상을 표시하고 있다. 액정표시장치의 액정셀들은 화소전극에 공급되는 데이터 전압과 공통전극에 공급되는 공통전압의 전위차에 따라 투과율을 변화시킴으로써 화상을 표시한다.

[0003]

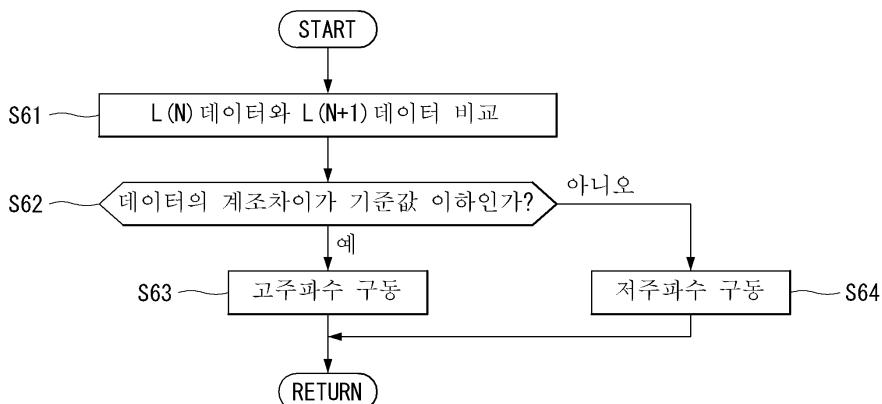

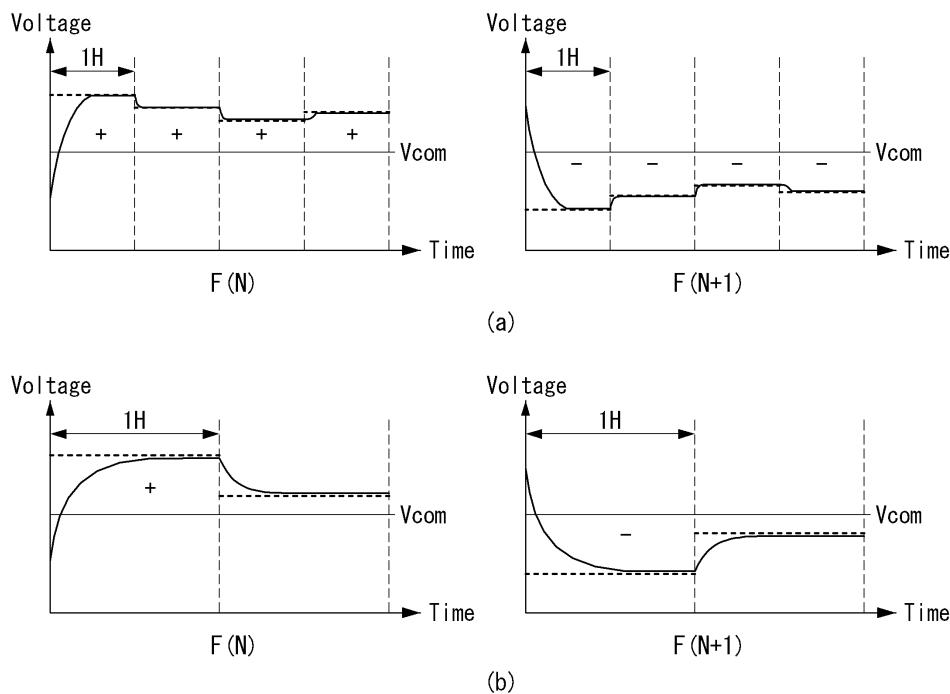

액정표시장치는 도 1과 같이 액정셀에 충전되는 데이터 전압에 따라 입력 영상의 계조를 표현하고 있고 잔상과 플리커를 방지하기 위하여 데이터 전압의 극성을 매 프레임 기간( $F(N)$ ,  $F(N+1)$ ) 마다 반전시키고 있다. 도 1에서 '1H'는 1 수평기간이고,  $F(N)$ 은 제 $N$ ( $N$ 은 양의 정수) 프레임 기간,  $F(N+1)$ 은 제 $N+1$  프레임 기간을 각각 의미한다.

[0004]

액정표시장치에서, 입력 영상 데이터의 계조 차이가 클수록 액정셀에 공급되는 데이터 전압의 차이가 커진다. 도 1은 같은 데이터 라인을 통해 4 개의 액정셀들에 데이터 전압이 4 수평 기간 동안 연속적으로 공급되는 예를 보여 준다. 도 1의 (a)와 같이, 데이터 전압의 계조 차이가 작으면 액정셀의 전압이 목표 계조 전압까지 충전될 수 있다. 이에 비하여, 데이터 전압의 계조 차이가 크면 도 1의 (b)와 같이 액정셀의 전압이 목표 계조 전압까지 충전되지 않을 수 있다. 액정표시장치의 화면 크기가 커지고 해상도가 높아지면 액정표시패널의 저항(Resistance)과 용량(Capacitance)이 커져 데이터 라인을 통해 공급되는 데이터 전압의 RC 지연이 커진다. 따라서, 고해상도의 대화면 액정표시장치에서는 화면 위치에 따라 액정셀의 충전 특성의 차이가 커지므로 도 1과 같은 데이터 전압의 미충전 문제가 더 심하게 나타난다.

### 발명의 내용

#### 해결하려는 과제

[0005]

본 발명은 고해상도의 대화면 액정표시장치에서 액정셀들의 데이터 전압 충전 특성을 개선할 수 있는 액정표시장치와 그 구동 방법을 제공한다.

### 과제의 해결 수단

[0006]

본 발명의 액정표시장치는 데이터 라인들과 게이트 라인들이 교차되고 픽셀들이 매트릭스 타입으로 배치된 표시 패널; 상기 데이터 라인들에 데이터 전압을 공급하는 데이터 구동부; 상기 데이터 전압들과 동기되는 게이트펄스를 상기 게이트 라인들에 순차적으로 공급하는 게이트 구동부; 및 상기 표시패널의 제 $N$ ( $N$ 은 양의 정수) 라인에 배치된 픽셀들에 기입될 제 $N$  라인 데이터와, 상기 표시패널의 제 $N+1$  라인의 픽셀들에 기입될 제 $N+1$  라인 데이터 간의 계조 차이가 미리 설정된 기준값 보다 클 때 상기 데이터 구동부와 상기 게이트 구동부의 동작 주파수를 낮추어 상기 데이터 전압의 주파수를 낮게 제어하는 타이밍 콘트롤러를 포함한다.

[0007] 상기 액정표시장치의 구동 방법은 상기 표시패널의 제N 라인에 배치된 픽셀들에 기입될 제N 라인 데이터와, 상기 표시패널의 제N+1 라인의 픽셀들에 기입될 제N+1 라인 데이터 간의 계조 차이를 계산하는 단계; 및 상기 계조 차이가 미리 설정된 기준값 보다 클 때 상기 데이터 구동부와 상기 게이트 구동부의 동작 주파수를 낮추어 상기 데이터 전압의 주파수를 낮게 제어하는 단계를 포함한다.

### 발명의 효과

[0008] 본 발명의 액정표시장치는 제N 라인 데이터와 제N+1 라인 데이터를 비교하여 그 라인 데이터들 간의 계조 차이가 클 때 데이터 전압의 주파수를 낮게 제어한다. 그 결과, 본 발명의 액정표시장치는 고해상도 및 대화면에서도 액정셀들의 데이터 전압 충전 특성을 균일하게 제어할 수 있으므로 표시품질을 향상시킬 수 있다.

### 도면의 간단한 설명

[0009] 도 1은 데이터의 계조 차이에 따른 액정셀의 충전 차이를 보여 주는 과정도이다

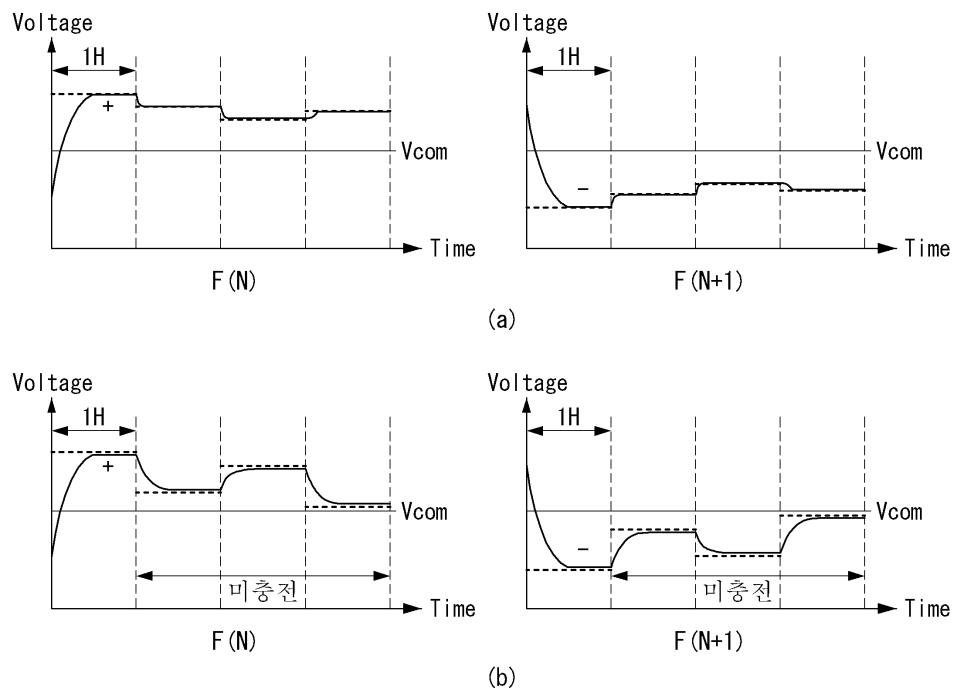

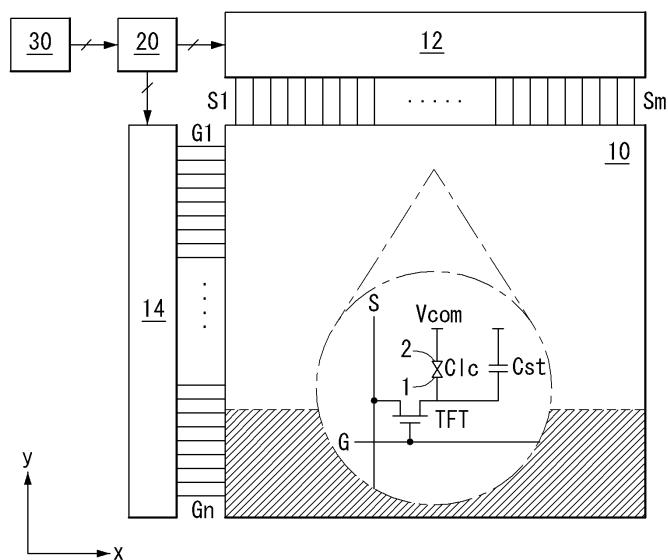

도 2 및 도 3은 본 발명의 실시예에 따른 액정표시장치를 나타내는 블록도들이다.

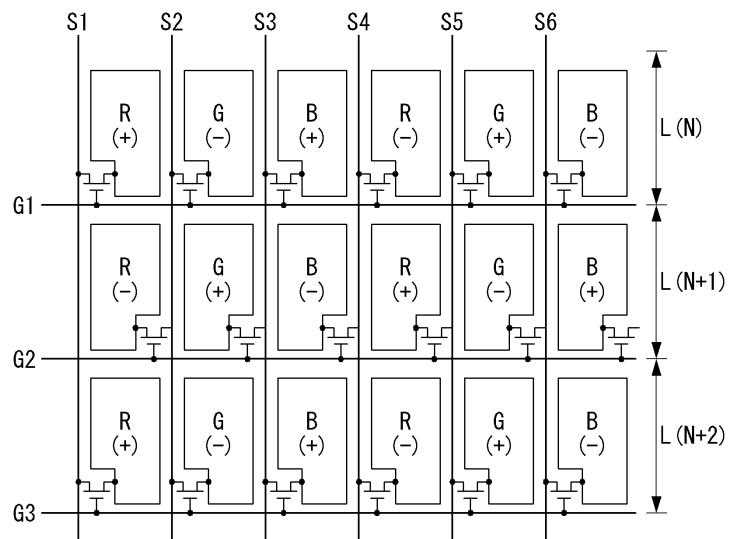

도 4는 도 2 및 도 3에 도시된 표시패널의 TFT 어레이 일부를 보여 주는 등가 회로도이다.

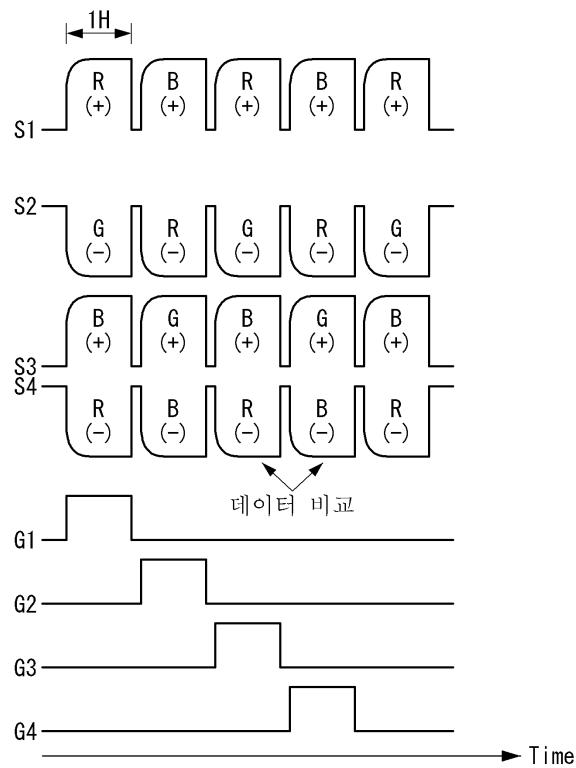

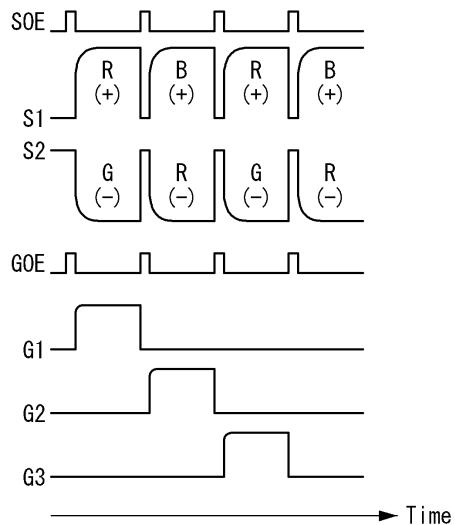

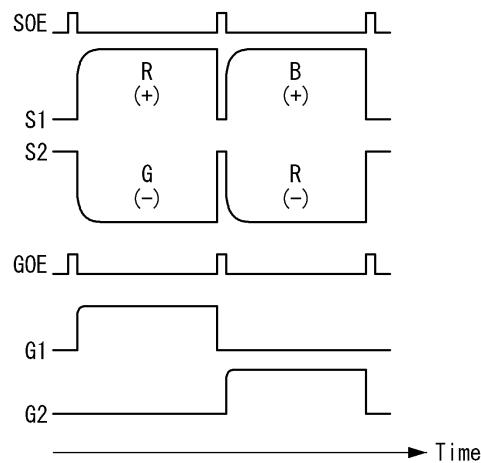

도 5는 도 4에 도시된 TFT 어레이에 인가되는 데이터 전압과 게이트 펄스를 보여 주는 과정도이다.

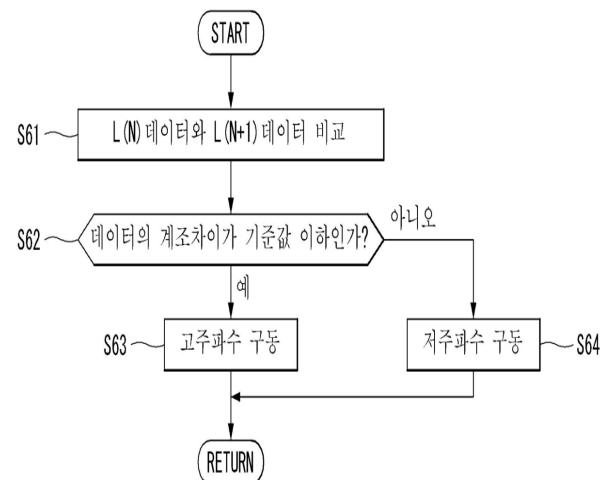

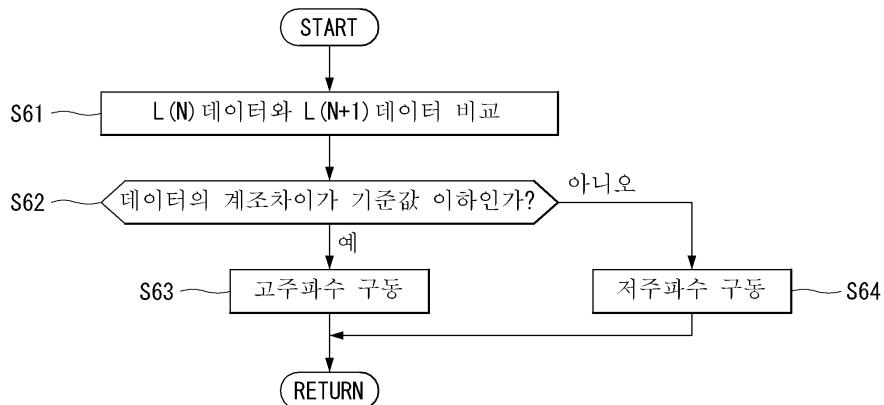

도 6은 본 발명의 제1 실시예에 따른 액정표시장치의 구동 방법을 보여 주는 흐름도이다.

도 7은 본 발명의 실시예에 따른 액정표시장치의 구동 방법에서 액정셀들에 충전되는 데이터 전압의 주파수 가변 예를 보여 주는 도면이다.

도 8은 본 발명의 실시예에 따른 액정표시장치의 구동 방법에서 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 작을 때 데이터 전압과 게이트 펄스를 보여 주는 과정도이다.

도 9는 본 발명의 실시예에 따른 액정표시장치의 구동 방법에서 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 클 때 데이터 전압과 게이트 펄스를 보여 주는 과정도이다.

도 10은 버티컬 블랭크 기간을 보여 주는 입력 타이밍 신호들의 과정도이다.

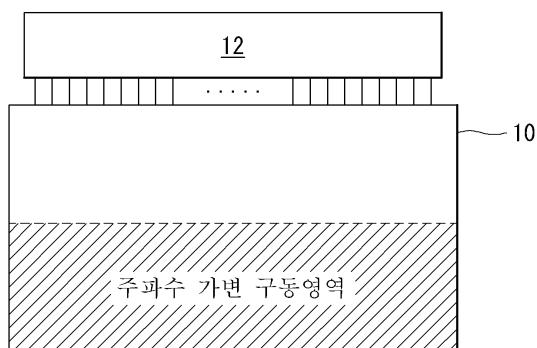

도 11은 표시패널 내의 일부 영역으로 설정된 주파수 가변 구동 영역의 일 예를 보여 주는 도면이다.

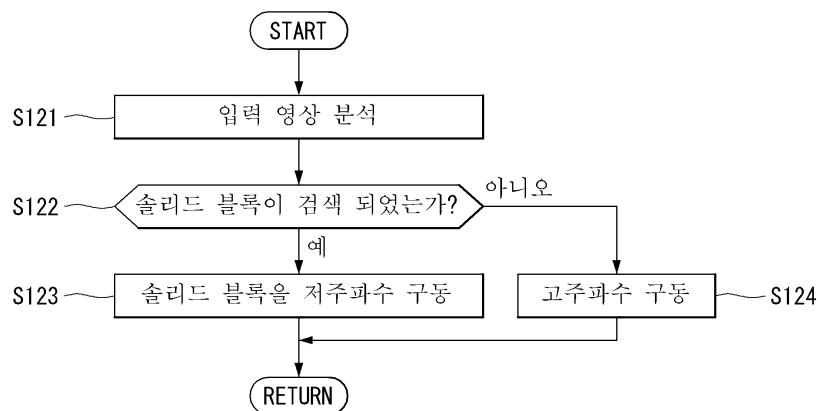

도 12는 본 발명의 제1 실시예에 따른 액정표시장치의 구동 방법을 보여 주는 흐름도이다.

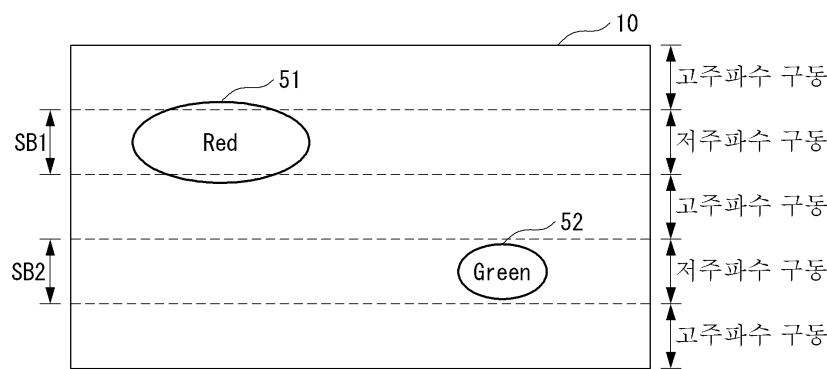

도 13은 표시패널에서 솔리드 블록의 일 예를 보여 주는 도면이다.

### 발명을 실시하기 위한 구체적인 내용

[0010] 이하 첨부된 도면을 참조하여 본 발명에 따른 바람직한 실시예들을 상세히 설명한다. 명세서 전체에 걸쳐서 동일한 참조번호들은 실질적으로 동일한 구성요소들을 의미한다. 이하의 설명에서, 본 발명과 관련된 공지 기능 혹은 구성에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우, 그 상세한 설명을 생략한다.

[0011] 도 2는 액정표시장치의 더블 뱅크(double bank) 구동회로를 보여 준다. 도 3은 액정표시장치의 싱글 뱅크(single bank) 구동회로를 보여 준다.

[0012] 도 2 및 도 3을 참조하면, 본 발명의 실시예에 따른 액정표시장치는 표시패널(10), 타이밍 콘트롤러(20), 데이터 구동부(12, 12A, 12B), 및 게이트 구동부(14, 14A, 14B)를 구비한다.

[0013] 표시패널(10)은 두 장의 유리기판 사이에 액정층이 형성된다. 액정표시패널은 데이터 라인들(S1~Sm)과 게이트 라인들(G1~Gn)의 교차 구조에 의해 매트릭스 형태로 배치된 픽셀들을 포함한다. 픽셀들은 도 4와 같이 적색 서브픽셀, 녹색 서브픽셀, 및 청색 서브픽셀로 나뉘어진다. 서브픽셀들 각각은 액정셀들(C1c), TFT, 및 스토리지 커패시터(Cst)를 포함한다.

[0014] 표시패널(10)에서 입력 영상이 표시되는 픽셀 어레이는 TFT 어레이와 컬러 필터 어레이로 나뉘어진다. 표시패

널(10)의 하부 유리기판에는 도 4와 같은 TFT 어레이가 형성된다. TFT 어레이는 데이터 라인들(S1~Sm), 데이터 라인들(S1~Sm)과 교차하는 게이트 라인들(G1~Gn), 액정셀들(Cl1c)의 화소전극(1)에 접속된 TFT들, 및 스토리지 커페시터(Cst) 등을 포함한다. 액정셀들(Cl1c)은 TFT에 접속되어 화소전극들(1)과 공통전극(2) 사이의 전계에 의해 구동된다. 표시패널(10)의 상부 유리기판 상에는 블랙매트릭스, 컬러필터 등을 포함한 컬러 필터 어레이가 형성된다. 표시패널(10)의 상부 유리기판과 하부 유리기판 각각에는 편광판이 부착되고 액정의 프리틸트각(pre-tilt angle)을 설정하기 위한 배향막이 형성된다.

[0015] 공통전극(2)은 TN(Twisted Nematic) 모드와 VA(Vertical Alignment) 모드와 같은 수직전계 구동방식에서 상부 유리기판 상에 형성되며, IPS(In Plane Switching) 모드와 FFS(Fringe Field Switching) 모드와 같은 수평전계 구동방식에서 화소전극(1)과 함께 하부 유리기판 상에 형성된다.

[0016] 본 발명에서 적용 가능한 표시패널(10)은 TN 모드, VA 모드, IPS 모드, FFS 모드뿐 아니라 어떠한 액정모드로도 구현될 수 있다. 본 발명의 액정표시장치는 투과형 액정표시장치, 반투과형 액정표시장치, 반사형 액정표시장치 등 어떠한 형태로도 구현될 수 있다. 투과형 액정표장치와 반투과형 액정표시장치에서는 백라이트 유닛이 필요하다. 백라이트 유닛은 직하형(direct type) 백라이트 유닛 또는, 에지형(edge type) 백라이트 유닛으로 구현될 수 있다.

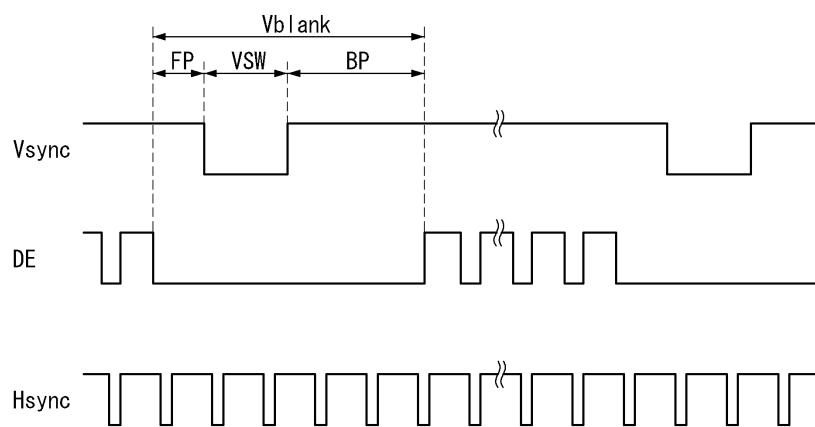

[0017] 타이밍 콘트롤러(20)는 호스트 시스템(Host system)(30)으로부터 입력된 입력 영상의 디지털 비디오 데이터를 데이터 구동부(12A, 12B)에 공급한다. 타이밍 콘트롤러(20)는 호스트 시스템(30)으로부터 수직 동기신호(Vsync), 수평 동기신호(Hsync), 데이터 인에이블 신호(Data Enable, DE), 클럭(CLK) 등의 타이밍신호를 입력 받는다. 도 10은 수직 동기신호(Vsync), 수평 동기신호(Hsync), 데이터 인에이블 신호(Data Enable, DE)을 보여 준다.

[0018] 타이밍 콘트롤러(20)는 호스트 시스템(30)으로부터 입력된 타이밍 신호를 바탕으로 데이터 구동부(12A, 12B)와 게이트 구동부(14A, 14B)의 동작 타이밍을 제어하기 위한 타이밍 제어신호들을 발생한다. 타이밍 제어신호들은 게이트 구동부(14, 14A, 14B)의 동작 타임을 제어하기 위한 게이트 타이밍 제어신호와, 데이터 구동부(12, 12A, 12B)의 동작 타이밍과 데이터 전압의 수직 극성을 제어하기 위한 데이터 타이밍 제어신호를 포함한다.

[0019] 게이트 타이밍 제어신호는 게이트 스타트 펄스(GSP), 게이트 시프트 클럭(GSC), 게이트 출력 인에이블신호(GOE) 등을 포함한다. 게이트 스타트 펄스(GSP)는 게이트 구동부(14, 14A, 14B)를 구성하는 게이트 드라이브 IC(Integrated Circuit)의 동작 스타트 타이밍을 제어한다. 게이트 시프트 클럭(GSC)은 게이트 드라이브 IC들에 공통으로 입력되는 클럭신호로써 게이트 펄스의 시프트 타이밍을 제어한다. 게이트 출력 인에이블신호(GOE)는 게이트 드라이브 IC들의 출력 타이밍을 제어한다.

[0020] 데이터 타이밍 제어신호는 소스 스타트 펄스(SSP), 소스 샘플링 클럭(SSC), 극성제어신호(POL), 소스 출력 인에이블신호(SOE) 등을 포함한다. 소스 스타트 펄스(SSP)는 데이터 구동부(12, 12A, 12B)를 구성하는 소스 드라이브 IC들의 데이터 샘플링 시작 타이밍을 제어한다. 소스 샘플링 클럭(SSC)은 소스 드라이브 IC들 각각에서 데이터의 샘플링 타이밍을 제어하는 클럭신호이다. 소스 출력 인에이블신호(SOE)는 데이터 구동부(12, 12A, 12B)의 출력 타이밍을 제어한다. 타이밍 콘트롤러(20)와 데이터 구동부(12, 12A, 12B) 사이에서 신호 전송을 위한 인터페이스가 mini LVDS(Low Voltage Differential Signaling)이면, 소스 스타트 펄스(SSP)와 소스 샘플링 클럭(SSC)은 생략될 수 있다.

[0021] 타이밍 콘트롤러(20)는 도 6과 같이 표시패널(10)에서 이웃한 라인들의 데이터를 비교하여 그 데이터들의 계조 차이가 크면 데이터 구동회로(12, 12A, 12B)와 게이트 구동회로(14, 14A, 14B)의 동작 타이밍을 제어하여 그 라인들에 표시될 데이터 전압의 구동 주파수를 낮춘다. 데이터 전압의 구동 주파수가 낮아지면 액정셀(Cl1c)의 데이터 전압 충전시간이 길어지기 때문에 도 1의 (b)와 같이 데이터들 간의 계조 차이가 클 때에도 액정셀의 데이터 전압 충전율을 높일 수 있다. 타이밍 콘트롤러(20)는 도 6과 같이 표시패널(10)에서 이웃한 라인들의 데이터를 비교하여 그 데이터들의 계조 차이가 상대적으로 작으면 데이터 구동회로(12, 12A, 12B)와 게이트 구동회로(14, 14A, 14B)의 동작 타이밍을 제어하여 그 라인들에 표시될 데이터 전압의 구동 주파수를 높인다. 데이터 전압의 구동 주파수가 낮아지면 액정셀(Cl1c)의 데이터 전압 충전시간이 짧아진다. 도 1의 (a)와 같이 데이터들 간의 계조 차이가 작으면 액정셀은 짧은 시간 내에 데이터 전압을 목표 계조 전압까지 충전한다. 따라서, 타이밍 콘트롤러(20)는 데이터의 계조 차이로 인한 액정셀들의 충전을 차이를 줄일 수 있다. 이를 위하여, 타이밍 콘트롤러(20)는 2 라인 분량의 데이터를 저장하는 라인 메모리, 2 라인 데이터를 비교하는 데이터 비교부, 데이터 비교 결과 데이터 구동부(12, 12A, 12B)와 게이트 구동부(14, 14A, 14B)의 동작 타이밍 주파수를 제어하는 타이밍 제어신호 발생부 등을 포함한다.

- [0022] 데이터 구동부(12, 12A, 12B)는 하나 이상의 소스 드라이브 IC들을 포함한다. 소스 드라이브 IC들 각각은 시프트 레지스터, 래치, 디지털-아날로그 변환기, 출력 버퍼 등을 포함한다. 소스 드라이브 IC들은 타이밍 콘트롤러(20)의 제어 하에 디지털 비디오 데이터(RGB)를 래치한다. 소스 드라이브 IC들은 디지털 비디오 데이터(RGB)를 아날로그 정극성/부극성 감마보상전압으로 변환하여 데이터 전압을 발생하고 극성제어신호(POL)에 응답하여 그 데이터 전압의 극성을 반전시킨다. 소스 드라이브 IC들은 소스 출력 인에이블 신호(SOE)에 응답하여 데이터 전압을 데이터 라인들(S1~Sm)로 출력한다. 이러한 소스 드라이브 IC들은 도 5와 같이 제N 프레임 기간 동안 기수 번째 데이터 라인들(S1, S3, ..., Sm-1)에 제1 극성의 데이터 전압을 공급하고, 우수 번째 데이터 라인들(S2, S2, ..., Sm)에 제2 극성의 데이터 전압을 공급하고, 제N+1 프레임 기간에 데이터 전압의 극성을 반전시킨다. 따라서, 본 발명의 소스 드라이브 IC들은 데이터 라인들에 공급되는 전압의 극성을 1 프레임 기간 동안 같은 극성을 유지하고, 다음 프레임 기간에 데이터 전압의 극성을 반전시키므로 매 수평 기간마다 극성을 반전시키는 소스 드라이브 IC들에 비하여 전류 소비가 작기 때문에 소비전력을 줄일 수 있다.

- [0023] 게이트 구동부(14, 14A, 14B)의 게이트 드라이브 IC들은 시프트 레지스터와 레벨 쉬프터를 포함한다. 게이트 구동부(14A, 14B)는 게이트 타이밍 제어신호에 응답하여 데이터 전압에 동기되는 게이트펄스를 게이트 라인들(G1~Gn)에 순차적으로 공급한다.

- [0024] 호스트 시스템(30)은 텔레비전 시스템, 홈 시어터 시스템, 셋톱박스, 네비게이션 시스템, DVD 플레이어, 블루레이 플레이어, 개인용 컴퓨터(PC), 폰 시스템(Phone system) 중 어느 하나로 구현될 수 있다. 호스트 시스템(30)은 입력 영상의 디지털 비디오 데이터(RGB)를 표시패널(10)의 해상도에 맞게 스케일링한다. 호스트 시스템(30)은 입력 영상의 디지털 비디오 데이터(RGB)와 함께 타이밍 신호들(Vsync, Hsync, DE, MCLK)을 타이밍 콘트롤러(20)로 전송한다.

- [0025] 도 2에 도시된 더블 뱅크 구동 회로는 표시패널(10)의 상단에 배치되는 제1 데이터 구동부(12A), 표시패널(10)의 하단에 배치된 제2 데이터 구동부(12B), 표시패널(10)의 좌측에 배치되는 제1 게이트 구동부(14A), 및 표시패널(10)의 좌측에 배치되는 제2 게이트 구동부(14B)를 포함한다. 제1 데이터 구동부(12A)는 데이터 라인들(S1~Sm)의 상측 끝단에 연결된 데이터 패드들을 통해 그 데이터 라인들(S1~Sm)에 데이터 전압을 공급한다. 제2 데이터 구동부(12B)는 데이터 라인들(S1~Sm)의 하측 끝단에 연결된 데이터 패드들을 통해 그 데이터 라인들(S1~Sm)에 데이터 전압을 공급한다. 제1 및 제2 데이터 구동부(12A, 12B)는 타이밍 콘트롤러(20)의 제어 하에 동시에 동작하여 데이터 라인들(S1~Sm)의 양쪽에서 동시에 데이터 전압을 공급함으로써 데이터 라인들(S1~Sm)의 RC 딜레이를 보상한다. 제1 게이트 구동부(14A)는 게이트 라인들(G1~Gn)의 좌측 끝단에 연결된 게이트 패드들을 통해 그 게이트 라인들(G1~Gn)에 데이터 전압에 동기되는 게이트 펄스를 공급한다. 제2 게이트 구동부(14B)는 게이트 라인들(G1~Gn)의 우측 끝단에 연결된 게이트 패드들을 통해 그 게이트 라인들(G1~Gn)에 데이터 전압에 동기되는 게이트 펄스를 공급한다. 제1 및 제2 게이트 구동부(14A, 14B)는 타이밍 콘트롤러(20)의 제어 하에 동시에 동작하여 게이트 라인들(G1~Gn)의 양쪽에서 동시에 데이터 전압을 공급함으로써 게이트 라인들(G1~Gn)의 RC 딜레이를 보상한다. 이러한 더블 뱅크 구동회로는 RC 딜레이를 보상하여 액정셀들(ClC)의 충전율 편차를 줄일 수 있으나, 더블 뱅크 구동 회로를 구현하기 위하여 필요한 IC 개수가 도 3의 싱글 뱅크 구현회로에 비하여 많아지기 때문에 액정표시장치의 비용 상승을 초래한다.

- [0026] 도 3과 같은 싱글 뱅크 구동 회로는 표시패널(10)의 상단 또는 하단에 배치되는 데이터 구동부(12), 표시패널(10)의 좌측 또는 우측에 배치되는 게이트 구동부(14)를 포함한다. 이러한 싱글 뱅크 구동 회로는 데이터 라인들의 일측 끝단을 통해 데이터 전압을 공급하고 게이트 라인들의 일측 끝단을 통해 게이트 펄스를 공급하기 때문에 데이터 라인들을 타측 끝단으로 갈수록 그리고 게이트 라인들의 타측 끝단으로 갈수록 커지는 RC 딜레이로 인하여 액정셀들의 데이터 전압 충전율이 낮아진다. 반면에 싱글 뱅크 구동회로는 필요한 IC 개수가 더블 뱅크 구동회로에 비하여 작기 때문에 액정표시장치의 단가를 낮출 수 있다. 이러한 싱글 뱅크 구동회로는 종래 기술에서 주로 중소형 크기의 액정표시장치에 적용되고 있다.

- [0027] 본 발명의 액정표시장치의 구동회로는 싱글 뱅크 데이터 구동부(12)와 더블 뱅크 구동부(14A, 14B)의 조합으로 구현될 수도 있다. 본 발명은 대화면 및 고해상도 액정표시장치에 적용하고 이하에서 설명되는 구동 방법을 적용하여 화면 전체에서 액정셀들의 충전율을 비슷한 수준으로 제어한다.

- [0028] 도 4는 도 2 및 도 3에 도시된 표시패널의 TFT 어레이 일부를 보여 주는 등가 회로도이다. 도 5는 도 4에 도시된 TFT 어레이에 인가되는 데이터 전압과 게이트 펄스를 보여 주는 과정도이다.

- [0029] 도 4 및 도 5를 참조하면, 표시패널(10)의 기수 번째 라인들(L(N), L(N+2))은 데이터라인들(S1~S6)의 우측에 배치된 화소전극에 연결되는 TFT들을 포함한다. 표시패널(10)의 우수 번째 라인들(L(N+1))은 데이터라인들

(S1~S6)의 좌측에 배치된 화소전극에 연결되는 TFT들을 포함한다. 따라서, 하나의 데이터 라인에 컬럼 방향(도 2 및 도 3의 y축 방향)을 따라 연결된 TFT들은 그 데이터 라인의 좌측과 우측에 번갈아가며 연결되어 지그재그(zigzag) 형태로 배치된다.

[0030] 데이터 구동부(12, 12A, 12B)의 소스 드라이브 IC들은 1 프레임 기간 동안 기수 번째 데이터 라인들(S1, S3, ..., Sm-1)에 제1 극성의 데이터 전압을 공급하고, 우수 번째 데이터 라인들(S2, S4, ..., Sm)에 제2 극성의 데이터 전압을 공급한다. 따라서, 1 프레임 기간 동안 하나의 데이터 라인에 연속으로 공급되는 데이터 전압의 극성은 같은 극성을 유지한다. 이렇게 하나의 데이터 라인에 같은 극성이 데이터 전압이 1 프레임 기간 동안 공급되면, 라인 방향(도 2 및 도 3의 x축 방향)에서 이웃하는 픽셀들은 TFT들의 지그재그 배치로 인하여 1 도트(dot) 단위로 극성이 상반된 데이터 전압을 충전한다. 여기서, 1 도트는 1 서브 픽셀 또는 1 액정셀을 의미한다. 또한, 컬럼 방향(도 2 및 도 3의 y축 방향)에서 이웃하는 픽셀들은 TFT들의 지그재그 배치로 인하여 1 도트(dot) 단위로 극성이 상반된 데이터 전압을 충전한다. 따라서, 데이터 구동부(12, 12A, 12B)의 소스 드라이브 IC들은 컬럼 인버전 방식으로 데이터 전압의 극성을 반전시키고, 표시패널(10)의 픽셀들은 1 도트 인버전 방식으로 반전되는 데이터 전압을 충전한다.

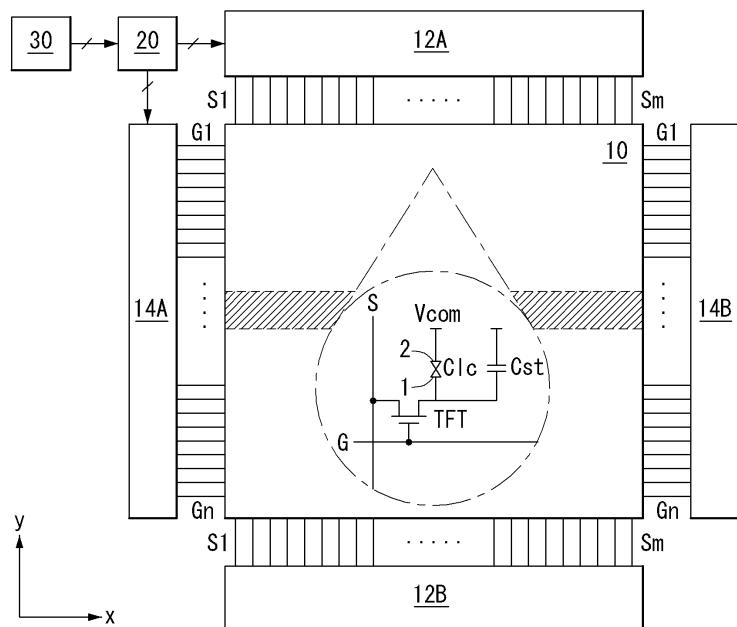

[0031] 도 6은 본 발명의 제1 실시예에 따른 액정표시장치의 구동 방법을 보여 주는 흐름도이다. 이 구동 방법은 타이밍 콘트롤러(20)에 의해 제어된다. 도 7은 본 발명의 실시예에 따른 액정표시장치의 구동 방법에서 액정셀들에 충전되는 데이터 전압의 주파수 가변 예를 보여 주는 도면이다. 도 7에서 '1H'는 1 수평기간이고, F(N)은 제N 프레임 기간, F(N+1)은 제N+1 프레임 기간을 각각 의미한다.

[0032] 도 6 및 도 7을 참조하면, 타이밍 콘트롤러(20)는 제N 라인 데이터와 제N+1 라인 데이터들 간의 계조 차이를 계산하고, 그 계조 차이를 소정의 기준값과 비교한다.(S61) 제N 라인 데이터는 제N 라인(L(N))에 배치된 픽셀들에 기입될 데이터이고, 제N+1 라인 데이터는 제N+1 라인(L(N+1))에 배치된 픽셀들에 기입될 데이터이다.

[0033] S61 단계의 데이터 비교 방법은 다양한 방법이 가능하다. 데이터 비교 방법의 일 예는 특정 데이터 라인에 연결된 이웃한 서브 픽셀들에 기입될 데이터들을 비교하는 방법이다. 예를 들어, 도 4에서 제4 데이터 라인(S4)에는 제N 수평 기간에 적색(R) 데이터에 공급된 후에, 제N+1 수평 기간에 청색(B) 데이터가 공급된다. 적색 데이터는 제N 라인(L(N))에서 TFT를 통해 제4 데이터 라인(S4)의 우측에 연결된 적색 서브픽셀에 기입된다. 청색 데이터는 제N+1 라인(L(N+1))에서 TFT를 통해 제4 데이터 라인(S4)의 좌측에 연결된 청색 서브픽셀에 기입된다. 데이터 비교 방법은 제4 데이터 라인(S4)에 연속으로 공급되는 적색 데이터(또는 제1 색 데이터)와 청색 데이터(또는 제2 색 데이터)의 계조 차이를 계산하고, 그 계조 차이를 소정의 기준값과 비교할 수 있다. 마찬가지로, 데이터 비교 방법은 제3 데이터 라인(S3)에 연속으로 공급되는 청색 데이터(또는 제1 색 데이터)와 녹색 데이터(또는 제2 색 데이터)의 계조 차이를 계산하고, 그 계조 차이를 소정의 기준값과 비교할 수 있다.

[0034] 데이터 비교 방법의 다른 예는 라인 데이터들의 대표값들을 비교하는 방법이다. 여기서 라인 데이터들의 대표값들은 제N 라인 대표값과, 제N+1 라인 데이터의 대표값을 포함한다. 예를 들어, 데이터 비교 방법은 제N 라인의 적색 데이터들(또는 제1 색 데이터들)을 바탕으로 계산된 제N 라인 대표값과, 제N+1 라인의 청색 데이터들(제2 색 데이터들)을 바탕으로 계산된 제N+1 라인 대표값 간의 계조 차이를 계산하고, 그 계조 차이를 소정의 기준값과 비교할 수 있다. 다른 방법으로, 데이터 비교 방법은 제N 라인의 청색 데이터들의 대표값과 제N+1 라인의 녹색 데이터들의 대표값의 계조 차이를 계산하고, 그 계조 차이를 소정의 기준값과 비교할 수 있다. 또 다른 방법으로, 데이터 비교 방법은 제N 라인의 녹색 데이터들의 대표값과 제N+1 라인의 적색 데이터들의 대표값의 계조 차이를 계산하고, 그 계조 차이를 소정의 기준값과 비교할 수 있다.

[0035] 대표값은 평균값이나 최빈값으로 계산될 수 있다. 예를 들어, 제N 라인 대표값은 제N 라인 데이터에서 선택된 제1 색 데이터들의 평균값 또는 최빈값으로 계산될 수 있다. 제N+1 라인 대표값은 제N+1 라인 데이터에서 선택된 제2 색 데이터들의 평균값 또는 최빈값으로 계산될 수 있다.

[0036] 타이밍 콘트롤러(20)는 도 7의 (a)와 같이 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 소정의 기준값 이하로 작으면 데이터라인들(S1~Sm)에 공급되는 데이터 전압의 주파수를 높게 제어한다.(S62 및 S63) 반면에, 타이밍 콘트롤러(20)는 도 7의 b와 같이 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 기준값보다 크면 데이터라인들(S1~Sm)에 공급되는 데이터 전압의 주파수를 상대적으로 낮게 제어한다.(S62 및 S64) 기준값은 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이와 데이터 전압 주파수를 조정하면서 액정셀들(C1c)의 충전율을 측정한 실험 결과를 바탕으로 결정될 수 있다. 기준값은 표시패널의 크기와 해상도, 표시패널의 구조, 구동 방법, 액정 모드에 따라 달라질 수 있다.

- [0037] 데이터 구동부(12, 12A, 12B)는 타이밍 콘트롤러(20)의 제어 하에 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 작을 때 도 7의 (a)와 같이 데이터 라인들(S1~Sm)로 출력되는 데이터 전압을 고주파수로 출력하는 반면, 그 계조 차이가 클 때 도 7의 (b)와 같이 데이터 라인들(S1~Sm)로 출력되는 데이터 전압의 주파수를 낮춘다. 게이트 구동부(14, 14A, 14B)는 타이밍 콘트롤러(20)의 제어 하에 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이에 따라 주파수가 달라지는 데이터 전압에 동기되는 게이트 펄스를 출력한다.

- [0038] 도 8은 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 작을 때 데이터 전압과 게이트 펄스를 보여 주는 파형도이다. 도 9는 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 클 때 데이터 전압과 게이트 펄스를 보여 주는 파형도이다.

- [0039] 타이밍 콘트롤러(20)는 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 작을 때 도 8과 같이 데이터 타이밍 제어신호와 게이트 타이밍 제어신호의 주파수를 높게 제어한다. 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 작을 때 발생되는 데이터 타이밍 제어신호와 게이트 타이밍 제어신호의 주파수는 종래 기술과 동등 수준일 수 있다. 데이터 구동부(12, 12A, 12B)는 소스 출력 인에이블 신호(SOE)의 로우(low) 로직 구간 동안 데이터 전압을 출력한다. 게이트 구동부(14, 14A, 14B)는 게이트 출력 인에이블 신호(GOE)의 로우 로직 구간 동안 데이터 전압에 동기되는 게이트 펄스를 출력한다.

- [0040] 타이밍 콘트롤러(20)는 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 클 때 도 9와 같이 데이터 타이밍 제어신호와 게이트 타이밍 제어신호의 주파수를 낮춘다. 예를 들어, 도 9에서 소스 출력 인에이블 신호(SOE)와 게이트 출력 인에이블 신호(GOE)는 도 8에 비하여 낮아진다.

- [0041] 본 발명은 프레임 레이트(Frame rate)와 프레임 기간을 고정한 경우에, 이웃한 라인 데이터들 간의 계조 차이가 클 때 주파수를 낮추면 프레임 기간이 부족할 수 있다. 이를 고려하여, 본 발명의 구동 방법은 프레임 레이트(Frame rate)와 프레임 기간을 고정하고 도 10에서 버티컬 블랭크 기간(Vblank) 내에서 표시패널의 데이터 어드레싱 시간을 연장할 수 있다.

- [0042] 도 10에서, 수직 동기신호(Vsync)는 1 프레임 기간의 주기를 가지며, 수평 동기신호(Hsync)와 데이터 인에이블 신호(DE)는 1 수평기간의 주기를 갖는다. 입력 영상의 1 라인 데이터은 데이터 인에이블 신호(DE)의 하이 로직 구간에 동기되어 타이밍 콘트롤러(20)에 입력된다. "FP"는 1 프레임 기간 내에서 마지막 데이터 인에이블 신호(DE)의 폴링 에지(falling edge)부터 수직 동기신호(Vsync)가 다시 시작되는 폴링 에지까지의 버티컬 프론트 포치(Vertical Front Porch, FP)이다. "VSW"는 수직 동기신호(Vsync)의 폴링 에지부터 그 직후의 라이징 에지(rising edge) 사이의 버티컬 싱크 위쓰(Vertical Sync Width, VSW) "BP"는 수직 동기신호(Vsync)의 라이징 에지부터 다음 프레임 기간의 제1 데이터 인에이블 신호(DE)의 라이징 에지까지의 버티컬 백 포치(Vertical Back, BP)이다. 버티컬 블랭크 기간(Vblank)은 버티컬 프론트 포치(FP), 버티컬 싱크 위쓰(VSW), 버티컬 백 포치(BP)를 합한 시간으로서, 입력 영상의 데이터가 없는 기간이다.

- [0043] 입력 영상의 데이터는 버티컬 블랭크 기간(Vblank) 동안 타이밍 콘트롤러(20)에 입력되지 않는다. 데이터 어드레싱 시간은 다음 프레임 데이터가 누락되지 않도록 다음 프레임 기간에서 데이터 인에이블 신호(DE)가 입력되는 액티브 기간까지 연장되어서는 안된다.

- [0044] 데이터 전압이 저주파수로 어드레싱되는 라인들이 많다면 데이터 어드레싱 시간의 연장 시간이 버티컬 블랭크 기간(Vblank)을 초과할 수 있다. 이를 고려하여, 본 발명은 도 11과 같이 표시패널(10)의 일부 영역을 주파수 가변 구동 영역으로 지정하고 나머지 영역을 주파수 고정 영역으로 설정할 수 있다. 주파수 가변 구동 영역은 버티컬 블랭크 기간(Vblank) 내에서 허용되는 추가 데이터 어드레스 기간 내에서 데이터가 어드레싱될 수 있는 최대 라인 개수를 포함한 국부 영역으로 정의된다. 주파수 가변 구동 영역은 표시패널(10)에서 RC 딜레이가 큰 영역으로 설정되는 것이 바람직하다. 이는 RC 딜레이가 큰 영역의 액정셀들이 다른 액정셀들에 비하여 데이터 전압 충전율이 낮기 때문이다. 도 2와 같이 더블 뱅크 구동회로가 적용된 경우에, 주파수 가변 구동 영역은 표시패널(10)에서 RC 딜레이가 큰 패널의 중앙 영역으로 지정될 수 있다. 도 3과 같이 싱글 뱅크 구동회로가 적용된 경우에, 주파수 가변 구동 영역은 표시패널(10)에서 데이터 구동부(12)의 반대측 이 RC 딜레이가 크기 때문에 데이터 구동부(12)의 반대측에 위치하는 표시패널(10)의 일측 가장자리 영역으로 지정될 수 있다. 도 2와 도 3에서 빛금친 부분이 주파수 가변 구동 영역으로 지정될 수 있다.

- [0045] 도 12은 본 발명의 제2 실시예에 따른 액정표시장치의 구동 방법을 보여 주는 흐름도이다. 이 구동 방법은 타이밍 콘트롤러(20)에 의해 제어된다. 도 13은 표시패널에서 솔리드 블록의 일 예를 보여 주는 도면이다.

- [0046] 도 12를 참조하면, 타이밍 콘트롤러(20)는 입력 영상을 분석하여 솔리드(solid) 데이터를 검출하고 그 솔리드

데이터가 소정 크기의 픽셀 영역 이상의 크기로 집중된 솔리드 블록을 검색한다.(S121) 솔리드 데이터는 적색, 녹색 및 청색 중 어느 한 색의 데이터만이 고계조이고 다른 색의 데이터가 저계조인 픽셀 데이터이다. 솔리드 데이터는 적색, 녹색 및 청색 데이터 중 어느 하나만이 고계조이므로 그 데이터들 간의 계조 차이가 크다. 따라서, 타이밍 콘트롤러(20)는 적색 데이터, 녹색 데이터 및 청색 데이터들 간의 계조 차이를 바탕으로 솔리드 데이터를 판단할 수 있다. 고계조와 저계조는 데이터의 최상위 비트(Most Significant Bit, MSB)로 판단될 수 있다. 예를 들여, 타이밍 콘트롤러(20)는 MSB 2 비트가 "11XXXXX<sub>2</sub>(X는 0 또는 1)"인 데이터를 고계조 데이터로 판단하고, MSB 2 비트가 "00XXXXX<sub>2</sub>"인 데이터를 저계조 데이터로 판단할 수 있다.

[0047] 입력 영상에서 도 13과 같이, 적색 영역(51)과 녹색 영역(52)이 포함된 경우에, 솔리드 블록은 적색 영역(51)을 포함한 제1 솔리드 블록(SB1)과, 녹색 영역(52)을 포함한 제2 솔리드 블록(SB2)을 포함한다. 도 4에서, 제4 데이터 라인(S4)을 통해 연속으로 공급되는 적색 데이터와 청색 데이터를 가정할 때, 적색 영역(51) 내에서 적색 데이터만 고계조이므로 적색 데이터와 청색 데이터의 계조 차이가 커진다. 도 4에서, 제3 데이터 라인(S3)을 통해 연속으로 공급되는 청색 데이터와 녹색 데이터를 가정할 때, 녹색 영역(52) 내에서 녹색 데이터만 고계조이므로 청색 데이터와 녹색 데이터의 계조 차이가 커진다.

[0048] 솔리드 블록(SB1, SB2)에서 데이터 라인들(S1~Sm)에 연속으로 공급되는 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 크다. 이러한 계조 차이로 인한 액정셀의 충전을 저하를 보상하기 위하여, 타이밍 콘트롤러(20)는 솔리드 블록(SB1, SB2)의 액정셀들에 공급될 데이터 전압의 주파수를 도 7의 (b)와 같이 낮춘다.(S122 및 S123) 타이밍 콘트롤러(20)는 솔리드 블록(SB1, SB2) 이외의 표시 영역의 액정셀들에 공급될 데이터 전압의 주파수를 도 7의 (a)와 같이 높인다.(S122 및 S124) 이는 솔리드 블록(SB1, SB2) 이외의 표시 영역에서 제N 라인 데이터와 제N+1 라인 데이터 간의 계조 차이가 크지 않아 액정셀의 데이터 전압 충전율이 높기 때문이다.

[0049] 버티컬 블랭크 기간(Vblank) 내에서 허용되는 추가 데이터 어드레스 기간을 고려하여, 솔리드 블록은 도 2, 도 3 및 도 11에서 벗금친 부분 같이 표시패널(10)에서 RC 딜레이가 큰 주파수 가변 구동 영역 내에서만 검색될 수 있다.

[0050] 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특허 청구의 범위에 의해 정하여져야만 할 것이다.

### 부호의 설명

|                        |                        |

|------------------------|------------------------|

| 10 : 표시패널              | 12, 12A, 12B : 데이터 구동부 |

| 14, 14A, 14B : 게이트 구동부 | 20 : 타이밍 콘트롤러          |

## 도면

## 도면1

## 도면2

도면3

도면4

## 도면5

## 도면6

## 도면7

## 도면8

## 도면9

## 도면10

## 도면11

## 도면12

## 도면13

|                |                                                                                           |         |            |

|----------------|-------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 标题 : 液晶显示装置及其驱动方法                                                                         |         |            |

| 公开(公告)号        | <a href="#">KR1020140081555A</a>                                                          | 公开(公告)日 | 2014-07-01 |

| 申请号            | KR1020120151441                                                                           | 申请日     | 2012-12-21 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                  |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                 |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                                 |         |            |

| [标]发明人         | KIM SUNG WON<br>김성원<br>LIM JONG JIN<br>임종진<br>LEE DONG WOO<br>이동우<br>HONG HEE JUNG<br>홍희정 |         |            |

| 发明人            | 김성원<br>임종진<br>이동우<br>홍희정                                                                  |         |            |

| IPC分类号         | G02F1/133 G09G3/36                                                                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                 |         |            |

## 摘要(译)

液晶显示装置及其驱动方法本发明涉及液晶显示装置及其驱动方法。根据本发明实施例的液晶显示装置包括显示面板，向数据线提供数据电压的数据驱动单元，栅极驱动单元和控制以降低数据频率的定时控制器当第N行的数据与( N + 1 )行的数据之间的灰度差大时，电压变为高。