(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2017-0045618

(43) 공개일자 2017년04월27일

(51) 국제특허분류(Int. Cl.)

*G02F 1/1337* (2006.01) *G02F 1/1343* (2006.01)

*G02F 1/1368* (2006.01)

(52) CPC특허분류

*G02F 1/1337* (2013.01)

*G02F 1/1343* (2013.01)

(21) 출원번호 10-2015-0145448

(22) 출원일자 2015년10월19일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

김슬기

경기도 파주시 가람로116번길 130, 710동 1902호

(와동동, 가람마을7단지 한라비발디)

(74) 대리인

박장원

전체 청구항 수 : 총 14 항

(54) 발명의 명칭 **균일한 배향막을 가진 액정표시소자**

### (57) 요 약

본 발명에서는 컨택홀 주위에 배치되는 화소전극에 의해 발생하는 단차를 제거하여 컨택홀내에 배향액을 유입하며, 이때, 컨택홀 주위의 화소전극의 일측 전체를 제거하여 배향액이 유입되는 유입통로를 형성할 수도 있고 일정 폭 및 길이의 특정 영역을 제거하여 유입통로를 형성하여 배향액이 상기 유입통로를 통해 컨택홀 내부에 원활하게 유입됨과 동시에 화소전극을 식각하기 위해 사용된 식각액의 침투경로를 최대로 연장하여 식각액이 화소전극 내부로 침투하는 것을 방지할 수 있게 된다.

**대 표 도** - 도8a

(52) CPC특허분류

*G02F 1/1368* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

복수의 화소를 포함하는 기판;

화소 각각에 배치된 박막트랜지스터;

화소 각각에 배치된 공통전극 및 화소전극;

화소에 배치되어 상기 박막트랜지스터와 화소전극을 접속하는 컨택홀; 및

상기 기판 전체에 걸쳐 배치된 배향막으로 구성되며,

상기 화소전극은 컨택홀 내부 및 컨택홀 주위에 배치되며, 상기 컨택홀 주위의 화소전극에는 컨택홀과 연결되어

배향막의 형성시 배향액이 유입되는 유입통로가 구비된 액정표시소자.

#### 청구항 2

제1항에 있어서, 상기 박막트랜지스터는,

제1기판에 배치된 게이트전극;

상기 게이트전극 위에 배치된 게이트절연층;

상기 게이트절연층 위에 배치된 반도체층;

상기 반도체층 위에 배치된 소스전극 및 드레인전극을 포함하는 액정표시소자.

#### 청구항 3

제2항에 있어서,

상기 박막트랜지스터를 덮는 제1보호층; 및

상기 공통전극 및 화소전극 사이에 배치된 제2보호층을 추가로 포함하는 액정표시소자.

#### 청구항 4

제3항에 있어서, 상기 컨택홀은 드레인전극 상부의 제1보호층 및 제2보호층에 형성되는 액정표시소자.

#### 청구항 5

제4항에 있어서, 상기 화소전극은 컨택홀 주위의 제2보호층 상부에 배치되는 액정표시소자.

#### 청구항 6

제5항에 있어서, 배향액 유입통로는 컨택홀 주위의 사각형상 화소전극의 4변중 적어도 일변 전체에 구성되는 액정표시소자.

#### 청구항 7

제5항에 있어서, 상기 배향액 유입통로는 컨택홀 주위의 화소전극에 소정의 폭으로 구성되는 액정표시소자.

#### 청구항 8

제7항에 있어서, 상기 배향액 유입통로는 컨택홀 주위의 화소전극에 소정의 폭으로 구비된 홈인 액정표시소자.

#### 청구항 9

제8항에 있어서, 상기 홈의 입구는 배향액의 퍼짐방향을 따라 배치되는 액정표시소자.

**청구항 10**

제7항에 있어서, 상기 배향액 유입통로는 사각형상, 지그재그형상 또는 곡면형상으로 이루어진 액정표시소자.

**청구항 11**

제7항에 있어서, 상기 배향액 유입통로는 화소전극에 복수개 구비되는 액정표시소자.

**청구항 12**

제4항에 있어서, 상기 공통전극은 제1보호층 상부에 배치되고 화소전극은 제2보호층 상부에 배치되며, 상기 공통전극은 언더컷되어 공간에 의해 화소전극과 전기적으로 절연되는 액정표시소자.

**청구항 13**

복수의 화소를 포함하는 기판;

화소 각각에 배치된 박막트랜지스터;

상기 기판 위에 배치된 제1보호층;

상기 화소의 제1보호층 위에 배치된 공통전극;

상기 공통전극 상부에 배치된 제2보호층;

상기 제2보호층 위에 배치되며, 상기 제1보호층 및 제2보호층에 형성된 컨택홀을 통해 박막트랜지스터와 접속되는 화소전극; 및

상기 기판 전체에 걸쳐 배치된 배향막으로 구성되며,

상기 화소전극에는 배향막의 배향액을 상기 컨택홀로 유입하는 유입통로가 구비되며, 상기 유입통로는 화소전극의 가장자리를 따라 침투하는 식각액의 침투거리를 최대화하는 액정표시소자.

**청구항 14**

제13항에 있어서, 상기 유입통로는 설정된 폭 및 길이의 사각형상, 지그재그형상 또는 곡면형상으로 이루어진 액정표시소자.

**발명의 설명****기술 분야**

[0001] 본 발명은 액정표시소자에 관한 것으로, 특히 잉크젯방식에 의해 배향막을 형성할 때, 화소전극의 단차 및 컨택홀에 의해 배향막이 불균일하게 형성되어 화면상에 빛샘이 발생하는 것을 방지할 수 있는 액정표시소자에 관한 것이다.

**배경 기술**

[0002] 근래, 기술발전에 따라 핸드폰(Mobile Phone), PDA, 노트북컴퓨터와 같은 각종 휴대용 전자기기나 텔레비전에 적용되던 평판표시장치(Flat Panel Display Device)의 크기가 점차 대형화되고 있다. 이러한 평판표시장치로는 LCD(Liquid Crystal Display), PDP(Plasma Display Panel), OLED(Organic Light Emitting Device Panel) 등이 활발히 연구되고 있으며, 특히 양산화 기술, 구동수단의 용이성, 고화질의 구현이라는 이유로 인해 액정표시소자(LCD)가 많이 적용되고 있다.

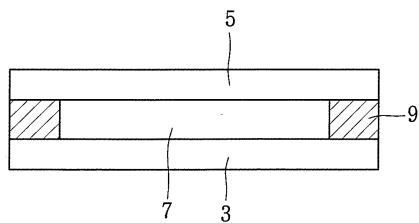

[0003] 도 1은 일반적인 액정표시소자의 단면을 개략적으로 나타낸 것이다. 도면에 도시한 바와 같이, 액정표시소자(1)는 제1기판(3)과 제2기판(5) 및 상기 제1기판(3)과 제2기판(5) 사이에 형성된 액정층(7)으로 구성되어 있다. 제1기판(3)은 구동소자 어레이(Array)기판으로써, 도면에는 도시하지 않았지만, 상기 제1기판(5)에는 복수의 화소가 형성되어 있으며, 각각의 화소에는 박막트랜지스터(Thin Film Transistor)와 같은 구동소자가 형성되어 있다. 제2기판(5)은 컬러필터(Color Filter)기판으로써, 실제 컬러를 구현하기 위한 컬러필터층이 형성되어 있다. 또한, 상기 제1기판(3) 및 제2기판(5)에는 각각 화소전극 및 공통전극이 형성되어 있으며 액정층(7)의 액정분자를 배향하기 위한 배향막이 도포되어 있다.

- [0004] 상기 제1기판(3) 및 제2기판(5)은 실링재(Sealing material)(9)에 의해 합착되어 있으며, 그 사이에 액정층(7)이 형성되어 상기 제1기판(3)에 형성된 구동소자에 의해 액정분자를 구동하여 액정층을 투과하는 광량을 제어함으로써 정보를 표시하게 된다.

- [0005] 액정표시소자의 제조공정은 크게 제1기판(3)에 구동소자를 형성하는 구동소자 어레이기판공정과 제2기판(5)에 컬러필터를 형성하는 컬러필터기판공정 및 셀(Cell)공정으로 구분될 수 있는데, 이러한 액정표시소자의 제조공정을 간략하게 설명하면 다음과 같다.

- [0006] 우선, 구동소자 어레이공정에 의해 제1기판(3)상에 배열되어 화소영역을 정의하는 복수의 게이트라인(Gate Line) 및 데이터라인(Data Line)을 형성하고 상기 화소영역 각각에 상기 게이트라인과 데이터라인에 접속되는 구동소자인 박막트랜지스터를 형성한다. 또한, 상기 구동소자 어레이공정을 통해 상기 박막트랜지스터에 접속되어 박막트랜지스터를 통해 신호가 인가됨에 따라 액정층을 구동하는 화소전극 및 공통전극을 형성한다.

- [0007] 또한, 제3기판(5)에는 컬러필터공정에 의해 컬러를 구현하는 R,G,B의 컬러 필터층과 화상비표시영역으로 광이 투과되는 것을 차단하는 블랙매트릭스를 형성한다.

- [0008] 이어서, 상기 제1기판(3) 및 제2기판(5)에 각각 배향막을 도포한 후 제1기판(3)과 제2기판(5) 사이에 형성되는 액정층의 액정분자에 배향규제력 또는 표면고정력(즉, 프리틸트각(Pretilt Angle)과 배향방향)을 제공하기 위해 상기 배향막을 러빙(Rubbing)한다. 그 후, 제1기판(3)에 셀갭(Cell Gap)을 일정하게 유지하기 위한 스페이서(Spacer)를 산포하고 제1기판(3) 또는 제2기판(5)의 외곽부에 실링재를 도포한 후 상기 제1기판(3)과 제2기판(5)에 압력을 가하여 합착한다. 한편, 상기 제1기판(3)과 제2기판(5)은 대면적의 유리기판으로 이루어져 있다. 다시 말해서, 대면적의 유리기판에 복수의 패널(Panel)영역이 형성되고, 상기 패널영역 각각에 구동소자인 TFT 및 컬러필터층이 형성되기 때문에 낱개의 액정패널을 제작하기 위해서는 상기 유리기판을 절단, 가공해야만 한다. 이후, 상기와 같이 가공된 개개의 액정패널에 액정주입구를 통해 액정을 주입하고 상기 액정주입구를 봉지하여 액정층을 형성한 후 각 액정패널을 검사함으로써 액정표시소자를 제작하게 된다.

- [0009] 상기와 같은 과정을 통하여 제작된 액정표시소자는 액정의 전기광학효과를 이용하는 것으로, 이 전기광학효과는 액정 자체의 이방성과 액정분자의 배열상태에 의해 결정되므로, 액정분자의 배열에 대한 제어는 액정표시장치의 표시품질 안정화에 큰 영향을 미치게 된다. 따라서, 액정분자를 보다 효과적으로 배향시키기 위한 배향막 형성 공정은 액정셀 공정에 있어서 화질특성과 관련하여 매우 중요하다.

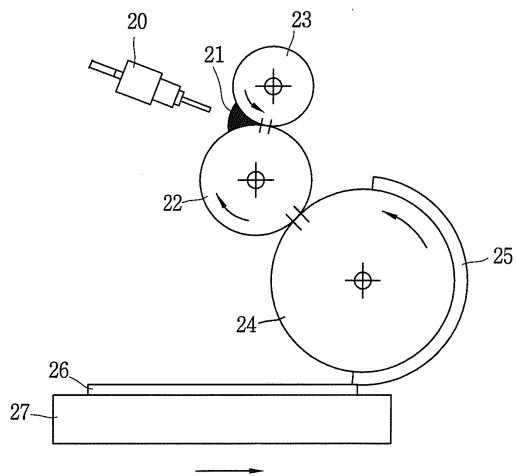

- [0010] 상기 배향막은 롤인쇄방식에 의해 형성되는데, 도 2에 배향막을 형성하는 종래 롤인쇄방법이 개시되어 있다. 도 2에 도시된 바와 같이, 종래 배향막형성은 복수개의 률을 이용한 인쇄법을 사용한다. 즉, 원통형의 어닐록스롤(22)과 닉터롤(23) 사이에 공급된 배향액(24)이 상기 어닐록스롤(22)과 닉터롤(23)이 회전함에 따라 어닐록스롤(22) 전체에 걸쳐 균일하게 도포된다. 이때 배향액(24)의 공급은 주사기 형태의 디스펜서(21)에 의해 이루어진다.

- [0011] 한편 상기 어닐록스롤(22)은 표면의 일정 영역에 고무판(25)이 부착된 인쇄롤(24)과 맞닿아 회전하게 되면 상기 어닐록스롤(22) 표면의 배향액이 고무판(25)으로 전사된다. 상기 고무판(25)은 배향액이 도포될 기판(26)에 대응하여, 기판에 선택적으로 배향막을 인쇄할 수 있도록 마스크가 패턴이 형성되어 있다. 기판(26)이 적재된 인쇄테이블(27)이 인쇄롤(24)과 접촉하여 이동함에 따라 고무판(25)에 전사된 배향액이 기판(6) 상으로 재전사되어 배향막이 형성된다. 보통 배향막의 두께는 500~1000Å 정도이며, 동일기판에서는 100Å 정도의 두께 차이에 의해서도 액정표시소자(LCD) 화면에서 배향 불균일에 의한 얼룩과 같은 불량이 발생될 수 있기 때문에 배향막을 균일하게 도포하는 것이 화면의 특성을 좌우하게 된다.

- [0012] 그러나, 상기와 같은 률 인쇄방법에서는 디스펜서가 어닐록스롤 상부에서 좌우로 움직이면서 어닐록스롤 상에 배향액을 공급하기 때문에 균일한 두께의 배향막을 형성하는데 한계가 있었으며, 특히, 기판이 대형화됨에 됨에 따라 배향막을 균일하게 도포하는 것이 더욱 힘들어진다. 더욱이, 고무판(25)에 전사된 배향액이 모두 기판에 전사되지 않기 때문에 실질적으로 기판에 형성되는 배향액보다 버려지는 것이 더 많아서 재료비낭비가 심하다는 문제점이 있었다.

- [0013] 또한, 기판의 크기에 다른 모델이 바뀜에 따라 상기 률(닉터롤, 어닐록스롤, 인쇄롤)들을 교체해 주어야 하며, 주기적으로 세정공정이 이루어지기 때문에 공정이 번거롭고 생산성이 떨어지는 문제점이 있었다.

- [0014] 더욱이, 기판이 대형화됨에 따라 률인쇄장비(어닐록스롤, 인쇄롤)의 크기도 함께 커져야 하기 때문에 기판의 대형화 따른 장비의 거대화를 야기하며, 배향막의 균일한 두께(uniformity)를 유지하는 것이 더욱 어려워진다.

## 발명의 내용

### 해결하려는 과제

- [0015] 본 발명은 상기한 점을 감안하여 이루어진 것으로, 배향막을 잉크젯방식에 의해 형성할 때 기판 전체에 배향막 두께를 일정하게 함으로써 배향막의 불균일에 의한 불량을 방지할 수 있는 액정표시소자를 제공하는 것을 목적으로 한다.

### 과제의 해결 수단

- [0016] 상기한 목적을 달성하기 위해, 본 발명에 따른 액정표시소자에서는 기판 전체에 배향액을 균일하게 도포하기 위해, 특히 컨택홀 내부에 배향액을 원활하게 유입한다. 이를 위해, 본 발명에서는 컨택홀 주위에 배치되는 화소전극에 의해 발생하는 단차를 제거하여 컨택홀내에 배향액을 유입한다.

- [0017] 이때, 본 발명에서는 컨택홀 주위의 화소전극의 일측 전체를 제거하여 배향액이 유입되는 유입통로를 형성할 수도 있고 일정 폭 및 길이의 특정 영역을 제거하여 유입통로를 형성할 수 있다. 유입통로를 일정 폭 및 길이로 형성함에 따라 배향액이 상기 유입통로를 통해 컨택홀 내부에 원활하게 유입됨과 동시에 화소전극을 삭각하기 위해 사용된 삭각액의 침투경로를 최대로 연장하여 삭각액이 화소전극 내부로 침투하는 것을 방지할 수 있게 된다. 그 결과, 삭각액 침투에 의한 화소전극의 단선을 방지할 수 있게 된다.

- [0018] 상기 유입통로는 다양한 형태로 형성될 수 있다. 예를 들어, 상기 유입통로는 설정된 폭 및 길이로 하나 또는 복수개 형성되어 배향액을 컨택홀을 유입하게 된다.

- [0019] 공통전극과 화소전극은 각각 제1보호층 및 제2보호층 상에 배치되며, 상기 공통전극과 제1보호층은 동일한 공정에 의해 삭각되어 제1컨택홀과 공통전극을 형성할 수 있게 된다. 이때, 상기 공통전극은 삭각속도 차이로 인해 오버에칭되어 제1보호층 하부에서 언더컷된다. 화소전극이 제2보호층상에 배치되어 컨택홀을 통해 박막트랜지스터의 드레인전극과 접속될 때, 상기 언더컷에 의해 발생한 공간에 의해 공통전극과 화소전극이 전기적으로 절연된다.

### 발명의 효과

- [0020] 본 발명에서는 잉크젯방식에 의해 배향액을 적하하여 배향막을 형성하므로, 신속한 배향막의 형성이 가능하고 대형 액정표시소자에도 적용할 수 있게 된다.

- [0021] 또한, 본 발명에서는 적하된 배향액이 컨택홀 내부로 원활하게 퍼질 수 있도록 컨택홀 주위의 화소전극에 컨택홀을 배향액을 유입하는 유입통로를 형성함으로써 기판 전체에 걸쳐서 균일한 배향막이 형성될 수 있게 된다.

- [0022] 그리고, 본 발명에서는 화소전극의 유입통로가 화소전극의 삭각시 화소전극 내부로 침투하는 삭각액의 침투거리 를 증가시킴으로써 화소전극의 단선을 방지할 수 있게 된다.

### 도면의 간단한 설명

- [0023] 도 1은 종래 액정표시소자의 구조를 간략하게 나타내는 단면도.

도 2는 롤인쇄방식의 액정표시소자 배향막 형성장치를 나타내는 도면.

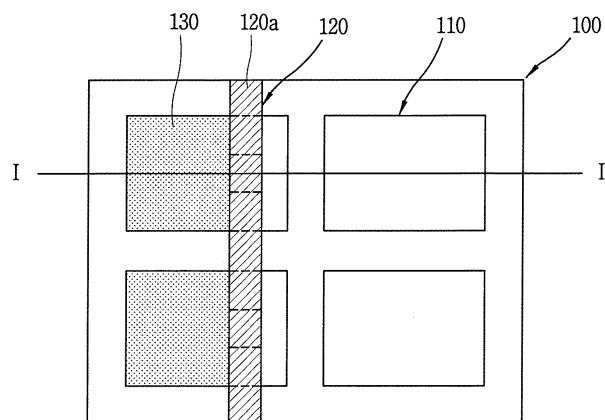

도 3a 및 도 3b는 잉크젯방식 액정표시소자 배향막 형성장치를 나타내는 도면.

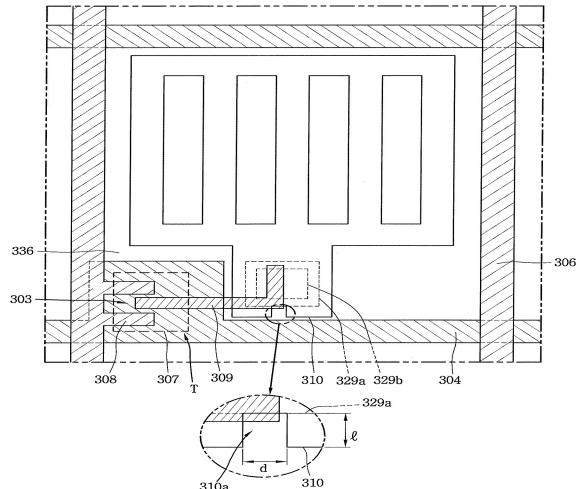

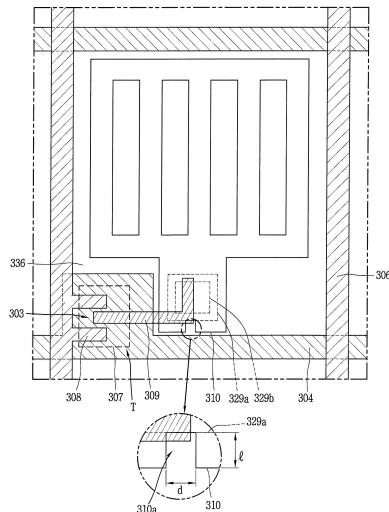

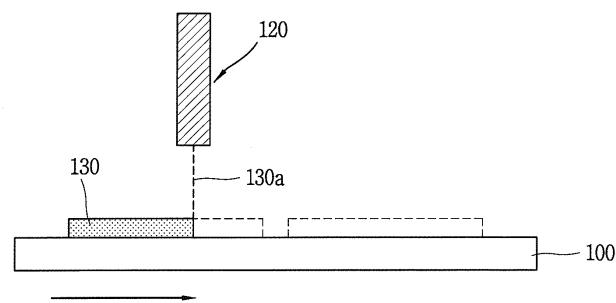

도 4는 본 발명의 제1실시예에 따른 액정표시소자의 구조를 나타내는 평면도.

도 5a는 도 4의 I-I'선 단면도.

도 5b는 도 4의 II-II'선 단면도.

도 6a는 화소전극이 컨택홀 및 주위를 덮는 구조의 액정표시소자에서의 배향액의 흐름경로를 나타내는 평면도.

도 6b는 화소전극이 컨택홀 및 주위를 덮는 구조의 액정표시소자에서 화소전극의 단차에 의해 배향액의 흐름경로가 차단되는 것을 나타내는 평면도.

도 6c는 불균일한 배향막에 의한 액정분자의 불균일한 배열을 나타내는 도면.

도 7a-도 7e는 본 발명의 제1실시예에 따른 액정표시소자의 제조방법을 나타내는 도면.

도 8a 및 도 8b는 본 발명의 제2실시예에 따른 액정표시소자의 구조를 나타내는 평면도.

도 9a 및 도 9b는 컨택홀 일측의 화소전극이 전부 제거된 구조에서 식각액이 화소전극 내부로 침투하는 경로를 나타내는 도면.

### 발명을 실시하기 위한 구체적인 내용

- [0024] 본 발명에서는 잉크젯방식에 의해 배향막을 형성함으로써 대형 액정표시소자의 배향막 형성을 용이하게 하고 배향액의 낭비를 최소화할 수 있을 뿐만 아니라 공정이 단순하고 생산성을 향상시킬 수 있게 된다.

- [0025] 특히, 본 발명에서는 잉크젯방식에 의해 형성되는 배향막을 표시소자 전체에 걸쳐 균일하게 형성하기 위해, 액정표시소자의 구조를 변경한다. 이러한 액정표시소자의 구조 변경은 잉크젯방식에 의해 적하된 배향액이 기판 표면에서 퍼질 때 퍼짐을 방해하는 단차 등을 최소화함으로서 불균일한 배향에 의한 화질저하를 방지할 수 있게 된다. 특히, 본 발명에서는 화소전극을 박막트랜지스터와 접속시키는 컨택홀 내부에 배향막이 원활하게 도포되도록 하여, 표시소자 전체에 걸쳐 균일한 배향막이 형성되도록 한다.

- [0026] 도 3은 잉크젯방식 배향막 형성장치를 나타내는 도면으로, 도 3a는 단면도이고, 도 3b는 평면도이다.

- [0027] 도면에 도시된 바와 같이, 잉크젯방식 배향막 형성장치는 복수의 액정패널(110)이 형성되는 모기판(100)에 직접 배향액을 적하하는 잉크젯헤드부(120)와 상기 잉크젯헤드부(120)에 배향액을 공급하는 배향액공급부(미도시) 및 상기 잉크젯헤드부(120)와 배향액공급부(미도시)를 기구적으로 연결하는 연결배선부(미도시)로 구성되어 있다. 상기 잉크젯헤드부(120)는 적어도 한개 이상의 헤드(120a)로 구성되며, 각각의 헤드(120a)에는 복수의 홀이 형성되어 있다. 상기 홀의 열리고 닫힘에 의해서 기판에 도포하는 배향액의 공급량 및 배향액의 적하 위치가 조절된다. 또한, 상기 홀의 수를 조절함으로써 배향막의 공정시간을 조절할 수도 있다.

- [0028] 배향액이 저장된 배향액공급부(미도시)에 질소가스( $N_2$ )가 공급되면, 상기 질소가스에 의해서 배향액공급부의 압력이 높아지고 이 압력에 의해서 배향액은 연결배선부를 통해 잉크젯헤드부(120)로 유입된다. 이때, 유입된 배향액은 상기 잉크젯헤드부(120)에 형성된 홀을 통하여 모기판(100) 위에 적하된다. 상기 홀을 통하여 토출(吐出)된 배향액은 기판에 적하되어 균일한 두께의 배향막을 형성하게 된다.

- [0029] 배향막 형성은 기판이 위치하는 스테이지 또는 헤드가 이동하면서 이루어지며, 잉크젯헤드부를 지나간 모기판(100) 영역에는 선택적으로 배향막(130)이 형성된다. 이때, 상기 잉크젯헤드부(120)는 기판 상에 배향액을 공급하면서 스테이지(미도시)의 이동도중 잉크젯헤드부(120)에 형성된 홀의 일부를 닫음으로써, 기판 상에 선택적으로 배향막(130)을 형성할 수 있다. 배향막(130)이 형성되는 영역은 실질적으로 박막트랜지스터 어레이 및 컬러 필터기판이 형성된 영역(120)이다.

- [0030] 상기 잉크젯헤드부(120)는 모기판(100)의 크기에 따라 배향액의 적하면적을 자유롭게 조절할 수 있도록 복수의 홀을 가지는 적어도 한개 이상의 헤드(120a)로 구성되어 있으므로, 모기판(100)이 대형화됨에 따라, 상기 헤드 수를 증가시켜 기판의 대형화에 용이하게 대처할 수가 있다.

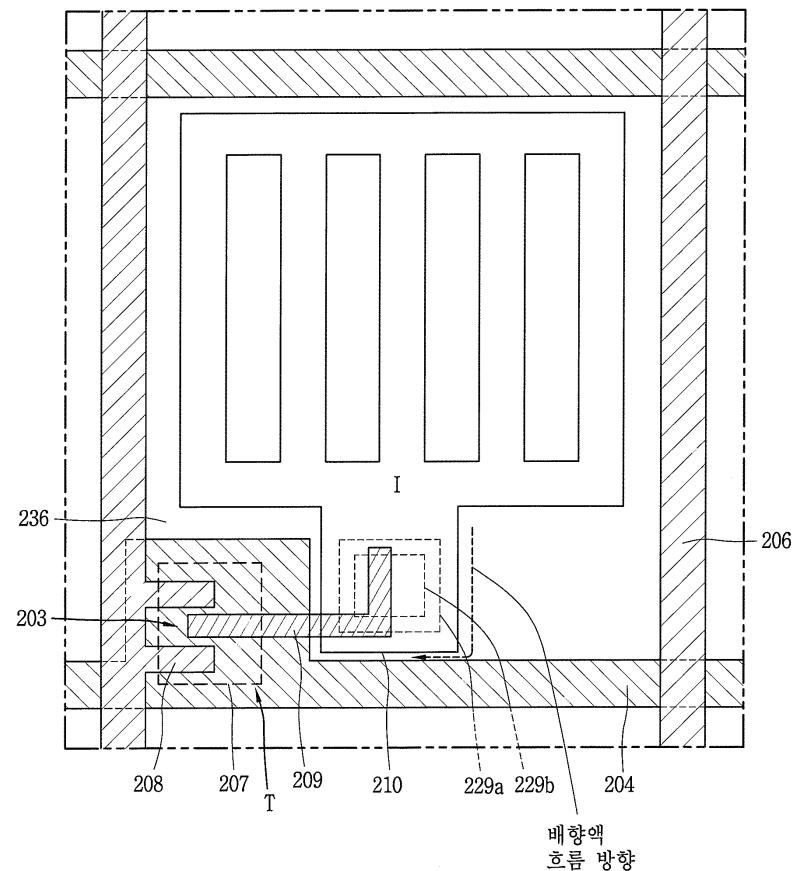

- [0031] 도 4는 상기 잉크젯방식 배향막 형성장치가 적용되는 본 발명의 제1실시예에 따른 액정표시소자의 구조를 나타내는 도면이다. 일반적으로 액정표시소자는 종횡으로 배치되는  $N \times M$ 개의 화소로 이루어지지만, 도면에서는 설명의 편의를 위하여 하나의 화소만을 도시하였다.

- [0032] 도 4에 도시된 바와 같이, 본 발명의 제1실시예에 따른 액정표시소자의 각 화소에는 외부의 구동회로로부터 주사신호가 인가되는 게이트라인(204)과 화상신호가 인가되는 데이터라인(206)의 교차영역에 배치된 박막트랜지스터(T)를 포함하고 있다. 상기 박막트랜지스터(T)는 상기 게이트라인(204)과 연결된 게이트전극(203)과, 상기 게이트전극(203) 위에 배치되어 게이트전극(203)에 주사신호가 인가됨에 따라 활성화되는 반도체층(207)과, 상기 반도체층(207) 위에 배치된 소스전극(208) 및 드레인전극(209)으로 구성된다.

- [0033] 또한, 상기 화소내에는 상기 소스(208) 및 드레인전극(209)과 연결되어 반도체층(208)이 활성화됨에 따라 상기 소스전극(208) 및 드레인전극(209)을 통해 화상신호가 인가되어 액정(도면표시하지 않음)을 동작시키는 화소전극(210) 및 상기 화소전극(210)과 함께 전계를 형성하는 공통전극(236)이 배치된다.

- [0034] 이때, 상기 공통전극(236)은 기판 전체에 걸쳐 배치되고 화소전극(210)은 화소영역에 배치되어 공통전극(236)에는 기판 전체에 걸쳐 동일한 공통전압이 인가되고 화소전극(210)에는 각각의 화소에 대응하는 화상신호가 인

가된다. 이때, 상기 화소전극(210)은 절연층을 사이에 두고 공통전극(236)의 상부에 배치되며 일정 폭 및 간격을 가진 복수의 띠형상으로 배치된다. 도면에서는 상기 화소전극(210)이 평행하게 형성되지만, 하나의 화소내에서 일정 각도로 배치될 수 있고 적어도 1회 절곡된 대칭형상으로 구성될 수도 있다.

[0035] 상기 화소전극(210)은 제1컨택홀(229a) 및 제2컨택홀(229b)을 통해 드레인전극(209)과 전기적으로 접속된다. 이 때, 상기 화소전극(210)은 제1컨택홀(229a) 및 제2컨택홀(229b) 내부에 배치되지만, 상기 제2컨택홀(229b)의 주위에 모두 배치되지 않고 일측이 제2컨택홀(229b)의 내부에만 형성되는데, 그 이유는 추후 자세히 설명한다.

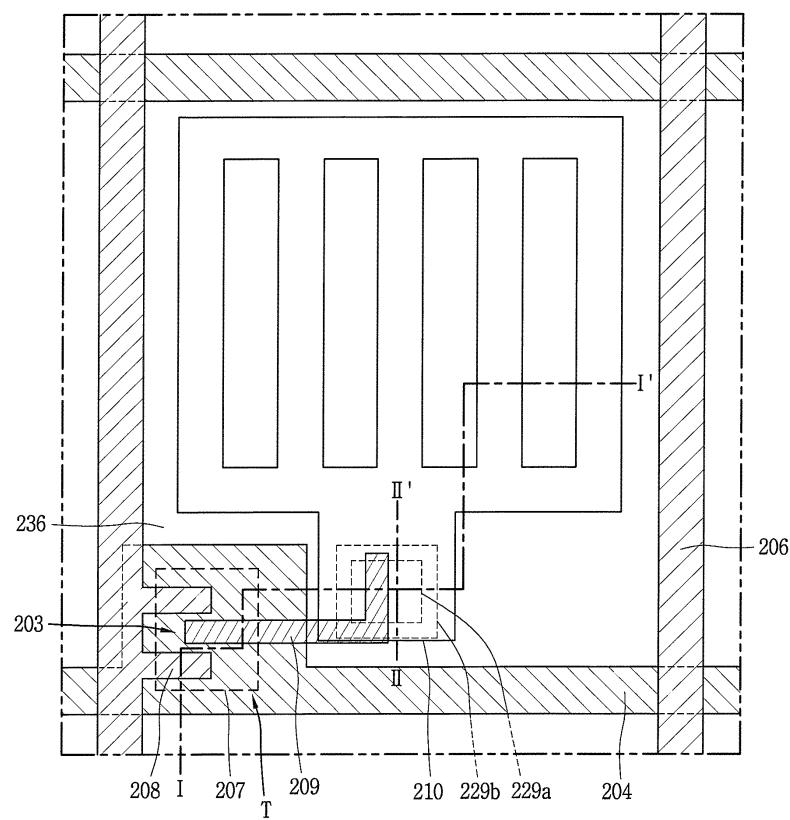

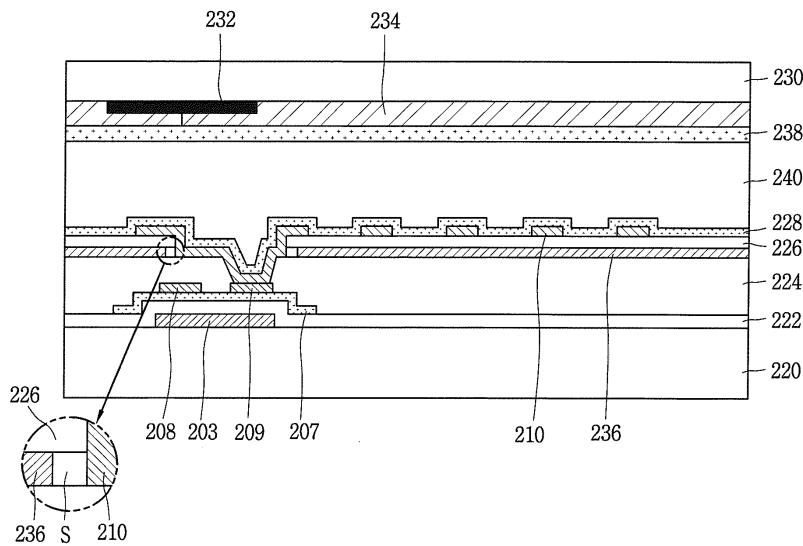

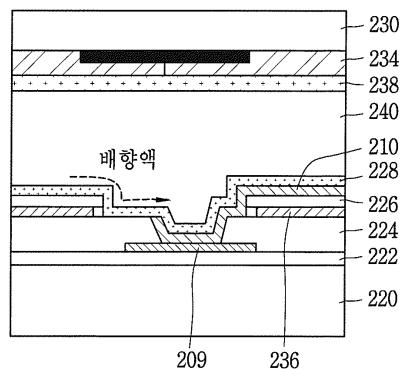

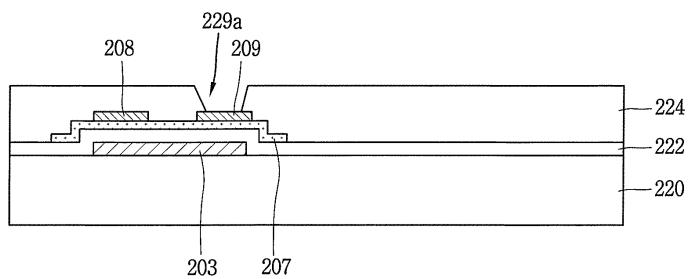

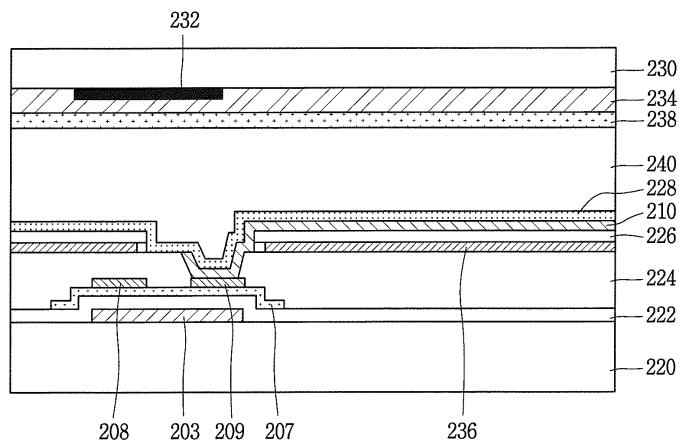

[0036] 상기와 같은 구조의 액정표시소자를 도 5a 및 도 5b를 참조하여 좀더 상세히 설명하면 다음과 같다. 이때, 도 5a는 도 4의 I-I'선 단면도이고 도 5b는 II-II'선 단면도이다.

[0037] 도 5a에 도시된 바와 같이, 제1기판(220) 위에는 게이트전극(203)이 배치되고 제1기판(220) 전체에 걸쳐 게이트 절연층(222)이 적층된다. 상기 게이트전극(203)은 게이트라인과 일체로 구성되지만, 별개로 구성되어 전기적으로 접속될 수도 있다. 상기 게이트절연층(222) 위에는 게이트전극(203)에 신호가 인가됨에 따라 활성화되는 반도체층(207)이 구비되고 그 위에 소스전극(208) 및 드레인전극(209)이 배치되며, 상기 제1기판(220) 전체에 걸쳐 제1보호층(passivation layer; 224)이 적층된다. 이때, 상기 드레인전극(209) 상부의 제1보호층(224)의 일부가 제거되어 상기 제1보호층(224)에 제1컨택홀(229a)이 형성되어, 드레인전극(209)이 외부로 노출된다.

[0038] 상기 제1보호층(224) 위에는 공통전극(236)이 배치되고, 그 위에 제1기판(220) 전체에 걸쳐 제2보호층(226)이 적층된다. 또한, 상기 제2보호층(226) 위에는 화소전극(210)이 배치된다. 이때, 상기 화소전극(210)은 일정 폭 및 일정 간격으로 제2보호층(226) 위에 배치된다.

[0039] 상기 제2보호층(226)에는 일부가 제거되어 제2컨택홀(229b)이 형성된다. 이때, 상기 제2보호층(226)은 제1보호층(224)과 정렬되어, 하나의 컨택홀로 형성된다. 상기 제1컨택홀(229a) 및 제2컨택홀(229b)은 각각 동일한 위치의 제1보호층(224) 및 제2보호층(226)을 식각하여 형성되지만, 상기 제1보호층(224) 및 제2보호층(226)을 한꺼번에 식각함으로써 형성할 수도 있다. 상기 화소전극(210)은 제1컨택홀(229a) 및 제2컨택홀(229b)를 통해 박막 트랜지스터(T)의 드레인전극(209)과 전기적으로 접속된다.

[0040] 상기 화소전극(210)과 공통전극(236)은 제2보호층(226)을 사이에 두고 배치되어, 화소전극(210)에 신호가 인가됨에 따라 화소전극(210)과 공통전극(236) 사이에 전계가 형성된다. 이때, 상기 공통전극(236)은 화소 전체에 걸쳐 배치되고 화소전극(210)은 일정 폭 및 간격으로 공통전극(236) 상부에 배치되므로, 화소전극(210)과 공통전극(236) 사이에는 제1기판(220)의 표면과 평행한 전계가 형성된다.

[0041] 이후 설명하지만, 상기 제2보호층(226)과 공통전극(236)은 하나의 식각공정에 의해 형성되므로, 제2보호층(226)이 공통전극(236)의 상면 및 측면을 완전히 커버하지 못하고 공통전극(236)의 측면이 외부로 노출된다. 그러나, 본 발명에서는 도면에 도시된 바와 같이, 제2보호층(226)과 공통전극(236)의 식각공정시 상기 공통전극(246)이 오버식각(over etching)되어 상기 공통전극(246)이 언더컷(under cut)되어 공통전극(246)이 제1보호층(224)의 단부로부터 일정 거리 안쪽에 배치된다.

[0042] 따라서, 화소전극(210)이 제1컨택홀(229a) 및 제2컨택홀(229b) 내부에 배치되는 경우에도, 제1컨택홀(229a) 및 제2컨택홀(229b) 내부에 배치되는 화소전극(210)과 공통전극(236) 사이에는 언더컷에 의한 빈 공간(S)이 발생하게 되며, 이 빈 공간(S)에 의해 화소전극(210)과 공통전극(236)이 전기적으로 절연된다.

[0043] 이와 같이, 본 발명에서는 화소전극(210)과 제2보호층(226)을 하나의 공정에 의해 식각하고 화소전극(210)과 공통전극(236)은 언더컷에 의한 빈 공간에 의해 전기적으로 절연시키므로, 제조공정을 단순화할 수 있고 제조비용을 절감할 수 있게 된다.

[0044] 상기 화소전극(210)이 형성된 제1기판(220)에는 제1배향막(228)이 형성된다. 상기 제1배향막(228)은 주로 폴리이미드(polyimide) 또는 폴리아미드(polyamide)로 이루어지며, 러빙처리에 의해 표면에 복수의 미세홈(mirco grooves)이 형성된다. 이러한 미세홈은 배향막에 배향규제력을 발생시켜 상기 배향막과 접촉하는 액정분자를 일정한 방향으로 배향시킨다. 이와 같이, 배향막의 배향규제력에 의해 액정분자가 일정방향으로 배향되는 것은 배향막의 배향규제력에 의해 액정분자가 배향막의 표면에 고정되기 때문이다(이러한 이유로 anchoring energy를 표면고정력이라고도 한다).

[0045] 제2기판(230)에는 화상비표시영역으로 광이 투과하는 것을 차단하는 블랙매트릭스(232)와 실제 컬러를 구현하기 위한 컬러필터층(234)이 배치되어 있으며, 상기 제1기판(220) 및 제2기판(230) 사이에 액정층(240)이 배치된다. 상기 블랙매트릭스(232)는 화소와 화소 사이의 영역 및 박막트랜지스터 형성영역에 배치되어 해당 영역으로 광

이 누설되는 것을 차단하며, 상기 컬러필터층(234)은 R,G,B 컬러필터층으로 구성되어 실제 컬러를 구현한다.

[0046] 상기 컬러필터층(234) 위에는 제2배향막(238)이 배치된다. 상기 제2배향막(238)과 제1배향막(228)과 마찬가지로 폴리아미드나 폴리아미드로 형성되며, 일정 방향으로 러빙처리되어 액정층(240)의 액정분자를 특정 방향으로 배향한다. 이때, 상기 제1배향막(228)과 제2배향막(238)의 러빙방향으로 서로 평행 또는 수직일 수 있다.

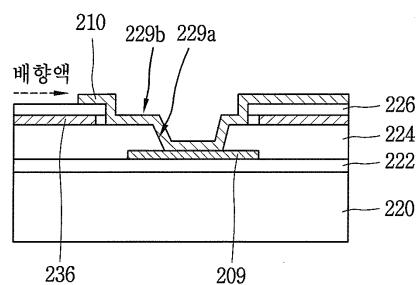

[0047] 도 5b에 도시된 바와 같이, 드레인전극(209) 상부의 제1보호층(224)이 제거되어 제1컨택홀(229a)이 형성되며, 그 상부의 제2보호층(226)이 식각되어 제2컨택홀(229b)이 형성된다. 상기 제2컨택홀(229b)의 식각시 하부의 공통전극(236)이 오버 식각되어 공통전극(236)이 언더컷되어 제2컨택홀(229b)의 벽면으로부터 일정 거리 안쪽으로 배치되며, 그 결과 상기 제2보호층(226) 위에 배치되는 화소전극(210)이 언더컷에 의한 공간에 의해 공통전극(236)과 전기적으로 절연된다.

[0048] 상기 화소전극(210)은 그 일부가 제1컨택홀(229a) 및 제2컨택홀(229b)의 내부와 제1컨택홀(229a) 및 제2컨택홀(229b) 주위의 제2보호층(226) 상부로 연장되도록 배치되어, 상기 화소전극(210)이 제1컨택홀(229a) 및 제2컨택홀(229b)을 통해 드레인전극(209)에 전기적으로 접속되는 것이 바람직하다.

[0049] 그러나, 본 발명에서는 화소전극(210)이 제1컨택홀(229a) 및 제2컨택홀(229b) 상부의 제2보호층(226)의 전체 주위에 배치되지 않고 일측(도 5b에서는 제2컨택홀(229b)의 좌측영역, 도 4에서는 제2컨택홀(229b) 하부영역)을 제거하여 해당 영역에서 화소전극(210)이 제2보호층(226) 상부에 배치되지 않도록 한다. 즉, 제1컨택홀(229a) 및 제2컨택홀(229b) 주위의 제2보호층(226) 상부에 배치되는 사각형상의 화소전극(210)중에서 일변의 화소전극(210)을 제거하여 해당 영역의 제2보호층(226)에는 화소전극(210)이 형성되지 않고 단지 제1컨택홀(229a) 및 제2컨택홀(229b) 내부에만 배치되도록 한다.

[0050] 이와 같이, 제2컨택홀(229b) 주위의 일측(일변)의 화소전극(210)을 제거하여 해당 영역의 제2보호층(226) 위에 화소전극(210)을 배치하지 않는 것은 화소전극(210)에 의해 발생하는 단차를 제거하여 배향막 형성시 제1컨택홀(229a) 및 제2컨택홀(229b) 내부로 배향액이 원활하게 도포되도록 하여 액정표시소자 전체에 걸쳐 균일한 배향막을 형성하기 위한 것으로, 도면을 참조하여 이를 좀더 자세히 설명한다.

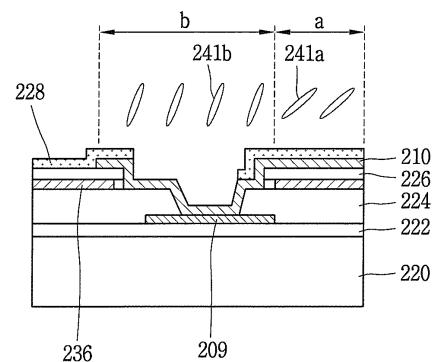

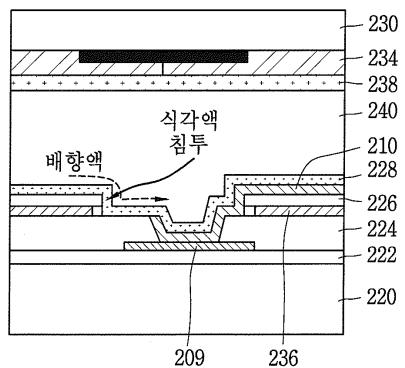

[0051] 도 6a 및 도 6b는 각각 제2보호층(226) 상부의 제2컨택홀(229b) 주위에 모두 화소전극(210)이 형성된 구조의 평면도 및 단면도를 나타내는 도면이고, 도 6c는 이러한 구조에서의 액정분자의 배향을 나타내는 도면이다.

[0052] 도 6a에 도시된 바와 같이, 이 구조의 액정표시소자에서는 화소전극(210)이 제2컨택홀(229b) 내부에 배치될 뿐만 아니라 제2컨택홀(229b) 주위 외부 전체 영역에도 배치된다.

[0053] 한편, 제1배향막(228)의 도포시 도 3a 및 도 3b에 도시된 배향막 형성장치를 이용하여 도 6a에 도시된 구조를 가진 제1기판(220)상에 배향액을 적하한 후 경화시킨다. 제1기판(220) 상에 적하된 배향액은 제1기판(220) 상에서 퍼져 제1기판(220) 전체에 걸쳐 제1배향막(228)을 형성하게 된다. 따라서, 제1기판(220) 전체에 걸쳐 균일한 제1배향막(228)을 형성하기 위해서는 적하된 배향액이 제1기판(220) 전체에 걸쳐 균일하게 퍼져야만 한다.

[0054] 배향막 형성장치를 통해 적하된 배향액은 제1기판(220) 상에서 적하된 영역 외부로 퍼져나간다. 이때, 제1기판(220) 상에는 화소전극(210)과 같은 단차가 존재하므로, 적하된 배향액은 우선 단차를 따라 배향액이 흐르고 점차 단차를 넘어 제1기판(220) 전체로 퍼지게 된다.

[0055] 화소전극(210)과 제2보호층(226) 뿐만 아니라 제1컨택홀(229a) 및 제2컨택홀(229b) 내부에도 균일한 제1배향막(228)이 형성되기 위해서는 적하되어 퍼지는 배향액이 상기 제1컨택홀(229a) 및 제2컨택홀(229b) 내부에도 균일하게 도포되어야만 한다. 그런데, 도 6a에 도시된 바와 같이, 제2컨택홀(229b) 주위로 퍼지는 배향액은 상기 화소전극(210)의 단차를 따라 흐르게 된다. 즉, 화소전극(210)의 단차가 배향액이 흐르는 통로의 역할을 하여 배향액이 제2컨택홀(229b)을 덮는 화소전극(210)의 단차를 따라 퍼지게 된다.

[0056] 도 6b에 도시된 바와 같이, 배향액이 상기 화소전극(210)의 단차를 따라 퍼질 때, 상기 화소전극(210)의 단차에 의해 배향액이 상기 제1컨택홀(229a) 및 제2컨택홀(229b) 내부로 퍼지는 것이 차단된다. 따라서, 제1컨택홀(229a) 및 제2컨택홀(229b) 내부로의 배향액의 도포가 원활하게 이루어지지 않게 되어, 제1배향막(228)을 형성했을 때 제1컨택홀(229a) 및 제2컨택홀(229b) 내부의 제1배향막(228)의 두께가 다른 영역의 제1배향막(228)의 두께보다 작게 되므로, 균일한 제1배향막(228)을 형성할 수 없게 되며, 심지어 상기 제1컨택홀(229a) 및 제2컨택홀(229b) 내부에 제1배향막(228)이 형성되지 않을 수도 있게 된다.

[0057] 도 6c에 도시된 바와 같이, 일부 영역(b)(예를 들면, 제1컨택홀(229a) 및 제2컨택홀(229b) 내부)의 제1배향막(228)의 두께가 다른 영역(a)의 제1배향막(228)의 두께보다 작거나 일부 영역(b)에 제1배향막(228)이 형성되지

않는 경우, b영역의 제1배향막(228)의 배향규제력이 a영역의 제1배향막(228)의 배향규제력보다 약해지기 때문에, b영역의 액정분자(241b)의 배향방향(또는 프리틸트각)과 a영역의 액정분자(241a)의 배향방향(또는 프리틸트각)이 다르게 된다. 따라서, b영역과 a영역의 광투과율이 서로 다르게 되어, a영역을 통해 화상신호에 따른 화상이 구현될 때 광투과율의 차이로 인해 b영역을 통해 빛샘현상이 발생하게 되며, 그 결과 액정표시소자에 화질저하라는 불량이 발생하게 된다.

[0058] 그러나, 본 발명에서는 도 5a 및 도 5b에 도시된 바와 같이, 제2컨택홀(229b) 주위에 배치되는 화소전극(210) 중 일변(일측)의 화소전극(210)을 제거하여, 해당 영역에서는 제2보호층(226)에 화소전극(210)을 형성하지 않고 제2컨택홀(229b) 내부에만 화소전극(210)을 형성함으로써, 화소전극(210)에 의한 단차를 제거할 수 있게 된다. 따라서, 배향액이 퍼질 때 배향액이 화소전극(210)의 단차에 의해 차단되지 않고 상기 제1컨택홀(229a) 및 제2컨택홀(229b) 내부로 원활하게 유입된다. 즉, 본 발명에서는 제1컨택홀(229a) 및 제2컨택홀(229b)로 배향액을 유입하는 배향액 유입영역을 구성함으로써, 제1기판(220) 전체에 걸쳐 균일한 두께의 제1배향막(228)을 형성할 수 있게 된다.

[0059] 한편, 도면에서는 상기 배향액 유입영역이 제2컨택홀(229b)의 하부영역(즉, 게이트라인(203)에 인접하는 영역)에 형성되지만, 본 발명이 이러한 구성에 한정되는 것은 아니다. 상기 배향액 유입영역은 배향액이 기판상에서 퍼질 때 제1컨택홀(229a) 및 제2컨택홀(229b) 내부로 원활하게 유입되도록 하기 위한 것이므로, 이러한 목적을 달성할 수만 있다면 어떠한 구성이라도 가능하다. 예를 들어, 제2컨택홀(229b) 주위의 제2보호층(226) 상부의 화소전극(210) 중 위쪽(즉, 화소중앙측)의 화소전극이 제거되어 배향액 유입영역이 이 영역에 형성될 수도 있고 제2컨택홀(229b) 주위의 제2보호층(226) 상부의 화소전극(210) 중 측면(즉, 데이터라인측 및 그 반대측)의 화소전극이 제거되어 배향액 유입영역이 이 영역에 형성될 수도 있을 것이다.

[0060] 또한, 상기 컨택홀(229a, 229b) 주위의 화소전극이 사각형상이 아니 다른 형상, 예를 들어, 원형상으로 형성될 때에도 배향액 유입영역이 형성될 수 있다. 이 경우, 상기 배향액 유입영역은 배향막의 형성시 배향액이 퍼지는 방향의 일정 영역, 예를 들면 원형상 화소전극의 각 4분점(상하, 좌우측의)을 제거함으로써 형성될 수 있다.

[0061] 이하에서는 도면을 참조하여 본 발명의 제1실시예에 따른 액정표시소자 제조방법을 상세히 설명한다.

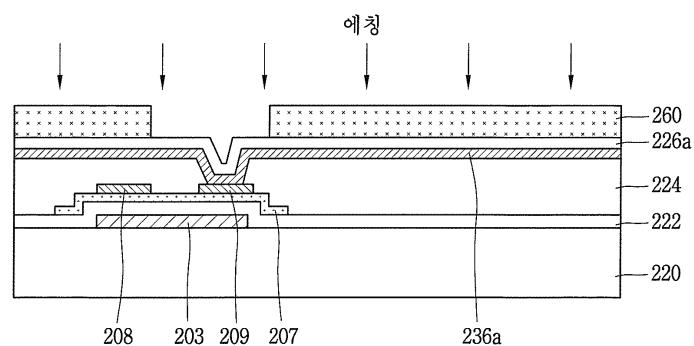

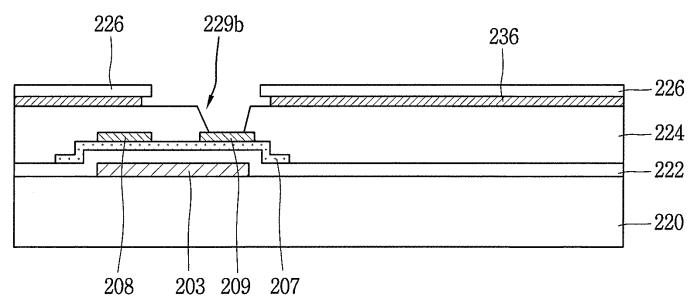

[0062] 도 7a-도 7e는 본 발명의 제1실시예에 따른 액정표시소자의 제조방법을 나타내는 도면이다.

[0063] 우선, 도 7a에 도시된 바와 같이, 유리 또는 플라스틱과 같은 투명한 제1기판(220)상에 게이트전극(203)을 형성한다. 도면에는 도시하지 않았지만, 상기 게이트전극(203)의 형성시 게이트라인을 형성한다. 상기 게이트전극(203)과 게이트라인은 Al이나 Al합금 등과 같은 금속을 증착(evaporation)이나 스퍼터링(sputtering)에 의해 제1기판(220)에 적층한 후 마스크를 이용한 포토공정(photolithography process)에 의해 패터닝함에 따라 형성할 수 있다.

[0064] 이어서, 상기 게이트전극(203)이 형성된 제1기판(220) 전체에 걸쳐 CVD방법(Chemical Vapor Deposition process)에 의해 SiO<sub>x</sub>나 SiN<sub>x</sub> 등을 적층함으로써 게이트절연층(222)을 형성한다.

[0065] 그 후, 상기 게이트절연층(222) 위에 반도체층(207)을 형성하고 상기 반도체층(312) 위에 소스전극(208) 및 드레인전극(209)을 형성한다. 상기 반도체층(207)은 비정질실리콘이나 결정질실리콘으로 이루어지는 것으로, 비정질반도체층을 형성하는 경우에는 CVD방법에 의해 비정질실리콘을 적층한 후 패터닝하여 형성하며 결정질반도체층을 형성하는 경우에는 비정질실리콘층을 형성한 후 이를 결정화하거나 결정질실리콘을 적층함으로써 형성한다. 상기 소스전극(208) 및 드레인전극(209)은 Cr, Mo, Al, Al합금 등과 같은 금속을 증착이나 스퍼터링에 의해 적층한 후 마스크를 이용한 포토공정에 의해 패터닝함으로써 형성한다. 또한, 도면에는 도시하지 않았지만, 상기 소스전극(208) 및 드레인전극(209)을 형성할 때 데이터라인도 형성한다.

[0066] 이어서, 상기 박막트랜지스터가 형성된 제1기판(220) 위에 제1보호층(224)을 형성한 후, 식각하여 상기 드레인전극(209) 상부의 제1보호층(224)에 제1컨택홀(229a)을 형성한다. 이때, 상기 제1보호층(224)은 SiO<sub>x</sub>나 SiN<sub>x</sub> 등의 무기절연물질을 CVD 등에 의해 적층함으로써 형성하거나 포토아크릴(photo acryl)과 같은 유기절연물질을 도포함으로써 형성할 수 있다.

[0067] 그 후, 도 7b에 도시된 바와 같이, 상기 제1기판(220) 전체에 걸쳐서 ITO(Indium Tin Oxide)나 IZO(Indium Zinc Oxide)와 같은 투명도전물질로 이루어진 도전층(236a) 및 절연층(226a)을 적층한 후, 그 위에 포토레지스트를 적층하고 포토마스크에 의해 현상하여 상기 절연층(226a) 위에 포토레지스트패턴(260)을 형성한다. 이때, 상기 포토레지스트패턴(260)의 현상에 의해 제1컨택홀(229a)을 포함하는 절연층(226a)의 일부 영역이 외부로 노

출된다. 이어서, 상기 포토레지스트패턴(260)에 의해 절연층(226a) 및 도전층(236a)을 식각한다.

[0068] 도 7c에 도시된 바와 같이, 상기 식각에 의해 절연층(226a) 및 도전층(236a)이 제거되어 공통전극(236) 및 제2보호층(226)이 형성됨과 동시에 제2컨택홀(229b)이 형성된다. 이때, 절연층(226a) 및 도전층(236a)은 식각속도가 다르므로, 절연층(226a) 및 도전층(236a)을 1회의 식각공정에 의해 식각할 때 상기 도전층(236a)이 오버식각되어 제2보호층(226) 하부에 공통전극(2360이 언더컷(under cut)된다.

[0069] 그 후, 도 7d에 도시된 바와 같이, 제1기판(220) 전체에 걸쳐서 ITO나 IZO와 같은 투명도전물질로 이루어진 도전층(210a)을 적층하고 식각하여 화소전극(210)을 형성하고, 이어서 도 3에 도시된 배향막 형성장치를 이용하여 폴리미이드 또는 폴리아미드과 같은 배향액을 약 500-1000Å의 두께로 도포하여 제1기판(200) 전체에 걸쳐 제1배향막(228)을 형성한다.

[0070] 상기 화소전극(210)은 제2컨택홀(229b)를 전부 덮도록 배치되지만, 상기 제2컨택홀(229b)의 주위 전체에 배치되는 것이 아니라 주변 3번을 따라 배치된다. 즉, 제2컨택홀(229b)의 일변 주위에는 화소전극(210)이 형성되지 않고 제거되어 이 영역에 화소전극(210)에 의한 단차가 발생하지 않게 된다.

[0071] 제1배향막(228)은 도 3에 도시된 배향막 형성장치에 의해 배향액을 적하한 후, 적하된 배향액을 제1기판(220) 전체에 걸쳐서 퍼지게 한 후 경화시킴으로써 형성된다. 이때, 상기 배향액은 배향액 유입영역을 통해 제2컨택홀(229b) 내부로 퍼지게 되므로, 컨택홀(229a, 229b) 내부를 포함한 제1기판(220) 전체에 걸쳐서 균일한 제1배향막(228)을 형성할 수 있게 된다. 또한, 상기 제1배향막(228)은 러빙처리되어 설정된 배향방향이 주어진다.

[0072] 그 후, 도 7e에 도시된 바와 같이, 제2기판(230)에 Cr이나 Cr0x 등의 금속을 적층하고 식각하여 화상비표시영역에 블랙매트릭스(232)를 형성한 후, 제2기판(230) 전체에 걸쳐 R(red), G(green), B(blue) 안료 또는 염료를 적층하고 식각하여 컬러필터층(234)을 형성한다. 이어서, 상기 컬러필터층(234)위에 배향막 형성장치에 의해 배향액을 도포하고 경화하여 제2배향막(238)을 형성한다. 도면에는 도시하지 않았지만, 제2배향막(238)을 형성하기 전에, 상기 컬러필터층(234) 위에 유기절연물질로 이루어진 평탄화층을 형성할 수도 있다.

[0073] 이어서, 상기 제1기판(220) 및 제2기판(230) 사이에 액정층(240)을 형성하여 액정표시소자를 완성한다.

[0074] 상술한 바와 같이, 본 발명에서는 컨택홀(229a, 229b) 주위의 일측의 화소전극(210)를 제거하여 배향액의 도포시 컨택홀(229a, 229b) 내부로 배향액이 원활하게 유입되도록 함으로써 제1기판(220) 전체에 걸쳐 제1배향막(228)이 균일한 두께로 형성되도록 한다. 그 결과, 제1배향막(228)의 불균일에 의해 야기되는 빛샘현상을 방지할 수 있게 된다.

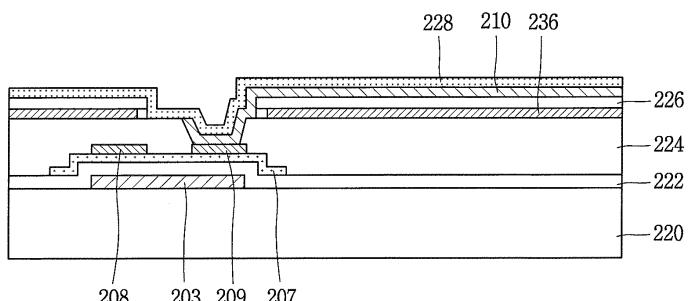

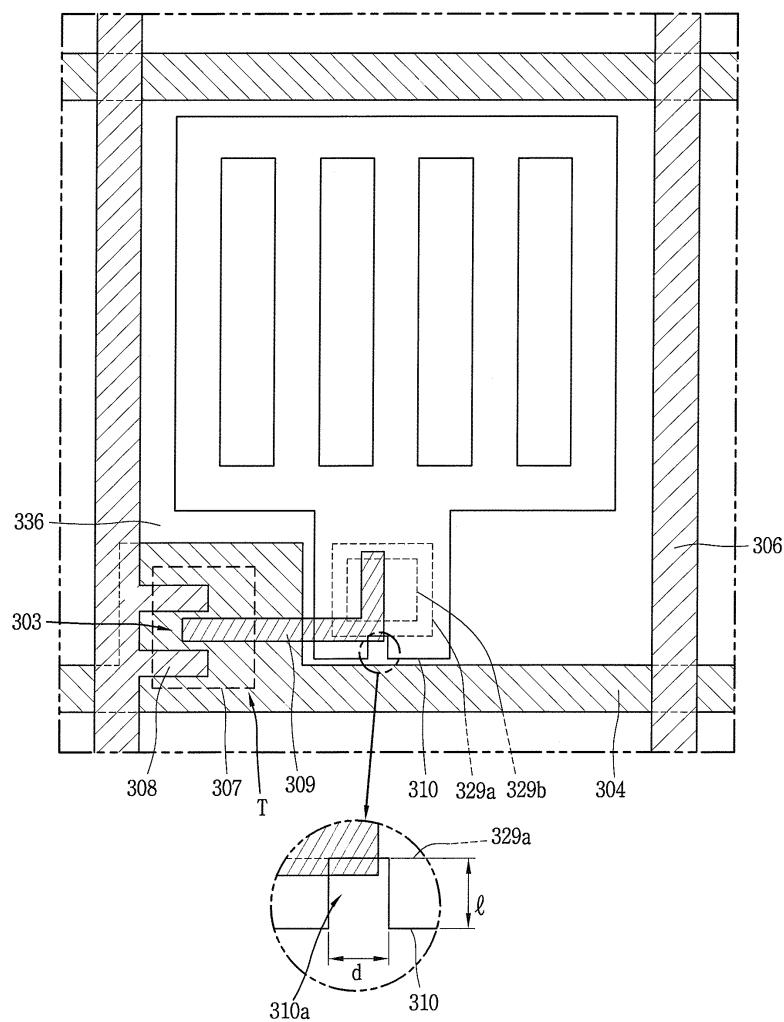

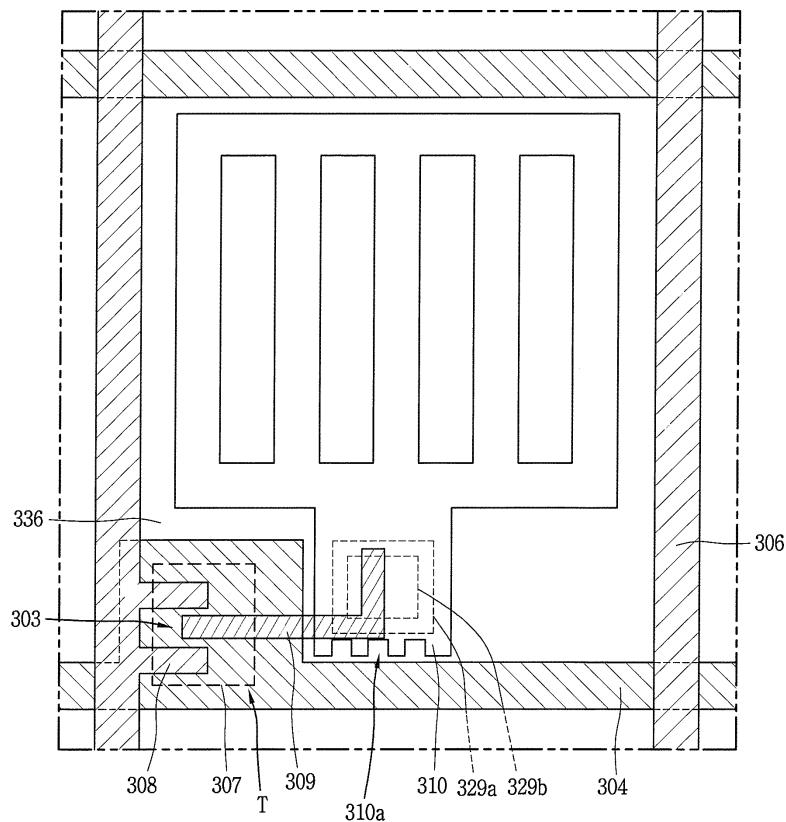

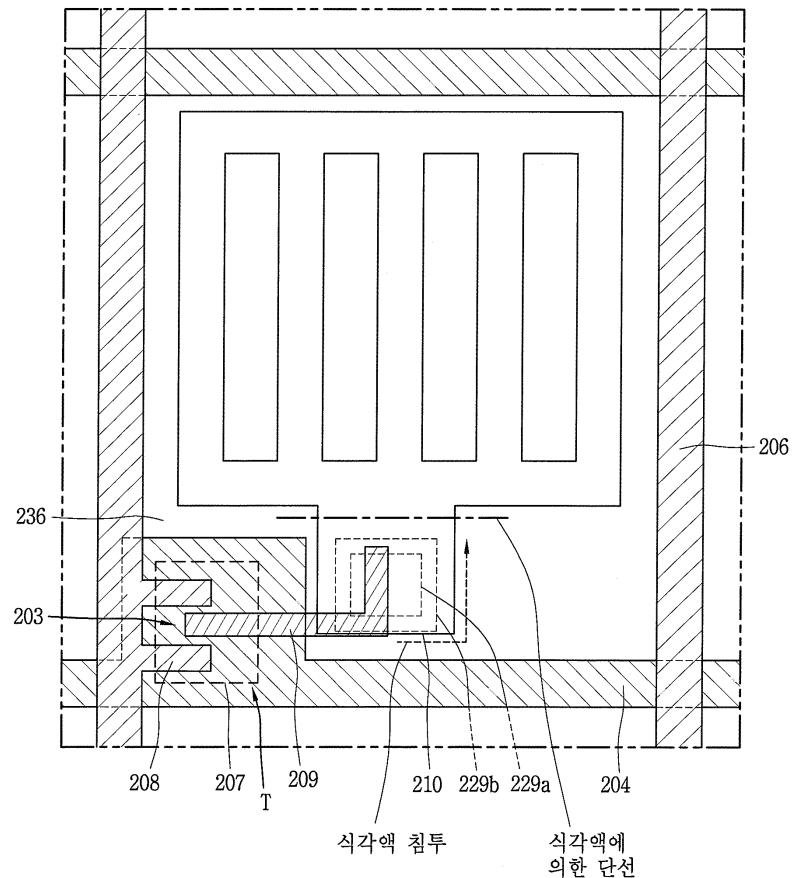

[0075] 도 8a 및 도 8b는 본 발명의 제2실시예에 따른 액정표시소자의 구조를 나타내는 도면이다. 이때, 이 실시예의 구조는 제1실시예와 유사하므로, 동일한 구조에 대해서는 설명을 생략하고 다른 구조에 대해서만 자세히 설명한다.

[0076] 도 8a에 도시된 바와 같이, 이 구조의 액정표시소자에서는 제2컨택홀(329b) 및 그 주위에 화소전극(310)이 배치된다. 제1실시예에서는 제2컨택홀의 일측(또는 일변측) 화소전극이 모두 제거되어 사각형상의 제2컨택홀의 일변측에 화소전극이 배치되지 않고 컨택홀 내부에만 화소전극이 형성되어, 제2컨택홀의 일변 전체 영역을 통해 컨택홀(329b) 내부로 퍼지는데 반해, 본 발명에서는 제2컨택홀(329b)의 둘러싸는 화소전극(310)에 설정 폭(d)의 홈으로 이루어진 배향액 유입통로(310a)가 형성된다. 이때, 상기 홈은 그 입구가 배향막의 형성시 액정표시소자의 전체로 퍼지는 배향액 퍼짐방향을 따라 형성된다. 또한, 상기 홈의 연장방향도 배향액 퍼짐방향과 대략 평행하게 배치되는 것이 바람직할 것이다.

[0077] 즉, 제1실시예에 비해, 이 실시예에서는 제2컨택홀(329b)로 유입되는 배향액의 유입통로가 작게 형성되는데, 제1실시예의 구조인 도 9a 및 도 9b를 참조하여 그 이유를 설명한다.

[0078] 도 9a에 도시된 바와 같이, 제1실시예에서는 제2컨택홀(229b)의 일측 화소전극(210)이 모두 제거되므로, 다른 영역에서는 화소전극(210)이 제2보호층(226) 및 공통전극(236)의 측단면을 덮고 있는 반면에, 해당 영역에서는 제2보호층(226) 및 공통전극(236)이 외부로 노출된다. 따라서, 화소전극(210)의 형성시 식각액에 의해 도전층을 식각할 때 상기 노출된 영역의 공간(S)을 통해 식각액이 침투하게 된다.

[0079] 도 9b에 도시된 바와 같이, 침투한 식각액은 화소전극(210)의 가장자리를 따라 화소전극(210)의 내부로 침투하여 화소전극(210)을 단선시키게 된다. 화소전극(210)이 단선되는 경우, 박막트랜지스터를 통해 공급되는 화상신호가 해당 화소의 화소전극(210)으로 인가되지 않게 되어 해당 화소가 암점으로 되므로, 액정표시소자가 불량으

로 된다.

- [0080] 상기와 같이 제1실시예에서는 배향액을 제2컨택홀(229b)로 유입하기 위해 제거된 영역으로 식각액이 침투한 후, 화소전극(210)의 가장자리 영역을 따라 화소전극(210)의 내부로 침투하게 된다. 만약, 화소전극(210)의 일측을 제거하지 않는 경우, 식각액의 침투에 의한 화소전극(210)의 단선이 발생하지 않지만, 이 경우 배향막의 불균일한 도포에 의한 빛샘현상이 발생한다.

- [0081] 이 실시예에서는 배향막을 균일하게 형성함과 동시에 식각액의 침투에 의한 화소전극(310)의 단선을 방지할 수 있게 된다. 이를 위해 이 실시예에서는 제2컨택홀(329b) 주위의 화소전극(310)를 제거하여 제2컨택홀(329b) 내부로 유입되는 배향액 유입통로를 형성함과 동시에 상기 배향액 유입통로를 최소화하여 화소전극(310)의 가장자리를 따라 침투하는 식각액 침투경로를 최대한 길게 하여 식각액이 화소전극(310)의 내부까지 침투하지 못하도록 한다.

- [0082] 즉, 도 8a에 도시된 바와 같이, 제2보호층(326) 상부의 제2컨택홀(329b) 주위의 화소전극(310)을 제거하여 제2컨택홀(329b)의 일측 전체를 제거하는 것이 아니라 일정 영역만을 제거하여 화소전극(310)에 설정된 폭(d) 및 길이(l)의 배향액이 유입되는 홈형상의 유입통로(310a)를 형성한다. 배향액이 적혀되어 퍼질 때, 화소전극(310)의 가장자리 단차를 통해 퍼지는 배향액이 상기 유입통로(310a)를 통해 제2컨택홀(329b) 내부로 흘러들어 가게 되므로, 상기 컨택홀(329a, 329b)을 포함하는 제1기판(320) 전체에 걸쳐 균일한 두께의 배향액 도포가 가능하게 된다.

- [0083] 한편, 이 실시예에서도 화소전극(310)의 식각시, 상기 유입통로(310a)를 통해 식각액이 유입되며, 이 식각액이 화소전극(310)의 가장자리를 따라 화소전극(310) 내부에 침투하게 된다. 그런데, 이 실시예에서는 유입통로(310a)가 일정 폭(d) 및 길이(l)로 형성되므로, 이 영역으로 침투한 식각액이 유입통로(310a)의 가장자리를 따라 l의 길이만큼 화소전극(310)의 외곽 가장자리로 퍼진 후, 다시 화소전극(310)의 외곽 가장자리를 따라 화소전극(310) 내부로 침투하게 된다.

- [0084] 따라서, 제1실시예에 비해, 식각액의 침투거리가 증가( $2l + a$  (유입경로가 형성되는 변의 유입경로의 폭을 제외한 화소전극의 일변 길이))하게 되므로, 화소전극(310) 내부로 식각액의 침투가 어렵게 된다. 일부의 식각액이 화소전극(310) 내부로 침투하는 경우에도 그 양이 최소화되어 화소전극(310)을 단선시킬 수 없게 된다.

- [0085] 한편, 도면에서는 상기 유입통로(310a)가 특정 폭(a) 및 길이(l)를 가진 직사각형상으로 이루어져 있지만, 상기 유입통로(310a)가 특정 형상으로 이루어질 필요는 없다. 상기 유입통로(310a)의 목적은 배향액을 제2컨택홀(329b) 내부로 유입함과 아울러 화소전극(310)의 가장자리를 따라 화소전극(310) 내부로 침투하는 식각액의 침투거리를 증가시키기 위한 것이므로, 이러한 목적을 달성할 수 있는 형상이라면 어떠한 형상도 가능하다. 예를 들어, 상기 유입통로(310a)는 일정 각도로 지그재그 형상의 직선으로 이루어질 수 있고 일정 곡률을 갖고 복수회 구부러진 곡면형상으로 이루어질 수도 있다.

- [0086] 또한, 상기 유입통로(310a)는 특정 위치에 한정되어 배치될 필요는 없다. 도면에서는 상기 유입통로(310a)가 제2컨택홀(329b) 주위의 사각형상 화소전극(310)의 하변측에 형성되지만, 상기 유입통로(310a)가 측변이나 상변과 같이 다양한 위치에 형성될 수 있을 것이다.

- [0087] 화소전극(310)의 원형상인 경우, 상기 유입통로(310a)는 설정폭으로 원주를 방향으로 컨택홀(329b)의 경계까지 제거되어 홈형상의 유입통로(310a)가 형성될 수 있다. 이때, 상기 유입통로(310a)의 원주를 방향으로 원주상 어디에도 형성될 수 있지만, 배향막의 형성시 배향액의 퍼짐방향을 따라 구비되는 것이 바람직하다.

- [0088] 그리고, 도 9b에 도시된 바와 같이, 상기 유입통로(310a)는 복수개 형성될 수 있다. 앞서 설명한 바와 같이, 유입통로(310a)의 목적은 배향액을 컨택홀(329a, 329b) 내부로 유입함과 아울러 화소전극(310)의 가장자리를 따라 화소전극(310) 내부로 침투하는 식각액의 침투거리를 증가시키기 위한 것이므로, 유입통로(310a)를 복수개 형성함으로써 이러한 목적을 더욱 용이하게 달성할 수 있다. 즉, 유입통로(310a)를 복수개 형성함에 따라 제2컨택홀(329b) 내부로의 배향액 유입이 원활하게 되며, 유입통로(310a)에 의해 침투되는 식각액은 복수의 유입통로(310a)의 가장자리를 따라 화소전극(310)의 내부로 침투해야만 하므로, 식각액의 침투거리가 증가하게 되어 화소전극(310)의 단선을 방지할 수 있게 된다.

- [0089] 도면에서는 복수의 유입통로(310a)가 특정 형상으로 구성되지만, 유입통로(310a)는 지그재그의 직선형상이나 구불구불한 곡면형상과 같이 다양한 형상으로 구성될 수 있다. 또한, 도면에서는 복수의 유입통로(310a)가 제2컨택홀(329b) 주위의 사각형상 화소전극(310)의 특정 일변측(즉, 하변측)에 모두 형성되지만, 유입통로(310a)가 타변(즉, 상변이나 측변)에 형성될 수 있고 두변이나 그 이상의 변에 형성될 수도 있다. 복수의 유입통로(310a)

a)가 두번 이상의 변에 형성되는 경우, 각 변에 형성되는 유입통로(310a)는 모두 동일한 형상으로 구성될 수도 있고 다른 형상으로 구성될 수 있다.

[0090] 상술한 설명에서는 본 발명을 특정 구조로 설명하고 있지만, 이는 설명의 편의를 위한 것이지 발명을 한정하기 위한 것은 아니다. 예를 들어, 상술한 상세한 설명에서는 화소전극과 공통전극의 구조가 특정 구조로 개시되어 있지만, 본 발명이 이러한 특정 구조의 화소전극과 공통전극에 한정되는 것이 아니다. 본 발명은 액정표시장치에 관한 것으로, 배향막이 구비된 모든 구조의 액정표시장치에 적용될 수 있을 것이다.

[0091] 또한, 상기한 설명에 많은 사항이 구체적으로 기재되어 있으나 이것은 발명의 범위를 한정하는 것이라기보다 바람직한 실시예의 예시로서 해석되어야 한다. 따라서 발명은 설명된 실시예에 의하여 정할 것이 아니고 특허청구 범위와 특허청구범위에 균등한 것에 의하여 정하여져야 한다.

### 부호의 설명

[0092] 120,130,220,230 : 기판 210,310 : 화소전극

224,324 : 제1보호층 226,326 : 제2보호층

229a,229b,329a,329b : 컨택홀 236,336 : 공통전극

228,238,328,338 : 배향막

### 도면

#### 도면1

#### 도면2

도면3a

도면3b

도면4

도면5a

도면5b

도면6a

도면6b

도면6c

도면7a

도면7b

도면7c

도면7d

도면7e

도면8a

도면8b

도면9a

도면9b

|                |                                  |         |            |

|----------------|----------------------------------|---------|------------|

| 专利名称(译)        | 一种具有均匀取向膜的液晶显示装置                 |         |            |

| 公开(公告)号        | <a href="#">KR1020170045618A</a> | 公开(公告)日 | 2017-04-27 |

| 申请号            | KR1020150145448                  | 申请日     | 2015-10-19 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                         |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                        |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                        |         |            |

| [标]发明人         | KIM SULKI<br>김슬기                 |         |            |

| 发明人            | 김슬기                              |         |            |

| IPC分类号         | G02F1/1337 G02F1/1343 G02F1/1368 |         |            |

| CPC分类号         | G02F1/1337 G02F1/1368 G02F1/1343 |         |            |

| 代理人(译)         | 박장원                              |         |            |

| 外部链接           | <a href="#">Espacenet</a>        |         |            |

### 摘要(译)

在本发明中，由围绕接触孔布置的像素电极产生的阶梯式滑轮被移除，并且对准液体流入接触孔内，并且它防止了蚀刻剂的穿透路径，该蚀刻剂用于随后移除一个接触孔的整个像素电极围绕并且可以形成进入通道，其中对准液体流入并移除给定的长度区域并给予涡旋并形成入口通道并且对准液体顺畅地流动通过接触孔内部的入口通道并同时蚀刻像素电极作为最大值并且蚀刻剂穿透到像素电极内部。