(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2017-0117263

(43) 공개일자 2017년10월23일

- (51) 국제특허분류(Int. Cl.)

*G02F 1/136* (2006.01) *G02F 1/1333* (2006.01)

*H01B 1/02* (2006.01)

- (52) CPC특허분류

*G02F 1/136* (2013.01)

*H01B 1/02* (2013.01)

- (21) 출원번호 10-2016-0044793

(22) 출원일자 2016년04월12일

심사청구일자 없음

- (71) 출원인

삼성디스플레이 주식회사

경기도 용인시 기흥구 삼성로 1 (농서동)

(72) 발명자

정형기

충청남도 천안시 서북구 월봉7길 16-2 (쌍용동,

아트스타 미술학원 3층)

(74) 대리인

윤여광, 조우제, 허창준, 이재형, 노환옥, 염주석

전체 청구항 수 : 총 16 항

(54) 발명의 명칭 **액정 표시 장치**

### (57) 요 약

본 발명은 정전기 유입에 따른 기판 전극 및 구동 소자의 손상을 방지할 수 있는 액정 표시 장치에 관한 것으로, 기판; 기판의 표시 영역에 배치되고, 게이트 라인과 데이터 라인에 연결된 박막 트랜지스터; 박막 트랜지스터와 연결되는 화소 전극; 화소 전극과 마주보며 위치하는 루프층; 표시 영역과 인접하는 비표시 영역에 배치되는 제1 정전기 분산 패턴; 제1 정전기 분산 패턴과 전기적으로 연결된 접지 라인; 및 화소 전극과 루프층 사이에 액정 주입구를 갖는 미세 공간(Microcavity)이 형성되며, 미세 공간에 위치하고 액정 분자로 이루어진 액정층을 포함한다.

**대 표 도** - 도2

(52) CPC특허분류

*G02F 2001/133334 (2013.01)*

*G02F 2001/13606 (2013.01)*

*G02F 2202/22 (2013.01)*

---

## 명세서

### 청구범위

#### 청구항 1

기판;

상기 기판의 표시 영역에 배치되고, 게이트 라인과 데이터 라인에 연결된 박막 트랜지스터;

상기 박막 트랜지스터와 연결되는 화소 전극;

상기 화소 전극과 마주보며 위치하는 루프층;

상기 표시 영역과 인접하는 비표시 영역에 배치되는 제 1 정전기 분산 패턴;

상기 제 1 정전기 분산 패턴과 전기적으로 연결된 접지 라인; 및

상기 화소 전극과 상기 루프층 사이에 액정 주입구를 갖는 미세 공간(Microcavity)이 형성되며, 상기 미세 공간에 위치하고 액정 분자로 이루어진 액정층을 포함하는 액정 표시 장치.

#### 청구항 2

제 1 항에 있어서,

상기 제 1 정전기 분산 패턴은 투명 도전성 물질을 포함하는 액정 표시 장치.

#### 청구항 3

제 2 항에 있어서,

상기 투명 도전성 물질은 ITO(Indium Tin Oxide) 또는 IZO(Indium Zinc Oxide)인 액정 표시 장치.

#### 청구항 4

제 1 항에 있어서,

상기 제 1 정전기 분산 패턴은 상기 화소 전극과 동시에 패턴된 액정 표시 장치.

#### 청구항 5

제 1 항에 있어서,

상기 화소 전극 상에 위치하여 상기 미세 공간을 사이에 두고 이격된 공통 전극을 더 포함하는 액정 표시 장치.

#### 청구항 6

제 5 항에 있어서,

상기 제 1 정전기 분산 패턴은 상기 공통 전극과 동시에 패턴된 액정 표시 장치.

#### 청구항 7

제 1 항에 있어서,

상기 제 1 정전기 분산 패턴은 상기 접지 라인의 적어도 일부와 중첩하는 액정 표시 장치.

#### 청구항 8

제 1 항에 있어서,

상기 접지 라인은 상기 게이트 라인과 동시에 패턴된 액정 표시 장치.

#### 청구항 9

제 5 항에 있어서,

상기 접지 라인은 상기 공통 전극과 전기적으로 연결된 액정 표시 장치.

#### 청구항 10

제 9 항에 있어서,

상기 접지 라인과 연결되며, 상기 접지 라인으로 유입되는 정전기를 분산시키기 위한 정전 다이오드를 더 포함하는 액정 표시 장치.

#### 청구항 11

제 10 항에 있어서,

상기 정전 다이오드는 상기 박막 트랜지스터와 동시에 패턴된 액정 표시 장치.

#### 청구항 12

제 1 항에 있어서,

상기 루프층 상에 위치하고, 상기 액정 주입구를 덮는 캐핑막을 더 포함하는 액정 표시 장치.

#### 청구항 13

제 12 항에 있어서,

상기 캐핑막 상에 배치된 제 2 정전기 분산 패턴을 더 포함하는 액정 표시 장치.

#### 청구항 14

제 13 항에 있어서,

상기 제 2 정전기 분산 패턴은 상기 기판의 전면(全面)에 배치되는 액정 표시 장치.

#### 청구항 15

제 13 항에 있어서,

상기 제 2 정전기 분산 패턴은 투명 도전성 물질을 포함하는 액정 표시 장치.

#### 청구항 16

제 15 항에 있어서,

상기 투명 도전성 물질은 ITO(Indium Tin Oxide) 또는 IZO(Indium Zinc Oxide)인 액정 표시 장치.

### 발명의 설명

#### 기술 분야

[0001] 본 발명은 액정 표시 장치에 관한 것이다.

#### 배경 기술

[0002] 액정 표시 장치는 현재 가장 널리 사용되고 있는 평판 표시 장치 중 하나로서, 화소 전극과 공통 전극 등 전기 장 생성 전극이 형성되어 있는 두 장의 표시판과 그 사이에 들어 있는 액정층으로 이루어진다.

[0003] 전기장 생성 전극에 전압을 인가하여 액정층에 전기장을 생성하고 이를 통하여 액정층의 액정 분자들의 배향을 결정하고 입사광의 편광을 제어함으로써 영상을 표시한다.

[0004] 액정 표시 장치 가운데 NCD(Nano Crystal Display) 액정 표시 장치는 유기 물질 등으로 희생층을 형성하고 상부에 루프층(Roof layer)을 형성한 후에 희생층을 제거하고, 희생층 제거로 형성된 미세 공간(Microcavity)에 액

정을 채워 디스플레이를 만드는 장치이다.

[0005] NCD 액정 표시 장치의 제조시 상부 기판은 생략될 수 있다. 이때, 액정층 및 기판 소자 등을 수분, 물리적인 충격 및 제조 공정시 발생하는 이물로부터 보호하기 위한 캐핑막이 형성된다. 그러나, 공정 상에서 발생하는 정전기는 상부 기판이 생략된 NCD 액정 패널의 금속 배선에 유입될 수 있다. 이러한 정전기는 금속 배선들의 단선 및 단락과 같은 배선 불량을 발생시키고, 박막 트랜지스터를 손상시킬 수 있다.

### 발명의 내용

#### 해결하려는 과제

[0006] 본 발명은 상기와 같은 문제점을 해결하기 위하여 안출된 것으로, 정전기 유입에 따른 기판 전극 및 구동 소자의 손상을 방지할 수 있는 액정 표시 장치를 제공하는데 그 목적이 있다.

#### 과제의 해결 수단

[0007] 상기와 같은 목적을 달성하기 위한 본 발명에 따른 액정 표시 장치는, 기판; 기판의 표시 영역에 배치되고, 게이트 라인과 데이터 라인에 연결된 박막 트랜지스터; 박막 트랜지스터와 연결되는 화소 전극; 화소 전극과 마주보며 위치하는 루프층; 표시 영역과 인접하는 비표시 영역에 배치되는 제 1 정전기 분산 패턴; 제 1 정전기 분산 패턴과 전기적으로 연결된 접지 라인; 및 화소 전극과 루프층 사이에 액정 주입구를 갖는 미세 공간(Microcavity)이 형성되며, 미세 공간에 위치하고 액정 분자로 이루어진 액정층을 포함한다.

[0008] 제 1 정전기 분산 패턴은 투명 도전성 물질을 포함한다.

[0009] 투명 도전성 물질은 ITO(Indium Tin Oxide) 또는 IZO(Indium Zinc Oxide)를 포함한다.

[0010] 제 1 정전기 분산 패턴은 화소 전극과 동시에 패턴된다.

[0011] 화소 전극 상에 위치하여 미세 공간을 사이에 두고 이격된 공통 전극을 더 포함한다.

[0012] 제 1 정전기 분산 패턴은 공통 전극과 동시에 패터닝된다.

[0013] 제 1 정전기 분산 패턴은 접지 라인의 적어도 일부와 중첩한다.

[0014] 접지 라인은 게이트 라인과 동시에 패터닝된다.

[0015] 접지 라인은 공통 전극과 전기적으로 연결된다.

[0016] 접지 라인과 연결되며, 접지 라인으로 유입되는 정전기를 분산시키기 위한 정전 다이오드를 더 포함한다.

[0017] 정전 다이오드는 박막 트랜지스터와 동시에 패터닝된다.

[0018] 루프층 상에 위치하고, 액정 주입구를 덮는 캐핑막을 더 포함한다.

[0019] 캐핑막 상에 배치된 제 2 정전기 분산 패턴을 더 포함한다.

[0020] 제 2 정전기 분산 패턴은 기판의 전면(全面)에 배치된다.

[0021] 제 2 정전기 분산 패턴은 투명 도전성 물질을 포함한다.

[0022] 투명 도전성 물질은 ITO(Indium Tin Oxide) 또는 IZO(Indium Zinc Oxide)를 포함한다.

### 발명의 효과

[0023] 본 발명에 따른 액정 표시 장치는 접지 라인에 접속하는 제 1 정전기 분산 패턴을 배치함으로써, 정전기로 인해 유입된 전하들을 분산될 수 있다. 따라서, 정전기 유입에 따른 기판 전극 및 구동 소자의 손상을 방지할 수 있다.

### 도면의 간단한 설명

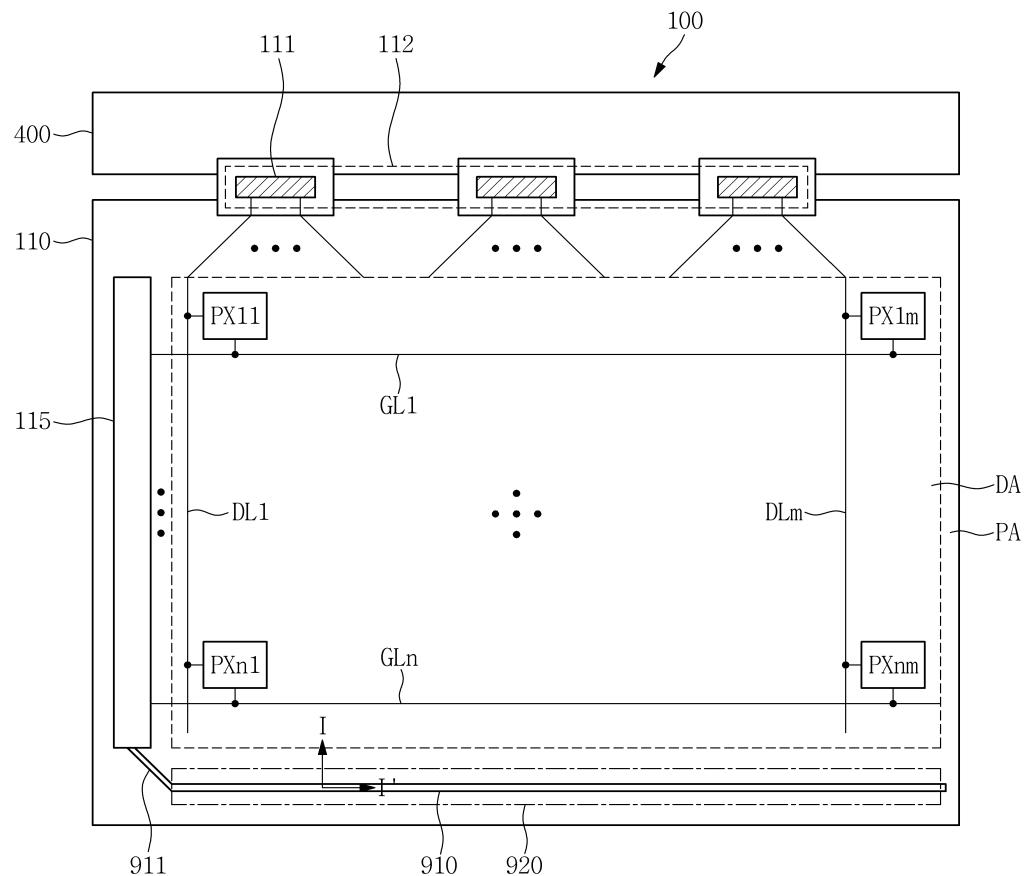

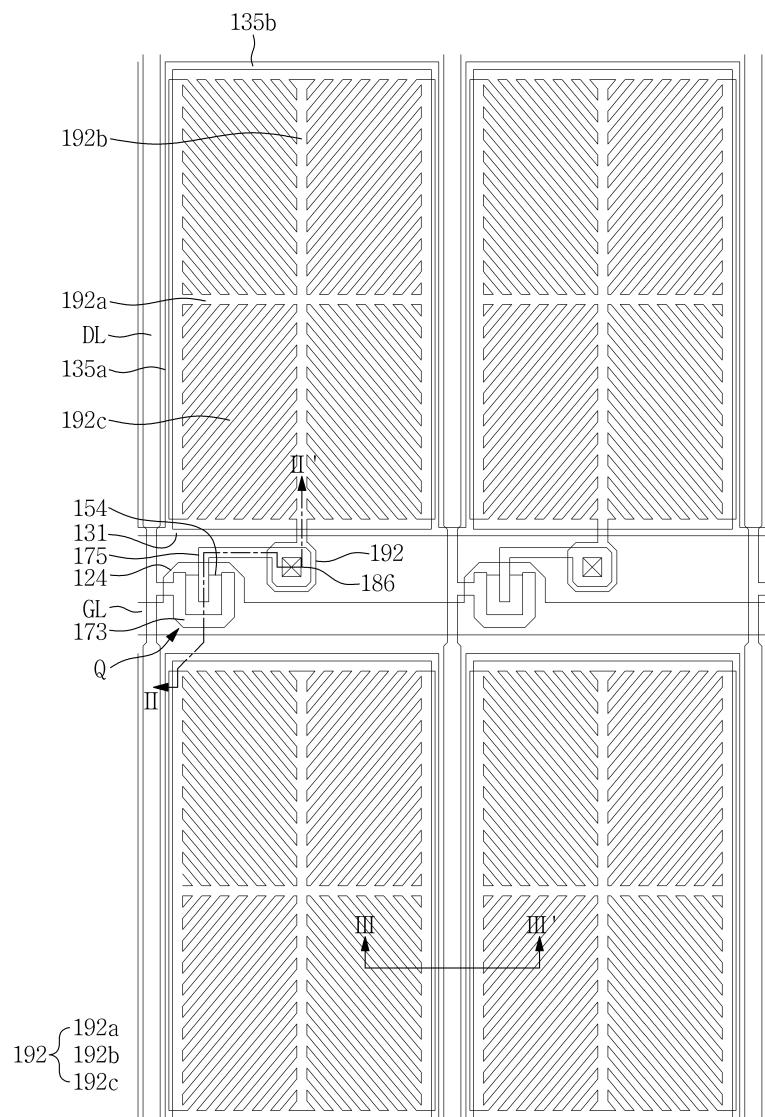

[0024] 도 1은 본 발명의 일 실시예에 따른 액정 표시 장치의 평면도이다.

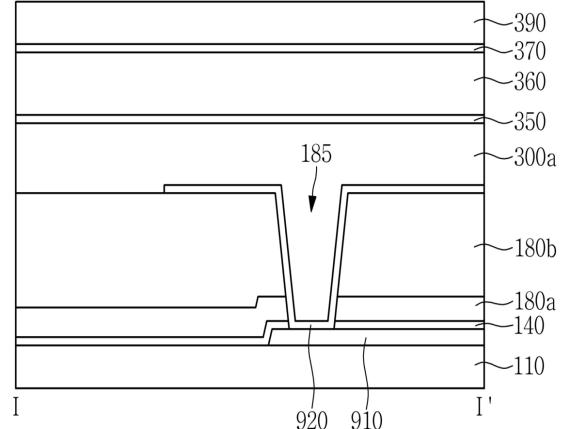

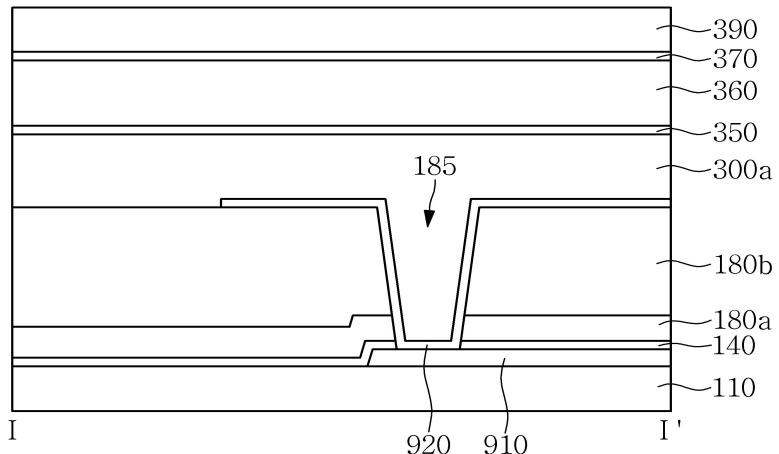

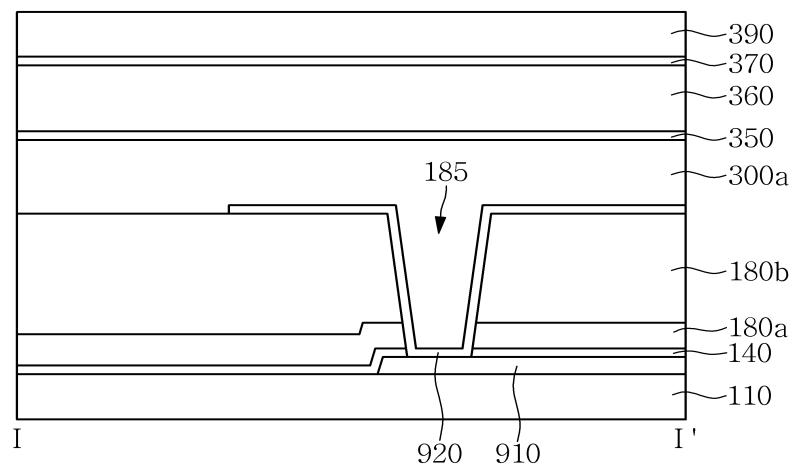

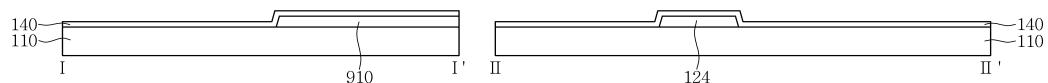

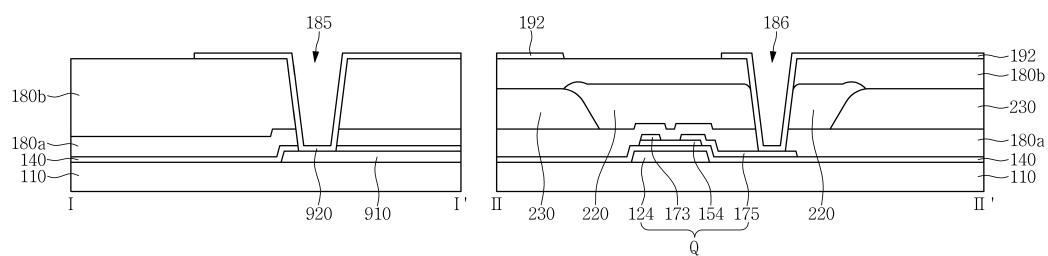

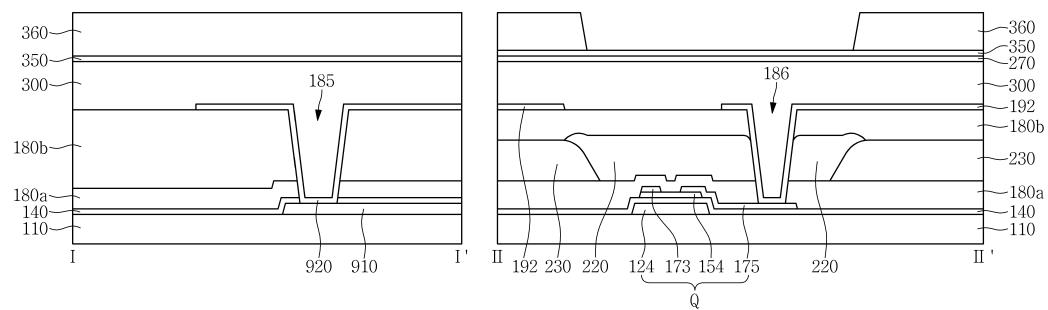

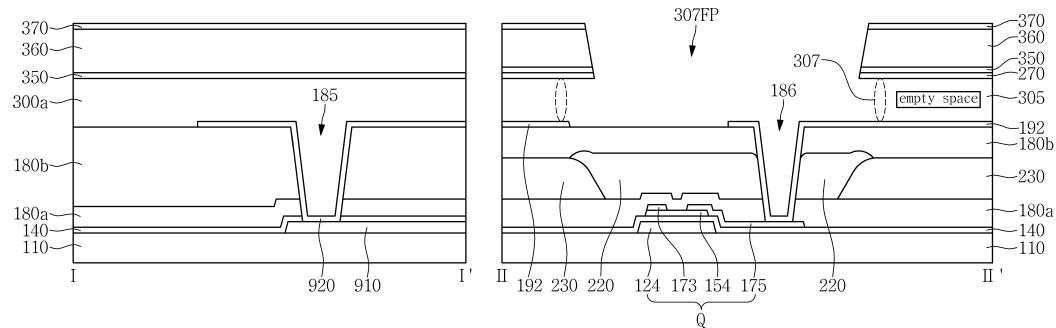

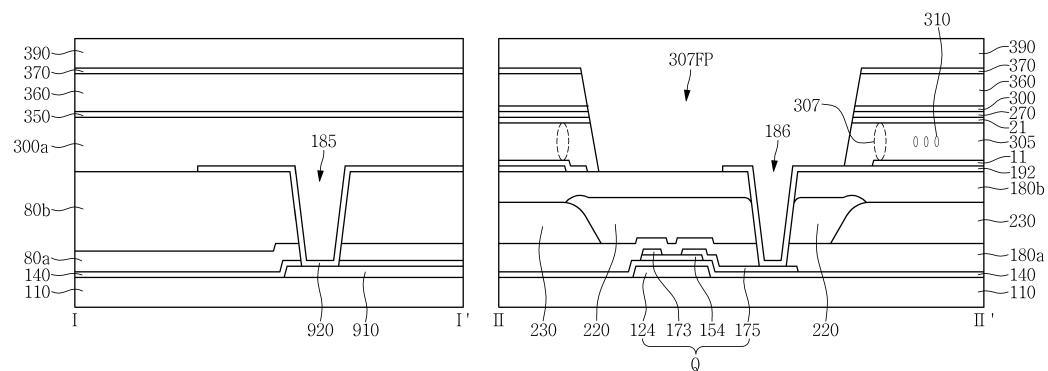

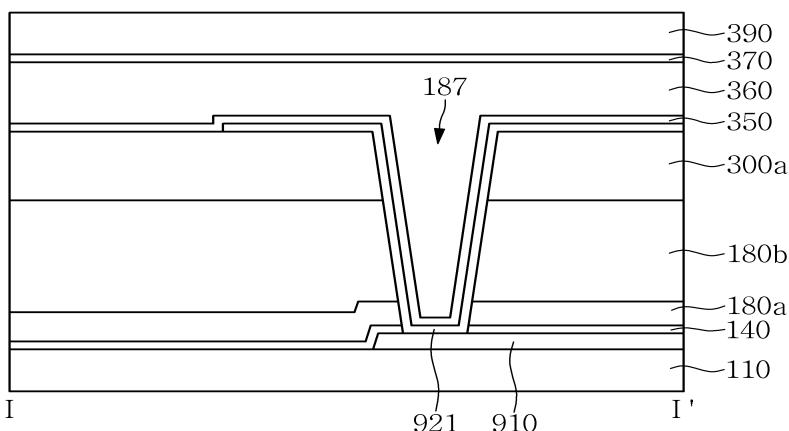

도 2는 도 1의 I-I'선을 따라 자른 단면도이다.

도 3은 도 1의 화소 영역에 대한 확대 평면도이다.

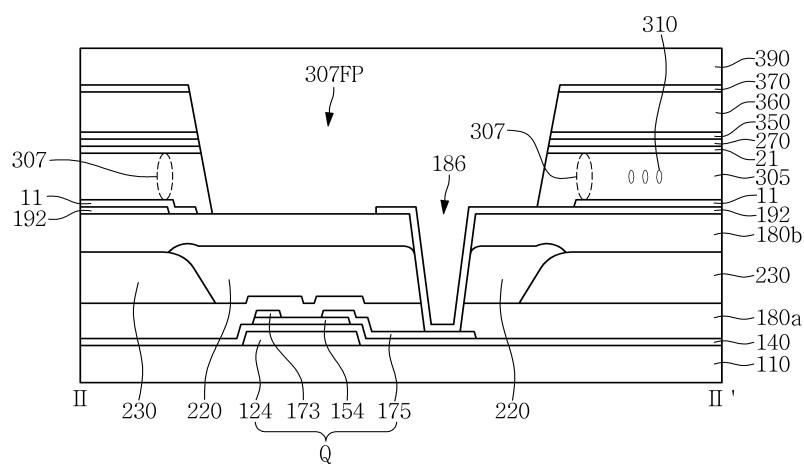

도 4는 도 3의 II-II'선을 따라 자른 단면도이다.

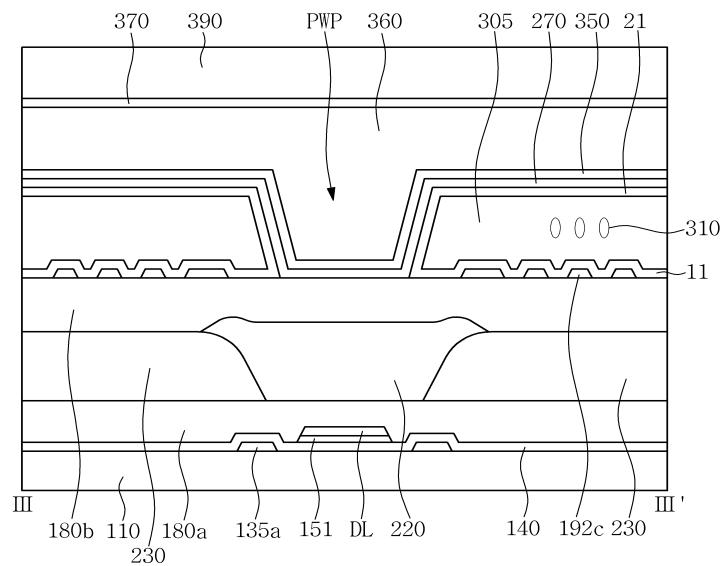

도 5는 도 3의 III-III'선을 따라 자른 단면도이다.

도 6a 내지 도 6e는 본 발명의 일 실시예에 따른 액정 표시 장치의 제조 공정을 나타낸 단면도이다.

도 7은 본 발명의 다른 실시예에 따른 액정 표시 장치의 단면도이다.

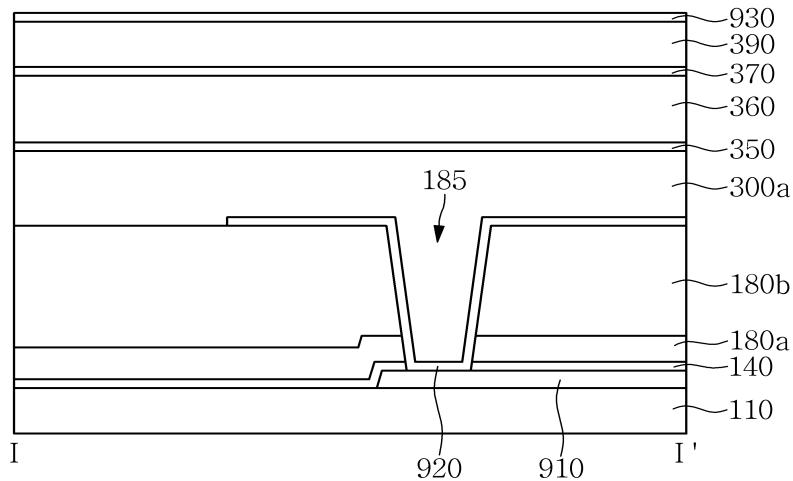

도 8은 본 발명의 또 다른 실시예에 따른 액정 표시 장치의 단면도이다.

### 발명을 실시하기 위한 구체적인 내용

[0025]

본 발명의 이점 및 특징, 그리고 그것들을 달성하는 방법은 첨부되는 도면과 함께 상세하게 후술되어 있는 실시 예들을 참조하면 명확해질 것이다. 그러나 본 발명은 이하에서 개시되는 실시예들에 한정되는 것이 아니라 서로 다른 다양한 형태로 구현될 것이며, 단지 본 실시예들은 본 발명의 개시가 완전하도록 하며, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자에게 발명의 범주를 완전하게 알려주기 위해 제공되는 것이며, 본 발명은 청구항의 범주에 의해 정의될 뿐이다. 따라서, 몇몇 실시예에서, 잘 알려진 공정 단계들, 잘 알려진 소자 구조 및 잘 알려진 기술들은 본 발명이 모호하게 해석되는 것을 피하기 위하여 구체적으로 설명되지 않는다. 명세서 전체에 걸쳐 동일 참조 부호는 동일 구성 요소를 지칭한다.

[0026]

도면에서 여러 층 및 영역을 명확하게 표현하기 위하여 두께를 확대하여 나타내었다. 명세서 전체를 통하여 유사한 부분에 대해서는 동일한 도면 부호를 붙였다. 층, 막, 영역, 판 등의 부분이 다른 부분 "위에" 있다고 할 때, 이는 다른 부분 "바로 위에" 있는 경우뿐 아니라 그 중간에 또 다른 부분이 있는 경우도 포함한다. 반대로 어떤 부분이 다른 부분 "바로 위에" 있다고 할 때에는 중간에 다른 부분이 없는 것을 뜻한다. 또한, 층, 막, 영역, 판 등의 부분이 다른 부분 "아래에" 있다고 할 때, 이는 다른 부분 "바로 아래에" 있는 경우뿐 아니라 그 중간에 또 다른 부분이 있는 경우도 포함한다. 반대로 어떤 부분이 다른 부분 "바로 아래에" 있다고 할 때에는 중간에 다른 부분이 없는 것을 뜻한다.

[0027]

공간적으로 상대적인 용어인 "아래(below)", "아래(beneath)", "하부(lower)", "위(above)", "상부(upper)" 등은 도면에 도시되어 있는 바와 같이 하나의 소자 또는 구성 요소들과 다른 소자 또는 구성 요소들과의 상관관계를 용이하게 기술하기 위해 사용될 수 있다. 공간적으로 상대적인 용어는 도면에 도시되어 있는 방향에 더하여 사용시 또는 동작시 소자의 서로 다른 방향을 포함하는 용어로 이해되어야 한다. 예를 들면, 도면에 도시되어 있는 소자를 뒤집을 경우, 다른 소자의 "아래(below)" 또는 "아래(beneath)"로 기술된 소자는 다른 소자의 "위(above)"에 놓여질 수 있다. 따라서, 예시적인 용어인 "아래"는 아래와 위의 방향을 모두 포함할 수 있다. 소자는 다른 방향으로도 배향될 수 있고, 이에 따라 공간적으로 상대적인 용어들은 배향에 따라 해석될 수 있다.

[0028]

본 명세서에서 어떤 부분이 다른 부분과 연결되어 있다고 할 때, 이는 직접적으로 연결되어 있는 경우뿐 아니라, 그 중간에 다른 소자를 사이에 두고 전기적으로 연결되어 있는 경우도 포함한다. 또한, 어떤 부분이 어떤 구성 요소를 포함한다고 할 때, 이는 특별히 그에 반대되는 기재가 없는 한 다른 구성요소를 제외하는 것이 아니라 다른 구성요소를 더 포함할 수 있는 것을 의미한다.

[0029]

본 명세서에서 제 1, 제 2, 제 3 등의 용어는 다양한 구성 요소들을 설명하는데 사용될 수 있지만, 이러한 구성 요소들은 상기 용어들에 의해 한정되는 것은 아니다. 상기 용어들은 하나의 구성 요소를 다른 구성 요소들로부터 구별하는 목적으로 사용된다. 예를 들어, 본 발명의 권리 범위로부터 벗어나지 않고, 제 1 구성 요소가 제 2 또는 제 3 구성 요소 등으로 명명될 수 있으며, 유사하게 제 2 또는 제 3 구성 요소도 교호적으로 명명될 수 있다.

[0030]

다른 정의가 없다면, 본 명세서에서 사용되는 모든 용어(기술 및 과학적 용어를 포함)는 본 발명이 속하는 기술 분야에서 통상의 지식을 가진 자에게 공통적으로 이해될 수 있는 의미로 사용될 수 있을 것이다. 또 일반적으로 사용되는 사전에 정의되어 있는 용어들은 명백하게 특별히 정의되어 있지 않은 한 이상적으로 또는 과도하게 해석되지 않는다.

[0031]

도 1은 본 발명의 일 실시예에 따른 액정 표시 장치의 평면도이고, 도 2는 도 1의 I-I'선을 따라 자른 단면도이다.

[0032]

도 1에 도시된 바와 같이, 본 발명의 일 실시예에 따른 액정 표시 장치(100)는 기판(110), 데이터 드라이버

(112), 게이트 드라이버(115) 및 회로 기판(400)을 포함한다.

[0033] 기판(110)은 표시 영역(DA)와 표시 영역(DA)을 둘러싸는 비표시 영역(PA)을 포함한다.

[0034] 표시 영역(DA)은 복수의 게이트 라인들(GL1-GLn), 복수의 게이트 라인들(GL1-GLn)과 교차하는 복수의 데이터 라인들(DL1-DLm), 상기 복수의 게이트 라인들(GL1-GLn)과 상기 복수의 데이터 라인들(DL1-DLm)에 전기적으로 연결된 복수의 화소들(PX11-PXnm)을 포함한다.

[0035] 게이트 라인들(GL1-GLn)은 게이트 드라이버(115)에 연결된다. 게이트 라인들(GL1-GLn)은 게이트 드라이버(115)로부터 순차적으로 발생되는 게이트 신호들을 차례로 입력 받는다. 게이트 드라이버(115)는 후술할 공통 전극(270)으로 공통 전압을 전달하는 공통 라인(미도시)을 더 포함할 수 있다.

[0036] 데이터 라인들(DL1-DLm)은 데이터 드라이버(112)에 연결된다. 데이터 라인들(DL1-DLm)은 데이터 드라이버(112)로부터 아날로그 형태의 데이터 전압들을 입력 받는다.

[0037] 데이터 드라이버(112)는 복수의 데이터 구동 접적 회로(111)를 포함한다. 데이터 구동 접적 회로(111)는 데이터 캐리어에 실장된다. 데이터 캐리어들은 상기 기판(110)과 회로 기판(400) 사이에 접속된다. 즉, 데이터 드라이버(112)는 TCP(Tape Carrier Package) 또는 COF(Chip On Film)의 구조로 이루어질 수 있으며, 상기 기판(110) 상에 실장되는 COG(Chip On Glass)의 구조로 이루어질 수도 있다.

[0038] 화소들(PX11-PXnm)은 게이트 라인들(GL1-GLn)과 데이터 라인들(DL1-DLm)이 교차하는 영역에 위치한다. 화소들(PX11-PXnm)은 서로 교차하는 n개의 행들 및 m개의 열들로 배열될 수 있다. n 및 m은 0보다 큰 정수이다.

[0039] 화소들(PX11-PXnm)은 각각 대응하는 게이트 라인들(GL1-GLn)과 데이터 라인들(DL1-DLm)에 연결된다. 화소들(PX11-PXnm)은 게이트 라인(GL)으로부터의 게이트 신호에 응답하여, 데이터 라인(DL)으로부터 데이터 전압을 공급 받는다. 화소들(PX11-PXnm)은 데이터 전압에 대응하는 계조를 표시한다.

[0040] 도 1 및 도 2를 참조하면, 본 발명의 일 실시예에 따른 액정 표시 장치(100)는 기판(110)의 비표시 영역(PA)에 배치되는 접지 라인(910), 게이트 절연막(140), 제 1 및 제 2 충간 절연막(180a, 180b), 제 1 정전기 분산 패턴(920), 잔류 희생층(300a), 하부 절연층(350), 루프층(360), 상부 절연층(370) 및 캐핑막(390)을 더 포함한다.

[0041] 투명한 유리 또는 플라스틱 등으로 만들어진 절연성을 갖는 기판(110) 상에 접지 라인(910)이 형성된다. 접지 라인(910)은 게이트 라인(GL)과 동일한 금속층으로 이루어지거나, 데이터 라인(DL)과 동일한 금속층으로 이루어질 수 있다. 본 실시예들에서는 접지 라인(910)이 게이트 라인(GL)과 동일한 금속층으로 이루어진 것을 예로 설명한다.

[0042] 또한, 접지 라인(910)은 기판(110) 하측의 비표시 영역(PA)에 형성되어, 보조 라인(911)을 통해 게이트 드라이버(115) 내의 공통 라인(미도시)과 연결될 수 있다. 이에 따라, 접지 라인(910)은 후술할 공통 전극(270)과 전기적으로 연결된다.

[0043] 본 발명의 일 실시예에 따른 공통 라인(미도시)은 게이트 드라이버(115) 내에 포함되는 것으로 설명하고 있으나 이에 한정되는 것은 아니며, 공통 라인(미도시)은 게이트 드라이버(115)의 외부에 별도로 배치되거나 표시 영역(DA)의 3면을 둘러싸는 형태로 배치될 수도 있다.

[0044] 보조 라인(911)은 접지 라인(910)으로 유입되는 정전기를 상쇄 및 분산시키기 위한 복수개의 정전 다이오드(미도시)를 포함할 수 있다. 정전 다이오드(미도시)는 후술한 박막 트랜지스터(Q)와 동시에 패터닝될 수 있다.

[0045] 정전 다이오드(미도시)는 정전기 유입시 항복 전압 이상의 정전기 전압을 접지 라인(910)으로 전달하거나 자체적으로 정전기를 상쇄시킬 수 있으며, 보조 라인(911)과 연결된 공통 라인(미도시)으로 정전기가 빠져나가도록 할 수 있다. 이에 따라, 정전기 유입에 따른 기판 전극 및 구동 소자의 손상을 방지할 수 있다.

[0046] 접지 라인(910) 상에 게이트 절연막(140), 제 1 충간 절연막(180a) 및 제 2 충간 절연막(180b)이 배치된다.

[0047] 게이트 절연막(140), 제 1 및 제 2 충간 절연막(180a, 180b)은 질화 규소(SiNx), 산화 규소(SiOx) 및 질산화 규소(SiOxNy)와 같은 무기 절연물 또는 아크릴계 레진(Acrylic resin) 및 벤조사이클로부텐(BCB)과 같은 유기 절연물을 포함할 수 있다.

[0048] 이때, 도시되지 않았으나, 제 1 충간 절연막(180a)과 제 2 충간 절연막(180b) 사이에는 차광 부재가 더 배치될 수 있다.

[0049] 게이트 절연막(140), 제 1 및 제 2 충간 절연막(180a, 180b)에는 접지 라인(910)을 노출하는 제 1 컨택홀(18

## 5)이 형성된다

- [0050] 본 발명의 일 실시예에 따르면, 제 1 정전기 분산 패턴(920)은 제 2 충간 절연막(180b) 상에 배치되어, 제 1 컨택홀(185)을 통해 접지 라인(910)과 접속된다. 따라서, 제 1 정전기 분산 패턴(920)과 접지 라인(910)이 전기적으로 연결된다.

- [0051] 이에 따라, 정전기로 인해 유입된 전하들이 제 1 정전기 분산 패턴(920) 및 접지 라인(910)을 통해 대면적으로 분산될 수 있다. 또한, 접지 라인(910)과 연결된 상기 보조 라인(911)의 정전 다이오드(미도시)가 유입된 전하들의 일부를 통과시키고, 이에 따라 일부 전하들은 공통 라인(미도시)으로 빠져나갈 수 있다. 따라서, 정전기 유입에 따른 기판 전극 및 구동 소자의 손상을 방지할 수 있다.

- [0052] 이때, 제 1 정전기 분산 패턴(920)은 ITO(Indium tin oxide) 또는 IZO(Indium zinc oxide) 등의 투명 도전 물질로 만들어질 수 있다. 이때, ITO는 다결정 또는 단결정의 물질일 수 있으며, 또한 IZO 역시 다결정 또는 단결정의 물질일 수 있다.

- [0053] 제 1 정전기 분산 패턴(920) 및 제 2 충간 절연막(180b) 상에 후술할 잔류 희생층(300a) 및 하부 절연층(350)이 배치된다. 하부 절연층(350)은 질화 규소(SiNx) 및 산화 규소(SiO<sub>2</sub>)와 같은 무기 절연물을 포함할 수 있다.

- [0054] 하부 절연층(350) 상에 루프층(Roof Layer; 360)이 위치한다. 루프층(360)은 포토 레지스트 또는 그 밖의 유기 물질을 포함할 수 있다.

- [0055] 루프층(360) 상에 상부 절연층(370)이 위치한다. 상부 절연층(370)은 질화 규소(SiNx) 및 산화 규소(SiO<sub>2</sub>)와 같은 무기 절연물을 포함할 수 있다.

- [0056] 상부 절연층(370) 위에 캐핑막(390)이 위치한다. 캐핑막(390)은 열경화성 수지, 실리콘 옥시카바이드(SiOC) 또는 그라핀(Graphene)으로 형성될 수 있다.

- [0057] 도 3은 도 1의 화소 영역에 대한 확대 평면도이고, 도 4는 도 3의 II-II'선을 따라 자른 단면도이며, 도 5는 도 3의 III-III'선을 따라 자른 단면도이다.

- [0058] 상세하게는 도 3 내지 도 5를 참고하면, 본 발명의 일 실시예에 따른 액정 표시 장치(100)는 기판(110)의 표시 영역(DA)에 배치된 박막 트랜지스터(Q), 게이트 절연막(140), 제 1 및 제 2 충간 절연막(180a, 180b), 화소 전극(192), 공통 전극(270), 하부 절연층(350), 루프층(360), 상부 절연층(370) 및 캐핑막(390)을 포함한다.

- [0059] 투명한 유리 또는 플라스틱 등으로 만들어진 절연성을 갖는 기판(110) 상에 게이트 라인(GL) 및 유지 전압 라인(131)이 형성된다. 게이트 라인(GL)은 게이트 전극(124)을 포함하며, 유지 전압 라인(131)은 유지 전극(135a, 135b)을 포함한다. 유지 전극(135a, 135b)은 화소 전극(192)을 둘러싸는 구조를 가질 수 있다.

- [0060] 게이트 라인(GL) 및 유지 전압 라인(131) 상에 게이트 절연막(140)이 위치하며, 게이트 절연막(140)은 질화 규소(SiNx) 및 산화 규소(SiO<sub>2</sub>)와 같은 무기 절연물을 포함할 수 있다.

- [0061] 게이트 절연막(140) 상에는 반도체층(151, 154)이 위치한다. 반도체층(151, 154)은 데이터 라인(DL) 하부에 위치하는 반도체층(151) 및 소스/드레인 전극(173, 175)의 하부와 박막 트랜지스터(Q)의 채널 부분에 위치하는 반도체층(154)을 포함한다.

- [0062] 데이터 라인(DL) 또는 소스/드레인 전극(173, 175)과 각 반도체층(151, 154) 사이에는 복수의 저항성 접촉 부재(미도시)가 추가로 형성될 수 있다.

- [0063] 각 반도체층(151, 154) 및 게이트 절연막(140) 상에 데이터 라인(DL), 소스 전극(173) 및 드레인 전극(175)을 포함하는 데이터 도전체(DL, 173, 175)가 형성된다.

- [0064] 게이트 전극(124), 소스 전극(173), 및 드레인 전극(175)은 반도체층(154)과 함께 박막 트랜지스터(Q)를 형성하며, 박막 트랜지스터의 채널(channel)은 소스 전극(173)과 드레인 전극(175) 사이의 반도체층(154) 부분에 형성된다.

- [0065] 본 발명의 일 실시예에 따른 데이터 라인(DL)은 박막 트랜지스터(Q) 형성 영역에서 폭이 좁아지는 구조를 가진다. 이는 인접하는 배선과의 간격을 유지하고 신호 간섭을 줄이기 위한 구조이나, 데이터 라인(DL)의 구조는 이에 한정되지 않는다.

- [0066] 데이터 도전체(DL, 173, 175) 및 노출된 반도체층(154) 부분 상에는 제 1 충간 절연막(180a)이 형성되어 있다. 제 1 충간 절연막(180a)은 질화 규소(SiNx), 산화 규소(SiO<sub>x</sub>) 및 질산화 규소(SiO<sub>x</sub>Ny)와 같은 무기 절연물 또는

아크릴계 레진(Acryl resin) 및 벤조사이클로부텐(BCB)과 같은 유기 절연물을 포함할 수 있다.

[0067] 제 1 층간 절연막(180a) 상에는 컬러 필터(230) 및 차광 부재(220)가 형성된다.

[0068] 차광 부재(220)는 화상을 표시하는 영역에 대응하는 개구부를 가지는 격자 구조로 이루어져 있으며, 빛이 투과하지 못하는 물질로 형성되어 있다. 차광 부재(220)의 개구부에는 컬러 필터(230)가 형성된다.

[0069] 컬러 필터(230)는 적색, 녹색 및 청색의 삼원색 등 기본색(primary color) 중 하나를 표시할 수 있다. 또한, 적색, 녹색, 및 청색의 삼원색에 제한되지 않고, 청록색(cyan), 자홍색(magenta), 황색(yellow), 화이트 계열의 색 중 하나를 표시할 수도 있다. 컬러 필터(230)는 인접하는 화소(PX)마다 서로 다른 색을 표시하는 물질로 형성될 수 있다.

[0070] 차광 부재(220) 및 컬러 필터(230) 상에는 이를 덮는 제 2 층간 절연막(180b)이 형성되어 있다.

[0071] 제2 층간 절연막(180b)은 질화 규소(SiNx), 산화 규소(SiOx) 및 질산화 규소(SiOxNy)와 같은 무기 절연물을 포함할 수 있다. 또한, 컬러 필터(230) 및 차광 부재(220)의 배치로 인하여 단차가 발생된 경우 제 2 층간 절연막(180b)은 아크릴계 레진(Acryl resin) 및 벤조사이클로부텐(BCB)과 같은 유기 절연물을 포함하여 단차를 감소시키거나 제거할 수 있다.

[0072] 차광 부재(220), 제 1 및 제 2 층간 절연막(180a, 180b)에는 드레인 전극(175)을 노출하는 제 2 컨택홀(186)이 형성된다.

[0073] 본 발명의 일 실시예에서는 차광 부재(220), 제 1 및 제 2 층간 절연막(180a, 180b)을 식각하여 제 2 컨택홀(186)을 형성하고 있으나, 실제 차광 부재(220)의 식각은 그 재질에 따라서 제 1 및 제 2 층간 절연막(180a, 180b)에 비하여 어려울 수 있다. 따라서, 제 2 컨택홀(186)이 형성되는 위치의 차광 부재(220)는 미리 제거될 수도 있다.

[0074] 한편, 실시예에 따라서는 차광 부재(220)의 위치를 변경하여 제 1 및 제 2 층간 절연막(180a, 180b)만을 식각하여 제 2 컨택홀(186)을 형성할 수도 있다.

[0075] 본 발명의 일 실시예에 따르면, 화소 전극(192)은 제 2 층간 절연막(180b) 상에 배치되어, 제 2 컨택홀(186)을 통해 드레인 전극(175)과 접속된다. 따라서, 화소 전극(192)과 드레인 전극(175)이 전기적으로 연결된다.

[0076] 이때, 화소 전극(192) ITO(Indium tin oxide) 또는 IZO(Indium zinc oxide) 등의 투명 도전 물질로 만들어질 수 있다. 이때, ITO는 다결정 또는 단결정의 물질일 수 있으며, 또한 IZO 역시 다결정 또는 단결정의 물질일 수 있다.

[0077] 화소 전극(192)은 전체적인 모양은 사각형이며 가로 줄기부(192a) 및 이와 교차하는 세로 줄기부(192b)로 이루어진 십자형 줄기부를 포함한다. 또한 가로 줄기부(192a)와 세로 줄기부(192b)에 의해 네 개의 부영역으로 나뉘어지며 각 부영역은 복수의 미세 가지부(192c)를 포함한다. 또한, 본 실시예에서 화소 전극(192)의 외곽을 둘러싸는 외곽 줄기부를 더 포함할 수 있다.

[0078] 화소 전극(192)의 미세 가지부(192c)는 게이트 라인(GL) 또는 가로 줄기부(192a)와 대략 40도 내지 45도의 각을 이룬다. 또한, 이웃하는 두 부영역의 미세 가지부(192c)는 서로 직교할 수 있다. 또한, 미세 가지부(192c)의 폭은 점진적으로 넓어지거나 미세 가지부(192c) 간의 간격이 다를 수 있다.

[0079] 지금까지 설명한 박막 트랜지스터(Q) 및 화소 전극(192)에 관한 설명은 하나의 예시이고, 측면 시인성을 향상시키기 위해 박막 트랜지스터(Q) 구조 및 화소 전극(192) 디자인을 변형할 수 있다.

[0080] 화소 전극(192) 위에는 하부 배향막(11)이 형성되어 있고, 하부 배향막(11)은 수직 배향막일 수 있다. 하부 배향막(11)은 폴리 아믹산(Polyamic acid), 폴리 실록산(Polysiloxane) 또는 폴리 이미드(Polyimide) 등의 액정 배향막으로써 일반적으로 사용되는 물질들 중 적어도 하나를 포함하여 형성될 수 있다.

[0081] 하부 배향막(11)과 대향하는 부분에 상부 배향막(21)이 위치하고, 하부 배향막(11)과 상부 배향막(21) 사이에는 미세 공간(305)이 형성되어 있다. 미세 공간(305)에는 액정 분자(310)를 포함하는 액정 물질이 주입되어 있고, 미세 공간(305)은 액정 주입구(307)를 갖는다.

[0082] 미세 공간(305)은 화소 전극(192)의 열 방향, 즉 세로 방향을 따라 형성될 수 있다. 본 발명의 일 실시예에서 배향막(11, 21)을 형성하는 배향 물질과 액정 분자(310)를 포함하는 액정 물질은 모관력(capillary force)을 이용하여 미세 공간(305)에 주입될 수 있다.

- [0083] 미세 공간(305)은 게이트 라인(GL)과 중첩하는 부분에 위치하는 복수의 액정 주입구 형성 영역(307FP)에 의해 세로 방향으로 나누어지며, 또한 게이트 라인(GL)이 뻗어 있는 방향을 따라 복수개 형성되어 있다. 복수개 형성된 미세 공간(305) 각각은 하나 또는 둘 이상의 화소(PX) 영역에 대응할 수 있다.

- [0084] 상부 배향막(21) 상에는 공통 전극(270) 및 하부 절연층(350)이 위치한다. 공통 전극(270)은 공통 라인(미도시)을 통해 공통 전압을 인가 받고, 데이터 전압이 인가된 화소 전극(192)과 함께 전기장을 생성하여 두 전극 사이의 미세 공간(305)에 위치하는 액정 분자(310)의 기울어지는 방향을 결정한다.

- [0085] 공통 전극(270)은 화소 전극(192)과 축전기를 이루어 박막 트랜지스터(Q)가 턴 오프(turn-off)된 후에도 인가된 전압을 유지한다. 하부 절연층(350)은 질화 규소(SiNx) 및 산화 규소(SiO<sub>2</sub>)와 같은 무기 절연물을 포함할 수 있다.

- [0086] 본 발명의 일 실시예에서는 공통 전극(270)이 미세 공간(305) 위에 형성되는 것으로 설명하였으나, 다른 실시예로 공통 전극(270)이 미세 공간(305) 하부에 형성되어 수평 전계 모드에 따른 액정 구동도 가능하다.

- [0087] 하부 절연층(350) 상에 루프층(360)이 위치한다. 루프층(360)은 화소 전극(192)과 공통 전극(270)의 사이 공간인 미세 공간(305)이 형성될 수 있도록 지지하는 역할을 한다. 루프층(360)은 포토 레지스트 또는 그 밖의 유기 물질을 포함할 수 있다.

- [0088] 루프층(360) 상에 상부 절연층(370)이 위치한다. 상부 절연층(370)은 루프층(360)의 상부면과 접촉할 수 있다. 상부 절연층(370)은 질화 규소(SiNx) 또는 산화 규소(SiO<sub>2</sub>)를 포함할 수 있다.

- [0089] 상부 절연층(370) 위에 캐핑막(390)이 위치한다. 캐핑막(390)은 상부 절연층(370)의 상부면 및 측면과 접촉하며, 캐핑막(390)은 액정 주입구 형성 영역(307FP)에 의해 노출된 미세 공간(305)의 액정 주입구(307)를 덮는다. 캐핑막(390)은 열경화성 수지, 실리콘 옥시카바이드(SiOC) 또는 그라핀(Graphene)으로 형성될 수 있다.

- [0090] 도 5를 참조하면, 가로 방향으로 이웃하는 미세 공간(305) 사이에 격벽 형성부(PWP)가 형성되어 있다. 격벽 형성부(PWP)는 데이터 라인(DL)이 뻗어 있는 방향을 따라 형성될 수 있고, 루프층(360)에 의해 덮일 수 있다. 격벽 형성부(PWP)에는 하부 절연층(350), 공통 전극(270) 및 루프층(360)이 적층되어 있는데 이러한 구조물이 격벽(Partition Wall)을 형성함으로써 미세 공간(305)을 구획 또는 정의할 수 있다.

- [0091] 이하, 도 6a 내지 도 6e를 참조로 본 발명의 일 실시예에 따른 액정 표시 장치를 상세히 설명하면 다음과 같다. 도 6a 내지 도 6e는 본 발명의 일 실시예에 따른 액정 표시 장치의 제조 방법을 순서대로 도시한 도면이다.

- [0092] 먼저 도 6a에 도시된 바와 같이, 기판(110) 위에 금속층을 배치하고, 금속층을 패터닝하여, 기판(110) 위에 접지 라인(910)과 게이트 전극(124)을 형성한다. 금속층은 알루미늄(A1)이나 알루미늄 합금과 같은 알루미늄 계열의 금속, 또는 은(Ag)이나 은 합금과 같은 은 계열의 금속, 또는 구리(Cu)나 구리 합금과 같은 구리 계열의 금속, 또는 몰리브덴(Mo)이나 몰리브덴 합금과 같은 몰리브덴 계열의 금속으로 이루어질 수 있다. 또는, 금속층은 크롬(Cr), 탄탈륨(Ta) 및 티타늄(Ti) 중 어느 하나로 이루어질 수 있다.

- [0093] 상기 금속 패턴은 게이트 라인(GL), 박막 트랜지스터(Q)의 게이트 전극(GE) 및 접지 라인(910)을 포함한다. 접지 라인(910)은 상기 보조 라인(911)을 통해 공통 전압을 전달하는 공통 라인(미도시)과 전기적으로 연결된다.

- [0094] 금속 패턴이 이루어진 기판(110) 위에 금속 패턴을 덮도록 게이트 절연막(140)을 배치한다. 게이트 절연막(140)은 질화 규소(SiNx) 및 산화 규소(SiO<sub>2</sub>)와 같은 무기 절연물을 포함할 수 있다.

- [0095] 도 6b에 도시된 바와 같이, 게이트 전극(124)을 포함하는 박막 트랜지스터(Q)를 형성하기 위하여 게이트 절연막(140) 위에 반도체층(151, 154)을 배치하고, 소스 전극(173) 및 드레인 전극(175)을 배치한다. 이때, 소스 전극(173)과 연결된 데이터 라인(DL)은 게이트 라인(GL)과 교차하도록 배치할 수 있다.

- [0096] 게이트 절연막(140), 데이터 도전체(DL, 173, 175) 및 노출된 반도체층(154) 위에 제1 층간 절연막(180a)이 위치한다.

- [0097] 화소(PX) 영역에 대응하는 위치의 제 1 층간 절연막(180a) 상에 컬러 필터(230)를 배치하고, 컬러 필터(230) 사이에 차광 부재(220)를 배치한다. 이때, 도시되지 않았으나, 비표시 영역(PA)의 제 1 층간 절연막(180a) 상에 차광 부재(220)가 추가로 배치될 수 있다.

- [0098] 제 1 층간 절연막(180a), 차광 부재(220) 및 컬러 필터(230)의 상에 이를 덮는 제 2 층간 절연막(180b)을 형성한다. 이때, 접지 라인(910)을 노출하는 제 1 컨택홀(185)과 드레인 전극(175)을 노출하는 제 2 컨택홀(186)이

형성된다.

- [0099] 이후, 제 2 충간 절연막(180b) 위에 제 1 정전기 분산 패턴(920) 및 화소 전극(192)을 형성한다. 이때, 제 1 정전기 분산 패턴(920)은 제 1 컨택홀(185) 및 제 2 충간 절연막(180b) 상에 위치하고, 화소 전극(192)은 제 2 컨택홀(186) 및 제 2 충간 절연막(180b) 상에 위치한다. 예를 들어, ITO 또는 IZO를 포함하는 물질을 제 2 충간 절연막(180b) 위에 증착하여, 제 1 정전기 분산 패턴(920) 및 화소 전극(192)을 동시에 패터닝할 수 있다.

- [0100] 본 발명의 일 실시예에 따른 액정 표시 장치(100)는 제 1 정전기 분산 패턴(920)이 제 1 컨택홀(185)을 통해 접지 라인(910)에 접속됨으로써, 정전기 발생시 유입된 전하들을 대면적으로 분산시킬 수 있다.

- [0101] 도 6c를 참조하면, 제 2 충간 절연막(180b), 제 1 정전기 분산 패턴(920) 및 화소 전극(192) 위에 희생층(300)을 형성한다.

- [0102] 표시 영역(DA)에 대응하는 희생층(300) 위에 공통 전극(270)을 배치하고, 상기 희생층(300) 및 공통 전극(270) 상에 하부 절연층(350) 및 루프층(360)을 차례로 배치한다. 루프층(360)은 노광 및 현상 공정에 의해 세로 방향으로 이웃하는 화소(PX) 영역 사이에 위치하는 차광 부재(220)와 대응하는 영역에서 제거될 수 있다. 루프층(360)은 차광 부재(220)와 대응하는 영역에서 하부 절연층(350)을 외부로 노출시킨다.

- [0103] 도 6d를 참조하면, 노출된 하부 절연층(350)과 루프층(360) 위를 덮도록 상부 절연층(370)을 형성한다.

- [0104] 이후, 식각 마스크를 사용하여 차광 부재(220)와 대응하는 영역의 상부 절연층(370), 하부 절연층(350) 및 공통 전극(270)을 건식 식각한다. 이에 따라, 상부 절연층(370), 하부 절연층(350) 및 공통 전극(270)이 부분적으로 제거되어, 액정 주입구 형성 영역(307FP)을 형성한다.

- [0105] 액정 주입구 형성 영역(307FP)을 통해 표시 영역(DA)의 희생층(300)을 산소 애싱(Ashing) 처리 또는 습식 식각법 등으로 제거한다. 이때, 표시 영역(DA)은 희생층(300)이 제거되어 액정 주입구(307)를 갖는 미세 공간(305)을 가지며, 비표시 영역(PA)은 희생층(300)이 잔존하여 잔류 희생층(300a)을 갖는다.

- [0106] 도 6e를 참조하면, 액정 주입구(307)를 통해 배향 물질을 주입하여 화소 전극(192) 및 공통 전극(270) 위에 배향막(11, 21)을 형성한다. 구체적으로, 액정 주입구(307)를 통해 고형분과 용매를 포함하는 배향 물질을 주입한 후에 베이크 공정을 통해 배향막(11, 21)을 형성한다.

- [0107] 그 다음, 액정 주입구(307)를 통해 미세 공간(305)에 잉크젯 방법 등을 사용하여 액정 문자(310)를 포함하는 액정 물질을 주입하고, 상부 절연층(370)의 상부면 및 측면과 접촉하며, 액정 주입구(307)를 덮는 캐핑막(390)을 형성한다.

- [0108] 캐핑막(390) 위에 무기막 또는 유기막으로 형성된 오버코트막(미도시)이 위치할 수 있다. 오버코트막(미도시)은 외부 충격으로부터 미세 공간(305)에 주입된 액정 문자(310)를 보호하고 막을 평탄화시키는 역할을 한다.

- [0109] 기판(110)의 하부 및 캐핑막(390)의 상부에는 편광판(미도시)이 위치할 수 있다. 편광판(미도시)은 편광을 생성하는 편광 소자와 내구성을 확보하기 위한 TAC(Tri-acetyl-cellulose)층을 포함할 수 있으며, 실시예에 따라서는 상부 편광판과 하부 편광판은 투과축의 방향이 수직 또는 평행할 수 있다.

- [0110] 도 7은 본 발명의 다른 실시예에 따른 액정 표시 장치의 단면도이다. 본 발명의 다른 실시예에 관한 설명 가운데 본 발명의 일실시예에 관한 설명과 중복되는 내용은 생략한다.

- [0111] 도 7을 참조하면, 본 발명의 다른 실시예에 따른 액정 표시 장치(100)는 잔류 희생층(300a) 상에 배치된 제 1 정전기 분산 패턴(921)을 포함한다.

- [0112] 즉, 제 1 정전기 분산 패턴(921)은 잔류 희생층(300a) 상에 배치되어, 제 1 컨택홀(187)을 통해 접지 라인(910)과 접속된다. 이에 따라, 제 1 정전기 분산 패턴(921)과 접지 라인(910)이 전기적으로 연결된다.

- [0113] 본 발명의 일 실시예에 따른 제 1 정전기 분산 패턴(920)이 화소 전극(192)과 동시에 패터닝되는 반면, 다른 실시예에 따른 제 1 정전기 분산 패턴(921)은 공통 전극(270)과 동시에 패터닝된다.

- [0114] 본 발명의 다른 실시예에 따른 액정 표시 장치(100)는 제 1 정전기 분산 패턴(921)을 통해 정전기 유입에 따른 기판 전극 및 구동 소자의 손상을 방지할 수 있다.

- [0115] 도 8은 본 발명의 또 다른 실시예에 따른 액정 표시 장치의 단면도이다. 본 발명의 또 다른 실시예에 관한 설명 가운데 본 발명의 일실시예에 관한 설명과 중복되는 내용은 생략한다.

- [0116] 도 8을 참조하면, 본 발명의 또 다른 실시예에 따른 액정 표시 장치(100)는 캐핑막(390) 상에 배치된 제 2 정전기 분산 패턴(930)을 더 포함한다.

- [0117] 제 2 정전기 분산 패턴(930)은 기판(110)의 전면(全面)에 배치될 수 있다.

- [0118] 이때, 제 2 정전기 분산 패턴(930)은 ITO(Indium tin oxide) 또는 IZO(Indium zinc oxide) 등의 투명 도전 물질로 만들어질 수 있다. 이때, ITO는 다결정 또는 단결정의 물질일 수 있으며, 또한 IZO 역시 다결정 또는 단결정의 물질일 수 있다.

- [0119] 본 발명의 또 다른 실시예에 따른 액정 표시 장치(100)는 기판(110) 전면에 배치된 제 2 정전기 분산 패턴(930)을 포함함으로써, 정전기로 인해 유입된 전하들이 제 2 정전기 분산 패턴(930)을 통해 대면적으로 분산될 수 있다. 이에 따라, 정전기 유입에 따른 기판 전극 및 구동 소자의 손상을 방지할 수 있다.

- [0120] 이상, 첨부된 도면을 참조하여 본 발명의 실시예들을 설명하였지만, 본 발명이 속하는 기술분야에서 통상의 지식을 가진 자는 본 발명의 그 기술적 사상이나 필수적인 특징을 변경하지 않고서 본 발명이 다른 구체적인 형태로 실시될 수 있다는 것을 이해할 수 있을 것이다. 그러므로 이상에서 기술된 실시예들은 모든 면에서 예시적인 것이며 한정적이 아닌 것으로 이해되어야 한다.

### **부호의 설명**

- [0121]

- 100: 액정 표시 장치 110: 기판

- 300: 희생층 305: 미세 공간(Microcavity)

- 307: 액정 주입구 310: 액정 분자

- 350: 하부 절연층 360: 루프층

- 370: 상부 절연층 390: 캐핑막

- 910: 접지 라인 911: 보조 라인

- 920: 제 1 정전기 분산 패턴 930: 제 2 정전기 분산 패턴

- GL: 게이트 라인 DL: 데이터 라인

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

**도면5****도면6a****도면6b****도면6c**

## 도면6d

## 도면6e

## 도면7

도면8

|                |                                                               |         |            |

|----------------|---------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                                         |         |            |

| 公开(公告)号        | <a href="#">KR1020170117263A</a>                              | 公开(公告)日 | 2017-10-23 |

| 申请号            | KR1020160044793                                               | 申请日     | 2016-04-12 |

| [标]申请(专利权)人(译) | 三星显示有限公司                                                      |         |            |

| 申请(专利权)人(译)    | 三星显示器有限公司                                                     |         |            |

| [标]发明人         | JUNG HYUNG GI<br>정형기                                          |         |            |

| 发明人            | 정형기                                                           |         |            |

| IPC分类号         | G02F1/136 G02F1/1333 H01B1/02                                 |         |            |

| CPC分类号         | G02F1/136 H01B1/02 G02F2202/22 G02F2001/13606 G02F2001/133334 |         |            |

| 代理人(译)         | Yunyeogwang<br>Jowooje<br>李宰 - 亨<br>锡盐                        |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                     |         |            |

### 摘要(译)

本发明涉及根据静电流入和驱动部件防止基板电极损坏的液晶显示器，包括：基板；薄膜晶体管，设置在基板的显示区域中；并连接到栅极线和数据线；液晶层由连接到薄膜晶体管的像素电极，环层，布置在与显示区域相邻的非显示区域的第一静电分散图案，地线和液晶分子组成位于微空隙中的微空隙(Microcavity)在像素电极和环层之间形成有液晶注入孔；环层位于像素电极的同时，接地线与第一静电分散图案电连接。