(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2017-0067402

(43) 공개일자 2017년06월16일

(51) 국제특허분류(Int. Cl.)

*G09G 3/36* (2006.01) *G02F 1/1343* (2006.01)

*G02F 1/1362* (2006.01)

(52) CPC특허분류

*G09G 3/3648* (2013.01)

*G02F 1/1343* (2013.01)

(21) 출원번호 10-2015-0174042

(22) 출원일자 2015년12월08일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

김태한

서울특별시 마포구 월드컵북로 235 (성산동, 성산

시영아파트) 19동 1305호

(74) 대리인

특허법인로얄

전체 청구항 수 : 총 7 항

(54) 발명의 명칭 액정표시장치

### (57) 요 약

본 발명에 의한 액정표시장치는 제1 데이터라인, 공통전극 제1 및 제2 화소전극 및 차폐 패턴을 포함한다. 제1 데이터라인은 데이터 구동부로부터 데이터전압을 공급받는다. 공통전극은 제1 데이터라인의 상부에 배치되고, 공통전압을 제공받는다. 제1 화소전극은 공통전극과 이웃한 영역에 배치되고, 제1 데이터라인으로부터 제공받는다. 제2 화소전극은 공통전극으로부터 제1 화소전극의 반대측에 배치되고, 제1 데이터라인으로부터 제1 데이터 전압과 시분할로 공급되는 제2 데이터전압으로 충전된다. 절연막을 사이에 두고 제1 데이터라인의 하부에 위치하고, 제1 화소전극이 배치된 측면에서 제1 데이터라인과 평행하게 배치됨으로써, 제1 데이터라인으로부터의 전계가 공통전극 및 제1 화소전극 간의 전계에 영향을 미치지 않도록 차단한다.

### 대 표 도 - 도7

(52) CPC특허분류

*G02F 1/1362* (2013.01)

*G09G 2320/0252* (2013.01)

---

## 명세서

### 청구범위

#### 청구항 1

데이터 구동부로부터 데이터전압을 공급받는 제1 데이터라인;

상기 제1 데이터라인의 상부에 배치되고, 공통전압을 제공받는 공통전극;

상기 공통전극과 이웃한 영역에 배치되고, 상기 제1 데이터라인으로부터 제공받는 제1 데이터전압으로 충전되는 제1 화소전극;

상기 공통전극으로부터 상기 제1 화소전극의 반대측에 배치되고, 상기 제1 데이터라인으로부터 상기 제1 데이터전압과 시분할로 공급되는 제2 데이터전압으로 충전되는 제2 화소전극; 및

절연막을 사이에 두고 상기 제1 데이터라인의 하부에 위치하고, 상기 제1 화소전극이 배치된 측면에서 상기 제1 데이터라인과 평행하게 배치됨으로써, 상기 제1 데이터라인으로부터의 전계가 상기 공통전극 및 상기 제1 화소전극 간의 전계에 영향을 미치지 않도록 차단하는 차폐 전극을 포함하는 액정표시장치.

#### 청구항 2

제 1 항에 있어서,

상기 차폐 전극은 공통전압을 공급받는 액정표시장치.

#### 청구항 3

제 1 항에 있어서,

상기 제1 화소전극은 상기 제1 데이터전압과 상기 공통전극 간의 전계를 이용하여 계조표현을 하는 제1 화소를 이루고,

상기 제2 화소전극은 상기 제2 데이터전압과 상기 공통전극 간의 전계를 이용하여 계조표현을 하는 제2 화소를 이루며,

상기 데이터라인은 4 수평기간 단위로 상기 제1 데이터전압 또는 제2 데이터전압의 극성을 변경하는 액정표시장치.

#### 청구항 4

제 3 항에 있어서,

상기 차폐 전극이 배치되지 않는 상기 제2 화소는 계조 가중치가 상기 제1 화소 보다 낮은 청색 화소인 액정표시장치.

#### 청구항 5

제 1 항에 있어서,

상기 제1 데이터라인과 상기 제1 화소전극 사이에는 게이트필스에 응답하여 턴-온되는 제1 박막트랜지스터를 더 포함하고,

상기 차폐 전극은 상기 제1 트랜지스터의 게이트전극과 동일한 금속층에 배치되는 액정표시장치.

#### 청구항 6

제 1 항에 있어서,

상기 제1 데이터라인의 하부에는 반도체층이 형성되고,

상기 공통전극은 상기 데이터라인 및 반도체층의 수직 상부 영역을 덮지 않도록 배치되어, 상기 제2 화소의 발

광 영역은 상기 공통전극으로부터 노출되는 액정표시장치.

## 청구항 7

제 3 항에 있어서,

상기 제1 데이터라인의 인접한 곳에서 제2 데이터라인이 더 배치되고,

상기 제2 데이터라인의 양측에는 각각 제3 화소 및 제4 화소가 배치되며,

상기 제3 화소가 상기 제4 화소 보다 휙도 가중치가 높을 때에, 절연막을 사이에 두고 상기 제2 데이터라인의 하부에서, 상기 제3 화소 영역의 경계에는 상기 제2 데이터라인으로부터의 전계를 차단하는 제2 차폐 패턴이 더 배치되는 액정표시장치.

## 발명의 설명

### 기술 분야

[0001]

본 발명은 액정표시장치에 관한 것이다.

### 배경 기술

[0002]

액정표시장치(Liquid Crystal Display Device: LCD), 유기 발광 다이오드 표시장치(Organic Light Emitting Diode Display : OLED Display), 플라즈마 디스플레이 패널(Plasma Display Panel : PDP), 전기영동 표시장치(Electrophoretic Display Device: EPD) 등 각종 평판 표시장치가 개발되고 있다. 액정표시장치는 액정 분자에 인가되는 전계를 데이터 전압에 따라 제어하여 화상을 표시한다. 액티브 매트릭스(Active Matrix) 구동방식의 액정표시장치에는 픽셀마다 데이터 라인과 게이트 라인의 교차부에 박막트랜지스터(Thin Film Transistor : 이하 "TFT"라 함)가 형성되어 있다.

[0003]

액정표시장치의 화소들은 서로 교차하는 데이터라인 및 게이트라인을 포함하고, 그 교차부에 접속된 박막트랜지스터를 포함한다. 박막트랜지스터는 게이트라인으로부터의 게이트펄스에 응답하여 데이터라인을 통해 공급되는 데이터전압을 액정셀의 화소전극에 공급한다. 액정셀은 화소전극의 전압과 공통전극에 인가되는 공통전압(Vcom)의 전압차에 따라 발생되는 전계에 의해 회동하여 편광판을 통과하는 광양을 조절한다. 스토리지 커페시터는 액정셀의 화소전극에 접속되어 액정셀의 전압을 유지한다.

[0004]

정상적인 상태에서는 화소는 화소전극과 공통전극의 전압 차이에 대응하는 계조를 표현하지만 주변의 전계에 영향에 의해서 원하는 계조를 표현하지 못하는 경우가 발생하기도 한다. 또한 데이터전압을 공급하는 데이터라인의 부하(load)로 인한 문제점이 발생하기도 한다.

### 발명의 내용

#### 해결하려는 과제

[0005]

본 발명은 액정셀에 비정상적인 전계가 가해지는 것을 방지할 수 있는 액정표시장치를 제공하기 위한 것이다.

[0006]

또한, 본 발명은 데이터전압의 지연 현상을 개선할 수 있는 액정표시장치를 제공하기 위한 것이다.

#### 과제의 해결 수단

[0007]

본 발명에 의한 액정표시장치는 제1 데이터라인, 공통전극 제1 및 제2 화소전극 및 차폐 패턴을 포함한다. 제1 데이터라인은 데이터 구동부로부터 데이터전압을 공급받는다. 공통전극은 제1 데이터라인의 상부에 배치되고, 공통전압을 제공받는다. 제1 화소전극은 공통전극과 이웃한 영역에 배치되고, 제1 데이터라인으로부터 제공받는다. 제2 화소전극은 공통전극으로부터 제1 화소전극의 반대측에 배치되고, 제1 데이터라인으로부터 제1 데이터전압과 시분할로 공급되는 제2 데이터전압으로 충전된다. 절연막을 사이에 두고 제1 데이터라인의 하부에 위치하고, 제1 화소전극이 배치된 측면에서 제1 데이터라인과 평행하게 배치됨으로써, 제1 데이터라인으로부터의 전계가 공통전극 및 제1 화소전극 간의 전계에 영향을 미치지 않도록 차단한다.

#### 발명의 효과

[0008]

본 발명의 표시장치는 차폐 전극을 배치하여 데이터라인으로부터의 전계가 공통전극과 화소전극 간의 전계에 영

향을 끼치는 것을 방지할 수 있다. 그 결과, 본 발명은 데이터라인으로부터 전계에 의해서 계조가 변하는 것을 방지할 수 있다. 특히, 본 발명은 시분할로 데이터전압을 공급하는 DRD 구조에서 데이터라인이 배치되는 수직 경계면에서는 차폐 전극을 배치하지 않음으로써, 기생 커패시터를 제거할 수 있어서 데이터전압의 지연 현상을 방지할 수 있다. 또한, 차폐 전극(SP)을 배치하지 않더라도 데이터라인이 1/2인 구조를 이용함으로써 데이터라인으로부터의 전계의 영향을 덜 받도록 하여, 데이터라인의 전계에 의한 계조 변화를 둔화시킬 수 있다.

### 도면의 간단한 설명

[0009]

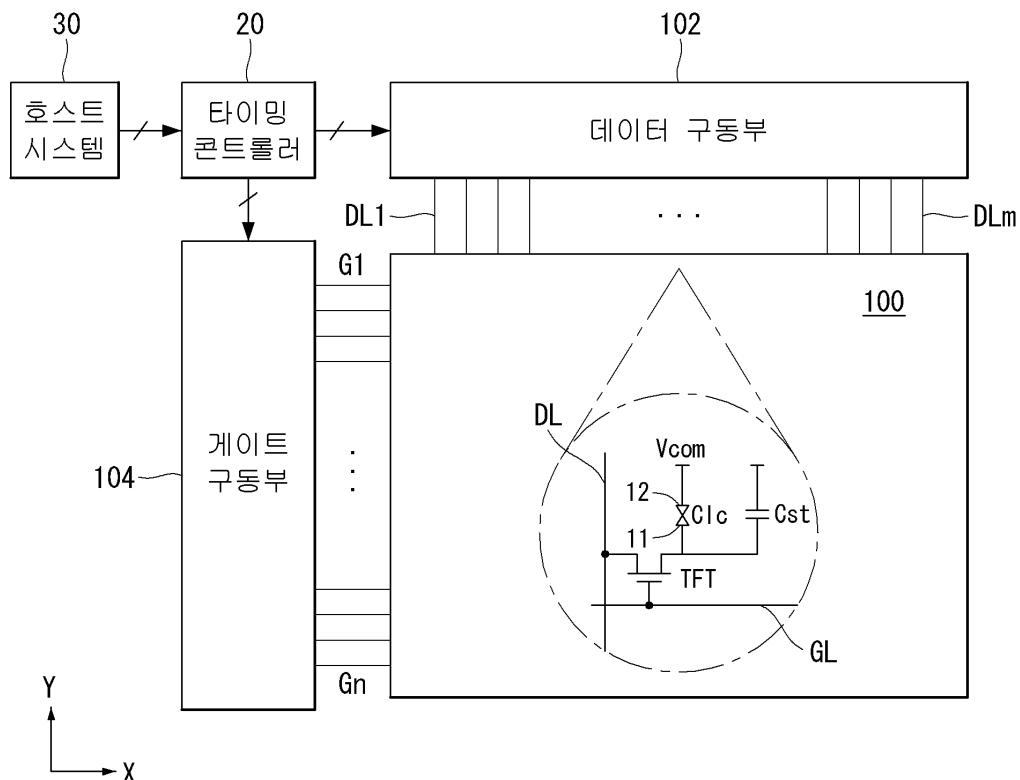

도 1은 본 발명의 실시예에 따른 표시장치를 보여 주는 블록도이다.

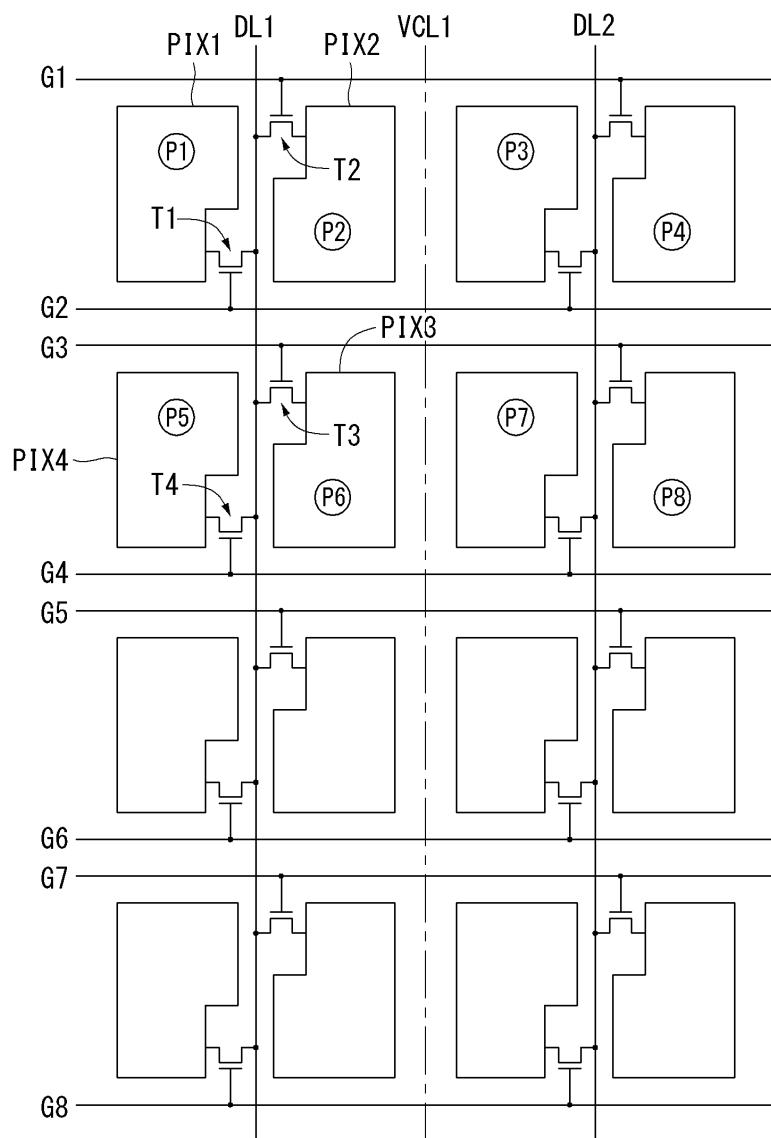

도 2는 도 1에 도시된 표시패널의 TFT 어레이 기판 일부를 보여 주는 등가 회로도이다.

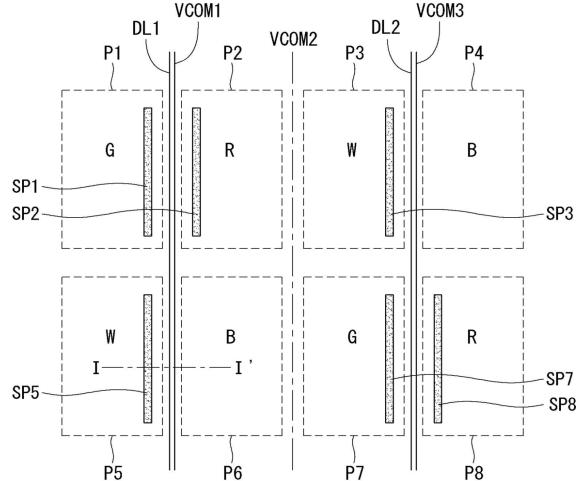

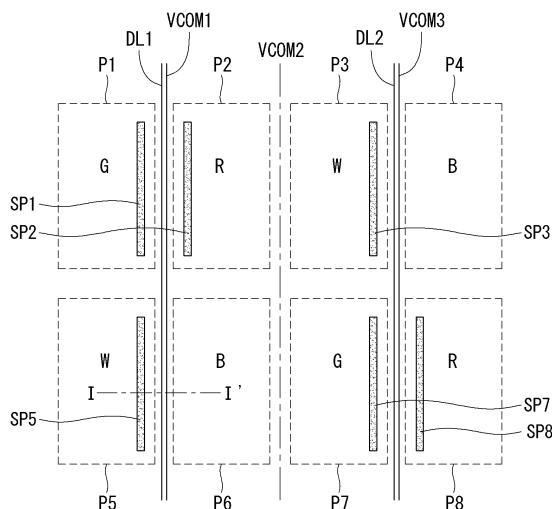

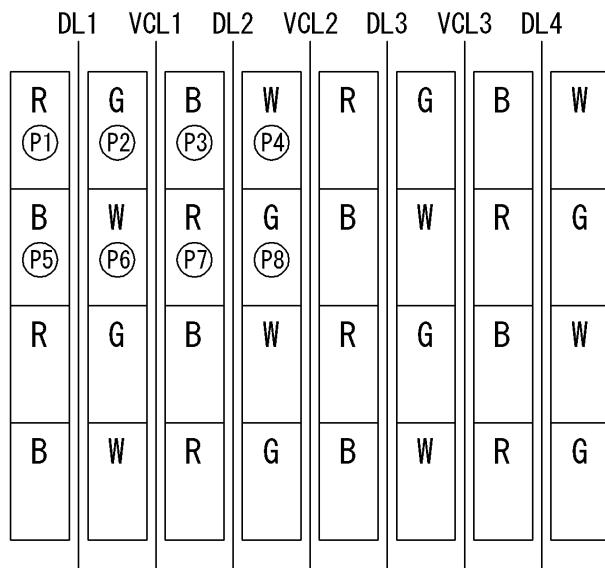

도 3은 RGBW 타입 표시장치에서 컬러 배열을 보여 주는 도면이다.

도 4는 RGB 타입 표시장치에서 컬러 배열을 보여 주는 도면이다.

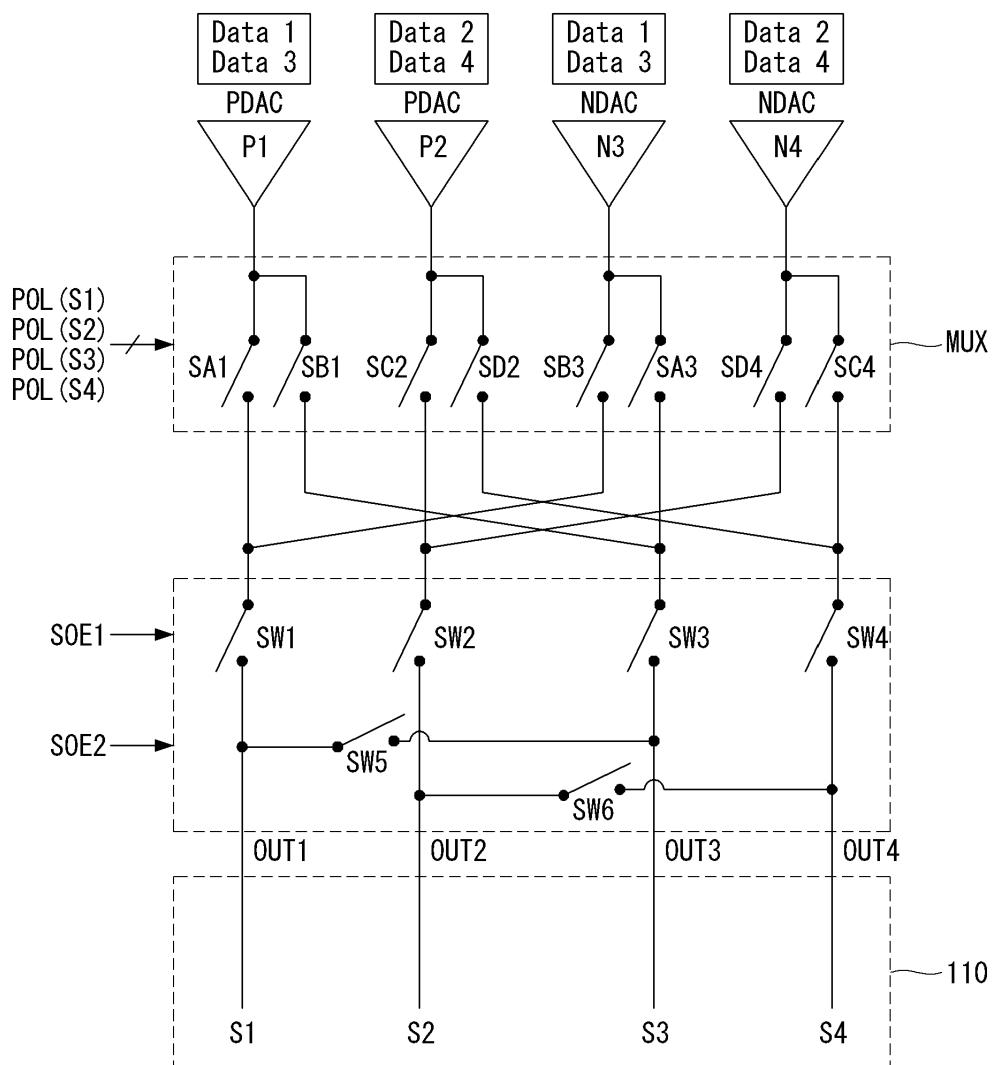

도 5는 제1 실시 예에 의한 소스드라이버 IC를 나타내는 도면이다.

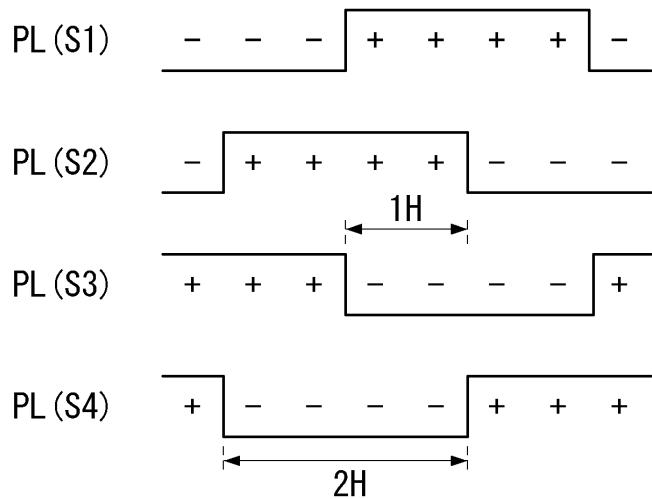

도 6은 RGBW 타입 표시장치의 극성 제어 신호를 보여 주는 파형도이다.

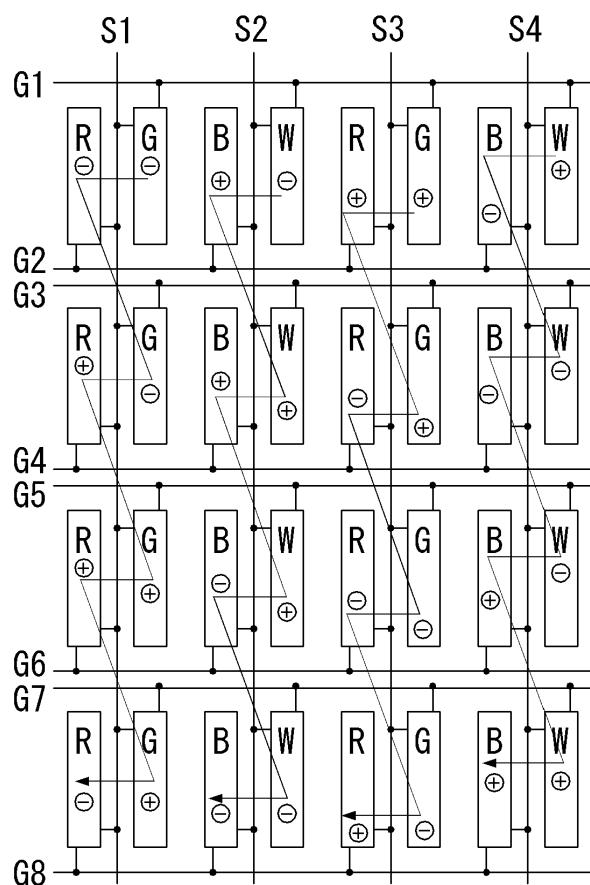

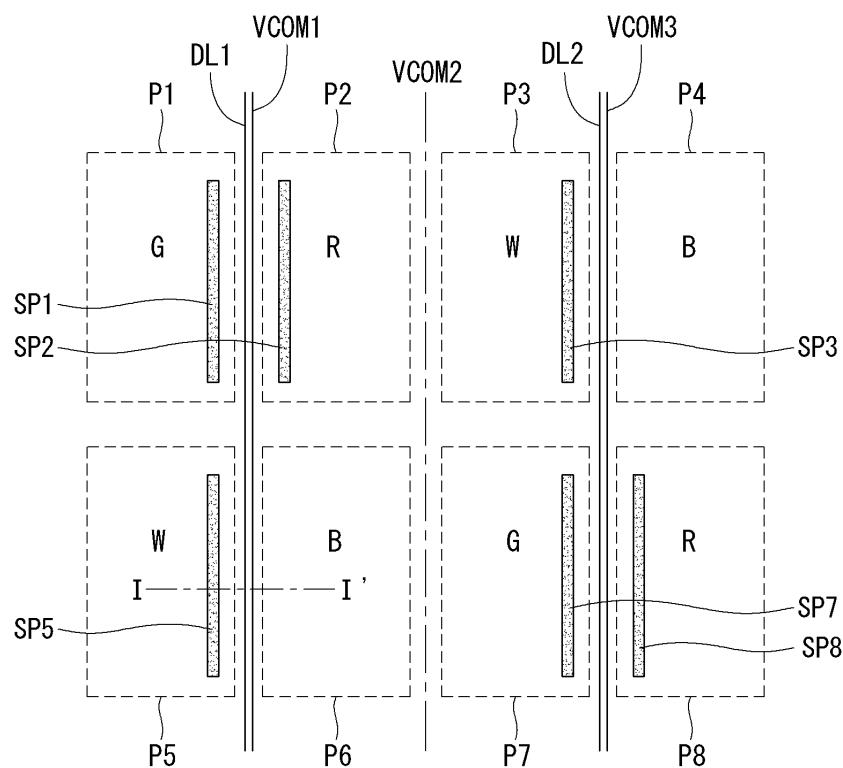

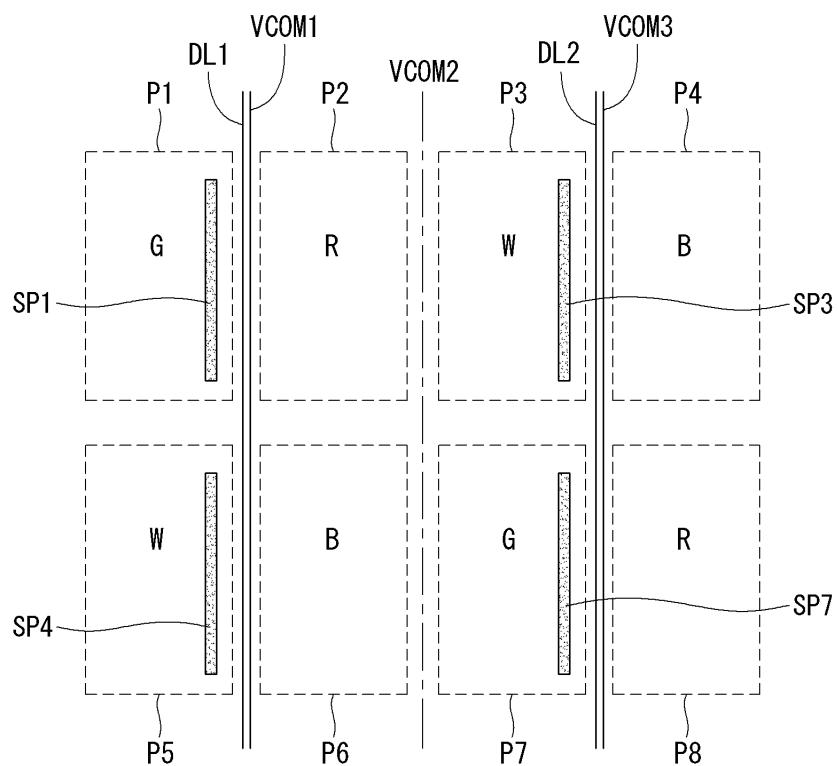

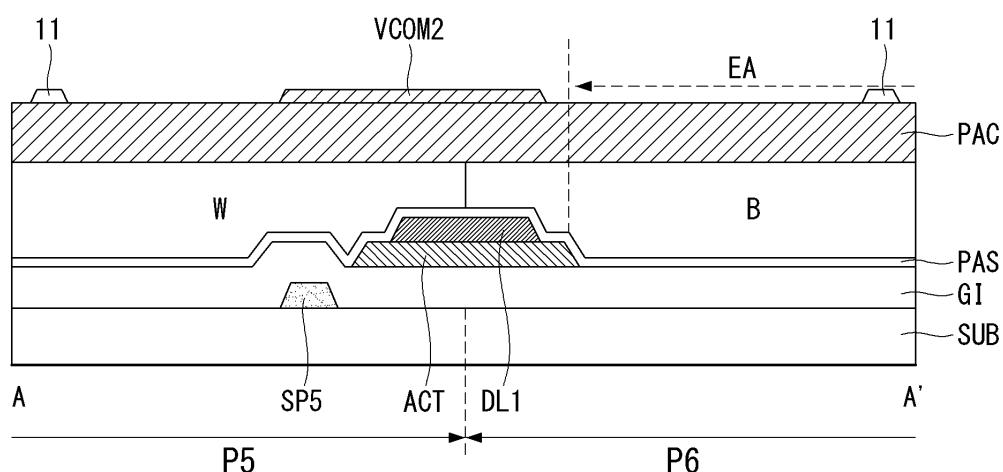

도 7은 본 발명에 의한 액정표시장치의 일부 화소들의 평면 어레이 구조를 나타내는 도면이다.

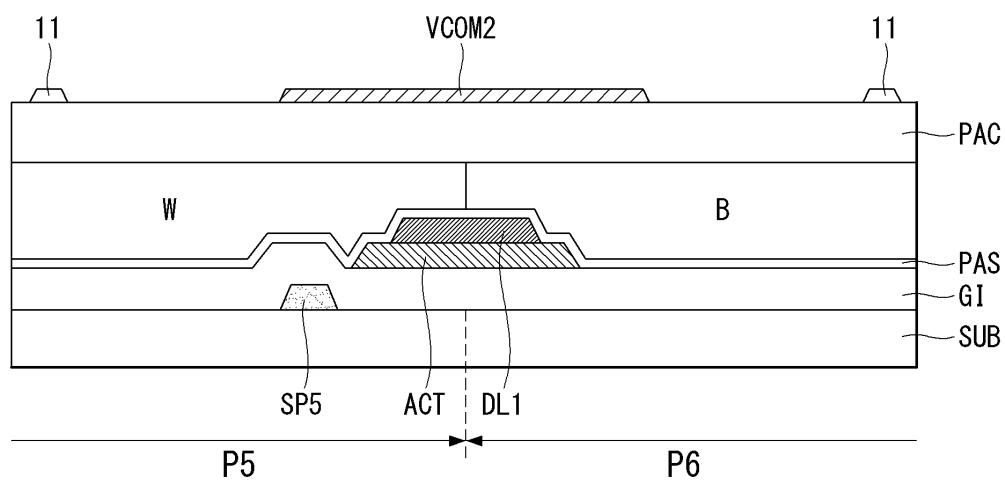

도 8은 도 7에 도시된 I-I'를 따라 절취한 단면을 나타내는 도면이다.

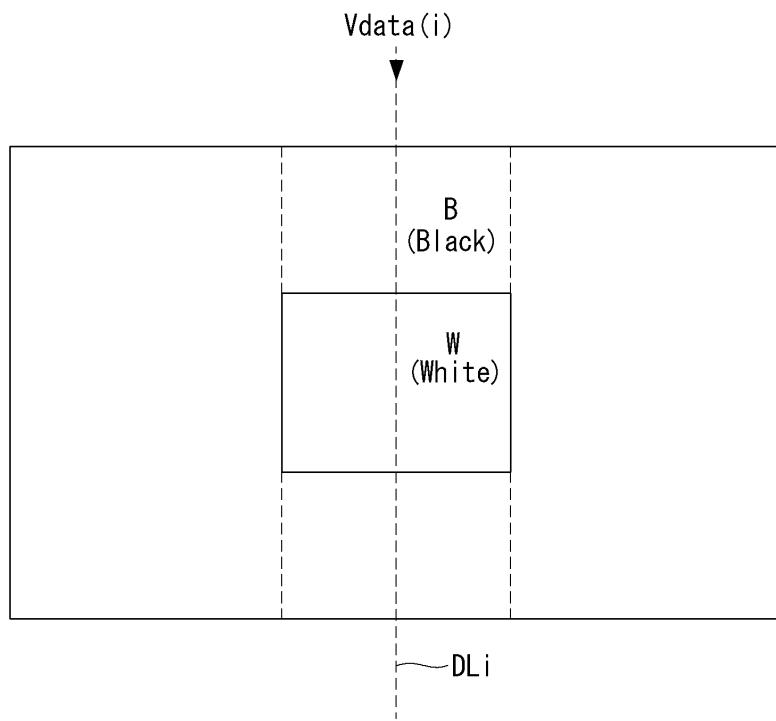

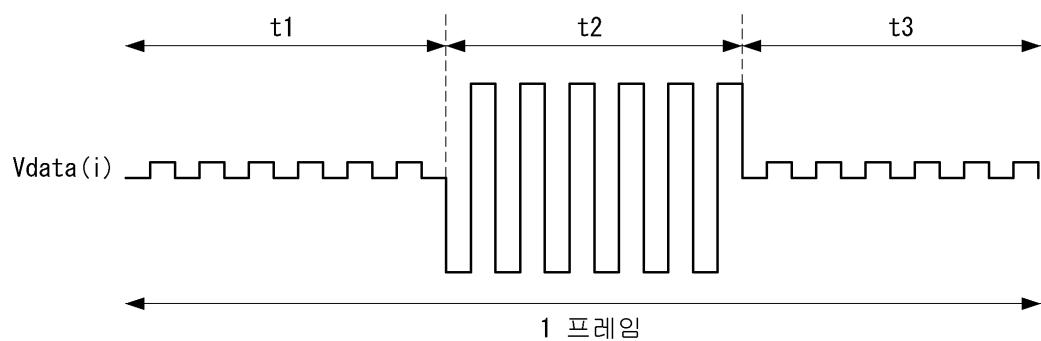

도 9 및 도 10은 크로스토크 현상을 설명하기 위한 도면.

도 11은 제2 실시 예에 의한 액정표시장치의 일부 화소들의 평면 어레이 구조를 나타내는 도면이다.

도 12는 다른 실시 예에 의한 화소 경계 영역의 단면을 나타내는 도면이다.

### 발명을 실시하기 위한 구체적인 내용

[0010]

이하, 첨부한 도면을 참조하여, 본 발명의 바람직한 실시 예를 설명한다. 명세서 전체에 걸쳐서 동일한 참조 번호들은 실질적으로 동일한 구성 요소들을 의미한다. 이하의 설명에서, 본 발명과 관련된 공지 기술 혹은 구성에 대한 구체적인 설명이 본 발명의 요지를 불필요하게 흐릴 수 있다고 판단되는 경우, 그 상세한 설명을 생략한다. 또한, 이하의 설명에서 사용되는 구성요소 명칭은 명세서 작성의 용이함을 고려하여 선택된 것일 수 있는 것으로서, 실제 제품의 부품 명칭과는 상이할 수 있다.

[0011]

도 1을 참조하면, 본 발명의 표시장치는 표시패널(100)과, 표시패널(100)에 입력 영상의 데이터를 기입하기 위한 표시패널 구동회로를 구비한다. 표시패널(100)의 아래에는 표시패널(100)에 빛을 균일하게 조사하기 위한 백라이트 유닛이 배치될 수 있다.

[0012]

이 표시장치는 소스 드라이브 IC들의 개수를 줄이기 위하여, 수평(x축 또는 로 라인 방향)으로 이웃한 두 개의 서브 픽셀들이 하나의 데이터 라인을 공유하는 DRD(Double rate driving) 표시장치로 구현한다. DRD 표시장치는 데이터 라인들의 개수가 감소되므로 소스 드라이브 IC들의 개수를 1/2로 줄일 수 있다. DRD 표시장치에서, 소스 드라이브 IC의 동작 주파수는 2 배 높아진다.

[0013]

표시패널(100)은 액정층을 사이에 두고 서로 대향하는 TFT 어레이 기판과 컬러 필터 어레이 기판을 포함한다. 표시패널(100)은 데이터라인들(S1~Sm)과 게이트라인들(G1~Gn)의 교차 구조에 의해 매트릭스 형태로 배열되는 픽셀들을 포함한다. 픽셀들 각각은 RGB 서브 픽셀들로 나뉘어지거나 RGBW 서브 픽셀들로 나뉘어진다.

[0014]

표시패널(100)의 TFT 어레이 기판에는 데이터라인들(S1~Sm), 게이트라인들(G1~Gn), 데이터 라인과 게이트 라인의 교차부에 배치된 TFT, TFT에 접속된 픽셀 전극(11), 및 픽셀 전극(11)에 접속된 스토리지 커패시터(Storage Capacitor, Cst) 등을 포함한다. 픽셀들 각각은 TFT를 통해 데이터전압을 충전하는 픽셀 전극(11)과 공통전압(Vcom)이 인가되는 공통 전극(12)의 전압차에 의해 구동되는 액정 분자들을 이용하여 빛의 투과양을 조정함으로써 비디오 데이터의 화상을 표시한다.

[0015]

표시패널(100)의 컬러 필터 기판에는 블랙 매트릭스(Black matrix)와 컬러 필터(Color filter)를 포함한 컬러 필터 어레이가 형성된다. 공통 전극(12)은 TN(Twisted Nematic) 모드와 VA(Vertical Alignment) 모드와 같은 수직 전계 구동방식의 경우에 상부 기판 상에 형성되며, IPS(In-Plane Switching) 모드와 FFS(Fringe Field Switching) 모드와 같은 수평 전계 구동방식의 경우에 픽셀 전극(11)과 함께 TFT 어레이 기판 상에 형성될 수

있다. 표시패널(100)의 TFT 어레이 기판과 컬러 필터 어레이 기판 각각에는 편광판이 부착되고 액정의 프리틸 트각(pre-tilt angle)을 설정하기 위한 배향막이 형성된다.

[0016] 본 발명의 표시장치는 투과형 액정표시장치, 반투과형 액정표시장치, 반사형 액정표시장치 등 어떠한 형태로도 구현될 수 있다. 투과형 액정표장치와 반투과형 액정표시장치에서는 백라이트 유닛이 필요하다. 백라이트 유닛은 직하형(direct type) 백라이트 유닛 또는, 에지형(edge type) 백라이트 유닛으로 구현될 수 있다.

[0017] 표시패널 구동회로는 픽셀들에 입력 영상의 데이터를 기입한다. 표시패널 구동회로는 데이터 구동부(102), 게이트 구동부(104), 타이밍 콘트롤러(20), 및 감마 보정부(22)를 포함한다. RGB 타입 표시장치에서, 픽셀들에 기입되는 데이터는 R 데이터, G 데이터 및 B 데이터를 포함한다. RGBW 타입 표시장치에서, 픽셀들에 기입되는 데이터는 R 데이터, G 데이터, B 데이터 및 W 데이터를 포함한다.

[0018] 데이터 구동부(102)는 다수의 소스 드라이브 IC를 포함한다. 소스 드라이브 IC들의 데이터 소스채널들은 데이터라인들(S1~Sm)에 연결된다. 소스 드라이브 IC들은 타이밍 콘트롤러(20)로부터 입력 영상의 디지털 비디오 데이터를 입력 받는다. RGB 타입 표시장치에서, 소스 드라이브 IC들로 전송되는 디지털 비디오 데이터는 R 데이터, G 데이터, 및 B 데이터를 포함한다. RGBW 타입 표시장치에서, 소스 드라이브 IC들로 전송되는 디지털 비디오 데이터는 R 데이터, G 데이터, B 데이터, 및 W 데이터를 포함한다. 소스 드라이브 IC들은 타이밍 콘트롤러(20)의 제어 하에 입력 영상의 디지털 비디오 데이터를 정극성/부극성 감마보상전압으로 변환하여 정극성/부극성 데이터전압을 출력한다. 데이터 구동부(102)의 출력 전압은 데이터 라인들(S1~Sm)에 공급된다.

[0019] 수평으로 이웃한 2 개의 서브 픽셀들은 도 2와 같이 하나의 데이터 라인을 공유하여 그 데이터 라인을 통해 시분할된 데이터 전압들을 공급받는다. 데이터 라인의 공유 구조로 인하여, 동일 해상도에서 일반적인 픽셀 어레이 구조에 비하여 데이터 라인들의 개수와 소스 드라이브 IC들의 개수를 줄일 수 있다.

[0020] 소스 드라이드 IC들 각각은 타이밍 콘트롤러(20)의 제어 하에 픽셀들에 공급될 데이터 전압의 극성을 2 수평기간 이상 N/2(N은 표시패널의 수직 해상도) 수평기간 이하의 반전 주기로 반전시킬 수 있다. 본 발명의 실시 예는 데이터 전압의 극성이 2 수평기간(2H) 마다 반전되는 예를 예시하였지만 이에 한정되지 않는다. 소스 드라이드 IC로부터 2 수평기간 동안 연속으로 출력되는 4 컬러의 데이터 전압은 같은 데이터 라인을 공유하는 4개의 서브 픽셀들에 충전된다.

[0021] 소스 드라이브 IC들은 타이밍 콘트롤러(20)로부터 수신된 극성 제어 신호(POL)에 응답하여 2 수평기간(2H) 동안 4 개의 서브 픽셀들에 충전될 4 컬러의 데이터 전압을 같은 극성으로 유지하고, 2 수평기간(2H) 마다 데이터 전압의 극성을 반전시킨다. 따라서, 소스 드라이브 IC들은 4 수평기간(4H) 동안 8 개의 데이터 전압을 연속으로 출력하되, 2 수평기간 마다 데이터 전압의 극성을 반전시킨다. 본 발명은 데이터 전압의 극성 반전 주기가 길어 데이터 전압의 트랜지션(transition) 횟수가 작다. 그 결과, 본 발명의 소스 드라이브 IC들의 소비 전력과 발열양을 줄일 수 있다. 소스 드라이드 IC들은 타이밍 콘트롤러(20)의 제어 하에 픽셀들에 공급될 데이터 전압의 극성을 4 수평기간 주기로 반전시켜 데이터 전압의 트랜지션 횟수를 더 줄일 수 있다.

[0022] 게이트 구동부(104)는 타이밍 콘트롤러(20)의 제어 하에 게이트 라인들(G1~Gn)에 게이트 펄스를 순차적으로 공급한다. 게이트 구동부(104)로부터 출력된 게이트 펄스는 픽셀들에 충전될 정극성/부극성 비디오 데이터 전압에 동기된다. 게이트 구동부(104)는 IC 비용을 줄이기 위하여, 같은 제조 공정에서 표시패널(100)의 TFT 어레이 기판 상에 직접 형성될 수 있다. 표시패널(100)의 하부 기판 상에 직접 형성된 게이트 구동부(104)는 "GIP(Gate in panel) 회로로 알려져 있다.

[0023] 타이밍 콘트롤러(20)는 호스트 시스템(30)으로부터 수신된 입력 영상의 데이터를 데이터 구동부(102)로 전송한다. 타이밍 콘트롤러(20)와 데이터 구동부(102)의 소스 드라이브 IC들 간의 데이터 전송을 위한 인터페이스는 mini LVDS(Low-voltage differential signaling) 인터페이스 또는 EPI(Embedded Panel Interface) 인터페이스를 적용할 수 있다.

[0024] 타이밍 콘트롤러(20)는 호스트 시스템(24)으로부터 입력 영상 데이터와 동기되는 타이밍 신호들을 입력받는다. 타이밍 신호들은 수직 동기신호(Vsync), 수평 동기신호(Hsync), 데이터 인레이블 신호(DE), 도트 클럭(DCLK) 등을 포함한다. 타이밍 콘트롤러(20)는 입력 영상의 픽셀 데이터와 함께 수신되는 타이밍 신호들(Vsync, Hsync, DE, DCLK)을 바탕으로 데이터 구동부(102)와 게이트 구동부(104)의 동작 타이밍을 제어한다. 타이밍 콘트롤러(20)는 픽셀들의 극성을 제어하기 위한 극성 제어 신호(POL)를 데이터 구동부(102)의 소스 드라이브 IC들 각각에 전송할 수 있다. Mini LVDS 인터페이스는 별도의 제어 배선을 통해 극성 제어 신호를 전송한다. EPI 인터페이스는 CDR(Clok and Data Recovery)을 위한 클럭 트레이닝 패턴(clock training pattern)과 RGB/RGBW 데이터

터 패킷 사이에 전송되는 콘트롤 데이터 패킷 내에 극성 제어 정보를 인코딩하여 소스 드라이브 IC들 각각에 전송하는 인터페이스 기술이다.

[0025] 타이밍 콘트롤러(20)는 공지된 화이트 게인 산출 알고리즘을 이용하여 입력 영상의 RGB 데이터를 RGBW 데이터로 변환할 수 있다. 화이트 게인 산출 알고리즘은 공지의 어떠한 것도 가능하다.

[0026] 호스트 시스템(24)은 TV(Television) 시스템, 셋톱박스, 네비게이션 시스템, DVD 플레이어, 블루레이 플레이어, 개인용 컴퓨터(PC), 홈 시어터 시스템, 폰 시스템(Phone system) 중 어느 하나일 수 있다.

[0027] 타이밍 콘트롤러(20)는 EEPROM(Electrically Erasable Programmable Read-Only Memory)(21)에 저장된 설정값을 참조하여 데이터 구동부(102)와 게이트 구동부(104)의 동작 타이밍을 제어하기 위한 데이터/게이트 타이밍 제어 신호를 발생한다. EEPROM(21)에는 데이터/게이트 타이밍 제어신호에 대한 라이징 에지 타이밍(rising edge timing), 펄스 데레이션(pulse duration), 폴링 에지 타이밍(falling edge timing) 등이 미리 설정되어 있다.

[0028] 본 발명은 RGB 타입 표시장치와 RGBW 타입 표시장치에서 TFT 어레이 기판과 데이터 구동부(102)를 공용화한다.

[0029] 도 2는 RGB 타입 표시장치와 RGBW 타입 표시장치에서 공용으로 사용될 수 있는 TFT 어레이 기판 일부를 나타내는 등가 회로도이다. 도 2에서 공통 전극(12)과 스토리지 커퍼시터(Cst)는 생략되어 있다.

[0030] 도 2를 참조하면, 같은 데이터 라인(S1)을 공유하고 동일 극성의 데이터 전압을 순차적으로 충전하는 서브 픽셀들의 연결 관계를 살펴 보면 아래와 같다.

[0031] 표시패널(100)의 기수 번째 라인(line)에 배치된 서브 픽셀들을 P1~P4이라 하고, 표시패널(100)의 우수 번째 라인에 배치된 서브 픽셀들을 P5~P8이라 할 때, 서브 픽셀들의 연결 관계를 설명하면 다음과 같다.

[0032] 제1 서브 픽셀(P1)은 제1 게이트 라인(G1)으로부터 제공받는 게이트 펄스에 응답하여 제1 데이터 라인(S1)을 통해 공급되는 제1 데이터 전압을 제1 픽셀 전극(PIX1)에 공급하는 제1 TFT(T1)를 포함한다. 제1 TFT(T1)는 제1 게이트 라인(G1)에 접속된 게이트, 제1 데이터 라인(S1)에 접속된 드레인, 및 제1 픽셀 전극(PIX1)에 접속된 소스를 포함한다.

[0033] 제2 서브 픽셀(P2)은 제2 게이트 라인(G2)으로부터 제공받는 게이트 펄스에 응답하여 제1 데이터 라인(S1)을 통해 공급되는 제2 데이터 전압을 제2 픽셀 전극(PIX2)에 공급하는 제2 TFT(T2)를 포함한다. 제2 TFT(T2)는 제2 게이트 라인(G2)에 접속된 게이트, 제1 데이터 라인(S1)에 접속된 드레인, 및 제2 픽셀 전극(PIX2)에 접속된 소스를 포함한다.

[0034] 제3 서브 픽셀(P6)은 제3 게이트 라인(G3)으로부터 제공받는 게이트 펄스에 응답하여 제1 데이터 라인(S1)을 통해 공급되는 제3 데이터 전압을 제3 픽셀 전극(PIX3)에 공급하는 제3 TFT(T3)를 포함한다. 제3 TFT(T3)는 제3 게이트 라인(G3)에 접속된 게이트, 제1 데이터 라인(S1)에 접속된 드레인, 및 제3 픽셀 전극(PIX3)에 접속된 소스를 포함한다.

[0035] 제4 서브 픽셀(P5)은 제4 게이트 라인(G4)으로부터의 제4 게이트 펄스에 응답하여 제J+1 데이터 라인(S1)을 통해 공급되는 제4 데이터 전압을 제4 픽셀 전극(PIX4)에 공급하는 제4 TFT(T4)를 포함한다. 제4 TFT(T4)는 제4 게이트 라인(G4)에 접속된 게이트, 제1 데이터 라인(S1)에 접속된 드레인, 및 제4 픽셀 전극(PIX4)에 접속된 소스를 포함한다.

[0036] 제2 데이터 라인(S2)을 공유하는 서브 픽셀들(P3, P4, P7, P8)은 데이터 라인을 제외하면 그 연결 관계가 서브 픽셀들(P1, P2, P5, P6)과 동일하다.

[0037] 도 3은 RGBW 타입 표시장치에서 컬러 배열을 나타낸다. 도 3에서, 컬러 필터 기판의 기수 번째 라인은 RGBW 순서로 컬러 필터가 배치되고, 우수 번째 라인은 BWRG 순서로 컬러 필터가 배치될 수 있다.

[0038] 도 4는 본 발명의 제1 실시예에 따른 소스 드라이브 IC를 보여 주는 회로도이다. 도 5는 RGBW 타입 표시장치의 극성 제어 신호를 보여 주는 회로도이다. 도 5는 제1 내지 제4 데이터 라인들(S1~S4)에 공급되는 극성 제어 신호(POL(S1)~POL(S4))를 보여 준다. 도 6은 도 5과 같은 극성 제어 신호에 따라 결정되는 픽셀들의 극성을 보여 주는 도면이다.

[0039] 도 4 내지 도 6을 참조하면, 소스 드라이브 IC는 다수의 버퍼들(P1, P2, N3, N4), 다수의 스위치들 및 다수의

소스채널들(OUT1~OUT4)을 포함한다.

[0040] 버퍼들(P1, P2, N3, N4)은 PDAC으로부터 입력되는 정극성 데이터 전압(+Vdata)을 소스채널들로 공급하는 P 버퍼들(P1, P2)과, NDAC으로부터 입력되는 부극성 데이터 전압(-Vdata)을 소스채널들로 공급하는 N 버퍼들(N3, N4)를 포함한다. 제1 P 버퍼(P1)는 제1 소스채널(OUT1)을 통해 제1 데이터 라인(S1)에 공급될 제1 데이터(Data1)와, 제3 소스채널(OUT3)을 통해 제3 데이터 라인(S3)에 공급될 제3 데이터(Data3)의 정극성 데이터 전압(+Vdata)을 출력한다. 제2 P 버퍼(P2)는 제2 소스채널(OUT2)을 통해 제2 데이터 라인(S2)에 공급될 제2 데이터(Data2)와, 제4 소스채널(OUT4)을 통해 제4 데이터 라인(S4)에 공급될 제4 데이터(Data4)의 정극성 데이터 전압(+Vdata)을 출력한다. 제1 N 버퍼(N3)는 제1 소스채널(OUT1)을 통해 제1 데이터 라인(S3)에 공급될 제1 데이터(Data1)와, 제3 소스채널(OUT3)을 통해 제3 데이터 라인(S3)에 공급될 제3 데이터(Data3)의 부극성 데이터 전압(-Vdata)을 출력한다. 제2 N 버퍼(N4)는 제2 소스채널(OUT2)을 통해 제2 데이터 라인(S2)에 공급될 제2 데이터(Data2)와, 제4 소스채널(OUT4)을 통해 제4 데이터 라인(S4)에 공급될 제4 데이터(Data4)의 부극성 데이터 전압(-Vdata)을 출력한다.

[0041] 스위치들은 데이터 분배를 위한 멀티플렉서(Multiplexer, MUX), 데이터 전압 공급용 스위치들(SW1~SW4), 차지 쉐어용 스위치들(SW5, SW6) 등을 포함한다.

[0042] 멀티플렉서는 하나의 버퍼를 통해 출력되는 데이터 전압을 다수의 소스채널들로 분배하는 벡스 스위치들(SA1, SB1, SA3, SB3, SC2, SD2, SC4, SD4)을 포함한다. 멀티플렉서는 도 5에 도시된 극성 제어 신호(POL(S1), POL(S2), POL(S3), POL(S4))에 응답하여 데이터 전압(+Vdata, -Vdata)의 극성을 선택한다.

[0043] 제1 P 버퍼(P1)에 연결된 제1 MUX 스위치(SA1)는 제1 극성 제어 신호(POL(S1))의 제1 논리값에 응답하여 제1 P 버퍼(P1)의 출력 단자를 제1 소스채널(OUT1)에 연결한다. 제1 P 버퍼(P1)에 연결된 제2 MUX 스위치(SB1)는 제1 극성 제어 신호(POL(S1))의 제1 논리값에 응답하여 제1 P 버퍼(P1)의 출력 단자를 제3 소스채널(OUT3)에 연결한다. 제1 및 제2 MUX 스위치(SA1, SB1)는 제1 극성 제어 신호(POL(S1))가 제2 논리값일 때 턴-오프(turn-off)된다.

[0044] 제2 P 버퍼(P2)에 연결된 제3 MUX 스위치(SC2)는 제2 극성 제어 신호(POL(S2))의 제1 논리값에 응답하여 제2 P 버퍼(P2)의 출력 단자를 제2 소스채널(OUT2)에 연결한다. 제2 P 버퍼(P2)에 연결된 제4 MUX 스위치(SD2)는 제2 극성 제어 신호(POL(S2))의 제1 논리값에 응답하여 제2 P 버퍼(P2)의 출력 단자를 제4 소스채널(OUT4)에 연결한다. 제3 및 제4 MUX 스위치(SC2, SD2)는 제2 극성 제어 신호(POL(S2))가 제2 논리값일 때 턴-오프된다.

[0045] 제1 N 버퍼(N3)에 연결된 제5 MUX 스위치(SB3)는 제3 극성 제어 신호(POL(S3))의 제2 논리값에 응답하여 제1 N 버퍼(N3)의 출력 단자를 제1 소스채널(OUT1)에 연결한다. 제1 N 버퍼(N3)에 연결된 제6 MUX 스위치(SA3)는 제3 극성 제어 신호(POL(S3))의 제2 논리값에 응답하여 제1 N 버퍼(N3)의 출력 단자를 제3 소스채널(OUT3)에 연결한다. 제5 및 제6 MUX 스위치(SB3, SA3)는 제3 극성 제어 신호(POL(S3))가 제1 논리값일 때 턴-오프된다.

[0046] 제2 N 버퍼(N4)에 연결된 제7 MUX 스위치(SD4)는 제4 극성 제어 신호(POL(S4))의 제2 논리값에 응답하여 제2 N 버퍼(N2)의 출력 단자를 제4 소스채널(OUT4)에 연결한다. 제2 N 버퍼(N4)에 연결된 제8 MUX 스위치(SC4)는 제4 극성 제어 신호(POL(S4))의 제2 논리값에 응답하여 제2 N 버퍼(N2)의 출력 단자를 제4 소스채널(OUT4)에 연결한다. 제7 및 제8 MUX 스위치(SD4, SC4)는 제4 극성 제어 신호(POL(S4))가 제1 논리값일 때 턴-오프된다.

[0047] 데이터 전압 공급용 스위치들(SW1~SW4)은 멀티플렉서와 소스채널 사이에 배치되어 멀티플렉서로부터의 정극성 데이터 전압(+Vdata)과 부극성 데이터 전압(-Vdata)을 소스채널들(OUT1~OUT4)에 공급한다. 데이터 전압 공급용 스위치들(SW1~SW4) 각각은 2 개의 MUX 스위치들에 연결된 입력 단자와, 하나의 소스채널에 연결된 출력 단자를 포함한다.

[0048] 차지 쉐어용 스위치들(SW5, SW6, 이하 "CS 스위치"라 함)은 데이터 전압의 극성이 변할 때 데이터 전압의 극성이 동시에 변하는 소스채널들을 연결한다.

[0049] 제1 CS 스위치(SW5)는 제1 데이터 라인 그룹의 데이터 라인들에 연결된 제1 및 제3 소스채널들(OUT1, OUT3)에 연결된다. 제1 CS 스위치(SW5)는 제1 차지 쉐어 타이밍에 턴-온(turn-on)되어 제1 데이터 라인 그룹의 데이터 라인들(S1, S3)을 차지 쉐어한다. 제1 차지 쉐어 타이밍은 제1 소스 출력 인에이블 신호(SOE1)에 의해 제어된다. 제1 CS 스위치(SW5)는 제1 소스 출력 인에이블 신호(SOE1)의 제1 논리값에 응답하여 제1 및 제3 소스채널들(OUT1, OUT3)을 연결하여 제1 데이터 라인 그룹의 차지 쉐어를 실시한다.

[0050] 제2 CS 스위치(SW6)는 제2 데이터 라인 그룹의 데이터 라인들(S2, S4)에 연결된 제1 및 제3 소스채널들(OUT1,

OUT3)에 연결된다. 제2 CS 스위치(SW6)는 제1 차지 쉐어 타이밍에 턴-온(turn-on)되어 제2 데이터 라인 그룹의 데이터 라인들(S2, S4)을 차지 쉐어한다. 제2 차지 쉐어 타이밍은 제2 소스 출력 인에이블 신호(SOE2)에 의해 제어된다. 제2 CS 스위치(SW6)는 제2 소스 출력 인에이블 신호(SOE2)의 제1 논리값에 응답하여 제2 및 제4 소스 채널들(OUT2, OUT4)을 연결하여 제2 데이터 라인 그룹의 차지 쉐어를 실시한다.

[0051] 소스 드라이브 IC는 제1 내지 제4 극성 제어 신호(POL(S1)~POL(S4))에 응답하여 데이터 전압의 극성을 반전시킨다. 픽셀들의 극성은 도 5와 같은 극성 제어 신호(POL(S1)~POL(S4))에 의해 도 6과 같이 제어된다. 픽셀 아래에는 이웃한 서브 픽셀들 간에 1 도트 단위로 데이터 전압의 극성이 반전되는 픽셀들과, 2 도트 단위로 데이터 전압의 극성이 반전되는 픽셀들을 포함한다. 1 도트(dot)는 1 서브 픽셀을 의미한다. 도 5과 같은 극성 제어 신호(POL(S1)~POL(S4))는 RGBW 표시장치에서 동일 극성이 라인 또는 블록 형태로 집중할 때 보일 수 있는 휘도차와 플리커(flicker)를 방지할 수 있다. 또한, 도 5과 같은 극성 제어 신호(POL(S1)~POL(S4))는 RGBW 표시장치에서 수직 및 수평 방향을 따라 배치되는 픽셀들의 극성이 어느 한쪽으로 치우치지 않게 하여 공통 전압(Vcom)의 시프트를 방지할 수 있다. 공통 전압(Vcom)이 시프트되면 같은 계조에서 정극성 픽셀과 부극성 픽셀 간에 데이터 전압 충전율이 달라져 정극성 픽셀과 부극성 픽셀의 휘도차를 초래한다. 따라서, 도 6과 같은 극성 제어 신호(POL(S1)~POL(S4))는 RGBW 표시장치에서 최적의 화질을 구현할 수 있다.

[0052] 도 7은 서로 인접하는  $2 \times 4$  화소들(P1~P8)의 차폐 전극(SP)의 배치를 나타내는 도면이고, 도 8은 도 7에서 I-I'를 따라 절취한 단면을 나타내는 도면이다. 도 7 및 도 8에 도시된 화소 구조 및 구동방법은 도 1 내지 도 6에 도시된 화소 구조 및 구동 방법을 이용할 수 있다.

[0053] 도 7 및 도 8을 참조하면, 수평으로 인접한 제5 화소(P5) 및 제6 화소(P6)들의 경계면에서 데이터라인들이 배치되는 영역에는 차폐 전극(SP)이 배치된다. 특히, 본 발명은 RGBW 화소들 중에서 W,R,G 화소들에 한정되어 차폐 전극(SP)이 배치된다.

[0054] 단면 구조를 살펴보면, 차폐 전극(SP)은 기판(SUB) 상에 배치되고, 차폐 전극(SP)을 덮도록 게이트 절연막(GI)이 배치된다. 게이트 절연막(GI) 상에는 반도체 활성층(ACT) 및 데이터라인(DL)이 배치된다. 보호막(PAS)은 데이터라인(DL)을 덮도록 형성된다.

[0055] 차폐 전극(SP)은 공통전압을 공급받아서, 데이터라인(DL1)으로부터의 전계를 차단한다. 차폐 전극(SP)은 기판(SUB) 상에서 게이트전극과 동일한 금속층에 배치될 수 있다. 게이트전극은 도 2에 도시된 바와 같이, 데이터라인과 화소전극 간의 전류 경로를 스위칭하는 박막 트랜ジ스터(T)의 게이트전극을 지칭한다.

[0056] 화소들은 공통전극(VCOM)과 화소전극(11) 간의 전압차이에 대응하는 계조표현을 한다. 즉, 제5 화소(P5)는 공통전극(VCOM)과 제5 화소전극(11a) 간의 전압차이에 대응하는 계조를 표현하고, 제6 화소(P6)는 공통전극(VCOM)과 제6 화소전극(11b) 간의 전압차이에 대응하는 계조를 표현한다. 하지만, 데이터라인(DL)을 경유하는 전류는 공통전극(VCOM)과 화소전극(11) 간의 전계에 영향을 미치기도 한다. 그 결과 액정층에 형성되는 전계가 왜곡되어 표시패널은 비정상적인 휘도를 표시하기도 한다. 이를 도 9 및 도 10을 참조하여 살펴보면 다음과 같다.

[0057] 도 9는 표시패널에서 수직 방향으로 계조 차이가 큰 영상을 표시하는 패턴을 나타내는 도면이다. 표시패널(100)의 중앙 영역에서 고계조(White)를 표시하고, 고계조 영역(W)의 수직 상부와 하부 영역에서는 저계조(Black)를 표시하는 저계조 영역(B)에 배치된 데이터라인(DLi)에 제공되는 데이터전압(Vdatai)은 도 10에 도시된 바와 같다.

[0058] 데이터전압(Vdatai)은 저계조 영역(B)에 데이터를 제공하는 제1 기간(t1)동안에서는 전압레벨의 스윙폭이 작고, 고계조 영역(W)에 데이터를 제공하는 제2 기간(t2)에서는 전압레벨의 스윙폭이 크다. 결국, 고계정 영역(W)과 저계조 영역(B)의 경계에서 크로스토크가 발생한다.

[0059] 제2 기간 동안, 저계조 영역(B)의 화소들은 제1 기간(t1) 내에서 제공받은 데이터전압을 훌딩하여 계조표현을 한다. 이때, 제2 기간(t2)에 데이터라인(DL)은 상대적으로 높은 전압을 출력하기 때문에, 저계조 영역(B)의 화소들은 데이터라인(DK)을 경유하는 높은 전압의 영향으로 공통전극(VCOM)과 화소 전극 간의 전계가 왜곡된다.

[0060] 그 결과, 저계조 영역(B)의 화소들은 저계조를 표시하지 못하고 보다 높은 계조를 표시한다. 예컨대, 저계조 영역(B)의 화소들은 그레이(gray) 계조를 표시하는 문제점이 발생할 수 있다.

[0061] 본 발명의 차폐 전극(SP)은 공통전압을 제공받아서, 데이터라인(DL)과 차폐 전극(SP) 간의 전위를 일정하게 유지시킨다. 그 결과 데이터라인(DL)의 전계가 공통전극(VCOM)과 화소전극(11) 간의 전계에 영향을 미치지 않도록

록 한다. 예컨대, 제5 차폐 전극(SP5)은 제1 데이터라인(DL1)으로부터의 전압이 제5 화소(P5)의 전계에 영향을 미치지 않도록 한다.

[0062] 제4 화소(P4) 및 제6 화소(P6)내에서는 차폐 전극(SP)이 배치되지 않는다.

[0063] 차폐 전극(SP)은 데이터라인()으로부터의 전계를 차단할 수 있지만 기생 커패시터로 인한 데이터전압이 지연(delay)되는 현상이 발생한다. 도 8에서 보는 바와 같이, 차폐 전극(SP)은 데이터라인(DL)이 위치하는 영역의 하부에서 배치되고 차폐 전극(SP)과 데이터라인(DL) 사이에는 게이트 절연막(GI)이 배치되기 때문에, 차폐 전극(SP)과 데이터라인(DL)은 기생 커패시터를 형성한다. 따라서, 데이터라인(DL)을 경유하는 데이터전압은 차폐 전극(SP)과의 기생 커패시터로 인해서 지연된다. 본 발명은 청색 화소(B)인 제4 화소(P4) 및 제6 화소(P6)에는 차폐 전극(SP)을 배치하지 않음으로써, 데이터라인(DL)을 경유하는 데이터전압의 지연 현상을 개선할 수 있다.

[0064] 차폐 전극(SP)이 배치되지 않는 화소에서는 데이터라인(DL)의 전계에 의해서 계조가 달라질 수 있다. 따라서, 본 발명은 휘도 가중치가 낮은 화소들에 한해서 차폐 전극(SP)을 배치하지 않는다. 휘도 가중치가 낮은 화소들은 계조가 왜곡된다고 할지라도, 삼원색을 조합한 색상을 표현하는 과정에서 시인성에 영향을 덜 끼치기 때문에, 휘도 가중치가 낮은 화소들내에는 차폐 전극(SP)을 배치하지 않는다. 네 가지 색상 화소의 휘도 가중치는 대략 W:R:G:B=10:2:7:1로 나타난다. 즉, 흰색 화소(W)와 녹색 화소(G)의 휘도 가중치에 비해서 적색 화소(R)와 청색 화소(B)의 휘도 가중치는 낮다. 따라서, 본 발명은 청색 화소(B)에서는 차폐 전극을 배치하지 않는다. 또 다른 실시 예로서, 도 11에서와 같이, 적색 화소(G)에서도 차폐 전극을 배치하지 않음으로써 데이터전압의 지연 현상을 더욱 개선할 수 있다. 특히, 본 발명은 도 6을 참조하여 살펴본 바와 같이, 수직 4도트 인버 전 구동을 하기 때문에, 크로스토크의 영향이 작기 때문에, 차폐 전극(SP)을 배치하지 않더라도 계조가 왜곡되는 현상이 둔화된다.

[0065] 도 12는 본 발명의 다른 실시 예에 의한 표시패널을 나타내는 도면이다.

[0066] 도 12를 참조하면, 다른 실시 예에 의한 표시패널은 차폐 전극(SP)이 배치되지 않는 영역에서는, 공통전극(VCOM)이 발광영역(EA)을 노출시키도록 배치된다. 도면에서 발광영역()의 경계선은 반도체 활성층(ACT)이 배치되는 경계를 지칭한다.

[0067] 공통전극(VCOM)의 부하(load)를 줄이면서 공통전압을 효율적으로 공급하기 위해서는 공통전극(VCOM)의 폭이 넓은 것이 유리하다. 반면에 공통전극(VCOM)이 클수록 개구율은 저하되는 단점이 있다. 제5 화소(P5)에서는 차폐 전극(SP)이 배치되기 때문에 차폐 전극(SP)으로 인해서 개구율이 일정부분 감소된다. 따라서, 제5 화소(P5)에서는 차폐 전극(SP)이 배치되는 영역까지는 공통전극(VCOM)을 배치하여도 무방하다. 제6 화소(P6)에서는 차폐 전극(SP)이 배치되지 않기 때문에, 도면에서와 같이 발광 영역(EA)을 모두 오픈 시킴으로써, 개구율을 높일 수 있다.

[0068] 살펴본 바와 같이, 본 발명은 차폐 전극(SP)을 배치하여 데이터라인()으로부터의 전계가 공통전극(VCOM)과 화소 전극(11) 간의 전계에 영향을 끼치는 것을 방지할 수 있다. 그 결과, 본 발명은 데이터라인으로부터 전계에 의해서 계조가 변하는 것을 방지할 수 있다. 특히, 본 발명은 시분할로 데이터전압을 공급하는 DRD 구조에서 데이터라인이 배치되는 수직 경계면에서는 차폐 전극(SP)을 배치하지 않음으로써, 기생 커패시터를 제거할 수 있어서 데이터전압의 지연 현상을 방지할 수 있다. 또한, 차폐 전극(SP)을 배치하지 않더라도 데이터라인이 1/2 인 구조를 이용함으로써 데이터라인으로부터의 전계의 영향을 덜 받도록 하여, 데이터라인의 전계에 의한 계조 변화를 둔화시킬 수 있다.

[0069] 이상 설명한 내용을 통해 당업자라면 본 발명의 기술사상을 일탈하지 아니하는 범위에서 다양한 변경 및 수정이 가능함을 알 수 있을 것이다. 따라서, 본 발명의 기술적 범위는 명세서의 상세한 설명에 기재된 내용으로 한정되는 것이 아니라 특히 청구의 범위에 의해 정하여져야만 할 것이다.

### 부호의 설명

[0070] 100 : 표시패널 102 : 데이터 구동부

104 : 게이트 구동부 20 : 타이밍 콘트롤러

SP: 차폐전극

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

## 도면5

## 도면6

## 도면7

## 도면8

도면9

도면10

도면11

도면12

|                |                                                |         |            |

|----------------|------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示器                                          |         |            |

| 公开(公告)号        | KR1020170067402A                               | 公开(公告)日 | 2017-06-16 |

| 申请号            | KR1020150174042                                | 申请日     | 2015-12-08 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                       |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                      |         |            |

| [标]发明人         | KIM TAE HAN<br>김태한                             |         |            |

| 发明人            | 김태한                                            |         |            |

| IPC分类号         | G09G3/36 G02F1/1343 G02F1/1362                 |         |            |

| CPC分类号         | G09G3/3648 G02F1/1343 G02F1/1362 G09G2320/0252 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                      |         |            |

### 摘要(译)

根据本发明的液晶显示器包括第一数据线，公共电极第一和第二像素电极，以及屏蔽图案。第一条数据线由数据驱动器提供数据电压。公共电极布置在第一数据线的上部，并且接收公共电压。它被布置在第一像素电极起公共电极和相邻电极并且从第一数据线接收的域中。第二像素电极布置在第一像素电极的与公共电极相对的一侧，并且其被提供给第一数据电压的第二数据电压和来自第一数据线的时间共享。绝缘层位于间隔中，绝缘层位于第一数据线的下部，绝缘层布置在第一像素电极布置到第一数据线的一侧。以这种方式，它阻挡，使得来自第一数据线的电场不影响第一像素电极和公共电极之间的电场。