# (19) 대한민국특허청(KR) (12) 공개특허공보(A)

(51) Int. Cl.

**G09G 3/36** (2006.01) **G11C 19/28** (2006.01)

(21) 출원번호 **10-2010-0086694**

(22) 출원일자 **2010년09월03일** 심사청구일자 **2010년09월03일**

(30) 우선권주장

200910092003.1 2009년09월04일 중국(CN)

(11) 공개번호 10-2011-0025630

(43) 공개일자 2011년03월10일

(71) 출원인

베이징 비오이 옵토일렉트로닉스 테크놀로지 컴퍼 니 리미티드

중국 베이징 100176 비디에이 시환중로 8호

(72) 발명자

샹 광리앙

중국 베이징 100176 비디에이 시환중로 8호

한 승우

중국 베이징 100176 비디에이 시환중로 8호

(74) 대리인

리앤목특허법인

전체 청구항 수 : 총 7 항

## (54) 쉬프트 레지스터 유닛 및 액정 디스플레이의 게이트 구동 장치

### (57) 요 약

본 발명은 쉬프트 레지스터 유닛 및 액정 디스플레이의 게이트 구동 장치를 개시하고 있다. 이 쉬프트 레지스터 유닛은 종래 기술에 관한 12개의 트랜지스터와 1개의 콘덴서의 구성을 토대로 하여 제7 박막 트랜지스터와 제8 박막 트랜지스터와 제9 박막 트랜지스터와 제10 박막 트랜지스터는 쉬프트 레지스터 유닛이 하이 레벨 신호를 출력할 때에 누설 전류를 일으키지 않고 쉬프트 레지스터 유닛의 소비전력을 줄이도록 제7 박막 트랜지스터의 드레인, 제9 박막 트랜지스터의 게이트 및 드레인이 제2 클럭 신호의 입력 단자에 접속되어 구성되어 있다.

### 대 표 도 - 도2a

## 특허청구의 범위

#### 청구항 1

쉬프트 레지스터 유닛으로서,

드레인 및 게이트가 신호 입력 단자에 접속되는 제1 박막 트랜지스터와,

드레인이 상기 제1 박막 트랜지스터의 소스에 접속되고, 게이트가 리셋 신호 입력 단자에 접속되고, 소스가 저전압 신호 입력 단자에 접속되는 제2 박막 트랜지스터와,

드레인이 제1 클럭 신호 입력 단자에 접속되고, 게이트가 상기 제1 박막 트랜지스터의 소스에 접속되고, 소스가 신호 출력 단자에 접속되는 제3 박막 트랜지스터와,

드레인이 상기 제3 박막 트랜지스터의 소스에 접속되고, 게이트가 상기 리셋 신호 입력 단자에 접속되고, 소스가 상기 저전압 신호 입력 단자에 접속되는 제4 박막 트랜지스터와,

드레인이 상기 제1 박막 트랜지스터의 소스에 접속되고, 소스가 상기 저전압 신호 입력 단자에 접속되는 제5 박 트랜지스터와.

드레인이 상기 제3 박막 트랜지스터의 소스에 접속되고, 소스가 상기 저전압 신호 입력 단자에 접속되는 제6 박 트랜지스터와.

드레인이 제2 클럭 신호 입력 단자에 접속되고, 소스가 각각 상기 제5 박막 트랜지스터의 게이트 및 상기 제6 박막 트랜지스터의 게이트에 접속되는 제7 박막 트랜지스터와,

드레인이 상기 제7 박막 트랜지스터의 소스에 접속되고, 게이트가 상기 제1 박막 트랜지스터의 소스에 접속되고, 소스가 상기 저전압 신호 입력 단자에 접속되는 제8 박막 트랜지스터와,

드레인과 게이트가 모두 상기 제2 클럭 신호 입력 단자에 접속되고, 소스가 상기 제7 박막 트랜지스터의 게이트 에 접속되는 제9 박막 트랜지스터와,

드레인이 상기 제9 박막 트랜지스터의 소스에 접속되고, 게이트가 상기 제1 박막 트랜지스터의 소스에 접속되고, 소스가 상기 저전압 신호 입력 단자에 접속되는 제10 박막 트랜지스터를 포함하는 것을 특징으로 하는 쉬프트 레지스터 유닛.

## 청구항 2

제1항에 있어서, 양단이 각각 상기 제3 박막 트랜지스터의 게이트 및 상기 신호 출력 단자에 접속되는 콘덴서를 더 포함한 것을 특징으로 하는 쉬프트 레지스터 유닛.

## 청구항 3

제2항에 있어서, 드레인이 상기 신호 출력 단자에 접속되고, 소스가 상기 저전압 신호 입력 단자에 접속되고, 게이트가 상기 제2 클럭 신호 입력 단자에 접속되는 제12 박막 트랜지스터를 더 포함한 것을 특징으로 하는 쉬프트·레지스터 유닛.

## 청구항 4

제3항에 있어서, 드레인이 상기 신호 입력 단자에 접속되고, 게이트가 상기 제2 클럭 신호 입력 단자에 접속되고, 소스가 상기 제1 박막 트랜지스터의 소스에 접속되는 제11 박막 트랜지스터를 더 포함한 것을 특징으로 하는 쉬프트 레지스터 유닛.

## 청구항 5

제1항 내지 제4항에 있어서, 상기 제7 박막 트랜지스터의 채널의 길이에 대한 폭의 비와 제8 박막 트랜지스터의 채널의 길이에 대한 폭의 비 간의 비례는  $1/1\sim1/50$ 이고, 상기 제9 박막 트랜지스터의 채널의 길이에 대한 폭비와 제10 박막 트랜지스터의 채널 길이에 대한 폭의 비 간의 비례는  $1/1\sim1/50$ 임을 특징으로 하는 쉬프트 레지스터 유닛.

### 청구항 6

제1항 내지 제5항에 있어서, 상기 제7 박막 트랜지스터의 채널의 길이에 대한 폭의 비와 제8 박막 트랜지스터의 채널의 길이에 대한 폭의 비 간의 비례는 1/5이고, 상기 제9 박막 트랜지스터의 채널의 길이에 대한 폭비와 제10 박막 트랜지스터의 채널 길이에 대한 폭의 비 간의 비례는 1/5임을 특징으로 하는 쉬프트 레지스터유닛.

#### 청구항 7

액정 디스플레이의 게이트 구동 장치로서, 액정 디스플레이 어레이 기판에 퇴적된 제1항 내지 제6항 중 어느 한 항에 기재된 여러 개의 쉬프트 레지스터 유닛을 포함하고,

제1 쉬프트 레지스터 유닛과 최후의 쉬프트 레지스터 유닛 이외에 다른 각 쉬프트 레지스터 유닛의 신호 출력 단자 각각은 자신과 인접한 다음 쉬프트 레지스터 유닛의 신호 입력 단자 및 자신과 인접한 앞의 쉬프트 레지스 터 유닛의 리셋 신호 입력 단자에 접속되고, 제1 쉬프트 레지스터 유닛의 신호 출력 단자가 제2 쉬프트 레지스 터 유닛의 신호 입력 단자에 접속되고, 최후의 쉬프트 레지스터 유닛의 신호 출력 단자는 자신과 인접한 앞의 쉬프트 레지스터 유닛의 리셋 신호 입력 단자 및 그 자신의 리셋 신호 입력 단자에 접속되고,

제1 쉬프트 레지스터 유닛의 신호 입력 단자에는 프레임 개시 신호가 입력되고,

홀수째의 쉬프트 레지스터 유닛의 제1 클럭 신호 입력 단자에는 제1 클럭 신호가 입력되고, 제2 클럭 신호 입력 단자에는 제2 클럭 신호가 입력되고, 짝수째의 쉬프트 레지스터 유닛의 제1 클럭 신호 입력 단자에는 제2 클럭 신호가 입력되고, 제2 클럭 신호 입력 단자에는 시스템의 제1 클럭 신호가 입력되고,

각 쉬프트 레지스터 유닛의 저전압 신호 입력 단자에는 저전압 신호가 입력되는 것을 특징으로 하는 액정 디스 플레이의 게이트 구동 장치.

## 명세서

## 기술분야

[0001] 본 발명은 액정 디스플레이 구동 기술에 관한 것으로서, 특히 쉬프트 레지스터 유닛 및 액정 디스플레이의 게이트 구동 장치에 관한 것이다.

## 배경기술

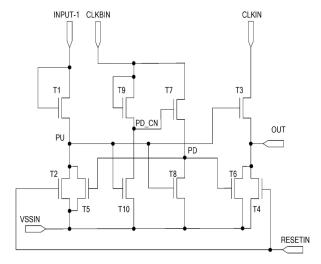

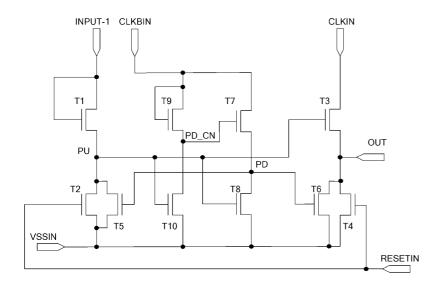

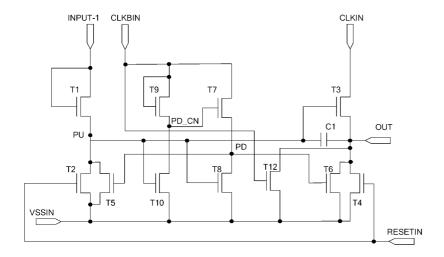

- [0002] 도 1a는 종래 기술에 관한 쉬프트 레지스터 유닛의 구성 개략도이다. 도 1b는 도 1a에 도시한 쉬프트 레지스터 유닛의 시퀀스도이다. 쉬프트 레지스터 유닛은 제1 박막 트랜지스터(T1)와, 제2 박막 트랜지스터(T2)와, 제3 박막 트랜지스터(T3)와, 제4 박막 트랜지스터(T4)와, 제5 박막 트랜지스터(T5)와, 제6 박막 트랜지스터(T6)와, 제7 박막 트랜지스터(T7)와, 제8 박막 트랜지스터(T8)와, 제9 박막 트랜지스터(T9)와, 제10 박막 트랜지스터(T1 0)의 드레인과, 제11 박막 트랜지스터(T11)와, 제12 박막 트랜지스터(T12)를 포함하고 또한 콘텐서(C1)를 포함한다. 신호 입력 단자(INPUT-1)에는 신호(INPUT)가 입력되고, 제1 클럭 신호 입력 단자(CLKIN)에는 제1 클럭 신호(CLK)가 입력되고, 제2 클럭 신호 입력 단자(CLKIN)에는 제2 클럭 신호(CLKB)가 입력되고, 저전압 신호 입력 단자(VSSIN)에는 저전압 신호(VSS)가 입력되고, 리셋 신호 입력 단자(RESETIN)에는 리셋 신호(RESET)가 입력되고, 신호 출력 단자(OUT)에서 게이트 구동 신호(OUTPUT)가 출력된다. 제1 박막 트랜지스터(T1)의 소스와, 제2 박막 트랜지스터(T2)의 드레인과, 제10 박막 트랜지스터(T10)의 게이트와, 콘덴서(C1)의 집합처가 PU접합부이고, 제5 박막 트랜지스터(T5)의 게이트와, 제6 박막 트랜지스터(T6)의 게이트와, 제8 박막 트랜지스 터(T8)의 드레인과, 제7 박막 트랜지스터(T7)의 소스의 집합처가 PD접합부이고, 제9 박막 트랜지스터(T9)의 소스와, 제10 박막 트랜지스터(T10)의 그합처가 PD\_CN접합부이다.

- [0003] 도 1b에 도시한 것처럼 게이트 구동 신호(OUTPUT)가 로우 레벨인 경우에 제1 클럭 신호(CLK) 또는 제2 클럭 신호(CLKB)가 하이 레벨이라 해도 게이트 구동 신호(OUTPUT)와 PU접합부에서의 신호는 로우 레벨로 유지될 수 있다. 게이트 구동 신호(OUTPUT)가 하이 레벨인 경우에 제1 클럭 신호(CLK)와 PU접합부에서의 신호는 모두 하이레벨이 된다. 콘텐서(C1)의 커플링 작용에 의해 PU접합부에서의 신호의 레벨이 특히 높아 제9 박막 트랜지스터(T9)와 제10 박막 트랜지스터(T10)는 동시에 온되어 보다 큰 누설 전류가 형성되기 때문에 쉬프트 레지스터 유닛의 소비전력의 증가를 초래한다. 그 결과, 이 쉬프트 레지스터 유닛을 사용한 액정 디스플레이의 소비전력의

증가를 초래한다.

#### 발명의 내용

#### 해결하려는 과제

[0004] 본 발명은 종래 기술에 존재하는 과제에 대해, 쉬프트 레지스터 유닛의 소비전력을 줄여 액정 디스플레이의 게이트 구동 장치의 소비전력을 줄일 수 있는 쉬프트 레지스터 유닛 및 액정 디스플레이의 게이트 구동 장치를 제공하는 것을 목적으로 한다.

## 과제의 해결 수단

- [0005] 상기 목적을 실현하기 위해 본 발명이 제공하는 쉬프트 레지스터 유닛은,

- [0006] 드레인 및 게이트가 함께 신호 입력 단자에 접속되는 제1 박막 트랜지스터와.

- [0007] 드레인이 상기 제1 박막 트랜지스터의 소스에 접속되고, 게이트가 리셋 신호 입력 단자에 접속되고, 소스가 저 전압 신호 입력 단자에 접속되는 제2 박막 트랜지스터와,

- [0008] 드레인이 제1 클럭 신호 입력 단자에 접속되고, 게이트가 상기 제1 박막 트랜지스터의 소스에 접속되고, 소스가 신호 출력 단자에 접속되는 제3 박막 트랜지스터와,

- [0009] 드레인이 상기 제3 박막 트랜지스터의 소스에 접속되고, 게이트가 상기 리셋 신호 입력 단자에 접속되고, 소스가 상기 저전압 신호 입력 단자에 접속되는 제4 박막 트랜지스터와,

- [0010] 드레인이 상기 제1 박막 트랜지스터의 소스에 접속되고, 소스가 상기 저전압 신호 입력 단자에 접속되는 제5 박 막 트랜지스터와,

- [0011] 드레인이 상기 제3 박막 트랜지스터의 소스에 접속되고, 소스가 상기 저전압 신호 입력 단자에 접속되는 제6 박 막 트랜지스터와.

- [0012] 드레인이 제2 클럭 신호 입력 단자에 접속되고, 소스가 각각 상기 제5 박막 트랜지스터의 게이트와 상기 제6 박 막 트랜지스터의 게이트에 접속되는 제7 박막 트랜지스터와,

- [0013] 드레인이 상기 제7 박막 트랜지스터의 소스에 접속되고, 게이트가 상기 제1 박막 트랜지스터의 소스에 접속되고, 소스가 상기 저전압 신호 입력 단자에 접속되는 제8 박막 트랜지스터와,

- [0014] 드레인과 게이트가 모두 상기 제2 클럭 신호 입력 단자에 접속되고, 소스가 상기 제7 박막 트랜지스터의 게이트 에 접속되는 제9 박막 트랜지스터와,

- [0015] 드레인이 상기 제9 박막 트랜지스터의 소스에 접속되고, 게이트가 상기 제1 박막 트랜지스터의 소스에 접속되고, 소스가 상기 저전압 신호 입력 단자에 접속되는 제10 박막 트랜지스터,를 포함한다.

- [0016] 본 발명은 또한 액정 디스플레이 어레이 기판에 퇴적된 복수의 전술한 쉬프트 레지스터 유닛을 포함한 액정 디스플레이의 게이트 구동 장치를 제공하고,

- [0017] 제1 쉬프트 레지스터 유닛과 최후의 쉬프트 레지스터 유닛 이외에 다른 각 쉬프트 레지스터 유닛의 신호 출력 단자 각각은 자신과 인접한 다음 쉬프트 레지스터 유닛의 신호 입력 단자 및 자신과 인접한 앞의 쉬프트 레지스터 유닛의 리셋 신호 입력 단자에 접속되고, 제1 쉬프트 레지스터 유닛의 신호 출력 단자가 제2 쉬프트 레지스터 유닛의 신호 합력 단자에 접속되고, 최후의 쉬프트 레지스터 유닛의 신호 출력 단자는 자신과 인접한 앞의 쉬프트 레지스터 유닛의 리셋 신호 입력 단자 및 그 자신의 리셋 신호 입력 단자에 접속되고,

- [0018] 제1 쉬프트 레지스터 유닛의 신호 입력 단자에는 프레임 개시 신호가 입력되고,

- [0019] 홀수째의 쉬프트 레지스터 유닛의 제1 클럭 신호 입력 단자에는 제1 클럭 신호가 입력되고, 제2 클럭 신호 입력 단자에는 제2 클럭 신호가 입력되고, 짝수째의 쉬프트 레지스터 유닛의 제1 클럭 신호 입력 단자에는 제2 클럭 신호가 입력되고, 제2 클럭 신호 입력 단자에는 시스템의 제1 클럭 신호가 입력되고,

- [0020] 각 쉬프트 · 레지스터 유닛의 저전압 신호 입력 단자에는 저전압 신호가 입력된다.

### 발명의 효과

- [0021] 본 발명의 실시 방식에서 제공하는 쉬프트 레지스터 유닛 및 액정 디스플레이의 게이트 구동 장치는, 제9 박막 트랜지스터의 드레인과 게이트 및 제7 박막 트랜지스터의 드레인과, 제2 클릭 신호 입력 단자가 접속되고, 게이트 구동 신호가 하이 레벨인 기간 중에 제7 박막 트랜지스터와 제8 박막 트랜지스터와 제9 박막 트랜지스터와 제10 박막 트랜지스터에서 누설 전류가 생기지 않기 때문에 쉬프트 레지스터 유닛의 소비전력을 줄여 이 쉬프트 레지스터 유닛을 사용한 액정 디스플레이의 소비전력을 줄일 수 있다.

- [0022] 이하, 도면과 실시예를 통해 본 발명의 기술 방안을 더욱 상세히 설명하기로 한다.

#### 도면의 간단한 설명

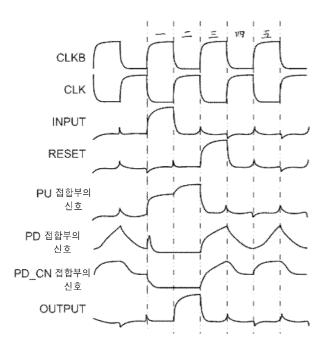

- [0023] 도 1a은, 종래 기술에 관한 쉬프트 레지스터 유닛의 구성 개략도.

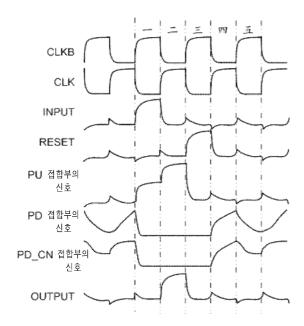

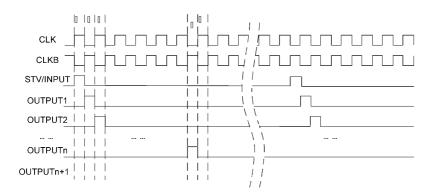

- 도 1b는, 도 1a에 도시한 쉬프트 레지스터 유닛의 시퀀스도.

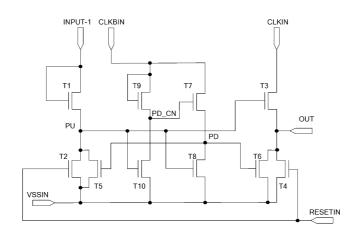

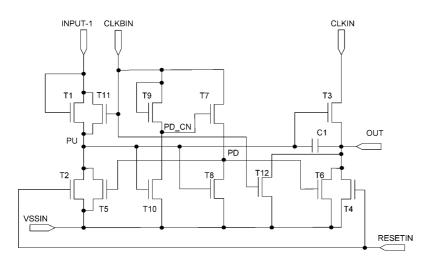

- 도 2a는, 본 발명에 관한 쉬프트 레지스터 유닛의 구성 개략도.

- 도 2b는, 도 2a에 도시한 쉬프트 레지스터 유닛의 시퀀스도.

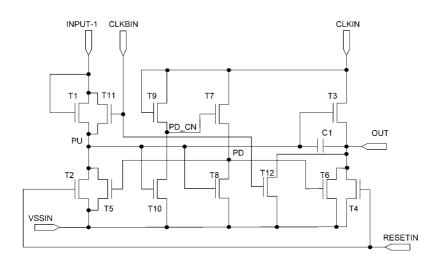

- 도 3a는, 본 발명에 관한 쉬프트 레지스터 유닛의 실시예 1의 구성 개략도.

- 도 3b는, 도 3a에 도시한 쉬프트 레지스터 유닛의 시퀀스도.

- 도 4는, 본 발명에 관한 쉬프트 레지스터 유닛의 실시예 2의 구성 개략도.

- 도 5는, 본 발명에 관한 쉬프트 레지스터 유닛의 실시예 3의 구성 개략도.

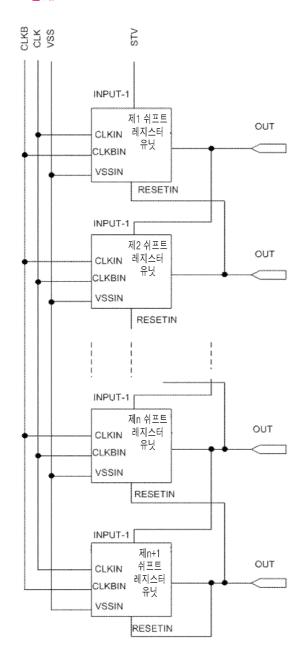

- 도 6a는, 본 발명에 관한 액정 디스플레이의 게이트 구동 장치의 구성 개략도.

- 도 6b는, 도 6a에 도시한 액정 디스플레이의 게이트 구동 장치의 입력 출력 시퀀스도.

#### 발명을 실시하기 위한 구체적인 내용

[0024]

- 도 2a는 본 발명에 관한 쉬프트 레지스터 유닛의 구성 개략도이다. 이 쉬프트 레지스터 유닛은 10개의 박막 트 랜지스터를 포함한다. 제1 박막 트랜지스터(T1)의 게이트와 드레인은 함께 신호 입력 단자(INPUT-1)에 접속되고, 제2 박막 트랜지스터(T2)의 드레인은 제1 박막 트랜지스터(T1)의 소스에 접속되고, 제2 박막 트랜지 스터(T2)의 게이트는 리셋 신호 입력 단자(RESETIN)에 접속되고, 제2 박막 트랜지스터(T2)의 소스는 저전압 신 호 입력 단자(VSSIN)에 접속되고, 제3 박막 트랜지스터(T3)의 드레인은 제1 클럭 신호 입력 단자(CLKIN)에 접속 되고, 제3 박막 트랜지스터(T3)의 게이트는 제1 박막 트랜지스터(T1)의 소스에 접속되고, 제3 박막 트랜지스터 (T3)의 소스는 신호 출력 단자(OUT)에 접속되고, 제4 박막 트랜지스터(T4)의 게이트는 리셋 신호 입력 단자 (RESETIN)에 접속되고, 제4 박막 트랜지스터(T4)의 드레인은 제3 박막 트랜지스터(T3)의 소스에 접속되고, 제4 박막 트랜지스터(T4)의 소스는 저전압 신호 입력 단자(VSSIN)에 접속되고, 제5 박막 트랜지스터(T5)의 드레인은 제1 박막 트랜지스터(T1)의 소스에 접속되고, 제5 박막 트랜지스터(T5)의 소스는 저전압 신호 입력 단자(VSSI N)에 접속되고, 제6 박막 트랜지스터(T6)의 드레인은 제3 박막 트랜지스터(T3)의 소스에 접속되고, 제6 박막 트 랜지스터(T6)의 소스는 저전압 신호 입력 단자(VSSIN)에 접속되고, 제7 박막 트랜지스터(T7)의 드레인은 제2 클 럭 신호 입력 단자(CLKBIN)에 접속되고, 제7 박막 트랜지스터(T7)의 소스는 각각 제5 박막 트랜지스터(T5)의 게 이트와 제6 박막 트랜지스터(T6)의 게이트에 접속되고, 제8 박막 트랜지스터(T8)의 게이트는 제1 박막 트랜지스 터(T1)의 소스에 접속되고, 제8 박막 트랜지스터(T8)의 드레인은 제7 박막 트랜지스터(T7)의 소스에 접속되고, 제8 박막 트랜지스터(T8)의 소스는 저전압 신호 입력 단자(VSSIN)에 접속되고, 제9 박막 트랜지스터(T9)의 게이 트와 드레인은 모두 제2 클럭 신호 입력 단자(CLKBIN)에 접속되고, 제9 박막 트랜지스터(T9)의 소스는 제7 박막 트랜지스터(T7)의 게이트에 접속되고, 제10 박막 트랜지스터(T10)의 게이트는 제1 박막 트랜지스터(T1)의 소스 에 접속되고, 제10 박막 트랜지스터(T10)의 드레인은 제9 박막 트랜지스터(T9)의 소스에 접속되고, 제10 박막 트랜지스터(T10)의 소스는 저전압 신호 입력 단자(VSSIN)에 접속되어 있다. 제1 박막 트랜지스터(T1)의 소스와 제2 박막 트랜지스터(T2)의 드레인과 제5 박막 트랜지스터(T5)의 드레인과 제10 박막 트랜지스터(T10)의 게이트 와 제8 박막 트랜지스터(T8)의 게이트와 제3 박막 트랜지스터(T3)의 게이트의 집합처는 PU접합부이고, 제7 박막 트랜지스터(T7)의 소스와 제8 박막 트랜지스터(T8)의 드레인과 제5 박막 트랜지스터(T5)의 게이트와 제6 박막 트랜지스터(T6)의 게이트와의 집합처는 PD접합부이고, 제9 박막 트랜지스터(T9)의 소스와 제10 박막 트랜지스터 (T10)의 드레인과 제7 박막 트랜지스터(T7)의 게이트의 집합처는 PD\_CN접합부이다.

- [0025] 본 발명에 기재된 쉬프트 레지스터 유닛과 도 1a에 도시한 쉬프트 레지스터 유닛의 구성상 구별은, 본 발명이

제공한 쉬프트 레지스터 유닛에서는 제9 박막 트랜지스터(T9)의 게이트 및 드레인과 제7 박막 트랜지스터(T7)의 드레인은 모두 제2 클럭 신호 입력 단자(CLKBIN)에 접속되어 있는데, 도 la에서는 제9 박막 트랜지스터(T9)의 게이트 및 드레인과 제7 박막 트랜지스터(T7)의 드레인이 모두 제1 클럭 신호 입력 단자(CLKIN)에 접속되고, 또한 본 발명이 제공한 쉬프트 레지스터 유닛에서 제11 박막 트랜지스터(T11)와 제12 박막 트랜지스터(T12)와 콘덴서(C1)가 생략되어 있다.

- [0026] 도 2b는 도 2a에 도시한 쉬프트 레지스터 유닛의 시퀀스도이다. 도 2a에서, 신호 입력 단자(INPUT-1)에 신호 (INPUT)가 입력되고, 제1 클럭 신호 입력 단자(CLKIN)에는 제1 클럭 신호(CLK)가 입력되고, 제2 클럭 신호 입력 단자(CLKBIN)에는 제2 클럭 신호(CLKB)가 입력되고, 저전압 신호 입력 단자(VSSIN)에는 저전압 신호(VSS)가 입력되고, 리셋 신호 입력 단자(RESETIN)에는 리셋 신호(RESET)가 입력되고, 신호 출력 단자(OUT)에서 게이트 구동 신호(OUTPUT)가 출력된다. 도 2b에서 저전압 신호(VSS)는 도시되지 않는다. 저전압 신호(VSS)는 쭉 로우 레벨로 유지되어 있는 신호이다.

- [0027] 이하, 본 발명의 쉬프트 레지스터 유닛의 동작 원리를, 도 2a와 도 2b를 결합하여 설명하기로 한다.

- [0028] 도 2b에 도시한 시퀀스도의 일부를 선택하여 5개의 단계로 나눈다. 제1 단계에서, 신호 입력 단자(INPUT-1)에 입력된 신호(INPUT)는 하이 레벨이고, 리셋 신호 입력 단자(RESETIN)에 입력된 리셋 신호(RESET)는 로우 레벨이 고, 제1 박막 트랜지스터(T1)는 온된다. PU접합부에서의 신호는 하이 레벨이고, 제3 박막 트랜지스터(T3)와 제8 박막 트랜지스터(T8)와 제10 박막 트랜지스터(T10)는 온된다. 제1 클럭 신호 입력 단자(CLKIN)에 입력된 제1 클 럭 신호(CLK)는 로우 레벨이고, 제2 클럭 신호 입력 단자(CLKBIN)에 입력된 제2 클럭 신호(CLKB)는 하이 레벨이 고, 제7 박막 트랜지스터(T7)와 제9 박막 트랜지스터(T9)는 온된다. 제7 박막 트랜지스터(T7)의 채널 길이에 대 한 폭의 비(width to length ratio)와 제8 박막 트랜지스터(T8)의 채널 길이에 대한 폭의 비간의 비례, 및 제9 박막 트랜지스터(T9)의 채널 길이에 대한 폭의 비와 제10 박막 트랜지스터(T10)의 채널 길이에 대한 폭의 비간 의 비례를 마련함으로써 PD접합부에서의 신호가 로우 레벨이 되도록 할 수 있다. 이렇게 해서 제5 박막 트랜지 스터(T5)와 제6 박막 트랜지스터(T6)는 오프된다. 제7 박막 트랜지스터(T7)의 채널 길이에 대한 폭의 비와 제8 박막 트랜지스터(T8)의 채널 길이에 대한 폭의 비간의 비례는  $1/1 \sim 1/50$ 이어도 좋다. 예컨대, 당해 비례는 1/5이어도 좋다. 제9 박막 트랜지스터(T9)의 채널 길이에 대한 폭의 비와 제10 박막 트랜지스터(T10)의 채널 길이 에 대한 폭의 비간의 비례는  $1/1\sim1/50$ 이어도 좋다. 예컨대, 당해 비례는 1/5이어도 좋다. 리셋 신호 입력 단자 (RESETIN)에 입력된 리셋 신호(RESET)는 로우 레벨이며 제2 박막 트랜지스터(T2)와 제4 박막 트랜지스터(T4)는 오프된다. 신호 출력 단자(OUT)에서 출력된 게이트 구동 신호(OUTPUT)는 로우 레벨이다.

- [0029] 제2 단계에서, 신호 입력 단자(INPUT-1)에 입력되는 신호(INPUT)는 로우 레벨이고, 리셋 신호 입력 단자 (RESETIN)에 입력되는 리셋 신호(RESET)는 로우 레벨이고, 제1 박막 트랜지스터는 오프되고 PU접합부에서의 신호는 하이 레벨로 유지됨으로써 제3 박막 트랜지스터(T3)와 제8 박막 트랜지스터(T8)와 제10 박막 트랜지스터 (T10)는 그대로 온으로 되어 있다. 제2 클럭 신호 입력 단자(CLKBIN)에 입력된 제2 클럭 신호(CLKB)는 로우 레벨이고, 제9 박막 트랜지스터(T9)는 오프된다. PD접합부에서의 신호는 로우 레벨로 유지되고, 제5 박막 트랜지스터(T5)와 제6 박막 트랜지스터(T6)는 그대로 오프로 되어 있다. 리셋 신호 입력 단자(RESETIN)에 입력된 신호 (RESET)는 로우 레벨이고, 제2 박막 트랜지스터(T2)와 제4 박막 트랜지스터(T4)는 그대로 오프로 되어 있다. 제1 클럭 신호 입력 단자(CLKIN)에 입력된 제1 클럭 신호(CLK)는 하이 레벨이고 또한 제3 박막 트랜지스터는 그대로 온되기 때문에 신호 출력 단자(OUT)에서 출력된 게이트 구동 신호(OUTPUT)는 하이 레벨이 된다.

- [0030] 제3 단계에서, 신호 입력 단자(INPUT-1)에 입력된 신호(INPUT)는 로우 레벨이고, 리셋 신호 입력 단자(RESETI N)에 입력된 리셋 신호(RESET)는 하이 레벨이고, 제2 박막 트랜지스터(T2)와 제4 박막 트랜지스터(T4)는 온된다. 제2 박막 트랜지스터(T2)의 소스는 저전압 신호 입력 단자(VSSIN)에 접속됨으로써 PU접합부는 로우 레벨로 풀다운되고 제3 박막 트랜지스터(T3)와 제8 박막 트랜지스터(T8)와 제10 박막 트랜지스터(T10)는 오프된다. 제2 클럭 신호 입력 단자(CLKBIN)에 입력된 제2 클럭 신호(CLKB)는 하이 레벨이고, 제7 박막 트랜지스터(T7)와 제9 박막 트랜지스터(T9)는 온되어 PD접합부는 하이 레벨이고, PD\_CN접합부는 하이 레벨이다. 이렇게 해서, 제5 박막 트랜지스터(T5)와 제6 박막 트랜지스터(T6)는 온된다. 제1 클럭 신호 입력 단자(CLKIN)에 입력된 제1 클럭 신호(CLK)는 로우 레벨이고, 또한 제4 박막 트랜지스터(T4)는 온되기 때문에 신호 출력 단자(OUT)에서 출력된 게이트 구동 신호(OUTPUT)는 로우 레벨로 풀다운된다.

- [0031] 제4 단계에서, 신호 입력 단자(INPUT-1)에 입력된 신호(INPUT)는 로우 레벨이고, 리셋 신호 입력 단자(RESETI N)에 입력된 리셋 신호(RESET)는 로우 레벨이고, 제1 박막 트랜지스터(T1)은 오프되어 PU접합부에서의 신호는 로우 레벨로 유지되고, 제8 박막 트랜지스터(T8)와 제10 박막 트랜지스터(T10)는 오프된다. 제2 클릭 신호 입력

단자(CLKBIN)에 입력된 제2 클럭 신호(CLKB)는 로우 레벨이고, 제9 박막 트랜지스터(T9)는 오프된다. 제3 단계의 PD\_CN접합부에서의 신호는 하이 레벨이고, 제4 단계에서 제9 박막 트랜지스터(T9)와 제10 박막 트랜지스터(T10)는 오프되기 때문에 PD\_CN접합부에서의 신호는 하이 레벨로 유지되고, 이렇게 해서 제7 박막 트랜지스터(T7)는 온된다. 제7 박막 트랜지스터(T7)의 드레인은 제2 클럭 신호 입력 단자(CLKBIN)에 접속되고, 제4 단계의제2 클럭 신호(CLKB)는 로우 레벨이고, 제3 단계의 PD접합부에서의 신호는 하이 레벨이기 때문에 제4 단계에서PD접합부에서의 신호는 하이 레벨에서 로우 레벨로 점차 줄어들고 제5 박막 트랜지스터(T5)와 제6 박막 트랜지스터(T6)는 점차 온에서 오프로 변화된다. 리셋 신호 입력 단자(RESETIN)에 입력된 리셋 신호(RESET)는 로우 레벨이며, 제2 박막 트랜지스터(T2)와 제4 박막 트랜지스터(T4)가 오프되어 신호 출력 단자(OUT)에서 출력된 게이트 구동 신호(OUTPUT)는 로우 레벨로 유지된다.

- [0032] 제5 단계에서, 신호 입력 단자(INPUT-1)에 입력된 신호(INPUT)는 로우 레벨이고, 리셋 신호 입력 단자(RESETI N)에 입력된 리셋 신호(RESET)는 로우 레벨이고, 제1 박막 트랜지스터(T1)은 오프되어 PU접합부에서의 신호는 로우 레벨이고, 제8 박막 트랜지스터(T8)와 제10 박막 트랜지스터(T10)는 오프된다. 제2 클럭 신호 입력 단자(CLKBIN)에 입력된 제2 클럭 신호(CLKB)는 하이 레벨이고, 제7 박막 트랜지스터(T7)와 제9 박막 트랜지스터(T9)는 온되어 PD접합부에서의 신호는 로우 레벨에서 하이 레벨로 점차 증가된다. 이렇게 해서 제5 박막 트랜지스터(T5)와 제6 박막 트랜지스터(T6)는 오프에서 온으로 점차 변화된다. 리셋 신호 입력 단자(RESETIN)에 입력된 리셋 신호(RESET)는 로우 레벨이고, 제2 박막 트랜지스터(T2)와 제4 박막 트랜지스터(T4)는 오프되어 신호 출력 단자(OUT)에서 출력된 게이트 구동 신호(OUTPUT)는 로우 레벨로 유지된다.

- [0033] 이 5개의 단계에서, 제1 단계의 신호 입력 단자(INPUT-1)에 입력된 신호(INPUT)는 하이 레벨이고, 제2 단계의 신호 출력 단자(OUT)에서 출력된 게이트 구동 신호(OUTPUT)는 하이 레벨이며 1회의 쉬프트가 완성된다. 제3 단계의 리셋 신호 입력 단자(RESETIN)에 입력된 리셋 신호(RESET)는 하이 레벨로서 리셋의 조작이 완성된다. 그래서 제1,2,3 단계를 쉬프트 레지스터 유닛의 동작 기간에 정의할 수 있다. 제4,5 단계에서 신호 입력 단자(INPUT-1)에 입력된 신호(INPUT)와 리셋 신호 입력 단자(RESETIN)에 입력된 리셋 신호(RESET)는 모두 로우 레벨이므로 제4,5 단계를 쉬프트 레지스터 유닛의 비동작 기간에 정의할 수 있다. 도 2b에, 쉬프트 레지스터 유닛의일부 시퀀스도만이 도시되어 있다. 액정 디스플레이가 1프레임의 화상을 표시할 때마다 한 행의 액정 화소를 제어하는 쉬프트 레지스터 유닛은 하나의 하이 레벨 신호를 출력하고, 신호 입력 단자(INPUT-1)에 입력된 신호(INPUT)와 리셋 신호 입력 단자(RESETIN)에 입력된 리셋 신호(RESET)와 제1 클럭 신호 입력 단자(CLKIN)에 입력된 전체 클럭 신호(INPUT)와 리셋 신호 입력 단자(DINPUT)와 리셋 신호 입력 단자(CLKIN)에 입력된 전치는 시간 중 제1,2,3 단계 이외의 시간에, 신호 입력 단자(INPUT-1)에 입력된 신호(INPUT)와 리셋 신호 입력 단자(RESETIN)에 입력된 리셋 신호(RESET)와 제1 클럭 신호(INPUT)와 리셋 신호 입력 단자(RESETIN)에 입력된 리셋 신호(RESET)와 제1 클럭 신호(INPUT)와 리셋 신호 입력 단자(RESETIN)에 입력된 리셋 신호(RESET)와 제1 클럭 신호(INPUT)와 리셋 신호 입력 단자(RESETIN)에 입력된 레게 클럭 신호(CLK)는 모두 제4와 제5 단계와 같은 입력 시퀀스를 반복한다.

- [0034] 5개의 단계에 대해 상세한 설명에서 설명한 첫처럼 제2 단계에서 제1 클릭 신호(CLK)와 PU접합부에서 출력된 신호는 동시에 하이 레벨이 되는데, 제9 박막 트랜지스터(T9)의 게이트는 제2 클릭 신호 입력 단자(CLKBIN)에 접속되기 때문에 제9 박막 트랜지스터(T9)는 오프된다. 제7 박막 트랜지스터(T7)의 게이트는 PD\_CN접합부에 접속되는데, PD\_CN접합부에서의 신호는 제2 단계에서도 로우 레벨이므로 제7 박막 트랜지스터(T7)는 오프된다. 제8 박막 트랜지스터(T8)와 제10 박막 트랜지스터(T10)는 제2 단계에서 온되어 제8 박막 트랜지스터(T8)의 소스와제10 박막 트랜지스터(T10)의 소스는 모두 저전압 신호 입력 단자(VSSIN)에 접속되기 때문에 제8 박막 트랜지스터(T8)와 제10 박막 트랜지스터(T10)의 소스는 로우 레벨이다. 제2 단계에서, 제2 클릭 신호(CLKB)는 로우 레벨이고, 그리고 제9 박막 트랜지스터(T9)의 드레인과 제10 박막 트랜지스터(T10)의 소스는 모두 로우 레벨이 되기때문에 제9 박막 트랜지스터(T9)와 제10 박막 트랜지스터(T10)에서 누설 전류가 생기지 않는다. 제7 박막 트랜지스터(T7)와 제8 박막 트랜지스터(T8)에서도 누설 전류가 생기지 않는다.

- [0035] 도 1a에 도시한 종래 기술의 쉬프트 레지스터 유닛에 비해 본 발명이 제공한 쉬프트 레지스터 유닛에서는 제7 박막 트랜지스터의 드레인 및 제9 박막 트랜지스터의 드레인과 게이트가 모두 제2 클럭 신호 입력 단자(CLKBI N)에 접속됨으로써 제2 단계에서 제7 박막 트랜지스터와 제8 박막 트랜지스터와 제9 박막 트랜지스터와 제10 박막 트랜지스터에서 누설 전류가 생기는 것을 방지할 수 있기 때문에 쉬프트 레지스터 유닛의 소비전력을 줄이고 이 쉬프트·레지스터 유닛을 사용한 액정 디스플레이의 소비전력을 줄일 수 있다. 또 본 발명이 제공한 쉬프트 레지스터 유닛은 제11 박막 트랜지스터(T11)와 제12 박막 트랜지스터(T12)와 콘텐서(C1)가 감소되기 때문에 쉬프트 레지스터 유닛의 구성이 단순해져 쉬프트 레지스터 유닛의 면적이 줄어든다.

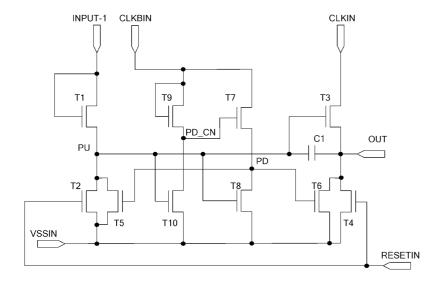

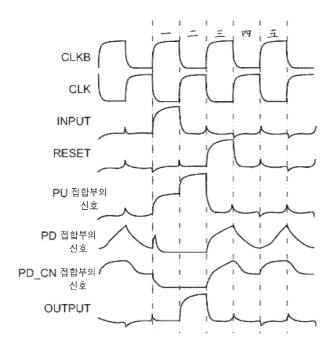

- [0036] 도 3a는 본 발명의 쉬프트 레지스터 유닛의 실시예 1의 구성 개략도이다. 도 3b는 도 3a에 도시한 쉬프트 레지

스터 유닛의 시퀀스도이다. 도 3a에 도시한 쉬프트 레지스터 유닛은 도 2a에 도시한 쉬프트 레지스터 유닛을 토대로 하여 양단이 각각 제3 박막 트랜지스터(T3)의 게이트와 신호 출력 단자(OUT)에 접속되어 있는 하나의 콘덴서(C1)를 추가하였다. 도 3b에 도시한 시퀀스도가 도 2b에 도시한 시퀀스도에 대해 구별되는 것은, 제2 단계에서 도 3b의 PU접합부에서의 신호의 레벨이, 콘덴서(C1)의 커플링 작용에 의해 도 2b의 것보다 높다는 것이다.

- [0037] 도 3a에서의 쉬프트 레지스터 유닛은 콘덴서(C1)가 추가되므로 쉬프트 레지스터 유닛의 노이즈 제거 능력을 강화할 수 있기 때문에 쉬프트 레지스터의 동작 안정화를 강화할 수 있다. 콘덴서(C1)는 PU접합부의 총용량을 증가시켜 제3 트랜지스터(T3)의 드레인의 기생 용량(Cgd3)이 PU접합부에서 차지하는 비중을 줄이기 때문에 제1 클릭 신호 입력 단자(CLKIN)가 기생 용량(Cgd3)을 통해 PU접합부에 커플링되는 노이즈를 줄여 간접적으로 신호 출력 단자(OUT)에 커플링되는 노이즈도 저감되는 반면, 제3 박막 트랜지스터(T3)의 누설 전류가 대응적으로 줄어들어 신호 출력 단자(OUT)의 노이즈가 더욱 줄어든다.

- [0038] 도 4는 본 발명의 쉬프트 레지스터 유닛의 실시예 2의 구성 개략도이다. 도 4에 도시한 쉬프트 레지스터 유닛의 시퀀스도는 도 3b와 동일하다. 이 실시예에서는, 도 3a에 도시한 쉬프트 레지스터 유닛을 토대로 하여 제12 박 막 트랜지스터(T12)가 추가되어 있다. 제12 박막 트랜지스터(T12)는 소스가 저전압 신호 입력 단자(VSSIN)에 접 속되고, 드레인이 신호 출력 단자(OUT)에 접속되고, 게이트가 제2 클럭 신호 입력 단자(CLKBIN)에 접속된다. 제 2 클럭 신호(CLKB)가 하이 레벨일 때에 제12 박막 트랜지스터(T12)는 신호 출력 단자(OUT)에서 출력된 게이트 구동 신호(OUT)의 레벨을 풀다운할 수 있고, 또한 쉬프트 레지스터 유닛의 노이즈 제거 능력을 향상시킨다.

- [0039] 도 5는 본 발명의 쉬프트 레지스터 유닛의 실시예 3의 구성 개략도이다. 도 5에 도시한 쉬프트 레지스터 유닛의 시퀀스도는 도 3b와 동일하다. 이 실시예에서는, 도 4에 도시한 쉬프트 레지스터 유닛을 토대로 하여 제11 박막 트랜지스터(T11)가 추가되어 있다. 제11 박막 트랜지스터(T11)는 게이트가 제2 클럭 신호 입력 단자(CLKBIN)에 접속되고, 드레인이 신호 입력 단자(INPUT-1)에 접속되고, 소스가 PU접합부에 접속된다. 이 실시예에서는, 제1 단계에서 제2 클럭 신호(CLKB)가 하이 레벨일 때에 제11 박막 트랜지스터(T11)는 온된다. 신호 입력 단자(INPUT-1)에 입력된 신호(INPUT)가 하이 레벨이고, 제11 박막 트랜지스터(T11)의 소스가 하이 레벨이므로 제11 박막 트랜지스터(T11)의 추가로 PU접합부에서 출력된 신호의 레벨의 상승 시간을 줄일 수 있고, PU접합부에서의 신호의 상승이 급격해지기 때문에 신호 출력 단자(OUT)가 출력한 게이트 구동 신호의 상승 시간을 줄인다.

- [0040] 도 5에 도시한 쉬프트 레지스터 유닛 및 도 5에 도시한 쉬프트 레지스터 유닛의 시퀀스도를 각각 도 1a 및 도 1b와 비교하면 알 수 있듯이, 도 1a에 도시한 쉬프트 레지스터 유닛 및 도 1b에 도시한 시퀀스도에서는, 제4 단계에서 제1 클럭 신호(CLK)의 상승으로 제1 클럭 신호(CLK)가 게이트 구동 신호(OUTPUT)에 커플링되는 노이즈가가장 크다. 이 때 PD접합부가 로우 레벨이고 제6 박막 트랜지스터와 제5 박막 트랜지스터는 모두 오프되기 때문에 게이트 구동 신호(OUTPUT)를 로우 레벨로 풀다운할 수 없어 노이즈를 제거하는 데 불리하다. 본 발명의 도 5에 도시한 실시예에서는, 제4 단계에서 제1 클럭 신호(CLK)의 상승으로 PD접합부에서의 신호가 하이 레벨이고, 제5 박막 트랜지스터와 제6 박막 트랜지스터는 온되기 때문에 게이트 구동 신호(OUTPUT)의 전압을 풀다운할 수 있어 제1 클럭 신호(CLK)가 커플링됨에 따른 노이즈를 제거할 수 있다.

- [0041] 도 6a는 본 발명 액정 디스플레이의 게이트 구동 장치의 구성 개략도이다. 도 6b는 도 6a에 도시한 액정 디스플레이의 게이트 구동 장치의 입력 출력 시퀀스도이다. STV는 프레임 개시 신호로서, 제1 쉬프트 레지스터 유닛의 신호 입력 단자(INPUT-1)에만 입력된다. 저전압 신호(VSS)(도 6b에 VSS가 도시되지 않는다)는 각 쉬프트 레지스터 유닛의 저전압 신호 입력 단자(VSSIN)에 입력된다. 홀수째의 쉬프트 레지스터 유닛의 제1 클럭 신호 입력 단자(CLKIN)에 제1 클럭 신호(CLKB)가 입력되고, 제2 클럭 신호 입력 단자(CLKIN)에 제2 클럭 신호(CLKB)가 입력되고, 제2 클럭 신호 입력 단자(CLKIN)에 제2 클럭 신호(CLKB)가 입력되고, 제2 클럭 신호 입력 단자(CLKBIN)에 제1 클럭 신호(CLKB)가 입력된다. 제1 쉬프트 레지스터 유닛과 최후의 쉬프트 레지스터 유닛 이외의 각 쉬프트 레지스터 유닛의 신호 출력 단자는 모두 자신과 인접한 앞의 쉬프트 레지스터 유닛의 리셋 신호 입력 단자(RETSETIN) 및 자신과 인접한 다음 쉬프트 레지스터의 신호 입력 단자(INPUT-1)에 접속되고, 제1 쉬프트 레지스터 유닛의 신호 출력 단자(OUT)는 제2 쉬프트 레지스터 유닛의 신호 입력 단자(INPUT-1)에만 접속되고, 최후의 쉬프트 레지스터 유닛(도 6a에 도시한 제n+1 쉬프트 레지스터 유닛)의 출력 단자(OUT)는 각각 자신과 인접한 제n 쉬프트 레지스터 유닛의 리셋 신호 입력 단자(RETSETIN), 그 자신의 리셋 신호 입력 단자(RETSETIN)에 접속된다.

- [0042] 박막 트랜지스터 액정 디스플레이는 순차 주사 방식을 사용하여 동일 행에서의 액정 화소와 직렬된 박막 트랜지스터의 게이트가 모두 동일한 쉬프트 레지스터 유닛에 접속되기 때문에 액정 디스플레이의 게이트 구동 장치에서의 쉬프트 레지스터 유닛은 동일 행에서의 전체 박막 트랜지스터의 온/오프를 제어할 수 있다. 도 6a에서의

액정 디스플레이의 게이트 구동 장치의 구체적인 원리는 이하와 같다. 즉, 액정 디스플레이 패널에서 n행의 액정 화소가 있으면, 도 6b에 도시한 시퀀스도를 참조하여 제1 단계에서 프레임 개시 신호가 제1 쉬프트 레지스터 유닛의 신호 합력 단자(INPUT-1)에 입력된다. 제2 단계에서 제1 쉬프트 레지스터 유닛의 신호 출력 단자(OUT)가하이 레벨 신호(OUTPUT1)를 출력함과 동시에 이 하이 레벨 신호(OUTPUT1)는 제2 쉬프트 레지스터 유닛의 신호 압력 단자(INPUT-1)에 입력된다. 제3 단계에서 제2 쉬프트 레지스터 유닛의 신호 출력 단자(OUT)가 하이 레벨 신호(OUTPUT2)를 출력하다. 그 후에 제2,3단계의 원리와 마찬가지로 각 쉬프트 레지스터 유닛은 순차적으로 하이 레벨 신호를 출력하여 이 쉬프트 레지스터 유닛에 접속되는 동일 행의 박막 트랜지스터의 온을 제어한다. 제4 단계에서 제n 쉬프트 레지스터 유닛이 하이 레벨 신호(OUTPUTn)를 출력함과 동시에 제n 쉬프트 레지스터 유닛이 출력한 하이 레벨 신호(OUTPUTn)는 제n+1 쉬프트 레지스터 유닛의 신호 입력 단자(INPUT-1)의 입력 신호로한다. 제5 단계에서, 제n+1 쉬프트 레지스터 유닛은 하이 레벨 신호(OUTPUTn+1)를 출력하고, 이 제n+1 쉬프트 레지스터 유닛은 하이 레벨 신호(OUTPUTn+1)를 출력하고, 이 제n+1 쉬프트 레지스터 유닛은 1행의 액정 화소를 제어하는 박막 트랜지스터를 구동하지 않고, 그것이 출력하는 하이 레벨 신호(OUTPUTn+1)는 제n 쉬프트 레지스터 유닛과 그 자신의 리셋 신호로만 사용된다. 도 6a에서의 각 쉬프트 레지스터 유닛은 도 2a, 도 3a, 도 4 또는 도 5에 도시한 쉬프트 레지스터 유닛이어도 좋다.

- [0043] 도 6a에서는, 최후의 쉬프트 레지스터 유닛, 즉 제n+1 쉬프트 레지스터 유닛은 부하의 구동에 사용되지 않아 여분의 쉬프트 레지스터 유닛으로 간주될 수 있다. 도 6a에 도시한 게이트 구동 장치에서, 하나의 여분의 쉬프트 레지스터 유닛만을 포함한다. 실제로는 여러 개의 여분의 쉬프트 레지스터 유닛을 더 포함할 수 있다. 각 여분의 쉬프트 레지스터 유닛을 조합하여 액정 디스플레이의 게이트 구동 장치가 더욱 신뢰성 있게 리셋되는 것을 보증할 수 있다.

- [0044] 본 발명의 실시예에 기재된 쉬프트 레지스터 유닛 및 액정 디스플레이의 게이트 구동 장치는, 제9 박막 트랜지스터의 드레인과 게이트 및 제7 박막 트랜지스터의 드레인이 제2 클럭 신호 입력 단자(CLKBIN)에 접속되고, 게이트 구동 신호(OUTPUT)가 하이 레벨인 기간 동안에는 제7 박막 트랜지스터와 제8 박막 트랜지스터와 제9 박막트랜지스터와 제10 박막 트랜지스터에서 누설 전류가 생기지 않기 때문에 쉬프트 레지스터 유닛의 소비전력을 줄일 수 있어 이 쉬프트 레지스터 유닛을 사용한 액정 디스플레이의 소비전력을 줄일 수 있다.

- [0045] 마지막으로 이하와 같이 설명할 필요가 있다. 즉, 상기 실시예는 본 발명의 기술안을 설명하는 데 사용되는 것일 뿐 그것을 제한하지는 않는다. 바람직한 실시예를 참조하여 본 발명을 상세히 설명하였으나, 당업자는 여전히 본 발명의 기술안을 보정하거나 또는 동등하게 대체할 수 있으며, 이 보정 또는 동등한 대체가 보정 후의 기술안을 본 발명의 기술안의 주지와 범위로부터 이탈시키지 않는다는 것을 이해해야 한다.

#### 도면

#### 도면1a

# 도면1b

# 도면2a

# 도면2b

# 도면3a

# 도면3b

# 도면4

# 도면5

# 도면6a

# 도면6b

| 专利名称(译)        | 移位寄存器单元和液晶显示器的栅极驱动装置                                      |         |            |  |

|----------------|-----------------------------------------------------------|---------|------------|--|

| 公开(公告)号        | KR1020110025630A                                          | 公开(公告)日 | 2011-03-10 |  |

| 申请号            | KR1020100086694                                           | 申请日     | 2010-09-03 |  |

| [标]申请(专利权)人(译) | 北京京东方光电科技有限公司                                             |         |            |  |

| 申请(专利权)人(译)    | 北京京东方光电科技有限公司                                             |         |            |  |

| 当前申请(专利权)人(译)  | 北京京东方光电科技有限公司                                             |         |            |  |

| [标]发明人         | SHANG GUANGLIANG<br>샹광리앙<br>HAN SEUNG WOO<br>한승우          |         |            |  |

| 发明人            | 샹광리앙<br>한승우                                               |         |            |  |

| IPC分类号         | G09G3/36 G11C19/28                                        |         |            |  |

| CPC分类号         | G11C19/28 G11C19/184 G09G3/3674 G09G2310/0286 G09G2310/08 |         |            |  |

| 优先权            | 200910092003.1 2009-09-04 CN                              |         |            |  |

| 其他公开文献         | KR101195440B1                                             |         |            |  |

| 外部链接           | Espacenet                                                 |         |            |  |

|                |                                                           |         |            |  |

# 摘要(译)

本发明公开了一种移位寄存器单元和液晶显示器的栅极驱动装置。在该移位寄存器单元中,第七薄膜晶体管,第八薄膜晶体管,第九薄膜晶体管和第十薄膜晶体管被布置成使得移位寄存器单元基于根据现有技术的十二个晶体管和一个电容器的配置输出高电平信号。第七薄膜晶体管的漏极和第九薄膜晶体管的栅极和漏极连接到第二时钟信号的输入端,以便在不引起漏电流的情况下降低移位寄存器单元的功耗。