(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2016-0083345

(43) 공개일자 2016년07월12일

(51) 국제특허분류(Int. Cl.)

**G02F 1/1362** (2006.01)

(21) 출원번호 10-2014-0194300

(22) 출원일자 2014년12월30일

심사청구일자 없음

(71) 출원인

**엘지디스플레이 주식회사**

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

**최성옥**

경상북도 칠곡군 석적읍 북중리3길 70 110동 80

3호 (중리, 부영아파트)

**송종훈**

광주광역시 북구 천지인로173번길 22 104동 150

7호 (문흥동, 광명아파트)

(74) 대리인

**특허법인네이트**

전체 청구항 수 : 총 10 항

(54) 발명의 명칭 **액정표시장치용 어레이 기판**

### (57) 요 약

본 발명은 표시 불량을 방지할 수 있는 액정표시장치용 어레이 기판을 제공하기 위하여, 기판 상의 각 화소영역 경계에 배치되는 제1 및 제2공통배선과 상기 제1 및 제2공통배선 상부 및 상기 기판 전면에 배치되는 게이트 절연막과 상기 게이트 절연막 상부에 상기 제1공통배선과 중첩되며 배치되는 데이터 배선과 상기 게이트 절연막 상부에 상기 제1공통배선과 중첩되고, 상기 데이터 배선과 이격되는 양단에 각각 배치되는 제1 및 제2쇼팅바와 상기 데이터 배선과 상기 제1 및 제2쇼팅바 상부에 배치되는 보호과 상기 보호층 상부에 상기 제1 및 제2공통배선을 경계로 각각 일정 간격 이격되며, 상기 제1 또는 제2공통배선과 각각 일부 중첩하며 배치되는 제1 내지 제3화소전극을 포함하는 액정표시장치용 어레이 기판을 제공한다.

### 대 표 도 - 도5

## 명세서

### 청구범위

#### 청구항 1

기판 상의 각 화소영역 경계에 배치되는 제1 및 제2공통배선;

상기 제1 및 제2공통배선 상부 및 상기 기판 전면에 배치되는 게이트 절연막;

상기 게이트 절연막 상부에 상기 제1공통배선과 중첩되며 배치되는 데이터 배선;

상기 게이트 절연막 상부에 상기 제1공통배선과 중첩되고, 상기 데이터 배선과 이격되는 양단에 각각 배치되는 제1 및 제2쇼팅바;

상기 데이터 배선과 상기 제1 및 제2쇼팅바 상부에 배치되는 보호층; 및

상기 보호층 상부에 상기 제1 및 제2공통배선을 경계로 각각 일정 간격 이격되며, 상기 제1 또는 제2공통배선과 각각 일부 중첩하며 배치되는 제1 내지 제3화소전극

을 포함하는 액정표시장치용 어레이 기판.

#### 청구항 2

제 1 항에 있어서,

상기 보호층은 상기 제1 및 제2쇼팅바 일부를 각각 노출시키는 제1 및 제2쇼팅 콘택홀을 구비하고, 상기 제1 및 제2화소전극은 상기 제1 및 제2쇼팅 콘택홀을 통해 상기 제1 및 제2쇼팅바와 각각 연결되는 액정표시장치용 어레이 기판.

#### 청구항 3

제 2 항에 있어서,

상기 게이트 절연막 상부에 상기 제2공통배선과 중첩되고 서로 일정간격 이격되며 각각 배치되는 제3 및 제4쇼팅바

를 더 포함하는 액정표시장치용 어레이 기판.

#### 청구항 4

제 3 항에 있어서,

상기 보호층은 상기 제3 및 제4쇼팅바 상부에 상기 제3 및 제4쇼팅바 일부를 각각 노출시키는 제3 및 제4쇼팅 콘택홀을 더 구비하고, 상기 제2 및 제3화소전극은 상기 제3 및 제4쇼팅 콘택홀을 통해 상기 제3 및 제4쇼팅바와 각각 연결되는 액정표시장치용 어레이 기판.

#### 청구항 5

제 4 항에 있어서,

상기 제1 및 제2공통배선을 연결하며 상기 제2화소전극과 중첩되는 제3공통배선; 및

상기 게이트 절연막 상부에 상기 제3공통배선과 중첩되며 배치되는 제5쇼팅바

를 더 포함하는 액정표시장치용 어레이 기판.

### 청구항 6

제 5 항에 있어서,

상기 보호층은 상기 제5쇼팅바 상부에 상기 제5쇼팅바 일부를 노출시키는 제5쇼팅 콘택홀을 더 구비하고, 상기 제2화소전극은 상기 제5쇼팅 콘택홀을 통해 상기 제5쇼팅바와 연결되는 액정표시장치용 어레이 기판.

### 청구항 7

제 6 항에 있어서,

상기 제1 내지 제4쇼팅바의 길이는 각각 상기 제1 및 제2공통배선과 대응되는 길이이고, 상기 제5쇼팅바의 길이는 상기 제3공통배선과 대응되는 길이인 액정표시장치용 어레이 기판.

### 청구항 8

제 7 항에 있어서,

상기 제2 및 제3쇼팅바와, 상기 제1 및 제4쇼팅바 각각은 상기 제5쇼팅바를 통해 연결된 액정표시장치용 어레이 기판.

### 청구항 9

제 8 항에 있어서,

상기 제1 내지 제5쇼팅바는 상기 데이터 배선과 동일층 및 동일물질로 이루어지는 액정표시장치용 어레이 기판.

### 청구항 10

제 9 항에 있어서,

상기 제1 및 제2쇼팅바는 상기 데이터배선과  $1\mu\text{m}$  내지  $5\mu\text{m}$  이격되는 액정표시장치용 어레이 기판.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 액정표시장치에 관한 것으로, 특히 표시 불량을 방지할 수 있는 액정표시장치용 어레이 기판에 관한 것이다.

### 배경 기술

[0002] 일반적으로 액정표시장치는 박막트랜지스터 및 화소전극을 형성하는 어레이 기판 제조 공정과 컬러필터 및 공통 전극을 형성하는 컬러필터 기판 제조 공정을 통해 각각 어레이 기판 및 컬러필터 기판을 형성하고, 이를 두 기판 사이에 액정을 개재하는 셀 공정을 거쳐 완성된다.

[0003] 구체적으로, 액정층을 사이에 두고 어레이 기판과 컬러필터 기판이 대면 합착된 구성을 갖는데, 이중 하부의 어레이 기판은 교차 배열되어 다수의 화소영역을 정의하는 복수개의 게이트 배선과 데이터 배선을 포함하며, 이들 두 배선의 교차점에는 박막트랜지스터가 구비되어 각 화소영역에 마련된 화소전극과 일대일 대응 접속되어 있

다.

[0004] 또한, 어레이 기판과 마주보는 컬러필터 기판은 게이트 배선과 데이터 배선 그리고 박막트랜지스터 등의 비표시 영역을 가리도록 각 화소영역을 포획하는 격자 형상의 블랙매트릭스가 형성되어 있으며, 이를 격자 내부에서 각 화소영역에 대응되게 순차적으로 반복 배열된 적, 녹, 청색 컬러필터층이 형성되어 있으며, 블랙매트릭스와 적, 녹, 청색 컬러필터층의 전면에 걸쳐 공통전극이 구비되어 있다.

[0005] 전술한 구성을 갖는 액정표시장치에 있어서, 최근에는 데이터 드라이브 IC의 수를 줄여 제조 원가를 저감할 수 있는 더블 레이트 드라이브(Double Rate Drive : DRD) 구조가 제안되었다.

[0006] 도 1은 일반적인 DRD구조의 액정표시장치용 어레이 기판의 표시영역 일부를 개략적으로 구성한 평면도이다.

[0007] 도면에 도시한 바와 같이, 일반적인 DRD구조의 액정표시장치용 어레이 기판(10)은 제1간격 이격되며 평행하게 일 방향으로 형성된 제1 및 2게이트 배선(53a, 53b)이 하나의 쌍을 이루며, 이러한 쌍을 이루는 제1 및 제2게이트 배선(53a, 53b)이 제2간격으로 이격되며 나란하게 다수 형성되어 있다.

[0008] 이 때, 제1간격은 제1 및 제2게이트 배선(53a, 53b)이 쇼트 되지 않을 정도의 이격 간격으로 수  $\mu\text{m}$ 정도이고, 제2간격은 하나의 화소영역의 장축크기의 간격이다.

[0009] 또한, 쌍으로 이루어진 다수의 제1 및 제2게이트 배선(53a, 53b)과 교차하여 다수의 데이터 배선(70)이 형성되어 있다.

[0010] 이때, 서로 교차하는 한 쌍의 제1 및 제2게이트 배선(53a, 53b)과 데이터 배선(70)에 의해 둘러싸인 영역은 서로 이웃한 2개의 화소영역을 이룬다.

[0011] 또한, 공통배선(56a 내지 56c)은 데이터 배선(70), 제1게이트 배선(53a), 2개의 화소영역의 경계 및 제2게이트 배선(53b)을 따라 각 화소영역을 둘러싸며 지그재그 형태로 형성됨으로써, 동일 화소라인(PL)에 대해서는 모두 연결된 형태가 되며, 게이트 배선(53)과 동일 층 및 동일 물질로 형성되어 있다.

[0012] 또한, 이웃한 화소라인(PL)의 공통배선(56a 내지 56c)끼리는 공통연결패턴(97)에 의해 연결되는데, 공통연결패턴(97)은 공통콘택홀(87)을 통해 노출된 각 공통배선(56a 내지 56c)과 접촉하며, 화소전극(93a 내지 93d)을 이루는 투명 도전성 물질로 이루어진다.

[0013] 이 때, 공통연결패턴(97)은 제1및 제2게이트 배선(53a, 53b)과 교차하여 각 화소라인(PL)에 걸쳐 형성되어 있다.

[0014] 또한, 각 화소영역에는 순차 적층된 형태로 게이트 전극(63)과 게이트 절연막(도 2의 35)과 반도체층(미도시)과 서로 이격하는 소스 및 드레인 전극(73, 76)으로 구성된 박막트랜지스터(Tr)가 구비되고 있으며, 화소전극(93a 내지 93d)은 드레인 콘택홀(85)을 통해 각각 박막트랜지스터(Tr)의 드레인 전극(76)과 접촉하며 각 화소영역 별로 형성되고 있다.

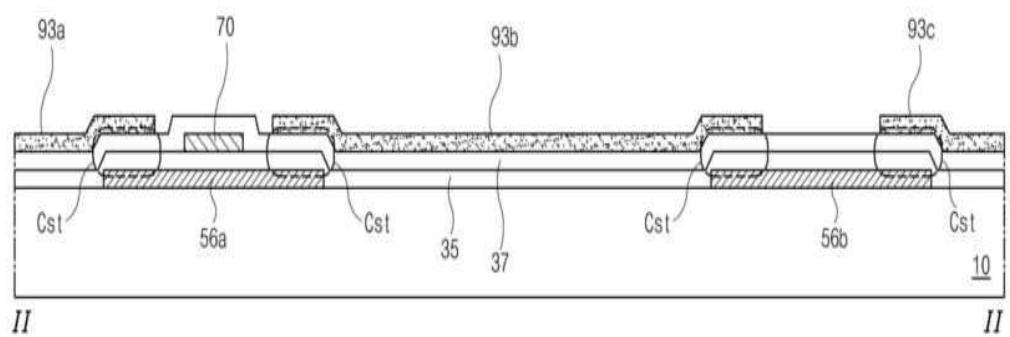

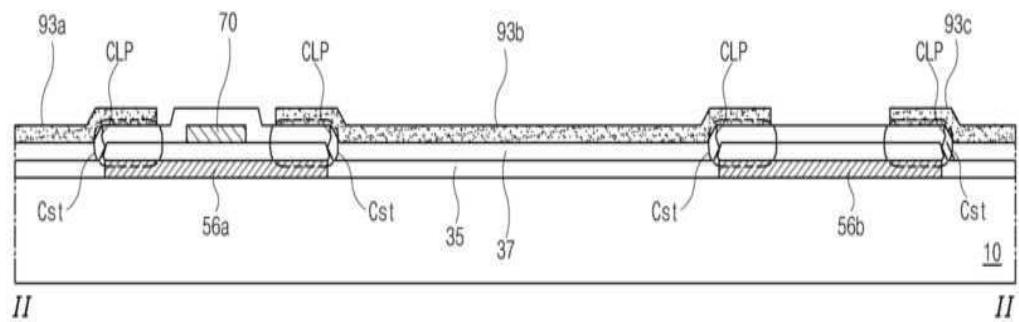

[0015] 도 2는 도 1의 II-II'를 따라 절단한 부분에 대한 단면도이고, 도 3은 도 2에서 고온 및 고전압 시 누설전류패스가 형성되는 것을 설명하기 위한 도면이다.

[0016] 도면에 도시한 바와 같이, 어레이 기판(10) 상에 하나의 화소영역 간격으로 이격되며 제1 및 제2공통배선(56a, 56b)이 배치되고, 제1 및 제2공통배선(56a, 56b) 상부 및 어레이 기판(10) 전면에 게이트 절연막(35)이 배치되고, 게이트 절연막(35) 상부에 제1공통배선(56a)과 중첩되는 데이터 배선(70)이 배치되고, 데이터 배선(70) 상부 및 어레이 기판(10) 전면에 보호층(37)이 배치되고, 보호층(37) 상부에 제1 및 제2공통배선(56a, 56b)을 경계로 각각 일정 간격 이격하며, 제1 및 제2공통배선(56a, 56b)의 일부와 각각 중첩하는 제1 내지 제3화소전극(93a 내지 93c)이 형성된다.

[0017] 이 때, 제1 및 제2공통배선(56a, 56b)과 각각 중첩되는 제1 내지 제3화소전극(93a 내지 93c)과 제1 및 제2공통배선(56a, 56b)과 이들 사이에 개재된 보호층(37) 및 게이트 절연막(35)은 각각 스토리지 커패시터(Cst)를 이룬다.

[0018] 한편, 게이트 절연막(35) 및 보호층(37) 형성 시, 제1 및 제2공통배선(56a, 56b) 양 끝단의 단차부 영역 상의 게이트 절연막(35) 및 보호층(37)의 두께는 제1 및 제2공통배선(56a, 56b) 양 끝단의 단차로 인해 타 영역보다 얇은 두께로 형성된다.

[0019] 이 때, 고온 및 고전압 시 제1 및 제2공통배선(56a, 56b)과 제1 내지 제3화소전극(93a 내지 93c) 사이에 개재되

어, 제1 및 제2공통배선(56a, 56b)과 제1 내지 제3화소전극(93a 내지 93c)을 전기적으로 절연시키는 게이트 절연막(35) 및 보호층(37)의 두께는 얇아지는데, 특히 단차부 영역의 두께는 더 얇아진 두께가 된다.

[0020] 또한, 제1 내지 제3화소전극(93a 내지 93c)과 제1 및 제2공통배선(56a, 56b) 사이에 형성되는 전계는 제1 내지 제3화소전극(93a 내지 93c)과 제1 및 제2공통배선(56a, 56b)이 중첩되는 영역 중 상대적으로 이들 사이의 거리가 짧은 단차부 영역에 집중되게 되고, 이러한 전계에 의해 누설전류가 흘러 단차부 영역의 게이트 절연막(35) 및 보호층(37)에 미세 균열이 생길 수 있다.

[0021] 또한, 미세 균열 사이로 누설전류 패스(Current leakage path : CLP)가 형성됨으로써, 제1공통배선(56a)과 제1 및 제2화소전극(93a 및 93b)이 쇼트(short)되거나, 제2공통배선(56b)과 제2 및 제3화소전극(93b, 93c)이 쇼트(short)되어 액정표시장치 구동 시 표시 불량을 일으키는 문제점이 있다.

## 발명의 내용

### 해결하려는 과제

[0022] 본 발명은 전술한 바와 같은 문제를 해결하기 위해 안출된 것으로, 고온 및 고전압 시 공통배선과 화소전극이 쇼트(short)됨으로써 발생되는 표시 불량 현상을 방지할 수 있는 액정표시장치용 어레이 기판을 제공하는 것을 그 목적으로 한다.

### 과제의 해결 수단

[0023] 전술한 바와 같은 목적을 달성하기 위하여, 기판 상의 각 화소영역 경계에 배치되는 제1 및 제2공통배선과 상기 제1 및 제2공통배선 상부 및 상기 기판 전면에 배치되는 게이트 절연막과 상기 게이트 절연막 상부에 상기 제1 공통배선과 중첩되며 배치되는 데이터 배선과 상기 게이트 절연막 상부에 상기 제1공통배선과 중첩되고, 상기 데이터 배선과 이격되는 양단에 각각 배치되는 제1 및 제2쇼팅바과 상기 데이터 배선과 상기 제1 및 제2쇼팅바 상부에 배치되는 보호층과 상기 보호층 상부에 상기 제1 및 제2공통배선을 경계로 각각 일정 간격 이격되며, 상기 제1 또는 제2공통배선과 각각 일부 중첩하며 배치되는 제1 내지 제3화소전극을 포함하는 액정표시장치용 어레이 기판을 제공한다.

[0024] 또한, 상기 보호층은 상기 제1 및 제2쇼팅바 일부를 각각 노출시키는 제1 및 제2쇼팅 콘택홀을 구비하고, 상기 제1 및 제2화소전극은 상기 제1 및 제2쇼팅 콘택홀을 통해 상기 제1 및 제2쇼팅바와 각각 연결된다.

[0025] 또한, 상기 게이트 절연막 상부에 상기 제2공통배선과 중첩되고 서로 일정간격 이격되며 각각 배치되는 제3 및 제4쇼팅바를 더 포함한다.

[0026] 또한, 상기 보호층은 상기 제3 및 제4쇼팅바 상부에 상기 제3 및 제4쇼팅바 일부를 각각 노출시키는 제3 및 제4 쇼팅 콘택홀을 더 구비하고, 상기 제2 및 제3화소전극은 상기 제3 및 제4쇼팅 콘택홀을 통해 상기 제3 및 제4쇼팅바와 각각 연결된다.

[0027] 또한, 상기 제1 및 제2공통배선을 연결하며 상기 제2화소전극과 중첩되는 제3공통배선 및 상기 게이트 절연막 상부에 상기 제3공통배선과 중첩되며 배치되는 제5쇼팅바를 더 포함한다.

[0028] 또한, 상기 보호층은 상기 제5쇼팅바 상부에 상기 제5쇼팅바 일부를 노출시키는 제5쇼팅 콘택홀을 더 구비하고, 상기 제2화소전극은 상기 제5쇼팅 콘택홀을 통해 상기 제5쇼팅바와 연결된다.

[0029] 또한, 상기 제1 내지 제4쇼팅바의 길이는 각각 상기 제1 및 제2공통배선과 대응되는 길이이고, 상기 제5쇼팅바의 길이는 상기 제3공통배선과 대응되는 길이이다.

[0030] 또한, 상기 제2 및 제3쇼팅바와, 상기 제1 및 제4쇼팅바 각각은 상기 제5쇼팅바를 통해 연결된다.

[0031] 또한, 상기 제1 내지 제5쇼팅바는 상기 데이터 배선과 동일층 및 동일물질로 이루어진다.

[0032] 또한, 상기 제1 및 제2쇼팅바는 상기 데이터배선과  $1\mu\text{m}$  내지  $5\mu\text{m}$  이격된다.

### 발명의 효과

- [0033] 본 발명은 고온 및 고전압 시 공통배선과 화소전극이 쇼트(short)됨으로써 발생되는 표시 불량 현상을 방지할 수 있는 효과가 있다.

- [0034] 또한, 스토리지 커패시터의 용량을 늘릴 수 있어, 칙백 전압( $\Delta V_p$ )을 낮춰 플리커, 잔상, 색편차 등을 방지할 수 있는 효과가 있다.

### 도면의 간단한 설명

- [0035] 도 1은 일반적인 DRD구조의 액정표시장치용 어레이 기판의 표시영역 일부를 개략적으로 구성한 평면도이다.

- 도 2는 도 1의 II-II를 따라 절단한 부분에 대한 단면도이다.

- 도 3은 도 2에서 고온 및 고전압 시 누설전류패스가 형성되는 것을 설명하기 위한 단면도이다.

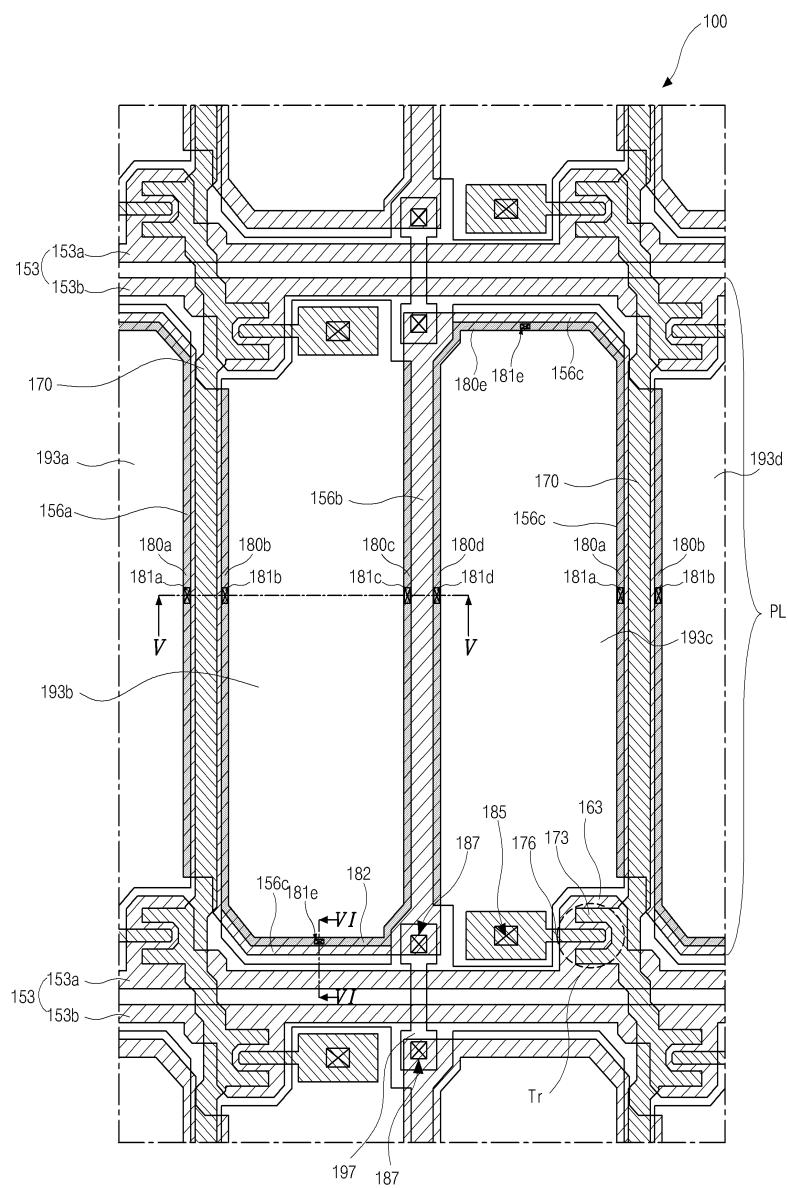

- 도 4는 본 발명의 실시예에 따른 DRD구조의 액정표시장치용 어레이 기판의 표시영역 일부를 개략적으로 구성한 평면도이다.

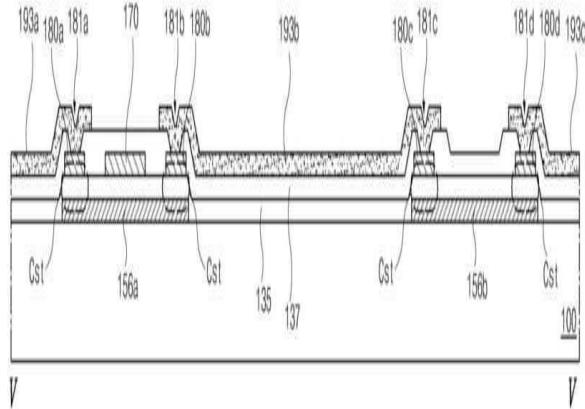

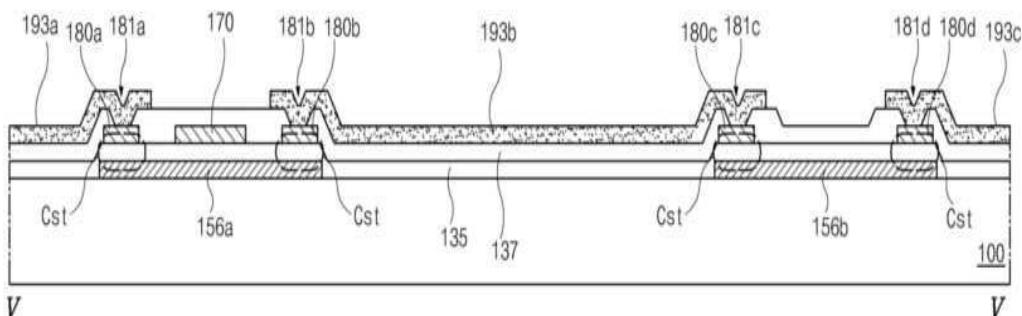

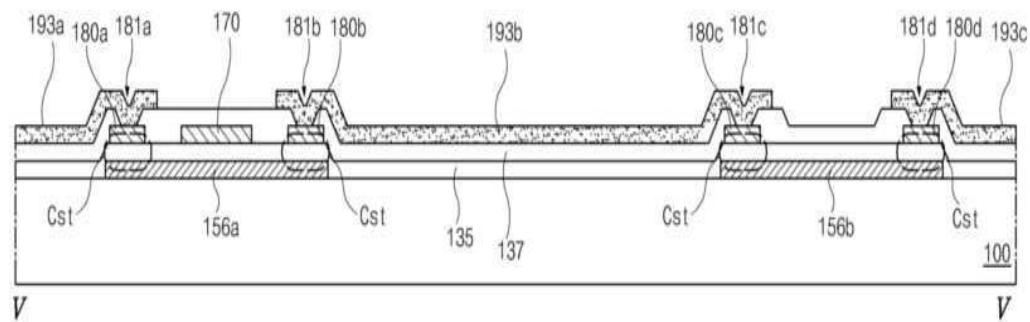

- 도 5는 도 4의 V-V를 따라 절단한 부분에 대한 단면도이다.

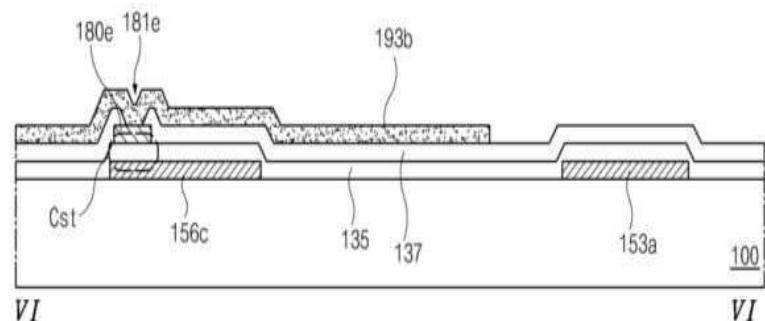

- 도 6은 VI-VI를 따라 절단한 부분에 대한 단면도이다.

### 발명을 실시하기 위한 구체적인 내용

- [0036] 이하, 첨부한 도면을 참조하여 본 발명의 바람직한 실시예를 설명한다.

- [0037] 도 4는 본 발명의 실시예에 따른 DRD구조의 액정표시장치용 어레이 기판의 표시영역 일부를 개략적으로 구성한 평면도이다.

- [0038] 도면에 도시한 바와 같이, 본 발명의 실시예에 따른 DRD구조의 액정표시장치용 어레이 기판(100)은 제1간격 이격되며 평행하게 일 방향으로 형성된 제1 및 2게이트 배선(153a, 153b)이 하나의 쌍을 이루며, 이러한 쌍을 이루는 제1 및 제2게이트 배선(153a, 153b)이 제2간격으로 이격되며 나란하게 다수 형성되어 있다.

- [0039] 이 때, 제1간격은 제1 및 제2게이트 배선(153a, 153b)이 쇼트 되지 않을 정도의 이격 간격으로 수  $\mu\text{m}$ 정도이고, 제2간격은 하나의 화소영역의 장축크기의 간격이다.

- [0040] 또한, 쌍으로 이루어진 다수의 제1 및 제2게이트 배선(153a, 153b)과 교차하여 다수의 데이터 배선(170)이 형성되어 있다.

- [0041] 이때, 서로 교차하는 한 쌍의 제1 및 제2게이트 배선(153a, 153b)과 데이터 배선(170)에 의해 둘러싸인 영역은 서로 이웃한 2개의 화소영역을 이룬다.

- [0042] 또한, 공통배선(156a 내지 156c)은 데이터 배선(170), 제1게이트 배선(153a), 2개의 화소영역의 경계 및 제2게이트 배선(153b)을 따라 각 화소영역을 둘러싸며 지그재그 형태로 형성됨으로써, 동일 화소라인(PL)에 대해서는 모두 연결된 형태가 되며, 게이트 배선(153)과 동일 층 및 동일 물질로 형성되어 있다.

- [0043] 또한, 이웃한 화소라인(PL)의 공통배선(156a 내지 156c) 끼리는 공통연결패턴(197)에 의해 연결되는데, 공통연결패턴(197)은 공통콘택홀(187)을 통해 노출된 각 공통배선(156a 내지 156c)과 접촉하며 화소전극(193a 내지 193d)을 이루는 투명 도전성 물질로 이루어진다.

- [0044] 이 때, 공통연결패턴(197)은 제1 및 제2게이트 배선(153a, 153b)과 교차하여 각 화소라인(PL)에 걸쳐 형성되어 있다.

- [0045] 또한, 각 화소영역에는 순차 적층된 형태로 게이트 전극(163)과 게이트 절연막(도 5의 135)과 반도체층(미도시)과 서로 이격하는 소스 및 드레인 전극(173, 176)으로 구성된 박막트랜지스터(Tr)가 구비되고 있으며, 화소전극(193a 내지 193d)은 드레인 콘택홀(185)을 통해 각각 박막트랜지스터(Tr)의 드레인 전극(176)과 접촉하며 각 화소영역 별로 형성되고 있다.

- [0046] 특히, 본 발명의 실시예에 따른 액정표시장치용 어레이기판(100)은, 제1 내지 제4화소전극(193a 내지 193d)과 제1공통배선(156a)이 각각 중첩되는 영역에 데이터 배선(170)과 이격되는 양단에 제1 및 제2쇼팅바(180a, 180b)가 각각 배치되며, 제1 및 제2쇼팅바(180a, 180b)는 제1 및 제2쇼팅 콘택홀(181a, 181b)을 통해 각각 제1 내지 제4화소전극(193a 내지 193d)과 연결된다.

- [0047] 또한, 제2 및 제3화소전극(193b, 193c)과 제2공통배선(156b)이 중첩되는 영역에 제3 및 제4쇼팅바(180c, 180d)가 각각 배치되며, 제3 및 제4쇼팅바(180c, 180d)는 제3 및 제4쇼팅 콘택홀(181c, 181d)을 통해 각각 제2 및 제3화소전극(193b, 193c)과 연결된다.

- [0048] 또한, 제1 및 제2공통배선(156a, 156b)을 연결하며 제2 또는 제3화소전극(193b, 193c)과 중첩되는 제3공통배선(156c)과 중첩되는 제5쇼팅바(180e)가 배치되며, 제5쇼팅바(180e)는 제5쇼팅 콘택홀(181e)을 통해 제2 또는 제3화소전극(193b, 193c)과 연결된다.

- [0049] 이 때, 제1 내지 제4쇼팅바(180a 내지 180d)의 길이는 각각 제1 및 제2공통배선(156a, 156b)과 대응되는 길이이고, 제5쇼팅바(180e)의 길이는 제3공통배선(156c)과 대응되는 길이이며, 제2 및 제3쇼팅바(180b, 180c)는 제5쇼팅바(180e)를 통해 연결되고, 제1 및 제4쇼팅바(180a, 180d)는 제5쇼팅바(180e)와 연결될 수 있다.

- [0050] 이 때, 데이터 배선(170)과 제1 내지 제5쇼팅바(180a 내지 180e)는 동일층에 형성되고, 이를 각각은 소스 및 드레인 전극(173, 176)과 동일층 및 동일물질로 형성된다.

- [0051] 이에 따라, 제1 및 제2쇼팅바(180a, 180b)는 인접한 데이터 배선(170)과 쇼트되지 않도록 충분히 이격되게 예를 들면  $1\mu\text{m}$  내지  $5\mu\text{m}$  이격되게 형성되는 것이 바람직하다.

- [0052] 도 5는 도 4의 V-V를 따라 절단한 부분에 대한 단면도이고, 도6은 VI-VI를 따라 절단한 부분에 대한 단면도이다.

- [0053] 도면에 도시한 바와 같이, 어레이 기판(100) 상에 하나의 화소영역의 단축 간격으로 이격되며 제1 및 제2공통배선(156a, 156b)이 배치되고, 제1 및 제2공통배선(156a, 156b) 상부 및 어레이 기판(100) 전면에 게이트 절연막(135)이 배치되고, 게이트 절연막(135) 상부에 제1공통배선(156a)과 중첩되는, 데이터 배선(170)과 데이터 배선(170) 양측과 이격되는 제1 및 제2쇼팅바(180a, 180b)가 각각 배치되고, 게이트 절연막(135) 상부에 제2공통배선(156b)과 중첩되는 제3 및 제4쇼팅바(180c, 180d)가 각각 배치되고, 데이터 배선(170)과 제1 내지 제4쇼팅바(180a 내지 180d) 상부에 제1 내지 제4쇼팅바(180a 내지 180d) 일부를 각각 노출시키는 제1 내지 제4쇼팅 콘택홀(181a 내지 181d)을 구비하는 보호층(137)이 배치되고, 보호층(137) 상부에 제1 및 제2공통배선(156a, 156b)을 경계로 각각 일정 간격 이격하며, 제1 및 제2공통배선(156a, 156b)과 각각 일부 중첩하고, 제1 내지 제4쇼팅 콘택홀(181a 내지 181d)을 통해 제1 내지 제4쇼팅바(180a 내지 180d)와 각각 연결되는 제1 내지 제3화소전극(193a 내지 193c)이 배치된다.

- [0054] 한편, 게이트 절연막(135) 상부에 제3공통배선(156c)과 중첩되며 제5쇼팅바(180e) 배치되고, 제5쇼팅바(180e) 상부에 제5쇼팅바(180e) 일부를 노출시키는 제5쇼팅 콘택홀(181e)을 더 구비하는 보호층(137)이 배치되고, 제5쇼팅 콘택홀(181e)을 통해 제5쇼팅바(180e)와 제2 또는 제3화소전극(193b, 193c)이 연결된다.

- [0055] 또한, 데이터 배선(170)과 제1 내지 제5쇼팅바(180a 내지 180e)는 동일층에 형성되고, 이를 각각은 소스 및 드레인 전극(173, 176)과 동일층 및 동일물질로 형성된다.

- [0056] 이에 따라, 제1 및 제2쇼팅바(180a, 180b)는 데이터 배선(170)과 쇼트되지 않도록 충분히 이격되게 예를 들면  $1\mu\text{m}$  내지  $5\mu\text{m}$  이격되게 형성되는 것이 바람직하다.

- [0057] 한편, 게이트 절연막(135) 및 보호층(137) 형성 시, 제1 내지 제3공통배선(156a 내지 156c) 양 끝단의 단차부 영역 상의 게이트 절연막(135) 및 보호층(137)의 두께는 제1 내지 제3공통배선(156a 내지 156c) 양 끝단의 단차로 인해 타 영역보다 얇은 두께로 형성된다.

- [0058] 본 발명의 액정표시장치용 어레이 기판은, 제1 내지 제3공통배선(156a 내지 156c)과 중첩되는 영역에 제1 내지 제5쇼팅바(180a 내지 180e)를 배치함으로써, 단차부 영역의 제1 내지 제3화소전극(193a 내지 193c)과 제1 내지 제3공통배선(156a 내지 156c) 사이의 거리를 넓혀, 게이트 절연막(135) 및 보호층(137)이 얇은 두께로 형성되더라도, 제1 내지 제3화소전극(193a 내지 193c)과 제1 내지 제3공통배선(156a 내지 156c) 사이에 각각 형성되는 전계로부터의 영향을 최소화 할 수 있다.

- [0059] 또한, 제1 내지 제3화소전극(193a 내지 193c)이 제1 내지 제5쇼팅바(180a 내지 180e)와 각각 연결됨으로써, 제1

내지 제3화소전극(193a 내지 193c)과 제1 내지 제3공통배선(156a 내지 156c) 사이에 각각 형성되는 전계를 단차 부영역 보다 상대적으로 거리가 가까운 제1 내지 제5쇼팅바(180a 내지 180e)와 제1 내지 제3공통배선(156a 내지 156c) 사이의 게이트 절연막(135)으로 집중시켜, 누설전류를 방지하고 단차부 영역의 게이트 절연막(135) 및 보호층(137)의 미세 균열을 방지할 수 있다.

[0060] 따라서, 미세 균열 사이로 누설전류 패스(Current leakage path : CLP)가 형성됨으로써, 제1공통배선(156a)과 제1 및 제2화소전극(193a 및 193b)이 쇼트(short)되거나, 제2공통배선(156b)과 제2 및 제3화소전극(193b, 193c)이 쇼트(short)되거나, 제3공통배선(156b)과 제2 또는 제3화소전극(193b, 193c)이 쇼트(short)되어 발생되는 표시 불량을 방지할 수 있다.

[0061] 구체적으로, 제1 및 제2쇼팅바(180a, 180b) 각각이 제1공통배선(156a)과 제1 및 제2화소전극(193a, 193b)이 쇼트(short)되는 것을 방지하고, 제3 및 제4쇼팅바(180c, 180d) 각각이 제2공통배선(156b)과 제2 및 제3화소전극(193b, 193c)이 쇼트(short)되는 것을 방지하고, 제5쇼팅바(180e)가 제3공통배선(156c)과 제2 또는 제3화소전극(193b, 193c)이 쇼트(short)되는 것을 방지하고 한다.

[0062] 한편, 킥백전압(Kickback Voltage, 또는 Feed Through Voltage,  $\Delta V_p$ )이 크면 표시 불량을 야기하는데, 킥백전압( $\Delta V_p$ )은 스토리지 커패시터(Cst) 용량에 반비례한다.

[0063] 이 때, 제1 및 제2쇼팅바(180a, 180b)는 제1 및 제2화소전극(193a, 193b)과 연결되어, 제1 및 제2쇼팅바(180a, 180b)와 제1공통배선(156a)과 이들 사이에 개재된 게이트 절연막(135)은 각각 스토리지 커패시터(Cst)를 이룬다.

[0064] 또한, 제3 및 제4쇼팅바(180c, 180d)는 제2 및 제3화소전극(193b, 193c)과 연결되어, 제3 및 제4쇼팅바(180c, 180d)와 제2공통배선(156b)과 이들 사이에 개재된 게이트 절연막(135)은 각각 스토리지 커패시터(Cst)를 이룬다.

[0065] 또한, 제5쇼팅바(180e)는 제2 또는 제3화소전극(193b, 193c)과 연결되어, 제5쇼팅바(180e)와 제3공통배선(156c)과 이들 사이에 개재된 게이트 절연막(135)은 각각 스토리지 커패시터(Cst)를 이룬다.

[0066] 이에 따라, 제1 및 제2공통배선(도2의 56a, 56b)과 각각 중첩되는 제1 내지 제3화소전극(도2의 93a 내지 93c)과 제1 및 제2공통배선(도2의 56a, 56b)과 이들 사이에 개재된 보호층(도2의 37) 및 게이트 절연막(도2의 35)이 각각 스토리지 커패시터(Cst)를 이루는 종래의 어레이 기판에 비해, 스토리지 커패시터(Cst) 용량이 증가되어 킥백전압(Kickback Voltage, 또는 Feed Through Voltage,  $\Delta V_p$ )이 감소되고, 이에 따라, 플리커, 잔상, 색편차 등을 방지할 수 있다.

[0067] 본 발명은 상기 실시예로 한정되지 않고, 본 발명의 취지를 벗어나지 않는 한도 내에서 다양하게 변경하여 실시할 수 있다.

### 부호의 설명

[0068] 100 : 어레이 기판

135 : 게이트 절연막

137 : 보호층

170 : 데이터 배선

156a, 156b : 제1 및 제2공통배선

180a~180d : 제1 내지 제4쇼팅바

181a~181d : 제1 내지 제4쇼팅콘택홀

193a~193c : 제1 내지 제3화소전극

## 도면

## 도면1

## 도면2

## 도면3

## 도면4

도면5

도면6

|                |                                                   |         |            |

|----------------|---------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种用于液晶显示器的阵列基板                                    |         |            |

| 公开(公告)号        | <a href="#">KR1020160083345A</a>                  | 公开(公告)日 | 2016-07-12 |

| 申请号            | KR1020140194300                                   | 申请日     | 2014-12-30 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                          |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                         |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                         |         |            |

| [标]发明人         | CHOI SEONG WOOK<br>최성욱<br>SONG JONG HUN<br>송종훈    |         |            |

| 发明人            | 최성욱<br>송종훈                                        |         |            |

| IPC分类号         | G02F1/1362                                        |         |            |

| CPC分类号         | G02F1/1362 G02F1/136204 G02F1/136209 G02F1/136286 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                         |         |            |

### 摘要(译)

为了提供能够防止显示缺陷的液晶显示器的阵列基板，设置在基板上的像素区域的边界上的第一和第二公共布线，第一和第二公共布线，数据线设置为与栅极绝缘层上方的第一公共线重叠，并且第二公共线设置在栅极绝缘层上方，重叠，并且所述第一和第二短路棒和所述数据线与所述第一和第二显示tingba保护和上述第一和第二保护层的共待放置在顶部被分别布置在每个端部被间隔开的数据线和各自间隔预定距离的边界线，对于包括第一至第三像素电极，其是在第一或第二公共布线，并且每个部分重叠和布置的液晶显示装置的阵列基板提供。