(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2014-0088935

(43) 공개일자 2014년07월14일

(51) 국제특허분류(Int. Cl.)

*G02F 1/1368* (2006.01) *G02F 1/1345* (2006.01)

*G02F 1/1343* (2006.01)

(21) 출원번호 10-2012-0157838

(22) 출원일자 2012년12월31일

심사청구일자 없음

(71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

정의현

경기 고양시 일산서구 강선로 71, 삼환마을 707동

2204호 (주엽동, 강선마을7단지아파트)

이준동

경기 안양시 동안구 관평로138번길 63, 705동 30

6호 (평촌동, 초원부영아파트)

장성용

경기도 파주시 교하읍 동폐리 1207동 201호

(74) 대리인

특허법인네이트

전체 청구항 수 : 총 5 항

(54) 발명의 명칭 **액정표시장치용 어레이기판**

### (57) 요 약

본 발명은 액정표시장치용 어레이기판에 관한 것으로, 기판과; 상기 기판 상부에 서로 교차하여 형성되어 다수의 화소영역을 정의하는 다수의 게이트배선 및 다수의 데이터배선과; 상기 다수의 화소영역에 각각 형성되는 박막트랜지스터와; 상기 박막트랜지스터와 연결되는 화소전극과; 상기 화소전극에 대응하여 적어도 하나의 개구부를 가지는 공통전극과; 상기 다수의 게이트배선 및 상기 다수의 데이터배선에 각각 공급되는 게이트신호 및 데이터신호를 생성하는 구동칩적회로와; 상기 게이트신호를 상기 다수의 게이트배선에 전달하며, 상기 다수의 게이트배선과 동일층, 동일물질로 형성되는 다수의 제 1 링크배선과; 상기 제 1 링크배선의 사이에 위치하며, 상기 제 1 링크배선과 다른 층에 형성되어 상기 데이터신호를 상기 다수의 데이터배선에 전달하는 다수의 제 2 링크배선과; 상기 제 1 링크배선과 상기 제 2 링크배선의 사이에 위치하며, 상기 공통전극과 동일층에 동일물질로 이루어지는 제 1 층과 상기 제 1 층 상부의 제 2 층으로 이루어지는 다수의 제 3 링크배선을 포함한다.

**대 표 도** - 도5

## 특허청구의 범위

### 청구항 1

기판과;

상기 기판 상부에 서로 교차하여 형성되어 다수의 화소영역을 정의하는 다수의 게이트배선 및 다수의 데이터배선과;

상기 다수의 화소영역에 각각 형성되는 박막트랜지스터와;

상기 박막트랜지스터와 연결되는 화소전극과;

상기 화소전극에 대응하여 적어도 하나의 개구부를 가지는 공통전극과;

상기 게이트배선 및 상기 데이터배선에 각각 공급되는 게이트신호 및 데이터신호를 생성하는 구동칩적회로와;

상기 게이트신호를 상기 다수의 게이트배선에 전달하며, 상기 다수의 게이트배선과 동일층, 동일물질로 형성되는 다수의 제 1 링크배선과;

상기 제 1 링크배선의 사이에 위치하며, 상기 제 1 링크배선과 다른 층에 형성되어 상기 데이터 신호를 상기 다수의 데이터배선에 전달하는 다수의 제 2 링크 배선과;

상기 제 1 링크배선과 상기 제 2 링크배선의 사이에 위치하며, 상기 공통전극과 동일층에 동일물질로 이루어지는 제 1 층과 상기 제 1 층 상부의 제 2 층으로 이루어지는 다수의 제 3 링크배선

을 포함하는 액정표시장치용 어레이기판.

### 청구항 2

제 1 항에 있어서,

상기 제 1 링크배선과 상기 제 2 링크배선 및 상기 제 3 링크배선의 상기 제 2 층은 서로 다른 층에 형성되는 것을 특징으로 하는 액정표시장치용 어레이기판.

### 청구항 3

제 1 항에 있어서,

상기 제 2 링크배선은 상기 다수의 데이터배선과 동일층, 동일물질로 형성되는 것을 특징으로 하는 액정표시장치용 어레이기판.

### 청구항 4

제 1 항에 있어서,

상기 제 3 링크배선은 하프 톤 마스크를 이용하여 공통전극과 동일층에 이중층으로 형성되는 것을 특징으로 하는 액정표시장치용 어레이기판.

### 청구항 5

제 1 항에 있어서.

상기 제 3 링크배선은 하프 톤 마스크를 이용하여 상기 공통 전극과 하나의 마스크 공정에 의해 형성되는 것을

특징으로 하는 액정표시장치용 어레이기판.

## 명세서

### 기술분야

[0001]

본 발명은 액정표시장치용 어레이기판에 관한 것으로서, 더욱 상세하게는 하나의 구동 집적회로가 게이트배선용 게이트신호와 데이터배선용 데이터신호를 모두 공급하는 액정표시장치용 어레이기판에 관한 것이다.

### 배경기술

[0002]

정보화 사회가 발전함에 따라 화상을 표시하기 위한 표시장치에 대한 요구가 다양한 형태로 증가하고 있으며, 근래에는 액정표시장치(LCD : liquid crystal display), 플라즈마표시장치(PDP : plasma display panel), 유기전계발광소자 (OLED : organic light emitting diode)와 같은 여러 가지 평판표시장치(FPD : flat panel display)가 활용되고 있다.

[0003]

일반적으로 액정표시장치는 각각 전극이 형성되어 있는 두 기판을 전극이 서로 마주보도록 배치하고, 상기 두 기판 사이에 액정을 주입한 다음, 전극에 전압을 인가하여 생성되는 전기장에 의해 액정 분자를 움직임으로써, 이에 따라 달라지는 빛의 투과율에 의해 영상을 표현하는 장치이다.

[0004]

이러한 액정표시장치는 힙착된 두 기판과 그 사이의 액정층으로 이루어지는 액정패널과, 액정패널 하부에 배치되어 빛을 공급하는 백라이트 유닛과, 액정패널 외곽에 배치되어 액정패널을 구동하기 위한 다수의 신호 및 전원을 공급하는 구동부로 이루어진다.

[0005]

통상적으로 구동부는 인쇄회로기판(printed circuit board: PCB)에 구현되는데, 액정패널의 게이트배선과 연결되는 게이트 구동부와 데이터배선과 연결되는 데이터 구동부로 나뉘어 게이트용 인쇄회로기판(gate PCB) 및 데이터용 인쇄회로기판(data PCB)으로 구현될 수 있으며, 이들 게이트용 인쇄회로기판 및 데이터용 인쇄회로기판은, 액정패널의 일 측에 형성되며 게이트배선과 연결되는 게이트패드와, 상기 게이트 패드가 형성된 일 측과 직교하는 타 측에 형성되며 데이터배선과 연결된 데이터패드 각각에 테이프 캐리어 패키지(tape carrier package: TCP)와 같은 형태로 실장될 수 있다.

[0006]

한편, 예를 들어 소형 모델의 경우 게이트배선 및 데이터배선의 수가 상대적으로 적으므로, 게이트배선용 구동 집적회로(driving integrated circuit: D-IC) 및 데이터배선용 구동집적회로를 별도로 구성하지 않고 하나의 구동집적회로가 게이트배선용 게이트신호와 데이터 배선용 데이터신호를 모두 공급하는 형태의 액정표시장치가 개발되고 있다.

[0007]

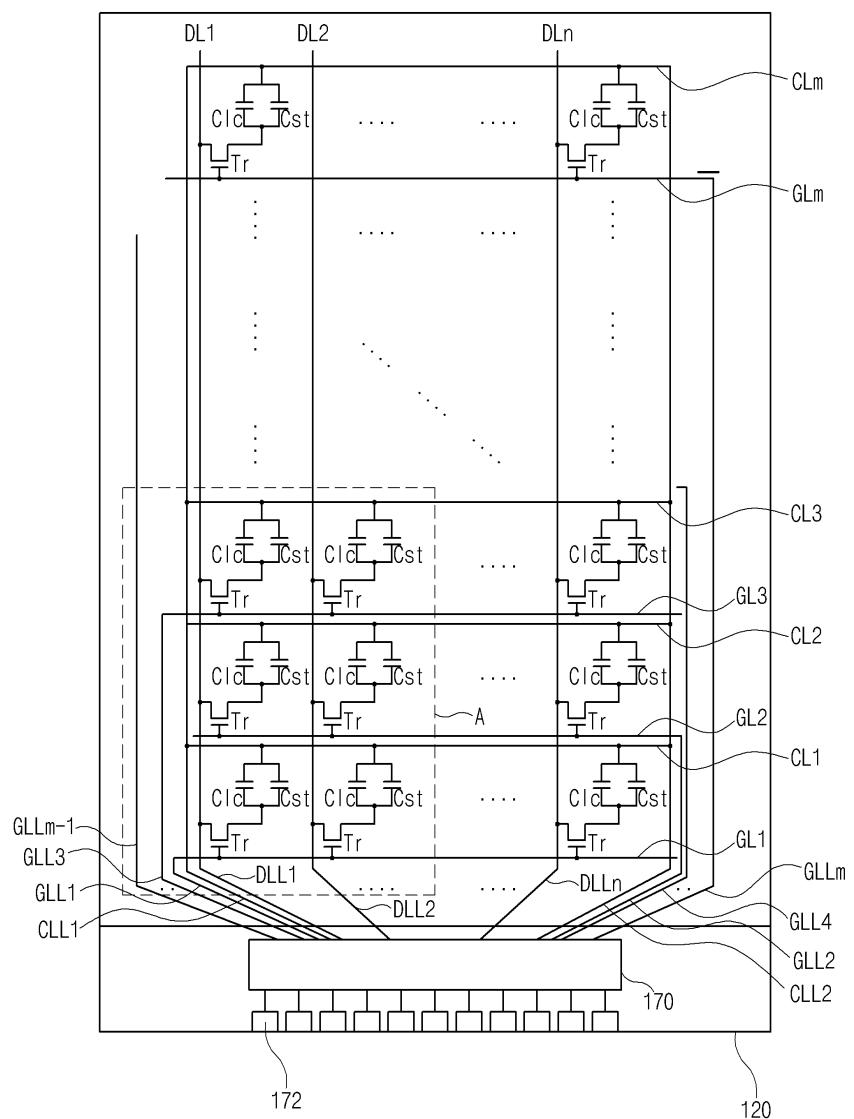

이하, 종래기술에 따른 이러한 형태의 액정표시장치용 어레이기판을 도 1의 개략회로도를 참조하여 설명한다.

[0008]

도 1에 도시한 바와 같이, 기판(20) 상부에는 일 방향으로 스캔 신호를 인가받는 다수의 게이트배선(GL1 내지 GLm)과 이들 다수의 게이트배선(GL1 내지 GLm)과 수직 교차하여 다수의 화소영역을 정의하며, 데이터전압을 인가받는 다수의 데이터배선(DL1 내지 DLn)이 매트릭스(matrix) 형태로 배치된다.

[0009]

다수의 게이트배선(GL1 내지 GLm)과 다수의 데이터 배선(DL1 내지 DLn)의 교차지점에는 스위칭 역할을 하는 다수의 박막 트랜지스터(Tr)가 위치하고, 박막트랜지스터(Tr)는 화소영역에 대응하여 구성된 화소전극(미도시)과 접촉된다.

[0010]

그리고, 각 화소영역에는 박막트랜지스터(Tr)에 연결되는 액정커패시터(C<sub>lc</sub>)와 스토리지커패시터(C<sub>st</sub>)가 형성되고, 액정커패시터(C<sub>lc</sub>)와 스토리지커패시터(C<sub>st</sub>)는 다수의 공통배선(CL1 내지 CLm) 각각에 연결된다.

[0011]

기판(20)의 일 가장자리에는 게이트배선 및 데이터배선에 게이트신호 및 데이터신호를 각각 공급하는 구동집적회로(70)가 형성되고, 구동집적회로(70) 바깥 부분에는 구동집적회로(70)와 연결되어 외부의 구동부로부터 다수의 구동신호와 전원을 입력받는 입력패드(72)가 형성된다.

[0012]

여기서, 구동집적회로(70)는 다수의 게이트링크 배선(GLL1 내지 GLLm)을 통하여 다수의 게이트배선(GL1 내지 GLm)과 연결되고, 다수의 공통링크 배선(CLL1 내지 CLLm)을 통하여 다수의 공통배선(CL1 내지 CLm)과 연결되고, 다수의 데이터링크배선(DLL1 내지 DLLn)을 통하여 다수의 데이터배선(DL1 내지 DLn)과 연결된다.

- [0013] 구동집적회로(70)는 외부의 구동부로부터 공급되는 다수의 구동신호를 이용하여 게이트신호 및 데이터신호를 생성하는데, 게이트신호는 게이트링크배선 및 게이트배선을 통하여 각 화소영역의 박막트랜지스터(Tr)의 게이트전극에 인가되어 박막트랜지스터(Tr)를 스위칭하고, 데이터신호는 데이터링크배선 및 데이터배선을 통하여 각 화소영역의 박막트랜지스터(Tr)의 소스전극에 공급되어 박막트랜지스터(Tr)를 통해 액정커패시터(C<sub>st</sub>) 및 스토리지커패시터(C<sub>st</sub>)에 인가된다.

- [0014] 여기서, 다수의 게이트링크배선(GLL1 내지 GLL<sub>m</sub>) 및 다수의 데이터링크배선(DLL1 내지 DLL<sub>n</sub>)은 짹수 번째의 제1 링크배선과 홀수 번째의 제2 링크배선으로 분리되어 구동집적회로(70)에 연결된다.

- [0015] 그리고, 다수의 게이트링크배선(GLL1 내지 GLL<sub>m</sub>)과 다수의 데이터링크배선(DLL1 내지 DLL<sub>n</sub>)의 각각은 동일한 선폭 및 배선간격으로 형성될 수 있다.

- [0016] 여기서, 종래의 액정표시 장치의 짹수 번째의 제1 링크배선과, 홀수 번째의 제2 링크배선은 서로 다른 층에서 다른 물질로 형성되어 교차되도록 설계된다.

- [0017] 이에 대해서 도 2를 더욱 참조하여 보다 상세히 설명하도록 한다.

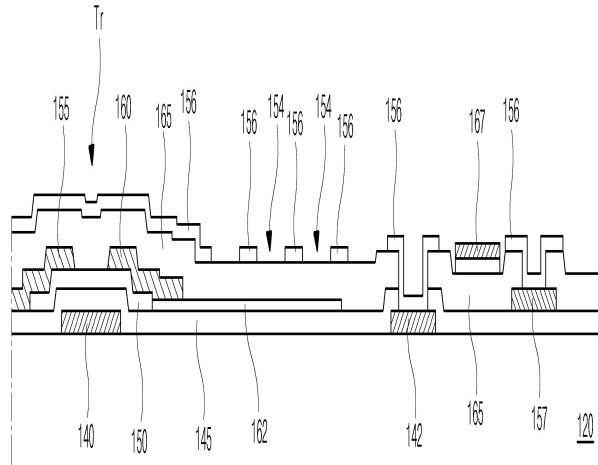

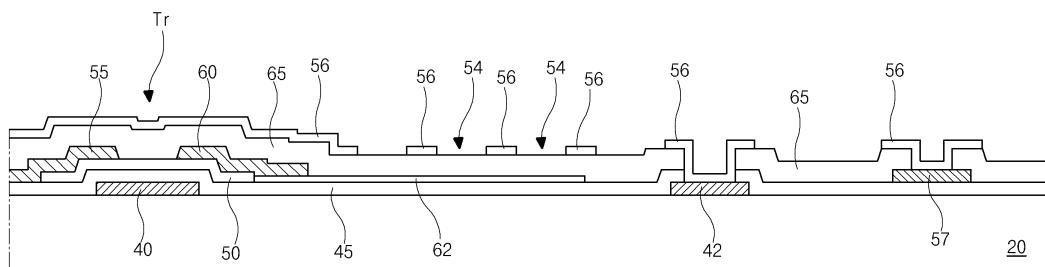

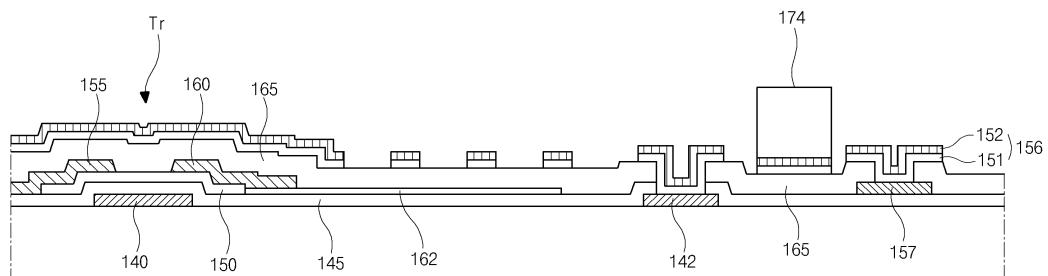

- [0018] 도 2는 종래의 액정표시장치용 어레이기판을 개략적으로 도시한 단면도이다.

- [0019] 도 2에 도시한 바와 같이, 어레이기판 상부 표면에는 서로 교차하여 화소영역을 정의하는 다수의 게이트배선(GL1 내지 GL<sub>m</sub>)과 다수의 데이터배선(DL1 내지 DL<sub>n</sub>)이 형성되고, 각 화소영역에는 게이트배선 및 데이터배선에 연결되는 박막트랜지스터(Tr)가 형성된다.

- [0020] 박막트랜지스터(Tr)는 기판(20) 상부에 형성되는 게이트 전극(40), 게이트 전극(40) 상부에 형성되는 게이트 절연막(45), 게이트 절연막(45) 상부에 형성되는 반도체층(50), 반도체층(50) 상부에 서로 이격되어 형성되는 소스전극(55) 및 드레인전극(60)을 포함하고, 박막트랜지스터(Tr) 상부에는 보호층(65)이 형성된다.

- [0021] 그리고, 각 화소영역의 게이트 절연막(45)과 보호층(65) 사이에는 박막트랜지스터(Tr)에 연결되는 화소전극(62)이 형성되고, 각 화소영역의 기판(20)과 게이트 절연막(45) 사이에는 화소전극(62)과 평행하게 이격되는 공통전극(56)이 형성된다.

- [0022] 이때, 다수의 게이트배선(GL1 내지 GL<sub>m</sub>)은 다수의 게이트링크배선(GLL1 내지 GLL<sub>m</sub>)과 연결되고, 다수의 데이터배선(DL1 내지 DL<sub>n</sub>)은 다수의 데이터링크배선(DLL1 내지 DLL<sub>n</sub>)과 연결되며, 다수의 공통배선(CL1 내지 CL<sub>m</sub>)은 다수의 공통링크배선(CL<sub>1</sub> 내지 CL<sub>m</sub>)과 연결된다. 다수의 게이트링크배선과 다수의 데이터링크배선 및 다수의 공통링크배선은 홀수 번째 링크배선인 제1 링크배선(42)과, 짹수 번째 링크배선인 제2 링크배선(57)으로 분리되어 게이트 절연막을 사이에 두고 서로 다른 층에서 교차되어 제1 링크배선은 게이트 전극과 동일한 층에 동일한 물질로 형성되고, 제2 링크배선은 소스전극 및 드레인전극과 동일한 층에 동일한 물질로 형성된다.

- [0023] 그러나, 제1 링크배선과 제2 링크배선은 서로 다른 층에 서로 다른 물질로 형성되는 바, 각 층에 형성되는 물질에 따라 비저항 값이 달라지게 되고 이에 따라 비저항차가 발생하게 되어, 각 배선에서의 데이터 전압의 지연시간차이에 따라 기판의 표시 영역에 영상이 밝거나 흐리게 표현되는 디밍(dim) 현상이 발생되고 기판의 표시 영역의 화질이 저하되는 문제점이 있다.

- [0024] 또한, 액정표시장치가 고해상도로 구성될 수록 늘어나는 픽셀 수에 비례하여 링크배선의 수가 같이 증가함으로 인해 배선영역이 더 필요하게 되어 베젤의 크기가 증가하는 문제점이 있다.

## 발명의 내용

### 해결하려는 과제

- [0025] 본 발명은 상기한 문제를 해결하기 위한 것으로, 각 배선의 비저항차에 의한 화질 저하를 방지하고, 베젤의 크기를 줄일 수 있는 액정표시장치용 어레이기판을 제공하는 것을 목적으로 한다.

## 과제의 해결 수단

[0026]

상기의 목적을 달성하기 위하여, 본 발명의 액정표시장치용 어레이기판은 기판과; 상기 기판 상부에 서로 교차하여 형성되어 다수의 화소영역을 정의하는 다수의 게이트배선 및 다수의 데이터배선과; 상기 다수의 화소영역에 각각 형성되는 박막트랜지스터와; 상기 박막트랜지스터와 연결되는 화소전극과; 상기 화소전극에 대응하여 적어도 하나의 개구부를 가지는 공통전극과; 상기 다수의 게이트배선 및 상기 다수의 데이터배선에 각각 공급되는 게이트신호 및 데이터신호를 생성하는 구동집적회로와; 상기 게이트신호를 상기 다수의 게이트배선에 전달하며, 상기 다수의 게이트배선과 동일층, 동일물질로 형성되는 다수의 제 1 링크배선과; 상기 제 1 링크배선의 사이에 위치하며, 상기 제 1 링크배선과 다른 층에 형성되어 상기 데이터 신호를 상기 다수의 데이터배선에 전달하는 다수의 제 2 링크 배선과; 상기 제 1 링크배선과 상기 제 2 링크배선의 사이에 위치하며, 상기 공통전극과 동일층에 동일물질로 이루어지는 제 1 층과 상기 제 1 층 상부의 제 2 층으로 이루어지는 다수의 제 3 링크배선을 포함한다.

[0027]

상기 제 1 링크배선과 상기 제 2 링크배선 및 상기 제 3 링크배선의 상기 제 2 층은 서로 다른 층에 형성된다.

[0028]

상기 제 2 링크배선은 상기 다수의 데이터배선과 동일층, 동일물질로 형성된다.

[0029]

상기 제 3 링크배선은 하프 톤 마스크를 이용하여 공통전극과 동일층에 이중층으로 형성된다.

[0030]

상기 제 3 링크배선은 하프 톤 마스크를 이용하여 상기 공통 전극과 하나의 마스크 공정에 의해 형성된다.

## 발명의 효과

[0031]

본 발명에 따른 액정표시장치용 어레이기판은, 제 1 링크배선과 제 2 링크배선 및 제 3 링크배선에 동일 비저항 특성을 가지는 금속을 적용하여 비저항차를 줄여 데이터 전압의 지연차를 방지할 수 있다.

[0032]

또한, 본 발명은 제 1 링크배선과 제 2 링크배선 및 제 3 링크 배선이 서로 다른 층에 위치되어 배선 영역을 감소시켜 베젤의 크기를 줄일 수 있다.

## 도면의 간단한 설명

[0033]

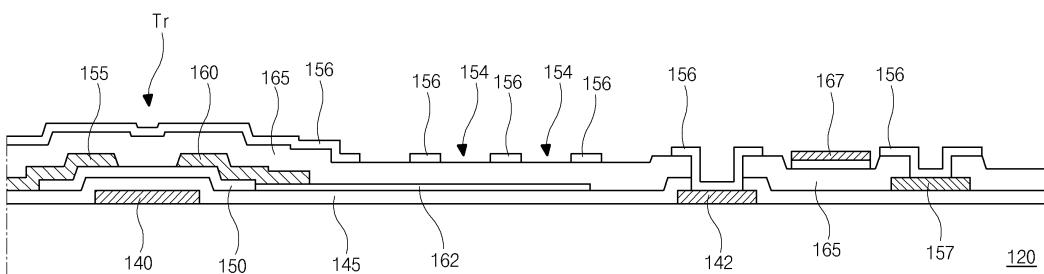

도 1은 종래의 액정표시장치용 어레이기판의 개략회로도이다.

도 2은 종래의 액정표시장치용 어레이기판을 개략적으로 도시한 단면도이다.

도 3는 본 발명의 실시예에 따른 액정표시장치용 어레이기판을 도시한 개략회로도이다.

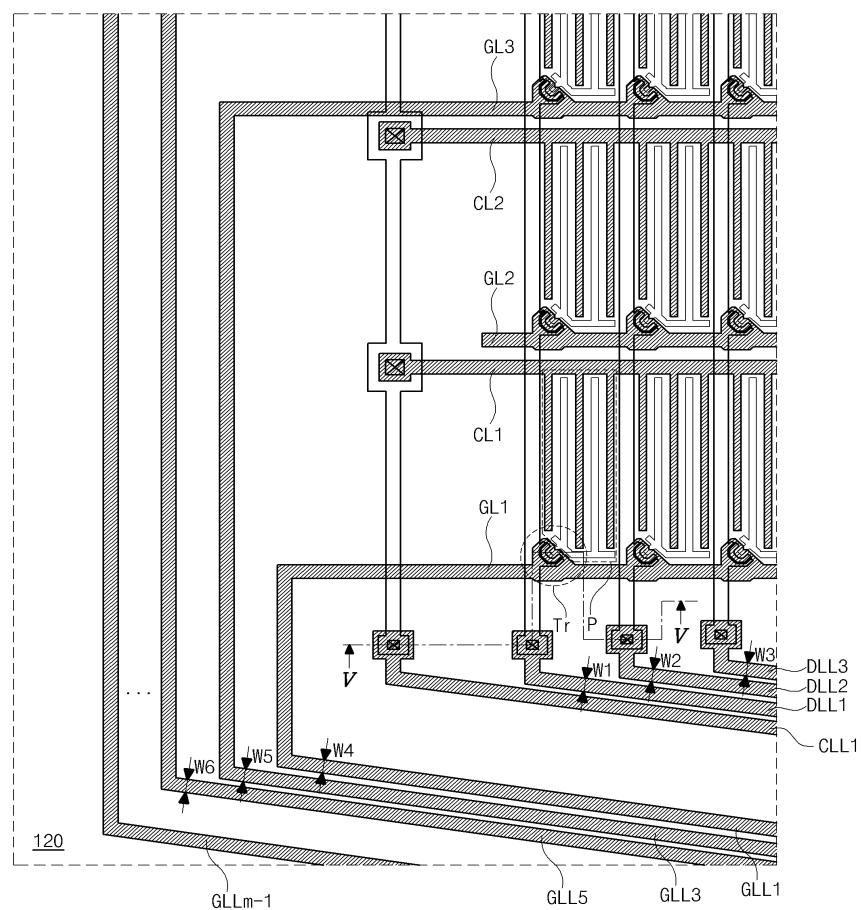

도 4는 도 3의 A부분에 대응되는 액정표시장치용 어레이기판을 도시한 평면도이다.

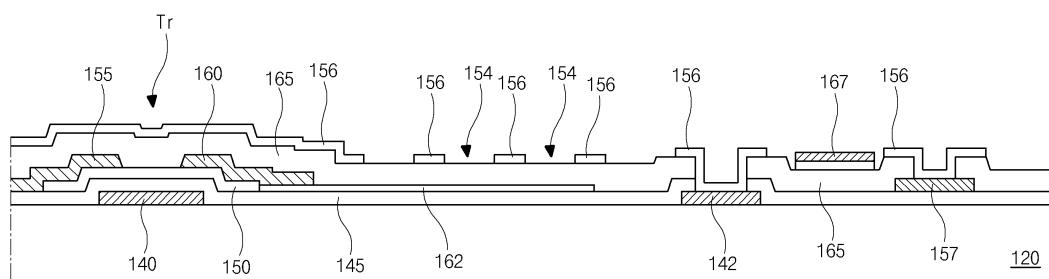

도 5는 도 4의 절단선 V-V에 따른 액정표시장치용 어레이기판의 단면도이다.

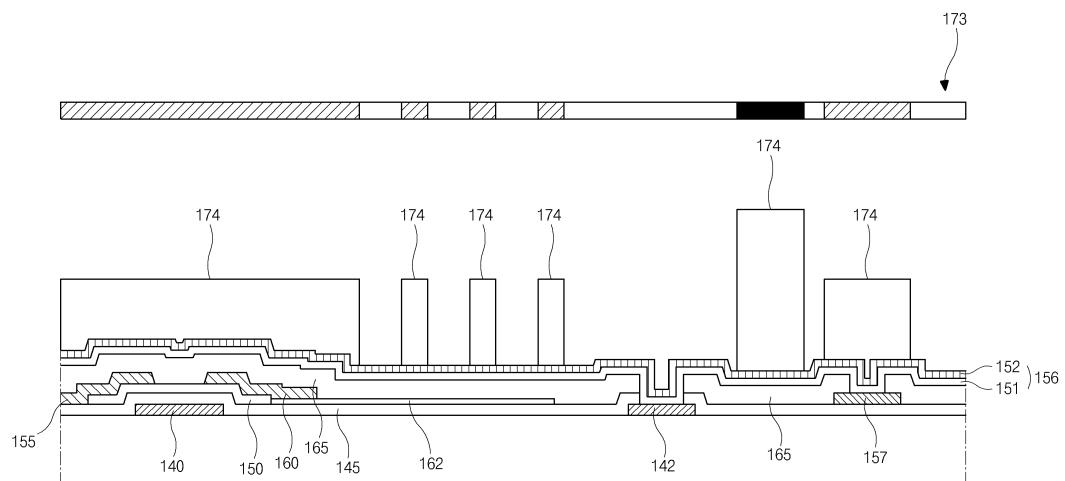

도 6a 내지 도 6c는 도 4의 절단선 V-V에 따른 액정표시장치용 어레이기판의 제조공정을 순차적으로 나타내는 단면도이다.

## 발명을 실시하기 위한 구체적인 내용

[0034]

이하, 첨부된 도면을 참조하여 본 발명에 따른 액정표시장치용 어레이기판의 바람직한 실시예를 상세히 설명한다.

[0035]

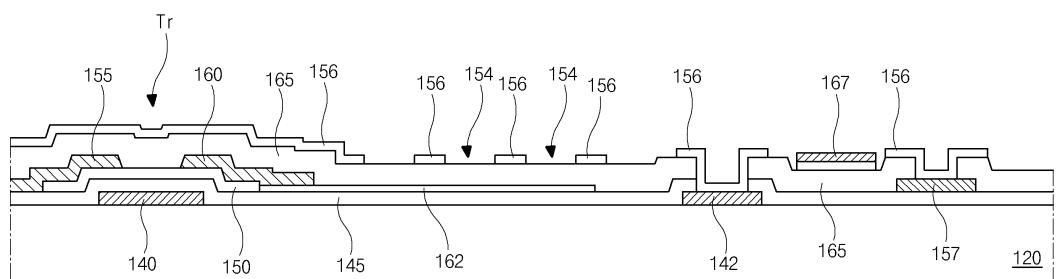

도 3은 본 발명의 실시예에 따른 액정표시장치용 어레이기판을 도시한 개략회로도이다. 설명의 편의를 위해 액정표시장치용 어레이기판의 단면도인 도 5를 참조한다.

[0036]

도 3에 도시한 바와 같이, 본 발명의 실시예에 따른 액정표시장치용 어레이기판의 기판(120) 상부에는 일 방향으로 스캔 신호를 인가받는 다수의 게이트배선(GL1 내지 GLm)과, 이들 다수의 게이트배선(GL1 내지 GLm)과 수직 교차하여 다수의 화소영역을 정의하며, 데이터전압을 인가받는 다수의 데이터배선(DL1 내지 DLn)이 매트릭스(matrix) 형태로 배치된다.

[0037]

다수의 게이트배선(GL1 내지 GLm)과 다수의 데이터배선(DL1 내지 DLn)의 교차지점에는 스위칭 역할을 하는 다수

의 박막트랜지스터(Tr)가 구성되고, 박막트랜지스터(Tr)는 화소영역에 대응하여 구성된 화소전극(도 5의 162 참조)과 접촉된다.

[0038] 그리고, 각 화소영역에는 박막트랜지스터(Tr)에 연결되는 액정커패시터(C<sub>lc</sub>)와 스토리지커패시터(C<sub>st</sub>)가 형성되고, 액정커패시터(C<sub>lc</sub>)와 스토리지커패시터(C<sub>st</sub>)는 다수의 공통배선(CL1 내지 CL<sub>m</sub>) 각각에 연결된다.

[0039] 기판(120)의 일 가장자리에는 게이트배선 및 데이터배선에 게이트신호 및 데이터신호를 각각 공급하는 구동집적회로(170)가 형성되고, 구동집적회로(170) 바깥 부분에는 구동집적회로(170)와 연결되어 외부의 구동부로부터 다수의 구동신호와 전원을 입력받는 입력패드(172)가 형성된다.

[0040] 여기서, 구동집적회로(170)는 다수의 게이트링크배선(GL1 내지 GL<sub>m</sub>)을 통하여 다수의 게이트배선(GL1 내지 GL<sub>m</sub>)과 연결되고, 다수의 공통링크배선(CL1 내지 CL<sub>m</sub>)을 통하여 다수의 공통배선(CL1 내지 CL<sub>m</sub>)과 연결되고, 다수의 데이터링크배선(DLL1 내지 DLL<sub>n</sub>)을 통하여 다수의 데이터배선(DL1 내지 DL<sub>n</sub>)과 연결된다. 이때, 구동집적회로(170)와 입력 패드(172)가 위치하는 영역은 베젤(Bezel)영역에 해당된다.

[0041] 구동집적회로(170)는 외부의 구동부로부터 공급되는 다수의 구동신호를 이용하여 게이트신호 및 데이터신호를 생성하는데, 게이트신호는 게이트링크배선 및 게이트배선을 통하여 각 화소영역의 박막트랜지스터(Tr)의 게이트전극(140)에 인가되어 박막트랜지스터(Tr)를 스위칭하고, 데이터신호는 데이터링크배선 및 데이터배선을 통하여 각 화소영역의 박막트랜지스터(Tr)의 소스전극(155)에 공급되어 박막트랜지스터(Tr)를 통해 액정커패시터(C<sub>lc</sub>) 및 스토리지커패시터(C<sub>st</sub>)에 인가된다.

[0042] 본 발명의 실시예에서는 다수의 게이트링크배선(GL1 내지 GL<sub>m</sub>)과 다수의 데이터링크배선(DLL1 내지 DLL<sub>n</sub>) 및 다수의 공통링크배선(CL1 내지 CL<sub>m</sub>)이 서로 다른 층에 위치되도록 설계함으로써 각 링크배선의 선폭을 줄여 밀접하게 배치할 수 있으므로 베젤영역의 면적을 축소할 수 있다.

[0043] 여기서, 설명의 편의를 위하여, 다수의 게이트링크배선(GL1 내지 GL<sub>m</sub>)을 제 1 링크배선(도 5의 142 참조), 다수의 데이터링크배선(DLL1 내지 DLL<sub>n</sub>)을 제 2 링크배선(도 5의 157 참조), 다수의 공통링크배선(CL1 내지 CL<sub>m</sub>)을 제 3 링크배선(도 5의 167 참조)이라 칭한다.

[0044] 상기 제 1 링크배선(142)과 제 2 링크배선(157) 및 제 3 링크배선(167)이 위치되는 액정표시장치용 어레이기판에 대하여 도 4 및 도 5를 참조하여 보다 상세히 설명하도록 한다.

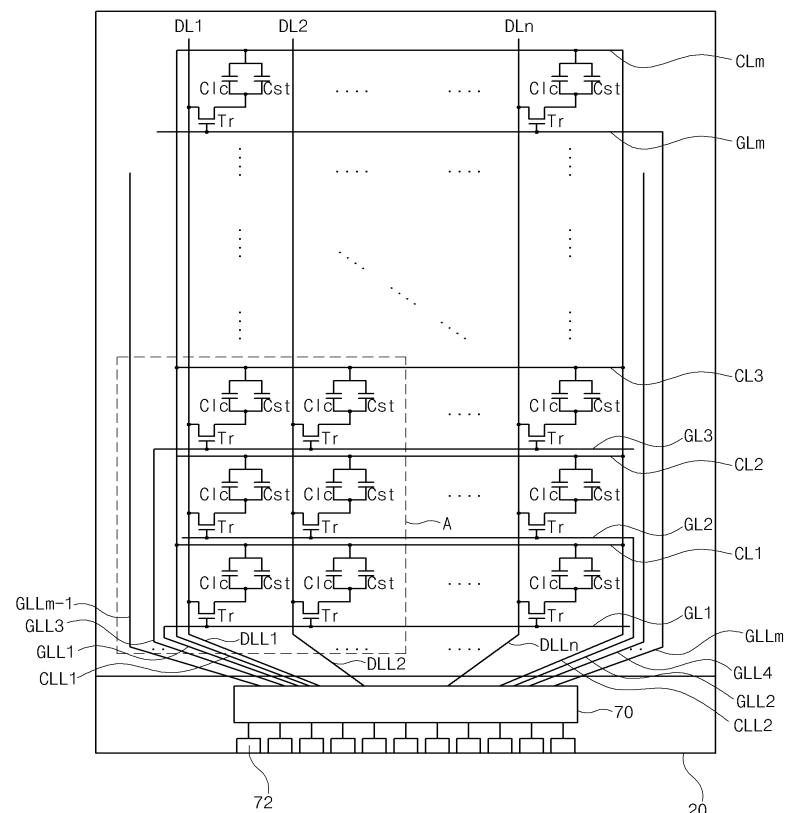

[0045] 도 4는 도 3의 A부분에 대응되는 어레이기판을 도시한 평면도이고, 도 5는 도 4의 절단선 V-V에 따른 어레이기판의 단면도이다.

[0046] 도 4 및 도 5에 도시한 바와 같이, 기판(120) 상부에는 서로 교차하여 화소 영역을 정의하는 다수의 게이트배선(GL1 내지 GL<sub>m</sub>)과 다수의 데이터배선(DL1 내지 DL<sub>n</sub>)이 형성되고, 각 화소영역에는 게이트배선 및 데이터배선에 연결되는 박막트랜지스터(Tr)가 형성된다. 박막트랜지스터(Tr)는 기판(120) 상부에 형성되는 게이트 전극(140), 게이트 전극(140) 상부에 형성되는 게이트 절연막(145), 게이트 절연막(145) 상부에 형성되는 반도체층(150), 반도체층(150) 상부에 서로 이격되어 형성되는 소스전극(155) 및 드레인전극(160)을 포함하고, 박막트랜지스터(Tr) 상부에는 보호층(165)이 형성된다.

[0047] 여기서, 게이트 전극(140)은 알루미늄(Al), 알루미늄 합금(AlNd), 구리(Cu), 구리합금, 크롬(Cr), 몰리브덴(Mo) 및 몰리브덴 합금(MoTi) 등의 도전성 물질의 단일층 또는 다중층으로 이루어질 수 있으며, 알루미늄(Al), 구리(Cu), 은(Ag), 티타늄(Ti)과 같은 금속에 칼슘(Ca), Mg(마그네슘), 아연(Zn), 티타늄(Ti), 몰리브덴(Mo), 니켈(Ni), 지르코늄(Zr), 카드뮴(Cd), 금(Au), 은(Ag), 코발트(Co), 인(In), 탄탈(Ta), 하프늄(Hf), 텉스텐(W) 및 크롬(Cr) 중 하나 이상이 포함된 합금의 단일층 또는 다중층으로 이루어질 수 있다.

[0048] 이때, 다수의 게이트배선(GL1 내지 GL<sub>m</sub>)과 구동집적회로(170)를 연결하는 다수의 제 1 링크배선(142)이 다수의 게이트 전극(140)과 동일층, 동일 물질로 이루어진다.

[0049] 또한, 게이트 절연막(145)은 산화실리콘(SiO<sub>2</sub>) 또는 질화실리콘(SiNx)으로 이루어지거나, 알루미늄(Al) 산화물 또는 하프늄(Hf) 산화물로 이루어질 수 있다.

[0050] 반도체층(150)은 인듐-탄-옥사이드(indium tin oxide: ITO)나 인듐-징크-옥사이드(indium zinc oxide: IZO)로 이루어질 수 있으며, 소스전극(155)과 드레인전극(160)은 비교적 낮은 비저항을 가지는 구리(Cu) 또는 구리합금

으로 이루어질 수 있다.

[0051] 이때, 다수의 데이터배선(DL1 내지 DLn)과 구동집적회로(170)를 연결하는 다수의 제 2 링크배선(157)이 소스전극(155) 및 드레인전극(160)과 동일층, 동일물질로 이루어진다.

[0052] 또한, 보호층(165)은 벤조사이클로부텐(benzocyclobutene: BCB) 또는 포토 아크릴(photo-acryl)과 같은 유기질연물질을 도포(coating)하거나, 화학기상증착(CVD)법을 통해 산화실리콘(SiO<sub>2</sub>) 또는 질화실리콘(SiNx)과 같은 무기질연물질을 증착하여 형성될 수 있다.

[0053] 그리고, 각 화소영역의 게이트 절연막(145)과 보호층(165) 사이에는 박막트랜지스터(Tr)에 연결되는 화소전극(162)이 형성되고, 화소전극(162)은 드레인전극(160)의 일 끝단에 접촉되어 드레인전극(160)과 전기적으로 연결된다.

[0054] 또한, 보호층(165) 상부에는 공통전극(156)이 기판(120) 전면에 형성되며, 화소전극(162)에 대응하여 다수의 개구부(154)를 가진다.

[0055] 화소전극(162)은 인듐-틴-옥사이드(indium tin oxide: ITO)나 인듐-징크-옥사이드(indium zinc oxide: IZO)의 투명도전물질로 이루어질 수 있으며, 공통전극(156)은 인듐-틴-옥사이드(indium tin oxide: ITO)나 인듐-징크-옥사이드(indium zinc oxide: IZO)와 같은 투명도전물질로 기판(120) 전면에 걸쳐 형성될 수 있다.

[0056] 공통전극(156)은 다수의 공통배선(CL1 내지 CLm)에 연결되어 공통전압을 공급받는다. 여기서, 다수의 제 3 링크배선(167)은 하프 톤 마스크(173)를 이용하여 공통전극(156)과 동일층, 동일 물질로 이루어지는 제 1 층과 상기 제 1 층 상부의 제 2 층으로 이루어지며, 공통전극(156)에 공통 전압을 공급한다.

[0057] 화소전극(162)과 공통전극(156)은 화소영역에 서로 교대로 배치되고, 각각 데이터신호 및 공통전압을 인가받아 수평 전기장을 생성하고, 액정층(미도시)의 액정 분자는 수평 전기장에 의하여 재배열되어, 투과율 변화로 영상을 표시한다.

[0058] 특히, 하프 톤 마스크(173)를 이용하여 형성되는 공통전극(156)과 제 3 링크배선(167)에 대하여 도 6a 내지 도 6c를 참조하여 상세히 설명한다.

[0059] 도 6a 내지 도 6c는 도 4의 절단선 V-V에 따른 액정표시장치용 어레이기판에서 하프 톤 마스크(173)를 이용한 제 3 링크배선(167)의 제조공정을 순차적으로 나타내는 단면도이다.

[0060] 도 6a에 도시한 바와 같이, 보호층(165)이 형성된 기판(120) 상에 공통전극과 동일한 물질로 이루어지는 제 1 층(151)을 기판(120)의 전 영역 상에 증착하고, 제 1 층(151) 상부에 알루미늄(Al), 구리(Cu) 등과 같은 금속으로 구성되는 제 2 층(152)을 증착하여 이중 금속막을 형성한다.

[0061] 그 후, 하프 톤 마스크(173)를 이용하여 제 2 층(152) 상부에 감광층(174)을 형성한다. 여기서, 하프 톤 마스크(173)에는 조사된 광이 투과되는 영역, 광이 일부만 투과되는 영역, 광이 차단되는 영역이 마련되어 있으며, 하프 톤 마스크(173)를 투과하는 광만이 감광층(174)에 조사되게 되어 감광층 패턴이 형성된다. 따라서 공통전극(156)이 형성되는 영역 상에 감광층(174)이 하프 톤 패턴으로 형성된다.

[0062] 그 후, 도 6b에 도시한 바와 같이, 하프 톤 패턴 감광층(174)을 마스크로 하여 식각을 진행하여, 도 6c에 도시한 바와 같이, 투명도전물질인 제 1 층(151)으로 이루어진 공통전극(156)과, 투명도전물질로 이루어진 제 1 층(151)과 금속으로 구성되는 제 2 층(152)의 이중층으로 구성되는 제 3 링크배선(167)을 형성한다.

[0063] 전술한 제 1 링크배선(142)과 제 2 링크배선(157) 및 제 3 링크배선(167)은 게이트 절연막(145) 및 보호층(160)을 사이에 두고 서로 다른 층에서 제 1 링크배선(142) 사이에 제 2 링크배선(157)과 제 3 링크배선(167)이 위치되도록 형성된다. 이와 같은 구조는 제 1 내지 제 3 링크배선(142, 157, 167)을 평면적으로 서로 중첩되도록 설계하더라도 쇼트 불량이 발생 될 염려가 없으므로 최소 선폭에 제한받지 않고 밀집하게 설계할 수 있다. 따라서, 베젤(Bezel)영역을 줄일 수 있다.

[0064] 또한, 제 1 링크배선 내지 제 3 링크배선(142, 157, 167)은 동일 비저항 특성을 가지는 금속을 포함하여 형성함으로써, 데이터전압의 지연 편차를 방지할 수 있다.

[0065]

전술한 본 발명의 실시예는 본 발명의 일예로서, 본 발명의 정신에 포함되는 범위 내에서 자유로운 변형이 가능하다. 따라서, 본 발명은, 첨부된 특허 청구 범위 및 이와 등가되는 범위 내에서의 본 발명의 변형을 포함한다.

### 부호의 설명

[0066]

|                 |                |

|-----------------|----------------|

| 110 : 액정표시장치    | 120 : 제 1 기판   |

| 130 : 제 2 기판    | 140 : 게이트 전극   |

| 142 : 제 1 링크 배선 | 145 : 게이트 절연막  |

| 150 : 반도체층      | 151 : 제 1 층    |

| 152 : 제 2 층     | 154 : 개구부      |

| 155 : 소스 전극     | 156 : 공통 전극    |

| 157 : 제 2 링크 배선 | 160 : 드레인 전극   |

| 162 : 화소 전극     | 165 : 보호층      |

| 167 : 제 3 링크 배선 | 170 : 구동 접적회로  |

| 172 : 입력 패드     | 173 : 하프 톤 마스크 |

| 174 : 감광층       |                |

### 도면

#### 도면1

## 도면2

## 도면3

도면4

도면5

## 도면6a

## 도면6b

## 도면6c

|                |                                                                            |         |            |

|----------------|----------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 一种用于液晶显示器的阵列基板                                                             |         |            |

| 公开(公告)号        | <a href="#">KR1020140088935A</a>                                           | 公开(公告)日 | 2014-07-14 |

| 申请号            | KR1020120157838                                                            | 申请日     | 2012-12-31 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                   |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                  |         |            |

| 当前申请(专利权)人(译)  | LG显示器有限公司                                                                  |         |            |

| [标]发明人         | CHUNG EUI HYUN<br>정의현<br>LEE JOON DONG<br>이준동<br>JANG SUNG YONG<br>장성용     |         |            |

| 发明人            | 정의현<br>이준동<br>장성용                                                          |         |            |

| IPC分类号         | G02F1/1368 G02F1/1345 G02F1/1343                                           |         |            |

| CPC分类号         | G02F1/136286 G02F1/136213 G02F1/1368 G02F1/13458 G02F1/136227 G02F1/134336 |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                  |         |            |

### 摘要(译)

本发明涉及一种用于液晶显示器的阵列基板，包括：基板;多条栅极线和多条数据线形成在基板上，以便彼此交叉以限定多个像素区域;形成在多个像素区域中的每个像素区域中的薄膜晶体管;像素电极连接到薄膜晶体管;公共电极，具有至少一个对应于像素电极的开口;一种驱动集成电路，用于产生分别提供给多条栅极布线和多条数据布线的栅极信号和数据信号;多个第一连接配线，用于将栅极信号传送到多个栅极配线，并由与多个栅极配线相同的层和相同的材料形成;多个第二连接配线，位于第一连接配线之间，形成在与第一连接配线不同的层中，并将数据信号传输到多个数据配线;以及多个第三连接线，其位于第一和第二连接线之间，并且由与第一层上的公共电极和第二层相同的层上的相同材料形成。