공개특허 10-2020-0082598

(19) 대한민국특허청(KR)

(12) 공개특허공보(A)(11) 공개번호 10-2020-0082598

(43) 공개일자 2020년07월08일

- (51) 국제특허분류(Int. Cl.)

*G09G 3/36* (2006.01) *G02F 1/1362* (2006.01)

(52) CPC특허분류

*G09G 3/3614* (2013.01)

*G02F 1/136286* (2013.01)

(21) 출원번호 10-2018-0173332

(22) 출원일자 2018년12월31일

심사청구일자 없음

- (71) 출원인

엘지디스플레이 주식회사

서울특별시 영등포구 여의대로 128(여의도동)

(72) 발명자

장훈

경기도 파주시 월롱면 엘지로 245

박주언

경기도 파주시 월롱면 엘지로 245

(74) 대리인

네이트특허법인

전체 청구항 수 : 총 9 항

(54) 발명의 명칭 액정표시장치

### (57) 요 약

본 발명의 목적은 데이터 라인과 데이터 구동회로의 개수를 저감시키고, 개구율을 향상시킬 수 있는 액정표시장치를 제공하는 것이다.

이를 위하여 본 발명은 표시영역에 2행 6열로 배열되는 제 1 내지 제 12 화소와; 제 1 내지 제 6 화소의 상부와 제 7 내지 제 12 화소의 하부에 각각 형성된 제 1 및 제 4 게이트 라인과; 제 1 내지 제 6 화소의 하부와 제 7 내지 제 12 화소의 상부 사이에 형성된 제 2 및 제 3 게이트 라인과; 제 1 및 제 7 화소의 좌측과 제 6 및 제 12 화소의 우측에 각각 형성된 제 1 및 제 5 데이터 라인과; 제 2 및 제 8 화소의 좌측에 형성된 제 2 데이터 라인과; 제 3 및 제 9 화소의 우측에 형성된 제 3 데이터 라인과; 제 5 및 제 11 화소의 좌측에 형성된 제 4 데이터 라인을 포함하는 액정표시장치를 제공한다.

**대 표 도** - 도3a

(52) CPC특허분류

*G09G 2300/0426 (2013.01)*

*G09G 2300/0465 (2013.01)*

*G09G 2320/0209 (2013.01)*

*G09G 2320/0247 (2013.01)*

*G09G 2330/021 (2013.01)*

---

## 명세서

### 청구범위

#### 청구항 1

표시영역에 2행 6열로 배열되는 제 1 내지 제 12 화소와;

제 1 내지 제 6 화소의 상부와 제 7 내지 제 12 화소의 하부에 각각 형성된 제 1 및 제 4 게이트 라인과; 제 1 내지 제 6 화소의 하부와 제 7 내지 제 12 화소의 상부 사이에 형성된 제 2 및 제 3 게이트 라인과;

제 1 및 제 7 화소의 좌측과 제 6 및 제 12 화소의 우측에 각각 형성된 제 1 및 제 5 데이터 라인과; 제 2 및 제 8 화소의 좌측에 형성된 제 2 데이터 라인과; 제 3 및 제 9 화소의 우측에 형성된 제 3 데이터 라인과; 제 5 및 제 11 화소의 좌측에 형성된 제 4 데이터 라인을 포함하는 액정표시장치.

#### 청구항 2

제 1 항에 있어서,

제 1 화소 및 제 4 화소에 형성된 박막 트랜지스터는 상부에 형성된 제 1 게이트 라인과 연결되고,

제 2, 3, 5, 6 화소에 형성된 박막 트랜지스터는 하부에 형성된 제 2 게이트 라인과 연결되며, 제 8, 9, 11, 12 화소에 형성된 박막 트랜지스터는 상부에 형성된 제 3 게이트 라인과 연결되고,

제 7 화소 및 제 10 화소에 형성된 박막 트랜지스터는 하부에 형성된 제 4 게이트 라인과 연결되는 액정표시장치.

#### 청구항 3

제 2 항에 있어서,

상기 제 1 화소에 형성된 박막 트랜지스터는 좌측에 형성된 제 1 데이터 라인과 연결되고, 상기 제 7 화소에 형성된 박막 트랜지스터는 우측에 형성된 제 2 데이터 라인과 연결되며,

상기 제 2, 8 화소에 형성된 박막 트랜지스터는 좌측에 형성된 제 2 데이터 라인과 연결되고, 상기 제 3, 9 화소에 형성된 박막 트랜지스터는 우측에 형성된 제 3 데이터 라인과 연결되며,

상기 제 4 화소에 형성된 박막 트랜지스터는 우측에 형성된 제 4 데이터 라인과 연결되고, 상기 제 10 화소에 형성된 박막 트랜지스터는 좌측에 형성된 제 3 데이터 라인과 연결되며,

상기 제 5, 11 화소에 형성된 박막 트랜지스터는 좌측에 형성된 제 4 데이터 라인과 연결되고, 상기 제 6, 12 화소에 형성된 박막 트랜지스터는 우측에 형성된 제 5 데이터 라인과 연결되는 액정표시장치.

#### 청구항 4

제 3 항에 있어서,

상기 제 5, 6, 8, 9 화소에 형성된 박막 트랜지스터는 각각 인접한 제 6, 5, 9, 8 화소에 형성된 화소 전극과 연결되는 액정표시장치.

#### 청구항 5

제 4 항에 있어서,

상기 제 1 내지 제 4 데이터 라인 중 인접한 데이터 라인에 인가되는 데이터 신호의 극성은 서로 다르며, 데이터 신호의 극성이 매 프레임마다 반전되는 액정표시장치.

### 청구항 6

제 1 항 내지 제 5 항 중 어느 하나의 항에 있어서,

스토리지 커패시터는 상기 제 1 내지 제 12 화소에 형성된 박막 트랜지스터 상에 형성되는 액정표시장치.

### 청구항 7

제 6 항에 있어서,

상기 제 1, 4, 7, 10 화소들의 박막 트랜지스터가 형성된 공간에 인접한 상기 데이터 라인은 개구부에 볼록한 형태로 형성되고,

상기 제 2, 3, 5, 6, 8, 9, 11, 12 화소들의 박막 트랜지스터가 형성된 공간에 인접한 상기 데이터 라인은 개구부에 오목한 형태로 형성되는 액정표시장치.

### 청구항 8

제 1 항 내지 제 5 항 중 어느 하나의 항에 있어서,

상기 제 2 및 제 3 화소, 제 5 및 제 6 화소, 제 8 및 제 9 화소, 제 11 및 제 12 화소 사이에는 각각 터치구동 신호 라인이 형성된 액정표시장치.

### 청구항 9

제 1 항 내지 제 5 항 중 어느 하나의 항에 있어서,

상기 제 1, 4, 7, 10 화소는 적색을 표시하고, 상기 제 2, 5, 8, 11 화소는 녹색을 표시하며, 상기 제 3, 6, 9, 12 화소는 청색을 표시하는 액정표시장치.

## 발명의 설명

### 기술 분야

[0001] 본 발명은 액정표시장치에 관한 것으로, 특히 데이터 라인과 데이터 구동회로의 개수를 줄일 수 있는 액정표시장치에 관한 것이다.

### 배경 기술

[0003] 최근의 표시장치는 기존의 브라운관과 대비하여 얇고, 가벼우며, 소비전력이 작은 장점을 가진, 액정표시장치, 유기발광 다이오드 표시장치와 같은 평판 표시장치가 주류를 이루고 있다.

[0004] 이중 액정표시장치는 액정 및 박막 트랜지스터를 포함하는 액정표시패널과 액정표시패널 구동회로, 백라이트 유닛을 포함한다. 액정표시패널 구동회로에서 액정표시패널의 각각의 화소에 데이터 신호를 인가하면, 인가된 데이터 신호에 의해 액정의 배열 상태가 변하게 되며, 이에 따라 백라이트 유닛에서 발광한 빛의 투과율이 조절되어 영상을 표시할 수 있게 된다.

[0005] 그러나 액정표시패널의 각각의 화소에 데이터 신호를 인가하기 위해서는 화소 라인마다 데이터 라인을 구비해야 된다.

## 발명의 내용

### 해결하려는 과제

[0007]

본 발명의 목적은 데이터 라인과 데이터 구동회로의 개수를 저감시키고, 개구율을 향상시킬 수 있는 액정표시장치를 제공하는 것이다.

### 과제의 해결手段

[0009]

상기와 같은 목적을 달성하기 위하여 본 발명은, 표시영역에 2행 6열로 배열되는 제 1 내지 제 12 화소와; 제 1 내지 제 6 화소의 상부와 제 7 내지 제 12 화소의 하부에 각각 형성된 제 1 및 제 4 게이트 라인과; 제 1 내지 제 6 화소의 하부와 제 7 내지 제 12 화소의 상부 사이에 형성된 제 2 및 제 3 게이트 라인과; 제 1 및 제 7 화소의 좌측과 제 6 및 제 12 화소의 우측에 각각 형성된 제 1 및 제 5 데이터 라인과; 제 2 및 제 8 화소의 좌측에 형성된 제 2 데이터 라인과; 제 3 및 제 9 화소의 우측에 형성된 제 3 데이터 라인과; 제 5 및 제 11 화소의 좌측에 형성된 제 4 데이터 라인을 포함하는 액정표시장치를 제공한다

[0010]

그리고, 제 1 항에 있어서, 제 1 화소 및 제 4 화소에 형성된 박막 트랜지스터는 상부에 형성된 제 1 게이트 라인과 연결되고, 제 2, 3, 5, 6 화소에 형성된 박막 트랜지스터는 하부에 형성된 제 2 게이트 라인과 연결되며, 제 8, 9, 11, 12 화소에 형성된 박막 트랜지스터는 상부에 형성된 제 3 게이트 라인과 연결되고, 제 7 화소 및 제 10 화소에 형성된 박막 트랜지스터는 하부에 형성된 제 1 게이트 라인과 연결되는 액정표시장치를 제공한다.

[0011]

그리고, 상기 제 1 화소에 형성된 박막 트랜지스터는 좌측에 형성된 제 1 데이터 라인과 연결되고, 상기 제 7 화소에 형성된 박막 트랜지스터는 우측에 형성된 제 2 데이터 라인과 연결되며, 상기 제 2, 8 화소에 형성된 박막 트랜지스터는 좌측에 형성된 제 2 데이터 라인과 연결되고, 상기 제 3, 9 화소에 형성된 박막 트랜지스터는 우측에 형성된 제 3 데이터 라인과 연결되며, 상기 제 4 화소에 형성된 박막 트랜지스터는 우측에 형성된 제 4 데이터 라인과 연결되고, 상기 제 10 화소에 형성된 박막 트랜지스터는 좌측에 형성된 제 3 데이터 라인과 연결되며, 상기 제 5, 11 화소에 형성된 박막 트랜지스터는 좌측에 형성된 제 4 데이터 라인과 연결되고, 상기 제 6, 12 화소에 형성된 박막 트랜지스터는 우측에 형성된 제 5 데이터 라인과 연결되는 액정표시장치를 제공한다.

[0012]

그리고, 상기 제 5, 6, 8, 9 화소에 형성된 박막 트랜지스터는 각각 인접한 제 6, 5, 9, 8 화소에 형성된 화소 전극과 연결되는 액정표시장치를 제공한다.

[0013]

그리고, 상기 제 1 내지 제 4 데이터 라인 중 인접한 데이터 라인에 인가되는 데이터 신호의 극성을 서로 다르며, 데이터 신호의 극성이 매 프레임마다 반전되는 액정표시장치를 제공한다.

[0014]

그리고, 스토리지 커패시터는 상기 제 1 내지 제 12 화소에 형성된 박막 트랜지스터 상에 형성되는 액정표시장치를 제공한다.

[0015]

그리고, 상기 제 1, 4, 7, 10 화소들의 박막 트랜지스터가 형성된 공간에 인접한 상기 데이터 라인은 개구부에 볼록한 형태로 형성되고, 상기 제 2, 3, 5, 6, 8, 9, 11, 12 화소들의 박막 트랜지스터가 형성된 공간에 인접한 상기 데이터 라인은 개구부에 오목한 형태로 형성되는 액정표시장치를 제공한다.

[0016]

그리고, 상기 제 2 및 제 3 화소, 제 5 및 제 6 화소, 제 8 및 제 9 화소, 제 11 및 제 12 화소 사이에는 각각 터치구동 신호 라인이 형성된 액정표시장치를 제공한다.

[0017]

그리고, 상기 제 1, 4, 7, 10 화소는 적색을 표시하고, 상기 제 2, 5, 8, 11 화소는 녹색을 표시하며, 상기 제 3, 6, 9, 12 화소는 청색을 표시하는 액정표시장치를 제공한다.

## 발명의 효과

[0019]

이상 설명한 바와 같이 본 발명의 액정표시장치는, 제 2 및 제 3 화소, 제 5 및 제 6 화소, 제 8 및 제 9 화소, 제 11 및 제 12 화소 사이에 형성될 수 있는 데이터 라인을 생략 할 수 있어, 데이터 라인의 개수와 소스 드라이버 IC의 개수를 저감하고 액정표시장치의 제조 비용을 절감할 수 있다. 그리고 스토리지 커패시터 박막 트랜

지스터 상에 형성하고 개구부에 인접한 데이터 라인을 볼록 또는 오목한 형태로 형성하여, 개구율을 증가시키고 액정표시장치의 소비 전력을 줄일 수 있다. 또한, 컬럼 인버전 방식으로 구동하여 전력 소모를 줄이고, 화소는 도트 인버전 방식과 같이 표시되어 플리커 또는 크로스토크 등의 화면 왜곡을 방지할 수 있다.

### 도면의 간단한 설명

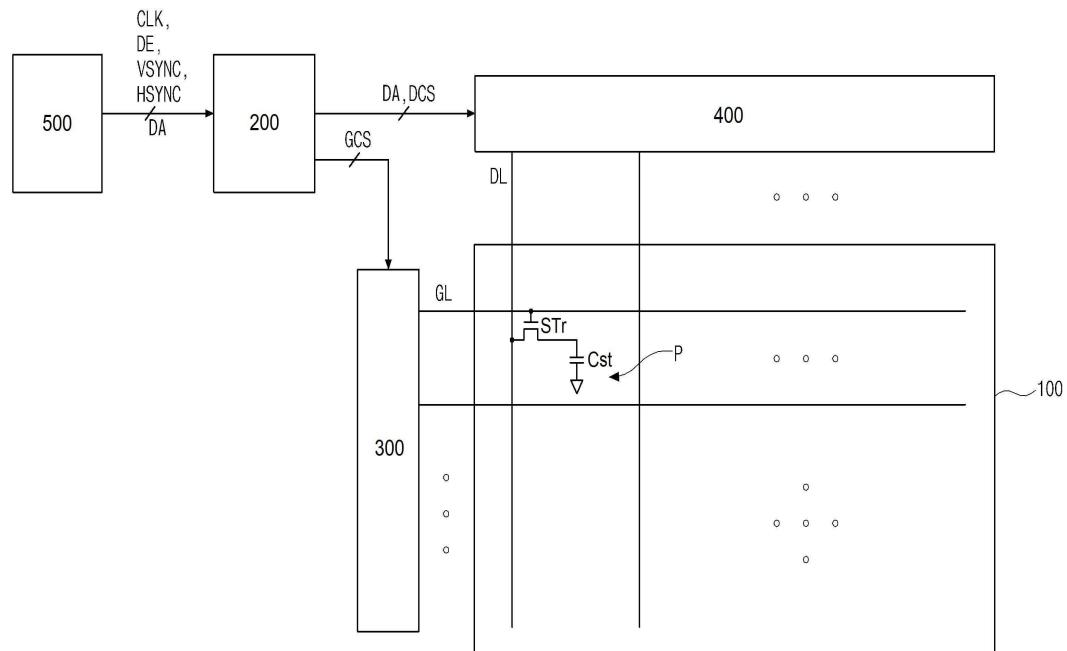

[0021] 도 1은 본 발명의 액정표시장치의 전체 구성을 나타낸 도면이다.

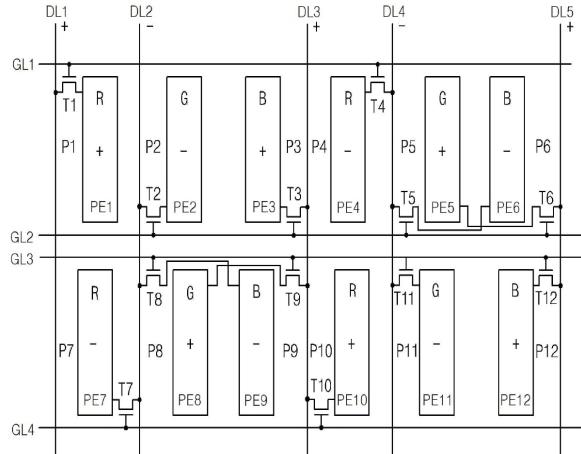

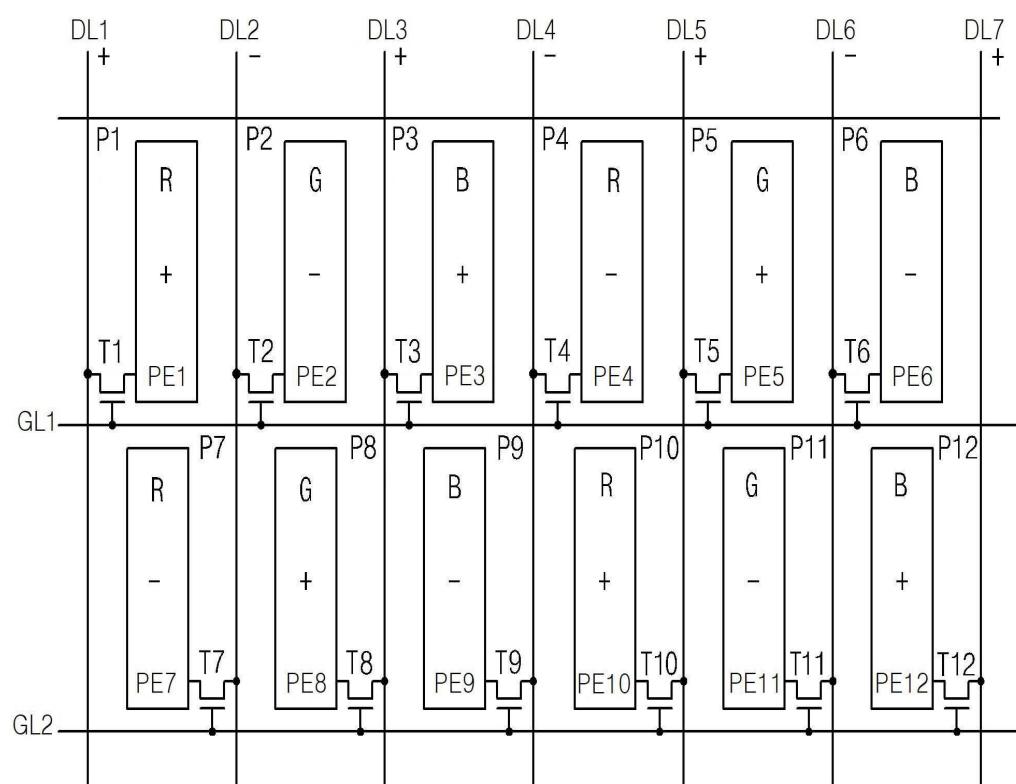

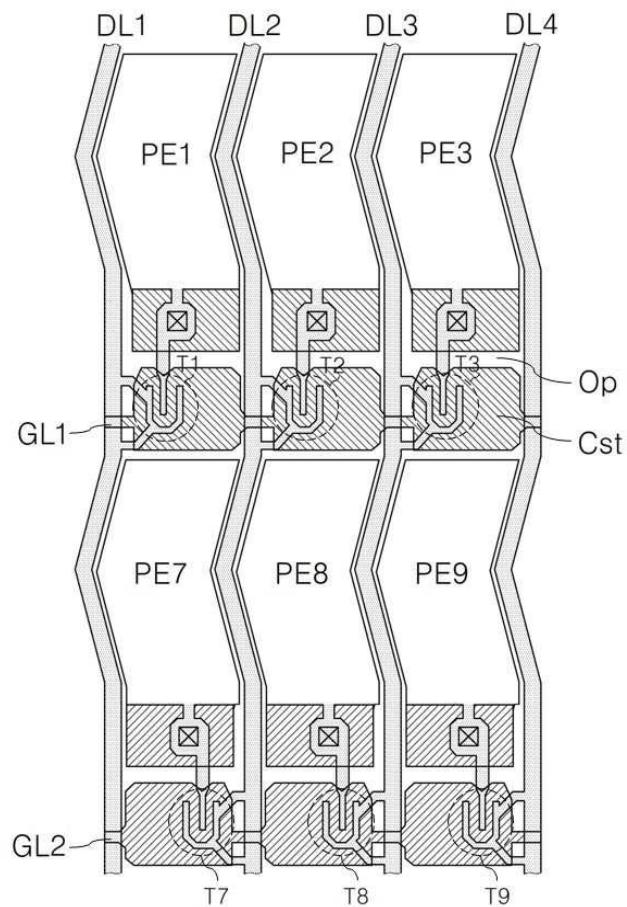

도 2a는 컬럼 인버전 방식으로 구동되는 액정표시패널을 나타낸 도면이며, 도 2b는 도 2a에 따른 액정표시패널 일부분의 화소영역의 구성을 나타낸 도면이다.

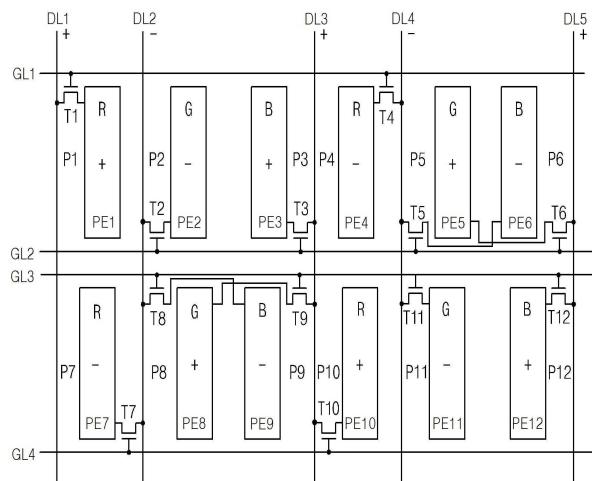

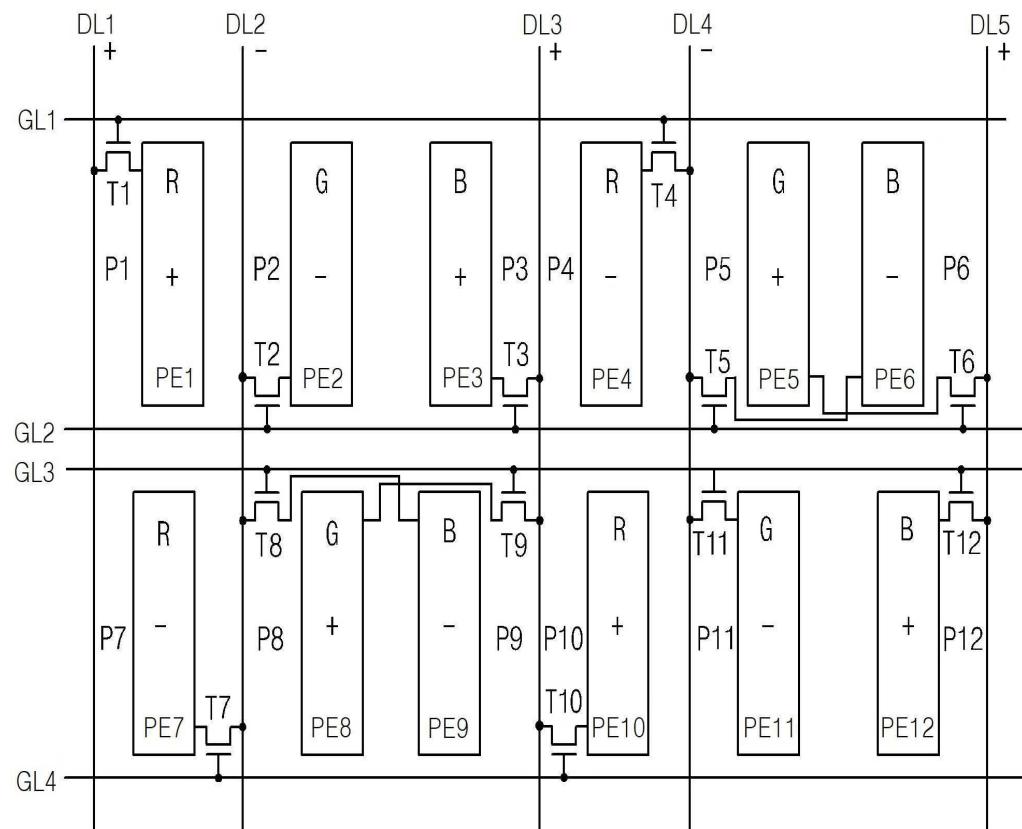

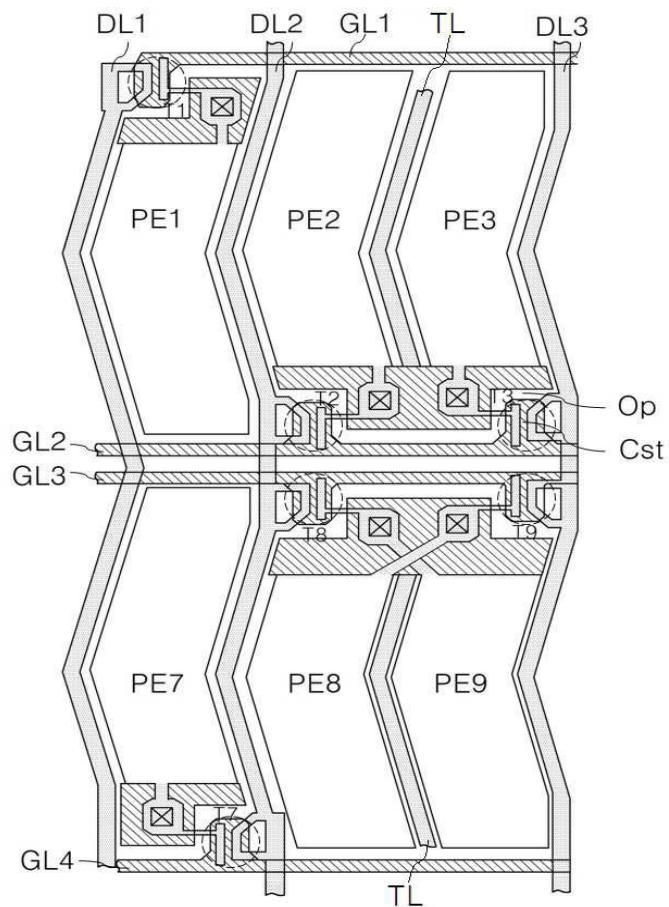

도 3a는 본 발명의 실시예에 따른 컬럼 인버전 방식으로 구동되는 액정표시패널을 나타낸 도면이며, 도 3b는 도 3a에 따른 액정표시패널 일부분의 화소영역의 구성을 나타낸 도면이다.

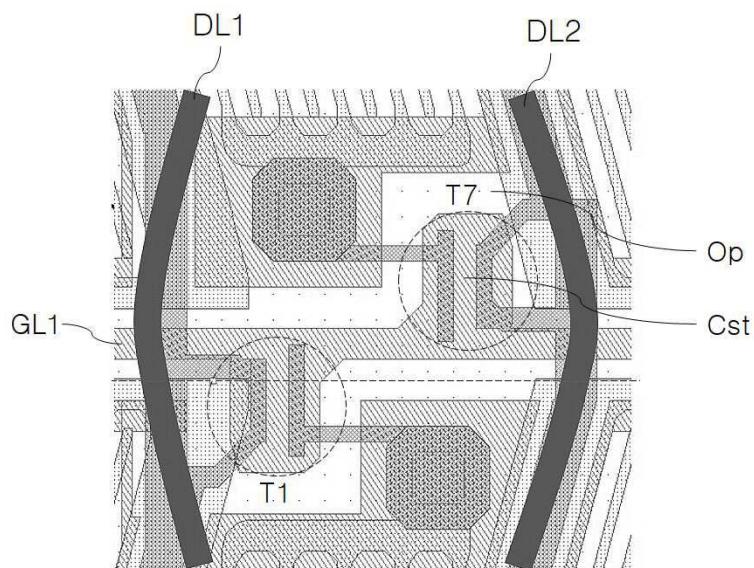

도 4a는 화소의 개구부 부근에서 볼록한 형태의 데이터 라인을 나타낸 도면이며, 도 4b는 화소의 개구부 부근에서 오목한 형태의 데이터 라인을 나타낸 도면이다.

### 발명을 실시하기 위한 구체적인 내용

[0022] 이하, 도면을 참조하여 본 발명에 따른 실시 예를 상세하게 설명한다.

[0024] 도 1은 본 발명의 액정표시장치의 전체 구성을 나타낸 도면이다.

[0025] 본 발명의 액정표시장치는 액정표시패널(100)과 타이밍 제어부(200), 게이트 구동부(300), 데이터 구동부(400)를 포함할 수 있다.

[0026] 액정표시패널(100)은 화소들이 매트릭스 형태로 이루어져 영상을 표시할 수 있고, 액정표시패널(100)의 제 1 기판에는 소정 간격 이격하여 평행하게 구성된 다수의 게이트 라인(GL)과, 게이트 라인(GL)과 교차하여 화소영역(P)을 정의하는 데이터 라인(DL)을 포함할 수 있다.

[0027] 다수의 화소영역(P)은 색상을 표시하기 위해, 적색, 녹색, 청색을 표시하는 화소를 포함할 수 있다. 적색, 녹색, 청색을 표시하는 화소는 게이트 라인(GL)이 배치된 가로 방향 또는 데이터 라인(DL)이 배치된 세로 방향을 따라 교대로 연속하여 배치될 수 있으며, 서로 연속하는 적색, 녹색, 청색을 표시하는 화소들을 묶어 하나의 영상 표시의 단위가 될 수 있다.

[0028] 게이트 라인(GL)과 데이터 라인(DL)의 교차점에는 데이터 신호에 따라 빛의 투과량을 조절하는 스위칭 트랜지스터(STr)와, 다음 프레임까지 데이터 신호의 전압을 유지하는 스토리지 커패시터(Cst)가 형성될 수 있다. 그리고 화소영역(P)에는 화소전극(미도시)과 공통전극(미도시)이 형성될 수 있고, 화소전극과 공통전극의 사이에는 액정층(미도시)이 형성될 수 있다. 또한, 화소전극은 스위칭 트랜지스터(STr)의 드레인 전극과 연결될 수 있다.

[0029] 게이트 라인(GL)을 통해 스위칭 트랜지스터(STr)를 턴-온(turn on) 시키는 게이트 신호가 인가된 후, 데이터 라인(DL)을 통해 영상 신호인 데이터 신호가 스위칭 트랜지스터(STr)의 소스 전극으로 인가되면, 스위칭 트랜지스터(STr)와 연결된 화소전극에 데이터 신호의 전압이 인가된다. 공통전극에는 공통전압(Vcom)이 인가되어 화소전극과 공통전극 사이에 전계가 발생하고, 전계의 크기에 따라 액정층 내부의 액정분자의 배열이 변하게 되어 백라이트에서 밝은 빛의 투과량이 결정될 수 있다.

[0030] 액정표시패널(100)의 제 2 기판에는 블랙 매트릭스(미도시), 컬러필터(미도시) 등이 형성될 수 있다. 블랙 매트릭스는 화소영역(P)의 경계마다 형성되어, 화소전극 주변에서의 빛샘을 억제하고 화소 간의 색 분리를 통해 색 순도를 높이며 외부 반사광을 줄여 명암비를 높일 수 있다.

[0031] 블랙 매트릭스 사이에는 색상을 표시하기 위해 컬러필터가 형성될 수 있다. 액정 표시장치의 백라이트에서 밝은 빛이 컬러필터를 통과함으로써 색상을 표시할 수 있게 된다. 컬러필터는 적색, 녹색, 청색의 안료를 포함하는 컬러필터 패턴을 형성하여, 액정 표시장치의 백라이트로부터 나온 백색광이 적색, 녹색, 청색의 컬러필터를 통과함으로써 색상을 표시할 수 있다.

[0032] 액정표시패널(100)은 화소영역(P)이 배치되는 표시영역과, 표시영역의 둘레를 따라 배치되며 표시패널 구동회로

를 포함하는 비표시영역을 포함할 수 있다.

[0033] 액정표시패널(100)은 자체적으로 발광할 수 없으므로, 별도로 빛을 공급해주는 장치인 백라이트 유닛(미도시)을 포함할 수 있다.

[0034] 백라이트 유닛은 광원과 이를 구동하는 백라이트 드라이버, 도광판, 반사판, 광학시트를 포함할 수 있다. 광원에는 냉음극 형광램프(CCFL), 외부전극 형광램프(EEFL), 발광 다이오드(LED)가 이용될 수 있으며, 이외에도 기타 빛을 액정표시패널(100)로 공급할 수 있는 장치를 모두 이용할 수 있다.

[0035] 도광판은 광원에서 발광한 빛을 액정표시패널(100)로 입사시키기 위하여 배치되며, 광원으로부터 입사된 빛이 전반사에 의해 도광판 내부를 진행하면서 골고루 퍼지게 되면서 액정표시패널(100)에 제공될 수 있다.

[0036] 반사판은 도광판의 하부에 위치하며, 도광판의 배면을 통과한 빛을 액정표시패널(100) 쪽으로 반사시킴으로써, 액정표시패널(100)로 입사되는 빛의 양을 증가시킬 수 있다.

[0037] 광학시트는 확산시트와 프리즘시트, 보호시트를 포함하며 도광판의 상부에 위치하고, 도광판을 통과한 빛을 확산 또는 집광하여 균일하게 액정표시패널(100)로 출사시킬 수 있다.

[0038] 타이밍 제어부(200)는 호스트 시스템(500)으로부터 영상 신호(DA), 클럭 신호(CLK), 타이밍 신호인 수평동기 신호(HSYNC), 수직동기 신호(VSYNC), 데이터 인에이블 신호(DE)를 입력 받을 수 있다.

[0039] 타이밍 제어부(200)는 호스트 시스템(500)으로부터 입력 받은 타이밍 신호(HSYNC, VSYNC, DE)를 이용하여, 게이트 구동부(300)의 동작을 제어하는 게이트 제어신호(GCS)와 데이터 구동부(400)의 동작을 제어하는 데이터 제어신호(DCS)를 생성한 후, 게이트 구동부(300) 및 데이터 구동부(400)로 각각 공급할 수 있다. 게이트 구동부(300) 및 데이터 구동부(400)는 타이밍 제어부(200)로부터 공급받은 게이트 제어신호(GCS) 및 데이터 제어신호(DCS)에 따라 영상 신호인 데이터 신호를 액정표시패널(100)로 공급하여 영상을 표시할 수 있게 한다.

[0040] 게이트 구동부(300)는 게이트 라인(GL)의 개수 만큼의 스테이지를 갖는 쉬프트 레지스터(미도시)를 포함할 수 있고, 쉬프트 레지스터에 포함되는 스테이지는 이전 단계의 스테이지와 종속적으로 연결될 수 있다.

[0041] 게이트 구동부(300)는 게이트 라인(GL)에 스위칭 트랜지스터(STr)를 턴-온(turn on) 시키는 게이트 하이 신호(VGH) 또는 스위칭 트랜지스터(STr)를 턴-오프(turn off) 시키는 게이트 로우 신호(VGL) 등의 게이트 신호를 생성하여 표시패널(100)에 공급할 수 있다.

[0042] 타이밍 제어부(200)로부터 공급받은 게이트 제어신호(GCS) 중 게이트 스타트 펄스신호(GSP)는 게이트 신호의 생성 시점을 지정하고, 게이트 출력 인에이블 신호(GOE)는 게이트 신호의 출력 시점을 지정하며, 게이트 쉬프트 클럭신호(GSC)는 게이트 라인(GL)에 순차적으로 게이트 신호를 인가할 수 있게 한다.

[0043] 게이트 구동부(300)는 게이트 스타트 펄스신호(GSP)를 게이트 쉬프트 클럭신호(GSC)에 따라 쉬프트 레지스터의 다음 단계의 스테이지로 쉬프트시켜, 게이트 라인(GL)에 스위칭 트랜지스터(STr)를 턴-온(turn on) 시키는 게이트 하이 신호(VGH)를 순차적으로 공급할 수 있다. 그리고 게이트 하이 신호(VGH)가 공급되지 않는 나머지 기간 동안에는 게이트 라인(GL)에 스위칭 트랜지스터(STr)를 턴-오프(turn off) 시키는 게이트 로우 신호(VGL)를 공급할 수 있다.

[0044] 게이트 구동부(300)는 표시패널(100) 안의 비표시영역에 형성되는 게이트 인 패널(gate in panel : GIP) 구조일 수 있으나, 이에 한정하지는 않는다.

[0045] 데이터 구동부(400)는 데이터 구동회로인 소스 드라이버 IC를 포함할 수 있다. 소스 드라이버 IC는 타이밍 제어부(200)로부터 데이터 제어신호(DCS)와 영상 데이터(DA)를 수신하여, 액정표시패널(100)에 1 수평 라인 단위로 데이터 신호를 출력할 수 있다. 그리고 소스 드라이버 IC는 s 개의 데이터 라인에 데이터 신호를 출력할 수 있다.

[0046] 타이밍 제어부(200)로부터 공급받은 데이터 제어신호(DCS) 중 소스 스타트 펄스신호(SSP)는 데이터 신호의 생성 시점을 지정하고, 소스 출력 인에이블 신호(SOE)는 데이터 신호의 출력 시점을 지정하며, 소스 쉬프트 클럭신호(SSC)는 데이터 라인(DL)에 순차적으로 게이트 신호를 인가할 수 있게 한다.

[0047] 데이터 구동부(400)는 소스 스타트 펄스신호(SSP)를 소스 쉬프트 클럭신호(SSC)에 따라 쉬프트 시켜 샘플링 신호를 발생할 수 있다. 그리고 데이터 구동부(400)는 영상 데이터(DA)를 샘플링 신호에 따라 래치하여 데이터 신호로 변경한 후, 소스 출력 인에이블 신호(SOE)에 응답하여 액정표시패널(100)의 수평 라인 단위로 데이터 신호

를 데이터 라인(DL)에 공급할 수 있다.

[0048] 이와 같은 구조에서는 액정표시패널(100)에 세로 방향으로 배치된 화소 라인마다 데이터 라인을 구비하고 있어야 한다. 즉, 액정표시패널(100)이 n 개의 행과 m 개의 열로 이루어진 화소를 가지고 있다면, n 개의 게이트 라인과 m 개의 데이터 라인이 필요하다. 그리고 s 개의 데이터 라인에 데이터 신호를 출력할 수 있는 소스 드라이버 IC는 n / s 개 만큼 필요하게 된다.

[0050] 도 2a는 컬럼 인버전 방식으로 구동되는 액정표시패널을 나타낸 도면이며, 도 2b는 도 2a에 따른 액정표시패널 일부분의 화소영역의 구성을 나타낸 도면이다.

[0051] 액정표시패널을 구동할 때에는 액정의 열화를 방지하고 영상의 표시 품질을 향상시키기 위하여, 일정한 단위로 데이터 신호의 극성을 반전하여 구동하는 인버전 구동 방식을 사용할 수 있다.

[0052] 인버전 구동 방식은 반전되는 단위에 따라, 액정표시패널의 가로 방향으로 위치한 화소 라인 별로 데이터 신호의 극성이 반전되는 라인 인버전 방식과, 액정표시패널의 세로 방향으로 위치한 화소 라인 별로 데이터 신호의 극성이 반전되는 컬럼 인버전 방식과, 가로 방향 및 세로 방향으로 인접한 화소 간에 데이터 신호의 극성이 반전되는 도트 인버전 방식으로 나눌 수 있다.

[0053] 이중 컬럼 인버전 방식은 이웃하는 데이터 라인간 공통전압(Vcom)이 반전되는 것으로, 공통전압(Vcom)이 고정되는 도트 인버전 방식보다 데이터 신호의 전압 변동폭이 작기 때문에 저전력으로 구동할 수 있는 장점이 있다.

[0054] 그리고 도트 인버전 방식은 전력 소모가 크지만 플리커(flicker) 또는 크로스토크(crosstalk)와 같은 화면의 왜곡에 대한 억제력이 다른 인버전 방식에 비해 효과적인 장점을 가진다.

[0055] 도 2a의 액정표시패널의 일부에는 가로 방향으로 위치한 화소 라인마다 하나의 게이트 라인(GL1~GL2)이 형성되고, 세로 방향으로 위치한 화소 라인마다 하나의 데이터 라인(DL1~DL7)이 형성되어 있다.

[0056] 첫 번째 게이트 라인(GL1)을 따라서는 제 1 내지 제 6 화소(P1~P6)에 형성된 박막 트랜지스터(T1~T6)의 소스 전극은 박막 트랜지스터의 좌측에 위치한 데이터 라인(DL1~DL6)과 연결되어 있다. 그리고 두 번째 게이트 라인(GL2)을 따라서는 제 7 내지 제 12 화소(P7~P12)에 형성된 박막 트랜지스터(T7~T12)의 소스 전극은 박막 트랜지스터의 우측에 위치한 데이터 라인(DL2~DL7)과 연결되어 있다.

[0057] 가로 방향의 게이트 라인(GL1~GL2)을 따라서 순차적으로 적색(R), 녹색(G), 청색(B)의 색상을 표시하는 화소가 연속하여 배치될 수 있다. 제 1 내지 제 12 화소(P1~P12)에 형성된 박막 트랜지스터(T1~T12)의 드레인 전극은 각각 자신의 화소에 형성된 화소전극(PE1~PE12)과 연결되고, 소스 전극에 인가된 데이터 신호는 화소전극(PE1~PE12)으로 전달되어 액정의 배열을 변화시킨다. 이에 따라 백라이트에서 발광한 빛의 투과량이 조절되며 색상을 표시할 수 있다. 그리고 색상을 표시하기 위해 각각의 화소(P1~P12)는 적색, 녹색, 청색의 컬러필터가 교대로 연속하여 형성될 수 있다.

[0058] 도 2a에서는 홀수 번째 데이터 라인들(DL1, DL3, DL5, DL7, ...)과 짝수 번째 데이터 라인들(DL2, DL4, DL6, ...)에 인가되는 데이터 신호의 극성이 서로 반대되도록 하는 컬럼 인버전 방식으로 구동된다. 그러나 홀수 번째 게이트 라인들(GL1, ...)을 따라 위치한 제 1 내지 제 6 화소(P1~P6)의 박막 트랜지스터(T1~T6)는 화소의 왼쪽에 위치한 데이터 라인(DL1~DL6)과 연결되고, 짝수 번째 게이트 라인들(GL2, ...)을 따라 위치한 제 7 내지 제 12 화소(P7~P12)의 박막 트랜지스터(T7~T12)는 화소의 오른쪽에 위치한 데이터 라인(DL2~DL7)과 연결되므로, 도 2a에서처럼 상, 하, 좌, 우로 인접하는 화소 간에 데이터 신호의 극성이 반전되는 도트 인버전 방식과 같이 나타날 수 있다. 이에 따라 컬럼 인버전 방식으로 구동하므로 전력 소모가 감소될 수 있고, 화소들은 도트 인버전 방식과 같이 나타나므로 플리커(flicker) 또는 크로스토크(crosstalk) 등이 표시되는 영상의 왜곡을 방지할 수 있다.

[0059] 한편 액정표시장치의 크기가 커지고 해상도가 높아질수록, 데이터 구동부에 포함되는 소스 드라이버 IC의 개수는 증가할 수 있다. 예를 들어, 8K 해상도의 Full UHD를 지원하는 액정표시장치는 가로 방향으로 7,680개, 세로 방향으로 4,320개의 화소를 가지며 각 화소에는 적색, 녹색, 청색을 표시하는 3개의 서브화소가 포함된다. 따라서 가로 방향으로 23,040개( $= 7,680 \times 3$ )의 서브화소가 포함되며, 데이터 라인의 개수도 23,040개만큼 구비되어야 한다. 그리고 1개의 소스 드라이버 IC가 s개의 채널을 가지면  $23,040 / s$  개만큼의 소스 드라이버 IC가 구비되어야 한다. 예를 들어 960개의 채널을 갖는 소스 드라이버 IC는 24개( $= 23,040 / 960$ ) 만큼 구비되어야 한다. 그러나 소스 드라이버 IC는 다른 소자에 비해 상대적으로 높은 비용을 갖기 때문에, 이와 같은 구조에서는 액정

표시장치의 제조 비용이 증가할 수 있다.

[0060] 그리고 박막 트랜지스터를 턴-오프(turn off) 한 후, 기생용량에 따른 캐apas에 의해 화소에 인가된 전압도 떨어질 수 있으므로, 화면이 깜빡이는 플리커 현상이 발생할 수 있다. 이를 방지하기 위하여 도 2b와 같이 화소영역(P)에 스토리지 커패시터(Cst)를 형성하여 화소에 인가된 전압을 다음 프레임까지 유지시킬 수 있다. 그러나 표시장치의 해상도가 높아질수록 화소영역의 크기가 감소하게 되므로, 스토리지 커패시터(Cst)가 개구부(Op)에서 차지하는 면적이 상대적으로 증가하며, 이에 따라 액정표시장치의 개구율이 저하될 수 있다. 이에 따라 백라이트에서 발광하여 액정층 내부로 입사되는 빛의 양이 줄어들게 되면서 액정표시장치의 전력 소모가 증가할 수 있다.

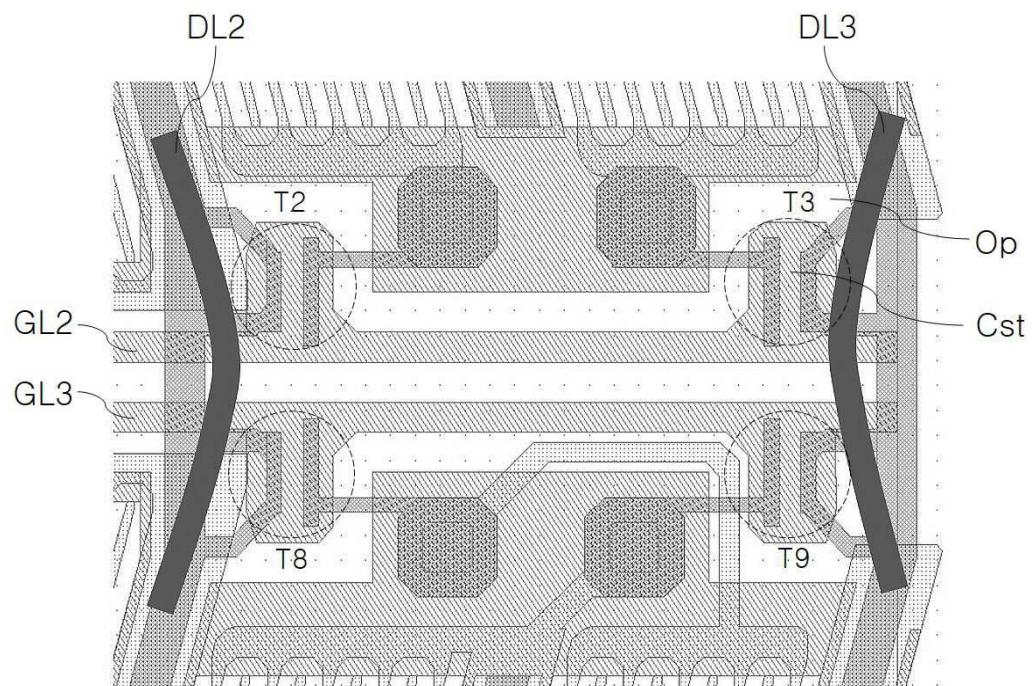

[0062] 도 3a는 본 발명의 실시예에 따른 컬럼 인버전 방식으로 구동되는 액정표시패널을 나타낸 도면이며, 도 3b는 도 3a에 따른 액정표시패널 일부분의 화소영역의 구성을 나타낸 도면이다.

[0063] 도 3a의 액정표시패널의 일부분에는 가로 방향으로 위치한 화소라인마다 게이트 라인(GL1~GL4)이 1개 또는 2개가 교대로 형성된다. 그리고 세로 방향으로 위치한 1개의 화소 라인 또는 2개의 화소라인마다 교대로 하나의 데이터 라인(DL1~DL5)이 형성되어 있다. 즉, 도 3a의 제 1 내지 제 6 화소(P1~P6)의 상부에는 하나의 게이트 라인(GL1)이 형성되어 있고, 제 7 내지 제 12 화소(P7~P12)의 하부에도 하나의 게이트 라인(GL4)이 형성되어 있으며, 제 1 내지 제 6 화소(P1~P6)와 제 7 내지 제 12 화소(P7~P12)의 사이에는 두 개의 게이트 라인(GL2, GL3)이 형성되어 있다. 그리고 제 1 데이터 라인(DL1)과 제 2 데이터 라인(DL2) 사이와 제 3 데이터 라인(DL3)과 제 4 데이터 라인(DL4) 사이에는 각각 하나의 화소(P1/P4/P7/P10)가 포함되어 있고, 제 2 데이터 라인(DL2)과 제 3 데이터 라인(DL3) 사이와 제 4 데이터 라인(DL4)과 제 5 데이터 라인(DL5) 사이에는 각각 두 개의 화소(P2, P3/P5, P6/P8, P9/P11, P12)가 포함되어 있다.

[0064] 도 3a에서 상부에 위치한 제 1 내지 제 6 화소(P1~P6) 중, 우선 제 1 화소(P1)의 상부에 위치한 박막 트랜지스터(T1)의 게이트 전극은 제 1 게이트 라인(GL1)과 연결되고, 소스 전극은 박막 트랜지스터(T1)의 좌측에 위치한 제 1 데이터 라인(DL1)과 연결되며, 드레인 전극은 제 1 화소(P1)에 위치한 화소전극(PE1)과 연결된다.

[0065] 제 2 화소(P2)의 하부에 위치한 박막 트랜지스터(T2)의 게이트 전극은 제 2 게이트 라인(GL2)과 연결되고, 소스 전극은 박막 트랜지스터(T2)의 좌측에 위치한 제 2 데이터 라인(DL2)과 연결되며, 드레인 전극은 제 2 화소(P2)에 위치한 화소전극(PE2)과 연결된다.

[0066] 제 3 화소(P3)의 하부에 위치한 박막 트랜지스터(T3)의 게이트 전극은 제 2 게이트 라인(GL2)과 연결되고, 소스 전극은 박막 트랜지스터(T3)의 우측에 위치한 제 3 데이터 라인(DL3)과 연결되며, 드레인 전극은 제 3 화소(P3)에 위치한 화소전극(PE3)과 연결된다.

[0067] 제 4 화소(P4)의 상부에 위치한 박막 트랜지스터(T4)의 게이트 전극은 제 1 게이트 라인(GL1)과 연결되고, 소스 전극은 박막 트랜지스터(T4)의 우측에 위치한 제 4 데이터 라인(DL4)과 연결되며, 드레인 전극은 제 4 화소(P4)에 위치한 화소전극(PE4)과 연결된다.

[0068] 제 5 화소(P5)의 하부에 위치한 박막 트랜지스터(T5)의 게이트 전극은 제 2 게이트 라인(GL2)과 연결되고, 소스 전극은 박막 트랜지스터(T5)의 좌측에 위치한 제 4 데이터 라인(DL4)과 연결되며, 드레인 전극은 제 6 화소(P6)에 위치한 화소전극(PE6)과 연결된다.

[0069] 제 6 화소(P6)의 하부에 위치한 박막 트랜지스터(T6)의 게이트 전극은 제 2 게이트 라인(GL2)과 연결되고, 소스 전극은 박막 트랜지스터(T6)의 우측에 위치한 제 5 데이터 라인(DL5)과 연결되며, 드레인 전극은 제 5 화소(P5)에 위치한 화소전극(PE5)과 연결된다.

[0070] 제 5 화소(P5) 및 제 6 화소(P6)에 위치한 박막 트랜지스터(T5, T6)는 각각 인접한 화소(P6, P5)에 위치한 화소전극(PE6, PE5)과 연결되는 것이 특징이다.

[0071] 하부에 위치한 제 7 내지 제 12 화소(P7~P12) 중, 우선 제 7 화소(P7)의 하부에 위치한 박막 트랜지스터(T7)의 게이트 전극은 제 4 게이트 라인(GL4)과 연결되고, 소스 전극은 박막 트랜지스터(T7)의 우측에 위치한 제 2 데이터 라인(DL2)과 연결되며, 드레인 전극은 제 7 화소(P7)에 위치한 화소전극(PE7)과 연결된다. 제 7 화소(P7)는 제 1 화소(P1)와 대칭적인 구조를 이루고 있다.

[0072] 제 8 화소(P8)의 상부에 위치한 박막 트랜지스터(T8)의 게이트 전극은 제 3 게이트 라인(GL3)과 연결되고, 소스

전극은 박막 트랜지스터(T8)의 좌측에 위치한 제 2 데이터 라인(DL2)과 연결되며, 드레인 전극은 제 9 화소(P9)에 위치한 화소전극(PE9)과 연결된다.

[0073] 제 9 화소(P9)의 상부에 위치한 박막 트랜지스터(T9)의 게이트 전극은 제 3 게이트 라인(GL3)과 연결되고, 소스 전극은 박막 트랜지스터(T8)의 우측에 위치한 제 3 데이터 라인(DL3)과 연결되며, 드레인 전극은 제 8 화소(P8)에 위치한 화소전극(PE8)과 연결된다.

[0074] 제 8 화소(P8) 및 제 9 화소(P9)에 위치한 박막 트랜지스터(T8, T9)는 각각 인접한 화소(P9, P8)에 위치한 화소 전극(PE9, PE8)과 연결되는 것이 특징이며, 제 5 화소(P5) 및 제 6 화소(P6)와 대칭적인 구조를 이루고 있다.

[0075] 제 10 화소(P10)의 하부에 위치한 박막 트랜지스터(T10)의 게이트 전극은 제 4 게이트 라인(GL4)과 연결되고, 소스 전극은 박막 트랜지스터(T10)의 좌측에 위치한 제 3 데이터 라인(DL3)과 연결되며, 드레인 전극은 제 10 화소(P10)에 위치한 화소전극(PE10)과 연결된다. 제 10 화소(P10)는 제 4 화소(P4)와 대칭적인 구조를 이루고 있다.

[0076] 제 11 화소(P11)의 상부에 위치한 박막 트랜지스터(T11)의 게이트 전극은 제 3 게이트 라인(GL3)과 연결되고, 소스 전극은 박막 트랜지스터(T11)의 좌측에 위치한 제 4 데이터 라인(DL4)과 연결되며, 드레인 전극은 제 11 화소(P11)에 위치한 화소전극(PE11)과 연결된다.

[0077] 제 12 화소(P12)의 상부에 위치한 박막 트랜지스터(T12)의 게이트 전극은 제 3 게이트 라인(GL3)과 연결되고, 소스 전극은 박막 트랜지스터(T12)의 우측에 위치한 제 5 데이터 라인(DL5)과 연결되며, 드레인 전극은 제 12 화소(P12)에 위치한 화소전극(PE12)과 연결된다. 제 11 화소(P11) 및 제 12 화소(P12)는 제 2 화소(P2) 및 제 3 화소(P3)와 대칭적인 구조를 이루고 있다.

[0078] 본 발명에 따른 게이트 라인은, 도 3a와 같이 제 1 및 제 4 게이트 라인(GL1, GL4)이 가로 방향의 화소 라인을 따라 각각 하나씩 배치되고, 제 2 및 제 3 게이트 라인(GL2, GL3)이 가로 방향의 화소 라인을 따라 2개씩 같이 배치되는 구조가 반복되어 형성된다.

[0079] 그리고 제 2 및 제 3 화소(P2, P3) 사이, 제 5 및 제 6 화소(P5, P6) 사이, 제 8 및 제 9 화소(P8, P9) 사이, 제 11 및 제 12 화소(P11, P12) 사이에는 데이터 라인이 형성되지 않는다.

[0080] 본 발명은 이와 같은 제 1 내지 제 12 화소(P1~P12)가 반복적으로 형성되어 표시영역을 이루고 있다.

[0081] 이에 따라 표시패널에 형성되는 데이터 라인의 개수를 저감할 수 있고, 데이터 라인의 개수가 줄어들게 되므로 이와 연결되는 소스 드라이버 IC의 개수 또한 저감할 수 있는 효과를 가진다. 특히 도 3a와 같이 3개의 화소 당 1개의 데이터 라인을 생략할 수 있으므로, 소스 드라이버 IC의 개수를 3분 2로 축소할 수 있다. 예를 들어, 8K 해상도의 Full UHD를 지원하는 액정표시장치에서는 가로 방향으로 23,040개의 서브화소가 포함되지만, 본 발명을 적용하면 데이터 라인은 15,360개( $= 23,040 \times 2 / 3$ )를 필요로 하고, 960개의 채널을 갖는 소스 드라이버 IC는 16개( $=15,360 / 960$ )를 필요로 하게 된다. 이에 따라, 소스 드라이버 IC에 대한 비용을 줄일 수 있어 액정표시장치의 제조 비용을 절감할 수 있다.

[0082] 제 2 및 제 3 화소(P2, P3) 사이, 제 5 및 제 6 화소(P5, P6) 사이, 제 8 및 제 9 화소(P8, P9) 사이, 제 11 및 제 12 화소(P11, P12) 사이에 데이터 라인을 생략하고 도 3b와 같이 터치구동 신호 라인(TL)을 형성한 후, 터치구동 신호 또는 플로팅 신호를 인가하여 터치스크린 표시패널로 이용할 수 있다. 이때 상기 화소 사이에 형성되는 터치구동 신호 라인(TL)과 소스 드라이버 IC를 연결할 필요가 없으므로, 터치구동 신호 라인(TL)은 소스 드라이버 IC 개수의 감소에 영향을 미치지 않게 된다.

[0083] 그리고 제 1 및 제 4 화소(P1, P4), 제 7 및 제 10 화소(P7, P10)와 같이, 상하로 인접하는 화소의 박막 트랜지스터들이 연결되는 데이터 라인을 서로 다르게 구성하고, 제 5 및 제 6 화소(P5, P6), 제 8 및 제 9 화소(P8, P9)와 같이 좌우로 인접하는 화소끼리 화소전극과 연결되는 박막 트랜지스터를 서로 엇갈리게 구성함으로써, 인접한 화소마다 데이터 신호의 극성을 다르게 형성할 수 있다. 이에 따라 컬럼 인버전 방식으로 구동하여 전력 소모를 방지하면서도, 화소에 인가되는 데이터 신호의 극성은 도트 인버전 방식과 같이 나타나 플리커 또는 크로스토크를 방지할 수 있다.

[0084] 본 발명은 도 3b와 같이 화소에 형성된 박막 트랜지스터(T1, T2, T3, T7, T8, T9) 상에만 스토리지 커패시터(Cst)를 형성하므로, 도 2b에서처럼 스토리지 커패시터가 화소전극이 형성되지 않는 공간에 구비될 때 보다, 개구부(Op)에서 스토리지 커패시터(Cst)가 차지하는 면적을 줄일 수 있다. 이에 따라 개구율을 향상시킬 수 있게

된다.

[0085] 도 4a는 화소의 개구부 부근에서 볼록한 형태의 데이터 라인을 나타낸 도면이다. 개구부(0p)에서 스토리지 커페시터(Cst)가 차지하는 면적을 저감시키기 위하여, 박막 트랜지스터(T1, T7)와 스토리지 커페시터(Cst)를 데이터 라인과 인접하여 형성할 수 있다.

[0086] 제 1 트랜지스터(T1)와 제 7 트랜지스터(T7)가 인접하여 형성된 것을 나타내었지만, 도 3a에서 서로 인접하여 형성되는 제 4 트랜지스터(T4)와 제 10 트랜지스터(T10)도 동일하게 적용된다. 본 발명은 개구부 부근의 데이터 라인을 '()'와 같이 볼록한 형태로 형성하고, 이에 따라 양 데이터 라인의 중앙에 생성된 공간에 박막 트랜지스터(T1, T7)와 스토리지 커페시터(Cst)를 형성함으로써 개구부(0p)의 면적을 증가시킬 수 있다.

[0087] 도 4b는 화소의 개구부 부근에서 오목한 형태의 데이터 라인을 나타낸 도면이다.

[0088] 제 2 및 제 3 트랜지스터(T2, T3)와 제 8 및 제 9 트랜지스터(T8, T9)가 인접하여 형성된 것을 나타내었지만, 도 3a에서 서로 인접하여 형성되는 제 5 및 제 6 트랜지스터(T5, T6)와 제 10 및 제 11 트랜지스터(T10, T11)에도 동일하게 적용된다. 본 발명은 개구부 부근의 데이터 라인을 '()'와 같이 오목한 형태로 형성하고, 이에 따라 양 데이터 라인의 가장자리에 생성된 공간에 박막 트랜지스터(T2, T3, T8, T9)와 스토리지 커페시터(Cst)를 형성함으로써 개구부(0p)의 면적을 증가시킬 수 있다. 이에 따라 개구율을 향상시켜 백라이트에서 발광하는 빛의 양을 줄일 수 있기 때문에, 액정표시장치의 전력 소모를 저감시킬 수 있다.

[0090] 이와 같이 본 발명은 상기 실시 예로 한정되지 않고, 본 발명의 취지를 벗어나지 않고 효과를 저해하지 않는 한도 내에서 다양하게 변경하여 실시할 수 있다.

### 부호의 설명

100 : 액정표시패널 200: 타이밍 제어부

300 : 게이트 구동부 400 : 데이터 구동부

500 : 호스트 시스템

GL1 ~ GL4 : 제 1 내지 제 4 게이트 라인

DL1 ~ DL7 : 제 1 내지 제 7 데이터 라인

P1 ~ P12 : 제 1 내지 제 12 화소

T1 ~ T12 : 제 1 내지 제 12 박막 트랜지스터

PE1 ~ PE12 : 제 1 내지 제 12 화소전극

Cst : 스토리지 커페시터

## 도면

## 도면1

## 도면2a

도면2b

## 도면3a

도면3b

도면4a

도면4b

|                |                                                                                                 |         |            |

|----------------|-------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 液晶显示装置                                                                                          |         |            |

| 公开(公告)号        | KR1020200082598A                                                                                | 公开(公告)日 | 2020-07-08 |

| 申请号            | KR1020180173332                                                                                 | 申请日     | 2018-12-31 |

| [标]申请(专利权)人(译) | 乐金显示有限公司                                                                                        |         |            |

| 申请(专利权)人(译)    | LG显示器有限公司                                                                                       |         |            |

| [标]发明人         | 장훈<br>박주언                                                                                       |         |            |

| 发明人            | 장훈<br>박주언                                                                                       |         |            |

| IPC分类号         | G09G3/36 G02F1/1362                                                                             |         |            |

| CPC分类号         | G09G3/3614 G02F1/136286 G09G2300/0426 G09G2300/0465 G09G2320/0209 G09G2320/0247<br>G09G2330/021 |         |            |

**摘要(译)**

本发明的目的是提供一种能够减少数据线和数据驱动电路的数量并提高开口率的液晶显示装置。为此,本发明包括在显示区域中以两行六列布置的第一至第十二像素;第一和第四栅极线分别形成在第一至第六像素的上部和第七至第十二像素的下部上;在第一至第六像素的下部与第七至第十二像素的上部之间形成第二和第三栅极线;第一和第五数据线分别形成在第一和第七像素的左侧以及第六和第十二像素的右侧;第二数据线形成在第二像素和第八像素的左侧;第三数据线形成在第三和第九像素的右侧;提供了一种液晶显示器,包括形成在第五像素和第十一像素的左侧上的第四数据线。