(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(51) Int. Cl.

G09G 3/36 (2006.01)

(11) 공개번호 10-2007-0009295

(43) 공개일자 2007년01월18일

(21) 출원번호 10-2005-0064446

(22) 출원일자 2005년07월15일

심사청구일자 없음

(71) 출원인 삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자 주승용

경기 성남시 분당구 구미동 무지개마을주공4단지아파트 404동1303호

박기찬

경기 안양시 동안구 평안동 초원럭키아파트 506동 1501호

이동엽

경기 시흥시 대야동 278번지 벽산 아파트 103동 1104호

(74) 대리인 박영우

전체 청구항 수 : 총 7 항

(54) 소스 회로 및 이를 구비한 액정표시장치

(57) 요약

데이터 충전시간을 충분히 확보함과 동시에 회로 구현을 간단화 하기 위한 소스 회로 및 이를 구비한 액정표시장치가 개시된다. 소스 회로는 샘플링 래치, 홀딩 래치, 제1 스위치, 제2 스위치 및 디지털 아날로그 변환기를 포함한다. 샘플링 래치는 입력된 데이터신호를 샘플링한다. 홀딩 래치는 샘플링 래치에서 출력된 데이터신호를 일정시간 동안 래치한다. 제1 스위치는 제1 선택제어신호에 기초하여 래치된 데이터신호를 제1 레벨로 쉬프팅시킨다. 제2 스위치는 제2 선택제어신호에 기초하여 제1 레벨로 쉬프팅된 데이터신호를 제2 레벨로 쉬프팅시킨다. 디지털 아날로그 변환기는 레벨 쉬프팅된 데이터신호를 아날로그 형태의 데이터전압으로 변환하여 출력한다. 이에 따라서, 1H 구간 중 구동 편차를 보상하는 보상 구간 동안 래치된 데이터신호를 제1 및 제2 레벨로 쉬프팅함으로써 기존 데이터 충전시간을 유지하면서 소스 회로를 간단하게 구현 할 수 있다.

**대표도**

도 4

**특허청구의 범위**

**청구항 1.**

입력된 데이터신호를 샘플링하는 샘플링 래치;

상기 샘플링 래치에서 출력된 데이터신호를 일정시간 동안 래치하는 홀딩 래치;

제1 선택제어신호에 기초하여 래치된 데이터신호를 제1 레벨로 쉬프팅시키는 제1 스위치;

제2 선택제어신호에 기초하여 상기 제1 레벨로 쉬프팅된 데이터신호를 제2 레벨로 쉬프팅시키는 제2 스위치;

레벨 쉬프팅된 데이터신호를 아날로그 형태의 데이터전압으로 변환하여 출력하는 디지털 아날로그 변환기를 포함하는 것을 특징으로 하는 소스 회로.

## 청구항 2.

제1항에 있어서, 상기 아날로그 형태의 데이터전압을 증폭하여 출력하는 버퍼를 더 포함하며,

상기 제1 및 제2 선택제어신호는 상기 버퍼의 구동 편차를 보상하는 보상구간동안 상기 제1 및 제2 스위치에 각각 입력되는 것을 특징으로 하는 소스 회로.

## 청구항 3.

복수의 게이트 배선들과 복수의 소스 배선들에 의해 정의된 복수의 화소부들이 형성된 표시 영역과, 상기 표시 영역을 둘러싸는 주변 영역으로 이루어진 액정표시패널;

외부로부터 데이터신호가 입력되며, 제1 선택제어신호 및 제2 선택제어신호를 출력하는 제어부; 및

상기 데이터신호를 아날로그형태의 데이터전압으로 변환하여 상기 소스 배선들에 출력하는 소스 회로부를 포함하며,

상기 소스 회로부는

입력된 데이터신호를 일정시간 동안 래치하는 래치;

상기 제1 선택제어신호에 기초하여 래치된 데이터신호를 제1 레벨로 쉬프팅시키는 제1 스위치;

상기 제2 선택제어신호에 기초하여 상기 제1 레벨로 쉬프팅된 데이터신호를 제2 레벨로 쉬프팅시키는 제2 스위치;

레벨 쉬프팅된 데이터신호를 상기 데이터전압으로 변환하여 출력하는 디지털 아날로그 변환기; 및

상기 데이터전압을 증폭하여 출력하는 버퍼를 포함하는 것을 특징으로 하는 액정표시장치.

## 청구항 4.

제3항에 있어서, 상기 제어부는 상기 제1 및 제2 선택제어신호를 1H 구간 중 상기 버퍼의 구동 편차를 보상하는 보상 구간 동안 상기 제1 및 제2 스위치에 각각 제공하는 것을 특징으로 하는 액정표시장치.

## 청구항 5.

제3항에 있어서, 상기 소스 회로부는 상기 주변 영역 중 제1 주변 영역에 집적되는 것을 특징으로 하는 액정표시장치.

## 청구항 6.

제3항에 있어서, 상기 게이트 배선들에 게이트 신호들을 출력하는 게이트 회로부를 더 포함하는 것을 특징으로 하는 액정표시장치.

## 청구항 7.

제6항에 있어서, 상기 게이트 회로부는 상기 주변 영역 중 제2 주변 영역에 접적되는 것을 특징으로 하는 액정표시장치.

**명세서**

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 소스 회로 및 이를 구비한 액정표시장치에 관한 것으로, 보다 상세하게는 데이터 충전시간을 충분히 확보함과 동시에 회로 구현을 간단화하기 위한 소스 회로 및 이를 구비한 액정표시장치에 관한 것이다.

일반적으로 액정표시장치는 액정표시패널과 상기 액정표시패널을 구동하기 위한 구동장치를 포함한다. 상기 액정표시패널은 복수의 스위칭 소자들이 배열된 어레이 기판과, 상기 어레이 기판에 대향하는 대향 기판과, 상기 어레이 기판과 대향 기판 사이에 개재된 액정층을 포함한다.

상기 구동장치는 상기 스위칭 소자들을 구동하기 위한 구동신호들을 출력한다. 구체적으로, 스위칭 소자를 턴-온시키는 게이트 신호를 출력하는 게이트 구동부와, 상기 스위칭 소자에 연결된 화소 전극에 인가되는 데이터 신호를 출력하는 소스 구동부를 포함한다.

최근 중소형 액정표시장치에서는 상기 게이트 구동부와 소스 구동부를 상기 액정표시패널, 즉 상기 어레이 기판 상에 접적하여 제품의 크기를 줄이기는 기술이 적용되고 있다. 상기 어레이 기판은 복수의 스위칭 소자들이 형성된 표시 영역과, 상기 표시 영역을 둘러싸는 주변 영역으로 이루어지며, 상기 게이트 구동부 및 소스 구동부는 상기 주변 영역에 접적된다.

#### 발명이 이루고자 하는 기술적 과제

이에 본 발명의 기술적 과제는 이러한 점에서 착안된 것으로, 본 발명의 목적은 데이터 충전시간을 충분히 확보함과 동시에 구현을 간단화하기 위한 소스 회로를 제공하는 것이다.

본 발명의 다른 목적은 상기 소스 회로를 구비한 액정표시장치를 제공하는 것이다.

#### 발명의 구성

상기한 본 발명의 목적을 실현하기 위한 실시예에 따른 소스 회로는 샘플링 래치, 홀딩 래치, 제1 스위치, 제2 스위치 및 디지털 아날로그 변환기를 포함한다. 상기 샘플링 래치는 입력된 데이터신호를 샘플링한다. 상기 홀딩 래치는 상기 샘플링 래치에서 출력된 데이터신호를 일정시간 동안 래치한다. 상기 제1 스위치는 제1 선택제어신호에 기초하여 래치된 데이터신호를 제1 레벨로 쉬프팅시킨다. 상기 제2 스위치는 제2 선택제어신호에 기초하여 상기 제1 레벨로 쉬프팅된 데이터신호를 제2 레벨로 쉬프팅시킨다. 상기 디지털 아날로그 변환기는 레벨 쉬프팅된 데이터신호를 아날로그 형태의 데이터전압으로 변환하여 출력한다.

상기 소스 회로는 상기 아날로그 형태의 데이터전압을 증폭하여 출력하는 버퍼를 더 포함하며, 상기 제1 및 제2 선택제어신호는 상기 버퍼의 구동 편차를 보상하는 보상구간동안 상기 제1 및 제2 스위치에 각각 입력된다.

상기한 본 발명의 다른 목적은 액정표시장치는 액정표시패널, 제어부 및 소스 회로부를 포함한다. 상기 액정표시패널은 복수의 게이트 배선들과 복수의 소스 배선들에 의해 정의된 복수의 화소부들이 형성된 표시 영역과, 상기 표시 영역을 둘러

싸는 주변 영역으로 이루어진다. 상기 제어부는 외부로부터 데이터신호가 입력되며, 제1 선택제어신호 및 제2 선택제어신호를 출력한다. 상기 소스 회로부는 상기 데이터신호를 아날로그형태의 데이터전압으로 변환하여 상기 소스 배선들에 출력한다. 상기 소스 회로부는 입력된 데이터신호를 일정시간 동안 래치하는 래치와, 상기 제1 선택제어신호에 기초하여 래치된 데이터신호를 제1 레벨로 쉬프팅 시키는 제1 스위치와, 상기 제2 선택제어신호에 기초하여 상기 제1 레벨로 쉬프팅된 데이터신호를 제2 레벨로 쉬프팅 시키는 제2 스위치와 레벨 쉬프팅된 데이터신호를 상기 데이터전압으로 변환하여 출력하는 디지털 아날로그 변환기 및 상기 데이터전압을 증폭하여 출력하는 버퍼를 포함한다. 상기 제어부는 상기 제1 및 제2 선택제어신호를 1H 구간 중 상기 버퍼의 구동 편차를 보상하는 보상 구간 동안 상기 제1 및 제2 스위치에 각각 제공한다.

바람직하게 상기 소스 회로부는 상기 주변 영역 중 제1 주변 영역에 접적된다.

이러한 소스 회로 및 이를 구비한 액정표시장치에 의하면, 1H 구간 중 증폭부의  $V_{th}$ 를 보상하는 구간 동안 래치된 데이터신호를 제1 및 제2 레벨로 쉬프팅함으로써 데이터 충전시간을 충분히 확보하면서 소스 회로를 간단하게 구현할 수 있다.

이하, 첨부한 도면을 참조하여, 본 발명을 보다 상세하게 설명하고자 한다.

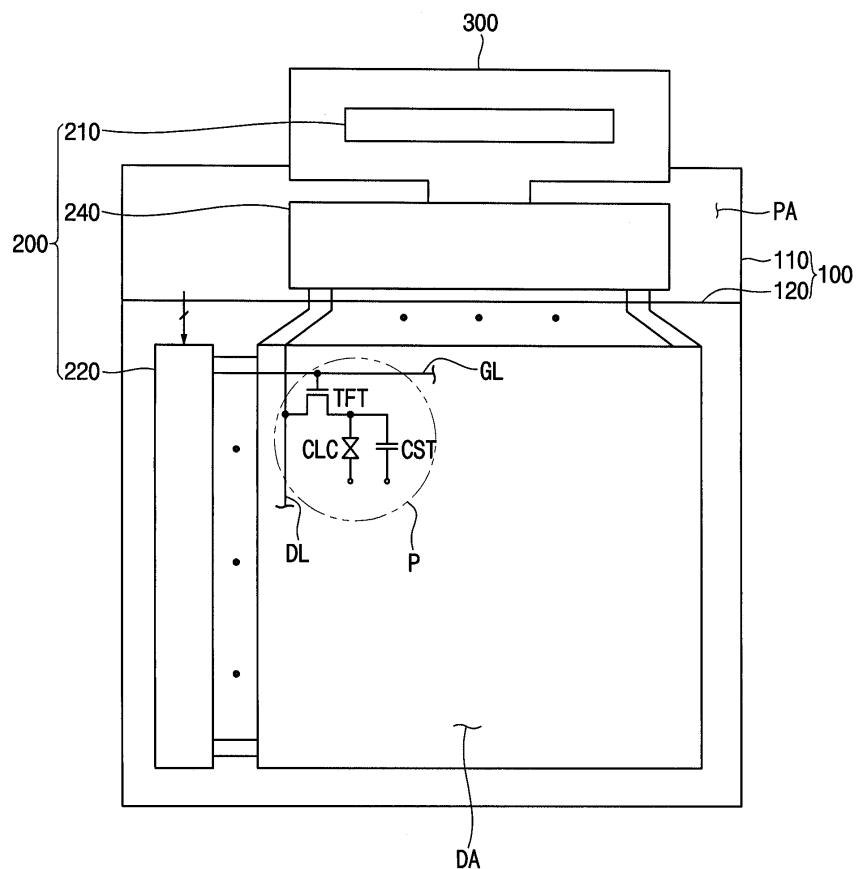

도 1은 본 발명의 실시예에 따른 액정표시장치의 개략적인 평면도이다.

도 2는 도 1에 도시된 메인 구동부에 대한 상세한 블록도이다.

도 1 및 도 2를 참조하면, 상기 액정표시장치는 액정표시패널(100), 구동 장치(200) 및 상기 구동 장치(200)의 메인 구동부(210)가 실장된 연성인쇄회로기판(300)을 포함한다.

상기 액정표시패널(100)은 하부기판(110)과 상부기판(120) 및 상기 하부 및 상부기판(110, 120) 사이에 개재된 액정층(미도시)을 포함하고, 표시 영역(DA)과 상기 표시 영역(DA)을 둘러싸는 주변 영역(PA)으로 이루어진다.

상기 표시 영역(DA)에는 복수의 소스 배선들(DL)과 상기 소스 배선들(DL)과 교차하는 복수의 게이트 배선들(GL)이 형성된다. 상기 소스 배선들(DL)과 게이트 배선들(GL)에 의해 복수의 화소부들(P)이 정의되고, 각각의 화소부(P)에는 스위칭 소자(TFT)와 상기 스위칭 소자(TFT)에 전기적으로 연결된 액정 캐패시터(CLC) 및 스토리지 캐패시터(CST)가 형성된다.

상기 구동 장치(200)는 메인 구동부(210), 게이트 회로부(220) 및 소스 회로부(230)를 포함한다.

상기 메인 구동부(210)는 상기 연성인쇄회로기판(300)에 실장된 단일 칩이며, 외부장치로부터 전달된 제어신호들 및 데이터신호들을 이용하여 상기 화소부들(P)을 구동시키는 구동신호들을 출력한다.

상기 메인 구동부(210)는 상기 게이트 회로부(220) 및 소스 회로부(230)의 구동을 제어하는 제어신호들을 출력한다. 또한, 외부로부터 입력된 데이터신호를 상기 소스 회로부(230)에 제공한다.

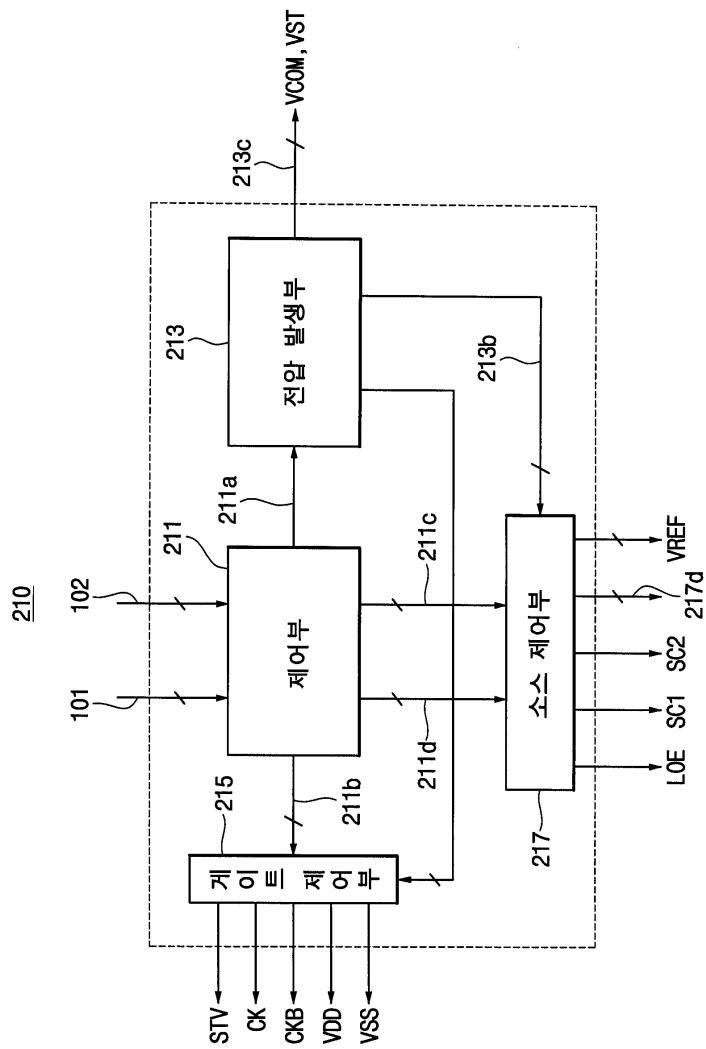

구체적으로 상기 메인 구동부(210)는 제어부(211), 전압 발생부(213), 게이트 제어부(215) 및 소스 제어부(217)를 포함한다.

상기 제어부(211)는 외부 장치로부터 입력된 제어신호(101)에 기초하여 제1 내지 제3 제어신호들(211a, 211b, 211c)을 생성하여 출력한다.

상기 제1 제어신호(211a)는 상기 전압 발생부(213)에 제공되고, 상기 제2 제어신호(211b)는 상기 게이트 제어부(215)에 제공되며, 상기 제3 제어신호(211c)는 상기 소스 제어부(217)에 제공되어, 각각의 구동을 제어한다.

상기 제어신호(101)는 수평 및 수직동기신호(HSYNC, VSYNC), 메인클럭신호(MCK) 및 데이터인에이블신호(DE)를 포함하고, 상기 제1 제어신호(211a)는 메인클럭신호(MCK)를 포함하며, 상기 제2 제어신호(211b)는 수직개시신호(STV), 제1 클럭신호(CK) 및 제2 클럭신호(CKB)를 포함한다. 상기 제3 제어신호(211c)는 수평시작신호(STH), 래치신호(LOE), 제1 선택제어신호(SC1), 제2 선택제어신호(SC2), 로드신호(TP) 및 반전신호(REV)를 포함한다.

상기 제어부(211)는 상기 외부 장치로부터 입력된 데이터신호(102)를 상기 소스 제어부(217)에 전달한다(211d).

상기 전압 발생부(213)는 상기 액정표시장치를 구동하기 위한 구동전압들을 발생한다. 구체적으로, 상기 게이트 제어부(215)에 제공되는 제1 구동전압들(213a)과, 상기 소스 구동부(217)에 제공되는 제2 구동전압들(213b) 및 상기 액정표시 패널(100)에 제공되는 제3 구동전압들(213c)을 포함한다.

상기 제1 구동전압들(213a)은 상기 게이트 회로부(220)에 제공되는 신호로서, 게이트 신호를 생성하기 위한 게이트 온 및 오프 전압(VDD, VSS)을 포함한다.

상기 제2 구동전압들(213b)은 상기 소스 회로부(240)에 제공되는 신호로서, 아날로그 구동전압(AVDD), 디지털 구동전압(DVDD), 기준감마전압들(VREF)을 포함한다. 상기 제3 구동전압들(213c)은 상기 액정 및 스토리지 캐패시터(CLC, CST)에 제공되는 공통전압들(VCOM, VST)을 포함한다.

상기 게이트 회로부(220)는 상기 주변 영역(PA)에 접적되거나, 실장된다. 상기 게이트 회로부(220)는 상기 메인 구동부(210)로부터 제공된 상기 제2 제어신호(211b) 및 상기 제1 구동전압들(213a)을 이용하여 게이트 신호들을 생성하고, 상기 액정표시 패널(100)의 표시 영역(DA)에 형성된 게이트 배선들에 출력한다.

여기서 상기 게이트 회로부(220)는 상호 종속적으로 연결된 복수의 스테이지드로 이루어진 하나의 쉬프트 레지스터를 예시하고 있다.

상기 소스 회로부(230)는 상기 표시 영역(DA)에 형성된 소스 배선들의 일단부에 해당하는 상기 주변 영역(PA)에 접적된다. 상기 소스 회로부(230)는 상기 메인 구동부(210)로부터 제공된 제3 제어신호(211c) 및 제2 구동전압들(213b)을 이용하여 상기 데이터신호(217d)를 아날로그 형태의 데이터전압들로 변환하여 상기 소소 배선들에 출력한다.

구체적으로, 상기 제3 제어신호(211c)는 래치신호(LOE), 제1 선택제어신호(SC1) 및 제2 선택제어신호(SC2)를 포함한다. 상기 래치 신호(LOE)가 상기 소스 회로부(230)에 입력되면, 입력된 데이터신호를 일정시간 래치하고, 상기 래치된 데이터신호를 상기 제1 선택제어신호(SC1)에 기초하여 제1 레벨로 쉬프팅 시키고, 상기 제2 선택제어신호(SC2)에 기초하여 상기 제1 레벨로 쉬프팅된 데이터신호를 제2 레벨로 쉬프팅시킨다.

여기서, 상기 데이터신호를 소정 레벨로 쉬프팅시키는 동작을 1H 구간 중 데이터신호가 충전되지 않는 비충전 구간 동안에 수행된다. 상기 비충전 구간은 예컨대 이후 설명되는 베퍼의 구동 편차(Vth)를 보상하는 보상 구간이다.

이후, 상기 소스 회로부(230)는 충전 구간 동안 상기 레벨 쉬프팅된 데이터신호를 아날로그 형태의 데이터전압으로 변환되어 해당하는 소스 배선으로 출력한다.

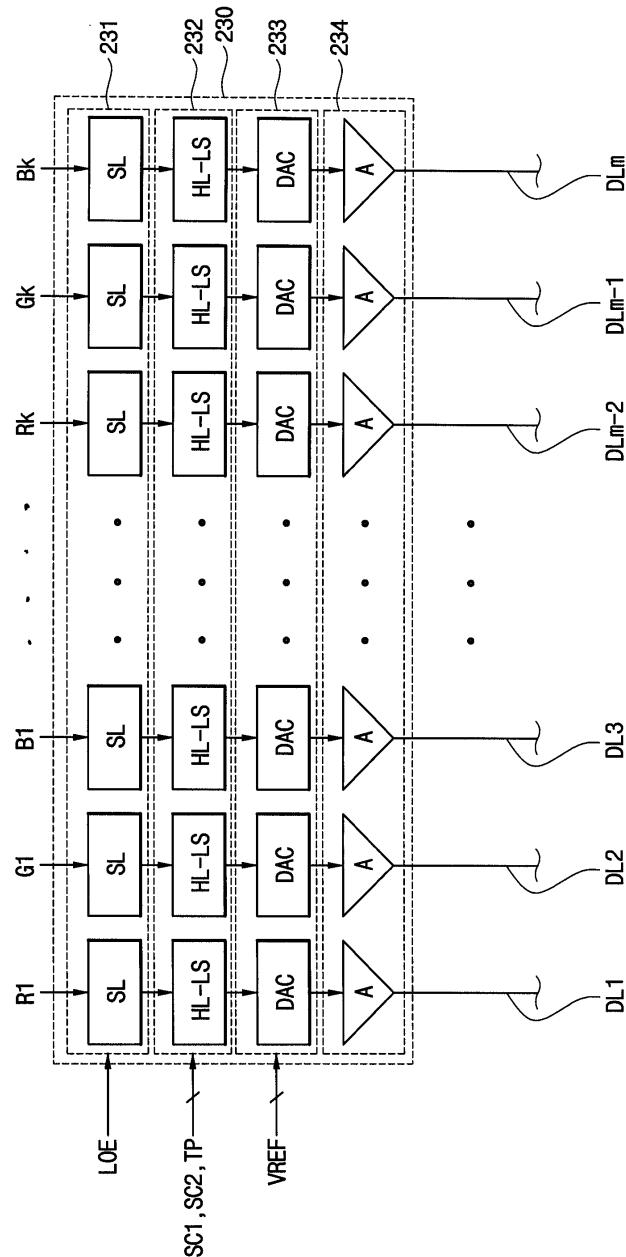

도 3은 도 1에 도시된 소스 회로부에 대한 상세한 블록도이다.

도 1 내지 도 3을 참조하면, 상기 소스 회로부(230)는 샘플링 래치부(231), 홀딩래치-레벨쉬프터부(이하, HL-LS부)(232), 디지털 아날로그 변환부(이하, DAC부)(233) 및 베퍼부(234)를 포함한다.

상기 샘플링 래치부(231)는 복수의 샘플링 래치들(SL)을 포함하고, 상기 소스 제어부(217)로부터 제공된 1H 구간에 대응하는 제1 데이터신호들(R1, G1, B1, ..., Rk, Gk, Bk)을 순차적으로 래치 시킨다. 상기 래치신호(LOE)에 기초하여 상기 샘플링 래치부(231)에 래치된 데이터신호들을 상기 HS-LS부(232)에 출력한다.

상기 HL-LS부(232)는 상기 래치신호(LOE)에 기초하여 입력되는 상기 제1 데이터신호들을 일정시간동안 래치 시킨다. 이후, 상기 소스 제어부(217)로부터 제공되는 제1 선택제어신호(SC1)에 기초하여 상기 래치된 데이터신호들을 제1 레벨로 쉬프팅시킨다. 이어, 상기 제2 선택제어신호(SC2)에 기초하여 상기 제1 레벨로 쉬프팅된 데이터신호들을 제2 레벨로 쉬프팅시킨다.

상기 소스 제어부(217)는 1H 구간 중 상기 베퍼부(234)의 구동 편차를 보상하는 보상 구간 동안에 상기 HL-LS부(232)에 상기 제1 및 제2 선택제어신호(SC1, SC2)를 출력한다. 상기 베퍼부(234)는 트랜지스터들을 포함하며, 상기 보상구간은 상기 트랜지스터의 Vth를 보상하는 구간으로, 대략 1H 구간의 초기 40% 내지 50% 구간이다.

이에 의해, 상기 래치된 제1 데이터신호들은 제1 레벨 내지 제2 레벨 범위 내의 레벨로 쉬프팅된 제2 데이터신호로 처리한다. 여기서, 상기 제1 레벨 및 제2 레벨은 상기 액정표시패널(100)에 접적된 소스 구동부(230)의 구동 마진이 고려된 전위 레벨이다.

예컨대, 상기 소스 회로부, 즉, 샘플링 래치부(231)에 입력된 제1 데이터신호는 0V 내지 3V 범위의 데이터신호이고, HL-LS 부(232)에서 레벨 쉬프팅된 제2 데이터신호는 6V 내지 -3V 범위로 레벨 쉬프팅된 데이터신호이다.

상기 HL-LS 부(232)는 상기 소스 제어부(217)로부터 로드신호(TP)가 제공되면, 상기 제2 데이터신호들을 상기 DAC부(233)에 출력한다.

상기 DAC부(233)는 복수의 디지털-아날로그 변환기들(DAC)을 포함하며, 상기 HL-LS 부(232)로부터 로딩된 제2 데이터신호들을 상기 기준감마전압들(VREF)을 이용하여 아날로그 형태의 데이터전압들, 즉, 제3 데이터신호들로 변환하여 출력한다.

상기 버퍼부(524)는 복수의 버퍼들(A)을 포함하며, 상기 DAC부(233)로부터 출력된 데이터전압들을 소정 레벨로 증폭하여 액정표시패널(100)에 형성된 소스 배선들(DL1, DL2, ..DLm)에 출력한다.

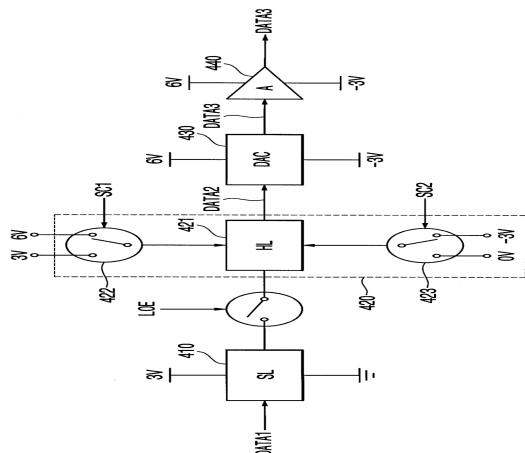

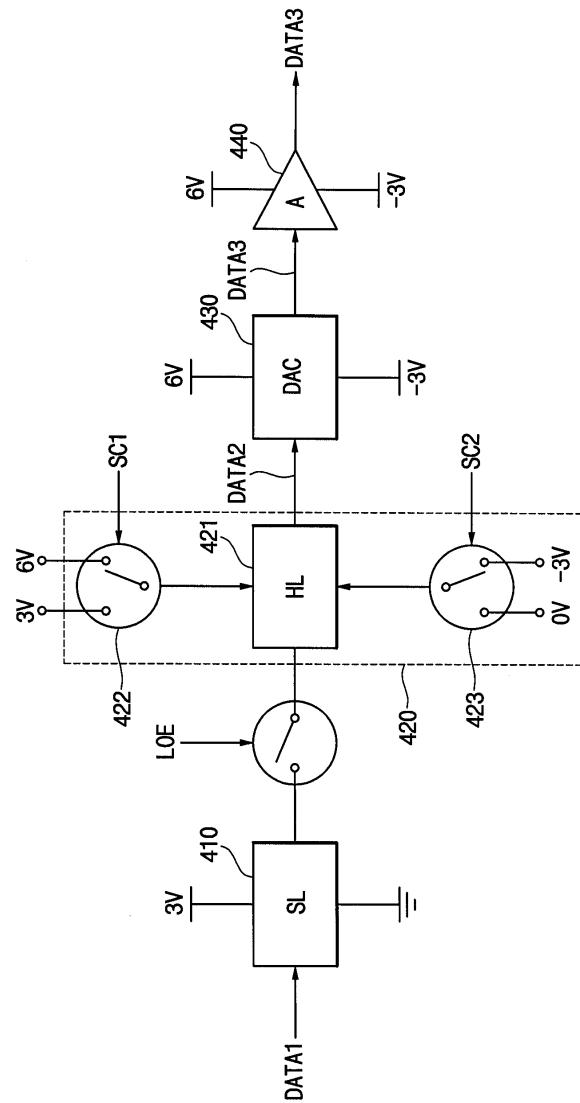

도 4는 도 1에 도시된 소스 회로부의 구동을 설명하기 위한 상세한 블록도이다.

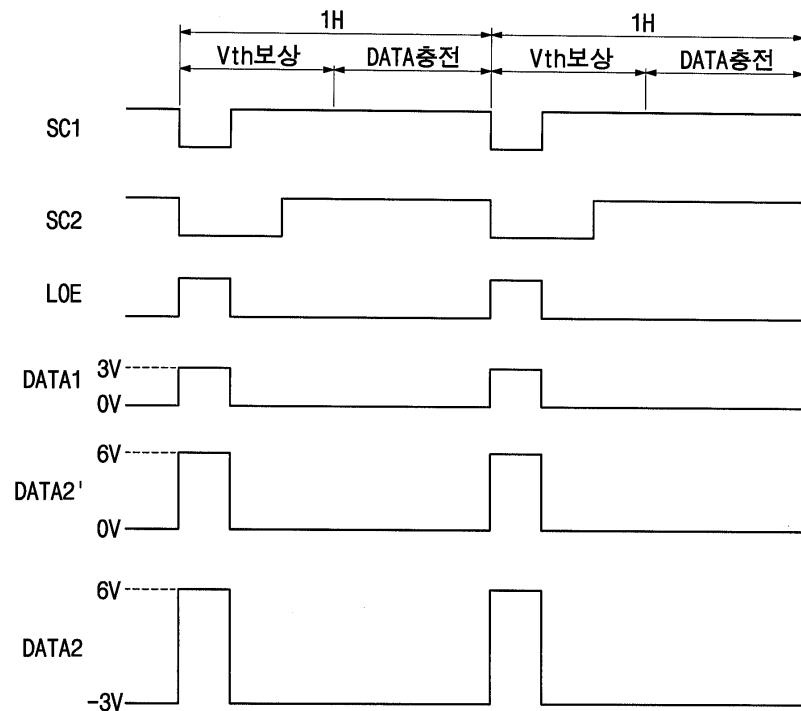

도 5는 도 4의 HL-LS부의 구동을 설명하기 위한 입출력신호의 타이밍도이다.

도 1 내지 도 5를 참조하면, 소스 회로부는 샘플링 래치(410), HL-LS(420), DAC(430) 및 버퍼(440)를 포함하며, 상기 HL-LS(420)는 훌딩 래치(421), 제1 스위치(422) 및 제2 스위치(423)를 포함한다.

상기 훌딩 래치(421)는 입력된 데이터신호를 일정시간동안 훌딩시키고, 상기 제1 스위치(422)는 제1 선택제어신호(SC1)에 기초하여 훌딩된 데이터신호를 제1 레벨로 쉬프팅 시키고, 상기 제2 스위치(423)는 제2 선택제어신호(SC2)에 기초하여 제1 레벨로 쉬프팅된 데이터신호를 제2 레벨로 쉬프팅 시킨다.

구체적으로, 입력된 제1 데이터신호(DATA1)는 샘플링 래치(410)에 래치된다. 이후, 래치 신호(LOE)가 입력되면, 상기 샘플링 래치(410)에 래치된 제1 데이터신호(DATA1)는 훌딩 래치(HL)(421)에 출력된다.

즉, 상기 래치 신호(LOE)가 하이 상태인 구간 동안 상기 훌딩 래치(421)는 상기 제1 데이터신호(DATA1)를 훌딩시킨다.

이때, 상기 제1 선택제어신호(SC1)가 하이 상태가 되면 상기 제1 스위치(422)는 상기 제1 레벨(예컨대, 6V)로 상기 제2 데이터신호(DATA2')를 레벨 쉬프팅시킨다. 이 후, 상기 제2 선택제어신호(SC2)가 하이 상태가 되면, 상기 제2 스위치(423)는 상기 제1 레벨로 쉬프팅된 제2 데이터신호(DATA')를 제2 레벨(예컨대, -3V)로 레벨 쉬프팅시켜 원하는 레벨의 제2 데이터신호(DATA2)를 생성한다.

상기 DAC(430)는 상기 HL-LS(420)로부터 출력된 제2 데이터신호(DATA2)를 아날로그 형태의 제3 데이터신호(DATA3)로 변환하여 출력한다. 상기 버퍼(440)는 상기 제3 데이터신호를 소스 배선(DL)에 출력한다.

이렇게 출력된 제3 데이터신호(DATA3)는 해당하는 게이트 배선이 활성화됨에 따라 액정 캐패시터(CLC)에 충전된다.

상기 제1 및 제2 선택제어신호(SC1, SC2)는 1H 구간 중 상기 버퍼(440)의 Vth 보상 구간 동안에 상기 제1 및 제2 스위치(422, 423)에 순차적으로 입력되며, 이에 따라서, 상기 훌딩된 제1 데이터신호(DATA1)의 상위 레벨은 제1 레벨로 쉬프팅되고, 하위 레벨은 제2 레벨로 쉬프팅된다.

따라서, 1H 구간 중 실질적으로 데이터신호가 충전되는 충전 구간을 충분히 확보하면서, Vth 보상 구간동안 레벨 쉬프팅된다.

또한, 하드웨어적으로는 별도의 레벨 쉬프터를 구현하지 않고 간단하게 소스 회로를 구현할 수 있다. 따라서, 액정표시패널 상에 소스 회로가 접적되는 면적을 줄일 수 있다.

## 발명의 효과

이상에서 설명한 바와 같이, 본 발명에 따르면 1H 구간 중 실질적으로 데이터가 충전되는 시간 이외의 시간을 활용하여 데이터신호를 소정의 원하는 레벨로 쉬프팅 시킴으로써 데이터 충전시간을 충분히 확보할 수 있다.

또한, 별도의 레벨 쉬프터를 구현하기 않고, 간단한 스위치 회로를 이용하여 레벨 쉬프팅을 수행함으로써 소스 회로를 간단하게 구현할 수 있다. 상기 소스 회로의 간단화함으로써 액정표시패널 상에 집적되는 회로 면적을 줄일 수 있다.

이상에서는 실시예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

## 도면의 간단한 설명

도 1은 본 발명의 실시예에 따른 액정표시장치의 개략적인 평면도이다.

도 2는 도 1에 도시된 메인 구동부에 대한 상세한 블록도이다.

도 3은 도 1에 도시된 소스 회로부에 대한 상세한 블록도이다.

도 4는 도 1에 도시된 소스 회로부의 구동을 설명하기 위한 상세한 블록도이다.

도 5는 도 4의 HL-LS부의 구동을 설명하기 위한 입출력신호의 타이밍도이다.

<도면의 주요부분에 대한 부호의 설명>

100 : 액정표시패널 200 : 구동 장치

210 : 메인 구동부 220 : 게이트 회로부

240 : 소스 회로부 300 : 연성인쇄회로기판

211 : 제어부 213 : 전압 발생부

231 : 샘플링 래치부 232 : 홀딩 래치-레벨쉬프터부

233 : 디지털아날로그변환부 234 : 버퍼부

421 : 홀딩 래치 422 : 제1 스위치

423 : 제2 스위치

도면

도면1

도면2

도면3

## 도면4

## 도면5

|                |                                                                      |         |            |

|----------------|----------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 源电路和具有该电路的液晶显示装置                                                     |         |            |

| 公开(公告)号        | KR1020070009295A                                                     | 公开(公告)日 | 2007-01-18 |

| 申请号            | KR1020050064446                                                      | 申请日     | 2005-07-15 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                             |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                             |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                                             |         |            |

| [标]发明人         | JOO SOONG YONG<br>주승용<br>PARK KEE CHAN<br>박기찬<br>LEE DONG YUB<br>이동엽 |         |            |

| 发明人            | 주승용<br>박기찬<br>이동엽                                                    |         |            |

| IPC分类号         | G09G3/36                                                             |         |            |

| CPC分类号         | G09G3/3688 G09G2300/0828 G09G2300/0871 G09G2310/0291                 |         |            |

| 代理人(译)         | PARK , YOUNG WOO                                                     |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                            |         |            |

## 摘要(译)

公开了用于简化电路实现的源电路，其具有足够的安全数据充电时间，并且包括该源电路的液晶显示器。源电路包括采样锁存器，保持锁存器，第一开关和第二开关，以及数字模拟转换器。输入采样锁存器的数据信号被采样。从保持锁存器输出的数据信号是采样锁存器被锁存预设时间。第一开关基于第一选择控制信号将锁存数据信号移位到第一电平。其中第二开关基于第二选择控制信号移位到第一电平的数据信号被移位到第二电平。数字模拟转换器被电平移位的数据信号被转换为模拟类型的数据电压并输出。因此，在通过将锁存数据信号移位到第一和第二电平来维持要补偿的部分的现有数据充电时间来补偿1H部分之间的驱动偏差的同时，可以简单地实现源电路。要补偿的Vth部分，源电路，电平shifter，保持锁存器。