(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2007-0110171

(43) 공개일자 2007년11월16일

(51) Int. Cl.

G02F 1/1343 (2006.01)

(21) 출원번호 10-2006-0043170

(22) 출원일자 2006년05월13일

### 심사청구일자      없음

(71) 출원인

삼성전자주식회사

경기도 수원시 영통구 매탄동 416

(72) 발명자

문현철

서울특별시 영등포구 당산동 삼성아파트 105동

903호

죽선아

## 부산광역시 금 (뒷)면에 계손)

(74) 대리의

제10장

저체 청구할 수 : 총 6 항

(54) 표시 기판 및 이를 포함하는 표시 장치

(57) 요약

잔상을 제거하여 표시 품질을 향상시킨 표시 기판 및 이를 포함하는 표시 장치가 개시된다. 표시 기판은 베이스 기판 상에 형성된 스위칭 소자를 포함하는 어레이층, 어레이층 상에 형성되는 복수의 서브 전극들 및 서브 전극들을 연결하는 연결부를 포함하고 스위칭 소자와 전기적으로 연결된 화소 전극 및 어레이층과 화소 전극 사이에 형성되고, 연결부에 대응하여 흄이 형성된 패시베이션층을 포함한다. 이에 따라, 액정 방향자의 제어력을 강화하여 순간잔상이 발생하는 것을 방지하고, 이로써 표시 품질을 향상시킬 수 있다.

대표도 - 도2

(72) 발명자

유재진

경기 용인시 기흥구 신갈동 새천년그린빌4단지

407동 1302호

도희옥

경기 수원시 팔달구 매교동 179-99 수연아트빌 30

2호

유혜란

인천광역시 서구 당하동 탑스빌아파트 115동 602호

## 특허청구의 범위

### 청구항 1

베이스 기판 상에 형성된 스위칭 소자를 포함하는 어레이층;

상기 어레이층 상에 형성되는 복수의 서브 전극들 및 상기 서브 전극들을 연결하는 연결부를 포함하고 상기 스위칭 소자와 전기적으로 연결된 화소 전극; 및

상기 어레이층과 상기 화소 전극 사이에 형성되고, 상기 연결부에 대응하여 홈이 형성된 패시베이션층을 포함하는 표시 기판.

### 청구항 2

제1항에 있어서, 상기 서브 전극들은 사각 형상의 라운딩된 에지(Rounded Edge)를 포함하는 것을 특징으로 하는 표시 기판.

### 청구항 3

제1항에 있어서, 상기 화소 전극은 제1 서브 전극과 제1 연결부를 통해 연결된 제2 서브 전극 및 상기 제2 서브 전극과 제2 연결부를 통해 연결된 제3 서브 전극을 포함하는 것을 특징으로 하는 표시 기판.

### 청구항 4

제3항에 있어서, 상기 패시베이션층은 상기 스위칭 소자와 상기 화소 전극을 전기적으로 연결하는 콘택홀을 포함하는 것을 특징으로 하는 표시 기판.

### 청구항 5

스위칭 소자를 포함하는 어레이층 상에 형성되고 서브 전극들 및 상기 서브 전극들을 연결하는 연결부를 포함하며 상기 스위칭 소자와 전기적으로 연결된 화소 전극과, 상기 어레이층 및 화소 전극 사이에 형성되고 상기 연결부에 대응하여 제1 홈이 형성된 패시베이션층을 포함하는 표시 기판;

상기 표시 기판에 대향하고, 차광 패턴 및 컬러필터들 상에 상기 화소 전극과 마주하여 형성된 공통 전극을 포함하는 대향기판; 및

상기 표시 기판 및 상기 대향기판 사이에 개재된 액정층을 포함하는 것을 특징으로 하는 표시 장치.

### 청구항 6

제5항에 있어서, 상기 공통 전극은 상기 서브 전극들과 대응하여 패터닝된 복수의 제2 홈들을 포함하고,

상기 제2 홈들 사이에 대응하는 표시 기판 상에 상기 제1 홈이 배치된 것을 특징으로 하는 표시 장치.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

<15> 본 발명은 표시 기판 및 이를 포함하는 표시 장치에 관한 것으로, 더욱 상세하게는 표시 품질을 향상시키기 위한 표시 기판 및 이를 포함하는 표시 장치에 관한 것이다.

<16> 일반적으로, 표시 장치는 디스플레이 유닛, 상기 디스플레이 유닛에 광을 공급하기 위한 백라이트 어셈블리 및 상기 디스플레이 유닛과 백라이트 어셈블리를 수납하기 위한 수납용기를 포함한다.

<17> 상기 디스플레이 유닛은 표시 패널을 포함하고, 상기 표시 패널은 스위칭 소자 및 상기 스위칭 소자와 전기적으로 연결되는 화소 전극을 포함하는 어레이 기판, 상기 어레이 기판과 대향하여 상기 화소 전극과 마주하는 공통 전극을 포함하는 컬러필터 기판 및 상기 어레이 기판과 컬러필터 기판 사이에 개재되어 형성되는 액정층을 포함

한다. 상기 표시 패널은 상기 액정층에 전압을 인가하여 광의 투과율을 제어하는 방식으로 화상을 표시한다.

<18> 상기 표시 패널은 상기 어레이 기판 및 컬러필터 기판 사이에 전압이 인가되지 않을 경우, 수직 방향으로 배열되어 블랙을 표시하는 VA모드와, 상기 VA모드의 시야각을 개선하기 위해 화소 전극 및 공통 전극을 패터닝하여 화소 내에 다중 도메인을 정의하는 PVA모드가 개발되고 있다.

<19> 최근, 소형 표시 패널 뿐만 아니라 중소형 표시 패널에서도 광시야각과 높은 대비비 및 빠른 응답 속도를 구현할 수 있는 적합한 구조에 대한 개발이 진행 중에 있다.

### **발명이 이루고자 하는 기술적 과제**

<20> 이에, 본 발명의 기술적 과제는 이러한 점에서 착안된 것으로 본 발명의 목적은 표시 품질을 향상시킨 표시 기판을 제공하는 것이다.

<21> 본 발명의 다른 목적은 이를 포함하는 표시 장치를 제공하는 것이다.

### **발명의 구성 및 작용**

<22> 상기한 본 발명의 목적을 실현하기 위한 실시예에 따른 표시 기판은 베이스 기판 상에 형성된 스위칭 소자를 포함하는 어레이층, 상기 어레이층 상에 형성되는 복수의 서브 전극들 및 상기 서브 전극들을 연결하는 연결부를 포함하고 상기 스위칭 소자와 전기적으로 연결된 화소 전극 및 상기 어레이층과 상기 화소 전극 사이에 형성되고, 상기 연결부에 대응하여 홈이 형성된 패시베이션층을 포함한다.

<23> 상기 본 발명의 다른 목적을 실현하기 위한 실시예에 따른 표시 장치는 스위칭 소자를 포함하는 어레이층 상에 형성되고 서브 전극들 및 상기 서브 전극들을 연결하는 연결부를 포함하며 상기 스위칭 소자와 전기적으로 연결된 화소 전극과, 상기 어레이층 및 화소 전극 사이에 형성되고 상기 연결부에 대응하여 제1 홈이 형성된 패시베이션층을 포함하는 표시 기판, 상기 표시 기판에 대향하고, 차광 패턴 및 컬러필터를 상에 상기 화소 전극과 마주하여 형성된 공통 전극을 포함하는 대향기판 및 상기 표시 기판 및 상기 대향기판 사이에 개재된 액정층을 포함한다.

<24> 이러한 표시 기판 및 이를 포함하는 표시 장치에 따르면, 상기 제1 홈을 포함하는 패시베이션층 상에 형성된 화소 전극 및 상기 제2 홈을 포함하는 공통 전극 사이에 형성된 액정층의 액정 방향자의 제어력을 강화하여 잔상이 발생하는 것을 방지하고, 이로써 표시 품질을 향상시킬 수 있다.

<25> 이하, 첨부한 도면들을 참조하여, 본 발명의 바람직한 실시예를 보다 상세하게 설명하고자 한다.

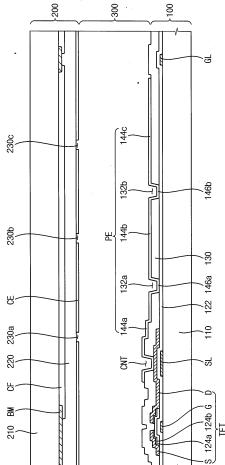

<26> 도 1은 본 발명의 실시예에 따른 표시 패널의 평면도이다.

<27> 도 2는 도 1의 I-I' 라인을 따라 절단한 단면도이다.

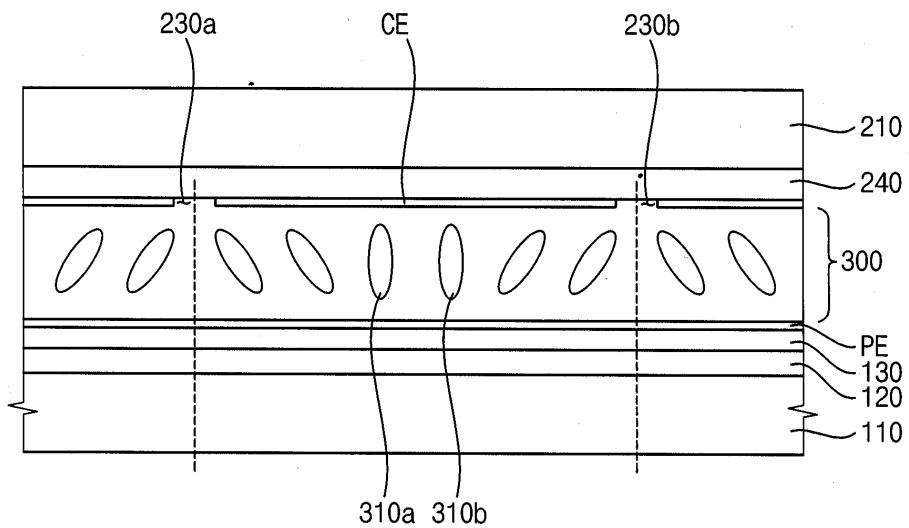

<28> 표시 패널(500)은 어레이 기판(100), 어레이 기판(100)과 대향하는 컬러필터 기판(200) 및 어레이 기판(100)과 컬러필터 기판(200) 사이에 개재되어 형성되는 액정층(300)을 포함한다. 어레이 기판(100)은 제1 베이스 기판(110) 상에 어레이층(120), 패시베이션층(130) 및 화소 전극(PE)을 포함한다.

<29> 어레이층(120)은 일 방향으로 형성된 게이트 배선(GL), 게이트 배선(GL)과 동일층으로 형성된 스토리지 배선(SL), 게이트 배선(GL)과 스토리지 배선(SL) 상에 형성된 게이트 절연층(122), 상기 일 방향과 수직한 다른 방향으로 형성된 소스 배선(DL) 및 스위칭 소자(TFT)를 포함한다. 게이트 배선(GL) 및 소스 배선(DL)이 교차하여 화소 영역(P)을 정의한다.

<30> 스위칭 소자(TFT)는 게이트 배선(GL)과 연결된 게이트 전극(G), 게이트 전극(G) 상에 형성된 반도체층(124a) 및 오믹 콘택층(124b), 소스 배선(DL)과 연결된 소스 전극(S) 및 소스 전극(S)과 이격된 드레인 전극(D)을 포함한다. 스토리지 배선(SL) 및 스토리지 배선(SL)과 중첩되는 드레인 전극(D)의 일단부는 캐페시터를 정의한다.

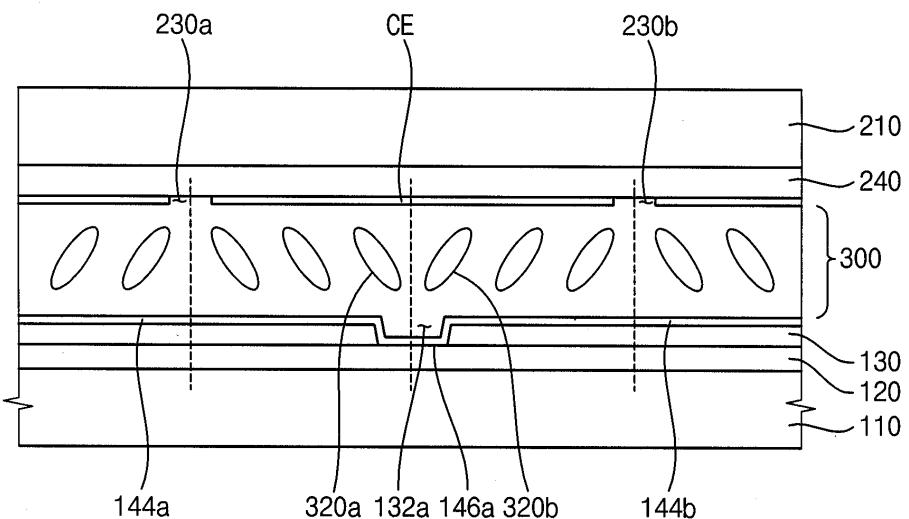

<31> 패시베이션층(130)은 어레이층(120) 상에 형성되고, 제1 홈들(132a, 132b) 및 콘택홀(CNT)을 포함한다. 콘택홀(CNT)은 스위칭 소자(TFT)의 드레인 전극(D)의 일단부 상의 패시베이션층(130)이 제거되어 상기 드레인 전극(D)의 일단부를 노출시킨다. 제1 홈들(132a, 132b)은 콘택홀(CNT)을 형성하는 마스크의 디자인을 변경하여 상기 마스크를 이용하여 콘택홀(CNT)을 형성함과 동시에 화소 영역(P)에 형성한다.

<32> 화소 영역(P)에는 게이트 절연층(122)과 패시베이션층(130)이 순차적으로 적층된 구조를 가지므로, 제1 홈들(132a, 132b)은 패시베이션층(130)의 일부 영역이 제거되어 게이트 절연층(122)을 노출시키거나, 패시베이션층

(130)의 일부 영역이 소정 두께 제거되어 형성된다. 이와 달리, 패시베이션층(130)상에 유기층이 더 형성된 경우에는 상기 유기층의 일부를 제거하여 상기 제1 홈들을 형성하며, 상기 제1 홈들 상에 화소 전극(PE)을 형성할 수 있다.

<33> 제1 홈들(132a, 132b)은 공통 전극(CE)이 패터닝되어 형성되는 제2 홈들(230a, 230b, 230c) 사이에 대응하는 어레이 기판(100)에 형성된다. 일 제2 홈(230a)과 다른 제2 홈(230b) 사이에 대응하는 영역에 일 제1 홈(132a)이 형성되고, 상기 다른 제2 홈(230b) 및 또 다른 제2 홈(230c) 사이에 대응하는 영역에 다른 제1 홈(132b)이 형성된다.

<34> 본 발명의 실시예에서는 표시 패널(500)이 3개의 제2 홈들(230a, 230b, 230c) 및 2개의 제1 홈들(132a, 132b)을 포함하지만, 이와 달리, n개의 제2 홈들 및 n-1개의 제1 홈들을 포함하는 표시 패널을 제작할 수 있다.

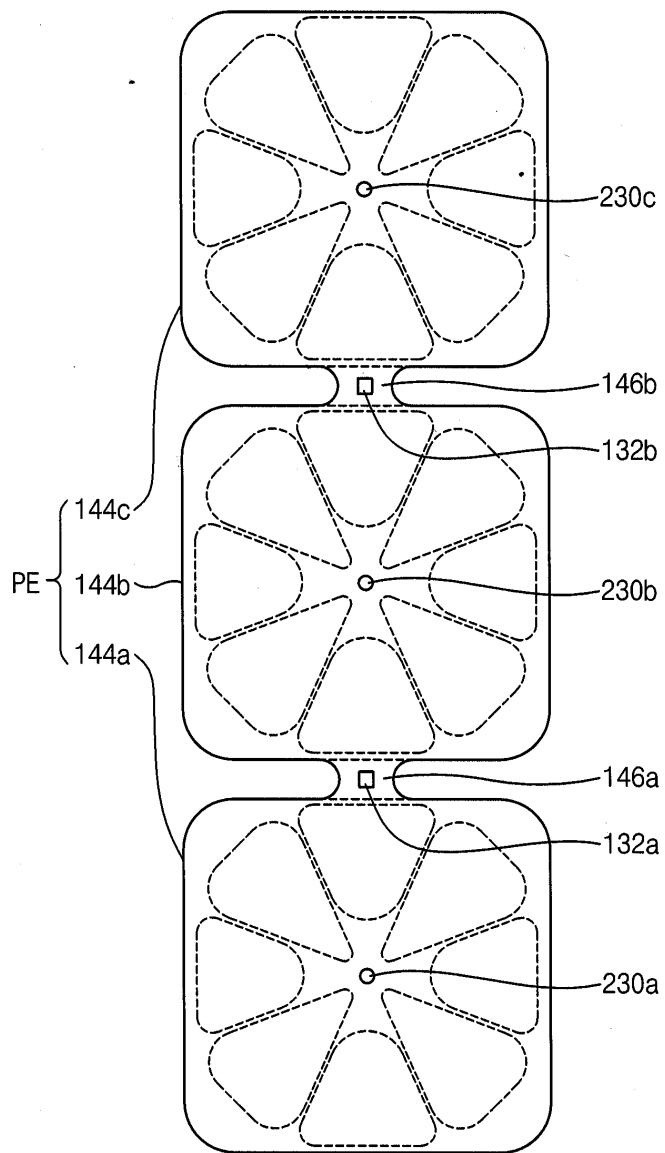

<35> 화소 전극(PE)은 제1 서브 전극(144a), 제2 서브 전극(144b), 제3 서브 전극(144c), 제1 연결부(146a) 및 제2 연결부(146b)를 포함한다. 제1 서브 전극(144a)은 콘택홀(CNT)을 통해 드레인 전극(D)의 일단과 접촉하여 화소 전극(PE)과 스위칭 소자(TFT)를 전기적으로 연결한다.

<36> 연결부(146a, 146b)들은 제1 홈(132a, 132b)들의 상부에 형성된다. 제1 연결부(146a)는 상기 일 제1 홈(132a) 상에 형성되고, 제2 연결부(146b)는 상기 다른 제1 홈(132b) 상에 형성된다.

<37> 제2 서브 전극(144b)은 제1 연결부(146a)를 통해 제1 서브 전극(144a)과 연결된다. 제3 서브 전극(144c)은 제2 연결부(146b)를 통해 제2 서브 전극(144b)과 연결된다. 바람직하게 제1 연결부(146a) 및 제2 연결부(146b)는 일직선 상에 배치되고, 제2 연결부(146b)는 제2 서브 전극(144b)을 기준으로 제1 연결부(146a)가 형성된 영역의 반대 방향에 형성된다.

<38> 제1, 제2 및 제3 서브 전극(144a, 144b, 144c)의 면적의 합은 화소 영역(P)의 면적과 유사한 값을 갖는 것이 바람직하다. 이에 따라, 제1, 제2 및 제3 서브 전극(144a, 144b, 144c)은 예를 들어, 사각형으로 형성되거나, 상기 사각형의 에지가 라운딩된(Rounded Edge) 형상으로 형성된다.

<39> 화소 전극(PE)은 투명한 도전성 물질을 패시베이션층(130) 상에 증착시킨 후, 상기 투명한 도전성 물질을 패터닝하여 형성한다. 상기 투명한 도전성 물질은 예를 들어, 산화 주석 인듐(Indium Tin Oxide, ITO), 산화 아연 인듐(Indium Zinc Oxide, IZO) 및 아몰퍼스 산화 주석 인듐(amorphous Indium Tin Oxide, a-ITO) 등으로 형성된다.

<40> 컬러필터 기판(200)은 어레이 기판(100)과 대향하는 제2 베이스 기판(210) 상에 형성된 차광 패턴(BM), 컬러필터(CF)들, 오버 코팅층(220) 및 공통 전극(CE)을 포함한다.

<41> 차광 패턴(BM)은 어레이 기판(100)의 화소 전극(PE)이 통제하지 못하는 영역의 액정층(300)을 통과해 나오는 빛을 차단한다. 차광 패턴(BM)은 어레이 기판(100)의 게이트 배선(GL) 및 소스 배선(DL)과 대응하여 형성되어 화소 영역(P)들에 대응하는 개구부들을 포함한다.

<42> 컬러필터(CF)들은 상기 개구부들에 형성되고, 백색광에 포함된 각각의 색을 출사시키는 레드(RED) 컬러필터(CF), 그린(Green) 컬러필터(CF) 및 블루(Blue) 컬러필터(CF)를 포함한다. 상기 레드, 그린 및 블루 컬러필터(CF)들이 상기 개구부들에 반복적으로 배치되어 되고, 컬러필터(CF)들의 투과율을 조절하면 밝기가 각각 다른 레드, 그린, 블루의 조합으로 다양한 종류의 색을 표현할 수 있다.

<43> 차광 패턴(BM) 및 컬러필터(CF)들 상에는 오버 코팅층(220)이 형성되고, 오버 코팅층(220) 상에는 공통 전극(CE)이 형성된다. 공통 전극(CE)은 화소 전극(PE)과 같이 투명한 도전성 물질로 형성된다.

<44> 공통 전극(CE)은 복수의 제2 홈들(230a, 230b, 230c)을 포함한다. 공통 전극(CE)은 오버 코팅층(220) 상에 투명한 도전성 물질을 증착시키고, 상기 투명한 도전성 물질을 패터닝하여 형성한다.

<45> 액정층(300)은 초기에는 수직으로 분포하며 전압이 인가되면 전기장 방향에 수직하게 배열되는 음의 유전율이 방성을 갖는 액정 분자들을 포함한다. 액정층(300)은 전기장이 인가되지 않았을 때, 편광자를 수직으로 놓아 블랙 상태를 만드는 수직 배향(vertical alignment; VA) 모드이다.

<46> 액정층(300)의 액정 분자들의 배향 상태에 대해서는 도 3, 도 4a 및 도 4b를 참조하여 이하 상세히 후술하도록 한다.

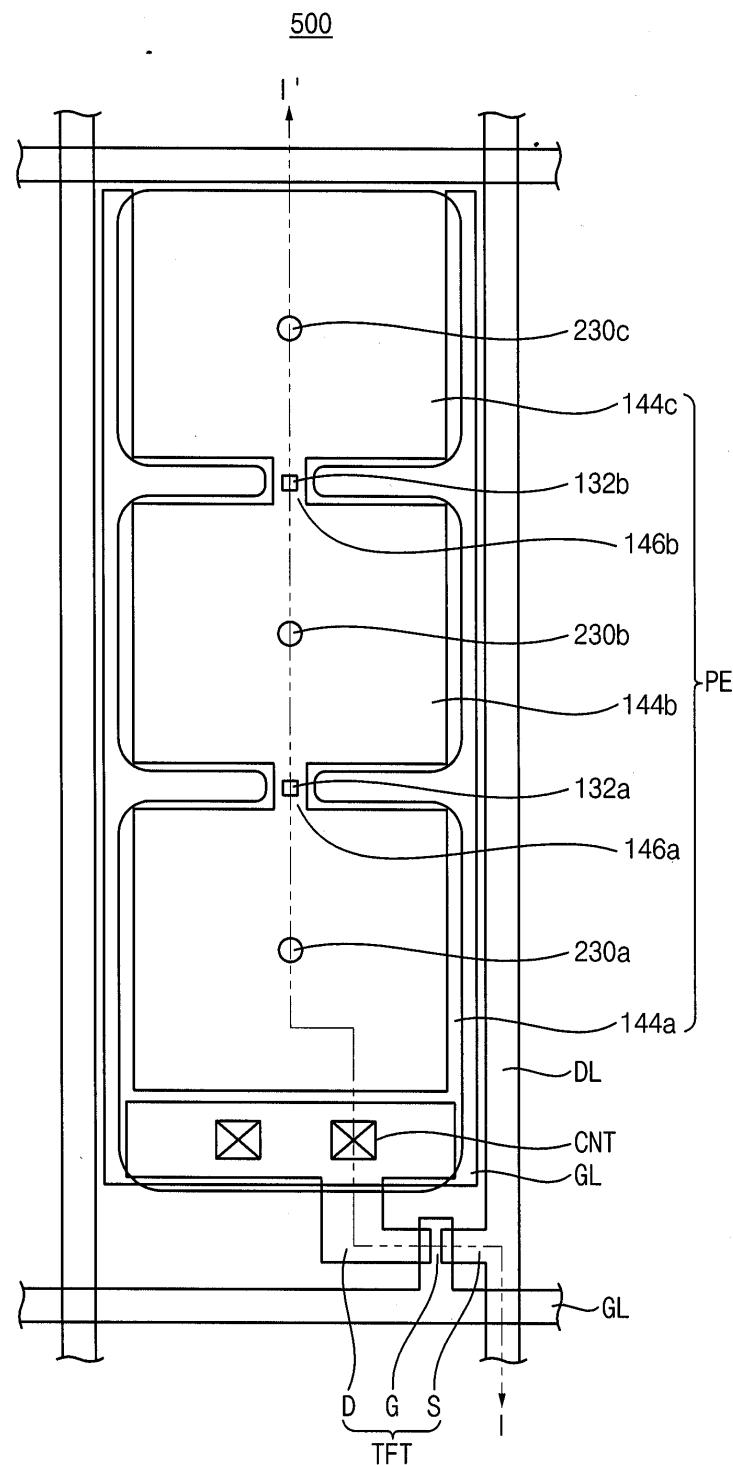

<47> 도 3은 도 2의 액정층 내에 형성된 다중 영역을 나타내는 평면도이다. 도 4a 및 도 4b는 제1 홈의 유무에 따른

액정층의 형상을 나타낸 개념도이다.

- <48> 도 3을 참조하면, 어레이 기판은 제1 홈들(132a, 132b)을 포함하는 패시베이션층(130), 제1 서브 전극(144a), 제2 서브 전극(144b) 및 제3 서브 전극(144c)을 포함하는 화소 전극(PE)을 포함한다. 컬러필터 기판은 제2 홈들(230a, 230b, 230c)을 포함하는 공통 전극(CE)을 포함한다.

- <49> 화소 전극(PE) 및 공통 전극(CE) 사이에 전기장이 인가되는 경우에, 액정층(300) 내의 액정 분자들은 제2 홈들(230a, 230b)을 중심으로 다중 영역이 형성되고, 상기 다중 영역에 의해 상기 액정 분자들이 다중 배향된다.

- <50> 상기 다중 영역을 형성함은, 화소 영역(P) 내에 작은 영역들을 서로 방향이 다르게 배치함으로써 상호 영역간 시야각 특성을 보상하도록 하여 화소(Pixel) 전체로는 넓은 시야각 특성을 얻도록 하기 위해서이다.

- <51> 상기 다중 영역은 화소 전극(PE) 및 공통 전극(CE) 사이에 인가된 전기장의 왜곡이 발생하는 복수의 영역을 포함한다. 상기 다중 영역은 일 제2 홈(230a)을 중심으로 제1 서브 전극(144a)과 대응되는 영역, 다른 제2 홈(230b)을 중심으로 제2 서브 전극(144b)과 대응되는 영역 및 또 다른 제2 홈(230c)을 중심으로 제3 서브 전극(144c)과 대응되는 영역을 포함한다.

- <52> 화소 전극(PE)이 제1 홈들(132a, 132b)을 포함한 패시베이션층(130) 상에 형성됨으로써, 상기 전기장이 왜곡되는 효과를 갖고 이에 의해 다중 배향된 액정 방향자(Director)의 제어력을 강화할 수 있다.

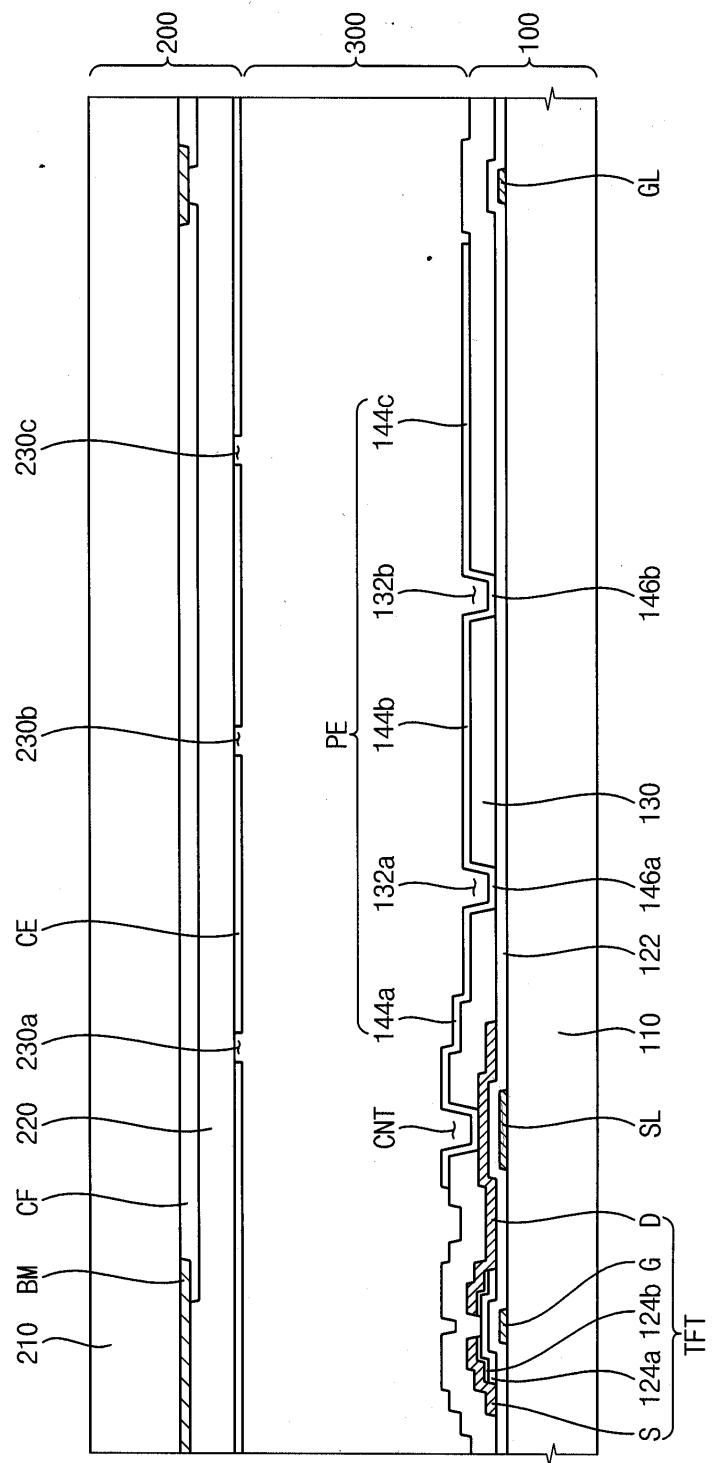

- <53> 도 4a 및 도 4b는 어레이 기판의 화소 전극과 컬러필터 기판의 공통 전극 사이에 전기장이 인가되었을 때의 전극 배치로 인한 전기장의 왜곡으로 다중 배향된 상태를 패시베이션층의 제1 홈의 유무에 따라 나타내었다.

- <54> 도 4a를 참조하면, 어레이 기판은 어레이층(120), 패시베이션층(130) 및 화소 전극(PE)이 순차적으로 제1 베이스 기판(110) 상에 형성된다.

- <55> 상기 어레이 기판과 마주하는 컬러필터 기판은 차광 패턴, 컬러필터들 및 상기 차광 패턴과 컬러필터들 상에 형성된 오버 코팅층을 포함하는 제1 층(240) 및 공통 전극(CE)이 순차적으로 제2 베이스 기판(210) 상에 형성된다. 공통 전극(CE)은 일 제2 홈(230b) 및 다른 제2 홈(230c)을 포함한다.

- <56> 상기 어레이 기판 및 상기 컬러필터 기판 사이에 액정층(300)이 형성되고 액정층(300)에는 머리부, 몸통부 및 꼬리부를 갖는 제1 액정분자(310a) 및 제2 액정분자(310b)를 포함하는 복수의 액정 분자들이 개재된다.

- <57> 상기 복수의 액정 분자들은 상기 어레이 기판의 화소 전극(PE)과 컬러필터 기판의 공통 전극(CE) 사이에 전기장이 인가되었을 때에, 상기 일 제2 홈(230b)을 중심으로 상기 다른 제2 홈(230b)을 향해서 머리부들이 모이고, 상기 복수의 액정 분자들의 꼬리부들이 상기 어레이 기판을 향해 하나의 원형을 이룬다. 제1 베이스 기판(110) 및 제2 베이스 기판(210)에 수직한 선을 기준으로 상기 액정 분자들은 소정의 선경사각을 갖도록 배향된다.

- <58> 상기 복수의 액정 분자들은 또 다른 제2 홈(230c)을 중심으로 상기 또 다른 제2 홈(230c)을 향해서 머리부들이 모이고, 상기 복수의 액정 분자들의 꼬리부들이 상기 어레이 기판을 향해 또 다른 원형을 이룬다.

- <59> 상기 복수의 액정 분자들의 꼬리부들이 형성하는 하나의 원형 및 또 다른 원형이 인접하는 부분의 액정 분자(310a, 310b)들은 제2 홈들(230b, 230c)들로부터 멀어짐에 따라 왜곡된 전기장의 영향을 받지 못하거나, 약한 전기장의 영향으로 다른 액정 분자들이 갖는 일정한 선경사각을 갖지 못하는 경우가 발생한다. 이와 같이 일정한 선경사각을 갖지 못하는 액정 분자들에 의해 순간 잔상이 발생하게 된다.

- <60> 도 4b를 참조하면, 어레이 기판에 제1 홈(132b)을 포함하는 패시베이션층(130)을 형성함으로써, 액정 방향자의 제어력을 강화하게 된다.

- <61> 구체적으로, 복수의 액정 분자들의 꼬리부들이 형성하는 하나의 원형 및 또 다른 원형이 인접하는 부분의 액정 분자(320a, 320b)들은 제2 홈들(230b, 230c)들로부터 멀어지더라도, 제2 홈들(230b, 230c) 사이에 대응되는 제1 홈(132b)에 의해 상기 액정 분자(320a, 320b)들은 선경사각을 갖게 된다.

- <62> 이상에서 상세하게 설명한 바에 의하면, 어레이 기판(100)의 제1 홈들(132a, 132b) 및 컬러필터 기판(200)의 제2 홈들(230a, 230b, 230c)에 의해 액정 방향자의 제어력을 강화하여 순간 잔상이 발생하는 것을 방지할 수 있다. 이로써 표시 패널의 표시 품질을 향상시킬 수 있다.

- <63> 제1 홈들(132a, 132b)이 형성된 패시베이션층(130)을 포함하는 어레이 기판(100)을 형성하는 공정에서는 콘택홀(CNT)을 형성하는 마스크의 디자인을 변경하고, 상기 마스크를 이용함으로써 원가의 상승 또는 공정의 복잡화와 같이 우려되는 문제들도 해결할 수 있다.

### 발명의 효과

- <64> 이와 같은 표시 기판 및 이를 포함하는 표시 패널에 따르면, 제1 홈들을 포함하는 패시베이션층, 상기 패시베이션층 상에 형성된 화소 전극 및 제2 홈들을 포함하는 공통 전극에 의해 액정 방향자의 제어력을 강화하여 순간 잔상이 발생하는 것을 방지하고, 이로써 표시 패널의 표시 품질을 향상시킬 수 있다.

- <65> 이상 실시예를 참조하여 설명하였지만, 해당 기술 분야의 숙련된 당업자는 하기의 특허 청구의 범위에 기재된 본 발명의 사상 및 영역으로부터 벗어나지 않는 범위 내에서 본 발명을 다양하게 수정 및 변경시킬 수 있음을 이해할 수 있을 것이다.

### 도면의 간단한 설명

- <1> 도 1은 본 발명의 실시예에 따른 표시 패널의 평면도이다.

<2> 도 2는 도 1의 I-I' 라인을 따라 절단한 단면도이다.

<3> 도 3은 도 2의 액정층 내에 형성된 다중 영역을 나타내는 평면도이다.

<4> 도 4a 및 도 4b는 제1 홈의 유무에 따른 액정층의 형상을 나타낸 개념도이다.

#### <도면의 주요 부분에 대한 부호의 설명

- |      |                                     |                 |

|------|-------------------------------------|-----------------|

| <6>  | 500 : 표시 패널                         | 100 : 어레이 기판    |

| <7>  | 110 : 제1 베이스 기판                     | 130 : 패시베이션층    |

| <8>  | 132a, 132b : 제1 홈                   | PE : 화소 전극      |

| <9>  | 144a, 144b, 144c : 제1, 제2, 제3 서브 전극 |                 |

| <10> | 146a, 146b : 제1, 제2 연결부             | CNT : 콘택홀       |

| <11> | 200 : 컬러필터 기판                       | 210 : 제2 베이스 기판 |

| <12> | 230a, 230b, 230c : 제2 홈             | CE : 공통 전극      |

| <13> | 300 : 액정층                           |                 |

| <14> | 310a, 310b, 320a, 320b : 액정분자       |                 |

## 도면

## 도면1

## 도면2

도면3

도면4a

도면4b

|                |                                                                                                                |         |            |

|----------------|----------------------------------------------------------------------------------------------------------------|---------|------------|

| 专利名称(译)        | 显示基板和包括其的显示装置                                                                                                  |         |            |

| 公开(公告)号        | KR1020070110171A                                                                                               | 公开(公告)日 | 2007-11-16 |

| 申请号            | KR1020060043170                                                                                                | 申请日     | 2006-05-13 |

| [标]申请(专利权)人(译) | 三星电子株式会社                                                                                                       |         |            |

| 申请(专利权)人(译)    | 三星电子有限公司                                                                                                       |         |            |

| 当前申请(专利权)人(译)  | 三星电子有限公司                                                                                                       |         |            |

| [标]发明人         | MOON HYUN CHEOL<br>문현철<br>CHO SEON AH<br>조선아<br>LYU JAE JIN<br>유재진<br>DO HEE WOOK<br>도희욱<br>YOU HYE RAN<br>유혜란 |         |            |

| 发明人            | 문현철<br>조선아<br>유재진<br>도희욱<br>유혜란                                                                                |         |            |

| IPC分类号         | G02F1/1343                                                                                                     |         |            |

| CPC分类号         | G02F1/134363 H01L21/28247 H01L27/124 H01L27/3248                                                               |         |            |

| 代理人(译)         | PARK , YOUNG WOO                                                                                               |         |            |

| 外部链接           | <a href="#">Espacenet</a>                                                                                      |         |            |

**摘要(译)**

公开了一种显示基板，其改善了显示质量，去除了余像，以及包括该显示基板的显示装置。显示基板包括阵列层，阵列层包括在基础基板上形成的开关元件，以及形成在阵列层上的多个子电极，开关元件，连接部分连接子电极，以及形成在两者之间的钝化层像素电极，电连接阵列层和像素电极，并对应于连接部分并开槽。因此，液晶指向矢的控制得到加强，并且可以防止产生余像。因此可以改善显示质量。域，PVA，钝化层，沟槽。